(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-134691

(P2007-134691A)

(43) 公開日 平成19年5月31日(2007.5.31)

| (51) Int.CI.                  | F 1        |         | テーマコード (参考) |

|-------------------------------|------------|---------|-------------|

| <b>H01L 21/3205 (2006.01)</b> | H01L 21/88 | A       | 5 F 0 3 3   |

| <b>H01L 23/52 (2006.01)</b>   | H01L 29/78 | 6 1 2 C | 5 F 1 1 O   |

| <b>H01L 29/786 (2006.01)</b>  | H01L 29/78 | 6 1 6 U |             |

|                               | H01L 29/78 | 6 1 7 L |             |

|                               | H01L 21/88 | B       |             |

審査請求 未請求 請求項の数 44 O L (全 47 頁)

|              |                              |          |                                                                                   |

|--------------|------------------------------|----------|-----------------------------------------------------------------------------------|

| (21) 出願番号    | 特願2006-276945 (P2006-276945) | (71) 出願人 | 390019839<br>三星電子株式会社<br>Samsung Electronics<br>Co., Ltd.<br>大韓民国京畿道水原市靈通区梅灘洞 416 |

| (22) 出願日     | 平成18年10月10日 (2006.10.10)     | (74) 代理人 | 110000408<br>特許業務法人高橋・林アンドパートナーズ                                                  |

| (31) 優先権主張番号 | 10-2005-0106274              | (72) 発明者 | 李 制 劍<br>大韓民国ソウル特別市陽川区木4洞 724<br>- 12 番地 デイルヴィラ 401号                              |

| (32) 優先日     | 平成17年11月8日 (2005.11.8)       | (72) 発明者 | 金 時 烈<br>大韓民国京畿道龍仁市上現洞 861 番地<br>マンヒョンマウル8団地斗山ウィーブアパ<br>ートメント806棟1601号            |

| (33) 優先権主張国  | 韓国 (KR)                      |          |                                                                                   |

最終頁に続く

(54) 【発明の名称】配線、これを含む薄膜トランジスタ基板、及びその製造方法

## (57) 【要約】

【課題】 配線、これを含む薄膜トランジスタ基板、及びその製造方法が開示される。

【解決手段】 本発明の一実施例による配線は、下部構造物上に形成されたバリア膜、前記バリア膜上に形成された銅又は銅合金を含む銅導電膜、前記銅導電膜上に形成された中間膜、及び前記中間膜上に形成されたキャッピング膜を含むか、又は下部構造物上に形成されたバリア膜、前記バリア膜上に形成された第1中間膜、前記第1中間膜上に形成された銅又は銅合金を含む銅導電膜、前記銅導電膜上に形成された第2中間膜、及び前記第2中間膜上に形成されたキャッピング膜を含む。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

下部構造物上に形成されたバリア膜と、

前記バリア膜上に形成された銅又は銅合金を含む銅導電膜と、

前記銅導電膜上に形成された中間膜と、

前記中間膜上に形成されたキャッピング膜と、

を含むことを特徴とする配線。

**【請求項 2】**

前記バリア膜は、Mo、MoN、又はMo合金を含むことを特徴とする請求項1記載の配線。 10

**【請求項 3】**

前記Mo合金は、MoW、MoTi、MoNb、MoZrのうち、少なくともいずれか1つを含むことを特徴とする請求項2記載の配線。

**【請求項 4】**

前記中間膜は、銅窒化物を含むことを特徴とする請求項1記載の配線。

**【請求項 5】**

前記中間膜は、銅酸化物を含むことを特徴とする請求項1記載の配線。

**【請求項 6】**

前記中間膜は、銅酸窒化物を含むことを特徴とする請求項1記載の配線。

**【請求項 7】**

前記キャッピング膜は、Mo、MoN、又はMo合金を含むことを特徴とする請求項1記載の配線。 20

**【請求項 8】**

前記Mo合金は、MoW、MoTi、MoNb、MoZrのうち、少なくともいずれか1つを含むことを特徴とする請求項7記載の配線。

**【請求項 9】**

前記下部構造物は、絶縁基板、半導体層、又は絶縁膜であることを特徴とする請求項1記載の配線。

**【請求項 10】**

下部構造物上に形成されたバリア膜と、

前記バリア膜上に形成された第1中間膜と、

前記第1中間膜上に形成された銅又は銅合金を含む銅導電膜と、

前記銅導電膜上に形成された第2中間膜と、

前記第2中間膜上に形成されたキャッピング膜と、

を含むことを特徴とする配線。 30

**【請求項 11】**

前記バリア膜は、Mo、MoN、又はMo合金を含むことを特徴とする請求項10記載の配線。

**【請求項 12】**

前記Mo合金は、MoW、MoTi、MoNb、MoZrのうち、少なくともいずれか1つを含むことを特徴とする請求項11記載の配線。 40

**【請求項 13】**

前記第1中間膜及び前記第2中間膜のうち、少なくとも1つは銅窒化物を含むことを特徴とする請求項10記載の配線。

**【請求項 14】**

前記第1中間膜及び前記第2中間膜のうち、少なくとも1つは銅酸化物を含むことを特徴とする請求項10記載の配線。

**【請求項 15】**

前記第1中間膜及び前記第2中間膜のうち、少なくとも1つは銅酸窒化物を含むことを特徴とする請求項10記載の配線。 50

**【請求項 1 6】**

前記キャッピング膜は、Mo、MoN、又はMo合金を含むことを特徴とする請求項10記載の配線。

**【請求項 1 7】**

前記Mo合金は、MoW、MoTi、MoNb、MoZrのうち、少なくともいずれか1つを含むことを特徴とする請求項16記載の配線。

**【請求項 1 8】**

前記下部構造物は、絶縁基板、半導体層、又は絶縁膜であることを特徴とする請求項10記載の配線。

**【請求項 1 9】**

下部構造物上にバリア膜を形成し、

前記バリア膜が形成されている下部構造物上に銅又は銅合金を含む銅導電膜を形成し、前記銅導電膜上に中間膜を形成し、

前記中間膜上にキャッピング膜を形成すること、

を特徴とする配線形成方法。

**【請求項 2 0】**

前記中間膜の形成は、窒素を含む雰囲気下で銅をターゲットとしてスパッタリングすることであることを特徴とする請求項19記載の配線形成方法。

**【請求項 2 1】**

前記中間膜の形成は、酸素を含む雰囲気下で銅をターゲットとしてスパッタリングすることであることを特徴とする請求項19記載の配線形成方法。

**【請求項 2 2】**

前記中間膜の形成は、酸素及び窒素を含む雰囲気下で銅をターゲットとしてスパッタリングすることであることを特徴とする請求項19記載の配線形成方法。

**【請求項 2 3】**

前記中間膜の形成は、真空破壊で形成されることを特徴とする請求項19記載の配線形成方法。

**【請求項 2 4】**

下部構造物上にバリア膜を形成し、

前記バリア膜上に第1中間膜を形成し、

前記第1中間膜上に銅又は銅合金を含む銅導電膜を形成し、

前記銅導電膜上に第2中間膜を形成し、

前記中間膜上にキャッピング膜を形成すること、

を特徴とする配線形成方法。

**【請求項 2 5】**

前記第1中間膜又は前記第2中間膜の形成は、窒素を含む雰囲気下で銅をターゲットとしてスパッタリングすることであることを特徴とする請求項24記載の配線形成方法。

**【請求項 2 6】**

前記第1中間膜又は前記第2中間膜の形成は、酸素を含む雰囲気下で銅をターゲットとしてスパッタリングすることであることを特徴とする請求項24記載の配線形成方法。

**【請求項 2 7】**

前記第1中間膜又は第2中間膜の形成は、酸素及び窒素を含む雰囲気下で銅をターゲットとしてスパッタリングすることであることを特徴とする請求項24記載の配線形成方法。

**【請求項 2 8】**

前記第2中間膜の形成は、真空破壊で形成されることを特徴とする請求項24記載の配線形成方法。

**【請求項 2 9】**

絶縁基板上に形成され第1方向に延びたゲート線及び前記ゲート線に接続されたゲート電極を含むゲート配線と、

10

20

30

40

50

前記絶縁基板上に前記ゲート配線と絶縁して形成され、前記ゲート線と交差するように第2方向に延びたデータ線、前記データ線に接続されたソース電極及び前記ソース電極と離隔して位置するドレイン電極を含むデータ配線と、

前記ゲート配線と前記データ配線上に各画素毎に形成され前記ドレイン電極と接続された画素電極と、を含むが、

前記ゲート配線及び／又は前記データ配線は、

下部構造物上に形成されたバリア膜と、

前記バリア膜上に形成された銅又は銅合金を含む銅導電膜と、

前記銅導電膜上に形成された銅窒化物を含む中間膜と、

前記中間膜上に形成されたキャッピング膜と、

を含むことを特徴とする薄膜トランジスタ基板。

10

#### 【請求項30】

前記バリア膜は、Mo、MoN、又はMo合金を含むことを特徴とする請求項29記載の薄膜トランジスタ基板。

#### 【請求項31】

前記Mo合金は、MoW、MoTi、MoNb、MoZrのうち、少なくともいずれか1つを含むことを特徴とする請求項30記載の薄膜トランジスタ基板。

#### 【請求項32】

前記中間膜は、銅窒化物を含むことを特徴とする請求項29記載の薄膜トランジスタ基板。

20

#### 【請求項33】

前記中間膜は、銅酸化物を含むことを特徴とする請求項29記載の薄膜トランジスタ基板。

#### 【請求項34】

前記中間膜は、銅酸窒化物を含むことを特徴とする請求項29記載の薄膜トランジスタ基板。

#### 【請求項35】

前記キャッピング膜は、Mo、MoN、又はMo合金を含むことを特徴とする請求項29記載の薄膜トランジスタ基板。

#### 【請求項36】

前記Mo合金は、MoW、MoTi、MoNb、MoZrのうち、少なくともいずれか1つを含むことを特徴とする請求項35記載の薄膜トランジスタ基板。

30

#### 【請求項37】

絶縁基板上に形成され第1方向に延びたゲート線及び前記ゲート線に接続されたゲート電極を含むゲート配線と、

前記絶縁基板上に前記ゲート配線と絶縁して形成され、前記ゲート線と交差するよう第2方向に延びたデータ線、前記データ線に連結されたソース電極及び前記ソース電極と離隔して位置するドレイン電極を含むデータ配線と、

前記ゲート配線と前記データ配線上に各画素毎に形成され前記ドレイン電極と接続された画素電極と、を含むが、

40

前記ゲート配線又は前記データ配線は、

下部構造物上に形成されたバリア膜と、

前記バリア膜上に形成された第1中間膜と、

前記第1中間膜上に形成された銅又は銅合金を含む銅導電膜と、

前記銅導電膜上に形成された第2中間膜と、

前記中間膜上に形成されたキャッピング膜と、

を含むことを特徴とする薄膜トランジスタ基板。

#### 【請求項38】

前記バリア膜は、Mo、MoN、又はMo合金を含むことを特徴とする請求項37記載の薄膜トランジスタ基板。

50

**【請求項 3 9】**

前記Mo合金は、MoW、MoTi、MoNb、MoZrのうち、少なくともいずれか1つを含むことを特徴とする請求項38記載の薄膜トランジスタ基板。

**【請求項 4 0】**

前記第1中間膜又は前記第2中間膜は、銅窒化物を含むことを特徴とする請求項37記載の薄膜トランジスタ基板。

**【請求項 4 1】**

前記第1中間膜又は前記第2中間膜は、銅酸化物を含むことを特徴とする請求項37記載の薄膜トランジスタ基板。

**【請求項 4 2】**

前記第1中間膜又は前記第2中間膜は、銅酸窒化物を含むことを特徴とする請求項37記載の薄膜トランジスタ基板。

**【請求項 4 3】**

前記キャッピング膜は、Mo、MoN、又はMo合金を含むことを特徴とする請求項37記載の薄膜トランジスタ基板。

**【請求項 4 4】**

前記Mo合金は、MoW、MoTi、MoNb、MoZrのうち、少なくともいずれか1つを含むことを特徴とする請求項43記載の薄膜トランジスタ基板。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は表示装置及びその製造方法に係り、より詳細には、銅又は銅合金を含む配線、これを含む表示装置用薄膜トランジスタ基板、及びその製造方法に関する。

**【背景技術】****【0002】**

薄膜トランジスタ基板は、マトリックス配列の画素を具備する液晶表示装置又は有機EL表示装置等、表示装置の基板として使用される。

**【0003】**

液晶表示装置は、電極が形成されている2枚の基板と、その間に挿入されている液晶層を含み、電極に電圧を印加して液晶層の液晶分子を再配列させ、このようにして再配列された液晶分子の屈折率異方性を利用して透過される光の量を調節する装置であって、電極に伝達される画像信号をイメージの各ドット別に制御するためのスイッチング素子として薄膜トランジスタを用いる。

**【0004】**

有機EL表示装置は、蛍光性有機物質を電気的に励起発光させて画像を表示する表示装置であって、それぞれの画素に発光のための電流を供給する駆動薄膜トランジスタとスイッチング薄膜トランジスタを具備する。

**【0005】**

一方、液晶表示装置又は有機EL表示装置等の表示面積が漸次大型化されるにつれて、薄膜トランジスタと接続されるゲート線及びデータ線が長くなり、配線抵抗の増加が問題になる。抵抗増加によって信号遅延等の問題が誘発される。このために、ゲート線及びデータ線を最大限低い比抵抗を有する材料で形成する必要がある。

**【0006】**

配線材料のうち、最も低い範囲の比抵抗を有しながら価格が低い物質として銅(Cu)が挙げられる。銅は、比抵抗が約 $1.67 \mu \text{cm}$ (薄膜状態では、 $2.0 \sim 2.3 \mu \text{cm}$ )であって、約 $2.65 \mu \text{cm}$ (薄膜状態では、 $3.1 \mu \text{cm}$ )であるアルミニウム(Al)に比して比抵抗が非常に低い。従って、実際の工程で銅からなるゲート線及びデータ線を用いると、アルミニウムを用いた場合に比べて信号遅延等の問題が改善することができる。

**【0007】**

10

20

30

40

50

しかし、銅は、ガラス等の絶縁基板又は半導体層等の下部構造物（銅の下にある絶縁基板、半導体層、又は絶縁膜など）に対する接着性が不良であるという問題、又、銅イオン状態でアモルファスシリコン（a-Si）又はシリコン（Si）内への拡散が非常に速いので、電圧と温度が加わる駆動条件下でa-Si又はSi内へ浸透するか、あるいは、配線パターン形成のための後続のエッチング工程時にエッチング液に溶解された銅イオン、又はエッチング後、フォトレジストパターンの除去のためのストリッピング工程でストリッパー液（stripper）に溶解された銅イオンがa-Si層に浸透して欠陥層を形成し、結局、リーク電流を誘発してTFT特性を低下させるという問題点がある。

#### 【0008】

加えて、銅内へ互いに拡散したSiも、銅配線の比抵抗を増加させて、銅配線の低抵抗配線としての特性を大幅減少させるという問題点、又、化学物質に対する耐化学性が弱くされて後続工程でエッチング液等の化学物質に露出される場合、容易に酸化されるか、腐食されるという問題点がある。

#### 【0009】

従って、銅のみでは配線材料として用いにくく、銅配線は下面にバリア膜と上面にキャッピング膜を含む多重膜の形態で用いることが一般的である。しかし、このような多重膜をパターンニングするためのエッチング工程、またはフォトレジストパターンを除去するためのストリッピング工程時に、キャッピング膜と銅膜の界面又はバリア膜と銅膜との界面でバッテリー効果によって銅膜が選択的に腐食され、キャッピング膜のオーバーハングが形成される等、配線の側面プロファイル不良が生じて、後続膜形成時に各種クラックを誘発する等の配線の信頼性が低下する。

#### 【発明の開示】

##### 【発明が解決しようとする課題】

#### 【0010】

本発明の第1目的は、配線パターンニング工程時に、良好な側面プロファイルを有する配線を提供することにある。

#### 【0011】

本発明の第2目的は、配線パターンニング工程時に、良好な側面プロファイルを有する配線を形成する方法を提供することにある。

#### 【0012】

本発明の第3目的は、前記配線を含む薄膜トランジスタ基板及びその製造方法を提供することにある。

##### 【課題を解決するための手段】

#### 【0013】

前記技術的課題を達成するための本発明の一実施例による配線は、下部構造物上に形成されたバリア膜、バリア膜上に形成された銅又は銅合金を含む導電膜（以下、単に銅導電膜と呼ぶことがある。）、銅導電膜上に形成された中間膜、及び中間膜上に形成されたキャッピング膜を含む。

#### 【0014】

又、バリア膜は、Mo、又はMo合金を含んでもよい。又、Mo合金は、MoN、MoW、MoTi、MoNb、MoZrのうち、少なくともいずれか1つを含んでもよい。又、中間膜は、銅窒化物、又は銅酸化物、又は銅酸窒化物を含んでもよい。又、キャッピング膜は、Mo又はMo合金を含んでもよい。又、Mo合金は、MoN、MoW、MoTi、MoNb、MoZrのうち、少なくともいずれか1つを含んでもよい。又、下部構造物は、絶縁基板、半導体層、又は絶縁膜などである。

#### 【0015】

又、前記技術的課題を達成するための本発明の他の実施例による配線は、下部構造物上に形成されたバリア膜、バリア膜上に形成された第1中間膜、第1中間膜上に形成された銅又は銅合金を含む導電膜、銅導電膜上に形成された第2中間膜、及び第2中間膜上に形成されたキャッピング膜を含む。

10

20

30

40

50

## 【0016】

又、バリア膜は、Mo又はMo合金を含んでもよい。又、Mo合金は、MoN、MoW、MoTi、MoNb、MoZrのうち、少なくともいずれか1つを含んでもよい。又、前記第1中間膜又は第2中間膜は、銅窒化物、又は銅酸化物、又は銅酸窒化物を含むことができる。又、前記キャッピング膜は、Mo又はMo合金を含むことができる。又、前記Mo合金は、MoN、MoW、MoTi、MoNb、MoZrのうち、少なくともいずれか1つを含むことができる。又、前記下部構造物は、絶縁基板、半導体層、又は絶縁膜などである。

## 【0017】

又、技術的課題を達成するための本発明の一実施例による配線形成方法は、下部構造物上にバリア膜を形成し、バリア膜が形成されている下部構造物上に銅又は銅合金を含む導電膜を形成し、銅又は銅合金を含む導電膜上に中間膜を形成し、及び中間膜上にキャッピング膜を形成することを特徴とする。又、中間膜の形成は、窒素を含む雰囲気下で銅をターゲットとしてスパッタリングすることを特徴としてもよい。又、中間膜の形成は、酸素を含む雰囲気下で銅をターゲットとしてスパッタリングすることを特徴としてもよい。又、中間膜の形成は、酸素及び窒素を含む雰囲気下で銅をターゲットとしてスパッタリングすることを特徴としてもよい。又、中間膜の形成は、真空破壊によって行われてもよい。

## 【0018】

又、技術的課題を達成するための本発明の他の実施例による配線構造形成方法は、下部構造物上にバリア膜を形成し、バリア膜上に第1中間膜を形成し、第1中間膜上に銅又は銅合金を含む導電膜を形成し、銅導電膜上に第2中間膜を形成し、及び中間膜上にキャッピング膜を形成することを特徴としてもよい。又、第1中間膜又は第2中間膜の形成は、窒素を含む雰囲気下で銅をターゲットとしてスパッタリングすることを特徴としてもよい。又、第1中間膜又は第2中間膜の形成は、酸素を含む雰囲気下で銅をターゲットとしてスパッタリングすることを特徴としてもよい。又、第1中間膜又は第2中間膜の形成は、酸素及び窒素を含む雰囲気下で銅をターゲットとしてスパッタリングすることを特徴としてもよい。又、第1中間膜又は第2中間膜の形成は、真空破壊によって行われてもよい。

## 【0019】

又、技術的課題を達成するための本発明の一実施例による薄膜トランジスタ基板は、絶縁基板上に形成され第1方向に延びたゲート線及びゲート線に接続されたゲート電極を含むゲート配線、絶縁基板上にゲート配線と絶縁して形成され、ゲート線と交差するよう第2方向に延びたデータ線、データ線に接続されたソース電極及びソース電極と離隔した位置にあるドレイン電極を含むデータ配線、ゲート配線とデータ配線上に各画素毎に形成されドレイン電極と接続された画素電極を含むが、ゲート配線及び/又はデータ配線は、下部構造物上に形成されたバリア膜、バリア膜上に形成された銅又は銅合金を含む銅導電膜、銅導電膜上に形成された銅窒化物を含む中間膜、及び中間膜上に形成されたキャッピング膜を含む。又、バリア膜は、Mo、MoN、又はMo合金を含んでもよい。又、Mo合金は、MoW、MoTi、MoNb、MoZrのうち、少なくともいずれか1つを含んでもよい。又、中間膜は、銅窒化物、又は銅酸化物、又は銅酸窒化物を含んでもよい。又、キャッピング膜は、Mo、MoN、又はMo合金を含んでもよい。又、Mo合金は、MoW、MoTi、MoNb、MoZrのうち、少なくともいずれか1つを含んでもよい。又、下部構造物は、絶縁基板、半導体層、又は絶縁膜などである。

## 【0020】

又、技術的課題を達成するための本発明の他の実施例による薄膜トランジスタ基板は、絶縁基板上に形成され第1方向に延びたゲート線及びゲート線に接続されたゲート電極を含むゲート配線、絶縁基板上にゲート配線と絶縁して形成され、ゲート線と交差するよう第2方向に延びたデータ線、データ線に接続されたソース電極及びソース電極と離隔した位置にあるドレイン電極を含むデータ配線、ゲート配線とデータ配線上に各画素毎に形成されドレイン電極と接続された画素電極を含むが、ゲート配線及び/又はデータ配線は

10

20

30

40

50

、下部構造物上に形成されたバリア膜、前記バリア膜上に形成された第1中間膜、第1中間膜上に形成された銅又は銅合金を含む銅導電膜、銅導電膜上に形成された第2中間膜、及び前記中間膜上に形成されたキャッピング膜を含む。又、バリア膜は、Mo、MoN、又はMo合金を含んでもよい。又、Mo合金は、MoW、MoTi、MoNb、MoZrのうち、少なくともいずれか1つを含んでもよい。又、第1中間膜又は第2中間膜は、銅窒化物、又は銅酸化物、又は銅酸窒化物を含んでもよい。又、キャッピング膜は、Mo、MoN、又はMo合金を含んでもよい。又、Mo合金は、MoW、MoTi、MoNb、MoZrのうち、少なくともいずれか1つを含んでもよい。又、下部構造物は、絶縁基板、半導体層、又は絶縁膜などである。

【発明を実施するための最良の形態】

10

【0021】

以下、添付図面を参照して、本発明の一実施例による配線構造及び配線形成方法を説明する。

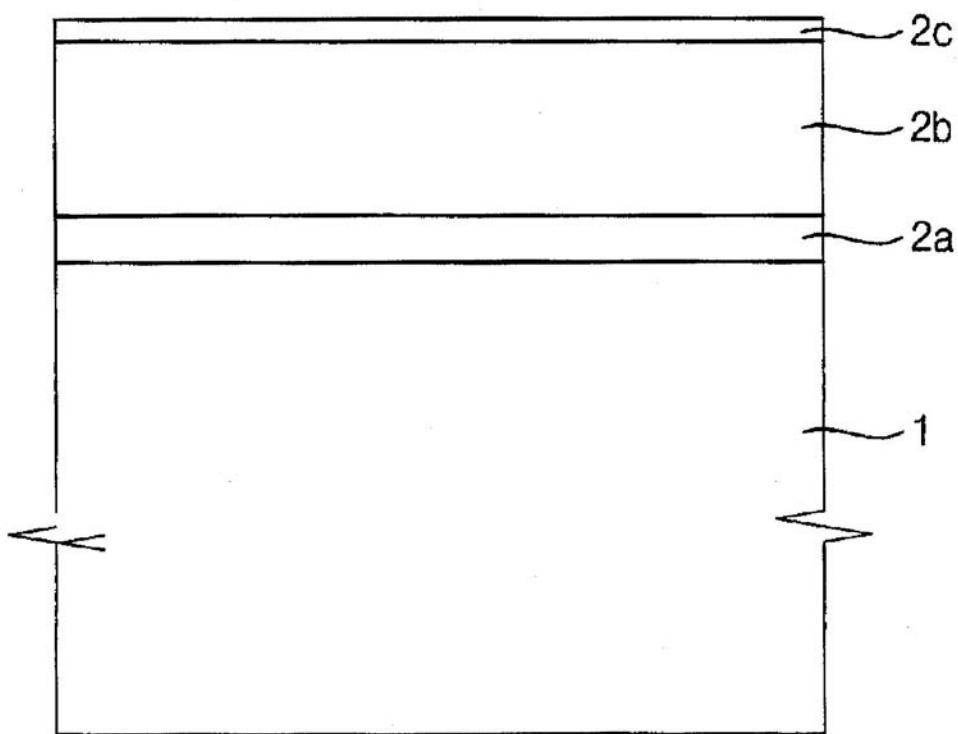

【0022】

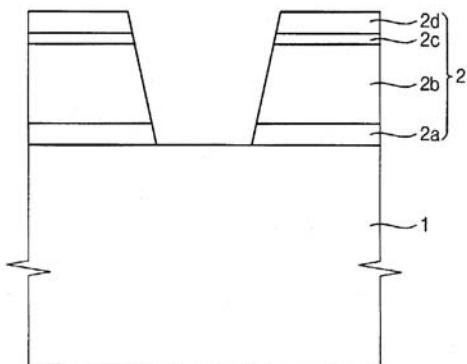

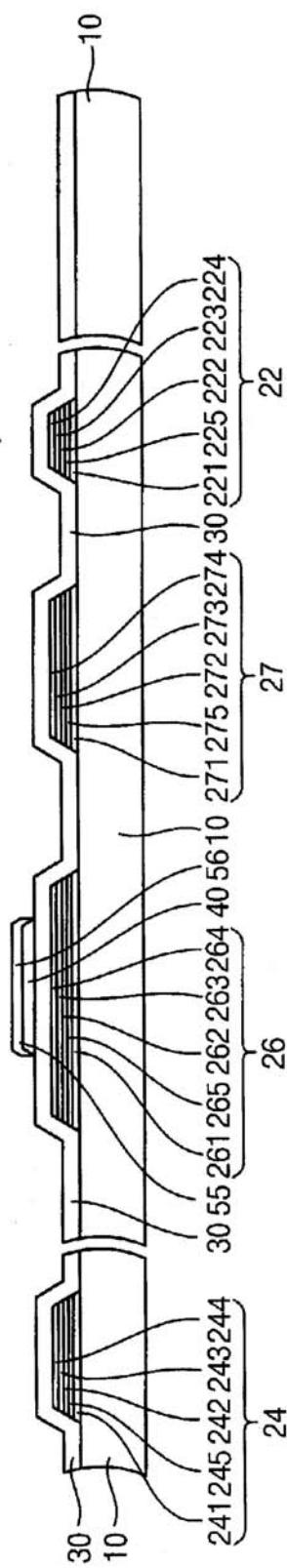

図1は、本発明の一実施例による配線構造の断面図である。

【0023】

図1を参照すると、下部構造物1上にバリア膜2aを介在させて、銅導電膜2bが形成されている。銅導電膜2bの上部にはキャッピング膜2dが配置され、銅導電膜2bとキャッピング膜2dとの間には中間膜2cが形成されている。

【0024】

下部構造物1は、配線2等が形成される面を提供し、配線等を支持する。下部構造物1は、上面に形成される配線2とは異なる構成を有し、複数の構成要素、素子、層等が組合されている複合物のみならず、1つの構成要素、素子、層等からなる単一構造物も含む。

【0025】

例えば、ガラス等からなる絶縁基板、アモルファスシリコン（非晶質シリコン）等からなる半導体層、絶縁膜などで、これに限定されない。

【0026】

下部構造物1上には、主配線材料として銅又は銅合金を含む銅導電膜2bが配置される。

【0027】

下部構造物1と銅導電膜2bとの間には、銅導電膜2bと下部構造物1の接着力を増加させ、銅イオンが下部構造物1に拡散されることを防止するバリア膜2aが配置される。

【0028】

銅は、下部構造物1との接着力が良くないため、銅導電膜2bを積層してパターニングする過程で浮くか、あるいは剥げる現象が発生するおそれがある。これを防止するために、銅以外の他の物質を含むバリア膜2aが銅導電膜2bと下部構造物1との間に形成される。又、バリア膜2aは、銅導電膜2bから銅イオンが、例えば、半導体層のような下部構造物1へ拡散することを防止して、下部構造物1の特性を維持し、同時に下部構造物1の物質が銅導電膜2bに拡散することを防止して、銅導電膜2bの比抵抗が増加することを防止する。

【0029】

バリア膜2aは、後述するキャッピング膜2dの場合のように、銅導電膜2b等と一緒にエッチングされ得る物質、即ち、銅とのエッチング選択比が少ない物質を用いることが工程単純化の側面で有利である。このような条件を満足させる物質として、例えば、モリブデン系列のMo、MoN、又は、MoTi、MoNb、MoZr等のMo合金を用いてよい。

【0030】

銅導電膜2bの上面には、銅導電膜2bがエッチング溶液などの化学物質と反応して腐食することを防止するためのキャッピング膜2dが形成されている。例えば、銅導電膜2bのパターニング工程に用いられるエッチング液は、銅を酸化及び腐食させて比抵抗を増

20

30

40

50

加させる。従って、銅導電膜 2 b が直接エッチング液等に露出しないように上面にキャッピング膜 2 d を配置する。この際、キャッピング膜 2 d は、銅導電膜 2 b パターニング用エッチング液等に腐食されない耐化学性の強い物質を用いるが、銅導電膜 2 b と一緒にエッチングされる物質を用いることは工程の単純化の側面で有利である。このような条件を満足させる物質として、例えば、モリブデン系列の Mo、MoN、又は、MoTi、MoNb、MoZr 等の Mo 合金を用いてもよい。

#### 【0031】

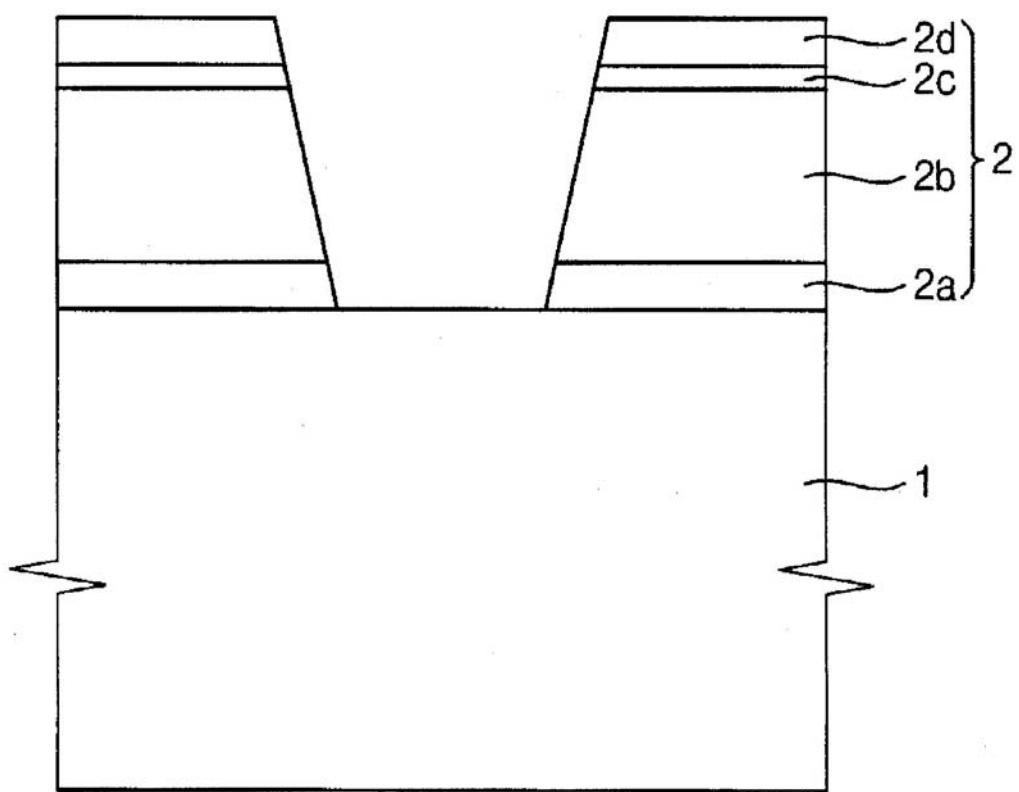

図 2 は、多重膜配線構造のパターンプロファイル不良を示す断面図である。

#### 【0032】

図 2 を参照すると、銅導電膜 2 b の下面にバリア膜 2 a が上面にキャッピング膜 2 d が形成される場合、配線のエッチング工程又はフォトレジストパターン除去時において、バリア膜 2 a 又はキャッピング膜 2 d と銅導電膜 2 b の界面では、銅とバリア膜 2 a 又はキャッピング膜 2 d を構成する物質（例えば、Mo）間の相互電子交換によるガルバニック腐食が生じる。従って、活性電位を有する銅の腐食速度が速くなり、界面での銅導電膜 2 b が選択的に腐食され配線プロファイルが不良になる。特に、キャッピング膜 2 d のオーバーハンプは、後続膜の形成時に、クラック等を誘発することになり、配線の信頼度を低下させることになる。

#### 【0033】

前記のようなガルバニック腐食を防止するために、図 1 に図示するように、キャッピング膜 2 d と銅導電膜 2 bとの間には、銅導電膜 2 b とキャッピング膜 2 d の電子交換を妨害する中間膜 2 c が挿入されている。中間膜 2 c は絶縁性を有してもよく、伝導性と絶縁性の中間形態である半導性を有しても電子交換を相当部分阻害するので、ガルバニック腐食によるオーバーハンプ現象を減少させる効果がある。このような中間膜 2 c を構成する物質は、絶縁性又は半導性を有する物質であれば良いが、望ましくは、工程単純化の観点で下部の銅導電膜 2 b の物質と同じ系列の金属を含む化合物を用いてもよい。中間膜 2 c を構成する物質としては、銅窒化物、銅酸化物、又は銅酸窒化物を含んでもよい。銅窒化物の例としては Cu<sub>3</sub>N 等を、銅酸化物の例としては Cu<sub>2</sub>O、CuO 等が挙げられ、銅酸窒化物の例としては銅酸化物と銅窒化物の混合形態として、Cu<sub>3</sub>N + CuO 又は Cu<sub>3</sub>N + Cu<sub>2</sub>O が挙げられる。ここで、ガルバニック腐食を防止することができる銅窒化物、又は銅酸化物、又は銅酸窒化膜の含量を中間膜を構成する全体の元素に対して窒素又は酸素の原子百分率で示すと、0.001 乃至 50 at% (atomic %) の範囲である。

#### 【0034】

中間膜 2 c の厚みは、中間膜の絶縁性の程度を考慮して決定してもよい。即ち、中間膜に窒素の原子百分率が相対的に高いか、あるいは全体的に絶縁性を示す場合、比較的薄い厚みであっても良いが、窒素の原子百分率が相対的に低いか、あるいは全体的に半導性乃至弱い伝導性を有する場合、比較的厚く形成することが望ましい。例えば、約 50 乃至 1000 の範囲で調節してもよい。

#### 【0035】

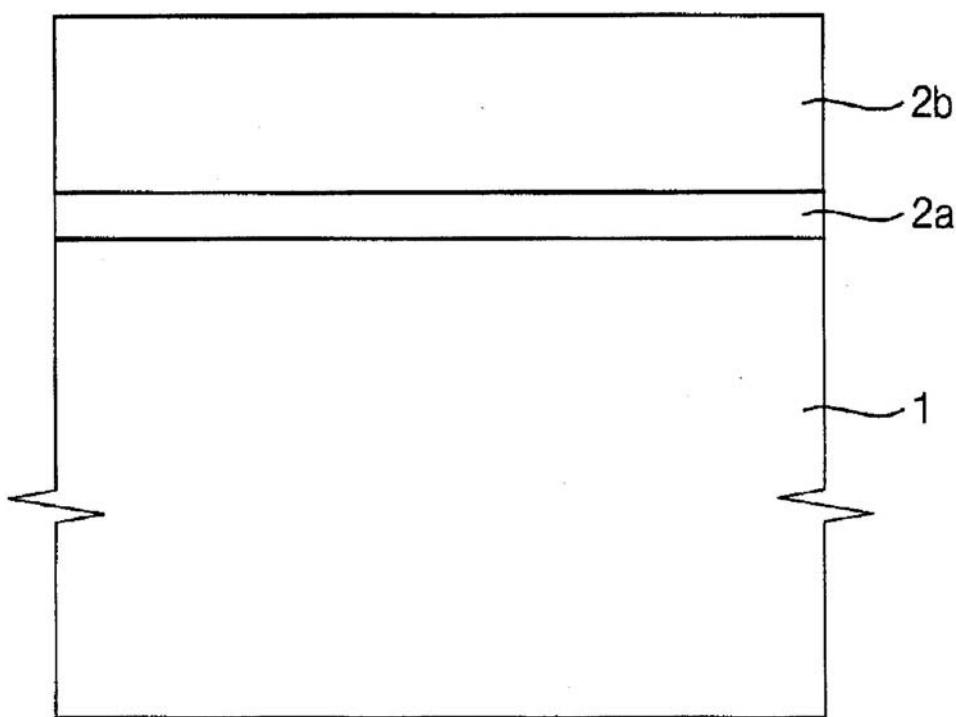

以下、図 1、図 3 乃至図 6 を参照して、前記のような配線構造を有する配線の形成方法について説明する。

#### 【0036】

図 3 乃至図 6 は、本発明の一実施例による薄膜トランジスタ配線形成方法の工程ステップ別の断面図である。

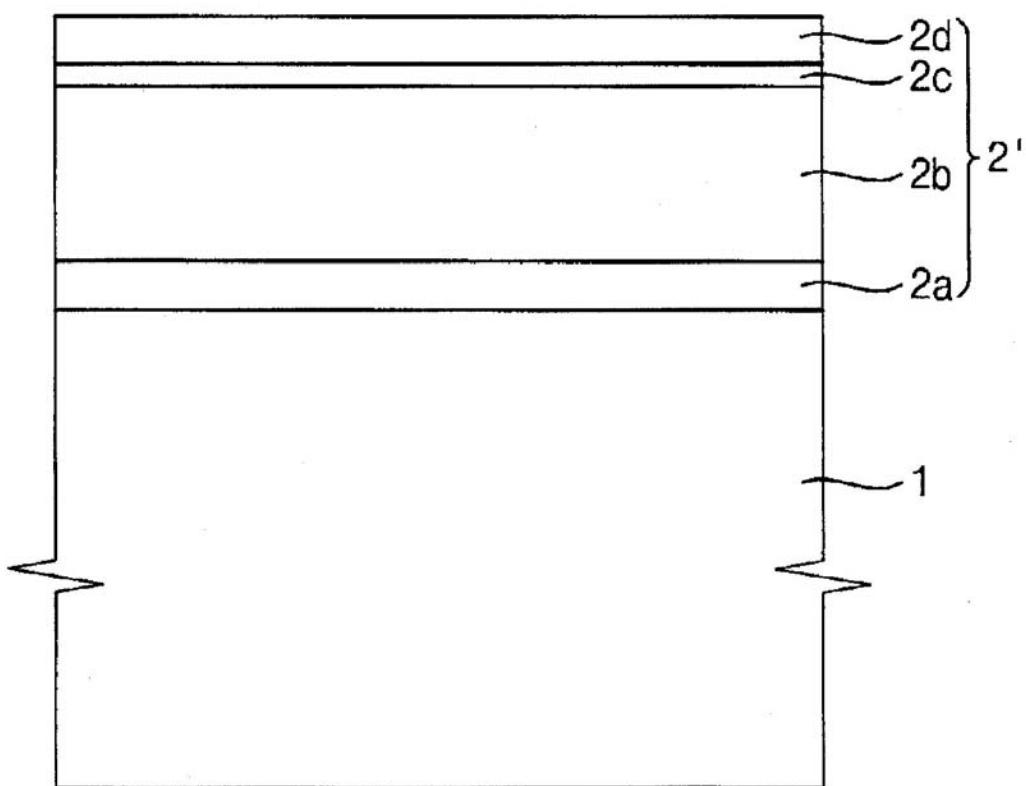

#### 【0037】

図 3 を参照すると、まず、ガラス等の絶縁基板、半導体層、絶縁膜等からなる下部構造物 1 を準備する。その後、下部構造物 1 の上にモリブデン系列の Mo、MoN、又は MoTi、MoNb、MoZr 等の Mo 合金を含む物質を、例えばスパッタリング等で蒸着してバリア膜 2 a を形成する。バリア膜 2 a の厚みは 50 乃至 500、好ましくは 100 乃至 300 で形成してもよい。

10

20

30

40

50

## 【0038】

その後、バリア膜2aの上に銅又は銅合金を、例えば、スパッタリング等で蒸着して銅導電膜2bを形成する。ここで、スパッタリングは、例えば、チャンバー内に非活性気体であるアルゴン(Ar)気体を流入しながら、銅又は銅合金をターゲットとしてプラズマ状態のイオン化されたAr正イオンを衝突させる方法で行われる。銅導電膜2bの厚みは、1000乃至3000、好ましくは1500乃至2500で形成してもよい。

## 【0039】

その後、同じチャンバーでアルゴン気体の流入量を減少させて窒素(N<sub>2</sub>)気体を流入させながら、in-situ(プロセスが起こっている時間/場所)で反応性スパッタリングを行う。窒素気体は、非活性気体であるアルゴン気体とは異なり、プラズマ状態にイオン化されターゲットに衝突する場合、ターゲット原子と反応する。従って、銅又は銅合金をターゲットとする場合、銅原子と化学反応して銅窒化物を形成することができる。

10

## 【0040】

このような銅窒化物が銅導電膜2b上に蒸着されることにより、中間膜2cが形成される。この際、全てのターゲット元素が窒素気体と反応することはない。従って、アルゴン気体と衝突した銅原子、窒素気体と衝突したが反応しない銅原子等が蒸着されて、銅窒化物と共に中間膜2cを構成することになる。

## 【0041】

チャンバー内に存在するアルゴン気体と窒素気体は、90:10乃至40:60の比率を有することができ、このような条件で中間膜2cの窒素の含量は0.001乃至50at%の範囲を有することができる。中間膜2cの厚みは、約50乃至1000範囲で調節することができる。

20

## 【0042】

一方、銅酸化物(Cu<sub>2</sub>O、CuO等)は、Arガスと共にO<sub>2</sub>ガスを添加することにより得ることができ、銅酸窒化物(Cu(O,N)<sub>x</sub>)層の場合、Arガスと共にN<sub>2</sub>+O<sub>2</sub>の混合ガス、NH<sub>3</sub>+O<sub>2</sub>の混合ガス、又はN<sub>2</sub>O、NO、NO<sub>2</sub>等のガスを投入して形成することができ、これらの混合比を調節して銅と結合する窒素と酸素の比率を変化させることができる。

## 【0043】

又、同じチャンバー内においてin-situで進行させず、他の真空チャンバーに移動した後、窒素ガス又は酸素ガスを含む雰囲気で反応性スパッタリングを行って中間膜2cを形成してもよい。

30

## 【0044】

又、スパッタリングで多重膜蒸着時において、それぞれの膜を蒸着している間に真空破壊(break)を通じて窒素と酸素の比率を変化させてもよい。即ち、図3に図示されたように、バリア膜2aと銅導電膜2bを連続蒸着した後、真空状態を解除すると、外気中の酸素の影響で図4に図示すように銅導電膜2bの上部に所定の厚みの酸化膜が形成される。このような酸化膜を、本発明の中間膜2cの一部にしてもよい。

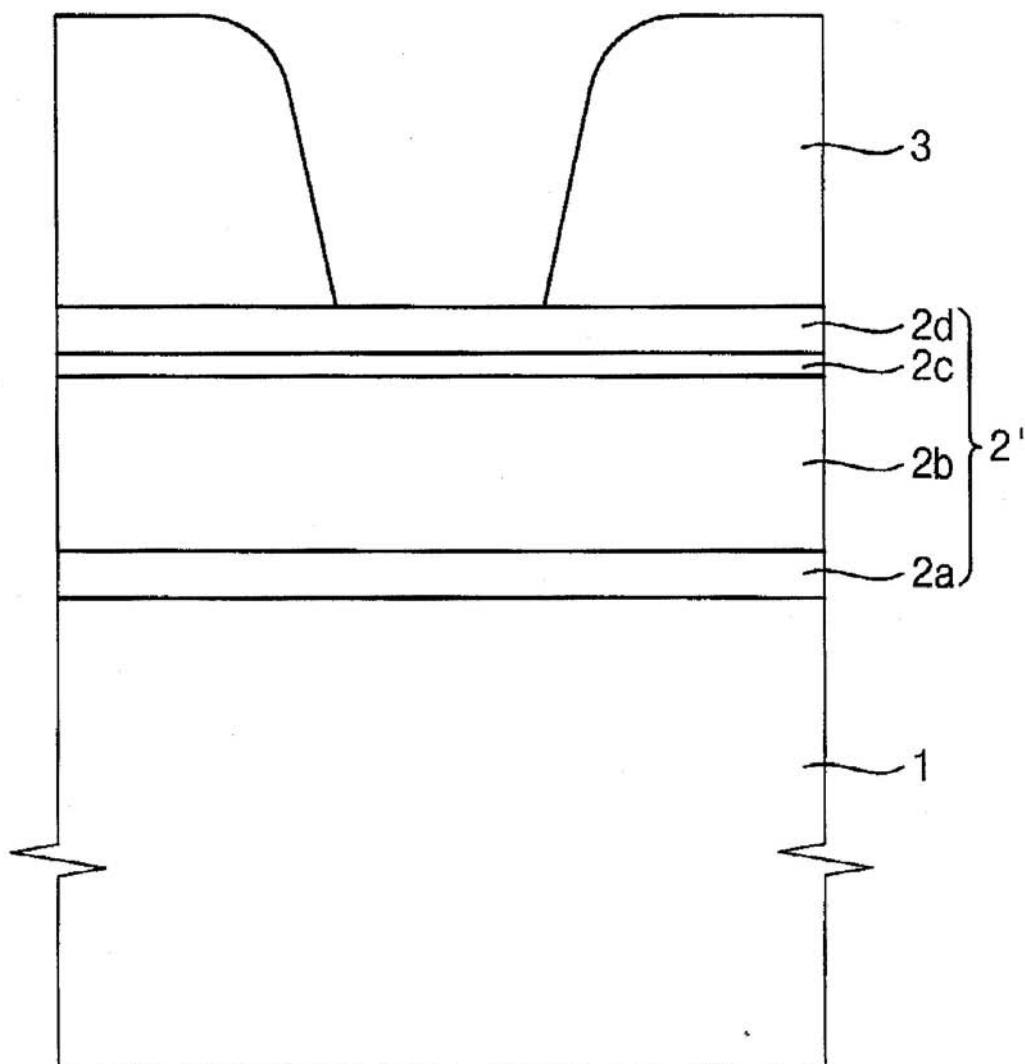

## 【0045】

その後、図5に図示すように、中間膜2cの上部にアルゴン気体を利用したスパッタリングでキャッピング膜2dを形成する。ここで、キャッピング膜2dを構成する物質である前記スパッタリングのターゲットとしては、下部の中間膜2c及び銅導電膜2bを構成する銅系物質と一括でウェットエッチングが可能な物質、即ち、エッチング選択比が小さい物質を用いることができ、例えば、モリブデン系列のMo、MoN、又はMoW、MoTi、MoNb、MoZr等のMo合金を用いてもよい。これによって、バリア膜2a、銅導電膜2b、中間膜2c、及びキャッピング膜2dで構成される4層多重膜2が形成される。

40

## 【0046】

その後、図6に図示すように、多重膜2の上面にフォトレジストを塗布し、露光及び現像して配線を定義するフォトレジストパターン3を形成する。

50

## 【0047】

その後、フォトレジストパターン3をエッチングマスクとしてキャッピング膜2d、中間膜2c、銅導電膜2b、及びバリア膜2aを一括エッチングして、下部構造物1を露出させる。エッチング液としては、過酸化水素又は窒酸をベースとするエッチング液を用いることができ、リン酸、酢酸成分を更に含んでもよい。

## 【0048】

一方、フォトレジストパターン3をエッチングマスクとしてキャッピング膜2d、中間膜2c、及び銅導電膜2bをまずウェットエッチングしてバリア膜2aを露出した後、フォトレジストパターン3をマスクとしてバリア膜2aをエッチングして、下部構造物1を露出させる方式で配線2をパターニングしてもよい。

10

## 【0049】

ここでのエッチングはドライエッチングで進行し、HCl、Cl<sub>2</sub>、H<sub>2</sub>、O<sub>2</sub>又はこれらの組み合わせを含むエッチング気体を用いてもよい。この場合、ウェットエッチング時に、バリア膜2aはエッチング液によってエッチングされずに下部構造物1を覆っているので、銅イオン等が溶解しているエッチング液による下部構造物1の特性変化を防止することができる。この後、フォトレジストパターン3を除去する。これによって、図1に図示する配線2パターンが形成される。又、バリア膜2aのエッチングの時に、フォトレジストパターン3をエッチングマスクとしてドライエッチングした例を示したが、バリア膜2aの上面の膜をウェットエッチングした後、フォトレジストパターン3を除去して、前記上面の膜パターンをエッチングマスクとしてドライエッチングすることにより配線2を形成してもよい。

20

## 【0050】

このように形成された配線2は、ウェットエッチング及びフォトレジスト膜除去工程で銅導電膜とキャッピング膜との間に介在している中間膜が電子の移動を妨害して、ガルバニック腐食の形成を抑制するため、配線が側面腐食なしに鮮明に形成される。よって、側面プロファイルが、オーバーハング等が発生することなく、良好なテープー角を有する。

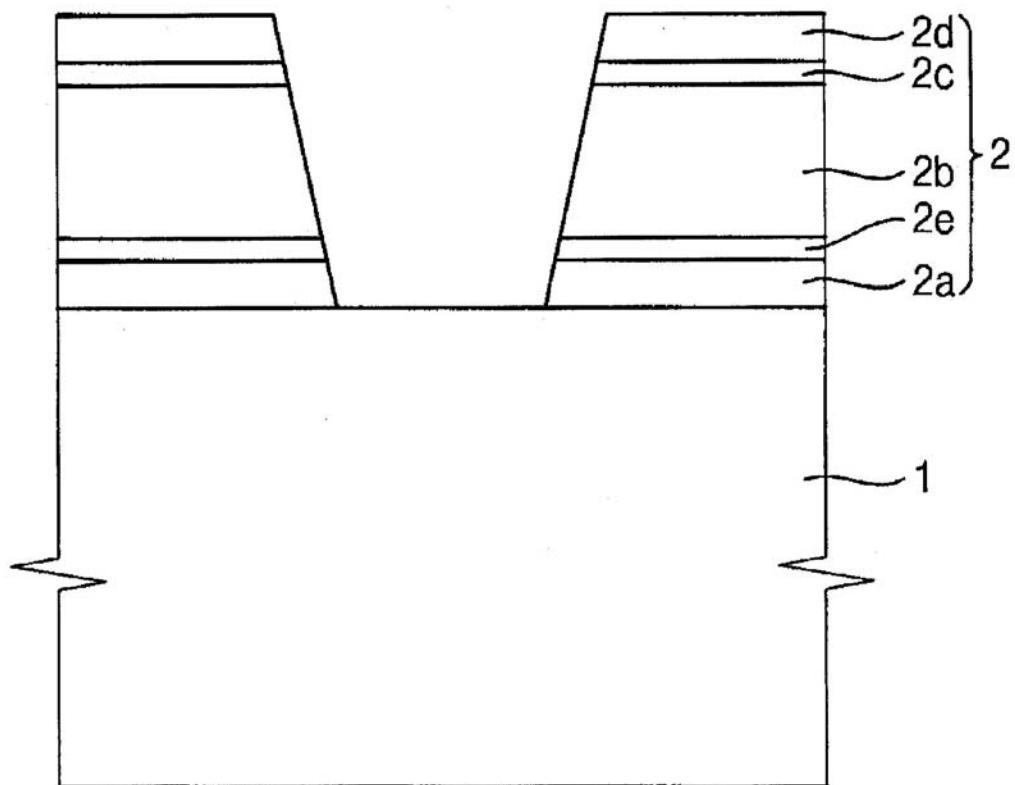

## 【0051】

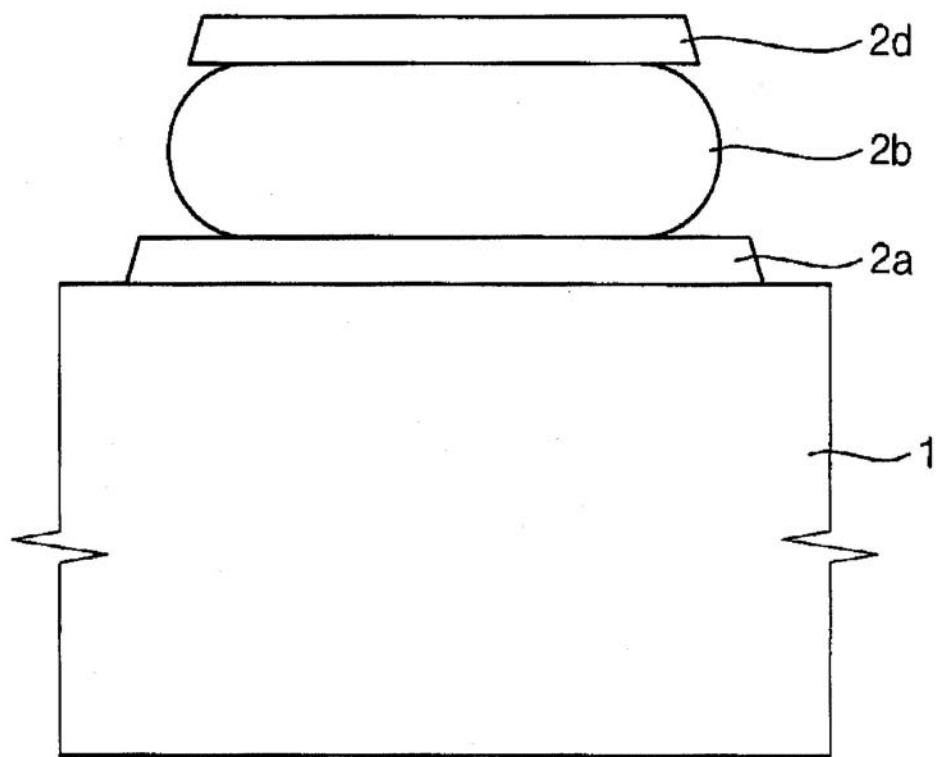

次に、図7を参照して、本発明の配線構造及び形成方法についての他の実施例を説明する。

30

## 【0052】

図7は、本発明の他の実施例による薄膜トランジスタ配線構造を示す図である。本実施例による配線構造の特徴は、バリア膜2aと銅導電膜2bとの間に形成された追加的な中間膜2eの構成にある。以下、図1乃至図6に図示した中間膜2cは、第1中間膜、前記追加的な中間膜2eは第2中間膜と称する。図7を参照すると、第2中間膜2eはバリア膜2aと銅導電膜2bとの間に形成され、銅導電膜2bとバリア膜2aの電子交換を妨害する役割を果たす。第2中間膜2eは、第1中間膜2cと同様に絶縁性を有してもよく、伝導性と絶縁性の中間の形態である半導性を有しても電子交換を相当部分阻害するので、ガルバニック腐食による銅導電膜2bの腐食を抑制する。第1中間膜2cと同様に、第2中間膜2eを構成する物質は、絶縁性又は半導性を有する物質であれば良いが、望ましくは、工程単純化の観点で下部の銅導電膜2bの物質と同じ系列の合金を用いるとよい。第2中間膜2eを構成する物質としては、銅窒化物、銅酸化物、又は銅酸窒化物を含んでもよい。銅窒化物の例としてはCu<sub>3</sub>N等を、銅酸化物の例としてはCu<sub>2</sub>O、CuO等が挙げられ、銅酸窒化物の例としては銅酸化物と銅窒化物の混合形態として、Cu<sub>3</sub>N+CuO又はCu<sub>3</sub>N+Cu<sub>2</sub>Oが挙げられる。

40

## 【0053】

ここで、ガルバニック腐食を防止することができる銅窒化物、又は銅酸化物、又は銅酸窒化膜の含量を中間膜を構成する全体の元素に対して窒素又は酸素の原子百分率で示すと、0.001乃至50at%の範囲である。

## 【0054】

第1中間膜2cと共に第2中間膜2eを追加的に形成する場合、よりなだらかな配線2

50

ロファイルを形成することができる。

【0055】

以下、中間膜2eの形成工程をより詳細に説明する。

【0056】

まず、ガラス等の絶縁基板、半導体層、絶縁膜等の下部構造物1を準備する。その後、下部構造物1上に、例えば、モリブデン系列のMo、MoN、又はMoTi、MoNb、MoZr等のMo合金を含む物質を、例えば、スパッタリング等で蒸着してバリア膜2aを形成する。バリア膜2aの厚みは50乃至500、望ましくは、100乃至300に形成することがよい。

【0057】

その後、銅又は銅合金をターゲットとしたチャンバー内に非活性気体であるアルゴン(Ar)気体を流入しながら、同時に窒素(N<sub>2</sub>)気体を流入させてin-situで反応性スパッタリングを行う。その結果、第2中間膜2eが形成される。窒素気体は、非活性気体であるアルゴン気体とは異なり、プラズマ状態でイオン化されてターゲットに衝突する場合、ターゲット原子と反応する。従って、銅又は銅合金をターゲットとする場合、銅原子と化学反応して銅窒化物を形成することができる。このような銅窒化物がバリア膜2a上に蒸着されることにより、第2中間膜2eが形成される。

【0058】

この際、全てのターゲット元素が窒素気体と反応することはない。従って、アルゴン気体と衝突した銅原子、窒素気体と衝突したが反応しない銅原子等が蒸着されて銅窒化物と共に第2中間膜2eを構成することになる。チャンバー内に存在するアルゴン気体と窒素気体は、90:10乃至40:60の比率を有してもよく、このような条件で第2中間膜2eの窒素の含量は0.001乃至50at%の範囲であってもよい。第2中間膜2eの厚みは、約50乃至1000の範囲で調節してもよい。

【0059】

一方、銅酸化物(Cu<sub>2</sub>O、CuO等)は、Arガスと共にO<sub>2</sub>ガスを添加することで得てもよく、銅酸窒化物層の場合、Arガスと共にN<sub>2</sub>+O<sub>2</sub>の混合ガス、NH<sub>3</sub>+O<sub>2</sub>の混合ガス、又はN<sub>2</sub>O、NO、NO<sub>2</sub>等のガスを投入して形成してもよく、これらの混合比を調節して、銅と結合する窒素と酸素の比率を変化させることができる。この後、窒素又は酸素ガスの流入を中断して、アルゴン気体雰囲気で銅又は銅合金ターゲットによるスパッタリングを行って銅導電膜2bを形成する。

【0060】

その後、窒素又は酸素ガスを更に流入して反応性スパッタリングを行って、銅窒化物、又は銅酸化物、又は銅酸窒化物の第1中間膜2cを形成する。ここで、第1中間膜2cの形成は、図4を参照して説明したように、真空破壊を通じた酸化膜形成で一部形成することができるるのは自明である。又、第2中間膜2eは、バリア膜2aの形成と同一のチャンバーでin-situで形成される代わりに、他のチャンバーに移動した後に、窒素又は酸素雰囲気で反応性スパッタリングを行って形成してもよい。

【0061】

その後は、前述の実施例の場合と同様に、キャッピング膜2dを形成し、フォトリソグラフィ等を用いて配線2のパターンを完成する。

【0062】

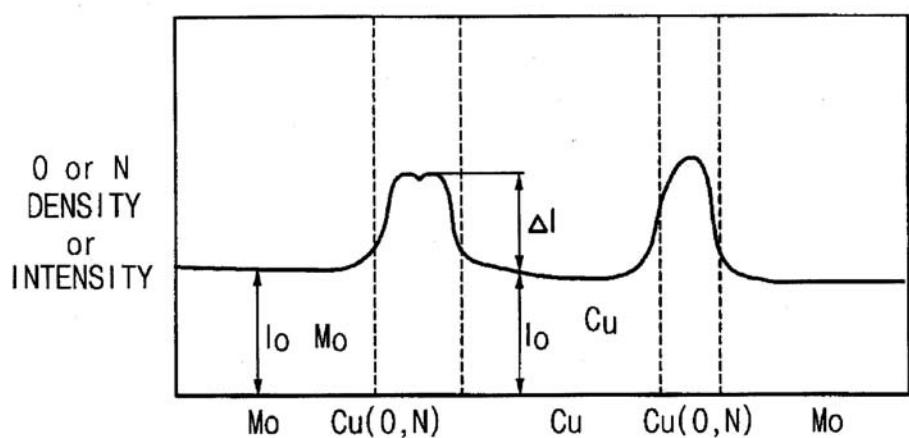

本発明の配線構造において第1及び第2中間膜(2c及び2e)の存在は、以下に説明する方法で確認することができる。

【0063】

図26を参照すると、バリア膜2a及びキャッピング膜2dをMoとし、導電膜2bをCuとした場合、バリア膜(Mo)と導電膜(Cu)又はキャッピング膜(Mo)と導電膜(Cu)との間の中間膜の存在を、SIMS(Secondary Ion Mass Spectroscopy)、XPS(X-ray Photoelectron Spectroscopy)等の分析ツールを用いて、薄膜に含有された酸素又は窒素元素

10

20

30

40

50

の濃度を検出する方法で確認することができる。

#### 【0064】

ここで、 $I_{OMo}$ は、バリア膜又はキャッピング膜(Mo)に存在する酸素、窒素、又は酸素と窒素とを足した濃度値を示し、 $I_{OCu}$ は、導電膜(Cu)に存在する酸素、窒素、又は酸素と窒素とを足した濃度値を示し、 $I$ は[ (中間膜に存在する酸素、窒素、又は酸素と窒素とを足した濃度値) - ( $I_{OMo}$ 、 $I_{OCu}$ 、又は $I_{OMo}$ 及び $I_{OCu}$ の平均値) ]を示す。このような方法で分析する場合、本発明の中間膜は、 $5 < [I / I_{OMo} \times 100, I / I_{OCu} \times 100, \text{又は } 2 \times I / (I_{OMo} + I_{OCu}) < 10000$  の範囲にあることが望ましい。

#### 【0065】

以上説明した本発明の一実施例による配線構造及び配線の形成方法は、液晶表示装置、有機EL表示装置等に用いられる薄膜トランジスタ基板、半導体素子、半導体装置等に適用させることができ、その他にも精密な配線パターンが要求されるいかなる分野にも適用可能である。以下、薄膜トランジスタ基板に適用された例を説明するが、本発明はこれに制限されない。まず、図8及び図9を参照して、前記したような配線構造を含む本発明の一実施例による薄膜トランジスタ基板について説明する。本発明の一実施例による配線構造が同様に適用される部分については、本実施例が当業者に明確に類推又は理解ができる範囲内で説明を省略するか簡略化する。

#### 【0066】

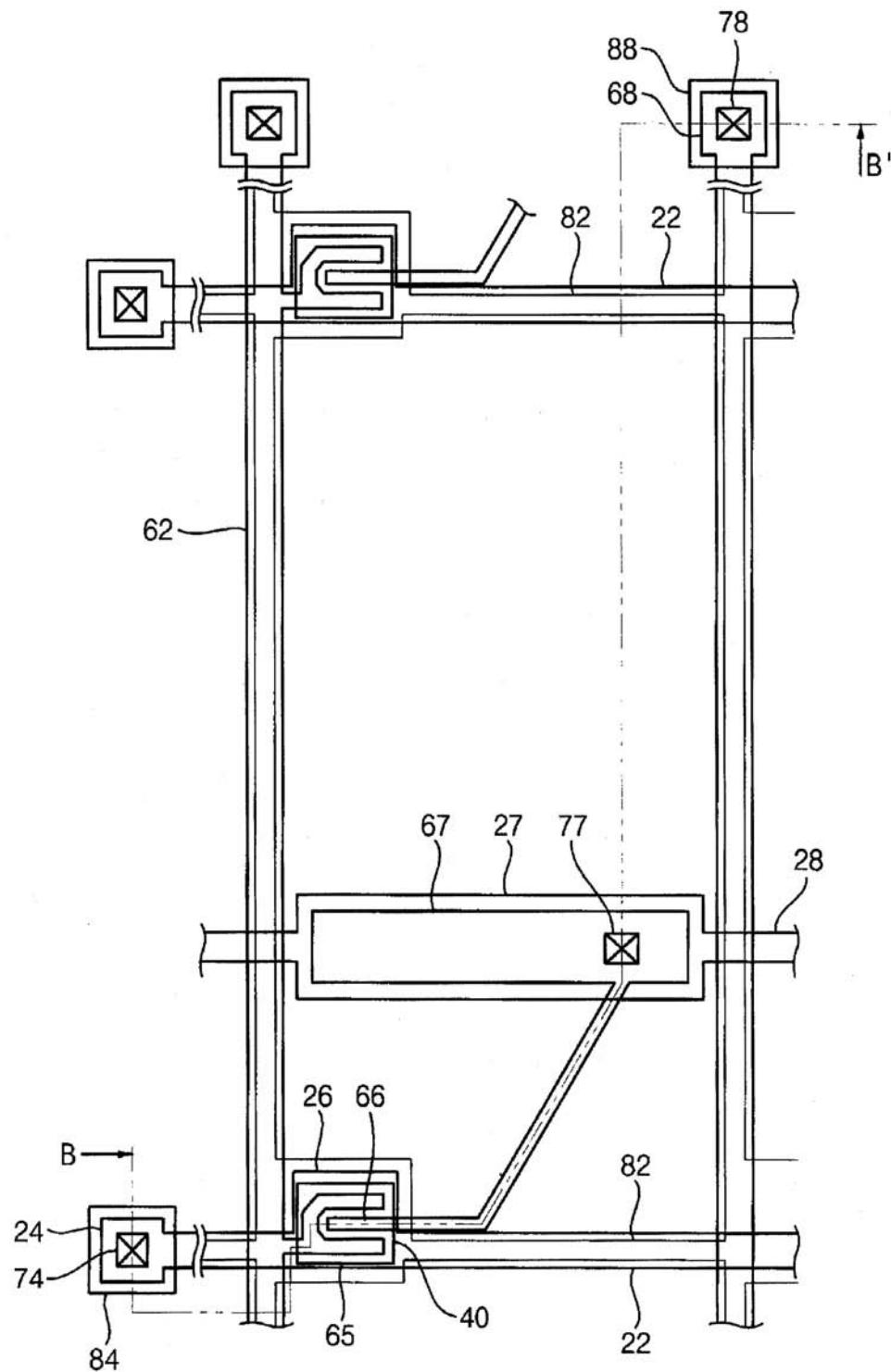

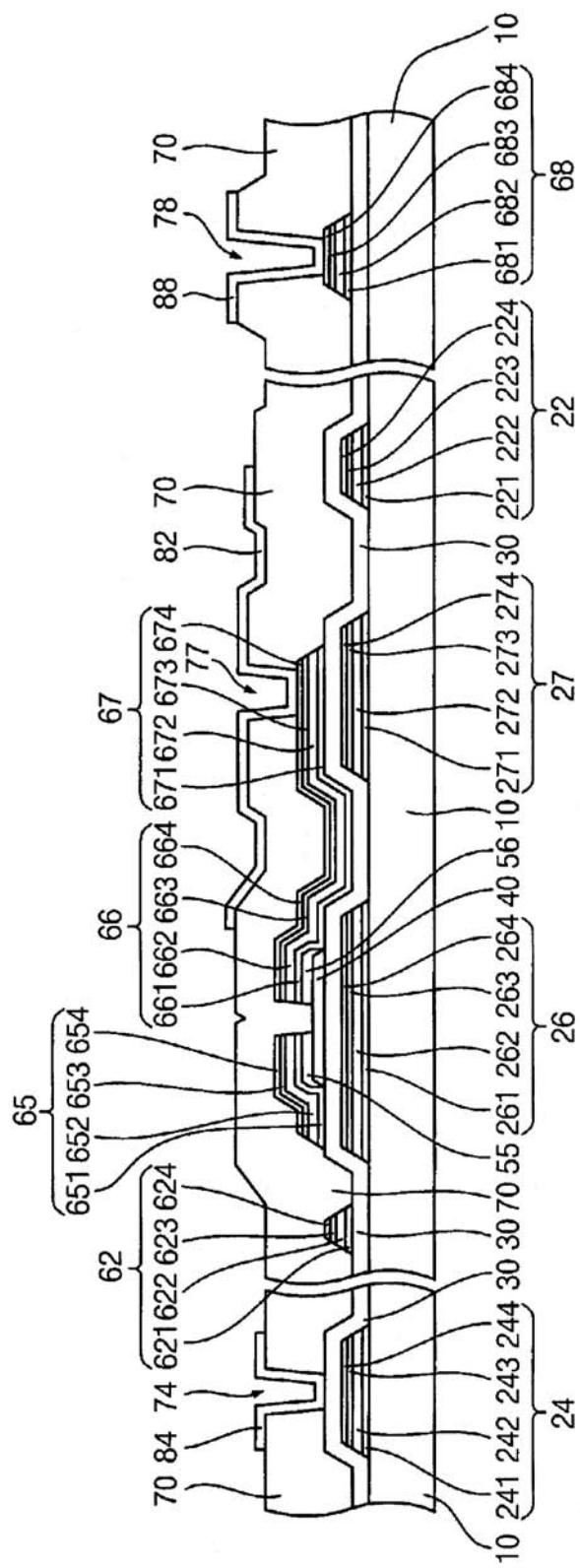

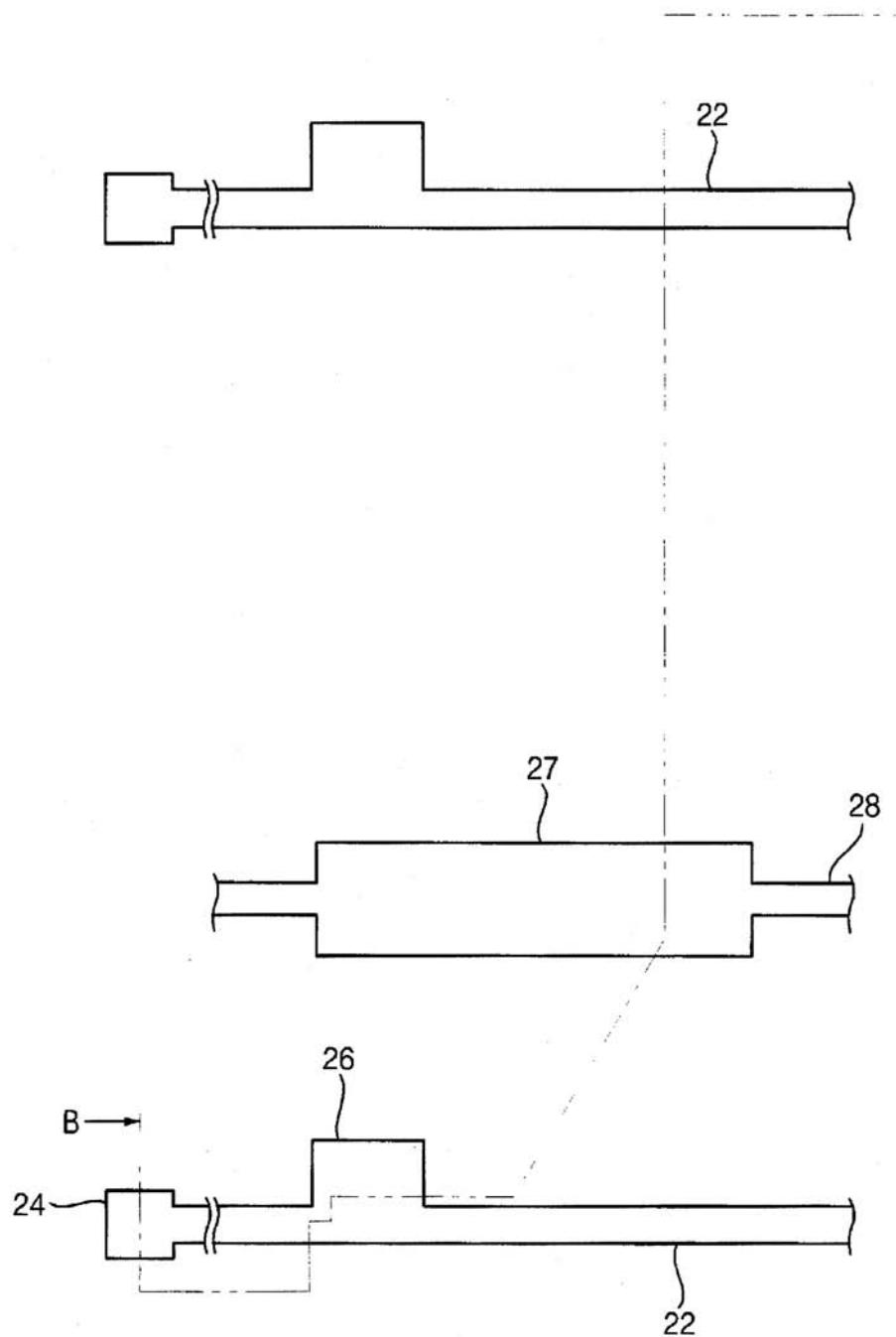

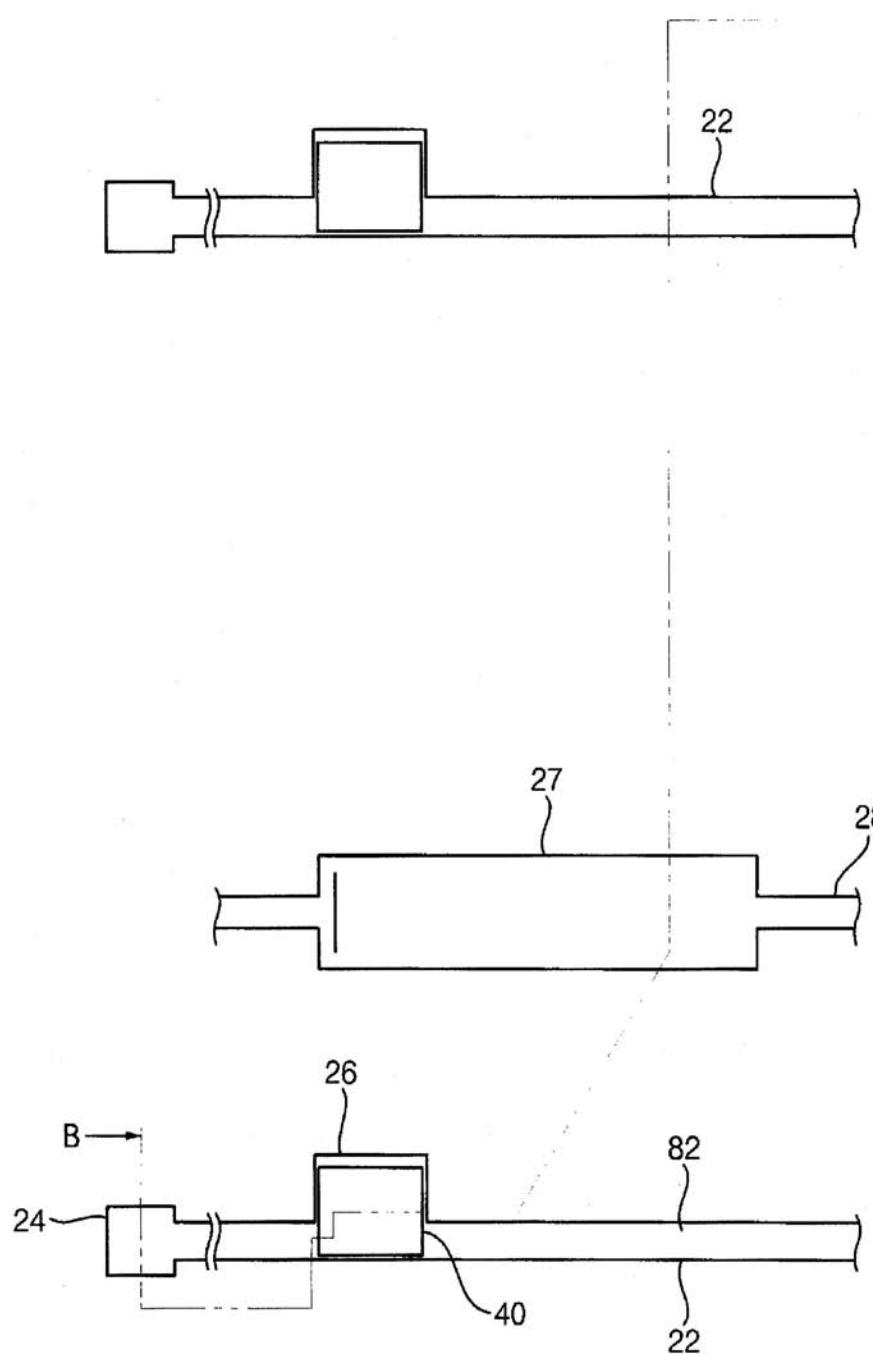

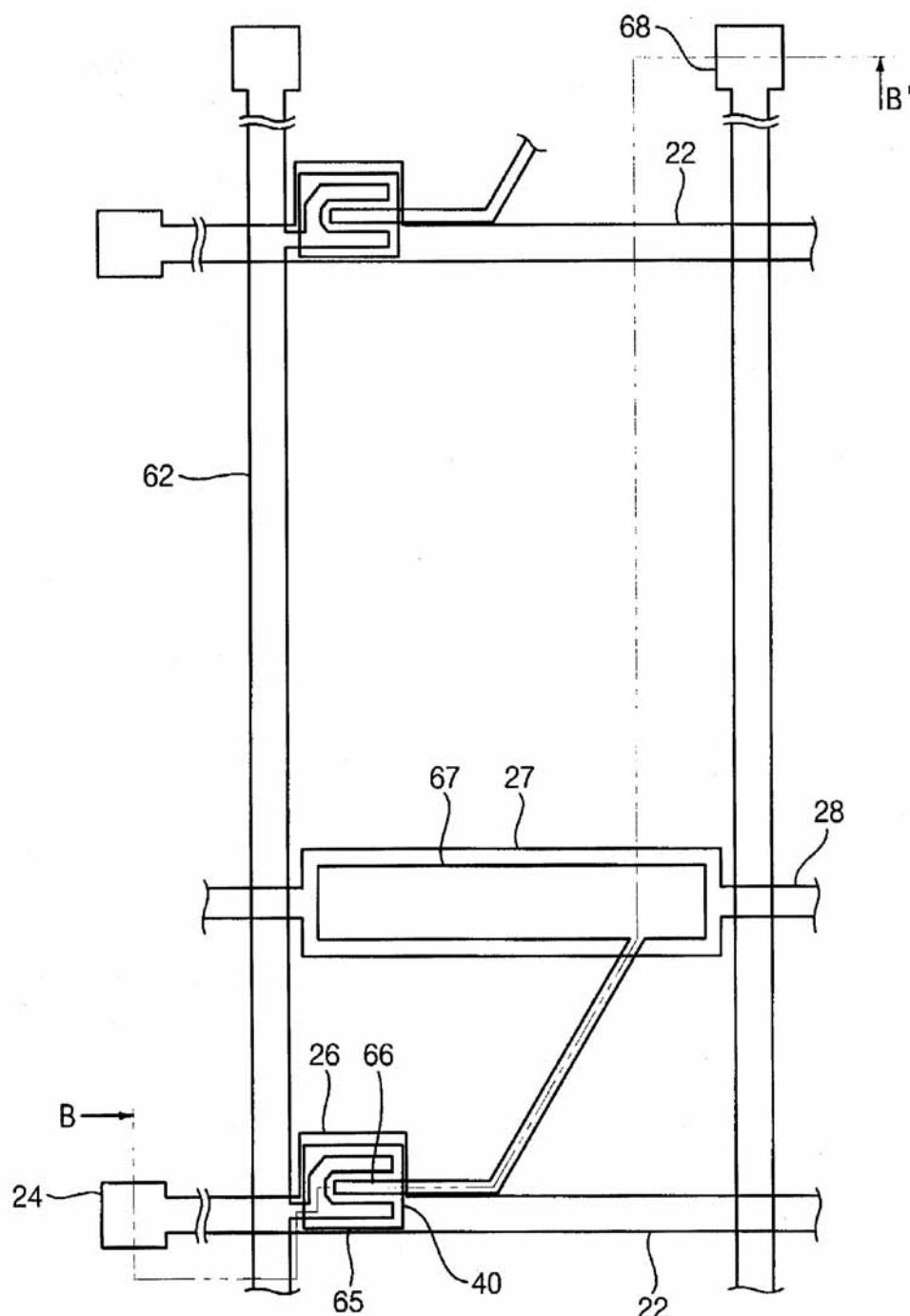

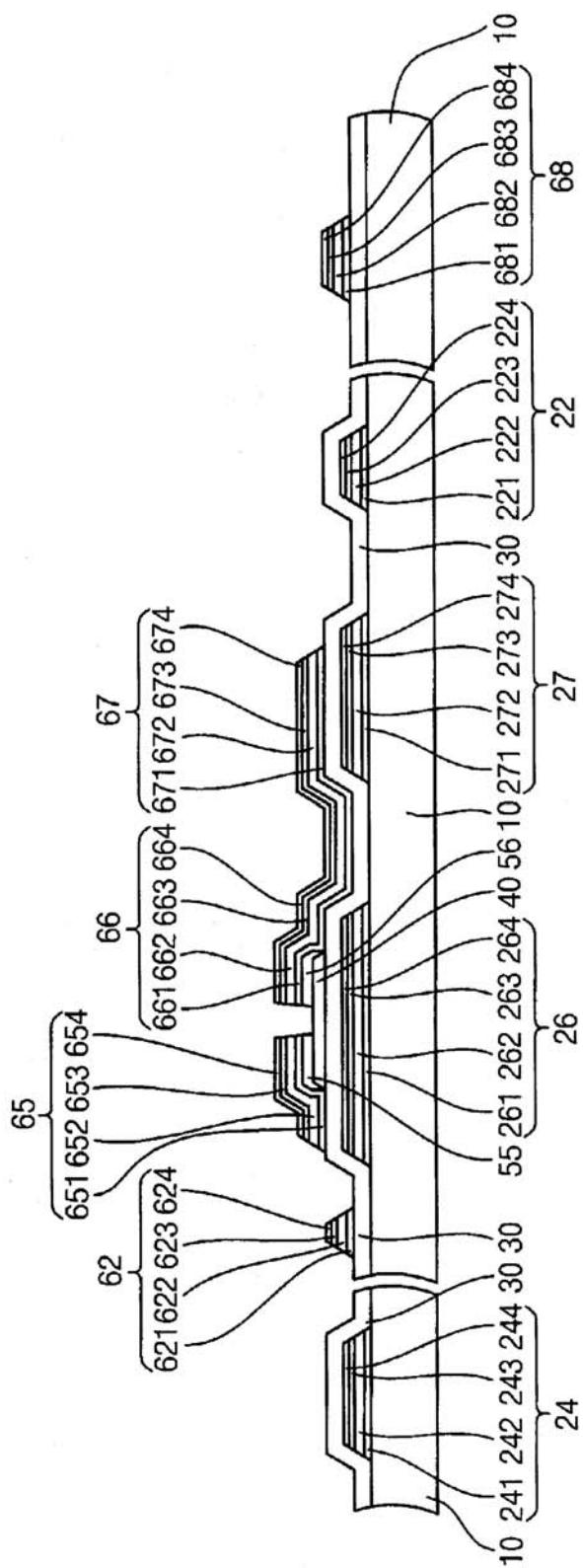

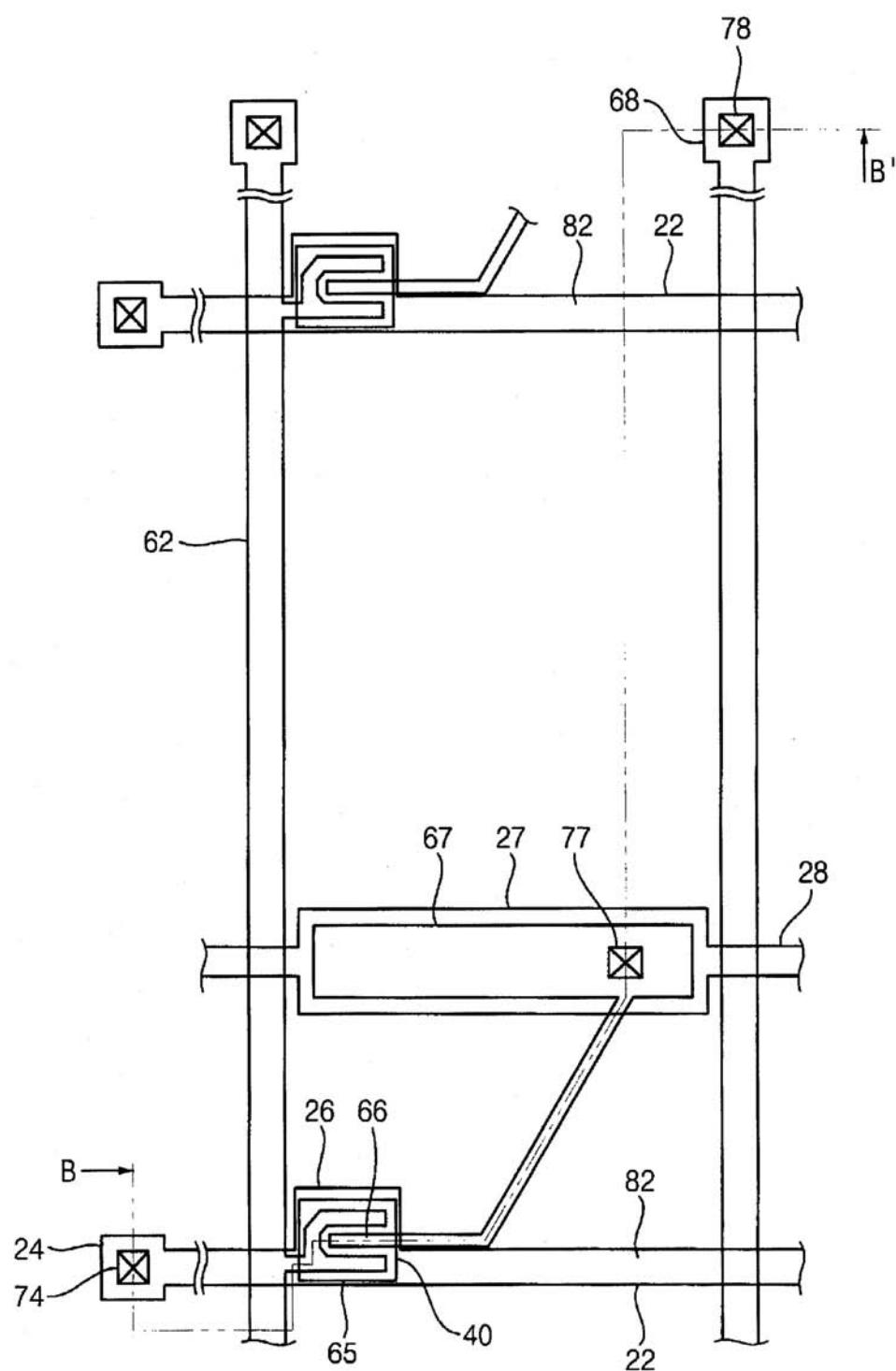

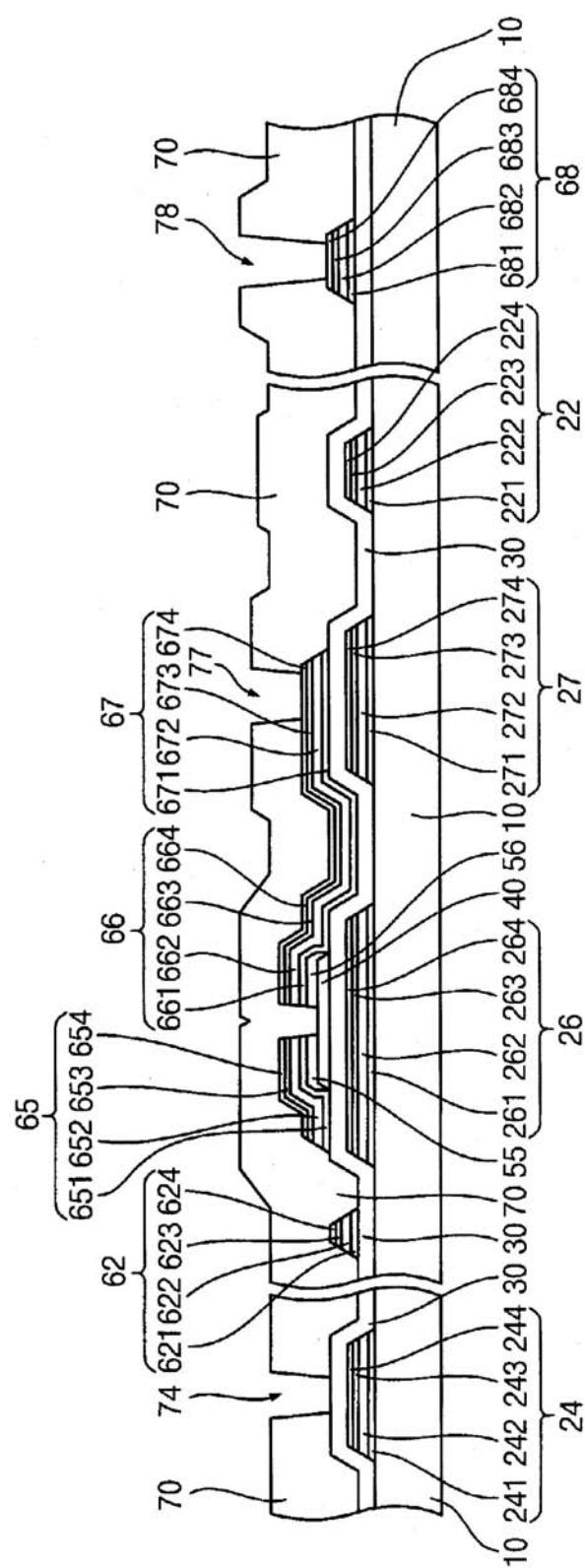

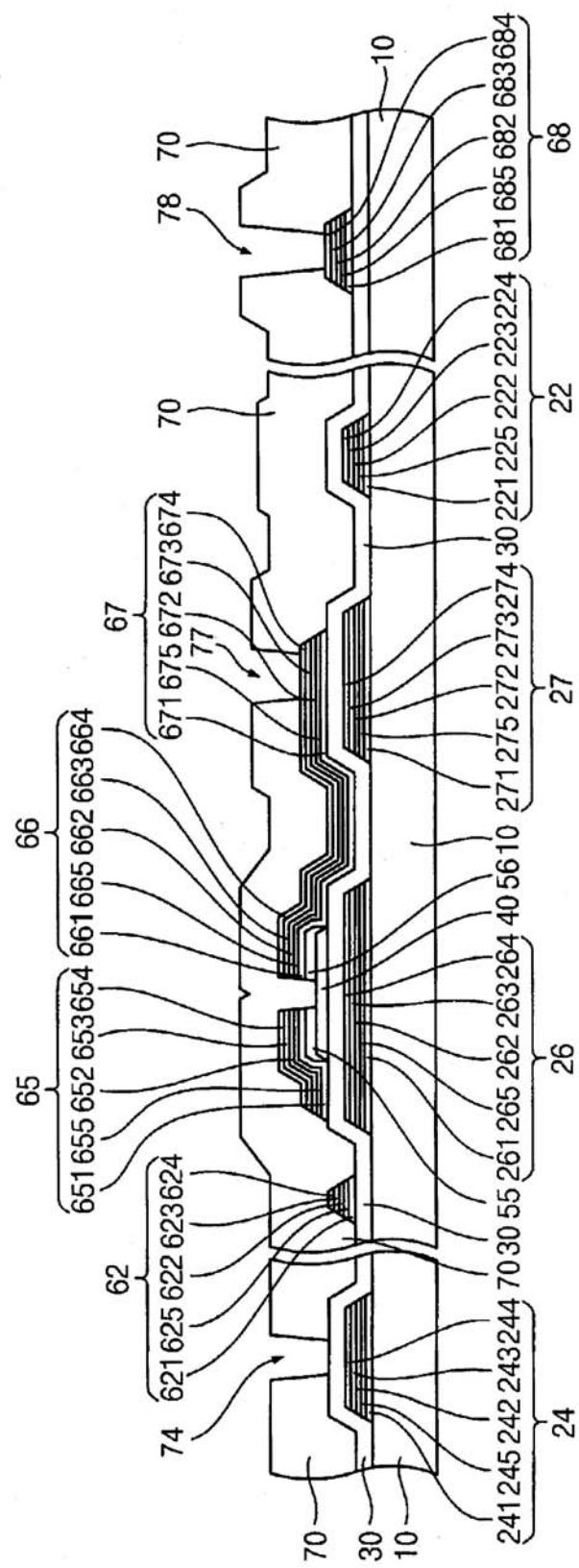

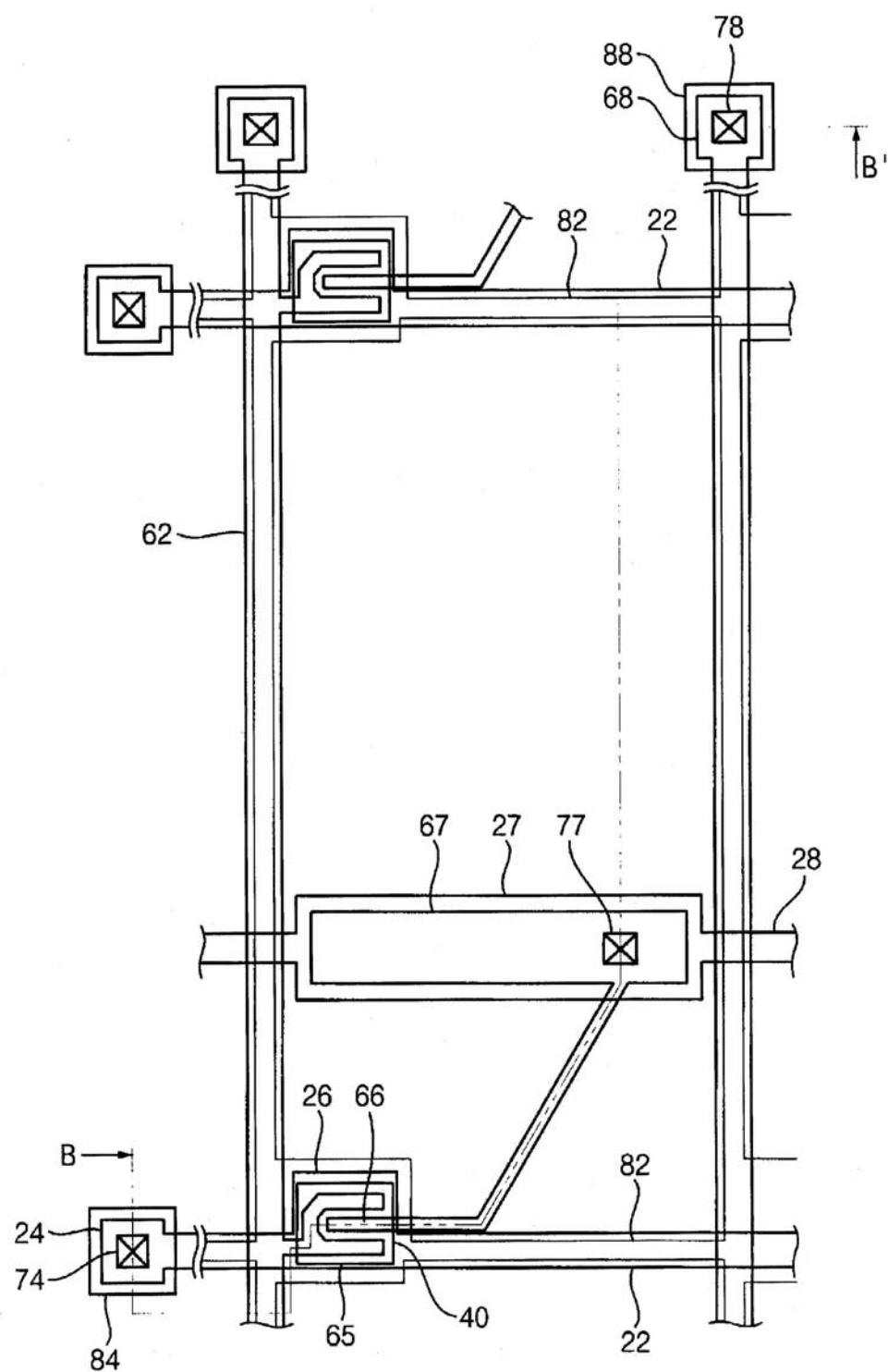

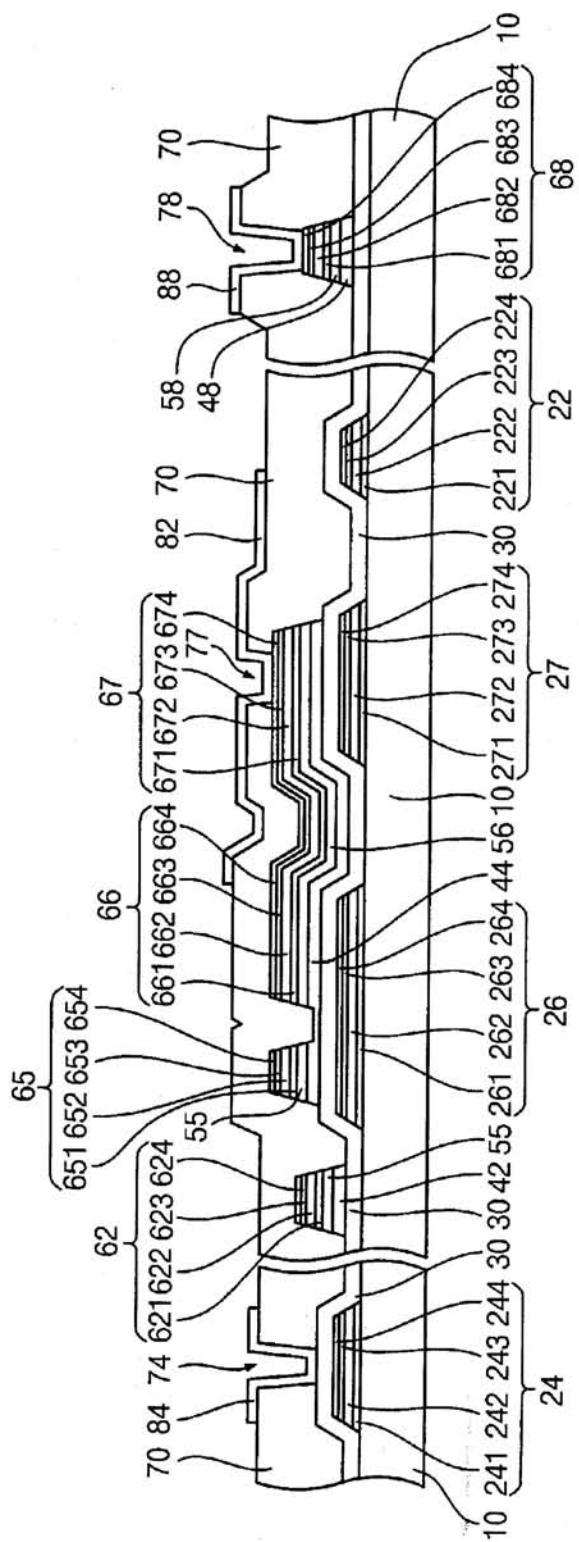

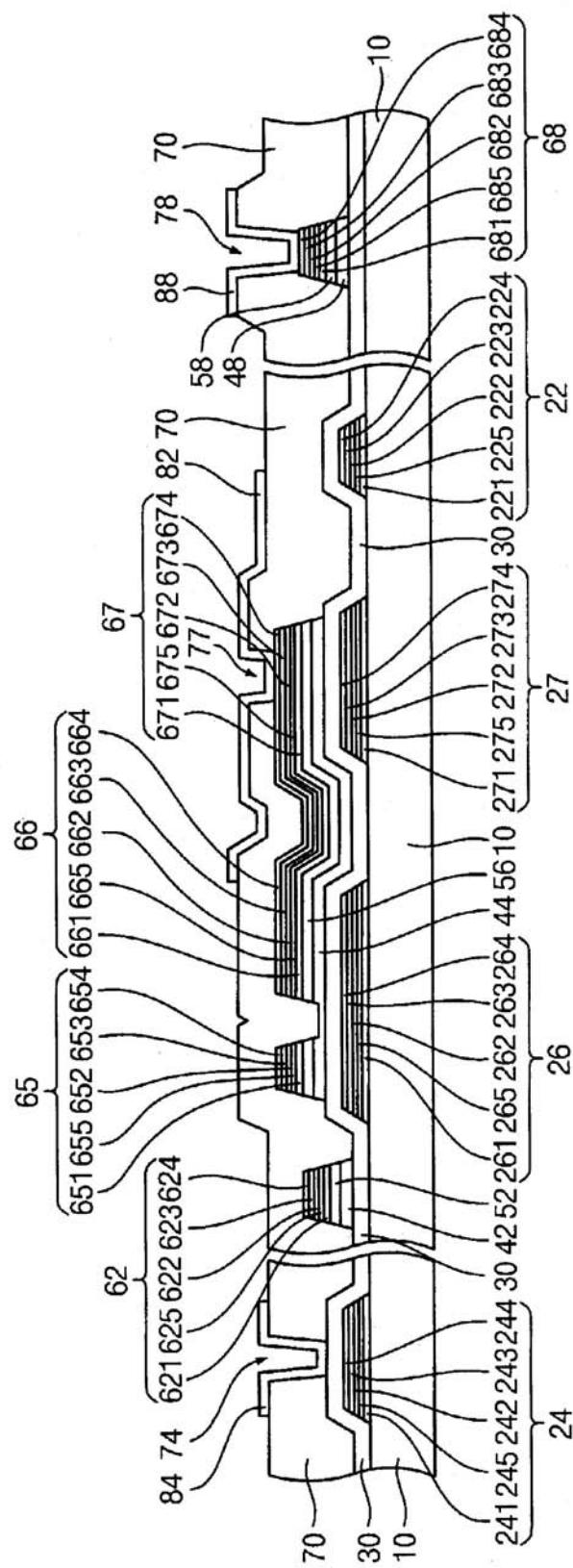

図8は本発明の一実施例による薄膜トランジスタ基板の配置図で、図9及び図10は、図8のB-B'に沿って切断した断面図である。図11、図14、図17、及び図20は、本発明の一実施例による薄膜トランジスタ基板の製造方法を順次に示す配置図である。図12、図13、図15、図16、図18、図19、図21、及び図22は、それぞれ図11、図14、図17、図20のB-B'に沿って切断した断面図である。

#### 【0067】

図11及び図12に図示すように、絶縁基板10上にゲート信号を伝達する複数のゲート配線が形成されている。ゲート配線は、横方向に伸びているゲート線22、ゲート線22の端に接続されていて外部回路からのゲート信号の印加を受けてゲート線に伝達するゲート端部24、ゲート線22に接続されたゲート電極26、蓄積電極(storage electrode)27、及び蓄積電極線28を含む。

#### 【0068】

各画素の蓄積電極27は、画素領域を横切って伸びている蓄積電極線28に電気的に接続されている。蓄積電極27は、後述する画素電極82と接続しているドレイン電極拡張部67と重畳(オーバーラップ)して画素の電荷保持能力を向上させる蓄積キャパシタを形成する。

#### 【0069】

このような蓄積電極27及び蓄積電極線28の形状及び配置等は多様な形態に変形してもよく、ゲート配線ではない他の配線と共に形成してもよい。又、画素電極82とゲート線22の重畳によって発生する蓄積容量(storage capacitance)が充分な場合には形成しなくてもよい。

#### 【0070】

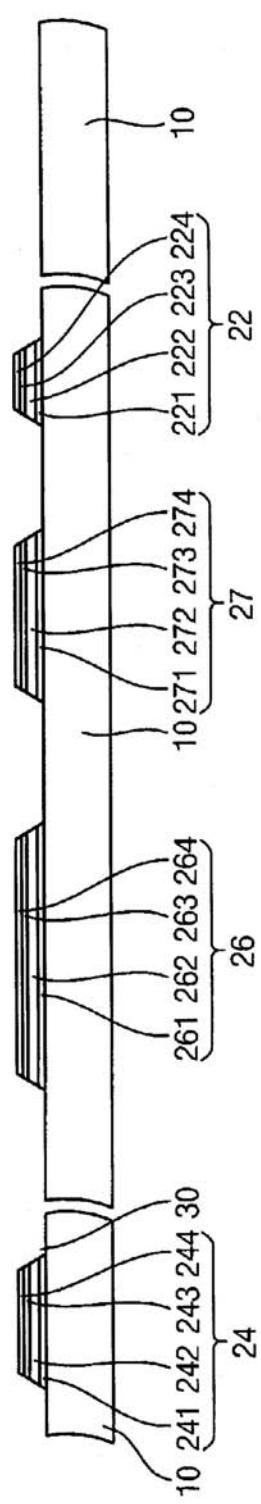

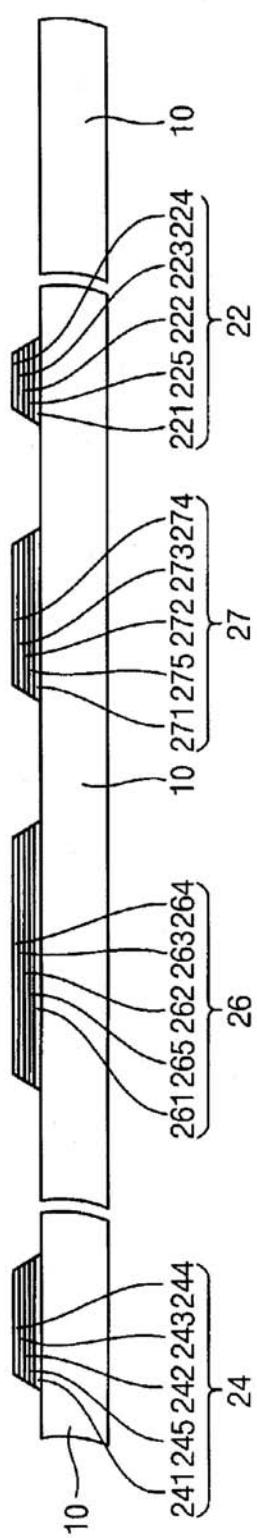

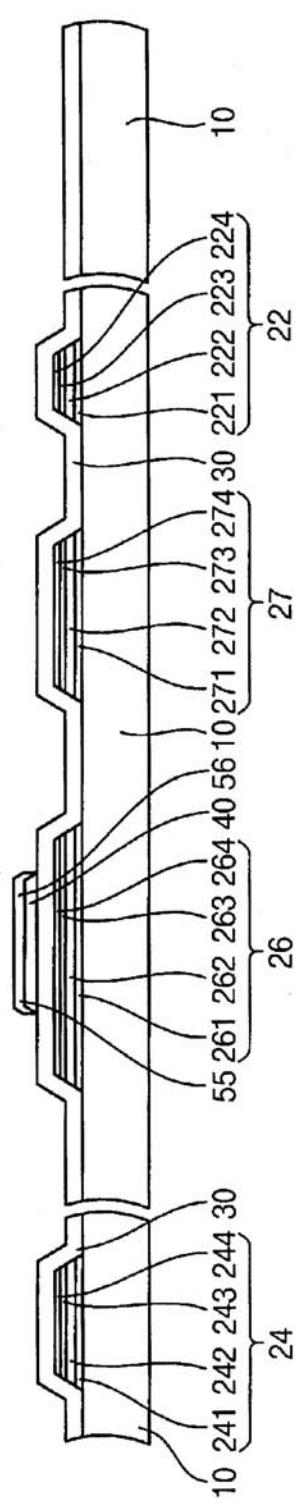

図9に図示すように、ゲート配線22、24、26、27は、バリア膜221、241、261、271、銅(Cu)又は銅合金からなる銅導電膜222、242、262、272、銅窒化物、又は銅酸化物、又は銅酸窒化物を含む中間膜223、243、263、273、及びキャッピング膜224、244、264、274の4層多重膜で形成されている。又、図面に図示されていないが、蓄積電極線28も他のゲート配線22、24、26、27と同じ構造を有する。以下に説明する多重膜構造のゲート配線には、蓄積電極線28も含まれ、他のゲート配線22、24、26、27の多層構造上の特徴が同様に用いられる。

#### 【0071】

10

20

30

40

50

このような多重膜構造のゲート配線 22、24、26、27、28には、前述した本発明の一実施例による配線構造が用いられる。ここで、バリア膜 221、241、271は、上部の銅導電膜 222、242、262、272の絶縁基板 10に対する接着を補助し、絶縁基板 10を構成する物質と銅導電膜 222、242、262、272を構成する物質が互いに拡散しないようにする。

#### 【0072】

又、銅導電膜 222、242、262、272とキャッピング膜 224、244、264、274との間に位置する中間膜 223、243、263、273は、電子交換によるガルバニック腐食を防止して、配線パターニング時に発生するおそれがある上部キャッピング膜 224、244、264、274のオーバーハング等配線プロファイル不良を防止する。

#### 【0073】

一方、ゲート配線 22、24、26、27、28のすぐ下の絶縁基板 10は、一括エッチングによる銅イオンの浸透が大きく問題にならないので、バリア膜 221、241、261、271をキャッピング膜 224、244、264、274の場合のように、銅導電膜 222、242、262、272等と一括エッチングができる物質を用いてもよい。

#### 【0074】

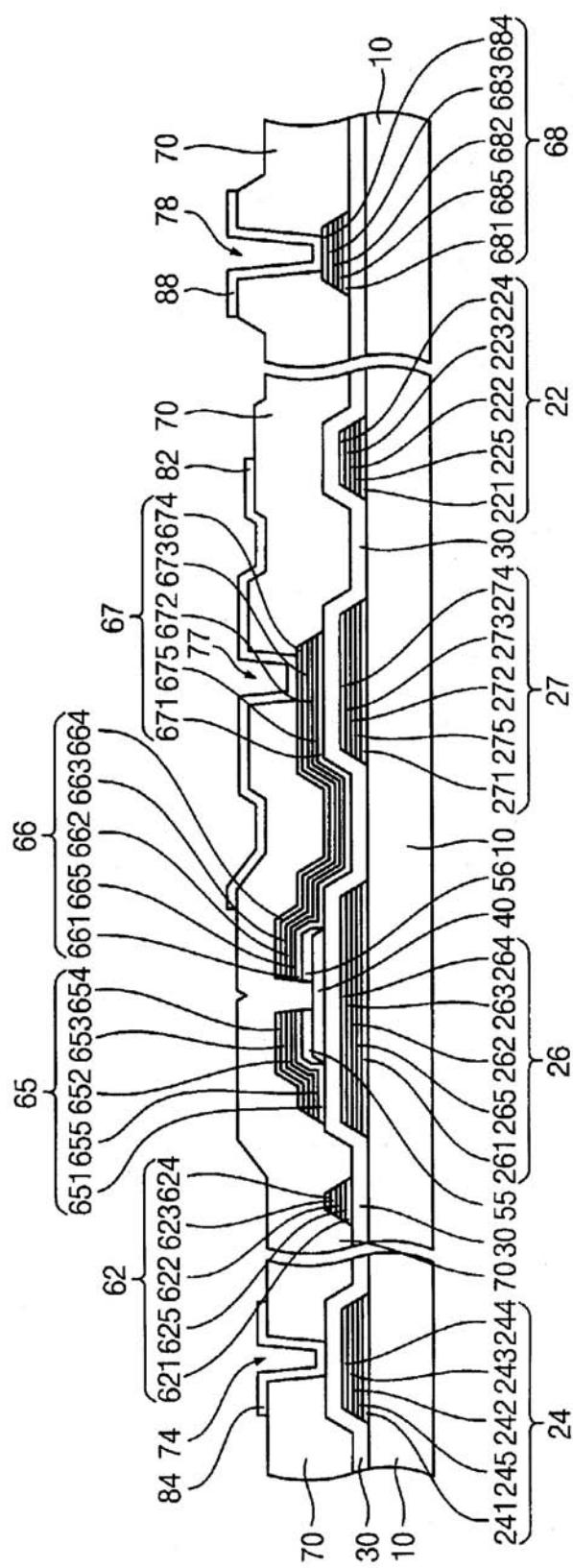

本実施例のゲート配線 22、24、26、27、28構造は、バリア膜 221、241、261、271、銅導電膜 222、242、262、272、中間膜 223、243、263、273、及びキャッピング膜 224、244、264、274の4層構造として説明した。これは、図1を参照して説明した配線構造と同様である。

#### 【0075】

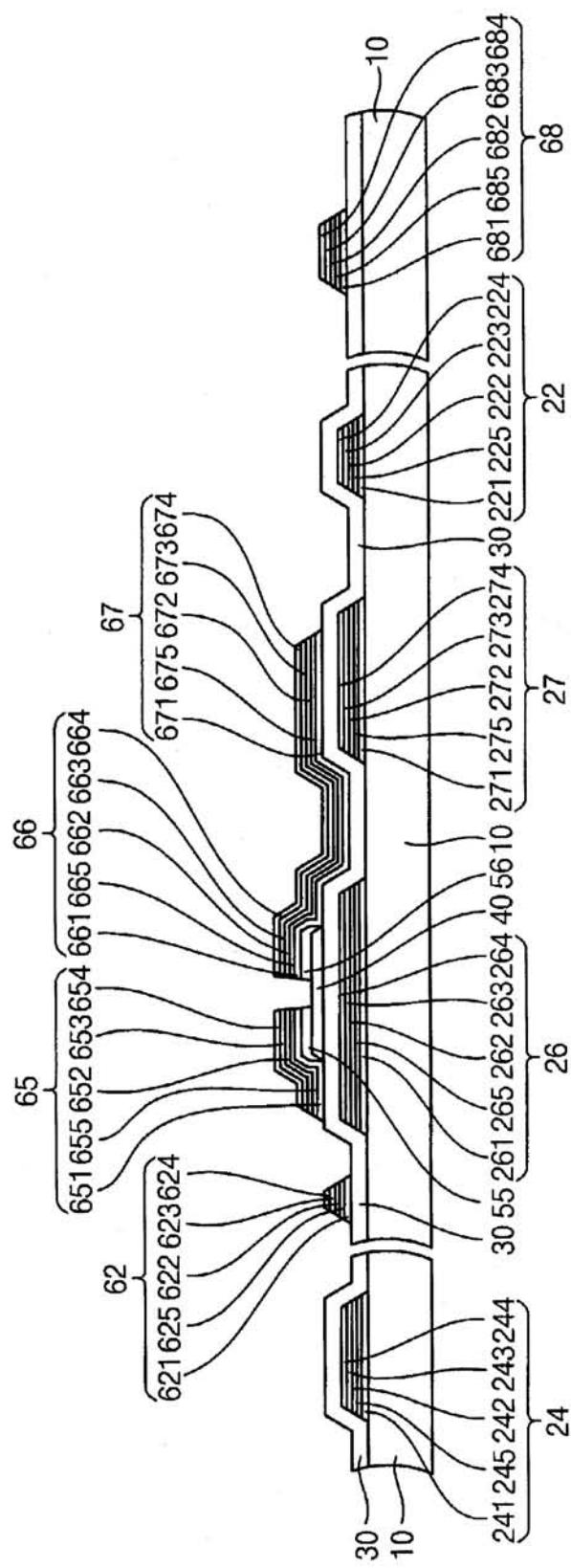

一方、図10に示すように、ゲート配線 22、24、26、27、28は、バリア膜 221、241、261、271、中間膜 225、245、265、275、銅導電膜 222、242、262、272、中間膜 223、243、263、273、及びキャッピング膜 224、244、264、274の5層構造で形成してもよい。これは、図7を参照して説明した配線構造と同じであり、その形成方法も前述したものと同様である。

#### 【0076】

基板 10、ゲート配線 22、24、26、27、28の上には窒化シリコン(SiNx)等からなるゲート絶縁膜 30が形成されている。

#### 【0077】

ゲート電極 26のゲート絶縁膜 30の上面には、水素化アモルファスシリコン等の半導体からなる半導体層 40が島形状に形成されており、半導体層 40の上面にはシリサイド又はn型不純物が高濃度でドーピングされたn<sup>+</sup>水素化アモルファスシリコン等の物質からなるオーミックコンタクト層 55、56がそれぞれ形成されている。

#### 【0078】

オーミックコンタクト層 55、56及びゲート絶縁膜 30上には、データ配線 62、65、66、67、68が形成されている。データ配線 62、65、66、67、68は、縦方向に形成されゲート線 22と交差して画素を定義するデータ線 62、データ線 62の分枝でオーミックコンタクト層 55の上面まで延びているソース電極 65、データ線 62の一側端に接続され外部からの画像信号の印加を受けるデータ端部 68、ソース電極 65と分離されており、ゲート電極 26又は薄膜トランジスタのチャンネル部に対してソース電極 65の反対側のオーミックコンタクト層 56の上面に形成されているドレイン電極 66、ドレイン電極 66から延びて蓄積電極 27と重畠する広い面積のドレイン電極拡張部 67を含む。

#### 【0079】

図9を参照すると、このようなデータ配線 62、65、66、67、68は、ゲート配線 22、24、26、27のように、バリア膜 621、651、661、671、681、銅(Cu)又は銅合金からなる銅導電膜 622、652、662、672、682、銅

窒化物を含む中間膜 623、653、663、673、683、及びキャッピング膜 624、654、664、674、684の4層多重膜構造を有する。このような多重膜構造のデータ配線 62、65、66、67、68には、図1を参照して説明した本発明の一実施例による配線構造を適用する。

## 【0080】

ここで、バリア膜 621、651、661、671、681は、下部構造物、即ち、ここではオーミックコンタクト層 55、56とゲート絶縁膜 30に対する銅導電膜 622、652、662、672、682の接着力を補助し、オーミックコンタクト層 55、56とゲート絶縁膜 30を構成する物質と銅導電膜 622、652、662、672、682を構成する物質が互いに拡散しないようにする。

10

## 【0081】

又、後続工程であるデータ配線 62、65、66、67、68のウェットエッチング工程、特に、チャンネル部のソース電極 65、及びドレイン電極 66を形成するためのウェットエッチング工程時に、エッチング液に溶解した銅イオンが薄膜トランジスタのチャンネル部を構成する下部のオーミックコンタクト層 55、56やその下面の半導体層 40まで浸透して、薄膜トランジスタ特性が悪化することを防止する。又、銅導電膜 622、652、662、672、682とキャッピング膜 624、654、664、674、684との間に中間膜 623、653、663、673、683が位置して電子交換によるガルバニック腐食を防止する。

20

## 【0082】

又、図10を参照すると、データ配線 62、65、66、67、68は、ゲート配線 22、24、26、27のようにバリア膜 621、651、661、671、681、中間膜 625、655、665、675、685、銅(Cu)又は銅合金からなる銅導電膜 622、652、662、672、682、銅室化物を含む中間膜 623、653、663、673、683、及びキャッピング膜 624、654、664、674、684の5層多重膜構造を有してもよい。このような多重膜構造のデータ配線 62、65、66、67、68には、図7を参照して説明した本発明の他の実施例による配線構造を適用する。

## 【0083】

ソース電極 65は半導体層 40と少なくとも一部分が重畠し、ドレイン電極 66はゲート電極 26を中心としてソース電極 65と対向して、半導体層 40と少なくとも一部分が重畠する。ここで、オーミックコンタクト層 55、56は、その下面の半導体層 40と、その上面のソース電極 65及びドレイン電極 66の間に存在して接触抵抗を低下させる役割を果たす。

30

## 【0084】

ドレイン電極拡張部 67は蓄積電極 27と重畠するように形成され、蓄積電極 27とゲート絶縁膜 30を挟んで蓄積容量が形成される。蓄積電極 27を形成しない場合、ドレイン電極拡張部 27も形成しない。

30

## 【0085】

ここで、ゲート電極 26、その上に形成された半導体層 40、オーミックコンタクト層 55、56、及びソース電極 65とドレイン電極 66が薄膜トランジスタを構成し、この際、半導体層 40は薄膜トランジスタのチャンネル部を構成する。

40

## 【0086】

データ配線 62、65、66、67、68、及びこれらが遮らない半導体層 40の上部には、保護膜 70が形成されている。保護膜 70は、例えば、平坦化特性に優れて感光性を有する有機物質、プラズマ化学気相成長(PECVD)で形成されるa-Si:C:O、a-Si:O:F等の低誘電率絶縁物質、又は無機物質である窒化シリコン(SiNx)等で形成してもよい。又、保護膜 70を有機物質で形成する場合には、ソース電極 65とドレイン電極 66との間の半導体層 40が露出した部分に保護膜 70の有機物質が接触することを防止するために、有機膜の下部に窒化シリコン(SiNx)又は酸化シリコン(SiO<sub>2</sub>)からなる絶縁膜(図示せず)が追加で形成してもよい。

50

## 【0087】

保護膜70には、ドレイン電極拡張部67及びデータ線端部68をそれぞれ露出させるコンタクトホール77、78が形成されており、保護膜70とゲート絶縁膜30にはゲート線端部24を露出させるコンタクトホール74が形成されている。保護膜70上には、コンタクトホール77を通じてドレイン電極66と電気的に接続され、画素に位置する画素電極82が形成されている。データ電圧が印加された画素電極82は、上部表示板の共通電極と共に電場を生成することにより、画素電極82と共に共通電極との間の液晶層の液晶分子の配列を決定する。

## 【0088】

又、保護膜70上には、コンタクトホール74、78を通じてそれぞれゲート端部24及びデータ端部68と接続されている補助ゲート端部84及び補助データ端部88が形成されている。画素電極82と補助ゲート及びデータ端部84、88はITOからなる。前述した本発明の一実施例による薄膜トランジスタ基板は、液晶表示装置等に適用してもよい。

## 【0089】

さらに、本発明の一実施例による薄膜トランジスタ基板の製造方法について、図11乃至図22を参照して詳細に説明する。

## 【0090】

まず、図11及び図12に示すように、絶縁基板10上にバリア膜221、241、261、271、銅又は銅合金を含む銅導電膜222、242、262、272、銅窒化物、又は銅酸化物、又は銅酸窒化物を含む中間膜223、243、263、273、及びキャッピング膜224、244、264、274を、例えば、スパッタリング等の方法で順次に積層したゲート多重膜を形成する。その後、ゲート多重膜の上面にゲート配線22、24、26、27、28を定義するフォトレジストパターンを形成し、これをエッチングマスクとしてキャッピング膜224、244、264、274、中間膜223、243、263、273、銅導電膜222、242、262、272、及びバリア膜221、241、261、271を順次にウェットエッチングする。

## 【0091】

又は、キャッピング膜224、244、264、274、中間膜223、243、263、273、及び銅導電膜222、242、262、272を順次にウェットエッチングした後、フォトレジストパターンをマスクとして、又はフォトレジスト除去後、キャッピング膜224、244、264、274、中間膜223、243、263、273、及び銅導電膜222、242、262、272の金属膜パターンを利用してバリア膜221、241、261、271をドライエッチングして、フォトレジストパターンを除去してもよい。これによって、ゲート線22、ゲート電極26、ゲート端部24、蓄積電極27、及び蓄積電極線28を含むゲート配線22、24、26、27、28が完成する。

## 【0092】

このようなゲート配線22、24、26、27、28の形成方法としては、図3乃至図6を参照して説明した本発明の一実施例による配線形成方法が同様に適用される。即ち、中間膜223、243、263、273は、下部の銅導電膜222、242、262、272の形成後、銅をターゲットとするチャンバー内で窒素ガス又は酸素ガス雰囲気で反応性スパッタリングを行って形成することができ、中間膜223、243、263、273の一部は銅導電膜222、242、262、272の形成後、真空破壊を導入して自然酸化膜等を用いて形成してもよい。

## 【0093】

又、図13を参照すると、ゲート配線22、24、26、27、28は、バリア膜221、241、261、271、中間膜225、245、265、275、銅導電膜222、242、262、272、中間膜223、243、263、273、及びキャッピング膜224、244、264、274の5層構造で形成してもよい。これは、図7を参照して説明した配線構造と同じであり、その形成方法も前述したものと同じである。

10

20

30

40

50

## 【0094】

即ち、バリア膜 221、241、261、271の形成後、銅をターゲットとするチャンバー内でアルゴンガスと共に窒素又は酸素雰囲気の反応性スパッタリングを行って、所定の厚みの中間膜 225、245、265、275を形成した後、チャンバー内の窒素又は酸素ガスの流入を遮断して、アルゴンガス雰囲気でスパッタリングを行って、銅導電膜 222、242、262、272を形成した後、更にチャンバー内に窒素又は酸化ガスをアルゴンガスと共に注入して、中間膜 223、243、263、273を形成する。中間膜 223、243、263、273の一部は、他の方法で形成してもよいが、中間膜 225、245、265、275及び銅導電膜 222、242、262、272を形成した後、真空破壊を行って銅導電膜 222、242、262、272上に形成された自然酸化膜等を用いてもよい。10

## 【0095】

完成したゲート配線 22、24、26、27、28は、図1の実施例で説明したように、ウェットエッチング及びフォトレジスト膜除去工程で銅導電膜 222、242、262、272とキャッピング膜 224、244、264、274との間に介在している中間膜 223、243、263、273、又はバリア膜 221、241、261、271と銅導電膜 222、242、262、272との間に形成された中間膜 225、245、265、275が電子の移動を遮断して、ガルバニック腐食形成を抑制するので、配線が側面腐食なしに鮮明に形成され、側面プロファイルがオーバーハング等を示すことなく、良好なテーパー角を有する。20

## 【0096】

その後、図14乃至図16に示すように、窒化シリコン等からなるゲート絶縁膜 30、真性アモルファスシリコン層、及びドーピングされたアモルファスシリコン層を、例えば、化学気相成長法(CVD)を用いて、それぞれ 1500乃至 5000、500乃至 2000、300乃至 600 の厚みに連続蒸着し、真性アモルファスシリコン層とドーピングされたアモルファスシリコン層をフォトリソグラフィして、ゲート電極 24の上面のゲート絶縁膜 30 上に一部が島形状の半導体層 40 とドーピングされた半導体層 55 を形成する。

## 【0097】

その後、図17及び図18を参照すると、ゲート絶縁膜 30 及びオーミックコンタクト層 50 上にスパッタリング等の方法でバリア膜 621、651、661、671、681、銅又は銅合金を含む銅導電膜 622、652、662、672、682、銅窒化物、又は銅酸化物、又は銅酸窒化物を含む中間膜 623、653、663、673、683、及びキャッピング膜 624、654、664、674、684を順次に積層したデータ多重膜を形成する。30

## 【0098】

その後、データ多重膜の上部にデータ配線 62、65、66、67、68を定義するフォトレジストパターンを形成し、これをエッチングマスクとしてキャッピング膜 624、654、664、674、684、中間膜 623、653、663、673、683、銅導電膜 622、652、662、672、682、及びバリア膜 621、651、661、671、681を一括してエッチングする。又は、他の方式として、キャッピング膜 624、654、664、674、684、中間膜 623、653、663、673、683、及び銅導電膜 622、652、662、672、682をウェットエッチングした後、下部のバリア膜 621、651、661、671、681を露出する。その後、フォトレジストパターンをマスクとしてバリア膜 621、651、661、671、681をドライエッチングする。又は、フォトレジストマスク除去後、上部の配線パターンを利用してバリア膜 621、651、661、671、681をドライエッチングしてもよい。又、バリア膜 621、651、661、671、681とオーミックコンタクト層 55、56、及び半導体層 40 を同時にドライエッチングしてもよい。40

## 【0099】

これによって、ゲート線 22 と交差するデータ線 62、データ線 62 と接続されゲート電極 26 の上部まで延びているソース電極 65、データ線 62 の一側端に連結されているデータ端部 68、ソース電極 65 と分離されており、ゲート電極 26 を中心としてソース電極 65 と向かい合うドレイン電極 66 及びドレイン電極 66 から延びて蓄積電極 27 と重畳する広い面積のドレイン電極拡張部 67 を含むデータ配線 62、65、66、67、68 が完成する。

#### 【0100】

以上説明したデータ配線 62、65、66、67、68 の形成方法としては、本発明の一実施例による配線形成方法が同様に適用される。従って、完成したデータ配線 62、65、66、67、68 は、図 1 の実施例で説明したように、ウェットエッチング及びフォトレジスト膜除去工程で銅導電膜 622、652、662、672、682 とキャッピング膜 624、654、664、674、684 との間に介在されている中間膜 623、653、663、673、683 が電子の移動を遮断して、ガルバニック腐食形成を抑制するので、配線が側面腐食なしに鮮明に形成され、側面プロファイルがオーバーハング等を示すことなく、良好なテーパー角を有する。

#### 【0101】

又、図 19 を参照すると、ゲート配線 22、24、26、27 の場合と同様にデータ配線 62、65、66、67、68 の構造も 5 層構造にしてもよい。即ち、銅導電膜 622、652、662、672、682 とバリア膜 621、651、661、671、681 との間に中間膜 625、655、665、675、685 を追加形成する。中間膜 623、653、663、673、683 以外に、中間膜 625、655、665、675、685 が追加されるので、エッチング工程後、配線プロファイルがより改善することができる。このための配線形成方法は、図 7 を参照して説明したものと同じである。

#### 【0102】

その後、バリア膜 621、651、661、671、681 のドライエッチングに続いてデータ配線 62、65、66、67、68 で遮らないドーピングされた半導体層 50 をドライエッチングして、データ配線 62、65、66、67、68 をゲート電極 26 を中心にしてその両側にオーミックコンタクト層 55、56 を形成し、その間の半導体層 40 を露出させる。この際、バリア膜 621、651、661、671、681 のエッチングに用いた気体をドーピングされた半導体層 50 のドライエッチングにそのまま利用することができ、エッチング気体を換えて連続的にエッチングしてもよい。これによって、ゲート電極 26、その上に形成された半導体層 40、オーミックコンタクト層 55、56、及びソース電極 65 とドレイン電極 66 で構成され、ゲート電極 26 が半導体層 49 のチャネル部の下部に存在するボトムゲート方式の薄膜トランジスタが完成する。

#### 【0103】

その後、図 20 及び図 22 に図示するように、平坦化特性に優れ感光性を有する有機物質、プラズマ化学気相成長 (PECVD) で形成される a-Si : C : O、a-Si : O : F 等の低誘電率の絶縁物質、又は、無機物質の窒化シリコン (SiNx) 等を単一層又は複数層で形成して保護膜 70 を形成する。

#### 【0104】

その後、フォトリソグラフィ工程でゲート絶縁膜 30 と共に保護膜 70 をパターニングして、ゲート端部 24、ドレイン電極拡張部 67、及びデータ端部 68 を露出させるコンタクトホール 74、77、78 を形成する。この際、感光性を有する有機膜である場合には、フォト工程のみでコンタクトホールを形成してもよく、ゲート絶縁膜 30 と保護膜 70 に対して実質的に同じエッチング比を有するエッチング条件で実施することが望ましい。

#### 【0105】

最後に図 8 及び図 10 に示すように、ITO 膜を蒸着してフォトエッチングしてコンタクトホール 77 を通じてドレイン電極 66 と接続される画素電極 82 とコンタクトホール 74、78 を通じてゲート端部 24 及びデータ端部 68 とそれぞれ接続される補助ゲート

10

20

30

40

50

端部 84 及び補助データ端部 88 を形成する。

【0106】

本実施例では半導体層が島形状に形成されており、データ配線と互いに異なるパターンを有する薄膜トランジスタ基板及びその製造方法について説明したが、半導体層とデータ配線が実質的に同じパターンを有する薄膜トランジスタ基板及びその製造方法についても同様に適用することができる。これについて、図23乃至図25を参照して説明する。

【0107】

図23は、本発明の一実施例による薄膜トランジスタ基板の変形例の配置図である。図24及び図25は、図23のB-B'に沿って切断した断面図である。

【0108】

図23乃至図25に示すように、本変形例では半導体層42、44、48とオーミックコンタクト層52、55、56、58がデータ配線62、65、66、67、68とほぼ同じパターンの線形で形成されていることを除いては、図11乃至図13とほぼ同じ構造を有する。但し、オーミックコンタクト層52、55、56、58は、データ配線62、65、66、67、68と実質的に同じパターンであるが、半導体層44はチャンネル部で分離されずに接続されている点が異なる。このような薄膜トランジスタ基板の製造方法は、互いに異なるマスクを用いて半導体層とデータ配線を形成した本発明の一実施例とは異なり、スリット又は半透過膜を含む1つのマスクを利用して、データ配線とオーミックコンタクト層及びデータ配線をパテーニングする。

【0109】

その他の工程は、本発明の一実施例による製造方法と実質的に同じであり、当業者の立場で容易に実施することができるので、それに対する具体的な説明は省略する。

【産業上の利用可能性】

【0110】

本発明の一実施例による配線構造及び配線形成方法によると、下部構造物に対する銅導電膜の良好な接着力を維持しながら、銅導電膜の化学的反応による酸化又は腐食を防止することができる。又、パテーニング工程で銅導電膜の選択的腐食によるオーバーハング現象を防止し、良好な側面プロファイルを形成することにより、低抵抗銅配線の信頼性を確保することができる。

【0111】

以上、本発明の実施例によって詳細に説明したが、本発明はこれに限定されず、本発明が属する技術分野において通常の知識を有するものであれば本発明の思想と精神を離れることなく、本発明を修正または変更できる。

【図面の簡単な説明】

【0112】

【図1】本発明の一実施例による薄膜トランジスタ配線構造を示す図である。

【図2】多重膜配線構造のパターンプロファイル不良を示す図である。

【図3】本発明の一実施例による薄膜トランジスタ配線形成方法の工程ステップ別断面図である。

【図4】本発明の一実施例による薄膜トランジスタ配線形成方法の工程ステップ別断面図である。

【図5】本発明の一実施例による薄膜トランジスタ配線形成方法の工程ステップ別断面図である。

【図6】本発明の一実施例による薄膜トランジスタ配線形成方法の工程ステップ別断面図である。

【図7】本発明の他の実施例による薄膜トランジスタ配線構造を示す図である。

【図8】本発明の一実施例による薄膜トランジスタ基板の配置図である。

【図9】図8のB-B'に沿って切断した断面図である。

【図10】図8のB-B'に沿って切断した断面図である。

【図11】本発明の一実施例による薄膜トランジスタ基板の製造方法を順次に示す配置図

10

20

30

40

50

である。

【図12】図11のB-B'に沿って切断した断面図である。

【図13】図11のB-B'に沿って切断した断面図である。

【図14】本発明の一実施例による薄膜トランジスタ基板の製造方法を順次に示す配置図である。

【図15】図14のB-B'に沿って切断した断面図である。

【図16】図14のB-B'に沿って切断した断面図である。

【図17】本発明の一実施例による薄膜トランジスタ基板の配置図である。

【図18】図17のB-B'に沿って切断した断面図である。

【図19】図17のB-B'に沿って切断した断面図である。

【図20】本発明の一実施例による薄膜トランジスタ基板の配置図である。

【図21】図20のB-B'に沿って切断した断面図である。

【図22】図20のB-B'に沿って切断した断面図である。

【図23】本発明の一実施例による薄膜トランジスタ基板の変形例の配置図である。

【図24】図23のB-B'に沿って切断した断面図である。

【図25】図23のB-B'に沿って切断した断面図である。

【図26】本発明のような配線構造で中間膜構成の存在を検出することができる原理を説明する図である。

#### 【符号の説明】

【0113】

10 絶縁基板

22 ゲート線

24 ゲート端部

26 ゲート電極

27 蓄積電極

28 蓄積電極線

30 ゲート絶縁膜

40 半導体層

55、56 オームикコンタクト層

62 データ線

65 ソース電極

66 ドレイン電極

67 ドレイン電極拡張部

68 データ端部

70 保護膜

82 画素電極

10

20

30

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【 図 2 1 】

【 図 2 2 】

【図23】

【図24】

【図25】

【図26】

---

フロントページの続き

(72)発明者 金 度 賢

大韓民国ソウル特別市永登浦区堂山洞5街7-2 ユウォン2次アパートメント204棟1002号

(72)発明者 金 柄 範

大韓民国大田広域市儒城区智足洞 ヨルメマウル5団地502棟1004号

(72)発明者 鄭 敝 午

大韓民国京畿道水原市靈通区網浦洞 東水原L Gヴィレッジ2次201棟203号

(72)発明者 李 俊 泳

大韓民国京畿道龍仁市器興邑甫羅里 民俗マウル双龍アパートメント101棟1804号

(72)発明者 康 盛 旭

大韓民国ソウル特別市瑞草区瑞草洞1357-63番地202戸

(72)発明者 悲 良 浩

大韓民国京畿道水原市勸善区谷伴亭洞4 プロック13ロットギボアートヴィル204号

F ターム(参考) 5F033 GG03 HH12 HH20 HH22 HH32 MM08 MM13 MM19 PP15 PP16

QQ08 QQ11 QQ19 QQ21 VV06 VV15 XX10 XX14 XX17 XX18

5F110 AA03 AA26 AA28 BB01 CC07 DD02 EE01 EE02 EE04 EE06

EE23 EE44 FF03 FF29 GG02 GG15 GG25 GG35 GG44 HK01

HK02 HK04 HK05 HK06 HK09 HK16 HK22 HK33 HK34 HL07

HL22 HM03 HM04 HM12 NN03 NN22 NN23 NN24 NN27 NN35

NN72 NN73 QQ04 QQ05 QQ09