(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6013336号

(P6013336)

(45) 発行日 平成28年10月25日(2016.10.25)

(24) 登録日 平成28年9月30日(2016.9.30)

|                |              |

|----------------|--------------|

| (51) Int.Cl.   | F 1          |

| HO 1 L 21/3205 | (2006.01)    |

| HO 1 L 21/768  | (2006.01)    |

| HO 1 L 23/522  | (2006.01)    |

| HO 1 L 25/065  | (2006.01)    |

| HO 1 L 25/07   | (2006.01)    |

| HO 1 L         | 21/88        |

|                | Z            |

|                | HO 1 L 25/08 |

|                | HO 1 L 23/12 |

|                | 5 O 1 P      |

請求項の数 17 (全 13 頁) 最終頁に続く

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2013-528332 (P2013-528332)  |

| (86) (22) 出願日 | 平成23年9月9日(2011.9.9)           |

| (65) 公表番号     | 特表2013-538460 (P2013-538460A) |

| (43) 公表日      | 平成25年10月10日(2013.10.10)       |

| (86) 國際出願番号   | PCT/US2011/051027             |

| (87) 國際公開番号   | W02012/034034                 |

| (87) 國際公開日    | 平成24年3月15日(2012.3.15)         |

| 審査請求日         | 平成26年9月9日(2014.9.9)           |

| (31) 優先権主張番号  | 12/878,542                    |

| (32) 優先日      | 平成22年9月9日(2010.9.9)           |

| (33) 優先権主張国   | 米国(US)                        |

(73) 特許権者 591016172

アドバンスト・マイクロ・ディバイシズ・

インコーポレイテッド

ADVANCED MICRO DEVICES INCORPORATED

アメリカ合衆国、94088-3453

カリフォルニア州、サンノイベイル、ビィ・

オウ・ボックス・3453、ワン・エイ・

エム・ディ・ブレイス、メイル・ストップ

・68 (番地なし)

前置審査

最終頁に続く

(54) 【発明の名称】冗長シリコン貫通ビアを伴う半導体チップ

## (57) 【特許請求の範囲】

## 【請求項 1】

第1の端部および第2の端部を含む複数の第1の導電ビアを、第1の半導体チップの層内に形成するステップと、

不動態化層を前記層上および前記複数の第1の導電ビアのうち一部の第1の導電ビアの前記第1の端部上に形成するステップと、

導電ビア延長部を、前記不動態化層内であって、前記一部の第1の導電ビアの各々の前記第1の端部に形成するステップと、

一つの第1の導体パッドを、複数の前記導電ビア延長部および前記複数の第1の導電ビアのうち前記一部以外の第1の導電ビアの前記第1の端部とオーミック接觸するように形成するステップと、

を含む製造方法。

## 【請求項 2】

第3の端部および第4の端部を含む複数の第2の導電ビアを、前記層内に形成するステップと、

第2の導体パッドを、前記第3の端部とオーミック接觸するように形成するステップと、

を含む請求項1に記載の方法。

## 【請求項 3】

導体構造を、前記複数の第1の導電ビアの前記第2の端部とオーミック接觸するように

形成するステップを含む、請求項 1 に記載の方法。

**【請求項 4】**

前記導体構造は、再配線層構造を備える、請求項 3 に記載の方法。

**【請求項 5】**

入力 / 出力構造を、前記第 1 の導体パッドに結合するステップを含む、請求項 1 に記載の方法。

**【請求項 6】**

前記入力 / 出力構造は、はんだバンプまたは導電ピラーを備える、請求項 5 に記載の方法。

**【請求項 7】**

第 2 の半導体チップを前記第 1 の半導体チップ上に積層するステップを含む、請求項 1 に記載の方法。

10

**【請求項 8】**

前記第 1 の半導体チップを回路基板上に実装するステップを含む、請求項 1 に記載の方法。

**【請求項 9】**

前記複数の第 1 の導電ビアは、トレンチを前記第 1 の半導体チップ内に形成し、前記トレンチ内に導電材料を配置することにより形成される、請求項 1 に記載の方法。

**【請求項 10】**

第 1 の端部および第 2 の端部を含む複数の第 1 の導電ビアを、第 1 の側面および反対側の第 2 の側面を有する第 1 の半導体チップの層内に形成するステップと、

20

不動態化層を前記層上および前記複数の第 1 の導電ビアのうち一部の第 1 の導電ビアの前記第 1 の端部上に形成するステップと、

導電ビア延長部を、前記不動態化層内であって、前記一部の第 1 の導電ビアの各々の前記第 1 の端部に形成するステップと、

一つの第 1 の導体を、前記第 1 の側面に隣接させ、かつ、複数の前記導電ビア延長部および前記複数の第 1 の導電ビアのうち前記一部以外の第 1 の導電ビアの前記第 1 の端部とオーミック接触させて形成するステップと、

第 2 の導体を、前記第 2 の側面に隣接させ、かつ、前記複数の第 1 の導電ビアの前記第 2 の端部とオーミック接触させて形成するステップと、

30

を含む製造方法。

**【請求項 11】**

前記第 1 の導体は導体パッドを備え、前記第 2 の導体は再配線層構造を備える、請求項 10 に記載の方法。

**【請求項 12】**

入力 / 出力構造を、前記第 1 の導体に結合するステップを含む、請求項 10 に記載の方法。

**【請求項 13】**

前記入力 / 出力構造は、はんだバンプまたは導電ピラーを備える、請求項 12 に記載の方法。

40

**【請求項 14】**

第 2 の半導体チップを前記第 1 の半導体チップ上に積層するステップを含む、請求項 10 に記載の方法。

**【請求項 15】**

前記第 1 の導電ビアは、ポリマーコアと、前記ポリマーコアの周囲の導電性の被覆とを含む、請求項 1 に記載の方法。

**【請求項 16】**

前記第 1 の導電ビアは、ポリマーコアと、前記ポリマーコアの周囲の導電性の被覆とを含む、請求項 10 に記載の方法。

**【請求項 17】**

50

第1の端部と、第2の端部と、ポリマーコアと、前記ポリマーコアの周囲の導電性の被覆とを含む複数の第1の導電ビアを、第1の半導体チップの層内に形成するステップと、一つの第1の導体パッドを、前記複数の第1の導電ビアのうち一部の第1の導電ビアの前記第1の端部とオーミック接觸するように形成するステップと、

を含む製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、概して半導体処理に関し、より詳細にはシリコン貫通ビアを組み込む半導体チップおよびその製作方法に関する。 10

【背景技術】

【0002】

先般、半導体チップの設計者は、必要とされるパッケージ基板または回路基板の面積を付随して増やすことなしに機能を増やすために、多重の半導体ダイス（別名「ダイ」）の垂直な積層を始めた。こうした積層配置において近接するダイスを電気的に接続するために、様々な技術が用いられてきた。1つの技術では、1つのダイのコンタクトパッドから対応する隣接のダイのコンタクトパッドへと導くワイヤボンドの使用を含む。より最近になって導入された別の技術では、いわゆるシリコン貫通ビア（TSV）の使用を含む。一般的なTSVは、チップの主たる表面の一方または他方におけるなんらかの介在する導体パッドの有無に応じて、ほぼあるいはおそらく完全に半導体チップを貫通して延在する導電性のビアである。 20

【0003】

一般的な従来型のTSVは、半導体チップの対向する主たる表面の間の電気的な経路選択を提供する。一方の側面上において、従来型のTSVは、なんらかのタイプの入力／出力構造（I/O）に接続される。これはしばしば、フリップチップ実装のはんだリフロー工程の間にパッケージ基板とはんだ接合を形成するように設計されたはんだバンプである。TSVは、直接はんだバンプに接続されるのではなく、バンプパッドのような最外メタライゼーション構造などの、なんらかの介在する構造に接続される。TSVの他方または背面の端部は、一般的にはなんらかの中間の導体構造を介して、なんらかの形の背面I/O構造に接続される。従来型のTSVの配置は、単一のバンプパッドに金属学的に接合される単一のTSVを含む。 30

【0004】

従来型のTSVは、電力レベル、熱管理、ダイの寸法およびその他の要因によって強度が異なる、ジュール発熱およびエレクトロマイグレーションの問題にさらされている。TSVとバンプパッドとの1対1配置は、こうした環境的な問題点の影響を受ける。

【発明の概要】

【発明が解決しようとする課題】

【0005】

本発明は、前述の不都合の1つ以上の影響を克服または低減するものを提供することを目的とする。 40

【0006】

本発明の1つの態様によると、第1の複数の導電ビアを第1の半導体チップの層内に形成することを含む製造の方法が提供される。第1の複数の導電ビアは、第1の端部および第2の端部を含む。第1の導体パッドは、第1の複数の導電ビアの第1の端部とオーミック接觸して形成される。

【0007】

本発明の別の態様によると、第1の複数の導電ビアを第1の半導体チップの層内に形成することを含む製造の方法が提供される。第1の複数の導電ビアは、第1の端部および第2の端部を含む。第1の半導体チップは、第1の側面および第2の対向する側面を有する。第1の導体は、第1の側面に隣接して形成され、また、第1の複数の導電ビアの第1の 50

端部とオーミック接触して形成される。第2の導体は、第2の側面に隣接して形成され、また、第1の複数の導電ビアの第2の端部とオーミック接触して形成される。

#### 【0008】

本発明の別の態様によると、層を有する第1の半導体チップと、第1の半導体チップに結合された第1の導体パッドとを含む装置が提供される。第1の複数の導電ビアは、層を縦貫し、第1の端部および第2の端部を含む。第1の端部は、第1の導体パッドとオーミック接触して形成される。

#### 【0009】

本発明の前述のおよびその他の利点は、以下の詳細な説明を読み、そして図面を参照することで明らかになるであろう。

10

#### 【図面の簡単な説明】

#### 【0010】

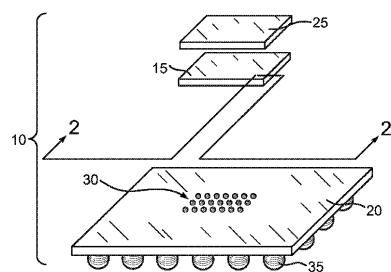

【図1】回路基板上に実装された半導体チップを含む半導体チップデバイスの例示的な実施形態の分解斜視図である。

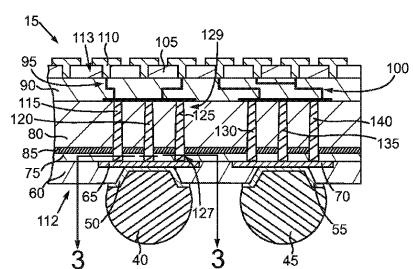

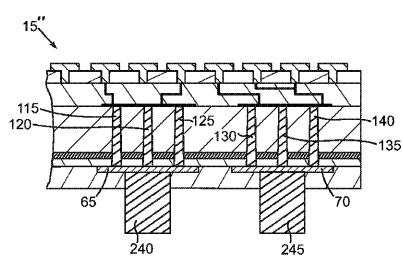

【図2】図1の断面2-2における断面図である。

【図3】図2の断面3-3における断面図である。

【図4】下層の導体パッドに接続される複数のTSVの、図3と同様であるが代替の例示的な実施形態を示す断面図である。

【図5】図3と同様であるが、多重のTSVが下層の導体パッドに接続される代替の例示的な実施形態を示す断面図である。

20

【図6】図2と同様であるが、複数のTSVが複数構成要素である半導体チップの代替の例示的な実施形態を示す断面図である。

【図7】例示的なリソグラフィ処理を受ける半導体チップの断面図である。

【図8】図7と同様であるが、例示的なTSVトレンチの形成を図示する断面図である。

【図9】図8の部分を拡大して図示する断面図である。

【図10】図8と同様であるが、例示的なTSV形成を図示する断面図である。

【図11】例示的な半導体チップの薄層化を図示する、図10と同様の断面図である。

【図12】薄層化後の半導体チップを図示する、図11と同様の断面図である。

【図13】図2と同様であるが、導電ピラーの入力/出力を有する複数のTSVを組み込む、代替の例示的な半導体チップを示す断面図である。

30

#### 【発明を実施するための形態】

#### 【0011】

2つ以上の積層された基板を含む半導体チップデバイスの様々な実施形態が本明細書において説明される。1つの例は、複数のTSVを有する少なくとも1つの半導体チップを含む。しかしながら、複数のTSVは、バンプまたはピラーパッドなどの所与の導体構造とオーミック接触して形成される。TSVとパッドとの接続の冗長性のために、所与のTSVに故障があってもパッドの回路を開放しないで済む。追加的な詳細が以下に説明される。

#### 【0012】

以下に説明する図面においては、同一の要素が2つ以上の図面に現れる場合には、参照番号は一般的に繰り返される。次に図面、具体的には図1をみると、回路基板20上に実装された半導体チップ15を含む半導体チップデバイス10の例示的な実施形態の分解斜視図が示されている。半導体チップ15は、積層された配置でその上に実装された1つ以上のその他の半導体チップを有するように適合される。このうちの1つが示され、符号を25とされている。半導体チップ15は、複数の相互接続構造を経由して回路基板20と電気的に接合していてもよく、相互接続構造は、導電ピラー、はんだ接合または他の種類の相互接続子であってもよい。この例示的な実施形態において、半導体チップ15は、複数のはんだ接合を経由して回路基板20と電気的に接合していてもよく、はんだ接合は、対応する回路基板20のはんだ構造30に金属学的に接合する半導体チップ15のそれぞれのはんだ構造(図示せず)から構成されていてもよい。回路基板20は、同様に、

40

50

複数の入力 / 出力構造により別の回路基板またはその他のデバイスなどの別の電子デバイスと電気的に接合していてもよい。この例示的な実施形態において、入力 / 出力構造は、はんだボール 35 のアレイから構成される。しかしながら、当業者であれば、ピングリッドアレイ、ランドグリッドアレイまたはその他の相互接続構造など、その他の種類の相互接続構造も同様に使用できることを理解するであろう。

#### 【0013】

本明細書において開示された半導体チップ 15 の例示的な構造は、特定の電子的機能に依存しない。このように、半導体チップ 15 および半導体チップ 25 は、エレクトロニクスにおいて用いられる任意の多種多様な異なる回路デバイス、例えば、マイクロプロセッサ、グラフィクスプロセッサ、組み合わされたマイクロプロセッサ / グラフィクスプロセッサ、特定用途向け集積回路、メモリデバイス、レーザなどの能動型光学デバイスなどであってよく、また、單一コアまたは多重コアであってよいし、さらに追加のダイスに水平に積層されてもよい。さらに、半導体チップ 15 および 25 の一方または両方は、なんらかの論理回路の有無によらず、インターポーラとして構成される可能性がある。したがって、用語「チップ」は、インターポーラを含む。半導体チップ 15 および 25 は、シリコンもしくはゲルマニウムなどのバルク半導体、または、シリコン・オン・インシユレータ材料などの絶縁材料上の半導体、または、他のチップ材料から構成されていてもよい。

10

#### 【0014】

本明細書において開示された半導体チップ 15 の例示的な構造は、特定の電子的回路基板機能に依存しない。このように、回路基板 20 は、半導体チップパッケージ基板、回路カード、または、実質的にいかなるその他のタイプのプリント回路基板であってよい。モノリシック構造を回路基板 20 のために使用することもできるが、より一般的な構成ではビルドアップ設計を使用する。この点で、回路基板 20 は、1 つ以上のビルドアップ層がその上に形成され、また、追加的な 1 つ以上のビルドアップ層がその下に形成される、中心コアから構成されていてもよい。コア自体は、1 つ以上の層の積層体から構成されてもよい。半導体チップパッケージ基板として実装される場合、回路基板 20 内の層の数は、4 層から 16 層以上まで変動することが可能である。とはいっても、4 層よりも少なくてもよい。いわゆる「コアレス」設計もまた使用されてもよい。回路基板 20 の層は、金属の相互接続子が組み入れられている、例えば様々な公知のエポキシなどの絶縁材料から構成されていてもよい。ビルドアップ以外の多重層構成も使用できる可能性がある。任意選択で、回路基板 20 は、パッケージ基板またはその他のプリント回路基板に適する、公知のセラミックまたはその他の材料から構成されていてもよい。回路基板 20 には、半導体チップ 15 および 25 と、例えば別の回路基板などの別のデバイスとの間に、電力、接地および信号伝達を提供するための多数の導体配線およびビアならびにその他の構造（図示せず）が備わっている。回路基板 20 は、図示されたボールグリッドアレイなどの入力 / 出力アレイにより、別のデバイス（図示せず）に電気的に接続されてもよい。ボールグリッドアレイは、それぞれのボールパッド（図示せず）に金属学的に結合される前述の複数のはんだボール 35 を含む。ボールパッド（図示せず）は、図示されていない、複数の相互接続配線およびビアならびにその他の構造により、回路基板 20 内の様々な導体パッドに相互接続される。

20

30

40

#### 【0015】

半導体チップ 15 の付加的な詳細は、図 2 と共に説明される。図 2 は、断面 2 - 2 における図 1 の断面図である。図 2 の説明の前に、図 1 の断面 2 - 2 は、半導体チップ 15 の小さい部分を通過することに注意されたい。そのことを踏まえて、次に図 2 に注目する。簡単に上述したように、半導体チップ 15 は、回路基板 20 のはんだ構造 30 に金属学的に接合するように設計された複数の入力 / 出力構造を含んでいてもよい。これらの例示的な相互接続構造のうちのいくつかは、それぞれはんだバンプ 40 および 45 から構成されていてもよい。はんだバンプ 40 および 45 は、例えば無鉛はんだまたは含鉛はんだなどの様々な種類のはんだから構成されていてもよい。適切な無鉛はんだの例は、錫 - 銀はんだ（およそ錫 97.3%、銀 2.7%）、錫 - 銅はんだ（およそ錫 99%、銅 1%）、錫

50

- 銀 - 銅はんだ（およそ錫 9 . 5 %、銀 3 %、銅 0 . 5 %）などを含む。含鉛はんだの例には、共晶点またはその近傍の組成比の錫 - 鉛はんだなどを含む。上述のように、はんだボール 4 0 および 4 5 は、所望に応じて、導電ピラーまたはその他の種類の相互接続構造に置き換えてよい。ここに、はんだバンプ 4 0 および 4 5 はそれぞれ、アンダーバンプメタル（UBM）構造 5 0 および 5 5 に結合される。UBM 構造 5 0 および 5 5 は、不動態化構造 6 0 の上および内部に形成され、これは、絶縁材料のモノリシック膜または積層膜であってもよい。UBM 構造 5 0 および 5 5 は、次に、導体構造すなわちパッド 6 5 および 7 0 に接続される。導体パッド 6 5 および 7 0 は、中間誘電体層とメタライゼーション層 7 5 であるもの的一部分を実際に形成する導体パッドから構成されていてもよい。図 2 は、導体パッド 6 5 および 7 0 、ならびに、メタライゼーション層 7 5 が、原寸に比例するように示されていないため、本質的にいくぶん概略的であることが理解されるべきである。いずれにしても、メタライゼーション層 7 5 に使用される中間誘電体層（図示せず）は、公知の二酸化ケイ素、その他の種類のケイ酸塩ガラス、低誘電率の誘電体膜などから構成されていてもよい。層 7 5 内のメタライゼーション構造は、金属パッド 6 5 および 7 0 、ならびに、UBM 構造 5 0 および 5 5 と同様に、例えば、銅、銀、ニッケル、白金、金、アルミニウム、パラジウム、これらの合金もしくは積層物などの様々な導体から構成されていてもよい。導体パッド 6 5 および 7 0 は、公知の、めっき、化学気相蒸着（CVD）などの材料配置技術、および、化学エッチング、レーザアブレーションなどによるリソグラフィなどのパターン形成技術によって形成されてもよい。

10

20

#### 【0016】

半導体チップ 1 5 は、バルク層またはレイヤ 8 0 と、多数のトランジスタ、キャパシタおよびその他の回路デバイスがそこに形成されていてもよいデバイス層またはレイヤ 8 5 と、メタライゼーション層またはレイヤ 7 5 とが存在してもよい点において重層的な構造である。メタライゼーション層 7 5 は、素子層 8 5 上に連続的に築きあげられた中間誘電体層の間に挟まれた一連のメタライゼーション層として形成されていてもよい。半導体チップ 1 5 は、半導体チップ 2 5 などの別の半導体チップをその上に積層するように設計されるため、背面のメタライゼーションスキームが提供される。この点において、再配線層（RDL）9 0 が半導体層 8 0 上に形成されていてもよい。RDL 9 0 は、ビルドアップまたは別の方で堆積された絶縁材料の 1 つ以上の層のモノリシックまたは積層構造であってもよく、絶縁材料は、同じまたは異なるレベル上にあってもよい 1 つ以上の RDL メタライゼーション構造と織り交ぜられている。この例示的な実施形態においては、RDL メタライゼーション構造 9 5 および 1 0 0 は視認可能である。絶縁または不動態化層 1 0 5 および複数の入力 / 出力構造 1 1 0 が RDL 9 0 の上に載せられてもよい。不動態化層 1 0 5 は、複数の絶縁膜のモノリシックまたは積層であってもよく、本明細書の他のところに記載した不動態化構造層 6 0 に使用されたものと同じ種類の材料から構成されていてもよい。入力 / 出力構造 1 1 0 は、導体ピラー、パッド、はんだ接合などであってもよく、図 2 に示す半導体チップ 2 5 との電気的接合を確立するために使用される。入力 / 出力構造 1 1 0 は、例えば、銅、銀、ニッケル、白金、金、アルミニウム、パラジウム、これらの合金もしくは積層物、はんだなどの様々な導体から構成されていてもよい。RDL 構造 9 5 および 1 0 0 は、入力 / 出力構造 1 1 0 のうちの 1 つ以上に接続してもよい。

30

40

#### 【0017】

半導体チップ 1 5 の対向する側面 1 1 2 と 1 1 3 との間、より詳細には、RDL 構造 9 5 および 1 0 0 と導体パッド 6 5 および 7 0 との間において、導電性の経路を確立するために、そのうちの 3 つが視認可能であり、符号 1 1 5 、 1 2 0 および 1 2 5 とされている複数の TSV が、半導体層 8 0 中に形成されて、デバイス層 8 5 およびメタライゼーション層 7 5 を通じて延び、RDL 構造 9 5 を導体パッド 6 5 に接続してもよい。このようにして、TSV のそれぞれの端部 1 2 7 は、導体パッド 6 5 に接触し、その反対の端部 1 2 9 は、RDL 構造 9 5 に接触する。同様の複数の TSV 1 3 0 、 1 3 5 および 1 4 0 は、RDL 構造 1 0 0 を導体パッド 7 0 に電気的に接続してもよい。本明細書において、用語

50

「T S V」および「半導体」は一般的に使用されており、ここで半導体層80は、シリコン以外の材料、またさらに、二酸化ケイ素、オルトケイ酸テトラエチルまたはその他などの絶縁材料から構成されていてもよいことが理解されるべきである。1つのパッドに対して単一のT S Vを使用する従来型の半導体チップ設計とは異なり、本明細書において開示された実施形態は、T S V 115、120および125、ならびに導体パッド65のように、所与の導体パッドに対して複数のT S Vを使用する。所与の導体パッドに対して多重のT S Vを使用することにより、熱ストレスの広がりを改善し、電流密度ひいてはジュール発熱を低減する。これにより、エレクトロマイグレーション寿命を増加できる。多重のT S Vを所与の導体パッドに接続することにより、例えば、ストレスマイグレーション破壊に起因する、T S Vのうちの1つの故障は、その他の残りのT S Vによって補償することができる。T S V 115、120、125、130、135および140は、例えば、銅、タンゲステン、グラフェン、アルミニウム、白金、金、パラジウム、これらの合金などの様々な材料から構成されていてもよい。クラッド構造が想定される。

#### 【0018】

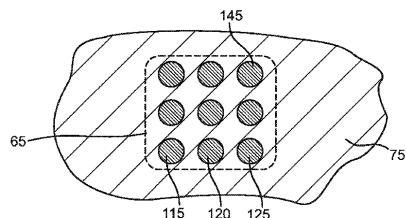

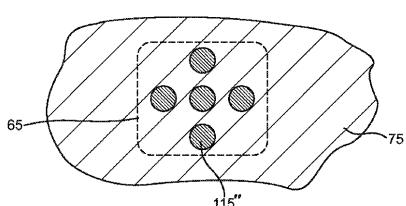

T S V 115、120および125の付加的な詳細は、図2における断面3-3での断面図である図3をここで参照することによって理解されるであろう。断面3-3に本格的に向かう前に、断面3-3は、導体パッド65近傍のT S V 115、120および125を通過することに注意されたい。ここで、図3に注目する。断面3-3の位置に起因して、T S V 115、120および125は断面として表れているが、下層の導体パッド65は、メタライゼーション層75によって覆い隠されており、したがって仮想線で示されていることに注意されたい。導体パッド65に接続されたT S Vは、3つのT S V 115、120および125よりも多数であってもよく、ここではまさしくさらに6つのT S Vを含んでいてもよく、まとめて符号145とされている。この例示的な実施形態において、T S V 115、120、125および145は、一般的に下層の導体パッド65の設置面をたどるアレイ状に配置されてもよい。しかしながら、当業者であれば、所与の導体パッドに接続されるT S Vの実際の空間的な配置は、導体パッド65が可能であるのと同様に様々な異なる形状をとってもよいことを理解するであろう。T S V 115、120、125および145の構成は、一般的にモノリシックであってもよいことにも注意されたい。しかしながら、また、図4に示す代替の実施形態と共に述べたように、他の配置もまた使用されてもよい。

#### 【0019】

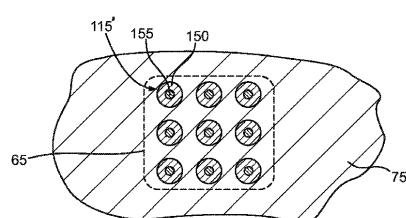

次に図4に注目すると、下層の導体パッド65に接続される複数のT S V 115'の、図3と同様であるが代替の例示的な実施形態を示す断面図である。ここに、導体パッド65は、実際にはメタライゼーション層75の下に配置されるために、ふたたび仮想線で示されている。ちょうど述べたように、所与のT S Vに対してモノリシック配置以外が使用されてもよい。このように、T S V 115'は、被覆150およびポリマーコア155から構成されていてもよい。被覆150は、銅、タンゲステン、グラフェン、アルミニウム、白金、金、パラジウム、これらの合金などから構成されていてもよい。ポリマーコア155は、所望に応じて、導電性または非導電性であってもよい、様々なポリマーから構成されていてもよい。例には、Namics 119、公知のエポキシなどを含む。これらのいわゆる環状T S Vは、めっきプロセスの間、電界発生を厳重に管理する方法による、入念に調整されためっきによって形成することができる。

#### 【0020】

上述のように、所与の導体パッドに関するT S Vの配置は、大きく変動することもある。この点で、次に図5に注目すると、図5は、図3と同様であるが代替の例示的な実施形態を示す断面図であり、多重のT S V 115''が下層の導体パッド65に接続される。導体パッド65は、メタライゼーション層75の下というその位置のために、ここでも仮想線で示されている。ここに、T S V 115''は、導体パッド65のいくらか矩形の設置面とは必ずしも一致しない十字様の配置で配置される。繰り返すが、非常に多様な配置が使用されて、さらに所与の導体パッドに関する多重のT S Vの技術的利点を得ることも

10

20

30

40

50

できる。

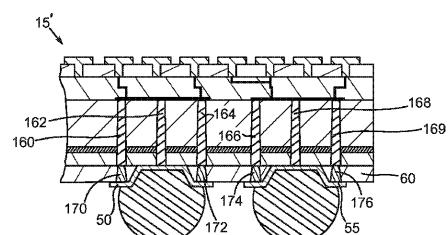

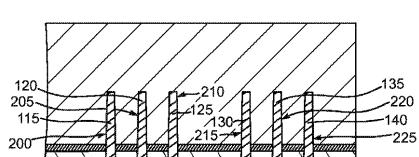

#### 【0021】

上述の例示的な実施形態において、頂部から底部まで連続的な構造として、すなわち、図2に示す半導体デバイス層85およびメタライゼーション層75を通過して、様々なTSVが製作されている。しかしながら、当業者であれば、多層構造がTSVに使用できることを理解するであろう。この点で、次に図6に注目すると、図6は、図2と同様であるが、半導体チップ15'の代替の例示的な実施形態を示す断面図であり、半導体チップ15'は、2~3の注目すべき例外を除いて、本明細書の他のところに記載した半導体チップ15と実質的に同様に構成されてもよい。ここに、複数のTSV160、162および164は、UBM構造50に接続してもよく、複数のTSV166、168および169は、UBM構造55に接続してもよい。しかしながら、TSV160および164は、それぞれTSV延長部170および172により接続し、TSV166および169は、それぞれTSV延長部174および176により接続する。ここで、TSV延長部170、172、174および176は、不動態化構造60を通り抜けて形成されていてもよい。

10

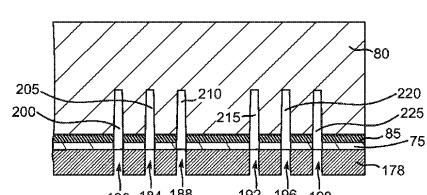

#### 【0022】

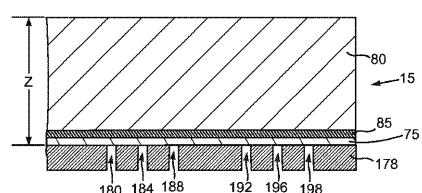

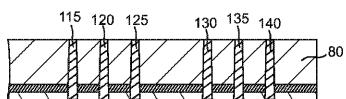

複数のTSVを形成するための例示的なプロセスは、ここで図7、8、9、10、11および12を参照することによって理解される場合があるが、最初に図7を参照すると、図7は、処理の準備段階における、半導体チップ15の断面図である。この段階において、デバイス層85は、数多くの公知の処理ステップを用いて製作されている。メタライゼーション層75はまた、TSVの形成前に、完全にもしくは部分的に完成してもよく、または、完成しなくてもよい。この時点で半導体チップ15は厚さZを有し、これは主に半導体層80によって占められ、図2に示すTSVおよびRDL90の形成後の最終的な厚さよりも大きい。この時点で、適切なリトグラフィマスク178がデバイス層85に適用され、リソグラフィでパターン形成されて、開口180、184、188、192、196および198を設けてもよい。これらは、引き続いて形成されるTSV115、120、125、130、135および140の所望の位置に対応する。マスク178は、公知のネガ型またはポジ型のいずれか一方のフォトレジスト材料から構成されていてもよい。任意選択で、非接触式またはハードマスクでさえも使用できる可能性がある。

20

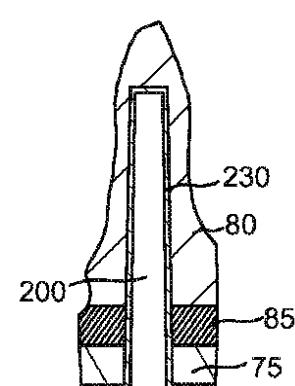

#### 【0023】

次に図8を参照すると、マスク178のパターン形成に続いて、半導体層80内に深型トレンチ200、205、210、215、220および225を形成するための材料除去プロセスが使用されてもよい。トレンチ200、205、210、215、220および225は、プラズマ支援を伴うもしくは伴わない化学エッチング、または、その他の材料除去技術により形成されていてもよい。過度の加熱を避けるために注意が必要であるが、レーザアブレーションを使用することもできる場合がある。言うまでもなく、マスク178内の開口180、184、188、192、196および198は、最終的に形成されるトレンチ200、205、210、215、220および225が所望の設置面を有するようにパターン形成される。後に形成されるTSVの組成に応じて、半導体層80への接着と、原子、分子、またはTSVの大部分の半導体層80およびデバイス層85内へのマイグレーション阻止との両方を容易にするために、トレンチ200、205、210、215、220および225内にライナ膜を適用する必要があるかもしれない。図9は、拡大されて示されているトレンチ200を示す断面図である。ライナ層230は、トレンチ200内に形成されて、トレンチ200の側壁だけでなく、素子層85の側壁も被覆されてもよい。ライナ層230は、二酸化ケイ素などの様々な材料から構成されていてもよい。公知のプラズマ支援を伴うもしくは伴わないCVD技術は、ライナ層230を堆積するために使用されてもよい。その他のトレンチ205、210、215、220および225に関しても同様になされてもよい。図8に示すマスク178は、灰化、溶媒の除去などによって、または、非接触式のマスクが使用される場合は剥離によって、ライナ層230の形成前または形成後に除去されてもよい。

30

40

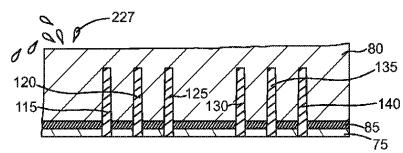

#### 【0024】

図7および図8に示すエッチマスク178の除去に続いて、TSV115、120、125、130、135および140は、図10に示すように、それぞれトレンチ200、205、210、215、220および225に形成されてもよい。本明細書の他のところに記載したように、TSV115、120、125、130、135および140は、所望に応じて完全な柱状体として、または、環状TSVとして、それぞれトレンチ200、205、210、215、220および225に形成されてもよい。めっきプロセスは、所望に応じて、単一工程バイアスめっきプロセスであってもよく、バイアスめっきプロセスに続く非バイアスシード層めっきプロセスであってもよい。

## 【0025】

TSV115、120、125、130、135および140が図2に示す後に形成されるRDL90内の構造とオーミック接触を確立可能にするために、半導体層80は、図11に示すように薄膜化されてもよい。ここに、半導体層80の部分227は、化学機械平坦化(CMP)により好都合に除去されてもよいが、その他の材料除去技術をCMPの代わりに、または、CMPと共に使用する可能性がある。TSV115、120、125、130、135および140を図12に示すように露出した状態で、図2に示すRDL90は、公知の絶縁材料堆積技術および導体材料堆積技術ならびにパターン形成技術を用いて製作されてもよく、これらの技術の数は、RDL90の複雑さに応じて、多重の層を超えることもあり得る。同様に、不動態化構造105および相互接続構造110の製作は、RDL90の形成の後に続いてもよい。

## 【0026】

ふたたび図1を参照すると、半導体チップ25は、半導体チップ15に積層され、そこへ、使用されるチップ間インターフェースの種類に応じて、はんだリフロー、圧着またはその他の技術により電気的に接続されていてもよい。当業者であれば、半導体チップ25は、所望に応じてウエハレベルまたはダイレベルにて、半導体チップ15上に積層する可能性があることを理解するであろう。半導体チップ15および25は、単独に、または、大量に回路基板20に実装されてもよい。

## 【0027】

本明細書において開示された例示的な実施形態のいずれかは、例えば、半導体、磁気ディスク、光学ディスクもしくはその他の記憶媒体などのコンピュータ読取可能媒体に、または、コンピュータデータ信号として、配置された命令として具現されてもよい。命令すなわちソフトウェアは、本明細書において開示された回路構造を統合および/またはシミュレート可能であってもよい。例示的な実施形態において、Cadence APD、Cadence Spectra、Encoreなどの電子設計自動化プログラムは、開示された回路構造を統合するために使用されてもよい。得られたコードは、開示された回路構造を製作するために使用されてもよい。

## 【0028】

図13は、図2と同様の断面図であるが、導電ピラー入力/出力240、245を有する複数のTSV115、120、125、130、135、140を組み込む、代替の例示的な半導体チップ15”を示す図である。TSV115、120、125は導体パッド65に接続されており、導体パッド65は導電ピラー240に接続されている。TSV130、135、140は導体パッド70に接続されており、導体パッド70は導電ピラー245に接続されている。

## 【0029】

本発明は種々の修正および代替的な形態の影響を受けやすい場合がある一方で、特定の実施形態が例示を目的として図面に示されそして本明細書において詳細に説明されてきた。しかし、本発明は開示されている特定の形態に限定されることを意図するものでないことが理解されるべきである。むしろ、本発明は、以下の添付の特許請求の範囲によって画定される本発明の精神及び範囲内に含まれる全ての修正、均等物および代替案に及ぶことになる。

10

20

30

40

【図1】

FIG. 1

【図3】

FIG. 3

【図2】

FIG. 2

【図4】

FIG. 4

【図5】

FIG. 5

【図6】

FIG. 6

【図9】

FIG. 9

【図7】

FIG. 7

【図10】

FIG. 10

【図8】

FIG. 8

【図 1 1】

FIG. 11

【図 1 2】

FIG. 12

【図 1 3】

FIG. 13

---

フロントページの続き

(51)Int.Cl. F I

H 0 1 L 25/18 (2006.01)

H 0 1 L 23/12 (2006.01)

(73)特許権者 508301087

エーティーアイ・テクノロジーズ・ユーエルシー

A T I T E C H N O L O G I E S U L C

カナダ、オンタリオ エル3ティー 7エックス6、マーカム、コマース バリー ドライブ

イースト 1

One Commerce Valley Drive East, Markham, Ontario, L3T 7X6 Canada

(74)代理人 100108833

弁理士 早川 裕司

(74)代理人 100111615

弁理士 佐野 良太

(74)代理人 100162156

弁理士 村雨 圭介

(72)発明者 ブライアン ブラック

アメリカ合衆国 78669 テキサス州、スパイスウッド、クリフ ビュー ドライブ 111

4

(72)発明者 マイケル ゼット. スー

アメリカ合衆国 78681 テキサス州、ラウンド ロック、ロック スプリング コーブ 9

09

(72)発明者 ガマル リファイ・アハメド

カナダ、エル3アール 5エス4、オンタリオ州、マークハム、ヴァインランド ストリート 1

7

(72)発明者 ジョー シーゲル

アメリカ合衆国 02445 マサチューセッツ州、ブルックライン、ビーコン ストリート 1

824、ユニット 4

(72)発明者 セス プレジアン

アメリカ合衆国 78735 テキサス州、オースティン、フォート ベントン ドライブ 54

08

審査官 長谷川 直也

(56)参考文献 特開2009-295616 (JP, A)

特開2010-135348 (JP, A)

特開2008-147224 (JP, A)

特開2006-237524 (JP, A)

特開2007-194669 (JP, A)

米国特許出願公開第2008/0258309 (US, A1)

特開2007-043154 (JP, A)

米国特許第06495454 (US, B2)

特開2001-326326 (JP, A)

米国特許第06461956 (US, B1)

(58)調査した分野(Int.Cl., DB名)

H 0 1 L 21 / 28 - 21 / 288, 21 / 3205 - 21 / 3213,

21/44 - 21/445、21/768、

23/12 - 23/15、23/52 - 23/522、

25/00 - 25/18、29/40 - 29/49、

29/872