**(19) 대한민국특허청(KR)**

**(12) 등록특허공보(B1)**

(51) Int. Cl.

H01L 21/265 (2006.01)

(45) 공고일자

2006년11월23일

(11) 등록번호

10-0647884

(24) 등록일자

2006년11월13일

|             |                   |             |                 |

|-------------|-------------------|-------------|-----------------|

| (21) 출원번호   | 10-2002-7006835   | (65) 공개번호   | 10-2002-0060980 |

| (22) 출원일자   | 2002년05월28일       | (43) 공개일자   | 2002년07월19일     |

| 심사청구일자      | 2005년06월22일       |             |                 |

| 번역문 제출일자    | 2002년05월28일       |             |                 |

| (86) 국제출원번호 | PCT/US2000/017271 | (87) 국제공개번호 | WO 2001/39273   |

| 국제출원일자      | 2000년06월23일       | 국제공개일자      | 2001년05월31일     |

(81) 지정국

국내특허 : 중국, 일본, 대한민국, 싱가포르,

EP 유럽특허 : 오스트리아, 벨기에, 스위스, 독일, 덴마크, 스페인, 프랑스, 영국, 그리스, 아일랜드, 이탈리아, 룩셈부르크, 모나코, 네덜란드, 포르투칼, 스웨덴, 핀란드, 사이프러스,

|            |            |             |        |

|------------|------------|-------------|--------|

| (30) 우선권주장 | 60/168,155 | 1999년11월29일 | 미국(US) |

|            | 09/497,320 | 2000년02월03일 | 미국(US) |

|           |                                                                            |

|-----------|----------------------------------------------------------------------------|

| (73) 특허권자 | 어드밴스드 마이크로 디바이시즈, 인코포레이티드<br>미국 캘리포니아 94088-3453 서니베일 원 에이 엠디 플레이스 메일 스텝68 |

|-----------|----------------------------------------------------------------------------|

|          |                                      |

|----------|--------------------------------------|

| (72) 발명자 | 가엠마가미아메드<br>미국캘리포니아95020길로이플로사웨이8295 |

|----------|--------------------------------------|

|                                          |

|------------------------------------------|

| 크리보카픽조란<br>미국캘리포니아95050산타클라라데바로나플레이스2321 |

|------------------------------------------|

|                                     |

|-------------------------------------|

| 스완슨브라이언<br>미국캘리포니아95125산호세엘렌애비뉴2131 |

|-------------------------------------|

(74) 대리인

박장원

심사관 : 이시근

전체 청구항 수 : 총 6 항

(54) 할로 이온주입법을 이용한 반도체 디바이스 제조 방법

(57) 요약

반도체 디바이스에 할로 이온 주입을 제공하는 방법 및 시스템이 개시된다. 상기 방법 및 시스템은 반도체 디바이스에 얇은 포토레지스트층을 제공하는 단계를 포함한다. 상기 방법 및 시스템은 반도체 디바이스의 적절한 영역에 할로 이온 주입을 제공하는 단계를 더 포함한다. 따라서, 본 발명에 따른 시스템 및 방법에서, 보다 얇은 프로파일을 가능하게 하는 포토

레지스트, 즉 DUV 포토레지스트가 사용된다. 이에 의해, 상기 포토레지스트 두께를 계획된 1000Å(현장에서)까지, 또는 공정이 허용하는 경우, 두께를 보다 얇게 할 수 있다. 상기 포토레지스트 두께로, 다른 높이 변수들을 고려하여, 소스 영역과 드레인 영역은 필요한 만큼만 개방될 수 있다. 45°각도에서, 상기 이온 주입은 목표 영역의 회로에 있는 모든 트랜지스터에 가해질 수 있을 뿐 아니라, 트렌치 에지에 위치하는 트랜지스터 에지에 대량의 도즈(도즈의 최대 3/4)를 이온 주입할 수 있다. 이에 의해, 또한 할로 공정의 규정에 의해 필요로 되는, 반대 종에 의한 상기 소스 드레인의 역 도핑을 최소화할 것이다. 0.18 $\mu$ m 이하의 기술들의 보다 작은 기하학적 구조들에서, 게이트 높이는 실제로는 유리하게 작용하고, 소스/드레인 영역의 원치않는 역 도핑을 줄이는데 도움을 준다. 이와 같이 하여, 상기 역 도핑은 절대적 최소로 유지될 수 있다. 마지막 장점은 보다 얇은 포토레지스트에 의해, 보다 작은 기하학적 구조들에 이온 주입을 제공할 수 있는 능력을 높일 수 있다는 것이다.

## 대표도

도 4

## 특허청구의 범위

### 청구항 1.

반도체 디바이스(400)에 할로 이온 주입을 제공하기 위한 방법에 있어서,

- (a) 상기 반도체 디바이스에 0.1 내지 0.2 $\mu$ m 두께의 얇은 포토레지스트층(402)을 제공하는 단계(308)와; 그리고

- (b) 상기 반도체 디바이스에 할로 이온 주입을 제공하는 단계(310)를 포함하며,

여기서, 상기 얇은 포토레지스트층은 상기 할로 이온 주입을 위한 마스크로서 사용되는 것을 특징으로 하는 할로 이온 주입 제공 방법.

### 청구항 2.

제 1 항에 있어서,

상기 포토레지스트층(402)은 원자외선(DUV) 층을 포함하는 것을 특징으로 하는 할로 이온 주입 제공 방법.

### 청구항 3.

제 1 항 또는 제 2 항에 있어서,

상기 포토레지스트층은 상기 반도체 디바이스(400)의 활성 영역의 전체가 아닌 전체에 가까운 부분을 덮는 것을 특징으로 하는 할로 이온 주입 제공 방법.

### 청구항 4.

제 3 항에 있어서,

상기 활성 영역은 상기 반도체 디바이스의 소스 영역(S)과 드레인 영역(D)을 포함하는 것을 특징으로 하는 할로 이온 주입 제공 방법.

### 청구항 5.

제 1 항에 있어서,

상기 할로 이온 주입은  $45^{\circ}$ 각도로 이루어지는 것을 특징으로 하는 할로 이온 주입 제공 방법.

### 청구항 6.

제 1 항에 있어서,

상기 할로 이온 주입 제공 단계 (b) 전에, 저도핑 드레인 이온 주입을 제공하는 단계(304)를 포함하는 것을 특징으로 하는 할로 이온 주입 제공 방법.

### 청구항 7.

삭제

### 청구항 8.

삭제

### 청구항 9.

삭제

### 청구항 10.

삭제

### 청구항 11.

삭제

### 청구항 12.

삭제

### 청구항 13.

삭제

명세서

### 기술분야

본 발명은 반도체 디바이스들에 관한 것으로, 특히 반도체 디바이스들을 제조할 때 할로 이온 주입을 제공하는 것에 관한 것이다.

### 배경기술

전형적으로, 할로 이온 주입(halo implant)은 반도체 디바이스 상에 불순물(dopant)을 이온 주입하는 데에 이용된다. 전형적으로, 인라인 리소그래피(in-line lithography) 또는 DUV(deep untra violet) 포토레지스트가 할로 이온 주입 공정을 마스크하는 데에 이용된다. 전형적으로, 동일한 마스크(저도핑 드레인 lightly doped drain)(LDD)가 할로 이온 주입에 사용되는데, 그 이유는 상기 할로 이온 주입이 상기 LDD 이온 주입 이후에 행해지기 때문이다. 상기 포토레지스트의 화학적 성질 때문에, 종래의 공정들(마스크 & 포토레지스트 세트)을 사용하면, 이온 주입 음영 문제(implant shadowing problem)가 종종 발생하기 때문에, 이는 제조 공정이 보다 작은 기하학적 구조(geometry)로 이동함에 따라, 디바이스들의 수율 및 성능에 악영향을 준다.

첫번째 문제는 45°각도로 이온 주입이 행해질 때, 이온 주입 영역의 포토레지스트 두께가 트랜지스터의 비대칭 및 누설을 초래할 수 있다는 것이다. 두번째 문제는 이 트랜지스터의 두께가 디바이스의 트렌치 산화 영역에 관계한다는 것이다. 따라서, 만일 두꺼운 포토레지스트( $0.55\mu\text{m}$  이상)가 상기 트렌치 산화물 상에 놓이면, 상기 포토레지스트의 부드러운 젤리 타입 특성 때문에 상기 포토레지스트가 종종 훌러 내려, 이온 주입될 영역을 덮어버린다. 비록 미세처리 기술에 의해 상기 포토레지스트를 일으켜 세운다고 하더라도, 상기 할로 이온 주입은 목표 영역에 도달하지 못한다. 또한, 종래의 공정들은 소스/드레인 영역에 대해 도핑을 선택적으로 행할 필요에 대해 일반적으로 고려하지 않는다.

따라서, 미세처리 기하학 구조들에서 상술한 문제들을 극복하기 위한 시스템 및 방법이 필요하다. 본 발명은 이러한 필요성에 대해 대처한다.

### 발명의 상세한 설명

반도체 디바이스에 할로 이온 주입을 제공하는 방법이 개시된다. 상기 방법은 약 0.1 내지  $0.2\mu\text{m}$  두께의 얇은 포토레지스트층을 반도체 디바이스에 제공하는 단계를 포함한다. 상기 방법은 반도체 디바이스에 할로 이온 주입을 제공하는 단계를 더 포함하며, 여기서 상기 얇은 포토레지스트층은 상기 할로 이온 주입을 위한 마스크로서 사용된다.

따라서, 본 발명에 따른 방법에서, 보다 얇은 프로파일(profile)을 가능하게 하는 광 포토레지스트, 즉 DUV 포토레지스트가 사용된다. 이에 의해, 상기 포토레지스트 두께를 계획된  $1000\text{\AA}$ (현장에서)까지, 또는 공정이 허용한다면, 두께를 보다 얇게 할 수 있다. 이러한 포토레지스트 두께를 이용하여, 그리고 다른 높이 변수들을 고려하여, 소스 영역 영역과 드레인 영역은 필요한 만큼만 개방될 수 있다.

45°각도에서, 목표 영역의 회로의 모든 트랜지스터에 이온 주입을 가할 수 있을 뿐 아니라 트렌치 에지에 위치하는 트랜지스터 에지에 대량의 도즈(dose)(도즈의 최대 3/4)를 이온 주입할 수 있다. 이에 의해, 또한 할로 공정의 규정에 의해 필요로 되는, 반대 종(species)에 의한 상기 소스 드레인의 역 도핑(counter doping)을 최소화한다.

$0.18\mu\text{m}$  이하의 기술들의 보다 작은 기하학적 구조들에서, 게이트 높이는 실제로 유리하게 작용하며, 소스/드레인 영역의 원하지 않는 역 도핑을 줄이는데 도움이 된다. 이와 같이 하여, 상기 역 도핑은 절대적 최소로 유지될 수 있다. 본 발명의 마지막 장점은 보다 얇은 포토레지스트를 사용하여, 보다 작은 기하학적 구조들에 이온 주입을 제공할 수 있는 능력을 높일 수 있다는 것이다.

따라서, 본 발명에 따른 공정은 제조 능력을 개선할 뿐 아니라, 공정 능력과 디바이스 성능 및 속도를 향상시킨다.

### 실시예

#### 작제

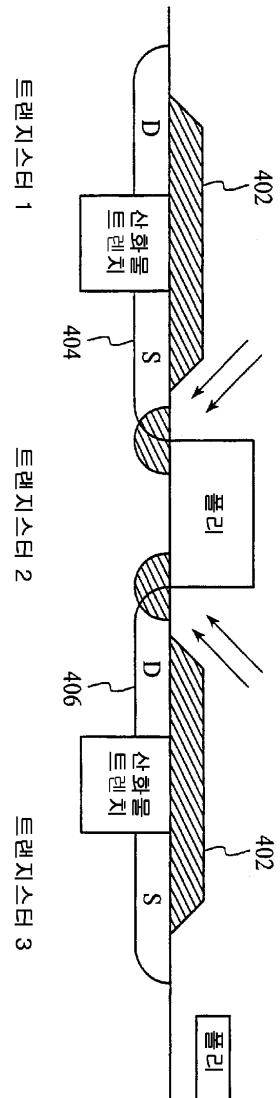

도 1은 할로 이온 주입을 제공하기 위한 종래의 공정을 예시하는 흐름도이다. 전형적으로, 이러한 종래의 공정에서, 먼저 단계(102)를 통해 두꺼운 포토레지스트가 제공된다. 이후, 단계(104)를 통해, LDD 이온 주입이 제공된다. 종래 공정의 두꺼운 포토레지스트 또는 LDD 마스크는 전형적으로 높이가  $0.55\mu\text{m}$ 인 포토레지스트이다. 상기 LDD 이온 주입이 제공된 후, 단계(106)를 통해 할로 이온 주입이라 칭하는 처리가 행해진다. 할로 이온 주입은 전형적으로, 상기 게이트 영역의 하부에 이온 주입되도록 45°각도로 제공된다. 웨이퍼에 45°이온 주입으로 일관성있게 의도된 영역에 이온 주입하도록, 소스 영역 또는 드레인 영역을 덮지 않는 LDD 마스크가 이용된다. 종래의 할로 이온 주입 공정의 예는 1998년 2월 27일(1998-02-07)에 출간된 일본 특허 요약(PATENT ABSTRACTS OF JAPAN) 제1998권, No. 03 및 EP-A-0 899 793에 개시되어 있다.

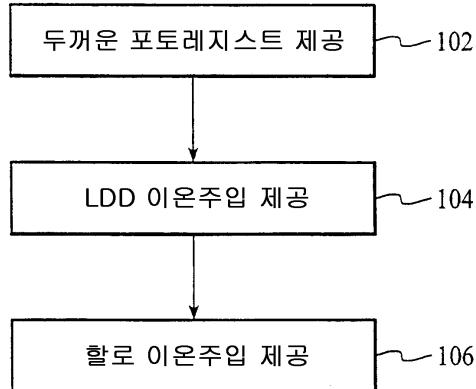

도 2는 종래의 할로 이온 주입 후의 반도체 디바이스(200)를 예시하는 도면이다. 따라서, 상기 할로 이온 주입(202)은 종종 상기 소스 영역(204) 및 드레인 영역(206) 전체에 불순물을 제공하게 된다. 상기 게이트(208)의 바로 아래 영역만이 상기 이온 주입을 위한 대상 영역이기 때문에, 누설 및 그와 관련된 다른 문제들이 존재한다. 따라서, 활성 영역(212) 전체가 개방되는데, 그 이유는 주로 포토레지스트 마스크(212)의 두께가 45°각도에서는, 자외선들을 게이트 영역 하부에 정확하게 제공할 수 없기 때문이다.

도시된 바와 같이, 포토레지스트 마스크(212)의  $0.5\mu\text{m}$  두께에 의해, 상기  $45^\circ$ 각도에서는 필연적으로, 대부분의 자외선 방사(untraviolet radiation)가 대상 영역에 도달하지 않는데, 이는 그 각도에서 상기와 같은 두꺼운 포토레지스트로는 그것이 불가능하기 때문이다. 또한, 만일 두꺼운 포토레지스트( $0.5\mu\text{m}$  이상)가 트랜치 산화물(207) 상에 놓여지면, 상기 포토레지스트의 부드러운 젤리 타입 성질 때문에 상기 포토레지스트는 종종 상기 트랜치 산화물 영역 위로 흘러 내리고, 이온 주입될 영역을 덮어버린다. 비록 미세처리 기술에 의해 상기 포토레지스트를 일으켜 세운다고 하더라도, 상기 할로 이온 주입은 목표 영역에 도달하지 못할 것이다.

본 발명에 따른 방법에 있어서, 상기 이온 주입 영역은 일괄 이온 주입(blanket implant)을 행하는 대신에 선택적으로 정해진다. 이는 종래의 공정에 사용되는  $0.55\mu\text{m}$  내지  $0.8\mu\text{m}$  두께의 포토레지스트 대신,  $0.1\mu\text{m}$  내지  $0.2\mu\text{m}$  두께의 보다 얇은 포토레지스트 마스크를 사용함으로써 달성된다. 본 발명의 특징들을 보다 특정하게 기재하기 위해, 이하에서는 도면들과 관련하여 설명한다.

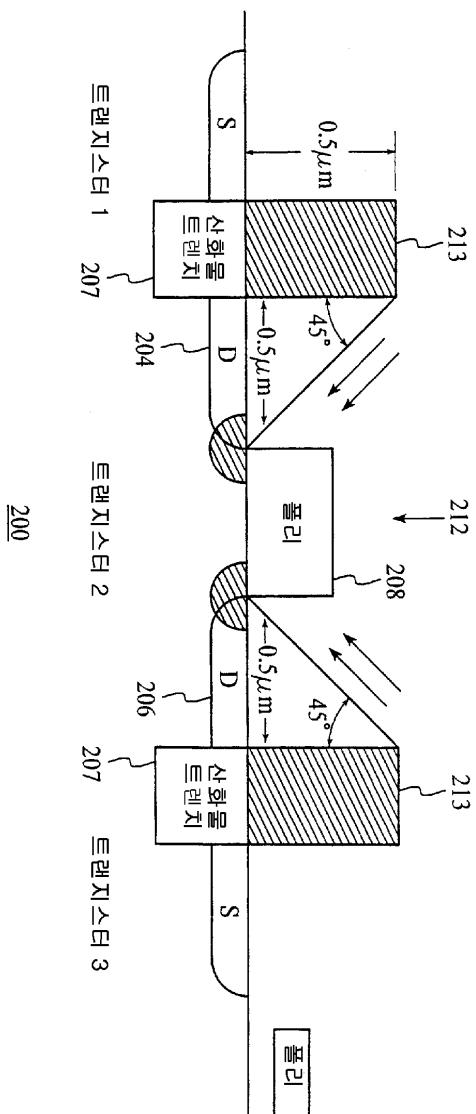

도 3은 본 발명에 따른 시스템의 흐름도이다. 종래의 공정에서 전형적인 바와 같이, 먼저 단계(302)를 통해 두꺼운 포토레지스트가 제공된다. 이후, 단계(304)를 통해, LDD 이온 주입이 제공된다. 이후, 단계(306)를 통해, 상기 두꺼운 포토레지스트가 제거된다. 이후, 단계(308)를 통해, 얇은 포토레지스트가 제공된다. 이후, 단계(310)를 통해 할로 이온 주입이 제공된다. 상기 할로 이온 주입은 상기 게이트 영역 아래에 이온 주입되도록 전형적으로  $45^\circ$ 각도로 제공된다. 웨이퍼에  $45^\circ$ 각도의 할로 이온 주입으로 일관성 있게 의도된 영역에 이온을 주입하기 위해, 소스 영역 또는 드레인 영역의 전체가 아닌 전체에 가까운 부분을 덮는 LDD 마스크가 이용된다.

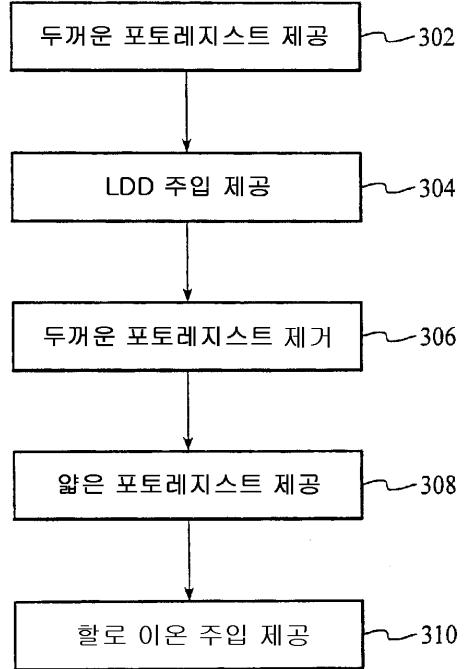

도 4는 본 발명에 따른 할로 이온 주입 이후의 반도체 디바이스(400)를 예시한다. 도시된 바와 같이, 상기 포토레지스트 마스크(402)는 종래의 공정에서보다 높이가 더 낮고( $0.1\mu\text{m}$  내지  $0.2\mu\text{m}$ ), 이에 의해 소스 영역(404)과 드레인 영역(406)의 보다 많은 부분이 포토레지스트(402)에 의해 각각 마스크될 수 있다.

따라서, 본 발명에 따른 방법에서는, 보다 얇은 프로파일이 가능한 포토레지스트, 즉 DUV 포토레지스트가 사용된다. 이에 의해, 상기 포토레지스트의 두께를 계획된  $1000\text{\AA}$ (현장에서)까지, 또는 공정이 허용한다면, 두께를 보다 얇게 할 수 있다. 이와 같은 포토레지스트 두께로, 다른 높이를 고려하여, 소스 영역과 드레인 영역은 필요한 만큼만 개방될 수 있다.  $45^\circ$ 각도에서, 상기 이온 주입은 목표 영역의 회로에 있는 모든 트랜지스터에 가해질 수 있을 뿐 아니라, 트랜치 에지에 위치하는 트랜지스터 에지에 대량의 도즈(도즈의 최대  $3/4$ )를 이온 주입할 수 있다. 이에 의해, 또한 할로 공정의 규정에 의해 요구되는, 반대 종에 의한 소스 드레인의 역 도핑을 최소화한다.

$0.18\mu\text{m}$  이하의 기술의 보다 작은 기하학적 구조에 대해, 게이트 높이는 실제로 유리하게 작용하고, 소스/드레인 영역의 원하지 않는 역 도핑을 감소시키는 데에 도움이 된다. 이와 같이, 상기 역 도핑은 절대적 최소로 유지될 수 있다. 본 발명의 마지막 장점은 보다 얇은 포토레지스트로, 보다 작은 기하학적 구조들에 이온 주입을 제공할 수 있는 능력을 높일 수 있다는 것이다. 따라서, 본 발명에 따른 공정에서는 제조 능력의 개선에 더하여, 공정 능력, 디바이스 성능 및 속도를 높일 수 있다.

## 삭제

## 도면의 간단한 설명

도 1은 할로 이온 주입을 제공하기 위한 종래의 공정을 예시하는 흐름도이다.

도 2는 종래의 할로 이온 주입 후의 반도체 디바이스를 예시하는 도면이다.

도 3은 할로 이온 주입을 제공하기 위한, 본 발명에 따른 방법의 흐름도이다.

도 4는 본 발명에 따른 할로 이온 주입 후의 반도체 디바이스를 예시하는 도면이다.

## 도면

## 도면1

## 도면2

도면3

도면4