(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2011-0097240

(43) 공개일자 2011년08월31일

(51) Int. Cl.

H04B 10/02 (2006.01) H04B 10/28 (2006.01)

(21) 출원번호 10-2010-0016981

(22) 출원일자 2010년02월25일

심사청구일자 없음

(71) 출원인

삼성전자주식회사

경기도 수원시 영통구 매탄동 416

(72) 발명자

지호철

경기도 용인시 기흥구 신갈동 녹원마을새천년그린

빌4단지아파트 411동 1102호

나경원

서울특별시 송파구 오금동 70-4 101호

(뒷면에 계속)

(74) 대리인

한지희, 권영규, 윤재석

전체 청구항 수 : 총 23 항

(54) 광 시리얼라이저, 광 디시리얼라이저, 및 이들을 포함하는 데이터 처리 시스템

### (57) 요 약

광 시리얼라이저가 개시된다. 상기 광 시리얼라이저는 복수의 변조되지 않은 광신호들의 소스(source); 상기 복수의 변조되지 않은 광신호들 각각과 복수의 전기 신호들 각각을 수신하고, 상기 복수의 변조되지 않은 광신호들을 변조하기 위하여 상기 복수의 전기 신호들을 사용하여 복수의 변조 광신호들 각각을 생성하기 위한 변조 유닛; 및 복수의 지연 변조 광신호들 각각을 생성하기 위하여 각각의 지연 량만큼 상기 복수의 변조 광신호들 각각을 지연시켜 시리얼라이즈된 변조 광신호를 생성하기 위하여 상기 복수의 지연 변조 광신호들을 결합하는 커플링 유닛을 포함한다.

대 표 도 - 도1

(72) 발명자

**서성동**

서울특별시 강남구 신사동 592-9호 성호빌딩 5층

**하경호**

서울특별시 강남구 논현동 262-9

**김성구**

경기도 평택시 평택동 288-36

**신동재**

서울특별시 송파구 잠실3동 트리지움아파트 323동

304호

**조인성**

서울특별시 강남구 도곡2동 도곡렉슬아파트 101동

904호

---

## 특허청구의 범위

### 청구항 1

복수의 변조되지 않은 광신호들의 소스(source);

상기 복수의 변조되지 않은 광신호들 각각과 복수의 전기 신호들 각각을 수신하고, 상기 복수의 변조되지 않은 광신호들을 변조하기 위하여 상기 복수의 전기 신호들을 사용하여 복수의 변조 광신호들 각각을 생성하기 위한 변조 유닛; 및

복수의 지연 변조 광신호들 각각을 생성하기 위하여 각각의 지연 량만큼 상기 복수의 변조 광신호들 각각을 지연시켜 시리얼라이즈된 변조 광신호를 생성하기 위하여 상기 복수의 지연 변조 광신호들을 결합하는 커플링 유닛을 포함하는 광 시리얼라이저.

### 청구항 2

제1항에 있어서, 상기 커플링 유닛은,

상기 복수의 지연 변조 광신호들 각각을 생성하기 위하여 상기 각각의 지연 량만큼 상기 복수의 변조 광신호들 각각을 지연시키기 위한 지연 유닛; 및

상기 시리얼라이즈된 변조 광신호를 생성하기 위하여 상기 복수의 지연 변조 광신호들을 결합하기 위한 광 결합기를 포함하는 광 시리얼라이저.

### 청구항 3

시리얼라이즈된 변조 광신호를 복수의 변조 분배 광신호들 각각으로 분배하기 위한 광 분배기;

상기 복수의 변조 분배 광신호들을 복조하여 복수의 복조 분배 광신호들 각각을 생성하기 위한 복조 유닛; 및

상기 시리얼라이즈된 변조 광신호를 복수의 병렬 복조 분배 광신호들로 변환하기 위하여 각각의 지연 량만큼 상기 복수의 복조 분배 광신호들 각각을 지연시키기 위한 지연 유닛을 포함하는 광 디시리얼라이저.

### 청구항 4

제3항에 있어서, 상기 광 디시리얼라이저는,

상기 복수의 병렬 복조 분배 광신호들 각각을 복수의 병렬 전기 신호들 각각으로 변환하기 위한 광-전 변환 유닛을 더 포함하는 광 디시리얼라이저.

### 청구항 5

시리얼라이즈된 변조 광신호를 복수의 변조 분배 광신호들 각각으로 분배하기 위한 광 분배기;

상기 복수의 변조 분배 광신호들 각각을 복조하여 복수의 복조 분배 광신호들 각각을 생성하기 위한 복조 유닛을 포함하며,

복수의 제어 신호들 각각은 복수의 지연 제어 신호들 각각을 생성하기 위하여 각각의 지연 량만큼 지연되고,

상기 복수의 지연 제어 신호들 각각은 상기 복수의 복조 분배 광신호들을 시간적으로 정렬시키기 위하여 복수의 복조기들 각각으로 공급되는 광 디시리얼라이저.

### 청구항 6

제5항에 있어서, 상기 광 디시리얼라이저는,

상기 복수의 지연 제어 신호들을 생성하기 위한 지연 유닛을 더 포함하는 광 디시리얼라이저.

### 청구항 7

제6항에 있어서, 상기 복수의 지연 제어 신호들은 클락 신호들인 광 디시리얼라이저.

**청구항 8**

제5항에 있어서, 상기 지연 유닛은 상기 복수의 복조 분배 광신호들을 동기시키는 광 디시리얼라이저.

**청구항 9**

제5항에 있어서, 상기 광 디시리얼라이저는,

시간적으로 정렬된 상기 복수의 복조 분배 광신호들 각각을 복수의 병렬 전기 신호들 각각으로 변환하기 위한 광-전 변환 유닛을 더 포함하는 광 디시리얼라이저.

**청구항 10**

제1송수신기 회로;

제2송수신기 회로; 및

상기 제1송수신기 회로와 상기 제2송수신기 회로 사이에 접속된 광통신 채널을 포함하며,

상기 제1송수신기 회로와 상기 제2송수신기 회로 각각은 병렬 전기 신호들과 시리얼라이즈된 광신호 사이를 변환하기 위한 시리얼라이저/디시리얼라이저 유닛을 포함하며,

상기 시리얼라이저/디시리얼라이저 유닛은 입력 광신호를 분배하여 얻어진 복수의 분배 광신호들 각각에 복수의 지연들 각각을 적용하는 데이터 처리 시스템.

**청구항 11**

제10항에 있어서, 상기 입력 광신호는 상기 시리얼라이즈된 광신호를 상기 병렬 전기 신호들로 디시리얼라이즈하기 위한 광신호인 데이터 처리 시스템.

**청구항 12**

제10항에 있어서, 상기 입력 광신호는 변조되지 않은 광신호이고,

상기 변조되지 않은 광신호는 상기 병렬 전기 신호들에 의하여 상기 병렬 전기 신호들을 상기 시리얼라이즈된 광신호로 시리얼라이즈하기 위하여 분배되고 변조되는 데이터 처리 시스템.

**청구항 13**

제10항에 있어서, 상기 시리얼라이저/디시리얼라이저 유닛 각각은 상기 복수의 지연들을 적용하기 위한 복수의 지연 회로들을 포함하는 데이터 처리 시스템.

**청구항 14**

제10항에 있어서, 상기 제1송수신기 회로와 상기 제2송수신기 회로 중에서 적어도 하나는 반도체 메모리 회로에 접속되는 데이터 처리 시스템.

**청구항 15**

제10항에 있어서, 상기 제1송수신기 회로와 상기 제2송수신기 회로 중에서 적어도 하나는 프로세서 회로에 접속되는 데이터 처리 시스템.

**청구항 16**

복수의 병렬 전기 신호들을 시리얼라이징하는 방법에 있어서,

복수의 변조되지 않은 광신호들을 수신하는 단계;

상기 복수의 병렬 전기 신호들 각각을 이용하여 상기 복수의 변조되지 않은 광신호들을 복수의 병렬 변조 광신호들로 변조하는 단계;

복수의 지연 변조 광신호들 각각을 생성하기 위하여 복수의 지연들 각각을 상기 복수의 병렬 변조 광신호들 각각에 적용하는 단계; 및

상기 복수의 지연 변조 광신호들을 하나의 시리얼라이즈된 변조 광신호로 결합하는 단계를 포함하는 복수의 병렬 전기 신호들을 시리얼라이징하는 방법.

### 청구항 17

시리얼라이즈된 변조 광신호를 복수의 병렬 신호들로 변환하는 방법에 있어서,

상기 시리얼라이즈된 변조 광신호를 복수의 변조 분배 광신호들로 분배하는 단계;

상기 복수의 변조 분배 광신호들을 복수의 복조 분배 광신호들로 복조하는 단계; 및

상기 복수의 복조 분배 광신호들을 시간적으로 정렬시키기 위하여 복수의 지연들 각각을 상기 복수의 변조 분배 광신호들 각각에 적용하는 단계를 포함하는 시리얼라이즈된 변조 광신호를 복수의 병렬 신호들로 변환하는 방법.

### 청구항 18

제17항에 있어서, 상기 복수의 지연들은 각각의 시간 량에 의하여 상기 복수의 변조 분배 신호들을 지연시키기 위해 상기 복수의 변조 분배 광신호들에 적용되는 시리얼라이즈된 변조 광신호를 복수의 병렬 신호들로 변환하는 방법.

### 청구항 19

제17항에 있어서,

상기 복수의 변조 분배 광신호들을 복수의 병렬 전기 신호들로 변환하는 단계를 더 포함하는 시리얼라이즈된 변조 광신호를 복수의 병렬 신호들로 변환하는 방법.

### 청구항 20

제17항에 있어서,

상기 복수의 변조 분배 광신호들을 동기시키는 단계를 더 포함하는 시리얼라이즈된 변조 광신호를 복수의 병렬 신호들로 변환하는 방법

### 청구항 21

시리얼라이즈된 변조 광신호를 복수의 병렬 신호들로 변환하는 방법에 있어서,

상기 시리얼라이즈된 변조 광신호를 복수의 변조 분배 광신호들로 분배하는 단계;

상기 복수의 변조 분배 광신호들을 복수의 복조 분배 광신호들로 복조하는 단계; 및

상기 복수의 복조 분배 광신호들을 시간적으로 정렬시키기 위하여 상기 복수의 변조 분배 광신호들을 복조하기 위하여 사용된 복수의 제어 신호들 각각에 복수의 지연들 각각을 적용하는 단계를 포함하는 시리얼라이즈된 변조 광신호를 복수의 병렬 신호들로 변환하는 방법.

### 청구항 22

제21항에 있어서,

상기 복수의 변조 분배 광신호들을 복수의 병렬 전기 신호들로 변환하는 단계를 더 포함하는 시리얼라이즈된 변조 광신호를 복수의 병렬 신호들로 변환하는 방법.

### 청구항 23

제21항에 있어서,

상기 복수의 변조 분배 광신호들을 동기시키는 단계를 더 포함하는 시리얼라이즈된 변조 광신호를 복수의 병렬 신호들로 변환하는 방법.

## 명세서

## 기술 분야

- [0001] 본 발명의 개념에 따른 실시 예는 신호 변환 기술에 관한 것으로, 특히 광 시리얼라이저/광 디시리얼라이저, 이들을 포함하는 데이터 처리 시스템, 및 상기 광 시리얼라이저/광 디시리얼라이저의 광 변환 방법에 관한 것이다.

## 배경 기술

- [0002] CPU(central processing unit)의 동작 속도가 증가함에 따라 상기 CPU와 통신을 할 수 있는 메모리 장치의 동작 속도도 급격히 증가하고 있다. 그러나, 상기 CPU와 상기 메모리 장치 사이에 존재하는 버스(bus)의 대역폭의 한계로 인하여 동작 속도의 증가가 제한을 받고 있다.

## 발명의 내용

### 해결하려는 과제

- [0003] 따라서 본 발명이 이루고자 하는 기술적인 과제는 광을 이용하여 병렬 전기신호들을 직렬 광신호로 변환할 수 있는 광 시리얼라이저와 그 방법, 상기 직렬 광신호를 광-전 변환 없이 병렬 광신호들로 변환할 수 있는 광 디시리얼라이저와 그 방법을 제공하는 것이다.

- [0004] 또한 본 발명이 이루고자 하는 다른 기술적인 과제는 상기 광 시리얼라이저와 상기 광 디시리얼라이저를 포함하는 데이터 처리 시스템을 제공하는 것이다.

- [0005] 또한 본 발명이 이루고자 하는 다른 기술적인 과제는 CPU와 같은 제1반도체 장치와 메모리 장치와 같은 제2반도체 장치 사이의 광 버스 구조를 제공하는 것이다.

### 과제의 해결 수단

- [0006] 본 발명의 실시 예에 따른 광 시리얼라이저는 복수의 변조되지 않은 광신호들의 소스(source); 상기 복수의 변조되지 않은 광신호들 각각과 복수의 전기 신호들 각각을 수신하고, 상기 복수의 변조되지 않은 광신호들을 변조하기 위하여 상기 복수의 전기 신호들을 사용하여 복수의 변조 광신호들 각각을 생성하기 위한 변조 유닛; 및 복수의 지연 변조 광신호들 각각을 생성하기 위하여 각각의 지연 량만큼 상기 복수의 변조 광신호들 각각을 지연시켜 시리얼라이즈된 변조 광신호를 생성하기 위하여 상기 복수의 지연 변조 광신호들을 결합하는 커플링 유닛을 포함한다.

- [0007] 상기 커플링 유닛은 상기 복수의 지연 변조 광신호들 각각을 생성하기 위하여 상기 각각의 지연 량만큼 상기 복수의 변조 광신호들 각각을 지연시키기 위한 지연 유닛; 및 상기 시리얼라이즈된 변조 광신호를 생성하기 위하여 상기 복수의 지연 변조 광신호들을 결합하기 위한 광 결합기를 포함한다.

- [0008] 본 발명의 실시 예에 따른 광 디시리얼라이저는 시리얼라이즈된 변조 광신호를 복수의 변조 분배 광신호들 각각으로 분배하기 위한 광 분배기; 상기 복수의 변조 분배 광신호들을 복조하여 복수의 복조 분배 광신호들 각각을 생성하기 위한 복조 유닛; 및 상기 시리얼라이즈된 변조 광신호를 복수의 병렬 복조 분배 광신호들로 변환하기 위하여 각각의 지연 량만큼 상기 복수의 복조 분배 광신호들 각각을 지연시키기 위한 지연 유닛을 포함한다.

- [0009] 상기 광 디시리얼라이저는 상기 복수의 병렬 복조 분배 광신호들 각각을 복수의 병렬 전기 신호들 각각으로 변환하기 위한 광-전 변환 유닛을 더 포함한다.

- [0010] 본 발명의 다른 실시 예에 따른 광 디시리얼라이저는 시리얼라이즈된 변조 광신호를 복수의 변조 분배 광신호들 각각으로 분배하기 위한 광 분배기; 상기 복수의 변조 분배 광신호들 각각을 복조하여 복수의 복조 분배 광신호들 각각을 생성하기 위한 복조 유닛을 포함하며, 복수의 제어 신호들 각각은 복수의 지연 제어 신호들 각각을 생성하기 위하여 각각의 지연 량만큼 지연되고, 상기 복수의 지연 제어 신호들 각각은 상기 복수의 복조 분배 광신호들을 시간적으로 정렬시키기 위하여 복수의 복조기들 각각으로 공급된다.

- [0011] 상기 광 디시리얼라이저는 상기 복수의 지연 제어 신호들을 생성하기 위한 지연 유닛을 더 포함한다.

- [0012] 상기 복수의 지연 제어 신호들은 클락 신호들이다.

- [0013] 상기 지연 유닛은 상기 복수의 복조 분배 광신호들을 동기시킨다.

- [0014] 상기 광 디시리얼라이저는 시간적으로 정렬된 상기 복수의 변조 분배 광신호들 각각을 복수의 병렬 전기 신호들 각각으로 변환하기 위한 광-전 변환 유닛을 더 포함한다.

- [0015] 본 발명의 실시 예에 따른 데이터 처리 시스템은 제1송수신기 회로; 제2송수신기 회로; 및 상기 제1송수신기 회로와 상기 제2송수신기 회로 사이에 접속된 광통신 채널을 포함한다. 상기 제1송수신기 회로와 상기 제2송수신기 회로 각각은 병렬 전기 신호들과 시리얼라이즈된 광신호 사이를 변환하기 위한 시리얼라이저/디시리얼라이저 유닛을 포함하며, 상기 시리얼라이저/디시리얼라이저 유닛은 입력 광신호를 분배하여 얻어진 복수의 분배 광신호들 각각에 복수의 지연들 각각을 적용한다.

- [0016] 상기 입력 광신호는 상기 시리얼라이즈된 광신호를 상기 병렬 전기 신호들로 디시리얼라이즈하기 위한 광신호이다.

- [0017] 상기 입력 광신호는 변조되지 않은 광신호이고, 상기 변조되지 않은 광신호는 상기 병렬 전기 신호들에 의하여 상기 병렬 전기 신호들을 상기 시리얼라이즈된 광신호로 시리얼라이즈하기 위하여 분배되고 변조된다.

- [0018] 상기 시리얼라이저/디시리얼라이저 유닛 각각은 상기 복수의 지연들을 적용하기 위한 복수의 지연 회로들을 포함한다.

- [0019] 상기 제1송수신기 회로와 상기 제2송수신기 회로 중에서 적어도 하나는 반도체 메모리 회로에 접속된다. 상기 제1송수신기 회로와 상기 제2송수신기 회로 중에서 적어도 하나는 프로세서 회로에 접속된다.

- [0020] 본 발명의 실시 예에 따른 복수의 병렬 전기 신호들을 시리얼라이징하는 방법은 복수의 변조되지 않은 광신호들을 수신하는 단계; 상기 복수의 병렬 전기 신호들 각각을 이용하여 상기 복수의 변조되지 않은 광신호들을 복수의 병렬 변조 광신호들로 변조하는 단계; 복수의 지연 변조 광신호들 각각을 생성하기 위하여 복수의 지연들 각각을 상기 복수의 병렬 변조 광신호들 각각에 적용하는 단계; 및 상기 복수의 지연 변조 광신호들을 하나의 시리얼라이즈된 변조 광신호로 결합하는 단계를 포함한다.

- [0021] 본 발명의 실시 예에 따른 시리얼라이즈된 변조 광신호를 복수의 병렬 신호들로 변환하는 방법은 상기 시리얼라이즈된 변조 광신호를 복수의 변조 분배 광신호들로 분배하는 단계; 상기 복수의 변조 분배 광신호들을 복수의 복조 분배 광신호들로 복조하는 단계; 및 상기 복수의 복조 분배 광신호들을 시간적으로 정렬시키기 위하여 복수의 지연들 각각을 상기 복수의 변조 분배 광신호들 각각에 적용하는 단계를 포함한다.

- [0022] 상기 복수의 지연들은 각각의 시간 량에 의하여 상기 복수의 변조 분배 신호들을 지연시키기 위해 상기 복수의 변조 분배 광신호들에 적용된다.

- [0023] 상기 복수의 변조 분배 광신호들을 복수의 병렬 전기 신호들로 변환하는 단계를 더 포함한다.

- [0024] 상기 복수의 변조 분배 광신호들을 동기시키는 단계를 더 포함한다.

- [0025] 본 발명의 다른 실시 예에 따른 시리얼라이즈된 변조 광신호를 복수의 병렬 신호들로 변환하는 방법은 상기 시리얼라이즈된 변조 광신호를 복수의 변조 분배 광신호들로 분배하는 단계; 상기 복수의 변조 분배 광신호들을 복수의 복조 분배 광신호들로 복조하는 단계; 및 상기 복수의 복조 분배 광신호들을 시간적으로 정렬시키기 위하여 상기 복수의 변조 분배 광신호들을 복조하기 위하여 사용된 복수의 제어 신호들 각각에 복수의 지연들 각각을 적용하는 단계를 포함한다.

- [0026] 상기 시리얼라이즈된 변조 광신호를 복수의 병렬 신호들로 변환하는 방법은 상기 복수의 변조 분배 광신호들을 복수의 병렬 전기 신호들로 변환하는 단계를 더 포함한다.

- [0027] 상기 시리얼라이즈된 변조 광신호를 복수의 병렬 신호들로 변환하는 방법은 상기 복수의 변조 분배 광신호들을 동기시키는 단계를 더 포함한다.

### 발명의 효과

- [0028] 본 발명의 실시 예에 따른 광 변화기와 이를 이용한 광 변환 방법은 광을 이용하여 병렬 전기 신호를 시리얼라이즈하고 시리얼라이즈된 변조된 광신호를 출력할 수 있으므로 데이터 전송 속도를 증가시킬 수 있는 효과가 있다.

- [0029] 또한 본 발명의 실시 예에 따른 광 변화기와 이를 이용한 광 변환 방법은 상기 시리얼라이즈된 변조된 광신호를 전-광 변환 없이 병렬 광신호들로 디시리얼라이즈할 수 있는 효과가 있다.

- [0030] 또한, 본 발명의 실시 예에 따른 광 변화기와 이를 이용한 광 변환 방법은 디시리얼라이즈된 병렬 광신호들을 저속/저가의 광-전 변환 모듈 또는 전-광 변환 모듈을 이용할 수 있으므로 저비용/저전력으로 구현할 수 있다.

- [0031] 본 발명의 실시 예에 따른 광 변화기들을 포함하는 데이터 처리 시스템은 고속으로 데이터를 처리할 수 있는 효과가 있다.

### 도면의 간단한 설명

- [0032] 본 발명의 상세한 설명에서 인용되는 도면을 보다 충분히 이해하기 위하여 각 도면의 상세한 설명이 제공된다.

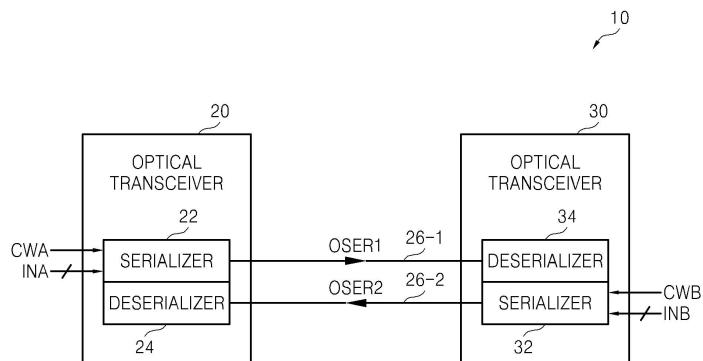

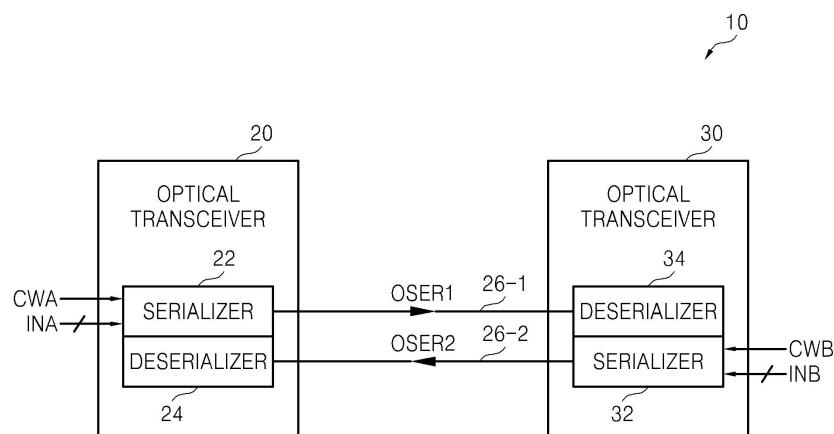

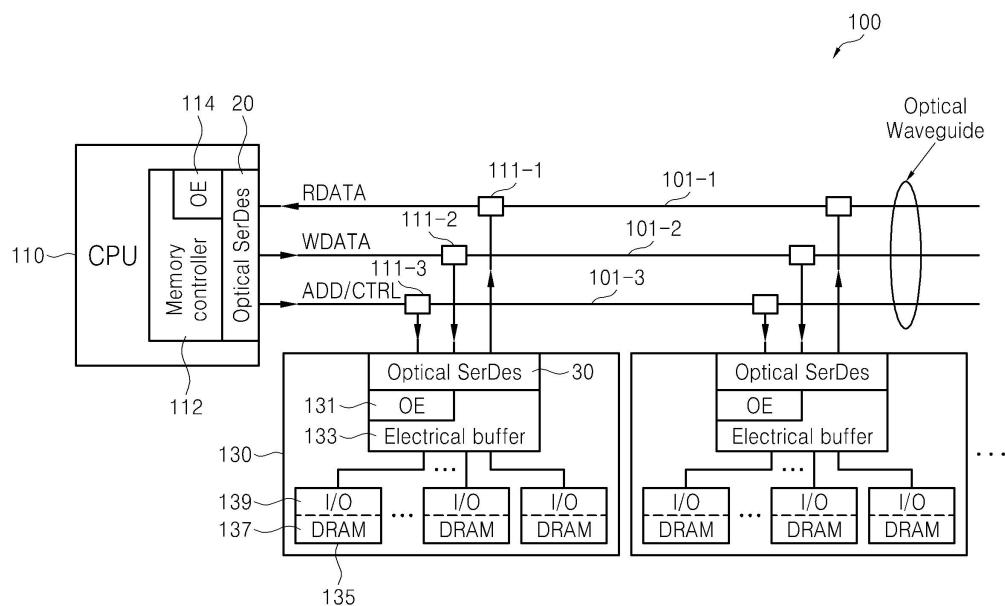

- 도 1은 본 발명의 실시 예에 따른 복수의 광 송수신기들을 포함하는 데이터 전송 시스템의 블록도를 나타낸다.

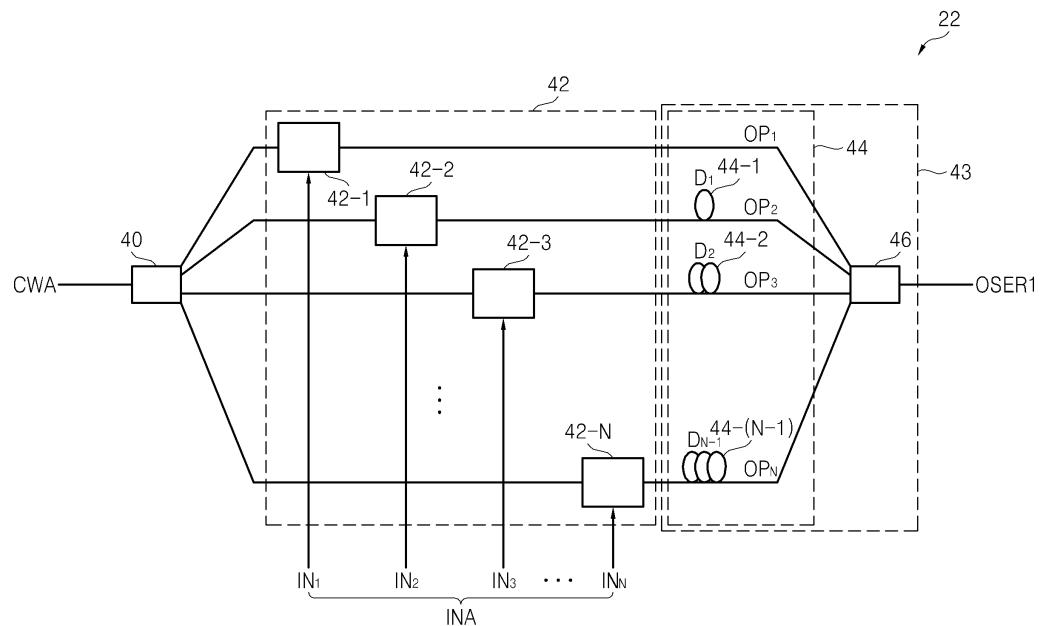

- 도 2는 도 1에 도시된 제1광 시리얼라이저의 블록도를 나타낸다.

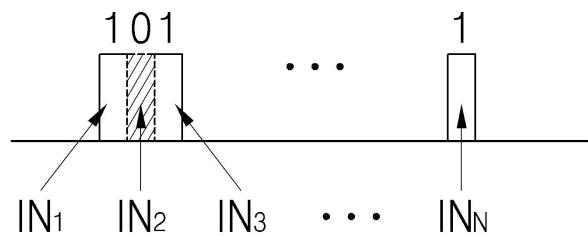

- 도 3은 도 2에 도시된 제1광 시리얼라이저로 입력되는 병렬 전기 신호들의 예를 나타낸다.

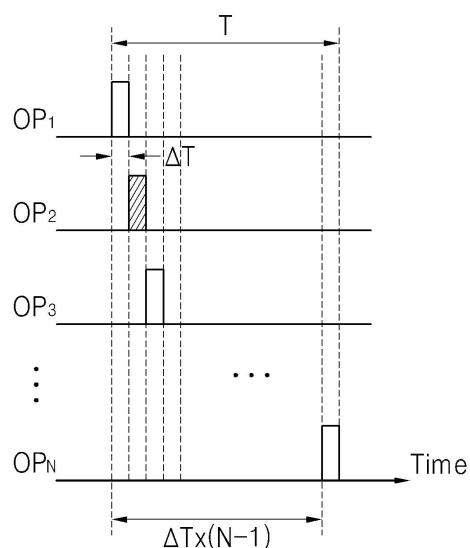

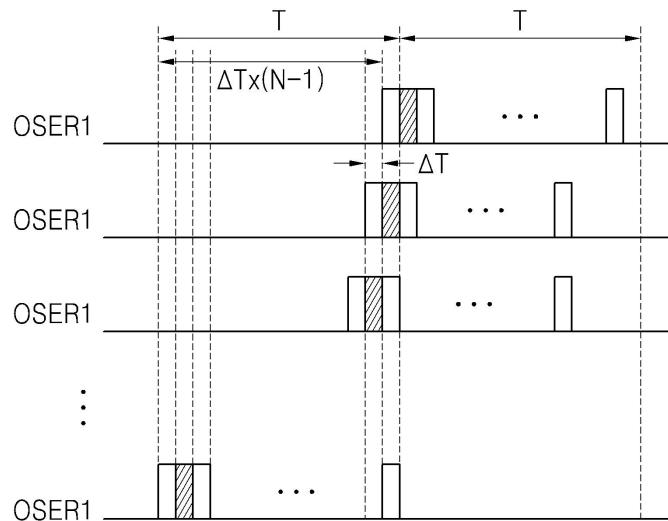

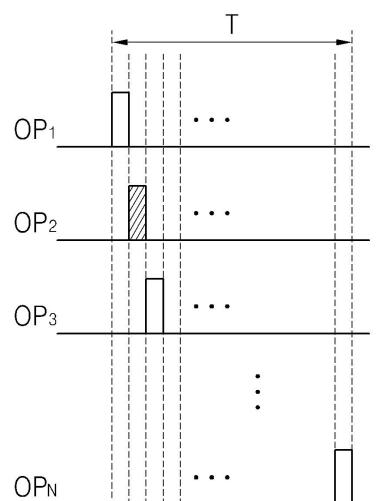

- 도 4는 도 2에 도시된 광학적 지연 소자들의 출력 신호들을 나타낸다.

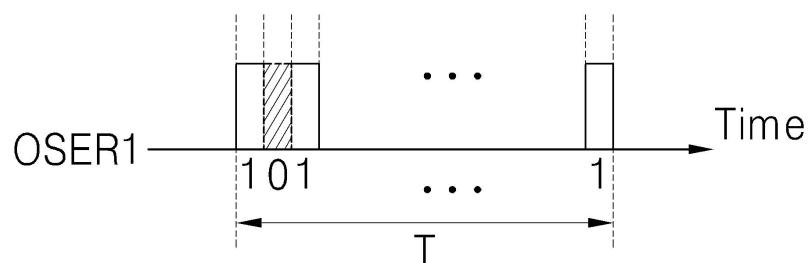

- 도 5는 도 2에 도시된 제1광 시리얼라이저에 의하여 시리얼라이즈된 광신호를 나타낸다.

- 도 6은 도 1에 도시된 제2광 디시리얼라이저의 일 실시 예를 나타내는 블록도를 나타낸다.

- 도 7은 도 6에 도시된 광학적 지연 소자들의 출력 신호들을 나타낸다.

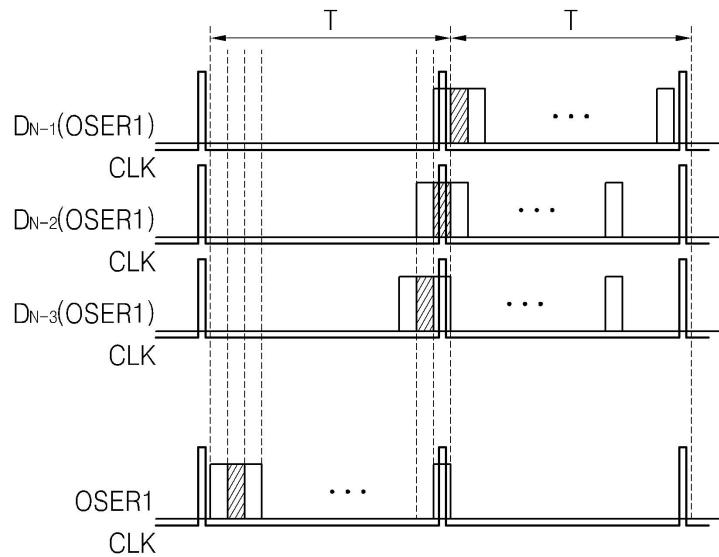

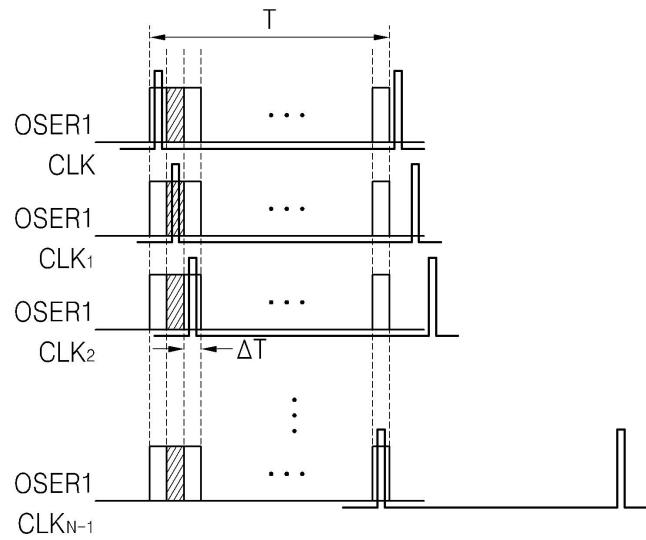

- 도 8은 도 6에 도시된 각 복조기들 각각이 각 광신호를 선택하는 과정을 설명하기 위한 타이밍들이다.

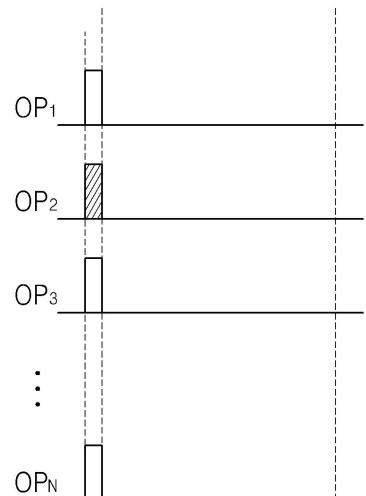

- 도 9는 도 6에 도시된 제2광 디시리얼라이저의 출력 신호들을 나타낸다.

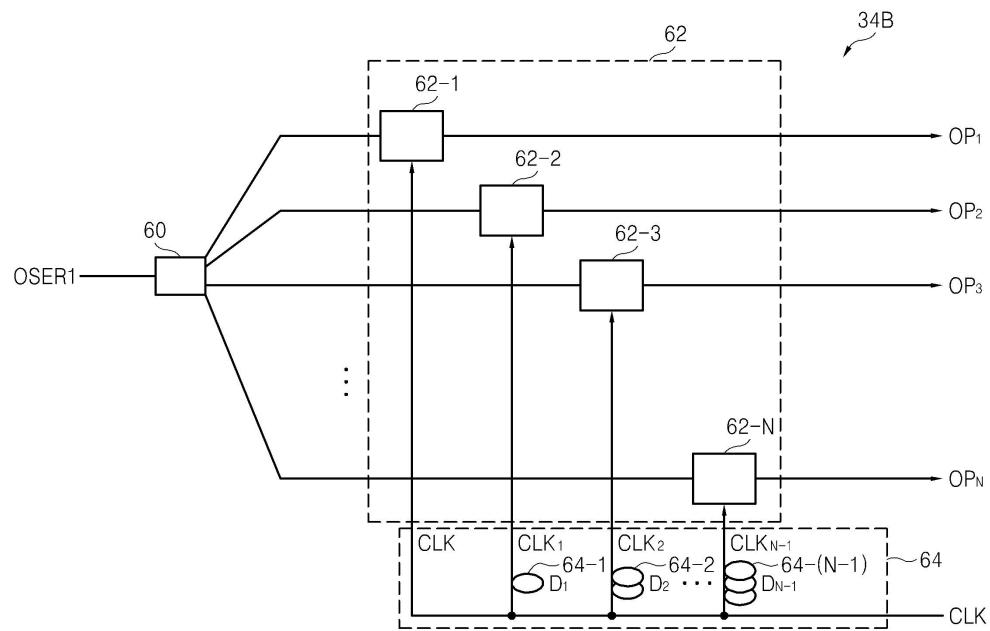

- 도 10은 도 1에 도시된 제2광 디시리얼라이저의 다른 실시 예를 나타내는 블록도를 나타낸다.

- 도 11은 도 10에 도시된 복조 블록으로부터 출력된 신호들의 타이밍 도를 나타낸다.

- 도 12는 도 10에 도시된 변조기들 각각의 광신호 선택 과정을 설명하기 위한 타이밍들이다.

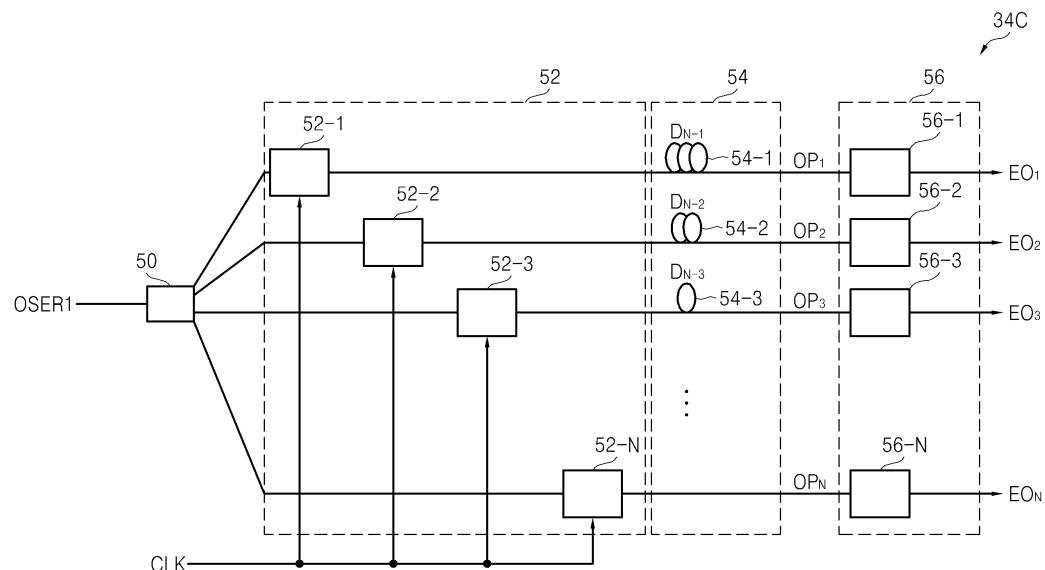

- 도 13은 도 1에 도시된 제2광 디시리얼라이저의 또 다른 실시 예를 나타내는 블록도를 나타낸다.

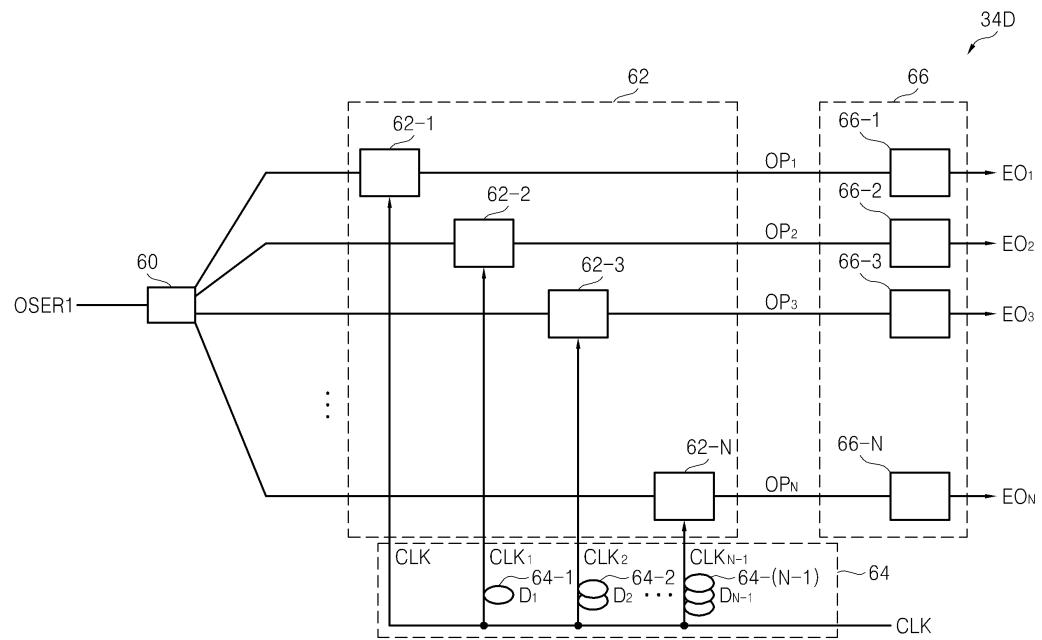

- 도 14는 도 1에 도시된 제2광 디시리얼라이저의 또 다른 실시 예를 나타내는 블록도를 나타낸다.

- 도 15는 도 1에 도시된 광 송수신기들을 포함하는 데이터 처리 시스템의 다른 실시 예를 나타낸다.

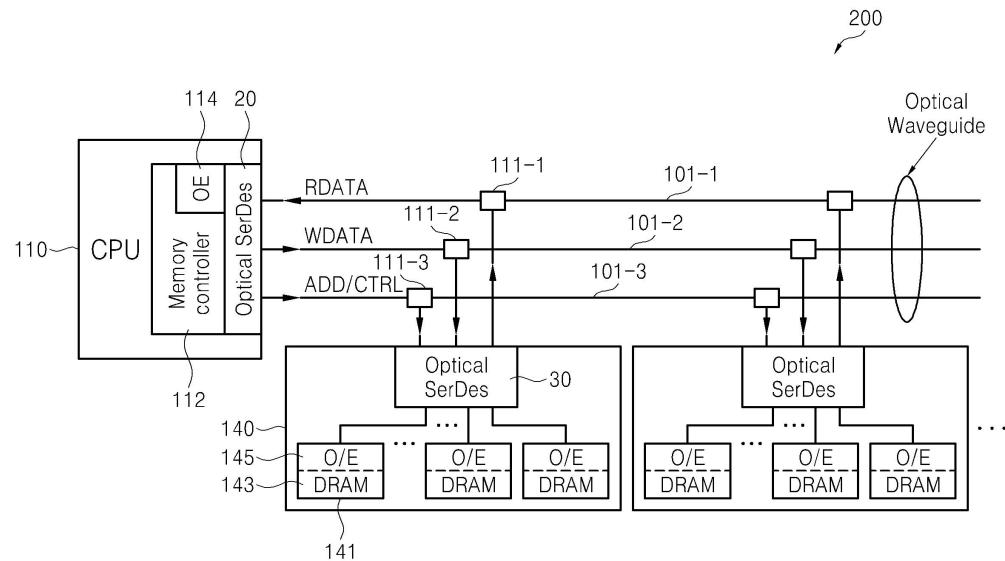

- 도 16은 도 1에 도시된 광 송수신기들을 포함하는 데이터 처리 시스템의 또 다른 실시 예를 나타낸다.

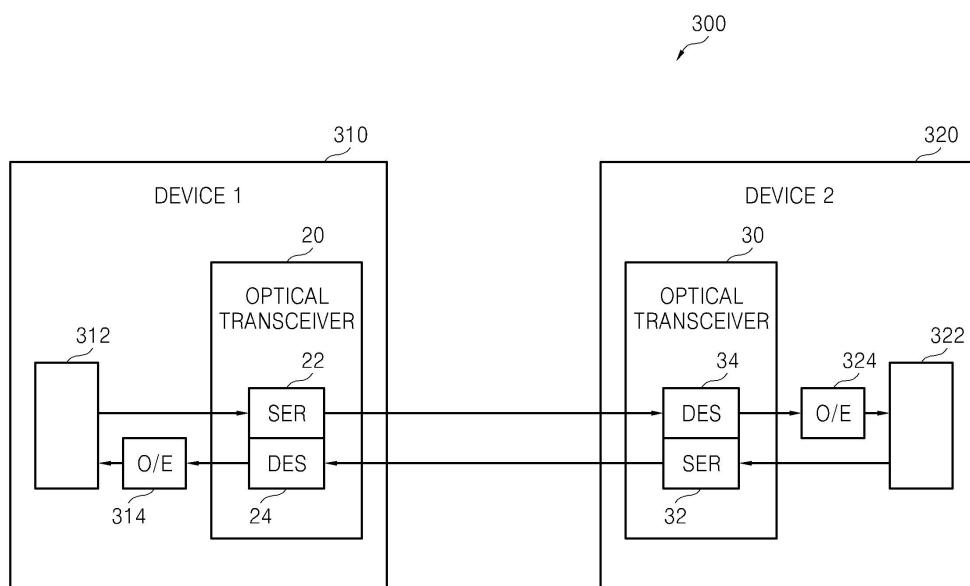

- 도 17은 도 1에 도시된 광 송수신기들을 포함하는 데이터 처리 시스템의 또 다른 실시 예를 나타낸다.

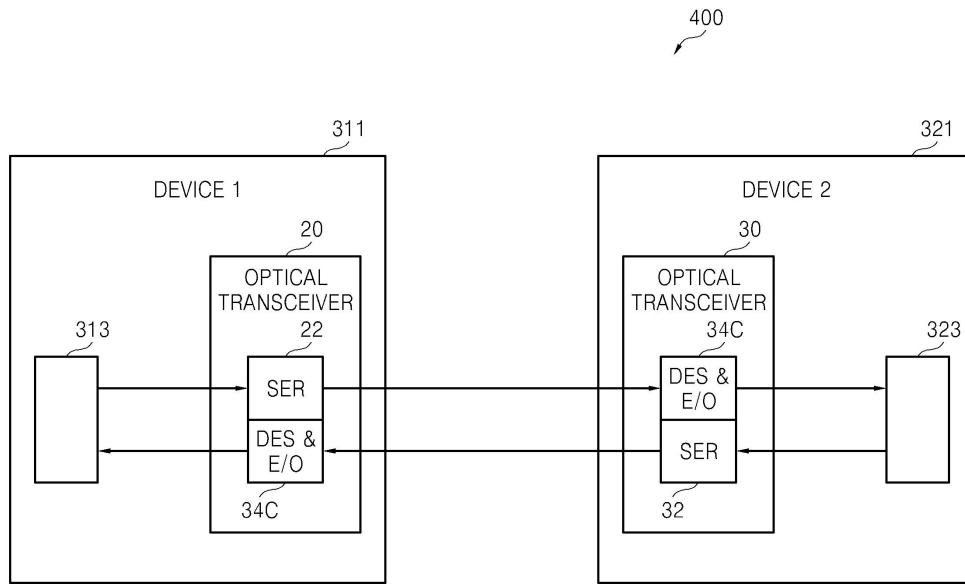

- 도 18은 도 1에 도시된 광 송수신기들을 포함하는 데이터 처리 시스템의 또 다른 실시 예를 나타낸다.

- 도 19는 도 1에 도시된 광 송수신기들을 포함하는 데이터 처리 시스템의 또 다른 실시 예를 나타낸다.

- 도 20은 도 1에 도시된 광 송수신기들을 포함하는 데이터 처리 시스템의 또 다른 실시 예를 나타낸다.

- 도 21은 도 1에 도시된 광 송수신기들을 포함하는 데이터 처리 시스템의 또 다른 실시 예를 나타낸다.

- 도 22는 도 1에 도시된 광 송수신기들을 포함하는 데이터 처리 시스템의 또 다른 실시 예를 나타낸다.

- 도 23은 도 1에 도시된 광 송수신기들을 포함하는 데이터 처리 시스템의 또 다른 실시 예를 나타낸다.

- 도 24는 도 1에 도시된 광 송수신기들을 포함하는 데이터 처리 시스템의 또 다른 실시 예를 나타낸다.

- 도 25는 도 2에 도시된 시리얼라이저의 시리얼라이징 방법을 설명하기 위한 플로우차트이다.

- 도 26은 도 6에 도시된 디시리얼라이저의 디시리얼라이징 방법을 설명하기 위한 플로우차트이다.

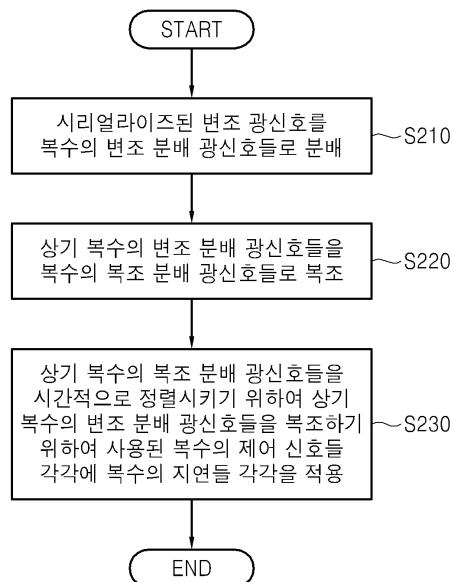

- 도 27은 도 10에 도시된 디시리얼라이저의 디시리얼라이징 방법을 설명하기 위한 플로우차트이다.

### 발명을 실시하기 위한 구체적인 내용

- [0033] 본 명세서에 개시되어 있는 본 발명의 개념에 따른 실시 예들에 대해서 특정한 구조적 또는 기능적 설명들은 단지 본 발명의 개념에 따른 실시 예들을 설명하기 위한 목적으로 예시된 것으로서, 본 발명의 개념에 따른 실시

예들은 다양한 형태들로 실시될 수 있으며 본 명세서에 설명된 실시 예들에 한정되지 않는다.

[0034] 본 발명의 개념에 따른 실시 예들은 다양한 변경들을 가할 수 있고 여러 가지 형태들을 가질 수 있으므로 실시 예들을 도면에 예시하고 본 명세서에 상세하게 설명하고자 한다. 그러나, 이는 본 발명의 개념에 따른 실시 예들을 특정한 개시 형태들에 대해 한정하려는 것이 아니며, 본 발명의 사상 및 기술 범위에 포함되는 모든 변경, 균등물, 또는 대체물을 포함한다.

[0035] 제1 또는 제2 등의 용어는 다양한 구성 요소들을 설명하는데 사용될 수 있지만, 상기 구성 요소들은 상기 용어들에 의해 한정되어서는 안 된다. 상기 용어들은 하나의 구성 요소를 다른 구성 요소로부터 구별하는 목적으로만, 예컨대 본 발명의 개념에 따른 권리 범위로부터 이탈되지 않은 채, 제1구성요소는 제2구성요소로 명명될 수 있고, 유사하게 제2구성요소는 제1구성요소로도 명명될 수 있다.

[0036] 어떤 구성요소가 다른 구성요소에 "연결되어" 있다거나 "접속되어" 있다고 언급된 때에는, 그 다른 구성요소에 직접적으로 연결되어 있거나 또는 접속되어 있을 수도 있지만, 중간에 다른 구성요소가 존재할 수도 있다고 이해되어야 할 것이다. 반면에, 어떤 구성요소가 다른 구성요소에 "직접 연결되어" 있다거나 "직접 접속되어" 있다고 언급된 때에는, 중간에 다른 구성요소가 존재하지 않는 것으로 이해되어야 할 것이다. 구성요소들 간의 관계를 설명하는 다른 표현들, 즉 "~사이에"와 "바로 ~사이에" 또는 "~에 이웃하는"과 "~에 직접 이웃하는" 등도 마찬가지로 해석되어야 한다.

[0037] 본 명세서에서 사용한 용어는 단지 특정한 실시 예를 설명하기 위해 사용된 것으로, 본 발명을 한정하려는 의도가 아니다. 단수의 표현은 문맥상 명백하게 다르게 뜻하지 않는 한, 복수의 표현을 포함한다. 본 명세서에서, "포함하다" 또는 "가지다" 등의 용어는 설시된 특징, 숫자, 단계, 동작, 구성요소, 부분품 또는 이들을 조합한 것이 존재함을 지정하려는 것이지, 하나 또는 그 이상의 다른 특징들이나 숫자, 단계, 동작, 구성요소, 부분품 또는 이들을 조합한 것들의 존재 또는 부가 가능성을 미리 배제하지 않는 것으로 이해되어야 한다.

[0038] 다르게 정의되지 않는 한, 기술적이거나 과학적인 용어를 포함해서 여기서 사용되는 모든 용어들은 본 발명이 속하는 기술 분야에서 통상의 지식을 가진 자에 의해 일반적으로 이해되는 것과 동일한 가진다. 일반적으로 사용되는 사전에 정의되어 있는 것과 같은 용어들은 관련 기술의 문맥상 가지는 의미와 일치하는 의미를 갖는 것으로 해석되어야 하며, 본 명세서에서 명백하게 정의하지 않는 한, 이상적이거나 과도하게 형식적인 의미로 해석되지 않는다.

[0039] 이하, 첨부한 도면을 참조하여 본 발명의 바람직한 실시 예를 설명함으로써, 본 발명을 상세히 설명한다.

[0040] 도 1은 본 발명의 실시 예에 따른 복수의 광 송수신기들을 포함하는 데이터 처리 시스템의 블록도를 나타낸다.

[0041] 도 1을 참조하면, 시리얼 통신 프로토콜을 사용하여 시리얼라이즈된 광 데이터를 주거나 받을 수 있는 데이터 처리 시스템(10)은 제1광 송수신기(20)와 제2광 송수신기(30)를 포함한다. 예컨대, 제1광 송수신기(20)는 마스터(master)와 슬레이브(slave) 중에서 어느 하나에 구현될 수 있고, 제2광 송수신기(30)는 상기 마스터와 상기 슬레이브 중에서 다른 하나에 구현될 수 있다.

[0042] 제1광 송수신기(20)는 제1광 시리얼라이저(optical serializer; 22)와 제1광 디시리얼라이저(optical deserializer; 24)를 포함한다.

[0043] 제2광 송수신기(30)는 제2광 시리얼라이저(32)와 제2광 디시리얼라이저(34)를 포함한다. 제2광 디시리얼라이저(34)는 도 6, 도 10, 도 13, 또는 도 14에 도시된 광 디시리얼라이저로 구현될 수 있다. 또한, 제1광 디시리얼라이저(24)의 구조는 제2광 디시리얼라이저(34)의 구조와 실질적으로 동일하다.

[0044] 송신기로서 사용될 수 있는 각 광 시리얼라이저(22와 32)는 변조되지 않은 광(신호)을 이용하여 저속의 병렬 전기신호들을 고속의 직렬 광신호들로 변환할 수 있다. 또한, 수신기로서 사용될 수 있는 각 광 디시리얼라이저(24와 34)는 고속의 직렬 광신호들을 저속의 병렬 전기신호들을 변환할 수 있다.

[0045] 제1광 시리얼라이저(22)는 변조되지 않고 연속적인(continuous) 제1광신호 (CWA)를 이용하여 병렬 전기신호들 (INA) 각각을 변조하고, 변조된 전기신호들 각각을 시리얼라이즈하고, 시리얼라이즈된 변조된 광신호(OSER1)를 제1광통신 버스(26-1)를 통하여 제2광 디시리얼라이저(34)로 전송할 수 있다.

[0046] 또한, 제2광 시리얼라이저(32)는 변조되지 않고 연속적인 제2광신호(CWB)를 이용하여 병렬 전기신호들(INB)을 변조하고, 변조된 전기신호들을 시리얼라이즈하고, 시리얼라이즈된 변조된 광신호(OSER2)를 제2광통신 버스(26-2)를 통하여 제1광 디시리얼라이저(24)로 전송할 수 있다.

- [0047] 도 1에서는 두 개의 광 통신 버스들(26-1과 26-2)을 공유하는 광 송수신기들 (20과 30)이 도시되어 있으나, 실시 예에 따라 두 개의 광 송수신기들(20과 30)은 하나의 광 통신 버스를 통하여 데이터를 주거나 받을 수 있다. 이때 광 통신 버스는 채널(channel)이라고 불릴 수도 있다.

- [0048] 각 광통신 버스(26-1과 26-2)로서 광 도파로(optical waveguide)가 사용될 수 있다. 상기 광 도파로는 광섬유 또는 직사각형의 도파로(rectangular waveguide)를 포함한다. 상기 광 도파로는 집적 광 회로들(integrated optical circuits)에서 구성 요소로서 사용될 수 있다. 상기 광 도파로의 구성 물질은 유리, 폴리머(polymer), 또는 반도체(semiconductor)일 수 있다.

- [0049] 본 명세서에서 사용되는 광신호는 특별한 언급이 없으면 광 도파로를 통하여 전송되는 것을 의미한다. 데이터 처리 시스템(10)은 시리얼 인터페이스(serial interface)를 통하여 데이터를 주거나 받을 수 있는 모든 전자 장치들을 포함한다.

- [0050] 도 2는 도 1에 도시된 제1광 시리얼라이저의 블록도를 나타낸다.

- [0051] 도 2에서는 설명의 편의를 위하여 제1광 시리얼라이저(22)를 도시하나, 제1광 시리얼라이저(22)의 구조는 제2광 시리얼라이저(32)의 구조와 동일하므로 제2광 시리얼라이저(32)에 대한 상세한 설명은 생략한다.

- [0052] 패러렐-시리얼 변환기(parallel-serial converter)로서 사용될 수 있는 제1광 시리얼라이저(22)는 광 분배기(optical splitter; 40), 복수의 광 변조기들(42-1~42-N)을 포함하는 광 변조 유닛(42), 및 커플링 유닛(coupling unit; 43)을 포함한다.

- [0053] 커플링 유닛(43)은 복수의 광학적 지연 소자들(44-1~44-(N-1))을 포함하는 제1지연 유닛(44)과 광 결합기(optical coupler; 46)를 포함한다. 여기서, N은 자연수이다.

- [0054] 1\*N 광 분배기로서 구현될 수 있는 광 분배기(40)는 변조되지 않은 하나의 광을 병렬 전기신호들(INA)의 수(N) 만큼 분배하고, 분배된 광들 각각을 N개의 변조기들(42-1~42-N) 각각으로 공급할 수 있다. 상기 광을 생성하기 위한 광원으로서 레이저 다이오드가 사용될 수 있다.

- [0055] 도 2에서는 하나의 광원(미 도시)으로부터 출력된 광(CWA)이 1\*N 광 분배기 (40)에 의하여 N개의 광들로 분배되고 N개로 분배된 광들 각각이 N개의 광 변조기들(42-1~42-N) 각각으로 공급되는 것을 도시하였으나, 실시 예에 따라 N개의 광 변조기들(42-1~42-N) 각각으로 공급되는 광을 생성하기 위한 광원은 서로 다를 수 있다. 또한, 다른 실시 예에 따라, 복수의 광원들 각각으로부터 생성된 광은 N개의 광 변조기들(42-1~42-N) 중에서 일부의 광 변조기들로 공급될 수 있다.

- [0056] 도 3은 도 2에 도시된 제1광 시리얼라이저로 입력되는 병렬 전기신호들의 예를 나타낸다. 도 2와 도 3을 참조하면, N개의 광 변조기들(42-1~42-N) 각각은 1\*N 광 분배기(40)로부터 출력된 광, 예컨대 변조되지 않은 광 또는 광 신호를 이용하여 N개의 병렬 전기신호들(IN<sub>1</sub>~IN<sub>N</sub>) 각각을 변조하고, 변조된 광 신호들 각각을 출력한다. N개의 광 변조기들(42-1~42-N) 각각은 전-광 변환기(Electrical to Optical converter)의 기능을 수행할 수 있다.

- [0057] 도 4는 도 2에 도시된 광학적 지연 소자들의 출력 신호들을 나타낸다. 도 2와 도 4를 참조하면, 각 광학적 지연 소자(44-1~44-(N-1))는 각 광 변조기(42-2~42-N)로부터 출력된 각 변조 광신호를 광학적으로 지연시키고, 지연된 각 변조 광신호(OP<sub>1</sub>, OP<sub>2</sub>, OP<sub>3</sub>, ..., OP<sub>N</sub>)를 출력한다. 각 광학적 지연 소자(44-1~44-(N-1))는 광학적 지연 라인(optical delay line)으로 구현될 수 있다.

- [0058] 도 4에 도시된 바와 같이, 제1광 변조기(42-1)로부터 출력된 변조된 제1광신호(OP<sub>1</sub>)는 광학적 지연 없이 N\*1 광 결합기로 구현될 수 있는 광 결합기(46)로 전송된다. 광학적 지연 소자(44-1)는 제2광 변조기(42-2)로부터 출력된 변조된 광신호를  $\Delta T(D_1=\Delta T)$  만큼 지연시키고  $\Delta T$  만큼 지연된 변조된 제2광신호(OP<sub>2</sub>)를 N\*1 광 결합기(46)로 전송한다. 광학적 지연 소자(44-2)는 제3광 변조기(42-3)로부터 출력된 변조된 광신호를  $2\Delta T(D_2)$  만큼 지연시키고  $2\Delta T$  만큼 지연된 변조된 제3광신호(OP<sub>3</sub>)를 N\*1 광 결합기(46)로 전송한다. 광학적 지연 소자(44-(N-1))는 변조된 제N광 변조기(42-N)로부터 출력된 변조된 광신호를  $(N-1) \times \Delta T(D_{N-1})$  만큼 지연시키고  $(N-1) \times \Delta T$  만큼 지연된 변조된 제N광신호(OP<sub>N</sub>)를 N\*1 광 결합기(46)로 전송한다.

- [0059] 도 5는 도 2에 도시된 제1광 시리얼라이저에 의하여 시리얼라이즈된 광신호를 나타낸다. 도 2와 도 5를 참조하

면,  $N*1$  광 결합기(46)는 제1지연 유닛(44)으로부터 출력되는 각 변조된 광신호( $OP_1, OP_2, OP_3, \dots, OP_N$ )를 시리얼라이즈하고, 시리얼라이즈된 변조된 광신호(OSER1)를 출력한다.

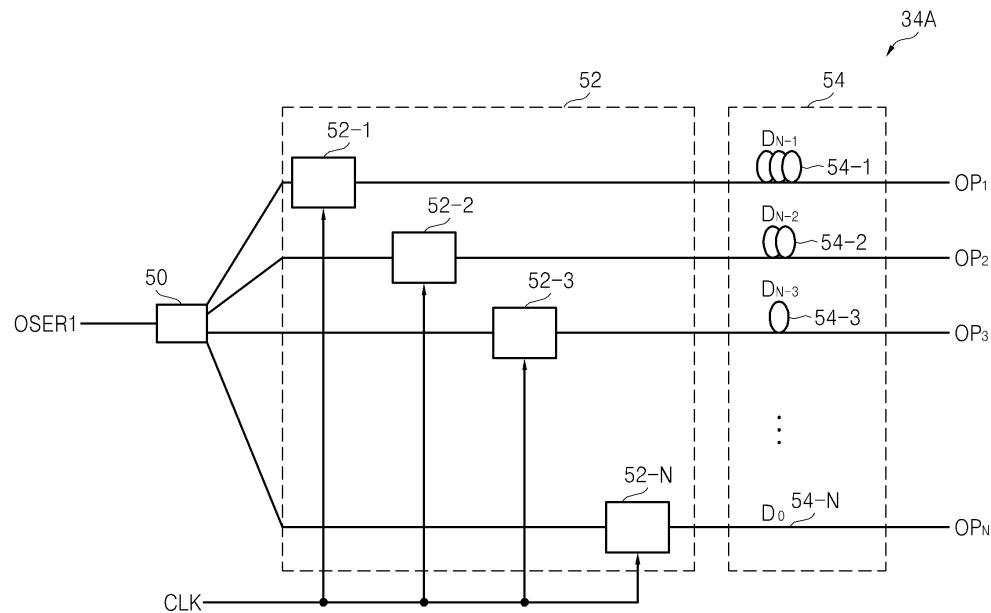

[0060] 도 6은 도 1에 도시된 제2광 디시리얼라이저의 일 실시 예를 나타내는 블록도를 나타내고, 도 7은 도 6에 도시된 광학적 지연 소자들의 출력 신호들을 나타낸다.

[0061] 제1광 디시리얼라이저(24)의 구조와 제2광 디시리얼라이저(34)의 구조는 동일하므로, 설명의 편의를 위하여 제2광 디시리얼라이저(34A)를 참조하여 설명한다.

[0062] 시리얼-패러렐 변환기(serial-parallel converter)로 사용될 수 있는 제2광 디시리얼라이저(34A)는 광 분배기(50), 복수의 광 복조기들(52-1~52-N)을 포함하는 복조 유닛(52), 및 복수의 광학적 지연 소자들(54-1, 54-2, 54-3, ... 54-N)을 포함하는 제2지연 유닛(54)을 포함한다.

[0063]  $1*N$  광 분배기로 구현될 수 있는 광 분배기(optical splitter; 50)는 제1광 시리얼라이저(22)로부터 출력되고 제1광통신 버스(26-1)를 통하여 입력된 시리얼라이즈된 변조 광신호(OSER1)를 복수의 변조 광신호들로 분배(split)할 수 있다.

[0064] 복조 유닛(52)은 복수의 변조 분배 광신호들을 복조하여 복수의 복조 분배 광신호들(demodulated split optical signals) 각각을 생성할 수 있다.

[0065] 제2지연 유닛(54)은 복조 유닛(52)에 의하여 복조된 복수의 복조 분배 광신호들 각각을 서로 다른 지연량만큼 지연시켜 지연된 복수의 병렬 광신호들 또는 복수의 복조 분배 광신호들( $OP_1, OP_2, OP_3, \dots, OP_N$ ) 각각을 출력할 수 있다.

[0066] 예컨대, 제2지연 유닛(54)은 복조 유닛(52)에 의하여 복조된  $N$ 개의 광신호들 각각을  $dT*(N-1)$ 부터 0까지  $dT$ 씩 순차적으로 지연시켜 상기 지연된 복수의 병렬 광신호들( $OP_1, OP_2, OP_3, \dots, OP_N$ )을 생성할 수 있다.

[0067] 예컨대, 광학적 지연 소자(54-1)는 광 복조기(52-1)로부터 출력된 복조 광신호를  $(N-1) \times \Delta T (=D_{N-1})$ 만큼 지연시켜  $(N-1) \times \Delta T$ 만큼 지연된 복조 광신호( $OP_1$ )를 출력하고, 광학적 지연 소자(54-2)는 광 복조기(52-1)로부터 출력된 복조 광신호를  $(N-2) \times \Delta T (=D_{N-2})$ 만큼 지연시켜  $(N-2) \times \Delta T$ 만큼 지연된 복조 광신호( $OP_2$ )를 출력하고, 광학적 지연 소자(54-3)는 광 복조기(52-3)로부터 출력된 복조 광신호를  $(N-3) \times \Delta T (=D_{N-3})$ 만큼 지연시켜  $(N-3) \times \Delta T$ 만큼 지연된 복조 광신호( $OP_3$ )를 출력하고,  $N$ 번째 광학적 지연 소자(54-N)는 광 복조기(52-1)로부터 출력된 복조 광신호( $OP_N$ )를 지연시키지 않고 그대로 출력한다.

[0068] 즉, 복조 유닛(52)으로부터 출력된 복조 광신호들의 개수가  $N$ 개일 때, 제2지연 유닛(54)은  $N$ 개의 복조 광신호들 각각을  $dT*(N-1)$ 부터 0까지  $dT$ 씩 순차적으로 지연시켜 지연된 복수의 병렬 광신호들 또는 복수의 복조 분배 광신호들( $OP_1, OP_2, OP_3, \dots, OP_N$ )을 생성한다. 복수의 병렬 광신호들( $OP_1, OP_2, OP_3, \dots, OP_N$ )은 시간적으로(in-time) 정렬(aligned)된다.

[0069] 복조 유닛(52)은 하나의 전기적인 클락 신호(CLK)를 이용하여 광 분배기(50)로부터 출력된 병렬 광신호들 각각을 복조할 수 있다.

[0070] 복조 유닛(52)에 포함된 복수의 광 복조기들(52-1~52-N) 각각의 구성은 도 2에 도시된 변조 유닛(42)에 포함된 복수의 광 변조기들(42-1~42-N) 각각의 구성과 실질적으로 동일할 수 있으나 기능적으로는 복조 기능 또는 스위치 기능을 수행할 수 있다.

[0071] 도 8은 도 6에 도시된 각 복조기들 각각이 각 광신호를 선택하는 과정을 설명하기 위한 타이밍 도들이고, 도 9는 도 6에 도시된 제2광 디시리얼라이저(34A)의 출력 신호들을 나타낸다.

[0072] 도 6부터 도 9를 참조하면, 각 복조기(52-1~52-N)는 하나의 전기적인 클락 신호(CLK)의 상승 에지에 응답하여 광 분배기(50)로부터 출력된 시리얼라이즈된 변조 광신호(OSER1)로부터 하나의 광신호만을 선택적으로 복조 또는 검출할 수 있다.

[0073] 즉, 각 복조기(52-1~52-N)는 전기적인 클락 신호(CLK)의 상승 에지에 응답하여 동작하는 스위치의 기능을 수행할 수 있다. 예컨대, 도 6에 도시된 전기적인 클락 신호(CLK)는 도 2에 도시된 병렬 전기신호들(INA)을 생성하기 위하여 사용된 클락 신호와 실질적으로 동기된 신호일 수 있다. 실시 예에 따라 각 복조기(52-1~52-N)는 하

나의 전기적인 클락 신호(CLK)의 상승 에지 또는 하강 에지 중에서 적어도 하나에 응답하여 복조 동작 또는 스위칭 동작을 수행할 수 있다.

[0074] 도 6과 도 9를 참조하면, 제2광 디시리얼라이저(34A)는 제1광 시리얼라이저(22)의 제1지연 유닛(44)으로부터 출력된 병렬 광신호들(OP<sub>1</sub>, OP<sub>2</sub>, OP<sub>3</sub>, ..., OP<sub>N</sub>)과 실질적으로 동일한 병렬 광신호들(OP<sub>1</sub>, OP<sub>2</sub>, OP<sub>3</sub>, ..., OP<sub>N</sub>)을 복원 또는 재생할 수 있다.

[0075] 도 10은 도 1에 도시된 제2광 디시리얼라이저의 다른 실시 예를 나타내는 블록도를 나타내고, 도 11은 도 10에 도시된 복조 유닛으로부터 출력된 신호들의 타이밍 도를 나타내고, 도 12는 도 10에 도시된 복조기들 각각의 광신호 선택 과정을 설명하기 위한 타이밍 도들이다.

[0076] 도 10에 도시된 바와 같이, 제2광 디시리얼라이저(34B)는 광 분배기(60), 복수의 광 복조기들(62-1~62-N)을 포함하는 복조 유닛(62), 및 복수의 광학적 지연 소자들(64-1~64-(N-1))을 포함하는 클락 신호 지연 유닛(64)을 포함한다.

[0077] 1\*N 광 분배기로 구현될 수 있는 광 분배기(60)는 제1광 시리얼라이저(22)에 의하여 시리얼라이즈되고 제1광통신 버스(26-1)를 통하여 입력된 시리얼라이즈된 변조 광신호(OSER1)를 N개의 변조된 분배 광신호들로 분배(split)한다.

[0078] 클락 신호 지연 유닛(64)은 전기적인 클락 신호(CLK)를 서로 다른 지연량만큼 지연시켜 복수의 지연 클락 신호들 또는 복수의 제어 신호들(CLK, CLK<sub>1</sub>, CLK<sub>2</sub>, ..., CLK<sub>N-1</sub>)을 생성한다.

[0079] 예컨대, 1\*N 광 분배기(60)에 의하여 분배된 광신호들의 개수가 N개일 때, 각각의 광학적 지연 소자들(64-1~64-(N-1))은 전기적인 클락 신호(CLK)를 dT부터 dT\*(N-1)까지 dT씩 순차적으로 지연시켜 복수의 지연 클락 신호들(CLK, CLK<sub>1</sub>, CLK<sub>2</sub>, ..., CLK<sub>N-1</sub>)을 생성한다. 즉, 클락 신호 지연 유닛(64)은 전기적인 클락 신호(CLK)를 0부터 dT\*(N-1)까지 dT씩 순차적으로 지연시켜 복수의 지연 클락 신호들(CLK, CLK<sub>1</sub>, CLK<sub>2</sub>, ..., CLK<sub>N-1</sub>)을 생성할 수 있다.

[0080] 각 광 복조기(62-1, 62-2, 62-3, ..., 62-N)는 각 지연 클락 신호(CLK, CLK<sub>1</sub>, CLK<sub>2</sub>, ..., CLK<sub>N-1</sub>)에 응답하여 1\*N 광 분배기(60)로부터 출력된 각 시리얼라이즈된 광신호로부터 대응되는 하나의 광신호(OP<sub>1</sub>, OP<sub>2</sub>, OP<sub>3</sub>, ..., OP<sub>N</sub>)만을 출력한다. 도 6과 도 10을 참조하면, 제2광 디시리얼라이저(34A 또는 34B)는 전기적인 클락 신호(CLK)를 이용하여 광-전 변환 없이 시리얼라이즈된 변조된 광신호로부터 디시리얼라이즈된 병렬 광신호들로 변환할 수 있다.

[0081] 도 13은 도 1에 도시된 제2광 디시리얼라이저의 또 다른 실시 예를 나타내는 블록도를 나타낸다.

[0082] 도 13에 도시된 제2광 디시리얼라이저(34C)의 구조는 복수의 광-전 변환기들(56-1~56-N)을 포함하는 광-전 변환 유닛(56)을 포함하는 것을 제외하면 도 6에 도시된 제2광 디시리얼라이저(34A)의 구조와 동일하다.

[0083] 각 광-전 변환기(56-1~56-N)는 각 광학적 지연 소자(54-1~54-N)로부터 출력된 각 복조 광신호(OP<sub>1</sub>, OP<sub>2</sub>, OP<sub>3</sub>, ..., OP<sub>N</sub>)를 각 전기 신호(E0<sub>1</sub>, E0<sub>2</sub>, E0<sub>3</sub>, ..., E0<sub>N</sub>)로 변환할 수 있다. 각 광-전 변환기(56-1~56-N)는 광 검출기, 광 감지 소자 또는 포토다이오드로 구현될 수 있다. 각 복조 광신호(OP<sub>1</sub>, OP<sub>2</sub>, OP<sub>3</sub>, ..., OP<sub>N</sub>)는 시간적으로 정렬되고 각 전기 신호(E0<sub>1</sub>, E0<sub>2</sub>, E0<sub>3</sub>, ..., E0<sub>N</sub>)는 시간적으로 정렬된다.

[0084] 도 14는 도 1에 도시된 제2광 디시리얼라이저의 또 다른 실시 예를 나타내는 블록도를 나타낸다.

[0085] 도 14에 도시된 제2광 디시리얼라이저(34D)의 구조는 복수의 광-전 변환기들(66-1~66-N)을 포함하는 광-전 변환 유닛(66)을 포함하는 것을 제외하면 도 10에 도시된 제2광 디시리얼라이저(34B)의 구조와 동일하다.

[0086] 각 광-전 변환기(66-1~66-N)는 각 광 복조기(62-1~62-N)로부터 출력된 각 복조 광신호(OP<sub>1</sub>, OP<sub>2</sub>, OP<sub>3</sub>, ..., OP<sub>N</sub>)를 각 전기 신호(E0<sub>1</sub>, E0<sub>2</sub>, E0<sub>3</sub>, ..., E0<sub>N</sub>)로 변환할 수 있다. 각 광-전 변환기(62-1~62-N)는 광 검출기, 광 감지 소자 또는 포토다이오드로 구현될 수 있다. 각 복조 광신호(OP<sub>1</sub>, OP<sub>2</sub>, OP<sub>3</sub>, ..., OP<sub>N</sub>)는 시간적으로 정렬되고 각 전기 신호(E0<sub>1</sub>, E0<sub>2</sub>, E0<sub>3</sub>, ..., E0<sub>N</sub>)는 시간적으로 정렬된다.

[0087] 도 15는 도 1에 도시된 광 송수신기들을 포함하는 데이터 처리 시스템의 일 실시 예를 나타낸다. 광 송수신기들

(20과 30) 각각은 인터페이스 또는 광 시리얼라이저/디시리얼라이저(SERDES)를 의미할 수 있다.

[0088] 도 15를 참조하면, 데이터 처리 시스템(100)은 CPU(110), 복수의 데이터 버스들(101-1~101-3), 및 복수의 메모리 모듈들(130)을 포함한다. 복수의 메모리 모듈들(130) 각각은 복수의 커플러들(111-1, 111-2, 및 111-3) 각각을 통하여 복수의 데이터 버스들(101-1~101-3) 각각과 시리얼라이즈된 데이터를 주거나 받을 수 있다.

[0089] 실시 예에 따라, 복수의 커플러들(111-1, 111-2, 및 111-3) 각각은 전기적인 커플러(electrical coupler) 또는 광학적인 커플러(optical coupler)로 구현될 수 있다.

[0090] CPU(110)는 제1인터페이스(또는 제1광 송수신기; 20), 메모리 컨트롤러 (112), 및 제1광-전 변환 모듈(114)을 포함한다. 메모리 컨트롤러(112)는 CPU(110)의 제어 하에 제1인터페이스(20)의 동작, 예컨대 송신 또는 수신을 제어할 수 있다. 실시 예에 따라 메모리 컨트롤러(112)는 CPU(110)의 제어 하에 제1광-전 변환 모듈(114)의 동작을 제어할 수 있다.

[0091] 예컨대, 라이트 동작 시, 제1인터페이스(20)는 메모리 컨트롤러(112)의 제어 하에 어드레스들과 제어 신호들을 도 2부터 도 5를 참조하여 설명한 바와 같이 시리얼라이즈하고 시리얼라이즈된 어드레스들과 제어 신호들 (ADD/CTRL)을 광 통신 버스(101-3)로 전송할 수 있다.

[0092] 실시 예에 따라, 제1인터페이스(20)는 메모리 컨트롤러(112)의 제어 하에 어드레스들과 제어 신호들을 전기적인 방법으로 시리얼라이즈하고 시리얼라이즈된 어드레스들과 제어 신호들(ADD/CTRL)을 전기적인 통신 버스(101-3)로 전송할 수 있다.

[0093] 또 다른 실시 예에 따라, 제1인터페이스(20)는 메모리 컨트롤러(112)의 제어 하에 어드레스들과 제어 신호들을 전-광 변환 모듈(미 도시)을 이용하여 시리얼라이즈하고 시리얼라이즈된 어드레스들과 제어 신호들(ADD/CTRL)을 광 통신 버스(101-3)로 전송할 수 있다.

[0094] 즉, 도 15에 도시된 데이터 버스(101-3)는 전기적 통신 버스 또는 광 통신 버스로 구현될 수 있다.

[0095] 제1인터페이스(20)가 시리얼라이즈된 어드레스들과 제어 신호들(ADD/CTRL)을 전기적인 통신 버스 또는 광 통신 버스(101-3)로 전송한 후, 제1인터페이스(20) 내에 구현된 제1광 시리얼라이저는 메모리 컨트롤러(112)의 제어 하에 별별 전기신호들(INA)을 시리얼라이즈하고, 시리얼라이즈된 광신호, 즉 시리얼라이즈된 변조된 라이트 데이터(WDATA=OSER1)를 생성하고, 생성된 라이트 데이터(WDATA=OSER1)를 광 통신 버스(101-2)로 전송할 수 있다.

[0096] 각 메모리 모듈(130)은 제2인터페이스(또는 제2광 송수신기; 30), 제2광-전 변환 모듈(131), 및 복수의 메모리 장치들(135)을 포함한다.

[0097] 각 메모리 모듈(130)은 광학적 DIMM(optical dual in-line memory module), 광학적 Fully Buffered DIMM, 광학적 SO-DIMM(small outline dual in-line memory module), Optical RDIMM(Registered DIMM), Optical LRDIMM(Load Reduced DIMM), UDIMM(Unbuffered DIMM), 광학적 MicroDIMM, 또는 광학적 SIMM(single in-line memory module)으로 구현될 수 있다.

[0098] 도 1부터 도 15를 참조하면, 제2인터페이스(30) 내에 구현된 제2광 디시리얼라이저(34)는 제1광 시리얼라이저 (20)에 의하여 시리얼라이즈되고 광통신 버스 (101-2)를 통하여 입력된 시리얼라이즈된 변조된 라이트 데이터 (WDATA=OSER1)를 디시리얼라이즈하고 디시리얼라이즈된 라이트 데이터를 제2광-전 변환 모듈(131)로 전송한다.

[0099] 제2광-전 변환 모듈(131)은 상기 디시리얼라이즈된 라이트 데이터를 디시리얼라이즈된 전기 신호들로 변환하고, 변환된 전기 신호들을 복수의 메모리 장치들 (135) 중에서 적어도 하나의 메모리 장치로 전송할 수 있다.

[0100] 실시 예에 따라, 각 메모리 모듈(130)은 제2광-전 변환 모듈(131)로부터 출력된 디시리얼라이즈된 전기 신호들을 버퍼링하기 위한 전기적인 버퍼(133)를 더 포함할 수 있다. 전기적인 버퍼(133)는 상기 디시리얼라이즈된 전기 신호들을 버퍼링하고 버퍼링된 전기 신호들을 복수의 메모리 장치들(135) 중에서 적어도 하나의 메모리 장치로 전송할 수 있다.

[0101] 복수의 메모리 장치들(135) 각각은 복수의 메모리 셀들을 포함하는 메모리 어레이(137), 메모리 어레이(137)를 액세스할 수 있는 액세스 회로(139), 및 액세스 회로(139)의 동작을 제어할 수 있는 컨트롤러(미 도시)를 포함할 수 있다.

[0102] 도 1과 도 15를 참조하면, 리드 동작 시, 메모리 장치(135)로부터 출력된 별별 전기신호들(INB)은 제2인터페이스(30)에 구현된 제2광 시리얼라이저(32)에 의하여 광학적으로 시리얼라이즈되고 시리얼라이즈된 변조된 리드

데이터(RDATA=OSER2)는 광통신 버스(101-1=26-2)를 통하여 CPU(110)에 구현된 제1디시리얼라이저(24)로 전송된다. 도 6에 도시된 제1광 디시리얼라이저(34A)는 입력된 시리얼라이즈된 리드 데이터(RDATA=OSER2)를 디시리얼라이즈하고, 디시리얼라이즈된 리드 데이터를 제1광-전 변환 모듈(114)로 전송한다.

- [0103] 제1광-전 변환 모듈(114)은 디시리얼라이즈된 리드 데이터를 병렬 전기신호들로 변환하고 변환된 전기 신호들을 메모리 컨트롤러(112)로 전송한다.

- [0104] 도 16은 도 1에 도시된 광 송수신들을 포함하는 데이터 처리 시스템의 다른 실시 예를 나타낸다. 광 송수신들(20과 30) 각각은 인터페이스 또는 광 시리얼라이저/디시리얼라이저(SERDES)를 의미할 수 있다.

- [0105] 도 16을 참조하면, 데이터 처리 시스템(200)은 CPU(110), 복수의 데이터 버스들(101-1, 101-2, 및 101-3), 및 복수의 메모리 모듈들(140)을 포함한다.

- [0106] 복수의 메모리 모듈들(140) 각각은 제2인터페이스(30)와, 복수의 메모리 장치들(141)을 포함한다.

- [0107] 복수의 메모리 장치들(141) 각각은 제2광-전 변환 모듈(145)을 포함한다. 또한, 복수의 메모리 장치들(141) 각각은 복수의 메모리 셀들을 포함하는 메모리 어레이(143), 메모리 어레이(143)를 액세스할 수 있는 액세스 회로(미 도시), 및 상기 액세스 회로의 동작을 제어할 수 있는 컨트롤러(미 도시)를 포함할 수 있다.

- [0108] 데이터 처리 시스템(200)의 라이트 동작은 도 1, 도 2, 도 6, 도 10, 및 도 16을 참조하여 상세히 설명된다. 우선, 라이트 동작을 수행하기 위한 어드레스들과 제어 신호들(ADD/CTRL)은 대응되는 데이터 버스(101-3)를 통하여 이미 복수의 메모리 장치들(141) 중에서 적어도 하나로 전송되었다고 가정한다.

- [0109] CPU(110)의 제1인터페이스(20) 내의 제1광 시리얼라이저(22)는 메모리 컨트롤러(112)의 제어 하에 광(CWA)을 이용하여 병렬 전기신호들(INA)을 직렬 광신호로 시리얼라이즈하고, 시리얼라이즈된 직렬 광신호, 즉 라이트 데이터(WDATA)를 광학적 데이터 버스(101-2)에 접속된 광학적 커플러(111-2)를 통하여 제1메모리 모듈(130)의 제2인터페이스(30)의 제2광 디시리얼라이저(34)로 전송한다.

- [0110] 제2인터페이스(30)의 제2광 디시리얼라이저(34A 또는 34B)는 시리얼라이즈된 직렬 광신호(WDATA)를 전기적인 클락 신호(CLK)를 이용하여 병렬 광신호들로 디시리얼라이즈하고, 디시리얼라이즈된 병렬 광신호들을 복수의 메모리 장치들(141) 중에서 어느 하나의 메모리 장치로 전송한다.

- [0111] 상기 어느 하나의 메모리 장치의 제2광-전 변환 모듈(145)은 제2인터페이스(30)의 제2광 디시리얼라이저(34)로부터 출력된 디시리얼라이즈된 병렬 광신호들을 병렬 전기신호들로 변환한다. 상기 액세스 회로는 상기 마이크로컨트롤러의 제어 하에 상기 병렬 전기신호들을 메모리 어레이(143)에 라이트한다.

- [0112] 데이터 처리 시스템(200)의 리드 동작은 도 1, 도 2, 도 6, 도 10, 및 도 16을 참조하여 상세히 설명된다. 우선, 리드 동작을 수행하기 위한 어드레스들과 제어 신호들(ADD/CTRL)은 대응되는 데이터 버스(101-3)를 통하여 이미 복수의 메모리 장치들(141) 중에서 적어도 하나로 전송되었다고 가정한다.

- [0113] 메모리 장치(141)의 제2인터페이스(30) 내의 제2광 시리얼라이저(32)는 상기 마이크로컨트롤러의 제어 하에 광(CWB)을 이용하여 병렬 전기신호들(INB)을 직렬 광신호로 시리얼라이즈하고, 시리얼라이즈된 직렬 광신호, 즉 리드 데이터(RDATA)를 광학적 데이터 버스(101-1)에 접속된 광학적 커플러(111-1)를 통하여 CPU(110)의 제1인터페이스(20)의 제1광 디시리얼라이저(24)로 전송한다.

- [0114] 제1인터페이스(20)의 제1광 디시리얼라이저(24)는 시리얼라이즈된 직렬 광신호(RDATA)를 전기적인 클락 신호(CLK)를 이용하여 병렬 광신호들로 디시리얼라이즈하고, 디시리얼라이즈된 병렬 광신호들을 제1광-전 변환 모듈(114)로 전송한다.

- [0115] 제1광-전 변환 모듈(114)은 제1인터페이스(20)의 제1광 디시리얼라이저(24)로부터 출력된 디시리얼라이즈된 병렬 광신호들을 병렬 전기신호들로 변환하고 상기 병렬 전기신호들을 메모리 컨트롤러(112)로 출력한다. 메모리 컨트롤러(112)는 병렬 전기신호들을 리드 데이터로서 처리한다.

- [0116] 도 17은 도 1에 도시된 광 송수신들을 포함하는 데이터 처리 시스템의 또 다른 일 실시 예를 나타낸다. 도 17을 참조하면, 데이터 처리 시스템(300)은 제1반도체 장치(310)와 제2반도체 장치(320)를 포함한다.

- [0117] 제1반도체 장치(310)와 제2반도체 장치(320) 각각은 시리얼 통신 프로토콜을 이용하여 데이터를 주거나 받을 수 있는 장치이다.

- [0118] 상기 시리얼 통신 프로토콜은 그 실시 예로서 UART(Universal Asynchronous Receiver Transmitter),

SPI(Serial Peripheral Interface), I2C(Inter-integrated Circuit), SMBus(System Management Bus), CAN(Controller Area Network), USB (Universal Serial Bus), MIPI®(mobile industry processor interface)에서 규정하는 CSI(camera serial interface), MIPI®에서 규정하는 DSI(display serial interface), MDDI(Mobile Display Digital Interface), 또는 LIN(Local Interconnect Network)을 지원하는 데이터 통신 프로토콜일 수 있다.

- [0119] 도 1, 도 2, 도 6, 도 10, 및 도 17을 참조하면, 제1반도체 장치(310)에 구현된 제1광 송수신기(20)의 제1광 시리얼라이저(22)는, 제1마이크로프로세서(312)의 제어 하에, 광을 이용하여 병렬 전기신호들을 시리얼라이즈하고 시리얼라이즈된 변조된 광신호를 데이터 버스를 통하여 제2반도체 장치(320)의 제2광 송수신기(30)의 제2광 디시리얼라이저(34는 34A 또는 34B로 구현될 수 있음)로 전송한다.

- [0120] 제2반도체 장치(320)의 제2광-전 변환 모듈(324)은 제2광 디시리얼라이저 (34A, 34B, 또는 34)에 의하여 디시리얼라이즈된 병렬 광신호들을 병렬 전기신호들로 광-전 변환한다.

- [0121] 제2마이크로프로세서(322)는 제2광-전 변환 모듈(324)로부터 출력된 병렬 전기신호들을 처리한다. 예컨대, 라이트 동작 시, 제2마이크로프로세서(322)는 상기 병렬 전기신호들을 메모리 어레이에 라이트할 수 있다.

- [0122] 제2반도체 장치(320)의 제2광 송수신기(30)의 제2광 시리얼라이저(32)는, 제2마이크로프로세서(322)의 제어 하에, 광을 이용하여 병렬 전기신호들(INB)을 시리얼라이즈하고 시리얼라이즈된 병렬 광신호들을 데이터 버스를 통하여 제1반도체 장치(310)의 제1광 송수신기(20)의 제1광 디시리얼라이저(24)로 전송한다.

- [0123] 제1광-전 변환 모듈(314)은 제1광 디시리얼라이저(24)에 의하여 디시리얼라이즈된 병렬 광신호들을 병렬 전기신호들로 광-전 변환한다.

- [0124] 제1마이크로프로세서(312)는 제1광-전 변환 모듈(314)로부터 출력된 병렬 전기신호들을 처리한다. 예컨대, 리드 동작 시, 제1마이크로프로세서(312)는 상기 병렬 전기신호들을 리드 데이터로서 처리할 수 있다. 각 마이크로프로세서(312 또는 322)는 그 명칭에도 불구하고 각 반도체 장치(310과 320)의 동작, 예컨대 라이트 동작 또는 리드 동작을 제어할 수 있는 반도체 프로세서이면 족하다.

- [0125] 도 18은 도 1에 도시된 광 송수신기들을 포함하는 데이터 처리 시스템의 또 다른 실시 예를 나타낸다. 도 18을 참조하면, 데이터 처리 시스템(400)은 제1반도체 장치(311)와 제2반도체 장치(321)를 포함한다.

- [0126] 제1반도체 장치(311)는 제1광 송수신기(20)와 제1마이크로프로세서(313)를 포함한다. 제2반도체 장치(321)는 제2광 송수신기(30)와 제2마이크로프로세서(323)를 포함한다.

- [0127] 각 반도체 장치(311과 321)에 구현된 각 광 디시리얼라이저(34C 또는 34D)는 도 13 또는 도 14에 도시된 바와 같이 광-전 변환 블록을 포함한다. 도 18에 도시된 각 반도체 장치(311과 321)의 각 광 디시리얼라이저(34C)는 도 14에 도시된 광 디시리얼라이저(34D)로 대체될 수 있다.

- [0128] 도 1, 도 2, 도 13, 도 14, 및 도 18을 참조하면, 제1광 송수신기(20)의 제1광 시리얼라이저(22)는 광을 이용하여 병렬 전기신호들을 시리얼라이즈하고 시리얼라이즈된 광신호를 데이터 버스를 통하여 제2광 송수신기(30)의 제2디시리얼라이저(34C)로 전송한다.

- [0129] 제2디시리얼라이저(34C)는 시리얼라이즈된 광신호를 전기적인 클락 신호를 이용하여 디시리얼라이즈하고 디시리얼라이즈된 광신호들을 광-전 변환 블록을 이용하여 병렬 전기신호들로 변환한다. 제2마이크로프로세서(323)는 제2디시리얼라이저(34C)로부터 출력된 병렬 전기신호들을 처리한다.

- [0130] 제2광 송수신기(30)의 제2광 시리얼라이저(32)는 광을 이용하여 병렬 전기신호들을 시리얼라이즈하고 시리얼라이즈된 광신호를 데이터 버스를 통하여 제1광 송수신기(20)의 제1디시리얼라이저(34C)로 전송한다.

- [0131] 제1광 송수신기(20)의 제1디시리얼라이저(34C)는 시리얼라이즈된 광신호를 전기적인 클락 신호를 이용하여 디시리얼라이즈하고 디시리얼라이즈된 광신호들을 광-전 변환 블록을 이용하여 병렬 전기신호들로 변환한다. 제1마이크로프로세서(313)는 제1디시리얼라이저(34C)로부터 출력된 병렬 전기신호들을 처리한다.

- [0132] 도 19는 도 1에 도시된 광 송수신기들을 포함하는 데이터 처리 시스템의 또 다른 실시 예를 나타낸다.

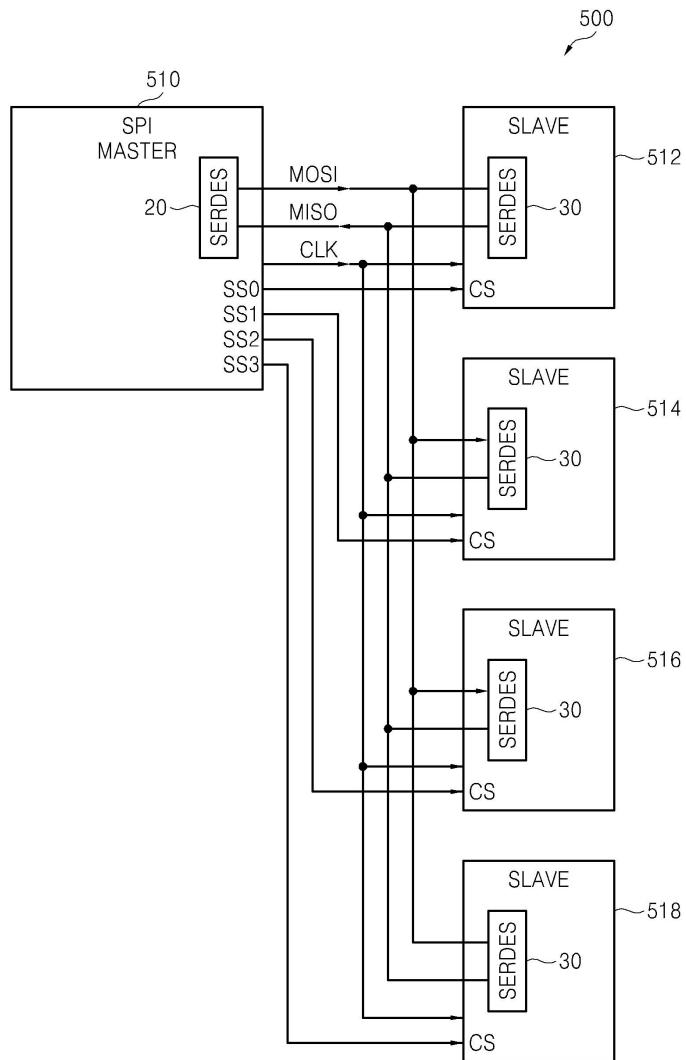

- [0133] 도 19를 참조하면, SPI(serial peripheral interface) 통신 프로토콜을 사용하여 시리얼 데이터를 주거나 받을 수 있는 데이터 처리 시스템(500)은 SPI 마스터(510)와 적어도 하나의 SPI 슬레이브(512, 514, 516, 및 518)를 포함할 수 있다.

- [0134] 적어도 하나의 SPI 슬레이브(512, 514, 516, 및 518) 중에서 어느 하나는 시프트 레지스터, 메모리 칩, 포트 확장기, 디스플레이 드라이버, 데이터 변환기, 프린터, 데이터 저장 장치, 센서, 또는 마이크로프로세서일 수 있다.

- [0135] 제1인터페이스(또는 SERDES; 20)와 제2인터페이스(또는 SERDES; 30)는 대응되는 광학적 데이터 버스를 통하여 시리얼라이즈된 광신호(MOSI(Master Out Slave In) 또는 MISO (Master In Slave Out))를 주거나 받을 수 있다.

- [0136] SPI 마스터(510)는 제1인터페이스(20)의 동작을 제어할 수 있는 마이크로프로세서(미 도시)를 포함하고, 적어도 하나의 SPI 슬레이브(512, 514, 516, 및 518)는 제2인터페이스(30)의 동작을 제어할 수 있는 마이크로프로세서(미 도시)를 포함한다.

- [0137] 또한, 제1인터페이스(20)는 시리얼 클락 신호(CLK)를 전기적인 데이터 버스 또는 광학적 데이터 버스를 통하여 제2인터페이스(30)로 전송할 수 있다.

- [0138] 각 SPI 슬레이브(512, 514, 516, 및 518)는 각 칩 선택 신호(SS0, SS1, SS2, 및 SS3)에 의하여 선택될 수 있다. 이 경우, 각 칩 선택 신호(SS0, SS1, SS2, 및 SS3)는 전기적인 데이터 버스 또는 광학적 데이터 버스를 통하여 제2인터페이스 (30)로 전송할 수 있다.

- [0139] 도 20은 도 1에 도시된 광 송수신기들을 포함하는 데이터 처리 시스템의 또 다른 실시 예를 나타낸다.

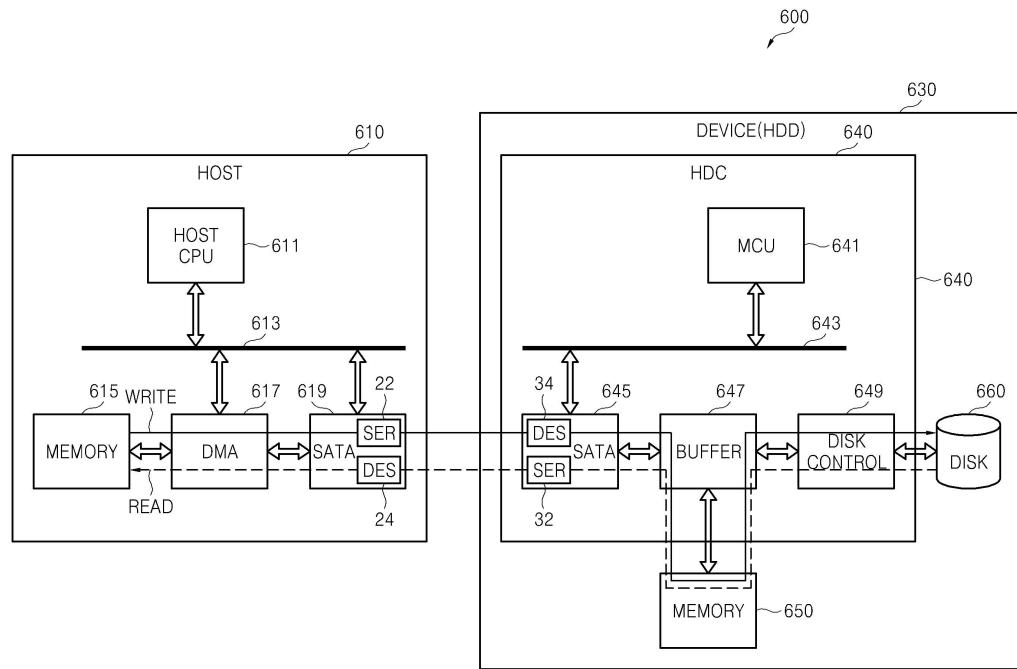

- [0140] SATA(Serial Advanced Technology Attachment) 통신 프로토콜을 사용하여 시리얼 데이터를 주거나 받을 수 있는 데이터 처리 시스템(600)은 SATA 호스트(610)와 SATA 장치(630)를 포함한다.

- [0141] SATA 호스트(610)는 호스트 CPU(611), 데이터 버스(613), 메모리(615), DMA 컨트롤러(617), 및 제1SATA 인터페이스(619)를 포함한다. 호스트 CPU(611)는 DMA 컨트롤러(direct memory access controller; 617) 또는 제1SATA 인터페이스(619)의 동작을 제어한다. 제1SATA 인터페이스(619)는 제1광 시리얼라이저(22)와 제1광 디시리얼라이저(24)를 포함한다. SATA 호스트(610)는 제1SATA 인터페이스(619)의 동작을 제어할 수 있는 컨트롤러를 포함한다. 실시 예에 따라 상기 컨트롤러는 제1SATA 인터페이스(619) 내부에 구현될 수 있고 호스트 CPU(611)가 상기 컨트롤러의 기능을 수행할 수 있다.

- [0142] SATA 장치(630)는 하드디스크 컨트롤러(640)와 메모리 장치(650), 및 자기적 기록 매체(660)를 포함한다. 하드디스크 컨트롤러(640)는 MCU(main control unit; 641), 데이터 버스 (643), 제2SATA 인터페이스(645), 베퍼(647), 및 디스크 컨트롤러(649)를 포함한다.

- [0143] MCU(641)는 제2SATA 인터페이스(645), 베퍼(647), 및 디스크 컨트롤러(649) 중에서 적어도 하나의 동작을 제어한다. 제2SATA 인터페이스(645)는 제2광 시리얼라이저(32)와 제2디시리얼라이저(34)를 포함한다. SATA 장치(630)는 제2SATA 인터페이스(645)의 동작을 제어할 수 있는 컨트롤러를 포함한다. 실시 예에 따라 상기 컨트롤러는 제2SATA 인터페이스(645) 내부에 구현될 수 있고 MCU (641)가 상기 컨트롤러의 기능을 수행할 수 있다.

- [0144] 라이트 동작 시, 메모리(615)에 저장된 라이트 데이터는 DMA 컨트롤러(617)의 제어 하에 제1SATA 인터페이스(619)의 제1광 시리얼라이저(22)로 전송된다. 제1광 시리얼라이저(22)는 병렬 전기 라이트 데이터를 광을 이용하여 시리얼라이즈하고, 시리얼라이즈된 광 데이터를 데이터 버스를 통하여 제2SATA(645)의 제2디시리얼라이저(34)로 전송한다.

- [0145] 제2디시리얼라이저(34)는 시리얼라이즈된 광 데이터를 전기적 클락 신호를 이용하여 디시리얼라이즈하고, 디시리얼라이즈된 병렬 광신호들을 병렬 전기신호들로 변환한다.

- [0146] 베퍼(647)는 상기 병렬 전기신호들을 베퍼링하고 베퍼링된 전기 신호들을 메모리 장치(650)에 일시적으로 저장한다.

- [0147] 디스크 컨트롤러(649)는 메모리 장치(650)에 저장된 병렬 전기신호들을 리드하여 라이트 어드레스에 의하여 지정된 자기적 기록 매체(660)에 라이트한다.

- [0148] 리드 동작 시, 디스크 컨트롤러(649)는 리드 어드레스에 의하여 지정된 자기적 기록 매체(660)로부터 데이터를 리드하고 리드된 데이터를 베퍼(647)를 통하여 메모리 장치(650)에 저장한다.

- [0149] 제2SATA 인터페이스(645)는 베퍼(647)를 통하여 메모리 장치(650)로부터 데이터를 리드하고, 리드된 병렬 데이터를 광을 이용하여 시리얼라이즈하고, 시리얼라이즈된 광 데이터를 데이터 버스를 통하여 제1SATA(619)의 제1디시리얼라이저 (24)로 전송한다.

- [0150] 제2디시리얼라이저(24)는 시리얼라이즈된 광 데이터를 전기적 클락 신호를 이용하여 디시리얼라이즈하고, 디시리얼라이즈된 병렬 광신호들을 병렬 전기신호들로 변환한다. DMA 컨트롤러(617)는 병렬 전기신호들을 메모리(615)에 저장한다.

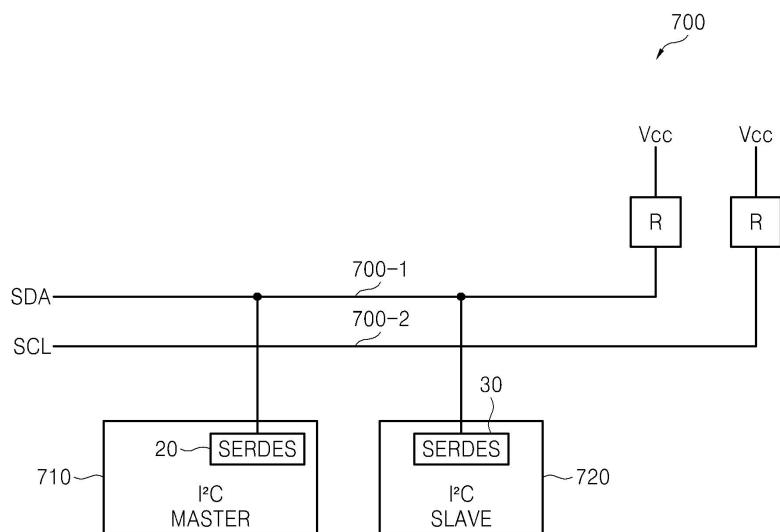

- [0151] 도 21은 도 1에 도시된 광 송수신기를 포함하는 데이터 처리 시스템의 또 다른 실시 예를 나타낸다. I2C(Integrated Circuit) 통신 프로토콜을 사용하여 시리얼 데이터를 주거나 받을 수 있는 데이터 처리 시스템(700)은 I2C 마스터(710)와 I2C 슬레이브(720)를 포함한다. I2C 마스터(710)와 I2C 슬레이브(720)는 I2C 버스(700-1과 700-2)를 통하여 시리얼라이즈된 광신호를 주거나 받을 수 있다.

- [0152] I2C 마스터(710) 내에 구현된 제1시리얼 인터페이스(또는 SERDES; 20)의 제1광 시리얼라이저에 의하여 시리얼라이즈된 광신호는 SDA 라인(700-1)을 통하여 I2C 슬레이브(720) 내에 구현된 제2시리얼 인터페이스(또는 SERDES; 30)의 제2디시리얼라이저에 의하여 병렬 전기신호들로 디시리얼라이즈된다. I2C 마스터(710)는 제1시리얼 인터페이스(또는 SERDES; 20)의 동작을 제어할 수 있는 마이크로컨트롤러(미 도시)를 포함할 수 있고 I2C 슬레이브(720)는 제2시리얼 인터페이스(또는 SERDES; 30)의 동작을 제어할 수 있는 마이크로컨트롤러(미 도시)를 포함할 수 있다.

- [0153] 제2시리얼 인터페이스(30)의 제2광 시리얼라이저에 의하여 시리얼라이즈된 광신호는 SDA 라인(700-1)을 통하여 제1시리얼 인터페이스(20)의 제1광 디시리얼라이저에 의하여 병렬 전기신호들로 디시리얼라이즈된다.

- [0154] 시리얼라이즈된 광신호를 전송하기 위하여 사용되는 시리얼 클락 신호는 SCL 라인(700-2)을 통하여 I2C 마스터(710)와 I2C 슬레이브(720) 중에서 어느 하나로부터 I2C 마스터(710)와 I2C 슬레이브(720) 중에서 다른 하나로 전송된다.

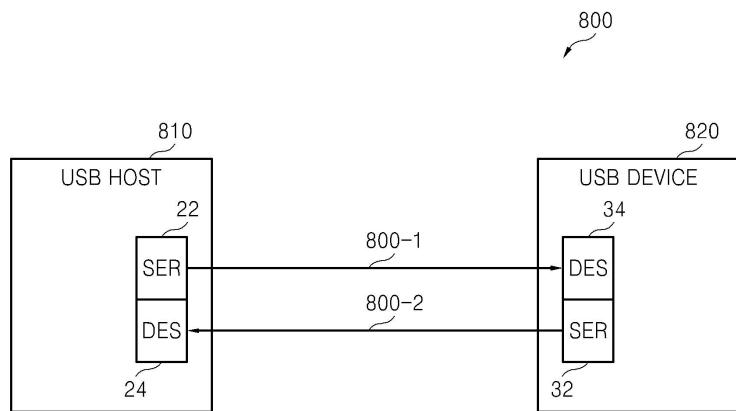

- [0155] 도 22는 도 1에 도시된 광 송수신기를 포함하는 데이터 전송 시스템의 또 다른 실시 예를 나타낸다. USB(Universal Serial Bus) 통신 프로토콜을 사용하여 시리얼 데이터를 주거나 받을 수 있는 데이터 처리 시스템(800)은 USB 호스트(810)와 USB 장치(820)를 포함한다.

- [0156] USB 호스트(810)의 시리얼라이저(22)에 의하여 시리얼라이즈된 광신호는 데이터 버스(800-1)를 통하여 USB 장치(820)의 디시리얼라이저(34)로 전송되고, USB 장치(820)의 디시리얼라이저(34)는 수신된 시리얼라이즈된 광신호를 전기적인 클락 신호를 이용하여 병렬 전기신호들로 디시리얼라이즈한다. USB 호스트(810)는 시리얼라이저(22)와 디시리얼라이저(34)의 동작을 제어할 수 있는 마이크로컨트롤러(미도시)를 포함할 수 있다.

- [0157] USB 장치(820)의 시리얼라이저(32)에 의하여 시리얼라이즈된 광신호는 데이터 버스(800-2)를 통하여 USB 호스트(810)의 디시리얼라이저(24)로 전송되고, USB 호스트(820)의 디시리얼라이저(24)는 수신된 시리얼라이즈된 광신호를 전기적인 클락 신호를 이용하여 병렬 전기신호들로 디시리얼라이즈한다. USB 장치(820)는 시리얼라이저(32)와 디시리얼라이저(34)의 동작을 제어할 수 있는 마이크로컨트롤러(미도시)를 포함할 수 있다.

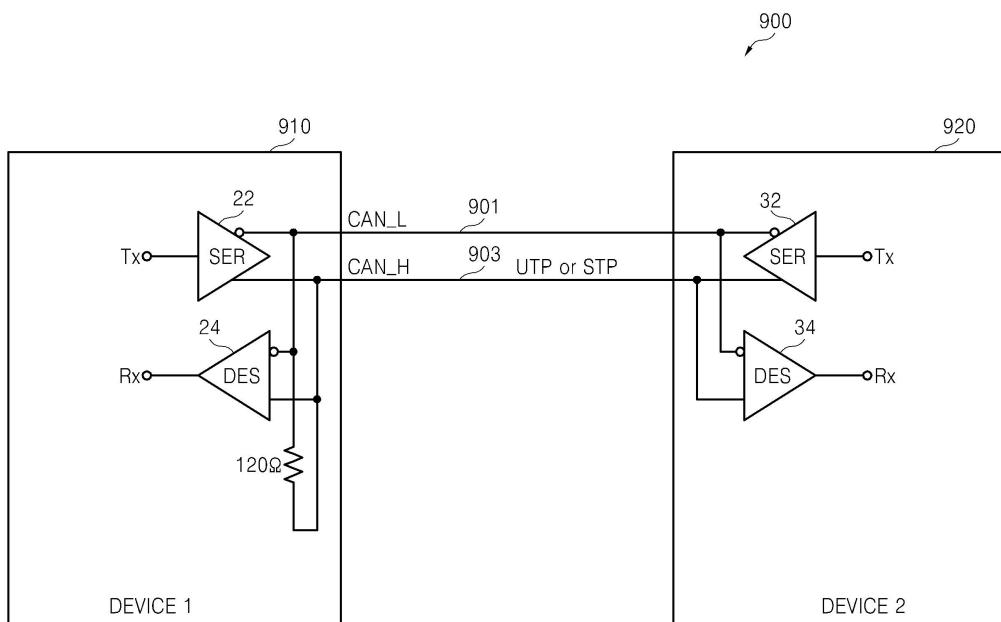

- [0158] 도 23은 도 1에 도시된 광 송수신기를 포함하는 데이터 전송 시스템의 또 다른 실시 예를 나타낸다. CAN(Controller Area Network) 또는 CAN-bus 통신 프로토콜을 사용하여 시리얼 데이터를 주거나 받을 수 있는 데이터 처리 시스템(900)은 제1장치(910)와 제2장치(920)를 포함한다.

- [0159] 제1장치(910)는 CAN 또는 CAN-bus 통신 프로토콜을 지원할 수 있는 제1시리얼 인터페이스를 포함한다. 상기 제1시리얼 인터페이스는 제1광 시리얼라이저(22)와 제1광 디시리얼라이저(24)를 포함한다. 제1장치(910)는 제1광 시리얼라이저(22)와 제1광 디시리얼라이저(24)의 동작을 제어할 수 있는 마이크로컨트롤러(미 도시)를 포함할 수 있다.

- [0160] 제2장치(920)는 CAN 또는 CAN-bus 통신 프로토콜을 지원할 수 있는 제2시리얼 인터페이스를 포함한다. 상기 제2시리얼 인터페이스는 제2광 시리얼라이저(32)와 제2광 디시리얼라이저(34)를 포함한다. 제2장치(920)는 제2광 시리얼라이저(32)와 제2광 디시리얼라이저(34)의 동작을 제어할 수 있는 마이크로컨트롤러(미 도시)를 포함할 수 있다.

- [0161] 제1장치(910)와 제2장치(920)는 STP(shielded twisted pair; 901과 903) 또는 UTP(unshielded twisted pair; 901과 903)를 통하여 시리얼라이즈된 광신호를 주거나 받을 수 있다. 여기서, CAN\_H와 CAN\_L는 차동 신호들이다.

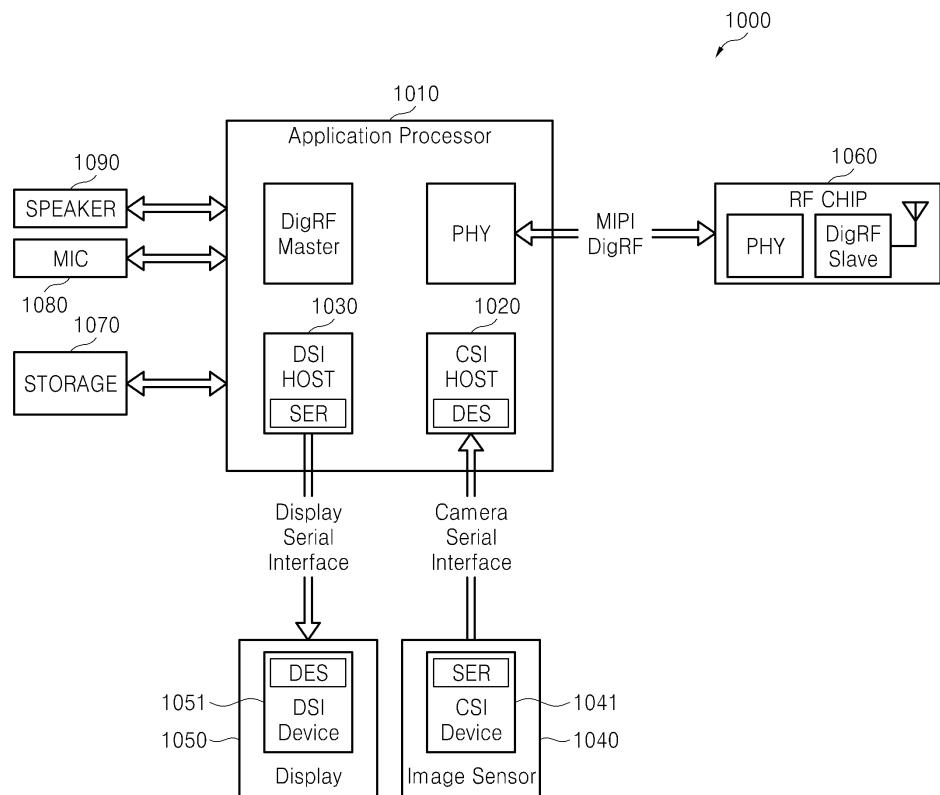

- [0162] 도 24는 도 1에 도시된 광 송수신기들을 포함하는 데이터 처리 시스템의 또 다른 실시 예를 나타낸다. 데이터 처리 시스템(1000)은 MIPI®(Mobile Industry Processor Interface)를 사용 또는 지원할 수 있는 데이터 처리

장치, 예컨대 이동 전화기(mobile phone), PDA(personal digital assistant), PMP(portable media player), 또는 스마트 폰(smart phone)으로 구현될 수 있다.

[0163] 데이터 처리 시스템(1000)은 어플리케이션 프로세서(1010), 이미지 센서 (1040), 및 디스플레이(1050)를 포함한다.

[0164] 어플리케이션 프로세서(1010)에 구현된 CSI 호스트(1020)는 카메라 시리얼 인터페이스(camera serial interface(CSI))를 통하여 이미지 센서(1040)의 CSI 장치(1041)와 시리얼 통신할 수 있다. 예컨대, CSI 호스트(1020)에는 도 1, 도 6, 도 10, 도 13, 또는 도 14에 도시된 광 디시리얼라이저가 구현될 수 있고, CSI 장치(1041)에는 도 1과 도 2에 도시된 광 시리얼라이저가 구현될 수 있다.

[0165] 어플리케이션 프로세서(1010)에 구현된 DSI 호스트(1030)는 디스플레이 시리얼 인터페이스(display serial interface(DSI))를 통하여 디스플레이(1050)의 DSI 장치 (1051)와 시리얼 통신할 수 있다. 예컨대, DSI 호스트(1030)에는 도 1과 도 2에 도시된 광 시리얼라이저가 구현될 수 있고, DSI 장치(1050)에는 도 1, 도 6, 도 10, 도 13, 또는 도 14에 도시된 광 디시리얼라이저가 구현될 수 있다.

[0166] 데이터 처리 시스템(1000)은 어플리케이션 프로세서(1010)와 통신할 수 있는 RF 칩(1060)을 더 포함할 수 있다. 데이터 처리 시스템(1000)의 PHY와 RF 칩(1060)의 PHY는 MIPI DigRF에 따라 데이터를 주고받을 수 있다.

[0167] 데이터 처리 시스템(1000)은 스토리지(1070), 마이크(1080), 및 스피커 (1090)를 더 포함할 수 있다.

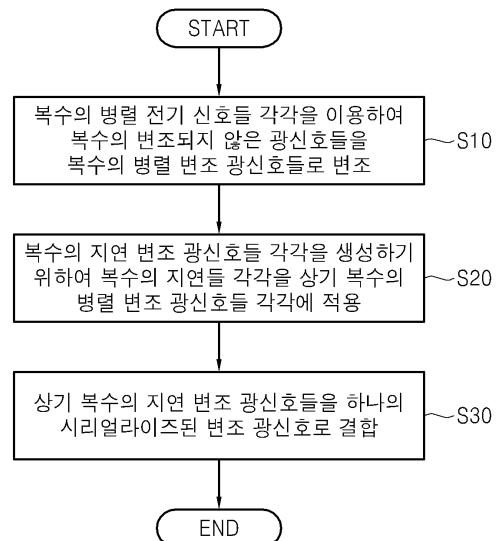

[0168] 도 25는 도 2에 도시된 시리얼라이저의 시리얼라이징 방법을 설명하기 위한 플로우차트이다. 시리얼라이저의 시리얼라이징 방법은 도 1, 도 2, 및 도 15~도 25를 참조하여 상세히 설명된다.

[0169] 각 광 시리얼라이저(22와 32)는 변조되지 않은 적어도 하나의 광신호(CWA와 CWB)를 수신한다.

[0170] 각 광 시리얼라이저(22와 32)의 광 변조 유닛(42)은 복수의 병렬 전기 신호들(INA와 INB) 각각을 이용하여 복수의 변조되지 않은 광신호들을 복수의 병렬 변조 광신호들로 변조한다(S10).

[0171] 각 광 시리얼라이저(22와 32)의 지연 유닛(44)은 변조된 광신호들 각각을 서로 다른 광학적 지연량만큼 지연시켜 지연된 광신호들을 생성한다(S20). 즉, 지연 유닛(44)은 복수의 지연 변조 광신호들 각각을 생성하기 위하여 복수의 지연들 각각을 상기 복수의 병렬 변조 광신호들 각각에 적용한다(S20).

[0172] 각 광 시리얼라이저(22와 32)의 광 결합기(46)는 지연 유닛(44)에 의하여 생성된 복수의 지연 변조 광신호들을 하나의 시리얼라이즈된 변조 광신호로 결합하고 시리얼라이즈된 변조 광신호를 출력한다(S30).

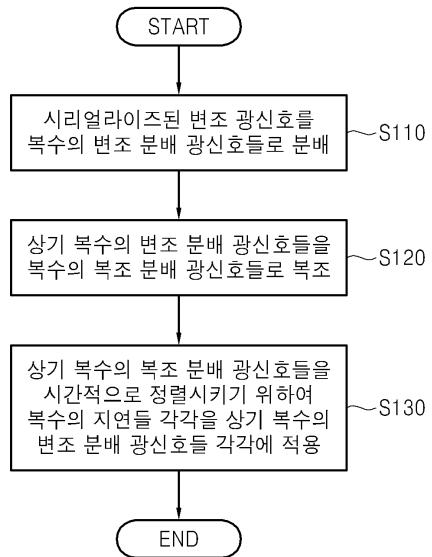

[0173] 도 26은 도 6에 도시된 디시리얼라이저의 디시리얼라이징 방법을 설명하기 위한 플로우차트이다. 디시리얼라이저의 디시리얼라이징 방법은 도 1, 도 6, 도 13, 도 15~도 24, 및 도 26을 참조하여 상세히 설명된다.

[0174] 각 디시리얼라이저(24와 34)의 광 분배기(50)는 수신된 시리얼라이즈된 변조 광신호를 복수의 변조 분배 광신호들로 분배한다(S110).

[0175] 각 디시리얼라이저(24와 34)의 복조 유닛(52)은 상기 복수의 변조 분배 광신호들을 복수의 복조 분배 광신호들로 복조한다(S120). 각 디시리얼라이저(24와 34)의 지연 유닛(54)은 상기 복수의 복조 분배 광신호들을 시간적으로 정렬시키기 위하여 복수의 지연들 각각을 상기 복수의 변조 분배 광신호들 각각에 적용한다 (S130).

[0176] 도 27은 도 10에 도시된 디시리얼라이저의 디시리얼라이징 방법을 설명하기 위한 플로우차트이다. 디시리얼라이저의 디시리얼라이징 방법은 도 1, 도 10, 도 14, 도 15~도 24, 및 도 27을 참조하여 상세히 설명된다.

[0177] 디시리얼라이저(34B)의 광 분배기(60)는 시리얼라이즈된 변조 광신호를 복수의 변조 분배 광신호들로 분배한다 (S210). 복조 유닛(62)은 광 분배기(60)로부터 출력된 상기 복수의 변조 분배 광신호들을 복수의 복조 분배 광신호들로 복조한다 (S220). 복조 유닛(62)은 상기 복수의 복조 광신호들을 시간적으로 정렬시키기 위하여 상기 복수의 변조 분배 광신호들을 복조하기 위하여 사용된 복수의 제어 신호들, 예컨대 복수의 지연 클락 신호들(CLK, CLK<sub>1</sub>, CLK<sub>2</sub>, ..., CLK<sub>N-1</sub>) 각각에 복수의 지연들 각각을 적용한다(S230).

[0178] 본 발명은 도면에 도시된 일 실시 예를 참고로 설명되었으나 이는 예시적인 것에 불과하며, 본 기술 분야의 통상의 지식을 가진 자라면 이로부터 다양한 변형 및 균등한 타 실시 예가 가능하다는 점을 이해할 것이다. 따라서, 본 발명의 진정한 기술적 보호 범위는 첨부된 등록청구범위의 기술적 사상에 의해 정해져야 할 것이다.

## 부호의 설명

[0179] 20: 제1광 송수신기

30: 제2광 송수신기

40, 50: 광 분배기

42: 광 변조 유닛

44: 제1지연 유닛

46: 광 결합기

52: 제2지연 유닛

54: 복조 유닛

**도면****도면1****도면2**

도면3

도면4

도면5

도면6

도면7

도면8

도면9

도면10

도면11

도면12

도면13

도면14

도면15

도면16

도면17

도면18

도면19

## 도면20

## 도면21

도면22

도면23

## 도면24

## 도면25

## 도면26

## 도면27