(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2016-0018781

(43) 공개일자 2016년02월17일

- (51) 국제특허분류(Int. Cl.)

*G06F 13/42* (2006.01) *G06F 13/364* (2006.01)

- (52) CPC특허분류(Coo. Cl.)

*G06F 13/4282* (2013.01)

*G06F 13/364* (2013.01)

- (21) 출원번호 10-2016-7000592

- (22) 출원일자(국제) 2014년06월12일

심사청구일자 없음

- (85) 번역문제출일자 2016년01월08일

- (86) 국제출원번호 PCT/US2014/042182

- (87) 국제공개번호 WO 2014/201289

국제공개일자 2014년12월18일

- (30) 우선권주장

61/834,151 2013년06월12일 미국(US)

(뒷면에 계속)

- (71) 출원인

퀄컴 인코포레이티드

미국 92121-1714 캘리포니아주 샌디에고 모어하우스 드라이브 5775

- (72) 발명자

센고쿠 쇼이치로

미국 92121-1714 캘리포니아주 샌디에고 모어하우스 드라이브 5775

와일리 조지 엘런

미국 92121-1714 캘리포니아주 샌디에고 모어하우스 드라이브 5775

청 조셉

미국 92121-1714 캘리포니아주 샌디에고 모어하우스 드라이브 5775

- (74) 대리인

특허법인코리아나

전체 청구항 수 : 총 30 항

(54) 발명의 명칭 카메라 제어 인터페이스 확장 버스

### (57) 요 약

인터-인티그레이티드 회로 (I2C) 및/또는 카메라 제어 인터페이스 (CCI) 동작들을 위해 이용되는 직렬 버스의 향상된 성능을 제공하는 시스템, 방법들, 및 장치들이 제공된다. CCI 확장 (CCIE) 디바이스들이 기술된다. CCIE 디바이스들은 버스 마스터로서 또는 슬레이브로서 구성될 수도 있다. 하나의 방법에서, CCIE 송신기는 비트들의 셋트로부터 천이 넘버를 생성하고, 그 천이 넘버를 심볼들의 시퀀스로 변환하며, 2-선 직렬 버스의 시그널링 상태에서 심볼들의 시퀀스를 송신한다. 타이밍 정보는 심볼들의 시퀀스에서 심볼들의 연속적인 쌍들의 심볼들 사이에서의 천이들에서 인코딩될 수도 있다. 예를 들어, 각각의 천이는 2-선 직렬 버스의 적어도 하나의 선의 시그널링 상태에서의 변화를 야기할 수도 있다. CCIE 수신기는 심볼들의 시퀀스를 수신 및 디코딩하기 위해 천이들로부터 수신 클럭을 도출할 수도 있다.

### 대 표 도

(52) CPC특허분류(Coo. Cl.)

*G06F 13/4291* (2013.01)

*G06F 13/4295* (2013.01)

(30) 우선권주장

61/836,777 2013년06월19일 미국(US)

61/886,002 2013년10월02일 미국(US)

14/302,359 2014년06월11일 미국(US)

---

## 특허청구의 범위

### 청구항 1

송신 디바이스 상에서 동작가능한 데이터 통신 방법으로서,

비트들의 셋트로부터 천이 넘버를 생성하는 단계;

상기 천이 넘버를 심볼들의 12-심볼 시퀀스로 변환하는 단계로서, 심볼들의 상기 시퀀스에서 심볼들 사이의 천 이들에서 타이밍 정보가 인코딩되는, 상기 천이 넘버를 심볼들의 12-심볼 시퀀스로 변환하는 단계; 및

2-선 직렬 버스가 제 1 동작 모드에서 동작될 때 상기 2-선 직렬 버스 상에서 상기 심볼들의 시퀀스를 송신하는 단계로서, 연속적인 심볼들 사이의 각각의 천이는 상기 2-선 직렬 버스의 시그널링 상태에서의 변화를 야기하는, 상기 2-선 직렬 버스 상에서 상기 심볼들의 시퀀스를 송신하는 단계를 포함하고,

상기 2-선 직렬 버스가 제 2 동작 모드에서 동작될 때, 상기 2-선 직렬 버스 상에서 통신하도록 구성된 디바이스에 의해 상기 심볼들의 시퀀스는 무시되는, 송신 디바이스 상에서 동작가능한 데이터 통신 방법.

### 청구항 2

제 1 항에 있어서,

상기 천이 넘버는 12 디지트 3진수를 포함하는, 송신 디바이스 상에서 동작가능한 데이터 통신 방법.

### 청구항 3

제 1 항에 있어서,

상기 천이 넘버를 심볼들의 시퀀스로 변환하는 단계는,

상기 비트들의 셋트를 12-디지트 3진 천이 넘버로 변환하는 단계; 및

상기 3진 천이 넘버를 트랜스코더에 제공하는 단계로서, 상기 3진 천이 넘버의 최상위 디지트가 제일 먼저 상기 트랜스코더에 제공되고, 상기 3진 천이 넘버의 최하위 디지트가 마지막으로 상기 트랜스코더에 제공되며, 상기 최상위 디지트와 상기 최하위 디지트 사이의 중간 디지트들은 상위 디지트에서 하위 디지트로의 내림차순으로 상기 트랜스코더에 제공되는, 상기 3진 천이 넘버를 트랜스코더에 제공하는 단계를 포함하는, 송신 디바이스 상에서 동작가능한 데이터 통신 방법.

### 청구항 4

제 1 항에 있어서,

상기 천이 넘버를 심볼들의 시퀀스로 변환하는 단계는,

상기 비트들의 셋트를 12-디지트 3진 천이 넘버로 변환하는 단계; 및

상기 3진 천이 넘버를 트랜스코더에 제공하는 단계로서, 상기 3진 천이 넘버의 최상위 디지트가 마지막으로 상기 트랜스코더에 제공되는, 상기 3진 천이 넘버를 트랜스코더에 제공하는 단계를 포함하는, 송신 디바이스 상에서 동작가능한 데이터 통신 방법.

### 청구항 5

제 1 항에 있어서,

4 개의 시그널링 상태들이 상기 2-선 직렬 버스에 대해 정의되고, 상기 천이 넘버는 12-디지트 3진수로서 트랜스코더에 제공되며, 상기 3진수의 각 디지트는 3 개의 이용가능한 심볼들 중 하나로부터 상기 2-선 직렬 버스 상에서 송신될 다음 심볼을 선택하고, 상기 3 개의 이용가능한 심볼들의 각각은 상기 2-선 직렬 버스 상에서 송신되고 있는 현재의 심볼과 상이한, 송신 디바이스 상에서 동작가능한 데이터 통신 방법.

### 청구항 6

제 1 항에 있어서,

상기 심볼들의 시퀀스에서 인코딩된 타이밍 정보는 수신기가 상기 심볼들의 시퀀스로부터 수신 클럭을 생성하는 것을 가능하게 하는, 송신 디바이스 상에서 동작가능한 데이터 통신 방법.

### 청구항 7

제 1 항에 있어서,

상기 2-선 직렬 버스는, 상기 2-선 직렬 버스가 상기 제 1 동작 모드에서 동작될 때 CCIe (camera control interface extension) 프로토콜들을 이용하여 통신들을 지원하는 다목적 버스이고, 상기 2-선 직렬 버스는 상기 제 2 동작 모드에서 I2C (Inter-Integrated Circuit) 프로토콜들을 이용하여 통신들을 지원하는, 송신 디바이스 상에서 동작가능한 데이터 통신 방법.

### 청구항 8

제 7 항에 있어서,

상기 2-선 직렬 버스 상에서 상기 심볼들의 시퀀스를 송신하는 단계는, 상기 제 1 동작 모드에서 상기 2-선 직렬 버스 상에서 송신되는 심볼들의 시퀀스들 사이에 I2C 시작 조건을 제공하는 단계를 포함하고,

상기 시작 조건의 타이밍은 상기 I2C 프로토콜들을 이용한 통신들을 위해 구성된 디바이스에서의 수신 로직의 리셋을 야기하는, 송신 디바이스 상에서 동작가능한 데이터 통신 방법.

### 청구항 9

제 7 항에 있어서,

상기 2-선 직렬 버스 상에서 상기 심볼들의 시퀀스를 송신하는 단계는,

상기 2-선 직렬 버스 상에서 제 1 I2C 시작 조건을 송신하는 단계;

상기 제 1 I2C 시작 조건이 송신된 후에 상기 2-선 직렬 버스 상에서 상기 심볼들의 시퀀스를 송신하는 단계; 및

상기 2-선 직렬 버스 상에서 제 2 I2C 시작 조건을 송신하는 단계를 포함하고,

상기 2-선 직렬 버스를 모니터링하는 I2C 수신기는, 상기 제 1 시작 조건 후에 그리고 상기 제 2 I2C 시작 조건 전에 상기 2-선 직렬 버스의 직렬 클럭 라인 (SCL) 상에서 최대 6 클럭 사이클들을 감지하는, 송신 디바이스 상에서 동작가능한 데이터 통신 방법.

### 청구항 10

제 1 항에 있어서,

제어 시퀀스가 상기 2-선 직렬 버스 상에서 송신된 후에 상기 제 1 동작 모드로부터 상기 제 2 동작 모드로 변경하는 단계를 더 포함하는, 송신 디바이스 상에서 동작가능한 데이터 통신 방법.

### 청구항 11

장치로서,

상기 장치를 복수의 다른 디바이스들과 공유되도록 동작가능한 2-선 직렬 버스에 커플링하도록 적응되는 버스 인터페이스; 및

상기 버스 인터페이스에 커플링된 프로세싱 회로를 포함하고,

상기 프로세싱 회로는,

비트들의 셋트로부터 천이 넘버를 생성하는 것;

상기 천이 넘버를 심볼들의 12-심볼 시퀀스로 변환하는 것으로서, 심볼들의 상기 시퀀스에서 심볼들 사이의 천이들에서 타이밍 정보가 인코딩되는, 상기 천이 넘버를 심볼들의 12-심볼 시퀀스로 변환하는 것; 및

2-선 직렬 버스가 제 1 동작 모드에서 동작될 때 상기 2-선 직렬 버스 상에서 상기 심볼들의 시퀀스를 송신하는 것으로서, 연속적인 심볼들 사이의 각각의 천이는 상기 2-선 직렬 버스의 시그널링 상태에서의 변화를 야기하는, 상기 2-선 직렬 버스 상에서 상기 심볼들의 시퀀스를 송신하는 것을 행하도록 구성되며,

상기 2-선 직렬 버스가 제 2 동작 모드에서 동작될 때, 상기 2-선 직렬 버스 상에서 통신하도록 구성된 디바이스에 의해 상기 심볼들의 시퀀스는 무시되는, 장치.

### 청구항 12

제 11 항에 있어서,

상기 천이 넘버는 12 디지트 3진수를 포함하는, 장치.

### 청구항 13

제 12 항에 있어서,

상기 프로세싱 회로는,

상기 비트들의 셋트를 12-디지트 3진 천이 넘버로 변환하는 것; 및

상기 3진 천이 넘버를 트랜스코더에 제공하는 것으로서, 상기 3진 천이 넘버의 최상위 디지트가 제일 먼저 상기 트랜스코더에 제공되고, 상기 3진 천이 넘버의 최하위 디지트가 마지막으로 상기 트랜스코더에 제공되며, 상기 최상위 디지트와 상기 최하위 디지트 사이의 중간 디지트들은 상위 디지트에서 하위 디지트로의 내림차순으로 상기 트랜스코더에 제공되는, 상기 3진 천이 넘버를 트랜스코더에 제공하는 것

에 의해, 상기 천이 넘버를 심볼들의 시퀀스로 변환하도록 구성되는, 장치.

### 청구항 14

제 12 항에 있어서,

상기 프로세싱 회로는,

상기 비트들의 셋트를 12-디지트 3진 천이 넘버로 변환하는 것; 및

상기 3진 천이 넘버를 트랜스코더에 제공하는 것으로서, 상기 3진 천이 넘버의 최상위 디지트가 마지막으로 상기 트랜스코더에 제공되는, 상기 3진 천이 넘버를 트랜스코더에 제공하는 것

에 의해, 상기 천이 넘버를 심볼들의 시퀀스로 변환하도록 구성되는, 장치.

### 청구항 15

제 12 항에 있어서,

4 개의 시그널링 상태들이 상기 2-선 직렬 버스에 대해 정의되고, 상기 천이 넘버는 12-디지트 3진수로서 트랜스코더에 제공되며, 상기 3진수의 각 디지트는 3 개의 이용가능한 심볼들 중 하나로부터 상기 2-선 직렬 버스 상에서 송신될 다음 심볼을 선택하고, 상기 3 개의 이용가능한 심볼들의 각각은 상기 2-선 직렬 버스 상에서 송신되고 있는 현재의 심볼과 상이한, 장치.

### 청구항 16

제 11 항에 있어서,

상기 심볼들의 시퀀스에서 인코딩된 타이밍 정보는 수신기가 상기 심볼들의 시퀀스로부터 수신 클럭을 생성하는 것을 가능하게 하는, 장치.

### 청구항 17

제 11 항에 있어서,

상기 2-선 직렬 버스는, 상기 2-선 직렬 버스가 상기 제 1 동작 모드에서 동작될 때 CCIe (camera control interface extension) 프로토콜들을 이용하여 통신들을 지원하는 다목적 버스이고, 상기 2-선 직렬 버스는 상기

제 2 동작 모드에서 I2C (Inter-Integrated Circuit) 프로토콜들을 이용하여 통신들을 지원하는, 장치.

### 청구항 18

제 17 항에 있어서,

상기 프로세싱 회로는, 상기 제 1 동작 모드에서 상기 2-선 직렬 버스 상에서 송신되는 심볼들의 시퀀스들 사이에 I2C 시작 조건을 제공하는 것에 의해, 상기 2-선 직렬 버스 상에서 상기 심볼들의 시퀀스를 송신하도록 구성되고,

상기 시작 조건의 타이밍은 상기 I2C 프로토콜들을 이용한 통신들을 위해 구성된 디바이스에서의 수신 로직의 리셋을 야기하는, 장치.

### 청구항 19

제 17 항에 있어서,

상기 프로세싱 회로는,

상기 2-선 직렬 버스 상에서 제 1 I2C 시작 조건을 송신하는 것;

상기 제 1 I2C 시작 조건이 송신된 후에 상기 2-선 직렬 버스 상에서 심볼들의 시퀀스를 송신하는 것; 및

상기 2-선 직렬 버스 상에서 제 2 I2C 시작 조건을 송신하는 것

에 의해, 상기 2-선 직렬 버스 상에서 상기 심볼들의 시퀀스를 송신하도록 구성되고,

상기 2-선 직렬 버스를 모니터링하는 I2C 수신기는, 상기 제 1 시작 조건 후에 그리고 상기 제 2 I2C 시작 조건 전에 상기 2-선 직렬 버스의 직렬 클럭 라인 (SCL) 상에서 최대 6 클럭 사이클들을 감지하는, 장치.

### 청구항 20

제 11 항에 있어서,

상기 프로세싱 회로는, 제어 시퀀스가 상기 2-선 직렬 버스 상에서 송신된 후에 상기 제 1 동작 모드로부터 상기 제 2 동작 모드로 변경하도록 더 구성되는, 장치.

### 청구항 21

데이터 통신 수신 디바이스 상에서 동작가능한 방법으로서,

2-선 직렬 버스가 제 1 동작 모드에서 동작될 때, 상기 2-선 직렬 버스의 시그널링 상태에서의 천이들로부터 수신 클럭을 도출하는 단계;

상기 제 1 동작 모드에 따라 상기 2-선 직렬 버스 상에서 송신되는 심볼들의 12-심볼 시퀀스를 수신하기 위해 상기 수신 클럭을 이용하는 단계로서, 상기 2-선 직렬 버스의 시그널링 상태에서의 천이들은 상기 심볼들의 시퀀스에서의 심볼들 사이의 천이들에 대응하는, 상기 심볼들의 12-심볼 시퀀스를 수신하기 위해 상기 수신 클럭을 이용하는 단계;

상기 심볼들의 시퀀스로부터 천이 넘버를 생성하는 단계로서, 상기 천이 넘버는 다중 디지트들을 가지고, 각 디지트는 상기 심볼들의 시퀀스에서의 연속적인 심볼들의 쌍 사이의 천이를 나타내는, 상기 심볼들의 시퀀스로부터 천이 넘버를 생성하는 단계; 및

상기 천이 넘버로부터 데이터를 디코딩하는 단계를 포함하고,

상기 2-선 직렬 버스가 제 2 동작 모드에서 동작될 때, 상기 2-선 직렬 버스 상에서 통신하도록 구성된 디바이스에 의해 상기 심볼들의 시퀀스는 무시되는, 데이터 통신 수신 디바이스 상에서 동작가능한 방법.

### 청구항 22

제 21 항에 있어서,

상기 천이 넘버는 12 디지트 3진수를 포함하는, 데이터 통신 수신 디바이스 상에서 동작가능한 방법.

### 청구항 23

제 22 항에 있어서,

4 개의 시그널링 상태들이 상기 2-선 직렬 버스에 대해 정의되고, 상기 3진수의 각 디지트는 상기 2-선 직렬 버스 상에서의 연속적인 시그널링 상태들의 쌍 사이의 관계를 나타내는, 데이터 통신 수신 디바이스 상에서 동작 가능한 방법.

### 청구항 24

제 22 항에 있어서,

상기 심볼들의 시퀀스에서의 각 심볼은 상기 2-선 직렬 버스의 상기 시그널링 상태에 의해 정의된 4 개의 심볼들 중 하나이고, 상기 3진수의 각 디지트는 상기 심볼들의 시퀀스에서의 연속적인 심볼들의 쌍 사이의 관계를 정의하는, 데이터 통신 수신 디바이스 상에서 동작 가능한 방법.

### 청구항 25

제 21 항에 있어서,

상기 2-선 직렬 버스는, 상기 2-선 직렬 버스가 상기 제 1 동작 모드에서 동작될 때 CCIe (camera control interface extension) 통신들을 지원하는 다목적 버스이고, 상기 2-선 직렬 버스는 상기 제 2 동작 모드에서 I2C (Inter-Integrated Circuit) 통신들을 지원하며,

상기 2-선 직렬 버스로부터 상기 심볼들의 시퀀스를 수신하는 것은,

상기 2-선 직렬 버스 상에서의 I2C 시작 조건을 결정하는 것; 및

상기 수신 클럭에 의해 정의된 타이밍에 따라 상기 2-선 직렬 버스로부터 상기 심볼들의 시퀀스를 수신하는 것을 포함하는, 데이터 통신 수신 디바이스 상에서 동작 가능한 방법.

### 청구항 26

장치로서,

상기 장치를 복수의 다른 디바이스들과 공유되도록 동작 가능한 2-선 직렬 버스에 커플링하도록 적응되는 버스 인터페이스;

2-선 직렬 버스의 시그널링 상태에서의 천이들로부터 수신 클럭을 도출하도록 구성된 클럭 복원 회로; 및

상기 버스 인터페이스에 커플링된 프로세싱 회로를 포함하고,

상기 프로세싱 회로는,

제 1 동작 모드에 따라 상기 2-선 직렬 버스 상에서 송신되는 심볼들의 12-심볼 시퀀스를 수신하기 위해 상기 수신 클럭을 이용하는 것으로서, 상기 2-선 직렬 버스의 시그널링 상태에서의 천이들은 상기 심볼들의 시퀀스에서의 심볼들 사이의 천이들에 대응하는, 상기 심볼들의 12-심볼 시퀀스를 수신하기 위해 상기 수신 클럭을 이용하는 것;

상기 심볼들의 시퀀스로부터 천이 넘버를 생성하는 것으로서, 상기 천이 넘버는 다중 디지트들을 가지고, 각 디지트는 상기 심볼들의 시퀀스에서의 연속적인 심볼들의 쌍 사이의 천이를 나타내는, 상기 심볼들의 시퀀스로부터 천이 넘버를 생성하는 것; 및

상기 천이 넘버로부터 데이터를 디코딩하는 것을 행하도록 구성되며,

상기 2-선 직렬 버스가 제 2 동작 모드에서 동작될 때, 상기 2-선 직렬 버스 상에서 통신하도록 구성된 디바이스에 의해 상기 심볼들의 시퀀스는 무시되는, 장치.

### 청구항 27

제 26 항에 있어서,

상기 천이 넘버는 12 디지트 3진수를 포함하는, 장치.

**청구항 28**

제 27 항에 있어서,

4 개의 시그널링 상태들이 상기 2-선 직렬 버스에 대해 정의되고, 상기 3진수의 각 디지트는 상기 2-선 직렬 버스 상에서의 연속적인 시그널링 상태들의 쌍 사이의 관계를 나타내는, 장치.

**청구항 29**

제 27 항에 있어서,

상기 심볼들의 시퀀스에서의 각 심볼은 상기 2-선 직렬 버스의 상기 시그널링 상태에 의해 정의된 4 개의 심볼들 중 하나이고, 상기 3진수의 각 디지트는 상기 심볼들의 시퀀스에서의 연속적인 심볼들의 쌍 사이의 관계를 정의하는, 장치.

**청구항 30**

제 26 항에 있어서,

상기 2-선 직렬 버스는, 상기 2-선 직렬 버스가 상기 제 1 동작 모드에서 동작될 때 CCIe (camera control interface extension) 통신들을 지원하는 다목적 버스이고, 상기 2-선 직렬 버스는 상기 제 2 동작 모드에서 I2C (Inter-Integrated Circuit) 통신들을 지원하며, 상기 2-선 직렬 버스로부터 수신된 상기 심볼들의 시퀀스는, 12 개의 심볼들을 포함하고, I2C 시작이 선행하는, 장치.

**명세서****기술 분야**

[0001] 본 특허 출원은, 2013년 6월 12일 출원된 "Increasing Data Transfer Rate Over I2C Bus"라는 제목의 미국 가출원 제 61/834,151 호, 2013년 6월 19일 출원된 "Camera Control Interface Extension Bus"라는 제목의 미국 가출원 제 61/836,777 호, 2013년 10월 2일 출원된 "Simplifying Symbol Transcoding And Transmission Over CCIE Bus"라는 제목의 미국 가출원 제 61/886,002 호, 및 2014년 6월 11일 출원된 "Camera Control Interface Extension Bus"라는 제목의 미국 정규 출원 제 14/302,359 호에 대해 우선권을 주장하고, 이 출원들은 모두 본 원의 양수인에게 양도되었고, 이에 의해 참조에 의해 본원에 명시적으로 통합된다.

[0002] 본 개시물은 일반적으로, 호스트 프로세서와 카메라와 같은 주변 디바이스 사이의 인터페이스에 관한 것이고, 보다 상세하게는, 클럭 (clock) 신호가 다중-선 공유된 버스 상에서 전송되는 심볼들에 임베딩되는 다중모드 동작들에 관한 것이다.

**배경기술**

[0003] I2C 버스 또는  $I^2C$  버스로서 또한 지칭될 수도 있는 인터-인티그레이티드 회로 직렬 버스 (Inter-Integrated Circuit serial bus)는 프로세서에 저속 주변장치들을 연결하는데 사용하도록 의도되었던 직렬 싱글-엔드형 (single-ended) 컴퓨터 버스이다. I2C 버스는 각 디바이스가 I2C 버스 상에서 송신된 상이한 메시지들에 대해 마스터 (master) 및 슬레이브 (slave)로서 기능할 수 있는 멀티-마스터 (multi-master) 버스이다. I2C 버스는 직렬 데이터 라인 (Serial Data Line; SDA) 및 직렬 클럭 라인 (Serial Clock Line; SCL)을 포함하는, 오직 2 개의 양방향 오픈-드레인 (open-drain) 커넥터들을 이용하여 데이터를 송신할 수 있다. 이 커넥터들은 통상적으로 풀-업 (pull-up) 저항기들에 의해 종단되는 신호 선들 (signal wires)을 포함한다.

[0004] I2C 버스 동작들을 지배하는 프로토콜들은 기본 타입들의 메시지들을 정의하고, 그 각각은 START로 시작하고 STOP로 끝난다. I2C 버스는 7-비트 어드레싱을 이용하고, 2 개 타입들의 노드들: 마스터 및 슬레이브를 정의한다. 마스터 노드는 클럭을 발생시키고 슬레이브 노드들과 통신을 개시하는 노드이다. 슬레이브 노드는 마스터에 의해 어드레싱될 때 클럭을 수신하고 응답하는 노드이다. I2C 버스는 멀티-마스터 버스이고, 이는 임의의 수의 마스터 노드들이 존재할 수 있는 것을 의미한다. 추가적으로, 마스터 및 슬레이브 역할들은 메시지들 사이에서 (즉, STOP 이 전송된 후에) 변경될 수도 있다.

[0005] I2C 버스의 원래의 구현들은 표준-모드 동작에서 초당 100 킬로비트들 (100kbps)을 지원하였고, 보다 최근의 표준들은 고속-모드 동작에서 400kbps, 및 고속-모드 플러스 동작에서는 초당 1 메가비트 (Mbps)의 속도를 지

원한다. 하지만, 몇몇 시스템들 및 장치에서, 특정 타입들의 디바이스들 사이의 통신들을 지원하기 위해 더 높은 대역폭들이 요구된다. 예를 들어, 셀룰러 폰들과 같은 모바일 통신 디바이스들은 카메라들, 디스플레이들, 및 상당한 대역폭을 소비하는 다양한 통신 인터페이스들을 채용할 수도 있다. 종래의 I2C 프로토콜들이 레거시 (legacy) 디바이스들과의 호환성을 유지하기 위해 사용될 때 더 높은 대역폭들을 획득하기 어려울 수도 있다.

[0006] 모바일 디바이스 내에서 마스터 및 슬레이브 컴포넌트들을 연결하는 버스로서 구성되는 직렬 인터페이스들에 대해 최적화된 통신들을 제공하기 위한 진행중인 필요성이 존재한다.

## 발명의 내용

### 과제의 해결 수단

[0007] 이하에서는 이러한 양태들의 기본적인 이해를 제공하기 위해, 본 개시의 하나 이상의 양태들의 간단한 개요를 제시한다. 이 개요는 본 개시의 모든 고려되는 특징들의 광범위한 개관이 아니고, 본 개시의 모든 양태들의 주요한 또는 결정적인 요소들을 식별하려는 의도도 아니고 본 개시의 임의의 또는 모든 양태들의 범위를 기술하려는 의도도 아니다. 그것의 유일한 목적은 본 개시의 하나 이상의 양태들의 몇몇 개념들을 나중에 제시되는 보다 상세한 설명에 대한 전제부로서 단순화된 형태로 제시하려는 것이다.

[0008] 본 명세서에서 개시된 실시형태들은 통상의 I2C 버스를 이용하여 종래의 I2C 버스 동작들 및 강화된 통신 인터페이스들 양자를 지원하는 직렬 버스를 이용하여 통신 인터페이스의 성능을 향상시킬 수 있는 시스템들, 방법들 및 장치를 제공한다. 카메라 제어 인터페이스들 (camera control interface; CCI)은 마스터와 하나 이상의 슬레이브들을 연결하는 버스로서 구성된 2-선, 양방향, 하프 듀플렉스, 직렬 (two-wire, bi-directional, half duplex, serial) 인터페이스를 이용하여 전개되고 (deployed), 여기서, CCI 동작들은 I2C 버스 동작들과 호환가능하다. 본 명세서에서 개시된 하나의 예에서, CCI 확장 (CCI extension; CCIE) 디바이스들은 2-선, 양방향, 하프 듀플렉스, 직렬 인터페이스를 제공하기 위해 I2C 버스를 이용하여 전개될 수도 있다. CCIE 디바이스들은 버스 마스터로서 또는 슬레이브로서 구성될 수도 있다. CCIE 디바이스들은, I2C 디바이스들이 I2C 버스를 모니터링하고 있을 때에도, CCIE 디바이스가 CCIE 프로토콜들 및 시그널링 사양들을 이용하여 하나 이상의 다른 CCIE 디바이스들과 통신할 수도 있도록, I2C 버스 상의 I2C 디바이스들과 호환가능 또는 공존할 수 있다. 본 명세서에서 개시된 하나의 예는, 양 CCIE 및 I2C 디바이스들이 동일한 버스 상에서 전개된 때에, 단일 마스터로, 버스 상의 다수의 슬레이브들을 핸들링할 수 있는 인터페이스를 제공한다. 후자의 예에서, 2 이상의 CCIE 디바이스들은 CCIE 프로토콜들을 이용하여 통신할 수도 있고, I2C 디바이스와의 임의의 통신 교류는 I2C 버스 프로토콜들을 이용하여 수행된다.

[0009] 본 개시의 하나의 양태에서, 본 개시는 송신 디바이스 상에서 동작가능한 데이터 통신 방법을 제공한다. 이 방법은, 비트들의 셋트로부터 천이 넘버 (transition number)를 생성하는 단계, 천이 넘버를 심볼들의 시퀀스로 변환하는 단계, 2-선 직렬 버스가 제 1 동작 모드에서 동작될 때 2-선 직렬 버스 상에서 심볼들의 시퀀스를 송신하는 단계를 포함한다. 타이밍 정보는 심볼들의 시퀀스에서의 심볼들 사이의 천이들에서 인코딩될 수도 있다. 각각의 천이는 2-선 직렬 버스의 시그널링 상태에서의 변화를 야기할 수도 있다. 2-선 직렬 버스가 제 2 동작 모드에서 동작될 때, 2-선 직렬 버스 상에서 통신하도록 구성된 디바이스에 의해 심볼들의 시퀀스는 무시될 (ignored) 수도 있다. 심볼들의 시퀀스는 12 심볼들을 포함할 수도 있다.

[0010] 다른 양태에서, 천이 넘버는 다중-디지트 3진수를 포함한다. 3진수 (ternary number)는 예를 들어 12 디지트들 (digits)을 가질 수도 있다. 천이 넘버는, 그 천이 넘버를 트랜스코더 (transcoder)에 제공함으로써 심볼들의 시퀀스로 변환될 수도 있다. 하나의 예에서, 3진수의 최상위 디지트 (most significant digit)가 제일 먼저 트랜스코더에 제공되고, 3진수의 최하위 디지트 (least significant digit)가 마지막으로 트랜스코더에 제공되며, 최상위 디지트와 최하위 디지트 사이의 중간 디지트들은 감소하는 순위의 순서로 트랜스코더에 제공된다. 또 다른 예에서, 3진수의 최상위 디지트가 마지막으로 트랜스코더에 제공된다. 4 개의 시그널링 상태들 (signaling states)이 2-선 직렬 버스에 대해 정의될 수도 있다. 3진수의 각 디지트는 3 개의 이용가능한 심볼들 중 하나로부터 2-선 직렬 버스 상에서 송신될 다음 심볼을 선택할 수도 있다. 이를 3 개의 이용가능한 심볼들의 각각은 2-선 직렬 버스 상에서 송신되고 있는 현재의 심볼과 상이하다. 심볼들의 시퀀스에서 인코딩된 타이밍 정보는 수신기가 심볼들의 시퀀스로부터 수신 클럭을 생성하는 것을 가능하게 한다.

[0011] 또 다른 양태에서, 2-선 직렬 버스는, 2-선 직렬 버스가 제 1 동작 모드에서 동작될 때 CCIE 프로토콜들을 이용

하는 통신들을 지원하는 다목적 버스일 수도 있다. 2-선 직렬 버스는 제 2 동작 모드에서 I2C 프로토콜들을 이용하는 통신들을 지원할 수도 있다. 심볼들의 시퀀스는, 제 1 동작 모드에서 2-선 직렬 버스 상에서 송신되는 심볼들의 시퀀스들 사이에 I2C 시작 조건을 제공함으로써 2-선 직렬 버스 상에서 송신될 수도 있다. 시작 조건은 I2C 프로토콜들을 이용하는 통신들을 위해 구성된 디바이스에서의 수신 로직 (receive logic) 의 리셋 (reset) 을 야기할 수도 있다. 심볼들의 시퀀스는 제 1 I2C 시작 조건이 2-선 직렬 버스 상에서 송신된 후에 2-선 직렬 버스 상에서 송신될 수도 있다. 2-선 직렬 버스 상에서 심볼들의 시퀀스 뒤에 제 2 I2C 시작 조건이 뒤따를 수도 있다. 2-선 직렬 버스를 모니터링하는 I2C 수신기는, 제 1 I2C 시작 조건 후에 그 리고 제 2 I2C 시작 조건 전에 2-선 직렬 버스의 SCL 상에서 최대 6 클럭 사이클들을 감지할 수도 있다.

[0012] 본 개시의 하나의 양태에서, 장치는, 그 장치를 복수의 다른 장치들 및 디바이스들과 공유되도록 동작가능한 2-선 직렬 버스에 커플링하도록 적응되는 (adapted) 버스 인터페이스, 및 버스 인터페이스에 커플링된 프로세싱 회로를 포함할 수도 있다. 프로세싱 회로는, 비트들의 셋트로부터 천이 넘버를 생성하고, 천이 넘버를 심볼들의 시퀀스로 변환하며, 2-선 직렬 버스가 제 1 동작 모드에서 동작될 때 2-선 직렬 버스 상에서 심볼들의 시퀀스를 송신하도록 구성될 수도 있다. 타이밍 정보는 심볼들의 시퀀스에서 심볼들 사이의 천이들에서 인코딩될 수도 있다. 각각의 천이는 2-선 직렬 버스의 시그널링 상태에서의 변화를 야기한다. 2-선 직렬 버스가 제 2 동작 모드에서 동작될 때, 2-선 직렬 버스 상에서 통신하도록 구성된 디바이스에 의해 심볼들의 시퀀스는 무시될 수도 있다.

[0013] 본 개시의 하나의 양태에서, 데이터 통신 수신 디바이스 상에서 동작가능한 방법은, 2-선 직렬 버스가 제 1 동작 모드에서 동작될 때, 2-선 직렬 버스의 시그널링 상태에서의 천이들로부터 수신 클럭을 도출하는 단계, 제 1 동작 모드에 따라 2-선 직렬 버스 상에서 송신되는 심볼들의 12-심볼 시퀀스를 수신하기 위해 수신 클럭을 이용하는 단계, 심볼들의 시퀀스로부터 천이 넘버를 생성하는 단계, 및 천이 넘버로부터 데이터를 디코딩하는 단계를 포함한다. 2-선 직렬 버스의 시그널링 상태에서의 천이들은 심볼들의 시퀀스에서의 심볼들 사이의 천이들에 대응할 수도 있다. 2-선 직렬 버스가 제 2 동작 모드에서 동작될 때, 2-선 직렬 버스 상에서 통신하도록 구성된 디바이스에 의해 심볼들의 시퀀스는 무시될 수도 있다. 심볼들의 시퀀스는 12 심볼들을 포함할 수도 있다.

[0014] 다른 양태에서, 천이 넘버는 다수의 디지트들을 가질 수도 있고, 각 디지트는 심볼들의 시퀀스에서의 연속적인 심볼들의 쌍 사이의 천이를 나타낸다. 천이 넘버는 12 디지트 3진수를 포함할 수도 있다. 4 개의 시그널링 상태들이 2-선 직렬 버스에 대해 정의될 수도 있다. 3진수의 각 디지트는 2-선 직렬 버스 상에서의 연속적인 시그널링 상태들의 쌍 사이의 관계를 나타낼 수도 있다. 심볼들의 시퀀스에서의 각 심볼은 2-선 직렬 버스의 시그널링 상태에 의해 정의된 4 개의 심볼들 중 하나일 수도 있다. 3진수의 각 디지트는 심볼들의 시퀀스에서의 연속적인 심볼들의 쌍 사이의 관계를 정의할 수도 있다.

[0015] 또 다른 양태에서, 2-선 직렬 버스는, 2-선 직렬 버스가 제 1 동작 모드에서 동작될 때 CCIe 통신들을 지원하는 다목적 버스일 수도 있다. 2-선 직렬 버스는 제 2 동작 모드에서 I2C 통신들을 지원할 수도 있다. 심볼들의 시퀀스는, 2-선 직렬 버스 상에서의 I2C 시작 조건의 발생을 결정하고, 수신 클럭에 의해 정의된 타이밍에 따라 2-선 직렬 버스로부터 12 심볼들을 수신함으로써, 2-선 직렬 버스로부터 수신될 수도 있다.

[0016] 본 개시의 하나의 양태에서, 장치는, 그 장치를 복수의 다른 디바이스들과 공유되도록 동작가능한 2-선 직렬 버스에 커플링하도록 적응되는 버스 인터페이스, 2-선 직렬 버스의 시그널링 상태에서의 천이들로부터 수신 클럭을 도출하도록 구성된 클럭 복원 (recovery) 회로, 및 버스 인터페이스에 커플링된 프로세싱 회로를 포함한다. 프로세싱 회로는, 2-선 직렬 버스가 제 1 동작 모드에서 동작될 때 2-선 직렬 버스의 시그널링 상태에서의 천이들로부터 수신 클럭을 도출하고, 제 1 동작 모드에 따라 2-선 직렬 버스 상에서 송신되는 심볼들의 시퀀스를 수신하기 위해 수신 클럭을 이용하며, 심볼들의 시퀀스로부터 천이 넘버를 생성하고, 그 천이 넘버로부터 데이터를 디코딩하도록 구성될 수도 있다. 2-선 직렬 버스의 시그널링 상태에서의 천이들은 심볼들의 시퀀스에서의 심볼들 사이의 천이들에 대응할 수도 있다. 천이 넘버는 다중 디지트들을 가질 수도 있고, 각 디지트는 심볼들의 시퀀스에서의 연속적인 심볼들의 쌍 사이의 천이를 나타낸다. 2-선 직렬 버스가 제 2 동작 모드에서 동작될 때, 2-선 직렬 버스 상에서 통신하도록 구성된 디바이스에 의해 심볼들의 시퀀스는 무시될 수도 있다.

## 도면의 간단한 설명

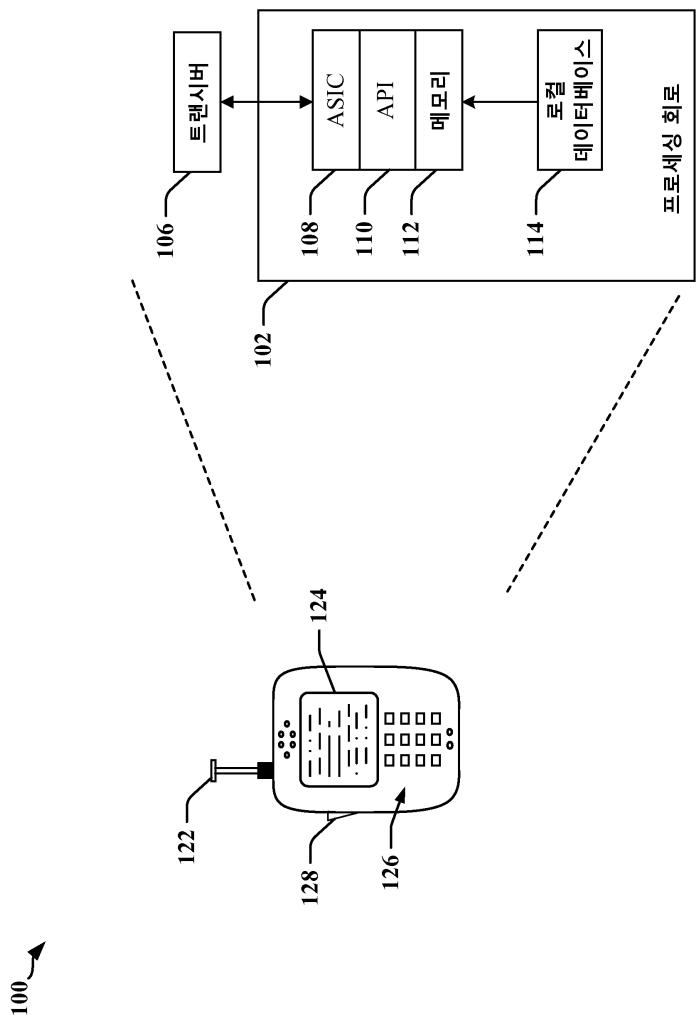

[0017] 도 1 은 복수의 이용가능한 표준들 중 하나에 따라 선택적으로 동작하는, IC 디바이스들 사이에 데이터 링크를

채용하는 장치를 나타낸다.

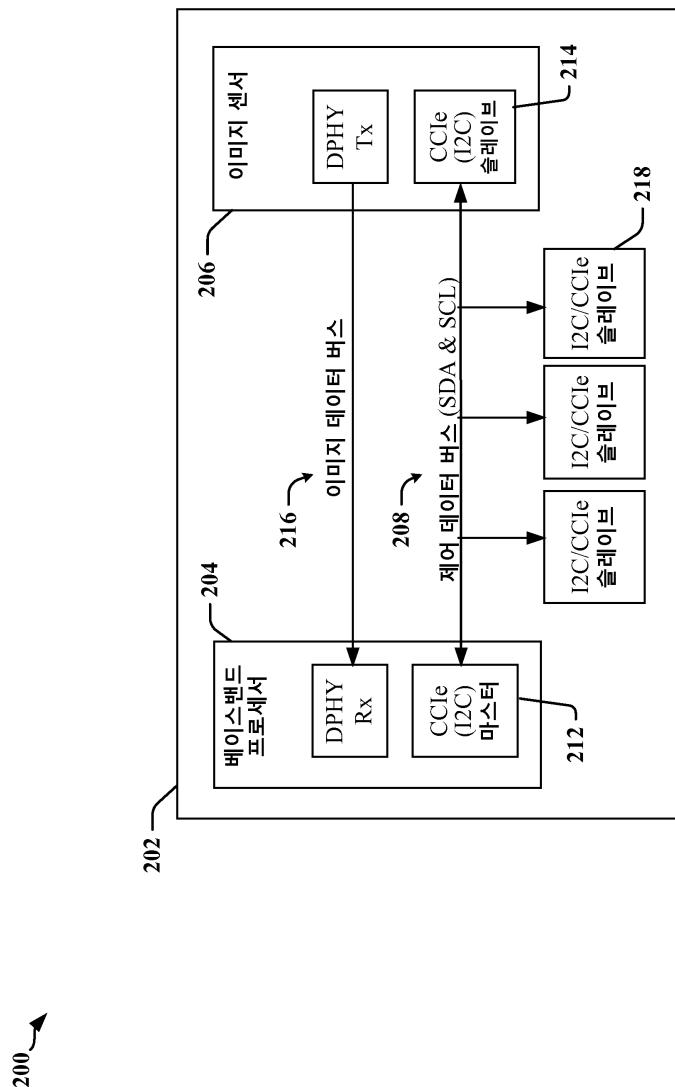

도 2 는 베이스밴드 프로세서 및 이미지 센서를 가지고, 이미지 데이터 버스 및 다중-모드 제어 데이터 버스를 구현하는 디바이스를 나타낸다.

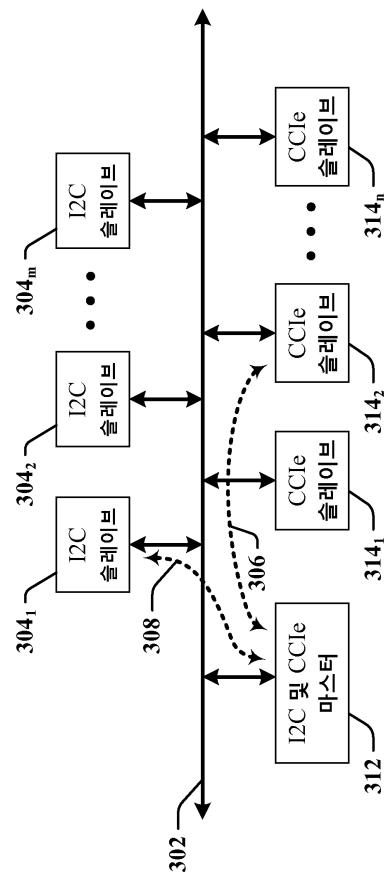

도 3 은 공존하는 I2C 모드 디바이스들 및 CCIe 모드 디바이스들을 지원하는 다목적 또는 공통 직렬 버스를 나타낸다.

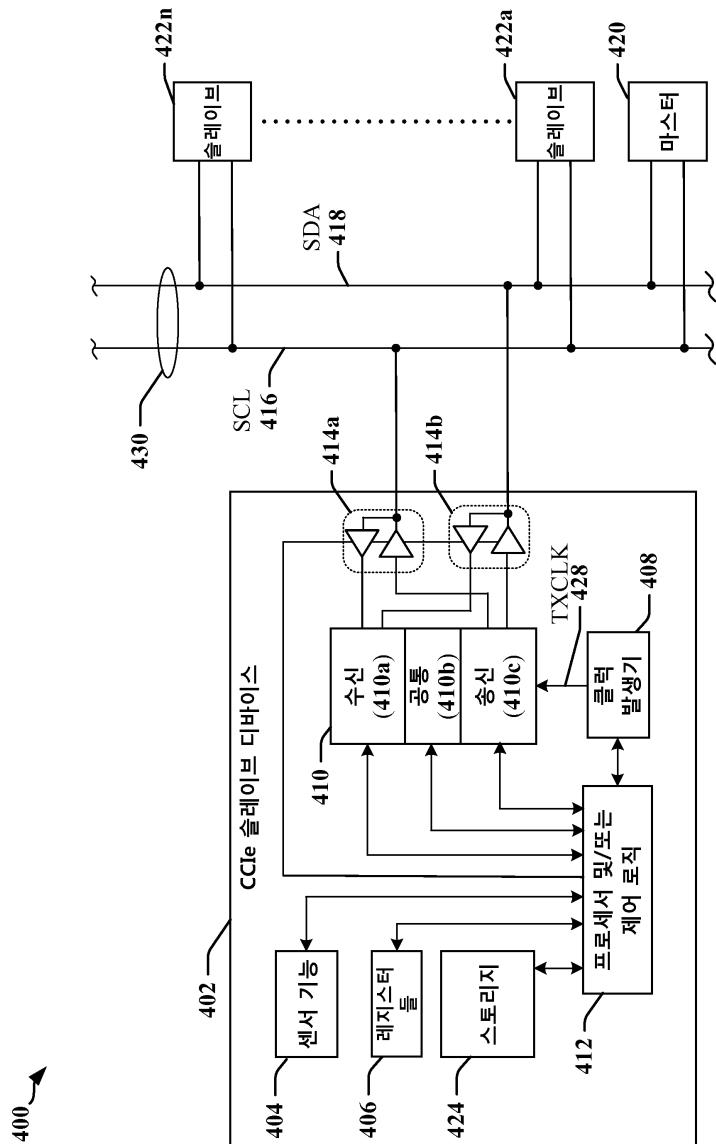

도 4 는 IC 디바이스들 사이에 데이터 링크를 채용하는 장치에 대한 시스템 아키텍처 (architecture) 를 나타낸다.

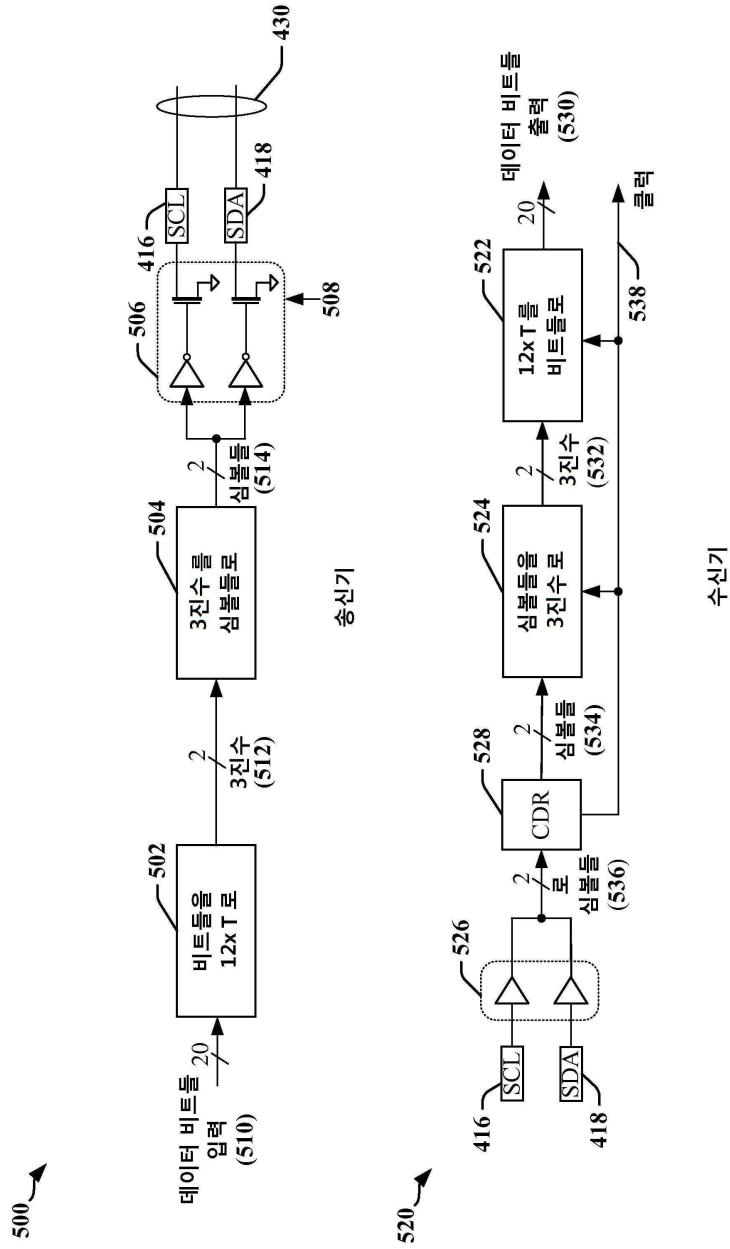

도 5 는 본 명세서에 개시된 특정 양태들에 따른 송신기 및 수신기의 특정 양태들을 나타낸다.

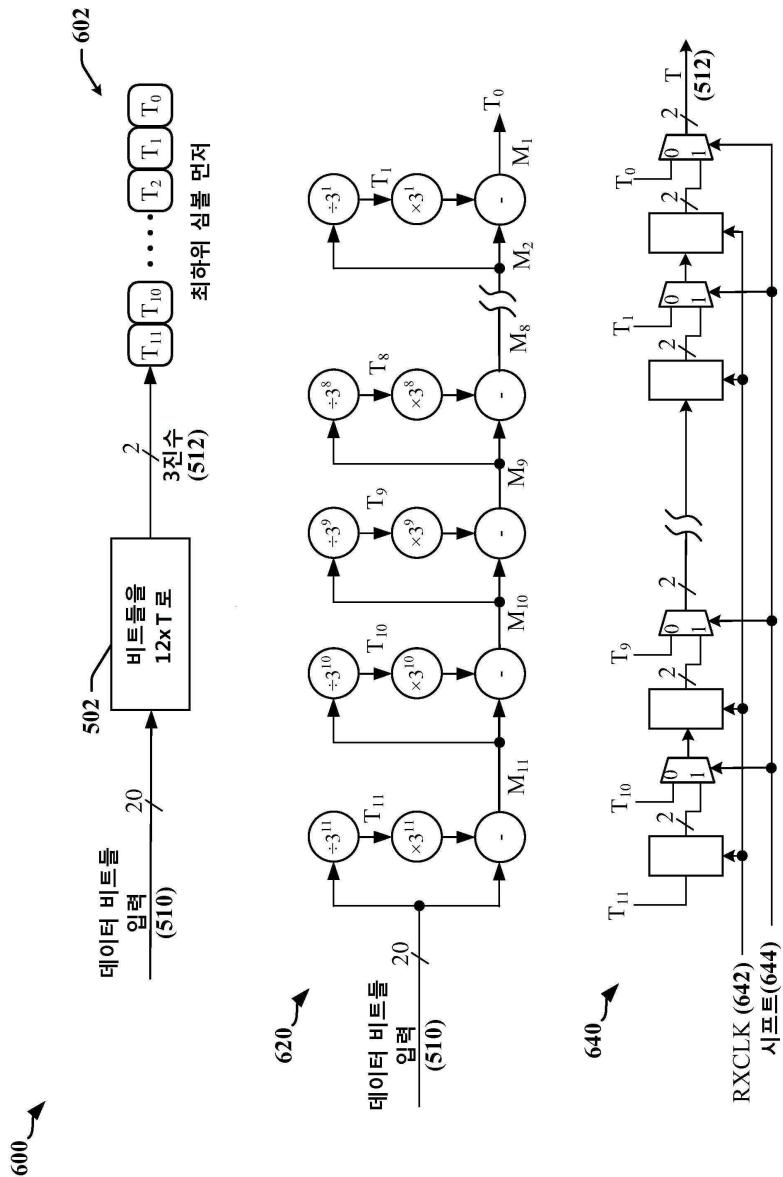

도 6 은 심볼들의 스트림에서의 최하위 심볼이 먼저 송신될 때 2진 비트들을 3진수들로 변환하도록 구성된 로직을 나타낸다.

도 7 은 심볼들의 스트림에서의 최상위 심볼이 먼저 송신될 때 2진 비트들을 3진수들로 변환하도록 구성된 로직을 나타낸다.

도 8 은 12 디지트 3진수를 복수의 비트들로 변환하기 위해 사용될 수도 있는 회로의 일 예를 나타낸다.

도 9 는 본 명세서에서 개시된 특정 양태들에 따라 데이터를 트랜스코딩하기 위한 인코딩 방식을 나타낸다.

도 10 은 레거시 I2C 프로토콜의 전형적인 I2C 비트 전송 사이클을 나타낸다.

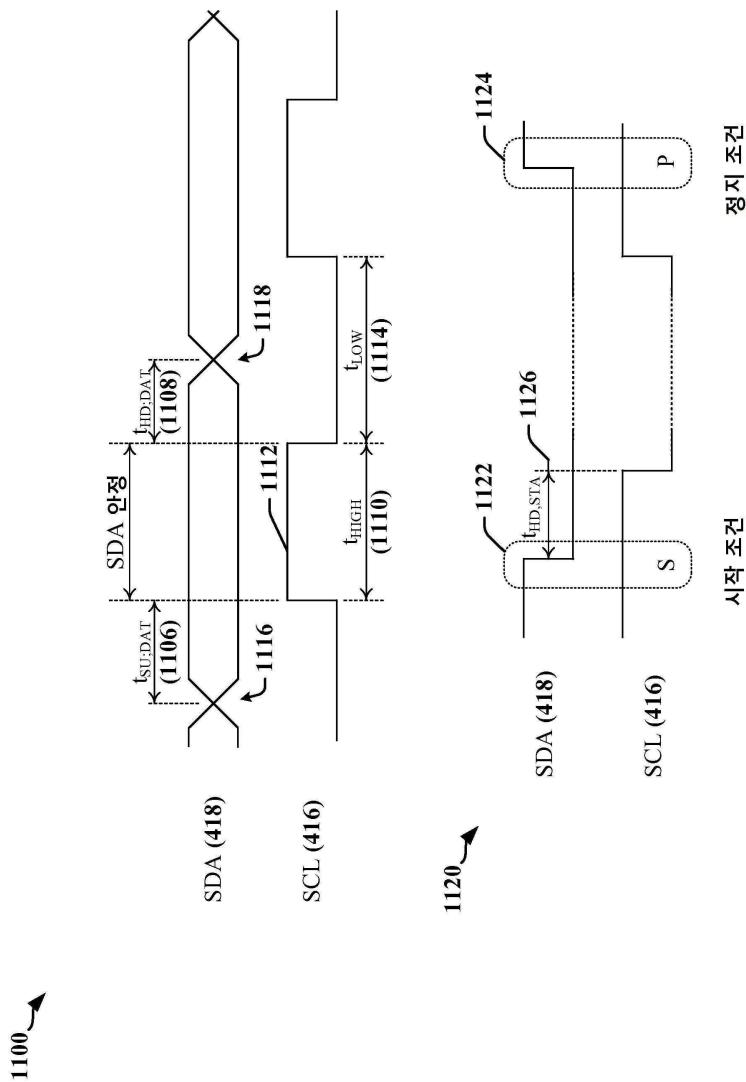

도 11 은 종래의 I2C 버스 상에서 SDA 및 SCL 신호 사이의 관계를 나타낸다.

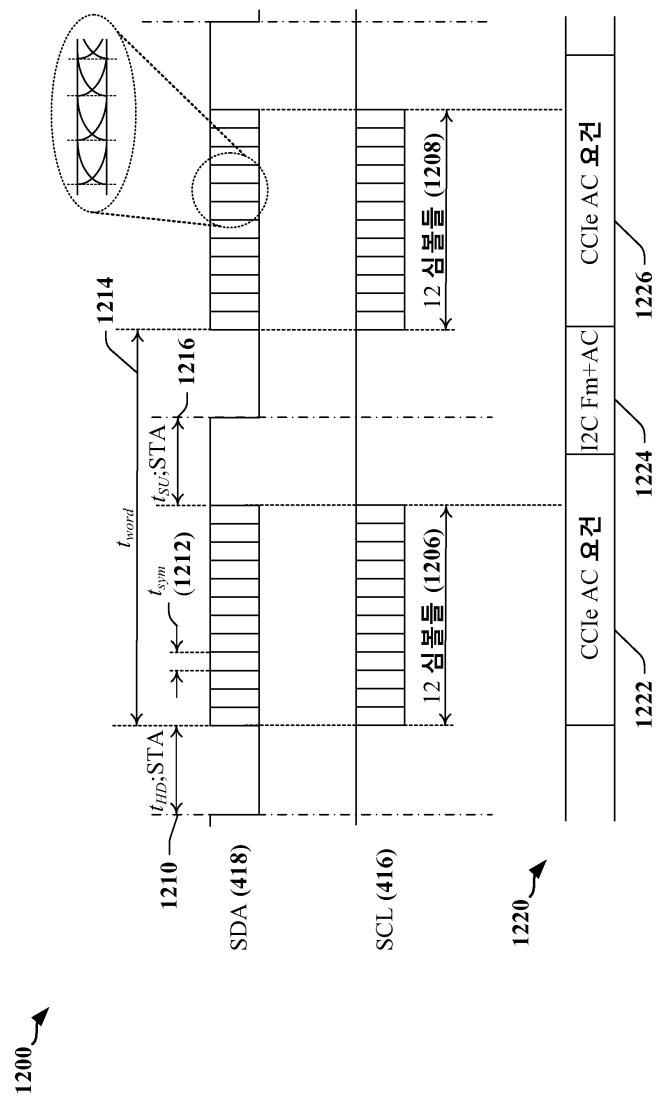

도 12 는 버스에 연결된 디바이스들이 I2C 디바이스를 포함할 때 공유된 버스 상에서 CCIe 모드에서의 데이터 송신의 일 예를 나타낸다.

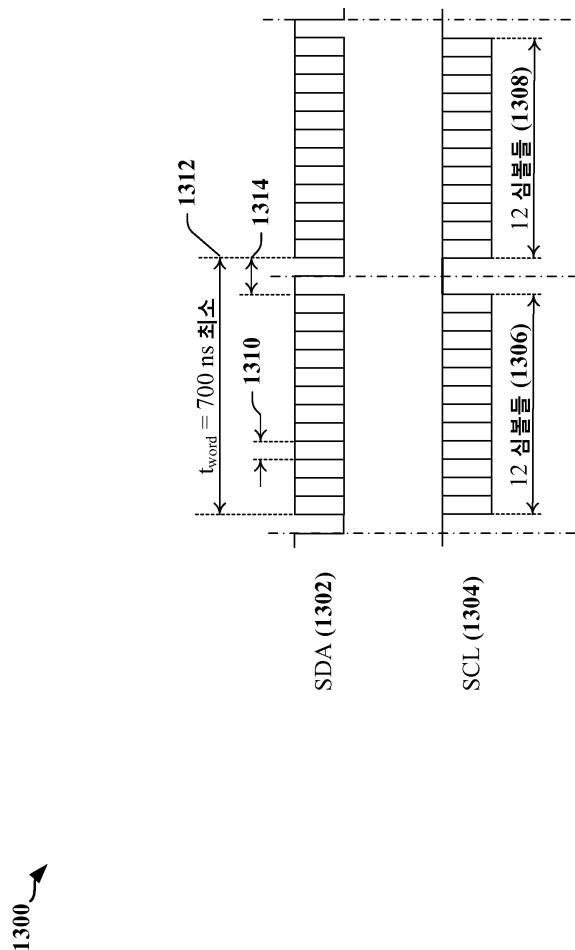

도 13 은 버스 (430) 상의 디바이스들이 활성 I2C 디바이스를 포함하지 않을 때 CCIe 버스 상에서의 데이터 송신을 나타낸다.

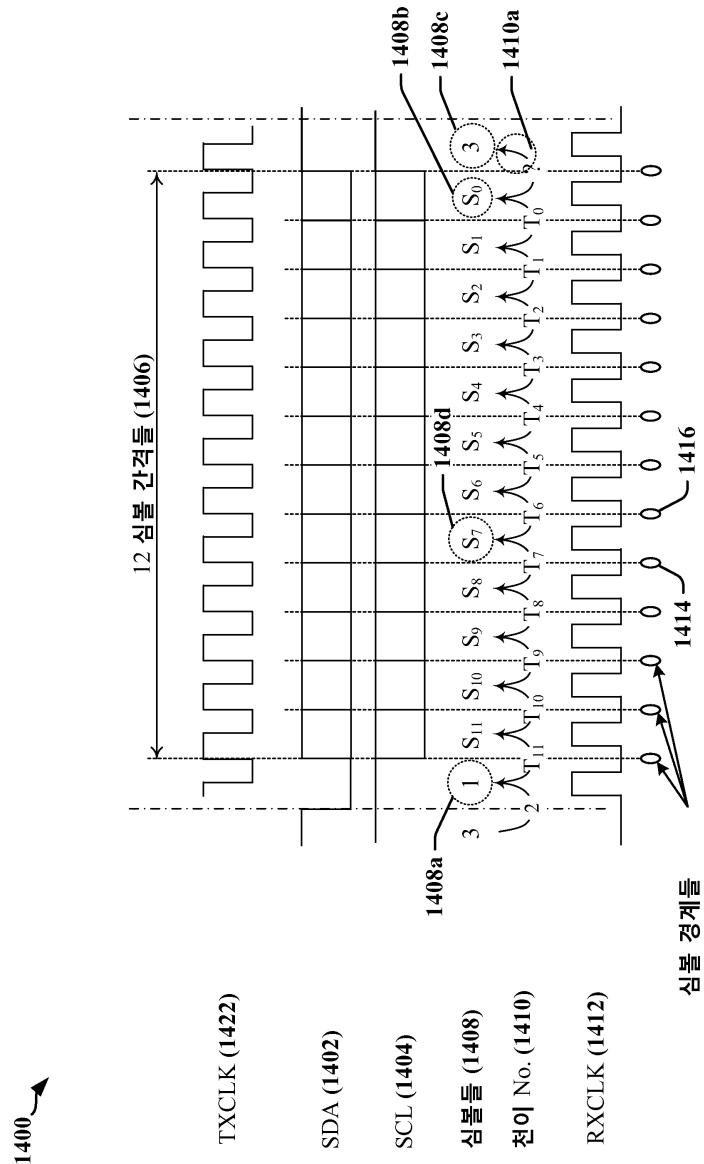

도 14 는 CCIe 동작 모드를 위해 구성되는 직렬 버스 상에서의 송신을 위한 심볼들의 생성을 나타낸다.

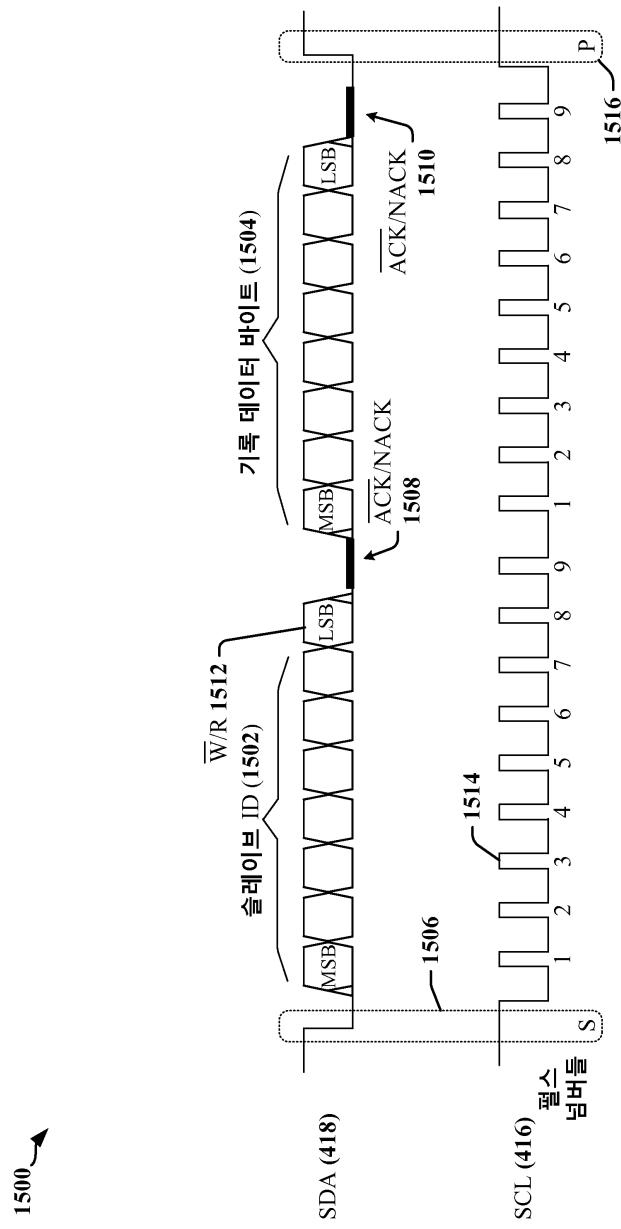

도 15 는 I2C 1 바이트 데이터 기록 동작을 나타낸다.

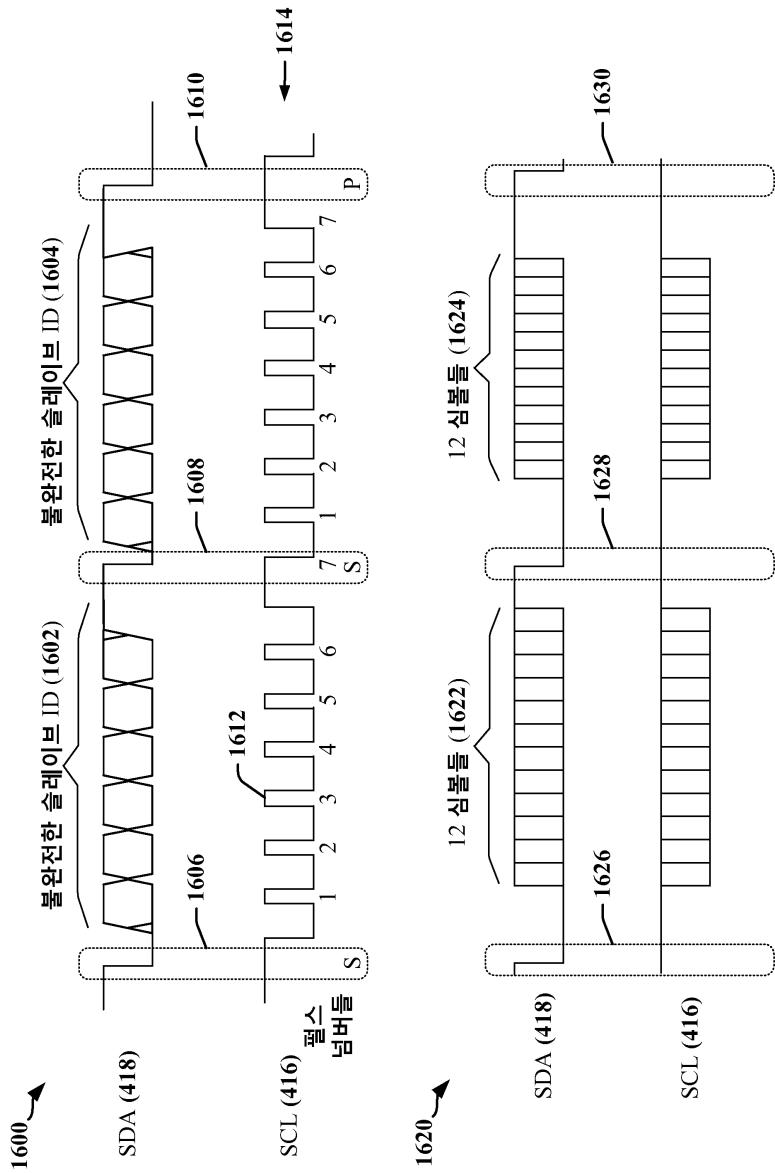

도 16 은 레거시 I2C 슬레이브 모드 상의 START 조건의 효과의 하나의 예를 나타낸다.

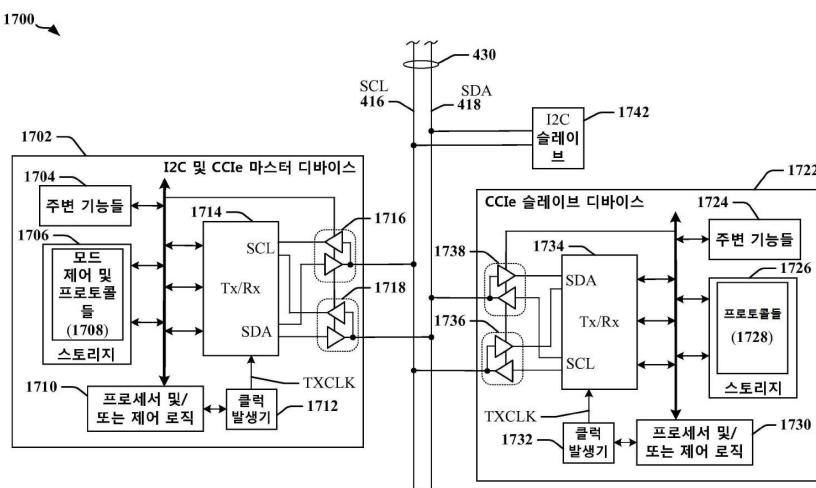

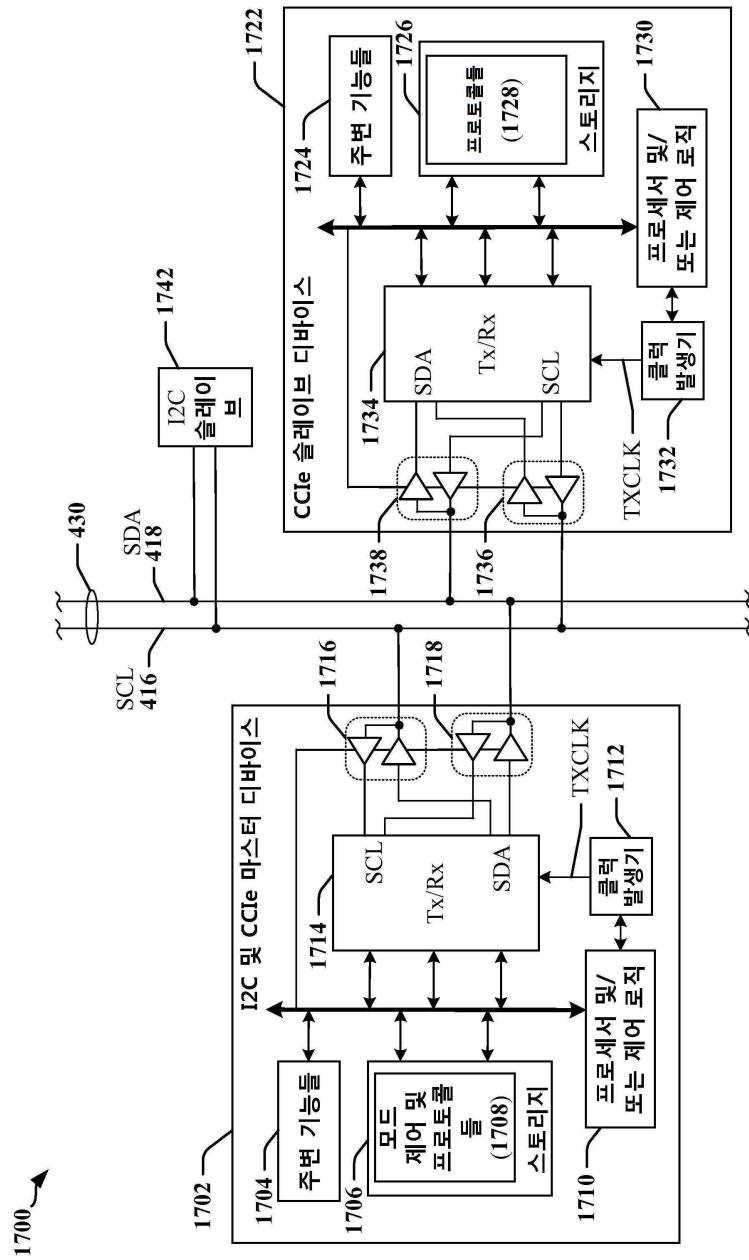

도 17 은 동일 직렬 버스 상에서 다중 모드들에서 통신할 수 있는 복수의 디바이스들을 포함하는 시스템을 나타낸다.

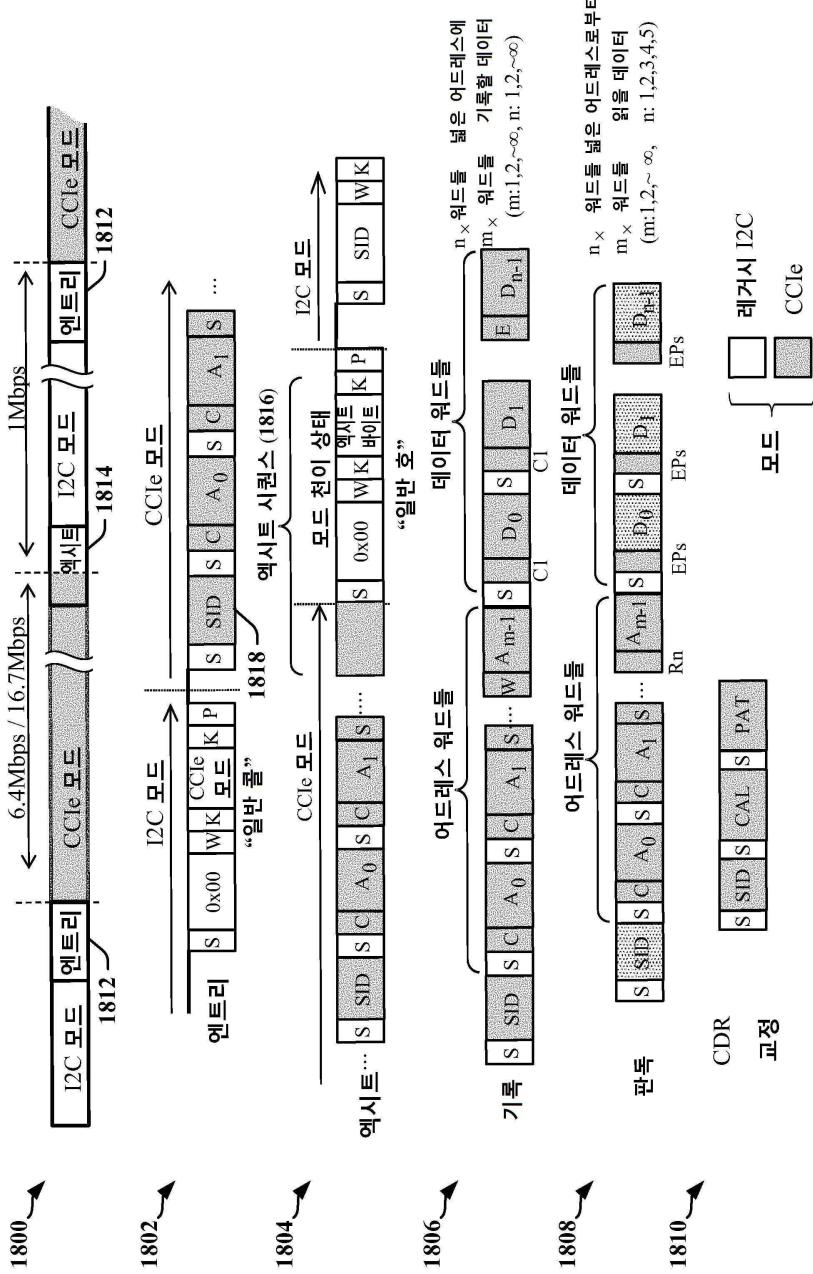

도 18 은 레거시 I2C 타이밍 및 시그널링을 또한 지원하는 공유된 직렬 버스 상에서 동작할 수 있는 CCIe 프로토콜의 일 예와 연관된 특정 타이밍 및 시그널링 양태들을 나타낸다.

도 19 는 CCIe 신호가 I2C Fm+ 모드를 위해 사용되는 동일한 물리적 드라이버에 의해 구동될 때 Fm+ 가능 I2C 버스 상에서의 CCIe 심볼 타이밍의 하나의 예를 나타낸다.

도 20 은 I2C 호환 버스에 커플링된 CCIe 디바이스들에 의해 이용될 수도 있는 오픈-드레인 드라이버들의 일 예를 나타낸다.

도 21 은 본 명세서에서 개시된 특정 양태들에 따라 적응될 수도 있는 프로세싱 시스템을 채용하는 장치의 일 예를 나타내는 블록도이다.

도 22 는 본 명세서에서 개시된 하나 이상의 양태들에 따라 CCIe 버스 상에서 정보를 송신하는 방법의 흐름도이다.

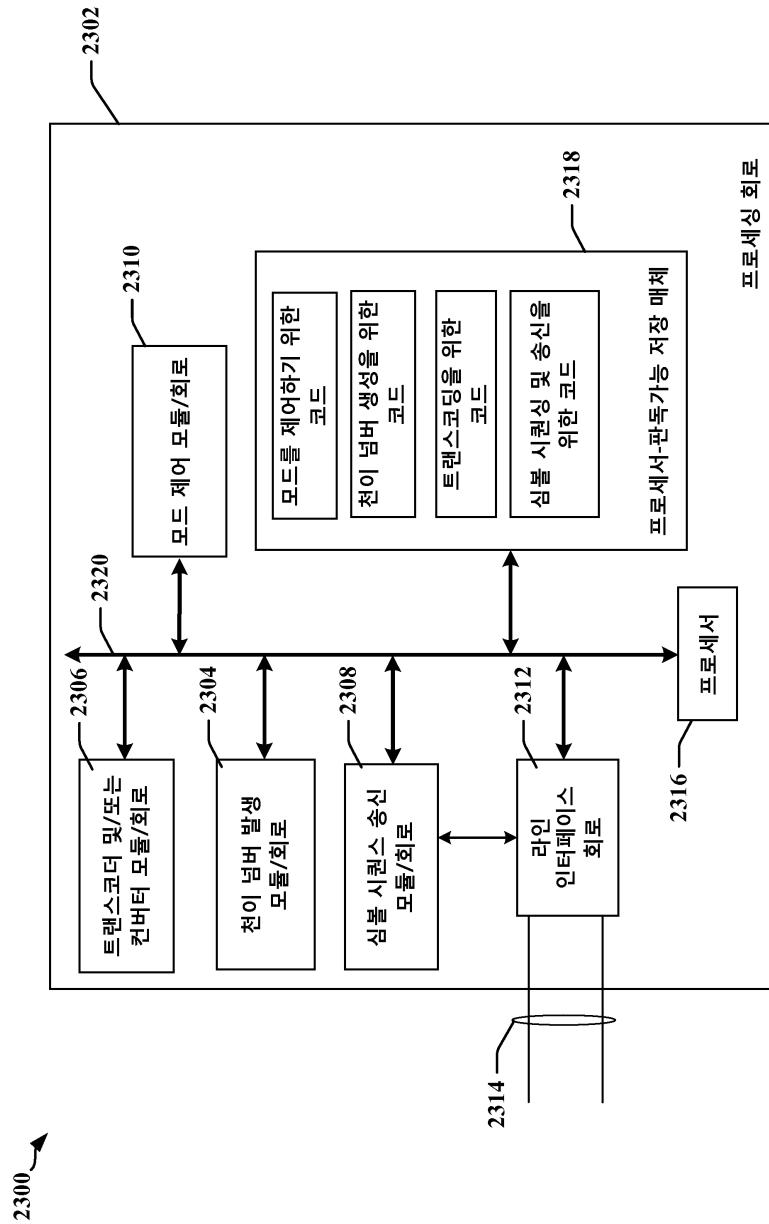

도 23 은 본 명세서에서 개시된 하나 이상의 양태들에 따라 CCIe 버스 상에서 정보를 통신하는 송신 장치에 대한 하드웨어 구현의 일 예를 나타내는 도이다.

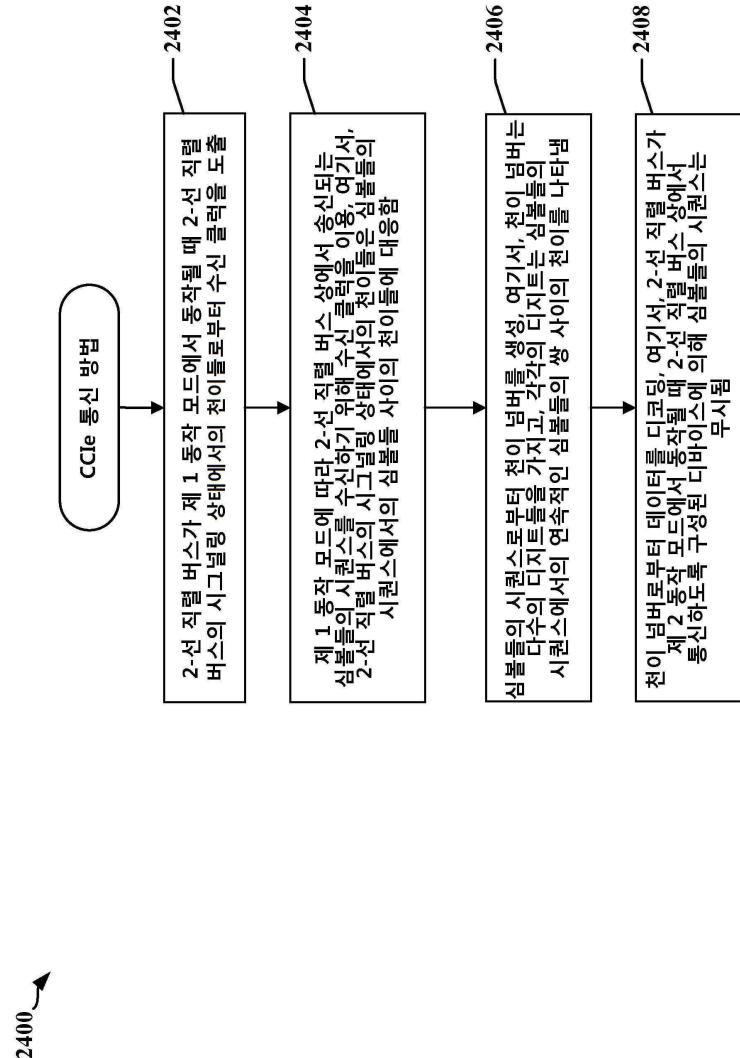

도 24 는 본 명세서에서 개시된 하나 이상의 양태들에 따라 CCIe 버스로부터 정보를 수신하는 방법의 흐름도이다.

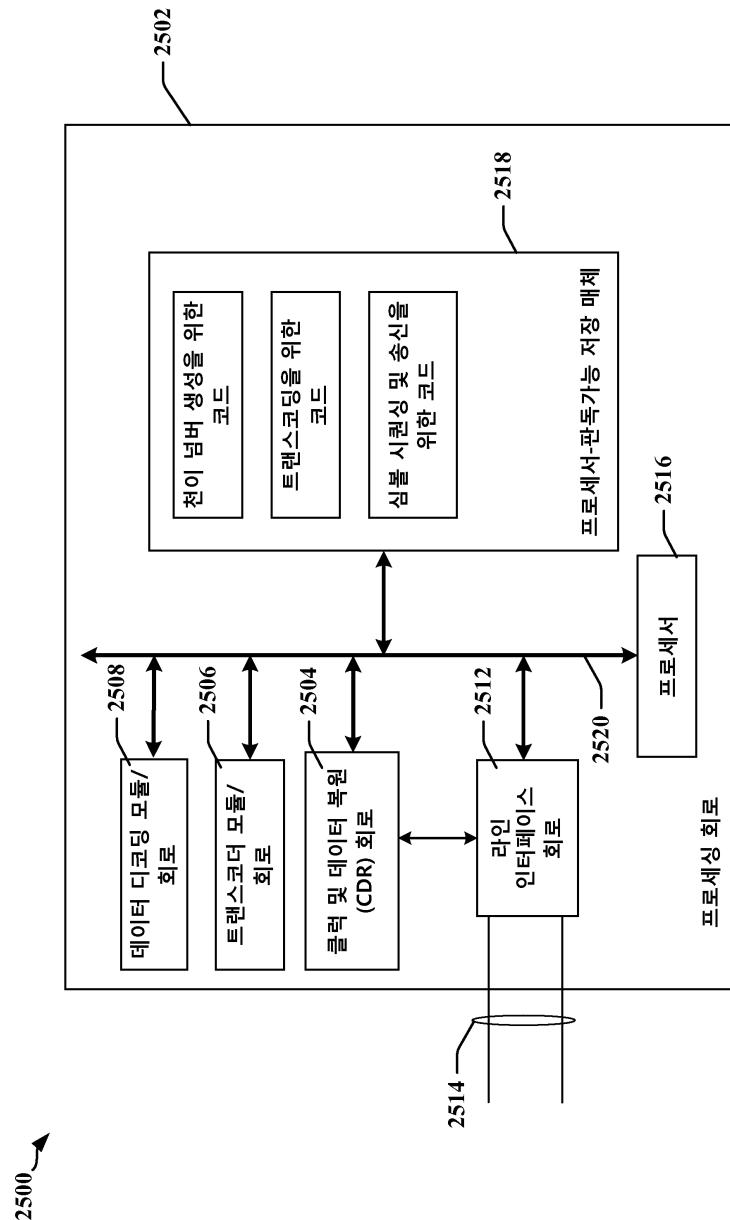

도 25 는 본 명세서에서 개시된 하나 이상의 양태들에 따라 CCIe 버스 상에서 송신되는 정보를 디코딩하는 수신

장치에 대한 하드웨어 구현의 일 예를 나타내는 도이다.

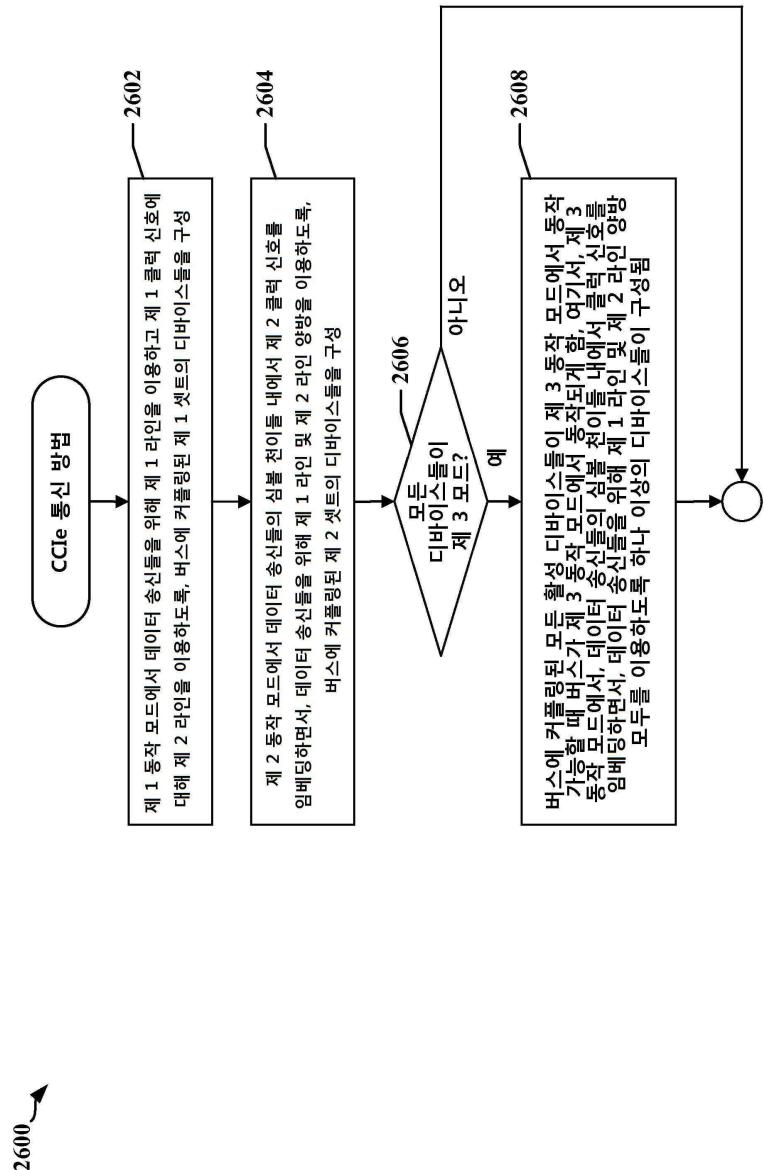

도 26 은 본 명세서에서 개시된 하나 이상의 양태들에 따른 버스를 채용하는 시스템 또는 디바이스를 동작시키는 방법의 흐름도이다.

### 발명을 실시하기 위한 구체적인 내용

[0018] 이제, 도면들을 참조하여 여러 양태들이 설명된다. 다음의 설명에서, 설명의 목적으로, 하나 이상의 양태들의 완전한 이해를 제공하기 위해 다양한 특정한 세부사항들이 제시된다. 그러나, 이러한 양태(들)은 이러한 특정한 세부사항들이 없이 구현될 수도 있음이 자명할 수도 있다.

[0019] 본 출원에서 이용된 바와 같이, 용어들 "컴포넌트", "모듈", "시스템" 등은, 이에 제한되지는 않으나, 하드웨어, 펌웨어, 하드웨어와 펌웨어의 조합, 소프트웨어, 실행 중인 소프트웨어와 같은 컴퓨터 관련 엔티티를 포함하고자 한다. 예를 들면, 컴포넌트는 프로세서 상에서 작동하는 프로세스, 프로세서, 오브젝트, 실행 가능한 물, 실행 스크립트, 프로그램, 및/또는 컴퓨터일 수도 있지만, 이들에 제한되는 것은 아니다. 예로서, 컴퓨팅 디바이스 상에서 작동하는 애플리케이션 및 컴퓨팅 디바이스 양자는 컴포넌트일 수 있다. 하나 이상의 컴포넌트들은 프로세스 및/또는 실행의 스크립트 내에 상주할 수도 있고, 컴포넌트는 하나의 컴퓨터 및/또는 두 개 이상의 컴퓨터들 사이에 분산되어 로컬라이징될 수도 있다. 또한, 이들 컴포넌트들은 여러 데이터 구조들이 저장된 여러 컴퓨터 관독 가능한 매체로부터 실행될 수도 있다. 컴포넌트들은 하나 이상의 데이터 패킷들 (예를 들면, 로컬 시스템의 다른 컴포넌트, 분산 시스템 및/또는 인터넷과 같은 네트워크를 통해 신호를 통해 다른 시스템들과 상호작용하는 하나의 컴포넌트로부터의 데이터) 을 구비하는 신호에 따르는 것과 같이 로컬 및/또는 원격 프로세스들을 통해 통신할 수도 있다.

[0020] 또한, 용어 "또는"은 배제하는 "또는"이라기 보다는 포함하는 "또는"을 의미하고자 한다. 즉, 달리 명시되지 않는 한, 또는 문맥에서 명확하지 않는 한, 구문 "X 는 A 또는 B 를 사용한다"는 자연적으로 포함하는 순열들 중 임의의 것을 의미하고자 한다. 즉, 구문 "X 는 A 또는 B 를 사용한다"는 다음의 예시들 중 임의의 예시에 의해 만족된다: X 는 A 를 사용한다; X 는 B 를 사용한다; 또는 X 는 A 와 B 양자 모두를 사용한다. 또한, 본 출원 및 첨부된 청구항들에서 이용된 바와 같은 관사 "하나 (a)" 및 "한 (an)"은 일반적으로, 단수 형태인 것으로 특정되거나 문맥에서 명확하지 않는 한 "하나 이상"을 의미하는 것으로 해석되어야 한다.

[0021] 본 발명의 특정 양태들은 전자 컴포넌트들 간에 배치된 통신 링크들에 적용가능할 수도 있으며, 이 전자 컴포넌트는 디바이스의 서브컴포넌트들, 이를 테면, 전화기, 모바일 컴퓨팅 디바이스들, 가전 제품들, 오토모바일 전자기기들, 항공 전자기기들 등을 포함할 수도 있다. 도 1 은 IC 디바이스들 사이의 통신 링크를 채택할 수도 있는 장치를 나타낸다. 일 예에서, 장치 (100)는 무선 액세스 네트워크 (RAN), 코어 액세스 네트워크, 인터넷 및/또는 다른 네트워크와 RF 트랜시버를 통하여 통신하는 무선 통신 디바이스를 포함할 수도 있다. 장치 (100)는 프로세싱 회로 (102)에 동작가능하게 커플링되는 통신 트랜시버 (106)를 포함할 수도 있다.

프로세싱 회로 (102)는 하나 이상의 IC 디바이스들, 이를 테면, 응용 주문형 IC (ASIC)(108)를 가질 수도 있다. ASIC (108)은 하나 이상의 프로세싱 디바이스들, 논리 회로들 등을 포함할 수도 있다. 프로세싱 회로 (102)는 프로세싱 회로 (102)에 의해 실행가능할 수도 있는 명령들 및 데이터를 유지할 수도 있는 프로세서 관독가능 저장부, 이를 테면 메모리 (112)를 포함 및/또는 커플링될 수도 있다. 프로세싱 회로 (102)는 무선 디바이스의 저장부 (112) 내에 상주하는 소프트웨어 모듈의 실행을 가능하게 하고 지원하는 애플리케이션 프로그래밍 인터페이스 (API)(110) 계층 및 오퍼레이팅 시스템 중 하나 이상에 의해 제어될 수도 있다. 메모리 디바이스 (112)는 ROM (read-only memory) 또는 RAM (random-access memory), EEPROM (electrically erasable programmable read-only memory), 플래시 카드들, 또는 프로세싱 시스템 및 컴퓨팅 플랫폼들에 이용될 수 있는 임의의 메모리 디바이스를 포함할 수도 있다. 프로세싱 회로 (102)는 장치 (100)를 구성하고 동작시키는데 사용된 동작 파라미터들 및 다른 정보를 유지할 수 있는 로컬 데이터베이스 (114)를 포함하거나 로컬 데이터베이스 (114)에 액세스할 수도 있다. 로컬 데이터베이스 (114)는 데이터베이스 모듈, 플래시 메모리, 자기 매체, EEPROM, 광학 매체, 테이프, 소프트 또는 하드 디스크, 등등 중 하나 이상을 사용하여 구현될 수도 있다. 프로세싱 회로는 또한, 다른 컴포넌트들 중에서 안테나 (122), 디스플레이 (124), 오퍼레이터 제어부들, 예컨대 버튼 (128) 및 키패드 (126)와 같은 외부 디바이스들에 동작가능하게 커플링될 수도 있다.

### I2C 및 CCIE 동작들 양자를 지원하는 버스 아키텍처의 예

[0022] 도 2 는 베이스밴드 프로세서 (204) 및 이미지 센서 (206)를 갖는 디바이스 (202)의 단순화된 예를 나타내는

블록도 (200) 이다. 이미지 데이터 (216) 및 다중-모드 제어 데이터 버스 (208) 가 디바이스 (202) 에서 구현될 수도 있다. 디바이스 (202) 는 카메라 디바이스 (202) 를 오직 예시적인 방식으로 나타내고, 제어 데이터 버스 (208) 를 이용하여 다양한 다른 디바이스들 및/또는 상이한 기능들이 구현, 동작 및/또는 통신할 수도 있다.

묘사된 예에서, 이미지 데이터는 MIPI 에 의해 정의된 "DPHY" 고속 차동 링크와 같은 이미지 데이터 버스 (216) 를 통해 이미지 센서 (206) 로부터 베이스밴드 프로세서 (204) 로 전송될 수도 있다. 하나의 예에서, 제어 데이터 버스 (208) 는 I2C 버스 모드에서의 동작을 위해 구성가능한 2 개의 선들을 가질 수도 있다. 따라서, 제어 데이터 버스 (208) 는 SCL 및 SDA 선들을 포함할 수도 있다. SCL 은 I2C 프로토콜들에 따라 제어 데이터 버스 (208) 를 통한 데이터 전송들을 동기화하기 위해 사용될 수도 있는 클럭 신호를 반송할 수도 있다. 데이터 라인 SDA 및 클럭 라인 SCL 은 I2C 버스 (제어 데이터 버스 (208)) 상에서 다수의 디바이스들 (212, 214, 및 218) 에 커플링될 수도 있다. 이 예에서, 제어 데이터는 제어 데이터 버스 (208) 를 통해 베이스밴드 프로세서 (204) 와 이미지 센서 (206) 및 다른 주변 디바이스들 (218) 사이에서 교환될 수도 있다.

I2C 프로토콜들에 따르면, SCL 선 상의 클럭 속도들은 보통의 I2C 동작에 대해 100KHz 까지, I2C 고속 모드에 대해 400KHz 까지, 그리고 I2C 고속 모드 플러스 (Fm+) 에 대해 1MHz 까지일 수도 있다. I2C 버스를 통한 이들 동작 모드들은 카메라 애플리케이션들에 대해 이용될 때 카메라 제어 인터페이스 (CCI) 로서 지칭될 수도 있다.

[0024] 하나의 양태에 따르면, 향상된 동작 모드는 카메라 동작을 지원하기 위해 다중-모드 제어 데이터 버스 (208) 를 통해 구현될 수도 있다. 향상된 동작 모드는 데이터가 1MHz 보다 더 큰 레이트 (rate) 에서 전송될 수 있게 할 수도 있고, 향상된 모드는 CCI 확장 (CCIE) 모드로서 지칭될 수도 있다.

[0025] 하나의 예에서, CCIE 버스는 CCIE 버스 동작들과 호환가능한 디바이스들에 대해 보다 높은 데이터 레이트들을 제공하기 위해 사용될 수도 있다. 이러한 디바이스들은 CCIE 디바이스들로서 지칭될 수도 있고, CCIE 디바이스들은 종래의 CCI 버스의 SCL 라인 및 SDA 라인 양자를 이용하여 송신되는 심볼들로서 데이터를 인코딩함으로써 서로 통신할 때 더 높은 데이터 레이트들을 획득할 수 있다. CCIE 는 카메라 애플리케이션들에 대해 이용될 수도 있다. CCIE 디바이스들 및 I2C 디바이스들은 동일 CCIE 버스 상에서 공존할 수도 있어, 제 1 시간 간격에서, 데이터는 CCIE 인코딩을 이용하여 송신될 수도 있고, 다른 데이터는 I2C 시그널링 규약들 및 프로토콜들에 따라 상이한 시간 간격에서 송신될 수도 있다.

[0026] 디바이스 (202) 가 CCIE 모드를 위해 구성될 때, 베이스밴드 프로세서 (204) 는 마스터 노드 (212) 를 포함하고, 이미지 센서 (206) 는 슬레이브 노드 (214) 를 포함하며, 양 마스터 노드 (212) 및 슬레이브 노드 (214) 는 제어 데이터 버스 (208) 에 커플링된 임의의 레거시 I2C 디바이스들의 적절한 동작에 영향을 미침이 없이 제어 데이터 버스 (208) 를 통해 CCIE 모드 프로토콜들에 따라 동작한다. 제어 데이터 버스 (208) 는 CCIE 디바이스들과 레거시 I2C 슬레이브 디바이스들 사이에 브릿지 디바이스 없이 CCIE 모드 동작들을 지원할 수도 있다.

[0027] 하나의 예에서, 제어 데이터 버스 (208) 상에서의 제 1 교환 동안, 레거시 I2C 디바이스들은 제 1 클럭, 제 1 버스 속도, 및/또는 제 1 신호 프로토콜을 갖는 제 1 모드에서 동작할 수도 있는 한편, 제어 데이터 버스 (208) 상에서의 제 2 교환 동안 CCIE-가능 디바이스들은 제 2 클럭, 제 2 버스 속도, 및/또는 제 2 프로토콜을 갖는 제 2 모드에서 동작할 수도 있다. 제 1 클럭, 제 1 버스 속도, 및/또는 제 1 신호 프로토콜은 제 2 클럭, 제 2 버스 속도, 및/또는 제 2 프로토콜과 구분될 수도 있다. 예를 들어, 제 2 클럭 및/또는 제 2 버스 속도는 제 1 클럭 및/또는 제 1 버스 속도보다 각각 더 빠를 수도 있거나 더 큰 속도를 가질 수도 있다.

[0028] 다른 예에서, 모든 슬레이브 디바이스들 (218) 은 제 1 동작 모드와 제 2 동작 모드 사이에서 스위칭할 필요가 없도록 CCIE-가능 디바이스들일 수도 있다. 즉, 모든 시그널링 및/또는 통신은 제 2 클럭 및/또는 제 2 버스 속도를 이용하고 제 2 프로토콜을 이용하는 제 2 모드에 따라 수행될 수도 있다. 모든 슬레이브 디바이스들 (218) 이 CCIE-가능 디바이스들일 때 제 2 모드는 제 1 모드보다 더 큰 비트 레이트를 제공할 수도 있기 때문에 제 1 모드와 제 2 모드 사이에 스위칭할 필요성 또는 이점이 존재하지 않는다. 일부 경우들에서, 제 1 모드가 수용될 필요가 없을 때 제 2 모드보다 훨씬 더 큰 비트 레이트를 제공하지만 I2C 디바이스들과 호환가능하지 않은 제 3 동작 모드가 구현될 수도 있다.

[0029] 도 3 은 공존 I2C 모드 디바이스들 (304<sub>1</sub>-304<sub>n</sub>) 및 CCIE 모드 디바이스들 (312, 및 314<sub>1</sub>-314<sub>n</sub>) 을 지원하는 공통 버스 (302) 를 나타내는 블록도이다. I2C 모드 트랜잭션들 (transactions) (308) 에 대해, CCIE-가능 마스터 디바이스 (312) 는 1Mbps 의 최대 데이터 레이트를 획득하기 위해 I2C Fm+ 또는 CCI 프로토콜을 이용하여 버스 (302) 상에서 I2C 슬레이브 디바이스들 (304<sub>1</sub>-304<sub>n</sub>) 과 통신할 수도 있다. CCIE-가능 마스터 디바이스

(312) 가 완전한 CCI 또는 I2C Fm+ 성능을 지원할 수도 있는 한편, CCIE-가능 슬레이브 디바이스 (314<sub>1</sub>-314<sub>n</sub>)는 완전한 I2C 성능을 지원하도록 요구되지 않는다.

[0030]

CCIE-가능 마스터 디바이스 (312)는 또한 CCIE-가능 슬레이브 디바이스 (314<sub>1</sub>-314<sub>n</sub>)과 CCIE 모드 통신들 (306)을 확립할 수도 있다. CCIE 모드는 단일 마스터 동작을 허용하고, 다중 마스터들은 지원되지 않는다.

CCIE 모드에서, CCIE 마스터 디바이스 (312)는 제어 데이터 버스 (302) 상에서 오직 CCIE-가능 슬레이브 디바이스들 (314<sub>1</sub>-314<sub>n</sub>)과만 통신한다. CCIE-가능 디바이스들 (312, 및 314<sub>1</sub>-314<sub>n</sub>)은 I2C 모드들에서보다 CCIE 모드에서 상당히 더 높은 데이터 레이트들로 통신할 수도 있다. 예를 들어, CCIE-가능 디바이스들 (312, 및 314<sub>1</sub>-314<sub>n</sub>)은 6.4Mbps, 또는 16.7Mbps의 데이터 레이트들로 통신할 수도 있다.

[0031]

디폴트 기동 (start-up) 모드가 버스 (302)에 대해 구성 또는 정의될 수도 있다. 하나의 예에서, 버스 (302)는 전원 켜짐, 리셋 및/또는 다른 유형의 기동 조건 후에 CCIE 동작 모드에서 동작하도록 구성될 수도 있다. 다른 예에서, 버스 (302)는 초기에 레거시 I2C 모드에서 동작하도록 구성될 수도 있다. CCIE-가능 마스터 디바이스 (312)는, 예컨대 CCIE-가능 슬레이브 디바이스들 (314<sub>1</sub>-314<sub>n</sub>)에 대한 액세스 (access)가 소망될 때 송신되는 I2C 일반 콜 (call)을 통해 버스 (302)의 동작 모드가 I2C 모드로부터 CCIE 모드로 스위칭하게 할 수도 있다. CCIE-가능 마스터 디바이스 (312)는, 버스 (302) 상에서 I2C 슬레이브 디바이스들 (304<sub>1</sub>-304<sub>m</sub>)을 액세스하기 위해 CCIE "엑시트 (exit)" 프로토콜 및 I2C 일반 콜의 결합을 통해 CCIE 모드로부터 I2C 모드로 스위칭할 수도 있다.

[0032]

#### CCIE 동작들을 위해 적응되는 디바이스의 특정 양태들을 나타내는 예

[0033]

도 4는 CCIE 버스 (430)와 같은 통신 버스를 채용할 수도 있는 장치 (400)의 특정 양태들을 나타내는 블록 모식도이다. 장치 (400)는 무선 모바일 디바이스, 모바일 휴대폰, 모바일 컴퓨팅 시스템, 무선 휴대폰, 노트북 컴퓨터, 태블릿 컴퓨팅 디바이스, 미디어 플레이어, 게이밍 디바이스 등 중 하나 이상에서 구현될 수도 있다. 장치 (400)는 CCIE 버스 (430)를 이용하여 통신하는 다수의 디바이스들 (402, 420, 및/또는 422a-422n)을 포함할 수도 있다. CCIE 버스 (430)는, CCIE 버스 (430)에 의해 지원되는 개선된 특징들을 위해 구성되는 디바이스들에 대해 종래의 CCI 버스의 성능들을 확장할 수 있다. 예를 들어, CCIE 버스 (430)는 CCI 버스보다 더 높은 비트 레이트를 지원할 수도 있다. 본 명세서에서 개시된 특정 양태들에 따르면, CCIE 버스 (430)의 일부 버전들 (versions)은 16.7Mbps 이상의 비트 레이트들을 지원하도록 구성 또는 적응될 수도 있고, CCIE 버스의 일부 버전들은 적어도 초당 23 메가비트들의 데이터 레이트들을 지원하도록 구성 또는 적응될 수도 있다.

[0034]

도 4에서 도시된 예에서, 이미징 (imaging) 디바이스 (402)는 CCIE 버스 (430) 상에서 슬레이브 디바이스로서 동작하도록 구성된다. 이미징 디바이스 (402)는 예를 들어 이미지 센서를 관리하는 센서 제어 기능부 (404)를 제공한다. 또한, 이미징 디바이스 (402)는 구성 레지스터들 (configuration registers) (406) 및/또는 다른 스토리지 (storage) 디바이스 (402), 프로세싱 회로 및/또는 제어 로직 (412), 트랜시버 (410) 및 라인 드라이버들/수신기들 (414a 및 414b)을 포함할 수도 있다. 프로세싱 회로 및/또는 제어 로직 (412)은 상태 머신, 시퀀서, 신호 프로세서 또는 범용 프로세서와 같은 프로세서를 포함할 수도 있다. 트랜시버 (410)는, 타이밍, 로직 및 스토리지 회로들 및/또는 디바이스들을 포함하는, 수신기 (410a), 송신기 (410c) 및 소정의 공통 회로들 (410b)을 포함할 수도 있다. 일부 경우들에서, 트랜시버 (410)는 인코더들 및 디코더들, 클럭 및 데이터 복원 회로들 등을 포함할 수도 있다.

[0035]

송신 클럭 (TXCLK) 신호 (428)가 송신기 (410c)에 제공될 수도 있고, 여기서, TXCLK 신호 (428)는 CCIE 통신 모드를 위한 데이터 송신 레이트들을 결정하기 위해 사용될 수도 있다. SDA 선 (418) 및 SCL 선 (416)이 송신된 데이터를 인코딩하기 위해 사용될 때, TXCLK 신호 (428)는 CCIE 버스 (430) 상에서 송신되는 심볼들의 시퀀스들 내에 임베딩될 (embedded) 수도 있다. 하나의 예에서, TXCLK 신호 (428)는 천이 클럭 트랜스코딩을 이용하여 임베딩될 수도 있고, 이에 의해, 물리적 링크 (430)를 통해 송신될 데이터는, 적어도 하나의 선 (416 및/또는 418)의 상태의 변화가 CCIE 버스 (430) 상에서 송신되는 연속적인 심볼들의 각 쌍 사이에서 발생하도록 트랜스코딩된다.

[0036]

도 5는 본 명세서에서 개시된 특정 양태들에 따라 구성된 송신기 (500) 및 수신기 (520)의 일 예를 나타내는 블록도이다. CCIE 동작들에 대해, 송신기 (500)는 데이터 (510)를, SCL (416) 및 SDA (418) 신호 선들 상에서 송신되는 심볼들로서 인코딩되는 3진 (베이스-3) 천이 넘버들로 트랜스코딩할 수도 있다. 묘사된 예

에서, 입력 데이터 (510) 의 각 데이터 엘리먼트 (또한 데이터 워드로서도 지칭됨) 는 19 또는 20 비트들을 가질 수도 있다. 컨버터 및/또는 트랜스코더 (502) 는 입력 데이터 (510) 를 수신할 수도 있고, 각 데이터 엘리먼트에 대해 3진 천이 넘버를 생성할 수도 있다. 각 3진 천이 넘버는 12 개의 3진 디지트들의 시퀀스 (512) 로서 제공될 수도 있고, 각 3진 디지트는 2 개의 비트들에 의해 표현된다. 인코더 (504) 는 12 3진 디지트들의 시퀀스 (512) 를 수신하고, 라인 드라이버들 (line drivers) (506) 을 통해 송신되는 2-비트 심볼들 (514) 의 스트림을 생성한다. 묘사된 예에서, 라인 드라이버들 (506) 은 오픈-드레인 출력 트랜지스터들 (508) 을 포함한다. 하지만, 다른 예들에서, 라인 드라이버들 (506) 은 푸시-풀 (push-pull) 드라이버들을 이용하여 SCL (416) 및 SDA (418) 신호 선들을 구동할 수도 있다. 인코더 (504) 에 의해 생성되는 2-비트 심볼들 (514) 의 출력 스트림은, 연속적인 심볼들의 어느 쌍도 2 개의 동일한 심볼들을 포함하지 않는 것을 보장함으로써 연속적인 심볼들 (514) 사이에 SCL (416) 및 SDA (418) 신호 선들의 적어도 하나의 상태에서의 천이를 갖는다. 적어도 하나의 선 (416 및/또는 418) 에서의 상태의 천이의 이용가능성은, 수신 회로 (520) 가 심볼들의 스트림 (536) 의 수신된 버전으로부터 클럭 정보를 추출하고 데이터 심볼들의 스트림 (536) 으로부터 수신 클럭 (538) 을 도출하는 것을 허용한다.

[0037] CCIe 시스템에서, 수신기 (520) 는 클럭 및 데이터 복원 (clock and data recovery; CDR) 회로 (528) 를 포함하거나 그것과 협동할 수도 있다. 수신기 (520) 는 CDR 회로 (528) 에 로 (raw) 2-비트 심볼들 (536) 의 스트림을 제공하는 인터페이스 회로들 (526) 을 포함할 수도 있다. CDR 회로 (528) 는 로 심볼들 (536) 로부터 수신 클럭 (538) 을 추출하고, 2-비트 심볼들의 스트림 (534) 및 수신 클럭 (538) 을 수신기 (520) 의 다른 회로들 (524 및 522) 에 제공한다. 몇몇 예들에서, CDR 회로 (528) 는 다수의 클럭들 (538) 을 생성할 수도 있다. 하나의 예에서, CDR 회로 (528) 는 SCL 신호 선 (416) 상에서 및/또는 SDA 신호 선 (418) 상에서 천이들을 검출하고 이러한 검출 시에 수신 클럭 (538) 의 상태를 토글링하는 로직을 포함한다. CDR 회로 (528) 는, 동일한 심볼 경계에서 SCL 신호 선 (416) 및 SDA 신호 선 (418) 상에서의 천이들이 서로에 대해 지연될 때, 수신 클럭 (538) 의 상태의 다중 토글들 (toggles) 을 배제하기 위해, 원-샷들, 지연 회로들 또는 다른 이러한 엘리먼트들과 같은 시간-감지 회로를 포함할 수도 있다. 디코더 (524) 는 심볼들의 스트림 (534) 을 12 개의 3진 디지트들의 시퀀스들 (532) 로 디코딩하기 위해 수신 클럭 (538) 을 이용할 수도 있고, 각 시퀀스 (532) 는 천이 넘버를 나타낸다. 12-디지트 천이 넘버 (532) 의 각 디지트는 2-비트 3진 디지트로서 표현될 수도 있다. 트랜스코더 및/또는 컨버터 (522) 는 그 다음, 12 개의 3진 디지트들의 각 시퀀스 (532) 을 19-비트 또는 20-비트 출력 데이터 엘리먼트들 (530) 로 변환할 수도 있다.

[0038] 특정 양태들에 따르면, 천이 넘버를 나타내는 입력 2진 데이터 (510) 와 3진 디지트들의 시퀀스 (512) 사이의 및/또는 천이 넘버들 (532) 과 출력 데이터 비트들 (530) 사이의 변환들은 컨버터들 (502 및 522) 에 의해 수행된다. 하나의 예에서, 송신기 (500) 에서의 데이터 비트들 (510) 로부터 천이 넘버들로의 그 다음에 수신기 (520) 에서의 천이 넘버들로부터 데이터 비트들 (530) 로의 변환은 2-선 인터페이스 (430) 에 대해 12 개의 천이 심볼들을 수반한다. 셋트 또는 시퀀스  $\{T_{11}, T_{10}, \dots, T_2, T_1, T_0\}$  에서 각 천이 넘버  $T$  에 대한 결과적인  $r$  개의 가능한 심볼 천이 상태들은 12 개의 천이 넘버들에 대해 총  $r^{12}$  개의 상이한 상태들을 제공한다. 2-선 버스에 대해, 각 시그널링 상태로부터 이용가능한 천이 상태들의 수  $r = 2^2 - 1$  이다. 결과적으로, 천이들의 시퀀스  $\{T_{11}, T_{10}, \dots, T_2, T_1, T_0\}$  는  $(2^2 - 1)^{12} = 3^{12} = 531441$  의 상이한 상태들을 갖는 데이터를 인코딩할 수 있다. 이 후자의 예에서, 12-디지트 3진수  $\{T_{11}, T_{10}, \dots, T_2, T_1, T_0\}$  에서의 각 천이  $T_i$  는  $\{0, 1, 2\}$  로부터 선택된다.

[0039] 예를 들어,  $\{T_{11}, T_{10}, \dots, T_2, T_1, T_0\} = \{2, 1, 0, 0, 1, 1, 0, 1, 0, 1, 2, 1\}$  에 대해, 12-천이 시퀀스들을 나타내는 3진수는:

[0040] 2100\_1101\_01213 (3진수)

$$= 2 \times 3^{11} + 1 \times 3^{10} + 0 \times 3^9 + 0 \times 3^8$$

$$+ 1 \times 3^7 + 1 \times 3^6 + 0 \times 3^5 + 1 \times 3^4$$

$$+ 0 \times 3^3 + 1 \times 3^2 + 2 \times 3^1 + 1 \times 3^0$$

$$= 416356 (0x65A64) 이다.$$

[0045] 이러한 방식으로, 천이 넘버의 12 개의 3진 디지트들은 20-비트 데이터 출력 (530) 으로 변환될 수도 있다.

[0046] 도 5 에서 도시된 2-선 시스템의 예에서, 12 심볼 천이 넘버들은 n-선 시스템 및 m 심볼 천이 넘버들로서 일반화될 수도 있다. 셋트 또는 시퀀스  $\{T_{m-1}, \dots, T_1, T_0\}$  에서 각각의 천이 넘버  $T$  에 대해  $r$  개의 가능한 심볼 천이 상태들이 존재할 때, m 천이 시퀀스는  $r^m$  개의 상이한 상태들을 인코딩할 수 있고, 여기서,  $r = 2^n - 1$  이다. 결과적으로, 시퀀스  $\{T_{m-1}, \dots, T_1, T_0\}$  는  $(2^n - 1)^m$  개까지의 상이한 상태들을 갖는 데이터를 인코딩 할 수도 있다.

[0047] 하나의 예에서, 2-선, 12-심볼 인터페이스에서 심볼 천이 넘버 (532) 를 나타내는 3진수는 다음과 같이 2진수 출력 데이터 비트들 (bits) (530) 로 변환될 수 있다:

$$\text{Bits} = T_{11} \times 3^{11} + T_{10} \times 3^{10} + T_9 \times 3^9 + T_8 \times 3^8 + T_7 \times 3^7 + T_6 \times 3^6 \\ + T_5 \times 3^5 + T_4 \times 3^4 + T_3 \times 3^3 + T_2 \times 3^2 + T_1 \times 3 + T_0.$$

[0048] [0049] 송신기 (500) 에서, 2-선, 12-심볼 인터페이스에서 SCL 선 (416) 및 SDA 선 (418) 상에서의 송신을 위한 심볼들 (514) 로서 인코딩될 수도 있는 3진수 (512) 로 데이터 비트들 (510) 을 변환하는 알고리즘. 이 알고리즘은 내림차순으로 천이 넘버 ( $T_i$ ) 값들을 그들의 대응하는 나머지 ( $M_i$ ) 로 반복적으로 계산할 수도 있다. 즉, 다음과 같이 각 디지트는 상위 디지트 계산에서 사용된 모듈로 (modulo) 연산의 나머지를 디지트 넘버의 승수 (power) 로 나누고, 소수점 수들은 폐기함으로써 계산될 수 있다:

$$\begin{aligned} T_{11} &= \text{Bits} / 3^{11}, & M_{11} &= \text{Bits} \% 3^{11}; \\ T_{10} &= M_{11} / 3^{10}, & M_{10} &= M_{11} \% 3^{10}; \\ T_9 &= M_{10} / 3^9, & M_9 &= M_{10} \% 3^9; \\ T_8 &= M_9 / 3^8, & M_8 &= M_9 \% 3^8; \\ T_7 &= M_8 / 3^7, & M_7 &= M_8 \% 3^7; \\ T_6 &= M_7 / 3^6, & M_6 &= M_7 \% 3^6; \\ T_5 &= M_6 / 3^5, & M_5 &= M_6 \% 3^5; \\ T_4 &= M_5 / 3^4, & M_4 &= M_5 \% 3^4; \\ T_3 &= M_4 / 3^3, & M_3 &= M_4 \% 3^3; \\ T_2 &= M_3 / 3^2, & M_2 &= M_3 \% 3^2; \\ T_1 &= M_2 / 3, & M_1 &= M_2 \% 3; \\ T_0 &= M_1. \end{aligned}$$

[0051] 후자의 알고리즘은 다음으로부터 합성될 수도 있다:

$$\begin{aligned}

T_{11} &= (\text{Bits} \geq 3^{11} \times 2) ? 2 : (\text{Bits} \geq 3^{11}) ? 1 : 0, & M_{11} &= \text{Bits} - T_{11} \times 3^{11}; \\

T_{10} &= (M_{11} \geq 3^{10} \times 2) ? 2 : (M_{11} \geq 3^{10}) ? 1 : 0, & M_{10} &= M_{11} - T_{10} \times 3^{10}; \\

T_9 &= (M_{10} \geq 3^9 \times 2) ? 2 : (M_{10} \geq 3^9) ? 1 : 0, & M_9 &= M_{10} - T_9 \times 3^9; \\

T_8 &= (M_9 \geq 3^8 \times 2) ? 2 : (M_9 \geq 3^8) ? 1 : 0, & M_8 &= M_9 - T_8 \times 3^8; \\

T_7 &= (M_8 \geq 3^7 \times 2) ? 2 : (M_8 \geq 3^7) ? 1 : 0, & M_7 &= M_8 - T_7 \times 3^7; \\

T_6 &= (M_7 \geq 3^6 \times 2) ? 2 : (M_7 \geq 3^6) ? 1 : 0, & M_6 &= M_7 - T_6 \times 3^6; \\

T_5 &= (M_6 \geq 3^5 \times 2) ? 2 : (M_6 \geq 3^5) ? 1 : 0, & M_5 &= M_6 - T_5 \times 3^5; \\

T_4 &= (M_5 \geq 3^4 \times 2) ? 2 : (M_5 \geq 3^4) ? 1 : 0, & M_4 &= M_5 - T_4 \times 3^4; \\

T_3 &= (M_4 \geq 3^3 \times 2) ? 2 : (M_4 \geq 3^3) ? 1 : 0, & M_3 &= M_4 - T_3 \times 3^3; \\

T_2 &= (M_3 \geq 3^2 \times 2) ? 2 : (M_3 \geq 3^2) ? 1 : 0, & M_2 &= M_3 - T_2 \times 3^2; \\

T_1 &= (M_2 \geq 3 \times 2) ? 2 : (M_2 \geq 3) ? 1 : 0, & M_1 &= M_2 - T_1 \times 3; \\

T_0 &= M_1.

\end{aligned}$$

[0052]

도 6 은 심볼들의 스트림에서의 최하위 심볼이 먼저 송신될 때 2진 입력 데이터 비트들 (510) 을 3진 천이 넘버들 (512) 로 변환하기 위한 예시적인 로직 (620 및 640) 을 나타낸다. 로직 (620, 640) 은 컨버터 (502)에서 구현될 수도 있다. 단순화된 블록도 (600) 로 나타낸 바와 같이, 컨버터 (520) 에 의해 생성된 각각의 3진 천이 넘버 (512) 는 입력 데이터 비트들 (510) 에서의 다수의 비트들로부터 도출될 수도 있고, 각 3진 천이 넘버 (512) 는 12 디지트들 ( $T_0, T_1 \dots T_{11}$ ) (602) 을 포함할 수도 있다. 3진수들 (512) 은 그 후에 수신 디바이스 (520) 에 송신되는 심볼들 (514) 로 트랜스코딩된다. 12 디지트 3진 천이 넘버에 대해, 그 수를 나타내는  $T_0, T_1 \dots T_{11}$  에 있어서,  $T_0$  는  $3^0$  디지트를 나타내고 최하위 디지트인 반면,  $T_{11}$  은  $3^{11}$  디지트를 나타내고 최상위 디지트이다. 도 5 와 관련하여 논의된 바와 같이, 이를 3진 천이 넘버들 (512) 를 레이블과 함께 임베딩되고, 수신 디바이스 (520) 에 송신되는 순차적인 심볼들 (514) 로 인코딩된다. 로직 다이어그램 (620) 및 로직 회로 (640) 는 입력 데이터 비트들 (510) 을 "최하위 심볼 우선 (least significant symbol first)" 3진 천이 넘버들 (512) 의 스트림으로 변환한다.

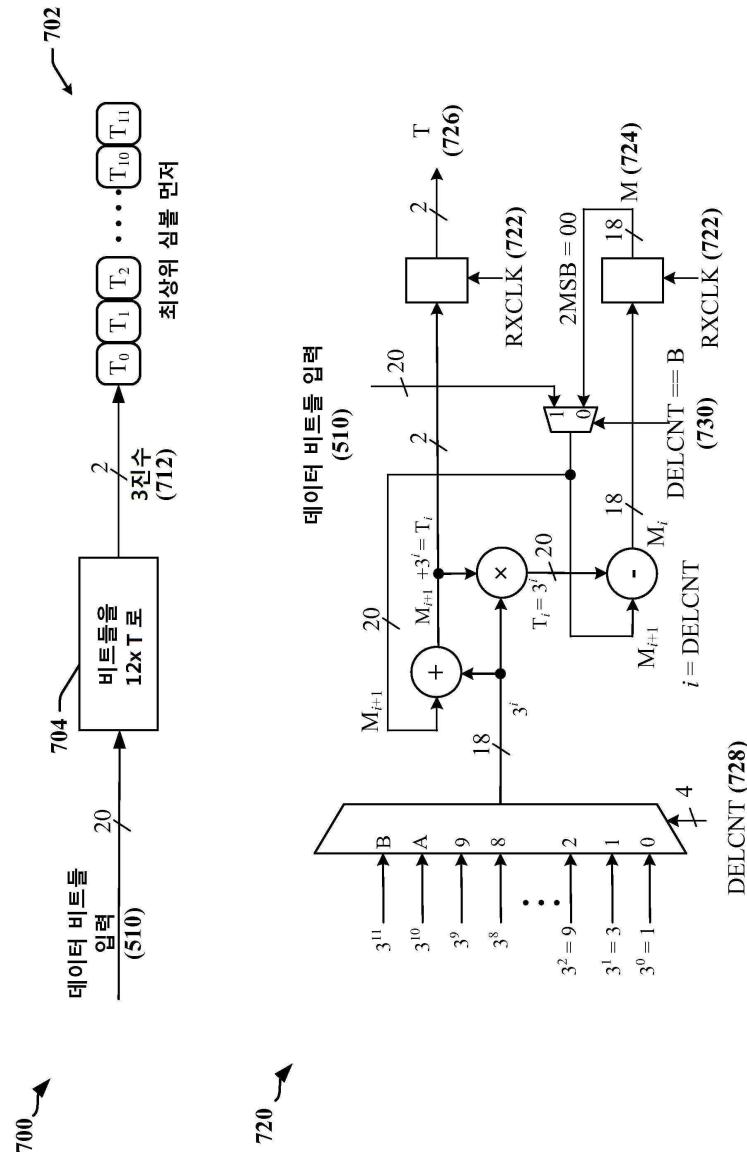

도 7 은, 심볼들의 스트림에서 최상위 심볼이 먼저 송신될 때 2진 입력 데이터 비트드르 (510) 을 3진 천이 넘버들 (712) 로 변환하기 위한 로직 (720) 을 나타낸다. 로직 (720) 은 컨버터 (704) (도 5 의 컨버터 (502) 와 비교) 에서 구현될 수도 있다. 단순화된 블록도 (700) 로 나타낸 바와 같이, 컨버터 (704) 에 의해 생성된 각각의 3진 천이 넘버 (712) 는 입력 데이터 비트들 (510) 에서의 다수의 비트들로부터 도출될 수도 있고, 각 3진 천이 넘버 (712) 는 12 디지트들 ( $T_0, T_1 \dots T_{11}$ ) (702) 을 포함할 수도 있으며, 이에 의해,  $T_0$  는  $3^0$  디지트를 나타내고 최하위 디지트인 반면,  $T_{11}$  은  $3^{11}$  디지트를 나타내고 최상위 디지트이다. 3진수들 (712) 은 그 후에 수신 디바이스에 송신되는 심볼들로 트랜스코딩된다.

[0055] 이 예에서, 변환은  $T_{11}$  로 시작한다. 도 6 은  $T_0, T_1, T_2, \dots, T_{11}$  의 순서로 전송되는 12 디지트 3진수 (602) 를 나타내는 반면, 도 7 은 12 디지트 3진수 (702) 가  $T_{11}, T_{10}, T_9, \dots, T_0$  의 순서로 전송되는 일 예에 관한 것이다. 도 6 의 예시적인 로직 (620 및 640) 과 도 7 에서의 회로 (720) 사이에 소정의 차이들이 식별가능하다. 도 6 의 회로 (640) 는 24 개의 플립-플롭들 (flip-flops) 을 포함하고, 멀티플렉서, 20 개의 플립-플롭들, 및 로직 디바이스들을 포함하는 도 7 의 회로 (720) 에 비해 훨씬 복잡하다. 따라서, 최상위 비트가 먼저 전송될 때, 로직 게이트들에서의 감소 때문에, 수반되는 로직 및 회로는 복잡성 면에서 단순화되고 덜 비싸다.

[0056] 언급된 바와 같이, 도 6 의 로직 (620, 640) 은 최하위 심볼이 수신 디바이스에 먼저 송신되기 때문에 최하위 심볼 우선 (least significant symbol first) (LSS 우선) 로직 및 회로를 나타내는 반면, 도 7 의 로직 (720)

은 최상위 심볼이 수신 디바이스에 먼저 송신되는 (MSS 우선) 예를 나타낸다. 본 명세서에서 사용된 바와 같이 "최하위 심볼 (least significant symbol)"은 3진수의 최하위 디지트에 대응하는 트랜스코딩된 심볼을 지칭한다. 예를 들어,  $T_0$  가 순차적인 심볼로 트랜스코딩될 때, 그 심볼은 그것이 최하위 3진 디지트로부터 유래되기 때문에 최하위 심볼이다. 그리고, 심볼-대-천이 넘버 컨버터 (예컨대, 도 5 의 트랜스코더 (524)) 가 그 후에 그 트랜스코딩된 (순차적인) 심볼을 천이 넘버 (532), 즉 하나의 3진 디지트 넘버로 변환할 때, 그 것은 최하위 디지트일 것이다. 유사하게, 본 명세서에서 사용된 바와 같이 "최상위 심볼 (most significant symbol)"은 3진수의 최상위 디지트에 대응하는 트랜스코딩된 심볼을 지칭한다.

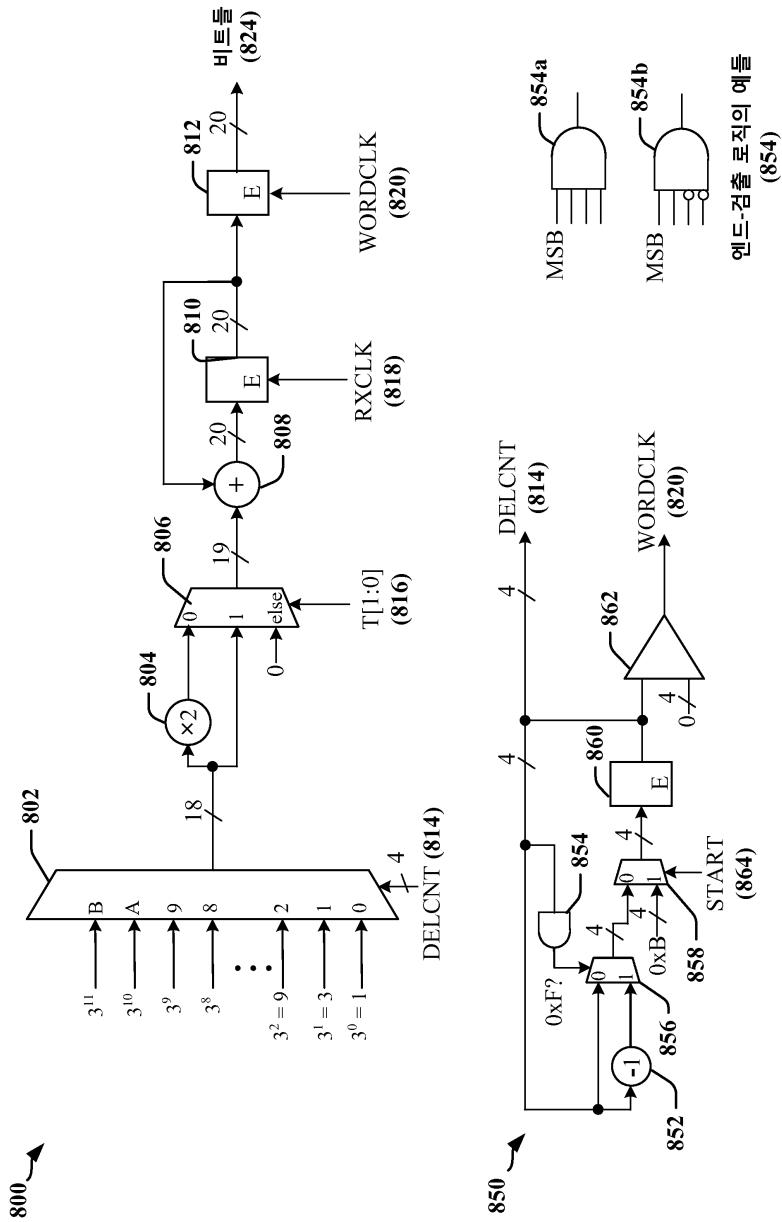

[0057] 도 8 은 12 디지트 3진수를 출력 비트들 (824) 로 변환하기 위해 사용될 수도 있는 회로의 일 예 (800) 를 나타낸다. 본 명세서에서 기술된 바와 같이, 예를 들어 열아홉 (19) 또는 스물 (20) 비트들의 원래 데이터 (510) 는 역순으로 3진 천이 넘버로 변환될 수도 있고, 이에 의해, 최상위 비트는 컨버터에 먼저 공급된다 (도 7 및 설명들 참조). 천이 넘버는 역순으로 다시 순차적인 심볼들로 변환 (즉, 트랜스코딩) 될 수도 있고, 이들 트랜스코딩된 심볼들은 역순으로 버스 상에서 송신된다. 수신 디바이스 (예컨대, 슬레이브 디바이스) 는 역순 송신물을 수신하고, 트랜스코딩된 심볼들을 다시 역으로 3진수로 변환하기 위해 클럭 복원 및 심볼 샘플링을 수행하며, 이 3진수는 그 후에, 3진수를 다시 역으로 20 비트 2진 원래 데이터로 변환하는 회로에 역순으로 공급된다. 회로 (800) 는 로직 디바이스에 대해 단일 출력에 커플링된 12 개의 입력들을 갖는 멀티플렉서 (802) 를 이용할 수도 있다.

[0058] 최상위 심볼 우선 동작 모드와 최하위 심볼 우선 동작 모드 사이의 선택은 카운터 (850) 가 카운트하는 방향에 의해 제어될 수도 있다. 예를 들어, 카운터 (850) 가 16진수 "0xB" (즉, 10진수 "11") 로부터 감분하는 다음 카운터로서 동작하도록 구성 또는 제어될 때, 최상위 심볼들이 먼저 핸들링될 수도 있다. 카운터 (850) 가 16진수 "0x0" (즉, 10진수 "0") 으로부터 증분하는 업 카운터로서 동작하도록 구성 또는 제어되는 경우, 최하위 심볼들이 먼저 핸들링될 수도 있다. 대안적으로 또는 추가적으로, 멀티플렉서 (802) 에 대한 입력들의 순서는, 멀티플렉서 (802) 가 소망된 순서의 출력 3진 천이 넘버들을 생성하기 위해 카운터 (850) 의 출력 (DELCNT) (814) 에 응답하도록 구성될 수도 있다.

[0059] 카운터 (850) 는, CDR 회로 (528) 의 출력 및/또는 시스템 클럭으로부터 도출될 수도 있는 클럭에 동기화된 레지스터 또는 래치 (860) 를 이용하여 DELCNT (814) 출력을 제공할 수도 있다. 레지스터 (860) 는 카운터 (850) 를 초기화하는 제어 신호 (START 신호) (864) 에 기초하여 다음 값 또는 시작 값 사이에서 선택하는 제 1 멀티플렉서 로직 (858) 으로부터 입력된 4-비트 입력을 수신한다. 시작 값은, 컨버터가 최상위 심볼 우선 모드에서 동작할 때 0xB 로 설정될 수도 있고, 컨버터가 컨버터가 최하위 심볼 우선 모드에서 동작할 때 0x0 으로 설정될 수도 있다. 제 1 멀티플렉서 로직 (858) 은, 종단-검출 로직 (854) 에 의한 종단 조건의 검출에 기초하여 DELCNT (814) 출력의 변형된 버전과 DELCNT (814) 출력 사이에서 선택하는 제 2 멀티플렉서 로직 (856) 으로부터 다음 값을 수신한다. 제 2 멀티플렉서 (856) 의 변형된 입력은, 카운트-다운 연산에 대해 감산 로직에 의해 또는 카운트-업 연산에 대해 가산 로직으로부터 제공될 수도 있는, 함수 (852) 의 결과일 수도 있다. 나타낸 바와 같이, 제 2 멀티플렉서 로직 (856) 은 DELCNT (814) 출력이 0x0 으로부터 0xF 로 감분되어 현재 변환의 종단을 나타낸 후에 DELCNT (814) 출력을 반복한다. 카운트 다운 동작 모드에 대해, 종단-검출 로직 (854a) 은 DELCNT (814) 에 대해 0xF 값을 검출하도록 구성될 수도 있고, 종단-검출 로직 (854a) 은, START 신호 (864) 가 시작 값이 로딩되게끔 할 때까지, DELCNT (814) 가 0xF 에서 유지되게 하도록 제 2 멀티플렉서 로직 (856) 출력을 스위칭한다. 카운트 업 동작에 대해, 종단-검출 로직 (854b) 은 DELCNT (814) 에 대해 0xC (10진수 "12" 또는 2진수 "1100") 값을 검출하도록 구성될 수도 있다.

#### CCIE 인코딩의 예

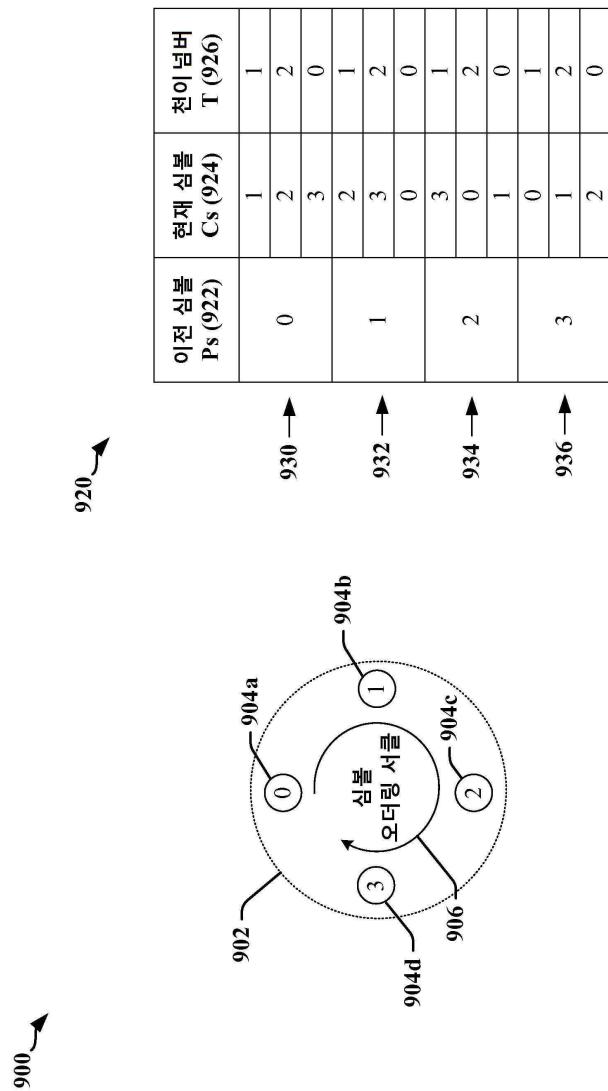

[0060] 도 9 는 3진 천이 넘버들 (512) 로부터 심볼들의 시퀀스 (514) 를 생성하기 위해 트랜스코더 (504) 에 의해 이용될 수도 있는 인코딩 방식 (900) 을 나타내는 도면이고, 여기서, 심볼들의 시퀀스 (514) 는 클럭 정보를 임베딩했고, CCIE 버스 (430) 상에서의 송신을 위한 것이다. 인코딩 방식 (900) 은 또한, CCIE 버스 (930) 상에서 송신되는 심볼들 (534) 로부터 3진 천이 넘버들 (532) 을 추출하기 위해 트랜스코더 (524) 에 의해 이용될 수도 있다. CCIE 인코딩 방식 (900) 에서, CCIE 버스 (430) 의 2 개의 선들은 4 개의 기본 심볼들 S: {0, 1, 2, 3} 의 정의를 허용한다. 심볼들의 시퀀스 (514, 534) 에서의 임의의 2 개의 연속적인 심볼들은 상이한 상태들을 가지고, 심볼 시퀀스들 0,0, 1,1, 2,2 및 3,3 은 연속적인 심볼들의 유효하지 않은 조합들이다. 따라서, 오직 3 개의 유효한 심볼 천이들이 각 심볼 경계에서 이용가능하고, 여기서, 심볼 경계는 송신 클럭에 의해 결정되며, 제 1 심볼 (이전 심볼 Ps) (922) 이 종결되고 제 2 심볼 (현재의 심볼 Cs) (924) 이 시작되

는 포인트를 나타낸다.

[0062] 본 명세서에서 개시된 특정 양태들에 따르면, 3 개의 이용가능한 천이들이 가 Ps 심볼 (922)에 대해 천이 넘버 (T) (926)를 할당받는다. T (926)의 값은 3진수에 의해 표현될 수 있다. 하나의 예에서, 천이 넘버 (926)의 값은 인코딩 방식에 대해 심볼-오더링 서클 (902)을 할당함으로써 결정된다. 심볼-오더링 서클 (902)은 4 개의 가능한 심볼들에 대해 서클 (902) 상의 로케이션들 (904a-904d), 및 로케이션들 (904a-904d) 사이의 회전의 방향 (906)을 할당한다. 나타낸 예에서, 회전의 방향 (906)은 시계방향이다. 천이 넘버 (926)는 유효한 현재 심볼들 (924)과 바로 선행하는 심볼 (922) 사이의 이격을 나타낼 수도 있다. 이 격은, 이전 심볼 (922)로부터 현재의 심볼 Cs (924)에 도달하기 위해 필요한 심볼-오더링 서클 (902) 상에서의 회전의 방향 (906)을 따른 스텝들의 수로서 정의될 수도 있다. 스텝들의 수는 단일 디지트 베이스-3 수로서 표현될 수 있다.

[0063] 심볼들 사이의 3-스텝 차이는  $0_{base-3}$ 로서 표현될 수 있다는 것이 이해될 것이다. 도 9에서의 테이블 (920)은 이러한 접근법을 채용하는 인코딩 방식을 요약한다. 이 예에서, 천이 넘버 T는 다음에 따라 할당될 수도 있다:

$$T_{tmp}[1:0] = 4 + Cs - Ps$$

$$T = T_{tmp}[1:0] == 3 ? 0 : T_{tmp}[1:0]$$

[0066] 반대로, 현재의 순차 심볼 (Cs)은 다음에 따라 할당될 수도 있다:

$$T_{tmp} = T == 0 ? 3 : T$$

$$Cs = Ps + T_{tmp}$$

[0069] 로 심볼들이 변화할 것을 보장하는, 임의의 n (예컨대, n=4, 5, 6, ...)에 대해 순차 심볼의 천이 넘버 테이블에 대한 맵핑 (mapping)을 수행함으로써, n-선 시스템에 대해 유사한 접근법이 이용될 수도 있다. 예를 들어, n-선 시스템의 경우에, 천이 넘버 T는 다음에 따라 할당될 수도 있다:

$$T = (Ps \leq Cs) ? Cs - Ps : 2^n + Cs - Ps.$$

[0071] 반대로, n-선 시스템의 경우에, 현재의 순차 심볼 (Cs)은 다음에 따라 할당될 수도 있다:

$$Cs_{tmp} = Ps + T$$

$$Cs = (Cs_{tmp} < 2^n) ? Cs_{tmp} : Cs_{tmp} - 2^n.$$

[0074] 송신기 (500)에서, 천이 넘버 (926)로서 이용되는, 입력 3진수 및 이전에 생성된 심볼 (922)의 지식이 주어지면, 송신될 현재 심볼 (924)을 찾기 위해 테이블 (920)이 이용될 수도 있다. 수신기 (520)에서, 이전에 수신된 심볼 (922)과 현재 수신되는 심볼 (924) 사이의 천이를 나타내는 천이 넘버 (926)를 결정하기 위해 테이블 (920)이 루업 (lookup)으로서 이용될 수도 있다. 천이 넘버 (926)는 3진수로서 출력될 수도 있다.

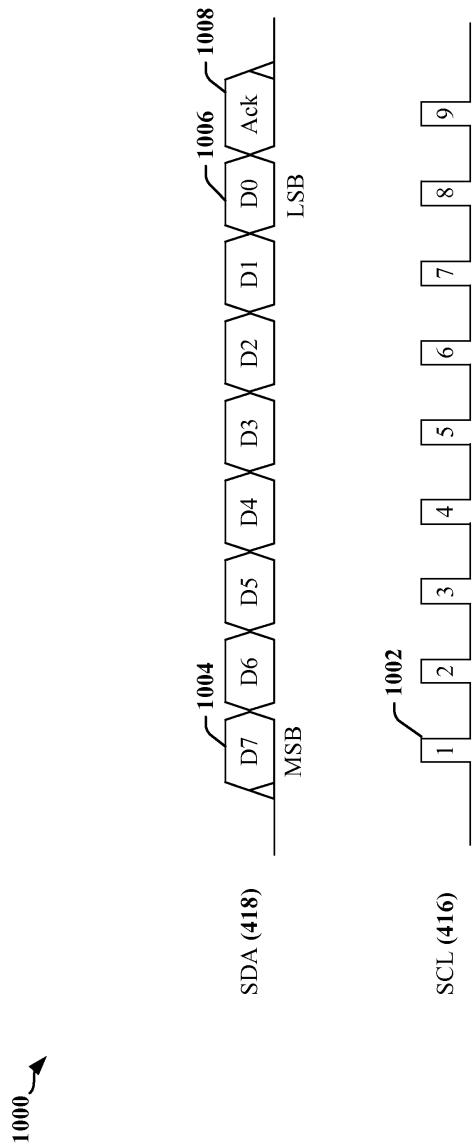

[0075] 도 10 및 도 11은 레거시 I2C 인터페이스의 특정 양태들을 나타낸다. 도 10은 레거시 I2C 프로토콜의 전형적인 I2C 비트 전송 사이클을 나타내는 타이밍도 (1000)이다. SCL 라인 (416)은 마스터 노드로부터 슬레이브 노드로 클럭 신호를 전송하기 위해 전용될 수도 있다. SDA 라인 (418)은 종단에서 수신기에 의해 제공되는 ACK (1008)를 갖는 7-비트 시퀀스들을 전송하도록 기능할 수도 있다. I2C 프로토콜은 판독 또는 기록 동작이 명령되는지 여부를 나타내기 위한 비트를 8-비트 데이터 (바이트) 및 7-비트 어드레스들의 송신을 위해 제공한다. 로우 (low) 시그널링 상태는 성공적인 수신을 나타내는 긍정확인응답 (ACK)을 나타내고 하이 (high) 시그널링 상태는 수신에 대한 실패 또는 수신에서의 에러를 나타내는 부정 확인응답 (NACK)을 나타내도록, 하나의 클럭 주기 (1008)에 대해 SDA 신호 선 (418)을 구동하는 수신기에 의해 데이터 송신들이 확인응답된다. 하나의 데이터 비트 (1004, 1006) 또는 ACK (1008)는 SCL 라인 (416) 상에서 각 클럭 사이클에 대해 송신된다. 하나의 예에서, 데이터 비트 상태 (1004)는, SCL 라인 (416)의 클럭 상태가 하이로직 상태 (1002)일 때, SDA 라인 (418)으로부터 판독될 수도 있다.

[0076] 도 11은 종래의 I2C 버스 상의 SDA와 SCL 신호 선들 사이의 관계를 나타내는 타이밍도이고, 이 도면들은 종래

의 I2C 버스 상의 SDA 와 SCL 신호 선들 (418, 416) 사이의 관계를 나타내는 타이밍도들 (1100 및 1120) 을 포함한다. 제 1 타이밍도 (1100) 는, 종래에 구성된 I2C 버스 상에서 데이터가 전송되는 동안 SDA 신호 선 (418) 과 SCL 신호 선 (416) 사이의 타이밍 관계를 나타낸다. SCL 신호 (416) 는 SDA 신호 선 (418) 에서 데이터를 샘플링하기 위해 사용될 수 있는 일련의 클럭킹 펄스들 (1112) 을 제공한다. SCL 신호 선 (416) 이 데이터 송신 동안 로직 하이 상태에 있을 때, SDA 신호 선 (418) 상의 데이터는 안정 또는 유효하도록 요구되어, SCL 신호 선 (416) 이 하이 상태에 있을 때 SDA 신호 선 (418) 의 상태가 변화하도록 허용되지 않는다.

[0077] 종래의 I2C 프로토콜 구현들을 위한 사양들은 SCL 신호 선 (416) 상에서 각 펄스 (1112) 의 하이 주기 ( $t_{HIGH}$ ) (1110) 에 대해 최소의 지속기간을 정의하고, 여기서, 펄스 (1112) 는 SCL 신호 선 (416) 이 하이 로직 상태에 있는 시간에 대응한다. I2C 사양들은 또한, SDA 신호 선 (418) 의 시그널링 상태가, SDA 신호 선 (418) 이 하이 로직 상태에 있는 펄스 (1112) 전 및 후에 안정적이어야 하는, 셋업 시간 ( $t_{SETUP:DAT}$ ) (1106) 및 유지 시간 ( $t_{HOLD:DAT}$ ) (1108) 에 대한 최소 지속기간들을 정의한다. 셋업 시간 (1106) 은, SDA 신호 선 (418) 상의 시그널링 상태들 사이의 천이 (1116) 후에 SCL 신호 선 (416) 상의 펄스 (1112) 의 상승 에지의 도달까지의 최대 시간 주기를 정의한다. 유지 시간 (1108) 은 SCL 신호 선 (416) 상의 펄스 (1112) 의 하강 에지 후에 SDA 신호 선 (418) 상의 시그널링 상태들 사이의 다음 천이 (1118) 까지의 최소 시간 주기를 정의한다. I2C 사양들은 또한, SDA 신호 선 (418) 상의 시그널링 상태가 변화할 수도 있을 때, SCL 신호 선 (416) 에 대한 로우 주기 ( $t_{LOW}$ ) (1114) 에 대한 최소 지속기간을 정의한다. SDA 신호 선 (418) 상의 데이터는 통상적으로, SCL 신호 선 (416) 이 펄스 (1112) 의 리딩 에지 후에 하이 로직 상태에 있을 때 시간 주기 ( $t_{HIGH}$ ) (1110) 에 대해 캡처된다.

[0078] 도 11 의 제 2 타이밍도 (1120) 는, 종래의 I2C 버스 상에서 데이터 송신들 사이에 SDA 신호 선 (418) 과 SCL 신호 선 (416) 상의 시그널링 상태들을 나타낸다. I2C 프로토콜은, SCL 신호 선 (416) 이 하이 상태에서 유지되는 동안 SDA 신호 선 (418) 이 하이에서 로우로 천이하는, 시작 조건 또는 시퀀스 (1122) 를 정의한다. I2C 프로토콜은, SCL 라인 (416) 이 하이인 동안 SDA 라인이 로우에서 하이 시그널링 상태들로 천이하는, 정지 조건 또는 시퀀스 (1124) 를 정의한다. 본 명세서에서 언급된 바와 같이, SDA 신호 선 (418) 의 시그널링 상태는, 데이터가 송신되고 있을 때 SCL 신호 선 (416) 상에서 송신되는 펄스 (1112) 의 하이 주기 동안 안정적 이게 유지하도록 기대된다. 따라서, SCL 신호 선 (416) 이 로직 하이 상태에 있는 동안 SDA 신호 선 (418) 의 천이는 슬레이브 디바이스들에 의해 시작 조건 (1122) 또는 정지 조건 (1124) 으로서 해석될 수도 있다.

[0079] 시작 조건 (1122) 은 현재 버스 마스터가 데이터가 송신될 것이라는 것을 신호하도록 허용하도록 정의된다. I2C 호환 슬레이브 노드들은 시작 조건 (1112) 의 수신 시에 그들의 버스 로직을 리셋하여야만 한다. SCL 신호 선 (416) 이 하이인 동안 SDA 신호 선 (418) 이 하이로부터 로우로 천이할 때 시작 조건 (1122) 이 발생된다. I2C 버스 마스터는 처음에 시작 조건 (1122) 을 송신하고, 이어서, 데이터를 교환하기를 희망하는 I2C 슬레이브 디바이스의 7-비트 어드레스가 뒤따른다. 판독 또는 기록 동작이 발생하여야 하는지 여부를 나타내는 단일 비트가 어드레스를 뒤따른다. 어드레싱된 I2C 슬레이브 디바이스는, 이용가능한 경우에, ACK 비트로 응답한다. 마스터 및 슬레이브 I2C 디바이스들은 그 다음, 프레임들에서 정보의 바이트들을 교환하고, 이 프레임들에서, 바이트들은 최상위 비트 (most significant bit; MSB) (1004) 가 먼저 송신되고, 최하위 비트 (1006) 가 마지막으로 송신되도록 직렬화된다. 바이트의 송신은 I2C 마스터 디바이스에 의해 정지 조건 (1124) 이 송신될 때 완료된다. 정지 조건 (1124) 은, SCL 신호 선 (416) 이 하이인 동안 SDA 신호 선 (418) 이 로우로부터 하이로 천이할 때 일어난다. I2C 프로토콜은, SDA 신호 선 (418) 의 모든 천이들은 SCL 신호 선 (416) 이 로우인 동안 발생할 것을 요구하고, 예외들은 시작 조건 (1122) 또는 정지 조건 (1124) 으로서 취급될 수도 있다.

[0080] 레거시 I2C 프로토콜들이 이용될 때, 공유된 직렬 버스 (430) 의 2-선들 (416, 418) 로 사이클 당 오직 1 비트 정보만이 전송된다. 즉, 선 당 사이클 당 오직 0.5 비트 정보만이 송신된다. 본 명세서에서 개시된 양태들에 따르면, 송신된 심볼들 내에 클럭을 임베딩하면서 SDA 라인 (418) 및 SCL 라인 (416) 양자 상에서 데이터를 송신함으로써, 향상된 데이터 레이트들 (즉, 선 당 사이클 당 0.5 보다 더 큰 비트 정보) 이 획득될 수도 있다. 클럭 정보는 위상 고정 루프 (phase locked loop; PLL) 를 이용함이 없이 수신기에서 추출될 수도 있다.

[0081] 도 12 는, 버스 (430) 에 연결된 디바이스들 (402, 420, 422a-n) 이 I2C 디바이스를 포함할 때 공유된 버스 (430) 상에서 CCIe 모드에서의 데이터 송신의 일 예를 나타내는 타이밍도 (1200) 이다. 이 예에서, CCIe 디

바이스들은, 신호 선들 (418, 416) 을 구동하기 위해, I2C 디바이스에 의해 사용된 오픈-트레인 드라이버들 보다는, 푸시-풀 드라이버들을 이용한다. 신호 선들 (418, 416) 상에서 송신되는 심볼들의 시퀀스 (1206, 1208) 에서 데이터가 인코딩된다. 대략 초당 14 메가비트들 (Mbps) 의 유효한 데이터 레이트가 심볼 레이트가 20MHz 일 때 CCIe 송신을 위해 달성될 수도 있다. 본 명세서에서 기술된 바와 같이, 19 비트들의 데이터가 12 심볼들의 시퀀스들 (1206, 1208) 로 변환될 수도 있고, 이는, 심볼들의 시퀀스 (1206 또는 1208) 에서의 각 심볼 주기 ( $t_{sym}$ ) (1212) 에 대해 SDA 신호 (418) 및 SCL 신호 (416) 의 상태를 제어한다. 나타낸 바와 같이, 각 심볼 주기 (1212) 는 지속기간이 50ns 일 수도 있다. 하나의 예에서, 19 비트들은 3 비트의 오버헤드를 가지고 16 비트의 데이터를 포함한다.

[0082] 심볼들의 연속적인 시퀀스들 (1206 및 1208) 사이의 타이밍은 I2C 디바이스들의 동작을 지배하는 프로토콜들을 만족하기 위해 요구되는 시간 주기들에 의해 지배될 수도 있다. 하나의 예에서, 시작 조건 (1210) 은 각 송신 (1206, 1208) 에 선행하고 적어도 260ns 의 지속기간 ( $t_{HD}$ ) 을 갖는다. 시작 조건 (1210) 은, SCL 신호 (416) 가 하이를 유지하는 동안 SDA 신호 (418) 가 로우를 유지하도록 "1" 의 심볼 값에 의해 정의될 수도 있다. 시작 조건 (1210) 은, "3" 의 심볼 값에 의해 정의되는 바와 같이 양 신호들 (418 및 416) 이 하이 상태에 있을 때 최소 셋업 주기 ( $t_{SU}$ ) (1216) 를 따를 수도 있다. 최소 셋업 주기 ( $t_{SU}$ ) (1216) 는, 송신 (1206 또는 1208) 이 종결된 후에 시작될 수도 있고, 그 최소 셋업 주기 ( $t_{SU}$ ) (1216) 는 적어도 260ns 동안 유지될 수도 있다. 따라서, 제 1 송신 (1206) 의 시작과 제 2 송신 (1208) 의 시작 사이의 최소 경과 시간 (1214) 은 다음과 같이 계산될 수도 있다:

$$t_{word} = t_{HD} + t_{SU} + 12 \times t_{sym} = (260 + 260 + 12 \times 50) \text{ ns} = 1120 \text{ ns}.$$

[0083] [0084] 셋업과 시작 시간 사이에 신호 하강 시간 ( $t_f$ ) 을 위해 추가적인, 공칭 20ns 가 포함될 수도 있다. 신호 하강 시간은 다음과 같이 계산될 수도 있다:

$$t_f = \left( 20 \times \frac{V_{DD}}{5.5} \right) \text{ ns (min)}, \quad t_f = 120 \text{ ns (max)}.$$

[0085] [0086] 따라서, 19 비트의 데이터는 최소 1140ns 에서 송신될 수도 있고, 16 비트들이 12 심볼들에서 송신되기 때문에, 대략 16.7Mbps 의 대응하는 로 비트 레이트 및 대략 14.04Mbps 의 유효 비트 레이트를 갖는다.

[0087] [0088] 송신들 (1206 및 1208) 사이의 최소 필요 시간은, 오직 CCIe 디바이스들만이 통신에 수반될 때보다 I2C 디바이스들이 버스 (430) 상에 수용될 때 상당히 더 크게 된다. 도 12 는, I2C 디바이스들에 대해 백워드 호환성을 제공하기 위해 I2C 셋업 및 시작 주기들을 부가하는 증가된 시간 (1224) 을 나타내는 타이밍도 (1220) 를 포함한다.

도 13 은 버스 (430) 상의 디바이스들 (402, 420, 422a-n) 이 활성 I2C 디바이스를 포함하지 않을 때 CCIe 버스 (430) 상에서의 데이터 송신을 나타내는 타이밍도 (1300) 이다. 시작 조건들의 지속기간은 감소될 수도 있다. 이 예에서, 푸시-풀 드라이버들이 신호 선들 (418, 416) 을 구동하기 위해 사용된다. 22.86Mbps 의 링크 레이트가 20MHz 심볼 레이트와 함께 달성될 수도 있다. 12 심볼들의 시퀀스들 (1306, 1308) 은 16 비트의 데이터 및 3 비트의 오버헤드를 인코딩한다. 12 심볼들의 시퀀스들 (1306, 1308) 에서의 각 심볼은 각 심볼 주기 ( $t_{sym}$ ) (1310) 에 대해 SDA 신호 (418) 및 SCL 신호 (416) 의 상태를 정의한다. 각 심볼 주기 (1310) 는 20MHz 심볼 클럭에 대해 지속기간이 50ns 일 수도 있다. 2-심볼 시퀀스 {3,1} 는 심볼들 (1306 및 1308) 의 연속적인 시퀀스들 사이의 주기 (1314) 에서 송신된다. 제 1 송신 (1306) 의 시작과 제 2 송신 (1308) 의 시작 사이의 최소 경과 시간 (1312) 은 다음과 같이 계산될 수도 있다:

$$t_{word} = 14 \times t_{sym} = 700 \text{ ns}.$$

[0089] [0090] 푸시-풀 드라이버들을 갖는 CCIe 디바이스들이 사용될 때, 19 비트의 데이터는 700ns 에서 송신될 수도 있어, 16 데이터 비트들이 각 12 심볼 워드 (1306, 1308) 에서 송신되기 때문에, 대략 22.86Mbps 의 유효 비트 레이트로 대략 27.1Mbps 의 로 비트 레이트를 제공한다.

[0091] [0092] 도 14 는 CCIe 인터페이스로서 구성되는 직렬 버스 (430) 와 연관된 특정 양태들을 나타낸다. 타이밍도 (1400) 는 도 5 에서 나타낸 CCIe 송신기 (500) 및 수신기 (520) 와 연관된 시그널링에 대응한다. 타이밍도

(1400) 는, 데이터 송신 동안 SDA 선 (418) 및 SCL 선 (416) 상에서 송신되는 심볼들의 시퀀스 (1408)에 송신 클럭 (TXCLK) (1422)가 임베딩되는 일 예를 나타낸다. 하나의 예에서, 클럭 정보는 천이 클럭 트랜스코딩을 이용하여 심볼들의 시퀀스 (1408)에서 임베딩될 수도 있다. 예를 들어, 물리적 링크 (430)를 통해 송신될 데이터 (510)는 송신된 심볼들 (1408)의 매 심볼 사이클 후에 상태 변화가 발생하도록 트랜스코딩된다.

그 결과로서, TXCLK (1422)는, 예를 들어 심볼  $S_7$  (1408d)과 연관된 심볼 경계들 (1414 및 1416)을 포함하는, 매 심볼 사이클의 심볼 경계들에서 발생하는 심볼 상태들의 변화들에서 임베딩될 수 있다. 수신기 (520)는 송신된 심볼들 (1408)의 시퀀스에서 각 심볼 경계 (1414, 1416)에서 상태 천이로부터 복원된 클럭 정보로부터 수신 클럭 (RXCLK) (1412)을 발생시킬 수 있다. 수신기 (520)는 그 다음, 원래의 데이터 (530)를 획득하기 위해 송신된 심볼들 (1408)의 트랜스코딩을 거꾸로 할 수 있다. 이것은 I2C 버스 (430)의 양 선들이 데이터를 전송하기 위해 이용되도록 허용한다. 추가적으로, 심볼 레이트는, 그것이 더 이상 클럭 및 데이터 신호들 사이에서 (도 11에서 도시된 바와 같이) 셋업 및 유지 시간을 가질 필요가 없기 때문에, 상당히 증가될 수 있다.

[0092] 타이밍도 (1400)에서 묘사된 예에서, 데이터 (510)는 12-심볼 시퀀스들 또는 간격들 (1406)에서 송신되는 심볼들의 스트림 (1408)에서 인코딩될 수도 있다. 각 12-심볼 시퀀스 (1406)는 시작 심볼 (1408a) 및 종결 또는 셋업 심볼 (1408c)을 포함한다. 셋업 심볼 (1408c)과 시작 심볼 (1408a)의 결합은 CCIe 버스 상에서 송신되는 12 심볼들의 시퀀스들 (1406) 사이에 심볼들의 시퀀스 {3, 1}를 형성한다. 본 명세서에서 기술된 바와 같이, 심볼의 시퀀스 (1406)에서의 임의의 2 개의 연속적인 심볼들은, 수신기가 12-심볼 시퀀스 (1406)에서의 심볼 경계들 (1414, 1416)에서 발생하는 심볼 천이들로부터 RXCLK (1412)를 도출할 수도 있도록, 공유된 버스 (430) 상에서 상이한 시그널링 상태들을 생성한다. 본 명세서에서 기술된 바와 같이, 심볼들 사이의 천이들은 천이 넘버들 (1410)로부터 식별될 수도 있다. CCIe 인코더는 12 심볼들의 시퀀스 (1408), 시작 심볼 (1408a), 및 셋업 심볼 (1408b)을 생성할 수도 있다.

[0093] 특정 양태들에 따르면, 직렬 버스 (430)는 동일 시간에서 I2C 디바이스들 및 CCIe 디바이스들 양자를 지원할 수 있다. 본 명세서에서 언급된 바와 같이, I2C 통신 모드들에 대해 SCL 신호 선 (416) 상에서 클럭 신호로서 송신될 클럭 정보는 심볼 천이들 내에 임베딩될 수 있고, 이에 의해, 심볼 정보를 반송하기 위해 이용되도록 하는 SCL 신호 선 (416)의 이용을 허용한다. I2C 프로토콜의 특정 시그널링 특성들은 I2C 및 CCIe 모드들에 대해 공유된 버스 (430)의 작동성을 가능하게 하도록 레버리지될 수도 있다. 예를 들어, I2C 프로토콜은, I2C 호환 가능한 슬레이브 노드들이, SCL 라인 (416)이 하이인 동안 SDA 라인 (418) 상에서 하이에서 로우로의 천이가 발생할 때 일어나는, 시작 조건의 수신 시에 그들의 버스 로직을 리셋하여야만 한다.

#### CCIe 및 I2C 통신을 위해 동작가능한 버스 상에서의 시그널링의 예

[0095] 도 15는 I2C 1-바이트 데이터 기록 동작을 예시하는 타이밍도 (1500)이다. I2C 마스터 노드는, I2C 버스 (430) 상의 어느 슬레이브 노드가 마스터 노드가 액세스하기를 원하는 슬레이브 노드인지를 나타내기 위해 SDA 라인 (418) 상에서 7-비트 슬레이브 ID (1502)를 송신하고, 이어서, 동작이 판독 동작인지 기록 동작인지 여부를 나타내는 판독/기록 비트 (1512)를 송신한다. 판독/기록 비트 (1512)는 기록 동작을 나타내기 위해 로직 0에 있고, 판독 동작을 나타내기 위해 로직 1에 있다. 오직 ID가 7-비트 슬레이브 ID (1502)에 매칭하는 슬레이브 노드만이 기록 (또는 판독) 동작에 응답할 수 있다. I2C 슬레이브 노드가 그 자신의 ID (1502)를 검출하기 위해, 마스터 노드는 SCL 라인 (416) 상에서 8 클럭 펄스들과 함께 SDA 라인 (418) 상에서 적어도 8-비트들을 송신한다. 이러한 행동은 레거시 I2C 슬레이브 노드들이 CCIe 동작들에 반응하는 것을 방지하기 위해 CCIe 동작 모드들에서 데이터를 송신하기 위해 이용된다.

[0096] 도 16은 레거시 I2C 슬레이브 노드 상에서의 시작 조건 (1606, 1608 또는 1610)의 영향을 나타내는 하나의 예 (1600)를 제공하고, 여기서, 시작 조건 (1606, 1608 또는 1612)은, SCL 라인 (416)이 하이 시그널링 상태에 있는 동안 SDA 라인 (418) 상에서 하이에서 로우로의 시그널링 상태 천이에 의해 표시된다. 이 예 (1600)에서, 특정 시작 조건 (1608 또는 1612)이, 완전한 7-비트 슬레이브 ID가 송신되기 전까지 검출될 수도 있다.

결과적인 불완전한 슬레이브 ID (1602, 1604)는 임의의 슬레이브 디바이스에 의해 인식되지 않는다. 동작에서, SCL 라인 (416) 상에서 오직 6 펄스들 (1612)을 전송한 후에 시작 조건 (1608, 1610)을 발생하는 마스터 노드의 효과는, 모든 레거시 I2C 슬레이브 노드들로 하여금, SDA 라인 (418) 상에서 그들 각각의 I2C 슬레이브 ID를 인식하는 가능성이 발생하기 전에 그들의 버스 로직을 리셋하게 하는 것을 포함한다. 다르게 말하면, 2 개의 시작 조건들 (1606, 1608 및/또는 1610) 사이에 전송된 SDA 라인 (418) 상의 6-비트 시퀀스들 (1602, 1604)이 슬레이브 노드들 중 어느 것에 의해서도 유효한 슬레이브 ID로서 디코딩되지 않는다. 그

결과로서, 레거시 I2C 슬레이브 노드들은 불완전한 슬레이브 ID 들 (1602, 1604) 에 응답하도록 기대되지 않는다.

[0097] 도 16 은, CCIe 모드에서의 데이터 통신을 위한 I2C 버스의 SCL 라인 (416) 과 SDA 라인 (418) 의 결합의 이용을 나타내는 일 예 (1620) 를 또한 포함한다. CCIe 심볼은 I2C 송신을 위해 SCL 라인 (416) 상에서 송신되는 클럭 신호 (1614) 의 각 토글에 대응하는 시간에서 송신될 수도 있다. 2 개의 시작 조건들 (1608, 1610) 사이에서 송신되는 클럭 토글들의 넘버는 따라서 각 CCIe 송신을 위해 송신될 수도 있는 심볼들의 넘버를 정의 할 수도 있다. 따라서, 12 심볼 송신들 (1622, 1624) 은, 임의의 슬레이브 노드들로 하여금 I2C 슬레이브 ID 로서 시퀀스를 검출하게 함이 없이, 불완전한 슬레이브 ID (1602, 1604) 와 동등한 6-SCL 펠스 시퀀스 동안 이용가능한 12 시그널링 상태들에서 제공될 수도 있다.

[0098] SCL 라인 (416) 상의 천이와 일치하여 SDA 라인 (418) 상에서 발생하는 천이들은, 이러한 천이들을 시작 조건으로서 해석할 수도 있는, 레거시 I2C 디바이스들에 대해 중요하지 않다. 하지만, 레거시 I2C 디바이스는, I2C 슬레이브 노드의 버스 로직 검출을 리셋하는, 나중에 일어나는 유효한 시작 조건 (1628, 1630) 을 검출한다. I2C 슬레이브 노드들은 또한, CCIe 송신들 (1622, 1624) 동안 일어나는 몇몇 SDA 천이들을 정지 조건으로서 해석할 수도 있지만, CCIe 송신들 (1622, 1624) 내에서의 이러한 정지 조건의 검출은 단지 불완전한 SID (1602, 1604) 의 이른 종결을 야기할 뿐이다. 유사하게, CCIe 송신들 (1622, 1624) 동안 시작 조건의 검출은 슬레이브 노드들의 I2C 기능에 의해 리셋되는 버스 로직의 퍼포먼스 (performance) 를 야기한다.

[0099] 따라서, 레거시 I2C 슬레이브 노드들은, 불완전한 I2C 슬레이브 ID (1602, 1604) 로서 6 SCL 펠스 시퀀스와 연관된 12 심볼 CCIe 송신들 (1622, 1624) 을 무시하도록 기대될 수 있다는 것은 명백하다. 따라서, 시작 조건들 (1606, 1608, 및 1610) 사이에서 이용가능한 12 SCL 토글들 동안, 열두개의 (12) 심볼들은 SCL 라인 (416) 및/또는 SDA 라인 (418) 상에서 송신될 수도 있다.

[0100] I2C 버스의 SCL 라인 (416) 및/또는 SDA 라인 (418) 은, 클럭 신호가 심볼 천이들 내에 임베딩되었을 때 CCIe 모드에서의 데이터 송신을 위해 활용될 수도 있다. 그 결과로서, SDA 라인 (418) 및 SCL 라인 (416) 은, 레거시 I2C 슬레이브 노드 기능성에 영향을 미침이 없이 그리고 CCIe-가능 노드들로부터 레거시 I2C 슬레이브 노드들을 분리하기 위해 브릿지 디바이스를 이용함이 없이, 2 개의 연속적인 시작 조건들 (1626, 1628 및/또는 1630) 사이에서 임의의 무작위의 12 개의 심볼들을 송신하기 위해 이용될 수 있다. I2C 모드에서, 시작 조건은 오직 I2C 마스터에 의해서만 전송되는 반면, CCIe 모드에서 12-심볼 워드를 송신하는 어느 노드에 의해서든지 시작 조건이 전송된다.

[0101] 도 17 은 동일한 2-선 직렬 버스 (430) 를 이용하여 통신할 수 있는 복수의 디바이스들 (1702, 1722 및 1742) 을 포함하는 시스템 (1700) 을 나타내는 블록도이다. 하나의 예에서, 2-선 직렬 버스 (430) 는 CCIe 프로토콜들에 따라 2 개 이상의 디바이스들 (1702, 1722) 사이에서의 통신을 지원하기 위해 하나의 모드에서 이용될 수도 있는 한편, 다른 모드에서, 2-선 직렬 버스 (430) 는 I2C 프로토콜들에 따라 하나 이상의 디바이스들 (1702, 1722, 및/또는 1742) 사이에서의 통신을 지원하기 위해 이용될 수도 있다. 따라서, 2-선 직렬 버스 (430) 상의 시그널링은, 2-선 직렬 버스 (430) 에 커플링된 디바이스들 (1702, 1722 및 1742) 이 송신 모드에 관계없이, 데이터 송신들 동안 신호 타이밍의 결과로서 서로 간섭하지 않는 것을 보장하기 위해 본 명세서에서 개시된 소정의 기술들을 채용할 수도 있다.

[0102] 나타낸 간단한 예에서, I2C 슬레이브 디바이스 (1742) 는 I2C 프로토콜들에 따라 통신 가능할 수도 있고, 버스 마스터 디바이스 (1702) 는 I2C 및 CCIe 프로토콜들에 따라 통신 가능하고, CCIe 슬레이브 디바이스 (1722) 는 CCIe 프로토콜들에 따라, 그리고 어쩌면 CCIe 및 I2C 프로토콜들에 따라 통신 가능하다. 일부 경우들에서, CCIe 디바이스 (1702 및/또는 1722) 는 CCIe 동작 모드를 동안 직렬 버스 상에서 슬레이브 또는 마스터로서 동작할 수도 있다. 2-선 직렬 버스 (430) 는 도 3 에서 도시된 바와 같이 다른 디바이스들에 커플링될 수도 있음이 이해될 것이다. 장치 (1700) 는, 무선 모바일 디바이스, 모바일 텔레폰, 모바일 컴퓨팅 시스템, 무선 텔레폰, 노트북 컴퓨터, 태블릿 컴퓨팅 디바이스, 미디어 플레이어, 게이밍 디바이스, 어플라이언스, 웨어러블 컴퓨팅 디바이스 등에 내장될 수도 있다.

[0103] CCIe 디바이스들 (1702, 1722) 은 시스템 (1700) 에서 하나 이상의 특정 또는 지정된 기능들을 서빙할 수도 있다. 예를 들어, CCIe 디바이스들 (1702, 1722) 은, 디스플레이, 이미지 센서, 카메라, 키보드, 터치스크린 센서, 마우스 또는 다른 포인터, 시청각 코덱, 모뎀, 글로벌 포지셔닝 센서, 모션 검출기, 및 다른 디바이스들과 같은, 사용자 인터페이스의 엘리먼트들 또는 시스템 (1700) 을 채용하는 장치의 컴포넌트들을 제어 또는 포함하는 주변 모듈들 또는 회로들 (1704, 1724) 을 포함할 수도 있다. 또한, CCIe 디바이스들 (1702, 1722)

은, 스토리지 (1706, 1726), 프로세싱 회로 및/또는 제어 로직 (1710, 1730), 트랜시버 (1714, 1734), 및 라인 드라이버들/수신기들 (1716, 1718, 1736, 1738) 을 포함할 수도 있다. 프로세싱 회로 및/또는 제어 로직 (1710, 1730) 은 상태 머신, 시퀀서, 신호 프로세서 또는 범용 프로세서와 같은 프로세서를 포함할 수도 있다.

트랜시버 (1714, 1734) 는, 타이밍, 제어 로직, 일반 로직, CDR, 인코딩, 및 디코딩 회로들 및/또는 디바이스들을 포함하는, 소정의 회로들 및 모듈들과 함께, 수신기 (Rx) 및 송신기 (Tx) 를 포함할 수도 있다. 트랜시버 (1714, 1734) 는 상태 구성을 유지하기 위해 그리고 데이터 버퍼들을 제공하기 위해 이용되는 스토리지를 포함할 수도 있다.

[0104] 클럭 발생 회로 (1712, 1732) 는 트랜시버 (1714, 1734) 내에 또는 그 외부에 제공될 수도 있고, 및/또는, I2C 및 CCIE 통신 모드들에 대한 데이터 송신 레이트들을 결정하기 위해 이용될 수 있는 송신 클럭 (TXCLK) 신호를 제공할 수도 있다. I2C 동작 모드에서 SCL 커넥터 (416) 는 클럭 발생 회로 (1712, 1732) 에 의해 제공된 클럭을 반송할 수도 있는 한편, CCIE 동작 모드들에서 타이밍 정보는 SCL 커넥터 (416) 와 SDA 커넥터 (418) 를 이용하여 송신되는 심볼들의 시퀀스들 내에 임베딩될 수도 있다.

[0105] 스토리지 (1706, 1726) 는 데이터, 구성 정보, 상태, 및/또는 소프트웨어 코드 및/또는 명령들을 저장하기 위해 이용될 수 있는 컴퓨터 관리 가능 매체 또는 프로세서를 포함할 수도 있다. 데이터는, 송신기 회로를 공급하는 버퍼들 및/또는 수신기 회로로부터 인입되는 데이터를 핸들링하는 버퍼들에서 저장될 수도 있다. 소프트웨어 코드 또는 명령들은, 프로세싱 회로 및/또는 제어 로직 (1710, 1730) 이 디바이스 (1702, 1722) 의 다양한 구성 엘리먼트들을 관리 또는 동작시키고 2-선 직렬 버스 (430) 의 현재 동작 모드에 따라 통신 프로토콜들을 핸들링하도록, 프로세싱 회로 및/또는 제어 로직 (1710, 1730) 를 구성 및/또는 그것들에 의해 실행될 수도 있다.

[0106] 마스터 디바이스 (1702) 는, 2-선 직렬 버스 (430) 의 동작 모드들을 제어하는 것, 및 2-선 직렬 버스 (430) 에 커플링된 디바이스들이 다른 디바이스들과 통신하는 것을 허용하기 위해 필요한 것으로서 동작 모드를 사이를 스위칭하는 것을 담당할 수도 있다. 따라서, 마스터 디바이스 (1702) 는 2-선 직렬 버스 (430) 에 대한 액세스를 필요로하거나 요청하는 슬레이브 디바이스 (1722, 1742) 를 식별할 수 있는 하나 이상의 프로토콜들 (1708) 을 구현할 수도 있다. 마스터 디바이스 (1702) 는, I2C 슬레이브 (1742) 가 어드레싱되어야 할 때 I2C-모드 통신 트랜잭션을 개시할 수도 있고, CCIE 슬레이브 (1722) 가 어드레싱되어야 할 때 CCIE-모드 통신 트랜잭션을 개시할 수도 있다. 일부 상황들에서, 2 개 이상의 디바이스들이 동일한 트랜잭션에서 어드레싱 될 수도 있고, 마스터 디바이스 (1702) 는 이러한 트랜잭션을 위해 통신의 모드를 결정할 수도 있다.

[0107] 도 18 은 I2C 및 CCIE 동작 모드들 양자를 위해 구성된 버스 마스터 (1702) 에 의해 수행되는 모드 제어의 소정의 예들을 나타낸다. 이 예에서, 공유된 직렬 버스 (430) 상의 소정의 일반 타이밍 및 시그널링 동작 양태들이 예시되고, 명령들 또는 콜들의 구조 및 콘텐츠는 본 명세서에서 예시된 개념들에 영향을 미침이 없이 애플리케이션들 사이에서 변화할 수도 있음이 이해될 것이다. 마찬가지로, 본 명세서에서 기술된 특정 양태들에 따라 구성된 시스템들의 작동성은, CDR 교정 송신들 (1810), 엔트리 워드들 (entry words) (1812), 엑시트 워드들 (exit words) (1814) 및/또는 엑시트 시퀀스들 (1816) 등과 같은 송신들의 콘텐츠들 또는 포맷에 의해 제한되거나 의존할 필요는 없다.

[0108] 제 1 타이밍도 (1800) 에서 예시된 바와 같이, 프로토콜은, 공유된 버스 (430) 가 CCIE 와 I2C 모드들 사이에서 스위칭하게끔 하는 절차들 및 시그널링을 정의할 수도 있다.

[0109] 하나의 예에서, 마스터 디바이스 (1702) 는 공유된 직렬 버스 (430) 를 이용하여 CCIE 모드 통신을 확립, 유지 또는 천이하도록 위해 CCIE 모드 엔트리 명령 (1812) 을 송신할 수도 있다. CCIE 모드 엔트리 명령은 I2C 모드에 있는 동안 CCIE-가능 디바이스 (1722) 에 어드레싱될 수도 있고, 어드레싱된 디바이스는 그것의 송신 및 수신 회로 (1734) 를 CCIE 통신을 지원하도록 재구성할 수도 있다. 수반되는 통신 트랜잭션의 타입에 기초하여, CCIE-가능 디바이스 (1722) 는, 공유된 직렬 버스 (430) 상에서 송신되는 심볼들의 시퀀스에서 임베딩된 클럭 정보를 가지면서, 공유된 직렬 버스 (430) 의 양 선들 상에서의 송신을 위해 데이터를 인코딩 또는 디코딩 할 수도 있다. 공유된 직렬 버스 (430) 에 커플링된 I2C 슬레이브 디바이스 (1742) 는 통상적으로 CCIE 트랜잭션을 무시한다. I2C 슬레이브 디바이스는 불완전한 슬레이브 ID 를 감지할 수도 있지만, I2C 시작 조건이 CCIE 송신들 사이에서 공유된 직렬 버스 (430) 상에서 송신될 때 그것의 수신 회로를 리셋할 것이다. 일부 상황들에서, 다른 어드레싱되지 않은 CCIE 디바이스들 (314<sub>1</sub>-314<sub>n</sub>) (도 3 참조) 은 CCIE 통신을 모니터링 할 수도 있다.

[0110] 마스터 디바이스 (1702) 는 공유된 직렬 버스 (430) 상에서의 I2C 모드 통신으로 복귀하기 위해 CCIE 모드 엑시

트 명령 (1814) 을 송신할 수도 있다. 하나의 예에서, 공유된 버스 (430) 는, CCIe 모드에 대한 엔트리 (1812) 가 실행된 후에, CCIe 모드로부터의 엑시트 (1814) 가 실행될 때까지 그리고 그 엑시트가 실행되지 않는 한, CCIe 동작 모드를 유지한다.

[0111] 또 다른 타이밍도 (1802) 는 CCIe 모드로의 진입에 영향을 미치기 위해 이용될 수도 있는 엔트리 시퀀스를 나타내는 일 예를 포함한다. CCIe 모드 엔트리 (1812) 는, 공유된 버스 (430) 가 I2C 모드에서 동작하고 있는 동안 송신되는 일반 콜의 일부로서 달성될 수도 있다. CCIe 모드가 진입된 후에, 적절한 슬레이브 식별자 (SID) (1818) 가 송신되고, 이어서 하나 이상의 CCIe-가능 슬레이브들 (1722) 을 식별하는 어드레스가 뒤따르고, 이어서, 데이터 송신들이 뒤따른다. 어드레스는 멀티-워드 어드레스일 수도 있고, 각각의 어드레스 워드 및 각각의 데이터 워드는, 임의의 I2C 슬레이브 디바이스 (1742) 로 하여금 공유된 직렬 버스 (430) 상에서 비활성으로 유지하게 하도록 하는 I2C 시작 명령에 의해 분리될 수도 있다.

[0112] 유사하게, CCIe 모드 엑시트 (1814) 는, 공유된 버스 (430) 가 CCIe 모드에서 동작하고 있는 동안 송신된 일반 콜의 일부로서 제공된 CCIe 모드 엑시트 시퀀스 (1804) 에 의해 달성될 수도 있다. CCIe 엑시트 명령 (1814) 은 모든 CCIe 디바이스들 (1722, 및/또는 314<sub>1</sub>-314<sub>n</sub>) 로 하여금 I2C 동작 모드로 복귀하게 할 수도 있다. 따라서, CCIe-가능 노드들 (1702, 1722, 및/또는 314<sub>1</sub>-314<sub>n</sub>) 은, I2C 모드로부터 CCIe 모드로 그리고 CCIe 모드로부터 I2C 모드로 각각 스위칭함으로써 엔트리/엑시트 시퀀스들 (1802, 1804) 을 포함하는 일반 콜들에 응답할 수도 있다.

[0113] 도 18 은 또한, CCIe 기록 데이터 시퀀스 또는 프로토콜 (1806), 및 CCIe 판독 데이터 시퀀스 또는 프로토콜 (1808) 의 일 예를 제공한다. CCIe 기록 데이터 프로토콜 (1806) 은, SID 에 의해 식별된 슬레이브 노드/디바이스 (1722, 및/또는 314<sub>1</sub>-314<sub>n</sub>) 에 무작위 수의 어드레스 워드들 및 데이터 워드들을 전송하기 위해 수행될 수도 있다. CCIe 판독 데이터 시퀀스 또는 프로토콜 (1808) 은, SID 에 의해 식별된 슬레이브 노드/디바이스 (1722, 및/또는 314<sub>1</sub>-314<sub>n</sub>) 로부터 1 내지 5 의 데이터 워드들을 판독하기 위해 수행될 수도 있다. 어드레스 워드들의 넘버는 무작위로 정의될 수도 있다.

[0114] 일부 경우들에서, CDR 교정 프로토콜 (1810) 은, 표시된 CCIe 노드 (그 자신의 마스터 노드를 포함) 로 하여금 그것의 CDR 로직을 교정하게 하기 위해 그리고 링크 레이트를 최대화하기 위해 CCIe 마스터 노드에 의해 이용될 수도 있다. 이 목적을 위해, CCIe 마스터 노드는 또한 그 자신의 SID 를 가질 수도 있다. CCIe 워드들은 19-비트 정보를 반송하는 12-심볼들에서 전송될 수도 있다. CDR 교정 프로토콜을 제외하고는, 19-비트들 중 3 개의 최상위 비트들이 제어 정보와 같은 다른 정보에 대해 이용될 수도 있는 한편 19-비트들 중 16 개의 최하위 비트들이 데이터를 반송한다.

[0115] CCIe 인터페이스 (430) 의 데이터 레이트들은 푸시-풀 드라이버들의 선택 및/또는 이용에 의해 향상될 수도 있다. F<sub>m</sub>+ 가능 I2C 버스 (430) 상에서의 CCIe 심볼 타이밍의 하나의 예를 나타내는 도 12 를 다시 참조한다.

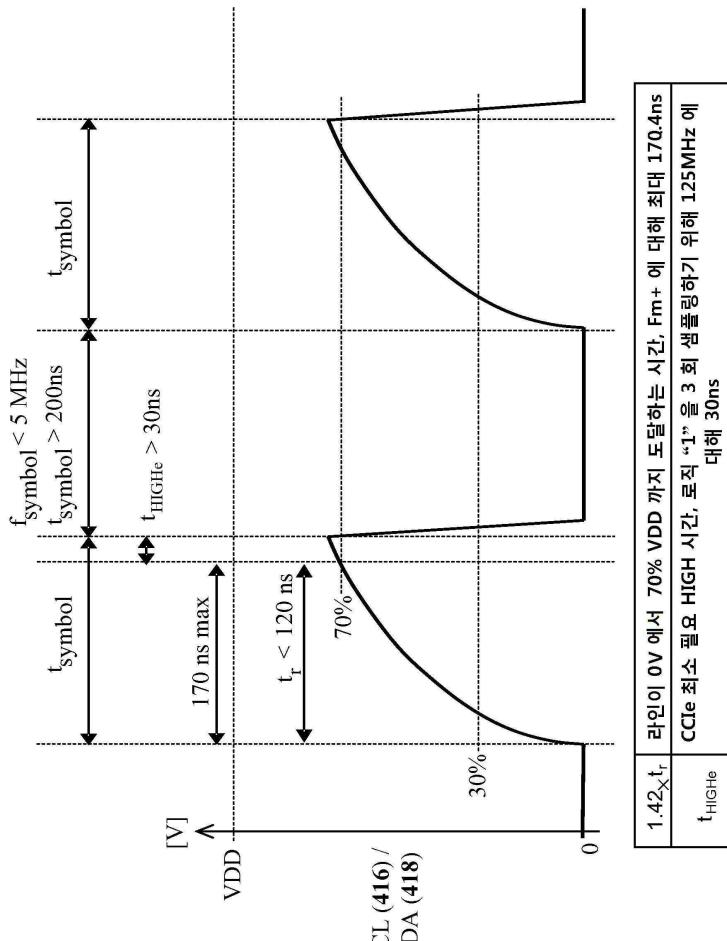

I2C F<sub>m</sub>+ 모드를 위해 사용되는 동일한 물리적 드라이버에 의해 구동되는 CCIe 신호의 타이밍은 드라이버들의 상승 시간에 의해 제한될 수도 있고, 여기서, 상승 시간은 그것이 VDD 레벨의 30% 에서 70% 로 변화하기 위해 라인 전압을 취하는 시간이다. 도 19 는, CCIe 신호가 I2C F<sub>m</sub>+ 모드를 위해 사용되는 동일한 물리적 드라이버에 의해 구동될 때 F<sub>m</sub>+ 가능 I2C 버스 상에서의 CCIe 심볼 타이밍의 하나의 예를 나타내는 도이다. I2C F<sub>m</sub>+ 를 위한 상승 시간은 120ns 이고, 0V 에서 70% 까지의 신호 전압 레벨을 위한 시간은 170ns 로서 계산될 수도 있다. 시그널링이 종종 마이크로컨트롤러 기반 동작들에 의해 헨들링되는 I2C 모드에서 이러한 상승 시간들은 만족스러울 수도 있지만, CCIe 모드에서는, 시그널링 동작들은 통상적으로 하드웨어에서 구현된다. 또한, 마이크로컨트롤러 기반의 또는 소프트웨어 동작되는 I2C 디바이스들은, 특히 SCL 선 (416) 이 로직 로우 상태에 있는 동안, 데이터를 프로세싱하기 위해 많은 사이클들을 필요로 할 수도 있다. 따라서, SCL 의 최소 로우 주기는 F<sub>m</sub>+ 에 대해 1300ns 이상일 수도 있는 한편, I2C 프로토콜들에 의해 600ns 의 최소 하이 주기가 명시될 수도 있다.

[0116] 본 명세서에서 개시된 특정 양태들에 따르면, CCIe 모드 디바이스들은 각 라인 (416, 418) 상의 로직 1 또는 로직 0 의 지속기간들의 차이를 또는 지속기간들의 평균에 집착하지 않을 수도 있다. CCIe 통신은 오직, 수신기가 하드웨어 기술들을 이용하여 로직 1 및 0 을 정확히 디코딩할 수 있는 것만을 요구하고, CCIe 는 더 이상 수개의 액션들을 수행하기 위해 긴 하이 또는 로우 주기들을 필요로 하지 않는다. 따라서, CCIe 시스템은 8ns 주기를 생성하는 125MHz 이상의 클럭을 이용할 수도 있다. 수신기가 비동기 입력 값들을 정확하게 검출하도록 하기 위해, 수신기는 적어도 3 번 동일한 값을 샘플링할 수도 있다. 하나의 예에서, CCIe 신호의 최

소 하이 주기,  $t_{HIGH}$  는 30ns 로 설정될 수도 있고, 이는 125MHz 클럭과 연관된 최소 요구되는 24ns 를 훨씬 초과한다. 따라서, 170ns + 30ns (= 200ns) 하이 시간의 0-에서-70% 상승 시간은 최소 가능 심볼 시간이고, 결과적인 최대 심볼 레이트는 5MHz 이다.

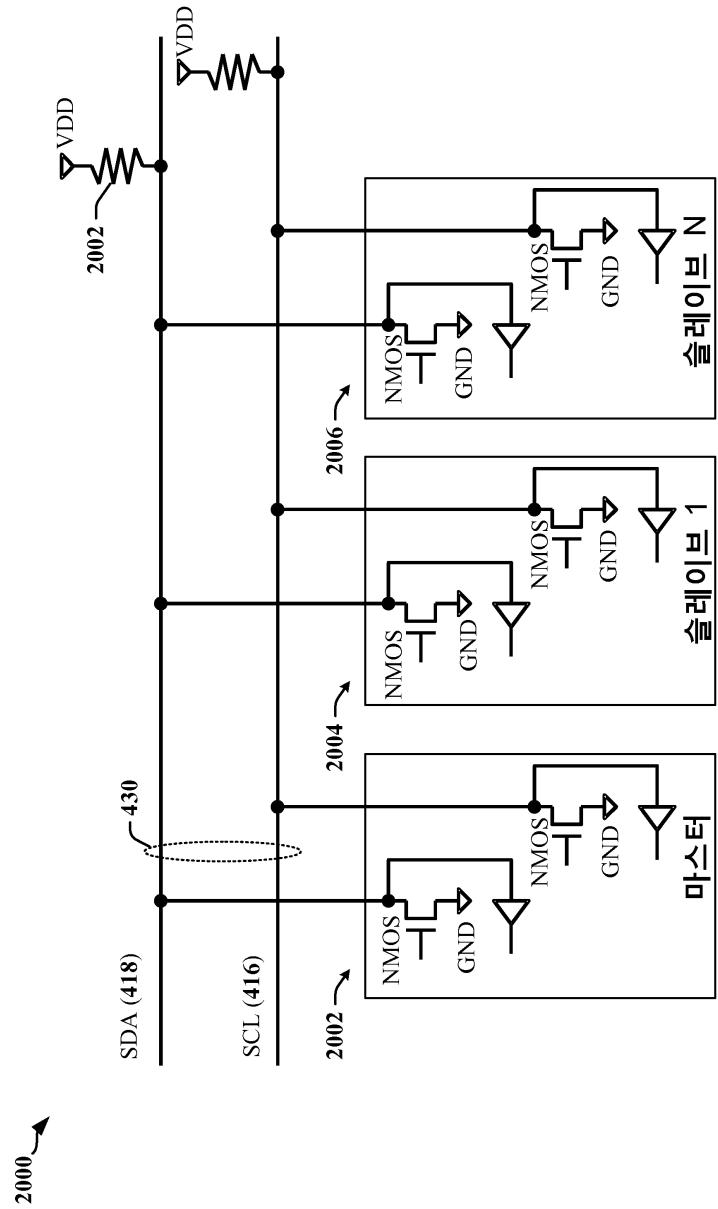

[0117] I2C 호환 버스를 통해 달성가능한 최대 CCIE 링크 레이트는 CCIE 가능 디바이스들에 의해 사용되는 드라이버들의 탑재에 의해 영향을 받을 수도 있다. 하나의 예에서, 오픈-드레인 드라이버들 (2002, 2004, 2006) (도 20 참조) 은 I2C 호환 버스 (430) 에 커플링된 CCIE 디바이스들에 의해 사용될 수도 있다. 이 예에서, 12 심볼들 (1206, 1208) 의 각 심볼은, 그 12 심볼들 (1206, 1208) 이 2400ns 에서 송신될 수도 있도록, 200 나노세컨드 (ns) 의 최소 심볼 시간 (1212) 에서 전송될 수도 있다. 추가적으로, 레거시 I2C 슬레이브 디바이스들이 공유된 버스 (430) 에 커플링될 때 I2C 타이밍 사양들에 부합하는 시작 조건들이 필요하다. 최소 시작 조건 셋업 시간 (1216) 및 최소 시작 조건 유지 시간 (1210) 은 I2C 고속-모드 플러스 (Fm+) 동작에 대해 260ns 의 특정된 최소 지속기간을 갖는다. 또한, SDA 라인 (418) 동작에 대해 허용되는 최대 하강 시간은 I2C Fm+ 에 대해 120ns 이고, 이는, SDA 라인 (418) 이 송신기 (500) 의 트랜지스터 (508) 에 의해 풀 다운될 때에도, 풀-업 저항기 (2002) 의 최대 상승 시간에 대응한다. CCIE 디바이스에 대해, SDA 라인 (418) 에 대한 하강 시간은 I2C 최대 하강 시간보다 상당히 더 빠른 하강 시간을 갖는 것으로 가정될 수도 있다. 예를 들어, CCIE 디바이스는 시작 조건에 대해 SDA 라인 (418) 에 대해 20ns 의 공칭 하강 시간을 제공할 수도 있다. 따라서, CCIE 디바이스는 2940ns 에서 시작 조건으로 CCIE 워드를 송신할 수도 있다. 19 비트들의 정보를 반송하는 CCIE 워드에 대한 로비트 레이트는 다음과 같이 계산될 수도 있다:

$$19 \text{ bits} / 2940 \text{ ns} \approx 6.4 \text{ Mbps.}$$

[0119] 하지만, 각 CCIE 워드는 16-비트들의 데이터 및 3 비트들의 오버헤드를 포함하여, 5.4Mbps ( $\approx 16 \text{ bits} / 2940 \text{ ns}$ ) 로서 계산되는 네트 (net) 데이터 레이트를 제공할 수도 있다.

$$16 \text{ bits} / 2940 \text{ ns} \approx 5.4 \text{ Mbps.}$$

[0121] 다른 예에서, CCIE 디바이스는 12-심볼 CCIE 워드를 송신하기 위해 오픈-드레인 드라이버들 대신에 푸시-풀 드라이버들을 이용할 수도 있다. 향상된 성능이 초래될 수도 있고, 적어도 16.7Mbps 의 링크 레이트가 20MHz 심볼 레이트에서 달성될 수 있다. CCIE 디바이스들은, CCIE 모드에서의 시작 조건들을 포함하는, I2C 동작들 동안 오픈-드레인 드라이버 거동을 모방할 수 있는 CMOS 푸시-풀 드라이버들을 사용할 수도 있다. CCIE 디바이스들은 푸시-풀 드라이버들의 PMOS 트랜지스터들을 선택적으로 디스에이블시킴으로써 오픈-드레인 드라이버 거동을 모방할 수도 있다. 대안적으로 또는 추가적으로, CCIE 디바이스들은 CCIE 모드에서 12-심볼들 동안 푸시-풀 드라이버들의 PMOS 트랜지스터들로부터 하이 신호 상태를 능동적으로 구동할 수도 있다. 그 결과로서, 50ns 심볼 주기 (1212) 가 이용되어, 600ns 에서 12-심볼 CCIE 워드들 (1206, 1208) 의 송신을 가능하게 할 수도 있다.  $t_{SU} + t_{HD} = 540 \text{ ns}$  주기의 시작 조건 지속기간 (셋업 시간 (1216) 및 유지 시간 (1210)) 이 유지된다. 이 구성에서, CCIE 모드 송신들에 대해 1140ns 에서 1 워드를 전송하는 것이 가능하고, 이는 다음과 같이 계산된 로비트 레이트와 동등하다:

$$19 \text{ bits} / 1140 \text{ ns} \approx 16.7 \text{ Mbps.}$$

[0123] 하지만, 각 CCIE 워드는 16-비트들의 데이터 및 3 비트들의 오버헤드를 포함하여, 다음과 같이 계산되는 네트 데이터 레이트를 제공할 수도 있다:

$$16 \text{ bits} / 1140 \text{ ns} \approx 14.0 \text{ Mbps.}$$

[0125] 제 3 예에서, CCIE-가능 디바이스들은, 오직 CCIE-가능 디바이스들이 버스 (430) 에 커플링될 때 모든 송신들에 대해 CMOS 푸시-풀 드라이버들을 사용할 수도 있다. 그 결과로서, 심볼 주기 (1212) 는 대략적으로 50ns 로 단축될 수 있고, 600ns 에서의 12-심볼 CCIE 워드들 (1206, 1208) 의 송신은 600ns 에서 전송될 수 있다. I2C-호환 시작 조건이 요구되기 때문에, 시작 조건 주기는 50ns 심볼 주기 (1212) 와 동등한 지속기간에 대한 셋업 주기 (1216) 및 50ns 심볼 주기 (1212) 와 동등한 지속기간에 대한 유지 주기 (1210) 를 제공하여, 시작 조건을 100ns 의 지속기간으로 단축시킴으로써 구현될 수 있다. 이 예에서, 하나의 19-비트 워드는 700ns 에서 송신될 수 있고, 이는 27.1 Mbps ( $\approx 19 \text{ bits} / 700 \text{ ns}$ ) 의 비트 레이트와 동등하고, 이는 다음과 같이 계산된 로비트 레이트와 동등하다:

[0126] 19 bits / 700 ns  $\approx$  27.1 Mbps.

[0127] 하지만, 각 CCIe 위드는 16-비트들의 데이터 및 3 비트들의 오버헤드를 포함하여, 다음과 같이 계산되는 네트 데이터 레이트를 제공할 수도 있다:

[0128] 16 bits / 700 ns  $\approx$  22.9 Mbps.

#### [0129] 다중 모드들의 통신을 지원하는 시스템의 제 1 예

[0130] 도 3, 도 4, 및 도 17 을 다시 참조하면, 시스템 또는 장치 (300, 1700) 는 다중모드 버스 (302) 에 의해 상호 연결되는 복수의 디바이스들 (304<sub>1</sub>-304<sub>n</sub>, 312, 및 314<sub>1</sub>-314<sub>n</sub>) 을 채용할 수도 있다. 다중모드 버스 (302) 는 제 1 라인 (416) 및 제 2 라인 (418) 을 포함하는 2-선 직렬 버스를 포함할 수도 있다. 제 1 동작 모드는 직렬 버스 (430) 를 통한 데이터 송신들을 위해 제 1 프로토콜을 구현하고, 제 2 동작 모드는 직렬 버스 (430) 를 통한 데이터 송신들을 위해 제 2 프로토콜을 구현한다. 직렬 버스 (430) 는 I2C 및 CCIe 동작 모드들에 서 동작할 수도 있다. 버스는 I2C-호환 버스일 수도 있다. 하나의 예에서, 직렬 버스 (430) 가 I2C 버스로서 동작할 때 제 1 라인 (416) 은 SCL 라인으로서 기능할 수도 있고, 직렬 버스 (430) 가 I2C 버스로서 동작할 때 제 2 라인 (418) 은 SDA 라인 (418) 으로서 기능할 수도 있다.

[0131] 제 1 동작 모드에서, 버스 (302) 에 커플링된 제 1 셋트의 디바이스들 (312 및/또는 304<sub>1</sub>-304<sub>n</sub>) 은 데이터 송신들을 위해 제 1 라인을 이용하고 제 1 클럭 신호를 위해 제 2 라인을 이용하도록 구성될 수도 있고, 제 2 동작 모드에서, 버스에 커플링된 제 2 셋트의 디바이스들 (312 및/또는 314<sub>1</sub>-314<sub>n</sub>) 은 데이터 송신들의 심볼 천이들 내에 제 2 클럭 신호를 임베딩하면서 데이터 송신들을 위해 제 1 라인 및 제 2 라인 양자를 이용하도록 구성될 수도 있다. 제 2 클럭 신호는 제 1 클럭 신호보다 더 큰 주파수를 가질 수도 있다.

[0132] 제 1 셋트의 디바이스들 (312 및/또는 304<sub>1</sub>-304<sub>n</sub>) 및 제 2 셋트의 디바이스들 (312 및/또는 314<sub>1</sub>-314<sub>n</sub>) 은 제 1 동작 모드 및 제 2 동작 모드 양자에서 적어도 제 1 라인을 동시에 모니터링할 수도 있다. 제 1 셋트의 디바이스들 (312 및/또는 304<sub>1</sub>-304<sub>n</sub>) 및 제 2 셋트의 디바이스들 (312 및/또는 314<sub>1</sub>-314<sub>n</sub>) 은 제 1 동작 모드 및 제 2 동작 모드 양자에서 적어도 제 2 라인을 동시에 모니터링할 수도 있다.

[0133] 제 1 동작 모드에서, 제 1 셋트의 디바이스들 (312 및/또는 304<sub>1</sub>-304<sub>n</sub>) 로부터의 마스터 디바이스 (312) 는 버스의 제 1 라인을 통해 제 1 셋트의 디바이스들 (312 및/또는 304<sub>1</sub>-304<sub>n</sub>) 로부터의 슬레이브 디바이스들 (304<sub>1</sub>-304<sub>n</sub>) 에 데이터를 송신할 수도 있다.

[0134] 제 2 동작 모드에서, 제 2 셋트의 디바이스들 (312 및/또는 314<sub>1</sub>-314<sub>n</sub>) 로부터의 마스터 디바이스 (312) 는 버스의 제 1 라인을 통해 제 2 셋트의 디바이스들 (312 및/또는 314<sub>1</sub>-314<sub>n</sub>) 로부터의 슬레이브 디바이스들 (314<sub>1</sub>-314<sub>n</sub>) 에 데이터를 송신할 수도 있다.

[0135] 제 2 동작 모드에서, 제 1 셋트의 슬레이브 디바이스들 (304<sub>1</sub>-304<sub>n</sub>) 은 유효한 슬레이브 노드 어드레스의 검출을 억제하는 리셋 표시자를 제 1 라인 및 제 2 라인을 통해 수신할 수도 있다. 리셋 표시자는 예를 들어 I2C 시작 조건일 수도 있다. 제 2 동작 모드에서, 리셋 표시자가 제 1 라인 및 제 2 라인에서 삽입될 때 데이터 송신들은 주기적으로 인터럽트되고 (interrupted), 이에 의해, 제 1 셋트의 디바이스들 (304<sub>1</sub>-304<sub>n</sub>) 로 하여금 유효한 비트들의 시퀀스를 검출하기 이전에 그들의 버스 로직을 리셋하게 한다.

[0136] 제 1 동작 모드에서, 마스터 노드 (312) 는 제 2 동작 모드로의 스위치 (switch) 를 표시하는 제 1 비트 시퀀스를 제 1 라인을 통해 제 2 셋트의 디바이스들 (314<sub>1</sub>-314<sub>n</sub>) 에 전송할 수도 있다. 마스터 노드 (312) 는 제 1 모드로의 스위치를 표시하는 엑시트 심볼 시퀀스를 버스 (430) 를 통해 제 2 셋트의 디바이스들 (314<sub>1</sub>-314<sub>n</sub>) 에 전송할 수도 있다.

[0137] 제 2 동작 모드는 제 1 동작 모드보다 버스 (430) 를 통한 더 높은 송신 비트 레이트를 가질 수도 있다. 예를 들어, 제 1 동작 모드는 버스 (430) 를 통한 초당 1 메가비트들의 최대 비트 레이트를 지원할 수도 있고, 제 2 동작 모드는 초당 6.4 메가비트들의 최대 비트 레이트를 지원할 수도 있다. 다른 예에서, 제 1 동작 모드는 버스 (430) 를 통한 초당 1 메가비트들의 최대 비트 레이트를 지원할 수도 있고, 제 2 동작 모드는 초

당 16.7 메가비트들의 최대 비트 레이트를 지원할 수도 있다.

[0138] 제 2 셋트의 디바이스들 ( $314_1$ - $314_n$ ) 은 제 1 동작 모드 및 제 2 동작 모드 양자에서 동작 가능할 수도 있다.

[0139] 하나의 예에서, 버스 (430) 는 제 2 셋트의 디바이스들 ( $314_1$ - $314_n$ ) 로부터의 제 1 디바이스를 포함하는 베이스 밴드 프로세서에, 그리고, 제 2 셋트의 디바이스들 ( $314_1$ - $314_n$ ) 로부터의 제 2 디바이스를 포함하는 이미지 센서에 커플링된다. 버스 (430) 는 베이스밴드 프로세서와 이미지 센서 사이의 데이터 신호들을 제어할 수도 있다.

[0140] 일부 경우들에서, 제 2 셋트의 디바이스들 ( $314_1$ - $314_n$ ) 에서의 각 디바이스는, 데이터 비트들의 시퀀스를 복수의  $M$  개의 천이 넘버들로 변환하고, 각 천이 넘버를 순차적인 넘버들의 셋트로부터의 순차적인 넘버 (sequential number) 로 변환하며, 버스를 통해 그 순차적인 넘버를 송신하도록 적응된다.  $M$  개의 천이 넘버들은 3진 디지트들로서 표현될 수도 있다. 순차적인 넘버는 어떤 2 개의 순차적인 넘버들도 동일하지 않는 것을 보장하기 위해 바로 이전의 순차 넘버로부터의 천이에 기초하여 천이 넘버로부터 선택될 수도 있다. 각 천이 넘버는 복수의 천이 넘버들을 순차적인 넘버로 변환함으로써 순차적인 넘버들의 셋트로부터의 순차적인 넘버로 변환될 수도 있다.

#### 다중 모드들의 통신을 지원하는 시스템의 제 2 예

[0142] 도 3, 도 4, 및 도 17 을 계속 참조하면, 시스템 또는 장치 (300, 1700) 는 다중모드 버스 (302) 에 의해 상호 연결되는 복수의 디바이스들 ( $304_1$ - $304_n$ , 312, 및  $314_1$ - $314_n$ ) 을 채용할 수도 있다. 버스 (302) 는 제 1 라인 (418) 및 제 2 라인 (416) 을 갖는 2-선 직렬 버스 (430) 를 포함할 수도 있다. 버스는 I2C-호환 버스 일 수도 있다. 제 1 동작 모드에서, 제 1 셋트의 디바이스들 ( $304_1$ - $304_n$ , 312) 은 데이터 송신들을 위해 제 1 라인 (418) 을 이용하고 제 1 클럭 신호를 위해 제 2 라인 (416) 을 이용할 수도 있는 한편, 버스에 커플링된 제 2 셋트의 디바이스들 (312, 및  $314_1$ - $314_n$ ) 은 제 2 동작 모드에서 데이터 송신들을 위해 제 1 라인 및 제 2 라인 양자를 이용하면서 데이터 송신들의 심볼 천이들 내에 제 2 클럭 신호를 임베딩하도록 구성될 수도 있다.

[0143] 제 1 셋트의 디바이스들 ( $304_1$ - $304_n$ , 312) 및 제 2 셋트의 디바이스들 (312 및  $314_1$ - $314_n$ ) 은 제 1 동작 모드 및 제 2 동작 모드 양자에서 적어도 제 1 라인 (418) 을 동시에 모니터링할 수도 있다. 제 1 셋트의 디바이스들 ( $304_1$ - $304_n$ , 312) 및 제 2 셋트의 디바이스들 (312, 및  $314_1$ - $314_n$ ) 은 제 1 동작 모드 및 제 2 동작 모드 양자에서 적어도 제 2 라인 (416) 을 동시에 모니터링할 수도 있다.

[0144] 하나의 예에서, 제 1 셋트의 디바이스들 ( $304_1$ - $304_n$ , 312) 로부터의 마스터 디바이스 (312) 는 제 1 동작 모드에서 버스 (430) 의 제 1 라인 (418) 을 통해 슬레이브 디바이스들 ( $304_1$ - $304_n$ ) 에 데이터를 송신한다. 다른 예에서, 제 2 셋트의 디바이스들 (312,  $314_1$ - $314_n$ ) 로부터의 마스터 디바이스 (312) 는 제 2 동작 모드에서 버스 (430) 의 제 1 라인을 통해 슬레이브 디바이스들 ( $314_1$ - $314_n$ ) 에 데이터를 송신한다. 제 2 동작 모드는 제 1 동작 모드보다 버스 (430) 를 통한 더 높은 송신 비트 레이트를 가질 수도 있다. 하나의 예에서, 제 1 동작 모드는 버스 (430) 를 통한 초당 1 메가비트들의 최대 비트 레이트를 가질 수도 있고, 제 2 동작 모드는 버스 (430) 를 통한 초당 6.4 메가비트들의 최대 비트 레이트를 가질 수도 있다. 제 2 예에서, 제 1 동작 모드는 버스 (430) 를 통한 초당 1 메가비트들의 최대 비트 레이트를 가질 수도 있고, 제 2 동작 모드는 버스 (430) 를 통한 초당 16.7 메가비트들의 최대 비트 레이트를 가질 수도 있다. 제 2 클럭 신호는 제 1 클럭 신호보다 더 큰 주파수를 가질 수도 있다.

[0145] 제 1 동작 모드는 직렬 버스 (430) 를 통한 데이터 송신들을 위해 제 1 프로토콜을 구현하고, 제 2 동작 모드는 직렬 버스 (430) 를 통한 데이터 송신들을 위해 제 2 프로토콜을 구현한다.

[0146] 제 1 셋트의 디바이스들은 제 2 동작 모드에서 유효한 슬레이브 노드 어드레스의 검출을 억제하는 리셋 표시자를 제 1 라인 (418) 및 제 2 라인 (416) 을 통해 수신할 수도 있다. 제 2 동작 모드에서, 리셋 표시자를 제 1 라인 (418) 및 제 2 라인 (416) 에 삽입함으로써 데이터 송신들은 주기적으로 인터럽트되어, 제 1 셋트의 디바이스들 ( $304_1$ - $304_n$ ) 로 하여금 유효한 비트들의 시퀀스를 검출하기 이전에 그들의 버스 로직을 리셋하게 한다.

[0147] 제 1 동작 모드 동안, 마스터 노드 (312) 는 제 2 동작 모드로의 스위칭이 이루어지는 것을 표시하는 제 1 비트 시퀀스를 제 1 라인을 통해 제 2 셋트의 디바이스들 ( $314_1$ - $314_n$ ) 에 전송할 수도 있다. 제 2 동작 모드 동

안, 마스터 노드 (312) 는 제 1 동작 모드로의 스위칭이 이루어지는 것을 표시하는 엑시트 심볼 시퀀스를 버스 (430) 를 통해 제 2 셋트의 디바이스들 (314<sub>1</sub>-314<sub>n</sub>) 에 전송할 수도 있다.

[0148] 하나의 예에서, 제 2 셋트의 디바이스들 (314<sub>1</sub>-314<sub>n</sub>) 은 제 1 동작 모드 및 제 2 동작 모드 양자에서 동작 가능할 수도 있다.

[0149] 일부 경우들에서, 버스 (430) 는 제 2 셋트의 디바이스들 (314<sub>1</sub>-314<sub>n</sub>) 로부터의 제 1 디바이스를 포함하는 베이스밴드 프로세서에, 그리고, 제 2 셋트의 디바이스들 (314<sub>1</sub>-314<sub>n</sub>) 로부터의 제 2 디바이스를 포함하는 이미지 센서에 커플링된다. 버스 (430) 는 베이스밴드 프로세서 및 이미지 센서 사이의 데이터 신호들을 제어할 수도 있다. 제 2 셋트의 디바이스들 (314<sub>1</sub>-314<sub>n</sub>) 에서의 각 디바이스는, 데이터 비트들의 시퀀스를 복수의 M 개의 천이 넘버들로 변환하고, 각 천이 넘버를 순차적인 넘버들의 셋트로부터의 순차적인 넘버로 변환하며, 버스 (430) 를 통해 그 순차적인 넘버를 송신하도록 적응될 수도 있다. 순차적인 넘버는 어떤 2 개의 순차적인 넘버들도 동일하지 않는 것을 보장하기 위해 바로 이전의 순차 넘버로부터의 천이에 기초하여 천이 넘버로부터 선택될 수도 있다. 각 천이 넘버는 복수의 천이 넘버들을 순차적인 넘버로 변환함으로써 순차적인 넘버들의 셋트로부터의 순차적인 넘버로 변환될 수도 있다.

#### 다중 모드들의 통신을 지원하는 시스템의 제 3 예

[0151] 도 3, 도 4, 및 도 17 을 계속 참조하면, 시스템 또는 장치 (300, 1700) 는 다중모드 버스 (302) 에 의해 상호 연결되는 복수의 디바이스들 (304<sub>1</sub>-304<sub>n</sub>, 312, 및 314<sub>1</sub>-314<sub>n</sub>) 을 채용할 수도 있다. 버스 (302) 는 제 1 라인 (418) 및 제 2 라인 (416) 을 갖는 2-선 직렬 버스 (430) 를 포함할 수도 있다. 버스는 I2C-호환 버스 일 수도 있다. 제 1 동작 모드에서, 제 1 셋트의 디바이스들 (304<sub>1</sub>-304<sub>n</sub>, 312) 은 데이터 송신들을 위해 제 1 라인 (418) 을 이용하고 제 1 클럭 신호를 위해 제 2 라인 (416) 을 이용할 수도 있는 한편, 버스에 커플링된 제 2 셋트의 디바이스들 (312, 및 314<sub>1</sub>-314<sub>n</sub>) 은 제 2 동작 모드에서 데이터 송신들을 위해 제 1 라인 및 제 2 라인 양자를 이용하면서 데이터 송신들의 심볼 천이들 내에 제 2 클럭 신호를 임베딩하도록 구성될 수도 있다.

[0152] 동작에서, 프로세싱 회로는 송신기 및 수신기 회로로 및로부터 데이터를 전송 및 수신하도록 구성될 수도 있고, 송신기 및 수신기 회로는 제 1 라인 (418) 및 제 2 라인 (416) 을 포함하는 버스 (430) 를 통해 통신하도록 구성될 수도 있다.

[0153] 송신기 및 수신기 회로는, 제 1 동작 모드에서, 데이터 송신들을 위해 제 1 라인 (418) 을 이용하고 제 1 클럭 신호를 위해 제 2 라인을 이용하도록 구성될 수도 있고, 제 2 동작 모드에서, 데이터 송신들의 심볼 천이들 내에 제 2 클럭 신호가 임베딩되도록 데이터를 송신하기 위해 제 1 라인 (418) 및 제 2 라인 (416) 양자를 이용하도록 구성될 수도 있다.

[0154] 디바이스는, 버스에 커플링된 다른 디바이스들의 셋트와 공존할 수도 있지만, 제 1 동작 모드 및 제 2 동작 모드 양자 동안 적어도 제 1 라인 (418) 을 항상 모니터링하면서 오직 제 1 모드에서만 동작할 수도 있다. 디바이스는, 버스 (430) 에 커플링된 다른 디바이스들의 셋트와 공존할 수도 있지만, 제 1 동작 모드 및 제 2 동작 모드 양자 동안 적어도 제 2 라인 (416) 을 항상 모니터링하면서 오직 제 1 모드에서만 동작할 수도 있다.

[0155] 디바이스는 제 1 동작 모드에서 버스 (430) 의 제 1 라인 (418) 을 통해 슬레이브 디바이스에 데이터를 송신할 수도 있다. 디바이스는 제 2 동작 모드에서 버스 (430) 의 제 1 라인 (418) 및 제 2 라인 (416) 을 통해 슬레이브 디바이스에 데이터를 송신할 수도 있다. 제 1 동작 모드는 버스 (430) 를 통한 데이터 송신들을 위해 제 1 프로토콜을 구현할 수도 있고, 제 2 동작 모드는 버스 (430) 를 통한 데이터 송신들을 위해 제 2 프로토콜을 구현할 수도 있다.

[0156] 송신기 및 수신기 회로는 제 1 동작 모드에서 동작하는 다른 디바이스들이 유효한 슬레이브 노드 어드레스를 검출하는 것을 억제하기 위해 제 2 동작 모드 동안 제 1 라인 (418) 및 제 2 라인 (416) 을 통해 리셋 표시자를 송신하도록 구성될 수도 있다. 리셋 표시자를 제 1 라인 (418) 및 제 2 라인 (416) 에 삽입함으로써 제 2 동작 모드 동안의 데이터 송신들은 주기적으로 인터럽트되어, 제 1 모드에서 동작하는 다른 디바이스들로 하여금 유효한 비트들의 시퀀스를 검출하기 이전에 그들의 버스 리스를 리셋하게 할 수도 있다.

[0157] 일부 예들에서, 송신기 및 수신기 회로는 제 1 모드 및 제 2 모드 양자에서 동작 가능한 다른 디바이스들에 대해 제 2 동작 모드로의 스위치를 나타내는 제 1 비트 시퀀스를 제 1 동작 모드에서 제 1 라인 (418) 을 통해 전

송할 수도 있다. 마스터 노드 (312) 는 제 1 모드 및 제 2 모드 양자에서 동작 가능한 다른 디바이스들에 대해 제 1 동작 모드로의 스위치를 나타내는 엑시트 심볼 시퀀스를 제 2 동작 모드에서 버스 (430) 를 통해 전송할 수도 있다.

[0158] 제 2 동작 모드는 제 1 동작 모드보다 버스를 통한 더 높은 송신 비트 레이트를 가질 수도 있다. 하나의 예에서, 제 1 동작 모드는 버스 (430) 를 통한 초당 1 메가비트들의 최대 비트 레이트를 가지고, 제 2 동작 모드는 초당 6.4 메가비트들의 최대 비트 레이트를 갖는다. 다른 예에서, 제 2 클럭 신호는 제 1 클럭 신호보다 더 큰 주파수를 가질 수도 있다.

#### [0159] 다중 모드들의 통신을 지원하는 시스템의 제 4 예

[0160] 도 3, 도 4, 및 도 17 을 계속 참조하면, 시스템 또는 장치 (300, 1700) 는 다중모드 버스 (302) 에 의해 상호 연결되는 복수의 디바이스들 (304<sub>1</sub>-304<sub>n</sub>, 312, 및 314<sub>1</sub>-314<sub>n</sub>) 을 채용할 수도 있다. 버스 (302) 는 제 1 라인 (418) 및 제 2 라인 (416) 을 갖는 2-선 직렬 버스를 포함할 수도 있다. 버스는 I2C-호환 버스일 수도 있다. 제 1 동작 모드에서, 제 1 셋트의 디바이스들 (304<sub>1</sub>-304<sub>n</sub>, 312) 은 데이터 송신들을 위해 제 1 라인 (418) 을 이용하고 제 1 클럭 신호를 위해 제 2 라인 (416) 을 이용할 수도 있는 한편, 버스에 커플링된 제 2 셋트의 디바이스들 (312, 및 314<sub>1</sub>-314<sub>n</sub>) 은 제 2 동작 모드에서 데이터 송신들을 위해 제 1 라인 및 제 2 라인 양자를 이용하면서 데이터 송신들의 심볼 천이들 내에 제 2 클럭 신호를 임베딩하도록 구성될 수도 있다.

[0161] 본 명세서에서 개시된 특정 양태들에 따르면, 마스터 디바이스 (312) 는, 버스에 커플링된 모든 디바이스들이, 제 1 클럭 신호를 위한 데이터 송신들 라인의 심볼 천이들 내에 제 2 클럭 신호를 임베딩하면서 데이터 송신들을 위해 제 1 라인 및 제 2 라인 양자를 이용하는 제 3 동작 모드에 따라 동작할 수 있는지 여부를 확인할 수도 있고, 버스에 커플링된 모든 디바이스들이 제 3 동작 모드에서 동작 가능한 경우에만, 디바이스들 (304<sub>1</sub>-304<sub>n</sub>, 312, 및 314<sub>1</sub>-314<sub>n</sub>) 이 제 3 동작 모드에서 동작되게끔 한다. 하나의 예에서, 제 3 동작 모드는 제 2 모드에 대해 감소된 시그널링 오버헤드를 제공할 수도 있다. 디바이스들의 셋트 (304<sub>1</sub>-304<sub>n</sub>, 312, 및 314<sub>1</sub>-314<sub>n</sub>) 는, 버스에 커플링된 모든 디바이스들 (304<sub>1</sub>-304<sub>n</sub>, 312, 및 314<sub>1</sub>-314<sub>n</sub>) 이 제 3 모드에서 동작할 수 있는 한, 또는, 버스에 커플링된 모든 활성 디바이스들 (304<sub>1</sub>-304<sub>n</sub>, 312, 및 314<sub>1</sub>-314<sub>n</sub>) 이 제 3 모드에서 동작할 수 있는 한, 제 3 모드에서 동작하도록 구성된다. 활성 디바이스는, 전원이 켜지고, 버스 (430) 에 커플링되고, 및/또, 버스 (430) 를 모니터링하고 있는 디바이스일 수도 있다. 디바이스들 (304<sub>1</sub>-304<sub>n</sub>, 312, 및 314<sub>1</sub>-314<sub>n</sub>) 은 제 1 동작 모드 및 제 2 동작 모드 양자에서 적어도 제 1 라인 (418) 을 동시에 모니터링할 수도 있다. 제 1 셋트의 디바이스들 (304<sub>1</sub>-304<sub>n</sub>, 312) 및 제 2 셋트의 디바이스들 (312, 및 314<sub>1</sub>-314<sub>n</sub>) 은 제 1 동작 모드 및 제 2 동작 모드 양자에서 적어도 제 2 라인 (416) 을 동시에 모니터링할 수도 있다.

[0162] 하나의 양태에서, 제 1 동작 모드는 버스 (430) 를 통한 데이터 송신들을 위해 제 1 프로토콜을 구현하고, 제 2 모드는 버스 (430) 를 통한 데이터 송신들을 위해 제 2 프로토콜을 구현하며, 제 3 모드는 버스 (430) 를 통한 데이터 송신들을 위해 제 3 프로토콜을 구현한다. 제 2 동작 모드는 레거시 디바이스들이, 유효한 슬레이브 노드 어드레스의 검출을 억제하는 리셋 표시자를 제 1 라인 (418) 및 제 2 라인 (416) 을 통해 수신하는 것을 허용할 수도 있다. 제 2 동작 모드에서, 버스 (430) 에 커플링된 레거시 디바이스들로 하여금 유효한 비트들의 시퀀스를 검출하기 이전에 그들의 버스 로직을 리셋하게 하는 리셋 표시자를 제 1 라인 (418) 및 제 2 라인 (416) 에 삽입함으로써 데이터 송신들은 주기적으로 인터럽트된다. 제 3 동작 모드에서, 제 1 라인 (418) 및 제 2 라인 (416) 에서 아무런 리셋 표시자도 전송되지 않는다.

[0163] 제 3 동작 모드는 제 2 동작 모드보다 버스 (430) 를 통한 더 높은 송신 비트 레이트를 가질 수도 있다. 제 3 동작 모드는 버스 (430) 를 통한 초당 최대 27.1 메가비트들의 비트 레이트를 가질 수도 있다.

[0164] 하나의 양태에서, 마스터 (312) 는, 버스에 커플링된 모든 디바이스들이 제 3 모드에 따라 동작할 수 있는지를 확인하고, 버스에 커플링된 모든 디바이스들 (304<sub>1</sub>-304<sub>n</sub>, 312, 및 314<sub>1</sub>-314<sub>n</sub>) 에 제 3 동작 모드에서 동작하도록 하는 명령을 전송할 수도 있다.

#### [0165] CCIe 및 I2C 동작들을 위해 구성가능한 프로세싱 시스템들의 예

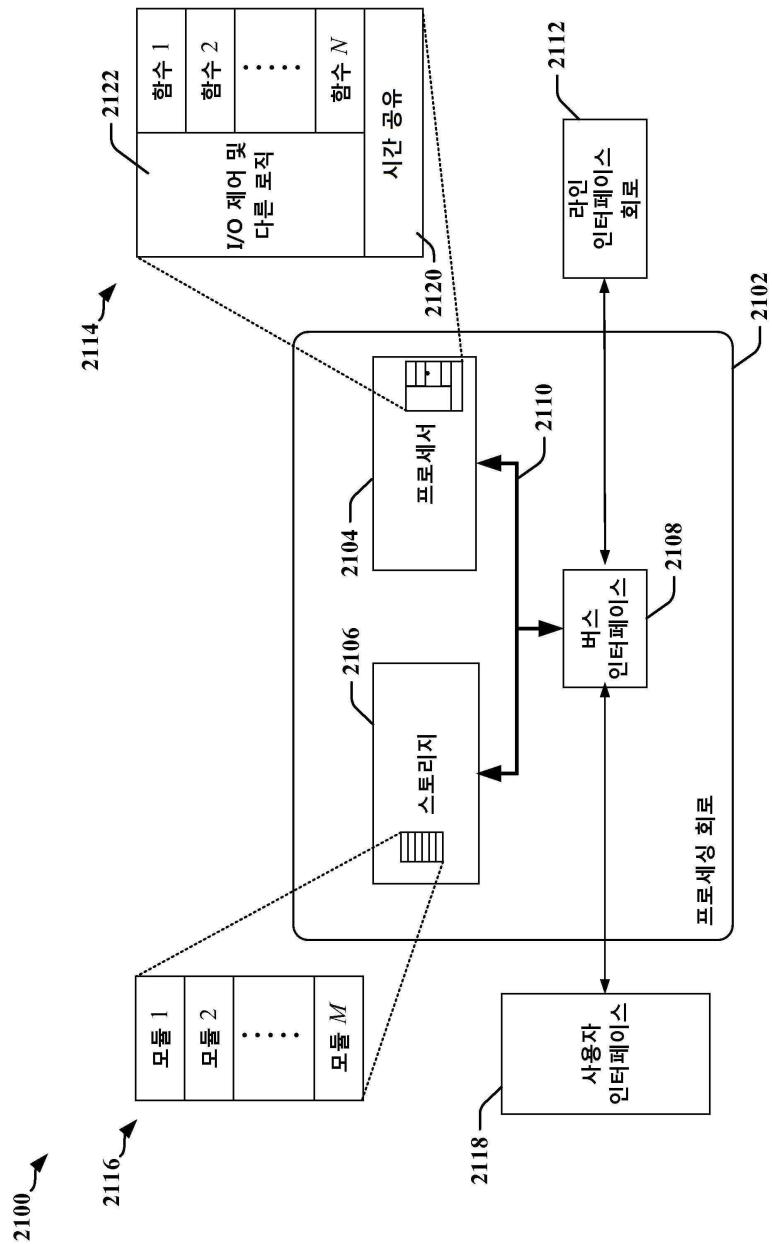

[0166] 도 21 은 본 명세서에서 개시된 하나 이상의 기능들을 수행하도록 구성될 수도 있는 프로세싱 회로 (2102) 를 채용하는 장치에 대한 하드웨어 구현의 단순화된 예를 나타내는 개념도 (2100) 이다. 본 개시의 다양한 양

태들에 따르면, 엘리먼트, 엘리먼트의 임의의 부분, 또는 엘리먼트들의 임의의 조합이 프로세싱 회로 (2102) 를 이용하여 구현될 수도 있다. 프로세싱 회로 (2102) 는 하드웨어 및 소프트웨어 모듈들의 몇몇 조합에 의해 제어되는 하나 이상의 프로세서들 (2104) 을 포함할 수도 있다. 프로세서들 (2104) 의 예들은, 마이크로프로세서들, 마이크로컨트롤러들, 디지털 신호 프로세서 (DSP) 들, 펠드 프로그래머블 게이트 어레이 (FPGA) 들, 프로그래머블 로직 디바이스 (PLD) 들, 상태 머신들, 시퀀서들, 게이티드 로직, 이산 하드웨어 회로들, 및 이 개시물 전체를 통해 기술된 다양한 기능성을 수행하도록 구성된 다른 적합한 하드웨어를 포함한다. 하나 이상의 프로세서들 (2104) 은 특정 기능들을 수행하고 소프트웨어 모듈들 (2116) 중 하나에 의해 구성, 증강, 또는 제어될 수도 있는 특수화된 프로세서들을 포함할 수도 있다. 하나 이상의 프로세서들 (2104) 은 초기화 동안 로딩되는 소프트웨어 모듈들 (2116) 의 조합을 통해 구성될 수도 있고, 또한, 동작 동안 하나 이상의 소프트웨어 모듈들 (2116) 을 로딩 또는 언로딩함으로써 추가로 구성될 수도 있다.

[0167] 도시된 예에서, 프로세싱 회로 (2102) 는 버스 (2110) 에 의해 일반적으로 표현된 버스 아키텍처와 함께 구현될 수도 있다. 버스 (2110) 는 프로세싱 회로 (2102) 의 특정 애플리케이션 및 전체 설계 제약들에 의존하여 임의의 수의 상호연결하는 버스들 및 브릿지들을 포함할 수도 있다. 버스 (2110) 는 하나 이상의 프로세서들 (2104), 스토리지 (2106) 를 포함하는 다양한 회로들을 함께 링크한다. 스토리지 (2106) 는 메모리 디바이스들 및 대용량 스토리지 디바이스들 (2104) 을 포함할 수도 있고, 본 명세서에서 컴퓨터 관독가능 매체들이라 지칭될 수도 있다. 버스 (2110) 는 또한, 타이밍 소스들, 타이머들, 주변장치들, 전압 조정기들, 및 전력 관리 회로들과 같은 다양한 다른 회로들을 링크할 수도 있고, 이들은 당해 기술 분야에서 잘 알려져 있고, 따라서, 그들의 일부는 더 이상 설명되지 않을 수도 있다. 버스 인터페이스 (2108) 는 버스 (2110) 와 라인 인터페이스 회로 (2112) 사이에 인터페이스를 제공할 수도 있다. 라인 인터페이스 회로 (2112) 는 직렬 버스와 같은 송신 매체를 통해 다양한 다른 장치와 통신하기 위한 수단을 제공한다. 장치의 성질에 의존하여, 사용자 인터페이스 (2118) (예컨대, 키패드, 디스플레이, 스피커, 마이크로폰, 조이스틱) 가 또한 제공될 수도 있고, 버스 (2110) 에 직접, 또는 버스 인터페이스 (2108) 를 통해서 통신가능하게 커플링될 수도 있다.

[0168] 프로세서 (2104) 는, 버스 (2110) 를 관리하는 것, 및 스토리지 (2106) 를 포함할 수도 있는 컴퓨터 관독가능 매체에 저장된 소프트웨어의 실행을 포함할 수도 있는 일반적인 프로세싱을 담당할 수도 있다. 이 점에서, 프로세서 (2104) 를 포함하는, 프로세싱 회로 (2102) 는 본 명세서에서 개시된 방법들, 기능들 및 기법들 중 어느 것을 구현하기 위해 이용될 수도 있다. 스토리지 (2106) 는, 소프트웨어를 실행할 때 프로세서 (2104) 에 의해 조작되는 데이터를 저장하기 위해 이용될 수도 있고, 소프트웨어는 본 명세서에서 개시된 방법들 중 임의의 하나를 구현하도록 구성될 수도 있다.

[0169] 프로세싱 회로 (2102) 내의 하나 이상의 프로세서들 (2104) 은 소프트웨어를 실행할 수도 있다. 소프트웨어는, 소프트웨어, 펌웨어, 미들웨어, 마이크로코드, 하드웨어 디스크립션 언어, 또는 기타로서 지칭되든지 간에, 명령들, 명령 셋트들, 코드, 코드 세그먼트들, 프로그램 코드, 프로그램들, 서브프로그램들, 소프트웨어 모듈들, 애플리케이션들, 소프트웨어 애플리케이션들, 소프트웨어 패키지들, 루틴들, 서브루틴들, 오브젝트들, 실행가능체들, 실행 스레드들, 절차들, 함수들, 알고리즘들 등을 의미하는 것으로 넓게 해석되어야 할 것이다.

소프트웨어는 스토리지 (2106) 에 또는 외부 컴퓨터 관독가능 매체에 컴퓨터 관독가능한 형태로 존재할 수도 있다. 컴퓨터 관독가능 매체 및/또는 스토리지 (2106) 는 비-일시적 (non-transitory) 컴퓨터 관독가능 매체일 수도 있다. 비-일시적 컴퓨터 관독가능 매체는, 예시로서, 자기 저장 디바이스 (예컨대, 하드 디스크, 플로피 디스크, 자기 스트립), 광학 디스크 (예컨대, 콤팩트 디스크 (CD) 또는 디지털 다기능 디스크 (DVD)), 스마트 카드, 플래시 메모리 디바이스 (예컨대, "플래시 드라이브", 카드, 스틱, 또는 키 드라이브), 랜덤 액세스 메모리 (RAM), 관독 전용 메모리 (ROM), 프로그래머블 ROM (PROM), 소거가능 PROM (EPROM), 전기적으로 소거가능한 PROM (EEPROM), 레지스터, 착탈형 디스크, 및 컴퓨터에 의해 액세스 및 관독될 수도 있는 소프트웨어 및/또는 명령들을 저장하기 위한 임의의 다른 적합한 매체를 포함한다. 컴퓨터 관독가능 매체 및/또는 스토리지 (2106) 는 또한, 예시로서, 반송파, 송신 라인, 및 컴퓨터에 의해 액세스 및 관독될 수도 있는 소프트웨어 및/또는 명령들을 송신하기 위한 임의의 다른 적합한 매체를 포함할 수도 있다. 컴퓨터 관독가능 매체 및/또는 스토리지 (2106) 는, 프로세싱 회로 (2102) 에, 프로세서 (2104) 에, 프로세싱 회로 (2102) 외부에 존재할 수도 있거나, 프로세싱 회로 (2102) 를 포함하는 다수의 엔티티들에 걸쳐 분산될 수도 있다. 컴퓨터 관독가능 매체 및/또는 스토리지 (2106) 는 컴퓨터 프로그램 제품에 포함될 수도 있다. 예시로서, 컴퓨터 프로그램 제품은 패키징 재료들에 컴퓨터 관독가능 매체를 포함할 수도 있다. 당해 기술분야에서 통상의 지식을 가진 자 (이하, '통상의 기술자' 라 함) 는, 특정 애플리케이션 및 전체 시스템에 부과된 전체적인 설계 제약들에 의존하여 이 개시물 전체를 통해 제시된 설명된 기능성을 어떻게 최선으로 구현할 수 있는지를 인식할 것이

다.

[0170] 스토리지 (2106) 는, 본 명세서에서 소프트웨어 모듈들 (2116) 으로 지칭될 수도 있는, 로딩 가능한 코드 세그먼트들, 모듈들, 애플리케이션들, 프로그램들 등에서 유지 및/또는 조작화되는 소프트웨어를 유지할 수도 있다.

소프트웨어 모듈들 (2116) 의 각각은, 프로세싱 회로 (2102) 에 의해 설치 또는 로딩되거나 하나 이상의 프로세서들 (2104) 에 의해 실행될 때, 그 하나 이상의 프로세서들 (2104) 의 동작을 제어하는 런-타임 이미지 (2114) 에 기여하는 명령들 및 데이터를 포함할 수도 있다. 실행될 때, 어떤 명령들은 프로세싱 회로 (2102) 로 하여금 본 명세서에서 기술된 소정의 방법들, 알고리즘들 및 프로세스들에 따라 기능들을 수행하게 할 수도 있다.

[0171] 소프트웨어 모듈들 (2116) 의 일부는 프로세싱 회로 (2102) 의 초기화 동안 로딩될 수도 있고, 이를 소프트웨어 모듈들 (2116) 은 본 명세서에 개시된 다양한 기능들의 수행을 가능하게 하도록 프로세싱 회로 (2102) 를 구성할 수도 있다. 예를 들어, 일부 소프트웨어 모듈들 (2116) 은 프로세서 (2104) 의 내부 디바이스들 및/또는 로직 회로들 (2122) 을 구성할 수도 있고, 라인 인터페이스 회로 (2112), 버스 인터페이스 (2108), 사용자 인터페이스 (2118), 타이머들, 연산 코프로세서들 등과 같은 외부 디바이스들에 대한 액세스를 관리할 수도 있다.

소프트웨어 모듈들 (2116) 은, 인터럽트 핸들러들 (interrupt handlers) 및 디바이스 드라이버들과 상호작용하고 프로세싱 회로 (2102) 에 의해 제공되는 다양한 리소스들에 대한 액세스를 제어하는 제어 프로그램 및/또는 오퍼레이팅 시스템을 포함할 수도 있다. 리소스들은 메모리, 스토리지 (2106), 프로세싱 시간, 라인 인터페이스 회로 (2112) 에 대한 액세스, 사용자 인터페이스 (2118) 등을 포함할 수도 있다.

[0172] 프로세싱 회로 (2102) 의 하나 이상의 프로세서들 (2104) 은 다기능적일 수도 있고, 이에 의해, 소프트웨어 모듈들 (2116) 의 일부는 상이한 기능들, 또는 동일한 기능의 상이한 인스턴스들을 수행하도록 로딩 및 구성된다.

하나 이상의 프로세서들 (2104) 은, 예를 들어, 사용자 인터페이스 (2118), 라인 인터페이스 회로 (2112), 및 디바이스 드라이버들로부터의 입력들에 응답하여 개시되는 백그라운드 태스크들을 관리하도록 추가적으로 적응될 수도 있다. 다중 기능들의 수행을 지원하기 위해, 하나 이상의 프로세서들 (2104) 은 멀티태스킹 환경을 제공하도록 구성될 수도 있고, 이에 의해 복수의 기능들의 각각은 필요에 따라 또는 소망에 따라 하나 이상의 프로세서들 (2104) 에 의해 서비스되는 태스크들의 셋트로서 구현된다. 하나의 예에서, 멀티태스킹 환경은, 상이한 태스크들 사이에 프로세서 (2104) 의 제어를 패스하는 시간공유 프로그램 (2120) 을 이용하여 구현될 수도 있고, 이에 의해, 각 태스크는 임의의 미결 동작들의 완료 시에 및/또는 인터럽트와 같은 입력에 대해 응답하여 시간공유 프로그램 (2120) 에 그 하나 이상의 프로세서들 (2104) 의 제어를 리턴한다. 태스크가 하나 이상의 프로세서들 (2104) 의 제어를 가질 때, 프로세싱 회로는 제어 태스크와 연관된 함수에 의해 어드레싱된 목적들을 위해 유효하게 특수화된다. 시간공유 프로그램 (2120) 은 오퍼레이팅 시스템, 순환식으로 제어를 전송하는 메인 루프, 함수들의 우선순위화에 따라서 하나 이상의 프로세서들 (2104) 의 제어를 할당하는 함수, 및/또는 핸들링 함수에 하나 이상의 프로세서들 (2104) 의 제어를 제공함으로써 외부 이벤트들에 응답하는 인터럽트 구동된 메인 루프를 포함할 수도 있다.

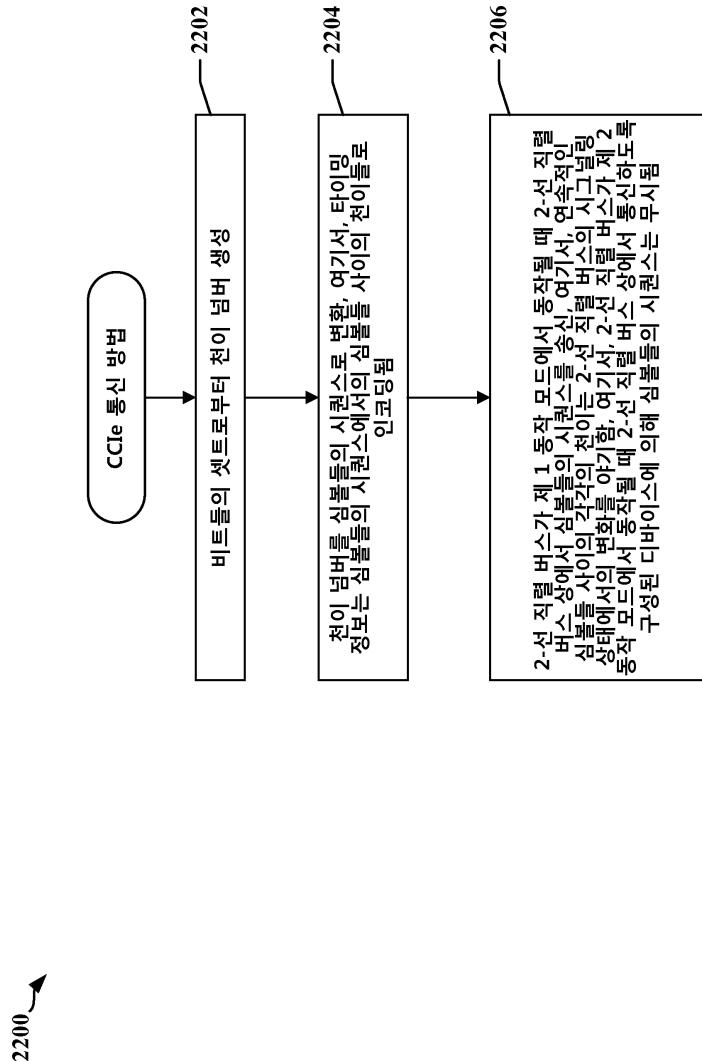

[0173] 도 22 는 CCIe 버스 상에서의 데이터 통신들을 위한 방법을 나타내는 흐름도 (2200) 이다. 이 방법의 다양한 단계들은 예를 들어 도 1-8, 20, 22, 및/또는 24 에서 예시된 디바이스들 및 회로들의 몇몇 조합을 포함하는 송신기 디바이스에 의해 수행될 수도 있다.

[0174] 블록 2202 에서, 디바이스는 비트들의 셋트로부터 천이 넘버를 생성할 수도 있다. 천이 넘버는 12 디지트 3진수를 포함할 수도 있다. 하나의 예에서, 디바이스는 비트들의 셋트로부터 천이 넘버를 생성할 수도 있다. 천이 넘버는 12 디지트 3진수일 수도 있다.

[0175] 블록 2204 에서, 디바이스는 그 천이 넘버를 심볼들의 시퀀스로 변환할 수도 있다. 심볼들의 시퀀스에서의 심볼들 사이의 천이드레서 타이밍 정보가 인코딩될 수도 있다. 심볼들의 시퀀스에서 인코딩된 타이밍 정보는 수신기가 심볼들의 시퀀스로부터 수신 클럭을 생성하는 것을 가능하게 한다. 천이 넘버는 3진수를 트랜스코더에 제공함으로써 심볼들의 시퀀스로 변환될 수도 있다.