(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-363256

(P2004-363256A)

(43) 公開日 平成16年12月24日(2004.12.24)

(51) Int.Cl.<sup>7</sup>H01L 21/768

H01L 21/3205

F 1

H01L 21/90

H01L 21/88

H01L 21/88

テーマコード(参考)

A 5FO33

K

M

審査請求 未請求 請求項の数 13 O L (全 21 頁)

(21) 出願番号

(22) 出願日特願2003-158487 (P2003-158487)

平成15年6月3日 (2003.6.3)

(71) 出願人 302062931

NECエレクトロニクス株式会社

神奈川県川崎市中原区下沼部1753番地

(74) 代理人 100102864

弁理士 工藤 実

(72) 発明者 竹脇 利至

神奈川県川崎市中原区下沼部1753番地

NECエレクトロニクス株式会社内

(72) 発明者 小田 典明

神奈川県川崎市中原区下沼部1753番地

NECエレクトロニクス株式会社内

(72) 発明者 本間 一郎

神奈川県川崎市中原区下沼部1753番地

NECエレクトロニクス株式会社内

最終頁に続く

(54) 【発明の名称】半導体装置及び半導体装置の製造方法

## (57) 【要約】

【課題】半導体装置のローカル配線層部での配線間容量を抑え、配線の信頼性を向上する。

【解決手段】半導体基板40上に形成された第1配線層部33と、第1配線層部33上に形成された第2配線層部32とを具備する半導体装置を用いる。第1配線層部33は、第1層間絶縁膜と、第1層間絶縁膜内に第1間隔以上で設けられた複数の第1ビアプラグ37-1及び複数の第1配線37-2を有する。第2配線層部32は、第2層間絶縁膜と、第2層間絶縁膜内に第1間隔よりも大きい第2間隔以上で設けられた複数の第2ビアプラグ34-1及び複数の第2配線34-2を有する。第1ビアプラグ37-1、第1配線37-2、第2ビアプラグ34-1及び第2配線34-2は、銅を含む金属からなる。第1配線層部33は、シングルダマシン構造であり、第2配線層部32は、デュアルダマシン構造である。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

半導体基板上に形成された第1配線層部と、

前記第1配線層部上に形成された第2配線層部と

を具備し、

前記第1配線層部は、

第1層間絶縁膜と、

前記第1層間絶縁膜内に設けられ第1間隔以上で互いに隔てられた複数の第1ビアプラグ

と、

前記第1層間絶縁膜内において前記複数の第1ビアプラグ上に設けられ前記複数の第1ビア

プラグに接続された複数の第1配線と

10

を有し、

前記第2配線層部は、

第2層間絶縁膜と、

前記第2層間絶縁膜内に設けられ前記第1間隔よりも大きい第2間隔以上で互いに隔てら

れた複数の第2ビアプラグと、

前記第2層間絶縁膜内において前記複数の第2ビアプラグ上に設けられ前記複数の第2ビア

プラグに接続された複数の第2配線と

20

を有し、

前記複数の第1ビアプラグ、前記複数の第1配線、前記複数の第2ビアプラグ及び前記複

数の第2配線は、銅を含む金属からなり、

前記第1配線層部は、シングルダマシン構造であり、

前記第2配線層部は、デュアルダマシン構造である

半導体装置。

**【請求項 2】**

請求項1に記載の半導体装置において、

前記第1配線層部は、前記第1層間絶縁膜内に設けられた前記複数の第1ビアプラグと前

記複数の第1配線とを含む複数の層を備え、

前記第2配線層部は、前記第2層間絶縁膜内に設けられた前記複数の第2ビアプラグと前

記複数の第2配線とを含む複数の層を備える

30

半導体装置。

**【請求項 3】**

請求項1又は2に記載の半導体装置において、

前記第1間隔は、前記複数の第1ビアプラグに関する単位面積あたりのビアプラグの個数

としてのビア密度が、所定の条件を満たすように設定され、

前記所定の条件は、前記複数の第1配線の各々間の配線間容量が、前記第1配線層部をデ

ュアルダマシン法で形成した場合に比較して、小さくなることである

半導体装置。

**【請求項 4】**

請求項3に記載の半導体装置において、

前記ビア密度は、1個/ $\mu\text{m}^2$ 以上である

40

半導体装置。

**【請求項 5】**

請求項3又は4に記載の半導体装置において、

前記第1間隔は、0.5 $\mu\text{m}$ である

半導体装置。

**【請求項 6】**

請求項1乃至6のいずれか一項に記載の半導体装置において、

前記複数の第1ビアプラグの各々の直径は、0.4 $\mu\text{m}$ 以下である

50

半導体装置。

## 【請求項 7】

- (a) 半導体基板上に第1絶縁膜を形成する工程と、

(b) 前記第1絶縁膜に第1間隔以上で互いに隔てられた銅を含む金属からなる複数の第1ビアプラグをシングルダマシン法により形成する工程と、

(c) 前記第1絶縁膜及び前記複数の第1ビアプラグ上に第2絶縁膜を形成する工程と、

(d) 前記第2絶縁膜に前記複数の第1ビアプラグに接続された銅を含む金属からなる複数の第1配線をシングルダマシン法により形成する工程と、

(e) 前記第2絶縁膜及び前記複数の第1配線上に第3絶縁膜を形成する工程と、

(f) 前記第3絶縁膜に前記第1間隔よりも大きい第2間隔以上で互いに隔てられた複数の第2ビアプラグ及び前記複数の第2ビアプラグに接続された銅を含む金属からなる複数の第2配線をデュアルダマシン法により形成する工程と

を備える

半導体装置の製造方法。

## 【請求項 8】

請求項7に記載の半導体装置の製造方法において、

前記デュアルダマシン法は、トレントチファースト法である

半導体装置の製造方法。

## 【請求項 9】

請求項8に記載の半導体装置の製造方法において、

- (g) 前記(d)工程と前記(e)工程との間で、前記(a)工程から前記(d)工程を、所望の層数分繰り返す工程と、

(h) 前記(f)工程の後で、前記(e)工程から前記(f)工程を、所望の層数分繰り返す工程と

を更に備える

半導体装置の製造方法。

## 【請求項 10】

請求項7乃至9のいずれか一項に記載の半導体装置の製造方法において、

前記第1間隔は、前記複数の第1ビアプラグに関する単位面積あたりのビアプラグの個数としてのビア密度が、所定の条件を満たすように設定され、

前記所定の条件は、前記複数の第1配線の各々間の配線間容量が、前記複数の第1ビアプラグ及び前記複数の第1配線をデュアルダマシン法で形成した場合に比較して、小さくなることである

半導体装置の製造方法。

## 【請求項 11】

請求項10に記載の半導体装置の製造方法において、

前記ビア密度は、1個/ $\mu\text{m}^2$ 以上である

半導体装置の製造方法。

## 【請求項 12】

請求項10又は11に記載の半導体装置の製造方法において、

前記第1間隔は、0.5 $\mu\text{m}$ である

半導体装置の製造方法。

## 【請求項 13】

請求項7乃至12のいずれか一項に記載の半導体装置の製造方法において、

前記複数の第1ビアプラグの各々の直径は、0.4 $\mu\text{m}$ 以下である

半導体装置の製造方法。

## 【発明の詳細な説明】

## 【0001】

## 【発明の属する技術分野】

本発明は、半導体装置及び半導体装置の製造方法に関し、特に、銅を含む金属からなるダマシン構造の配線及びビアプラグを備える半導体装置及び半導体装置の製造方法に関する

。

## 【0002】

## 【従来の技術】

半導体装置の配線に関わる構造として、半導体基板上に設けられた複数の素子上に、ローカル配線層部と電源配線層部とが順に積層された構造が知られている。そのような半導体装置では、各層における配線には材料として銅(Cu)を用い、各層間の接続に用いられるビアプラグには材料としてタンゲステン(W)を用いるのが一般的である。

## 【0003】

しかし、タンゲステンの成膜温度は非常に高いため、微細化された配線の銅が耐え切れず、凝集が起こり、断線する確率が高くなる。一方、銅を用いたビアプラグは、タンゲステンを用いたビアプラグに比較して、ビア抵抗が低い、熱応力に対する耐性が高いなどの利点がある。このような理由から、近年、ビアプラグにも銅を用いることが多くなってきて 10 いる。

## 【0004】

配線及びビアプラグを共に銅で形成する方法として、デュアルダマシン法及びシングルダマシン法がある。デュアルダマシン法は、シングルダマシン法に比較して、CMPの工程が1回少ない、配線とビアプラグとの間にバリアメタル膜が挟まっていないので配線抵抗が小さい、という点で利点がある。そのため、現在、配線及びビアプラグを全てデュアルダマシン法で形成することが多い。そのような半導体装置の構造について図7を参照して説明する。 20

## 【0005】

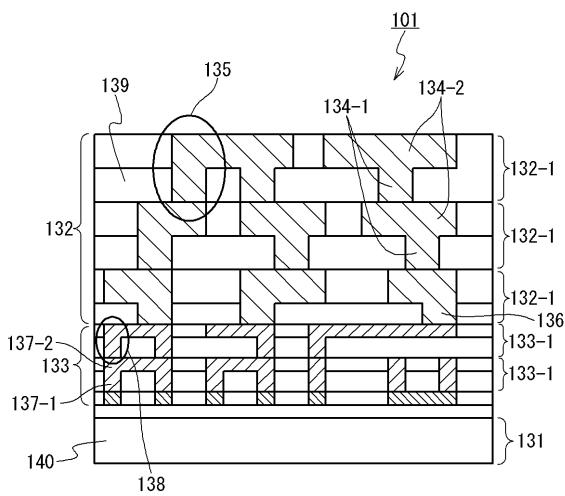

図7は、半導体装置の配線に関わる構造を示す断面図である。半導体装置101は、半導体基板140上に設けられ、素子部131、ローカル配線層部133及び電源配線層部132を具備する。素子部131は、半導体基板140及びその上に設けられた複数の素子及びその配線(図示されず)を備える。

## 【0006】

ローカル配線層部133は、素子部131上に設けられ、複数の配線137-2と複数のビアプラグ137-1とを含む配線層133-1を備える。配線137-2は、複数の素子に対して信号の入出力を行う信号線、又は、複数の素子と電源配線層部132とを接続する電源線又は接地線である。ビアプラグ137-1は、配線137-2同士、又は、配線137-2と素子との間を接続する。 30

そして、配線137-2とビアプラグ137-1とで形成される接合部138は、デュアルダマシン法で形成されている。

## 【0007】

電源配線層部132は、ローカル配線層部133の上に設けられ、複数の配線134-2と複数のビアプラグ134-1とを含む配線層132-1を備える。ローカル配線層部133と接続するビアプラグ134-1を特にビアプラグ136ともいう。配線134-2は、複数の素子に対して電源を接続する電源線、又は、接地を行う接地線である。ビアプラグ134-1は、配線134-2同士を接続する。そして、配線134-2とビアプラグ134-1とで形成される接合部135は、デュアルダマシン法で形成されている。 40

## 【0008】

ここで、デュアルダマシン法には、ビアファースト法とトレンチファースト法がある。ビアファースト法は、露光時の反射防止のために、ビアホールの開口後、配線溝(トレンチ)を形成する前に、ビアホールをB A R C (Bottom Anti-Reflection Coating)で埋める必要がある。そのため、工程が煩雑になる。従って、工程の少ないトレンチファースト法が好んで用いられる。

## 【0009】

しかし、トレンチファースト法では、ビアホールをフォトリソグラフィーの技術で形成する際、配線溝(トレンチ)の段差を有する半導体装置上にレジストを塗布し、所定のパターンを露光する必要がある。そのため、配線溝のパターンによっては、段差により焦点を 50

適切に合わすことが困難となる。特に、微細な形状を正確に露光できなくなる。従って、ローカル配線層部 133 のようなビアプラグの大きさが小さく、かつ、そのピッチが狭いところでは、ビアファースト法でビアホールを形成することが一般的となっている。

#### 【0010】

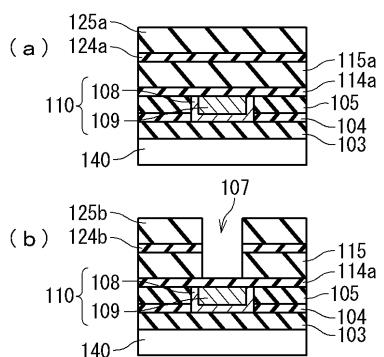

以下、デュアルダマシン法の一つであるビアファースト法について説明する。図 8 ~ 図 11 は、ビアファースト法のプロセスを示す半導体装置の断面図である。ここでは、2つの層のそれぞれに設けられた配線と、それらを繋ぐビアプラグとを形成する例を示す。

#### 【0011】

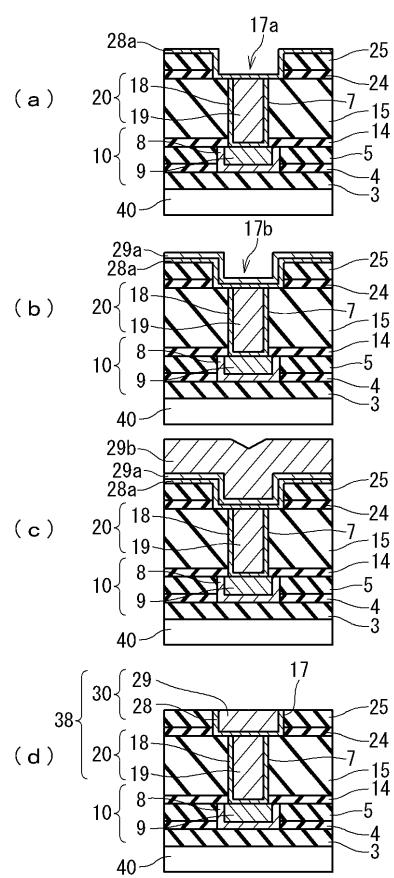

図 8 (a) に示すように、基板 140 上において、層間絶縁膜 103 上のストップ絶縁層 104 及び低誘電率絶縁層 105 の中に、第 1 層の配線 110 が設けられる。配線 110 10 は、銅 (Cu) の配線 109 とタンタル / 窒化タンタル (Ta / TaN) のバリアメタル層 108 を含み、ダマシン構造を有する。従来知られた配線製造プロセスで設けられる。そして、配線 110 と低誘電率絶縁層 105 とを覆うようにストップ絶縁膜 114a が設けられる。更に、ストップ絶縁膜 114a を覆うように層間絶縁膜 115a が設けられる。更に、層間絶縁膜 115a を覆うようにストップ絶縁膜 124a が設けられる。更に、ストップ絶縁膜 124a を覆うように低誘電率絶縁膜 125a が設けられる。

#### 【0012】

続いて、図 8 (a) の状態から、フォトリソグラフィーのプロセスを用いて、層間絶縁膜 115a、ストップ絶縁膜 124a 及び低誘電率絶縁膜 125a に、ビアホール 107 を形成する。この状態が図 8 (b) である。このとき、ビアホール 107 を形成された層間絶縁膜 115a、ストップ絶縁膜 124a 及び低誘電率絶縁膜 125a を、それぞれ、層間絶縁層 115、ストップ絶縁層 124b 及び低誘電率絶縁層 125b とする。

#### 【0013】

次に、図 8 (b) の状態から、ビアホール 107 に有機物 142 (例示: BARC) を埋め込む。有機物 142 の量 (ビアホール 107 での有機物 142 の高さ  $h_A$ ) は、ビアホール 107 の密度やその他の要因で決まる。ここでは、ストップ絶縁層 124b の高さまでとする。この状態が図 9 (a) 及び (c) である。ただし、図 9 (c) は、図 9 (a) での AA' 断面である。このときのビアホール 107 をビアホール 107a とする。

#### 【0014】

続いて、図 9 (a) 及び (c) の状態から、フォトリソグラフィーのプロセスを用いて、低誘電率絶縁層 125b に、配線溝 117a を形成する。この状態が図 9 (b) 及び (d) 30 である。ただし、図 9 (d) は、図 9 (b) での BB' 断面である。このとき、低誘電率絶縁層 125b 及びビアホール 107a を、それぞれ、低誘電率絶縁層 125 及びビアホール 107b とする。

#### 【0015】

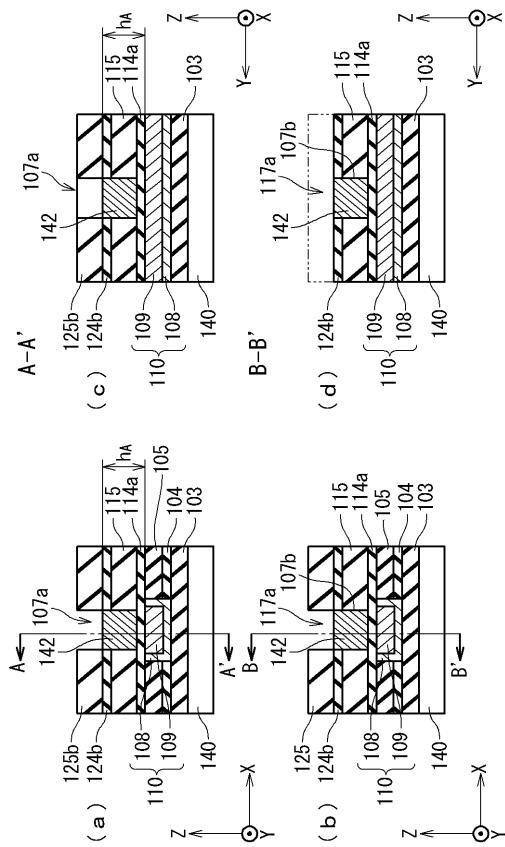

次に、図 9 (b) 及び (d) の状態から、有機物 142 を除去する。そして、ビアホール 107b の底部のストップ絶縁膜 114a と、配線溝 117 の底部のストップ絶縁膜 124b とをエッチバックして除去する。この状態が図 10 (a) 及び (c) である。ただし、図 10 (c) は、図 10 (a) での CC' 断面である。このとき、ビアホール 107b 40 、配線溝 117a、ストップ絶縁膜 114a 及びストップ絶縁膜 124a を、それぞれビアホール 107c、配線溝 117、ストップ絶縁層 114 及びストップ絶縁層 124 とする。

#### 【0016】

続いて、図 10 (a) 及び (c) の状態から、低誘電率絶縁層 125 の表面と、配線溝 117 の側壁 (側面) 及び底部と、ビアホール 107c の側壁 (側面) 及び底部とを覆うように、Ta / TaN からなるバリアメタル膜 118a をスパッタ法で設ける。次に、バリアメタル膜 118a を覆うように Cu からなるシード導体膜 119a を設ける。続いて、シード導体膜 119a を覆い、且つ、配線溝 117b 及びビアホール 107e を埋めるように Cu からなる導体膜 119b を設ける。この状態が図 10 (b) 及び (d) である。ただし、図 10 (d) は、図 10 (b) での DD' 断面である。

## 【0017】

次に、図10(b)及び(d)の状態から、低誘電率絶縁層125表面及び配線溝117上方における不要なバリアメタル膜118a、シード導体膜119a及び導体膜119bをCMP(Chemical Mechanical Polishing)で除去する。このようにして、元々のビアホール107においてバリアメタル層118及び導体層119とからなるビアプラグ120(コンタクト)が形成される。また、元々の配線溝117においてバリアメタル層118及び導体層119とからなる配線130が形成される。この状態が図11(a)及び(b)である。ただし、図11(b)は、図11(a)でのEE'断面である。

## 【0018】

このように図8～図11の製造方法により、デュアルダマシン法の一つであるビアファースト法により配線及びビアプラグが形成される。ただし、図11におけるビアプラグ120、配線130及び配線110は、それぞれ図7におけるビアプラグ137-1、配線137-2に対応する。

## 【0019】

電源配線層部132に用いるデュアルダマシン法の一つであるトレンチファースト法は、ビアファースト法とは逆に、まず、配線溝117を形成する。そして、配線溝117の底部の所定の位置に、フォトリソグラフィーの技術によりビアホール107を形成する。その後のプロセス(バリアメタル層118及び導体層119の形成等)は、ビアファースト法と同様である。

## 【0020】

関連する技術として、特開2001-156168号公報(特許文献1)に、半導体装置とその製造方法の技術が開示されている。この技術の半導体装置は、半導体基板と、複数の配線層とを有する。半導体基板は、複数の素子が形成されている。複数の配線層は、前記半導体基板上に形成されている。複数の配線層は、前記複数の素子同士を接続するための銅からなる信号線や前記複数の素子に電源を供給するための銅からなる電源線及び接地線を備える。そして、前記複数の配線層間ににおける信号線、電源線及び接地線の接続が、前記信号線、電源線及び接地線下に形成されたビアによってなされる。ここで、前記信号線及び前記信号線下に形成された第1ビアは、該ビアにタンゲステンを用いてシングルダマシン工程によって形成されている。前記電源線及び接地線、並びに該電源線及び接地線下に形成された第2ビアは、デュアルダマシン工程によって形成されている。第2ビアの面積は、第1ビアの面積よりも予め設定された割合だけ大きくなるように形成されている。

この技術は、機械的強度が強く、かつ、放熱性に優れた半導体装置及びその製造方法を提供することを目的とする。

## 【0021】

## 【特許文献1】

特開2001-156168号公報(図1(b)、図6、図7、図8)

## 【0022】

## 【発明が解決しようとする課題】

図9(b)及び(d)において、有機物142の最上部の位置は、ビアホール107内のストッパ絶縁層124bの位置と同じになっている。実際の半導体装置では、同一層に複数のビアホール107が存在し、ビアホール107が密集した領域(密領域)とそうでない領域(疎領域)とがある。同一層上には、表面の単位面積あたり、一定の有機物142が供給される。そのため、密領域において有機物142の最上部の位置とストッパ絶縁層124bの位置とが同じになるように、BARCを供給すると、疎領域において有機物142の最上部の位置がストッパ絶縁膜124bの位置より高くなる。反対に、疎領域において有機物142の最上部の位置とストッパ絶縁層124bの位置とが同じになるように、BARCを供給すると、密領域において有機物142の最上部の位置がストッパ絶縁膜124bの位置より低くなる。

## 【0023】

ビアホール107において、有機物142の最上部の位置がストップ絶縁膜124bの位置より高くなると、以下のような問題が生じる。

## 【0024】

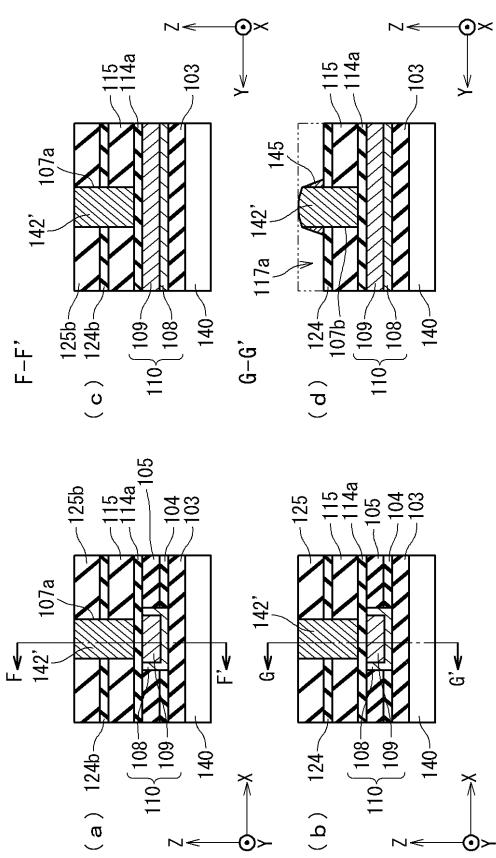

図12は、有機物の最上部の位置がストップ絶縁膜の位置より高くなるように有機物を入れた場合の半導体装置の断面を示す図である。図12(a)は、図9(a)に対応する。図12(c)は、図12(a)のFF'断面である。有機物142'は、低誘電率層125bの高さまで埋め込まれている。この状態から、フォトリソグラフィーのプロセスを用いて、低誘電率絶縁層125bに、配線溝117aを形成する。この状態が図12(b)及び(d)である。ただし、図12(d)は、図12(b)でのGG'断面である。この場合、配線溝117aをエッチングで形成する際、エッチング残渣が、配線溝117内に出て有機物142'の側面に付着して、フェンス(膜)145を形成する。フェンス145は、有機物142'を除去した後も残る。そのため、フェンス145は、その後のバリアメタル膜118aやシード導体膜119aを形成する障害となる。そして、配線の抵抗の増大や断線のような問題が発生し、信頼性を低下させる原因となる。

## 【0025】

一方、ビアホール107において、有機物142の最上部の位置がストップ絶縁膜124bの位置より低くなると、以下のような問題が生じる。

## 【0026】

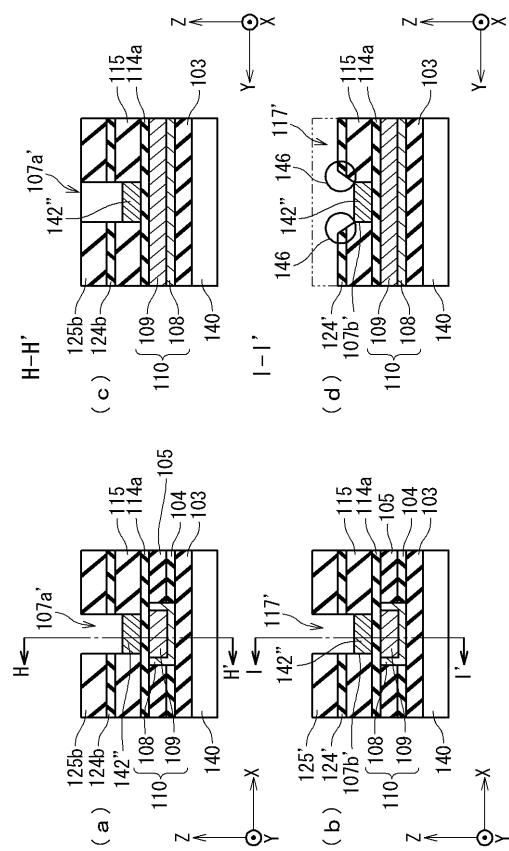

図13は、有機物の最上部の位置がストップ絶縁膜の位置より低くなるように有機物を入れた場合の半導体装置の断面図である。図13(a)は、図9(a)に対応する。図13(c)は、図13(a)のHH'断面である。このときのビアホール107をビアホール107a'とする。この状態から、フォトリソグラフィーのプロセスを用いて、低誘電率絶縁層125bに、配線溝117を形成する。この状態が図13(b)及び(d)である。ただし、図13(d)は、図13(b)でのII'断面である。このとき、ストップ絶縁層124b、低誘電率絶縁層125b及びビアホール107a'を、それぞれ、ストップ絶縁層124'、低誘電率絶縁層125'及びビアホール107b'とする。このとき、ストップ絶縁層124'及び層間絶縁膜115は、ビアホール107b'との境界部分において、一部分がエッチングされてしまう。それにより、ストップ絶縁層124'の除去された肩落ち部146が形成される。図13(d)に示すように、特に配線溝117'の方向にそれが顕著に現れる。その理由は、角の部分(この場合、ビアホール107b'の開口部)ができると、その部分のエッチング速度が、他の部分のエッチング速度と比較して速くなるからである。

## 【0027】

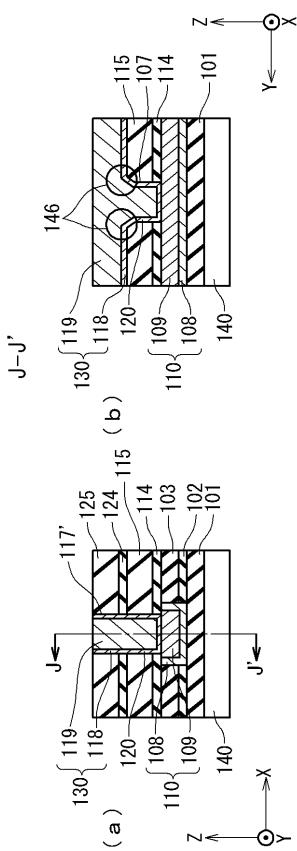

その後、図13(b)及び(d)の状態から、有機物142'を除去する。その後、ビアホール107b'の底部のストップ絶縁膜114aと、配線溝117'の底部のストップ絶縁膜124とをエッチバックして除去する。続いて、バリアメタル膜118a、シード導体膜119a、導体膜119bを設ける。そして、低誘電率絶縁層125表面及び配線溝117'上方における不要なバリアメタル膜118a、シード導体膜119a及び導体膜119bをCMPで除去し、ビアプラグ120及び配線130が形成される。この状態が図14(a)及び(b)である。ただし、図14(b)は、図14(a)でのJJ'断面である。このとき、肩落ち部146の配線130は、配線の長さ方向の断面積を増加させることになる。すなわち、配線間容量の増加の原因となる。

## 【0028】

近年の半導体装置の微細化の進展において、配線の信頼性を維持することは重要である。具体的には、バリアメタル膜を厚く成膜して銅のマイグレーションや絶縁膜への拡散を防止すること、図12で説明した理由からビアホールに埋め込む有機物を多くせずキャップ絶縁層の高さより低くすること、などが必要である。その場合、バリアメタル膜が厚いことによる配線の抵抗の増加、図13及び図14で説明した肩落ち部146aの形成、などが起きる。

## 【0029】

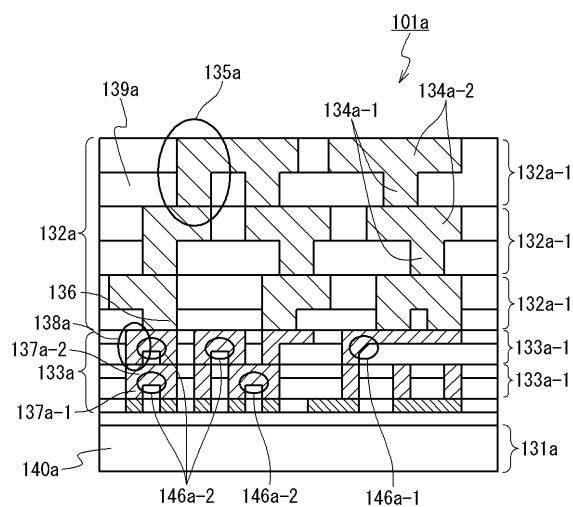

図15は、図13及び図14の肩落ちを含む半導体装置の配線に関する構造を示す断面図である。半導体装置101aは、素子部131a、ローカル配線層部133a及び電源配線層部132aを具備する。素子部131a、ローカル配線層部133a及び電源配線層部132aは、基本的に図7の素子部131、ローカル配線層部133及び電源配線層部132と同様である。ただし、ローカル配線層部133aは、ビアプラグ137a-1のピッチが狭くなっている。また、図13及び図14で説明したように、肩落ち部146a(-1~2)が形成されることになる。ただし、肩落ち部146a-2は、肩落ち部146a-1と向きが90度異なり、紙面に垂直な方向において、図14(b)のような肩落ちが生じている。

10

## 【0030】

この場合、ビアプラグ137a-1のピッチが小さくなり、個々の肩落ち部146a同士の距離は近くなっている。加えて、肩落ち部146aにより、配線の長さ方向の断面積が増加している。それらのことから、ビアプラグ周辺での肩落ち部146aの形成による配線間容量の増加は無視できない問題となる。

## 【0031】

半導体装置におけるローカル配線層部での配線やビアプラグの信頼性を向上する技術が望まれている。配線間容量の増加を防止する技術が求められている。配線の抵抗の増加を防止する技術が望まれている。電源配線層部でのビアプラグの抵抗を低く保ち、その工程数を削減することが可能な技術が求められている。

20

## 【0032】

従って、本発明の目的は、ローカル配線層部での配線やビアプラグの信頼性を向上する半導体装置及び半導体装置の製造方法を提供することである。

## 【0033】

また、本発明の別の目的は、ローカル配線層部で配線間容量及び配線抵抗の増加を防止する半導体装置及び半導体装置の製造方法を提供することである。

## 【0034】

本発明の更に別の目的は、動作の信頼性を向上することが可能な半導体装置及び半導体装置の製造方法を提供することである。

30

## 【0035】

本発明の他の目的は、電源配線層部でのビアプラグの抵抗を低く保ち、その工程数を削減することが可能な半導体装置及び半導体装置の製造方法を提供することである。

## 【0036】

【課題を解決するための手段】

以下に、[発明の実施の形態]で使用される番号・符号を用いて、課題を解決するための手段を説明する。これらの番号・符号は、[特許請求の範囲]の記載と[発明の実施の形態]との対応関係を明らかにするために付加されたものである。ただし、これらの番号・符号を、[特許請求の範囲]に記載されている発明の技術的範囲の解釈に用いてはならない。

40

## 【0037】

従って、上記課題を解決するために、本発明の半導体装置は、半導体基板(40)上に形成された第1配線層部(33)と、第1配線層部(33)上に形成された第2配線層部(32)とを具備する。第1配線層部(33)は、第1層間絶縁膜と、複数の第1ビアプラグ(37-1)と、複数の第1配線(37-2)を有する。複数の第1ビアプラグ(37-1)は、その第1層間絶縁膜内に設けられ第1間隔以上で互いに隔てられている。複数の第1配線(37-2)は、その第1層間絶縁膜内において複数の第1ビアプラグ(37-1)上に設けられ複数の第1ビアプラグ(37-1)に接続されている。第2配線層部(32)は、第2層間絶縁膜と、複数の第2ビアプラグ(34-1)と、複数の第2配線(34-2)を有する。複数の第2ビアプラグ(34-1)は、その第2層間絶縁膜内に設けられその第1間隔よりも大きい第2間隔以上で互いに隔てられている。複数の第2配

50

線（34-2）は、その第2層間絶縁膜内において複数の第2ビアプラグ（34-1）上に設けられ複数の第2ビアプラグ（34-1）に接続されている。複数の第1ビアプラグ（37-1）、複数の第1配線（37-2）、複数の第2ビアプラグ（34-1）及び複数の第2配線（34-2）は、銅を含む金属からなる。第1配線層部（33）は、シングルダマシン構造であり、第2配線層部（32）は、デュアルダマシン構造である。

【0038】

本発明により、半導体装置の第2配線層部（32）よりもビアプラグの間隔が狭い第1配線層部（33）において、シングルダマシン構造を採用することにより、図14に示す肩落ち部（146）の生成を防止することができる。それにより、デュアルダマシン構造の場合に比較して、配線間容量を抑えることが可能となる。

10

【0039】

上記の半導体装置において、第1配線層部（33）は、その第1層間絶縁膜内に設けられた複数の第1ビアプラグ（37-1）と複数の第1配線（37-2）とを含む複数の層を備える。第2配線層部（32）は、その第2層間絶縁膜内に設けられた複数の第2ビアプラグ（34-1）と複数の第2配線（34-2）とを含む複数の層を備える。

【0040】

上記の半導体装置において、その第1間隔は、複数の第1ビアプラグ（37-1）に関する単位面積あたりのビアプラグの個数としてのビア密度（n）が、所定の条件を満たすように設定される。その所定の条件は、複数の第1配線（37-2）の各々間の配線間容量（C<sub>s</sub>）が、第1配線層部（33）をデュアルダマシン法で形成した場合（C<sub>d</sub>）に比較して、小さくなることである。

20

【0041】

ビア密度（n）が大きくなるとデュアルダマシン法による肩落ち部（146）の影響が大きくなるが、本発明ではそのような影響の出る状況（所定の条件）において、シングルダマシン法で作成しているので、配線間容量の増加を防止することができる。

【0042】

上記の半導体装置において、ビア密度（n）は、1個/μm<sup>2</sup>以上である。肩落ち部（146）の影響がするのは、特に、ビア密度（n）が1個/μm<sup>2</sup>以上においてであり、本発明をその範囲に適用することで、配線間容量の増加を防止することができる。

30

【0043】

上記の半導体装置において、その第1間隔は、0.5μmである。

本発明をその範囲に適用することで、配線間容量の増加を防止することができる。

【0044】

上記の半導体装置において、複数の第1ビアプラグ（37-1）の各々の直径は、0.4μm以下である。

第1ビアプラグ（37-1）の各々の直径が0.4μm以下の場合、特に、ビアファースト法を用いるので、本発明をその範囲に適用することで、配線間容量の増加を防止することができる。

【0045】

また、上記課題を解決するために、本発明の半導体装置の製造方法は、（a）～（f）工程を備える。（a）は、半導体基板（40）上に第1絶縁膜を形成する工程である。（b）は、その第1絶縁膜に第1間隔以上で互いに隔てられた銅を含む金属からなる複数の第1ビアプラグ（37-1）をシングルダマシン法により形成する工程である。（c）は、その第1絶縁膜及び複数の第1ビアプラグ（37-1）上に第2絶縁膜を形成する工程である。（d）は、その第2絶縁膜に複数の第1ビアプラグ（37-1）に接続された銅を含む金属からなる複数の第1配線（37-2）をシングルダマシン法により形成する工程である。（e）は、その第2絶縁膜及び複数の第1配線（37-2）上に第3絶縁膜を形成する工程である。（f）は、その第3絶縁膜にその第1間隔よりも大きい第2間隔以上で互いに隔てられた複数の第2ビアプラグ（34-1）及び複数の第2ビアプラグ（34-

40

50

1)に接続された銅を含む金属からなる複数の第2配線(34-2)をデュアルダマシン法により形成する工程である。

【0046】

上記の半導体装置の製造方法において、そのデュアルダマシン法は、トレンチファースト法である。

【0047】

上記の半導体装置の製造方法において、(g)～(h)工程を更に備える。(g)は、(d)工程と(e)工程との間で、(a)工程から(d)工程を、所望の層数分繰り返す工程である。(h)は、(f)工程の後で、(e)工程から(f)工程を、所望の層数分繰り返す工程である。

10

【0048】

上記の半導体装置の製造方法において、その第1間隔は、複数の第1ビアプラグ(37-1)に関する単位面積あたりのビアプラグの個数としてのビア密度(n)が、所定の条件を満たすように設定される。その所定の条件は、複数の第1配線(37-2)の各々間の配線間容量(C<sub>S</sub>)が、複数の第1ビアプラグ(37-1)及び複数の第1配線(37-2)をデュアルダマシン法で形成した場合(C<sub>D</sub>)に比較して、小さくなることである。

【0049】

上記の半導体装置の製造方法において、ビア密度(n)は、1個/μm<sup>2</sup>以上である。

【0050】

上記の半導体装置の製造方法において、その第1間隔は、0.5μmである。

20

【0051】

上記の半導体装置の製造方法において、複数の第1ビアプラグ(37-1)の各々の直径は、0.4μm以下である。

【0052】

【発明の実施の形態】

以下、本発明の半導体装置及び半導体装置の製造方法の実施の形態に関して、添付図面を参照して説明する。

【0053】

まず、本発明の半導体装置の実施の形態の構成について説明する。

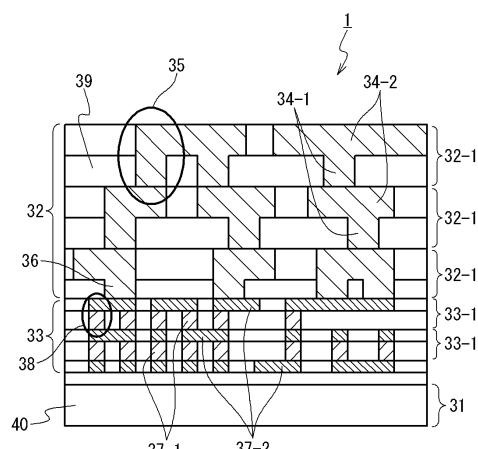

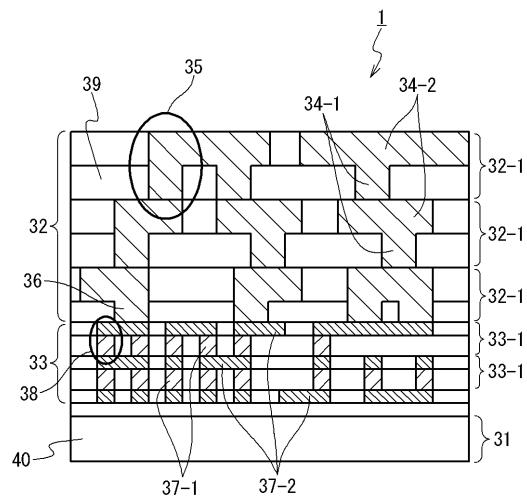

図1は、本発明の半導体装置の配線に関する構造を示す断面図である。半導体装置1は、

素子部31、ローカル配線層部33及び電源配線層部32を具備する。

30

【0054】

素子部31は、半導体基板40及びその上に設けられた複数の素子(図示せず)を備える。

【0055】

ローカル配線層部33は、素子部31上に設けられ、複数の配線37-2(図中、その一部を例示)と複数のビアプラグ37-1(図中、その一部を例示)とを含む複数の配線層33-1備える。配線37-2は、複数の素子に対して信号の入出力を行う信号線、又は、複数の素子と電源配線層部32とを接続する電源線又は接地線である。ビアプラグ37-1は、配線37-2同士、又は、配線37-2と素子との間を接続する。配線37-2は、タンタル/窒化タンタルに例示されるバリアメタル膜と、バリアメタル膜に囲まれた銅とで形成される。そして、配線37-2の一部とビアプラグ37-1とで形成される接合部38は、シングルダマシン法で形成されている。ローカル配線層部33の他の配線37-2の一部と他のビアプラグ37-1とで形成される接合部も同様である。

40

【0056】

電源配線層部32は、ローカル配線層部33の上に設けられ、複数の配線34-2(図中、その一部を例示)と複数のビアプラグ34-1(図中、その一部を例示)とを含む複数の配線層32-1を備える。複数の配線34-2は、複数の素子に対して電源を接続する電源線、又は、接地を行う接地線である。ビアプラグ34-1は、配線34-2同士を接続する。配線34-2及びビアプラグ34-1は、タンタル/窒化タンタルに例示される

50

バリアメタル膜と、バリアメタル膜に囲まれた銅とで形成される。そして、配線 34-2 の一部とビアプラグ 34-1 とで形成される接合部 35 は、デュアルダマシン法の一つであるトレーナーファースト法で形成されている。電源配線層部 32 の他の配線 34-2 の一部と他のビアプラグ 34-1 とで形成される接合部も同様である。ローカル配線層部 33 と接続するビアプラグ 34-1 を特にビアプラグ 36 ともいう。

#### 【0057】

ここで、ローカル配線層部 33 におけるシングルダマシン構造を有する配線 37-2 及びビアプラグ 37-1 の構成について説明する。

図 4 (d) は、シングルダマシン構造を有する配線及びビアプラグの構成を示す断面図である。この配線及びビアプラグは、基板 40 上に設けられ、層間絶縁層 3、キャップ絶縁層 4、低誘電率絶縁層 5、バリアメタル層 8 と導体部 9 とを含む第 1 配線 10、キャップ絶縁層 14、層間絶縁層 15、バリアメタル層 18 と導体部 19 とを含むビア 20、キャップ絶縁層 24、低誘電率絶縁層 25、バリアメタル層 28 と導体部 29 とを含む第 2 配線 30 を具備する。

#### 【0058】

基板 40 は、複数の配線構造や素子が埋め込まれた絶縁膜の多層構造を有する半導体基板である。

#### 【0059】

層間絶縁層 3 は、基板 40 を覆うように設けられている。CVD 法やスピンドルコート法などで形成された絶縁膜である。配線間や配線と素子、素子間を絶縁する。配線の寄生容量を低減するために、低誘電率の材料を用いる。本実施例では、3.0 以下の低い比誘電率を有する有機ポリマー系の低誘電率膜を用いる。

#### 【0060】

キャップ絶縁層 4 は、層間絶縁層 3 を覆うように設けられている。層間絶縁膜 3 上に、CVD 法やスピンドルコート法などで形成された絶縁膜である。第 1 配線 10 の配線溝を形成するフォトリソグラフィーのプロセスにおいて、層間絶縁膜 3 を保護する。本実施例では、炭化窒化シリコン (SiCN) である。膜厚は、例えば、およそ 100 nm である。

#### 【0061】

低誘電率絶縁層 5 は、キャップ絶縁層 4 を覆うように設けられている。CVD 法やスピンドルコート法などで形成された絶縁膜である。配線間や配線と素子、素子間を絶縁する。配線の寄生容量を低減するために、低誘電率の材料を用いる。本実施例においては、3.0 以下の低い比誘電率を有する有機ポリマー系の低誘電率膜を用いる。膜厚は、例えば、およそ 200 nm である。

#### 【0062】

第 1 配線 10 は、層間絶縁層 3 の表面からキャップ絶縁層 4 及び低誘電率絶縁層 5 を貫通する配線溝を埋めるように設けられている。バリアメタル層 8 と導体部 9 とを含む。

#### 【0063】

バリアメタル層 8 は、配線溝の側壁及び底部を覆うように設けられている。スパッタ法により形成された金属薄膜である。導体部 9 が低誘電率絶縁層 5 へ拡散することや、導体部 9 が凝集することを防止する。高融点金属あるいはその窒化物である。本実施例では、タンタル / 窒化タンタル (Ta / TaN) の積層膜である。膜厚は、例えば、およそ 30 nm である。

#### 【0064】

導体部 9 は、バリアメタル層 8 を設けられた配線溝を満たす（埋める）ように設けられている。スパッタ法、メッキ法などにより形成された金属である。この部分は、コンタクト用に、抵抗率の低い金属で形成される。例えば、銅、銅 - アルミニウムのような銅を含む金属である。本実施例では、銅 (Cu) を用いる。第 1 配線 10 は、基板 40 と反対側の上部に、ビア 20 と接合する。第 1 配線 10 の深さ及び幅は、例えば、それぞれ 300 nm 及び幅 300 nm である。

#### 【0065】

10

20

30

40

50

キャップ絶縁層 14 は、低誘電率絶縁層 5 と第 1 配線 10 とを覆うように設けられている。材質、製法及び膜厚は、キャップ絶縁層 4 と同様である。

また、層間絶縁層 15 は、キャップ絶縁層 14 を覆うように設けられている。材質及び製法は、層間絶縁層 3 と同様である。膜厚は、例えば、およそ 400 nm である。

#### 【 0066 】

バリアメタル層 18 は、ピアホール 7 の側壁及び底部を覆うように設けられている。材質、製法及び膜厚は、バリアメタル層 8 と同様である。

導体部 19 は、バリアメタル層 18 を設けられたピアホール 7 を満たす（埋める）ように設けられている。材質、及び製法は、導体部 9 と同様である。ピア 32 の大きさは、例えば、幅 200 nm、深さ 500 nm である。導体部 19 は、バリアメタル層 18 と共にピア 20 を形成する。

#### 【 0067 】

キャップ絶縁層 24 は、層間絶縁層 15 を覆うように設けられている。材質、製法及び膜厚は、キャップ絶縁層 4 と同様である。

低誘電率絶縁層 25 は、キャップ絶縁膜 24 を覆うように設けられている。材質、製法及び膜厚は、低誘電率絶縁層 5 と同様である。

#### 【 0068 】

バリアメタル層 28 は、層間絶縁層 15 及びピア 20 の表面からキャップ絶縁膜 24 及び低誘電率絶縁層 25 を貫通する配線溝 17 の側壁及び底部に設けられている。材質、製法及び膜厚は、バリアメタル膜 8 と同様である。ただし、配線溝 17 は、第 2 配線 30 を形成するための溝である。

導体部 19 は、バリアメタル膜 28 を設けられた配線溝 17 を満たす（埋める）ように設けられている。材質、製法及び膜厚は、導体部 9 と同様である。

#### 【 0069 】

ここで、電源配線層部 32 におけるデュアルダマシン構造を有する配線 34-2 及びピア プラグ 34-1 の構成については、トレントファースト法を用いているほかは、既述（図 8 から図 11）のとおりなので、その説明を省略する。また、ピアファースト法を用いても良い。

ただし、電源配線層部 32 における層間絶縁層は、CVD 法やスピンドルコート法などで形成された絶縁膜である。配線間を絶縁する。この部分の配線層は、配線間容量の影響が少ない。そのため、層間絶縁層は、二酸化シリコンに代表される無機系の絶縁膜を用いる。本実施例では、二酸化シリコンである。そのような絶縁層は、機械的な強度が強いため、組み立て時の半導体装置の損傷を防止することが出来る。

#### 【 0070 】

本発明では、ローカル配線層部 33 において、デュアルダマシン構造を採用せず、銅のピア プラグを有するシングルダマシン構造を採用している。その理由を以下に説明する。

#### 【 0071 】

デュアルダマシン構造を有するローカル配線層部 33 をピアファースト法により作成する従来の場合、図 9 (a) 及び (c) の工程において、近傍に他のピアホールが無い孤立したピアホール（以下「孤立ピアホール」という）と、近傍に他のピアホールが多く密集したピアホール（以下「密集ピアホール」という）とでは、詰め込まれる ARC (Anti-Reflection Coating : 有機物 142) の厚さ（高さ : 図 9 (a) 及び (c) の  $h_A$ ）が変わってくる。それは、以下の理由による。同一配線層上には、配線層の表面の単位面積あたり、一定の ARC が供給される。そのため、周辺に他のピアホールが無い孤立ピアホールには多くの ARC が詰め込まれる。しかし、周辺に他の多くのピアホールがある密集ピアホールには、孤立ピアホールに詰め込まれるよりも少なく ARC が詰め込まれることになる。

#### 【 0072 】

このような場合、詰め込まれる ARC の高さ  $h_A$  の上限を、孤立ピアホールでの高さで律速することとする。すなわち、図 12 に示すようなフェンス 145 の形成を防止するため

10

20

30

40

50

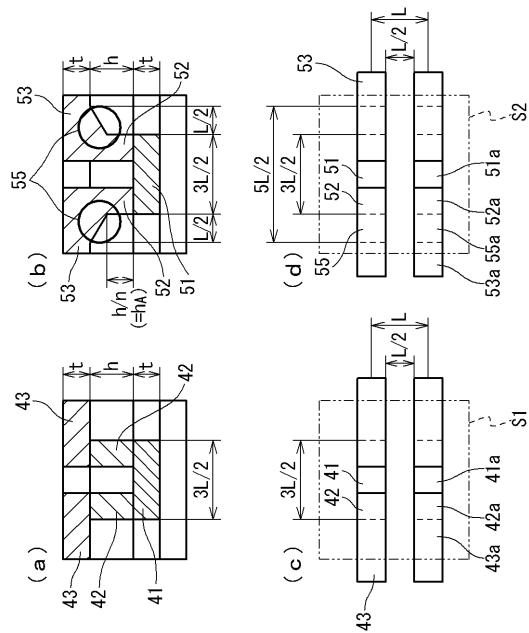

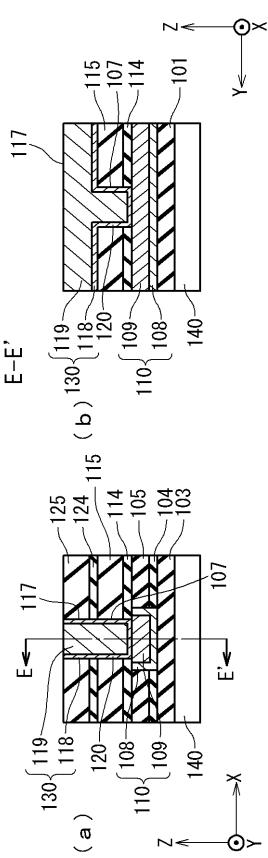

に、孤立ピアホールのある部分では、詰め込まれるARCの高さ $h_A$ は異層間の絶縁層(図12等におけるストップ絶縁層124+層間絶縁層115)の膜厚 $h$ 以下となるようする。その場合、同じ配線層にある密集ピアホールにおいて、異層間の絶縁層の膜厚を $h$ ( $\mu m$ )、単位面積あたりの密集ピアホールの個数(=単位面積あたりのピアプラグの個数、以下「ピア密度」ともいう)を $n$ (個/ $\mu m^2$ )とすると、ここでの詰め込みARCの高さ $h_A$ は、おおむね $h/n$ となる。配線の最小ピッチを $L$ ( $\mu m$ )とすると密集ピアホールのピッチは、 $L$ ( $\mu m$ )となる。このようなピアホールでピアプラグを作製した場合、図14(b)に示すような肩落ち部が形成される。その状態を改めて示したのが、図5(b)及び(d)である。

【0073】

10

図5は、シングルマシン構造の配線及びピアプラグ((a)及び(c))と、ピアファースト法によるデュアルダマシン構造の配線及びピアプラグ((b)及び(d))を示す半導体装置の断面図である。図5(a)及び図5(b)は側面図、図5(c)及び図5(d)は上面図である。

図5(b)を参照して、このデュアルダマシン構造は、第1層の配線51とピアプラグ52と第2層の配線53と肩落ち部55を備えている。配線51及び配線53は、膜厚 $t$ ( $\mu m$ )、ピアプラグ52は、高さ $h$ ( $\mu m$ )である。また、上記の議論から肩落ち部55の高さ(=詰め込みARCの高さ $h_A$ )は、おおむね $h/n$ となる。

【0074】

20

ここで、図5(d)を参照して、配線53(肩落ち部55を含む)-ピアプラグ52-配線51-ピアプラグ52-配線53(肩落ち部55を含む)の組に対して、同様の配線53a(肩落ち部55aを含む)-ピアプラグ52a-配線51a-ピアプラグ52a-配線53a(肩落ち部55aを含む)の組が、平行に設けられている場合を考える。このような構造は、DRAMやSRAMのようなメモリに例示される半導体装置に典型的に見られる構造である。

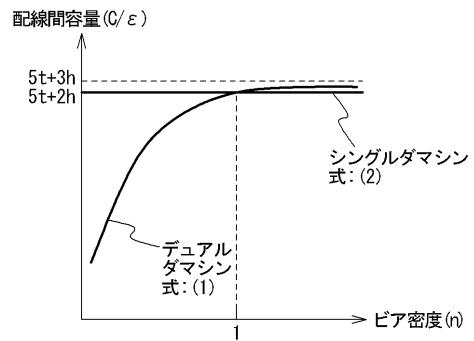

配線ピッチを $L$ ( $\mu m$ )、配線幅を $L/2$ ( $\mu m$ )、配線間の距離を $L/2$ ( $\mu m$ )とすれば、点線で囲まれた部分の配線間容量( $C_D$ /:は異層間の絶縁層の誘電率)は、(A)デュアルダマシン構造の場合

$$C_D/\epsilon = [2 \times \{(t+h) \times (L/2)\} + t \times (3L/2)] / (L/2) \\ + [ \{(h-h/n) \times (L/2)\} / 2 ] \times 2 \\ = 5t + 2h + h \times (1 - 1/n) \quad (1)$$

30

となる。

【0075】

一方、図5(a)を参照して、このシングルダマシン構造では、第1層の配線41とピアプラグ42と第2層の配線43とを備えている。配線41及び配線43は、膜厚 $t$ ( $\mu m$ )、ピアプラグ42は、高さ $h$ ( $\mu m$ )である。

ここで、図5(c)を参照して、図5(d)の場合と同様に、配線43-ピアプラグ42-配線41-ピアプラグ42-配線43の組に対して、同様の配線43a-ピアプラグ42a-配線41a-ピアプラグ42a-配線43aの組が、平行に設けられている場合を考える。配線ピッチを $L$ ( $\mu m$ )、配線幅を $L/2$ ( $\mu m$ )、配線間の距離を $L/2$ ( $\mu m$ )とすれば、点線で囲まれた部分の配線間容量( $C_S$ /:は異層間の絶縁層の誘電率)は、

(B)シングルダマシン構造の場合

$$C_S/\epsilon = [2 \times \{(t+h) \times L/2\} + t \times (3L/2)] / (L/2) \\ = 5t + 2h \quad (2)$$

40

となる。

【0076】

50

図6は、式(1)及び式(2)を示すグラフである。縦軸は配線間容量(C/F)、横軸はピア密度nである。ピア密度nが増加する、すなわちビアプラグ間のピッチが狭くなると、デュアルダマシンの場合、配線容量が増加する。しかし、シングルダマシンの場合、配線容量はピア密度によらない。つまり、配線間容量がシングルダマシンの場合の値に比較して大きくなるようなピア密度nで、シングルダマシン法を採用すればよい。

【0077】

図6及び式(1)及び式(2)から、n=1以上の場合、シングルダマシン構造での配線間容量が、デュアルダマシン構造のそれを下回ることがわかる。すなわち、ピア密度nは、n=1が好ましい。この場合、ピッチは、無関係である。さらに、DRAMやSRAMのようなメモリに例示される半導体装置に平均的な値として、t=0.3μm、h=0.4μmを用い、設計の要請から配線間容量を0.18fF/μm以下にする場合、n=25となり、ピッチは、0.4μmとなる。

【0078】

本発明により、半導体装置のローカル配線層部での配線が微細化してピア密度nが大きくなる場合でも、シングルダマシン構造を採用することにより、デュアルダマシン構造の場合に比較して配線間容量を抑えることが可能となる。

【0079】

次に、本発明の半導体装置の製造方法について説明する。

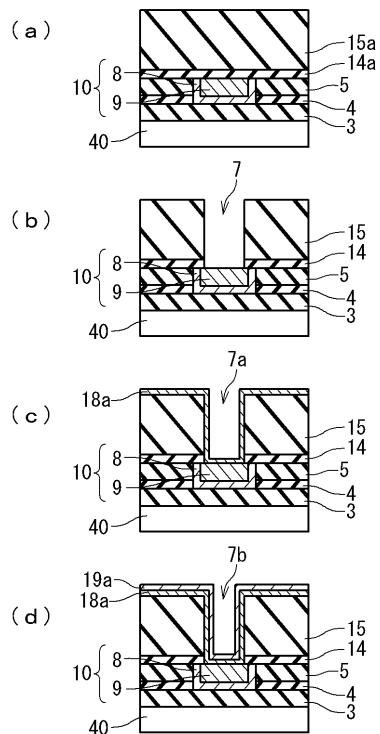

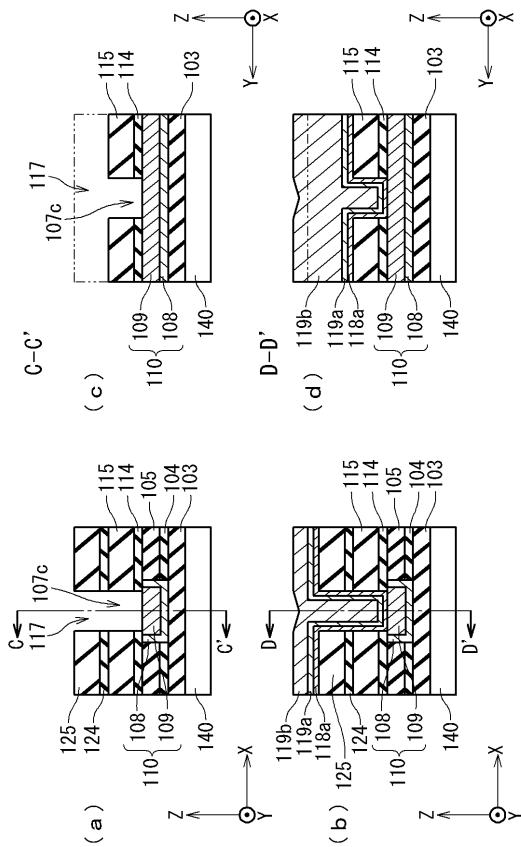

まず、ローカル配線層部33の製造方法について説明する。ここでは、シングルダマシン構造を有する一配線層33-1分の配線及びビアプラグを製造する方法について説明する。図2～図4は、シングルダマシン構造を構成する配線及びビアプラグの製造方法を示す半導体装置の断面図である。ここでは、2つの層のそれぞれに設けられた配線と、それらを繋ぐビアプラグとを形成する例を示す。

【0080】

図2において、複数の半導体素子を設けられた基板40上に、層間絶縁膜3上のストップ絶縁層4及び低誘電率絶縁層5の中に、第1層の配線10が設けられる。配線10は、銅(Cu)の配線9とタンタル/窒化タンタル(Ta/TaN)のバリアメタル層8とを含み、ダマシン構造を有する。従来知られた配線製造プロセスで設けられる。そして、配線10と低誘電率絶縁層5とを覆うようにストップ絶縁膜14aが設けられる。更に、ストップ絶縁膜14aを覆うように層間絶縁膜15aが設けられる。この、図2(a)の状態において、フォトリソグラフィーのプロセスを用いて、ストップ絶縁膜14aと層間絶縁膜15aとにビアホール7を形成する。ビアホール7を形成されたストップ絶縁膜14aと層間絶縁膜15aを、それぞれ、ストップ絶縁層14と層間絶縁層15とする。この図2(b)の状態において、層間絶縁層5の表面とビアホール7の側壁(側面)及び底部とを覆うように、Ta/TaNからなるバリアメタル膜18aをスパッタ法で設ける。このときビアホール7aとなる。この図2(c)の状態において、バリアメタル膜18aを覆うようにCuからなるシード導体膜19aを設ける。このときビアホール7bとなる。この状態が図2(d)である。

【0081】

次に、図2(d)の状態において、シード導体膜19aを覆い、且つ、ビアホール7bを埋めるようにCuからなる導体膜19bを設ける。この図3(a)の状態において、層間絶縁層15表面及びビアホール7上方における不要なバリアメタル膜18a、シード導体膜19a及び導体膜19bをCMP(Chemical Mechanical Polishing)で除去する。このようにして、バリアメタル層18及び導体層19とからなるビアプラグ20(コンタクト)が形成される。この図3(b)の状態において、ビアプラグ20と層間絶縁膜15とを覆うようにストップ絶縁膜24aが設けられる。更に、ストップ絶縁膜24aを覆うように低誘電率絶縁膜25aが設けられる。この図3(c)の状態において、フォトリソグラフィーのプロセスを用いて、ストップ絶縁膜24aと低誘電率絶縁膜25aとに第2層の配線溝17を形成する。このとき、配線溝17を形成されたストップ絶縁膜24aと低誘電率絶縁膜25aを、それぞれ、ストップ絶縁層24と

低誘電率絶縁層 25 とする。この状態が図 3 (d) である。

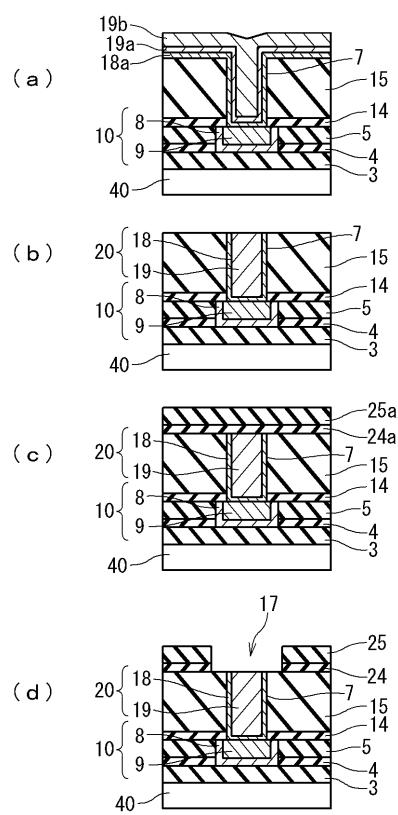

【0082】

次に、図 3 (d) の状態において、低誘電率絶縁層 25 と配線溝 17 の側壁及び底部とを覆うように、Ta/TaN からなるバリアメタル膜 28a をスパッタ法で設ける。このとき配線溝 17a となる。この図 4 (a) の状態において、バリアメタル膜 28a を覆うように Cu からなるシード導体膜 29a を設ける。このとき配線溝 17b となる。この図 4 (b) の状態において、シード導体膜 29a を覆い、且つ、ビアプラグ 17 を埋めるように Cu からなる導体膜 29b を設ける。この図 4 (c) の状態において、低誘電率絶縁層 25 表面及び配線溝 17 上方における不要なバリアメタル膜 28a、シード絶縁膜 29a 及び導体膜 29b を CMP で除去する。このようにして、バリアメタル層 28 及び導体層 29 とからなる配線 30 が形成される。配線 30 及びビアプラグ 20 は、接合体 38 (図 1、シングルダマシン法で形成) に対応する。

10

【0083】

そして、以上の図 2 ~ 図 4 の製造方法により、シングルダマシン構造を有する一配線層 33-1 分の配線及びビアプラグが形成される。ただし、図 4 におけるビアプラグ 20、配線 10 及び配線 30 は、それぞれ図 1 におけるビアプラグ 37-1、配線 37-2 に対応する。積層された他の配線層 33-1 も同様にして形成できる。

20

【0084】

ビアプラグ 36 の製造方法については、上述のシングルダマシン法又は従来のデュアルダマシン法を用いて形成できるのでその説明を省略する。また、電源配線層部 32 の製造方法については、層間絶縁層に二酸化シリコンに代表される無機系の絶縁膜を用いる他は、既述のデュアルダマシン法 (トレンチファースト法) を用いて形成しているのでその説明を省略する。

20

【0085】

本発明では、シングルダマシン構造を採用することにより、微細な配線の形成を安定して行うことができる。それにより、配線のピッチが短く配線が微細なローカル配線部において、バリアメタル膜を厚くつける必要がなくなり、配線の抵抗を低減することが出来る。

30

【0086】

更に、電源配線層部では、デュアルダマシン構造を採用しているので、ビアプラグの抵抗を低く保ち、その工程数を少なく維持できる。

30

【0087】

加えて、電源配線層部における層間絶縁層は、二酸化シリコンに代表される無機系の絶縁膜を用いるので、機械的な強度が強く、組み立て時の半導体装置の損傷を防止することが出来る。

40

【0088】

【発明の効果】

本発明により、半導体装置のローカル配線層部での配線が微細化してビア密度 n が大きくなる場合でも、シングルダマシン構造を採用することにより、デュアルダマシン構造の場合に比較して配線間容量を抑えることが可能となる。

【図面の簡単な説明】

40

【図 1】図 1 は、本発明の半導体装置の配線に関わる構造を示す断面図である。

【図 2】図 2 は、シングルダマシン構造を構成する配線及びビアプラグの製造方法を示す半導体装置の断面図である。

【図 3】図 3 は、シングルダマシン構造を構成する配線及びビアプラグの製造方法を示す半導体装置の断面図である。

【図 4】図 4 は、シングルダマシン構造を構成する配線及びビアプラグの製造方法を示す半導体装置の断面図である。

【図 5】図 5 は、シングルダマシン構造及びデュアルダマシン構造の配線及びビアプラグを示す半導体装置の断面図である。

【図 6】図 6 は、式 (1) 及び式 (2) を示すグラフである。

50

【図7】図7は、半導体装置の配線に関する構造を示す半導体装置の断面図である。

【図8】図8は、ビアファースト法のプロセスを示す半導体装置の断面図である。

【図9】図9は、ビアファースト法のプロセスを示す半導体装置の断面図である。

【図10】図10は、ビアファースト法のプロセスを示す半導体装置の断面図である。

【図11】図11は、ビアファースト法のプロセスを示す半導体装置の断面図である。

【図12】図12は、ビアホールを完全に埋めるように有機物を入れた場合の半導体装置の断面を示す図である。

【図13】図13は、有機物の量をストップ絶縁層の高さよりも低くした場合の半導体装置の断面図である。

【図14】図14は、有機物の量をストップ絶縁層の高さよりも低くした場合の半導体装置の断面図である。 10

【図15】図15は、図13及び図14の肩落ちを含む半導体装置の配線に関する構造を示す断面図である。

【符号の説明】

1、101、101a 半導体装置

3、15、103、115 層間絶縁層

15a、115a 層間絶縁膜

4、14、24、104、114、124 ストップ絶縁層

14a、24a、114a、124a ストップ絶縁膜

5、25、105、125 低誘電率絶縁層

25a、125a 低誘電率絶縁膜

7、7a、7b、107、107a(')、107b、107c ビアホール

8、18、28、118 バリアメタル層

18a、28a、118a バリアメタル膜

9、19、29、119 導体部

19a、29a、119a シード導体膜

19b、29b、129a 導体膜

10、30、41、43、51、53、110 配線

17、17a、17b、117(') 配線溝

20、42、52、120 ビアプラグ

30、130 ビアプラグ

31、131、131a 素子部

32、132、132a 電源配線層部

32-1、132-1、132a-1 配線層

33、133、133a 口-カル配線層部

33-1、133-1、133a-1 配線層

34-1、37-1、134-1、137-1、134a-1、137a-1 ビアプラグ

34-2、37-2、134-2、137-2、134a-2、137a-2 配線

35、38、135、138、135a、138a 接合部

36、136、136a ビアプラグ

40、140、140a 基板

142(',',') 有機物

146、146a 肩落ち部

10

20

30

40

【 図 1 】

【 図 2 】

【図3】

【 図 4 】

【 図 5 】

【 図 6 】

【図7】

【 図 8 】

【 义 9 】

【 図 1 1 】

【 図 1 0 】

【 図 1 2 】

【図13】

【図14】

【図15】

## フロントページの続き

F ターム(参考) 5F033 HH11 HH12 HH21 HH32 JJ01 JJ11 JJ12 JJ21 JJ32 KK11

KK12 KK21 KK32 MM01 MM02 MM12 MM13 NN06 NN07 PP15

PP27 PP28 QQ09 QQ10 QQ25 QQ37 QQ48 RR04 RR05 RR21

SS11 SS21 TT04 VV00 VV04 WW00 WW01 XX01 XX03 XX09

XX10 XX24 XX25 XX28