**(19) 대한민국특허청(KR)**

**(12) 등록특허공보(B1)**

(51) Int. Cl.<sup>6</sup>

H01L 21/336

(45) 공고일자 1999년03월30일

(11) 등록번호 특0171437

(24) 등록일자 1998년10월20일

(21) 출원번호 특1994-004934

(65) 공개번호 특1994-022675

(22) 출원일자 1994년03월12일

(43) 공개일자 1994년10월21일

(30) 우선권주장

93-79004 1993년03월12일 일본(JP)

93-79005 1993년03월12일 일본(JP)

(73) 특허권자

가부시끼 가이샤 한도따이 에네르기 겐큐쇼 야마자끼 순베이

일본국 가나가와엔 아쓰기시 하세 398

(72) 발명자

장충용

일본국 가나가와엔 야마또시 후까마다이 1-10-15 파레스 미야가미 302

다까야마 도루

일본국 가나가와엔 요꼬하마시 미도리구 가모이 1-16-1 1-1104

다께무라 야스히코

(74) 대리인

일본국 가나가와엔 아쓰기시 하세 931-1 플랫 아쓰기 208

이병호, 최달용

**심사관 : 정희환**

**(54) 반도체 회로 및 그 제조 방법**

**요약**

본 발명은 박막 트랜지스터(thin-film transistors; TFTs) 및 TFTs 제조 방법에 관한 것이다. 또한 본 발명은 복수개의 TFTs를 사용하는 반도체 회로 및 반도체 회로 제조 방법에 관한 것이기도 하다. 본 발명에 따라 제조된 박막 트랜지스터는 유리등의 절연 기판상에 또는 단결정(single crystal) 실리콘으로된 반도체 기판상에 형성된다. 특히, 본 발명은 액정 표시 장치 등에 사용되는 모놀리식형(monolithic) 액티브-매트릭스 회로와 같은 매트릭스 회로를 운영하는 저속 매트릭스 회로와 고속 주변 회로를 구비하는 반도체 회로에 적용되어 상당한 장점이 얻어진다.

**대표도**

**명세서**

[발명의 명칭]

반도체 회로 및 그 제조 방법

[도면의 간단한 설명]

제1a도 내지 제1e도는 반도체 회로를 제조하기 위해 연속적으로 수행되는 단계를 설명하는 본 발명의 실시예 1에 따른 반도체 회로의 단면도.

제2a도 내지 제2e도는 제1a도 내지 제1e도와 유사하고, 실시예 2에 따르는 반도체 디바이스를 설명하는 단면도.

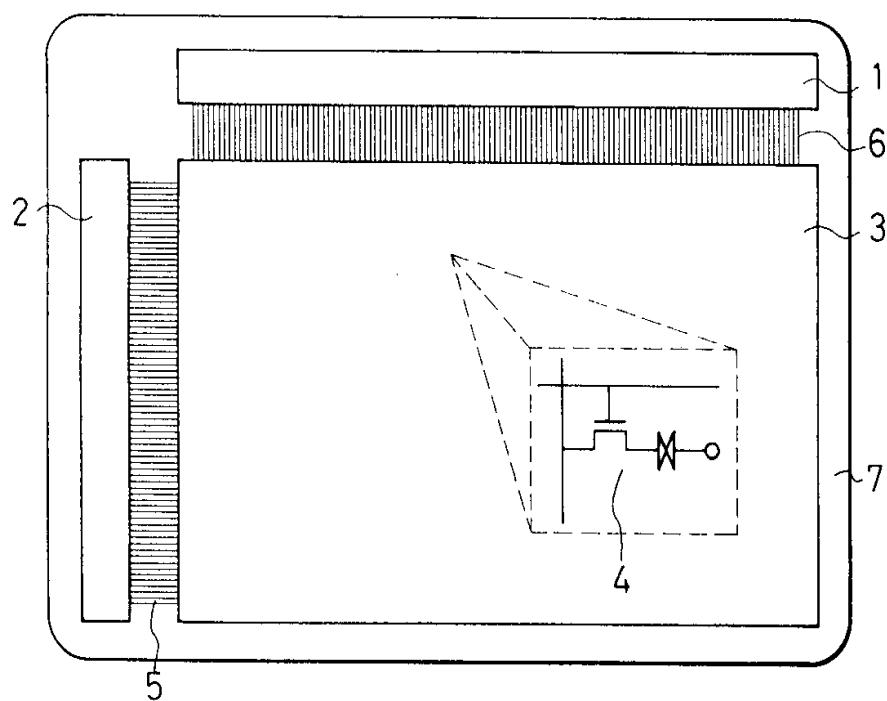

제3도는 모놀리식형(monolithic) 액티브 매트릭스 회로의 다이어그램.

제4a도 내지 제4e도는 반도체 회로를 제조하기 위해 연속적으로 수행되는 단계를 설명하는 본 발명의 실시예 3에 따르는 반도체 회로의 단면도.

제5a도 내지 제5e도는 제4a도 내지 제4e도와 유사하고, 실시예 4에 따르는 반도체 디바이스를 설명하는 단면도.

#### \* 도면의 주요부분에 대한 부호의 설명

|                    |                               |

|--------------------|-------------------------------|

| 10,21 : 기판         | 12,23 : 비결정 실리콘막              |

| 13 : 규화 니켈막        | 14a, 14b : 실리콘 아일랜드 영역        |

| 15 : 게이트 절연막       | 16a 내지 16c : 게이트 전극           |

| 17a,30a : N형 도핑 영역 | 17b, 17c, 30b, 30c : P형 도핑 영역 |

| 18,31 : 총간 절연물     | 19,32 : 화소 전극                 |

| 20a 내지 20e : 배선    | 30a 내지 33e : 배선               |

[발명의 상세한 설명]

#### [발명의 분야]

본 발명은 박막 트랜지스터(thin-film transistors; TFTs) 및 TFTs 제조 방법에 관한 것이다. 또한 본 발명은 복수개의 TFTs를 사용하는 반도체 회로 및 반도체 회로 제조 방법에 관한 것이기도 하다. 본 발명에 따라 제조된 박막 트랜지스터는 유리등의 절연 기판상에 또는 단결정(single crystal) 실리콘으로된 반도체 기판상에 형성된다. 특히, 본 발명은 액정 표시 장치 등에 사용되는 모놀리식형(monolithic) 액티브-매트릭스 회로와 같은 매트릭스 회로를 운영하는 저속 매트릭스 회로와 고속 주변 회로를 구비하는 반도체 회로에 적용되어 상당한 장점이 얻어진다.

#### [발명의 배경]

근래에, 박막형상의 활성층(일명 활성 영역이라고도 함)을 가진 절연 게이트 반도체 디바이스가 연구 개발되어 왔다.

특히, TFT로 알려진 박막 형상의 절연 게이트 트랜지스터가 일찍이 연구 개발되어져 왔다. 이러한 종류의 트랜지스터는 투명한 절연 기판상에 형성되고 매트릭스 구조를 가진 액정 표시와 같은 표시 기구의 각각의 화소(pixel)를 조절하거나 또는 드라이버 회로를 형성하는데 사용된다. 사용되는 반도체의 결정 재료 또는 결정 상태에 따라 비결정 실리콘 TFTs 또는 결정 실리콘 TFTs로 분류된다.

일반적으로, 비결정 반도체는 작은 전계 이동도를 가지며, 그래서 이들은 고속도고 동작하는데 요구되는 TFTs에 사용될 수 없다. 따라서, 근래에 결정 실리콘 TFTs가 연구 개발되어져 고성능의 회로 구조로 개발되어져 왔다.

결정 반도체가 비결정 반도체보다 훨씬 높은 전계 이동도를 가지므로 결정 반도체는 보다 빠른 속도에서 동작 가능하다. 결정 실리콘이라는 면에서, PMOS TFTs는 NMOS TFTs와 같이 제조될 수 있다. 예로서, 알려진 바와 같이 액티브 매트릭스 액정 표시의 주변 회로는 액티브 매트릭스 회로 부분과 유사한 CMOS 결정형 TFTs와 복합된다. 즉, 이것은 모놀리식형 구조이다.

제3도는 액정 표시에 사용되는 모놀리식형 액티브 매트릭스 회로(monolithic active-matrix circuit)의 블록 다이어그램이다. 열 디코더(column decoder; 1)와 행 디코더(row decoder; 2)가 기판(7)상에 형성되어 주변 드라이버 회로를 형성한다. 트랜지스터와 캐패시터로 각각 구성된 화소 회로(4)는 매트릭스 영역(3)에 형성된다. 매트릭스 영역은 전도성 배선(5, 6)으로 주변 회로에 접속된다. 주변 회로에 사용되는 TFTs는 고속도로 동작하는 것이 요구되고, 반면에 화소 회로에 사용되는 TFTs는 저 누설 전류(leakage current)를 가지는 것이 요구된다.

이들 특성은 물리적으로 모순되는 것이지만 동일 기판상에 동시에 두 종류의 TFTs를 형성하는 것이 요구되고 있다.

그런데, 동일한 공정으로 구조된 모든 TFTs는 유사한 특성을 나타낸다. 예로서, 열간 어닐링(thermal annealing)으로 구조되는 결정 실리콘을 사용하는 TFTs, 매트릭스 영역에 사용되는 TFTs 및 주변 드라이버 회로에 TFTs 모두는 유사한 특성을 가지고 있다. 주변 드라이버 회로용으로 적합한 고 이동도 및 화소 회로용으로 적합한 저 누설 전류를 동시에 얻어지는 것은 어렵다. 열간 어닐링과 선택적인 레이저 어닐링을 사용한 결정화를 동시에 사용하여 상기 어려움을 해결하는 것이 가능했다. 이러한 경우에, 열간 어닐링에 의해 구조된 TFTs가 매트릭스 영역에 사용되며, 여기서 레이저 어닐링으로 구조된 TFTs는 주변 드라이버 회로 영역에 이용된다. 그런데, 레이저 어닐링으로 결정화된 실리콘의 결정은 극히 낮는 균질성을 갖는다. 특히, 무결함이 요구되는 주변 드라이버 회로에 이를 TFTs를 사용하기는 곤란하다.

또한, 결정 실리콘을 얻기 위해 레이저 어닐링에 의존하는 결정화를 사용할 수 있다. 만일 반도체 회로가 레이저 어닐링으로 결정화되는 실리콘으로부터 제조되면 매트릭스 영역에 TFTs와 주변 드라이버 회로에 TFTs 모두가 유사한 특성을 갖는다. 따라서, 선택적인 실리콘 결정화 방법이 완성될 수 있다. 특히, 매트릭스 영역의 TFTs는 열간 어닐링을 사용하여 형성된다. 주변 드라이버 회로의 TFTs는 레이저 어닐링을 사용하여 형성된다. 그런데, 열간 어닐링이 채택되는 곳에서는 실리콘은 24시간 동안 600°C로 어닐링되거나 또는 실리콘이 1000°C를 초과하는 고온에서 어닐링되어야만 한다. 앞의 방법에서는 처리량이 떨어지고,

뒤의 방법에서는 활용가능한 기판의 재료가 석영(quartz)으로 한정된다.

#### [발명의 요약]

본 발명의 목적은 생산율 또는 생산 가격을 나쁘게하지 않고 복잡한 공정에 의지하지 않고 반도체 회로를 제조하는 방법을 제공하는 것이다.

본 발명의 다른 목적은 공정에 최소한의 변화로 두종류의 TFTs의 대량 생산을 용이하게 하는 방법을 제공하는 것이며, 두 종류중 한개는 고 이동도를 가지도록 요구되고 다른 한개는 저 누설 전류를 가지도록 요구되는 것이다.

본원의 연구팀은 거의 비결정의 실리콘 막에 미량의 촉매 물질을 첨가하는 것은 결정화를 향상시키고, 결정화 온도가 낮았으며, 결정화 시간을 짧게한다는 것을 밝혔다. 접촉 재료로는 니켈(Ni), 철(Fe), 코발트(Co) 및 백금의 단일 물질과 그 규소화합물을 포함한다. 특히, 촉매 원소를 가진 막, 원소의 입자 또는 원소의 클러스터(clusters)는 비결정 실리콘 막과 제1막이 밀착하도록 비결정 실리콘 막 위에 또는 밑에 제1막을 형성하는데 사용된다. 다르게는, 상기 촉매 원소가 이온 주입 또는 다른 방법으로 비결정 실리콘 막내로 주입된다. 다음에, 막은 8시간내의 짧은 시간에 적절한 온도로 일반적으로 580°C 이하에서 열간 어닐링된다. 그 결과, 비결정 막이 결정화된다.

막이 촉매 원소로 제조되는 곳에서 원소의 밀도는 충분히 낮으므로 막은 극히 얇다. 이러한 막을 형성하기 위해서 스팍터링 또는 진공 증발과 같은 진공 펌프를 사용하는 방법이 이용된다. 또한, 스핀 코팅(spin coating) 또는 디핑(dipping)과 같은 대기압 하에서 수행되는 방법이 활용된다. 이런 대기압 방법은 높은 생산성을 제공하고, 수행이 용이하다. 이러한 경우에, 촉매 원소를 함유한 초산염(acetate), 질산염(nitrate), 유기염(organic salt) 등이 적절한 용매로 용해되고 농도는 적절한 값으로 조정된다.

비결정 실리콘 막이 CVD법으로 형성될때 촉매 물질이 원료(raw material) 가스에 첨가된다. 비결정 실리콘 막이 스팍터링과 같은 물리적 증착법(physical vapor deposition)으로 형성될때 촉매 물질이 막 형성을 위해 타겟트(target) 또는 증착원(evaporation source)에 첨가될 수 있다. 물론 어닐링 온도가 상승하면 결정화 시간은 짧아진다. 더우이, 니켈, 철, 코발트 및 백금의 농도가 증가되면 결정화 온도가 저하되고 결정화 시간이 짧아진다. 본 발명인의 연구에서는 결정화를 진행시키기 위해서 상기 원소중 하나 이상의 농도가  $10^{17} \text{ cm}^{-3}$ 를 초과할 필요성을 발견하였다. 양호하게, 농도는  $5 \times 10^{18} \text{ cm}^{-3}$  이상이 좋다.

전술된 모든 촉매 물질이 실리콘에는 좋지 않으므로, 그 농도는 가능한 낮게 하는 것이 좋다. 본 발명인의 연구에서는 이들 촉매 물질의 전체 농도가  $1 \times 10^{20} \text{ cm}^{-3}$ 를 넘지 않는 것이 좋다는 것을 알았다. 또한 국부(local) 농도(예로서, 입자 경계)는  $1 \times 10^{20} \text{ cm}^{-3}$ 를 넘지 않는 것이 좋다.

본 발명에서, 액티브 매트릭스 회로를 구동하기 위한 TFTs로서 사용되고 고속도로 동작하는 TFTs는 레이저 결정화로 선택적으로 형성된다. 다르게는, 액티브 매트릭스 회로의 화소의 저 누설 전류 TFTs로서 사용되고 상대적인 저 속도로 동작하는 TFTs는 전술된 촉매 원소에 의해 촉진되는 결정화 특성을 능동적으로 사용하여 구조된다. 후자의 TFTs를 형성하기 위해서, 실리콘이 짧은 시간의 저 온도로 결정화된다. 그 결과, 일반적으로 상반되는 특성인 저 누설 전류와, 고속도 동작 모두를 달성하는 트랜지스터를 가진 회로가 동일 기판상에 형성된다.

또한, 본 발명자는 니켈, 철, 코발트, 백금 및 팔라듐과 같은 촉매 원소를 함유한 막이 레이저 광 또는 다른 같은 성질의 광으로 조사되면, 촉매 원소의 농도가 열평형 상태에서 결정화를 수행하는데 정상적으로 필요한 농도보다 훨씬 작더라도, 극히 빠른 결정화가 일어난다는 것을 발견했다. 일반적으로, 앞의 농도는 뒤의 농도의 1/10 보다 낮다.

보다 특정하게, 결정화는  $1 \times 10^{15}$  내지  $1 \times 10^{19} \text{ cm}^{-3}$ , 양호하게는  $1 \times 10^{16}$  내지  $5 \times 10^{17} \text{ cm}^{-3}$ 로 이들 촉매 원소의 농도를 설정하여 진행된다. 다음에 막은 적절한 에너지의 레이저 광 또는 다른 동일한 성질의 광으로 조사된다. 레이저 광 또는 다른 동일한 성질의 광의 에너지 밀도는 조사되는 광의 파장, 필스폭, 비결정 실리콘 막(또는 결정 실리콘) 및 다른 인자들에 따라서 변화된다. 예로서, 비결정 실리콘의 온도가 100 내지 450°C, 양호하게는 250 내지 350°C로 설정되면 결정화는 더 낮은 농도의 촉매 원소로 달성될 수 있다.

본 발명에서, 비결정 실리콘 막은 전술된 촉매 물질을 사용하는 결정 특징을 활용하여 형성된다. 촉매 원소를 함유하는 물질로 만들어진 막은 비결정 실리콘 막과 깊이(intimate) 접촉하거나 또는 원소가 비결정 실리콘 막에 첨가된다. 다음에, 비결정 막이 레이저 광 또는 다른 동일한 성질의 광으로 조사받아 비결정 실리콘 막을 결정화시킨다. 이때, 촉매 원소를 함유한 물질이 기판의 선택 부위와 깊이 접촉하거나 이들 부위로 도입된다. 이어서, 막은 레이저 광 또는 다른 동일한 성질의 광으로 조사 또는 주사된다. 이러한 방식에서는 결정도의 차이가 있는 실리콘 막이 동일 기판상에 형성된다. 또한, 레이저 조사 전에 350–650°C에서(바람직하게는 400–550°C) 1 내지 24시간(바람직하게는 2 내지 8시간) 동안 예비 어닐링이 수행될 수 있다.

이러한 방식으로, 결정화가 향상되게 된다. 더우이, 열 어닐링만이 도입되어 제거되지 않는 입자 경계부에 장벽이 낮아지게 된다. 또한, 입자 경계부에 남아있는 비결정 성분도 결정화된다. 이러한 방법이 채택되는 곳에서는 열 어닐링에 의해 달성되는 결정화가 낮더라도 이어지는 레이저 조사로 완전한 결정이 달성될 수 있다. 따라서, 사용되는 촉매 원소의 농도는 낮게 된다.

본 발명에서, 촉매 원소로 도핑된 영역의 결정화는 예비 어닐링이 레이저 조사전에 수행되든지 안되든지, 촉매 원소가 적게 도핑된 결정화 영역위에 수반되는 레이저 조사에 의해 향상된다. 더욱이, 얻어진 TFTs는 비결정 실리콘 막이 레이저 광으로 조사되는 종래의 레이저 어닐링으로 제조되는 TFTs의 성질과 비견되거나 우월한 특성을 나타낸다. 또한, 이러한 특성들은 종래의 레이저 어닐링에서 사용되는 레이저 광의 에너지보다 덜한 레이저 광 또는 다른 동일한 성질의 광의 에너지에 의해서도 안정되게 얻어진다. 다르게는, 촉매 원소로 도핑되지 않은 영역은 레이저 조사에 의해 결정화된다. 또한 이러한 경우에 안정된 특성

은 종래의 레이저 어닐링에 사용되는 레이저 광의 에너지보다 덜한 레이저 광 또는 다른 동일한 성질의 광 에너지를 만들어 얻어진다. 물론, 촉매 원소로 도핑되지 않은 영역의 특성은 촉매 원소로 도핑된 영역의 특성보다는 열등하다.

이러한 특징을 사용하므로, 촉매 원소로 연하게 도핑된 영역은 액티브 매트릭스 회로의 화소 회로에 저 누설 전류 TFTs를 형성하는데 사용된다. 촉매 원소로 농후하게 도핑된 영역은 주변 드라이버 회로에 사용되는 고속도 TFTs를 형성하는데 사용된다. 결과적으로, 일반적으로 상호 상충되는 저 누설 전류와 고속도 동작 모두를 달성하는 트랜지스터를 가진 회로가 기판상에 형성된다.

본 발명에서 저 누설 전류를 가지도록 요구되는 TFTs 형성 부분에 촉매 원소의 농도는 고속도 TFTs 형성 부분에 촉매 원소의 농도보다 낮게 될 필요성이 있다. 이 격차를 더 크게 하거나 누설 전류를 더 낮게 하기 위해서, 저 누설 전류를 가지도록 요구되는 TFTs의 활성 영역에 촉매 원소의 농도는  $1 \times 10^{15} \text{ cm}^{-3}$  보다 작은 것이 바람직하다.

본 발명의 다른 목적 및 특징들을 도면을 참조로 하여 상세히 기술하면 다음과 같다.

#### [발명의 상세한 설명]

##### [실시예 1]

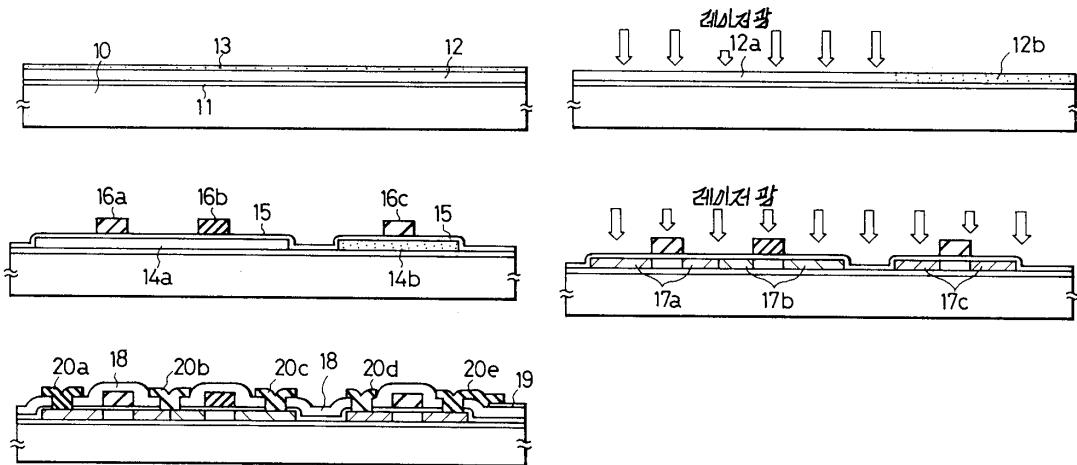

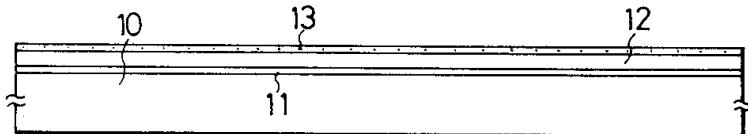

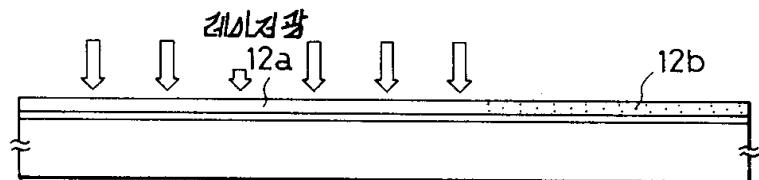

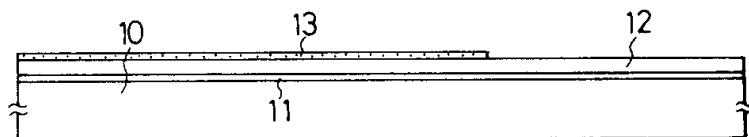

본 실시예는 제3도에 도시된 바와 같이 단독 유리 기판상에 형성된 액티브 매트릭스 회로 및 상기 액티브 매트릭스 회로 주위에 형성된 드라이버 회로(driver circuit)를 포함하는 반도체 회로에 관한 것이다. 제 1a도 내지 제1e도는, 상기 장치를 제조하기 위하여 연속적으로 수행되는 단계를 도시한, 본 실시예에 따른 반도체 회로의 획단면도이다. 먼저, 산화 실리콘 코팅(Corning 7059)로 제조된 기판(10)상에 2000 Å의 두께까지 기저막(base film; 11)으로 스팍터링된다. 500 내지 1500 Å, 예로서, 1500 Å의 두께를 가진 본질적인 비결정 실리콘 막(12)이 LPCVD에 의해 산화 실리콘 막(11)위에 형성된다. 그 직후에, 규화 니켈이 스팍터링에 의해 5 내지 200 Å, 예로서, 20 Å의 두께를 가진 막(13)으로 증가되었다. 상기 규화 니켈막(13)은 화학식  $\text{NiSi}_x$ ( $0.4 \leq x \leq 2.5$ , 예로서,  $x=2.0$ )에 의해 주어진다.

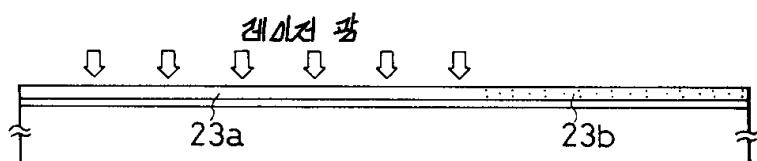

그뒤, 박막은 레이저 광에 의해 선택적으로 조사되어 소정의 영역을 결정화 했다. 248nm의 파장과 20nsec의 폴스폭을 가지는 광을 발산하는 KrF 액시머 레이저가 조사에 사용되었다. 353nm의 파장을 가지는 광을 발생하는 XeF 액시머 레이저, 308nm의 파장을 가지는 광을 발산하는 XeCl 액시머 레이저, 193nm의 파장을 가지는 광을 발산하는 ArF 액시머 레이저 및 기타 레이저 등과 같은 다른 레이저가 이용될 수도 있다. 레이저 광의 에너지 밀도는 200 내지 500mJ/cm<sup>2</sup>, 예로서, 350mJ/cm<sup>2</sup>이었다. 레이저 광이 2 내지 10회, 예로서, 2회 각 위치에 대해 발산되었다. 레이저 조사동안에, 기판은 200 내지 450°C, 예로서, 300°C까지 가열되었다.

제3도에 도시된 바와 같이, 레이저 조사에 의해 결정화되는 주변 회로 범위는 열적 어닐링(annealing)에 의해 처리되기에 충분한 매트릭스 변위로부터 상당한 거리만큼 이격되어 있다. 따라서, 포토리소그래픽(photolithographic)이 필요하지 않았다.

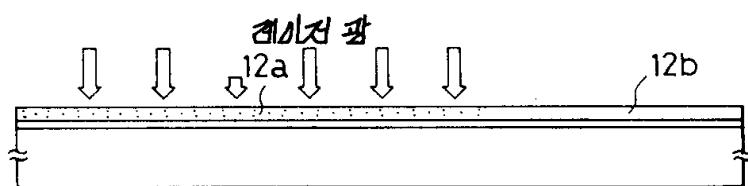

그뒤, 박판의 레이저 광으로 조사되지 않은 영역(액티브 매트릭스 회로의 화소)을 결정화시키도록 환원 분위기내에서 4시간동안 500°C에서 어닐링되었다. 그 결과, 두 종류의 결정 실리콘 영역(12a, 12b)이 얻어졌다. 영역(12a)의 필드 이동성이 레이저 결정화 단계에 의해 향상되었다. 한편, 열적 어닐링에 의해 결정화된 영역(12b)은 낮은 누설 전류를 가진다(제1b도).

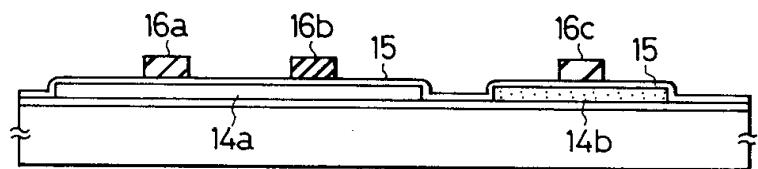

이러한 방법으로 얻어진 실리콘막은 포토리소그래픽적으로 패턴팅되어 주변 드라이버 회로를 형성하는 실리콘 아일랜드 영역(14a)과 매트릭스 영역을 형성하는 실리콘 아일랜드 영역(14b)을 형성하였다. 산화 실리콘은 스팍터링에 의해 1000 Å의 두께를 가지는 게이트 절연막(15)으로 증착되었다. 산화 실리콘으로 구성된 타겟이 스팍터링 공정 동안에 사용되었다. 스팍터링동안 기판 온도는 200 내지 400°C, 예로서, 350°C였다. 스팍터링 분위기는 산소와 아르곤으로 구성되었다. 아르곤 대 산소의 비는 0 내지 0.5, 예로서, 0.1 이하였다. 0.1 내지 2%의 인을 함유한 실리콘은 6000 내지 8000 Å, 예로서, 6000 Å의 두께까지 LPCVD에 의해 증착되어 실리콘 막을 형성하였다. 산화 실리콘 막을 형성하는 단계와 실리콘 막을 형성하는 단계가 연속적으로 수행되는 것이 바람직하다. 실리콘 막은 게이트 전극(16a, 16b, 16c)을 형성하도록 패턴팅되었다(제1c도).

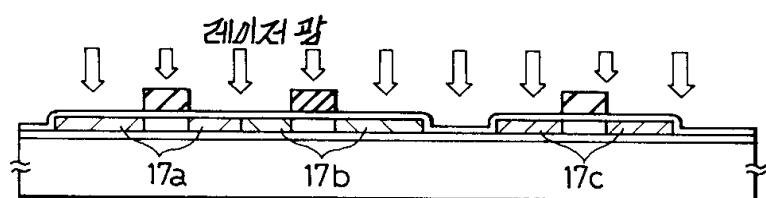

그뒤, 게이트 전극으로 실리콘 영역을 마스킹(masking)함으로써, 인과 붕소로 구성된 불순물이 플라즈마 도핑에 의해 실리콘 영역내로 주입되었다. 포스핀( $\text{PH}_3$ ) 및 디보란(diborane:  $\text{B}_2\text{H}_6$ )이 도핑 가스로 사용되었다. 전자의 가스가 사용된 곳에는 가속 전압이 60 내지 90KV, 예로서, 80KV 이었고, 후자의 가스가 사용된 곳에는 가속 전압이 40 내지 80KV, 예로서, 65KV이었다. 투여량(dose)은  $1 \times 10^{15}$  내지  $8 \times 10^{15} \text{ cm}^{-2}$  였다.

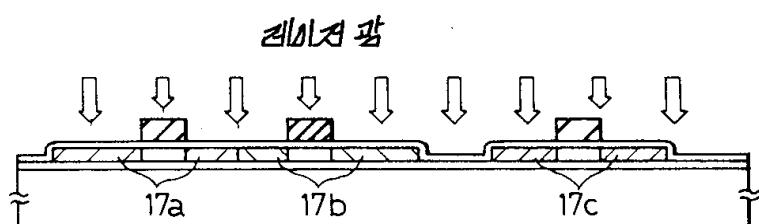

인의 경우에 투여량은  $2 \times 10^{15} \text{ cm}^{-2}$  이었고, 붕소의 경우에 투여량은  $5 \times 10^{15} \text{ cm}^{-2}$  이었다. 그 결과 N형 도핑 영역(17a), P형 도핑 영역(17b, 17c)이 형성되었다.

그 다음에, 불순물이 레이저 어닐링에 의해 활성화되었다.

248nm의 파장과 20nsec의 폴스폭을 가지는 광을 발산하는 KrF 액시머 레이저가 레이저 어닐링에 사용되었다. 353nm의 파장을 가지는 광을 발산하는 XeF 액시머 레이저, 308nm의 파장을 가지는 광을 발산하는 XeCl 레이저, 193nm의 파장을 가지는 광을 발산하는 ArF 액시머 레이저 및 기타 레이저 등과 같은 다른 레이저가 사용될 수도 있다. 레이저 광의 에너지 밀도는 200 내지 400mJ/cm<sup>2</sup>, 예로서, 250mJ/cm<sup>2</sup>이다. 레이저 광의 2 내지 10회, 예로서, 2회가 각 위치에 대해 발산되었다.

레이저 조사 동안에, 기판은 200 내지 450°C까지 가열될 수 있다. 레이저 조사대신에, 박막이 450 내지 500°C에서 2 내지 8시간동안 어닐링될 수 있다. 이 방법에서, 도핑된 영역(17a-17c)은 활성화되었다(제1d도).

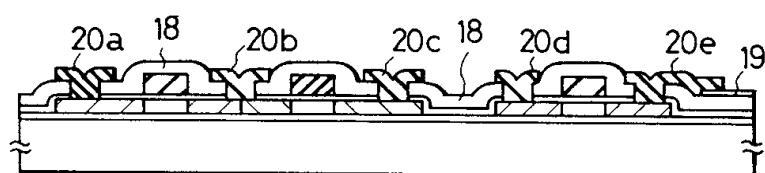

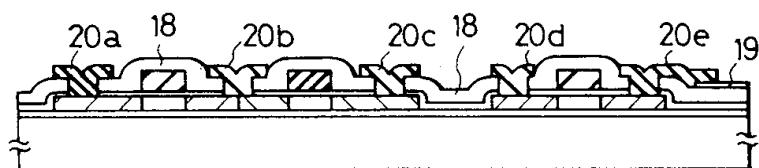

그후, 산화 실리콘이 플라즈마 CVD에 의해 6000 Å의 두께를 가진 층간 절연물(18)로 층착되었다. 인듐 석산화막(ITO)이 500 내지 1000 Å, 예컨대 800 Å 까지 스퍼터링되었고, 화소 전극(19)을 형성하도록 패턴링되었다. 접촉 구멍이 층간 절연물(18)내에 형성되었다. 주변 드라이버 회로를 형성하는 TFT를 위한 전극 및 전도성 배선(20a, 20b, 20c)과 매트릭스 화소 회로를 형성하는 TFT를 위한 전극 및 전도성 배선(20d, 20e)이 금속 재료, 예로서, 질화 티타늄 및 알루미늄의 다층막으로 부터 형성되어 있다. 최종적으로, 박막이 수소 분위기 속에서 350°C 1기압에서 30분 동안 어닐링되었다. 이러한 방법으로, 반도체 회로가 완성되었다(제1e도).

얻어진 TFT의 활성 영역내의 니켈 농도는 2차 이온 질량 분광기(secondary ion mass spectroscopy; SIMS)로 측정되었다. 상기 농도는 주변 드라이버 회로와 화소 회로 모두가  $1 \times 10^{18}$  내지  $5 \times 10^{18} \text{ cm}^{-3}$  였다.

### [실시예 2]

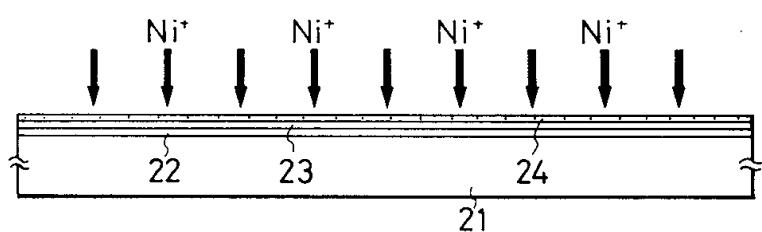

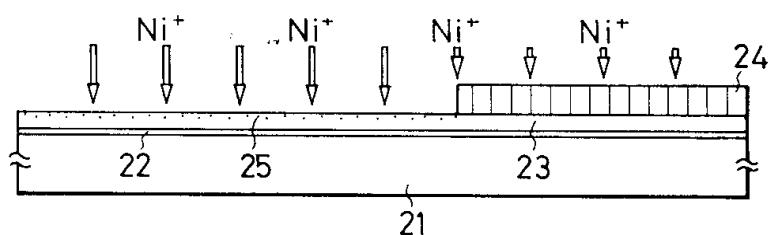

제2a도 내지 제2e도는 본 실시예를 제조하기 위하여 연속적으로 수행되는 단계를 도시한 횡단면도이다. 산화 실리콘은 코닝 7059로 제조된 기판(21)상에 2000 Å의 두께를 가진 산화 실리콘 막(22)으로 스퍼터링 되었다. 그뒤, 200 내지 1500 Å, 예로서, 500 Å의 두께를 가지는 비결정 실리콘 막(23)이 LPCVD에 의해 산화 실리콘 막(22)상에 형성되었다. 니켈 이온이 주입되어 비결정 실리콘 막의 표면내에 영역(24)을 형성하였고, 상기 영역(24)은  $1 \times 10^{18}$  내지  $2 \times 10^{19} \text{ cm}^{-3}$  농도의 니켈로 도핑된다. 도핑 영역(24)의 깊이는 200 내지 500 Å 였다. 가속 에너지는 도핑된 영역의 깊이에 따라 선택되었다(제2a도).

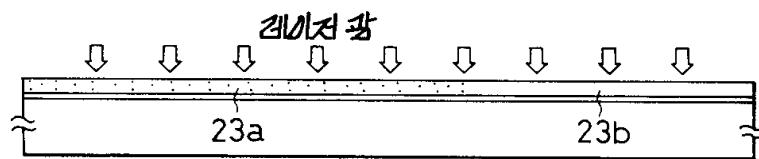

그후, 비결정 실리콘 막은 소정 영역을 결정화시키는 레이저 광으로 선택적으로 조사되었다. 248nm의 파장과 20nsec의 펄스폭을 가지는 광을 발산하는 KrF 액시머 레이저가 상기 레이저 조사에 사용되었다. 레이저 광의 에너지 밀도는 200 내지 500mJ/cm<sup>2</sup>, 예로서, 350mJ/cm<sup>2</sup> 였다. 레이저 광이 2 내지 10회, 예로서, 2회 각 위치에 대해 발산되었다. 레이저 조사동안에, 기판은 200 내지 450°C, 예로서, 400°C까지 가열되었다. 박판은 비결정 실리콘 막의 조사되지 않은 부분을 결정화시키기 위하여 환원 분위기 내에서 500°C로 4시간동안 어닐링되었다. 이러한 결정화 단계의 결과, 두 종류의 결정 실리콘(23a, 23b)이 얻어졌다(제2b도).

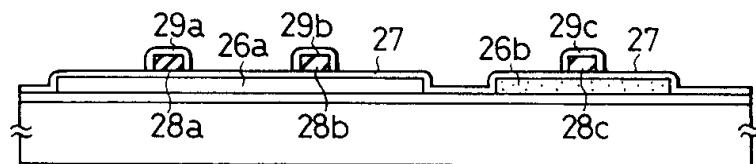

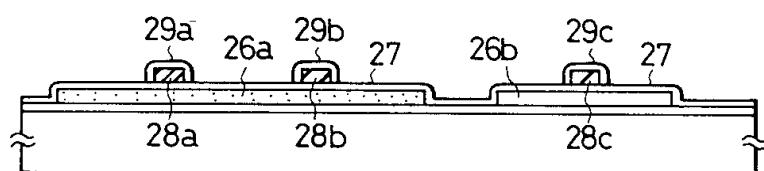

그후, 실리콘 막이 실리콘 아일랜드 영역(26a; 주변 드라이버 회로 영역) 및 (26b; 매트릭스 화소 회로 영역)을 형성하도록 패턴링되었다.

TFT의 게이트 절연막으로, 1000 Å의 두께를 가지는 산화 실리콘 막(27)이 테트라에톡시실란(tetraethoxysilane; TEOS; Si(OC<sub>2</sub>H<sub>5</sub>)<sub>4</sub>)와 산소로부터 형성되었다.

트리클로로에틸렌(trichloroethylene; C<sub>2</sub>HCl<sub>3</sub>)이 원료 가스에 첨가되었다. 막의 형성전에, 산소가 400SCCM의 유량으로 챔버내에 공급되었다. 플라즈마가 300°C의 기판 온도, 5Pa의 총압력과 150W의 RF파워에서 발생되었다.

이러한 조건은 10분동안 유지되었다. 그 다음에, 산소, TEOS 및 트리클로로에틸렌이 300SCCM, 15SCCM 및 2SCCM의 유량으로 챔버내에 첨가되었다. 이러한 방법으로, 산화 실리콘 막이 형성되었다. 기판의 온도는 300°C였고, RF 파워는 75W, 총 압력은 5Pa 였다. 막이 완성된 후에, 수소가 100torr의 압력으로 챔버내에 도입되었다. 박판은 350°C에서 35 분동안 어닐링되었다.

그다음에, 2% 실리콘을 함유하는 알루미늄이 6000 내지 8000 Å, 예로서 6000 Å의 두께를 가진 알루미늄막으로 스퍼터링에 의해 층착되었다. 탄탈, 텅스텐, 티타늄, 또는 몰리브데니이 알루미늄 대신에 사용될 수도 있다. 산화 실리콘 막(27)을 형성하는 단계와 알루미늄 막을 형성하는 단계는 연속적으로 수행되는 것이 바람직하다. 알루미늄 막은 TFT의 게이트 전극(28a, 28b, 28c)을 형성하도록 패턴링되었다. 알루미늄 배선의 표면은 그 표면상에 산화물 층(29a, 29b, 29c)을 형성하도록 양극 산화되었다. 양극 산화는 주석산의 1 내지 5% 에틸렌 글리콜 용액내에서 실행되었다. 얻어진 산화물 층의 두께는 2000 Å 였다(제2c도).

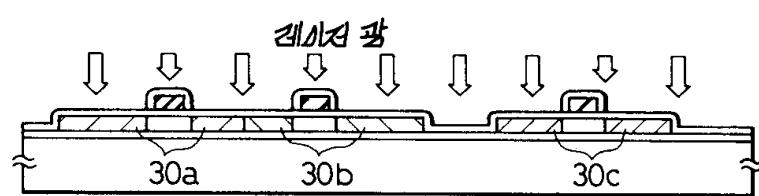

그뒤, 불순물, 즉, 인이 플라즈마 도핑에 의해 실리콘 영역내로 주입되었다. 포스핀(PH<sub>3</sub>)이 도우편트 가스(dopant gas)로 사용되었다. 가속 전압은 60 내지 90KV, 예로서 80KV 였고, 투여량은  $1 \times 10^{15}$  내지  $8 \times 10^{15} \text{ cm}^{-2}$ , 예로서,  $2 \times 10^{15} \text{ cm}^{-2}$  였다. 이러한 방법으로, N형 도핑 영역(30a)이 형성되었다. 포토레지스트로 좌측 TFT(N-채널 TFT)를 마스킹함으로써, 불순물 즉 불소가 플라즈마 도핑에 의해 우측 주변 회로 영역 TFT의 실리콘 영역 및 매트릭스 회로를 다시 형성하는 TFT의 실리콘 영역내로 주입되었다. 디보란(B<sub>2</sub>H<sub>6</sub>)이 도우편트 가스로 사용되었다. 가속 전압은 50 내지 80KV, 예로서 65KV 였고, 투여량은 앞서 주입된 인의 투여량 보다 큰  $1 \times 10^{15}$  내지  $8 \times 10^{15} \text{ cm}^{-2}$ , 예로서,  $5 \times 10^{15} \text{ cm}^{-2}$  였다. 이 방법으로, P형 도핑 영역(30b, 30c)이 형성되었다.

그뒤, 불순물이 레이저 어닐링에 의해 활성화되었다. 248nm의 파장과 20nsec의 펄스폭을 가지는 광을 발산하는 KrF 액시머 레이저가 레이저 조사에 사용되었다. 레이저 광의 에너지 밀도는 200 내지 400mJ/cm<sup>2</sup>, 예로서, 250mJ/cm<sup>2</sup> 였다. 레이저 광이 2 내지 10회, 예로서, 2회가 각 위치에 대해 발산되었다(제2d도).

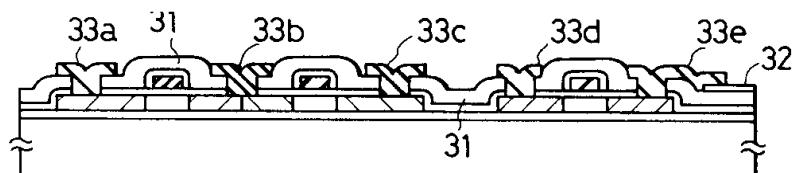

그다음에, 2000 Å의 두께를 가지는 산화 실리콘 막(31)이 플라즈마 CVD에 의해 TEOS로부터 층간 절연물로 형성되었다. 인듐 주석 산화물(ITO)이 스퍼터링에 의해 500 내지 1000 Å, 예로서, 800 Å의 두께를 가지는 인듐 주석 산화물 막으로 층착되었다. 이 막은 화소 전극(32)을 형성하도록 애칭되었다. 접촉 구멍이 층간 절연물(31)내에 형성되었다. 소스 및 드레인 전극, 주변 드라이버 회로 및 전극의 TFT를 위한 전도성 배선(33a, 33b, 33c) 및 매트릭스 화소 회로의 TFT를 위한 전도성 배선(33d, 33e)이 질화 티타늄 및 알루미늄과 같은 금속 재료의 다층막으로 부터 형성되었다. 이러한 방법으로, 반도체 회로가 완성되었다(제2e도).

제조된 반도체 회로의 주변 드라이버 회로의 TFT 특성은 종래의 레이저 결정화에 의해 제조된 TFT 특성에 대해 결코 떨어지지 않았다. 본 실시예에 따른 TFT를 사용함으로써 시프트 레지스터(shift register)가 형성되었다. 이러한 시프트 레지스터는 15V의 드레인 전압에 대해 11MHz에서, 17V의 드레인 전압에 대해

16MHz에서 작동하는 것이 확인되었다. 또한, 신뢰성 테스트에서, 본 발명의 TFT와 종래 방법으로 제조된 TFT 간에 차이가 없음을 발견하였다. 매트릭스 영역(화소 회로)내의 TFT 특성에 관하여, 누설 전류는  $10^{-13} \text{ A}$  이하였다.

#### [실시예 3]

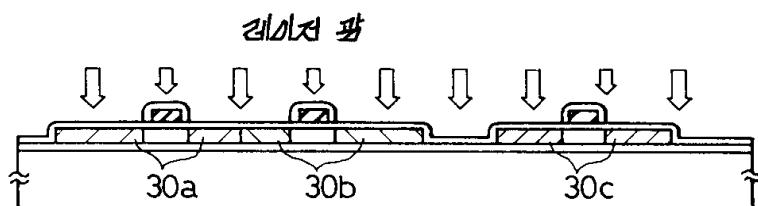

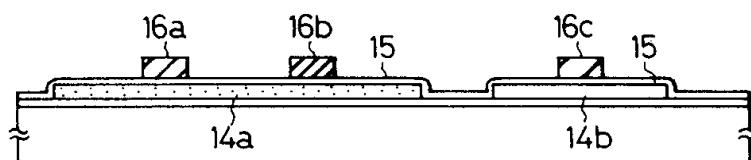

제4a도 내지 제4e도는, 본 실시예에 따른 회로를 제조하기 위하여 연속적으로 수행되는 단계를 도시한 반도체 회로의 획단면도이다. 먼저, 산화 실리콘 코팅 7059로 제조된 기판(10)상에 2000Å의 두께를 가지는 기저층(11)으로 스팍터링되었다. 500 내지 1500Å, 예로서, 500Å의 두께를 가지는 고유 형태(1)의 비결정 실리콘 막(12)이 플라즈마 CVD에 의해 기저층(11)상에 형성되었다. 그 직후, 5 내지 200Å, 예로서, 50Å의 두께를 가지며  $1 \times 10^{18} \text{ cm}^{-3}$  농도의 니켈을 함유하는 실리콘 막(13)이 도시된 바와 같이 스팍터링에 의해 선택적으로 형성되었다. 라프트 오프(lift-off) 공정이 이러한 니켈막(13)을 제조하기 위하여 사용되었다. 스팍터링 대신에, 스피너 코팅이 사용될 수 있다(제4a도).

비결정 실리콘 막(12)의 전체 표면이 결정화되기 위하여 레이저 광으로 조사되었다. 이러한 레이저 조사용으로, 248nm의 파장과 20nsec의 펄스폭을 가지는 광을 발산하는 KrF 액시머 레이저가 조사에 사용되었다.

353nm의 파장을 가지는 XeF 액시머 레이저, 308nm의 파장을 가지는 XeCl 액시머 레이저, 193nm의 파장을 가지는 ArF 액시머 레이저 및 기타 레이저 등과 같은 다른 레이저가 사용될 수도 있다. 레이저 광의 에너지 밀도는 200 내지 500mJ/cm<sup>2</sup>, 예로서, 350mJ/cm<sup>2</sup>이다. 레이저 광이 2 내지 10회, 예로서, 2회 각 위치에 대해 발산되었다. 레이저 조사동안에, 기판은 100 내지 450°C, 예로서, 300°C까지 가열되었다. 그 결과, 비결정 실리콘 막의 전체 표면이 결정화되었다. 그러나, 규화 니켈 막(13) 아래에 위치된 실리콘 막(12a) 영역에 대한 결정화는 니켈이 결정화를 촉진시키기 때문에 다른 영역에서의 실리콘 막(12b) 결정화보다 양호하였다(제4b도).

상기 실리콘 막은 실리콘 아일랜드 영역(14a; 주변 드라이버 회로 영역, 14b; 매트릭스 영역)을 형성하도록 포토-리소그래픽으로 패턴화된다. 산화 실리콘은 스팍터링에 의해 1000Å의 두께를 갖는 게이트 절연막(15)으로서 증착된다. 스팍터링 중에는 산화 실리콘으로 구성되는 타겟이 사용된다. 이 과정에서 기판 온도는 200 내지 400°C이며 예로서, 350°C이다. 스팍터링 분위기는 산소와 아르곤으로 구성된다. 산소에 대한 아르곤의 비율은 0 내지 0.5이고 예로서, 0.1이다. 이어서 예로서, 6000Å와 같이 3000 내지 8000Å의 두께를 갖고 인을 0.1 내지 2% 함유하는 실리콘 막이 LPCVD에 의해 형성된다. 통상적으로, 산화 실리콘 막(15) 형성 단계와 실리콘 막 형성 단계는 연속적으로 이루어진다. 실리콘 막은 게이트 전극(16a, 16b, 16c)을 형성하도록 패턴화된다(제4c도 참조).

따라서, 게이트 전극을 마스크로서 사용하여 불순물이나 인 및 봉소가 플라즈마 도핑에 의해 실리콘 영역에 주입된다. 포스핀(PH<sub>3</sub>)과 디보란(B<sub>2</sub>H<sub>6</sub>)이 도핑 가스로서 사용된다. 포스핀이 사용될 경우 가속 전압은 60 내지 90KV이며 예로서, 80KV이다. 디보란이 사용될 경우 가속 전압은 40 내지 80KV이며 예로서, 65KV이다. 투여량은  $1 \times 10^{15}$  내지  $8 \times 10^{15} \text{ cm}^{-2}$ 이다. 예로서, 인의 투여량은  $2 \times 10^{15} \text{ cm}^{-2}$ 이다. 봉소의 투여량은  $5 \times 10^{15} \text{ cm}^{-2}$ 이다. 그 결과, N형 도핑 영역(17a), P형 도핑 영역(17b, 17c)이 형성된다.

이후, 불순물들은 레이저 어닐링에 의해 활성화된다. 상기 레이저 어닐링을 위해, 파장이 248nm이고 펄스 폭이 20nsec인 광을 발하는 KrF 액시머 레이저가 사용되었다. 파장이 353nm인 광을 발하는 XeF 액시머 레이저, 파장이 308nm인 광을 발하는 XeCl 액시머 레이저, 파장이 193nm인 광을 발하는 ArF 액시머 레이저 및, 기타 레이저와 같은 다른 레이저가 사용될 수도 있다. 레이저 광의 에너지 밀도는 200 내지 400mJ/cm<sup>2</sup>이고, 예로서, 250mJ/cm<sup>2</sup>이다. 매 위치마다 레이저 광이 2 내지 10회, 예로서, 2회 방사된다. 레이저 어닐링 도중에, 기판은 100 내지 450°C까지, 예로서, 250°C까지 가열된다. 이같은 방식으로 도핑 영역(17a 내지 17c)이 활성화된다(제4d도 참조).

이후, 6000Å의 두께를 갖는 산화 실리콘 막(18)이 플라즈마 CVD에 의해 층간 절연물로서 형성된다. 두께가 500 내지 1000Å인, 예로서, 800Å인 인듐 석산화막(ITO)이 스팍터링에 의해 형성된다. 이 막은 화소 전극(19)을 형성하도록 패턴화된다. 이후 층간 절연물에는 접촉 구멍이 형성된다. 주변 드라이버 회로의 전극 및 전도성 배선(20a, 20b, 20c)과 매트릭스 화소 회로의 TFT의 전극 및 전도성 배선(20d, 20e)은 예로서, 알루미늄과 질화 티타늄과 같은 금속 재료 다층막으로 제조된다. 최종적으로 적층제(laminate)는 수소 분위기의 1기압에서 30분간 350°C로 어닐링된다. 따라서, 반도체 회로가 완성된다(제4e도 참조).

본 실시예에서 얻어진 TFT의 활성 영역에 함유되어 있는 니켈의 농도는 SIMS에 의해 측정된다. 주변 드라이버 회로에서의 TFT내 니켈 농도는  $1 \times 10^{17}$  내지  $5 \times 10^{17} \text{ cm}^{-3}$ 이다. 화소 회로에서의 TFT내 니켈 농도는 검출 하한치인  $1 \times 10^{16} \text{ cm}^{-3}$  이하이다.

#### [실시예 4]

제5a도 내지 제5e도는 본 실시예에 따른 반도체 디바이스를 제조하기 위해 연속적으로 수행되는 단계들을 도시하는, 반도체 디바이스의 단면도이다. 두께 2000Å의 산화 실리콘 막(22)이 스팍터링에 의해 코팅 7059 재질의 기판(21)상에 형성된다. 이후 200 내지 1500Å의, 예로서, 500Å의 두께를 갖는 비결정 실리콘 막(23)이 플라즈마 CVD에 의해 산화 실리콘 막(22)상에 형성된다. 비결정 실리콘 막(23)에는 니켈 이온이 이 막을 포토레지스트(24)로 마스킹하면서 이온 주입에 의해 선별 주입된다. 따라서,  $1 \times 10^{15}$  내지  $1 \times 10^{18} \text{ cm}^{-3}$ , 예로서,  $5 \times 10^{16} \text{ cm}^{-3}$  농도의 니켈을 함유하는 영역(25)이 형성된다. 이들 영역(25)의 깊이는 200 내지 500Å이다. 가속 전압은 이 깊이에 따라 결정된다. 본 실시예에서의 이온 주입 사용은 니켈 농도 조정에 있어서 실시예 3의 기술보다 효과적이다(제5a도 참조).

이후, 기판은 질소 분위기에서 두시간동안 350 내지 650°C, 통상은 400 내지 550°C, 예로서, 500°C의 온도로 어닐링된다. 그 결과 니켈이 도핑 영역의 결정화가 예비적으로 진전된다. 이후, 비결정 실리콘 막

(23)의 전체 표면에는 레이저 광이 조사되어 상기 영역을 결정화시킨다. 이 레이저 조사를 위해, 파장이 248nm이고 폴스폭이 20nsec인 광을 방출하는 KrF 액시머 레이저가 사용된다. 레이저 광의 에너지 밀도는 200 내지 500mJ/cm<sup>2</sup>이고 예로서, 350mJ/cm<sup>2</sup>이다. 매 위치마다 레이저 광이 2 내지 10회, 예로서, 2회 방출된다. 레이저 조사중에, 기판은 100 내지 450°C까지 예로서, 350°C까지 가열된다. 그결과, 실리콘 막이 결정화된다. 실리콘 막의 니켈이 도핑되는 영역(23a)은 비도핑 영역(23b)보다 결정도가 우수하다(제5b도 참조).

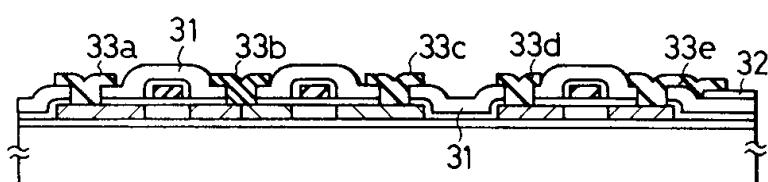

이후, 실리콘 막은 실리콘 아일랜드 영역(26a; 주변 드라이버 회로 영역, 26b; 매트릭스 화소 회로 영역)을 형성하도록 패턴화된다. 1000Å의 두께를 갖는 산화 실리콘 막(27)이 테트라에톡시실란(TEOS; Si(OC<sub>2</sub>H<sub>5</sub>)<sub>4</sub>)과 산소를 원료로 사용하여 플라즈마 CVD에 의해 TFT의 게이트 절연막으로서 형성된다. 이 원료 가스에는 트리클로로에틸렌(C<sub>2</sub>HCl<sub>3</sub>)이 첨가된다. 막 형성 이전에, 챔버에는 400SCCM의 유량으로 산소가 공급된다. 플라즈마는 기판 온도 300°C, 총압력 5Pa 및, RF 파워 150W의 상태에서 생성된다. 이 상태는 10분간 유지된다. 계속해서 산소, TEOS, 트리클로로에틸렌은 300SCCM, 15SCCM, 2SCCM에서 각각 챔버로 유입된다. 이런 식으로, 산화 실리콘 막이 형성된다. 기판의 온도는 300°C이다. RF 파워는 75W이다. 총 압력은 5Pa이다. 막의 완성 이후, 챔버에는 수소가 100Torr의 압력으로 유입된다. 적층체는 350°C에서 35분간 어닐링된다.

이어서, 실리콘을 2% 함유하는 알루미늄이 스팍터링에 의해 6000 내지 8000Å, 예로서 6000Å의 두께까지 증착된다. 알루미늄 대신에 탄탈, 텅스텐, 티탄 또는 몰리브덴이 사용될 수도 있다. 통상적으로, 산화 실리콘 막(27) 형성 단계와 알루미늄 막 형성 단계는 연속적으로 이루어진다. 알루미늄 막은 TFT의 게이트 전극(28a, 28b, 28c)을 형성하도록 패턴화된다. 알루미늄 배선의 표면은 그 표면에 산화층(29a, 29b, 29c)을 형성하도록 양극 산화 처리된다. 양극 산화 처리는 타르타르산의 1 내지 5% 에틸렌 글리콜 수용액 내에서 이루어진다. 얹어지는 산화층의 두께는 2000Å이다(제5c도 참조).

이후, 플라즈마 도핑에 의해 불순물이나 인이 실리콘 영역에 주입된다. 포스핀(PH<sub>3</sub>)이 도핑 가스로서 사용된다. 가속 전압은 60 내지 90KV이며 예로서, 80KV이다. 투여량은  $1 \times 10^{15}$  내지  $8 \times 10^{15} \text{ cm}^{-2}$ 이고 예로서,  $2 \times 10^{15} \text{ cm}^{-2}$ 이다. 이런 방식으로 N형 도핑 영역(30a)이 형성된다. 포토레지스트, 불순물 또는 봉소에 의한 잔여 TFT(N-채널 TFT)의 마스킹이 우측 주변 회로 영역 TFT의 실리콘 영역과 매트릭스 회로를 다시 형성하는 TFT의 실리콘 영역으로 플라즈마 도핑에 의해 주입된다. 디보란(B<sub>2</sub>H<sub>6</sub>)이 도핑 가스로서 사용된다. 가속 전압은 50 내지 80KV이고 예로서, 65KV이다. 투여량은  $1 \times 10^{15}$  내지  $8 \times 10^{15} \text{ cm}^{-2}$ 이고 예로서,  $5 \times 10^{15} \text{ cm}^{-2}$ 인 바, 이는 먼저 주입된 인의 투여량보다 많다. 이러한 방식으로, P형 도핑 영역(30b, 30c)이 형성된다.

이후, 불순물은 레이저 어닐링에 의해 활성화된다. 상기 어닐링을 위해서는, 248nm의 파장과 20nsec의 폴스폭을 갖는 광을 방출하는 KrF 액시머 레이저가 사용된다. 레이저 광의 에너지 밀도는 200 내지 400mJ/cm<sup>2</sup>이고 예로서, 250mJ/cm<sup>2</sup>이다. 레이저 광은 매 위치마다 2 내지 10회, 예로서, 2회 조사된다(제2d도 참조).

이후, 2000Å의 두께를 갖는 산화 실리콘 막(31)이 플라즈마 CVD에 의해 TEOS로부터 층간 절연물로서 형성된다. 500 내지 1000Å, 예로서, 800Å의 두께를 갖는 인듐 석산화막(ITO)이 스팍터링에 의해 형성된다. 이 막은 화소 전극(32)을 형성하도록 패턴화된다. 이후 층간 절연물(31)에는 접촉 구멍이 형성된다. 주변 드라이버 회로의 TFT의 전극 및 전도성 배선(33a, 33b, 33c)과 매트릭스 화소 회로의 전극 및 전도성 배선(33d, 33e)은 질화 티탄 및 알루미늄과 같은 금속 재료로된 다층 막으로 제조된다. 이렇게해서 반도체 회로가 완성된다(제5e도 참조).

제조된 반도체 회로의 주변 드라이버 회로의 TFT 특성은 종래의 레이저 결정화로 제조되는 TFT의 특성보다 결코 떨어지지 않는다. 본 실시예에 따른 TFT를 사용하여 시프트 레지스터가 제조된다. 상기 시프트 레지스터는 15V의 드레인 전압에서는 11MHz로 그리고 17V의 드레인 전압에서는 16MHz로 작동하는 것이 확인된다. 또는 신뢰도 테스트에서, 종래 방법으로 제조된 TFT와 신규한 TFT 사이에는 차이점이 전혀 발견되지 않았다. 매트릭스 영역(화소 회로)의 TFT의 특성과 관련하여, 누설 전류는 10<sup>-13</sup> A 이하이다.

본 발명은 고속 작동가능한 TFT와 상기 실시예들에서 논의된 것과 동일한 기판상에서의 누설 전류가 적은 TFT를 제조할 수 있다. 이러한 구조가 액정 표시판에 적용되는 경우 TFT의 대량 생산은 보다 쉬워진다. 특성 또한 개선된다. 물론, 이들 두 특성중 하나의 특성만 나타내는 TFT가 기판상에 제조될 수도 있다.

또한, 본 발명에서는 예로서, 500°C 정도의 저온에서 그리고 4시간 정도의 짧은 시간내에 실리콘을 결정화하므로서 처리량이 향상될 수 있다. 600°C 이상에서 실시되는 종래의 방법이 채택될 경우 유리 기판은 수축되어 뒤틀리고, 생산량을 감소시킨다. 이 문제는 본 발명을 이용하므로서 완전히 해결된다. 이는 또한 넓은 면적의 기판이 하나의 동작으로 처리될 수 있음을 의미한다. 특히 넓은 면적의 기판을 매트릭스 회로와 같은 여러개의 반도체 회로로 분할하므로서 각 회로의 가격이 현저히 낮아질 수 있다. 이런 식으로 본 발명은 산업상 유리한 점을 갖는다.

## (57) 청구의 범위

### 청구항 1

반도체 회로를 제조하는 방법에 있어서, 기판의 절연표면상에 비결정 실리콘을 포함하는 반도체 막을 형성하는 단계와, 상기 반도체 막의 결정화를 촉진시키기 위해 상기 반도체 막과 접촉하는 촉매 물질을 형성하는 단계와, 상기 반도체 막을 선택적으로 결정화시키도록 광으로 상기 반도체 막을 선택적으로 조사하는 단계와, 상기 조사 단계 이후에 가열에 의해 상기 반도체 막을 어닐링하는 단계를 포함하는 반도체 회로 제조 방법.

**청구항 2**

제1항에 있어서, 상기 촉매 물질은 니켈, 철, 코발트, 백금으로 구성된 그룹으로부터 선택된 하나 이상의 촉매 원소를 포함하는 반도체 회로 제조 방법.

**청구항 3**

제1항에 있어서, 상기 어닐링 단계는 580°C 이하의 온도에서 수행되는 반도체 회로 제조 방법.

**청구항 4**

제1항에 있어서, 상기 광은 레이저 광 또는 이와 동등한 세기의 광인 반도체 회로 제조 방법.

**청구항 5**

반도체 회로를 제조하는 방법에 있어서, 기판의 절연표면상에 비결정 실리콘을 포함하는 반도체 막을 형성하는 단계와, 상기 반도체 막의 결정화를 촉진하기 위해 상기 반도체 막내로 하나 이상의 촉매 원소를 도입하는 단계와, 상기 반도체 막을 선택적으로 결정화시키도록 광으로 상기 반도체 막을 선택적으로 조사하는 단계와, 상기 조사단계 이후에 가열에 의해 상기 반도체 막을 어닐링하는 단계를 포함하는 반도체 회로 제조 방법.

**청구항 6**

제5항에 있어서, 2 차이온 질량 분석(SIMS)으로 측정된 상기 반도체 막내의 하나 이상의 촉매 원소의 농도의 최저값이 상기 도입 단계에서  $1 \times 10^{16} \text{ cm}^{-3}$  를 초과하는 반도체 회로 제조 방법.

**청구항 7**

제5항에 있어서, 상기 어닐링 단계는 580°C 이하의 온도에서 실시되는 반도체 회로 제조 방법.

**청구항 8**

제5항에 있어서, 상기 광은 레이저 광 또는 이와 동등한 세기의 광인 반도체 회로 제조 방법.

**청구항 9**

반도체 회로를 제조하는 방법에 있어서, 제1부분 및 제2부분과 표면을 구비하고, 실리콘을 포함하는 반도체 막을 기판의 절연표면 위에 형성하는 단계와, 상기 반도체 막의 결정화를 촉진하기 위해 상기 반도체 막의 상기 제1부분에만 접촉하는 하나 이상의 촉매 원소를 함유하는 물질을 선택적으로 형성하는 단계와, 상기 반도체 막의 결정화를 촉진하도록 광으로 상기 막의 모든 상기 표면을 조사하는 단계를 포함하는 반도체 회로 제조 방법.

**청구항 10**

제9항에 있어서, 상기 하나 이상의 촉매 원소인 니켈, 철, 코발트, 백금중의 하나 이상인 반도체 회로 제조 방법.

**청구항 11**

제9항에 있어서, 상기 광은 레이저 광 또는 이와 동등한 세기의 광인 반도체 회로 제조 방법.

**청구항 12**

반도체 회로를 제조하는 방법에 있어서, 제1부분 및 제2부분과 표면을 구비하고, 실리콘을 포함하는 반도체 막을 기판의 절연 표면상에 형성하는 단계와, 상기 반도체 막의 결정화를 촉진하기 위해 상기 반도체 막의 상기 제1부분내로만 하나 이상의 촉매 원소를 선택적으로 도입하는 단계와, 상기 반도체 막의 결정화를 촉진하도록 광으로 상기 반도체 막의 모든 상기 표면을 조사하는 단계를 포함하고, 상기 반도체 막의 결정도가 상기 제2부분에서 보다 상기 제1부분에서 더 많이 증가되는 반도체 회로 제조 방법.

**청구항 13**

제12항에 있어서, 상기 하나 이상의 촉매 원소가 니켈, 철, 코발트, 백금중의 하나 이상인 반도체 회로 제조 방법.

**청구항 14**

제12항에 있어서, 상기 광은 레이저 광 또는 이와 동등한 세기의 광인 반도체 회로 제조 방법.

**청구항 15**

반도체 회로에 있어서, 기판상에 제공되고, 액티브 매트릭스 회로와 주변 드라이버 회로를 포함하는 모듈리식형 회로와, 상기 주변 드라이버 회로내에 제공되며, 하나 이상의 촉매 원소를  $1 \times 10^{15}$  내지  $1 \times 10^{19} \text{ cm}^{-3}$  의 농도로 함유하는 활성 영역을 갖는 트랜지스터와, 상기 액티브 매트릭스 회로내에 제공되며, 상기 하나 이상의 촉매 원소를 상기 주변 드라이버 회로에 제공된 트랜지스터의 활성 영역의 농도 보다 낮은 농도로 함유하는 활성 영역을 갖는 트랜지스터를 포함하는 반도체 회로.

**청구항 16**

제15항에 있어서, 상기 주변 드라이버 회로에 제공된 상기 트랜지스터의 상기 활성 영역내의 하나 이상의

촉매 원소는  $1 \times 10^{16}$  내지  $5 \times 10^{17} \text{ cm}^{-3}$  의 농도를 갖는 반도체 회로.

### 청구항 17

제15항에 있어서, 상기 액티브 매트릭스 회로에 제공된 트랜지스터의 활성 영역내의 하나 이상의 촉매 원소는  $1 \times 10^{15} \text{ cm}^{-3}$  미만의 농도를 갖는 반도체 회로.

### 청구항 18

제15항에 있어서, 상기 하나 이상의 촉매 원소는 니켈, 철, 코발트, 백금중의 하나 이상인 반도체 회로.

### 청구항 19

제15항에 있어서, 상기 하나 이상의 촉매 원소의 농도는 2 차이온 질량 분석(SIMS)으로 측정된 수치로 규정되는 반도체 회로.

### 청구항 20

반도체 회로에 있어서, 기판상에 제공되고 하나 이상의 촉매 원소로 도핑되는 활성 영역을 갖는 복수개의 트랜지스터를 포함하며, 가장 진하게 도핑된 활성 영역내의 상기 하나 이상의 촉매 원소의 농도와 가장 연하게 도핑된 활성 영역내의 하나 이상의 촉매 원소의 농도의 비율이 10 이상인 반도체 회로.

### 청구항 21

제1항에 있어서, 상기 촉매 물질은 결정화 이후에  $1 \times 10^{20} \text{ atoms/cm}^3$ 을 초과하지 않는 농도로 상기 실리콘 막에 함유되는 반도체 회로 제조 방법.

### 청구항 22

반도체 디바이스를 형성하는 방법에 있어서, 기판의 절연표면상에 실리콘을 포함하는 반도체 막을 형성하는 단계와, 상기 반도체 막과 접촉하고, 실리콘의 결정화를 촉진할수 있는 촉매를 함유하는 재료를 형성하는 단계와, 상기 촉매 형성 이후에, 펄스된 레이저 광으로 상기 반도체 막을 조사함에 의해 상기 반도체 막을 결정화 하는 단계를 포함하고, 상기 반도체 막의 조사 동안, 상기 기판은 펄스된 레이저와는 다른 열원에 의해 가열되는 반도체 디바이스 형성 방법.

### 청구항 23

제22항에 있어서, 상기 조사 단계에 앞서 상기 비결정 실리콘 막을 결정화하는 가열 단계를 추가로 포함하는 반도체 디바이스 형성 방법.

### 청구항 24

제22항에 있어서, 상기 재료는  $1 \times 10^{20} \text{ atoms/cm}^3$ 을 초과하지 않는 농도로 상기 실리콘에 첨가되는 디바이스 형성 방법.

### 청구항 25

제22항에 있어서, 상기 재료는 상기 비결정 실리콘 막과 접촉하도록 상기 재료를 배치하는 것에 의해 첨가되는 반도체 디바이스 형성 방법.

### 청구항 26

제22항에 있어서, 상기 재료는 이온 주입에 의해 첨가되는 반도체 디바이스 형성 방법.

### 청구항 27

액티브 매트릭스 회로를 구성하기 위해 기판의 제1부분상에 형성된 복수개의 제1박막 트랜지스터와, 상기 액티브 매트릭스 회로를 구동하기 위한 주변 회로를 구성하기 위해 상기 기판의 제2부분상에 형성된 복수개의 제2박막 트랜지스터를 적어도 포함하는 액티브 매트릭스형 반도체 회로를 촉진하는 방법에 있어서, 상기 기판위에 비결정 실리콘을 포함하는 반도체 막을 형성하는 단계와, 상기 반도체 막의 결정화를 촉진하기 위해 상기 반도체 막의 상기 제2부분에만 제2부분상으로 또는 제2부분내부로 촉매 물질을 도입하는 단계와, 상기 반도체 막을 결정화하기 위해 기판의 제1 및 제2부분 양쪽 모두상에 광으로 상기 반도체 막을 조사하는 단계와, 상기 복수개의 제1박막 트랜지스터와 상기 복수개의 제2박막 트랜지스터를 구성하기 위한 각각의 반도체 아일랜드로 상기 반도체 막을 패터닝하는 단계를 포함하는 액티브 매트릭스형 반도체 회로 촉진 방법.

### 청구항 28

제27항에 있어서, 상기 결정화를 위한 조사 단계 이전에 가열 냉각함에 의해 상기 반도체 막을 어닐링하는 단계를 추가로 포함하는 액티브 매트릭스형 반도체 회로 촉진 방법.

### 청구항 29

제28항에 있어서, 상기 어닐링 단계는  $400^{\circ}\text{C}$  내지  $500^{\circ}\text{C}$  범위 내의 온도에서 수행되는 액티브 매트릭스형 반도체 회로 촉진 방법.

### 청구항 30

제27항에 있어서, 상기 촉매 물질은 상기 반도체 막과 접촉하도록 상기 촉매 물질을 배치함에 의해 첨가

되는 액티브 매트릭스형 반도체 회로 촉진 방법.

### 청구항 31

제27항에 있어서, 상기 촉매 물질은 이온 주입에 의해 첨가되는 액티브 매트릭스형 반도체 회로로 촉진 방법.

### 청구항 32

액티브 매트릭스 회로와 상기 액티브 매트릭스 회로를 구동하기 위한 드라이버 회로를 적어도 포함하는 반도체 회로에 있어서, 절연 표면을 가진 기판과, 상기 활성 매트릭스 회로를 형성하기 위해 상기 기판상에 형성되고, 결정 반도체를 포함하는 활성 영역을 각각 가지는 복수개의 제1박막 트랜지스터와, 상기 주변 회로를 형성하기 위해 상기 기판상에 형성되고, 결정 반도체를 포함하는 활성 영역을 각각 가지는 복수개의 제2박막 트랜지스터를 포함하고, 상기 복수개의 제2박막 트랜지스터의 활성 영역은 실리콘의 결정화를 촉진하기 위한 촉매 요소를 함유하는 반면에, 상기 복수개의 제1박막 트랜지스터의 활성 영역은 촉매 요소를 함유하지 않는 반도체 회로.

### 청구항 33

제32항에 있어서, 상기 복수개의 제2박막 트랜지스터의 활성 영역이 상기 복수개의 제1박막 트랜지스터보다 더 높은 전계 이동도를 갖는 반도체 회로.

### 청구항 34

제32항에 있어서, 상기 복수개의 제2박막 트랜지스터의 활성 영역이 상기 복수개의 제1박막 트랜지스터보다 더 높은 결정도를 갖는 반도체 회로.

### 청구항 35

활성 매트릭스 회로와 상기 활성 매트릭스 회로를 구동하기 위한 드라이버 회로를 적어도 포함하는 반도체 회로에 있어서, 절연 표면을 가진 기판과, 상기 활성 매트릭스 회로를 형성하기 위해 상기 기판상에 형성되고, 결정 반도체를 포함하는 활성 영역을 각각 가지는 복수개의 제1박막 트랜지스터와, 상기 주변 회로를 형성하기 위해 상기 기판상에 형성되고, 결정 반도체를 포함하는 활성 영역을 각각 가지는 복수개의 제2박막 트랜지스터를 포함하고, 상기 복수개의 제2박막 트랜지스터의 활성 영역은 실리콘의 결정화를 촉진하기 위한 촉매 요소를 상기 복수개의 제1박막 트랜지스터의 활성 영역이 촉매 요소를 함유하는 것보다 더 높은 농도로 함유하는 반도체 회로.

### 청구항 36

반도체 디바이스에 있어서, 기판상의 제1채널 반도체 영역을 가진 제1박막 트랜지스터와, 상기 기판상의 제2채널 반도체 영역을 가진 제2박막 트랜지스터를 포함하고, 상기 제1 및 제2채널 반도체 영역 양쪽 모두가 결정도를 가지며, 상기 제1채널 반도체 영역에 함유된 촉매 금속의 농도가 상기 제2채널 반도체 영역내의 촉매 금속의 농도보다 큰 반도체 디바이스.

### 청구항 37

제5항 또는 제6항에 있어서, 상기 하나 이상의 촉매 원소는 니켈, 철, 코발트, 백금중의 하나 이상인 반도체 회로 제조 방법.

## 도면

### 도면 1a

### 도면 1b

도면 1c

도면 1d

도면 1e

도면 2a

도면 2b

도면2c

도면2d

도면2e

도면3

도면4a

도면4b

도면4c

도면4d

도면4e

도면5a

도면5b

도면5c

도면5d

도면5e