(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5160441号

(P5160441)

(45) 発行日 平成25年3月13日(2013.3.13)

(24) 登録日 平成24年12月21日(2012.12.21)

(51) Int.Cl.

F 1

G 11 C 16/02 (2006.01)

G 11 C 17/00 6 12 B

G 11 C 16/06 (2006.01)

G 11 C 17/00 6 12 E

G 11 C 17/00 6 33 C

請求項の数 4 (全 13 頁)

(21) 出願番号 特願2008-543553 (P2008-543553)

(86) (22) 出願日 平成18年11月8日 (2006.11.8)

(65) 公表番号 特表2009-518766 (P2009-518766A)

(43) 公表日 平成21年5月7日 (2009.5.7)

(86) 國際出願番号 PCT/US2006/060671

(87) 國際公開番号 WO2007/111688

(87) 國際公開日 平成19年10月4日 (2007.10.4)

審査請求日 平成21年11月5日 (2009.11.5)

(31) 優先権主張番号 11/290,321

(32) 優先日 平成17年11月30日 (2005.11.30)

(33) 優先権主張国 米国(US)

(73) 特許権者 504199127

フリースケール セミコンダクター イン

コーポレイテッド

アメリカ合衆国 テキサス州 78735

オースティン ウィリアム キャノン

ドライブ ウエスト 6501

(74) 代理人 100116322

弁理士 桑垣 衡

(72) 発明者 スハイル、モハメッド

アメリカ合衆国 78749 テキサス州

オースティン モパック サウス 57

01 アパートメント ナンバー823

審査官 園田 康弘

最終頁に続く

(54) 【発明の名称】不揮発性メモリをプログラムする／消去する方法および装置

## (57) 【特許請求の範囲】

## 【請求項 1】

不揮発性メモリ(NVM)をプログラム／消去する方法であって、

第1の消去電圧を有する複数の消去パルスを用いて前記NVMの少なくとも1部の消去動作を開始させること、

第1の読み取り電流閾値を選択すること、

前記NVMの少なくとも1部の第1の実際の読み取り電流を判定すること、

前記第1の実際の読み取り電流と前記第1の読み取り電流閾値とを比較すること、

前記第1の実際の読み取り電流が前記第1の読み取り電流閾値より低い場合、

前記第1の消去電圧よりも高い第2の消去電圧と、前記第1の読み取り電流閾値よりも低い第2の読み取り電流閾値を選択するステップと、 10

前記第2の消去電圧を有する複数の消去パルスを前記NVMの少なくとも1部に印加するステップと、

前記NVMの前記少なくとも1部の第2の実際の読み取り電流を判定するステップと、

前記第2の実際の読み取り電流と前記第2の読み取り電流閾値とを比較するステップと、

を実行すること、

前記第2の実際の読み取り電流が前記第2の読み取り電流閾値以上である場合、消去動作を完了すること、

を備える、方法。

## 【請求項 2】

前記複数の消去パルスはN個の消去パルスを備え、Nは前記NVMに記憶される値によって決定される、請求項1に記載の方法。

【請求項3】

前記第2の実際の読み取り電流が前記第2の読み取り電流閾値以上である場合、又は前記NVMの少なくとも1部に、予め設定された数の消去パルスが印加された場合、消去動作を完了すること、を備える、請求項1に記載の方法。

【請求項4】

前記第1の消去電圧を有する複数の消去パルスの数は、前記第2の消去電圧を有する複数の消去パルスの数と異なる、請求項1に記載の方法。

【発明の詳細な説明】

10

【技術分野】

【0001】

本発明は不揮発性メモリ、特に、不揮発性メモリをプログラムする／消去する方法および装置に関する。

【背景技術】

【0002】

複数回、プログラムされ且つ消去されることのできる不揮発性メモリ(NVM)は、通常幅広い用途で使用される。概して、NVMは、データ保持仕様を確実に満たしつつ実行可能な最大数のプログラム／消去サイクルを有する。

【発明の開示】

20

【課題を解決するための手段】

【0003】

本発明の1実施形態は、第1の消去電圧を用いてNVMの少なくとも1部の消去動作を開始させることと、第1の読み取り電流／電圧閾値を選択することと、NVMの少なくとも1部の第1の実際の読み取り電流／電圧を判定することと、第1の実際の読み取り電流／電圧と第1の読み取り電流／電圧閾値とを比較することと、を含む不揮発性メモリ(NVM)をプログラム／消去する方法に関する。第1の実際の読み取り電流／電圧が第1の読み取り電流／電圧閾値より低い場合、該方法は、少なくとも1つの消去パルスをNVMの少なくとも1部に印加することと、第2の読み取り電流／電圧閾値を選択することと、NVMの少なくとも1部の第2の実際の読み取り電流／電圧を判定することと、第2の実際の読み取り電流／電圧と第2の読み取り電流／電圧閾値とを比較することと、をさらに含む。第2の実際の読み取り電流／電圧が第2の読み取り電流／電圧閾値より高い場合、消去動作が完了する。第1の読み取り電流／電圧閾値と第2の読み取り電流／電圧閾値は異なる。

30

【0004】

別の実施形態では、少なくとも1つの消去パルスは、第1の複数の第1の消去パルスを備える。第1の複数の第1の消去パルスは、N個の消去パルスを含み、NはNVMに記憶される値によって決定される。第1の複数の第1の消去パルスはそれぞれほぼ第1の電圧を有する。

【0005】

40

さらに別の実施形態では、第2の実際の読み取り電流／電圧が第2の読み取り電流／電圧閾値より低い場合、該方法は、第2の複数の第2の消去パルスをNVMの少なくとも1部に印加することをさらに含み、第2の消去パルスそれぞれは、ほぼ第2の電圧を有し、第2の電圧は第1の電圧と異なる。第2の電圧は第1の電圧より大きくすることができる。第2の複数は第1の複数と同数にすることができる。第2の複数に追加された第1の複数が消去パルスの所定の最大総数に達し、第2の実際の読み取り電流／電圧が第2の読み取り電流／電圧閾値より低い場合、NVMは失敗したとみなされる。

【0006】

別の実施形態では、第2の読み取り電流／電圧閾値は第1の読み取り電流／電圧閾値より小さい。

別の実施形態は、プログラム／消去サイクルの第1の部分間に複数の読み取り電流／電圧閾値

50

のうちの第1の閾値を選択し、プログラム／消去サイクルの第2の部分間に複数の読み取り電流／電圧閾値のうちの第2の閾値を選択する閾値選択器を含む不揮発性メモリ（NVM）を有する集積回路に関し、複数の読み取り電流／電圧閾値のうちの第1の閾値と複数の読み取り電流／電圧閾値のうちの第2の閾値とは異なる。

【0007】

別の実施形態では、プログラム／消去サイクルの第1の部分は、プログラム／消去サイクルの第2の部分の前の適切な時期に発生し、複数の読み取り電流／電圧閾値のうちの第2の閾値は、複数の読み取り電流／電圧閾値のうちの第1の閾値より小さい。

【0008】

さらに別の実施形態では、集積回路はさらに、プログラム／消去サイクルの第1の部分間に第1の実際の読み取り電流／電圧と複数の読み取り電流／電圧閾値のうちの第1の閾値とを比較し、プログラム／消去サイクルの第2の部分間に第2の実際の読み取り電流／電圧と複数の読み取り電流／電圧閾値のうちの第2の閾値とを比較する読み取り確認回路をさらに含み、前記読み取り確認回路は前記閾値選択器に連結される。さらに別の実施形態では、集積回路はさらに、第1の実際の読み取り電流／電圧が複数の読み取り電流／電圧閾値のうちの第1の閾値より低い場合に少なくとも1つの第1の消去パルスをNVMに印加し、第2の実際の読み取り電流／電圧が複数の読み取り電流／電圧閾値のうちの第2の閾値より低い場合に少なくとも1つの第2の消去パルスをNVMに印加する消去パルス発生器を含む。さらに別の実施形態では、少なくとも1つの第1の消去パルスは、第1の電圧を有する第1の複数の消去パルスを含み、少なくとも1つの第2の消去パルスは第2の電圧を有する第2の複数の消去パルスを備える。第2の電圧は第1の電圧より高くすることができる。

10

【0009】

別の実施形態は、複数の読み取り電流／電圧閾値を生成する手段と、プログラム／消去サイクルの第1の部分間に複数の読み取り電流／電圧閾値のうちの第1の閾値を選択する手段と、プログラム／消去サイクルの第2の部分間に複数の読み取り電流／電圧閾値のうちの第2の閾値を選択する手段と、プログラム／消去サイクルの第1の部分間に第1の実際の読み取り電流／電圧と複数の読み取り電流／電圧閾値のうちの第1の閾値とを比較し、プログラム／消去サイクルの第2の部分間に第2の実際の読み取り電流／電圧と複数の読み取り電流／電圧閾値のうちの第2の閾値とを比較する手段と、第1の実際の読み取り電流／電圧が複数の読み取り電流／電圧閾値のうちの第1の閾値より低い場合に第1の複数の第1の消去パルスをNVMアレイに供給し、第2の実際の読み取り電流／電圧が複数の読み取り電流／電圧閾値のうちの第2の閾値より低い場合に第2の複数の第2の消去パルスをNVMアレイに供給する手段と、を備えるNVMアレイを含む不揮発性メモリ（NVM）に関する。

20

【0010】

別の実施形態では、プログラム／消去サイクルの第1の部分は、プログラム／消去サイクルの第2の部分の前の適切な時期に発生し、複数の読み取り電流／電圧閾値のうちの第2の閾値は複数の読み取り電流／電圧閾値のうちの第1の閾値より小さい。別の実施形態では、第1の複数の第1の消去パルスは第1の電圧を有し、第2の複数の第2の消去パルスは第2の電圧を有する。さらに別の実施形態では、第2の電圧は第1の電圧より高い、さらに別の実施形態では、第2の複数は第1の複数と同数である。

30

【発明を実施するための最良の形態】

【0011】

本発明は、貼付の図面に限定されず、例として示され、図面において同じ参照符号は同様の構成要素を指す。

40

当業者であれば、図面中の構成要素は簡潔化と明瞭化のために示されており、必ずしも等縮尺ではないことを理解するであろう。たとえば、図面中の構成要素のいくつかの寸法は、本発明の実施形態に関する理解を深める助けとして他の構成要素に対して誇張して描かれているかもしれない。

【0012】

NVMセルのデータ保持能力は、NVMセルから取り出すことができるよう、所定の

50

データ値が適切に記憶され続ける時間の量で定まる。NVMセルの持続時間は、NVMセルの状態を確実に変更できなくなるまでに実行可能なプログラム／消去サイクルの最大数である。1つまたはそれ以上のNVMセルが試験中または使用中に故障したとき、NVMアレイの実行可能性を拡張するのに使用可能な多種多様な技術（たとえば、冗長性、エラー修正コードなど）があることに注目されたい。

【0013】

NVMは、所望の精度でプログラムすることができる。多くのNVMはバイト毎にプログラムされるが、別の実施形態は、ビット、ワード、ロングワード、セクタ、ブロック、または任意のその他の所望の単位毎にプログラムすることができる。NVMは、所望の精度で消去することができる。多くのNVMはセクタ毎に消去されるが、別の実施形態は、ビット、ワード、ロングワード、セクタ、ブロック、または任意のその他の所望の単位毎に消去することができる。10

【0014】

単独のNVMアレイ30（図2を参照）が、第2群のカスタマによって要求される耐久性の最大仕様を満たしつつ、第1群のカスタマによって要求されるデータ保持の最大仕様を満たさなければならないとき、1つの問題が生じる。

【0015】

1例として、第1群のカスタマは、製品の寿命期間中（たとえば、20年間）記憶しておかねばならないソフトウェアコード、たとえば、プロセッサ12に対する指示（図1を参照）を記憶する。上記製品の1例は、エンジン制御を実行するソフトウェアコードを記憶するためにNVMを使用する自動車である。この第1群のカスタマは、NVMが多数のプログラム／消去サイクルを実行するように要求できない。本例では、NVMがソフトウェアコードを記憶する場合、ソフトウェアコードはいったん最初にNVMに記憶されれば2度と消去および書き換えする必要がないかもしれない。ほとんどの用途では、自己修正ソフトウェアコードは通常使用されない。20

【0016】

第2の例として、第2群のカスタマは、比較的短期間（たとえば、1ヶ月～5年）記憶しておく必要があるデータ値、たとえば、不揮発性だが変動可能なデータを記憶する。上記製品の1例は、エンジン調整情報を表すデータ値を記憶するためにNVMを使用する自動車である。この第2群のカスタマは、NVMが多くのプログラム／消去サイクルを実行する（たとえば、自動車の点火システムがオフおよびオンになるたびに1プログラム／消去サイクル）ことを要求する。本例では、NVMがデータ値を記憶する場合、データ値は新たなプログラム／消去サイクルによってリフレッシュされるため、長いデータ保持時間を持つ必要がない。30

【0017】

加えて、同じ用途で両方の種類のNVMを要求するカスタマもいる。たとえば、上述の自動車のカスタマは、ソフトウェアコードに対して長いデータ保持を有するNVMを必要とするとともに、頻繁に書き換えられるデータ値には長い持続時間を持つNVMを必要とする。

【0018】

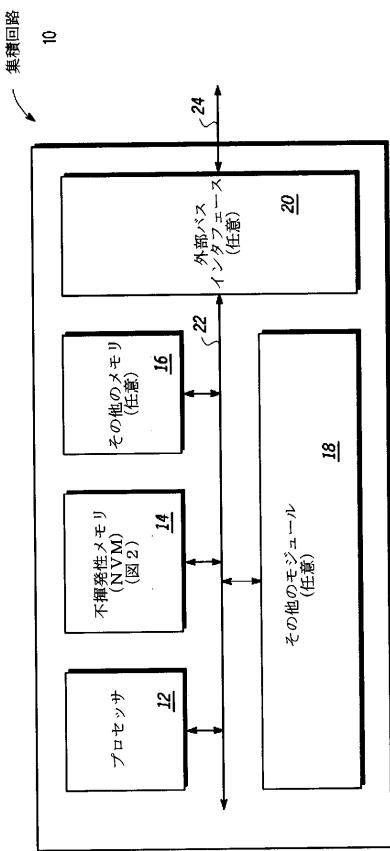

図1は、本発明の1実施形態に係る集積回路（IC）10のブロック図である。図示される実施形態では、IC10は、プロセッサ12、NVM14、任意の他のメモリ16、1つまたはそれ以上の任意の他のモジュール18、および任意の外部バスインターフェース20を有し、そのそれぞれがバス22に双方向に連結される。本明細書で使用されるように、バスという用語は、データ、アドレス、制御、または状態などの1つまたはそれ以上の各種情報を送信するのに使用可能な複数の信号または導体を指すために使用される。40

【0019】

いくつかの実施形態では、IC10は独立型NVMで、回路12、16、および18は実装されない。この場合、外部バスインターフェース20は、NVM14用のアドレスおよびデータバスドライバを含む。別の実施形態では、IC10は、マイクロコントローラ上50

で利用可能なただ 1 つの回路として N V M 1 4 を有するマイクロコントローラである。回路 1 2 、 1 4 、 1 6 、 1 8 、および 2 0 のうちの任意の 1 つまたはそれ以上は、 I C 1 0 の外部と連通するのに使用可能な 1 つまたはそれ以上の集積回路端子（図示せず）と連結する。いくつかの実施形態では、外部バス 2 4 は、 I C 1 0 の外部の回路（図示せず）と連通するのに使用される。他のメモリ 1 6 は任意の種類のメモリである。他のモジュール 1 8 は、所望の目的のために使用される回路を含む。他のモジュール 1 8 内の回路のいくつかの例は、タイマ回路、通信インターフェース回路、ディスプレイドライバ回路、アナログデジタル変換器、デジタルアナログ変換器、電力管理回路などである。

#### 【 0 0 2 0 】

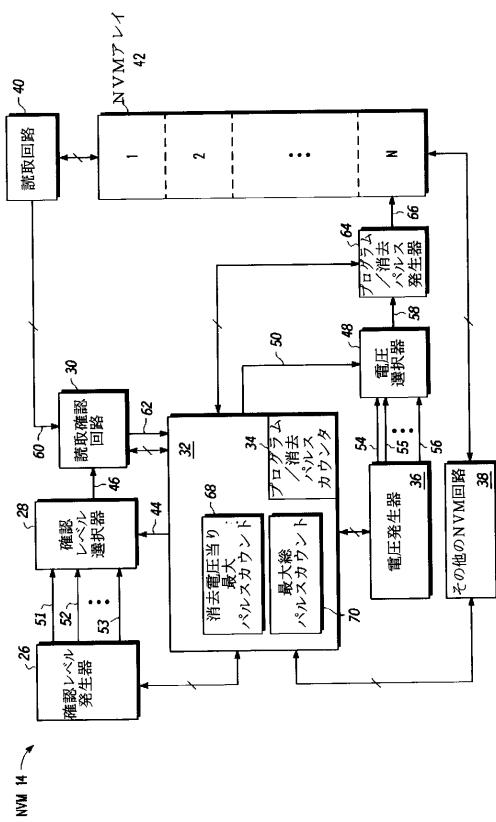

図 2 は、本発明の 1 実施形態に係る図 1 の N V M 1 4 のブロック図である。 1 実施形態では、 N V M 1 4 は N 個のブロックを有する N V M アレイ 4 2 を有し、 N は 1 以上の任意の整数である。破線は N V M アレイ 4 2 のブロックを示すために使用される。これらのブロックは任意のサイズである。各ブロックに対応する制御情報は、各ブロック内に記憶される。

#### 【 0 0 2 1 】

N V M 1 4 は、制御回路 3 2 、読み取り回路 4 0 、確認レベル発生器 2 6 、確認レベル選択器 2 8 、読み取り確認回路 3 0 、電圧発生器 3 6 、電圧選択器 4 8 、プログラム / 消去パルス発生器 6 4 、および他の N V M 回路 3 8 も含む。確認レベル発生器 2 6 は、導体 5 1 ～ 5 3 を介して複数の確認レベルを確認レベル選択器に供給する。確認レベル選択器 2 8 は、制御回路 3 2 から導体 4 4 を介して受信された選択信号に基づき、導体 4 6 を介してこれらの確認レベルのうちの 1 つを読み取り確認回路 3 0 に供給する。読み取り回路 4 0 は N V M アレイ 4 2 に双方向に連結され、導体 6 0 を介して実際の読み取り電流を読み取り確認回路 3 0 に供給する。読み取り確認回路 3 0 は制御回路 3 2 に双方向に連結され、導体 6 2 を介して制御回路 3 2 に確認結果を供給する。制御回路 3 2 は、確認レベル発生器 2 6 、他の N V M 回路 3 8 、電圧発生器 3 6 、およびプログラム / 消去パルス発生器 6 4 に双方向に連結される。電圧発生器 3 6 は、導体 5 4 ～ 5 6 を介して複数の電圧を電圧選択器 4 8 に供給する。電圧選択器 4 8 は制御回路 3 2 から導体 5 0 を介して受信された選択信号に基づき、導体 5 8 を介してこれらの電圧のうちの 1 つをプログラム / 消去パルス発生器 6 4 に供給する。制御回路 3 2 は、プログラム / 消去パルスカウンタ 3 4 、電圧当り最大パルスカウント 6 8 、および最大総パルスカウント 7 0 を含む。電圧当り最大パルスカウント 6 8 および最大総パルスカウント 7 0 は、たとえば、制御回路 3 2 内のレジスタなどの記憶回路、あるいは N V M 1 4 または I C 1 0 内のどこか別の場所などに記憶される。

#### 【 0 0 2 2 】

プログラム / 消去サイクルは、 N V M アレイ 4 2 の全部または 1 部のプログラミングあるいは N V M アレイ 4 2 の全部または 1 部の消去を含む。 1 実施形態では、消去はビットを論理レベル 1 に設定することを指し、プログラミングは N V M アレイ 4 2 に記憶される所望の情報を表すために、必要に応じて当該ビットを論理レベル 1 または論理レベル 0 に設定することを指す。 1 実施形態では、 N V M アレイ 4 2 の 1 部のプログラミングは、プログラムされる部分のすべてのビットをまず消去する消去サイクルと、次に、記憶される所望の情報を表すために変更する必要のあるビットの状態を（たとえば、論理レベル 0 に）変更することを含む。また、本明細書で使用されるように、プログラム / 消去サイクルは、単なる消去動作を含むことができることに注目されたい。 1 実施形態では、ブロック全体を 1 度に消去するか、または、おおよそ 1 つのブロックを 1 度に消去する。また、別の実施形態では、消去は、論理レベル 1 ではなく論理レベル 0 にビットを設定することを指す。

#### 【 0 0 2 3 】

N V M アレイ 4 2 の 1 部をプログラミングまたは消去したあと、プログラム / 消去サイクルが成功したかどうかを判定する確認が次に実行される。確認のため、プログラム / 消去されたビットの読み取りが行われ、ビットが適切にプログラム / 消去されたかどうかを判定するため確認レベルと比較される。たとえば、 N V M アレイ 4 2 での選択されたビットセ

10

20

30

40

50

ルの適切な消去を確認するために、読み取り確認回路 30 が使用される。読み取り回路 40 は、確認される選択ビットセルを読み取るために使用される複数のセンス増幅器（図示せず）を含む。読み取り回路 40 は、各選択されたビットセルを感知し、導体 60 を介して実際の読み取り電流を読み取り確認回路 30 に供給する。（回路と読み取り回路 40 の動作は当該技術において既知であるので、ここではより詳細に説明しないことに注意されたい）。次に、読み取り確認回路 30 は、導体 60 を介して受信された実際の読み取り電流と導体 46 を介して供給された選択された確認レベルとを比較し、実際の読み取り電流が選択された確認レベル以上であるかどうかを判定する。確認レベル以上であれば、対応する消去されたビットセルの記憶値は、消去が成功したことを示す論理レベル 1 として確認される。

## 【0024】

10

1 実施形態では、1 群のビットセルの消去が同時に確認される。たとえば、NVM アレイ 42 の 1 部のすべてのビットセルが消去される場合、消去後、すべてが論理レベル 1 になると予測される。本例では、読み取り回路 40 は、消去された NVM アレイ 42 の部分の各ビットセルを感知し、最小の実際の読み取り電流を読み取り確認回路 30 に供給される。この場合の最小の実際の読み取り電流が選択された確認レベル以上である場合、消去された部分のすべてのビットセルの消去が成功したことになる。

## 【0025】

20

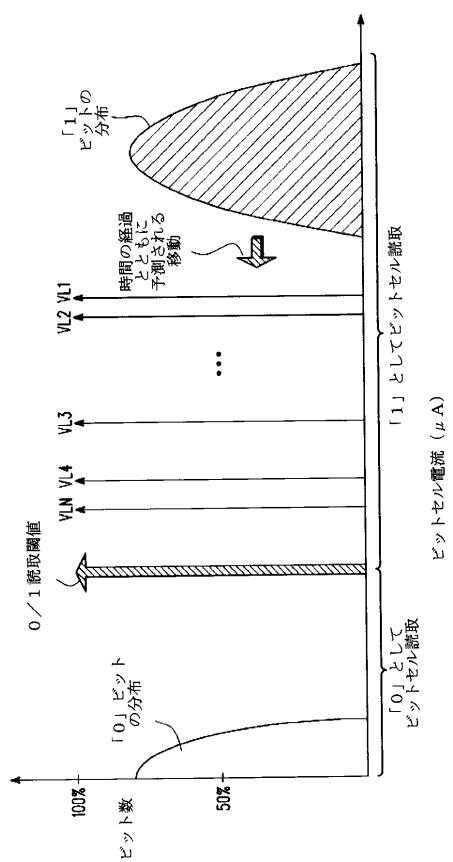

図 4 は、NVM アレイ 42 に存在する 0（「0」）ビットと 1（「1」）ビットの分布と、様々な異なる確認レベル VL1 ~ VLN を示すグラフである。y 軸はビット数を表し、x 軸はビットのビットセル電流を表す。したがって、「0」ビット（記憶された論理レベル 0 を有するビットセル）の場合、各ビットセルのビットセル電流は 0 / 1 読取閾値電流より小さい。「1」ビット（記憶された論理レベル 1 を有するビットセル）の場合、各ビットセルのビットセル電流は 0 / 1 読取閾値電流より大きい（さもなければ電流が 0 / 1 読取閾値電流より小さなどの「1」ビットも「0」ビットと誤って読み取られる）。したがって、0 / 1 読取閾値電流未満の電流を有するビットセルは「0」を記憶するとして読み取られ、0 / 1 読取閾値電流を超える電流を有するビットセルは「1」を記憶するとして読み取られる。ただし、強力な 1 ビットを確保するため、「1」ビットのビットセル電流が、0 / 1 読取閾値電流よりも大きな所定量であることが望ましい。たとえば、図 4 では、最適な動作に関して、「1」ビットのビットセル電流は確認レベル VL1 より大きいはずである。したがって、図 4 に示されるように、「1」ビットの分布は VL1 の右で発生する。ただし、時間の経過とともに、たとえば、「1」ビットの分布はプログラム / 消去サイクルによって引き起こされる装置酸化物へのダメージにより、左に移動し始め、0 / 1 読取閾値に近づいていく。

## 【0026】

30

図 4 に示されるように、「1」ビットの分布は 0 / 1 読取閾値に近づきながら移動することがあるが、様々な他の確認レベル VL2 ~ VLN（N は任意の整数値である）によって示されるように少なくとも所定の量離れていることに注意されたい。たとえば、確認レベル VL4 が VL1 でなく「1」ビットを確認するのに使用された場合、小さなビットセル電流が有効な「1」ビットとみなされるために必要であるため、もっと多くのビットが「1」を有効に記憶するとして「合格」とする。ただし、ビットセル電流が VL1 ~ VL3 ではなく VL4 のみを上回る場合、「1」ビットは実際には、もはや確実にプログラムできなくなる点まで NVM が劣化するまでに残された寿命が短い、より微弱な「1」ビットである。したがって、1 実施形態では、確認レベル VL1 は「1」ビットを確認するのにできるだけ長く使用され、それが不可能になったとき、「1」ビットを確認するには、VL2 ~ VLN などのより小さな確認レベルが代わりに使用されることによって、NVM アレイ 42 の寿命を延長させる。

## 【0027】

40

再度図 2 を参照すると、読み取り確認回路 30 は、「1」ビットを確認するために（確認レベル選択器 28 によって供給される）様々な確認レベルのうちの 1 つを使用できることに注目されたい。たとえば、確認レベル発生器 26 は、（たとえば、図 4 の VL1 ~ VLN

50

に対応する) N個の確認レベルを生成し、導体51～53を介してそれらを確認レベル選択器28に供給する。次に、確認レベル選択器28は導体44を介して制御回路32から受信した選択信号に基づき、これらのうちの1つを選択し、実際に確認を行うために導体46を介して選択された確認レベルを読み取確認回路30に供給する。次に、読み取確認回路30は読み取回路40から受け取った実際の読み取電流をこの選択された確認レベルと比較し、導体62を介してその結果を制御回路32に供給する。制御回路32の動作を、図3のフロー図を参照してより詳細に説明する。

#### 【0028】

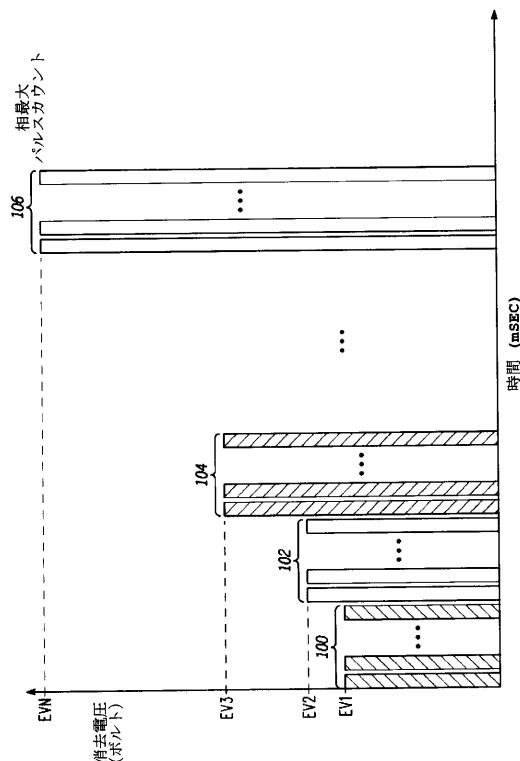

NVMアレイ42の1部を消去するための消去動作を実行するプログラム／消去サイクルの1例を、図2および5を参照して以下に説明する。1実施形態では、NVMアレイ42の1部を消去するため、複数の消去パルスがたとえば、プログラム／消去パルス発生器64によって生成される。これらのパルスの例を図5に示す。1実施形態では、ほぼ第1の消去電圧(EV1)を有する複数のパルス(たとえば、パルス100)が印加され、その後にほぼ第2の消去電圧(EV2)を有する複数のパルス(たとえば、パルス102)が印加され、その後にほぼ第3の消去電圧(EV3)を有する複数のパルス(たとえば、パルス104)が印加される。1実施形態では、第1の消去電圧(たとえば、EV1)での各パルス後、消去パルスが成功したかどうかを判定するための確認が実行される。成功しなかった場合、別の消去パルスが同じ消去電圧で供給され、再度確認される。消去が成功したことが確認された時点でプログラム／消去サイクルは終了する。ただし、同じ消去電圧で所定数のパルス(たとえば、パルス100の全部)が実行された後、消去がまだ成功していない場合、より高い消去電圧(たとえば、EV2)でパルスが供給される。再度、この高い消去電圧での各パルス後、消去が成功したかどうかを判定するための確認が行われ、そうであれば、プログラム／消去サイクルは無事その地点で終了する。ただし、その高い消去電圧での所定数のパルス(パルス102の全部)が実行され、消去がまだ成功していない場合、さらに高い消去電圧(たとえば、EV3)でパルスが供給される。

#### 【0029】

消去の成功が確認されるまで、あるいは最大総パルスカウントに達するまで、このプロセスは継続する。たとえば、パルス106の全部が完了し(つまり、パルス100、102、104、...106の全部が完了した)、消去の成功がまだ確認されない場合、プログラム／消去サイクルは成功した消去なしで終了する(すなわち、失敗した消去)。1実施形態では、より高い消去電圧に移る前に消去電圧毎に供給される所定数のパルスは同じである。たとえば、最大5つのパルスが消去電圧毎に供給され、パルスの最大総数は20である。ただし、別の実施形態では、より高い消去電圧に移る前に各消去電圧毎に供給されるパルスの数は異なる。これらの値は、たとえば、図2の電圧当たり最大パルスカウント62および最大総パルスカウント70に記憶される。もしくは、この種の情報は、NVMアレイ42の各ブロックに記憶され、各ブロックは異なるカウントを使用する。また、消去パルスカウント34は、消去電圧当たりのパルス数とパルスの総数を把握しておくため、任意の数のカウントまたは他の回路を含む。次第に高くなる消去電圧を有するパルスの使用は、結果的にNVMアレイ42に対するダメージを軽減することに注目されたい。

#### 【0030】

したがって、各プログラム／消去サイクルは複数の異なる消去電圧と複数の異なる確認レベルを使用することができることに注意されたい。たとえば、確認レベル選択器28は、プログラム／消去サイクルの第1の部分間に第1の確認レベルを選択し、次に、(たとえば、第1の確認レベルでの消去パルスが失敗した場合)(第1の部分後の適切な時期に生じる)プログラム／消去サイクルの第2の部分間に第2の確認レベルを選択する。したがって、プログラム／消去サイクルの第1の部分間に、読み取確認回路30は、第1の実際の読み取電流と第1の確認レベルとを比較し、プログラム／消去サイクルの第2の部分間に、読み取確認回路30は第2の実際の読み取電流と第2の確認レベルとを比較する。

#### 【0031】

図示される実施形態では、図2の他のNVM回路38は、NVM14の動作に必要なす

10

20

30

40

50

べての他の回路を含む。1実施形態では、他のNVM回路38は、チャージポンプ、高電圧調整器、高電圧スイッチ、ワードラインドライバ、ソースラインドライバ、行デコーダ、列デコーダ、バス22へのインターフェース、レジスタ、およびNVM14の機能にとって望ましい任意の他の回路(図示せず)を有する。1実施形態の場合、他のNVM回路38は従来のように可能であることに注意されたい。また、読み取り確認回路30と同様の回路が「0」ビットを確認するために使用され、「0」ビットのビットセル電流は、有効性を判定するために0/1読み取り閾値電流より通常小さい確認レベルに照らして比較されことに注意されたい。また、別の実施形態では、0/1読み取り閾値電流より小さい電流を有するビットセルは「1」ビットに対応し、0/1読み取り閾値電流より大きい電流を有するビットセルは「0」ビットに対応する。

10

#### 【0032】

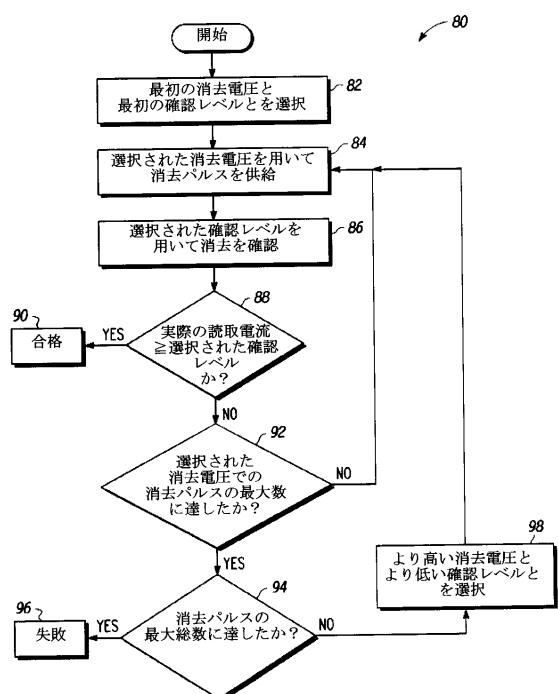

図3は、本発明の1実施形態に係る消去および確認手順を示すフロー図である。NVMアレイ42の外部の刺激は、フロー80の消去動作を開始させるために使用される。このような外部刺激の1例は、NVM14内の消去を開始させるプロセッサ12(図1を参照)である。フローはブロック82から開始され、最初の消去電圧と最初の確認レベルが選択される。たとえば、最初に、制御回路32は、確認レベル発生器から第1の確認レベル(たとえば、図4のVL1)を選択するために(たとえば、導体44を介して)確認レベル選択器28を指示する。同様に、制御回路32は、電圧発生器36から第1の消去電圧(たとえば、EV1)を選択するために(たとえば、導体50を介して)電圧選択器48を指示する。

20

#### 【0033】

その後、フローはブロック84に進み、消去パルスは、(ブロック82で選択された)選択された消去電圧を用いて供給される。たとえば、プログラム/消去パルス発生器64は、たとえば、図5に示されるように、パルスを生成するため電圧選択器48によって供給される消去電圧を使用する。制御回路32は、パルス継続時間に関連するような、プログラム/消去パルス発生器64の制御情報も供給できることに注意されたい。この第1のパルスは、NVMアレイ42の選択された部分を消去するためにNVMアレイ42に供給される(当該技術において既知なように、選択された部分は、他のNVM回路38によって示される)。

30

#### 【0034】

再び図3を参照すると、フローはブロック86に進み、選択された確認レベルを用いて消去が確認される。たとえば、いったんパルスがパルス発生器64によって供給されると、読み取り確認回路30は図2を参照して上記したように消去が確認される。たとえば、読み取り回路40は、読み取り確認回路30に実際の読み取り電流を供給し、読み取り確認回路30は、それを確認レベル選択器28から選択された確認レベルと比較される。次に、フローは判定ブロック88に進み、実際の読み取り電流が選択された確認レベル以上であるかどうかが判定される。そうであれば、フローは、消去が成功し、プログラム/消去サイクルが完了したことを示すブロック90に進む。すなわち、ブロック90で、フロー80の消去動作が完了する。判定ブロック88で、実際の読み取り電流が選択された確認レベル以上でないと判定される場合、フローは判定ブロック92に進む。

40

#### 【0035】

判定ブロック92で、選択された電圧レベルでの消去パルスの最大数に達したかどうかが判定される。達していない場合、フローはブロック84に戻り、別の消去パルスが同じ選択された電圧レベルで供給され、同じ確認レベルで(ブロック86で)確認が実行される。判定ブロック92で、選択された電圧レベルでの消去パルスの最大数に達したことが判定された場合、フローは判定ブロック94に進む。たとえば、判定ブロック92の判定を行うために、制御回路32は、現在の消去電圧でのパルス数を把握する第1の消去パルスカウンタのカウントと、(たとえば、消去電圧当りの最大パルスカウント68の1部として記憶することのできる)現在の消去電圧の最大パルスカウントとが比較される。

#### 【0036】

50

判定ブロック 9 4 では、消去パルスの最大総数に達したかどうかが判定される。たとえば、制御回路 3 2 はこの判定を行うため、現行のプログラム / 消去サイクルでのパルス総数を把握する第 2 の消去パルスカウンタのカウントと最大総パルスカウント 7 0 とが比較される。消去パルスの最大総数に達した場合、フローは、現行のプログラム / 消去サイクルが消去の失敗で終わる（すなわち、失敗した消去）ことを示すブロック 9 6 に進む。消去またはプログラミング間の失敗は、NVMアレイ 4 2 および / または他のNVM回路 3 8 内の回路による場合があることに注意されたい。

#### 【 0 0 3 7 】

ただし、判定ブロック 9 4 で、消去パルスの最大総数に達していない場合、フローはブロック 9 8 に進み、現行のプログラム / 消去サイクルが継続する。ブロック 9 8 では、高い消去電圧と低い確認レベルが選択され、フローはブロック 8 4 に戻る。たとえば、ブロック 8 2 で最初の消去電圧および確認レベルが EV 1 と VL 1 にそれぞれ対応する場合、ブロック 9 8 で、高い消去電圧と低い確認レベルは EV 2 と VL 2 にそれぞれ対応する。この新たな高い消去電圧では、より強力な消去パルスが、消去を実行するためにNVMアレイ 4 2 に供給される。

#### 【 0 0 3 8 】

さらに、このより高い消去電圧での各消去パルス後、低い確認レベルを用いて確認が実行される。この低い確認レベルは、読み取り確認回路 3 0 が消去の成功を確認しやすくする。すなわち、各プログラム / 消去サイクルは、複数の異なる消去電圧と複数の異なる確認レベルが使用される。次第に低くなる確認レベル（たとえば、それぞれ VL 1 、 VL 2 、 . . . VL N ）とともに次第に高くなる消去電圧（たとえば、EV 1 、 EV 2 、 . . . EV N ）を使用することによって、プログラム / 消去サイクルによって生じるダメージが最小化され、用途に関係なく最適なデータ保持および持続性能がNVMアレイ中のすべてのビットセルに対して確実に達成されるように、消去が実行および確認される。

#### 【 0 0 3 9 】

消去電圧および確認レベルの任意のシーケンスを選択できることに注意されたい。たとえば、使用される消去電圧のシーケンス中の各消去電圧は、均等に間隔が置かれる。もしくは、たとえば、EV 1 から EV 2 へのジャンプがその後の EV 2 から EV 3 へのジャンプより小さくなるように、均等に間隔を置く必要はない。また、各消去電圧は、必ずしも前の消去電圧より大きい必要はない。同様に、選択される確認レベルのシーケンス中の各確認レベルは、均等に間隔を置いても置かなくてもよい。また、各確認レベルは、必ずしも先の確認レベルよりも低い必要はない。1実施形態では、消去電圧のシーケンスは、1 3 ボルト、1 3 . 2 ボルト、1 3 . 4 ボルト . . . 1 4 ボルト（EV 1 、 EV 2 、 EV 3 、 EV N にそれぞれ対応）というように1 3 ボルトから始まり、1 4 ボルトに達するまで 2 0 0 ミリボルトずつ増大し、確認レベルのシーケンスは、3 0 マイクロアンペア、2 6 マイクロアンペア、2 2 マイクロアンペア、. . . 1 0 マイクロアンペア（VL 1 、 VL 2 、 VL 3 、. . . VL N にそれぞれ対応）というように3 0 マイクロアンペアから始まり、1 0 マイクロアンペアに達するまで4 マイクロアンペアずつ減少する。ただし、上記したように、各消去電圧および確認レベルに対して、多くの異なるシーケンスが利用可能である。

#### 【 0 0 4 0 】

1実施形態の場合、確認レベルは、NVMセルからの実際の読み取り電流に比較される基準電流であることにも注意されたい。別の実施形態は、確認レベルを表すのに基準電流以外のものが使用される。たとえば、確認レベルは基準電圧である。また、基準は、読み取り電流以外のものと比較してもよい。たとえば、確認レベルは、NVMセル電圧（たとえば、トランジスタ閾値電圧）と比較される基準電圧である。別の実施形態は、確認レベルを表すために任意の所望の回路特性が使用される。したがって、1実施形態では、確認レベルは読み取り電流 / 電圧閾値と称し、実際の読み取り電流は実際の読み取り電流 / 電圧と称する。また、1実施形態では、確認レベル選択器 2 8 は、閾値選択器と称する。

#### 【 0 0 4 1 】

10

20

30

40

50

NVM14は、図2に示される構造以外の他の構造を含むことができることに注意されたい。たとえば、確認レベル発生器26および確認レベル選択器28は様々な様式で実装される。1実施形態では、確認レベル発生器26は任意の数の確認レベル（所望の種類の比較に応じて、電流または電圧）を生成し、確認レベル選択器28は制御回路32からの選択信号に基づき、これらのうちの1つを選択する。たとえば、確認レベル28は、様々な生成された確認レベルから選択する、あるいは、選択された確認レベルを生成するために、確認レベル発生器26内でイネーブルにされる回路を選択する。もしくは、これらの機能は単独のブロックに結合される。また、1実施形態では、以後の確認レベルはそれぞれ、最初の確認レベルまたはその他の先の確認レベルから生成される。確認レベル発生器26および確認レベル選択器28を参照して記載される同じ代替物が、電圧発生器36および電圧選択器48にもそれぞれ適用される。また、制御回路32は、どの確認レベルおよび消去電圧を選択または生成するかを示す任意の種類の制御信号を必要に応じて供給される。

#### 【0042】

また、任意の種類の既知の回路が、NVM14の部品を実装するために使用される。たとえば、任意の種類の電流／電圧レベル発生器が、確認レベル発生器26および電圧発生器36を実装するために使用される。同様に、選択器28および48（たとえば、マルチプレクサ）の機能の選択を実行するために任意の種類の回路が使用される。また、プログラム／消去パルスカウンタ34のカウンタ、およびプログラム／消去パルス発生器64を実装するために既知の回路が使用される。また、プロセッサ12上で動作するソフトウェア内で、あるいは、たとえば、フロー80の制御を実行するハードウェア、またはハードウェアとソフトウェアの組み合わせとして制御回路32が使用される。制御回路32の部分は、NVM14全体に分布して配置する、図2に示されるように、中心に集めなくてもよい。制御回路32は、NVM14の機能に関連するNVM14の部分に制御情報と信号を供給するために使用される。また、たとえば、発生器26および36、選択器28および48、読取確認回路30、プログラム／消去パルス発生器64、および制御回路32などの、本明細書に記載のNVM14の特定の部分は、「0」ビットのプログラミングや確認などのNVM14の他の機能を実行する、あるいは実行するのを助けることもできることに注意されたい。本発明の実施形態は、複数回プログラムおよび消去可能な任意の種類のNVMに適用可能であることも注意されたい。

#### 【0043】

上記明細書では、本発明を特定の実施形態を参照して説明した。ただし、当業者であれば、下の請求項に記載される本発明の範囲を逸脱せずに、様々な修正や変更を行うことができると認識している。したがって、明細書および図面は限定的な意味ではなく例示的にみなすべきであって、上記すべての修正は本発明の範囲に含まれると意図される。

#### 【0044】

利益、その他の利点、および問題の解決策を、特定の実施形態を参照して説明した。ただし、利益、利点、問題の解決策、および利益、利点、または解決策を生じさせる、あるいはより明白にする構成要素は、請求項の1部または全部の重要で、必須で、または不可欠な特徴または構成要素と解釈すべきではない。本明細書で使用されるように、「備える」という用語またはその変形は、構成要素のリストを備えるプロセス、方法、品、または装置がこれらの構成要素だけを含むのではなく、明確にリストアップされていない、あるいは上記プロセス、方法、品、または装置に本来備わる他の構成要素を含むことができるように、非排他的な包含を対象とすることを目的とする。

#### 【図面の簡単な説明】

#### 【0045】

【図1】本発明の1実施形態に係る集積回路のブロック図である。

【図2】本発明の1実施形態に係る図1のNVM14のブロック図である。

【図3】本発明の1実施形態に係るNVMを消去する方法のフロー図である。

【図4】本発明の1実施形態に係るプログラムされ消去されたビットの分布を示すグラフ

10

20

30

40

50

である。

【図5】本発明の1実施形態に係る各種消去パルスを示すグラフである。

【図1】

【図2】

【図3】

【図4】

【図5】

---

フロントページの続き

(56)参考文献 特開平10-228784(JP,A)

特開2004-185803(JP,A)

特開2004-110986(JP,A)

特表2005-506653(JP,A)

特開2000-090675(JP,A)

特開平06-068688(JP,A)

特開2005-276428(JP,A)

特開2001-319486(JP,A)

(58)調査した分野(Int.Cl., DB名)

G11C 16/02

G11C 16/06