(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7113219号

(P7113219)

(45)発行日 令和4年8月5日(2022.8.5)

(24)登録日 令和4年7月28日(2022.7.28)

(51)国際特許分類

|         |                 |         |        |

|---------|-----------------|---------|--------|

| H 0 4 N | 5/369(2011.01)  | H 0 4 N | 5/369  |

| H 0 1 L | 27/146(2006.01) | H 0 1 L | 27/146 |

| H 0 1 L | 51/42 (2006.01) | H 0 1 L | 27/146 |

| H 0 4 N | 5/33 (2006.01)  | H 0 1 L | 31/08  |

| H 0 4 N | 5/374(2011.01)  | H 0 4 N | 5/33   |

請求項の数 14 (全25頁) 最終頁に続く

(21)出願番号 特願2018-7237(P2018-7237)

(22)出願日 平成30年1月19日(2018.1.19)

(65)公開番号 特開2018-125848(P2018-125848

A)

(43)公開日 平成30年8月9日(2018.8.9)

審査請求日 令和2年12月9日(2020.12.9)

(31)優先権主張番号 特願2017-18776(P2017-18776)

(32)優先日 平成29年2月3日(2017.2.3)

(33)優先権主張国・地域又は機関

日本国(JP)

(73)特許権者 314012076

パナソニックIPマネジメント株式会社

大阪府大阪市中央区城見2丁目1番61

号

(74)代理人 100109210

弁理士 新居 広守

(74)代理人 100137235

弁理士 寺谷 英作

(74)代理人 100131417

弁理士 道坂 伸一

(72)発明者 町田 真一

大阪府門真市大字門真1006番地 パ

ナソニック株式会社内

(72)発明者 村上 雅史

大阪府門真市大字門真1006番地 パ

最終頁に続く

(54)【発明の名称】 撮像装置

## (57)【特許請求の範囲】

## 【請求項1】

画素電極、前記画素電極に電気的に接続された電荷蓄積領域、及び前記電荷蓄積領域に電気的に接続された信号検出回路を含む単位画素セルと、

前記画素電極に対向する対向電極と、

前記画素電極及び前記対向電極の間に配置され、

前記画素電極及び前記対向電極の間に第1電圧が印加されると、第1波長域の第1の光を第1電気信号に変換し、

前記画素電極及び前記対向電極の間に前記第1電圧と異なる第2電圧が印加されると、前記第1波長域とは異なる第2波長域の第2の光を第2電気信号に変換する光電変換層と、

前記画素電極及び前記対向電極の間に前記第1電圧が印加されることにより、前記第1電気信号に基づき、前記第1の光を用いて撮像された画像に相当する第1信号を取得し、

前記画素電極及び前記対向電極の間に前記第2電圧が印加されることにより、前記第2電気信号に基づき、前記第2の光を用いて撮像された画像に相当する第2信号を取得し、

前記第1信号と前記第2信号とを用いて所定の演算を行うことにより、前記第1波長域および前記第2波長域の何れとも異なる第3波長域の第3の光を用いて撮像された画像に相当する第3信号を生成する演算回路と、を備える

撮像装置。

## 【請求項2】

前記画素電極及び前記対向電極の間に、前記第1電圧または前記第2電圧を選択的に供給可能な電圧供給回路をさらに備える、

請求項1に記載の撮像装置。

【請求項3】

前記演算回路は、前記第1信号から、前記第2信号にゲインを乗算することにより得られた信号を減算することにより、前記第3信号を生成する、

請求項1に記載の撮像装置。

【請求項4】

前記ゲインは、

前記画素電極及び前記対向電極の間に前記第2電圧が印加された場合の前記光電変換層の量子効率に対する、前記画素電極及び前記対向電極の間に前記第1電圧が印加された場合の前記光電変換層の量子効率の比に相当する、

請求項3に記載の撮像装置。

【請求項5】

前記ゲインは、

前記画素電極及び前記対向電極の間に前記第2電圧が印加された場合の前記光電変換層の量子効率に対する、前記画素電極及び前記対向電極の間に前記第1電圧が印加された場合の前記光電変換層の量子効率の比と、

前記画素電極及び前記対向電極の間に前記第2電圧が印加されている時間である第2露光時間に対する、前記画素電極及び前記対向電極の間に前記第1電圧が印加されている時間である第1露光時間の比と、の積に相当する、

請求項3に記載の撮像装置。

【請求項6】

前記第1露光時間は、前記第2露光時間より短い、

請求項5に記載の撮像装置

【請求項7】

前記演算回路は、前記第1信号に第1ゲインを乗算することにより得られた第4信号から、前記第2信号に前記第1ゲインと異なる第2ゲインを乗算することにより得られた第5信号を減算することにより、前記第3信号を生成する、

請求項1に記載の撮像装置。

【請求項8】

前記第2ゲインに対する前記第1ゲインの比は、

前記画素電極及び前記対向電極の間に前記第1電圧が印加された場合の前記光電変換層の量子効率に対する、前記画素電極及び前記対向電極の間に前記第2電圧が印加された場合の前記光電変換層の量子効率の比に相当する、

請求項7に記載の撮像装置。

【請求項9】

前記第2ゲインに対する前記第1ゲインの比は、

前記画素電極及び前記対向電極の間に前記第1電圧が印加された場合の前記光電変換層の量子効率に対する、前記画素電極及び前記対向電極の間に前記第2電圧が印加された場合の前記光電変換層の量子効率の比と、

前記画素電極及び前記対向電極の間に前記第1電圧が印加されている時間である第1露光時間に対する、前記画素電極及び前記対向電極の間に前記第2電圧が印加されている時間である第2露光時間の比と、の積に相当する、

請求項7に記載の撮像装置。

【請求項10】

前記第1露光時間は、前記第2露光時間より短い、

請求項9に記載の撮像装置。

【請求項11】

前記光電変換層は、複数の光電変換膜を含む、

10

20

30

40

50

請求項 1 に記載の撮像装置。

【請求項 1 2】

前記複数の光電変換膜のうち少なくとも 1 つは、有機材料を含む、

請求項 1 1 に記載の撮像装置。

【請求項 1 3】

前記第 1 波長域は可視波長域および赤外波長域であり、

前記第 2 波長域は可視波長域であり、

前記第 3 波長域は赤外波長域である、

請求項 1 に記載の撮像装置。

【請求項 1 4】

前記撮像装置は、

前記単位画素セルを含む複数の単位画素セルを備え、

前記対向電極は前記複数の単位画素セルにまたがって設けられ、

前記第 1 電圧および前記第 2 電圧は前記複数の単位画素セルに一括して印加され、

グローバルシャッタ機能を有する、

請求項 1 から 1 3 のいずれか 1 項に記載の撮像装置。

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

本開示は撮像装置に関する。

10

【背景技術】

【0 0 0 2】

従来、可視光によるカラー画像と赤外光によるモノクロ画像とを一つのイメージセンサで取得する際、赤外光が多い環境下で撮影が行われる場合、赤外光の影響により色再現が損なわれる。そのため、カラー画像の撮像時にはセンサ前面に赤外光を遮断する赤外カットフィルタを設けて良好な色再現を実現することが考案されている（例えば、特許文献 1 参照）。また、夜間などは赤外カットフィルタを除去することで、モノクロ画像を撮像することができる。環境光に赤外光と可視光の両方が含まれる場合には、可視光を遮断する可視光カットフィルタを設けることで、赤外光のみによる画像を取得することも考えられる。

20

【先行技術文献】

【特許文献】

【0 0 0 3】

【文献】特許第 5 1 0 0 6 1 5 号公報

30

【発明の概要】

【発明が解決しようとする課題】

【0 0 0 4】

本開示は、可動式のフィルタを設けることなく、可視光による画像と、可視光及び赤外光による画像と、赤外光による画像とを生成できる撮像装置を提供する。

40

【課題を解決するための手段】

【0 0 0 5】

本開示の一態様に係る撮像装置は、画素電極、前記画素電極に電気的に接続された電荷蓄積領域、及び前記電荷蓄積領域に電気的に接続された信号検出回路を含む単位画素セルと、前記画素電極に対向する対向電極と、前記画素電極及び前記対向電極の間に配置された光電変換層と、演算回路と、を備える。前記光電変換層は、前記画素電極及び前記対向電極の間に第 1 電圧が印加されると、第 1 波長域の第 1 の光を第 1 電気信号に変換し、前記画素電極及び前記対向電極の間に前記第 1 電圧と異なる第 2 電圧が印加されると、前記第 1 波長域とは異なる第 2 波長域の第 2 の光を第 2 電気信号に変換する。前記演算回路は、前記画素電極及び前記対向電極の間に前記第 1 電圧が印加されることにより、前記第 1 電気信号に基づき、前記第 1 の光を用いて撮像された画像に相当する第 1 信号を取得し、

50

前記画素電極及び前記対向電極の間に前記第2電圧が印加されることにより、前記第2電気信号に基づき、前記第2の光を用いて撮像された画像に相当する第2信号を取得し、前記第1信号と前記第2信号とを用いて所定の演算を行うことにより、前記1波長域および前記第2波長域の何れとも異なる第3波長域の第3の光を用いて撮像された画像に相当する第3信号を生成する。

【発明の効果】

【0006】

本開示によると、可視光による画像と、可視光及び赤外光による画像と、赤外光による画像とを生成できる撮像装置を提供できる。

【図面の簡単な説明】

【0007】

【図1】図1は、実施形態に係る撮像装置の例示的な回路構成を示す模式図である。

【図2】図2は、実施形態に係る単位画素セルの例示的なデバイス構造を示す模式的な断面図である。

【図3】図3は、実施形態に係る光電変換層の構成の一例を示す模式的な断面図である。

【図4】図4は、実施形態に係る撮像装置における動作の一例を説明するためのタイミングチャートである。

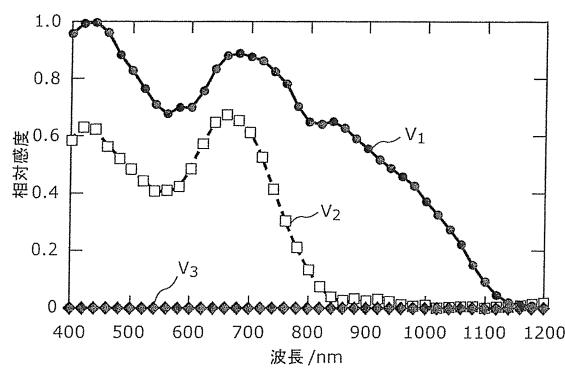

【図5】図5は、実施形態に係る撮像装置において、光電変換層が有する分光感度特性の電圧依存性を示す一例である。

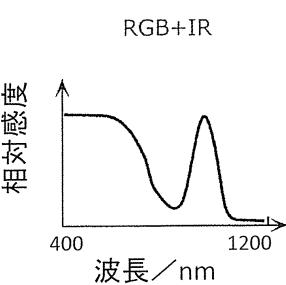

【図6A】図6Aは、実施形態に係る可視光及び赤外光の分光感度特性の一例を示す図である。

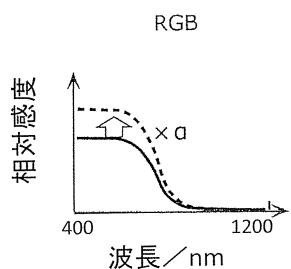

【図6B】図6Bは、実施形態に係る可視光の分光感度特性の一例を示す図である。

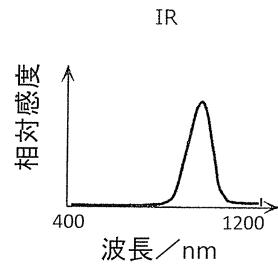

【図6C】図6Cは、実施形態に係る赤外光の分光感度特性の一例を示す図である。

【図6D】図6Dは、実施形態に係る画素構成、及び可視光及び赤外光のモードにおいて得られる信号を模式的に示す図である。

【図6E】図6Eは、実施形態に係る画素構成、及び可視光のモードにおいて得られる信号を模式的に示す図である。

【図6F】図6Fは、実施形態に係る画素構成、及び赤外光のモードにおいて得られる信号を模式的に示す図である。

【図7】図7は、実施形態に係る撮像装置のモード切替動作の一例を示す図である。

【図8】図8は、実施形態に係る撮像装置のモード切替動作の別の例を示す図である。

【発明を実施するための形態】

【0008】

上記の背景技術の項目で記述した、可動式のフィルタを機械的に挿抜することでカラー撮像と赤外撮像を切替える方式は、挿抜にかかる期間は良好な撮像結果が得られないため、デイナイトカメラのようにカラー撮像と赤外モノクロ撮像との切り換え頻度が少ない用途には有用である。しかしながら、カラー画像と赤外画像とを同時に取得したい場合、挿抜期間内に被写体が動いてしまうと動体ブレを起こすことになる。また、可動部を繰り返し高速に動かすことは、装置の耐久性及び消費電力の観点からも好ましくない。

【0009】

本開示の一態様に係る撮像装置は、画素電極、前記画素電極に電気的に接続された電荷蓄積領域、及び前記電荷蓄積領域に電気的に接続された信号検出回路を含む単位画素セルと、前記画素電極に対向する対向電極と、前記画素電極及び前記対向電極の間に配置された光電変換層と、演算回路と、を備える。前記光電変換層は、前記画素電極及び前記対向電極の間に第1電圧が印加されると、可視光及び赤外光を第1電気信号に変換し、前記画素電極及び前記対向電極の間に、前記第1電圧と異なる第2電圧が印加されると、前記可視光を第2電気信号に変換する。前記演算回路は、前記画素電極及び前記対向電極の間に前記第1電圧が印加されることにより、前記第1電気信号に基づき、前記可視光及び前記赤外光を用いて撮像された画像に相当する第1信号を取得し、前記画素電極及び前記対向電極の間に前記第2電圧が印加されることにより、前記第2電気信号に基づき、前記可視

10

20

30

40

50

光を用いて撮像された画像に相当する第2信号を取得し、前記第1信号と前記第2信号とを用いて所定の演算を行うことにより、前記赤外光を用いて撮像された画像に相当する第3信号を生成する。

【0010】

この構成によれば、当該撮像装置は、光電変換層への印加電圧を変更することで、可視光による撮像と、可視光及び赤外光による撮像を全画素同時に切り換えることが可能である。さらに、当該撮像装置は、可視光が撮影された画像と、可視光及び赤外光が撮影された画像とを用いて、赤外光が撮影された画像を生成できる。このように、当該撮像装置は、可動式のフィルタを設けることなく、可視光による画像と、可視光及び赤外光による画像と、赤外光による画像とを生成できる。

10

【0011】

本開示の一態様に係る撮像装置は、前記画素電極及び前記対向電極の間に、前記第1電圧または前記第2電圧を選択的に供給可能な電圧供給回路をさらに備えていてもよい。

【0012】

本開示の一態様に係る撮像装置において、前記演算回路は、前記第1信号から、前記第2信号にゲインを乗算することにより得られた信号を減算することにより、前記第3信号を生成してもよい。

【0013】

本開示の一態様に係る撮像装置において、前記ゲインは、前記画素電極及び前記対向電極の間に前記第2電圧が印加された場合の前記光電変換層の量子効率に対する、前記画素電極及び前記対向電極の間に前記第1電圧が印加された場合の前記光電変換層の量子効率の比に相当してもよい。

20

【0014】

本開示の一態様に係る撮像装置において、前記ゲインは、前記画素電極及び前記対向電極の間に前記第2電圧が印加された場合の前記光電変換層の量子効率に対する、前記画素電極及び前記対向電極の間に前記第1電圧が印加された場合の前記光電変換層の量子効率の比と、前記画素電極及び前記対向電極の間に前記第2電圧が印加されている時間である第2露光時間に対する、前記画素電極及び前記対向電極の間に前記第1電圧が印加されている時間である第1露光時間の比と、の積に相当してもよい。

【0015】

本開示の一態様に係る撮像装置において、前記演算回路は、前記第1信号に第1ゲインを乗算することにより得られた第4信号から、前記第2信号に前記第1ゲインと異なる第2ゲインを乗算することにより得られた第5信号を減算することにより、前記第3信号を生成してもよい。

30

【0016】

本開示の一態様に係る撮像装置において、前記第2ゲインに対する前記第1ゲインの比は、前記画素電極及び前記対向電極の間に前記第1電圧が印加された場合の前記光電変換層の量子効率に対する、前記画素電極及び前記対向電極の間に前記第2電圧が印加された場合の前記光電変換層の量子効率の比に相当してもよい。

【0017】

本開示の一態様に係る撮像装置において、前記第2ゲインに対する前記第1ゲインの比は、前記画素電極及び前記対向電極の間に前記第1電圧が印加された場合の前記光電変換層の量子効率に対する、前記画素電極及び前記対向電極の間に前記第2電圧が印加された場合の前記光電変換層の量子効率の比と、前記画素電極及び前記対向電極の間に前記第1電圧が印加されている時間である第1露光時間に対する、前記画素電極及び前記対向電極の間に前記第2電圧が印加されている時間である第2露光時間の比と、の積に相当してもよい。

40

【0018】

本開示の一態様に係る撮像装置において、前記第1露光時間は、前記第2露光時間より短くてもよい。

50

## 【0019】

本開示の一態様に係る撮像装置において、前記光電変換層は、複数の光電変換膜を含んでいてもよい。

## 【0020】

本開示の一態様に係る撮像装置において、前記複数の光電変換膜のうち少なくとも1つは、有機材料を含んでいてもよい。

## 【0021】

本開示において、回路、ユニット、装置、部材又は部の全部又は一部、又はブロック図の機能ブロックの全部又は一部は、半導体装置、半導体集積回路（IC）、又はLSI（large scale integration）を含む一つ又は複数の電子回路によって実行されてもよい。LSI又はICは、一つのチップに集積されてもよいし、複数のチップを組み合わせて構成されてもよい。例えば、記憶素子以外の機能ブロックは、一つのチップに集積されてもよい。ここでは、LSIまたはICと呼んでいるが、集積の度合いによって呼び方が変わり、システムLSI、VLSI（very large scale integration）、若しくはULSI（ultra large scale integration）と呼ばれるものであってもよい。LSIの製造後にプログラムされる、Field Programmable Gate Array（FPGA）、又はLSI内部の接合関係の再構成又はLSI内部の回路区画のセットアップができるreconfigurable logic deviceも同じ目的で使うことができる。

10

## 【0022】

さらに、回路、ユニット、装置、部材又は部の全部又は一部の機能又は操作は、ソフトウェア処理によって実行することが可能である。この場合、ソフトウェアは一つ又は複数のROM、光学ディスク、ハードディスクドライブなどの非一時的記録媒体に記録され、ソフトウェアが処理装置（processor）によって実行されたときに、そのソフトウェアで特定された機能が処理装置（processor）および周辺装置によって実行される。システム又は装置は、ソフトウェアが記録されている一つ又は複数の非一時的記録媒体、処理装置（processor）、及び必要とされるハードウェアデバイス、例えばインターフェース、を備えていても良い。

20

## 【0023】

以下、図面を参照しながら、本開示の実施形態を詳細に説明する。なお、以下で説明する実施形態は、いずれも包括的または具体的な例を示す。以下の実施形態で示される数値、形状、材料、構成要素、構成要素の配置、および接続形態、ステップ、ステップの順序などは、一例であり、本開示を限定する主旨ではない。本明細書において説明される種々の態様は、矛盾が生じない限り互いに組み合わせることが可能である。また、以下の実施形態における構成要素のうち、最上位概念を示す独立請求項に記載されていない構成要素については、任意の構成要素として説明される。以下の説明において、実質的に同じ機能を有する構成要素は共通の参照符号で示し、説明を省略することがある。

30

## 【0024】

## （撮像装置の実施形態）

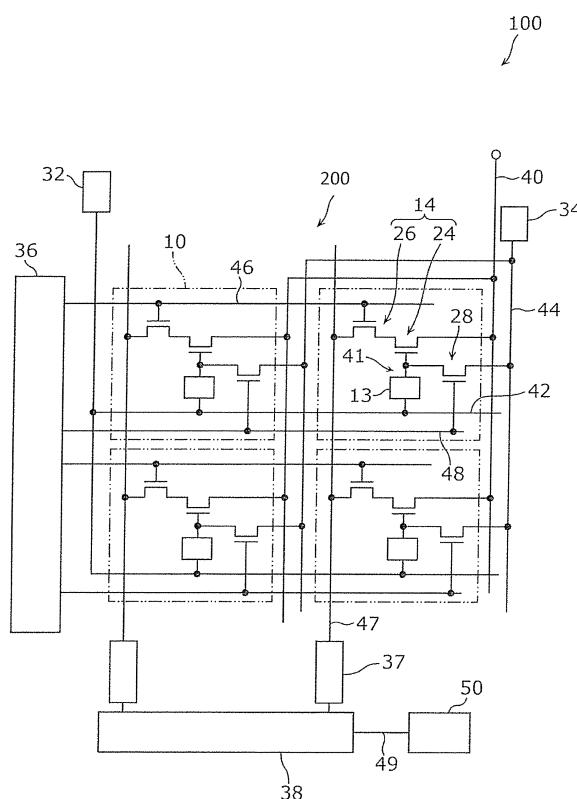

図1は、本開示の実施形態に係る撮像装置の例示的な回路構成を示す。図1に示す撮像装置100は、2次元に配列された複数の単位画素セル10を含む画素アレイ200を有する。図1は、単位画素セル10が2行2列のマトリクス状に配置された例を模式的に示している。撮像装置100における単位画素セル10の数および配置は、図1に示す例に限定されない。

40

## 【0025】

各単位画素セル10は、光電変換部13および信号検出回路14を有する。後に図面を参照して説明するように、光電変換部13は、互いに対向する2つの電極の間に挟まれた光電変換層を有し、入射した光を受けて信号電荷を生成する。光電変換部13は、その全体が、単位画素セル10毎に独立した素子である必要はなく、光電変換部13の例えば一部分または全部が複数の単位画素セル10にまたがっていてもよい。本実施の形態の場合

50

は、光の入射側の電極についても、光の入射側の電極の一部分または全部が複数の単位画素セル 10 にまたがっている。

【 0 0 2 6 】

信号検出回路 14 は、光電変換部 13 によって生成された信号を検出する回路である。この例では、信号検出回路 14 は、信号検出トランジスタ 24 およびアドレストランジスタ 26 を含んでいる。信号検出トランジスタ 24 およびアドレストランジスタ 26 は、典型的には電界効果トランジスタ (FET) であり、ここでは、信号検出トランジスタ 24 およびアドレストランジスタ 26 として N チャンネル MOSFET (Metal Oxide Semiconductor Field Effect Transistor) を例示する。

10

【 0 0 2 7 】

図 1 において模式的に示すように、信号検出トランジスタ 24 の制御端子 (ここではゲート) は、光電変換部 13 との電気的な接続を有する。光電変換部 13 によって生成される信号電荷 (正孔または電子) は、信号検出トランジスタ 24 のゲートと光電変換部 13 との間の電荷蓄積ノード (「フローティングディフュージョンノード」とも呼ばれる。) 41 に蓄積される。電荷蓄積ノード 41 は、電荷蓄積領域に相当する。光電変換部 13 の構造の詳細は、後述する。

【 0 0 2 8 】

各単位画素セル 10 の光電変換部 13 は、さらに、感度制御線 42 との接続を有している。図 1 に例示する構成において、感度制御線 42 は、電圧供給回路 32 に接続されている。この電圧供給回路 32 は、少なくとも第一電圧、第二電圧、および、第三電圧の 3 種類の電圧のいずれかを光電変換部 13 に選択的に供給可能に構成された回路である。電圧供給回路 32 は、撮像装置 100 の動作時、感度制御線 42 を介して光電変換部 13 に所定の電圧を供給する。電圧供給回路 32 は、特定の電源回路に限定されず、所定の電圧を生成する回路であってもよいし、他の電源から供給された電圧を所定の電圧に変換する回路であってもよい。後に詳しく説明するように、電圧供給回路 32 から光電変換部 13 に供給される電圧が、互いに異なる複数の電圧の間で切り替えられることにより、光電変換部 13 からの電荷蓄積ノード 41 への信号電荷の蓄積の開始および終了が制御される。換言すれば、本開示の実施形態では、電圧供給回路 32 から光電変換部 13 に供給される電圧を第三電圧と他の電圧との間で切り替えることによって、電子シャッタ動作が実行される。撮像装置 100 の動作の例は、後述する。

20

【 0 0 2 9 】

各単位画素セル 10 は、電源電圧 VDD を供給する電源線 40 との接続を有する。図示するように、電源線 40 には、信号検出トランジスタ 24 の入力端子 (典型的にはドレイン) が接続されている。電源線 40 がソースフォロア電源として機能することにより、信号検出トランジスタ 24 は、光電変換部 13 によって生成された信号電荷を、その信号電荷に応じた電圧に増幅して信号電圧として出力する。

30

【 0 0 3 0 】

信号検出トランジスタ 24 の出力端子 (ここではソース) には、アドレストランジスタ 26 の入力端子 (ここではドレイン) が接続されている。アドレストランジスタ 26 の出力端子 (ここではソース) は、画素アレイ 200 の列ごとに配置された複数の垂直信号線 47 のうちの 1 つに接続されている。アドレストランジスタ 26 の制御端子 (ここではゲート) は、アドレス制御線 46 に接続されており、アドレス制御線 46 の電位を制御することにより、信号検出トランジスタ 24 の出力を、対応する垂直信号線 47 に選択的に読み出すことができる。

40

【 0 0 3 1 】

図示する例では、アドレス制御線 46 は、垂直走査回路 (「行走査回路」とも呼ばれる) 36 に接続されている。垂直走査回路 36 は、アドレス制御線 46 に所定の電圧を印加することにより、各行に配置された複数の単位画素セル 10 を行単位で選択する。これにより、選択された単位画素セル 10 の信号の読み出しが実行される。

50

## 【0032】

垂直信号線 47 は、画素アレイ 200 からの画素信号を周辺回路へ伝達する主信号線である。垂直信号線 47 には、カラム信号処理回路（「行信号蓄積回路」とも呼ばれる）37 が接続される。カラム信号処理回路 37 は、相関二重サンプリングに代表される雑音抑圧信号処理およびアナログ - デジタル変換（A/D 変換）などを行う。図示するように、カラム信号処理回路 37 は、画素アレイ 200 における単位画素セル 10 の各列に対応して設けられる。これらのカラム信号処理回路 37 には、水平信号読み出し回路（「列走査回路」とも呼ばれる）38 が接続される。水平信号読み出し回路 38 は、複数のカラム信号処理回路 37 から水平共通信号線 49 に信号を順次読み出す。

## 【0033】

図 1 に例示する構成において、単位画素セル 10 は、リセットトランジスタ 28 を有する。リセットトランジスタ 28 は、例えば、信号検出トランジスタ 24 およびアドレストランジスタ 26 と同様に、電界効果トランジスタである。以下では、特に断りの無い限り、リセットトランジスタ 28 として N チャンネル MOSFET を適用した例を説明する。図示するように、このリセットトランジスタ 28 は、リセット電圧  $V_r$  を供給するリセット電圧線 44 と、電荷蓄積ノード 41 との間に接続される。リセットトランジスタ 28 の制御端子（ここではゲート）は、リセット制御線 48 に接続されており、リセット制御線 48 の電位を制御することによって、電荷蓄積ノード 41 の電位をリセット電圧  $V_r$  にリセットすることができる。この例では、リセット制御線 48 が、垂直走査回路 36 に接続されている。したがって、垂直走査回路 36 がリセット制御線 48 に所定の電圧を印加することにより、各行に配置された複数の単位画素セル 10 を行単位でリセットすることができる。

10

## 【0034】

この例では、リセットトランジスタ 28 にリセット電圧  $V_r$  を供給するリセット電圧線 44 が、リセット電圧源 34 に接続されている。リセット電圧源 34 は、撮像装置 100 の動作時にリセット電圧線 44 に所定のリセット電圧  $V_r$  を供給可能な構成を有していればよく、上述の電圧供給回路 32 と同様に、特定の電源回路に限定されない。電圧供給回路 32 およびリセット電圧源 34 の各々は、単一の電圧供給回路の一部分であってもよいし、独立した別個の電圧供給回路であってもよい。なお、電圧供給回路 32 およびリセット電圧源 34 の一方または両方が、垂直走査回路 36 の一部分であってもよい。あるいは、電圧供給回路 32 からの感度制御電圧および / またはリセット電圧源 34 からのリセット電圧  $V_r$  が、垂直走査回路 36 を介して各単位画素セル 10 に供給されてもよい。

20

## 【0035】

リセット電圧  $V_r$  として、信号検出回路 14 の電源電圧  $V_{DD}$  を用いることも可能である。この場合、各単位画素セル 10 に電源電圧を供給する電圧供給回路（図 1 において不図示）と、リセット電圧源 34 とを共通化し得る。また、電源線 40 と、リセット電圧線 44 を共通化できるので、画素アレイ 200 における配線を単純化し得る。ただし、リセット電圧  $V_r$  と、信号検出回路 14 の電源電圧  $V_{DD}$  とに互いに異なる電圧を用いることは、撮像装置 100 のより柔軟な制御を可能にする。

30

## 【0036】

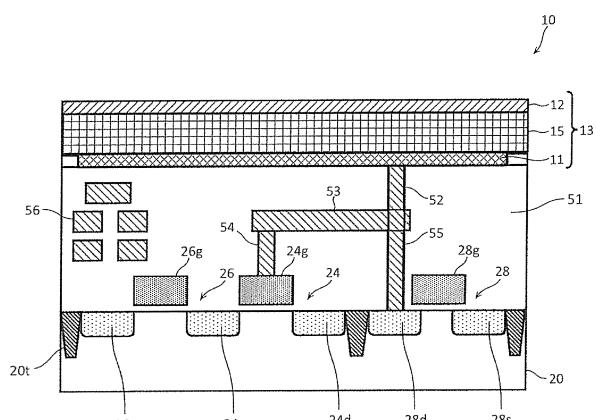

## （単位画素セルのデバイス構造）

図 2 は、単位画素セル 10 の例示的なデバイス構造を模式的に示す。図 2 に例示する構成では、上述の信号検出トランジスタ 24、アドレストランジスタ 26 およびリセットトランジスタ 28 が、半導体基板 20 に形成されている。半導体基板 20 は、その全体が半導体である基板に限定されない。半導体基板 20 は、感光領域が形成される側の表面に半導体層が設けられた絶縁性基板などであってもよい。ここでは、半導体基板 20 として P 型シリコン（Si）基板を用いる例を説明する。

40

## 【0037】

半導体基板 20 は、不純物領域（ここでは N 型領域）26s、24s、24d、28d、28s と、単位画素セル 10 間の電気的な分離のための素子分離領域 20t とを有する

50

。ここでは、素子分離領域 20t は、不純物領域 24d と不純物領域 28d との間にも設けられている。素子分離領域 20t は、例えば所定の注入条件のもとで、半導体基板 20 にアクセプターのイオン注入を行うことによって形成される。

【 0 0 3 8 】

不純物領域 26s、24s、24d、28d、28s は、典型的には、半導体基板 20 内に形成された拡散層である。図 2 に模式的に示すように、信号検出トランジスタ 24 は、不純物領域 24s、24d と、ゲート電極 24g (典型的にはポリシリコン電極) と、を含む。不純物領域 24s、24d は、それぞれ、信号検出トランジスタ 24 の例えばソース領域およびドレイン領域として機能する。不純物領域 24s と不純物領域 24d との間に、信号検出トランジスタ 24 のチャネル領域が形成される。

10

【 0 0 3 9 】

同様に、アドレストランジスタ 26 は、不純物領域 26s、24s と、アドレス制御線 46 (図 1 参照) に接続されたゲート電極 26g (典型的にはポリシリコン電極) と、を含む。この例では、信号検出トランジスタ 24 およびアドレストランジスタ 26 は、不純物領域 24s を共有することによって互いに電気的に接続されている。不純物領域 26s は、アドレストランジスタ 26 の例えばソース領域として機能する。不純物領域 26s は、図 2 において不図示の垂直信号線 47 (図 1 参照) との接続を有する。

【 0 0 4 0 】

リセットトランジスタ 28 は、不純物領域 28d、28s と、リセット制御線 48 (図 1 参照) に接続されたゲート電極 28g (典型的にはポリシリコン電極) と、を含む。不純物領域 28s は、リセットトランジスタ 28 の例えばソース領域として機能する。不純物領域 28s は、図 2 において不図示のリセット電圧線 44 (図 1 参照) との接続を有する。

20

【 0 0 4 1 】

半導体基板 20 上には、信号検出トランジスタ 24、アドレストランジスタ 26 およびリセットトランジスタ 28 を覆うように層間絶縁層 51 (典型的には二酸化シリコン層) が配置されている。図示するように、層間絶縁層 51 中には、配線層 56 が配置され得る。配線層 56 は、典型的には、銅などの金属から形成され、例えば、上述の垂直信号線 47 などの配線をその一部に含み得る。層間絶縁層 51 に含まれる絶縁層の数、および、層間絶縁層 51 中に配置される配線層 56 に含まれる配線層の数は、任意に設定可能であり、図 2 に示す例に限定されない。

30

【 0 0 4 2 】

層間絶縁層 51 上には、上述の光電変換部 13 が配置される。別の言い方をすれば、本開示の実施形態では、画素アレイ 200 (図 1 参照) を構成する複数の単位画素セル 10 が、半導体基板 20 上に形成されている。半導体基板 20 上に 2 次元に配列された複数の単位画素セル 10 は、感光領域を形成する。隣接する 2 つの単位画素セル 10 間の距離である画素ピッチは、例えば 2  $\mu\text{m}$  程度である。

【 0 0 4 3 】

光電変換部 13 は、画素電極 11 と、対向電極 12 と、これらの間に配置された光電変換層 15 とを含む。この例では、対向電極 12 および光電変換層 15 は、複数の単位画素セル 10 にまたがって形成されている。

40

【 0 0 4 4 】

他方、画素電極 11 は、単位画素セル 10 ごとに設けられており、隣接する他の単位画素セル 10 の画素電極 11 と空間的に分離されることによって、他の単位画素セル 10 の画素電極 11 から電気的に分離されている。

【 0 0 4 5 】

対向電極 12 は、典型的には、透明な導電性材料から形成される透明電極である。対向電極 12 は、光電変換層 15 において光が入射される側に配置される。したがって、光電変換層 15 には、対向電極 12 を透過した光が入射する。なお、撮像装置 100 によって検出される光は、可視光の波長範囲 (例えば、380 nm 以上 780 nm 以下) 内の光に

50

限定されない。本明細書における「透明」は、検出しようとする波長範囲の光の少なくとも一部を透過することを意味する。本明細書では、赤外線および紫外線を含めた電磁波全般を、便宜上「光」と表現する。対向電極12には、例えば、ITO (Indium doped Tin Oxide)、IZO (Indium Zinc Oxide)、AZO (Aluminum doped Zinc Oxide)、FTO (Fluorine doped Tin Oxide)、SnO<sub>2</sub>、TiO<sub>2</sub>、ZnO<sub>2</sub>などの透明導電性酸化物 (Transparent Conducting Oxide (TCO)) を用いることができる。

#### 【0046】

光電変換層15は、入射する光を受けて正孔-電子対を発生させる。光電変換層15は、本実施の形態の場合、有機材料から形成される。光電変換層15を構成する材料の具体例は、後述する。

#### 【0047】

図1を参照して説明したように、対向電極12は、電圧供給回路32に接続された感度制御線42との接続を有する。また、ここでは、対向電極12は、複数の単位画素セル10にまたがって形成されている。したがって、感度制御線42を介して、電圧供給回路32から所望の大きさの感度制御電圧を複数の単位画素セル10の間に一括して印加することが可能である。なお、電圧供給回路32から所望の大きさの感度制御電圧を印加することができれば、対向電極12は、単位画素セル10ごとに分離して設けられていてもよい。同様に、光電変換層15が単位画素セル10ごとに分離して設けられていてもよい。

#### 【0048】

後に詳しく説明するように、電圧供給回路32は、露光期間と非露光期間との間で互いに異なる電圧を対向電極12に供給する。本明細書において、「露光期間」は、光電変換により生成される正および負の電荷の一方を電荷蓄積領域に蓄積するための期間を意味し、「電荷蓄積期間」と呼んでもよい。また、本明細書では、撮像装置の動作中であって露光期間以外の期間を「非露光期間」と呼ぶ。なお、「非露光期間」は、光電変換部13への光の入射が遮断されている期間に限定されず、光電変換部13に光が照射されている期間を含んでいてもよい。

#### 【0049】

画素電極11の電位に対する対向電極12の電位を制御することにより、光電変換によって光電変換層15内に生じた正孔-電子対のうち、正孔および電子のいずれか一方を、画素電極11によって収集することができる。例えば信号電荷として正孔を利用する場合、画素電極11よりも対向電極12の電位を高くすることにより、画素電極11によって正孔を選択的に収集することができる。以下では、信号電荷として正孔を利用する場合を例示する。もちろん、信号電荷として電子を利用することも可能である。

#### 【0050】

対向電極12に対向する画素電極11は、対向電極12と画素電極11との間に適切なバイアス電圧が与えられることにより、光電変換層15において光電変換によって発生した正および負の電荷のうちの一方を収集する。画素電極11は、アルミニウム、銅などの金属、金属窒化物、または、不純物がドープされることにより導電性が付与されたポリシリコンなどから形成される。

#### 【0051】

画素電極11を遮光性の電極としてもよい。例えば、画素電極11として、厚さが100nmのTaN電極を形成することにより、十分な遮光性を実現し得る。画素電極11を遮光性の電極とすることにより、半導体基板20に形成されたトランジスタ（この例では信号検出トランジスタ24、アドレストランジスタ26およびリセットトランジスタ28の少なくともいずれか）のチャネル領域または不純物領域への、光電変換層15を通過した光の入射を抑制し得る。上述の配線層56を利用して層間絶縁層51内に遮光膜を形成してもよい。半導体基板20に形成されたトランジスタのチャネル領域への光の入射を抑制することにより、トランジスタの特性のシフト（例えば閾値電圧の変動）などを抑制し

10

20

30

40

50

得る。また、半導体基板 20 に形成された不純物領域への光の入射を抑制することにより、不純物領域における意図しない光電変換によるノイズの混入を抑制し得る。このように、半導体基板 20 への光の入射の抑制は、撮像装置 100 の信頼性の向上に貢献する。

#### 【 0 0 5 2 】

図 2 に模式的に示すように、画素電極 11 は、プラグ 52、配線 53 およびコンタクトプラグ 54 を介して、信号検出トランジスタ 24 のゲート電極 24g に接続されている。言い換れば、信号検出トランジスタ 24 のゲートは、画素電極 11 との電気的な接続を有する。プラグ 52、配線 53 は、例えば銅などの金属から形成される。プラグ 52、配線 53 およびコンタクトプラグ 54 は、信号検出トランジスタ 24 と光電変換部 13 との間の電荷蓄積ノード 41 (図 1 参照) の少なくとも一部を構成する。配線 53 は、配線層 56 の一部であり得る。また、画素電極 11 は、プラグ 52、配線 53 およびコンタクトプラグ 55 を介して、不純物領域 28d にも接続されている。図 2 に例示する構成において、信号検出トランジスタ 24 のゲート電極 24g、プラグ 52、配線 53、コンタクトプラグ 54、55、ならびに、リセットトランジスタ 28 のソース領域およびドレイン領域の一方である不純物領域 28d は、画素電極 11 によって収集された信号電荷を蓄積する電荷蓄積領域として機能する。

#### 【 0 0 5 3 】

画素電極 11 によって信号電荷が収集されることにより、電荷蓄積領域に蓄積された信号電荷の量に応じた電圧が、信号検出トランジスタ 24 のゲートに印加される。信号検出トランジスタ 24 は、この電圧を增幅する。信号検出トランジスタ 24 によって増幅された電圧が、信号電圧としてアドレストランジスタ 26 を介して選択的に読み出される。

#### 【 0 0 5 4 】

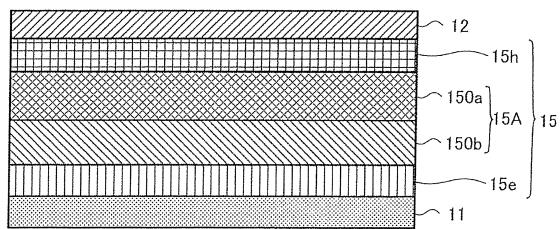

##### (光電変換層の構成の例)

上述したように、光電変換層 15 に光を照射し、画素電極 11 と対向電極 12 との間にバイアス電圧を印加することにより、光電変換によって生じる正および負の電荷のうちの一方を画素電極 11 によって収集し、収集された電荷を電荷蓄積領域に蓄積することができる。本実施の形態では、以下に説明するような互いに吸収スペクトルの異なる光電変換膜を一定の条件のもとで積層した感光層 15A を光電変換部 13 に用いている。これによると、画素電極 11 と対向電極 12 との間の電位差によって、光電変換層 15 の波長感度特性、つまり、撮像波長範囲を切り替えることが可能となる。また、電荷蓄積領域に既に蓄積された信号電荷は、画素電極 11 と対向電極 12 との間の電位差を所定の電位差以下にすることで、光電変換層 15 を介して対向電極 12 へ移動することを抑制できる。また、画素電極 11 と対向電極 12 との間の電位差を所定の電位差以下にすれば、その後、電荷蓄積領域へ信号電荷がさらに蓄積されることを抑制できる。このことは、本発明者らが新しく見出した知見の 1 つである。つまり、光電変換層 15 に印加するバイアス電圧の大きさの制御により、複数の画素のそれぞれに転送トランジスタなどの素子を別途設けることなく、グローバルシャッタ機能を有し、また、撮像波長の電気的な切り換えが可能である。撮像装置 100 における動作の典型例は、後述する。

#### 【 0 0 5 5 】

以下、光電変換層 15 の構成の例および光電変換層 15 における波長感度特性を説明する。

#### 【 0 0 5 6 】

図 3 は、光電変換層 15 の構成の一例を示す模式的な断面図である。図 3 に例示される構成において、光電変換層 15 は、正孔ブロッキング層 15h と、感光層 15A と、電子ブロッキング層 15e とを有している。正孔ブロッキング層 15h は、感光層 15A と対向電極 12 との間に配置されている。電子ブロッキング層 15e は感光層 15A と画素電極 11 との間に配置されている。光電変換層 15 は、典型的には、半導体材料を含む。ここでは、半導体材料として、有機半導体材料を用いる。有機半導体材料は、撮像で必要とする撮像波長において吸収ピークをもつ材料であればよいが、通常は電子供与性の有機半導体材料と、電子受容性の有機半導体材料を混合して光電変換膜を得る。これにより、光

電変換層 15 内で発生した励起子を電子と正孔に分離するのに必要な電界強度を半導体素子として十分使用可能な程度にまで小さくすることができる。言い換えると、同じ電圧における量子効率が増大し、光電変換特性が向上する。

【 0 0 5 7 】

本実施の形態の場合、対向電極 12 側に配置される第一光電変換膜 150a は、可視波長域のみに感度を有する波長感度特性を有し、画素電極 11 側に配置される第二光電変換膜 150b は、可視波長域に感度を有し、かつ赤外波長域に可視波長域よりも強い感度を有する波長感度特性を有している。なおここでは、ピーク波長の十分の一未満の感度は、感度がないものとして記載している。

【 0 0 5 8 】

有機半導体材料で構成した光電変換層 15 は、対向電極 12 と画素電極 11 との間に印加する電圧の大きさを変えることで、画素電極 11 まで到達する信号電荷の量を制御することができる。この理由は、有機半導体材料のキャリア輸送性能が非常に低く、光電変換層 15 内で発生した電荷を画素電極 11 に引っ張る電界強度が強くなければ、光電変換層 15 の中を移動中に再結合等で電荷が消失してしまうためである。

10

【 0 0 5 9 】

本実施の形態では、互いに吸収スペクトルの異なる第一光電変換膜 150a と第二光電変換膜 150b を対向電極 12 と画素電極 11 で挟む構成とした場合、第一光電変換膜 150a と第二光電変換膜 150b が所定の条件を満たす場合にのみ、対向電極 12 と画素電極 11 との間に印加する電圧に応じて信号電荷の画素電極 11 への輸送を制御できる。このことも本発明者らが新しく見出した知見の 1 つである。

20

【 0 0 6 0 】

上述した所定の条件としては、例えば、第一光電変換膜 150a と第二光電変換膜 150b のもつ膜抵抗の値に一定以上の差を設けることである。対向電極 12 と画素電極 11 間に印加された電圧は、第一光電変換膜 150a と第二光電変換膜 150b のそれぞれの光電変換膜がもつ膜抵抗の比で分配される。第一光電変換膜 150a と第二光電変換膜 150b のもつ膜抵抗に例えば 44 倍以上の差を設けることで、膜抵抗の高い光電変換膜に印加電圧の多くが分配され、他方へ分配される電圧を光電変換閾値以下とすることができる。したがって、対向電極 12 と画素電極 11 間の印加電圧が低い場合は、膜抵抗の高い光電変換膜にのみ光電変換閾値以上の電界がかかり、膜抵抗の高い光電変換膜で発生した信号のみが画素電極 11 へ輸送される。一方、対向電極 12 と画素電極 11 間の印加電圧を高くすると、膜抵抗の低い光電変換膜にも光電変換閾値以上の電界がかかるようになり、膜抵抗の低い光電変換膜も信号電荷を画素電極 11 へ輸送可能な状態へと遷移する。膜抵抗は光電変換膜を構成する電子供与性材料と電子受容性材料のエネルギー準位、混合比、膜厚などによって調整可能である。

30

【 0 0 6 1 】

また、光電変換層 15 に印加される電圧（すなわち、対向電極 12 と画素電極 11 間の印加電圧）が、積層された第一光電変換膜 150a と第二光電変換膜 150b のそれぞれの光電変換閾値を下回ると、いずれの光電変換層も信号電荷を画素電極へ輸送できなくなる。この結果、第一光電変換膜 150a と第二光電変換膜 150b の波長感度を実質的にゼロとなり、第一光電変換膜 150a 及び第二光電変換膜 150b が感度を有しなくなる。したがって、対向電極 12 と画素電極 11 との間の印加電圧を選択することによって、全ての波長に対して光電変換感度がない状態と、感光層 15A の第一光電変換膜 150a と第二光電変換膜 150b のいずれか一方のみが光電変換感度をもつ状態と、感光層 15A の第一光電変換膜 150a と第二光電変換膜 150b の双方が光電変換感度をもつ状態と、を切り替えることができる。以上により、画素電極 11 と対向電極 12 との間の電位差によって、光電変換層 15 の波長感度特性、つまり、撮像波長範囲を切り替え、かつ、電気的なシャッタ動作を実現することが可能となる。

40

【 0 0 6 2 】

上述した第一光電変換膜 150a と第二光電変換膜 150b としては、例えば、D T D

50

C T B ( 2 - { [ 7 - ( 5 - N , N - D i t o l y l a m i n o t h i o p h e n - 2 - y l ) - 2 , 1 , 3 - b e n z o t h i a d i a z o l - 4 - y l ] m e t h y l e n e } m a l o n o n i t r i l e ) と C 7 0 フラーレンとの共蒸着膜、スズナフタロシアニンと C 7 0 フラーレンとの共蒸着膜を用いることができる。さらに詳細には以下の材料を用いることができる。典型的には、第一光電変換膜 1 5 0 a および第二光電変換膜 1 5 0 b は、それぞれ、電子供与性（ドナー性、p型）の分子と、電子受容性（アクセプター性、n型）の分子とを含む。

#### 【 0 0 6 3 】

電子供与性の分子の典型例は、有機p型半導体であり、主に正孔輸送性有機化合物に代表され、電子を供与しやすい性質を有する。有機p型半導体の例は、D T D C T B 等のトリアリールアミン化合物、ベンジジン化合物、ピラゾリン化合物、スチリルアミン化合物、ヒドラゾン化合物、トリフェニルメタン化合物、カルバゾール化合物、ポリシラン化合物、-セキシチオフェン（以下、「-6T」と呼ぶ）、P 3 H T（ポリ3-ヘキシリチオフェン）等のチオフェン化合物、フタロシアニン化合物、シアニン化合物、メロシアニン化合物、オキソノール化合物、ポリアミン化合物、インドール化合物、ピロール化合物、ピラゾール化合物、ポリアリーレン化合物、縮合芳香族炭素環化合物（ナフタレン誘導体、アントラセン誘導体、フェナントレン誘導体、ルブレン等のテトラセン誘導体、ピレン誘導体、ペリレン誘導体、フルオランテン誘導体）、含窒素ヘテロ環化合物を配位子として有する金属錯体等である。フタロシアニン化合物の例は、銅フタロシアニン（C u P c）、サブフタロシアニン（S u b P c）、塩化アルミニウムフタロシアニン（C 1 A 1 P c）、S i ( O S i R 3 ) 2 N c（Rは、炭素数が1から18のアルキル基を表し、N c はナフタロシアニンを表す。）、スズナフタロシアニン（S n N c）および鉛フタロシアニン（P b P c）等である。ドナー性有機半導体は、これらに限らず、n型（アクセプター性）化合物として用いた有機化合物よりもイオン化ポテンシャルの小さい有機化合物であればドナー性有機半導体として用い得る。イオン化ポテンシャルは、真空準位と最高被占分子軌道（H O M O）のエネルギー準位との差である。

#### 【 0 0 6 4 】

電子受容性の分子の典型例は、有機n型半導体であり、主に電子輸送性有機化合物に代表され、電子を受容しやすい性質を有する。有機n型半導体の例は、C 6 0 およびC 7 0 等のフラーレン、フェニルC 6 1 酯酸メチルエステル（P C B M）等のフラーレン誘導体、縮合芳香族炭素環化合物（ナフタレン誘導体、アントラセン誘導体、フェナントレン誘導体、テトラセン誘導体、ピレン誘導体、ペリレン誘導体、フルオランテン誘導体）、窒素原子、酸素原子、硫黄原子を含有する5ないし7員のヘテロ環化合物（例えばピリジン、ピラジン、ピリミジン、ピリダジン、トリアジン、キノリン、キノキサリン、キナゾリン、フタラジン、シンノリン、イソキノリン、ブテリジン、アクリジン、フェナジン、フェナントロリン、テトラゾール、ピラゾール、イミダゾール、チアゾール、オキサゾール、インダゾール、ベンズイミダゾール、ベンゾトリアゾール、ベンゾオキサゾール、ベンゾチアゾール、カルバゾール、プリン、トリアゾロピリダジン、トリアゾロピリミジン、テトラザインデン、オキサジアゾール、イミダゾピリジン、ピラリジン、ピロロピリジン、チアジアゾロピリジン、ジベンズアゼピン、トリベンズアゼピン等）、サブフタロシアニン（S u b P c）、ポリアリーレン化合物、フルオレン化合物、シクロペンタジエン化合物、シリル化合物、ペリレンテトラカルボキシルジイミド化合物（P T C D I）、含窒素ヘテロ環化合物を配位子として有する金属錯体等である。アクセプター性有機半導体は、これらに限らず、p型（ドナー性）有機化合物として用いた有機化合物よりも電子親和力の大きな有機化合物であればアクセプター性有機半導体として用い得る。電子親和力は、真空準位と最低空分子軌道（L U M O）のエネルギー準位との差である。

#### 【 0 0 6 5 】

第一光電変換膜 1 5 0 a として例えば可視波長域に光電変換感度を有する有機半導体材料を用い、第二光電変換膜 1 5 0 b として例えば赤外波長域に感度を有する有機半導体材料を用いることができる。

10

20

30

40

50

## 【0066】

上記と同様の効果は、感光層 15 A の第一光電変換膜 150 a と第二光電変換膜 150 b の界面にエネルギー障壁を設けることでも実現可能である。例えば、信号電荷として正孔を蓄積する場合は、感光層 15 A の第一光電変換膜 150 a と第二光電変換膜 150 b の界面に、正孔に対して例えば 0.2 eV 以上のエネルギー障壁が形成されるように、第一光電変換膜 150 a と第二光電変換膜 150 b のイオン化ポテンシャルを選択すれば良い。

## 【0067】

第一光電変換膜 150 a と第二光電変換膜 150 b の界面にエネルギー障壁を設けない場合には、波長感度特性の電圧依存性はそれぞれの第一光電変換膜 150 a と第二光電変換膜 150 b の膜抵抗に支配され、波長感度特性の切り換え動作は積層順に依存しない。しかしながら、光電変換効率に着目した場合、より好ましい積層条件が存在する。上述したように、一般に、光電変換膜は電子供与性の有機半導体材料と電子受容性の有機半導体材料を混合することで得る。ここで、電子受容性材料としては C60 フラーレン、C70 フラーレンおよびその類縁体を用いてもよい。これは、フラーレンの LUMO 軌道が球殻上に空間的に広がっているため、接触する電子供与性の有機半導体材料から高い効率でフラーレン分子へ電子の移動が起こるためと考えられる。従って、高効率な光電変換素子を実現しようとする場合、所望の波長に吸収をもつ電子供与性有機半導体材料と、フラーレン及びその類縁体とを混合して光電変換膜を得てもよい。ところで、フラーレン及びその類縁体は一般に可視波長域、特に青色に相当する波長帯域に強い吸収をもつことが知られている。従って、赤外波長域に吸収をもつ電子供与性有機半導体材料を用いて赤外光電変換膜を設計すると、赤外のみならず、可視波長域にも吸収をもつ特性となる。この場合、第一光電変換膜 150 a に赤外光電変換膜を用い、第二光電変換膜 150 b に可視光域に感度を有する可視光電変換膜を用いるように積層すると、光の入射側に配置する第一光電変換膜で可視光の一部が吸収され、可視光電変換膜である第二光電変換膜に入射する可視光域の光量が減衰する。従って、このような場合には、可視光電変換膜を第一光電変換膜 150 a とし、赤外光電変換膜を第二光電変換膜 150 b とすると、第二光電変換膜に入射する可視光域の光の光量が減衰するのを抑制することができる。一方、可視光に吸収をもつ電子供与性有機半導体とフラーレン及びその類縁体を用いて可視光電変換膜を構成する場合には、赤外波長域に吸収をもたない特性となる。このため、このような可視光電変換膜を光の入射側に配置しても赤外光を透過し、十分な光量の赤外光を赤外光電変換膜に入射させることができる。このように、良好な撮像結果を得るためにには、所望の光電変換膜に所望の波長の光が十分に入射するよう、複数の光電変換膜の積層順序を決めてよい。

## 【0068】

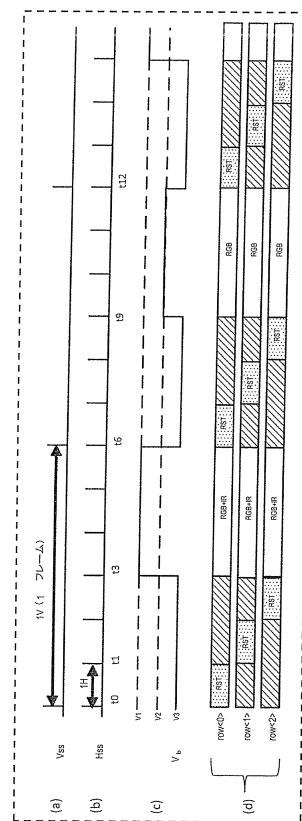

## (撮像装置 100 の動作の例)

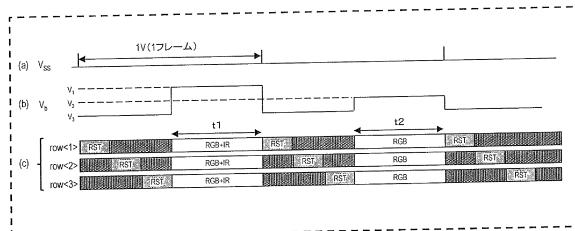

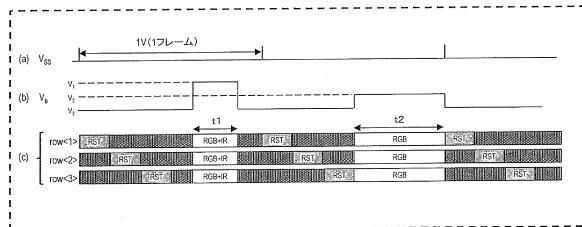

図 4 は、本開示の実施形態に係る撮像装置における動作の一例を説明するタイミングチャートである。図 4 において、部分 (a)、(b) は同期信号の立ち下がりまたは立ち上がりのタイミング、部分 (c) は光電変換層 15 に印加されるバイアス電圧の大きさの時間的变化、部分 (d) は画素アレイ 200 (図 1 参照) の各行におけるリセットおよび露光のタイミング、を示している。より具体的には、図 4 において、部分 (a) は垂直同期信号 Vss の立ち下がりまたは立ち上がりのタイミングを示し、部分 (b) は水平同期信号 Hss の立ち下がりまたは立ち上がりのタイミングを示している。部分 (c) は感度制御線 42 を介して電圧供給回路 32 から対向電極 12 に印加される電圧 Vb の時間的变化を示している。さらに部分 (d) は画素アレイ 200 の各行におけるリセットおよび露光のタイミングを示している。なお、感度制御線 42 を介して電圧供給回路 32 から対向電極 12 に印加される電圧 Vb の時間的变化は、画素電極 11 の電位を基準としたときの対向電極 12 の電位の時間的变化に相当する。

## 【0069】

なお図 4 では、説明を簡単にするために画素アレイ 200 中には 3 行の単位画素セル 10 が存在する場合を示しているが、画素アレイ 200 はさらに多くの行を備えていてもか

10

20

30

40

50

まわない。

**【 0 0 7 0 】**

以下、図1、図2および図4を参照しながら、撮像装置100における動作の一例を説明する。簡単のため、ここでは、画素アレイ200に含まれる画素の行数が、 $row < 0 >$ 行、 $row < 1 >$ 行、 $row < 2 >$ 行の合計3行である場合における動作の例を説明する。

**【 0 0 7 1 】**

画像の取得においては、まず、画素アレイ200中の各単位画素セル10の電荷蓄積領域のリセットと、先に露光していた場合にはその画素信号の読み出しが実行される。例えば、図4に示すように、垂直同期信号Vssに基づき、 $row < 0 >$ 行に属する複数の画素のリセットを開始する(時刻t0)。なお、図4中の網掛けの矩形は、信号の読み出し期間を模式的に表している。この読み出し期間は、単位画素セル10の電荷蓄積領域の電位をリセットするためのリセット期間をその一部に含む。

10

**【 0 0 7 2 】**

$row < 0 >$ 行に属する画素のリセットにおいては、 $row < 0 >$ 行のアドレス制御線46の電位の制御により、そのアドレス制御線46にゲートが接続されているアドレストランジスタ26をONとし、さらに、 $row < 0 >$ 行のリセット制御線48の電位の制御により、そのリセット制御線48にゲートが接続されているリセットトランジスタ28をONとする。これにより、電荷蓄積ノード41とリセット電圧線44とが接続され、電荷蓄積領域である電荷蓄積ノード41にリセット電圧Vrが供給される。すなわち、信号検出トランジスタ24のゲート電極24gおよび光電変換部13の画素電極11の電位が、リセット電圧Vrにリセットされる。その後、垂直信号線47を介して、 $row < 0 >$ 行の単位画素セル10からリセット後の画素信号を読み出す。このときに得られる画素信号は、リセット電圧Vrの大きさに対応した画素信号である。画素信号の読み出し後、リセットトランジスタ28およびアドレストランジスタ26をOFFとする。

20

**【 0 0 7 3 】**

この例では、図4に模式的に示すように、水平同期信号Hssにあわせて、 $row < 0 >$ 行、 $row < 1 >$ 行、 $row < 2 >$ 行の各行に属する画素のリセットを行単位で順次に実行する。以下では、水平同期信号Hssのパルスの間隔、換言すれば、ある行が選択されてから次の行が選択されるまでの期間を「1H期間」と呼ぶことがある。この例では、時刻t0から時刻t1までの期間が1H期間に相当する。

30

**【 0 0 7 4 】**

図4に示すように、少なくとも画素アレイ200の単位画素セル10がそれぞれ備える電荷蓄積領域の全てをリセットする期間であるリセット期間、画像取得の開始から、画素アレイ200の全ての行のリセットおよび画素信号の読み出しが終了するまでの期間(時刻t0からt3)においては、画素電極11と対向電極12との間には、所定の波長範囲における光電変換層15の感度が実質的に0となる第三電圧V3が、電圧供給回路32により印加されている。ここで、第三電圧V3は例えば0V(ボルト)である。すなわち、光電変換部13の光電変換層15に第三電圧V3のバイアス電圧を印加することにより、画素アレイ200から画像信号の取得を開始するタイミング(時刻t0)から露光期間の開始(時刻t3)までの期間(非露光期間)を創出することができる。

40

**【 0 0 7 5 】**

光電変換層15に第三電圧V3のバイアス電圧が印加された状態では、光電変換層15からの電荷蓄積領域への信号電荷の移動は、ほとんど起こらない。これは、光電変換層15に第三電圧V3のバイアス電圧が印加された状態では、光の照射によって生じた正および負の電荷のほとんどが、速やかに再結合し、画素電極11によって収集される前に消滅してしまうためであると推測される。したがって、光電変換層15に第三電圧V3のバイアス電圧が印加された状態では、光電変換層15に光が入射しても、電荷蓄積領域への信号電荷の蓄積は、ほとんど起こらない。そのため、露光期間以外の期間における、意図しない感度(以下、「寄生感度」と呼ぶことがある。)の発生が抑制される。

50

## 【 0 0 7 6 】

図 4 の部分 ( d ) において、ある行 ( 例えば  $row < 0 >$  行 ) に着目したとき、濃い網掛けの矩形および薄い網掛けの矩形で示される期間が、非露光期間を表している。なお、第三電圧  $V_3$  は、  $0 V$  に限定されない。

## 【 0 0 7 7 】

画素アレイ 200 の全ての行のリセットおよび画素信号の読み出しの終了後、水平同期信号  $H_{ss}$  に基づき、露光を開始する ( 時刻  $t_3$  )。図 4 の部分 ( d ) において、白の矩形は、各行における露光期間を模式的に表している。なお、図 4 では網掛けのある矩形が示す非露光期間と白の矩形が示す露光期間は同じ長さに記載されているが、これは説明のためであり同じ長さに限定する趣旨ではない。露光期間は被写体の暗さ及び被写体の動きの速さなどにより任意に調整される。露光期間は、電圧供給回路 32 が、画素電極 11 と対向電極 12 との間に印加する電圧を第三電圧  $V_3$  とは異なる第一電圧  $V_1$  ( または第二電圧  $V_2$  ) に切り替えることによって開始される。第一電圧  $V_1$  は、例えば、感光層 15 A のいずれもが光電変換閾値を超えて感度をもつような電圧である。光電変換層 15 に第一電圧  $V_1$  が印加されることにより、光電変換層 15 中の信号電荷 ( この例では正孔 ) が画素電極 11 によって収集され、電荷蓄積領域に蓄積される。図 5 は、実施形態に係る撮像装置 100 において、光電変換層 15 が有する波長感度特性の電圧依存性を示す一例である。本実施の形態の場合、図 5 に示すような波長感度特性にて、可視波長域および赤外波長域の光に基づき光電変換された信号電荷が電荷蓄積領域に蓄積される。図 4 の部分 ( d ) において、  $RGB + IR$  と記載された白い矩形の期間は、可視波長域及び赤外波長域の光に基づく信号電荷が電荷蓄積領域に蓄積される露光期間を表す。

10

20

30

## 【 0 0 7 8 】

電圧供給回路 32 が、画素電極 11 と対向電極 12 との間に印加する電圧を再び第三電圧  $V_3$  に切り替えることにより、露光期間が終了する ( 時刻  $t_6$  )。次に、水平同期信号  $H_{ss}$  に基づき、画素アレイ 200 の各行に属する画素からの信号電荷の読み出しを行う。この例では、時刻  $t_6$  から、  $row < 0 >$  行、  $row < 1 >$  行、  $row < 2 >$  行の各行に属する画素からの信号電荷の読み出しが行単位で順次に実行されている。以下では、ある行に属する画素が選択されてからその行に属する画素が再び選択されるまでの期間を「1V期間」と呼ぶことがある。この例では、時刻  $t_0$  から時刻  $t_6$  までの期間が 1V 期間に相当する。1V 期間は 1 フレームに相当する。光電変換層 15 に第一電圧  $V_1$  が印加された 1V 期間の、次の 1V 期間における露光期間には、光電変換層 15 に印加する電圧を第一電圧  $V_1$  および第三電圧  $V_3$  とは異なる第二電圧  $V_2$  に切り替える。第二電圧  $V_2$  は、例えば感光層 15 A のどちらか一方のみが光電変換閾値を超えるような電圧であり、例えば、第一電圧  $V_1$  と第三電圧  $V_3$  の中間にに対応する電圧である。本実施の形態の場合、光電変換層 15 に印加される電圧が第二電圧  $V_2$  のとき、図 5 に示すように、可視波長域の光のみに基づき光電変換された信号電荷が電荷蓄積領域に蓄積される。図 4 の部分 ( d ) において、  $RGB$  と記載された白い矩形の期間は、可視波長域の光のみに基づく信号電荷が電荷蓄積領域に蓄積される露光期間を表す。

30

## 【 0 0 7 9 】

光電変換層 15 に印加する電圧を再び第三電圧  $V_3$  に切替えることによって露光期間が終了する ( 時刻  $t_{12}$  )。その後、水平同期信号  $H_{ss}$  に基づき、画素アレイ 200 の各行に属する画素からの信号電荷の読み出しを行う。

40

## 【 0 0 8 0 】

このように、本開示の実施形態では、画素電極 11 と対向電極 12 との間に印加する電圧が露光期間中は第一電圧  $V_1$  及び第二電圧  $V_2$  のいずれか一方が選択され、第一電圧  $V_1$  から第二電圧  $V_2$  、または、第二電圧  $V_2$  から第一電圧  $V_1$  へ光電変換層 15 に印加する供給電圧を切り替える間、つまり、少なくとも電荷蓄積領域を全て読み出す期間を含む非露光期間は第三電圧  $V_3$  が選択される。これによって、波長感度特性が異なる光電変換層 15 から得られる 2 種類の画像をいわゆるグローバルシャッタによって得ることができる。

50

## 【0081】

また、画素電極11と対向電極12との間に、第一電圧V1を印加する1V期間と第二電圧V2を印加する1V期間とを交互に実行することで、波長感度特性が異なる光電変換層15から得られる2種類の動画をほぼ同時に1つの撮像装置100で得ることができる。また、これらの2種類の動画が電気的に実現されるグローバルシャッタにより得られるため、いずれの動画においても、高速に動く被写体を歪みなく撮像された動画となる。

## 【0082】

また、画素電極11と対向電極12との間に、第一電圧V1を印加する期間と第二電圧V2を印加する期間は交互ではなく、変更頻度は任意でよい。また、電圧変更の処理が行われる頻度はフレーム数で規定されてもよい。また、定期的に電圧変更の処理が行われるのではなく、何らかのトリガに基づくタイミングに基づいて電圧変更の処理が行われてもよい。例えば、電圧変更の処理は数十フレームに1回、実施してもよい。また、必要なタイミングで赤外光を検出するため、例えば1秒に1回だけ、可視光及び赤外光による撮像モードで撮像して赤外光による撮像情報を得、通常は可視光による撮像モードでカラー画像を取得するとしてもよい。

10

## 【0083】

本実施の形態の場合、第一電圧V1を印加することによって可視波長域に感度を有し、かつ、赤外波長域に所定の第一閾値以上の感度を有する波長感度特性となり、第一電圧V1よりも低電圧の第二電圧V2を印加することによって可視波長域のみに所定の第二閾値以上の感度を有する波長感度特性となる光電変換層15が採用されている。従って、可視波長域から赤外波長域までの波長を使った露光期間と、可視波長域の波長のみを使った露光期間とが切り替えられる。図4からわかるように、この例における露光期間の開始（時刻t3、時刻t9）および終了（時刻t6、時刻t12）は、画素アレイ200に含まれる全ての画素において同じタイミングである。すなわち、ここで説明する動作は、所謂グローバルシャッタである。

20

## 【0084】

一方、画素電極11と対向電極12との間に印加する電圧を、第一電圧V1と第二電圧V2との間で切り替える間に第三電圧V3に設定しない場合、電気的に非露光状態を創出することができない。このため、画像の取得が所謂ローリングシャッタになる。また、2種類の波長感度特性であるときに生成した信号電荷、つまり可視波長域の光のみによる信号電荷と、可視波長域及び赤外波長域を含む光による信号電荷とが、混在した状態で、電荷蓄積領域に蓄積されることになる。したがって、正しい画像を得ることが困難になる。

30

## 【0085】

本実施の形態では、露光期間の終了後における、`row < 0 >`行に属する画素からの信号電荷の読み出しにおいては、`row < 0 >`行のアドレストランジスタ26をONとする。これにより、露光期間において電荷蓄積領域に蓄積された電荷量に対応した画素信号が垂直信号線47に出力される。画素信号の読み出しに続けて、リセットトランジスタ28をONとして画素のリセットを行って、画素のリセット電圧をその画素の基準信号として読み出してもよい。画素信号の読み出し後、アドレストランジスタ26（およびリセットトランジスタ28）をOFFとする。画素アレイ200の各行に属する画素からの信号電荷の読み出し後、時刻t0と時刻t3との間において、読み出された画素信号と基準信号との差分をとることにより、固定ノイズを除去した信号が得られる。

40

## 【0086】

このとき、画素電極11と対向電極12との間には第三電圧V3が印加されているので、光電変換層15は、感度が実質的に0となるバイアス電圧が印加された状態にある。そのため、光電変換層15に光が入射した状態であっても、電荷蓄積領域への信号電荷のさらなる蓄積はほとんど起こらない。したがって、意図しない電荷の混入に起因するノイズの発生が抑制される。

## 【0087】

なお、非露光期間における電荷蓄積領域への信号電荷のさらなる蓄積を抑制するという

50

観点から、画素電極 1 1 と対向電極 1 2 との間に、上述の第三電圧 V 3 の極性を反転させた電圧を印加することによって、露光期間を終了させてもよい。なお、画素電極 1 1 と対向電極 1 2 との間に印加する電圧の極性を単純に反転させると、電荷蓄積領域に既に蓄積された信号電荷が光電変換層 1 5 を介して対向電極 1 2 へ移動することがある。この信号電荷の移動は、例えば、取得された画像中の黒点として観察される。つまり、非露光期間における電荷蓄積領域からの光電変換層 1 5 を介した対向電極 1 2 への信号電荷の移動は、マイナスの寄生感度の要因になり得る。

#### 【 0 0 8 8 】

本実施形態では、光電変換層 1 5 に印加される電圧を第三電圧 V 3 に変更することで露光期間を終了させているので、電荷蓄積領域への信号電荷の蓄積が終わった後の光電変換層 1 5 は、感度が実質的に 0 となるバイアス電圧が印加された状態にある。第三電圧 V 3 がバイアス電圧として印加された状態では、電荷蓄積領域に既に蓄積された信号電荷の光電変換層 1 5 を介した対向電極 1 2 への移動を抑制することが可能である。換言すれば、光電変換層 1 5 への第三電圧 V 3 の印加により、露光期間において蓄積された信号電荷を電荷蓄積領域に保持しておくことが可能である。つまり、電荷蓄積領域から信号電荷が失われることによるマイナスの寄生感度の発生を抑制し得る。

#### 【 0 0 8 9 】

このように、本実施形態では、露光期間の開始と終了、および露光期間の撮像波長が、画素電極 1 1 と対向電極 1 2 との間に印加される電圧 V b によって制御される。すなわち、本実施形態によれば、各単位画素セル 1 0 の撮像波長を全画素同時に切り換えて撮像することができる。

#### 【 0 0 9 0 】

有機半導体材料を含む光電変換層を備える有機光電変換素子は、従来のフォトダイオードを有する無機光電変換素子に比べて、構造及び製造プロセスを簡素化できる。また、有機半導体材料は、光電変換に寄与する波長範囲を任意に設計でき、所望の波長感度特性を有する光電変換素子を実現できる。

#### 【 0 0 9 1 】

有機光電変換素子を複数配列したイメージセンサでは、各光電変換素子に印加する電圧を変更することで露光期間毎に感度を変更できるが、撮像波長を変更することはできない。撮像波長を変更するためには、イメージセンサの前面に所望の波長のみを透過する挿抜可能なフィルタを配置する方法が考えられる。しかし、この場合は装置構成が大きくなることに加え、フィルタの挿抜期間中は良好な撮像結果が得られないという課題がある。

#### 【 0 0 9 2 】

##### ( 赤外画像信号の抽出方法 )

以下に、本実施形態に係る撮像装置 1 0 0 において、赤外画像信号を抽出する方法について説明する。なお、以下では、便宜上可視光による撮像を R G B モード、可視光及び赤外光による撮像を R G B + I R モードと記述する。

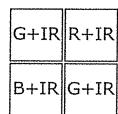

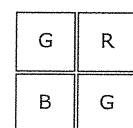

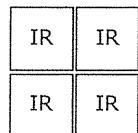

#### 【 0 0 9 3 】

図 6 A から図 6 F は、この赤外画像信号の抽出方法を説明するための図である。図 6 A は第一電圧 V 1 を印加したときの可視光及び赤外光（図では R G B + I R と記載）に対するイメージセンサの分光感度曲線、図 6 B は第二電圧 V 2 を印加したときの可視光（図では R G B と記載）に対するイメージセンサの分光感度曲線、図 6 C は赤外光（図では I R と記載）の分光感度曲線を示している。図 6 A から図 6 C において、横軸は光の波長、縦軸は感度を示す。図 6 D から図 6 F に示すように、各画素は、例えば、1 つの R 画素、2 つの G 画素、及び 1 つの B 画素を含むベイヤ配列を有する。このようなベイヤ配列の画素アレイを構成するにはイメージセンサ上に R、G、B それぞれに対応する透過率を示すよう染料または顔料等で構成されたカラーフィルタを設けることで実現できる。すなわち、各画素の信号はイメージセンサの分光感度曲線と用いるカラーフィルタの透過率曲線との積で与えられる波長依存性をもつことになる。ところで、通常用いられる染料カラーフィルタ及び顔料カラーフィルタは所望の波長域のみならず、赤外領域にも高い透過率を示す

10

20

30

40

50

。R画素に用いられるカラーフィルタは赤色(R)とともに赤外光に高い透過率をもつ。同様にG画素に用いられるカラーフィルタは緑色(G)とともに赤外光に高い透過率をもち、B画素に用いられるカラーフィルタは青色(B)とともに赤外光に対する高い透過率をもつ。従って、図6Eに示すように、RGBモードにおいては、R画素では、赤色(R)に対応する信号が得られ、G画素では、緑色(G)に対応する信号が得られ、B画素では、青色(B)に対応する信号が得られる。図6Dに示すように、RGB+IRモードにおいては、R画素では、赤色及び赤外(すなわち、R+IR)に対応する信号が得られ、G画素では、緑色及び赤外(すなわち、G+IR)に対応する信号が得られ、B画素では、青色及び赤外(すなわち、B+IR)に対応する信号が得られる。

## 【0094】

10

RGB+IRモードにより得られる画像信号は、図6Aの分光感度曲線に示すように、赤外光による信号に、R、G、Bそれぞれのカラーフィルタを透過する色情報に基づいた信号が重畠されている。したがって、このままでは赤外光による信号情報のみを画像化することはできない。しかし、図6A及び図6Bに示すように、RGB+IRモードにおける分光感度曲線とRGBモードにおける分光感度曲線が可視波長域で同一の形状を有していれば、RGBモードで取得した画像信号に所定のゲインを掛けることによってRGB+IRモードで取得される画像信号のRGB成分を再現できる。なお、図6Bでは、RGBモードにおける分光感度曲線を実線で示し、当該分光感度曲線に係数を乗算した分光感度曲線を点線で示している。

## 【0095】

20

ゲインは、ゲインR、G、Bを含む。RGBモードにおいて、R画素で生成されたR信号に対してゲインRが乗算され、G画素で生成されたG信号に対してゲインGが乗算され、B画素で生成されたB信号に対してゲインBが乗算される。これによって、RGBモードで取得される画像信号から、RGB+IRモードで取得される画像信号のRGB成分に対応する信号が生成される。

## 【0096】

次に、RGB+IRモードで得られた画像信号から、RGBモードで得られた画像信号にゲインを乗算した信号を減算することで、図6C及び図6Fに示すように、赤外光に対応する画像信号を得ることができる。

## 【0097】

30

なお、上記処理は、図1に示す演算回路50により行われる。演算回路50は、例えば、DSP(Digital Signal Processor)等のマイクロプロセッサにより実現される信号処理回路に含まれる。なお、演算回路50は、単位画素セル10を含むイメージセンサ内に設けられてもよい。

## 【0098】

このように、演算回路50は、複数の露光期間の各々において、(i)画素電極11及び対向電極12の間に第1電圧が印加されることにより、可視光及び赤外光を用いて撮像された画像に相当する第1信号を取得し、(ii)画素電極11及び対向電極12の間に、第1電圧と異なる第2電圧が印加されることにより、可視光を用いて撮像された画像に相当する第2信号を取得し、(iii)第1信号及び第2信号を用いて所定の演算を行うことにより、赤外光を用いて撮像された画像に相当する第3信号を生成する。

40

## 【0099】

これにより、撮像装置100は、光電変換層15への印加電圧を変更することで、可視光による撮像と、可視光及び赤外光による撮像を全画素同時に切り換えることが可能である。さらに、撮像装置100は、可視波長域で撮影された画像と、可視及び赤外波長域で撮影された画像とを用いて、赤外波長域で撮影された画像を生成できる。このように、撮像装置100は、可動式のフィルタを設けることなく、可視光による画像と、可視光及び赤外光による画像と、赤外光による画像とを生成できる。

## 【0100】

以下、ゲインの算出方法について説明する。

50

## 【0101】

図5において、分光感度曲線のR、G、Bの各波長領域における、RGBモードでの量子効率に対するRGB+IRモードでの量子効率の比を各々、R、G、Bとすれば、このR、G、Bを用いて、RGB+IRモードで取得した各画素の信号量からR、G、Bのカラー情報を除去して赤外信号情報のみを抽出することができる。

## 【0102】

ここで、R、G、Bは、下記(式1)から(式3)で表される。Q1R、Q1G、Q1Bは、RGB+IRモードにおける赤色(R)、緑色(G)、青色(B)の量子効率であり、Q2R、Q2G、Q2Bは、RGBモードにおける赤色(R)、緑色(G)、青色(B)の量子効率である。

10

## 【0103】

$$R = R = Q1R / Q2R \quad \dots \quad (\text{式1})$$

## 【0104】

$$G = G = Q1G / Q2G \quad \dots \quad (\text{式2})$$

## 【0105】

$$B = B = Q1B / Q2B \quad \dots \quad (\text{式3})$$

## 【0106】

このように、 $= Q1 / Q2$ が満たされる。ここで、Q1は、Q1R、Q1G、Q1Bを含み、Q2は、Q2R、Q2G、Q2Bを含む。

20

## 【0107】

なお、上記説明は、図7に示すように、RGB+IRモードの露光時間t1と、RGBモードの露光時間t2とが等しい場合の例である。図8に示すように、RGB+IRモードの露光時間t1と、RGBモードの露光時間t2とが異なる場合には、以下の演算が用いられる。図7及び図8において、部分(a)は垂直同期信号Vssの立ち下がりまたは立ち上がりのタイミング、部分(b)は光電変換層15に印加されるバイアス電圧の大きさの時間的变化、部分(c)は画素アレイ200の各行におけるリセットおよび露光のタイミング、を示している。

## 【0108】

信号電荷量はセンサの感度と露光時間との積で決まる。感度は量子効率で言い換えられるので、RGB+IRモードでの露光時間t1とRGBモードでの露光時間t2に基づいて、ゲイン $\times$ を以下の(式4)から(式6)で表される値とすることで赤外画像の抽出が行える。

30

## 【0109】

$$R = R \times (t1 / t2) \quad \dots \quad (\text{式4})$$

## 【0110】

$$G = G \times (t1 / t2) \quad \dots \quad (\text{式5})$$

## 【0111】

$$B = B \times (t1 / t2) \quad \dots \quad (\text{式6})$$

## 【0112】

このようにして、 $= (Q1 / Q2) \times (t1 / t2)$ が満たされる。

40

## 【0113】

なお、上記説明では、RGBモードで得られた信号にゲイン $\times$ を乗算する例を述べたが、これに限定されず、上記と同様に、RGB+IRモードで得られた信号と、RGBモードで得られた信号との比率を変更できればよい。例えば、RGB+IRモードで得られた信号にゲインを乗算してもよいし、RGB+IRモードで得られた信号と、RGBモードで得られた信号との両方に、異なるゲインを乗算してもよい。具体的には、RGB+IRモードで得られた信号に乗算するゲインを $1$ とし、RGBモードで得られた信号に乗算するゲインを $2$ とする。この場合、 $1 / 2 = Q2 / Q1$ が満たされればよい。また、露光時間が異なる場合には、 $1 / 2 = (Q2 / Q1) \times (t2 / t1)$ が満たされればよい。

50

**【0114】**

また、露光時間の比  $t_1 / t_2$  を  $1 /$  となるように設定すればゲインは 1 となるため、特別なアンプを介さずに直接差分演算を行うことも可能である。

**【0115】**

また、通常、RGB モードでは光電変換層にかかる電圧が低い分だけ量子効率が低下する。したがって、図 8 に示すように、RGB モードの露光時間  $t_2$  を RGB+IR モードの露光時間  $t_1$  よりも長くすれば十分な信号量を取得できるため、RGB+IR モードでの画素の信号量と RGB モードでの画素の信号量との差分演算時の精度を高くできる。

**【0116】**

また、RGB+IR モードの露光時間が短いことによって光量不足となる場合は、別途高輝度の赤外線投光器からの照明光を、光電変換層 15 に照射してもよい。この照明光は連続光でもパルス光でもよい。この照明光が、RGB+IR モードの露光期間と同期したパルス光であると、赤外線投光器の消費電力を低減することができる。

10

**【0117】**

以上、本実施の形態に係る撮像装置について説明したが、本開示は、この実施の形態に限定されるものではない。

**【0118】**

また、上記実施形態に係る撮像装置に含まれる各処理部は典型的には集積回路である LSIs として実現される。これらは個別に 1 チップ化されてもよいし、一部又は全てを含むように 1 チップ化されてもよい。

20

**【0119】**

また、集積回路化は LSIs に限るものではなく、専用回路又は汎用プロセッサで実現してもよい。LSIs 製造後にプログラムすることが可能な FPGA (Field Programmable Gate Array)、又は LSIs 内部の回路セルの接続及び設定を再構成可能なリコンフィギュラブル・プロセッサを利用してよい。

**【0120】**

以上、一つまたは複数の態様に係る撮像装置について、実施の形態に基づいて説明したが、本開示は、この実施の形態に限定されるものではない。本開示の趣旨を逸脱しない限り、当業者が思いつく各種変形を本実施の形態に施したもの、及び異なる実施の形態における構成要素を組み合わせて構築される形態も、一つまたは複数の態様の範囲内に含まれてもよい。

30

**【産業上の利用可能性】****【0121】**

本開示の一態様に係る撮像装置は、医療用カメラ、ロボット用カメラ、セキュリティカメラ、又は車載カメラなどに用いることができる。

**【符号の説明】****【0122】**

10 単位画素セル

11 画素電極

12 対向電極

40

13 光電変換部

14 信号検出回路

15 光電変換層

15A 感光層

15e 電子ブロッキング層

15h 正孔ブロッキング層

20 半導体基板

24 信号検出トランジスタ

26 アドレストランジスタ

32 電圧供給回路

50

4 1 電荷蓄積ノード

5 0 演算回路

1 0 0 撮像装置

1 5 0 a 第一光電変換膜

1 5 0 b 第二光電変換膜

2 0 0 画素アレイ

【図面】

【図 1】

【図 2】

10

20

30

40

50

【図 3】

【図 4】

【図 5】

【図 6 A】

【図 6 B】

【図 6 C】

【図 6 D】

【図 6 E】

【図 6 F】

【図 7】

10

20

【図 8】

30

40

50

## フロントページの続き

## (51)国際特許分類

|         |                 |     |         |       |

|---------|-----------------|-----|---------|-------|

| H 0 4 N | 9/07 (2006.01)  | F I | H 0 4 N | 5/374 |

| H 0 1 L | 27/30 (2006.01) |     | H 0 4 N | 9/07  |

|         |                 |     | H 0 1 L | 27/30 |

ナソニック株式会社内

## (72)発明者

徳原 健富

大阪府門真市大字門真1006番地 パナソニック株式会社内

## (72)発明者

柳田 真明

大阪府門真市大字門真1006番地 パナソニック株式会社内

## (72)発明者

宍戸 三四郎

大阪府門真市大字門真1006番地 パナソニック株式会社内

## (72)発明者

中田 学

大阪府門真市大字門真1006番地 パナソニック株式会社内

## (72)発明者

井土 真澄

大阪府門真市大字門真1006番地 パナソニック株式会社内

## 審査官

大室 秀明

## (56)参考文献

特開2008-227092 (JP, A)

特開2007-288549 (JP, A)

特開2016-076807 (JP, A)

特開平11-331855 (JP, A)

## (58)調査した分野 (Int.Cl., DB名)

H 0 1 L 2 1 / 3 3 9

H 0 1 L 2 7 / 1 4 - 2 7 / 1 4 8

H 0 1 L 2 7 / 3 0

H 0 1 L 2 9 / 7 6 2

H 0 1 L 3 1 / 0 0 - 3 1 / 0 2

H 0 1 L 3 1 / 0 2 3 2

H 0 1 L 3 1 / 0 2 4 8

H 0 1 L 3 1 / 0 2 6 4

H 0 1 L 3 1 / 0 8

H 0 1 L 3 1 / 1 0

H 0 1 L 3 1 / 1 0 7 - 3 1 / 1 0 8

H 0 1 L 3 1 / 1 1 1

H 0 1 L 3 1 / 1 8

H 0 1 L 5 1 / 4 2

H 0 4 N 5 / 3 0 - 5 / 3 7 8

H 0 4 N 9 / 0 4 - 9 / 1 1