(12) 发明专利申请

(10) 申请公布号 CN 111971884 A

(43) 申请公布日 2020.11.20

(21) 申请号 201980025569.4

(74) 专利代理机构 北京尚诚知识产权代理有限

(22) 申请日 2019.03.11

公司 11322

(30) 优先权数据

代理人 龙淳

2018-082704 2018.04.24 JP

(51) Int.CI.

H02M 1/08 (2006.01)

(85) PCT国际申请进入国家阶段日

H03K 17/08 (2006.01)

2020.10.13

H03K 17/0812 (2006.01)

(86) PCT国际申请的申请数据

PCT/JP2019/009651 2019.03.11

(87) PCT国际申请的公布数据

W02019/207977 JA 2019.10.31

(71) 申请人 株式会社日立制作所

地址 日本东京都

(72) 发明人 铃木弘 栗原直树

权利要求书2页 说明书8页 附图5页

(54) 发明名称

栅极驱动电路和栅极驱动方法

(57) 摘要

本发明的目的涉及在使用了SiC的电压驱动型的半导体元件的栅极驱动电路中抑制栅极-源极间电压的变动。为此，本发明的栅极驱动电路是通过将P型MOSFET和N型MOSFET串联连接并将N型MOSFET与负侧电源直接连接而构成的，是位于P型MOSFET与N型MOSFET的中间的输出级在使用了SiC的电压驱动型的半导体元件处于关断状态时成为负偏压的结构。根据本发明，因为用过渡阻抗小的MOSFET构成输出级，所以能够抑制使用了SiC的电压驱动型的半导体元件的驱动时的栅极-源极间电压的变动，在使用了SiC的电压驱动型的半导体元件关断中使栅极成为负偏压，所以能够防止误导通。从而能够提供适合SiC元件的驱动的高可靠性的栅极驱动电路。

1. 一种用于驱动使用了SiC的电压驱动型的半导体元件的栅极驱动电路,其特征在于:

所述栅极驱动电路是通过将P型MOSFET和N型MOSFET串联连接并将所述N型MOSFET与负侧电源直接连接而构成的,以使得位于所述P型MOSFET与所述N型MOSFET的中间的输出级在所述半导体元件处于关断状态时成为负偏压的方式使所述P型MOSFET和所述N型MOSFET互补地导通和关断。

2. 如权利要求1所述的栅极驱动电路,其特征在于:

具有在所述半导体元件处于关断状态时将输出级维持为负偏压的电压维持单元。

3. 如权利要求2所述的栅极驱动电路,其特征在于:

所述电压维持单元包括在所述输出部和所述负侧电源之间与所述N型MOSFET并联连接的二极管。

4. 如权利要求3所述的栅极驱动电路,其特征在于:

所述二极管是肖特基势垒二极管、齐纳二极管或PN二极管。

5. 如权利要求2所述的栅极驱动电路,其特征在于:

所述电压维持单元包括:与位于所述输出级和N型MOSFET的中间的关断侧栅极电阻并联连接的并联化电阻、与所述并联化电阻串联连接的开关、以及在所述半导体元件处于关断状态的情况下使所述开关导通的判断部。

6. 如权利要求2所述的栅极驱动电路,其特征在于:

所述电压维持单元包括:在所述输出级和所述负侧电源之间与所述N型MOSFET并联连接的MOSFET、以及在所述半导体元件处于关断状态的情况下使所述MOSFET短路的判断部。

7. 如权利要求1~6中任一项所述的栅极驱动电路,其特征在于:

所述半导体元件是常断型的半导体元件。

8. 如权利要求1~7中任一项所述的栅极驱动电路,其特征在于:

所述负侧电源产生电压时使用绝缘型电源变压器或绝缘型DCDC转换器。

9. 一种三相交流逆变器,其特征在于:

搭载有权利要求1~8中任一项所述的栅极驱动电路。

10. 一种使用了SiC的电压驱动型的半导体元件的栅极驱动方法,其特征在于:

使P型MOSFET和与负极电源直接连接的N型MOSFET互补地导通和关断,使得位于串联连接的所述P型MOSFET与所述N型MOSFET的中间的输出级在所述半导体元件处于关断状态时成为负偏压。

11. 如权利要求10所述的栅极驱动方法,其特征在于:

在所述半导体元件处于关断状态时用电压维持单元将输出级维持为负偏压。

12. 如权利要求11所述的栅极驱动方法,其特征在于:

所述电压维持单元包括在所述输出部和所述负侧电源之间与所述N型MOSFET并联连接的二极管。

13. 如权利要求12所述的栅极驱动方法,其特征在于:

所述二极管是肖特基势垒二极管、齐纳二极管或PN二极管。

14. 如权利要求11所述的栅极驱动方法,其特征在于:

在所述半导体元件处于关断状态的情况下,使与并联化电阻串联连接的开关导通,其中所述并联化电阻与位于所述输出级和N型MOSFET的中间的关断侧栅极电阻并联连接。

15. 如权利要求11所述的栅极驱动方法,其特征在于:

在所述半导体元件处于关断状态的情况下,使在所述输出级与所述负侧电源之间与所述N型MOSFET并联连接的MOSFET短路。

16. 如权利要求11~15中任一项所述的栅极驱动方法,其特征在于:

所述半导体元件是常断型的半导体元件。

17. 如权利要求11~16中任一项所述的栅极驱动方法,其特征在于:

用绝缘型电源变压器或绝缘型DCDC转换器生成所述负侧电源的电压。

## 栅极驱动电路和栅极驱动方法

### 技术领域

[0001] 本发明涉及SiC-MOSFET等使用了SiC的电压驱动型的半导体元件的栅极驱动电路。

### 背景技术

[0002] 能够高速地开关、并且能够控制大电力的IGBT (Insulated Gate Bipolar Transistor: 绝缘栅双极晶体管) 被广泛应用于从家庭用的小容量逆变器到铁路等中使用的大容量的逆变器。作为驱动IGBT等电压驱动型的半导体元件的电路，使用通过控制对栅极施加的电压而控制半导体元件的导通/关断的栅极驱动器等栅极驱动电路。近年来，代替Si的IGBT，使用了低损耗的使用了SiC的MOSFET (Metal-Oxide-Semi conductor Field Effect Transistor: 金属-绝缘体-半导体场效应晶体管) 的逆变器正在逐渐普及，对于铁路用途也要求适合SiC-MOSFET的驱动的栅极驱动器。

[0003] 现有技术文献

[0004] 专利文献

[0005] 专利文献1:日本特开2012-9962号公报

[0006] 专利文献2:日本特开2014-57491号公报

### 发明内容

[0007] 发明要解决的课题

[0008] 本发明人认真研究了对SiC-MOSFET等使用了SiC的电压驱动型的半导体元件进行驱动用的栅极驱动电路，结果得到了以下结论。

[0009] 作为SiC-MOSFET等使用了SiC的电压驱动型的半导体元件的特征之一，已知现状下对于对栅极施加的电场应力的耐性与Si-IGBT相比更低。例如，SiC-MOSFET中，栅极氧化膜的材料与Si-IGBT同为二氧化硅(SiO<sub>2</sub>)，但因为制造工艺和源自基板材料的缺陷，SiC元件中与Si元件相比施加栅极电场应力引起的元件特性的变动更显著。从而，栅极驱动器的输出电压超过半导体元件的栅极-源极间的额定电压地输出的情况下，与栅极驱动器连接的半导体元件的栅极-源极间电压也超过额定电压，所以存在元件特性的变动和栅极氧化膜的可靠性降低等风险。于是，要求栅极驱动器的输出电压稳定在不足半导体元件的栅极-源极间的额定电压的电压。

[0010] 作为SiC-MOSFET的其他特征，可以举出栅极-漏极间的反向传输电容大、开关速度(dV/dt)大。从而，存在易于发生MOSFET的栅极-源极间电压的变动(抬升)引起的误导通的课题。即，对MOSFET的漏极-源极间施加了较高的dV/dt时，经过反向传输电容的位移电流(C<sub>gd</sub>\*dV/dt)从MOSFET一侧向栅极驱动器一侧流动，所以因为该电流在栅极配线的电感成分和栅极驱动器电路内的电阻成分中流动的效果，SiC-MOSFET的栅极的电位易于抬升。结果，SiC-MOSFET的栅极-源极间电压超过阈值电压而成为误导通状态的情况下，例如存在引起臂短路等的风险。另外，SiC-MOSFET的反向传输电容与Si-IGBT相比一般更大的理由，在

于SiC-MOSFET是单极元件且基板的掺杂浓度高,所以耗尽层的宽度难以增大。

[0011] 因为以上SiC-MOSFET的2个特征,作为驱动它的栅极驱动器,要求具有能够抑制SiC-MOSFET的栅极-源极间电压的变动的特性。

[0012] 使用如专利文献1中记载的由使用了双极晶体管的推挽电路构成输出级的栅极驱动器对SiC-MOSFET进行导通/关断驱动的情况下,因为双极晶体管的过度阻抗大,所以栅极驱动器的输出电压超过栅极驱动器电路的电源电压地变动,结果SiC-MOSFET的栅极-源极间电压也会超过电源电压。即,如图9所示,在MOSFET导通时栅极-源极间电压( $V_{gs}$ )发生过度地超过栅极驱动器电路的正侧电源电压(+ $V_p$ )的过冲,在MOSFET关断时发生过度低于负侧电源电压(- $V_m$ )的下冲。因为该现象,MOSFET的栅极-源极间电压超过额定电压,或者与额定电压之间的裕度减少,所以在确保栅极氧化膜的可靠性的观点上存在风险。

[0013] 另外,SiC-MOSFET关断时,在关断一方的SiC-MOSFET中对漏极-源极间施加正的dV/dt(>0),在与关断一方相对一方的SiC-MOSFET中,施加负的dV/dt(<0)。此时,发生相对一方的SiC-MOSFET的栅极-源极间电压( $V_{gs}$ )沉降至低于栅极驱动器的负侧电源电压(- $V_m$ )的现象。

[0014] 专利文献2中,对于栅极驱动器的负侧电源经由二极管连接了输出级的MOSFET,但该结构中, $V_{gs}$ 沉降时,因为栅极驱动器的负侧电源与SiC-MOSFET的栅极端子之间存在上述二极管的电容成分,所以SiC-MOSFET的 $V_{gs}$ 不稳定,不能抑制栅极-源极间的电压变动。

[0015] 本发明的目的涉及在使用了SiC的电压驱动型的半导体元件的栅极驱动电路中抑制栅极-源极间电压的变动。

[0016] 用于解决课题的技术方案

[0017] 本发明涉及栅极驱动电路是将P型MOSFET和N型MOSFET串联连接并将N型MOSFET与负侧电源直接连接而构成的,位于P型MOSFET与N型MOSFET的中间的输出级在使用了SiC的电压驱动型的半导体元件处理关断状态时成为负偏压。

[0018] 发明的效果

[0019] 根据本发明,因为用过渡阻抗小的MOSFET构成输出级,所以能够抑制使用了SiC的电压驱动型的半导体元件的驱动时的栅极-源极间电压的变动,在使用了SiC的电压驱动型的半导体元件关断中使栅极负偏压,所以能够防止误导通。从而,能够提供一种适合SiC元件的驱动的高可靠性的栅极驱动电路。

## 附图说明

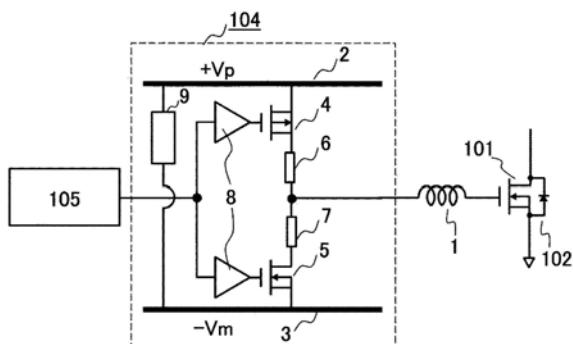

[0020] 图1是实施例1的铁路用逆变器系统的结构图。

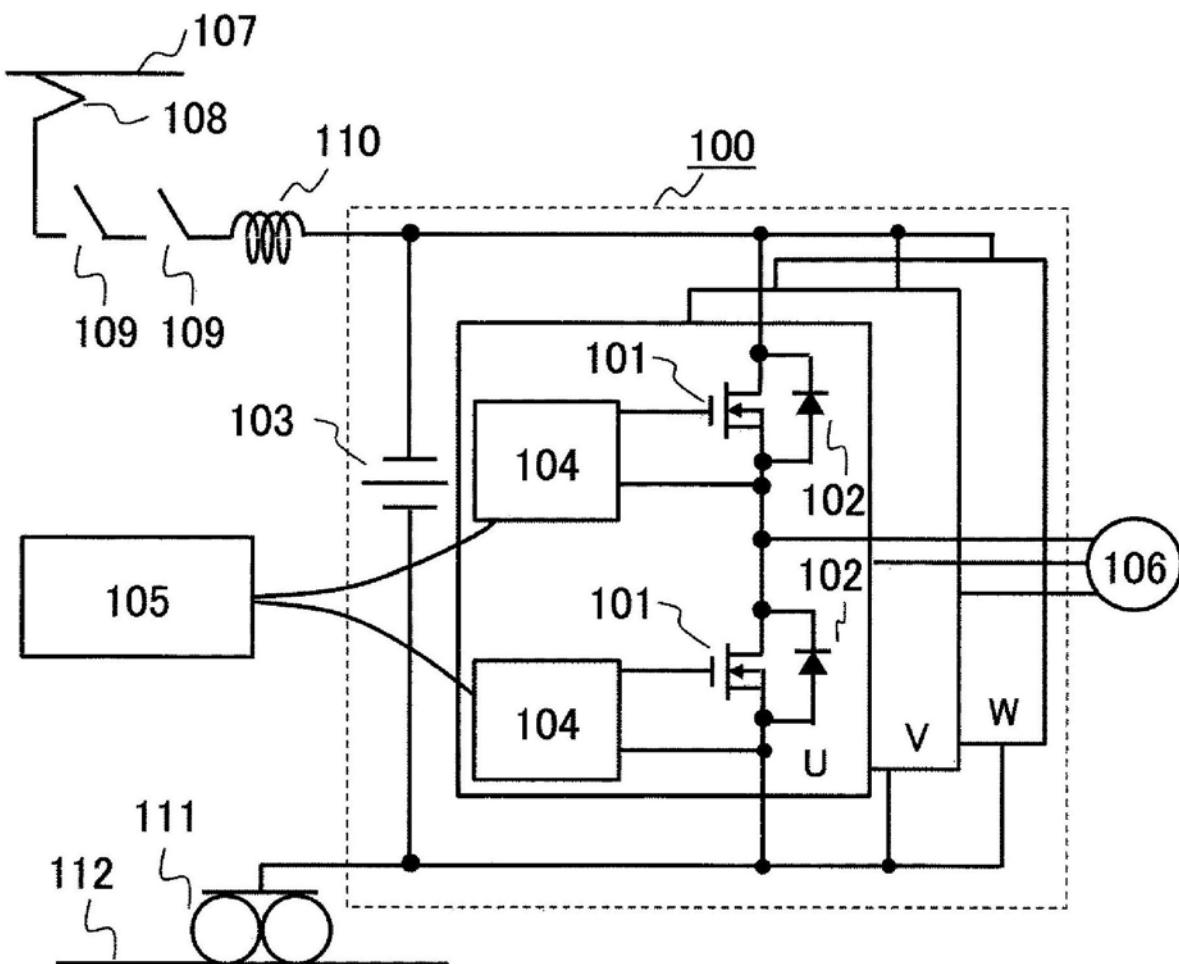

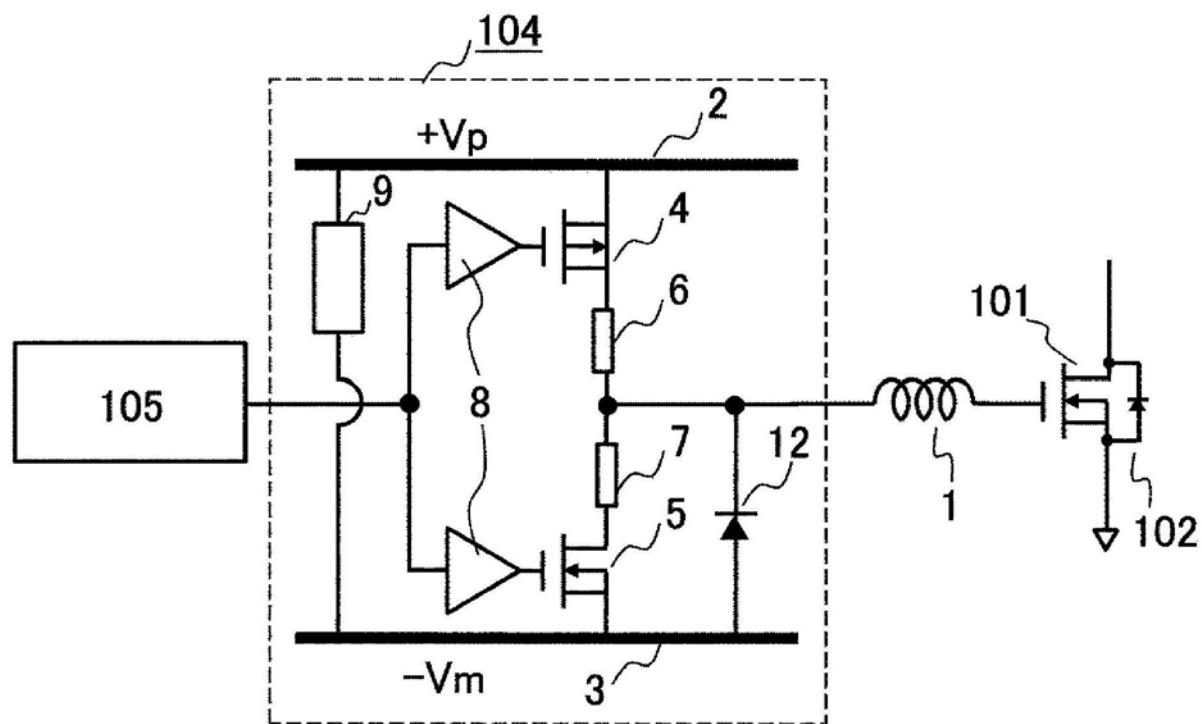

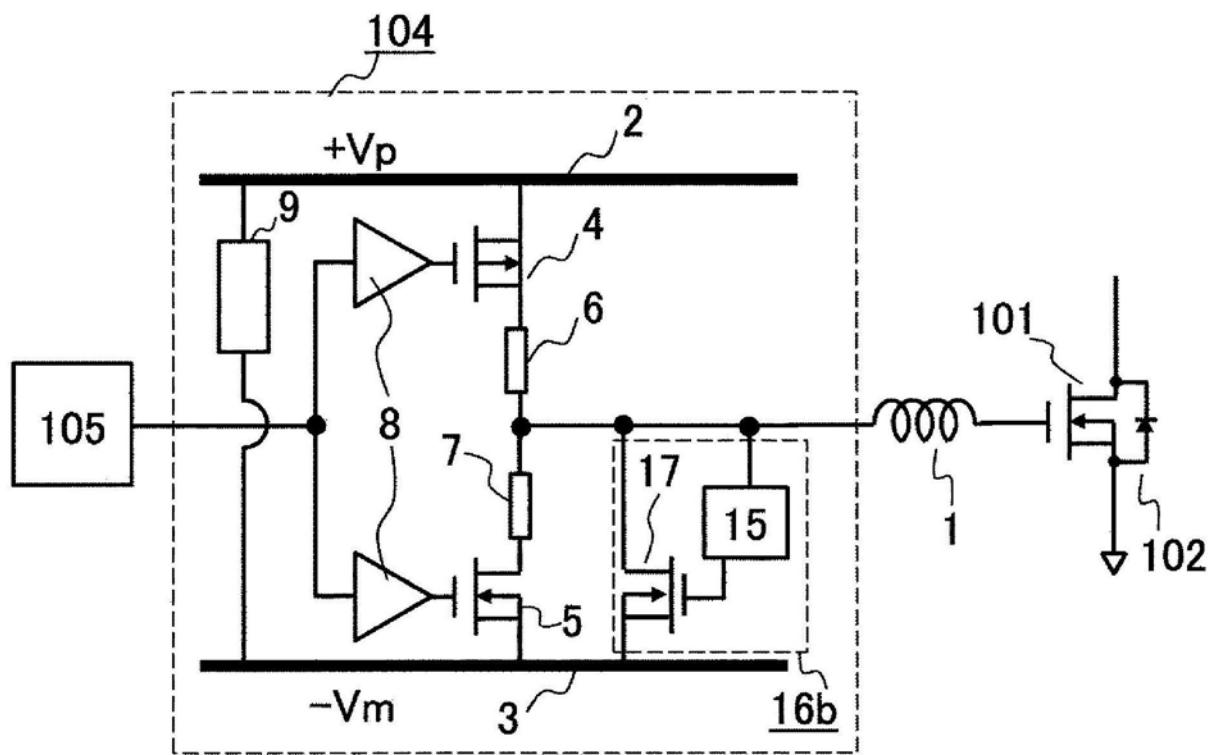

[0021] 图2是实施例1的栅极驱动器的结构图。

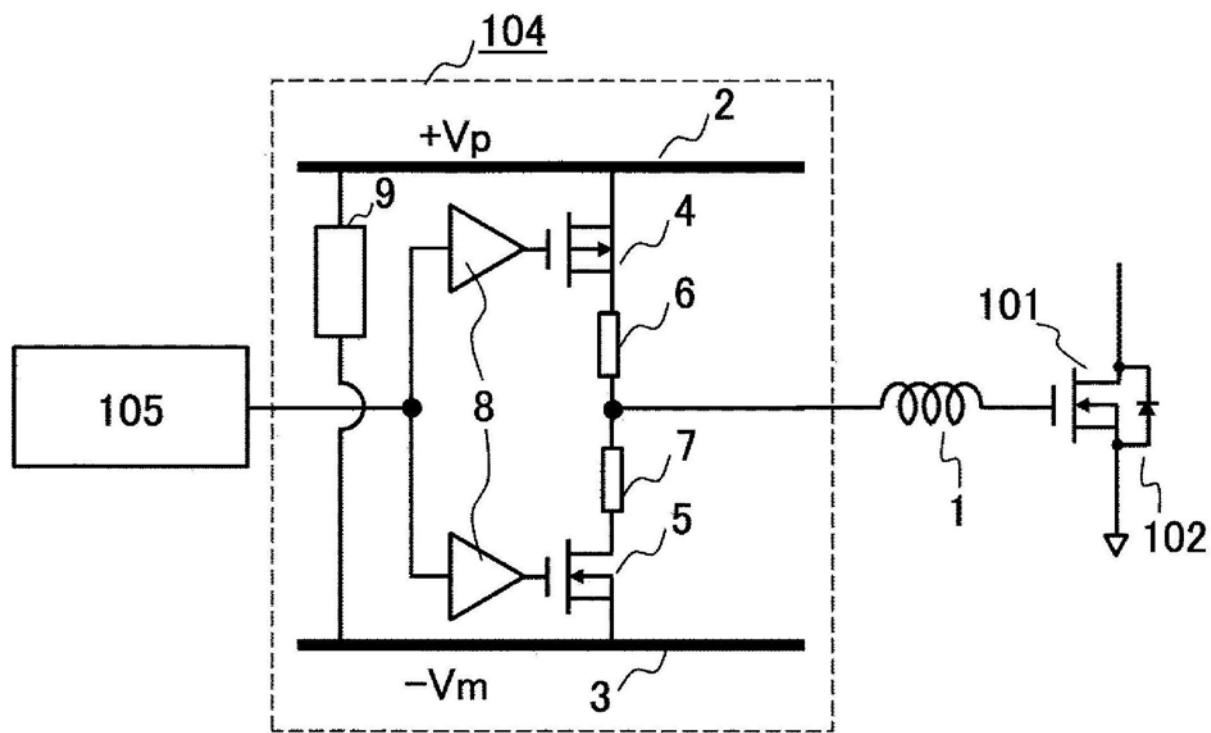

[0022] 图3是输出级的元件是双极晶体管的栅极驱动器的结构图。

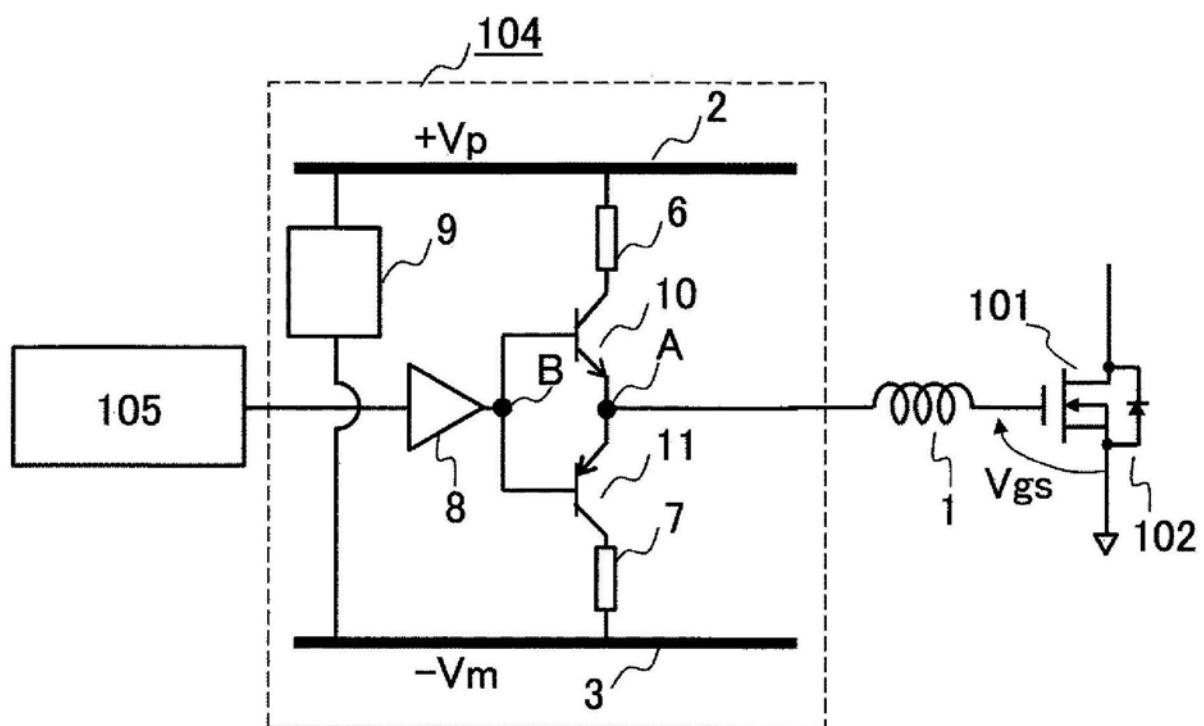

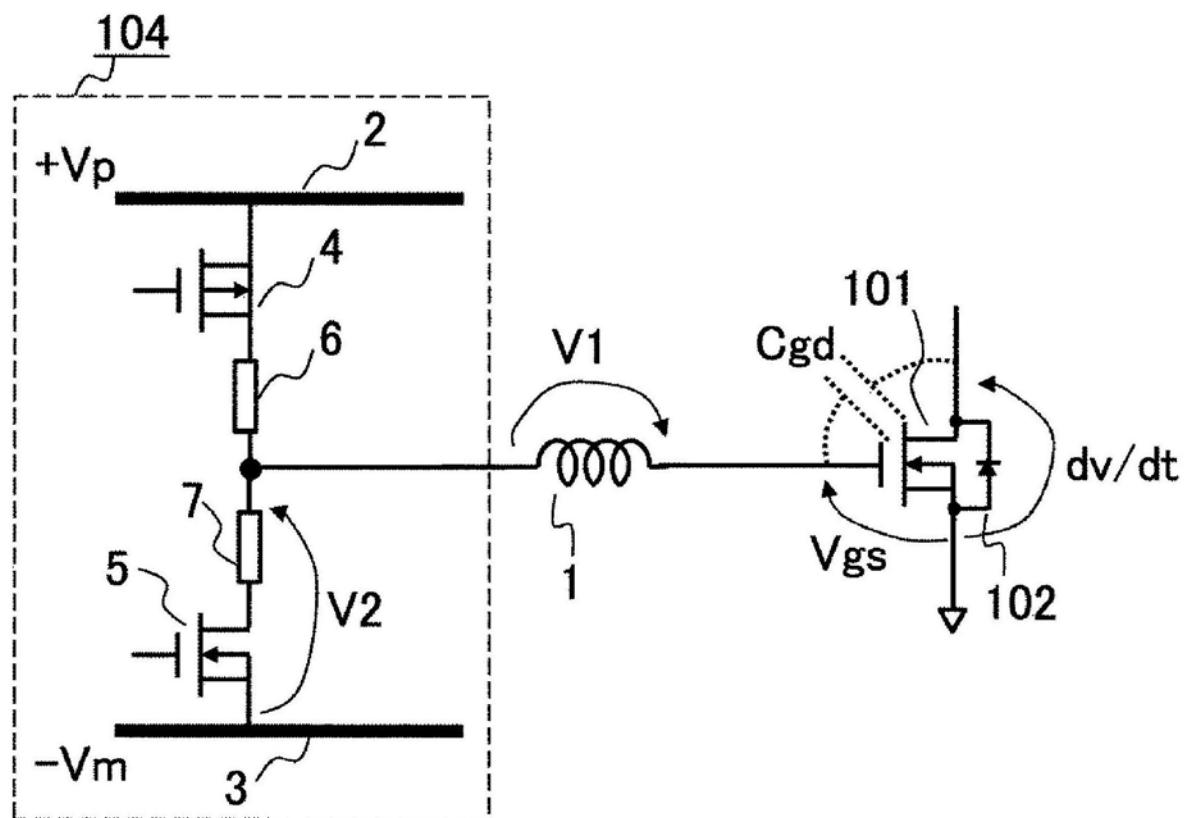

[0023] 图4是栅极-源极间电压的抬升现象的说明图。

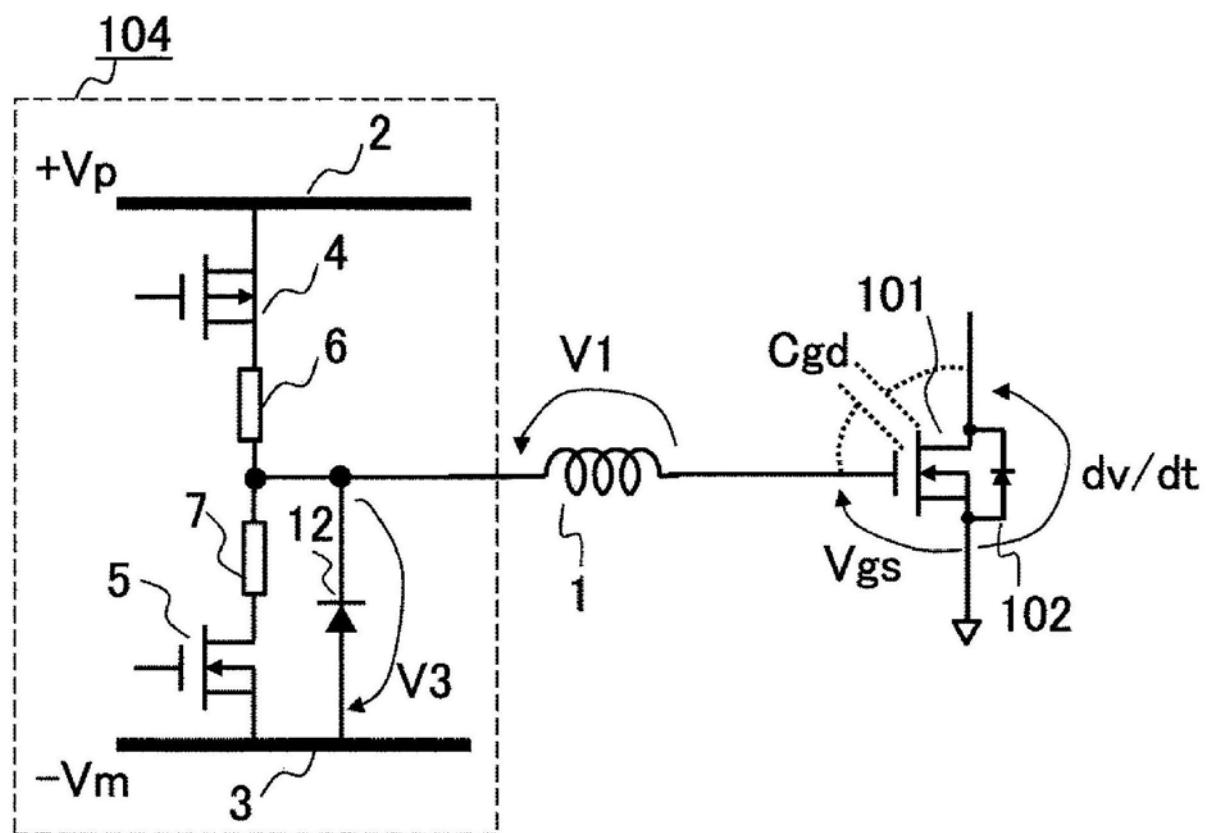

[0024] 图5是实施例2的栅极驱动器的结构图。

[0025] 图6是栅极-源极间电压的沉降现象的说明图。

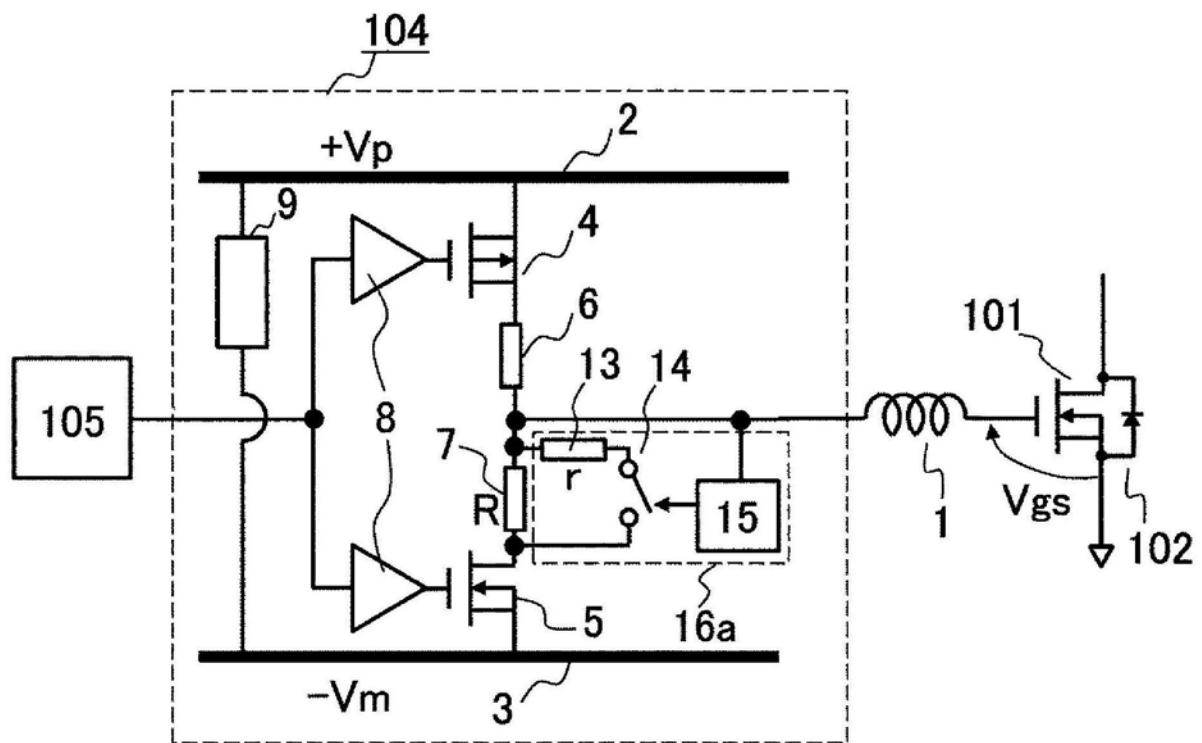

[0026] 图7是实施例3的栅极驱动器的结构图。

[0027] 图8是实施例4的栅极驱动器的结构图。

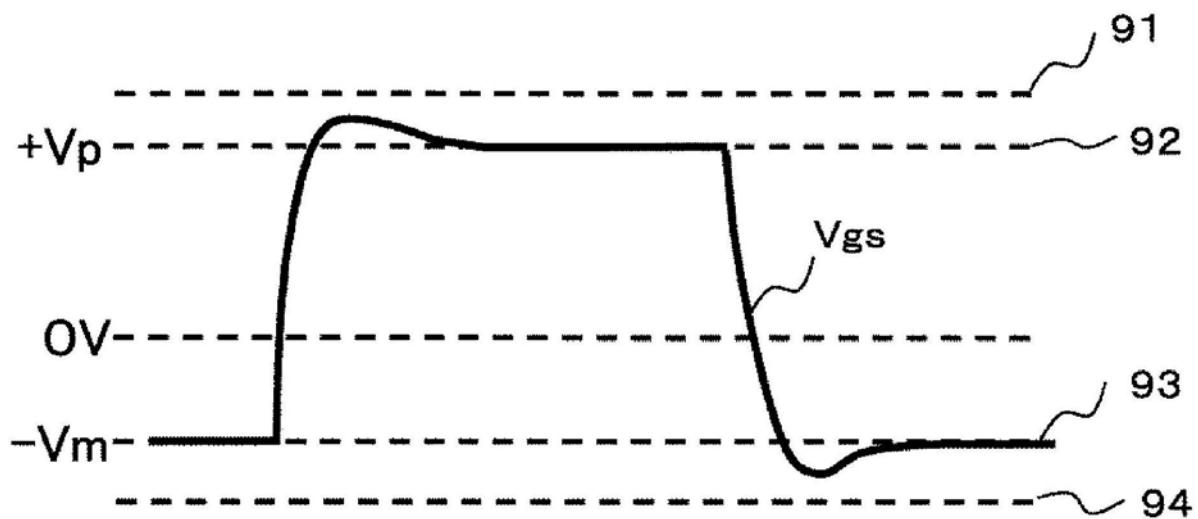

[0028] 图9是栅极驱动器的输出级的元件是双极晶体管的情况下栅极-源极间电压波

形的示意图。

### 具体实施方式

[0029] 在实施例中,公开一种用于驱动使用了SiC的电压驱动型的半导体元件的栅极驱动电路,栅极驱动电路是通过将P型MOSFET和N型MOSFET串联连接并将N型MOSFET与负侧电源直接连接而构成的,以使得位于P型MOSFET与N型MOSFET的中间的输出级在半导体元件关断时成为负偏压的方式使P型MOSFET和N型MOSFET互补地导通和关断。

[0030] 另外,在实施例中,公开一种使用了SiC的电压驱动型的半导体元件的栅极驱动方法,使P型MOSFET和与负极电源直接连接的N型MOSFET互补地导通和关断,以使位于串联连接的P型MOSFET与N型MOSFET的中间的输出级在半导体元件关断时成为负偏压。

[0031] 另外,在实施例中,公开具有在半导体元件关断中将输出级维持为负偏压的电压维持单元的栅极驱动电路。另外,公开用电压维持手段在半导体元件关断中将输出级维持为负偏压的栅极驱动方法。

[0032] 另外,在实施例中,公开电压维持单元包括在输出部和负侧电源之间与N型MOSFET并联连接的二极管。另外,公开二极管是肖特基势垒二极管、齐纳二极管或PN二极管。

[0033] 另外,在实施例中,公开电压维持单元包括:与位于输出级和N型MOSFET的中间的关断侧栅极电阻并联连接的并联化电阻、与并联化电阻串联连接的开关、在半导体元件处于关断状态的情况下使开关导通的判断部的栅极驱动电路。另外,公开在半导体元件处于关断状态的情况下使与位于输出级和N型MOSFET的中间的关断侧栅极电阻并联连接的并联化电阻上串联连接的开关导通的栅极驱动方法。

[0034] 另外,在实施例中,公开电压维持单元包括在输出级与负侧电源之间与N侧MOSFET并联连接的MOSFET、和在半导体元件是关断状态的情况下使MOSFET短路的判断部的栅极驱动电路。另外,公开在半导体元件是关断状态的情况下、使在输出级和负侧电源之间与N侧MOSFET并联连接的MOSFET短路的栅极驱动方法。

[0035] 另外,在实施例中,公开电压驱动型的半导体元件是常断型的半导体元件。

[0036] 另外,在实施例中,公开在负侧电源产生电压时使用绝缘型电源变压器或绝缘型DCDC转换器的栅极驱动电路。另外,公开用绝缘型电源变压器或绝缘型DCDC转换器生成负侧电源的电压的栅极驱动方法。

[0037] 另外,在实施例中,公开搭载了栅极驱动电路的三相交流逆变器。

[0038] 以下,对于上述和其他本发明的新特征和效果参考附图进行说明。

[0039] 另外,附图只是为了理解发明而使用的,并不缩小权利范围。

[0040] 实施例1

[0041] 图1是本实施例的铁路用逆变器系统的结构图。

[0042] 本实施例的铁路用逆变器系统中,由电压驱动型的半导体元件(IGBT、MOSFET等)101和滤波电容器103构成功率单元100。在UVW相各自中,MOSFET101串联连接,对于各MOSFET101,以导通方向是反方向的方式并联连接了续流二极管102。另外,对于各MOSFET101,配置了按照来自指令逻辑部105的指令驱动MOSFET的栅极驱动电路104。UVW相各自的上侧MOSFET(上臂)与下侧MOSFET(下臂)的连接点,作为功率单元100的输出与电动机106连接。

[0043] 来自架空线107的直流电力,经由集电装置108、多个断路器109和滤波电抗器110被平滑化,并被输入至除去噪声用的滤波电容器103的高压侧。另外,滤波电容器103的低压侧经由车轮111与作为电接地的轨道112连接。然后,铁路用逆变器系统通过使功率单元内的UVW相的MOSFET交替地开关而生成三相交流并输送至电动机106。与MOSFET101和滤波电容器103一同配置在功率单元100内的栅极驱动电路104,按照来自指令逻辑部105的指令驱动MOSFET101。指令逻辑部105具备运算装置、存储器和输入输出单元,按照规定的程序输出驱动MOSFET的指令。另外,本实施例的栅极驱动电路中,说明驱动MOSFET作为半导体元件的例子,但半导体元件不限于MOSFET,只要是电压驱动型的元件即可,例如也可以是IGBT。

[0044] 图2是本实施例的栅极驱动电路的结构图。如图2所示,栅极驱动电路104由正侧电源2、负侧电源3、P型MOSFET4、N型MOSFET5、导通侧栅极电阻6、关断侧栅极电阻7、驱动控制装置8、电源生成部9构成,成为使用了互补型的一对MOSFET的推挽结构。电源生成部9与正侧电源2和负侧电源3连接。P型MOSFET4的源极与正侧电源2连接,漏极与导通侧栅极电阻6连接。N型MOSFET5的源极与负侧电源3连接,漏极与关断侧栅极电阻7连接。此时,如图2所示,优选N型MOSFET5的源极与负侧电源3直接连接的结构。导通侧栅极电阻6与关断侧栅极电阻7的连接点成为栅极驱动电路104的输出部,经由栅极配线1与半导体元件10的栅极连接。P型MOSFET4和N型MOSFET5的栅极都与驱动控制装置8的输出部连接。驱动控制装置8的输入部连接指令逻辑部105。

[0045] 从电源生成部9分别对正侧电源2和负侧电源3供给正负的电源电压。从指令逻辑部105对驱动控制装置8输入栅极驱动指令时,驱动控制装置8以使位于栅极驱动电路的输出级的P型MOSFET4和N型MOSFET5互补地导通/关断的方式进行控制,经由栅极配线1使电荷对半导体元件101的栅极充电或放电。充电或放电的速度,分别能够用导通侧栅极电阻6、关断侧栅极电阻7控制。

[0046] 图3是将图2所示的栅极驱动电路的输出级的元件从MOSFET(P型MOSFET4和N型MOSFET5)置换为双极晶体管(NPN晶体管10和PNP晶体管11)的情况下栅极驱动电路的结构图,是对于本实施例的比较例。

[0047] NPN晶体管10的集电极经由导通侧栅极电阻6与正侧电源2连接。PNP晶体管11的集电极经由关断侧栅极电阻7与负侧电源3连接。NPN晶体管10和PNP晶体管11各自的发射极在图3的A点相互连接而成为栅极驱动电路104的输出部,经由栅极配线1与半导体元件101的栅极连接。NPN晶体管10和PNP晶体管11的基极都与驱动控制装置8的输出部连接。其他连接方式与图2相同。

[0048] 如图3所示,栅极驱动电路的输出级的元件由双极晶体管构成的情况下,驱动控制装置8以使NPN晶体管10和PNP晶体管11互补地导通/关断的方式进行控制时,不可避免地产生NPN晶体管10和PNP晶体管11同时关断的期间。这是因为必然产生驱动控制装置8的输出部(图3的B点)的电位成为NPN晶体管10和PNP晶体管11的基极-发射极间电压都没有被正向偏置的电位的工作点。此时,在从栅极驱动电路的输出部(图3的A点)到半导体元件101的通路中难以流动电流,过渡性地成为高阻抗状态。结果,栅极驱动电路104的输出电压超过栅极驱动电路的电压电源(图3的+Vp、-Vm)地变动,半导体元件101的栅极电压也超过电压电源地变动。即,半导体元件101导通时发生栅极-源极间电压(Vgs)过度地超过栅极驱动电路的电压电源的过冲(Vgs>+Vp),半导体元件101关断时发生下冲(Vgs<-Vm)(参考图9)。

[0049] 于是,如图2所示,用MOSFET构成栅极驱动电路的输出级的元件,由此能够抑制半导体元件101的栅极-源极间电压超过电压电源地变动的现象。这是因为双极晶体管是注入电流控制的,所以在NPN和PNP晶体管的导通/关断切换时,基极中充分蓄积电荷需要一定程度的时间,与此相对,MOSFET是施加电压控制的,导通/关断切换本质上较快,无需成为如上所述的过渡性的高阻抗状态,栅极的电位就可以稳定化。

[0050] 接着,对于栅极电压的抬升现象进行说明。图4是栅极-源极间电压的抬升现象的说明图。如图4所示,相对臂一侧(图4的半导体元件101是下臂的MOSFET的情况下是上臂一侧)的半导体元件导通时,半导体元件101处于关断状态,并联连接的续流二极管102进行反向恢复动作。此时,半导体元件101的漏极-源极间电压增加,所以 $dv/dt > 0$ ,所以从半导体元件101向栅极驱动电路104流动位移电流( $C_{gd} \cdot dv/dt$ )。此处, $dv/dt$ 表示漏极-源极间电压的时间变化率, $C_{gd}$ 表示半导体元件101的栅极-漏极间电容(反向传输电容)。

[0051] 该位移电流经由半导体元件101、栅极配线1、关断侧栅极电阻7、N型MOSFET5流入栅极驱动电路的负侧电源3。此时,如图4所示,与电流通路中的电路阻抗相应地,在半导体元件101的栅极端子与栅极驱动电路的负侧电源3之间产生电位差。从而,与该电位差相当,半导体元件101的栅极-源极间电压( $V_{gs}$ )被抬升至比栅极驱动电路的负侧电源3的电压( $-V_m$ )更高。即,如(式1)所示地产生 $V_1+V_2$ 的电位差。此处, $V_1$ 是栅极配线1的寄生电感引起的电位差, $V_2$ 是关断侧栅极电阻7和N型MOSFET5的寄生电阻引起的电位差。

$$V_{gs} = -V_m + (V_1 + V_2) \quad (\text{式1})$$

[0053] 因为上述栅极电压的抬升,存在半导体元件101的 $V_{gs}$ 超过其阈值电压( $V_{th}$ )而成为误导通状态时引起臂短路的风险。

[0054] 铁路用途中一般而言使用常断型的元件作为半导体元件101,所以即使关断时的 $V_{gs}$ 是0V在工作原理上也没有问题,但本实施例中,通过在栅极驱动电路中设置负侧电源3,而使关断时的 $V_{gs}$ 为负(例如 $V_{gs} = -10V$ )。由此,即使关断时在栅极电压中发生抬升,达到 $V_{th}$ 的电位差裕度也扩大,所以能够防止误导通。假设半导体元件101是常导通型的元件,以即使栅极电压中发生抬升、关断时的 $V_{gs}$ 也不会达到 $V_{th}$ 的方式设计负偏压电压,由此能够防止误导通。

[0055] 作为生成负电源电压的方法,例如使用绝缘型电源变压器作为图2的电源生成部9。即,方法是设置2个系统的二次侧绕组线圈,将一方作为正侧电源电压(+ $V_p$ )生成用、将另一方作为负侧电源电压( $-V_m$ )生成用地设计各自的匝数比。或者,也可以代替绝缘型电源变压器地使用绝缘型DCDC转换器生成正负两个电源。

#### [0056] 实施例2

[0057] 本实施例中,相对于实施例1的栅极驱动电路的结构,具有在半导体元件的栅极端子的电位沉降时将栅极电位连接至栅极驱动电路的负侧电源的单元,这一点不同。以下,以与实施例1的不同点为中心进行说明。

[0058] 图5表示本实施例的栅极驱动电路的结构图。对于栅极驱动电路104的输出部、即导通侧栅极电阻6与关断侧栅极电阻7的连接点连接了二极管12的阴极。二极管12的阳极与栅极驱动电路的负侧电源3连接。其他连接方式与实施例1相同。

[0059] 通过设置二极管12,在半导体元件101的栅极端子的电位沉降时栅极驱动电路104的输出部与栅极驱动电路的负侧电源3低阻抗地连接,所以能够抑制栅极电压的变动(沉

降)。

[0060] 图6是栅极电压的沉降现象的说明图。如图6所示,相对臂一侧的半导体元件关断时,半导体元件101处于关断状态,并联连接的续流二极管102进行正向恢复动作。此时,半导体元件101的漏极-源极间电压减少,所以 $dv/dt < 0$ ,所以从栅极驱动电路104向半导体元件101流动位移电流( $C_{gd} \cdot dv/dt$ )。

[0061] 该位移电流经由栅极驱动电路的负侧电源3、二极管12、栅极配线1流入半导体元件101。此时,如图6所示,与电流通路中的电路阻抗相应地在半导体元件101的栅极端子与栅极驱动电路的负侧电源3之间产生电位差,半导体元件101的V<sub>gs</sub>沉降至低于栅极驱动电路的负侧电源3的电压(-V<sub>m</sub>)。即,如(式2)所示地产生V<sub>1</sub>+V<sub>3</sub>的电位差。此处,V<sub>3</sub>是二极管12导通引起的电位差,等于二极管12的正向电压。

[0062]  $V_{gs} = -V_m - (V_1 + V_3)$  (式2)

[0063] 因为栅极电压的沉降现象,半导体元件101的V<sub>gs</sub>降至低于其额定电压的下限值(例如-20V)时存在栅极氧化膜的可靠性降低的风险,但本实施例中,在沉降时电流经过二极管12,由此能够抑制与栅极驱动电路的负侧电源3相比的电压降(V<sub>1</sub>+V<sub>3</sub>),能够确保栅极氧化膜的可靠性。从而,作为二极管12的候选,优选正向电压(V<sub>3</sub>)小的肖特基势垒二极管等,但也可以是齐纳二极管或PN二极管。

[0064] 另外,根据(式1)(式2),为了抑制栅极电压的变动量(抬升、沉降),减少栅极配线1中产生的电位差(V<sub>1</sub>)也是有效的,优选减少栅极配线1的寄生电感(L<sub>g</sub>)。作为减少L<sub>g</sub>的方法,有使栅极配线长度最小化的方法,和以栅极电流引起的磁场有效地相互抵消的方式应用层叠汇流条结构等的方法。

[0065] 实施例3

[0066] 图7表示本实施例的栅极驱动电路的结构图。作为使栅极电位与栅极驱动电路的负侧电源连接的单元,实施例2中使用了二极管12,但本实施例中使用低阻抗化电路16a,这一点不同。以下,以与实施例1至2的不同点为中心进行说明。

[0067] 低阻抗化电路16a由并联化电阻13、模拟开关14和栅极关断判断部15构成。并联化电阻13经由模拟开关14与关断侧栅极电阻7并联连接。栅极关断判断部15连接在栅极驱动电路104的输出部与模拟开关14之间。

[0068] 栅极关断判断部15监视半导体元件101的栅极-源极间电压(V<sub>gs</sub>),根据V<sub>gs</sub>的值判断半导体元件101处于关断状态。栅极关断判断部15判断半导体元件101处于关断状态时,使模拟开关14闭合,使关断侧栅极电阻7(电阻值R)与并联化电阻13(电阻值r)并联连接。并联连接时的电阻从R减少至R/(1+R/r)(<R)。从而,在半导体元件101关断中、栅极的电位沉降时栅极驱动电路104的输出部与栅极驱动电路的负侧电源3低阻抗地连接,所以能够抑制栅极电压的变动(沉降)。

[0069] 实施例2中,因为二极管12的整流作用而仅在栅极沉降时具有变动抑制效果,与此相对,本实施例中,因为低阻抗化电路16a的双向性,对于栅极的沉降和抬升双方具有变动抑制效果,在这一点上具有优势。通过抑制栅极电压的抬升量,在半导体元件101关断时,直到半导体元件101的栅极-源极间电压被抬升至阈值电压(V<sub>th</sub>)的电位差裕度增大,所以能够防止误导通。

[0070] 实施例4

[0071] 图8表示本实施例的栅极驱动电路的结构图。本实施例中,作为低阻抗化电路,不是使用模拟开关,而是使用MOSFET,这一点不同。以下,以与实施例1至3的不同点为中心进行说明。

[0072] 低阻抗化电路16b由电压钳位用MOSFET17和栅极关断判断部15构成。电压钳位用MOS17连接在栅极驱动电路104的输出部与栅极驱动电路的负侧电源3之间。栅极关断判断部15连接在栅极驱动电路104的输出部与电压钳位用MOS17的栅极端子之间。

[0073] 栅极关断判断部15判断半导体元件101处于关断状态时,使电压钳位用MOS17导通,使栅极驱动电路104的输出部与栅极驱动电路的负侧电源3短路。从而,在半导体元件101关断中栅极的电位沉降时,栅极驱动电路104的输出部与栅极驱动电路的负侧电源3极低阻抗地连接,所以能够有效地抑制栅极电压的变动(沉降)。

[0074] 本实施例中,存在于栅极驱动电路104的输出部与栅极驱动电路的负侧电源3之间的阻抗成分,仅是电压钳位用MOSFET17的导通电阻,较小(例如数十 $\text{m}\Omega$ ),所以具有与实施例3相比能够更有效地抑制栅极的变动(沉降、抬升)的优点。

[0075] 附图标记说明

[0076] 1:栅极配线

[0077] 2:栅极驱动电路的正侧电源

[0078] 3:栅极驱动电路的负侧电源

[0079] 4:P型MOSFET

[0080] 5:N型MOSFET

[0081] 6:导通侧栅极电阻

[0082] 7:关断侧栅极电阻

[0083] 8:驱动控制装置

[0084] 9:电源生成部

[0085] 10:NPN晶体管

[0086] 11:PNP晶体管

[0087] 12:二极管

[0088] 13:并联化电阻

[0089] 14:模拟开关

[0090] 15:栅极关断判断部

[0091] 16a:低阻抗化电路

[0092] 16b:低阻抗化电路

[0093] 17:电压钳位用MOSFET

[0094] 91:额定电压(上限值)

[0095] 92:正侧电压电源

[0096] 93:负侧电压电源

[0097] 94:额定电压(下限值)

[0098] 100:功率单元

[0099] 101:电压驱动型的半导体元件(IGBT、MOSFET等)

[0100] 102:续流二极管

- [0101] 103: 滤波电容器

- [0102] 104: 栅极驱动电路

- [0103] 105: 指令逻辑部

- [0104] 106: 电动机

- [0105] 107: 架空线

- [0106] 108: 集电装置

- [0107] 109: 断路器

- [0108] 110: 滤波电抗器

- [0109] 111: 车轮

- [0110] 112: 轨道。

图1

图2

图3

图4

图5

图6

图7

图8

图9