(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-164765

(P2007-164765A)

(43) 公開日 平成19年6月28日(2007.6.28)

(51) Int.CI.

G 06 F 13/38

(2006.01)

F 1

G O 6 F 13/38

3 5 0

テーマコード(参考)

5 B O 7 7

|              |                              | 審査請求 未請求 請求項の数 14 O L (全 15 頁)                 |

|--------------|------------------------------|------------------------------------------------|

| (21) 出願番号    | 特願2006-277720 (P2006-277720) | (71) 出願人 000005821<br>松下電器産業株式会社               |

| (22) 出願日     | 平成18年10月11日 (2006.10.11)     | 大阪府門真市大字門真1006番地                               |

| (31) 優先権主張番号 | 特願2005-330744 (P2005-330744) | (74) 代理人 110000040<br>特許業務法人池内・佐藤アンドパートナーズ     |

| (32) 優先日     | 平成17年11月15日 (2005.11.15)     | (72) 発明者 林下 洋之<br>大阪府門真市大字門真1006番地 松下電器産業株式会社内 |

| (33) 優先権主張国  | 日本国 (JP)                     | F ターム(参考) 5B077 MM01 MM02 NN02                 |

(54) 【発明の名称】 I I Cバス通信システム、スレーブ装置およびI I Cバス通信制御方法

## (57) 【要約】

【課題】スレーブ装置が間違ったビットでアクノリッジ信号を返してI I Cバス通信がフリーズした場合に、システムを復帰させることを可能とする。

【解決手段】S C L ライン1およびS D A ライン2からなる2本のバスラインに、並列に複数のマスター装置3、4および複数のスレーブ装置5、6が接続され、バスラインとI I C信号用電源9との間にプルアップ抵抗7、8が接続される。状態検出部15は、S C LおよびS D A ラインの状態に基づき、フリーズ状態を検出してフリーズ検出信号を出し、かつフリーズの解除状態を検出してフリーズ解除検出信号を出す。パルス発生部16aはフリーズ検出信号に応じてS C Lラインにクロック信号に相当するパルス信号を供給する。リセット信号発生部16bはフリーズ解除検出信号に応じて複数のマスター装置にリセット信号を送信する。複数のマスター装置はリセット信号の供給により通常の通信状態に復帰する。

【選択図】図1A

**【特許請求の範囲】**

**【請求項 1】**

SCL (シリアルクロック) ラインおよびSDA (シリアルデータ) ラインからなる 2 本のバスラインと、

前記バスラインに並列に接続された複数のマスター装置とを用いた IIC バス通信システムにおいて、

前記 SCL ラインおよび前記 SDA ラインの状態に基づき、IIC バス通信のフリーズ状態を検出してフリーズ検出信号を出力し、かつ前記フリーズ状態が解除された状態を検出してフリーズ解除検出信号を出力する状態検出部と、

前記状態検出部から出力される前記フリーズ検出信号に応じて前記 SCL ラインにクロック信号に相当するパルス信号を供給するパルス発生部と、10

前記状態検出部から出力されるフリーズ解除検出信号に応じて前記複数のマスター装置にリセット信号を送信するリセット信号発生部とを備え、

前記複数のマスター装置は前記リセット信号の供給により通常の通信状態に復帰することを特徴とする IIC バス通信システム。

**【請求項 2】**

前記状態検出部は、前記 SDA および前記 SCL の所定の状態が一定時間継続することを検出することにより、前記フリーズ状態を検出する請求項 1 に記載の IIC バス通信システム。

**【請求項 3】**

SCL (シリアルクロック) ラインおよびSDA (シリアルデータ) ラインからなる 2 本のバスラインと、

前記バスラインに並列に接続された複数のマスター装置とを用いた IIC バス通信システムにおいて、

前記複数のマスター装置を相互に接続する STA 制御ラインと、

前記 STA 制御ラインと電源との間に接続されたプルアップ抵抗とを備え、

通信を開始しようとする前記マスター装置は、事前に前記 STA 制御ラインに通信開始用の認識信号 STA を一定期間送信し、20

通信中の前記マスター装置は、前記 STA 制御ラインを通じて前記認識信号 STA が送信されていることを検出したときに、前記 SCL を停止することを特徴とする IIC バス通信システム。30

**【請求項 4】**

SCL ラインおよび SDA ラインからなる 2 本のバスラインと、

前記バスラインに並列に接続された複数のマスター装置と、

前記バスラインに並列に接続された複数のスレーブ装置と、

前記 SCL ラインおよび前記 SDA ラインにそれぞれ一端が接続されたプルアップ抵抗と、

前記プルアップ抵抗の他端に接続された電源とを用いた IIC バス通信システムにおいて、

前記複数のマスター装置および前記複数のスレーブ装置を相互に接続する RESET 制御ラインと、40

前記 RESET 制御ラインと前記電源との間に接続されたプルアップ抵抗とを備え、

前記複数のマスター装置は IIC 仕様に基づく IIC 信号の自己診断機能を内蔵して、ビットエラーが発生したとき、前記 RESET 制御ラインにリセット信号を送信し、

前記複数のスレーブ装置は、前記 RESET 制御ラインを通じて前記リセット信号が送信されたとき、前記ビットエラーに対応する状態をリセットすることを特徴とする IIC バス通信システム。

**【請求項 5】**

IIC バス通信システムの SCL ラインに接続するための SCL 端子と、

IIC バス通信システムの SDA ラインに接続するための SDA 端子と、50

前記 SCL 端子を介して入力される SCL 信号を基準電圧と比較した結果を出力する SCL コンパレータと、

前記 SDI 端子を介して入力される SDI 信号を基準電圧と比較した結果を出力する SDI コンパレータと、

前記 SCL コンパレータおよび前記 SDI コンパレータの出力が供給されるデコーダとを備え、

前記 SCL コンパレータおよび前記 SDI コンパレータの少なくとも一方はヒステリシス付きコンパレータであることを特徴とする IIC バス通信システムのスレーブ装置。

#### 【請求項 6】

前記 SCL コンパレータおよび前記 SDI コンパレータの少なくとも一方の出力側にノイズ除去用のコンデンサが接続された請求項 5 に記載のスレーブ装置。 10

#### 【請求項 7】

前記 SCL コンパレータおよび前記 SDI コンパレータの少なくとも一方に供給される前記基準電圧は、前記デコーダに基準電圧を供給する基準電圧源とは異なる基準電圧源から供給される請求項 5 に記載のスレーブ装置。

#### 【請求項 8】

IIC 信号用電源に接続するための電源入力端子と、

前記電源入力端子と接地間に接続された電圧分割用の抵抗とを備え、

前記 SCL コンパレータおよび前記 SDI コンパレータの少なくとも一方に供給される前記基準電圧として、前記電源の電圧が前記抵抗により分割された電圧を用いる請求項 5 に記載のスレーブ装置。 20

#### 【請求項 9】

前記 SCL コンパレータおよび前記 SDI コンパレータの少なくとも一方の出力側に出力インピーダンスを下げるためのバッファ回路が接続された請求項 5 に記載のスレーブ装置。

#### 【請求項 10】

SCL ラインおよび SDI ラインからなる 2 本のバスラインと、前記バスラインに並列に接続された複数のマスター装置とを用いた IIC バス通信システムを制御するための IIC バス通信制御方法において、

前記 SCL ラインおよび前記 SDI ラインの状態の監視を行い、 30

前記 SCL ラインおよび前記 SDI ラインの状態に基づき、IIC バス通信のフリーズ状態、および前記フリーズ状態が解除された状態を検出し、

前記フリーズ状態が検出されたときに前記 SCL ラインにクロック信号に相当するパルス信号を供給し、

前記フリーズ状態が解除された状態を検出したとき、前記複数のマスター装置にリセット信号を送信して通常の通信状態に復帰させることを特徴とする IIC バス通信制御方法。

#### 【請求項 11】

前記フリーズ状態の検出を、前記 SDI および前記 SCL の所定の状態が一定時間継続することを検出することにより行う請求項 10 に記載の IIC バス通信制御方法。 40

#### 【請求項 12】

SCL ラインおよび SDI ラインからなる 2 本のバスラインと、前記バスラインに並列に接続された複数のマスター装置とを用いた IIC バス通信システムを制御するための IIC バス通信制御方法において、

通信を開始しようとする前記マスター装置は、事前に他の全ての前記マスター装置に通信開始用の認識信号 STA を一定期間送信し、

通信中の前記マスター装置は、前記認識信号 STA が送信されていることを検出したとき、前記 SCL を停止するように制御することを特徴とする IIC バス通信制御方法。

#### 【請求項 13】

SCL ラインおよび SDI ラインからなる 2 本のバスラインと、前記バスラインに並列

50

に接続された複数のマスター装置と、前記バスラインに並列に接続された複数のスレーブ装置を用いた I I C バス通信システムを制御するための I I C バス通信制御方法において、

前記複数のマスター装置は I I C 信号の自己診断機能を内蔵して、ビットエラーが発生したとき、他の全ての前記マスター装置および全ての前記スレーブ装置にリセット信号を送信し、

前記複数のスレーブ装置は、前記リセット信号が送信されたとき、前記ビットエラーに対応する状態をリセットするように制御することを特徴とする I I C バス通信制御方法。

【請求項 1 4】

請求項 1 ~ 4 のいずれか 1 項に記載の I I C バス通信システムにおいて、電気的に動作し若しくは制御されるデバイスを備え、

前記デバイスがスレーブ装置として構成された I I C バス通信システム用装置。

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

本発明は、 I I C 通信システムにおける、フリーズ対策、およびそのためのノイズ耐性改善に関する。

【背景技術】

【0 0 0 2】

家庭用機器（テレビ、ラジオ、D V D レコーダなど）、通信機器（携帯電話、パーソナルコンピュータなど）あるいは産業機器の内部を構成するデバイス間相互のコントロールを効率よく行うために用いられる、 2 本のワイヤーからなる双方向バスを用いた通信方式の 1 つとして、 I I C （ Inter-Integrated Circuit ）バス通信という方式が知られている。

【0 0 0 3】

I I C バス通信を用いることで、システムの制御を、シリアルデータ（ S D A ）・ラインとシリアルクロック（ S C L ）・ラインの 2 本のバスラインのみで構成できる。また、アドレス指定およびデータ転送手段が I I C 仕様で定義されているため、ソフトウェアによるシステムの定義が可能であること、およびシステム内での I C の追加または除去が簡単であることなどの利点がある。バスに接続されている各デバイスはそれぞれ固有のアドレスをもち、機器の機能に応じてトランスマッタまたはレシーバとして動作でき、各デバイス間でデータ転送できるようになっている。

【0 0 0 4】

各デバイス間には、マスター装置とスレーブ装置という関係が常に成立し、マスター装置はマスター・トランスマッタまたはマスター・レシーバとして機能する。マスター装置とは、バス上でデータ転送を開始するデバイスであり、転送を可能にするクロック信号を発生する。そのときマスター装置によってアドレス指定されるデバイスは、スレーブ装置となる。 S D A ラインに出力される各バイトの長さは 8 ビットであり、 1 回の転送で送信できるバイト数には制限がなく、何バイトでも送ることができる。各バイトの後にはアクノリッジ・ビットが必要になる。アクノリッジ用のクロック・パルスはマスター装置によって生成される。アクノリッジ・クロック・パルスが生成されると、トランスマッタは S D A ラインを開放する。レシーバは、アクノリッジ・クロック・パルスが “ H ” 状態のときに、 S D A ラインが “ L ” 状態で安定するように、アクノリッジ・クロック・パルスの出力に合わせて S D A ラインを “ L ” にしなければならない。

【0 0 0 5】

I I C バスは複数のマスター装置が同時にバスをコントロールすることができるマルチ・マスター・バスで、セットの高機能化、システムの複雑化に伴い、今後、主流となることが予測される。 I I C バスに複数のマスター装置を接続できるということは、同時に複数のマスター装置がデータ転送を開始しようとする可能性があることになる。そこでこのような現象が発生するのを防ぐために、 I I C バスと全ての I I C バス・インターフェー

10

20

30

40

50

ス間はワイヤードAND接続されている。複数のマスター装置がバスに情報を送信しようとした場合、他のマスター装置が‘0’を生成したときに最初に‘1’を生成したマスター装置は通信を行うことができなくなる。以下、上記IICバス通信時に発生するビットエラーについて説明する。

#### 【0006】

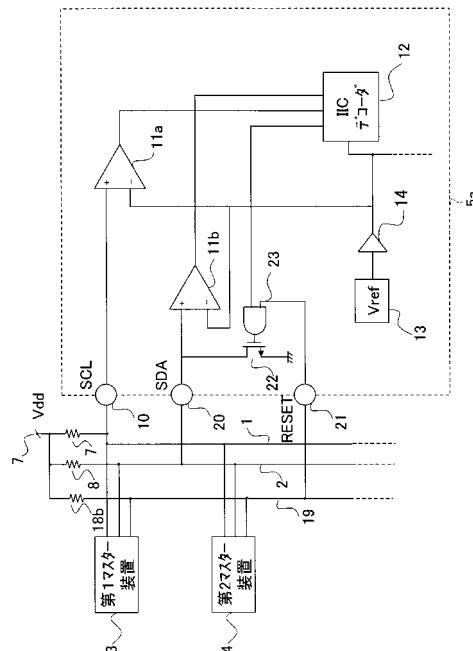

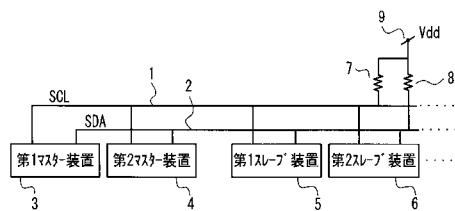

図6Aは、2つのマスター装置を含む従来のIICバスシステムの構成例を示す。このシステムにおいては、SCLライン1とSDAライン2からなるバスラインに、第1マスター装置3、第2マスター装置4、第1スレーブ装置5、および第2スレーブ装置6が、それぞれ並列に接続されている。また、SCLライン1にはSCLラインプルアップ抵抗7の一端が、SDAライン2にはSDAラインプルアップ抵抗8の一端が接続され、両プルアップ抵抗7、8の他端は、IIC信号用電源9に接続されている。10

#### 【0007】

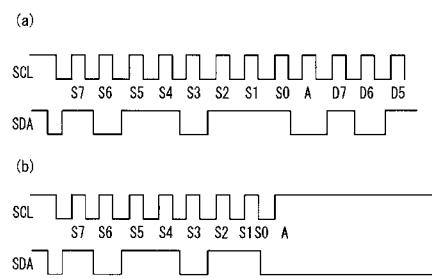

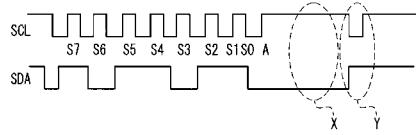

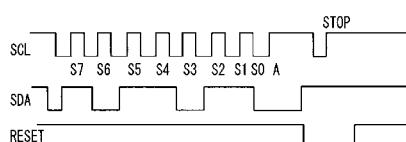

図6B(a)は、このIICバスシステムにおける、正常通信時のSCLおよびSDAの波形を示す。SCLにおけるクロック・パルスS7～S0は、1バイトのデータの各ビットに対応し、Aはアクノリッジ・クロック・パルスである。アクノリッジ・クロック・パルスが“H”状態のときに、SDAラインが“L”状態になっている。

#### 【0008】

図6B(b)は、アクノリッジ信号が1ビットずれて通信がフリーズした状態の波形を示す。例えば、第1マスター装置3が第1スレーブ装置5のリードデータを連続で取得する通信を行う際に、第1スレーブ装置5がスレーブアドレス受信中に外来ノイズなどの影響でビットエラーを起こした場合を考える。それにより、例えば、アクノリッジ・ビットの1ビット手前でアクノリッジ・パルスを返した場合、第1マスター装置3はスレーブアドレスの8ビット目を“H”で送信しているのに、スレーブ装置側でSDAラインを“L”にしてしまっていることになる。第1マスター装置3はこの現象を、第2マスター装置4がデータ転送を開始しようとしたものと認識して、SCLライン1に対するクロックの供給を停止してしまう。この結果、SCLライン1にはクロックが入らないため、SDAライン2は第1スレーブ装置5によって“L”に引き込まれた状態で、IICバス通信がフリーズする。20

#### 【0009】

IICバス通信システムにおける通信異常に対処する技術の例としては、特許文献1に記載されたものがある。特許文献1に記載の技術は、停電等の以上事態が発生して通信が中止された後、通信を再開したとき、スレーブ装置の誤動作や暴走を防ぐ方法に関する。しかし、上述のような、外来ノイズなどの影響によりIICバス通信がフリーズする問題に対処できる方法ではない。30

#### 【0010】

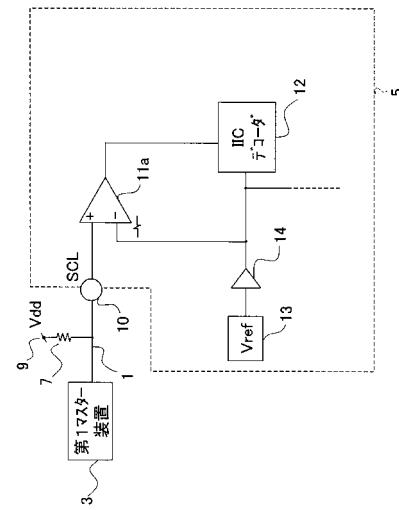

図7は、第1スレーブ装置5の内部ブロック図を示す。ただし、SCL入力端子10を通じて入力されるSCL信号の処理に関する部分のみを記載し、SDA信号の処理に関する部分については図示を省略する。

#### 【0011】

SCL信号は、第1スレーブ装置5内部のコンパレータ11aを介して、IICデコード回路12でデコードされる。コンパレータ11aの基準電圧としては、基準電圧回路13の出力電圧がバッファ回路14を介して供給される。バッファ回路14を介した基準電圧回路13の出力電圧は、IICデコード回路12にも供給される。40

#### 【0012】

この第1スレーブ装置5の回路においてアクノリッジ信号がずれる原因としては、以下のことが考えられる。

- (1) SCLライン1に外部からノイズが重畠する

- (2) コンパレータ11aの基準電圧側にノイズが重畠する。

- (3) コンパレータ11aの出力にノイズが重畠する。

**【発明の開示】****【発明が解決しようとする課題】****【0013】**

上述のように、外来ノイズなどの影響により、第1スレーブ装置5が間違ったビットでアクノリッジ信号を返した場合、IICバス通信がフリーズするといった不具合があった。

**【0014】**

本発明は、スレーブ装置が間違ったビットでアクノリッジ信号を返して、IICバス通信がフリーズした場合に、システムを復帰させることが可能なIICバス通信システムを提供することを目的とする。

**【0015】**

また、本発明は、スレーブ装置が間違ったビットでアクノリッジ信号を返しても、IICバス通信がフリーズすることを防止することが可能なIICバス通信システムを提供することを目的とする。

**【0016】**

また、本発明は、スレーブ装置の外部あるいは内部で信号にノイズが重畠されても、IICバス通信がフリーズしないように、スレーブ装置の内部回路のノイズ耐性を改善することを目的とする。

**【課題を解決するための手段】****【0017】**

本発明の第1の構成のIICバス通信システムは、SCL(シリアルクロック)ラインおよびSDA(シリアルデータ)ラインからなる2本のバスラインと、前記バスラインに並列に接続された複数のマスター装置とを用い、前記SCLラインおよび前記SDAラインの状態に基づき、IICバス通信のフリーズ状態を検出してフリーズ検出信号を出力し、かつ前記フリーズ状態が解除された状態を検出してフリーズ解除検出信号を出力する状態検出部と、前記状態検出部から出力される前記フリーズ検出信号に応じて前記SCLラインにクロック信号に相当するパルス信号を供給するパルス発生部と、前記状態検出部から出力されるフリーズ解除検出信号に応じて前記複数のマスター装置にリセット信号を送信するリセット信号発生部とを備え、前記複数のマスター装置は前記リセット信号の供給により通常の通信状態に復帰する。

**【0018】**

本発明の第2の構成のIICバス通信システムは、SCL(シリアルクロック)ラインおよびSDA(シリアルデータ)ラインからなる2本のバスラインと、前記バスラインに並列に接続された複数のマスター装置とを用い、前記複数のマスター装置を相互に接続するSTA制御ラインと、前記STA制御ラインと電源との間に接続されたプルアップ抵抗とを備え、通信を開始しようとする前記マスター装置は、事前に前記STA制御ラインに通信開始用の認識信号STAを一定期間送信し、通信中の前記マスター装置は、前記STA制御ラインを通じて前記認識信号STAが送信されていることを検出したときに、前記SCLを停止する。

**【0019】**

本発明の第3の構成のIICバス通信システムは、SCLラインおよびSDAラインからなる2本のバスラインと、前記バスラインに並列に接続された複数のマスター装置と、前記バスラインに並列に接続された複数のスレーブ装置と、前記SCLラインおよび前記SDAラインにそれぞれ一端が接続されたプルアップ抵抗と、前記プルアップ抵抗の他端に接続された電源とを用い、前記複数のマスター装置および前記複数のスレーブ装置を相互に接続するRESET制御ラインと、前記RESET制御ラインと前記電源との間に接続されたプルアップ抵抗とを備え、前記複数のマスター装置はIIC仕様に基づくIIC信号の自己診断機能を内蔵して、ビットエラーが発生したとき、前記RESET制御ラインにリセット信号を送信し、前記複数のスレーブ装置は、前記RESET制御ラインを通じて前記リセット信号が送信されたとき、前記ビットエラーに対応する状態をリセットす

る。

【0020】

本発明のIICバス通信システムのスレーブ装置は、IICバス通信システムのSCLラインに接続するためのSCL端子と、IICバス通信システムのSDAラインに接続するためのSDA端子と、前記SCL端子を介して入力されるSCL信号を基準電圧と比較した結果を出力するSCLコンパレータと、前記SDA端子を介して入力されるSDA信号を基準電圧と比較した結果を出力するSDAコンパレータと、前記SCLコンパレータおよび前記SDAコンパレータの出力が供給されるデコーダとを備え、前記SCLコンパレータおよび前記SDAコンパレータの少なくとも一方はヒステリシス付きコンパレータである。10

【0021】

本発明の第1の構成のIICバス通信制御方法は、SCLラインおよびSDAラインからなる2本のバスラインと、前記バスラインに並列に接続された複数のマスター装置とを用いたIICバス通信システムを制御するため、前記SCLラインおよび前記SDAラインの状態の監視を行い、前記SCLラインおよび前記SDAラインの状態に基づき、IICバス通信のフリーズ状態、および前記フリーズ状態が解除された状態を検出し、前記フリーズ状態が検出されたときに前記SCLラインにクロック信号に相当するパルス信号を供給し、前記フリーズ状態が解除された状態を検出したとき、前記複数のマスター装置にリセット信号を送信して通常の通信状態に復帰させる。20

【0022】

本発明の第2の構成のIICバス通信制御方法は、SCLラインおよびSDAラインからなる2本のバスラインと、前記バスラインに並列に接続された複数のマスター装置とを用いたIICバス通信システムを制御するため、通信を開始しようとする前記マスター装置は、事前に他の全ての前記マスター装置に通信開始用の認識信号STAを一定期間送信し、通信中の前記マスター装置は、前記認識信号STAが送信されていることを検出したとき、前記SCLを停止するように制御する。30

【0023】

本発明の第3の構成のIICバス通信制御方法は、SCLラインおよびSDAラインからなる2本のバスラインと、前記バスラインに並列に接続された複数のマスター装置と、前記バスラインに並列に接続された複数のスレーブ装置を用いたIICバス通信システムを制御するため、前記複数のマスター装置はIIC信号の自己診断機能を内蔵して、ビットエラーが発生したとき、他の全ての前記マスター装置および全ての前記スレーブ装置にリセット信号を送信し、前記複数のスレーブ装置は、前記リセット信号が送信されたとき、前記ビットエラーに対応する状態をリセットするように制御する。30

【発明の効果】

【0024】

第1の構成のIICバス通信システムおよびIICバス通信制御方法によれば、IICバス通信がフリーズしたことを検出して、SCLラインにクロックパルスを入力することにより、フリーズ状態を解除して正常な通信状態に復帰させることができる。

【0025】

第2の構成のIICバス通信システムおよびIICバス通信制御方法によれば、他のマスター装置が通信を開始するために認識信号STAを送出しない限り、マスター装置は通信をしようとクロックを入力し続けるため、IICバス通信のフリーズを防止できる。40

【0026】

第3の構成のIICバス通信システムおよびIICバス通信制御方法によれば、マスター装置が内蔵しているIICの自己診断機能でビットエラーを検出した場合に、リセット信号を送出して各装置にリセットをかけることにより、IICバス通信のフリーズを防止することができる。

【0027】

本発明のIICバス通信システムのスレーブ装置によれば、ヒステリシス付コンパレー50

タ 11 c を用いることにより、外部あるいは内部で信号に重畳されるノイズの影響によるビットエラーの発生を低減することができ、スレーブ装置のノイズ耐性を改善して、I I C バス通信のフリーズ発生を抑制することができる。

**【発明を実施するための最良の形態】**

**【0028】**

本発明の第1の構成のI I Cバス通信システムにおいて、前記状態検出部は、前記S D Aおよび前記S C Lの所定の状態が一定時間継続することを検出することにより、前記フリーズ状態を検出する構成とすることができる。

**【0029】**

本発明のI I Cバス通信システムのスレーブ装置において、前記S C Lコンパレータおよび前記S D Aコンパレータの少なくとも一方の出力側にノイズ除去用のコンデンサが接続された構成とすることが好ましい。

**【0030】**

また、前記S C Lコンパレータおよび前記S D Aコンパレータの少なくとも一方に供給される前記基準電圧は、前記デコーダに基準電圧を供給する基準電圧源とは異なる基準電圧源から供給される構成とすることが好ましい。

**【0031】**

また、I I C信号用電源に接続するための電源入力端子と、前記電源入力端子と接地間に接続された電圧分割用の抵抗とを備え、前記S C Lコンパレータおよび前記S D Aコンパレータの少なくとも一方に供給される前記基準電圧として、前記電源の電圧が前記抵抗により分割された電圧を用いる構成とすることができる。

**【0032】**

また、前記S C Lコンパレータおよび前記S D Aコンパレータの少なくとも一方の出力側に出力インピーダンスを下げるためのバッファ回路が接続された構成とすることが好ましい。

**【0033】**

本発明の第1の構成のI I Cバス通信制御方法において、前記フリーズ状態の検出を、前記S D Aおよび前記S C Lの所定の状態が一定時間継続することを検出することにより行うことができる。

**【0034】**

以下、本発明の実施形態について、図面を参照して説明する。

**【0035】**

(第1の実施形態)

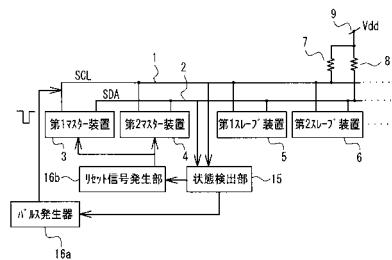

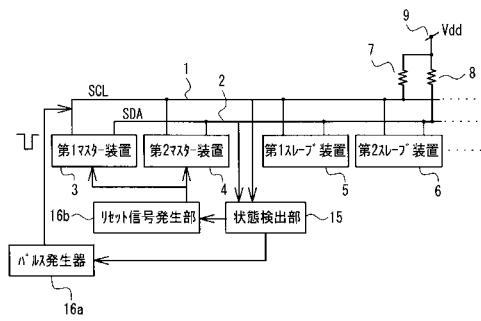

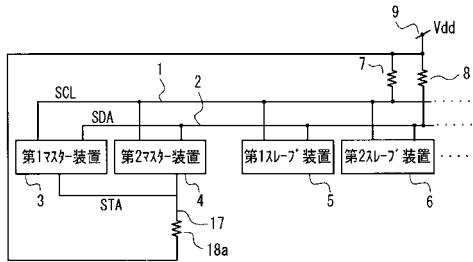

図1Aは、本発明の第1の実施形態に係るI I Cバス通信システムの構成を示すプロック図である。図1Aにおいて、図6Aに示した従来のI I Cバス通信システムの要素と同一の要素には、同一の参照符号を付して説明する。

**【0036】**

このI I Cバス通信システムは、S C Lライン1とS D Aライン2からなるバスラインに、第1マスター装置3、第2マスター装置4、第1スレーブ装置5、および第2スレーブ装置6を、それぞれ並列に接続して構成されている。また、S C Lライン1にはS C Lラインプルアップ抵抗7の一端が、S D Aライン2にはS D Aラインプルアップ抵抗8の一端が接続され、両プルアップ抵抗7、8の他端は、I I C信号用電源9に接続されている。

**【0037】**

さらに、フリーズ対策の機能を与えるために、状態検出部15、パルス発生部16a、およびリセット信号発生部16bの組み合わせが構成される。状態検出部15は、S C Lライン1およびS D Aライン2に接続されて、S C L信号とS D A信号が入力され、両信号の状態に基づいて、S C Lライン1およびS D Aライン2のフリーズ状態の検出およびフリーズの解除状態の検出を行う。

**【0038】**

10

20

30

40

50

状態検出部 15 の出力信号であるフリーズ検出信号およびフリーズ解除検出信号は、パルス発生部 16 a およびリセット信号発生部 16 b に供給される。パルス発生部 16 a は、状態検出部 15 から出力されるフリーズ検出信号に応じて SCL ライン 1 にクロック信号に相当するパルス信号を供給する。リセット信号発生部 16 b は、状態検出部 15 から出力されるフリーズ解除検出信号に応じて第 1 マスター装置 3、および第 2 マスター装置 4 にリセット信号を送信する。第 1 マスター装置 3、および第 2 マスター装置 4 は、リセット信号の供給により通常の通信状態に復帰する。

#### 【 0 0 3 9 】

次に、図 1B を参照して、本実施形態における IIC バス通信システムのフリーズ対策動作について説明する。図 1B は、図 1A のシステムにおいて、第 1 スレーブ装置 5 がアクノリッジ信号を 1 ビット早めに返した場合の SCL、SDA の波形を示している。

10

#### 【 0 0 4 0 】

第 1 マスター装置 3 が第 1 スレーブ装置 5 (リードアドレス : B7\_Hex) のデータを連續受信している途中で、ノイズ等の影響で、第 1 スレーブ装置 5 が 7 ビット目で SDA を 2 回分カウントしてしまった場合、SCL の 7 ビット目の立下りで SDA を “L” に引き込んでしまう。一方、第 1 マスター装置 3 では、リードアドレスの 8 ビット目を送信しているため、第 2 マスター装置 4 が通信を開始しようとして SDA ラインを “L” に引き下げているものと認識して、SCL を停止する。その結果、バスラインはフリーズし、フリーズ状態 X (SCL : “H”、SDA : “L”) に固定される。状態検出部 15 は、そのフリーズ状態 X が一定の時間続いたことを検出するように構成されている。

20

#### 【 0 0 4 1 】

状態検出部 15 は、フリーズ状態 X (SCL : “H”、SDA : “L”) が一定の時間続いたことを検出すると、フリーズ検出信号を発生してパルス発生部 16 a に出力する。それにより、パルス発生部 16 a から SCL ライン 1 に 1 クロック分のパルス信号が入力される。その結果、第 1 スレーブ装置 5 は SDA ライン 2 を “H” に開放し、バスラインは解除状態 Y となる。

30

#### 【 0 0 4 2 】

状態検出部 15 はまた、フリーズ状態 X が解除された解除状態 Y (SCL : “H”、SDA : “H”) が一定の時間続いたことを検出するように構成されている。状態検出部 15 は、解除状態 Y が一定の時間続いたことを検出すると、フリーズ解除検出信号を出力する。それに応じてリセット信号発生部 16 b は、第 1 マスター装置 3 および第 2 マスター装置 4 にリセット信号を送信し、通常の通信状態に復帰させる。

30

#### 【 0 0 4 3 】

SDA ライン 2 が “L” に固定されたままで、フリーズ状態 X が続いている場合には、状態検出部 15 は再度フリーズ検出信号を発生し、パルス発生部 16 a はパルスを出力する。つまり、SDA ライン 2 が “H” に開放されるまで、パルス発生部 16 a から SCL ライン 1 にクロック信号が入力され続ける。フリーズ状態 X が解除されたら、第 1 マスター装置 3、および第 2 マスター装置 4 がリセットされ、正常な通信状態に復帰することができる。

40

#### 【 0 0 4 4 】

##### ( 第 2 の実施形態 )

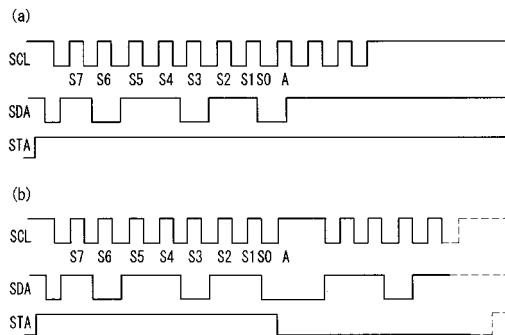

図 2A は、本発明の第 2 の実施形態に係る IIC バス通信システムの構成を示すブロッケーションである。この IIC バス通信システムは、従来の基本構成に加えて、フリーズ対策のための要素として、STA (スタート) 制御ライン 17 と、STA 制御ライン プルアップ抵抗 18 a が設けられている。

40

#### 【 0 0 4 5 】

第 1 マスター装置 3 と第 2 マスター装置 4 は、STA 制御ライン 17 で相互に接続されており、通信を開始しようとするマスター装置は事前に、所定の一定期間 “L” を STA 制御ライン 17 に出力するように設定されている。STA 制御ライン 17 は、SCL ライン 1、SDA ライン 2 と同様に、第 1 マスター装置 3 および第 2 マスター装置 4 内部では

50

オーブンドレイン接続されている。STA プルアップ抵抗 17a は、一端が STA 制御ライン 17 に接続され、他端が IIC 信号用電源 9 に接続されている。マスター通信中の第 1 マスター装置 3 および第 2 マスター装置 4 は、STA 制御ライン 17 が "L" になったことを検出して、SCL を停止するという制御システムになっている。

#### 【0046】

次に、図 2B を参照して、本実施形態における IIC バス通信システムのフリーズ対策動作について説明する。

#### 【0047】

図 2B (a) は、図 2A のシステムで第 1 スレーブ装置 5 がアクノリッジ信号を 1 ビット早めに返し、かつマスター装置が切り替わらない場合の SCL 信号、SDA 信号、STA 信号の波形を示す。第 1 マスター装置 3 が第 1 スレーブ装置 5 (リードアドレス: B7\_Hex) のデータを連続受信している途中で、ノイズ等の影響で、第 1 スレーブ装置 5 が 7 ビット目で SDA を 2 回分カウントしてしまった場合、SCL の 7 ビット目の立下りで SDA を "L" に引き込んでしまう。しかし、第 2 マスター装置 4 は通信を開始しようとしていないので、STA は "H" のままである。その結果、第 1 マスター装置 3 は、SCL を停止させることなく、通信を続けるので、バスラインはフリーズしない。

#### 【0048】

図 2B (b) は、図 2A のシステムで第 1 スレーブ装置 5 がアクノリッジ信号を 1 ビット早めに返し、かつ第 2 マスター装置 4 が第 1 マスター装置 3 の通信の途中で割り込んでマスター装置が切り替わる場合の SCL、SDA、STA の波形を示している。第 1 マスター装置 3 が第 1 スレーブ装置 5 (リードアドレス: B7\_Hex) のデータを連続受信している途中で、ノイズ等の影響で、第 1 スレーブ装置 5 が 7 ビット目で SDA を 2 回分カウントしてしまった場合、SCL の 7 ビット目の立下りで SDA を "L" に引き込んでしまう。そのタイミングで、第 2 マスター装置 4 が通信を開始するために STA 制御ラインを "L" にしている。この結果、第 1 マスター装置 3 は SCL を停止し、第 2 マスター装置 4 が STOP コンディションおよびスタートコンディションを入力した後、通信を開始するため、バスラインはフリーズしない。

#### 【0049】

##### (第 3 の実施形態)

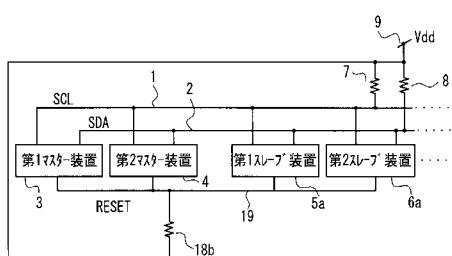

図 3A は、本発明の第 3 の実施形態に係る IIC バス通信システムの構成を示すブロック図である。この IIC バス通信システムは、従来の基本構成に加えて、フリーズ対策のための要素として、RESET (リセット) 制御ライン 19 と、RESET 制御ライン プルアップ抵抗 18b が設けられている。

#### 【0050】

全マスター装置すなわち第 1、第 2 マスター装置 3、4 と全スレーブ装置すなわち第 1、第 2 スレーブ装置 5a、6a は、RESET 制御ライン 19 で相互接続されている。全てのマスター装置 3、4 は IIC 信号の自己診断機能を内蔵しており、ビットエラーが発生すると、RESET 制御ライン 19 を "L" にするという制御システムになっている。

#### 【0051】

次に、図 3B を参照して、本実施形態における IIC バス通信システムのフリーズ対策動作について説明する。

#### 【0052】

図 3B は、図 3A のシステムで第 1 スレーブ装置 5a がアクノリッジ信号を 1 ビット早めに返した場合の SCL、SDA、RESET の波形を示す。

#### 【0053】

図 3C は、図 3A の IIC バス通信システムに用いられるスレーブ装置 5a である IC 回路の構成を示すブロック図である。

#### 【0054】

第 1 スレーブ装置 5a に設けられた SCL 入力端子 10、SDA 入力端子 20 および RESET 入力端子 21 はそれぞれ、SCL ライン 1、SDA ライン 2 および RESET 制

10

20

30

40

50

御ライン 19 に接続されている。SCL、SDA 信号は、第 1 スレーブ装置 5a 内部のコンパレータ 11a、11b を介して、IIC デコード回路 12 でデコードされる。コンパレータ 11a、11b の基準電圧としては、基準電圧回路 13 からの基準電圧がバッファ回路 14 を介して供給される。

#### 【0055】

SDA 入力端子 20 は、Nch-MOS トランジスタ 22 を介して接地されている。IIC デコード回路 12 のデコード出力は、AND 回路 23 の一方の入力端子に供給される。AND 回路 23 の他方の入力端子は、RESET 入力端子 21 と接続されている。

#### 【0056】

例えば、第 1 マスター装置 3 が第 1 スレーブ装置 5a（リードアドレス：B7\_Hex）のデータを連続受信している途中で、ノイズ等の影響で、第 1 スレーブ装置 5a が 7 ビット目で SDA を 2 回分カウントしてしまった場合、SCL の 7 ビット目の立下りで SDA を “L” に引き込んでしまう。

#### 【0057】

この場合、第 1 マスター装置 3 は B7\_Hex を出力しているにもかかわらず、第 1 スレーブ装置 5a のアクノレッジビットずれのために IIC 信号は B6\_Hex になっている。この IIC 信号のずれを、第 1 マスター装置 3 自身が内蔵している IIC 自己診断機能により検知して、RESET 制御ライン 19 に “L” を出力し、その間に第 1 マスター装置 3 自身が STOP コンディションを生成し、スレーブ装置の RESET 端子 21 に入力する。その結果、スレーブ装置内部の IIC デコーダ回路 12 がリセットされ、正常に通信が開始するため、バスラインはフリーズしない。

#### 【0058】

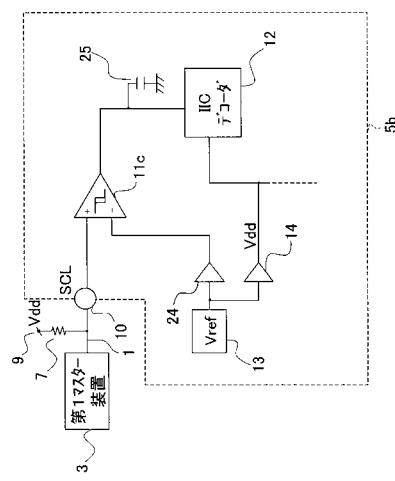

##### （第 4 の実施形態）

図 4 は、本発明の第 4 の実施形態に係る IIC バス通信システムに用いられるスレーブ装置 5b の構成を示すブロック図である。IIC バス通信システム全体の構成は、図 6A に示した従来例と同様でも、あるいは、上述の各実施形態に示したものと同様であってもよい。なお、このスレーブ装置 5b は、SCL 入力端子 10 を通じて入力される SCL 信号の処理に関する部分のみが図示され、他の信号の処理に関する部分については図示が省略されている。

#### 【0059】

SCL 信号は、ヒステリシス付コンパレータ 11c を介して、IIC デコード回路 12 に供給されてデコードされる。コンパレータ 11c の基準電圧としては、基準電圧回路 13 の出力電圧が、バッファ回路 24 を介して供給される。すなわち、コンパレータ 11c の基準電圧は、IIC デコード回路 12 に供給される電圧とは別経路で供給されるようになっている。さらに、コンパレータ 11c の出力側は、ノイズ除去用コンデンサ 25 を介して接地されている。

#### 【0060】

上記構成によれば、次のように、スレーブ装置 5b 内部のノイズ耐性を改善させる対策がなされる。

(1) ヒステリシス付コンパレータ 11c を用いることにより、SCL ライン 1 に外部から重畳するノイズの影響によるビットエラーの発生を低減することができる。

(2) バッファ回路 24 を用いて、IIC デコード回路 12 等のロジック回路とコンパレータ 11c の基準バイアスを分離することにより、コンパレータ 11c の基準電圧側に重畳するノイズの影響によるビットエラーの発生を低減することができる。

(3) コンパレータ 11c の出力側にノイズ除去用コンデンサ 25 を設けることにより、コンパレータ 11c の出力に重畳するノイズの影響によるビットエラーの発生を低減することができる。

#### 【0061】

なお、上記対策の全てを同時に実施する必要はなく、いずれか 1 つの対策を用いれば、相応の効果を得ることは可能である。

10

20

30

40

50

## 【0062】

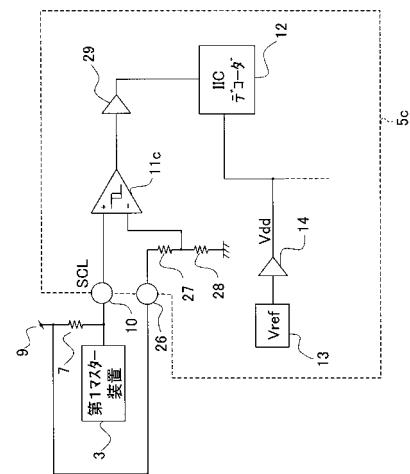

(第5の実施形態)

図5は、本発明の第5の実施形態に係るIICバス通信システムに用いられるスレーブ装置5cの構成を示すブロック図である。IICバス通信システム全体の構成は、図6Aに示した従来例と同様でも、あるいは、上述の各実施形態に示したものと同様であってよい。なお、このスレーブ装置5cは、SCL入力端子10を通じて入力されるSCL信号の処理に関する部分のみが図示され、他の信号の処理に関する部分については図示が省略されている。

## 【0063】

このスレーブ装置5cにはIIC信号用電源端子26が設けられ、IIC信号用電源9と接続されている。電源端子26は、基準電圧設定用抵抗27、28の直列回路を介して接地されている。SCL入力端子10を通じて入力されるSCL信号は、ヒステリシス付コンパレータ11cに入力される。コンパレータ11cの出力信号は、バッファ回路29を介してIICデコード回路12に供給され、デコードされる。

## 【0064】

IICデコード回路12の基準電圧としては、基準電圧回路13の出力電圧が、バッファ回路14を介して供給される。コンパレータ11cの基準電圧としては、IIC信号用電源9の電圧が基準電圧設定用抵抗27、28により抵抗分割された電圧が供給される。

## 【0065】

上記構成によれば、次のように、スレーブ装置5c内部のノイズ耐性を改善させる対策がなされる。

(4) コンパレータ11cの基準電圧にIIC信号用電源9から抵抗分割した電圧を用いることにより、コンパレータ11cの基準電圧側に重畠するノイズの影響によるビットエラーの発生を低減することができる。

(5) ヒステリシス付コンパレータ11cの出力ライン直後にバッファ回路29を追加して出力インピーダンスを下げることで、IICデコード回路12内部やその他の場所で発生するノイズが重畠することによる、ビットエラーの発生を低減することができる。

## 【0066】

なお、以上の実施形態においては、2個のマスター装置、2個のスレーブ装置がバスラインに接続されている例を示したが、マスター装置、スレーブ装置とも、バスラインに接続される個数は2個に限られない。

## 【産業上の利用可能性】

## 【0067】

本発明によれば、IICバス通信システムにおけるノイズの影響によるフリーズの対策を効果的に行うことができ、家庭用機器、通信機器あるいは産業機器の内部を構成するデバイス間相互のコントロールに有用である。

## 【図面の簡単な説明】

## 【0068】

【図1A】本発明の第1の実施形態に係るIICバス通信システムの構成を示すブロック図

【図1B】同IICバス通信システムにおけるIIC信号パターンを示す図

【図2A】本発明の第2の実施形態に係るIICバス通信システムの構成を示すブロック図

【図2B】同IICバス通信システムにおけるIIC信号波形およびSTA信号波形を示す図

【図3A】本発明の第3の実施形態に係るIICバス通信システムの構成を示すブロック図

【図3B】同IICバス通信システムにおけるIIC信号パターンおよびRESET制御信号を示す図

【図3C】同IICバス通信システムに用いられるスレーブIIC回路の構成を示すブロック図

10

20

30

40

50

## ク図

【図4】本発明の第4の実施形態のIICバス通信システムに用いられるスレーブIIC回路の構成を示すブロック図

【図5】本発明の第5の実施形態のIICバス通信システムに用いられるスレーブIIC回路の構成を示すブロック図

【図6A】従来のIICバス通信システムの構成を示すブロック図

【図6B】従来のIICバス通信システムのIIC信号波形を示す図

【図7】従来のスレーブIIC回路の構成を示すブロック図

【符号の説明】

【0069】

10

1 SCLライン

2 SDAライン

3 第1マスター装置

4 第2マスター装置

5 第1スレーブ装置

6 第2スレーブ装置

7 SCLラインプルアップ抵抗

8 SDAラインプルアップ抵抗

9 IIC信号用電源

10 SCL入力端子

20

11a、11b コンパレータ

11c ヒステリシス付きコンパレータ

12 IICデコード回路

13 基準電圧回路

14、24、29 バッファ回路

15 状態検出部

16a パルス発生部

16b リセット信号発生部

17 STA制御ライン

18a STA制御ラインプルアップ抵抗

30

18b RESET制御ラインプルアップ抵抗

19 RESET制御ライン

20 SDA入力端子

21 RESET入力端子

22 Nch-MOSトランジスタ

23 AND回路

25 ノイズ除去用コンデンサ

26 IIC信号用電源端子

27、28 基準電圧設定用抵抗

【図 1 A】

【図 1 B】

【図 2 A】

【図 2 B】

【図 3 A】

【図 3 C】

【図 3 B】

【図4】

【図5】

【図6A】

【図6B】