(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4901729号

(P4901729)

(45) 発行日 平成24年3月21日(2012.3.21)

(24) 登録日 平成24年1月13日(2012.1.13)

|                |             |

|----------------|-------------|

| (51) Int.Cl.   | F 1         |

| HO 1 L 27/115  | (2006.01)   |

| HO 1 L 21/8247 | (2006.01)   |

| HO 1 L 29/423  | (2006.01)   |

| HO 1 L 29/49   | (2006.01)   |

| HO 1 L 21/283  | (2006.01)   |

| HO 1 L         | 27/10 4 3 4 |

|                | 29/58 G     |

|                | 21/283 B    |

|                | 29/78 3 7 1 |

|                | 27/10 4 8 1 |

請求項の数 4 (全 17 頁) 最終頁に続く

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2007-518064 (P2007-518064)  |

| (86) (22) 出願日 | 平成17年5月11日 (2005.5.11)        |

| (65) 公表番号     | 特表2008-504681 (P2008-504681A) |

| (43) 公表日      | 平成20年2月14日 (2008.2.14)        |

| (86) 國際出願番号   | PCT/US2005/016495             |

| (87) 國際公開番号   | W02006/007080                 |

| (87) 國際公開日    | 平成18年1月19日 (2006.1.19)        |

| 審査請求日         | 平成20年5月9日 (2008.5.9)          |

| (31) 優先権主張番号  | 10/876,805                    |

| (32) 優先日      | 平成16年6月25日 (2004.6.25)        |

| (33) 優先権主張国   | 米国(US)                        |

|           |                                                                                                            |

|-----------|------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 504199127<br>フリースケール セミコンダクター イン<br>コーポレイテッド<br>アメリカ合衆国 テキサス州 78735<br>オースティン ウィリアム キャノン<br>ドライブ ウエスト 6501 |

| (74) 代理人  | 100116322<br>弁理士 桑垣 衛                                                                                      |

| (72) 発明者  | シェタイムル、ロバート エフ.<br>アメリカ合衆国 78737 テキサス州<br>オースティン エルドラド ドライブ<br>7928                                        |

審査官 須原 宏光

最終頁に続く

(54) 【発明の名称】ナノクラスタ電荷蓄積デバイスの形成方法

## (57) 【特許請求の範囲】

## 【請求項 1】

ナノクラスタ電荷蓄積デバイスの形成方法であつて、

1 つまたは複数の非電荷蓄積デバイスを配置するための、半導体装置の第1の領域を特定し、

1 つまたは複数の電荷蓄積デバイスを配置するための、前記半導体装置の第2の領域を特定し、

前記半導体装置の前記第1の領域中に前記1 つまたは複数の非電荷蓄積デバイスのゲート絶縁体として使用されるゲート酸化物を形成し、

その後、前記半導体装置の少なくとも前記第1及び第2の領域中にナノクラスタ電荷蓄積層を形成し、

前記半導体装置の前記第1の領域と前記半導体装置の前記第2の領域の両方の中に前記ゲート酸化物を形成した後でかつ前記ナノクラスタ電荷蓄積層を形成する前に、前記非電荷蓄積デバイスの上にゲート電極層と上に横たわるバリア層を形成し、

前記バリア層を使用して、前記半導体装置の前記第1の領域中の前記ゲート電極層を保護することにより、前記半導体装置の前記第1の領域から前記ナノクラスタ電荷蓄積層を除去する

ことを備える前記方法。

## 【請求項 2】

少なくとも5 ナノメートルのゲート酸化物厚みを有する高電圧トランジスタを形成するた

10

20

めの領域として前記半導体装置の前記第1の領域を特定することをさらに備える請求項1の方法。

【請求項3】

非電荷蓄積トランジスタを前記第1の領域中に形成し、

前記ナノクラスタ電荷蓄積層を前記半導体装置の少なくとも前記第1及び第2の領域中に形成した後に、前記第2の領域中に電荷蓄積トランジスタを形成することをさらに備える請求項1の方法。

【請求項4】

1つまたは複数の入出力トランジスタまたはロジックトランジスタあるいはこれらの組合せを形成するための領域として、前記半導体装置の第3の領域を特定することをさらに含み、前記第3の領域は、前記第1の領域中の前記1つまたは複数の非電荷蓄積デバイスの前記ゲート酸化物よりも厚みが薄いゲート酸化物を有する1つまたは複数の非電荷蓄積トランジスタを配置するためのものである、請求項1の方法。

10

【発明の詳細な説明】

【技術分野】

【0001】

本発明は半導体装置に関し、より詳細にはナノクラスタを有するこのようなデバイスに関する。

【背景技術】

【0002】

メモリ(例えば、不揮発性メモリ)など一部のデバイスは、トランジスタの電荷蓄積位置に電荷を蓄積するための(例えば、シリコン、アルミニウム、金、またはゲルマニウムの)ナノクラスタと呼ばれる離散的な電荷蓄積要素を利用している。一部の例においては、これらのナノクラスタは、2層の誘電体層、すなわち底部誘電体と制御誘電体との間に位置している。このようなトランジスタの例は、薄膜蓄積トランジスタを含む。メモリは概してこのようなトランジスタのアレイを含む。ナノクラスタタイプの例は、シリコンナノクラスタ、ゲルマニウムナノクラスタ、これらのアロイなど、ドープされた半導体ナノクラスタおよび非ドープの半導体ナノクラスタを含む。ナノクラスタタイプの他の例は、金属ナノクラスタ(例えば、金のナノクラスタおよびアルミニウムナノクラスタ)や、金属合金ナノクラスタなど、様々な導電性構造を含む。一部の例では、ナノクラスタのサイズは10~100オングストロームである。

20

【発明の開示】

【発明が解決しようとする課題】

【0003】

ナノクラスタを有する電荷蓄積トランジスタを有する一部のメモリは、これらの電荷蓄積トランジスタのこれらの電荷蓄積位置を充電し、放電するために使用される回路中に高電圧トランジスタも含む集積回路上に実装される。これらの電荷蓄積位置を充電すること、または放電することを使用して、1ビットまたは複数ビットの情報を記憶し、これらの充電すること、または放電することについては、プログラミングまたは消去と称されることもある。これらの高電圧トランジスタは概して比較的厚いゲート酸化物を含む。このゲート酸化物を成長させるために使用される酸化プロセスは、これらの電荷蓄積トランジスタの制御誘電体に強い影響を及ぼす可能性があり、それによってこれらのナノクラスタを酸化してしまうことが望ましくなく、またこの底部誘電体の厚みを増大させてしまうことが望ましくない。したがって、ナノクラスタを有するデバイスを作製するための方法を改善することが望ましい。

30

【課題を解決するための手段】

【0004】

添付図面を参照することにより、本発明は、より良好に理解することができ、また本発明の非常に多数の目的、特徴、および利点については、当業者には明らかになろう。

異なる図面中において、類似したまたは同じ構成要素が同じ参照記号を使用して示され

40

50

ている。図面中の構成要素は、簡潔に明確になるように示され、必ずしも縮尺して描かれているとは限らないことが当業者であれば理解できる。例えば、本発明の実施形態の理解を助けるために、図面中の一部の構成要素の寸法は、他の構成要素に対して相対的に誇張されていることもある。

#### 【0005】

以下の説明は、本発明の少なくとも1つの実施例を詳細に説明することを意図しており、本発明それ自体について限定するものと解釈すべきではない。正確に言えば、任意の変形態様が本明細書に添付された特許請求の範囲によって適切に定義された本発明の範囲内に含まれる。

#### 【0006】

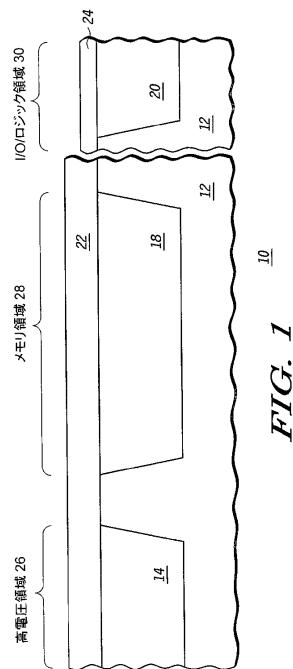

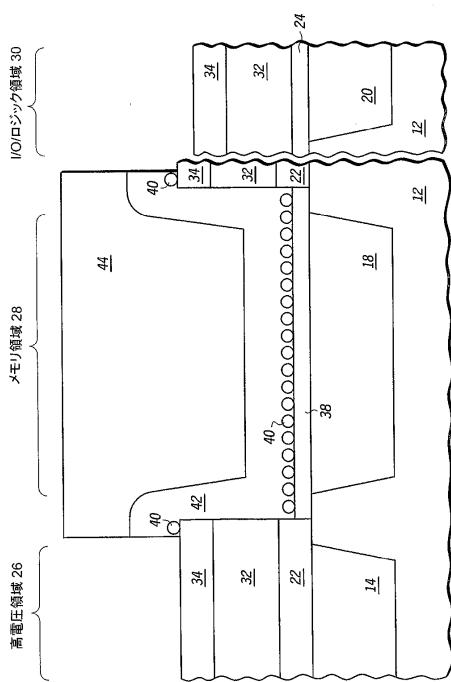

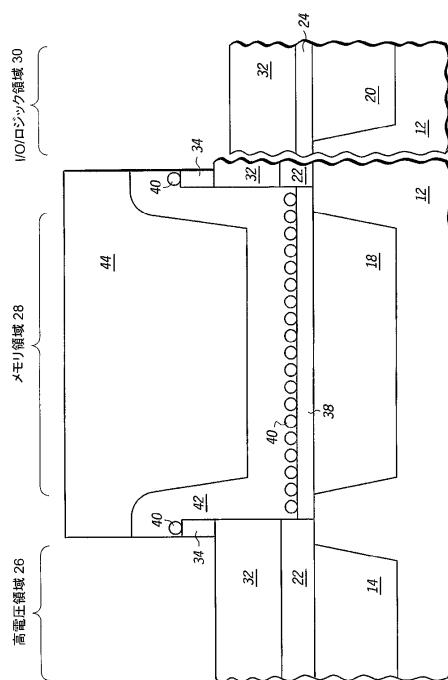

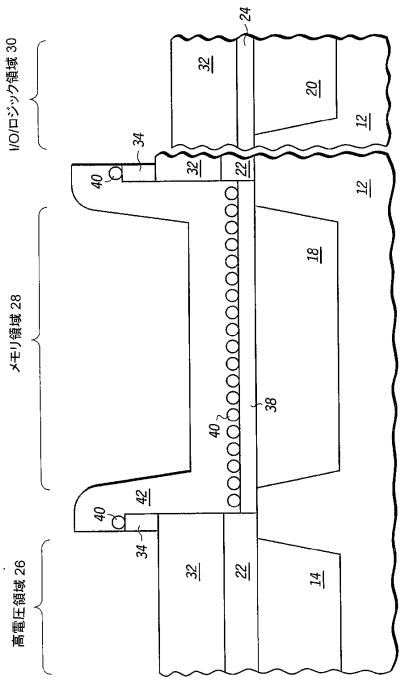

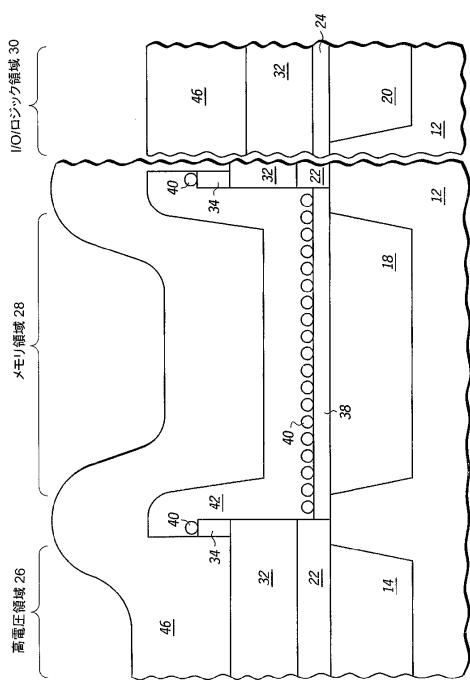

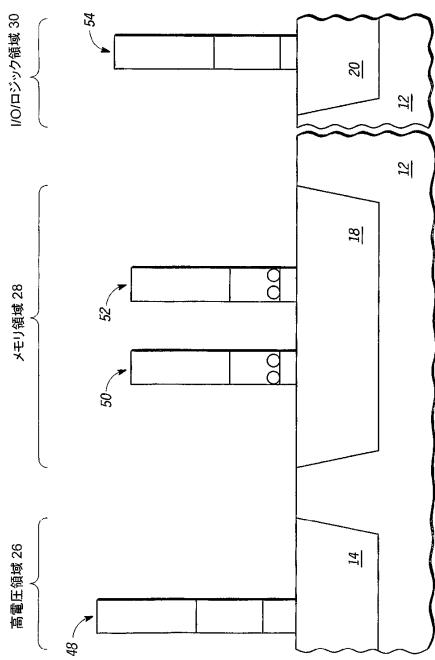

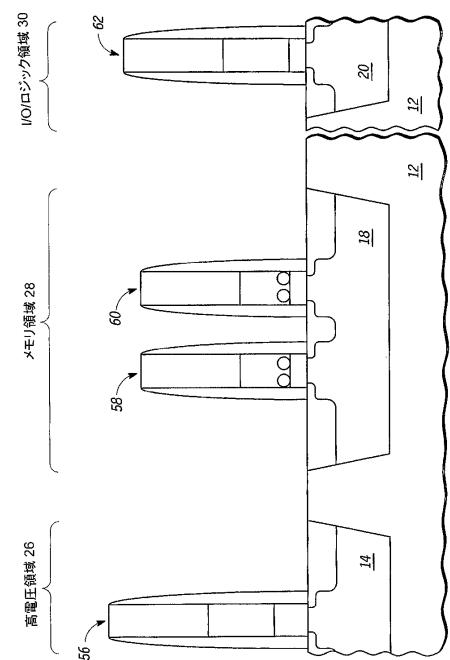

図1～14は本発明の第1の実施形態によるナノクラスタを含むメモリの製造段階中における半導体ウェーハの部分的な側面図を示す。後で説明しているように、この現在開示している実施形態では、これらのメモリデバイスのためのナノクラスタの形成に先立って、これらの高電圧トランジスタの比較的厚いゲート酸化物が形成される。このようにして、これらのナノクラスタは、高電圧トランジスタのゲート酸化物の形成中には影響を受けない。このような技法は、この下に存在するトンネル誘電体の厚みを保持しながら、これらのナノクラスタの酸化を防止することができる。

#### 【発明を実施するための最良の形態】

#### 【0007】

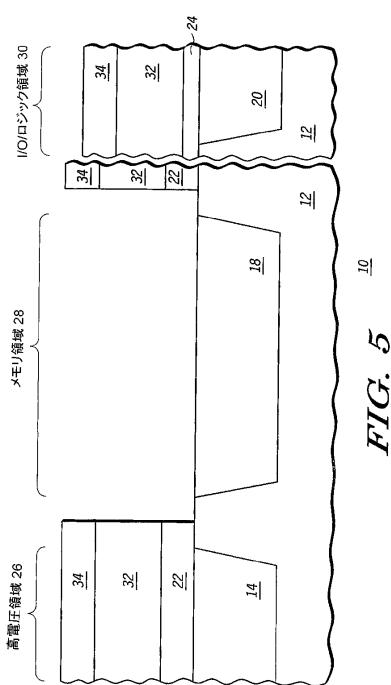

図1は、本発明の一実施形態による半導体装置10を示している。半導体装置10は集積回路ダイの一部分であってもよい。半導体装置10は、現在示されている製造段階における全体のウェーハの一部分である基板12を含む。基板12は、例えば、シリコン基板、シリコンゲルマニウム基板、ゲルマニウム基板、ガリウムヒ素基板など、どのようなタイプの半導体基板であってもよい。半導体装置10は、半導体装置10の機能回路の一部分を形成する様々なドーパントウェル14、18および20も含む。基板はまた異なるデバイスを分離し、本明細書中で説明されるこれらのウェルを横方向に分離する様々な予め形成された浅いトレンチ分離構造（図示せず）を含む。半導体装置10は、高電圧トランジスタを形成することができる高電圧領域26、（例えば、NVM（不揮発性メモリ）トランジスタなどの）メモリトランジスタを形成することができるメモリ領域28、（入出力機能を実施する際に使用することができる）I/Oトランジスタ、および／または（ロジック機能を実施する際に使用することができる）ロジックトランジスタを形成することができるI/O/ロジック領域30など、様々な異なるデバイス領域を含むことができる。変更実施形態においては、デバイス10は、任意数の、また任意タイプのデバイス領域を含んでいてもよく、ここでこれらの異なる領域内のこれらのデバイスは、異なる電気的特性を含んでいてもよいことに留意されたい。

#### 【0008】

この図に示される実施形態においては、ドーパントウェル14は、高電圧領域26内に存在し、ドーパントウェル18は、メモリ領域28内に存在し、ドーパントウェル20は、I/O/ロジック領域30内に存在する。ドーパントウェル14、18、および20は、様々な形態を取ることができることに留意されたい。一実施形態においては、ウェル18は、例えば不揮発性メモリ（NVM）アレイなどのメモリアレイの蓄積セル回路の一部分を形成し、ウェル14および20は、（高電圧デバイス、I/Oデバイス、および／またはロジックデバイスなど）様々なタイプの周辺デバイスを含めて、周辺回路の一部分を形成する。この図に示される実施形態においては、ウェル18は、p-ウェルであり、このp-ウェルの中に蓄積セルのアレイが存在することになる。一部の場合には、周辺デバイスは、HV（高電圧）デバイス（例えば、セル充電／放電デバイス）しか含んでいないが、本明細書中で説明しているこれらの実施形態においては、周辺デバイスは、このメモリアレイの外側に様々なデバイスを含んでおり、HVデバイス、集積回路ダイ入出力（I/O）デバイス、およびLV（低電圧）デバイス（例えば、ロジックデバイス）を含んでいてもよい。この図に示される実施形態においては、これらの周辺デバイスは、領域26

10

20

30

40

50

および / または領域 3 0 中に存在していてもよい。したがって、一実施形態においては、領域 2 8 は、電荷蓄積デバイスを形成するためのものであり、領域 2 6 および 3 0 は、非電荷蓄積デバイスを形成するためのものである。高電圧領域 2 6 内のウェル 1 4 は、このメモリアレイのセルをプログラムし、消去するための回路の一部分（例えば、高電圧トランジスタ）を形成することができる。この図に示される実施形態においては、ウェル 1 4 は、n - ウェルである。半導体装置 1 0 は、代わりに、または追加して深い n - 型分離ウェル内に HV p - ウェルを含んでいてもよい。この図に示される実施形態においては、ウェル 2 0 は、半導体装置 1 0 の I / O / ロジック回路の一部分を形成する。この図に示されるウェル 2 0 は、n - ウェルである。半導体装置は、代わりに、または追加して深い n - 型分離ウェル内に p - ウェルを含んでいてもよい。一実施形態においては、ウェル 2 0 は、D G O (デュアルゲート酸化物) ウェルである。10

#### 【 0 0 0 9 】

半導体装置 1 0 はまた、領域 2 6 および 2 8 内の基板 1 2 上に横たわる HV トランジスタゲート酸化物層 2 2 と、領域 3 0 の基板 1 2 上に横たわる I / O トランジスタゲート酸化物層 2 4 も含む。酸化物層 2 2 を使用して、領域 2 6 中の高電圧トランジスタのためのゲートスタックを形成することになり、酸化物層 2 4 を使用して領域 3 0 中の I / O および / またはロジックデバイスのためのゲートスタックを形成することになる。一実施形態においては、HV トランジスタゲート酸化物層 2 2 は、二酸化ケイ素層である。代わりに、酸窒化ケイ素 (silicon oxynitride)、酸化ハフニウム、酸化アルミニウム、酸化ランタン、またはランタンシリケートなど、他の誘電体を酸化物層 2 2 について使用することができる。酸化物層 2 2 は、例えば（酸素環境中または水蒸気環境中において）酸化物を成長させることにより、または C V D (化学的気相成長法) により、基板 1 2 上に形成することができる。一実施形態においては、酸化物層 2 2 は、少なくとも 5 ナノメートルの厚みを有するが、他の実施形態においては他の厚みからなっていてもよい。（一実施形態においては、酸化物層 2 2 は、ゲート誘電体層 2 2 と称することもできることに留意されたい。）一実施形態においては、I / O トランジスタゲート酸化物層 2 4 は、二酸化ケイ素層である。代わりに、酸窒化ケイ素、酸化ハフニウム、酸化アルミニウム、酸化ランタン、ランタンシリケートなど、他の誘電体を酸化物層 2 4 について使用することもできる。一実施形態においては、例えば（酸素環境または水蒸気環境中において）酸化物を成長させることにより、または C V D により、酸化物層 2 4 を領域 3 0 内に形成することができるように、酸化物層 2 2 の形成後に、パターン形成されたマスキング層を使用して、領域 3 0 中の酸化物層 2 2 の部分を除去してもよい。（一実施形態においては、酸化物層 2 4 は、ゲート誘電体層またはゲート絶縁体と称することもできることに留意されたい。）この図に示される実施形態においては、酸化物層 2 4 は、酸化物層 2 2 よりも薄く、例えば少なくとも 2 . 5 ナノメートルの厚みを有してもよいが、他の実施形態においては他の厚みからなっていてもよい。さらに他の実施形態においては、酸化物層 2 2 は、酸化物層 2 4 の代わりに領域 3 0 内で使用されてもよい。2030

#### 【 0 0 1 0 】

従来の技法を使用して、ドーパントウェル 1 4、1 8、および 2 0 を形成することもできることに留意されたい。また、一実施形態においては、ドーパントウェル 1 4 および 2 0 は、酸化物層 2 2 および 2 4 の形成に先立って形成することができるが、ドーパントウェル 1 8 は、酸化物層 2 2 および 2 4 の形成後に形成することもできる（ここでは、ドーパントウェル 1 8 についての注入は、酸化物層 2 2 および 2 4 を介して実施される）。代わりに、ドーパントウェル 1 4、1 8、および 2 0 のすべては、酸化物層 2 2 および 2 4 の形成に先立って、または形成後に形成されてもよい。変更実施形態においては、任意数のウェルが領域 2 6、2 8、および 3 0 のそれぞれに存在していてもよいことにも留意されたい。40

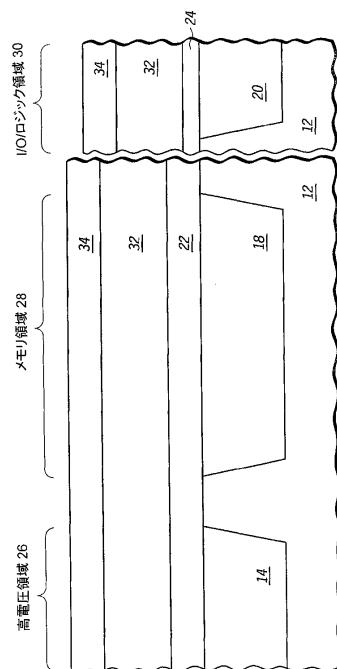

#### 【 0 0 1 1 】

図 2 を参照すると、（ゲート層とも称される）第 1 のゲート電極層 3 2 が酸化物層 2 2 および酸化物層 2 4 上に形成されている。一実施形態においては、第 1 のゲート電極層 350

2は、H V領域26およびI/O/ロジック領域30内のトランジスタのための底部ゲート電極層を実現する。一実施形態においては、第1のゲート電極層32は、(多結晶シリコンとも称される)ポリシリコンを含む。変更実施形態においては、第1のゲート電極層32は、ドープされたポリシリコンの仕事関数と同様の仕事関数を有する他の材料を含んでいてもよい。代わりに、第1のゲート電極層32は、金属であってもよい。一実施形態においては、第1のゲート電極層32は、CVDによって形成されてもよく、また少なくとも30ナノメートルの厚みを有していてもよい。引き続き図2を参照すると、第1のゲート電極層32の形成後に、酸化バリア層34が第1のゲート電極層32上に形成されている。一実施形態においては、酸化バリア層34は、窒化物を含む。代わりに、酸化バリア層34は、シリコンが豊富な窒化物を含んでいてもよい。他の実施形態においては、酸化バリア層34は、それによって後続の酸化中にその下に存在する層を保護する1つまたは複数の任意の材料から形成されてもよい。一実施形態においては、酸化バリア層34は、以下で説明しているように、後続のエッチング中に使用するためのエッティング停止層も実現する。したがって、酸化バリア層34は、エッティング停止層、または酸化バリア/エッティング停止層と称することもできる。他の実施形態においては、層34の代わりに複数の層を使用することもできる。一実施形態においては、酸化バリア層34は、CVDによって形成されてもよく、また少なくとも15ナノメートルの厚みを有していてもよい。

#### 【0012】

一実施形態においては、第1のゲート電極層32は、酸化バリア層34の形成の前または後にドーピングされてもよい。例えば、一実施形態においては、第1のゲート電極層32は、領域26、28、および30のそれぞれの領域内で異なるようにドーピングされてもよい。例えば一実施形態においては、第1のゲート電極層32は、領域28中においては非ドープにしたまま、第1のゲート電極層32が領域26および30のそれぞれの内部でp-型材料およびn-型材料をもたらすようにドープされる。従来のマスキング技法およびドーピング技法を使用して、第1のゲート電極層32をドープすることができることに留意されたい。一実施形態においては、第1のゲート電極層32のドーピングを使用して、これらの各領域中に形成されるこれらのトランジスタについての適切な仕事関数および閾値電圧を得ることができる。代わりに、これらの領域のうちの任意の領域内で、他のドーピングを実施してもよく、あるいはドーピングを実施しなくてもよい。

#### 【0013】

図3を参照すると、メモリ領域28内の基板12を露出させることができるようにメモリ領域28内に開口部を定義するパターン形成されたマスキング層36が酸化バリア層34上に形成されている。一実施形態においては、パターン形成されたマスキング層36は、フォトレジストを含む。図4を参照すると、パターン形成されたマスキング層36によって露出させられた、酸化バリア層34の部分が除去され、引き続いてパターン形成されたマスキング層36によって露出させられた、第1のゲート電極層32の部分が除去される。一実施形態においては、酸化バリア層34および第1のゲート電極層32の部分は、同じエッティングプロセスを使用して除去される。代わりに、異なるエッティング化学反応を使用して、酸化バリア層34と第1のゲート電極層32のそれぞれを除去することもできる。一実施形態においては、ドライエッティングを使用して、酸化バリア層34および第1のゲート電極層32を除去する。

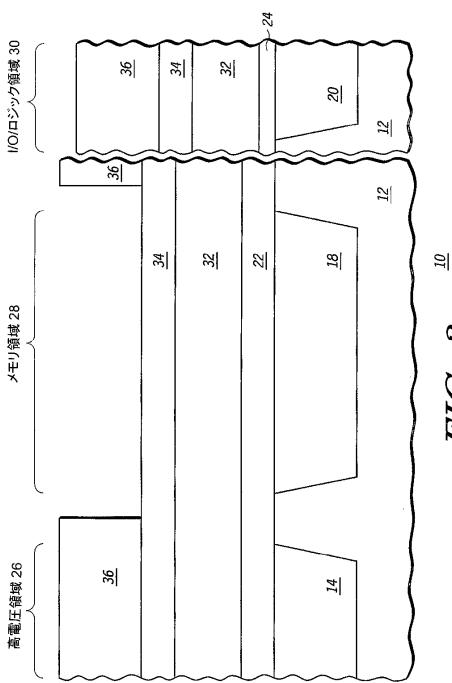

#### 【0014】

図5を参照すると、パターン形成されたマスキング層36によって露出させられた、酸化物層22の部分が除去される。一実施形態においては、酸化物層22のこれらの部分は、ウェットエッティングを使用して除去される。このウェットエッティングに続いて、パターン形成されたマスキング層36が除去される。パターン形成されたマスキング層36はまた、ウェットエッティングを使用して除去することもできる。

#### 【0015】

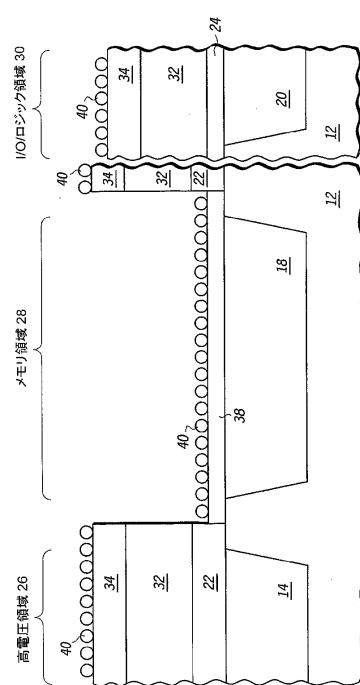

図6を参照すると、トンネル誘電体層38が、メモリ領域28中の、基板12のこれらの露出させられた部分上に形成される。一実施形態においては、トンネル誘電体層38は

、酸化物である。変更実施形態においては、酸窒化ケイ素、酸化ハフニウム、酸化アルミニウム、酸化ランタン、またはランタンシリケートなど、他の誘電体をトンネル誘電体層38について使用することができる。一実施形態においては、トンネル誘電体層38は、例えば（例えば、酸素環境または水蒸気環境中における）酸化、CVD、分子CVD、ALD（原子層堆積）、またはPVD（物理的気相成長）を使用して形成されてもよい。この図に示される実施形態においては、トンネル誘電体層38は、基板12上に酸化物を成長させることによって形成される。したがって、この実施形態においては、トンネル誘電体層38は、酸化バリア層34上には形成されない。酸化バリア層34は、トンネル誘電体層38の形成中に、第1のゲート電極層32を酸化から保護することにも留意されたい。しかし、トンネル誘電体層38が堆積される変更実施形態においては、領域26および30中の酸化バリア層34上、ならびに領域28中の基板12上には、トンネル誘電体層38が形成されるはずである。10

#### 【0016】

引き続き図6を参照すると、（例えば、シリコン、アルミニウム、金、ゲルマニウム、またはシリコンアロイおよびゲルマニウムアロイ、あるいは他のタイプの導電材料またはドープされた半導体材料もしくは非ドープの半導体材料の）ナノクラスタ40の層が、例えばCVD技法、エアロゾル堆積技法、スピンドルコーティング技法、または薄膜をアニールすることなどの自己集合技法によって酸化バリア層34およびトンネル誘電体層38上に形成されて、ナノクラスタが形成される。一実施形態においては、これらのナノクラスタ40は、シリコンナノクラスタである。これらのナノクラスタが不揮発性メモリ中で利用される一実施形態においては、これらのナノクラスタは、5から7ナノメートルのサイズを有する $1 \times 10^{12} \text{ cm}^2$ の平面密度を有する。一部の実施形態においては、ナノクラスタは、サイズが1～10ナノメートルからなっている。しかし、他の実施形態におけるこれらのナノクラスタは、他のサイズおよび/または他の密度からなっていてもよい。一実施形態においては、ナノクラスタ40は概してクラスタの平均サイズに等しい平均距離によって分離される。このような一実施形態における平均距離は、4ナノメートルよりも大きい。ナノクラスタ40は一様なサイズと分布を有するものとして示されているが、ナノクラスタ40は、実際面では非一様なサイズと、非一様な分布を有することになる。ナノクラスタ40は、半導体装置10の不揮発性メモリのトランジスタ（図14参照）中の電荷蓄積位置を実装するために利用されることになる。ナノクラスタ40は、ナノクラスタ電荷蓄積層40と称することもできることに留意されたい。20

#### 【0017】

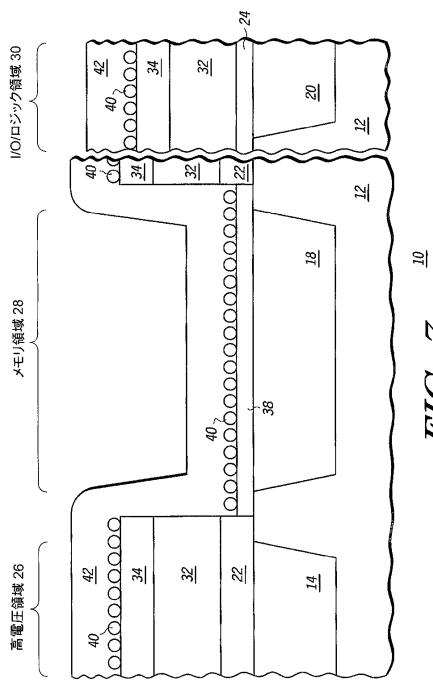

図7を参照すると、ナノクラスタ40が形成された後に、誘電体材料層が（例えば、化学的気相成長によって）ナノクラスタ40上に形成されて、制御誘電体層42が形成されている。一実施形態においては、制御誘電体層42は、これらのナノクラスタ上に堆積された二酸化ケイ素層であり、それによってこれらのナノクラスタの周囲を取り囲む。代わりに、酸窒化ケイ素、酸化ハフニウム、酸化アルミニウム、酸化ランタン、またはランタンシリケートなど、他の誘電体が層42のために使用されてもよい。他の実施形態においては、二酸化ケイ素と、窒化ケイ素と、二酸化ケイ素のONO（酸化物-窒化物-酸化物）スタックが層42について使用されてもよい。変更実施形態においては、他の材料または材料のスタックを使用して、制御誘電体層42を形成することもできる。一実施形態においては、制御誘電体層42は、約5～10ナノメートルの厚みを有するが、他の実施形態においては他の厚みからなっていてもよい。30

#### 【0018】

変更実施形態においては、トンネル誘電体層38、ナノクラスタ40、および制御誘電体層42は、様々な異なる方法で形成されてもよいことに留意されたい。例えば、一部の実施形態においては、トンネル誘電体層38、ナノクラスタ40、および制御誘電体層42は、誘電体材料層中のイオン注入（例えば、シリコンまたはゲルマニウム）（図示せず）によって形成されてもよく、その後これらのイオンのアニーリングが続いて、この誘電体材料層中にナノクラスタが形成される。他の実施形態においては、トンネル誘電体層40

38、ナノクラスタ40、および制御誘電体層42は、誘電体材料の2層間のシリコンが豊富な酸化物層の再結晶化により形成されて、これらのナノクラスタが形成されてもよい。他の実施形態においては、これらのナノクラスタは、このトンネル誘電体上に配置された複数の層の形で実装されてもよい。他の実施形態においては、これらのナノクラスタは、ナノクラスタ材料（例えば、1～5ナノメートル）の薄いアモルファス層を堆積することによって形成され、この場合にはこの結果の構造は、後続のアニーリングプロセス中にアニールされる。

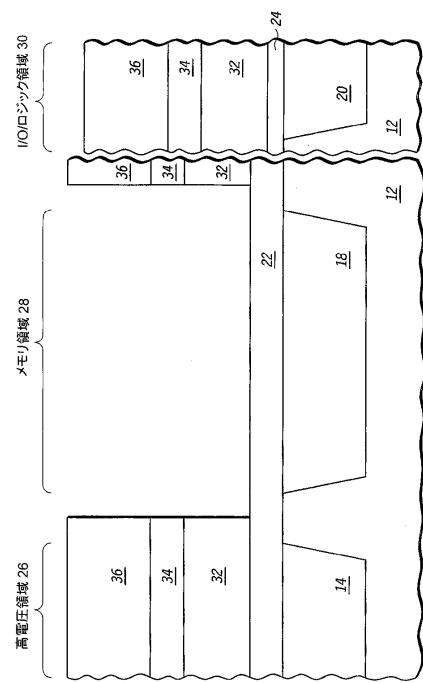

#### 【0019】

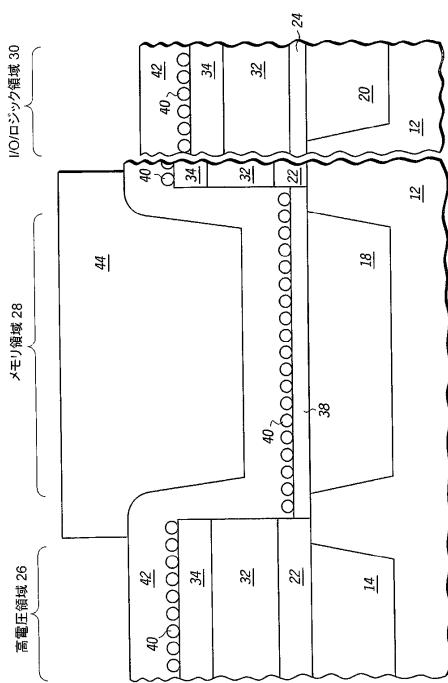

図8を参照すると、メモリ領域28を覆い、領域26および30を露出させるパターン形成されたマスキング層44が制御誘電体層42上に形成される。一実施形態においては、パターン形成されたマスキング層44は、フォトレジスト層であり、従来の技法を使用して形成することができる。図9を参照すると、（パターン形成されたマスキング層44によって露出させられた）領域26および30中の制御誘電体層42およびナノクラスタ40の部分が除去される。一実施形態においては、ドライエッチングが使用されてもよい。代わりに、これらのナノクラスタを除去するための後続の清浄化ステップを含むことができるウェットエッチングによって、これらの部分を除去することもできる。この図に示される実施形態においては、酸化バリア層34もエッチング停止層として機能することもあることに留意されたい。このようにして、酸化バリア層34はまた、ドライエッチングについての終止ポイントも実現する。（変更実施形態においては、追加層を使用してエッチング停止層を設けることもできることに留意されたい。）トンネル誘電体層38が成長されるのでなく堆積される実施形態においては、トンネル誘電体層38は、領域26および30中の酸化バリア層34上にもナノクラスタ40の下にも存在することに留意されたい。これらの実施形態においては、（パターン形成されたマスキング層44によって露出させられた）領域26および30中の制御誘電体層42およびナノクラスタ40の除去後に、これらの領域中のトンネル誘電体層38の部分もまた除去されるはずである。

#### 【0020】

図10を参照すると、パターン形成されたマスキング層44によって露出させられた酸化バリア層34の部分は、例えばドライエッチングまたはウェットエッチングを使用して除去されている。図11を参照すると、パターン形成されたマスキング層44は、従来の技法を使用して除去される。一実施形態においては、パターン形成されたマスキング層44を除去するのに先立って、フッ化水素酸清浄化を使用して、水素でシリコン表面を終端させ、これらの露出させられた表面上における酸化物の成長を防止することによりポリシリコン層32のこれらの露出させられた表面を保護（passivate）することができる。このようにして、後続の層の形成に先立つかなりの酸化物の自然形成（native oxide formation）が防止される。

#### 【0021】

図12を参照すると、第2のゲート電極層46が領域26および30中の第1のゲート電極層32上と、領域28中の制御誘電体層42上に形成されている。それによって、第1のゲート電極層32および第2のゲート電極層46は、領域26および30内のHVTトランジスタ、I/Oトランジスタ、およびロジックトランジスタ中で使用するためのゲートスタックの一部分を形成する。前述のフッ化水素酸清浄化は、もし使用されるなら、この第1のゲート電極層と第2のゲート電極層の間の深刻な酸化物層の形成を防止することに留意されたい。他の実施形態においては、（例えば、摂氏800度よりも高いなどの）高温炉中における水素バークを使用して、第2のゲート電極層46の形成に先立つどのような酸化物自然成長についても除去することができる。一実施形態においては、第2のゲート電極層46は、第1のゲート電極層32と同じ材料から形成される。代わりに、これらのゲート電極層は、異なった材料であってもよい。一実施形態においては、第2のゲート電極層46は、ポリシリコン層である。代わりに、第2のゲート電極層46は、シリサイド化されたポリシリコン材料を含んでいてもよい。

#### 【0022】

10

20

30

40

50

図13を参照すると、パターン形成技法およびエッチング技法を使用して、ゲートスタック48、50、52、および54が形成されており、ここでゲートスタック48は、領域26内にあり、ゲートスタック50および52は、領域28内にあり、ゲートスタック54は、領域30内にある。（例えば、異方性プラズマエッチングを介して）このマスキング層によって露出させられた、様々な層の部分の除去が後に追隨する、例えば従来のマスキング技法を使用して、これらのゲートスタックを形成することができる。領域28内のこれらのゲートスタックは、ナノクラスタを含むが、これらの周辺領域（例えば、領域26および30）中のこれらのゲートスタックは、ナノクラスタを含まないことに留意されたい。また、ゲートスタック48および54のこれらのゲート酸化物は、ゲートスタック50および52のナノクラスタの形成に先立って形成されるので、これらのナノクラスタは、このゲート酸化物形成中に消耗されないことも留意されたい。一実施形態においては、ゲートスタック48、50、52、および54を形成するためのエッチングは、同時に実施することができる。代わりに、ゲートスタック50および52は、ゲートスタック48および54の形成に先立って、またはその後に形成されてもよい。また変更実施形態においては、追加の層を、ゲートスタック48、50、52、および54のそれぞれに含めることもできることに留意されたい。例えば、各ゲートスタックは、この第2のゲート電極層上のARC（反射防止コーティング）を含んでいてもよい。代わりに、他の層または追加の層が含まれてもよい。

#### 【0023】

図14を参照すると、従来の処理を使用して、NVMトランジスタ58および60や周辺トランジスタ56および62など、ほぼ完成されたデバイスを形成することができる。ゲートスタック56、58、60、および62の形成に引き続いで、標準のCMOS処理技法を使用して、ソース／ドレイン拡張部、側壁スペーサ、およびソース／ドレイン領域が形成される。変更実施形態においては、任意数のデバイスを形成することができることに留意されたい。また、この図に示される実施形態においては、トランジスタ58と60とは、共通のソース／ドレイン領域を共有する。しかし、変更実施形態においては、各トランジスタは、それ自体のソース／ドレイン領域を有していてもよい。

#### 【0024】

したがって、メモリトランジスタのためのナノクラスタ電荷蓄積層の形成に先立ったこれらのHVトランジスタのためのゲート酸化物の形成がどのようにしてメモリトランジスタおよび周辺トランジスタの集積化の改善を可能にすることができるかについて理解することができる。すなわち、これらのナノクラスタがこの高電圧ゲート酸化物の成長の後に形成されるので、これらのナノクラスタは、これらのナノクラスタのサイズを減少させ、この下に存在するトンネル誘電体層（例えば、層38）の厚みを増大させる可能性があり得る酸化雰囲気にさらされることはない。また、一実施形態においては、このメモリ領域内の制御誘電体層（例えば、層42）は、どのようなエッチング薬剤にもさらされることがないことに留意されたい。このようにして、この下に存在するナノクラスタを保護する余分な犠牲層は必要とされない。またこの図に示される実施形態においては、このウェーハのこれらの周辺区域（例えば、領域26および30）からのこれらのナノクラスタの除去も、酸化バリア／エッチング停止層34の実装によりスムーズに実施される。

#### 【0025】

以上の説明では、本発明の少なくとも一実施形態を説明することが意図されている。以上の説明では、本発明の範囲を定義することは意図されていない。もっと正確に言えば、本発明の範囲については、添付の特許請求の範囲中において定義される。したがって、本発明の他の実施形態は、この以上の説明に対する他の変形、修正、追加、および／または改善を含む。

#### 【0026】

一実施形態においては、ナノクラスタ電荷蓄積デバイスを形成する方法が提供されている。半導体装置の第1の領域は、1つまたは複数の非電荷蓄積デバイスを配置するために特定される。この半導体装置の第2の領域は、1つまたは複数の電荷蓄積デバイスを配置

するために特定される。この1つまたは複数の非電荷蓄積デバイスのゲート絶縁体として使用されるゲート酸化物は、この半導体装置の第1の領域中に形成され、引き続きナノクラスタ電荷蓄積層がこの半導体装置の第2の領域中に形成される。

#### 【0027】

さらなる実施形態においては、この第1の領域は、少なくとも5ナノメートルのゲート酸化物の厚みを有する高電圧トランジスタを形成するための領域として特定される。さらなる他の実施形態においては、非電荷蓄積トランジスタは、この第1の領域中に形成され、電荷蓄積トランジスタは、この半導体装置の第2の領域中のナノクラスタ電荷蓄積層を形成した後にこの第2の領域中に形成される。さらなる他の実施形態においては、この半導体装置の第3の領域が、1つまたは複数の入出力トランジスタまたはロジックトランジスタ、あるいはこれらの組合せを形成するための領域として特定されており、この第3の領域は、この第1の領域中の1つまたは複数の非電荷蓄積デバイスのゲート酸化物よりも厚みが薄いゲート酸化物を有する1つまたは複数の非電荷蓄積トランジスタを配置するためのものである。10

#### 【0028】

さらなる他の実施形態においては、ゲート電極層、およびその上に横たわるゲート酸化バリア層が、このゲート酸化物の形成後に、またこの半導体装置の第1の領域とこの半導体装置の第2の領域の両方の中にこのナノクラスタ電荷蓄積層を形成するのに先立ってこの非電荷蓄積デバイス上に形成される。このナノクラスタ電荷蓄積層は、この酸化バリア層を使用してこの半導体装置の第1の領域中におけるゲート電極層を保護することにより、この半導体装置の第1の領域から除去される。20

#### 【0029】

さらなる他の実施形態においては、基板が設けられる。このゲート酸化物は、この基板上に横たわって、この半導体装置の第1の領域とこの半導体装置の第2の領域の両方の内部に形成される。この半導体装置の第1の領域とこの半導体装置の第2の領域のそれぞれにおける少なくとも1つのウェル領域が注入される。ゲート電極材料層がこの半導体装置の少なくとも第1の領域内に形成され、窒化物層がこのゲート電極材料層上に横たわって形成される。この半導体装置の第1の領域内のゲート電極材料層および窒化物層がパターン形成され、この半導体装置の第2の領域からのゲート電極材料層、窒化物層、およびゲート酸化物が除去される。メモリゲート酸化物がこの半導体装置の第2の領域内に形成され、このナノクラスタ電荷蓄積層は、この半導体装置の第1の領域とこの半導体装置の第2の領域の両方の中に形成される。制御誘電体がこのナノクラスタ電荷蓄積層を取り囲んで形成される。この半導体装置の第1の領域中のナノクラスタ電荷蓄積層および制御誘電体が除去され、この窒化物層の残りの部分が除去される。所定のゲートスタックの形成が、この半導体装置の第1の領域、およびこの半導体装置の第2の領域の内部において完了され、この非電荷蓄積デバイスおよびこの電荷蓄積デバイスの形成が完了されて、この半導体装置の第1の領域とこの半導体装置の第2の領域の両方の内部でトランジスタが形成される。さらなる他の実施形態においては、この半導体装置の第3の領域が、この半導体装置の第1の領域中のトランジスタよりも薄いゲート酸化物の厚みを有するトランジスタの形成のために特定される。この半導体装置の第3の領域中のこれらのトランジスタは、この半導体装置の第1の領域中の非電荷蓄積デバイスを形成するために使用されるものと同じ処理ステップを使用して形成される。3040

#### 【0030】

他の実施形態においては、ナノクラスタ電荷蓄積デバイスを形成する方法は、基板を設けること、1つまたは複数の非電荷蓄積デバイスを配置するための、この基板上に横たわる第1の領域を特定すること、1つまたは複数の電荷蓄積デバイスを配置するための、この基板上に横たわる第2の領域を特定すること、この第1の領域とこの第2の領域の両方の中に、この半導体装置の第1の領域中の1つまたは複数の非電荷蓄積デバイスのゲート絶縁体として機能するゲート酸化物を形成すること、このゲート酸化物上に横たわるゲート材料層を形成すること、このゲート材料層上に横たわる酸化バリア層を形成すること、50

この第2の領域からこの酸化バリア層、このゲート材料層、およびこのゲート酸化物を除去すること、この第2の領域中にこのゲート酸化物よりも薄い厚みを有する電荷蓄積デバイスのゲート酸化物を形成すること、この第1の領域とこの第2の領域の両方の中にナノクラスタ電荷蓄積層および制御誘電体を形成すること、この第1の領域中のゲート材料を保護する酸化バリア層を使用しながら、この第1の領域からこのナノクラスタ電荷蓄積層およびこの制御誘電体を除去すること、およびこの第1の領域およびこの第2の領域の中のトランジスタの形成を完了することを含む。

#### 【0031】

さらなる実施形態においては、この方法は、少なくとも5ナノメートルの厚みを有する、この第1の領域中のゲート酸化物を形成することにより、この第1の領域中に高電圧トランジスタを実装することをさらに含む。この第1の領域中の高電圧トランジスタは、この第2の領域中の電荷蓄積トランジスタを、プログラムすること、消去すること、または読み取ることのうちの少なくとも1つを実施する。10

#### 【0032】

さらなる他の実施形態においては、この方法は、この第1の領域およびこの第2の領域のそれぞれの内部に1つまたは複数のウェル領域を形成すること、および時間的に分離された、ゲート材料の2つの堆積を用いてこの第2の領域中のこれらのトランジスタのゲート電極を形成することをさらに含む。

#### 【0033】

さらなる他の実施形態においては、この方法は、この第1の領域内の1つまたは複数の非電荷蓄積デバイスとは異なる電気的特性を有する1つまたは複数の非電荷蓄積デバイスを配置するための、この基板上に横たわる第3の領域を特定することをさらに含む。さらなる他の実施形態においては、この方法は、この第3の領域中に、入出力機能またはロジック機能、あるいはこれらの両方の組合せを実装するトランジスタを形成することをさらに含む。さらなる他の実施形態においては、この方法は、この第2の領域中の電荷蓄積デバイスのゲート酸化物と実質的に同じ厚み、またはこの第2の領域中の電荷蓄積デバイスのゲート酸化物の厚みよりも薄い厚みを有するゲート酸化物を有する1つまたは複数の非電荷蓄積デバイスを実装することをさらに含む。20

#### 【0034】

さらなる他の実施形態においては、この方法は、この第1の領域およびこの第2の領域の中のトランジスタの形成を完了するのに先立って、この酸化バリア層を除去することをさらに含む。30

#### 【0035】

さらに他の実施形態においては、ナノクラスタ電荷蓄積デバイスを形成する方法は、基板を設けること、この基板上に横たわって、高電圧デバイス領域とメモリデバイス領域の両方の内部に高電圧ゲート酸化物を形成すること、この高電圧デバイス領域およびメモリデバイス領域上に横たわってゲート電極材料層を形成すること、このゲート電極材料層上に横たわって酸化バリア層を形成すること、このメモリデバイス領域からこの酸化バリア層、ゲート電極材料層および高電圧ゲート酸化物を除去すること、この半導体装置のメモリデバイス領域内にメモリゲート酸化物を形成すること、この高電圧ゲート酸化物およびこのメモリゲート酸化物上に横たわる高電圧デバイス領域とメモリデバイス領域の両方の中にナノクラスタ電荷蓄積層を形成すること、このナノクラスタ電荷蓄積層を取り囲む制御誘電体を形成すること、およびこの酸化バリア層を使用して、このゲート電極材料層の酸化を防止しながらこの高電圧デバイス領域中のこのナノクラスタ電荷蓄積層およびこの制御誘電体を除去することを含む。40

#### 【0036】

さらなる実施形態においては、この方法は、この酸化バリア層の残っている部分を除去することをさらに含む。

さらなる他の実施形態においては、この方法は、この高電圧デバイス領域とこのメモリデバイス領域の内部の所定のゲートスタックの形成を完了すること、およびこの高電圧デ50

バイス領域中の非電荷蓄積デバイスと、このメモリデバイス領域中の電荷蓄積デバイスの形成を完了して、これら両方の領域内にトランジスタを形成することをさらに含む。

#### 【0037】

さらなる他の実施形態においては、この方法は、この高電圧デバイス領域およびこのメモリ領域のそれぞれに少なくとも1つのウェル領域を注入することをさらに含む。

さらなる他の実施形態においては、この方法は、この高電圧ゲート酸化物よりも薄いメモリゲート酸化物を形成することをさらに含む。さらなる他の実施形態においては、この方法は、少なくとも5ナノメートル以上の厚みを有する高電圧ゲート酸化物を形成することをさらに含む。

#### 【0038】

本明細書中で説明されたこれらのデバイスの多くは、第1の電流取扱端子と第2の電流取扱端子との間の電流の流れを制御する制御端子を有するものとして概念化することができる。このようなデバイスの1例がトランジスタである。トランジスタの制御端子上の適切な状態により、この第1の電流取扱端子からこの第2の電流取扱端子へと、またこの第2の電流取扱端子からこの第1の電流取扱端子へと電流が流れようになる。また、FET（電界効果トランジスタ）は、多くの場合にドレイン、ゲート、およびソースを有するものとして説明されているが、このようなほとんどのデバイスにおいて、このドレインは、このソースと置き換えが可能である。これは、このトランジスタのレイアウトおよび半導体処理が多くの場合対称的であるからである。

#### 【0039】

以上の詳細な説明は例示的なものであり、「一実施形態」として説明したものは一つの例示した実施形態のことである。したがって、文脈における単語「一」の使用は、1つの、またただ1つの実施形態だけが説明した特徴を有することを意図していない。むしろ、他の多くの実施形態も、例示した「一実施形態」で説明した特徴を有することがしばしばある。このように、本発明が一実施形態の文脈で説明されているときには、一実施形態は、本発明の潜在的な多数の実施形態のうちの1つである。

#### 【0040】

この詳細な説明中のこれらの単語「一実施形態」の使用に関する以上の警告にもかかわらず、添付の特許請求の範囲中において特定数の請求項に記載の構成要素が意図されている場合には、このような意図については、この請求項中に明示的に列挙されることになり、このような列挙がない場合には、このような限定は、存在せず、あるいは意図されていないことが当業者には理解されよう。例えば、添付の特許請求の範囲において、1請求要素が「1つの（one）」機能を有するものとして説明されるときには、この要素は、説明されている1つの、またただ1つの機能だけに限定されることが意図されている。さらに、1請求要素が添付の特許請求の範囲中において、「1つの（a）」機能を含み、または備えるものとして説明されているときには、この要素は、説明されている1つの、またただ1つの機能だけに限定されることは意図されていない。もっと正確に言えば、例えば「1つの（a）」機能を含む請求項は、該当する1つまたは複数の機能を含む装置または方法と解釈される。すなわち、該当する装置または方法は、ある機能を含むので、この請求項は、この装置または方法がこのような他の類似した機能を含むかどうかにかかわらず、この装置または方法と解釈される。1請求項の1機能に対する非限定的な、導入の冠詞としての、この単語「1つの（a）」についてのこの使用については、見出される可能性があるものと反対のどのような変則的なまたは先例としての判例法にもかかわらず、過去における多数の法廷によって採用された解釈と同じであるものとして本明細書中では出願人によって採用されている。同様に、1請求要素が前述の機能（例えば「前記（the）」機能）を含み、または備えるものとして添付の特許請求の範囲中に説明されるときには、この要素は、この定冠詞の付隨的な使用により単に説明されているにすぎない1つ、またただ1つの機能だけには限定されないことが意図されている。

#### 【0041】

さらに、特許請求の範囲中における「少なくとも1つの」や「1つまたは複数の」など

10

20

30

40

50

の導入句の使用については、たとえ同じ請求項が導入句「1つまたは複数の」または「少なくとも1つの」、および「1つの(a)」や「1つの(an)」などの不定冠詞を含んでいたとしても、これらの不定冠詞「1つの(a)」または「1つの(an)」による他の請求要素の導入がこのようなただ1つの要素しか含まない本発明に対するこのような導入された請求要素を含むどのような特定の請求項を限定することを意味するものとも解釈すべきではない。この同じことが定冠詞の使用についても当てはまる。

#### 【0042】

本明細書中のこれらの教示に基づいて、当業者には、本明細書中に開示されたこれらの構造およびこれらの方法を実現するために必要なこれらのステップを簡単に実装することが可能になり、またこれらのプロセスパラメータ、材料、寸法、およびステップのシーケンスは、実施例としてしか提供されておらず、本発明の範囲に含まれる所望の構成ならびに修正形態を実現するために変更することができる理解されよう。本明細書中に開示されたこれらの実施形態の変形および修正態様については、添付特許請求の範囲に記載の本発明の趣旨および範囲を逸脱することなく、本明細書中に記載の説明に基づいて行うことができる。

10

#### 【0043】

本発明の特定の実施形態を図示し説明したが、本明細書中の教示に基づいて、様々な修正形態、代替構成、および等価形態が、請求している本発明を逸脱することなく使用することができることが、当業者には明らかであろう。したがって、添付の特許請求の範囲は、その範囲内に、本発明の真の趣旨および範囲内に含まれる、かかるすべての変形態、修正形態などを包含している。さらに、本発明は、添付の特許請求の範囲によってのみ定義されることを理解されたい。上記説明は、本発明の実施形態の網羅的なリストを提示することを意図したものではない。別に明示的に述べていない限り、これらの用語、すなわち非限定的な、非排他的な、または同様な用語が各実施例と共に同時に表現されているか否かにかかわらず、本明細書中に提示される各実施例は、非限定的または非排他的な実施例である。一部の例示の実施形態、およびそれらに対する例示の変形態の概要を説明しようとする試みが行われてきているが、他の実施形態および／または変形態についても、添付の特許請求の範囲内で定義される本発明の範囲内に含まれる。

20

#### 【図面の簡単な説明】

#### 【0044】

30

【図1】本発明の一実施形態による集積回路の様々な製造段階中における半導体装置の一連の部分側面図のうちの1つの側面図。

【図2】本発明の一実施形態による集積回路の様々な製造段階中における半導体装置の一連の部分側面図のうちの1つの側面図

【図3】本発明の一実施形態による集積回路の様々な製造段階中における半導体装置の一連の部分側面図のうちの1つの側面図

【図4】本発明の一実施形態による集積回路の様々な製造段階中における半導体装置の一連の部分側面図のうちの1つの側面図

【図5】本発明の一実施形態による集積回路の様々な製造段階中における半導体装置の一連の部分側面図のうちの1つの側面図

40

【図6】本発明の一実施形態による集積回路の様々な製造段階中における半導体装置の一連の部分側面図のうちの1つの側面図

【図7】本発明の一実施形態による集積回路の様々な製造段階中における半導体装置の一連の部分側面図のうちの1つの側面図

【図8】本発明の一実施形態による集積回路の様々な製造段階中における半導体装置の一連の部分側面図のうちの1つの側面図

【図9】本発明の一実施形態による集積回路の様々な製造段階中における半導体装置の一連の部分側面図のうちの1つの側面図

【図10】本発明の一実施形態による集積回路の様々な製造段階中における半導体装置の一連の部分側面図のうちの1つの側面図

50

【図1】本発明の一実施形態による集積回路の様々な製造段階中における半導体装置の一連の部分側面図のうちの1つの側面図

【図2】本発明の一実施形態による集積回路の様々な製造段階中における半導体装置の一連の部分側面図のうちの1つの側面図

【図3】本発明の一実施形態による集積回路の様々な製造段階中における半導体装置の一連の部分側面図のうちの1つの側面図

【図4】本発明の一実施形態による集積回路の様々な製造段階中における半導体装置の一連の部分側面図のうちの1つの側面図

【図1】

FIG. 1

【図2】

FIG. 2

【図3】

FIG. 3

【図4】

FIG. 4

【図5】

FIG. 5

【図6】

FIG. 6

【図7】

FIG. 7 10

【図8】

FIG. 8 10

【図9】

FIG. 9 10

【図10】

FIG. 10 10

【図 1 1】

FIG. 11 10

【図 1 2】

FIG. 12 10

【図 1 3】

FIG. 13 10

【図 1 4】

FIG. 14 10

---

フロントページの続き

(51)Int.Cl. F I

H 01 L 29/788 (2006.01)

H 01 L 29/792 (2006.01)

H 01 L 27/10 (2006.01)

(56)参考文献 特開平11-274420(JP,A)

特開2003-309182(JP,A)

特開2004-153037(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 27/115

H01L 21/8247

H01L 29/788