(19) 日本国特許庁(JP)

## (12) 特 許 公 報(B2)

(11) 特許番号

特許第4206397号

(P4206397)

(45) 発行日 平成21年1月7日(2009.1.7)

(24) 登録日 平成20年10月24日(2008.10.24)

(51) Int.Cl.

F 1

**G09G 3/28 (2006.01)**

G09G 3/28 G09G 3/20 G09G 3/20 G09G 3/20 G09G 3/20 G09G 3/20

H

611C

622C

624M

670D

請求項の数 9 (全 12 頁) 最終頁に続く

(21) 出願番号

特願2005-112268 (P2005-112268)

(22) 出願日

平成17年4月8日(2005.4.8)

(65) 公開番号

特開2005-301278 (P2005-301278A)

(43) 公開日

平成17年10月27日(2005.10.27)

審査請求日 平成17年4月8日(2005.4.8)

(31) 優先権主張番号 2004-024869

(32) 優先日 平成16年4月12日(2004.4.12)

(33) 優先権主張国 韓国(KR)

(73) 特許権者 590002817

三星エスディアイ株式会社

大韓民国京畿道水原市靈通区▲しん▼洞5

75番地

(74) 代理人 100083806

弁理士 三好 秀和

(74) 代理人 100095500

弁理士 伊藤 正和

(72) 発明者 鄭 宇 ▲俊▼

大韓民国京畿道水原市靈通区▲辛▼洞5

75番地

(72) 発明者 蔡 昇 煉

大韓民国京畿道水原市靈通区▲辛▼洞5

75番地

最終頁に続く

(54) 【発明の名称】 プラズマディスプレイパネルの初期起動方法及びプラズマ表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

第1電極、第2電極によって放電セルが形成されるプラズマディスプレイパネルの電源がオンする時に操作される初期起動方法において、

a) 前記第1電極の電圧を第1電圧から第2電圧まで上昇させ、前記第2電極に第3電圧が印加される間に前記第1電極の電圧を第4電圧から第5電圧まで下降させて前記放電セルに壁電荷を形成する段階、

b) 前記放電セルに壁電荷が形成された直後に、前記放電セルの第1電極と第2電極との間の電圧差が、交互に第6電圧または前記第6電圧の値で極性が負の電圧になるように前記第1電極と前記第2電極に電圧を印加して前記放電セルを放電させる段階、

を含む、プラズマディスプレイパネルの初期起動方法。

## 【請求項 2】

入力される画像信号によってプラズマディスプレイパネルを駆動する場合に、サブフィールドはリセット期間、アドレス期間及び維持期間を含み、

前記リセット期間は、前記第2電極に第7電圧を印加し、前記第1電極の電圧を第8電圧から第9電圧まで下降させる段階を含み、

前記第3電圧と前記第5電圧の差は、前記第7電圧と前記第9電圧の差より大きい、請求項1に記載のプラズマディスプレイパネルの初期起動方法。

## 【請求項 3】

前記第3電圧は前記第7電圧より大きい、請求項2に記載のプラズマディスプレイパネル

10

20

ルの初期起動方法。

【請求項 4】

前記第5電圧は前記第9電圧より小さい、請求項2に記載のプラズマディスプレイパネルの初期起動方法。

【請求項 5】

前記第3電圧は、前記第1電極と第2電極との間の電圧差を前記第6電圧とするために前記第2電極に印加される電圧と同一である、請求項2に記載のプラズマディスプレイパネルの初期起動方法。

【請求項 6】

前記維持期間において、前記第1電極と前記第2電極との間の電圧差が交互に前記第6電圧または前記第6電圧の値で極性が負の電圧になるように前記第1電極と前記第2電極に電圧を印加する、請求項2に記載のプラズマディスプレイパネルの初期起動方法。 10

【請求項 7】

第1電極、第2電極の間に放電セルが形成されるプラズマディスプレイパネルを備え、リセット期間、アドレス期間及び維持期間の間に前記第1電極及び第2電極に駆動電圧を印加する駆動回路を含み、

前記駆動回路は、前記プラズマディスプレイパネルの電源がオンする時、前記第2電極に第1電圧を印加した状態で、前記第1電極の電圧を第2電圧から第3電圧まで下降させて、前記第1電極の電圧が前記第3電圧まで下降され前記放電セルに壁電荷が形成された直後に、前記第1電極と前記第2電極に交互に第4電圧を印加して前記放電セルを維持放電させるプラズマ表示装置。 20

【請求項 8】

前記リセット期間は、前記第2電極に第5電圧を印加し、前記第1電極の電圧を第6電圧から第7電圧まで下降させ、

前記第1電圧と前記第3電圧の差は、前記第5電圧と前記第7電圧の差より大きい、請求項7に記載のプラズマ表示装置。

【請求項 9】

前記第4電圧は、前記維持期間で前記第1電極に印加される維持放電電圧と同一である、請求項7或いは8に記載のプラズマ表示装置。

【発明の詳細な説明】 30

【技術分野】

【0001】

本発明はプラズマディスプレイパネル(PDP)の初期起動方法に関する。

【背景技術】

【0002】

プラズマディスプレイパネルは気体放電によって生成されたプラズマを利用して文字または映像を表示する平面表示装置であって、その大きさによって数十から数百万個以上の画素がマトリックス形態で配列されている。このようなプラズマ表示パネルは印加される駆動電圧波形の形態と放電セルの構造によって直流形と交流形に区分される。

【0003】 40

直流形プラズマ表示パネルは電極が放電空間にそのまま露出されていて電圧が印加される間に電流が放電空間にそのまま流れため、電流制限のための抵抗を作らなければならぬ短所がある。これに反し、交流形プラズマ表示パネルでは電極を誘電体層が覆っていて自然なキャパシタンス成分の形成で電流が制限され、放電時イオンの衝撃から電極が保護されるので直流形に比べて寿命が長いという長所がある。

【0004】

このような交流形プラズマ表示パネルにはその一面に互いに平行な走査電極及び維持電極が形成され、他の面にこれら電極と直交する方向にアドレス電極が形成される。そして維持電極は各走査電極に対応して形成され、その一端が互いに共通に連結されている。

【0005】 50

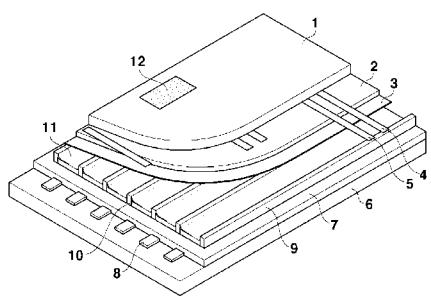

図1は一般的な交流形プラズマディスプレイパネルの一部斜視図である。

【0006】

図1に示したように、プラズマディスプレイパネルは互いに対向して離れている二つのガラス基板1、6を含む。ガラス基板1上には走査電極4と維持電極5が対をなして平行に形成されており、走査電極4と維持電極5は誘電体層2及び保護膜3で覆われている。

ガラス基板6上には複数のアドレス電極8が形成されており、アドレス電極8は絶縁体層7で覆われている。アドレス電極8の間にある絶縁体層7上にはアドレス電極8と隔壁9が形成されている。また、絶縁体層7の表面及び隔壁9の両側面に蛍光体10が形成されている。ガラス基板1、6は走査電極4とアドレス電極8及び維持電極5とアドレス電極8が直交するように放電空間11を間に置いて対向して配置されている。アドレス電極8と、対をなす走査電極4と維持電極5との交差部にある放電空間11が放電セル12を形成する。

【0007】

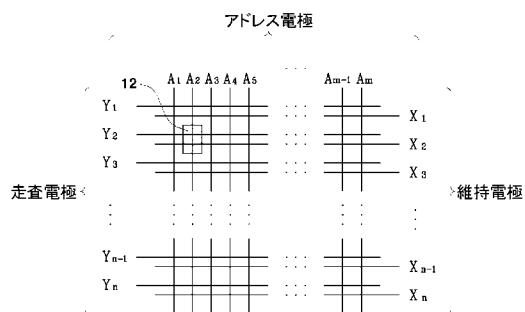

図2はプラズマ表示パネルの電極配列図を示す。

【0008】

図2に示したように、プラズマ表示パネルの電極は $n \times m$ のマトリックス形態を有しており、具体的に列方向にはアドレス電極 $A_1 \sim A_m$ が伸びていて、行方向には走査電極 $Y_1 \sim Y_n$ 及び維持電極 $X_1 \sim X_n$ が伸びている。図2に示された放電セル12は図1に示された放電セル12に対応する。

【0009】

一般にこのような交流形プラズマディスプレイパネルは1フレームが複数のサブフィールドに分けられて駆動され、サブフィールドの組み合わせによって階調が表現される。

【0010】

そして交流形プラズマディスプレイパネルの駆動方法を時間的な動作変化で表現すれば、各サブフィールドはリセット期間、アドレス期間、維持期間からなる。

【0011】

リセット期間は直前の維持放電で形成された壁電荷を消去し、次のアドレス放電を安定的に行うために壁電荷を初期化する期間であり、アドレス期間はパネルで点灯されるセルと点灯されないセルを選択して点灯されるセル（アドレッシングされたセル）に壁電荷を積む動作を行う期間である。そして維持期間はアドレッシングされたセルに実際に画像を表示するための維持放電を行う期間である。

【0012】

一方、リセット期間は初期化対象となるセルに対して放電が発生するように各電極間に十分に高い電圧を印加するが、全セルの壁電荷状態を均一に制御するために弱放電が発生するように電圧を印加する。そしてリセット期間はアドレス期間がなければ維持期間で放電が発生しないように壁電荷を制御する。

【0013】

しかし、パネル内電極に電圧を印加しないオフ状態から電源をオンする場合または電源をオフしてセル内の壁電荷状態がよく定義されていない状態で再び電源をオンする場合は、パネルの初期起動（パワーオン）時に数秒程度は低レベル放電をすることがある。

【0014】

また、明暗比や回路費用節減などの理由でリセット期間に印加する電圧の大きさを小さくした場合、初期起動時に瞬間的に低レベル放電をすることもある。

【0015】

プラズマディスプレイパネルにおける低レベル放電は、放電が正常に維持されないことを意味する。このような低レベル放電はセル内のプライミング粒子の不足やリセット期間によって制御できない壁電荷構造などによって、アドレス期間でのアドレス放電がよく行われないために発生する。

【0016】

アドレス放電は、スキャンパルスとアドレスパルスが同時に印加される2～3μs内外

10

20

30

40

50

の短い電圧印加の瞬間に放電が形成されなければならない。しかし、セル内にプライミング粒子が不足する場合には放電が容易に形成されない。このような理由で長時間オフ状態を維持したパネルの初期起動時に、長い場合には数秒間も継続する低レベル放電をする確率が高い。そして電源オフ時に壁電荷状態が予測不可能になった後、直ちに再起動しても、パネルオフ時に形成された壁電荷状態を、リセット期間に初期化することができないため低レベル放電が発生する。

#### 【0017】

このような低レベル放電を除去するために、従来は、非常に高い電圧を交互に印加する初期起動波形を使用した。しかし、このような初期起動波形により初期放電を行う場合、過度に強い放電が発生して回路にストレスを与えたり、そのための電源及び回路を備える費用が上昇する問題点がある。10

#### 【発明の開示】

##### 【発明が解決しようとする課題】

#### 【0018】

本発明が目的とする技術的課題はこのような従来の問題点を解決するためのものであって、プラズマディスプレイパネルの初期起動時に低レベル放電を除去できる初期起動方法を提供することである。

#### 【課題を解決するための手段】

#### 【0019】

このような課題を解決するために本発明の一つの特徴によると、第1電極、第2電極によって放電セルが形成されるプラズマディスプレイパネルの電源がオンする時に操作される初期起動方法が提供される。この駆動方法はa)前記第1電極の電圧を第1電圧から第2電圧まで上昇させ、前記第2電極に第3電圧が印加される間に前記第1電極の電圧を第4電圧から第5電圧まで下降させて前記放電セルに壁電荷を形成する段階；及びb)前記放電セルの第1電極と第2電極との間の電圧差が交互に第6電圧または前記第6電圧の値で極性が負の電圧になるように前記第1電極と前記第2電極に電圧を印加して前記放電セルを放電させる段階を含む。20

#### 【0020】

そして、入力される画像信号によってプラズマディスプレイパネルを駆動する場合に、サブフィールドはリセット期間、アドレス期間及び維持期間を含み、前記リセット期間は、前記第2電極に第7電圧を印加し、前記第1電極の電圧を第8電圧から第9電圧まで下降させる段階を含み、前記第3電圧と前記第5電圧の差は前記第7電圧と前記第9電圧の差より大きくする。この時、前記第3電圧は前記第7電圧より大きくすることができ、前記第5電圧は前記第9電圧より小さくすることもできる。そして前記第3電圧は、前記第1電極と第2電極との間の電圧差を前記第6電圧にするために前記第2電極に印加される電圧と同一にするすることもできる。30

#### 【0021】

そして本発明の他の特徴によると、第1電極、第2電極の間に放電セルが形成されるプラズマディスプレイパネル、そしてリセット期間、アドレス期間及び維持期間の間に前記第1電極及び第2電極に駆動電圧を印加する駆動回路を含み、前記駆動回路は前記プラズマディスプレイパネルの電源をオンにする時、前記第2電極に第1電圧を印加し、前記第1電極の電圧を第2電圧から第3電圧まで下降させた後、前記第1電極と前記第2電極に交互に第4電圧を印加する。この時、前記第4電圧は、前記維持期間で前記第1電極に印加される維持放電電圧と同一であり得る。40

#### 【発明の効果】

#### 【0022】

本発明によれば、リセット期間で急激な電圧変動を防止して電流ピーク、素子ストレス、EMI及びノイズを減少させて回路動作の安定性及び信頼性を向上させることができる。

#### 【発明を実施するための最良の形態】

10

20

30

40

50

**【0023】**

以下、添付した図面を参照して本発明の実施例について本発明の属する技術分野における通常の知識を有する者が容易に実施することができるように詳細に説明する。しかし、本発明は多様で相異なる形態で実現することができ、ここで説明する実施例に限定されない。図面で本発明を明確に説明するために説明と関係ない部分は省略した。明細書全体にわたって類似な部分については同一な図面符号を付けた。

**【0024】**

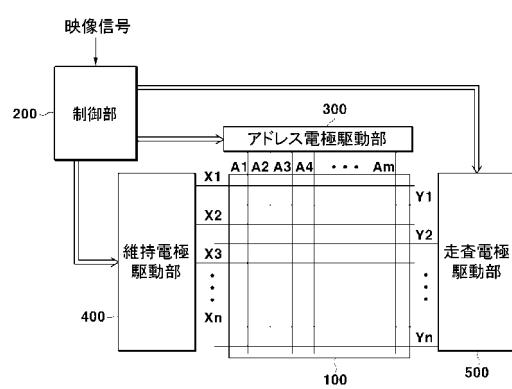

図3は本発明の実施例によるプラズマディスプレイパネルを示す図面である。

**【0025】**

図3に示したように、本発明の実施例によるプラズマディスプレイパネルはプラズマパネル100、制御部200、アドレス電極駆動部300、維持電極駆動部400及び走査電極駆動部500を含む。

10

**【0026】**

プラズマパネル100は列方向に長く配列されている複数のアドレス電極A<sub>1</sub>～A<sub>m</sub>、行方向に長く配列されている複数の維持電極X<sub>1</sub>～X<sub>n</sub>及び走査電極Y<sub>1</sub>～Y<sub>n</sub>を含む。

**【0027】**

制御部200は外部から映像信号を受信してアドレス駆動制御信号、維持電極X駆動制御信号及び走査電極Y駆動制御信号を出力する。

**【0028】**

アドレス電極駆動部300は制御部200からアドレス駆動制御信号を受信して表示しようとする放電セルを選択するための表示データ信号を各アドレス電極に印加する。

20

**【0029】**

維持電極駆動部400は制御部200から維持電極X駆動制御信号を受信して維持電極Xに駆動電圧を印加する。

**【0030】**

走査電極駆動部500は制御部200から走査電極Y駆動制御信号を受信して走査電極Yに駆動電圧を印加する。

**【0031】**

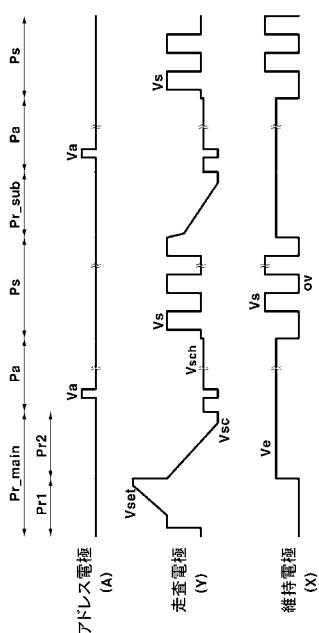

図4は本発明の第1実施例によるプラズマディスプレイパネルの駆動波形図である。

**【0032】**

図4に示したようなプラズマディスプレイパネルの駆動波形は、一般的に、一つのフレーム期間を複数のサブフィールド期間に分け、更に、各サブフィールドをリセット期間P<sub>r</sub>、アドレス期間P<sub>a</sub>及び維持期間P<sub>s</sub>に分ける。そしてリセット期間は、上昇ランプ期間P<sub>r1</sub>及び下降ランプ期間P<sub>r2</sub>に分けられる。

30

**【0033】**

リセット期間P<sub>r</sub>の上昇ランプ期間P<sub>r1</sub>は走査電極Y、維持電極X及びアドレス電極Aに壁電荷を形成する期間であり、下降ランプ期間P<sub>r2</sub>は上昇ランプ期間P<sub>r1</sub>で形成された壁電荷を一部消去してアドレス放電を容易にする期間である。そしてアドレス期間P<sub>a</sub>は複数の放電セルの中で維持期間で維持放電を起こす放電セルを選択する期間であり、維持期間P<sub>s</sub>は走査電極Yと維持電極Xに順次に維持パルスを印加してアドレス期間P<sub>a</sub>より選択された放電セルを維持放電させる期間である。

40

**【0034】**

そしてプラズマディスプレイパネルには各期間P<sub>r</sub>、P<sub>a</sub>、P<sub>s</sub>で走査電極Y及び維持電極Xに駆動電圧を印加する走査/維持駆動回路、そしてアドレス電極Aに駆動電圧を印加するアドレス駆動回路が連結されて一つの表示装置を構成する。

**【0035】**

図4に示すように、リセット期間P<sub>r</sub>の上昇ランプ期間P<sub>r1</sub>ではアドレス電極A及び維持電極Xを零ボルトに維持し、走査電極YにV<sub>s</sub>電圧からV<sub>set</sub>電圧までながらかに上昇するランプ電圧を印加する。このランプ電圧が上昇する間に全ての放電セルでは走査電極Yからアドレス電極A及び維持電極Xに各々微弱なりセット放電が起こる。その結果

50

、走査電極Yの絶縁層上に( - )壁電荷が形成され、同時にアドレス電極A及び維持電極Xの絶縁層上には( + )壁電荷が形成される。

#### 【0036】

ここで、壁電荷とは各電極を覆う絶縁性の壁(例えば、誘電体層)に形成されて蓄積される電荷のことを言う。このような壁電荷は、実際に電極自身に蓄積されることはないが、以下では、壁電荷が電極に“形成される”、“蓄積される”または“積まれる”的ように説明される。また、壁電圧とは壁電荷によって、放電セルの電極と壁表面との間に形成される電位差のことを言う。

#### 【0037】

リセット期間 $P_r$ の下降ランプ期間 $P_{r_2}$ では、維持電極Xを正の一定電圧 $V_e$ に維持した状態で、走査電極Yには、正の $V_s$ 電圧から負の $V_{s_c}$ 電圧に向かってなだらかに下降するランプ電圧を印加する。そして放電セルにおける放電開示電圧を $V_f$ 電圧とした時、このランプ電圧が下降する間に走査電極Xとアドレス電極Yに各々負の電荷と正の電荷が積まれていて、一定量の壁電圧が形成されていれば、全ての放電セルにおいて、走査電極Yに印加される電圧がなだらかに正から負に向かって変化する間に、走査電極Y及び維持電極Xに印加された電圧と壁電圧との差が放電開示電圧 $V_f$ を超える場合に再び全ての放電セルでは微弱なりセット放電が発生して壁電荷が消去される。一般に $V_e - V_{s_c}$ 電圧を維持電極Xと走査電極Yとの間の放電開示電圧まで印加して維持電極Xと走査電極Yとの間の壁電圧をほとんど零ボルトに設定する。10

#### 【0038】

そしてアドレス期間 $P_a$ では、維持電極Xと異なる走査電極Yを各々 $V_e$ 電圧と $V_{s_c}$ 電圧に維持した状態で走査電極Yに順次に $V_{s_c}$ 電圧を印加して走査電極Yを選択する。そして負の $V_{s_c}$ 電圧が印加された走査電極Yによって形成される放電セルのうちの選択しようとする放電セルを形成するアドレス電極Aにアドレス電圧 $V_a$ を印加する。その結果、アドレス電極Aに印加された電圧 $V_a$ と走査電極Yに印加された電圧 $V_{s_c}$ の差及びアドレス電極A及び走査電極Yに形成された壁電荷による壁電圧によってアドレス電極Aと走査電極Yとの間及び維持電極Xと走査電極Yとの間でアドレス放電が起こる。その結果、走査電極Yには( + )壁電荷が形成され、維持電極Xには( - )壁電荷が形成される。20

#### 【0039】

次に、維持期間 $P_s$ では走査電極Yと維持電極Xに順次に維持パルスが印加される。維持パルスは走査電極Yと維持電極Xの電圧差が交互に $V_s$ 電圧及び $-V_s$ 電圧になるようにするパルスである。 $V_s$ 電圧は走査電極Yと維持電極Xとの間の放電開示電圧より低い電圧である。アドレス期間 $P_a$ でアドレス放電によって走査電極Yと維持電極Xとの間に壁電圧が形成されれば、壁電圧と $V_s$ 電圧によって走査電極Yと維持電極Xで放電が起こる。30

#### 【0040】

一方、図4では一つのフレームを形成する複数のサブフィールドのうちの第1サブフィールドには主リセット期間 $P_{r_main}$ が形成されており、その後のサブフィールドには副リセット期間 $P_{r_sub}$ が形成されている。40

#### 【0041】

第1サブフィールドのリセット期間である主リセット期間 $P_{r_main}$ では上昇ランプ波形が印加された後、下降ランプ波形が印加される。そして2番目以後のサブフィールドリセット期間である副リセット期間 $P_{r_sub}$ では下降ランプ波形のみが印加される。

#### 【0042】

一般にリセット期間で放電セルに多量の壁電荷を形成するために前述のように走査電極Yに上昇ランプ波形を印加する。しかし、2番目以降のサブフィールドでは直前サブフィールドの維持期間で発光した放電セルには維持放電によって既に多量の壁電荷が形成されているので、リセット期間で壁電荷を形成する必要がない。また、維持期間で発光しない50

放電セルにはリセット期間で形成された壁電荷状態が変更されなかったために、次のサブフィールドでは再びリセット動作を行わなくてもよい。そしてこの状態で走査電極Yに下降ランプ波形のみ印加すれば放電が起こらないので放電セルはリセットされた状態を維持する。そして図4では1フレームを基準にして第1サブフィールドにのみ主リセット期間 $P_{r\_main}$ を置いたが、これとは異なって他のサブフィールドにも主リセット期間 $P_{r\_main}$ を置くことができる。

#### 【0043】

本発明の実施例では図4のような駆動波形になるように駆動させるためにプラズマディスプレイパネルのパワーをオンする時に発生する可能性がある低レベル放電を除去できる初期起動波形を挿入する。

10

#### 【0044】

以下、図5を参照して本発明の実施例によるプラズマディスプレイパネルの初期起動波形について詳細に説明する。

#### 【0045】

図5は本発明の実施例によるプラズマディスプレイパネルの初期起動波形を示した図面である。

#### 【0046】

図5に示したように、本発明の実施例によるプラズマディスプレイパネルの初期起動波形は全セル壁電荷形成期間 $P_{rr}$ 及び全セル放電期間 $P_{ss}$ を含む。

#### 【0047】

全セル壁電荷形成期間 $P_{rr}$ は維持期間で維持放電を起こす放全セルを選択するアドレス期間がなくても全セル放電期間 $P_{ss}$ で維持パルス印加によって全セルに放電が発生できるように壁電荷を形成する期間であり、全セル放電期間 $P_{ss}$ は走査電極Yと維持電極Xに順次に維持パルスを印加して全セルを放電させる期間である。

20

#### 【0048】

全セル壁電荷形成期間 $P_{rr}$ は電圧上昇期間及び電圧下降期間を含む。

#### 【0049】

全セル壁電荷形成期間 $P_{rr}$ の電圧上昇期間 $P_{rr1}$ は図4のリセット期間 $P_r$ の上昇ランプ期間 $P_{r1}$ におけるようにアドレス電極A及び維持電極Xを零ボルトに維持し、走査電極Yに $V_s$ 電圧から $V_{set}$ 電圧までなだらかに上昇するランプ電圧を印加する。このランプ電圧が上昇する間に全ての放全セルでは走査電極Yからアドレス電極A及び維持電極Xに各々微弱なリセット放電が起こる。その結果、走査電極Yに(-)壁電荷が形成され、同時に維持電極Xには(+)壁電荷が形成される。

30

#### 【0050】

そして全セル壁電荷形成期間 $P_{rr}$ の電圧下降期間 $P_{rr2}$ は維持電極Xを一定電圧である $V_e$ より高い電圧 $V_b$ に維持した状態で、走査電極Yに $V_s$ 電圧から $V_{sc}$ 電圧に向かってなだらかに下降するランプ電圧を印加する。

#### 【0051】

##### [数式1]

$$V_b - V_{sc} > V_e - V_{sc}$$

40

つまり、全セル壁電荷形成期間 $P_{rr}$ の電圧下降期間 $P_{rr2}$ では数式1のように走査電極Yと維持電極Xとの間の最終印加電圧の大きさが図4の下降ランプ期間での走査電極Yと維持電極Xとの間の最終印加電圧の大きさより大きい。一般に走査電極に印加される電圧がなだらかに減少する途中に全セル壁電荷形成期間 $P_{rr}$ において形成された壁電圧と走査電極Yと維持電極Xに印加された電圧差が放電開示電圧を超える場合には放電が起こり、走査電極Yと維持電極Xに印加された電圧差が維持電極Xと走査電極Yとの間で放電を起こすことがある放電開示電圧 $-V_f$ まで減少すれば維持電極Xと走査電極Yとの間の壁電圧はほとんど零ボルトとなる。

#### 【0052】

次に、走査電極Yと維持電極Xに印加された電圧差が $-V_f$ 電圧以下になれば、走査電

50

極Yは(+)壁電荷が形成され、同時にアドレス電極A及び維持電極Xには(-)壁電荷が形成されて壁電圧が高くなる。結局、前述した図4の駆動波形を有するアドレス期間でのアドレス放電と同一な役割を果たす。この時、 $V_b$ は $|V_b - V_{sc}|$ の大きさが全セル壁電荷形成期間以後に維持パルスを印加しても放電が起こる程度の大きさとする。

#### 【0053】

そして全セル放電期間 $P_{ss}$ では図4の駆動波形でのように走査電極Yと維持電極Xに順次に維持パルスが印加される。この時、全ての放電セルは全セル壁電荷形成期間 $P_{rr}$ で蓄積された壁電荷による壁電圧と維持パルスによる $V_s$ 電圧によって走査電極Yと維持電極Xで放電が起こる。この放電過程で全てのセル内に十分な放電プライミングが供給され、同時に全セルの壁電荷状態が制御可能な領域に存在するようになって初期低レベル放電現象が除去できる。10

#### 【0054】

そして本発明の第1実施例では電圧下降期間 $P_{rr2}$ の最終印加電圧 $|V_b - V_{sc}|$ の大きさを放電開示電圧より大きくするために維持電極Xに $V_e$ 電圧より高い $V_b$ 電圧を印加したが、これは $V_b$ 電圧を供給する別途の電源が追加されなければならない。したがって、 $V_b$ 電圧の代りに $V_s$ 電圧を印加することもできる。このようにすれば、別途の電源を追加する必要はない。

#### 【0055】

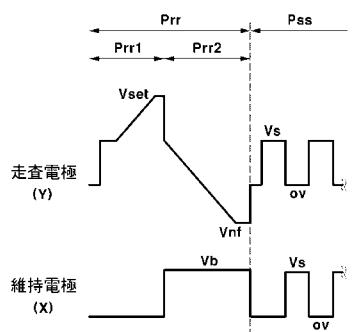

そして本発明の第1実施例では維持電極Xに印加された電圧下降期間 $P_{rr2}$ の電圧を変更して低レベル放電を除去したが、これと異なるようにすることもできる。このような実施例について図6を参照して詳細に説明する。20

#### 【0056】

図6は本発明の第2実施例によるプラズマディスプレイパネルの初期起動波形を示した図面である。

#### 【0057】

図6に示すように、本発明の第2実施例によるプラズマディスプレイパネルの初期起動波形で全セル壁電荷形成期間 $P_{rr}$ の電圧下降期間 $P_{rr2}$ では図5の電圧下降期間 $P_{rr2}$ に印加された $V_{sc}$ 電圧よりさらに低い $V_{nf}$ 電圧に向かってなだらかに下降するランプ電圧を印加する。

#### [数式2]

$$V_b - V_{nf} > V_b - V_{sc} > V_e - V_{sc}$$

つまり、電圧下降期間 $P_{rr2}$ では数式2のように走査電極Yと維持電極Xの間の最終印加電圧の大きさが図5の電圧下降期間 $P_{rr2}$ におけるより大きい。このようにすれば、図5におけるより多くの壁電荷が形成される。つまり、走査電極Yと維持電極Xに蓄積された壁電荷の消去される量が図5の駆動波形におけるより減少して直ちに維持パルスを印加しても放電が起こるようになる。

#### 【0058】

そして本発明の第2実施例とは異なって、維持電極Xに $V_e$ 電圧を印加し、走査電極Yに $V_{nf}$ 電圧を印加することもできる。

#### 【0059】

そして本発明の実施例によるプラズマディスプレイパネルの初期起動波形はパネルの電源オン時にのみ印加されるので、多様なシーケンスで構成することができる。全セル壁電荷形成期間を1回以上繰り返した後、全セル放電期間を数回以上繰り返すことができる。そしてこれとは異なって全セル壁電荷形成期間後、全セル放電期間を数回以上繰り返し、全体を再び数回以上繰り返すこともできる。このようにすれば、初期起動動作のための電源や回路を別途に備えなくても放電開示電圧より小さい維持パルスの交互印加によって安定な初期起動動作を行うことができる。

#### 【0060】

そして本発明の第1及び第2実施例では走査電極Yの電圧をランプ形態でなだらかに下降させたが、これとは異なって階段波形態で変更することもでき、パルス印加とフロー4050テ

イングの交替操作、または抵抗と静電容量による時定数設定を利用した時間によって変わる波形を印加することもできる。

#### 【0061】

以上、本発明の好ましい実施例について詳細に説明したが、本発明の権利範囲はこれに限定されず、請求範囲で定義している本発明の基本概念を利用した当業者の多様な変形及び改良形態もまた本発明の権利範囲に属する。

#### 【図面の簡単な説明】

#### 【0062】

【図1】交流形プラズマディスプレイパネルの概略的な一部斜視図である。

【図2】プラズマディスプレイパネルの電極配列図である。 10

【図3】本発明の実施例によるプラズマディスプレイパネルを示す図面である。

【図4】本発明の実施例によるプラズマディスプレイパネルの駆動波形図である。

【図5】本発明の第1実施例によるプラズマディスプレイパネルの初期起動波形を示した図面である。

【図6】本発明の第2実施例によるプラズマディスプレイパネルの初期起動波形を示した図面である。

#### 【符号の説明】

#### 【0063】

100 プラズマパネル

200 制御部

20

300 アドレス電極駆動部

400 維持電極駆動部

500 走査電極駆動部

A<sub>1</sub> ~ A<sub>m</sub> アドレス電極

X<sub>1</sub> ~ X<sub>n</sub> 維持電極

Y<sub>1</sub> ~ Y<sub>n</sub> 走査電極

P<sub>a</sub> アドレス期間

P<sub>r</sub> リセット期間

P<sub>r\_1</sub> 上昇ランプ期間

P<sub>r\_2</sub> 下降ランプ期間

30

P<sub>r\_r</sub> 全セル壁電荷形成期間

P<sub>r\_r\_2</sub> 電圧下降期間

P<sub>r\_main</sub> 主リセット期間

P<sub>r\_sub</sub> 副リセット期間

P<sub>s</sub> 維持期間

P<sub>s\_s</sub> 全セル放電期間

V<sub>a</sub> アドレス電極に印加された電圧

V<sub>s\_c</sub> 走査電極に印加された電圧

【図1】

【図2】

【図4】

【図3】

【図5】

【図6】

---

フロントページの続き

(51)Int.Cl.

F I

G 09 G 3/20 670 E

G 09 G 3/20 670 M

(72)発明者 梁 振 豪

大韓民国京畿道水原市靈通区 辛 洞575番地

(72)発明者 金 鎮 成

大韓民国京畿道水原市靈通区 辛 洞575番地

(72)発明者 金 泰 城

大韓民国京畿道水原市靈通区 辛 洞575番地

審査官 佐野 潤一

(56)参考文献 特開2002-175043 (JP, A)

特開2000-020021 (JP, A)

特開2003-131614 (JP, A)

特開2004-086076 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G 09 G 3 / 28

G 09 G 3 / 20