(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6300513号

(P6300513)

(45) 発行日 平成30年3月28日(2018.3.28)

(24) 登録日 平成30年3月9日(2018.3.9)

|               |           |

|---------------|-----------|

| (51) Int.Cl.  | F 1       |

| HO 1 L 21/822 | (2006.01) |

| HO 1 L 27/04  | (2006.01) |

| HO 1 L 29/786 | (2006.01) |

| HO 1 L 21/336 | (2006.01) |

| GO 2 F 1/1368 | (2006.01) |

| HO 1 L        | 27/04     |

| HO 1 L        | 29/78     |

| HO 1 L        | 29/78     |

| HO 1 L        | 29/78     |

| GO 2 F        | 1/1368    |

請求項の数 12 (全 102 頁) 最終頁に続く

|              |                               |

|--------------|-------------------------------|

| (21) 出願番号    | 特願2013-263874 (P2013-263874)  |

| (22) 出願日     | 平成25年12月20日(2013.12.20)       |

| (65) 公開番号    | 特開2014-143404 (P2014-143404A) |

| (43) 公開日     | 平成26年8月7日(2014.8.7)           |

| 審査請求日        | 平成28年9月28日(2016.9.28)         |

| (31) 優先権主張番号 | 特願2012-281873 (P2012-281873)  |

| (32) 優先日     | 平成24年12月25日(2012.12.25)       |

| (33) 優先権主張国  | 日本国(JP)                       |

|           |                     |

|-----------|---------------------|

| (73) 特許権者 | 000153878           |

|           | 株式会社半導体エネルギー研究所     |

|           | 神奈川県厚木市長谷398番地      |

| (72) 発明者  | 山崎 舜平               |

|           | 神奈川県厚木市長谷398番地 株式会社 |

|           | 半導体エネルギー研究所内        |

| 審査官       | 戸次 一夫               |

最終頁に続く

(54) 【発明の名称】回路、保護回路、及び表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

第1のトランジスタと、第2のトランジスタと、第3のトランジスタと、第4のトランジスタと、第1の抵抗素子と、第2の抵抗素子と、第1の配線と、第2の配線と、第3の配線と、を有し、

前記第1のトランジスタのソースまたはドレインの一方は、前記第1の配線と電気的に接続し、

前記第1のトランジスタのソースまたはドレインの他方は、前記第1のトランジスタのゲートと、前記第2のトランジスタのソースまたはドレインの一方と電気的に接続し、

前記第2のトランジスタのソースまたはドレインの他方は、前記第2のトランジスタのゲートと、前記第3の配線と電気的に接続し、

前記第1の抵抗素子の端子の一方は、前記第1の配線と電気的に接続し、

前記第1の抵抗素子の端子の他方は、前記第3の配線と電気的に接続し、

前記第3のトランジスタのソースとドレインの一方は、前記第3の配線と電気的に接続し、

前記第3のトランジスタのソースまたはドレインの他方は、前記第3のトランジスタのゲートと、前記第4のトランジスタのソースまたはドレインの一方と電気的に接続し、

前記第4のトランジスタのソースまたはドレインの他方は、前記第4のトランジスタのゲートと、前記第2の配線と電気的に接続し、

前記第2の抵抗素子の端子の一方は、前記第3の配線と電気的に接続し、

10

20

前記第2の抵抗素子の端子の他方は、前記第2の配線と電気的に接続し、

前記第1の抵抗素子は第1の酸化物半導体層を有し、

前記第2の抵抗素子は第2の酸化物半導体層を有することを特徴とする回路。

**【請求項2】**

請求項1において、

前記第1の配線は、高電源電位を与えられ、

前記第2の配線は、低電源電位を与えられることを特徴とする回路。

**【請求項3】**

請求項1または請求項2において、

前記第1のトランジスタのチャネルは、第3の酸化物半導体層を有し、 10

前記第2のトランジスタのチャネルは、第4の酸化物半導体層を有し、

前記第3のトランジスタのチャネルは、第5の酸化物半導体層を有し、

前記第4のトランジスタのチャネルは、第6の酸化物半導体層を有することを特徴とする回路。

**【請求項4】**

請求項1乃至3のいずれか一において、

前記第1の酸化物半導体層および前記第2の酸化物半導体層は、インジウム(Indium)、

亜鉛(Zinc)及びM(A1、Ga、Ge、Y、Zr、Sn、La、CeまたはHf)を有する、ことを特徴とする回路。

**【請求項5】**

請求項3または請求項4において、

前記第3乃至6の酸化物半導体層は、インジウム(Indium)、亜鉛(Zinc)及びM(A1、Ga、Ge、Y、Zr、Sn、La、CeまたはHf)を有する、ことを特徴とする回路。

**【請求項6】**

請求項1乃至5のいずれか一において、

前記回路を有する保護回路。

**【請求項7】**

駆動回路部と、画素部と、保護回路部と、を有し、

前記保護回路部は、前記画素部または前記駆動回路部のいずれか一方または双方に電気的に接続され、 30

前記保護回路部は、第1のトランジスタと、第2のトランジスタと、第3のトランジスタと、第4のトランジスタと、第1の抵抗素子と、第2の抵抗素子と、第1の配線と、第2の配線と、第3の配線と、を有し、

前記第1のトランジスタのソースまたはドレインの一方は、前記第1の配線と電気的に接続し、

前記第1のトランジスタのソースまたはドレインの他方は、前記第1のトランジスタのゲートと、前記第2のトランジスタのソースまたはドレインの一方と電気的に接続し、

前記第2のトランジスタのソースまたはドレインの他方は、前記第2のトランジスタのゲートと、前記第3の配線と電気的に接続し、 40

前記第1の抵抗素子の端子の一方は、前記第1の配線と電気的に接続し、

前記第1の抵抗素子の端子の他方は、前記第3の配線と電気的に接続し、

前記第3のトランジスタのソースとドレインの一方は、前記第3の配線と電気的に接続し、

前記第3のトランジスタのソースまたはドレインの他方は、前記第3のトランジスタのゲートと、前記第4のトランジスタのソースまたはドレインの一方と電気的に接続し、

前記第4のトランジスタのソースまたはドレインの他方は、前記第4のトランジスタのゲートと、前記第2の配線と電気的に接続し、

前記第2の抵抗素子の端子の一方は、前記第3の配線と電気的に接続し、

前記第2の抵抗素子の端子の他方は、前記第2の配線と電気的に接続し、 50

前記第1の抵抗素子は第1の酸化物半導体層を有し、

前記第2の抵抗素子は第2の酸化物半導体層を有することを特徴とする表示装置。

**【請求項8】**

請求項7において、

前記第1の配線は、高電源電位を与えられ、

前記第2の配線は、低電源電位を与えられることを特徴とする表示装置。

**【請求項9】**

請求項7または請求項8において、

前記第3の配線は、前記画素部または前記駆動回路部のいずれか一方または双方に電気的に接続されることを特徴とする表示装置。

10

**【請求項10】**

請求項7乃至9のいずれか一において、

前記第1のトランジスタのチャネルは、第3の酸化物半導体層を有し、

前記第2のトランジスタのチャネルは、第4の酸化物半導体層を有し、

前記第3のトランジスタのチャネルは、第5の酸化物半導体層を有し、

前記第4のトランジスタのチャネルは、第6の酸化物半導体層を有することを特徴とする表示装置。

**【請求項11】**

請求項7乃至10のいずれか一において、

前記第1の酸化物半導体層および前記第2の酸化物半導体層は、インジウム(Indium)、亜鉛(Zinc)及びM(A1、Ga、Ge、Y、Zr、Sn、La、CeまたはHf)を有する、ことを特徴とする表示装置。

20

**【請求項12】**

請求項10または請求項11において、

前記第3乃至6の酸化物半導体層は、インジウム(Indium)、亜鉛(Zinc)及びM(A1、Ga、Ge、Y、Zr、Sn、La、CeまたはHf)を有する、ことを特徴とする表示装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

30

本発明の一態様は、物、方法、製造方法、プロセス、マシーン、マニュファクチャー、または、組成物(コンポジションオブマター)に関する。特に、本発明の一態様は、例えば、半導体装置、表示装置、発光装置、電子機器、それらの駆動方法、または、それらの製造方法に関する。特に、本発明の一態様は、例えば、酸化物半導体を有する抵抗素子、半導体装置、表示装置、電子機器、または、発光装置に関する。

**【0002】**

なお、表示装置とは、表示素子を有する装置のことをいう。なお、表示装置は、複数の画素を駆動させる駆動回路等を含む。なお、表示装置は、別の基板上に配置された制御回路、電源回路、信号生成回路等を含む。

**【背景技術】**

**【0003】**

40

液晶表示装置に代表される表示装置は、近年の技術革新の結果、素子及び配線の微細化が進み、量産技術も各段に進歩してきている。今後はより、製造歩留まりの向上を図ることで、低コストを図ることが求められている。

**【0004】**

表示装置に静電気等によるサージ電圧が印加されると、素子が破壊してしまい、正常な表示ができなくなる。そのため、製造歩留まりが悪化するおそれがある。その対策として、表示装置には、サージ電圧を別の配線に逃がすための保護回路が設けられている(例えば特許文献1乃至7を参照)。

**【先行技術文献】**

50

**【特許文献】****【0005】**

【特許文献1】特開2010-92036号公報

【特許文献2】特開2010-92037号公報

【特許文献3】特開2010-97203号公報

【特許文献4】特開2010-97204号公報

【特許文献5】特開2010-107976号公報

【特許文献6】特開2010-107977号公報

【特許文献7】特開2010-113346号公報

**【発明の概要】**

10

**【発明が解決しようとする課題】****【0006】**

表示装置では、保護回路に代表されるように、信頼性の向上を目的とした構成が重要である。

**【0007】**

そこで、本発明の一態様では、新規な構成の抵抗素子などを提供することを課題の一とする。または信頼性を向上しうる、新規な構成の表示装置などを提供することを課題の一とする。または、本発明の一態様では、静電破壊を低減することができる、新規な構成の表示装置などを提供することを課題の一とする。または、本発明の一態様では、静電気の影響を低減することができる、新規な構成の表示装置などを提供することを課題の一とする。または、本発明の一態様では、ラビング工程において、トランジスタに与える影響を低減することができる、新規な構成の表示装置などを提供することを課題の一とする。または、本発明の一態様では、検査工程において、トランジスタに与える影響を低減することができる、新規な構成の表示装置などを提供することを課題の一とする。または、本発明の一態様では、タッチセンサを使用したときの不具合の影響を低減することができる、新規な構成の表示装置などを提供することを課題の一とする。または、本発明の一態様では、トランジスタの特性の変動または劣化を低減することができる、新規な構成の表示装置などを提供することを課題の一とする。または、本発明の一態様では、トランジスタのしきい値電圧の変動または劣化を低減することができる、新規な構成の表示装置などを提供することを課題の一とする。または、本発明の一態様では、トランジスタの製造歩留まりを向上することができる、新規な構成の表示装置などを提供することを課題の一とする。または、本発明の一態様では、導電率の向上した酸化物半導体層を有する、新規な構成の表示装置などを提供することを課題の一とする。または、本発明の一態様では、酸化物半導体層の導電率を制御することができる、新規な構成の表示装置などを提供することを課題の一とする。

20

**【0008】**

なお、これらの課題の記載は、他の課題の存在を妨げるものではない。なお、本発明の一態様は、これらの課題の全てを解決する必要はないものとする。なお、上記以外の課題は、明細書、図面、請求項などの記載から、自ずと明らかとなるものであり、明細書、図面、請求項などの記載から、上記以外の課題を抽出することが可能である。

30

**【課題を解決するための手段】****【0009】**

本発明の一態様は、半導体層と、半導体層上に形成された絶縁層と、を有し、半導体層は、少なくともインジウム(I n)、亜鉛(Z n)及びM(A l、G a、G e、Y、Z r、S n、L a、C eまたはH fの金属)を含むI n - M - Z n酸化物で表記される酸化物であり、絶縁層は、少なくとも水素を含むことを特徴とする抵抗素子である。

**【0010】**

また、本発明の他の一態様は、画素部と、画素部の外側に配置された駆動回路部と、画素部または駆動回路部のいずれか一方または双方に電気的に接続された保護回路部と、を有し、画素部は、マトリクス状に配置された画素電極と、画素電極に電気的に接続された

40

50

第1のトランジスタと、を有し、駆動回路部は、第1のトランジスタのオン状態、オフ状態を制御する第2のトランジスタと、を有し、第1のトランジスタ、及び第2のトランジスタは、チャネル形成領域に第1の酸化物半導体層を有し、保護回路部が、第1の酸化物半導体層と同一工程で形成された第2の酸化物半導体層を有し、第1の酸化物半導体層と、第2の酸化物半導体層とは、水素濃度が異なることを特徴とする表示装置である。

【発明の効果】

【0011】

本発明の一態様により、新規な構成の抵抗素子を提供できる。また、表示装置の信頼性を高めることができる。

【図面の簡単な説明】

10

【0012】

【図1】表示装置の平面模式図、及び保護回路部を説明する回路図。

【図2】抵抗素子の上面図、及び断面図を説明する図。

【図3】抵抗素子の上面図、及び断面図を説明する図。

【図4】表示装置の平面模式図、及び保護回路部を説明する回路図。

【図5】保護回路部を説明する回路図。

【図6】表示装置に用いることのできる画素回路図を説明する回路図。

【図7】表示装置の上面図を説明する図。

【図8】表示装置の上面図を説明する図。

【図9】表示装置の断面図を説明する図。

20

【図10】表示装置の作製方法を説明する断面図。

【図11】表示装置の作製方法を説明する断面図。

【図12】表示装置の作製方法を説明する断面図。

【図13】表示装置の作製方法を説明する断面図。

【図14】表示装置の作製方法を説明する断面図。

【図15】表示装置の作製方法を説明する断面図。

【図16】表示装置の作製方法を説明する断面図。

【図17】表示装置の作製方法を説明する断面図。

【図18】表示装置の作製方法を説明する断面図。

【図19】表示装置の作製方法を説明する断面図。

30

【図20】表示装置の作製方法を説明する断面図。

【図21】表示装置の作製方法を説明する断面図。

【図22】表示装置の作製方法を説明する断面図。

【図23】表示装置の作製方法を説明する断面図。

【図24】表示装置の断面図を説明する図。

【図25】表示装置の作製方法を説明する断面図。

【図26】表示装置の作製方法を説明する断面図。

【図27】表示装置の作製方法を説明する断面図。

【図28】表示装置の作製方法を説明する断面図。

【図29】表示装置の作製方法を説明する断面図。

40

【図30】表示装置の断面図を説明する図。

【図31】表示装置の作製方法を説明する断面図。

【図32】表示装置の作製方法を説明する断面図。

【図33】表示装置の作製方法を説明する断面図。

【図34】表示装置の作製方法を説明する断面図。

【図35】表示装置の作製方法を説明する断面図。

【図36】表示装置の断面図を説明する図。

【図37】表示装置の作製方法を説明する断面図。

【図38】表示装置の作製方法を説明する断面図。

【図39】表示装置の作製方法を説明する断面図。

50

- 【図40】表示装置の作製方法を説明する断面図。

- 【図41】表示装置の作製方法を説明する断面図。

- 【図42】表示装置の断面図を説明する図。

- 【図43】表示装置の断面図を説明する図。

- 【図44】表示装置の断面図を説明する図。

- 【図45】トランジスタの断面図、及び酸化物積層を説明する図。

- 【図46】成膜装置、基板加熱装置を説明する模式図。

- 【図47】D C電源によるスパッタリング装置を説明する断面図。

- 【図48】基板加熱装置を説明する断面図。

- 【図49】タッチセンサを説明する図。 10

- 【図50】タッチセンサを説明する回路図。

- 【図51】タッチセンサを説明する断面図。

- 【図52】本発明の一態様である表示装置を用いた表示モジュールを説明する図。

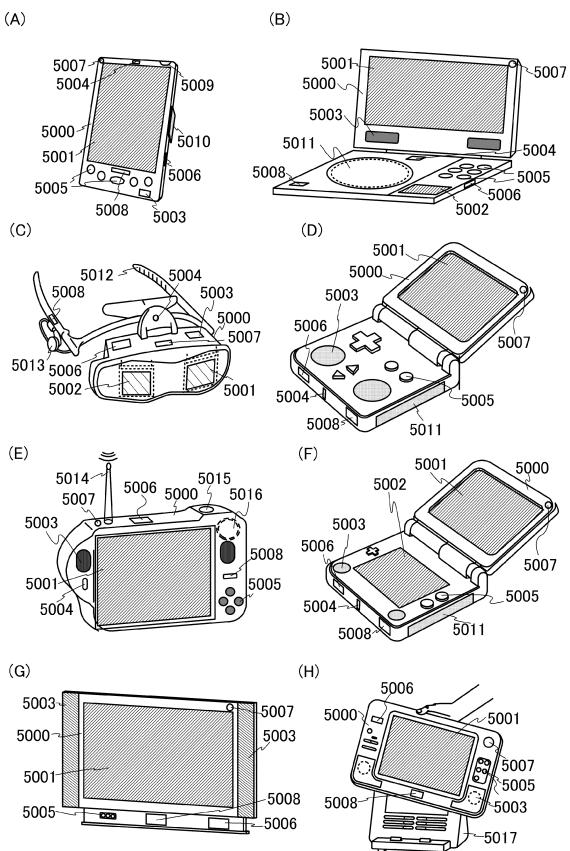

- 【図53】本発明の一態様である表示装置を用いた電子機器を説明する図。

- 【図54】本発明の一態様である表示装置を用いた電子機器を説明する図。

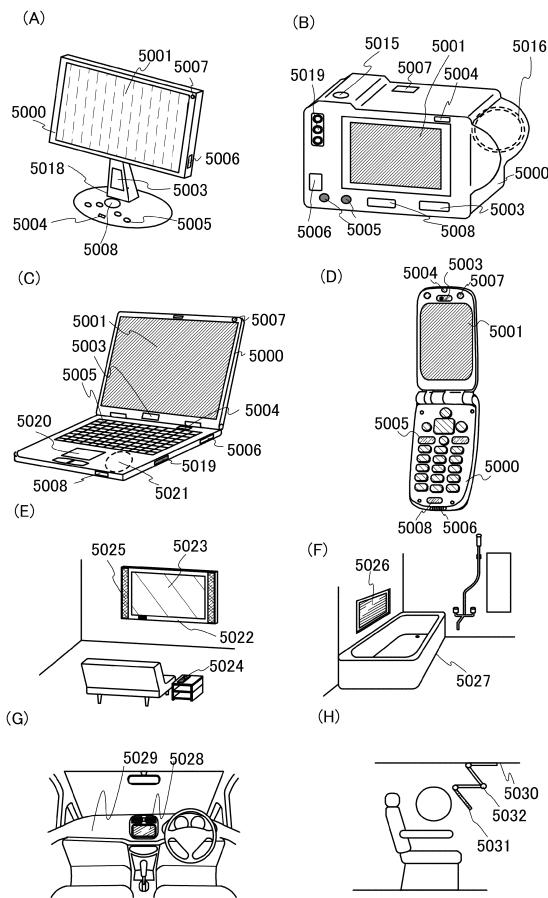

- 【図55】実施例1の試料を説明する上面図、及び断面図。

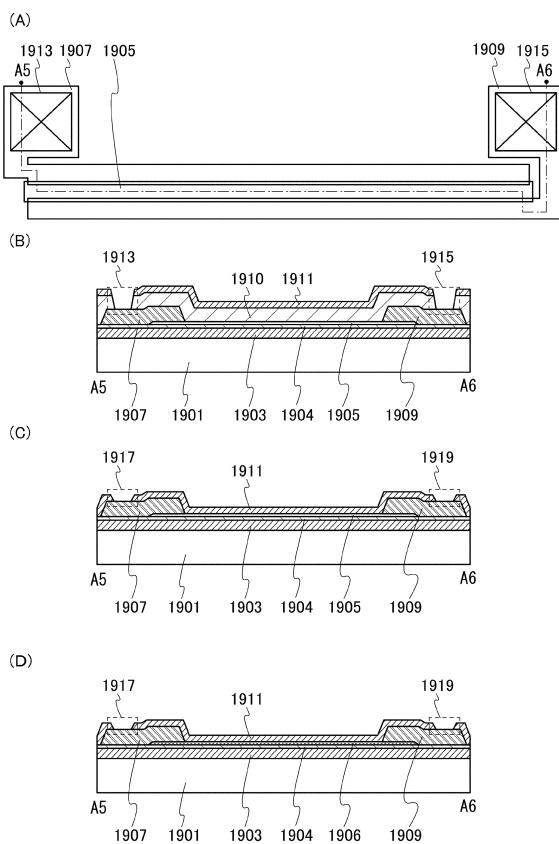

- 【図56】実施例1のシート抵抗の測定結果を説明する図。

- 【図57】実施例2の水素(H)濃度のプロファイルを説明する図。

- 【図58】実施例3のE S Rの測定結果を説明する図。 20

- 【図59】実施例3のE S Rの測定結果を説明する図。

- 【図60】酸化物半導体膜のC P M測定結果を示す図。

- 【図61】酸化物半導体膜のC P M測定結果を示す図。

- 【図62】C A A C - O S膜の断面T E M像を示す図。

- 【図63】C A A C - O S膜の電子線回折パターンを示す図。

- 【図64】C A A C - O S膜の断面T E M像を示す図。

- 【図65】C A A C - O S膜の断面T E M像およびX線回折スペクトルを示す図。

- 【図66】C A A C - O S膜の電子線回折パターンを示す図。

- 【図67】C A A C - O S膜の断面T E M像およびX線回折スペクトルを示す図。

- 【図68】C A A C - O S膜の電子線回折パターンを示す図。

- 【図69】C A A C - O S膜の断面T E M像およびX線回折スペクトルを示す図。 30

- 【図70】C A A C - O S膜の電子線回折パターンを示す図。

- 【図71】ナノ結晶酸化物半導体膜の断面T E M像及び極微電子線回折パターンを示す図。

- 【図72】ナノ結晶酸化物半導体膜の平面T E M像及び制限視野電子線回折パターンを示す図。

- 【図73】電子線回折強度分布の概念図を示す図。

- 【図74】石英ガラス基板の極微電子線回折パターンを示す図。

- 【図75】ナノ結晶酸化物半導体膜の極微電子線回折パターンを示す図。

- 【図76】ナノ結晶酸化物半導体膜の断面T E M像を示す図。

- 【図77】ナノ結晶酸化物半導体膜のX線回折分析結果を示す図。 40

- 【発明を実施するための形態】**

- 【0013】**

- 以下、実施の形態について図面を参照しながら説明する。但し、実施の形態は多くの異なる態様で実施することが可能であり、趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は、以下の実施の形態の記載内容に限定して解釈されるものではない。

- 【0014】**

- また、図面において、大きさ、層の厚さ、又は領域は、明瞭化のために誇張されている場合がある。よって、必ずしもそのスケールに限定されない。なお図面は、理想的な例を模式的に示したものであり、図面に示す形状又は値などに限定されない。例えば、ノイズ 50

による信号、電圧、若しくは電流のばらつき、又は、タイミングのずれによる信号、電圧、若しくは電流のばらつきなどを含むことが可能である。

#### 【0015】

また、本明細書等において、トランジスタとは、ゲートと、ドレインと、ソースとを含む少なくとも三つの端子を有する素子である。そして、ドレイン（ドレイン端子、ドレン領域またはドレン電極）とソース（ソース端子、ソース領域またはソース電極）の間にチャネル領域を有しており、ドレインとチャネル領域とソースとを介して電流を流すことができるものである。

#### 【0016】

ここで、ソースとドレインとは、トランジスタの構造又は動作条件等によって変わるために、それがソースまたはドレインであるかを限定することが困難である。そこで、ソースとして機能する部分、及びドレインとして機能する部分を、ソース又はドレインと呼ばず、ソースとドレインとの一方を第1電極と表記し、ソースとドレインとの他方を第2電極と表記する場合がある。10

#### 【0017】

また、本明細書にて用いる「第1」、「第2」、「第3」という序数詞は、構成要素の混同を避けるために付したものであり、数的に限定するものではないことを付記する。

#### 【0018】

また、本明細書において、AとBとが接続されている、とは、AとBとが直接接続されているものの他、電気的に接続されているものを含むものとする。ここで、AとBとが電気的に接続されているとは、AとBとの間で、何らかの電気的作用を有する対象物が存在するとき、AとBとの電気信号の授受を可能とするものをいう。20

#### 【0019】

また、本明細書において、「上に」、「下に」などの配置を示す語句は、構成同士の位置関係を、図面を参照して説明するために、便宜上用いている。また、構成同士の位置関係は、各構成を描写する方向に応じて適宜変化するものである。従って、明細書で説明した語句に限定されず、状況に応じて適切に言い換えることができる。

#### 【0020】

また、図面におけるブロック図の各回路ブロックの配置は、説明のため位置関係を特定するものであり、異なる回路ブロックで別々の機能を実現するよう示していても、実際の回路や領域においては同じ回路や同じ領域内で別々の機能を実現しうるよう設けられている場合もある。また図面におけるブロック図の各回路ブロックの機能は、説明のため機能を特定するものであり、一つの回路ブロックとして示していても、実際の回路や領域においては一つの回路ブロックで行う処理を、複数の回路ブロックで行うよう設けられている場合もある。30

#### 【0021】

また、画素とは、一つの色要素（例えばR（赤）G（緑）B（青）のいずれか1つ）の明るさを制御できる表示単位に相当するものとする。従って、カラー表示装置の場合には、カラー画像の最小表示単位は、Rの画素とGの画素とBの画素との三画素から構成されるものとする。ただし、カラー画像を表示するための色要素は、三色に限定されず、三色以上を用いても良いし、RGB以外の色を用いても良い。40

#### 【0022】

本明細書においては、本発明の実施の形態について図面を参照しながら説明する。なお各実施の形態での説明は、以下の順序で行う。

1. 実施の形態1 (本発明の一態様に関する基本構成について)

2. 実施の形態2 (表示装置の一態様について)

3. 実施の形態3 (表示装置の作製方法について)

4. 実施の形態4 (表示装置の変形例、及び作製方法について)

5. 実施の形態5 (表示装置の変形例、及び作製方法について)

6. 実施の形態6 (表示装置の変形例、及び作製方法について)

|      |          |                             |    |

|------|----------|-----------------------------|----|

| 7 .  | 実施の形態 7  | (表示装置の変形例について)              |    |

| 8 .  | 実施の形態 8  | (トランジスタの構成について)             |    |

| 9 .  | 実施の形態 9  | (酸化物半導体膜の電子線回折パターンについて)     |    |

| 10 . | 実施の形態 10 | (金属膜、半導体膜、無機絶縁膜などの成膜方法について) |    |

| 11 . | 実施の形態 11 | (酸化物半導体を成膜、及び加熱できる装置について)   |    |

| 12 . | 実施の形態 12 | (タッチセンサ、表示モジュールについて)        |    |

| 13 . | 実施の形態 13 | (電子機器について)                  |    |

| 14 . | 実施例 1    | (酸化物半導体層、酸化物積層の抵抗について)      |    |

| 15 . | 実施例 2    | (酸化物半導体層の不純物分析について)         |    |

| 16 . | 実施例 3    | (酸化物半導体膜、及び酸化物積層の ESRについて)  | 10 |

**【0023】**

(実施の形態 1)

本実施の形態では、本発明の一態様の表示装置について、図 1 乃至 図 5 を用いて説明を行う。

**【0024】**

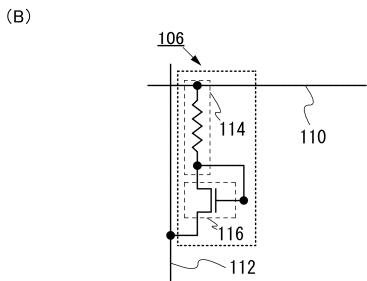

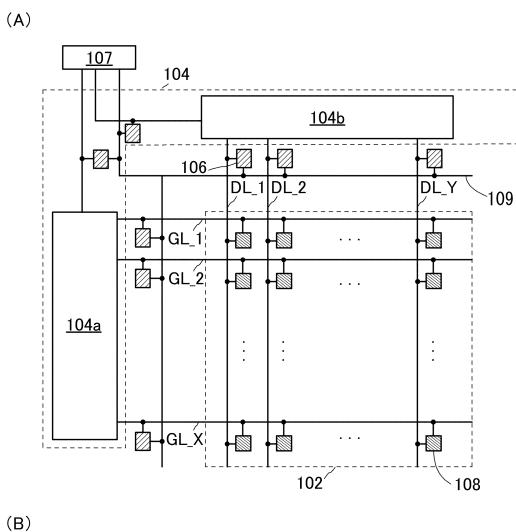

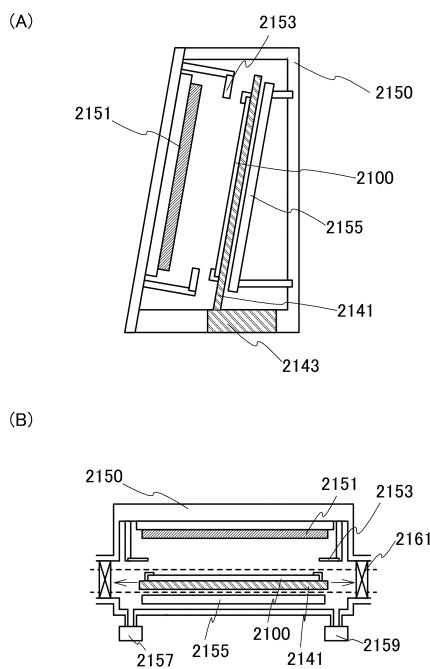

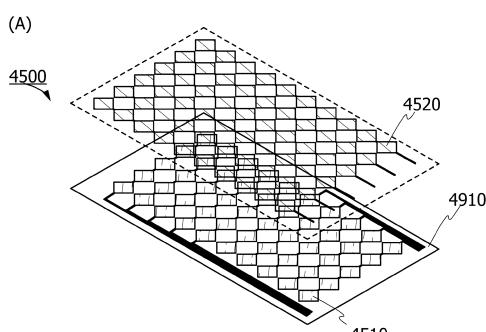

図 1 (A) に示す表示装置は、画素の表示素子を有する領域 (以下、画素部 102 という) と、画素を駆動するための回路を有する回路部 (以下、駆動回路部 104 という) と、素子の保護機能を有する回路部 (以下、保護回路部 106 という) と、端子部 107 と、を有する。

**【0025】**

画素部 102 は、X 行 (X は 2 以上の自然数) Y 列 (Y は 2 以上の自然数) に配置された複数の表示素子を駆動するための回路 (以下、画素回路部 108 という) を有し、駆動回路部 104 は、画素を選択する信号 (走査信号) を出力する回路 (以下、ゲートドライバ 104a という)、画素の表示素子を駆動するための信号 (データ信号) を供給するための回路 (以下、ソースドライバ 104b) などの駆動回路を有する。なお、画素回路部 108 は、マトリクス状に形成され、各々の画素回路部 108 には、画素電極が形成される。

**【0026】**

ゲートドライバ 104a は、シフトレジスタ等を有する。ゲートドライバ 104a は、端子部 107 を介して、シフトレジスタを駆動するための信号が入力され、信号を出力する。例えば、ゲートドライバ 104a は、スタートパルス信号、クロック信号等が入力され、パルス信号を出力する。ゲートドライバ 104a は、走査信号が与えられる配線 (以下、ゲート信号線 GL\_1 乃至 GL\_X という) の電位を制御する機能を有する。なお、ゲートドライバ 104a を複数設け、複数のゲートドライバ 104a により、ゲート信号線 GL\_1 乃至 GL\_X を分割して制御してもよい。または、ゲートドライバ 104a は、初期化信号を供給することができる機能を有する。ただし、これに限定されず、ゲートドライバ 104a は、別の信号を供給することも可能である。

**【0027】**

ソースドライバ 104b は、シフトレジスタ等を有する。ソースドライバ 104b は、端子部 107 を介して、シフトレジスタを駆動するための信号の他、データ信号の元となる信号 (画像信号) が入力される。ソースドライバ 104b は、画像信号を元に画素回路部 108 に書き込むデータ信号を生成する機能を有する。また、ソースドライバ 104b は、スタートパルス、クロック信号等が入力されて得られるパルス信号に従って、データ信号の出力を制御する機能を有する。また、ソースドライバ 104b は、データ信号が与えられる配線 (以下、データ線 DL\_1 乃至 DL\_Y という) の電位を制御する機能を有する。または、ソースドライバ 104b は、初期化信号を供給することができる機能を有する。ただし、これに限定されず、ソースドライバ 104b は、別の信号を供給することも可能である。

**【0028】**

ソースドライバ 104b は、例えば複数のアナログスイッチなどを用いて構成される。

10

20

30

40

50

ソースドライバ104bは、複数のアナログスイッチを順次オン状態にすることにより、画像信号を時分割した信号をデータ信号として出力できる。また、シフトレジスタなどを用いてソースドライバ104bを構成してもよい。

#### 【0029】

複数の画素回路部108のそれぞれは、走査信号が与えられる複数の配線（以下、ゲート信号線GLという）の一つを介してパルス信号が入力され、データ信号が与えられる複数の配線（以下、データ線DLという）の一つを介してデータ信号が入力される。また、複数の画素回路部108のそれぞれは、ゲートドライバ104aによりデータ信号のデータの書き込み及び保持が制御される。例えば、m行n列目の画素回路部108は、ゲート信号線GL\_m（mはX以下の自然数）を介してゲートドライバ104aからパルス信号が入力され、ゲート信号線GL\_mの電位に応じてデータ線DL\_n（nはY以下の自然数）を介してソースドライバ104bからデータ信号が入力される。10

#### 【0030】

保護回路部106は、ゲートドライバ104aと画素回路部108とを接続する配線であるゲート信号線GLに接続される。または、保護回路部106は、ソースドライバ104bと画素回路部108とを接続する配線であるデータ線DLに接続される。または、保護回路部106は、ゲートドライバ104aと端子部107とを接続する配線に接続することができる。または、保護回路部106は、ソースドライバ104bと端子部107とを接続する配線に接続することができる。なお、端子部107は、外部の回路から表示装置に電源及び制御信号、及び画像信号を入力するための端子が設けられた部分をいう。20

#### 【0031】

保護回路部106は、自身が接続する配線に一定の範囲外の電位が与えられたときに、該配線と別の配線とを導通状態にする回路である。ただし、これに限定されず、保護回路部106は、別の信号を供給することも可能である。

#### 【0032】

図1(A)に示すように、画素部102、駆動回路部104、端子部107のそれぞれに保護回路部106を設けることにより、ESD(Electro Static Discharge: 静電気放電)などにより発生する過電流に対する表示装置の耐性を高めることができる。ただし、保護回路部106の構成はこれに限定されず、例えば、ゲートドライバ104aにのみ保護回路部106を接続した構成、またはソースドライバ104bにのみ保護回路部106を接続した構成とすることもできる。あるいは、端子部107にのみ保護回路部106を接続した構成とすることもできる。30

#### 【0033】

すなわち、保護回路部106は、画素部102と、駆動回路部104、または端子部107のいずれか一つと電気的に接続される。

#### 【0034】

また、図1(A)においては、ゲートドライバ104aとソースドライバ104bによって駆動回路部104を形成している例を示しているが、この構成に限定されない。例えば、ゲートドライバ104aのみを形成し、別途用意されたソースドライバ回路が形成された基板（例えば、単結晶半導体膜、多結晶半導体膜で形成された駆動回路基板）を実装する構成としても良い。40

#### 【0035】

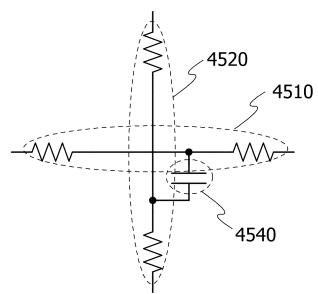

また、保護回路部106は、例えば、ダイオードと、抵抗素子と、を組み合わせた構成とすることができる。図1(B)に、具体的な保護回路部106の一例を示す。

#### 【0036】

図1(B)に示す保護回路部106は、配線110と、配線112との間に抵抗素子114と、ダイオード接続されたトランジスタ116と、を有している。

#### 【0037】

抵抗素子114は、トランジスタ116に直列に接続する構成とすることにより、トランジスタ116に流れる電流値の制御、または、トランジスタ116自身の保護抵抗とし50

て機能することができる。

#### 【0038】

また、配線 110 は、例えば、図 1 (A) に示すゲート信号線 G L やデータ線 D L、または端子部 107 から駆動回路部 104 に引き回される配線に相当する。また、配線 112 は、例えば、図 1 (A) に示すゲートドライバ 104a、またはソースドライバ 104b に電源を供給するための電源線の電位 (V DD、V SS または G ND) が与えられる配線に相当する。または、配線 112 は、共通電位 (コモン電位) が与えられる配線 (コモン線) に相当する。

#### 【0039】

配線 112 の一例としては、ゲートドライバ 104a に電源を供給するための電源線、

10 とくに低い電位を供給する配線と接続される構成が好適である。なぜなら、ゲート信号線 G L は、殆どの期間において、低い電位となっている。したがって、配線 112 の電位も低い電位となっていると、通常の動作時において、ゲート信号線 G L から配線 112 へ漏れてしまう電流を低減することが出来るからである。

#### 【0040】

ここで、保護回路部 106 に用いることのできる抵抗素子 114 の構成の一例について、図 2 及び図 3 を用いて説明を行う。

#### 【0041】

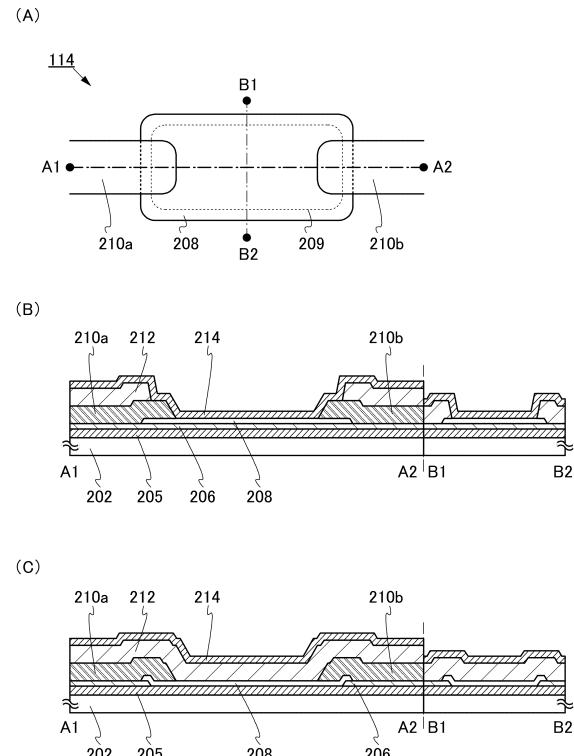

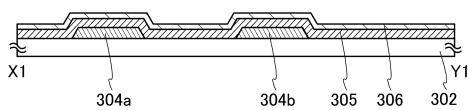

まず、図 2 に示す抵抗素子 114 について、以下説明を行う。

#### 【0042】

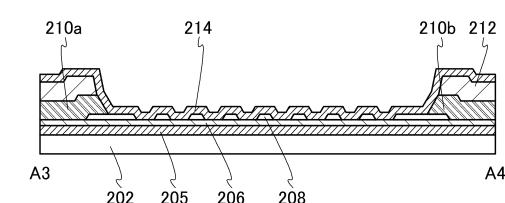

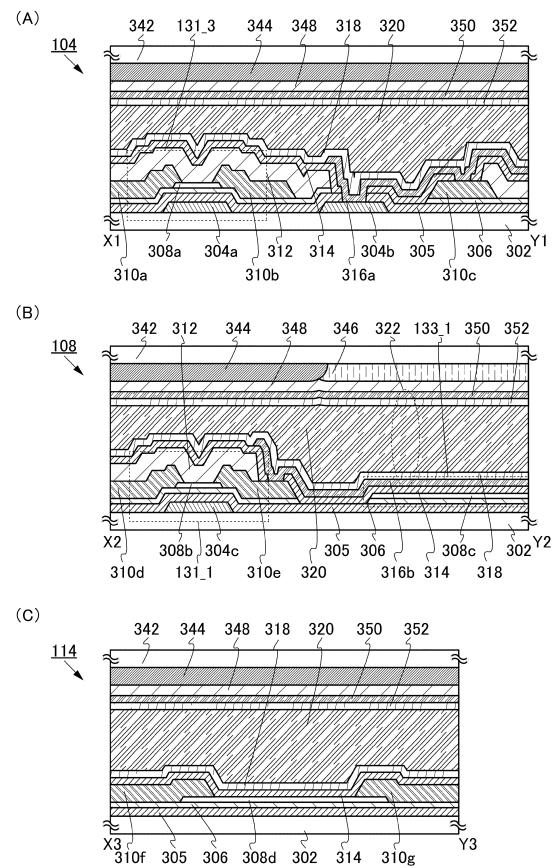

図 2 (A) は、抵抗素子 114 の上面図を示し、図 2 (B) は、図 2 (A) に示す一点鎖線 A1 - A2、及び B1 - B2 の切断面に相当する断面図を示し、図 2 (C) は、図 2 (A) に示す一点鎖線 A1 - A2、及び B1 - B2 の切断面に相当する断面図を示している。なお、図 1 (A) において、煩雑になることを避けるために、一部の構成要素を省略して図示している。

#### 【0043】

図 2 に示す抵抗素子 114 は、基板 202 と、基板 202 上の絶縁性を有する層 (以下、絶縁層 205 という) と、絶縁層 205 上の絶縁性を有する層 (以下、絶縁層 206 という) と、絶縁層 206 上の半導体層 208 と、半導体層 208 と電気的に接続された導電性を有する層 (以下、導電層 210a という) と、半導体層 208 と電気的に接続された導電性を有する層 (以下、導電層 210b という) と、導電層 210a、及び導電層 210b 上の絶縁性を有する層 (以下、絶縁層 212 という) と、絶縁層 212 上の絶縁性を有する層 (以下、絶縁層 214 という) と、を有する。

30

#### 【0044】

なお、図 2 (B) に示す抵抗素子 114 と、図 2 (C) に示す抵抗素子 114 は、絶縁層 206、及び絶縁層 212 の開口部 209 の形状が異なる。開口部 209 の形成工程の違いにより、半導体層 208 の下側、または上側と接触する絶縁層の構成を変えることができる。

#### 【0045】

より具体的には、図 2 (B) に示す抵抗素子は、絶縁層 205 と、絶縁層 205 上に形成された絶縁層 206 と、絶縁層 206 上に形成された半導体層 208 と、半導体層 208 上に形成された絶縁層 214 と、を有する。一方、図 2 (C) に示す抵抗素子は、絶縁層 205 と、絶縁層 205 上に形成された半導体層 208 と、半導体層 208 上に形成された絶縁層 212 と、絶縁層 212 上に形成された絶縁層 214 と、を有する。

40

#### 【0046】

このように、半導体層 208 の下側、または上側と接触する絶縁層の構成を変えることによって、半導体層 208 の抵抗を制御することができる。具体的には、例えば、半導体層 208 に用いる材料として、酸化物半導体を用いた場合、該酸化物半導体中の酸素欠損、または酸化物半導体中の不純物 (水素、水等) によって、酸化物半導体の抵抗を制御することができる。半導体層 208 の抵抗としては、抵抗率が好ましくは、 $1 \times 10^{-3}$

50

$\text{cm}$  以上  $1 \times 10^{-4}$   $\text{cm}$  未満、さらに好ましくは、 $1 \times 10^{-3}$   $\text{cm}$  以上  $1 \times 10^{-1}$   $\text{cm}$  未満であるとよい。

#### 【0047】

また、酸化物半導体の抵抗の制御方法としては、イオン注入法、イオンドーピング法、プラズマイマージョンイオンインプランテーション法などを用いて、水素、ボロン、リン、または窒素を酸化物半導体に注入してもよい。

#### 【0048】

例えば、絶縁層 205、214 としては、水素を含む絶縁膜、換言すると水素放出することが可能な絶縁膜、代表的には窒化シリコン膜を用いることによって、半導体層 208 に水素を供給することができる。また、窒化シリコン膜としては、窒化シリコン膜中に含まれる水素濃度が、 $1 \times 10^{22} \text{ atoms/cm}^3$  以上であると好ましい。このような絶縁層を用いることで、半導体層 208 に水素を供給することができる。半導体層 208 に水素を供給することによって、半導体層 208 は、不純物が導入され低抵抗となる。また、絶縁層 206、212 としては、酸素を含む絶縁膜、換言すると酸素を放出することが可能な絶縁膜、代表的には酸化シリコン膜、または酸化窒化シリコン膜を用いることによって、半導体層 208 に酸素を供給することができる。半導体層 208 に酸素を供給することによって、半導体層 208 は、酸素欠損が補填され高抵抗となる。

#### 【0049】

例えば、半導体層 208 としては、例えば、酸化物半導体を用いることができる。半導体層 307 に適用できる酸化物半導体は、少なくともインジウム (In)、亜鉛 (Zn) 及び M (Al, Ga, Ge, Y, Zr, Sn, La, Ce または Hf 等の金属) を含む In - M - Zn 酸化物で表記される層を含むことが好ましい。または、In と Zn の双方を含むことが好ましい。また、該酸化物半導体を用いたトランジスタの電気特性のばらつきを減らすため、それらと共に、スタビライザーを含むことが好ましい。

#### 【0050】

また、半導体層 208 としては、微結晶領域を含み、微結晶領域は、ビーム径が 5 nm 以上 10 nm 以下とした電子線回折パターンにおいて、円周状に配置された複数のスポットが観察され、且つ、ビーム径が 300 nm 以上とした電子線回折パターンにおいては、複数のスポットが観察されないと好ましい。

#### 【0051】

このように、抵抗素子 114 に酸化物半導体を用い、該酸化物半導体の上側、または下側に接する絶縁層の構造を変えることにより、該酸化物半導体の抵抗を制御することができる。したがって、抵抗素子 114 の抵抗を制御することが可能となり、新規な抵抗素子を提供することができる。

#### 【0052】

なお、抵抗素子 114 が有する、基板 202 については、抵抗素子 114 を保持できるものであれば、特に限定はない。例えば、ガラス基板等を用いることができる。また、抵抗素子 114 が有する、導電層 210a、210b については、抵抗素子と他の配線と接続、または引き回すためであればよく、導電性を有していればよい。

#### 【0053】

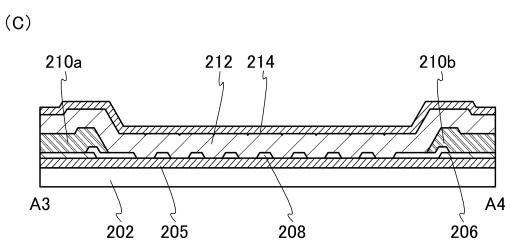

次に、図 3 に示す抵抗素子について、説明を行う。

#### 【0054】

図 3 に示す抵抗素子は、図 2 に示す抵抗素子の変形例であり、図 3(A) は、抵抗素子 114 の上面図を示し、図 3(B) は、図 3(A) に示す一点鎖線 A3 - A4 の切断面に相当する断面図を示し、図 3(C) は、図 3(A) に示す一点鎖線 A3 - A4 の切断面に相当する断面図を示している。なお、図 3(A) において、煩雑になることを避けるために、一部の構成要素を省略して図示している。

#### 【0055】

図 3 に示す抵抗素子 114 は、基板 202 と、基板 202 上の絶縁層 205 と、絶縁層 205 上の絶縁層 206 と、絶縁層 206 上の半導体層 208 と、半導体層 208 と電気

10

20

30

40

50

的に接続された導電層 210a と、半導体層 208 と電気的に接続された導電層 210b と、導電層 210a、及び導電層 210b 上の絶縁層 212 と、絶縁層 212 上の絶縁層 214 と、を有する。

#### 【0056】

なお、図 3 (B) に示す抵抗素子 114 と、図 3 (C) に示す抵抗素子 114 は、絶縁層 206、及び絶縁層 212 の開口部 209 の形状が異なる。開口部 209 の形成工程の違いにより、半導体層 208 の下側、または上側と接触する絶縁層の構成を変えることができる。

#### 【0057】

半導体層 208 の下側、または上側と接触する絶縁層の構成については、図 2 に示す抵抗素子 114 と同様である。10

#### 【0058】

図 2 に示す抵抗素子 114 と、図 3 に示す抵抗素子 114 の違いとしては、半導体層 208 の形状が異なる。図 3 に示すように半導体層 208 の形状、具体的には長さ、または幅を適宜調整することで、任意の抵抗値を有する抵抗素子とすることができます。

#### 【0059】

また、図 2 及び図 3 に示す抵抗素子 114 は、図 1 (A) に示す表示装置の駆動回路部 104、及び画素回路部 108 を構成するトランジスタの作製工程と同時に形成することができる。20

#### 【0060】

具体的には、例えば、絶縁層 205、206 は、トランジスタのゲート絶縁層と同一工程で作製することができ、半導体層 208 は、トランジスタの半導体層と同一工程で作製することができ、導電層 210a、210b は、トランジスタのソース電極層またはドレイン電極層と同一工程で作製することができ、絶縁層 212、214 は、トランジスタの保護絶縁層として機能する絶縁層と同一工程で作製することができる。

#### 【0061】

また、図 2 及び図 3 に示す抵抗素子 114 は、図 1 (B) においては、ダイオード接続されたトランジスタと直列に接続する場合において、例示したがこれに限定されず、ダイオード接続されたトランジスタと並列に接続することもできる。

#### 【0062】

また、図 2 及び図 3 に示す抵抗素子 114 は、独立して保護回路部 106 として表示装置に設けてもよい。また、図 2 及び図 3 に示す抵抗素子 114 は、複数のトランジスタと、複数の抵抗素子を組み合わせて、表示装置に設けてもよい。具体的には、図 4 に示す構成とすることができます。30

#### 【0063】

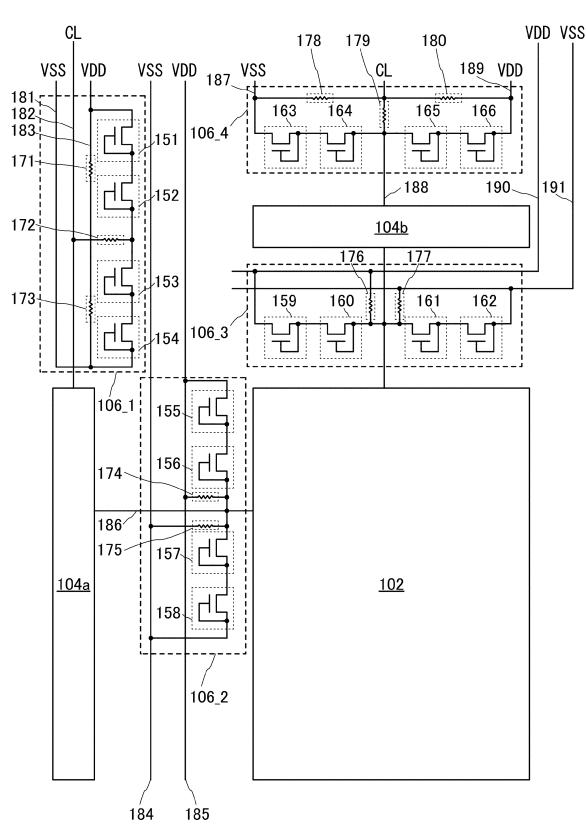

図 4 に示す表示装置は、画素部 102 と、駆動回路部として機能するゲートドライバ 104a と、ソースドライバ 104b と、保護回路部 106\_1 と、保護回路部 106\_2 と、保護回路部 106\_3 と、保護回路部 106\_4 と、を有する。

#### 【0064】

なお、画素部 102、ゲートドライバ 104a、及びソースドライバ 104b は、図 1 (A) に示す構成と同様である。40

#### 【0065】

保護回路部 106\_1 は、トランジスタ 151、152、153、154 と、抵抗素子 171、172、173 と、を有する。また、保護回路部 106\_1 は、ゲートドライバ 104a と接続される配線 181、182、183 の間に設けられる。また、トランジスタ 151 は、ソース電極としての機能を有する第 1 端子と、ゲート電極としての機能を有する第 2 端子と、が接続され、ドレイン電極としての機能を有する第 3 端子と、配線 183 と、が接続されている。トランジスタ 152 は、ソース電極としての機能を有する第 1 端子と、ゲート電極としての機能を有する第 2 端子と、が接続され、ドレイン電極としての機能を有する第 3 端子と、トランジスタ 151 の第 1 端子と、が接続されている。トランジスタ 151 の第 2 端子と、トランジスタ 152 の第 2 端子と、が接続されている。50

ンジスタ153は、ソース電極としての機能を有する第1端子と、ゲート電極としての機能を有する第2端子と、が接続され、ドレイン電極としての機能を有する第3端子と、トランジスタ152の第1端子と、が接続されている。トランジスタ154は、ソース電極としての機能を有する第1端子と、ゲート電極としての機能を有する第2端子と、が接続され、ドレイン電極としての機能を有する第3端子と、トランジスタ153の第1端子と、が接続されている。また、トランジスタ154の第1端子と、配線183及び配線181、が接続されている。また、抵抗素子171、173は、配線183に設けられている。また、抵抗素子172は、配線182と、トランジスタ152の第1端子及びトランジスタ153の第3端子との間に設けられている。

## 【0066】

10

なお、配線181は、例えば、低電源電位VSSが与えられる電源線として用いることができる。また、配線182は、例えば、コモン線として用いることができる。また、配線183は、例えば、高電源電位VDDが与えられる電源線として用いることができる。

## 【0067】

保護回路部106\_2は、トランジスタ155、156、157、158と、抵抗素子174、175と、を有する。また、保護回路部106\_2は、ゲートドライバ104aと画素部102との間に設けられる。また、トランジスタ155は、ソース電極としての機能を有する第1端子と、ゲート電極としての機能を有する第2端子と、が接続され、ドレイン電極としての機能を有する第3端子と、配線185と、が接続されている。トランジスタ156は、ソース電極としての機能を有する第1端子と、ゲート電極としての機能を有する第2端子と、が接続され、ドレイン電極としての機能を有する第3端子と、トランジスタ155の第1端子と、が接続されている。トランジスタ157は、ソース電極としての機能を有する第1端子と、ゲート電極としての機能を有する第2端子と、が接続され、ドレイン電極としての機能を有する第3端子と、トランジスタ156の第1端子と、が接続されている。トランジスタ158は、ソース電極としての機能を有する第1端子と、ゲート電極としての機能を有する第2端子と、が接続され、ドレイン電極としての機能を有する第3端子と、トランジスタ157の第1端子と、が接続されている。また、トランジスタ158の第1端子と、配線184、が接続されている。また、抵抗素子174は、配線185と、トランジスタ156の第1端子及びトランジスタ157の第3端子との間に設けられている。また、抵抗素子175は、配線184と、トランジスタ156の第1端子及びトランジスタ157の第3端子との間に設けられている。

20

## 【0068】

30

なお、配線184は、例えば、低電源電位VSSが与えられる電源線として用いることができる。また、配線185は、例えば、高電源電位VDDが与えられる電源線として用いることができる。また、配線186は、例えば、ゲート線として用いることができる。

## 【0069】

40

保護回路部106\_3は、トランジスタ159、160、161、162と、抵抗素子176、177と、を有する。また、保護回路部106\_3は、ソースドライバ104bと画素部102との間に設けられる。また、トランジスタ159は、ソース電極としての機能を有する第1端子と、ゲート電極としての機能を有する第2端子と、が接続され、ドレイン電極としての機能を有する第3端子と、配線190と、が接続されている。トランジスタ160は、ソース電極としての機能を有する第1端子と、ゲート電極としての機能を有する第2端子と、が接続され、ドレイン電極としての機能を有する第3端子と、トランジスタ159の第1端子と、が接続されている。トランジスタ161は、ソース電極としての機能を有する第1端子と、ゲート電極としての機能を有する第2端子と、が接続され、ドレイン電極としての機能を有する第3端子と、トランジスタ160の第1端子と、が接続されている。トランジスタ162は、ソース電極としての機能を有する第1端子と、ゲート電極としての機能を有する第2端子と、が接続され、ドレイン電極としての機能を有する第3端子と、トランジスタ161の第1端子と、が接続されている。また、トランジスタ162の第1端子が配線191と接続されている。また、抵抗素子176は、配

50

線 190 と、トランジスタ 160 の第 1 端子及びトランジスタ 161 の第 3 端子との間に設けられている。また、抵抗素子 177 は、配線 191 と、トランジスタ 160 の第 1 端子及びトランジスタ 161 の第 3 端子との間に設けられている。

#### 【0070】

なお、配線 188 は、例えば、コモン線またはソース線として用いることができる。また、配線 189、190 は、例えば、高電源電位 VDD が与えられる電源線として用いることができる。また、配線 191 は、例えば、低電源電位 VSS が与えられる電源線として用いることができる。

#### 【0071】

保護回路部 106\_4 は、トランジスタ 163、164、165、166 と、抵抗素子 178、179、180 と、を有する。また、保護回路部 106\_4 は、ソースドライバ 104b と接続される配線 187、188、189、190、191 の間に設けられる。また、トランジスタ 163 は、ソース電極としての機能を有する第 1 端子と、ゲート電極としての機能を有する第 2 端子と、が接続され、ドレイン電極としての機能を有する第 3 端子と、配線 187 と、が接続されている。トランジスタ 164 は、ソース電極としての機能を有する第 1 端子と、ゲート電極としての機能を有する第 2 端子と、が接続され、ドレイン電極としての機能を有する第 3 端子と、トランジスタ 163 の第 1 端子と、が接続されている。トランジスタ 165 は、ソース電極としての機能を有する第 1 端子と、ゲート電極としての機能を有する第 2 端子と、が接続され、ドレイン電極としての機能を有する第 3 端子と、トランジスタ 164 の第 1 端子と、が接続されている。トランジスタ 166 は、ソース電極としての機能を有する第 1 端子と、ゲート電極としての機能を有する第 2 端子と、が接続され、ドレイン電極としての機能を有する第 3 端子と、トランジスタ 165 の第 1 端子と、が接続されている。また、トランジスタ 166 の第 1 端子が配線 189 と接続されている。また、抵抗素子 178 は、配線 187 と、配線 188 との間に設けられている。また、抵抗素子 179 は、配線 188 に設けられ、トランジスタ 164 の第 1 端子及びトランジスタ 165 の第 3 端子と接続されている。また、抵抗素子 180 は、配線 188 と、配線 189 との間に設けられている。

#### 【0072】

また、配線 187、191 は、例えば、低電源電位 VSS が与えられる電源線として用いることができる。また、配線 188 は、例えば、コモン線またはソース線として用いることができる。また、配線 189、190 は、例えば、高電源電位 VDD が与えられる電源線として用いることができる。

#### 【0073】

なお、配線 181 乃至配線 191 は、図 4 に示す高電源電位 VDD、低電源電位 VSS、コモン線 CL に示す機能のみに限定されず、それぞれ独立してゲート信号線、信号線、電源線、接地線、容量線またはコモン線等の機能を有していても良い。

#### 【0074】

図 2 及び図 3 に示す抵抗素子 114 は、図 4 に示す抵抗素子 171 乃至抵抗素子 180 に適用することができる。

#### 【0075】

このように、保護回路部 106\_1 乃至 106\_4 は、複数のダイオード接続されたトランジスタと、複数の抵抗素子により、構成されている。すなわち、保護回路部 106\_1 乃至 106\_4 は、ダイオード接続されたトランジスタと抵抗素子を並列に組み合わせて用いることができる。

#### 【0076】

また、図 4 に示すように保護回路部 106\_1 乃至保護回路部 106\_4 は、ゲートドライバ 104a と接続される配線との間、画素部 102 とゲートドライバ 104a との間、画素部 102 とソースドライバ 104b との間、またはソースドライバ 104b と接続される配線との間に設けることができる。

#### 【0077】

10

20

30

40

50

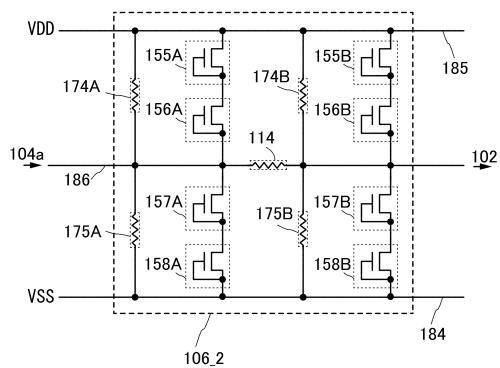

また、図2及び図3に示す抵抗素子114は、図5に示す保護回路部に用いることもできる。

#### 【0078】

図5に示す保護回路部の回路図では、トランジスタ155A、156A、157A、158A、トランジスタ155B、156B、157B、158B、抵抗素子174A、175A、抵抗素子174B、175B、抵抗素子199、配線184、配線185及び配線186を示している。なお、図5に示す回路図において付した符号は、図4で説明した保護回路部106\_2と同じ構成について、同じ符号を付して対応させている。図5に示す回路図が、図4に示した保護回路部106\_2と異なる点は、図4の保護回路部106\_2に相当する回路を並べて配置し、配線間に抵抗素子114を設けた点である。

10

#### 【0079】

また、図2及び図3に示す抵抗素子114は、図5に示す抵抗素子174A、174B、175A、175Bに適用してもよい。

#### 【0080】

このように図1(A)に示す表示装置に保護回路部106を設けることによって、画素部102(具体的には画素回路部108)、及び駆動回路部104は、ESDなどにより発生する過電流に対する耐性を高めることができる。したがって、信頼性を向上しうる新規な表示装置を提供することができる。

#### 【0081】

さらに、保護回路部106として、抵抗素子を用い、該抵抗素子の抵抗値を任意に調整できることから、保護回路部106として用いるダイオード接続されたトランジスタ等も保護することが可能となる。

20

#### 【0082】

なお、画素部102は、保護回路部106と同一基板上に形成されていることが望ましい。これにより、部品数や端子数を減らすことが出来る。さらに、駆動回路部104の一部、または全部は、一例としては、画素部102と同一基板上に形成されていることが望ましい。これにより、部品数や端子数を減らすことが出来る。駆動回路部104の一部、または全部が、画素部102と同一基板上に形成されていない場合には、駆動回路部104の一部、または全部は、COGやTABによって、実装されている場合が多い。

#### 【0083】

30

このように表示装置に複数の保護回路部106を設けることによって、画素部102、及び駆動回路部104(ゲートドライバ104a、ソースドライバ104b)は、ESDなどにより発生する過電流に対する耐性を、さらに高めることができる。したがって、信頼性を向上しうる新規な表示装置を提供することができる。

#### 【0084】

本実施の形態に示す構成は、他の実施の形態に示す構成と適宜組み合わせて用いることができる。

#### 【0085】

##### (実施の形態2)

本実施の形態では、本発明の一態様の表示装置について、図6乃至図9を用いて説明を行う。

40

#### 【0086】

図6は、図1(A)に示す表示装置の画素回路部108に用いることのできる回路構成を示している。

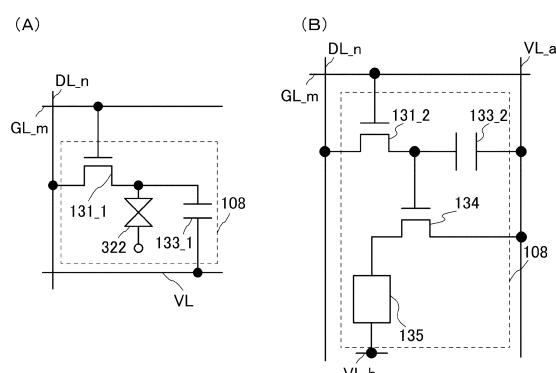

#### 【0087】

図6(A)に示す画素回路部108は、液晶素子322と、トランジスタ131\_1と、容量素子133\_1と、を有する。

#### 【0088】

液晶素子322の一対の電極の一方の電位は、画素回路部108の仕様に応じて適宜設定される。液晶素子322は、書き込まれるデータにより配向状態が設定される。なお、

50

複数の画素回路部 108 のそれぞれが有する液晶素子 322 の一対の電極の一方に共通の電位（コモン電位）を与えてよい。また、各行の画素回路部 108 每の液晶素子 322 の一対の電極の一方に異なる電位を与えてよい。

#### 【0089】

例えば、液晶素子 322 を備える表示装置の駆動方法としては、TN モード、STN モード、VA モード、ASM (Axially Symmetric Aligned Micro-cell) モード、OCB (Optically Compensated Birefringence) モード、FLC (Ferroelectric Liquid Crystal) モード、AFLC (AntiFerroelectric Liquid Crystal) モード、MVA モード、PVA (Patterned Vertical Alignment) モード、IPS モード、FFS モード、又は TBA (Transverse Bend Alignment) モードなどを用いてよい。<sup>10</sup> また、表示装置の駆動方法としては、上述した駆動方法の他、ECB (Electrically Controlled Birefringence) モード、PDLC (Polymer Dispersed Liquid Crystal) モード、PNLC (Polymer Network Liquid Crystal) モード、ゲストホストモードなどがある。ただし、これに限定されず、液晶素子及びその駆動方式として様々なものを用いることができる。

#### 【0090】

また、ブルー相 (Blue Phase) を示す液晶とカイラル剤とを含む液晶組成物により液晶素子を構成してもよい。ブルー相を示す液晶は、応答速度が 1 msec 以下と短く、光学的等方性であるため、配向処理が不要であり、視野角依存性が小さい。<sup>20</sup>

#### 【0091】

m 行 n 列目の画素回路部 108 において、トランジスタ 131\_1 のソース及びドレインの一方は、データ線 DL\_n に電気的に接続され、他方は液晶素子 322 の一対の電極の他方に電気的に接続される。また、トランジスタ 131\_1 のゲートは、ゲート信号線 GL\_m に電気的に接続される。トランジスタ 131\_1 は、オン状態又はオフ状態になることにより、データ信号のデータの書き込みを制御する機能を有する。

#### 【0092】

容量素子 133\_1 の一対の電極の一方は、電位が供給される配線（以下、電位供給線 VL）に電気的に接続され、他方は、液晶素子 322 の一対の電極の他方に電気的に接続される。なお、電位供給線 VL の電位の値は、画素回路部 108 の仕様に応じて適宜設定される。容量素子 133\_1 は、書き込まれたデータを保持する保持容量としての機能を有する。<sup>30</sup>

#### 【0093】

例えば、図 6 (A) の画素回路部 108 を有する表示装置では、ゲートドライバ 104\_a により各行の画素回路部 108 を順次選択し、トランジスタ 131\_1 をオン状態にしてデータ信号のデータを書き込む。

#### 【0094】

データが書き込まれた画素回路部 108 は、トランジスタ 131\_1 がオフ状態になることで保持状態になる。これを行毎に順次行うことにより、画像を表示できる。<sup>40</sup>

#### 【0095】

また、図 6 (B) に示す画素回路部 108 は、トランジスタ 131\_2 と、容量素子 133\_2 と、トランジスタ 134 と、発光素子 135 と、を有する。

#### 【0096】

トランジスタ 131\_2 のソース及びドレインの一方は、データ信号が与えられる配線（以下、データ線 DL\_n という）に電気的に接続される。さらに、トランジスタ 131\_2 のゲートは、ゲート信号が与えられる配線（以下、ゲート信号線 GL\_m という）に電気的に接続される。

#### 【0097】

トランジスタ 131\_2 は、オン状態またはオフ状態になることにより、データ信号のデータの書き込みを制御する機能を有する。

**【0098】**

容量素子 133\_2 の一対の電極の一方は、電源が与えられる配線（以下、電源線 VL\_a という）に電気的に接続され、他方は、トランジスタ 131\_2 のソース及びドレインの他方に電気的に接続される。

**【0099】**

容量素子 133\_2 は、書き込まれたデータを保持する保持容量としての機能を有する。

**【0100】**

トランジスタ 134 のソース及びドレインの一方は、電源線 VL\_a に電気的に接続される。さらに、トランジスタ 134 のゲートは、トランジスタ 131\_2 のソース及びドレインの他方に電気的に接続される。

**【0101】**

発光素子 135 のアノード及びカソードの一方は、電源線 VL\_b に電気的に接続され、他方は、トランジスタ 134 のソース及びドレインの他方に電気的に接続される。

**【0102】**

発光素子 135 としては、例えば有機エレクトロルミネセンス素子（有機 EL 素子ともいう）などを用いることができる。ただし、発光素子 135 としては、これに限定されず、無機材料からなる無機 EL 素子を用いても良い。

**【0103】**

なお、電源線 VL\_a 及び電源線 VL\_b の一方には、高電源電位 VDD が与えられ、他方には、低電源電位 VSS が与えられる。

**【0104】**

図 6 (B) の画素回路部 108 を有する表示装置では、ゲートドライバ 104\_a により各行の画素回路部 108 を順次選択し、トランジスタ 131\_2 をオン状態にしてデータ信号のデータを書き込む。

**【0105】**

データが書き込まれた画素回路部 108 は、トランジスタ 131\_2 がオフ状態になることで保持状態になる。さらに、書き込まれたデータ信号の電位に応じてトランジスタ 134 のソースとドレインの間に流れる電流量が制御され、発光素子 135 は、流れる電流量に応じた輝度で発光する。これを行毎に順次行うことにより、画像を表示できる。

**【0106】**

なお、本明細書等において、表示素子、表示素子を有する装置である表示装置、発光素子、及び発光素子を有する装置である発光装置は、様々な形態を用いること、又は様々な素子を有することが出来る。表示素子、表示装置、発光素子又は発光装置の一例としては、EL（エレクトロルミネッセンス）素子（有機物及び無機物を含む EL 素子、有機 EL 素子、無機 EL 素子）、LED（白色 LED、赤色 LED、緑色 LED、青色 LED など）、トランジスタ（電流に応じて発光するトランジスタ）、電子放出素子、液晶素子、電子インク、電気泳動素子、グレーティングライトバルブ（GLV）、プラズマディスプレイ（PDP）、MEMS（マイクロ・エレクトロ・メカニカル・システム）を用いた表示素子、デジタルマイクロミラーデバイス（DMD）、DMS（デジタル・マイクロ・シャッター）、IMOD（インターフェアレンス・モジュレーション）素子、圧電セラミックディスプレイ、カーボンナノチューブ、など、電気磁気的作用により、コントラスト、輝度、反射率、透過率などが変化する表示媒体を有するものがある。EL 素子を用いた表示装置の一例としては、EL ディスプレイなどがある。電子放出素子を用いた表示装置の一例としては、フィールドエミッショニングディスプレイ（FED）又は SED 方式平面型ディスプレイ（SED：Surface-conduction Electron-emitter Display）などがある。液晶素子を用いた表示装置の一例としては、液晶ディスプレイ（透過型液晶ディスプレイ、半透過型液晶ディスプレイ、反射型液晶ディス

10

20

30

40

50

プレイ、直視型液晶ディスプレイ、投射型液晶ディスプレイ)などがある。電子インク又は電気泳動素子を用いた表示装置の一例としては、電子ペーパーなどがある。

#### 【0107】

E L 素子の一例としては、陽極と、陰極と、陽極と陰極との間に挟まれたE L 層と、を有する素子などがある。E L 層の一例としては、1重項励起子からの発光(蛍光)を利用するもの、3重項励起子からの発光(燐光)を利用するもの、1重項励起子からの発光(蛍光)を利用するものと3重項励起子からの発光(燐光)を利用するものとを含むもの、有機物によって形成されたもの、無機物によって形成されたもの、有機物によって形成されたものと無機物によって形成されたものとを含むもの、高分子の材料の材料を含むもの、低分子の材料の材料を含むもの、又は高分子の材料と低分子の材料とを含むもの、などがある。ただし、これに限定されず、E L 素子として様々なものを用いることができる。10

#### 【0108】

液晶素子の一例としては、液晶の光学的変調作用によって光の透過又は非透過を制御する素子がある。その素子は一対の電極と液晶層により構造されることが可能である。なお、液晶の光学的変調作用は、液晶にかかる電界(横方向の電界、縦方向の電界又は斜め方向の電界を含む)によって制御される。なお、具体的には、液晶素子の一例としては、ネマチック液晶、コレステリック液晶、スマートチック液晶、ディスコチック液晶、サーモトロピック液晶、リオトロピック液晶、低分子液晶、高分子液晶、高分子分散型液晶(PDLC)、強誘電液晶、反強誘電液晶、主鎖型液晶、側鎖型高分子液晶、バナナ型液晶などを挙げることができる。20

#### 【0109】

電子ペーパーの表示方法の一例としては、分子により表示されるもの(光学異方性、染料分子配向など)、粒子により表示されるもの(電気泳動、粒子移動、粒子回転、相変化など)、フィルムの一端が移動することにより表示されるもの、分子の発色/相変化により表示されるもの、分子の光吸収により表示されるもの、又は電子とホールが結合して自発光により表示されるものなどを用いることができる。具体的には、電子ペーパーの表示方法の一例としては、マイクロカプセル型電気泳動、水平移動型電気泳動、垂直移動型電気泳動、球状ツイストボール、磁気ツイストボール、円柱ツイストボール方式、帯電トナー、電子粉流体、磁気泳動型、磁気感熱式、エレクトロウェッティング、光散乱(透明/白濁変化)、コレステリック液晶/光導電層、コレステリック液晶、双安定性ネマチック液晶、強誘電性液晶、2色性色素・液晶分散型、可動フィルム、ロイコ染料による発消色、フォトクロミック、エレクトロクロミック、エレクトロデポジション、フレキシブル有機E L などがある。ただし、これに限定されず、電子ペーパー及びその表示方法として様々なものを用いることができる。ここで、マイクロカプセル型電気泳動を用いることによって、泳動粒子の凝集、沈殿を解決することができる。電子粉流体は、高速応答性、高反射率、広視野角、低消費電力、メモリ性などのメリットを有する。30

#### 【0110】

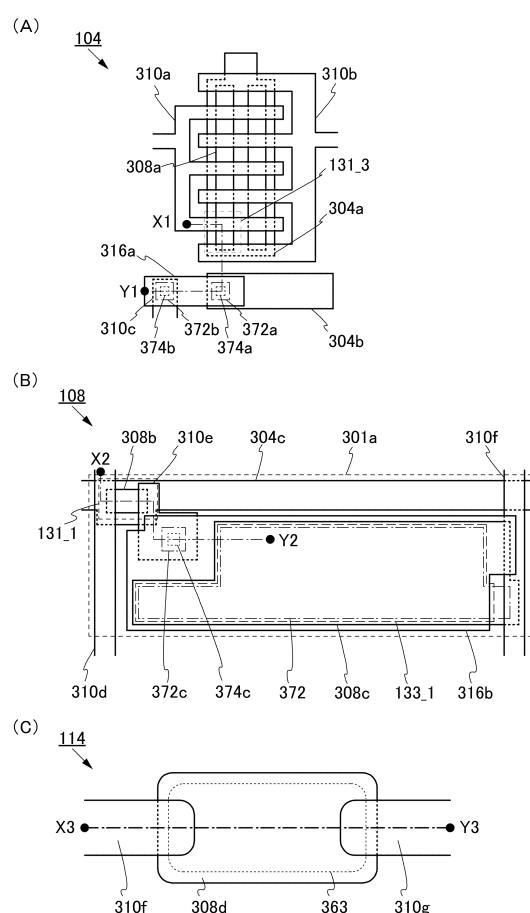

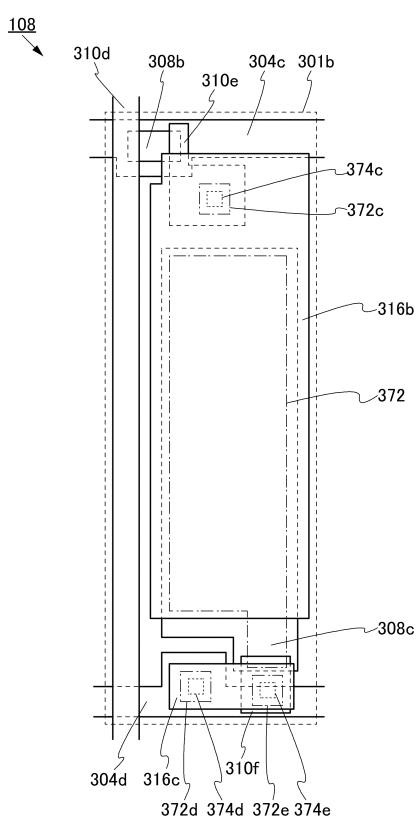

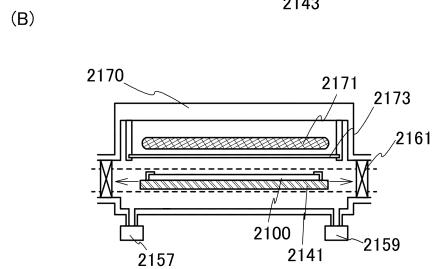

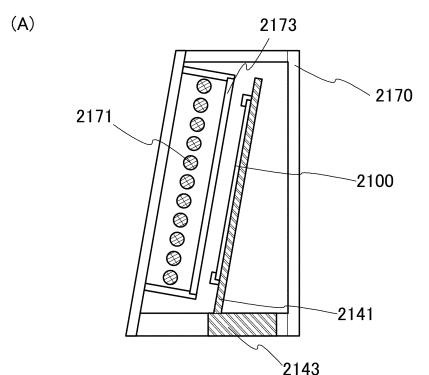

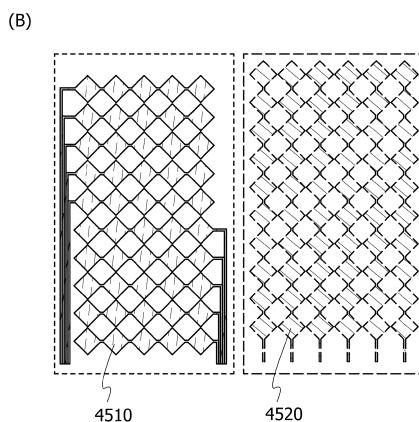

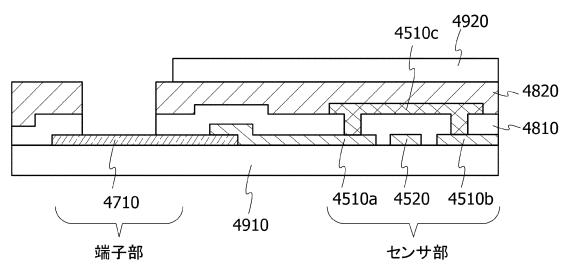

次に、図7に示す表示装置について、以下説明を行う。

#### 【0111】

図7に示す表示装置は、図1(A)に示す表示装置を、より具体的に表しており、駆動回路部104と、画素回路部108と、抵抗素子114と、を有する。なお、本実施の形態に示す表示装置は、液晶素子を用いる表示装置(液晶表示装置ともいう)の構成について説明を行う。また、画素回路部108に用いる構成は、図6(A)に示す回路構成と同様の機能を有する部分については、図6(A)に示す符号と同一の符号にて説明を行う。40

#### 【0112】

なお、図7(A)は、駆動回路部104の上面図を、図7(B)は、画素部102の上面図を、図7(C)は、抵抗素子114の上面図を、それぞれ表している。なお、図7(A)、(B)、(C)においては、図面の煩雑を避けるため、液晶素子等の一部の構成要素の記載を省略して図示している。

#### 【0113】

10

20

30

40

50

図7(A)において、ゲートとして機能する導電層304a、ゲート絶縁層(図7(A)に図示せず。)、チャネル領域が形成される半導体層308a、ソース及びドレインとして機能する導電層310a、310bによりトランジスタ131\_3を構成する。半導体層308aは、ゲート絶縁層上に設けられる。また、導電層304aと同時に形成された導電層304bと、導電層310a、310bと同時に形成された導電層310cと、導電層304b及び導電層310cを接続する透光性を有する導電層316aが設けられる。透光性を有する導電層316aは、開口部372a、374aにおいて導電層304bと接続し、開口部372b、374bにおいて導電層310cと接続する。

#### 【0114】

図7(B)において、ゲート信号線として機能する導電層304cは、信号線に略直交する方向(図中左右方向)に延伸して設けられている。信号線として機能する導電層310dは、ゲート信号線に略直交する方向(図中上下方向)に延伸して設けられている。容量線として機能する導電層310fは、信号線と平行方向に延伸して設けられている。なお、ゲート信号線として機能する導電層304cは、ゲートドライバ104a(図1(A)を参照。)と電気的に接続されており、信号線として機能する導電層310d及び容量線として機能する導電層310fは、ソースドライバ104b(図1(A)を参照。)に電気的に接続されている。

#### 【0115】

また、図7(B)において、トランジスタ131\_1は、ゲート信号線及び信号線が交差する領域に設けられている。トランジスタ131\_1は、ゲートとして機能する導電層304c、ゲート絶縁層(図7(B)に図示せず。)、ゲート絶縁層上に形成されたチャネル領域が形成される半導体層308b、ソース及びドレインとして機能する導電層310d、310eによりトランジスタを構成する。なお、導電層304cは、ゲート信号線としても機能し、半導体層308bと重畳する領域がトランジスタ131\_1のゲートとして機能する。また、導電層310dは、信号線としても機能し、半導体層308bと重畳する領域がトランジスタ131\_1のソースまたはドレインとして機能する。

#### 【0116】

また、図7(B)において、ゲート信号線は、上面形状において端部が半導体層308bの端部より外側に位置する。このため、ゲート信号線はバックライトなどの光源からの光を遮る遮光膜として機能する。この結果、トランジスタに含まれる半導体層308bに光が照射されず、トランジスタの電気特性の変動を抑制することができる。

#### 【0117】

また、図7(B)において、導電層310eは、開口部372c及び開口部374cにおいて、画素電極として機能する透光性を有する導電層316bと電気的に接続されている。

#### 【0118】

また、図7(B)において、容量素子133\_1は、開口部372において容量線として機能する導電層310fと接続されている。また、容量素子133\_1は、ゲート絶縁層上に形成される透光性を有する半導体層308cと、画素電極として機能する透光性を有する導電層316bと、トランジスタ131\_1上に設けられる窒化絶縁膜で形成される誘電体膜とで構成されている。即ち、容量素子133\_1は透光性を有する。

#### 【0119】

このように容量素子133\_1は透光性を有するため、画素回路部108内に容量素子133\_1を大きく(大面積に)形成することができる。従って、開口率を高めつつ、代表的には55%以上、好ましくは60%以上とすることが可能であると共に、電荷容量を増大させた表示装置を得ることができる。例えば、解像度の高い表示装置、例えば液晶表示装置においては、画素の面積が小さくなり、容量素子の面積も小さくなる。このため、解像度の高い表示装置において、容量素子に蓄積される電荷容量が小さくなる。しかしながら、本実施の形態に示す容量素子133\_1は透光性を有するため、当該容量素子を画素に設けることで、各画素において十分な電荷容量を得つつ、開口率を高めることができ

10

20

30

40

50

る。代表的には、画素密度が 200 ppi 以上、さらには 300 ppi 以上である高解像度の表示装置に好適に用いることができる。

#### 【0120】

また、図 7 (B) に示す画素回路部 108 は、信号線として機能する導電層 310d と平行な辺と比較してゲート信号線として機能する導電層 304c と平行な辺の方が長い形状であり、且つ容量線として機能する導電層 310f が、信号線として機能する導電層 310d と平行な方向に延伸して設けられている。この結果、画素回路部 108 に占める導電層 310f の面積を低減することが可能であるため、開口率を高めることができる。また、容量線として機能する導電層 310f が接続電極を用いず、直接透光性を有し導電層として機能する半導体層 308c と接するため、さらに開口率を高めることができる。 10

#### 【0121】

また、図 7 (C) に示す抵抗素子 114 は、図 2 (A) に示す抵抗素子 114 と同様の構成であり、図 2 (A) に示す導電層 210a が、図 7 (C) に示す導電層 310f に、図 2 (A) に示す半導体層 208 が、図 7 (C) に示す半導体層 308d に、図 2 (A) に示す開口部 209 が、図 7 (C) に示す開口部 363 に、図 2 (A) に示す導電層 210b が、図 7 (C) に示す導電層 310g に、それぞれ対応する。したがって、図 7 (C) に示す抵抗素子 114 の詳細の説明は、ここでは省略する。

#### 【0122】

また、本発明の一態様は、高解像度の表示装置においても、開口率を高めることができると、バックライトなどの光源の光を効率よく利用することができ、表示装置の消費電力を低減することができる。 20

#### 【0123】

次に、図 7 (B) に示す画素回路部 108 の変形例について、図 8 を用いて説明する。

#### 【0124】

図 8 において、ゲート信号線として機能する導電層 304c は、信号線に略直交する方向（図中左右方向）に延伸して設けられている。信号線として機能する導電層 310d は、ゲート信号線に略直交する方向（図中上下方向）に延伸して設けられている。容量線として機能する導電層 304d は、ゲート信号線と平行方向に延伸して設けられている。図 7 (B) に示す画素回路部 108 と比較して、図 8 に示す画素回路部 108 は、信号線として機能する導電層 310d と平行な辺と比較してゲート信号線として機能する導電層 304c と平行な辺の方が短い形状であること、容量線として機能する導電層 304d が、ゲート信号線と平行な方向に延伸して設けられていること、容量線として機能する導電層 304d が、ゲート信号線として機能する導電層 304c と同時に形成されていることが異なる。 30

#### 【0125】

また、半導体層 308c は、導電層 310f と接続されている。なお、透光性を有する導電層 316c は透光性を有する導電層 316b と同時に形成される。導電層 310f は、導電層 310d、310e と同時に形成される。

#### 【0126】

また、導電層 304d 上には、開口部 372c と同時に形成された開口部 372d と、開口部 374c と同時に形成された開口部 374d が形成される。また、導電層 310f 上には、開口部 372c と同時に形成された開口部 372e と、開口部 374c と同時に形成された開口部 374e が形成される。開口部 374d、374e はそれぞれ、開口部 372d、372e の内側に位置する。 40

#### 【0127】

開口部 374d において、導電層 304d 及び透光性を有する導電層 316c が接続される。また、開口部 374e において、導電層 310f 及び透光性を有する導電層 316c が接続される。即ち、導電層 304b と導電層 310c が透光性を有する導電層 316a で接続されるように、導電層 304d 及び導電層 310f は、透光性を有する導電層 316c で接続される。即ち、導電層 310f 及び透光性を有する導電層 316c を介して 50

、透光性を有し導電層として機能する半導体層 308c は容量線として機能する導電層 304d と接続される。

#### 【0128】

図 8 に示す画素回路部 108 は、信号線として機能する導電層 310d と平行な辺と比較してゲート信号線として機能する導電層 304c と平行な辺の方が短い形状とし、且つ容量線として機能する導電層 304d が、ゲート信号線として機能する導電層 304c と平行方向に延伸して設けられている。この結果、画素に占める導電層 304d の面積を低減することが可能であり、開口率を高めることができる。

#### 【0129】

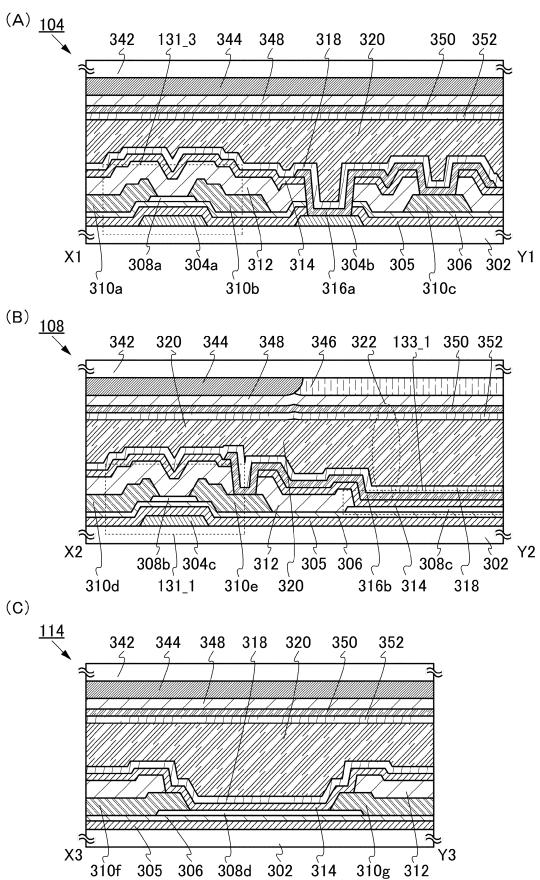

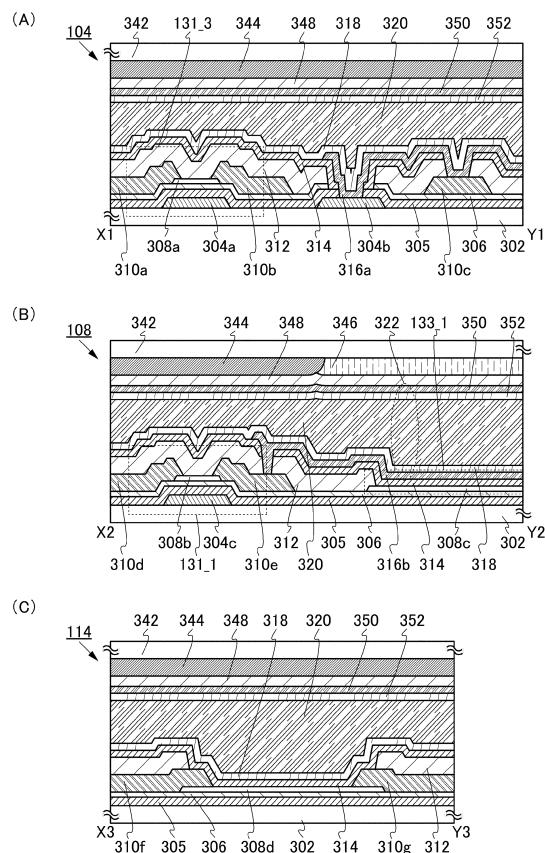

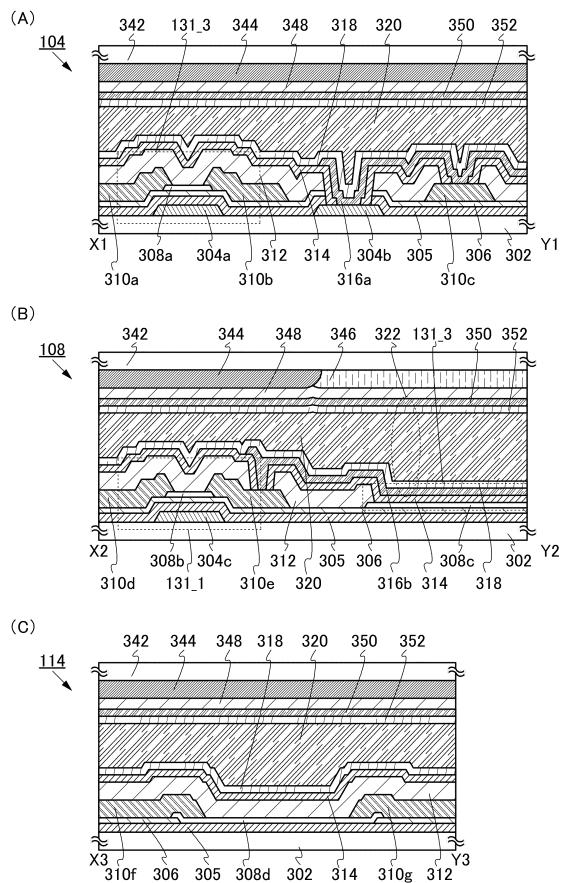

次に、図 7 に示す表示装置の断面図の構成について、図 9 を用いて説明を行う。

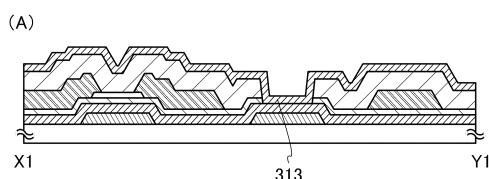

10

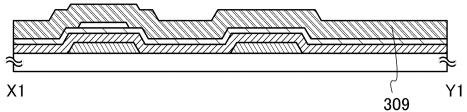

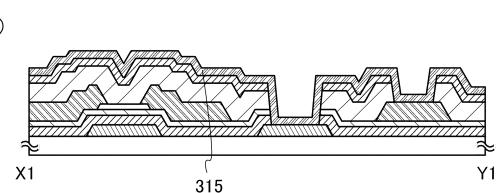

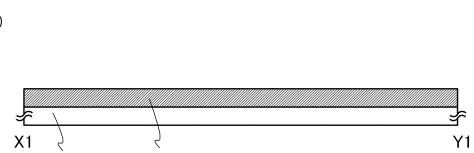

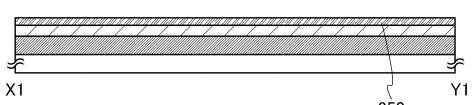

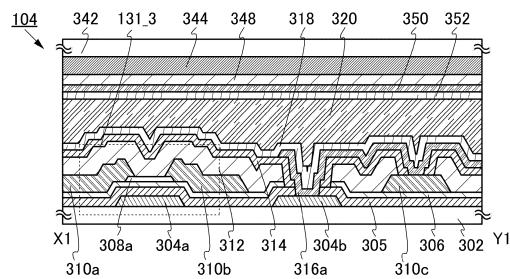

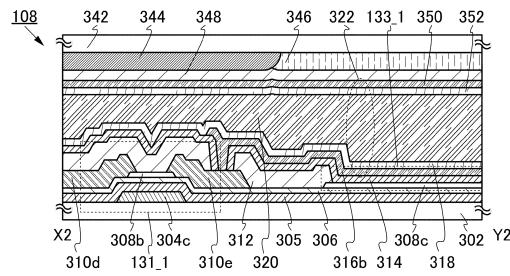

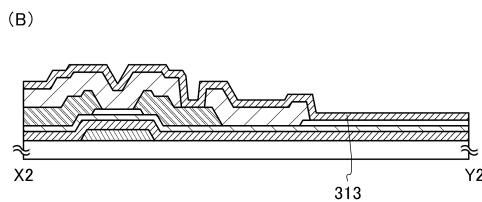

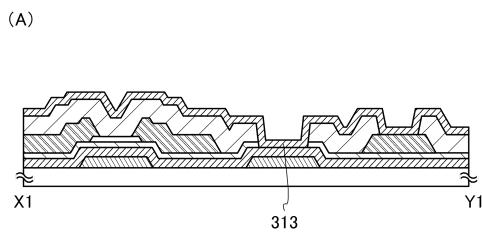

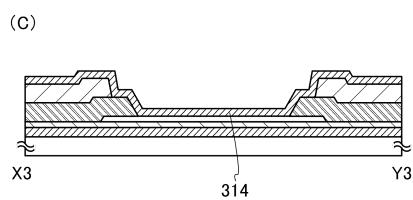

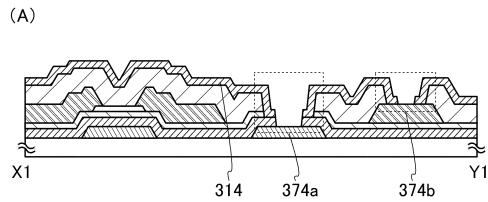

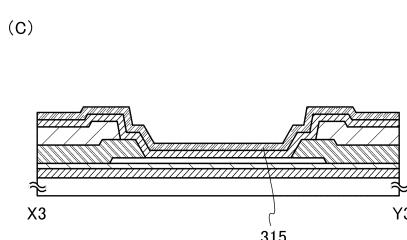

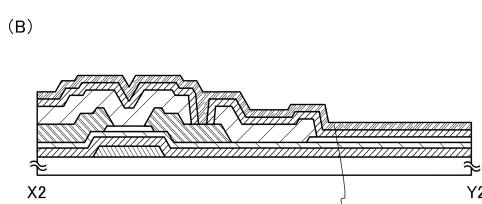

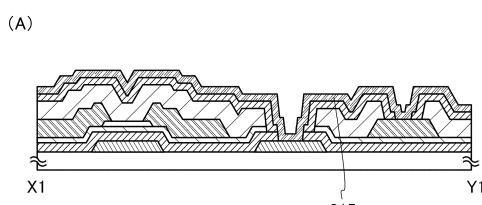

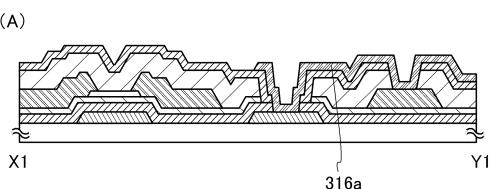

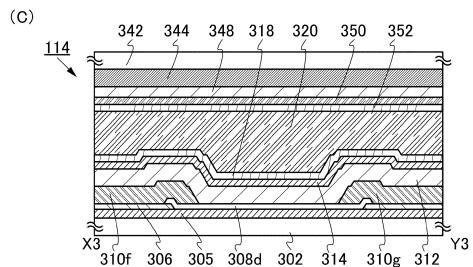

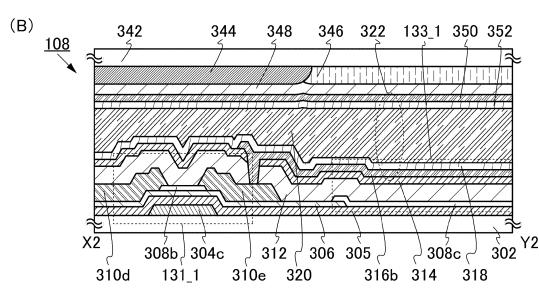

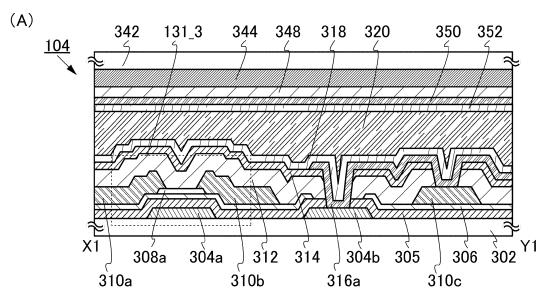

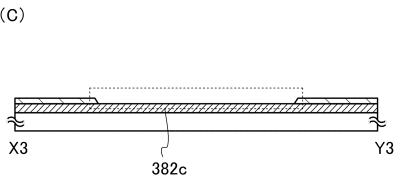

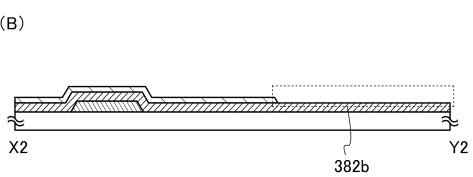

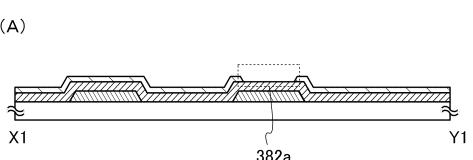

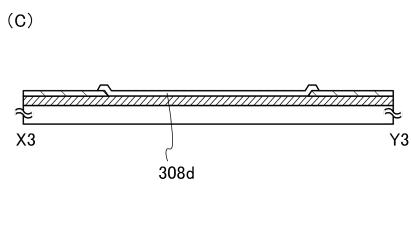

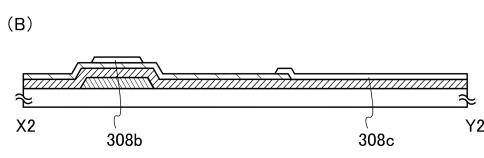

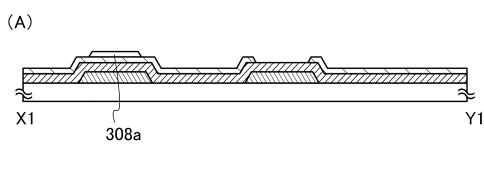

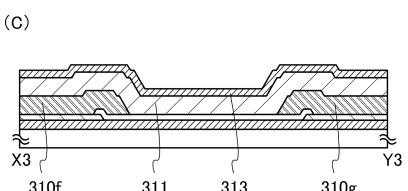

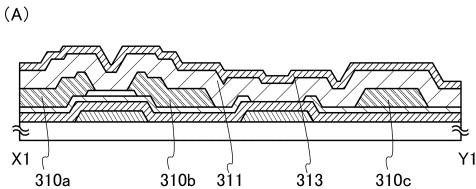

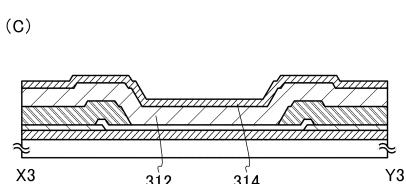

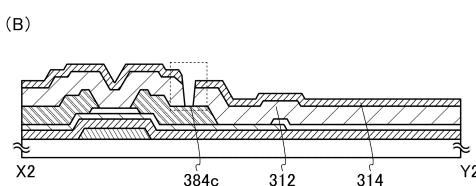

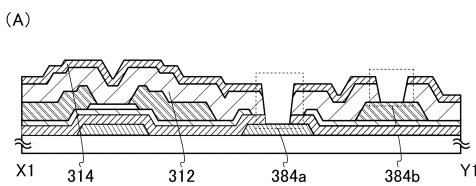

#### 【0130】

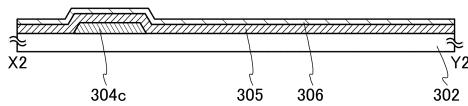

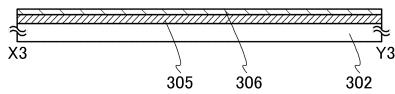

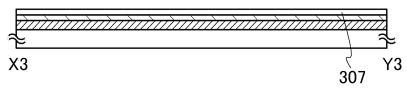

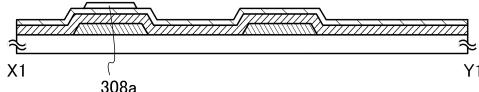

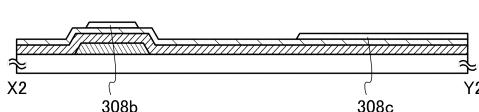

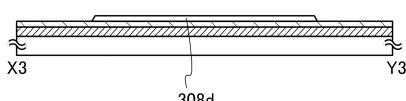

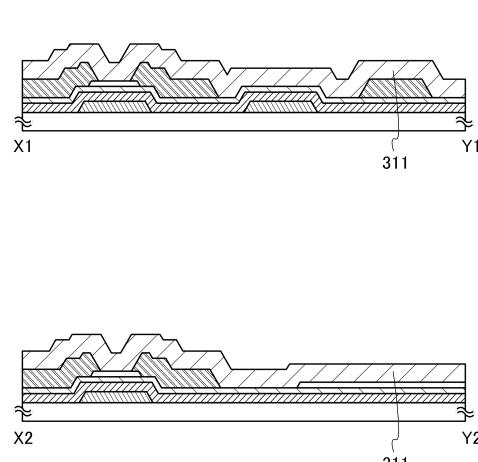

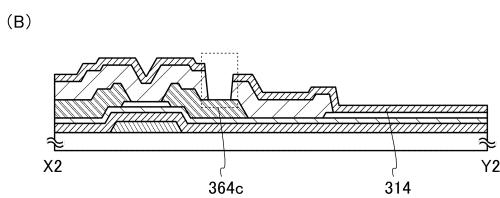

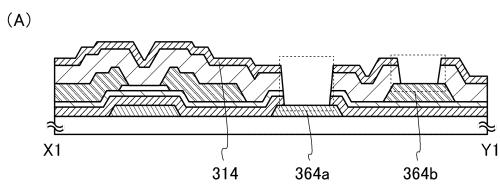

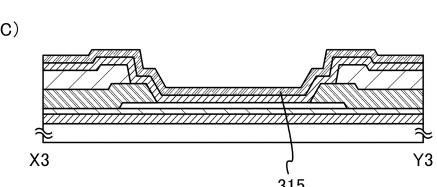

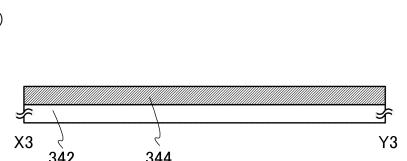

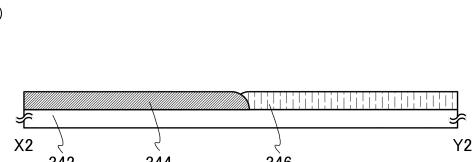

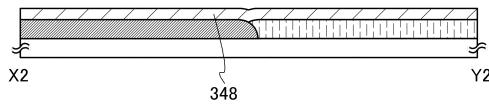

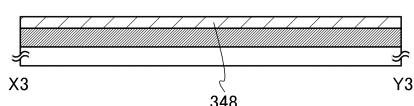

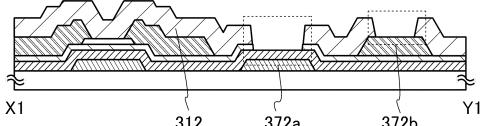

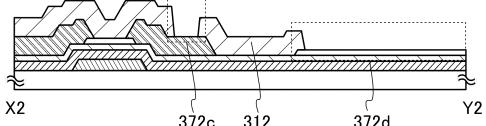

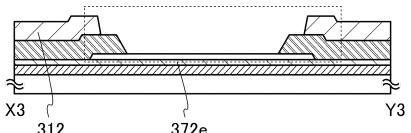

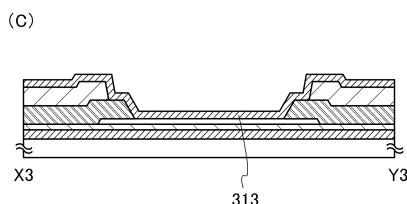

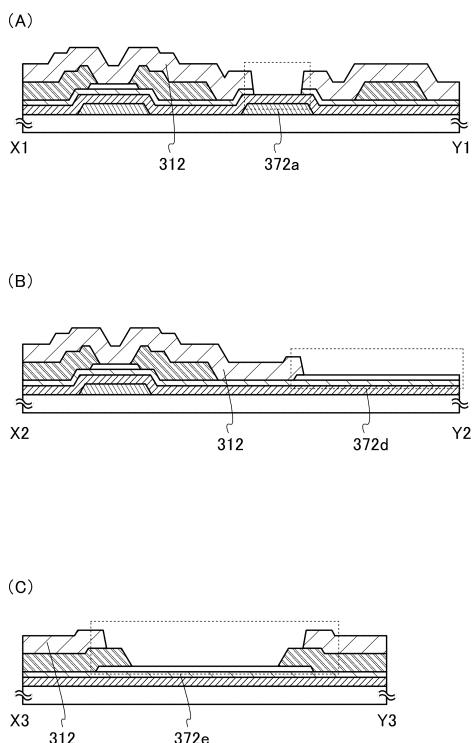

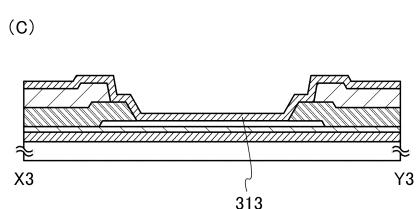

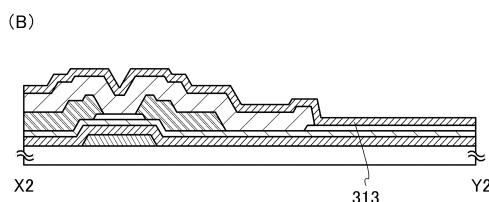

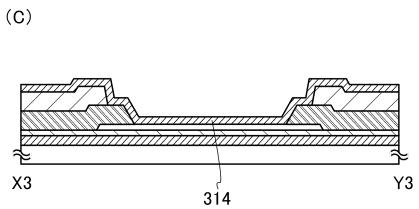

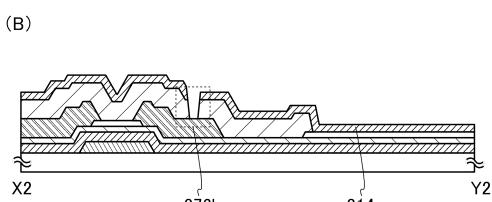

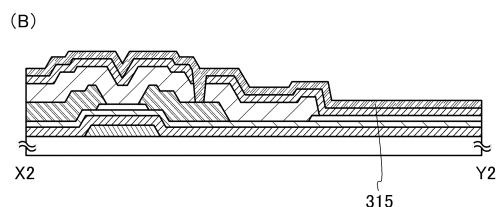

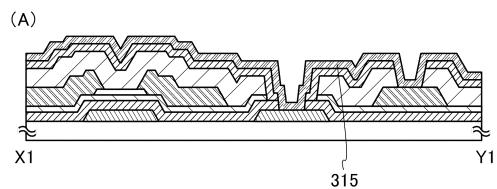

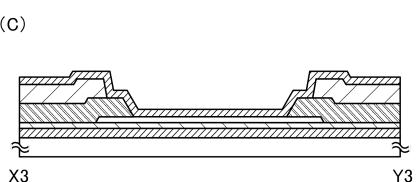

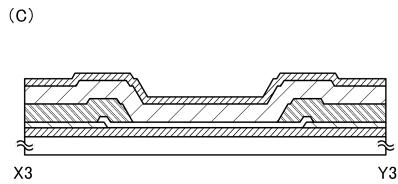

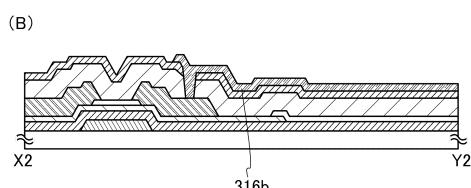

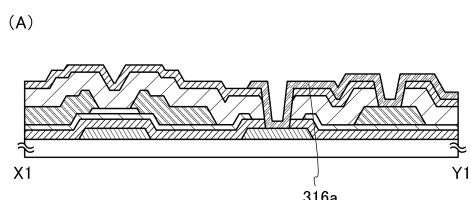

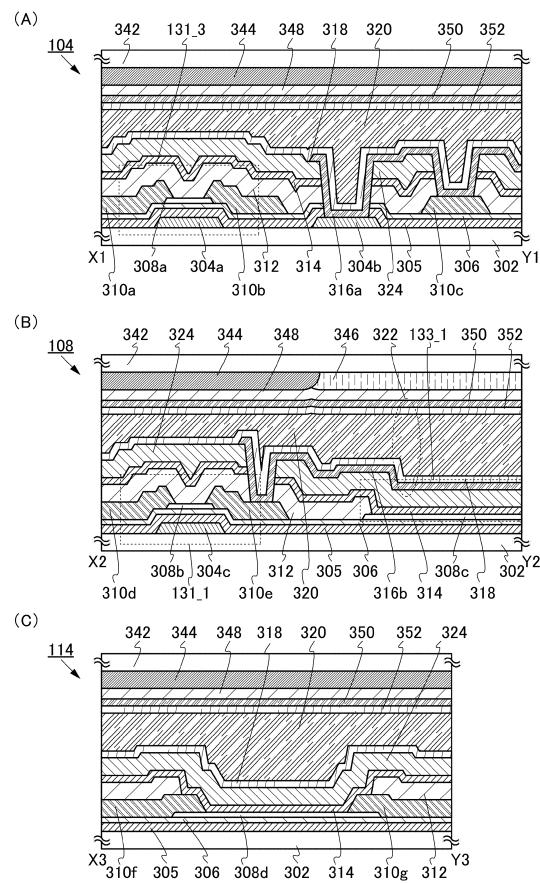

なお、図 9 (A) は、図 7 (A) に示す一点鎖線 X1 - Y1 の切断面に相当する断面図を示し、図 9 (B) は、図 7 (B) に示す一点鎖線 X2 - Y2 の切断面に相当する断面図を示し、図 9 (C) は、図 7 (C) に示す一点鎖線 X3 - Y3 の切断面に相当する断面図を示す。

#### 【0131】

図 9 に示す表示装置は、一対の基板（基板 302 と基板 342）間に液晶素子 322 が挟持されている（図 9 (B) 参照）。

#### 【0132】

液晶素子 322 は、基板 302 の上方の導電性を有する層（以下、導電層 316b という）と、配向性を制御する層（以下、配向膜 318、352 という）と、液晶層 320 と、導電性を有する層（以下、導電層 350 という）と、を有する。なお、導電層 316b は、液晶素子 322 の一方の電極として機能し、導電層 350 は、液晶素子 322 の他方の電極として機能する。

20

#### 【0133】

また、図 9においては、液晶素子 322 が縦電界方式の液晶素子について、説明を行う。縦電界方式の液晶素子としては、例えば、TN (Twisted Nematic) モード、STN (Super Twisted Nematic) モード、VA (Vertical Alignment) モード、MVA (Multi-domain Vertical Alignment) モード等が代表的である。ただし、液晶素子としては、これに限定されず、例えば横電界方式のIPS (In-Plane-Switching) モード、及びFFS (Fringe Field Switching) モード等を用いても良い。

30

#### 【0134】

このように、液晶表示装置とは、液晶素子を有する装置のことをいう。なお、液晶表示装置は、複数の画素を駆動させる駆動回路等を含む。また、液晶表示装置は、別の基板上に配置された制御回路、電源回路、信号生成回路及びバックライトモジュール等を含み、液晶モジュールと呼ぶこともある。

#### 【0135】

液晶表示装置において、液晶表示装置が有する駆動回路部 104、画素回路部 108 に設けられたトランジスタは、本実施の形態に示すように抵抗素子 114 を設けることによって、外部からの過電流に対する耐性を高めることができる。

40

#### 【0136】

なお、図 9 (C) においては、抵抗素子 114 について例示するが、図 1 (B) に示すようにトランジスタに抵抗素子 114 を直列に接続した構成としてもよい。

#### 【0137】

例えば、液晶素子を作製する際に行われるラビング処理によって、静電気が発生しうる。しかし、抵抗素子 114 を設けることによって、駆動回路部 104 及び画素回路部 108 に形成されたトランジスタには、上記静電気によって生じうる過電流が流れない、または抑制される。したがって、トランジスタの静電破壊が抑制され、信頼性の高い表示装置

50

とすることができる。

**【0138】**

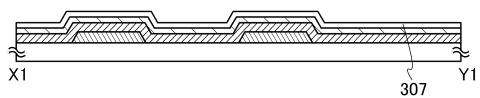

次に、図9(A)に示す駆動回路部104の構成の詳細について、以下説明を行う。

**【0139】**

(駆動回路部)

駆動回路部104は、基板302と、基板302上に形成された導電性を有する層(以下、導電層304a、304bという)と、基板302、及び導電層304a、304b上に形成された絶縁性を有する層(以下、絶縁層305という)と、絶縁層305上に形成された絶縁性を有する層(以下、絶縁層306という)と、絶縁層306上に形成され、導電層304aと重畠する位置に形成された半導体層308aと、絶縁層306、及び半導体層308a上に形成された導電性を有する層(以下、導電層310a、310bという)と、絶縁層306上に形成された導電性を有する層(以下、導電層310cという)と、半導体層308a、及び導電層310a、310b、310cを覆うように形成された絶縁性を有する層(以下、絶縁層312という)と、絶縁層312上に形成された絶縁性を有する層(以下、絶縁層314という)と、絶縁層314上に形成された導電性を有する層(以下、導電層316aという)と、を有する。

10

**【0140】**

なお、導電層316aは、導電層304bと、導電層310cを接続する配線としての機能を有する。導電層304bは、絶縁層305、306、312、314に形成された開口部を介して、導電層310cは、絶縁層312、314に形成された開口部を介して、導電層316aにより接続される。

20

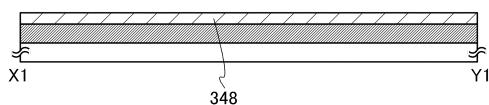

**【0141】**

また、駆動回路部104は、基板342と、基板342上に形成された遮光性を有する層(以下、遮光層344という)と、遮光層344上に形成された絶縁性を有する層(以下、絶縁層348という)と、絶縁層348上に形成された導電性を有する層(以下、導電層350という)と、を有する。

**【0142】**

また、駆動回路部104において、基板302と基板342の間に液晶層320が挟持されており、液晶層320に接して配向膜318、352が、基板302、及び基板342にそれぞれ形成されている。なお、液晶層320は、シール材(図示しない)を用いて、基板302と基板342の間に封入することができる。シール材は、外部からの水分の入り込みを抑制するために、無機材料と接触する構成が好ましい。また、液晶層320は、スペーサ(図示しない)を用いて、液晶層の厚さ(セルギャップともいう)を維持することができる。

30

**【0143】**

次に、図9(B)に示す画素回路部108の構成の詳細について、以下説明を行う。

**【0144】**

(画素回路部)

画素回路部108は、基板302と、基板302上に形成された導電性を有する層(以下、導電層304cという)と、基板302、及び導電層304c上に形成された絶縁層305と、絶縁層305上に形成された絶縁層306と、絶縁層306上に形成され、導電層304cと重畠する位置に形成された半導体層308bと、絶縁層306上に形成された半導体層308cと、絶縁層306、及び半導体層308b上に形成された導電性を有する層(以下、導電層310d、310eという)と、半導体層308b、及び導電層310d、310eを覆うように形成され、且つ半導体層308cの一部を覆う絶縁層312と、絶縁層312上に形成され、且つ半導体層308c上に形成された絶縁層314と、絶縁層314上に形成され、且つ導電層310eに接続された導電層316bと、を有する。

40

**【0145】**

なお、導電層316bは、絶縁層312、314に形成された開口部を介して、導電層

50

310eに接続される。なお、図7(B)に示す上面図においては、導電層316bと導電層310eの接続は、開口部372c、374cを介して行うが、図9(B)に示す断面図においては、導電層316bと導電層310eの接続は、1つの開口部(図18(B)に示す開口部364c)を介して行う。なお、開口部372c、374cを介して導電層316bと導電層310eを接続する方法については、図25(B)、図27(B)を用いて、後に説明する。

#### 【0146】

また、画素回路部108は、基板342と、基板342上に形成された遮光層344と、基板342上に形成された有色性を有する層(以下、有色層346という)と、遮光層344、及び有色層346上に形成された絶縁層348と、絶縁層348上に形成された導電層350と、を有する。

10

#### 【0147】

また、画素回路部108において、基板302と基板342の間に液晶層320が挟持されており、液晶層320に接して配向膜318、352が、基板302、及び基板342にそれぞれ形成されている。

#### 【0148】

次に、図9(C)に示す抵抗素子114の構成の詳細について、以下説明を行う。

#### 【0149】

##### (抵抗素子)

抵抗素子114は、基板302と、基板302上に形成された絶縁層305と、絶縁層305上に形成された絶縁層306と、絶縁層306上に形成された半導体層308dと、絶縁層306、及び半導体層308d上に形成された導電性を有する層(以下、導電層310f、310gという)と、導電層310f、310g上に形成された絶縁層312と、絶縁層312、導電層310f、310g、及び半導体層308d上に形成された絶縁層314と、を有する。

20

#### 【0150】

なお、図7(C)、及び図9(C)に示す抵抗素子114は、図2(A)、図2(B)に示す抵抗素子114と同様の構成である。ただし、本実施の形態においては、抵抗素子114の上方に形成された構成(液晶層320など)も示している。

#### 【0151】

また、抵抗素子114は、基板342と、基板342上に形成された遮光層344と、遮光層344上に形成された絶縁層348と、絶縁層348上に形成された導電層350と、を有する。

30

#### 【0152】

また、抵抗素子114において、基板302と基板342の間に液晶層320が挟持されており、液晶層320に接して配向膜318、352が、基板302、及び基板342にそれぞれ形成されている。

#### 【0153】

本実施の形態に示す表示装置は、駆動回路部104、及び画素回路部108が有するトランジスタと、抵抗素子114と、を同一基板上に同時に形成することができる。したがって、製造コスト等を増やさずに抵抗素子114を形成することが可能となる。

40

#### 【0154】

とくに、駆動回路部104、及び画素回路部108が有するトランジスタのチャネル領域を形成する半導体層と、画素回路部108が有する容量素子の一方の電極として機能する半導体層と、抵抗素子114が有する半導体層と、を同時に形成することができる。また、半導体層に接する絶縁層の構成を変えることによって、トランジスタ、容量素子、及び抵抗素子の半導体層は、それぞれ異なる抵抗となる。なお、本明細書等において、容量素子の一方の電極として機能する半導体層は、導電性が高められ低抵抗となることで導電層と呼ぶ場合もある。

#### 【0155】

また、本実施の形態においては、とくに上記半導体層として、酸化物半導体を用いた構造について説明を行う。

#### 【0156】

まず、酸化物半導体を用いたトランジスタの特徴について記載する。本実施の形態に示す酸化物半導体を用いたトランジスタはnチャネル型トランジスタである。また、酸化物半導体に含まれる酸素欠損はキャリアを生成することがあり、トランジスタの電気特性及び信頼性を低下させる恐れがある。例えば、トランジスタのしきい値電圧をマイナス方向に変動し、ゲート電圧が0Vの場合にドレイン電流が流れてしまうことがある。このように、ゲート電圧が0Vの場合にドレイン電流が流れてしまうことをノーマリーオン特性といい、このような特性を有するトランジスタをデプレッション型トランジスタという。なお、ゲート電圧が0Vの場合にドレイン電流が流れないとみなすことができるトランジスタをノーマリーオフ特性といい、このような特性を有するトランジスタをエンハンスマント型トランジスタという。10

#### 【0157】

トランジスタのチャネル領域が形成される酸化物半導体において、欠陥、代表的には酸素欠損はできる限り低減されていることが好ましい。例えば、磁場の向きを膜面に対して平行に印加した電子スピン共鳴法によるg値 = 1.93のスピン密度（酸化物半導体に含まれる欠陥密度に相当する。）は、測定器の検出下限以下まで低減されていることが好ましい。酸化物半導体に含まれる欠陥、代表的には酸素欠損をできる限り低減することで、トランジスタがノーマリーオン特性となることを抑制することができ、表示装置の電気特性及び信頼性を向上させることができる。また、表示装置の消費電力を低減することができる。20

#### 【0158】

トランジスタのしきい値電圧のマイナス方向への変動は酸素欠損だけではなく、酸化物半導体に含まれる水素（水などの水素化合物を含む。）によっても引き起こされることがある。酸化物半導体に含まれる水素は金属原子と結合する酸素と反応して水になると共に、酸素が脱離した格子（又は酸素が脱離した部分）に欠損（酸素欠損ともいえる。）を形成する。また、水素の一部が酸素と反応することで、キャリアである電子を生成してしまう。従って、水素が含まれている酸化物半導体を用いたトランジスタはノーマリーオン特性となりやすい。30

#### 【0159】

そこで、トランジスタのチャネル領域が形成される酸化物半導体において、水素ができる限り低減されていることが好ましい。具体的には、酸化物半導体において、二次イオン質量分析法（S I M S : Secondary Ion Mass Spectrometry）により得られる水素濃度を、 $5 \times 10^{19}$  atoms / cm<sup>3</sup>未満、好ましくは $5 \times 10^{18}$  atoms / cm<sup>3</sup>未満、好ましくは $1 \times 10^{18}$  atoms / cm<sup>3</sup>以下、より好ましくは $5 \times 10^{17}$  atoms / cm<sup>3</sup>以下、さらに好ましくは $1 \times 10^{16}$  atoms / cm<sup>3</sup>以下とする。

#### 【0160】

また、トランジスタのチャネル領域が形成される酸化物半導体は、二次イオン質量分析法により得られるアルカリ金属又はアルカリ土類金属の濃度を、 $1 \times 10^{18}$  atoms / cm<sup>3</sup>以下、好ましくは $2 \times 10^{16}$  atoms / cm<sup>3</sup>以下にする。アルカリ金属及びアルカリ土類金属は、酸化物半導体と結合するとキャリアを生成する場合があり、トランジスタのオフ電流を増大させることがある。40

#### 【0161】

このように、不純物（水素、窒素、アルカリ金属又はアルカリ土類金属など）をできる限り低減させ、トランジスタのチャネル領域が形成される酸化物半導体膜を高純度化させた酸化物半導体膜とすることで、エンハンスマント型となり、トランジスタがノーマリーオン特性となることを抑制でき、トランジスタのオフ電流を極めて低減することができる。従って、良好な電気特性に有する表示装置を作製できる。また、信頼性を向上させた表50

示装置を作製することができる。

**【0162】**

なお、高純度化された酸化物半導体膜を用いたトランジスタのオフ電流が低いことは、いろいろな実験により証明できる。例えば、チャネル幅が $1 \times 10^6 \mu\text{m}$ でチャネル長Lが $10 \mu\text{m}$ の素子であっても、ソースとドレイン間の電圧（ドレイン電圧）が $1\text{V}$ から $10\text{V}$ の範囲において、オフ電流が、半導体パラメータアナライザの測定限界以下、すなわち $1 \times 10^{-13}\text{A}$ 以下という特性を得ることができる。この場合、オフ電流をトランジスタのチャネル幅で除した値は、 $100\text{zA}/\mu\text{m}$ 以下であることが分かる。また、容量素子とトランジスタとを接続して、容量素子に流入又は容量素子から流出する電荷を当該トランジスタで制御する回路を用いて、オフ電流の測定を行う。当該測定では、上記トランジスタに高純度化された酸化物半導体膜をチャネル形成領域に用い、容量素子の単位時間あたりの電荷量の推移から当該トランジスタのオフ電流を測定する。その結果、トランジスタのソースとドレイン間の電圧が $3\text{V}$ の場合に、数十 $\text{yA}/\mu\text{m}$ という、さらに低いオフ電流が得られる。従って、高純度化された酸化物半導体膜を用いたトランジスタは、オフ電流が著しく小さい。10

**【0163】**

次に、半導体層、ここでは酸化物半導体の上部、及び下部に形成される絶縁層の詳細について、以下説明を行う。

**【0164】**

絶縁層305、314としては、外部からの不純物、例えば、水、アルカリ金属、アルカリ土類金属等が、酸化物半導体層へ拡散するのを防ぐ材料を用いることが好ましく、更には水素を含むことが好ましく、代表的には窒素を含む無機絶縁材料、例えば窒化絶縁膜を用いることができる。絶縁層305及び絶縁層314としては、代表的には、窒化シリコン、窒化酸化シリコン、窒化アルミニウム、窒化酸化アルミニウム等を用いて形成する。20

**【0165】**

絶縁層306、312としては、酸化物半導体膜との界面特性を向上させることができ可能な材料を用いることが好ましく、代表的には、酸素を含む無機絶縁材料を用いることが好ましく、例えば酸化絶縁膜を用いることができる。絶縁層306、312としては、代表的には、酸化シリコン、酸化窒化シリコン、酸化アルミニウム、酸化窒化アルミニウム等を用いて形成する。30

**【0166】**

上述した酸化物半導体層、及び該酸化物半導体層に接する絶縁層の構成を変更することで、以下のような構成とすることができる。

**【0167】**

図9(A)に示す駆動回路部104において、半導体層308aは、トランジスタのチャネル形成領域として機能する。したがって、半導体層308aに接する絶縁層としては、絶縁層306、及び絶縁層312となる。また、図9(B)に示す画素回路部108において、半導体層308bは、トランジスタのチャネル形成領域として機能する。したがって、半導体層308bに接する絶縁層としては、絶縁層306、及び絶縁層312となる。一方、図9(B)に示す画素回路部108において、半導体層308cは、容量素子133\_1の一方の電極として機能する。したがって、半導体層308cに接する絶縁層としては、絶縁層306、及び絶縁層314となる。このとき、絶縁層314が半導体層308bと直接接しないようにすることで、半導体層308bと半導体層308cの抵抗率を変えることができる。そして、半導体層308bをチャネル形成領域として機能させ、半導体層308cの抵抗素子として機能させることができる。また、図9(C)に示す抵抗素子114において、半導体層308dは、抵抗素子として機能する。したがって、半導体層308dに接する絶縁層としては、絶縁層306、及び絶縁層314となる。40

**【0168】**

絶縁層314は、水素を含む絶縁層である。このため、絶縁層314に含まれる水素が50

半導体層 308c、308d に拡散または移動すると、半導体層 308c、308d として用いる酸化物半導体層において、水素は酸素と結合し、キャリアである電子が生成される。この結果、酸化物半導体層は、導電性が高くなり導体として機能する。また、酸化物半導体層は、透光性を有する材料であるため、半導体層 308c、308d は、透光性を有し、且つ導電層として用いることができる。

#### 【0169】

本実施の形態に示す表示装置は、トランジスタの酸化物半導体層と同時に、容量素子の一方となる電極、及び抵抗素子の半導体層を同時に形成できる。また、画素電極として機能する透光性を有する導電層を容量素子の他方の電極として用いる。これらのため、容量素子を形成するために、新たに導電層を形成する工程が不要であり、表示装置の作製工程を削減できる。また、容量素子は、一対の電極が透光性を有する導電層で形成されているため、透光性を有する。この結果、容量素子の占有面積を大きくしつつ、画素の開口率を高めることができる。10

#### 【0170】

なお、その他の構成要素については、後述する表示装置の作製方法について詳細を記載する。

#### 【0171】

本実施の形態に示す構成は、他の実施の形態に示す構成と適宜組み合わせて用いることができる。20

#### 【0172】

##### (実施の形態 3 )

本実施の形態では、実施の形態 2 で説明した表示装置の作製方法について、図 10 乃至図 23 を用いて説明する。

#### 【0173】

先の実施の形態 2 で説明した表示装置は、駆動回路部 104 と、画素回路部 108 と、抵抗素子 114 と、を同時に作製される。したがって、本実施の形態においては、駆動回路部 104、画素回路部 108、抵抗素子 114 の作製方法について、それぞれ説明を行う。

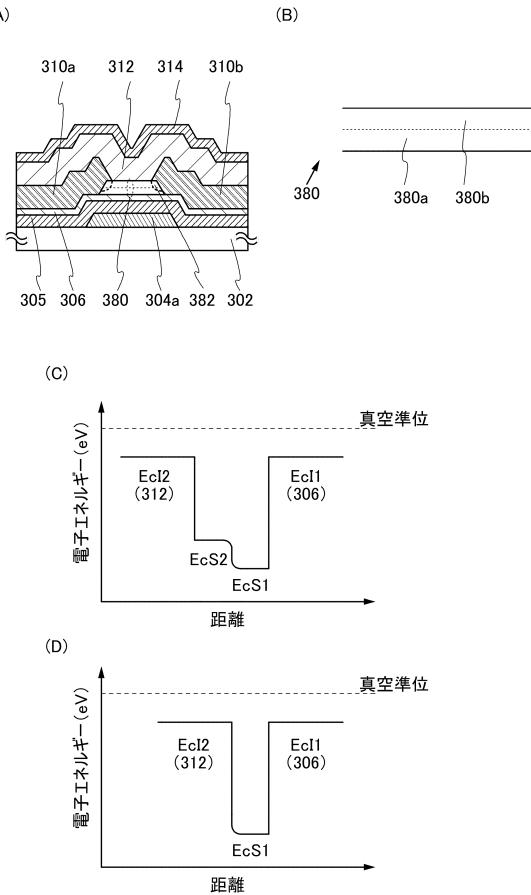

#### 【0174】

なお、駆動回路部 104 の作製方法については、図 10 (A)、図 11 (A)、図 12 (A)、図 13 (A)、図 14 (A)、図 15 (A)、図 16 (A)、図 17 (A)、図 18 (A)、図 19 (A)、図 20 (A)、図 21 (A)、図 22 (A)、及び図 23 (A) に示し、画素回路部 108 の作製方法については、図 10 (B)、図 11 (B)、図 12 (B)、図 13 (B)、図 14 (B)、図 15 (B)、図 16 (B)、図 17 (B)、図 18 (B)、図 19 (B)、図 20 (B)、図 21 (B)、図 22 (B)、及び図 23 (B) に示し、抵抗素子 114 の作製方法については、図 10 (C)、図 11 (C)、図 12 (C)、図 13 (C)、図 14 (C)、図 15 (C)、図 16 (C)、図 17 (C)、図 18 (C)、図 19 (C)、図 20 (C)、図 21 (C)、図 22 (C)、及び図 23 (C) に示す。30

#### 【0175】

まず、基板 302 を準備する。基板 302 としては、アルミニノシリケートガラス、アルミニノホウケイ酸ガラス、バリウムホウケイ酸ガラスなどのガラス材料を用いる。量産する上では、基板 302 は、第 8 世代 (2160 mm × 2460 mm)、第 9 世代 (2400 mm × 2800 mm、または 2450 mm × 3050 mm)、第 10 世代 (2950 mm × 3400 mm) 等のマザーガラスを用いることが好ましい。マザーガラスは、処理温度が高く、処理時間が長いと大幅に収縮するため、マザーガラスを使用して量産を行う場合、作製工程の加熱処理は、好ましくは 600 以下、さらに好ましくは 450 以下、さらに好ましくは 350 以下とすることが望ましい。40

#### 【0176】

次に、基板 302 上に導電膜を形成し、該導電膜を所望の領域に加工することで、導電50

層 304a、304b、304cを形成する。なお、導電層 304a、304b、304cの形成は、所望の領域に第1のパターニングによるマスクの形成を行い、該マスクに覆われていない領域をエッチングすることで形成することができる。

#### 【0177】

導電層 304a、304b、304cとしては、アルミニウム、クロム、銅、タンタル、チタン、モリブデン、タンゲステンから選ばれた金属元素、または上述した金属元素を成分とする合金か、上述した金属元素を組み合わせた合金等を用いて形成することができる。また、導電層 304a、304b、304cは、単層構造でも、二層以上の積層構造としてもよい。例えば、アルミニウム膜上にチタン膜を積層する二層構造、窒化チタン膜上にチタン膜を積層する二層構造、窒化チタン膜上にタンゲステン膜を積層する二層構造、窒化タンタル膜または窒化タンゲステン膜上にタンゲステン膜を積層する二層構造、チタン膜と、そのチタン膜上にアルミニウム膜を積層し、さらにその上にチタン膜を形成する三層構造等がある。また、アルミニウムに、チタン、タンタル、タンゲステン、モリブデン、クロム、ネオジム、スカンジウムから選ばれた元素の膜、または複数組み合わせた合金膜、もしくは窒化膜を用いてもよい。また、導電層 304a、304b、304cとしては、例えば、スパッタリング法を用いて形成することができる。

#### 【0178】

次に、基板 302、及び導電層 304a、304b、304c 上に絶縁層 305、306 を形成する(図 10 (A)、(B)、(C) 参照)。

#### 【0179】

絶縁層 305 としては、例えば、窒化酸化シリコン膜、窒化シリコン膜、酸化アルミニウム膜などを用いればよく、PE-CVD 装置を用いて積層または単層で設ける。また、絶縁層 306 を積層構造とした場合、第1の窒化シリコン膜として、欠陥が少ない窒化シリコン膜とし、第2の窒化シリコン膜として、水素放出量及びアンモニア放出量の少ない窒化シリコン膜を設けると好適である。この結果、絶縁層 305 に含まれる水素及び窒素が、半導体層 308a、308b、308c へ移動または拡散することを抑制できる。

#### 【0180】

絶縁層 306 としては、酸化シリコン膜、酸化窒化シリコン膜などを用いればよく、PE-CVD 装置を用いて積層または単層で設ける。

#### 【0181】

絶縁層 305、306 としては、例えば、絶縁層 305 として、厚さ 300 nm の窒化シリコン膜を形成し、その後、絶縁層 306 として、厚さ 50 nm の酸化窒化シリコン膜を形成することができる。該窒化シリコン膜と、該酸化窒化シリコン膜は、真空中で連続して形成すると不純物の混入が抑制され好ましい。なお、導電層 304a、304c と重畠する領域の絶縁層 305、306 は、トランジスタのゲート絶縁層として機能することができる。

#### 【0182】

なお、窒化酸化シリコンとは、窒素の含有量が酸素の含有量より大きい絶縁材料であり、他方、酸化窒化シリコンとは、酸素の含有量が窒素の含有量より大きな絶縁材料のことを行う。

#### 【0183】

ゲート絶縁層として、上記のような構成とすることで、例えば以下のよう効果を得ることができる。窒化シリコン膜は、酸化シリコン膜と比較して比誘電率が高く、同等の静電容量を得るのに必要な膜厚が大きいため、ゲート絶縁膜を物理的に厚膜化することができる。よって、トランジスタの絶縁耐圧の低下を抑制、さらには絶縁耐圧を向上させて、トランジスタの静電破壊を抑制することができる。

#### 【0184】

次に、絶縁層 306 上に半導体層 307 を形成する(図 11 (A)、(B)、(C) 参照)。

10

20

30

40

50

## 【0185】

半導体層307としては、例えば、酸化物半導体を用いることができる。半導体層307に適用できる酸化物半導体は、少なくともインジウム(Indium)、亜鉛(Zinc)及びM(Al、Ga、Ge、Y、Zr、Sn、La、CeまたはHf等の金属)を含むIn-M-Zn酸化物で表記される層を含むことが好ましい。または、InとZnの双方を含むことが好ましい。また、該酸化物半導体を用いたトランジスタの電気特性のばらつきを減らすため、それらと共に、スタビライザーを含むことが好ましい。

## 【0186】

スタビライザーとしては、ガリウム(Ga)、スズ(Sn)、ハフニウム(Hf)、アルミニウム(Al)、またはジルコニウム(Zr)等がある。また、他のスタビライザーとしては、ラントノイドである、ランタン(La)、セリウム(Ce)、プラセオジム(Pr)、ネオジム(Nd)、サマリウム(Sm)、ユウロピウム(Eu)、ガドリニウム(Gd)、テルビウム(Tb)、ジスプロシウム(Dy)、ホルミウム(Ho)、エルビウム(Er)、ツリウム(Tm)、イッテルビウム(Yb)、ルテチウム(Lu)等がある。

## 【0187】

例えば、酸化物半導体として、酸化インジウム、酸化スズ、酸化亜鉛、In-Zn酸化物、Sn-Zn酸化物、Al-Zn酸化物、Zn-Mg酸化物、Sn-Mg酸化物、In-Mg酸化物、In-Ga酸化物、In-Ga-Zn酸化物、In-Al-Zn酸化物、In-Sn-Zn酸化物、Sn-Ga-Zn酸化物、Al-Ga-Zn酸化物、Sn-Al-Zn酸化物、In-Hf-Zn酸化物、In-La-Zn酸化物、In-Ce-Zn酸化物、In-Pr-Zn酸化物、In-Nd-Zn酸化物、In-Sm-Zn酸化物、In-Eu-Zn酸化物、In-Gd-Zn酸化物、In-Tb-Zn酸化物、In-Dy-Zn酸化物、In-Ho-Zn酸化物、In-Er-Zn酸化物、In-Tm-Zn酸化物、In-Yb-Zn酸化物、In-Lu-Zn酸化物、In-Sn-Ga-Zn酸化物、In-Hf-Ga-Zn酸化物、In-Al-Ga-Zn酸化物、In-Sn-Al-Zn酸化物、In-Sn-Hf-Zn酸化物、In-Hf-Al-Zn酸化物を用いることができる。

## 【0188】

なお、ここで、例えば、In-Ga-Zn酸化物とは、InとGaとZnを主成分として有する酸化物という意味であり、InとGaとZnの比率は問わない。また、InとGaとZn以外の金属元素が入っていてもよい。また、本明細書等においては、In-Ga-Zn酸化物で構成した膜をIGZO膜とも呼ぶ。

## 【0189】

また、 $InMO_3 (ZnO)_m$ ( $m > 0$ 、且つ、 $m$ は整数でない)で表記される材料を用いてもよい。なお、Mは、Ga、Fe、Mn及びCoから選ばれた一つの金属元素または複数の金属元素を示す。また、 $In_2SnO_5 (ZnO)_n$ ( $n > 0$ 、且つ、 $n$ は整数)で表記される材料を用いてもよい。

## 【0190】

ここで酸化物半導体膜の構造について説明する。

## 【0191】

酸化物半導体膜は、非単結晶酸化物半導体膜と単結晶酸化物半導体膜とに大別される。非単結晶酸化物半導体膜とは、C A A C - O S (C Axis Aligned Crystalline Oxide Semiconductor)膜、多結晶酸化物半導体膜、微結晶酸化物半導体膜、非晶質酸化物半導体膜などをいう。

## 【0192】

まずは、C A A C - O S 膜について説明する。

## 【0193】

C A A C - O S 膜は、c軸配向した複数の結晶部を有する酸化物半導体膜の一つである。

10

20

30

40

50

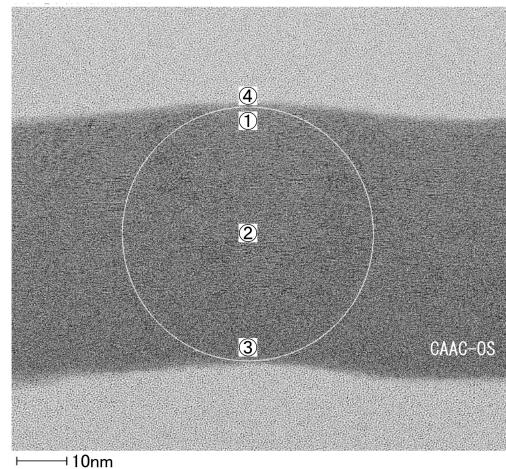

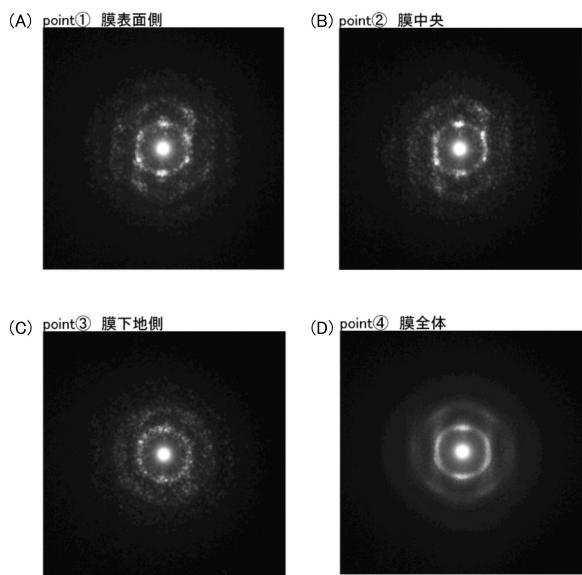

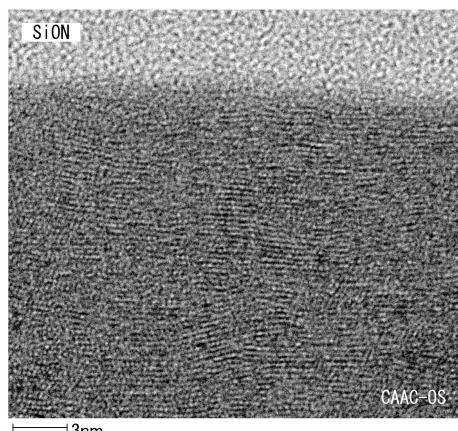

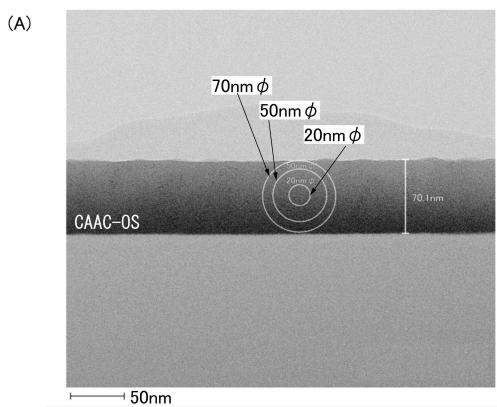

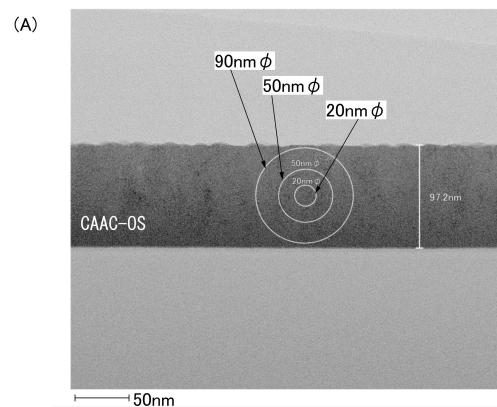

## 【0194】

C AAC - OS 膜を透過型電子顕微鏡 (TEM : Transmission Electron Microscope) によって観察すると、明確な結晶部同士の境界、即ち結晶粒界 (グレインバウンダリーともいう。) を確認することができない。そのため、C AAC - OS 膜は、結晶粒界に起因する電子移動度の低下が起こりにくいといえる。

## 【0195】

C AAC - OS 膜を、試料面と概略平行な方向から TEM によって観察 (断面 TEM 観察) すると、結晶部において、金属原子が層状に配列していることを確認できる。金属原子の各層は、C AAC - OS 膜の膜を形成する面 (被形成面ともいう。) または上面の凹凸を反映した形状であり、C AAC - OS 膜の被形成面または上面と平行に配列する。

10

## 【0196】

一方、C AAC - OS 膜を、試料面と概略垂直な方向から TEM によって観察 (平面 TEM 観察) すると、結晶部において、金属原子が三角形状または六角形状に配列していることを確認できる。しかしながら、異なる結晶部間で、金属原子の配列に規則性は見られない。

## 【0197】

断面 TEM 観察および平面 TEM 観察より、C AAC - OS 膜の結晶部は配向性を有していることがわかる。

## 【0198】

なお、本明細書において、「平行」とは、二つの直線が - 10° 以上 10° 以下の角度で配置されている状態をいう。従って、- 5° 以上 5° 以下の場合も含まれる。また、「垂直」とは、二つの直線が 80° 以上 100° 以下の角度で配置されている状態をいう。従って、85° 以上 95° 以下の場合も含まれる。

20

## 【0199】

また、C AAC - OS 膜に含まれるほとんどの結晶部は、一辺が 100 nm 未満の立方体内に収まる大きさである。従って、C AAC - OS 膜に含まれる結晶部は、一辺が 10 nm 未満、5 nm 未満または 3 nm 未満の立方体内に収まる大きさの場合も含まれる。ただし、C AAC - OS 膜に含まれる複数の結晶部が連結することで、一つの大きな結晶領域を形成する場合がある。例えば、平面 TEM 像において、2500 nm<sup>2</sup> 以上、5 μm<sup>2</sup> 以上または 1000 μm<sup>2</sup> 以上となる結晶領域が観察される場合がある。

30

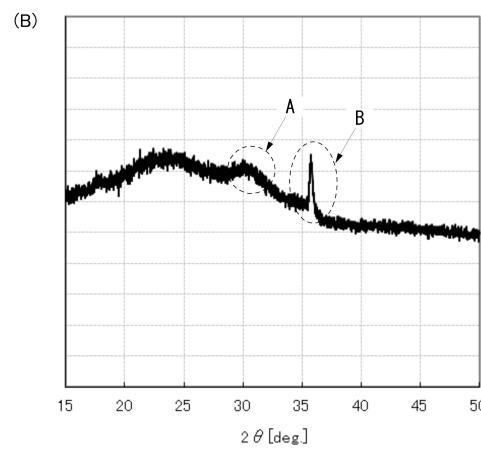

## 【0200】

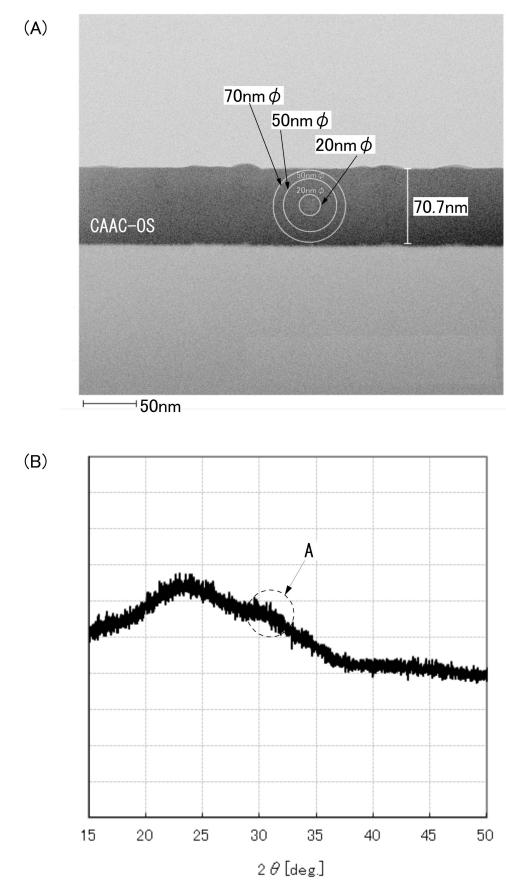

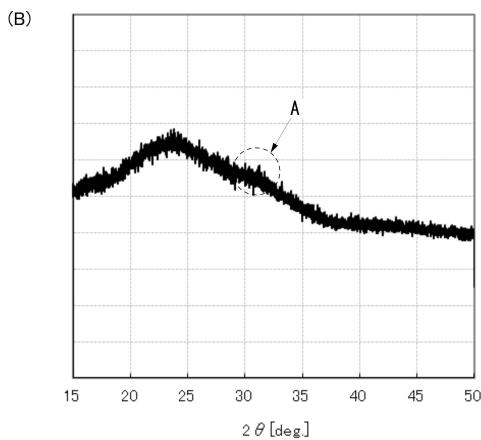

C AAC - OS 膜に対し、X 線回折 (XRD : X - Ray Diffraction) 装置を用いて構造解析を行うと、例えば InGaN<sub>0.4</sub> の結晶を有する C AAC - OS 膜の out-of-plane 法による解析では、回折角 (2θ) が 31° 近傍にピークが現れる場合がある。このピークは、InGaN<sub>0.4</sub> の結晶の (009) 面に帰属されることから、C AAC - OS 膜の結晶が c 軸配向性を有し、c 軸が被形成面または上面に概略垂直な方向を向いていることが確認できる。

## 【0201】

一方、C AAC - OS 膜に対し、c 軸に概略垂直な方向から X 線を入射させる in-plane 法による解析では、2θ が 56° 近傍にピークが現れる場合がある。このピークは、InGaN<sub>0.4</sub> の結晶の (110) 面に帰属される。InGaN<sub>0.4</sub> の単結晶酸化物半導体膜であれば、2θ を 56° 近傍に固定し、試料面の法線ベクトルを軸 (c 軸) として試料を回転させながら分析 (スキャン) を行うと、(110) 面と等価な結晶面に帰属されるピークが 6 本観察される。これに対し、C AAC - OS 膜の場合は、2θ を 56° 近傍に固定して スキャンした場合でも、明瞭なピークが現れない。

40

## 【0202】

以上のことから、C AAC - OS 膜では、異なる結晶部間では a 軸および b 軸の配向は不規則であるが、c 軸配向性を有し、かつ c 軸が被形成面または上面の法線ベクトルに平行な方向を向いていることがわかる。従って、前述の断面 TEM 観察で確認された層状に配列した金属原子の各層は、結晶の ab 面に平行な面である。

50

**【0203】**

なお、結晶部は、C A A C - O S 膜を成膜した際、または加熱処理などの結晶化処理を行った際に形成される。上述したように、結晶のc軸は、C A A C - O S 膜の被形成面または上面の法線ベクトルに平行な方向に配向する。従って、例えば、C A A C - O S 膜の形状をエッチングなどによって変化させた場合、結晶のc軸がC A A C - O S 膜の被形成面または上面の法線ベクトルと平行にならないこともある。

**【0204】**

また、C A A C - O S 膜中において、c軸配向した結晶部の分布が均一でなくてもよい。例えば、C A A C - O S 膜の結晶部が、C A A C - O S 膜の上面近傍からの結晶成長によって形成される場合、上面近傍の領域は、被形成面近傍の領域よりもc軸配向した結晶部の割合が高くなることがある。また、C A A C - O S 膜に不純物を添加する場合、不純物が添加された領域が変質し、部分的にc軸配向した結晶部の割合の異なる領域が形成されることもある。

10

**【0205】**

なお、InGaZnO<sub>4</sub>の結晶を有するC A A C - O S 膜のout-of-plane法による解析では、2θが31°近傍のピークの他に、2θが36°近傍にもピークが現れる場合がある。2θが36°近傍のピークは、C A A C - O S 膜中の一部に、c軸配向性を有さない結晶が含まれることを示している。C A A C - O S 膜は、2θが31°近傍にピークを示し、2θが36°近傍にピークを示さないことが好ましい。

20

**【0206】**

C A A C - O S 膜は、不純物濃度の低い酸化物半導体膜である。不純物は、水素、炭素、シリコン、遷移金属元素などの酸化物半導体膜の主成分以外の元素である。特に、シリコンなどの、酸化物半導体膜を構成する金属元素よりも酸素との結合力の強い元素は、酸化物半導体膜から酸素を奪うことで酸化物半導体膜の原子配列を乱し、結晶性を低下させる要因となる。また、鉄やニッケルなどの重金属、アルゴン、二酸化炭素などは、原子半径（または分子半径）が大きいため、酸化物半導体膜内部に含まれると、酸化物半導体膜の原子配列を乱し、結晶性を低下させる要因となる。なお、酸化物半導体膜に含まれる不純物は、キャリアトラップやキャリア発生源となる場合がある。

**【0207】**

また、C A A C - O S 膜は、欠陥準位密度の低い酸化物半導体膜である。例えば、酸化物半導体膜中の酸素欠損は、キャリアトラップとなることや、水素を捕獲することによってキャリア発生源となることがある。

30

**【0208】**

不純物濃度が低く、欠陥準位密度が低い（酸素欠損の少ない）ことを、高純度真性または実質的に高純度真性と呼ぶ。高純度真性または実質的に高純度真性である酸化物半導体膜は、キャリア発生源が少ないため、キャリア密度を低くすることができる。従って、当該酸化物半導体膜を用いたトランジスタは、しきい値電圧がマイナスとなる電気特性（ノーマリーオンともいう。）になることが多い。また、高純度真性または実質的に高純度真性である酸化物半導体膜は、キャリアトラップが少ない。そのため、当該酸化物半導体膜を用いたトランジスタは、電気特性の変動が小さく、信頼性の高いトランジスタとなる。なお、酸化物半導体膜のキャリアトラップに捕獲された電荷は、放出するまでに要する時間が長く、あたかも固定電荷のように振る舞うことがある。そのため、不純物濃度が高く、欠陥準位密度が高い酸化物半導体膜を用いたトランジスタは、電気特性が不安定となる場合がある。

40

**【0209】**

また、C A A C - O S 膜を用いたトランジスタは、可視光や紫外光の照射による電気特性の変動が小さい。

**【0210】**

次に、微結晶酸化物半導体膜について説明する。

**【0211】**

50

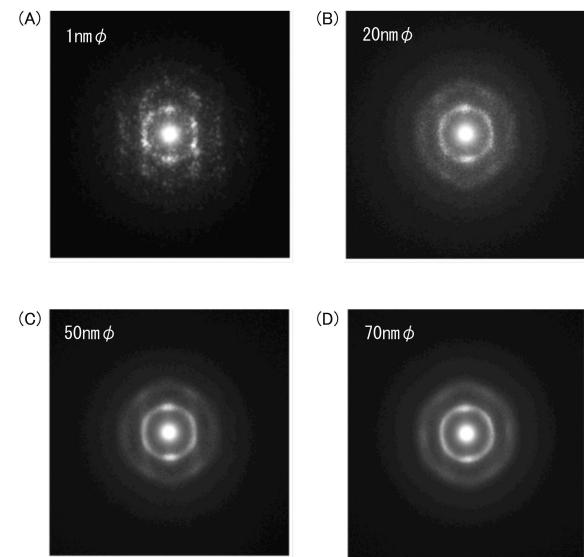

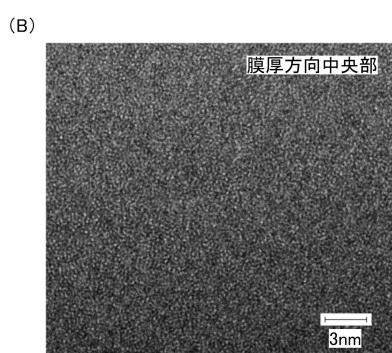

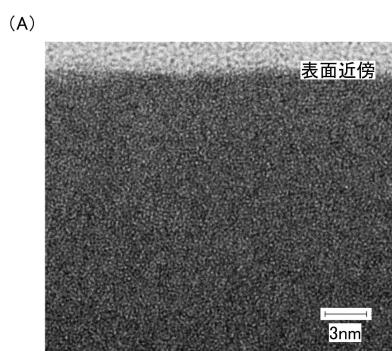

微結晶酸化物半導体膜は、TEMによる観察像では、明確に結晶部を確認することができない場合がある。微結晶酸化物半導体膜に含まれる結晶部は、1 nm以上100 nm以下、または1 nm以上10 nm以下の大きさであることが多い。特に、1 nm以上10 nm以下、または1 nm以上3 nm以下の微結晶であるナノ結晶(nano crystal)を有する酸化物半導体膜を、nc-OS(nanocrystalline Oxide Semiconductor)膜と呼ぶ。また、nc-OS膜は、例えば、TEMによる観察像では、結晶粒界を明確に確認できない場合がある。

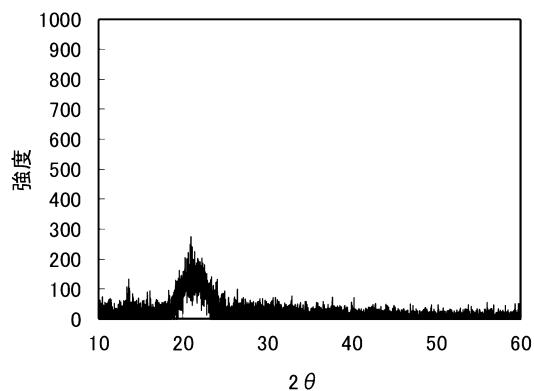

#### 【0212】

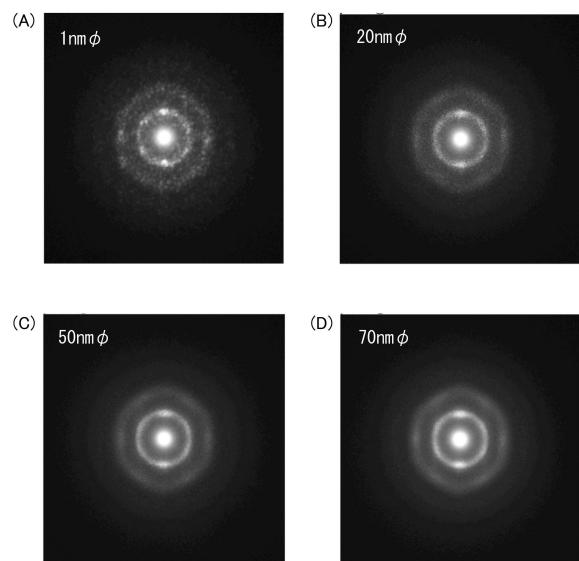

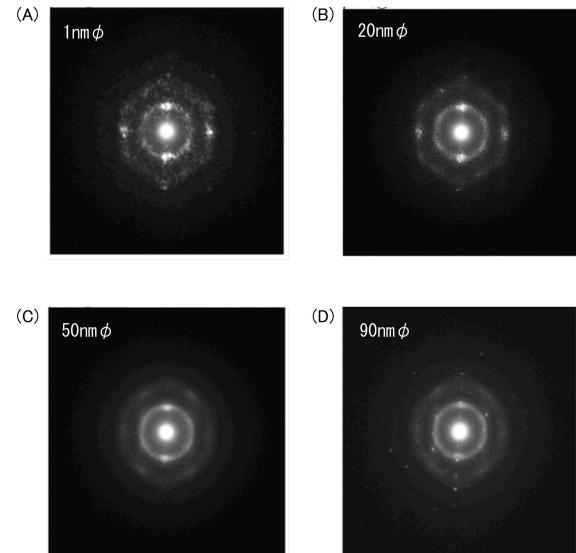

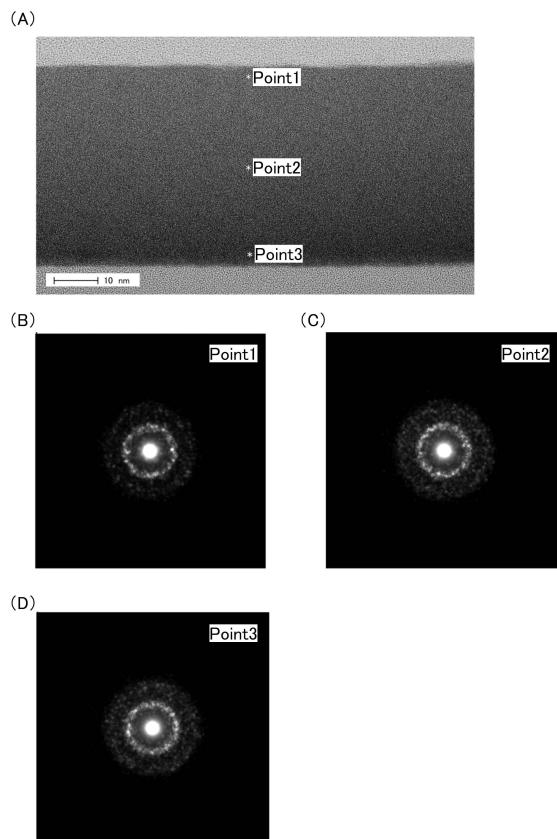

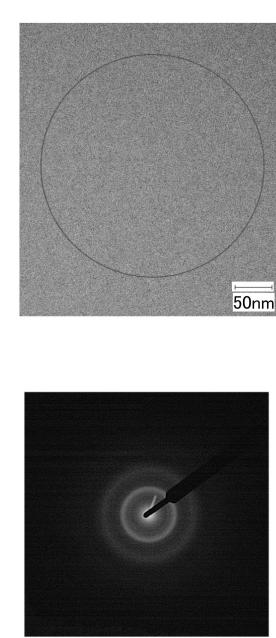

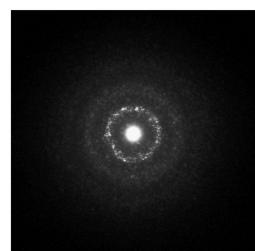

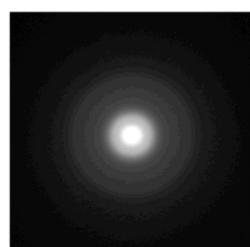

nc-OS膜は、微小な領域(例えば、1 nm以上10 nm以下の領域、特に1 nm以上3 nm以下の領域)において原子配列に周期性を有する。また、nc-OS膜は、異なる結晶部間で結晶方位に規則性が見られない。そのため、膜全体で配向性が見られない。従って、nc-OS膜は、分析方法によっては、非晶質酸化物半導体膜と区別が付かない場合がある。例えば、nc-OS膜に対し、結晶部よりも大きい径のX線を用いるXRD装置を用いて構造解析を行うと、out-of-plane法による解析では、結晶面を示すピークが検出されない。また、nc-OS膜に対し、結晶部よりも大きいプローブ径(例えば50 nm以上)の電子線を用いる電子線回折(制限視野電子線回折ともいう。)を行うと、ハローパターンのような回折パターンが観測される。一方、nc-OS膜に対し、結晶部の大きさと近いか結晶部より小さいプローブ径(例えば1 nm以上30 nm以下)の電子線を用いる電子線回折(ナノビーム電子線回折ともいう。)を行うと、スポットが観測される。また、nc-OS膜に対しナノビーム電子線回折を行うと、円を描くように(リング状に)輝度の高い領域が観測される場合がある。また、nc-OS膜に対しナノビーム電子線回折を行うと、リング状の領域内に複数のスポットが観測される場合がある。

#### 【0213】

nc-OS膜は、非晶質酸化物半導体膜よりも規則性の高い酸化物半導体膜である。そのため、nc-OS膜は、非晶質酸化物半導体膜よりも欠陥準位密度が低くなる。ただし、nc-OS膜は、異なる結晶部間で結晶方位に規則性が見られない。そのため、nc-OS膜は、CAC-OS膜と比べて欠陥準位密度が高くなる。

#### 【0214】

なお、酸化物半導体膜は、例えば、非晶質酸化物半導体膜、微結晶酸化物半導体膜、CAC-OS膜のうち、二種以上を有する積層膜であってもよい。

#### 【0215】

次に、半導体層307を所望の領域に加工することで、島状の半導体層308a、308b、308c、308dを形成する。なお、半導体層308a、308b、308c、308dの形成は、所望の領域に第2のパターニングによるマスクの形成を行い、該マスクに覆われていない領域をエッチングすることで形成することができる。エッチングとしては、ドライエッチング、ウェットエッチング、または双方を組み合わせたエッチングを用いることができる(図12(A)、(B)、(C)参照)。

#### 【0216】

次に、第1の加熱処理を行うことが好ましい。第1の加熱処理は、250以上650以下、好ましくは300以上500以下の温度で、不活性ガス雰囲気、酸化性ガスを10 ppm以上含む雰囲気、または減圧状態で行えばよい。また、第1の加熱処理の雰囲気は、不活性ガス雰囲気で加熱処理した後に、脱離した酸素を補うために酸化性ガスを10 ppm以上含む雰囲気で行ってもよい。第1の加熱処理によって、半導体層308a、308b、308c、308dに用いる酸化物半導体の結晶性を高め、さらに絶縁層305、306、及び半導体層308a、308b、308c、308dから水素や水などの不純物を除去することができる。なお、酸化物半導体を島状に加工する前に第1の加熱工程を行ってもよい。

#### 【0217】

なお、酸化物半導体をチャネルとするトランジスタに安定した電気特性を付与するため

10

20

30

40

50

には、酸化物半導体中の不純物濃度を低減し、酸化物半導体を真性または実質的に真性にすることが有効である。ここで、実質的に真性とは、酸化物半導体のキャリア密度が、 $1 \times 10^{17} / \text{cm}^3$  未満であること、好ましくは $1 \times 10^{15} / \text{cm}^3$  未満であること、さらに好ましくは $1 \times 10^{13} / \text{cm}^3$  未満であることを指す。

#### 【0218】

また、酸化物半導体において、水素、窒素、炭素、シリコン、及び主成分以外の金属元素は不純物となる。例えば、水素及び窒素は、ドナー準位を形成し、キャリア密度を増大させてしまう。また、シリコンは、酸化物半導体中で不純物準位を形成する。当該不純物準位はトラップとなり、トランジスタの電気特性を劣化させることがある。

#### 【0219】

酸化物半導体を真性または実質的に真性とするとには、S I M S における分析において、シリコン濃度を $1 \times 10^{19} \text{ atoms/cm}^3$  未満、好ましくは $5 \times 10^{18} \text{ atoms/cm}^3$  未満、さらに好ましくは $1 \times 10^{18} \text{ atoms/cm}^3$  未満とする。また、水素濃度は、 $2 \times 10^{20} \text{ atoms/cm}^3$  以下、好ましくは $5 \times 10^{19} \text{ atoms/cm}^3$  以下、さらに好ましくは $5 \times 10^{18} \text{ atoms/cm}^3$  以下とする。また、窒素濃度は、 $5 \times 10^{19} \text{ atoms/cm}^3$  未満、好ましくは $5 \times 10^{18} \text{ atoms/cm}^3$  以下、より好ましくは $1 \times 10^{18} \text{ atoms/cm}^3$  以下とする。また、炭素濃度は、 $1 \times 10^{18} \text{ atoms/cm}^3$  以下、さらに好ましくは $5 \times 10^{17} \text{ atoms/cm}^3$  以下とする。

#### 【0220】

また、酸化物半導体が結晶を含む場合、シリコンや炭素が高濃度で含まれると、酸化物半導体の結晶性を低下させことがある。酸化物半導体の結晶性を低下させないためには、シリコン濃度を $1 \times 10^{19} \text{ atoms/cm}^3$  未満、好ましくは $5 \times 10^{18} \text{ atoms/cm}^3$  未満とすればよい。また、炭素濃度を $1 \times 10^{19} \text{ atoms/cm}^3$  未満、好ましくは $5 \times 10^{18} \text{ atoms/cm}^3$  未満とすればよい。

#### 【0221】

また、上述のように高純度化された酸化物半導体をチャネル形成領域に用いたトランジスタのオフ電流は極めて小さく、トランジスタのチャネル幅で規格化したオフ電流は、数  $y \text{ A}/\mu\text{m} \sim \text{数 } z \text{ A}/\mu\text{m}$  にまで低減することが可能となる。

#### 【0222】

また、酸化物半導体は、膜中の局在準位を低減することで、酸化物半導体を用いたトランジスタに安定した電気特性を付与することができる。なお、トランジスタに安定した電気特性を付与するためには、酸化物半導体中の C P M 測定 ( C P M : Constant Photocurrent Method ) で得られる局在準位による吸収係数は、 $1 \times 10^{-3} / \text{cm}$  未満、好ましくは $1 \times 10^{-4} / \text{cm}$  未満とすればよい。

#### 【0223】

ここで、酸化物半導体膜の局在準位について説明する。

#### 【0224】

まず、ナノ結晶酸化物半導体膜を C P M 測定で評価した結果について説明する。

#### 【0225】

まず、測定試料の構造について説明する。

#### 【0226】

測定試料は、ガラス基板上に設けられた酸化物半導体膜と、該酸化物半導体膜に接する一対の電極と、酸化物半導体膜及び一対の電極を覆う絶縁膜と、を有する。

#### 【0227】

次に、測定試料に含まれる酸化物半導体膜の形成方法について説明する。

#### 【0228】

I n - G a - Z n 酸化物 ( I n : G a : Z n = 1 : 1 : 1 [ 原子数比 ] ) であるターゲ

10

20

30

40

50

ットを用い、成膜ガスとしてアルゴンガスを30 sccm、酸素ガスを15 sccm用い、圧力を0.4 Paとし、基板温度を室温とし、DC電力を0.5 kW印加する条件を用いたスパッタリング法により、第1の酸化物半導体膜を形成した。なお、第1の酸化物半導体膜はナノ結晶酸化物半導体膜である。

## 【0229】

また、第1の酸化物半導体膜を、450の窒素雰囲気で1時間加熱した後、450の酸素雰囲気で1時間加熱することで、第1の酸化物半導体膜に含まれる水素を脱離させる処理及び第1の酸化物半導体膜に酸素を供給する処理を行い、第2の酸化物半導体膜を形成した。なお、第2の酸化物半導体膜はナノ結晶酸化物半導体膜である。

## 【0230】

次に、第1の酸化物半導体膜を有する測定試料、及び第2の酸化物半導体膜を有する測定試料についてCPM測定を行った。具体的には、酸化物半導体膜に接して設けた第1の電極および第2の電極間に電圧を印加した状態で光電流値が一定となるように端子間の測定試料面に照射する光量を調整し、所望の波長の範囲において照射光量から吸収係数を導出した。

## 【0231】

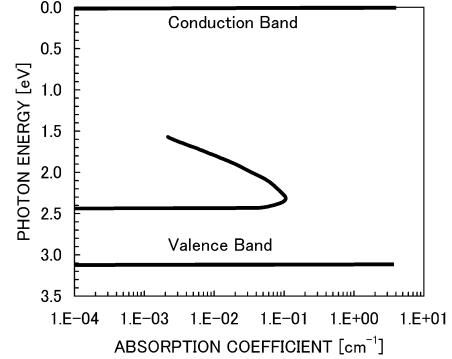

各測定試料をCPM測定して得られた吸収係数からバンドテイル起因の吸収係数を除いた吸収係数、即ち欠陥に起因する吸収係数を図60に示す。図60において、横軸は吸収係数を表し、縦軸は光エネルギーを表す。なお、図60の縦軸において、酸化物半導体膜の伝導帯の下端を0eVとし、価電子帯の上端を3.15eVとする。また、図60において、各曲線は吸収係数と光エネルギーの関係を示す曲線であり、欠陥準位に相当する。

## 【0232】

図60(A)は、第1の酸化物半導体膜を有する測定試料の測定結果であり、欠陥準位による吸収係数は、 $5.28 \times 10^{-1} \text{ cm}^{-1}$ であった。図60(B)は、第2の酸化物半導体膜を有する測定試料の測定結果であり、欠陥準位による吸収係数は、 $1.75 \times 10^{-2} \text{ cm}^{-1}$ であった。

## 【0233】

従って、加熱処理により、酸化物半導体膜に含まれる欠陥を低減することができる。

## 【0234】

なお、第1の酸化物半導体膜及び第2の酸化物半導体膜に関し、X線反射率法(XRR)(X-ray Reflectometry)を用いた膜密度の測定を行った。第1の酸化物半導体膜の膜密度は、 $5.9 \text{ g/cm}^3$ であり、第2の酸化物半導体膜の膜密度は $6.1 \text{ g/cm}^3$ であった。

## 【0235】

従って、加熱処理により、酸化物半導体膜の膜密度を高めることができる。

## 【0236】

即ち、酸化物半導体膜において、膜密度が高い程、膜中に含まれる欠陥が少ないことがわかる。

## 【0237】

次に、AAC-OSをCPM測定で評価した結果について説明する。

40

## 【0238】

まず、CPM測定した試料の構造について説明する。

## 【0239】

測定試料は、ガラス基板上に設けられた酸化物半導体膜と、該酸化物半導体膜に接する一対の電極と、酸化物半導体膜及び一対の電極を覆う絶縁膜と、を有する。

## 【0240】

次に、測定試料に含まれる酸化物半導体膜の形成方法について説明する。

## 【0241】

In-Ga-Zn酸化物( In : Ga : Zn = 1 : 1 : 1 [原子数比] )であるターゲットを用い、成膜ガスとしてアルゴンガスを30 sccm、酸素ガスを15 sccm用い

50

、圧力を0.4Paとし、基板温度を400とし、DC電力を0.5kW印加する条件を用いたスパッタリング法により、酸化物半導体膜を形成した。次に、450の窒素雰囲気で1時間加熱した後、450の酸素雰囲気で1時間加熱して、酸化物半導体膜に含まれる水素を脱離させる処理及び酸化物半導体膜に酸素を供給する処理を行った。なお、当該酸化物半導体膜はCAAC-OS膜である。

#### 【0242】

次に、酸化物半導体膜を有する測定試料についてCPM測定を行った。具体的には、酸化物半導体膜に接して設けた第1の電極および第2の電極間に電圧を印加した状態で光電流値が一定となるように端子間の試料面に照射する光量を調整し、所望の波長の範囲において照射光量から吸収係数を導出した。

10

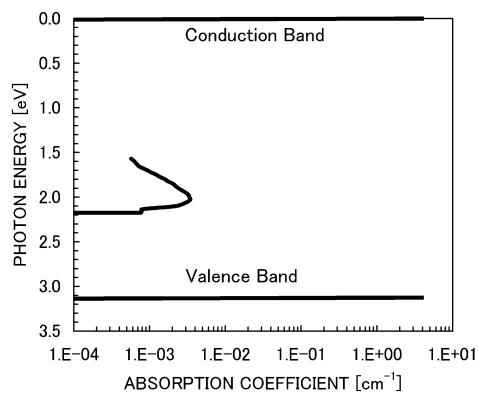

#### 【0243】

各測定試料をCPM測定して得られた吸収係数からバンドテイル起因の吸収係数を除いた吸収係数、即ち欠陥に起因する吸収係数を図61に示す。図61において、横軸は吸収係数を表し、縦軸は光エネルギーを表す。なお、図61の縦軸において、酸化物半導体膜の伝導帯の下端を0eVとし、価電子帯の上端を3.15eVとする。また、図61において、各曲線は吸収係数と光エネルギーの関係を示す曲線であり、欠陥準位に相当する。

#### 【0244】

図61に示す曲線において、欠陥準位による吸収係数は、 $5.86 \times 10^{-4} \text{ cm}^{-1}$ であった。即ち、CAAC-OS膜は、欠陥準位による吸収係数が $1 \times 10^{-3} / \text{cm未満}$ 、好ましくは $1 \times 10^{-4} / \text{cm未満}$ であり、欠陥準位密度の低い膜である。

20

#### 【0245】

なお、酸化物半導体膜に関し、X線反射率法(XRR)を用いた膜密度の測定を行った。酸化物半導体膜の膜密度は、 $6.3 \text{ g/cm}^3$ であった。即ち、CAAC-OS膜は、膜密度の高い膜である。

#### 【0246】

次に、結晶状態における酸化物半導体(OSと示す。)およびシリコン半導体(Siと示す。)の対比を表1に示す。なお、酸化物半導体には、In-Ga-Zn系酸化物を用いる。

#### 【0247】

#### 【表1】

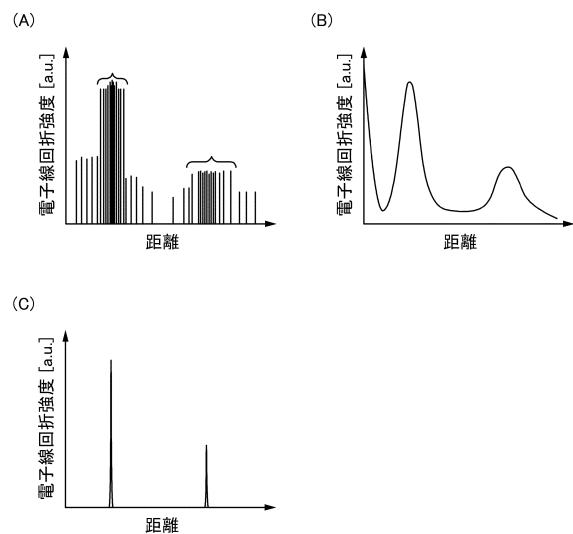

30

|    |                | 非晶質                 | 微結晶          | 多結晶     | 連続結晶         | 単結晶   |

|----|----------------|---------------------|--------------|---------|--------------|-------|

| OS | a-OS<br>a-OS:H | nc-OS<br>$\mu$ c-OS | 多結晶OS        | CAAC-OS | 単結晶OS        |       |

|    | 極微<br>電子線回折    | ハロー                 | リング<br>+スポット | スポット    | スポット         | スポット  |

|    | 結晶部            | —                   | nm~ $\mu$ m  | 不連続     | 連続的に<br>つながる | —     |

|    | DOS            | 高い                  | やや低い         | —       | 低い           | 極めて低い |

|    | 密度             | 低い                  | 中程度          | —       | 高い           | —     |

40

| Si | a-Si<br>a-Si:H | nc-Si<br>$\mu$ c-Si | 多結晶Si | CGシリコン | 単結晶Si |

|----|----------------|---------------------|-------|--------|-------|

|    |                |                     |       |        |       |

#### 【0248】

酸化物半導体の結晶状態には、例えば、表1に示すように、非晶質酸化物半導体(a-OS、a-OS:H)、微結晶酸化物半導体(nc-OS、 $\mu$ c-OS)、多結晶酸化物

50

半導体（多結晶OS）、連続結晶酸化物半導体（CAC-OS）、単結晶酸化物半導体（単結晶OS）などがある。なお、シリコンの結晶状態には、例えば、表1に示すように、非晶質シリコン（a-Siやa-Si:H）、微結晶シリコン（nc-Si、 $\mu$ c-Si）、多結晶シリコン（多結晶Si）、連続結晶シリコン（CG（Continuous Grain）シリコン）、単結晶シリコン（単結晶Si）などがある。

#### 【0249】

各結晶状態における酸化物半導体に対し、ビーム径を10nm以下に収束させた電子線を用いる電子線回折（極微電子線回折）を行うと、以下のような電子線回折パターン（極微電子線回折パターン）が観測される。非晶質酸化物半導体では、ハロー（ハローリングまたはハローとも言われる。）が観測される。微結晶酸化物半導体では、スポットまたはノおよびリングパターンが観測される。多結晶酸化物半導体では、スポットが観測される。連続結晶酸化物半導体では、スポットが観測される。単結晶酸化物半導体では、スポットが観測される。10

#### 【0250】

なお、極微電子線回折パターンより、微結晶酸化物半導体は、結晶部がナノメートル（nm）からマイクロメートル（ $\mu$ m）の径であることがわかる。多結晶酸化物半導体は、結晶部と結晶部との間に粒界を有し、境界が不連続であることがわかる。連続結晶酸化物半導体は、結晶部と結晶部との間に境界が観測されず、連続的に繋がることがわかる。

#### 【0251】

各結晶状態における酸化物半導体の密度について説明する。非晶質酸化物半導体の密度は低い。微結晶酸化物半導体の密度は中程度である。連続結晶酸化物半導体の密度は高い。即ち、連続結晶酸化物半導体の密度は微結晶酸化物半導体の密度より高く、微結晶酸化物半導体の密度は非晶質酸化物半導体の密度より高い。20

#### 【0252】

各結晶状態における酸化物半導体に存在するDOSの特徴を説明する。非晶質酸化物半導体はDOSが高い。微結晶酸化物半導体はDOSがやや低い。連続結晶酸化物半導体はDOSが低い。単結晶酸化物半導体はDOSが極めて低い。即ち、単結晶酸化物半導体は連続結晶酸化物半導体よりDOSが低く、連続結晶酸化物半導体は微結晶酸化物半導体よりDOSが低く、微結晶酸化物半導体は非晶質酸化物半導体よりDOSが低い。30

#### 【0253】

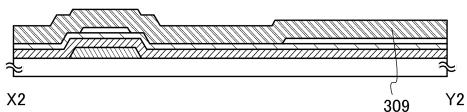

次に、絶縁層306、及び半導体層308a、308b、308c、308d上に導電層309を形成する（図13（A）、（B）、（C）参照）。

#### 【0254】

導電層309としては、導電材料として、アルミニウム、チタン、クロム、ニッケル、銅、イットリウム、ジルコニアム、モリブデン、銀、タンタル、またはタングステンからなる単体金属、またはこれを主成分とする合金を単層構造または積層構造として用いる。例えば、アルミニウム膜上にチタン膜を積層する二層構造、タングステン膜上にチタン膜を積層する二層構造、銅-マグネシウム-アルミニウム合金膜上に銅膜を積層する二層構造、チタン膜または窒化チタン膜と、そのチタン膜または窒化チタン膜上に重ねてアルミニウム膜または銅膜を積層し、さらにその上にチタン膜または窒化チタン膜を形成する三層構造、モリブデン膜または窒化モリブデン膜と、そのモリブデン膜または窒化モリブデン膜上に重ねてアルミニウム膜または銅膜を積層し、さらにその上にモリブデン膜または窒化モリブデン膜を形成する三層構造等がある。なお、酸化インジウム、酸化錫または酸化亜鉛を含む透明導電材料を用いてもよい。また、導電層309としては、例えば、スパッタリング法を用いて形成することができる。40

#### 【0255】

次に、導電層309を所望の領域に加工することで、導電層310a、310b、310c、310d、310e、310f、310gを形成する。なお、導電層310a、310b、310c、310d、310e、310f、310gの形成は、所望の領域に第3のパターニングによるマスクの形成を行い、該マスクに覆われていない領域をエッチン50

グすることで、形成することができる（図14（A）、（B）、（C）参照）。

**【0256】**

なお、本実施の形態では、導電層310a、310b、310d、310e、310f、310gとしては、半導体層308a、308b、308d上に形成したが、絶縁層306と半導体層308a、308b、308dの間に形成してもよい。

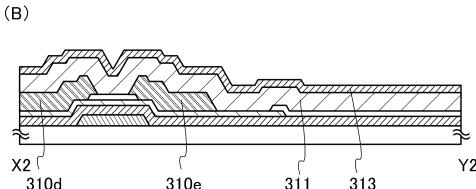

**【0257】**

次に、絶縁層306、半導体層308a、308b、308c、308d及び導電層310a、310b、310c、310d、310e、310f、310gを覆うように、絶縁層311を形成する（図15（A）、（B）、（C）参照）。

**【0258】**

絶縁層311としては、半導体層308a、308b、308c、308dとして用いる酸化物半導体との界面特性を向上させるため、酸素を含む無機絶縁材料を用いることができる。また、絶縁層311としては、例えば、PE-CVD法を用いて形成することができる。

**【0259】**

一例としては、絶縁層311としては、厚さ150nm以上400nm以下の酸化シリコン膜、酸化窒化シリコン膜、酸化アルミニウム膜等を用いることができる。本実施の形態においては、絶縁層311として、厚さ300nmの酸化窒化シリコン膜を用いる。

**【0260】**

次に、絶縁層311を所望の領域に加工することで、開口部362、363を形成する。また、絶縁層311は、開口部362が形成された絶縁層312となる。なお、絶縁層312、及び開口部362の形成は、所望の領域に第4のパターニングによるマスクの形成を行い、該マスクに覆われていない領域をエッチングすることで、形成することができる。（図16（A）、（B）、（C）参照）。

**【0261】**

なお、開口部362、363は、半導体層308c、308dが露出するように形成する。開口部362、363の形成方法としては、例えば、ドライエッチング法を用いることができる。ただし、開口部362、363の形成方法としては、これに限定されず、ウェットエッチング法、またはドライエッチング法とウェットエッチング法を組み合わせた形成方法としてもよい。

**【0262】**

次に、絶縁層312、及び半導体層308c、308d上に絶縁層313を形成する（図17（A）、（B）、（C）参照）。

**【0263】**

絶縁層313は、外部からの不純物、例えば、水、アルカリ金属、アルカリ土類金属等が、酸化物半導体層へ拡散するのを防ぐ材料で形成される膜であり、更には水素を含む。このため、絶縁層313の水素が半導体層308c、308dに拡散すると、該半導体層308c、308dにおいて水素は酸素と結合し、キャリアである電子が生成される。この結果、半導体層308c、308dは、導電性が高くなり透光性を有する導電層となる。

**【0264】**

なお、本実施の形態においては、半導体層308c、308dに接して絶縁層313から、水素を導入する方法について、例示したがこれに限定されない。例えば、トランジスタのチャネル形成領域となる部分にマスクを設け、該マスクに覆われていない領域に、水素、ボロン、リン、または窒素を導入してもよい。例えば、イオン注入法、イオンドーピング法、プラズマイマージョンイオンインプランテーション法などを用いて、半導体層308c、308dに水素、ボロン、リン、または窒素を導入することができる。また、半導体層308c、308d上にあらかじめ、透光性を有する導電膜、例えば、ITO等を形成しておいてもよい。

**【0265】**

10

20

30

40

50

一例としては、絶縁層313としては、厚さ150nm以上400nm以下の窒化シリコン膜、窒化酸化シリコン膜等を用いることができる。本実施の形態においては、絶縁層313として、厚さ150nmの窒化シリコン膜を用いる。

#### 【0266】

また、上記窒化シリコン膜は、ブロック性を高めるために、高温で成膜されることが好ましく、例えば基板温度100以上基板の歪み点以下、より好ましくは300以上400以下の温度で加熱して成膜することが好ましい。また高温で成膜する場合は、半導体層308a、308bとして用いる酸化物半導体から酸素が脱離し、キャリア濃度が上昇する現象が発生するがあるため、このような現象が発生しない温度とする。

#### 【0267】

次に、絶縁層313を所望の領域に加工することで、開口部364a、364b、364cを形成する。また、絶縁層313は、開口部364a、364b、364cが形成された絶縁層314となる。なお、絶縁層314、及び開口部364a、364b、364cは、所望の領域に第5のパターニングによるマスクの形成を行い、該マスクに覆われていない領域をエッチングすることで形成することができる（図18（A）、（B）、（C）参照）。

#### 【0268】

また、開口部364aは、導電層304bが露出するように形成する。また、開口部364bは、導電層310cが露出するように形成する。また、開口部364cは、導電層310eが露出するように形成する。

#### 【0269】

なお、開口部364a、364b、364cの形成方法としては、例えば、ドライエッチング法を用いることができる。ただし、開口部364a、364b、364cの形成方法としては、これに限定されず、ウェットエッチング法、またはドライエッチング法とウェットエッチング法を組み合わせた形成方法としてもよい。

#### 【0270】

次に、開口部364a、364b、364cを覆うように絶縁層314上に導電層315を形成する（図19（A）、（B）、（C）参照）。

#### 【0271】

導電層315としては、酸化タンクステンを含むインジウム酸化物、酸化タンクステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム錫酸化物（以下、ITOと示す。）、インジウム亜鉛酸化物、酸化ケイ素を添加したインジウム錫酸化物などの透光性を有する導電性材料を用いることができる。また、導電層315としては、例えば、スパッタリング法を用いて形成することができる。

#### 【0272】

次に、導電層315を所望の領域に加工することで、導電層316a、316bを形成する。なお、導電層316a、316bの形成は、所望の領域に第6のパターニングによるマスクの形成を行い、該マスクに覆われていない領域をエッチングすることで形成することができる（図20（A）、（B）、（C）参照）。

#### 【0273】

以上の工程でトランジスタを有する駆動回路部104と、トランジスタを有する画素回路部108と、抵抗素子114と、を同一基板上に形成することができる。なお、本実施の形態に示す作製工程においては、第1乃至第6のパターニング、すなわち6枚のマスクでトランジスタ、容量素子、及び抵抗素子を同時に形成することができる。

#### 【0274】

次に、基板302に対向して設けられる基板342上に形成される構造について、以下説明を行う。

#### 【0275】

まず、基板342を準備する。基板342としては、基板302に示す材料を援用する

10

20

30

40

50

ことができる。次に、基板 342 上に遮光層 344、及び有色層 346 を形成する（図 21（A）、（B）、（C）参照）。

【0276】

遮光層 344 としては、特定の波長帯域の光を遮光する機能を有していればよく、金属膜または黒色顔料等を含んだ有機絶縁膜などを用いることができる。

【0277】

有色層 346 としては、特定の波長帯域の光を透過する有色層であればよく、例えば、赤色の波長帯域の光を透過する赤色（R）のカラーフィルタ、緑色の波長帯域の光を透過する緑色（G）のカラーフィルタ、青色の波長帯域の光を透過する青色（B）のカラーフィルタなどを用いることができる。各カラーフィルタは、様々な材料を用いて、印刷法、インクジェット法、フォトリソグラフィ技術を用いたエッチング方法などでそれぞれ所望の位置に形成する。

【0278】

次に、遮光層 344、及び有色層 346 上に絶縁層 348 を形成する（図 22（A）、（B）、（C）参照）。

【0279】

絶縁層 348 としては、例えば、アクリル系樹脂等の有機絶縁膜を用いることができる。絶縁層 348 を形成することによって、例えば、有色層 346 中に含まれる不純物等を液晶層 320 側に拡散することを抑制することができる。ただし、絶縁層 348 は、必ずしも形成する必要はなく、絶縁層 348 を形成しない構造としてもよい。

【0280】

次に、絶縁層 348 上に導電層 350 を形成する（図 23（A）、（B）、（C）参照）。導電層 350 としては、導電層 315 に示す材料を援用することができる。

【0281】

以上の工程で基板 342 上に形成される構造を形成することができる。

【0282】

次に、基板 302 と基板 342 上、より詳しくは基板 302 上に形成された絶縁層 314、導電層 316a、316b と、基板 342 上に形成された導電層 350 上に、それぞれ配向膜 318 と配向膜 352 を形成する。配向膜 318、352 は、ラビング法、光配向法等を用いて形成することができる。その後、基板 302 と、基板 342 との間に液晶層 320 を形成する。液晶層 320 の形成方法としては、ディスペンサ法（滴下法）や、基板 302 と基板 342 を貼り合わせてから毛細管現象を用いて液晶を注入する注入法を用いることができる。

【0283】

以上の工程で、図 9 に示す表示装置を作製することができる。

【0284】

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせができる。

【0285】

（実施の形態 4）

本実施の形態では、本発明の一態様の表示装置について、図 24 乃至図 29 を用いて説明を行う。

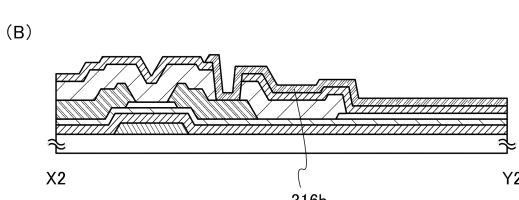

【0286】

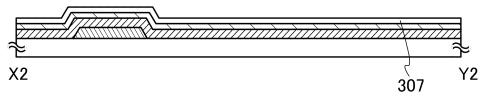

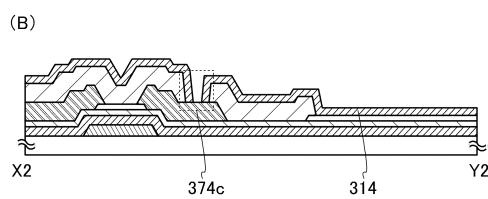

図 24 に示す表示装置は、図 9 に示す表示装置の変形例であり、図 25 乃至図 29 は、図 24 に示す表示装置の作製方法を示す断面図である。

【0287】

なお、図 24 乃至図 29 において、先の実施の形態に示す同様の箇所、または同様の機能を有する部分については、同様の符号を付し、その詳細の説明は省略する。

【0288】

図 24 に示す表示装置は、駆動回路部 104 と、画素回路部 108 と、抵抗素子 114

10

20

30

40

50

と、を有する。図24に示す表示装置について、以下説明を行う。

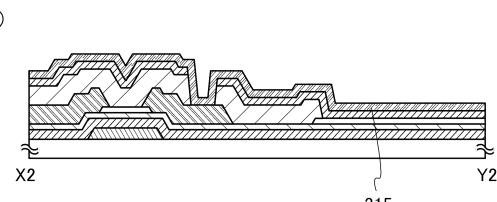

**【0289】**

(駆動回路部)

駆動回路部104は、基板302と、基板302上に形成された導電層304a、304bと、基板302、及び導電層304a、304b上に形成された絶縁層305と、絶縁層305上に形成された絶縁層306と、絶縁層306上に形成され、導電層304aと重畠する位置に形成された半導体層308aと、絶縁層306、及び半導体層308a上に形成された導電層310a、310bと、絶縁層306上に形成された導電層310cと、半導体層308a、及び導電層310a、310b、310cを覆うように形成された絶縁層312と、絶縁層312上に形成された絶縁層314と、絶縁層314上に形成された導電層316aと、を有する。10

**【0290】**

なお、導電層316aは、導電層304bと、導電層310cを接続する配線としての機能を有する。導電層304bは、絶縁層305、306、312、314に形成された開口部を介して、導電層310cは、絶縁層312、314に形成された開口部を介して、導電層316aにより接続される。

**【0291】**

(画素回路部)

画素回路部108は、基板302と、基板302上に形成された導電層304cと、基板302、及び導電層304c上に形成された絶縁層305と、絶縁層305上に形成された絶縁層306と、絶縁層306上に形成され、導電層304cと重畠する位置に形成された半導体層308bと、絶縁層306上に形成された半導体層308cと、絶縁層306、及び半導体層308b上に形成された導電層310d、310eと、半導体層308b、及び導電層310d、310eを覆うように形成され、且つ半導体層308cの一部を覆う絶縁層312と、絶縁層312上に形成され、且つ半導体層308c上に形成された絶縁層314と、絶縁層314上に形成され、且つ導電層310eに接続された導電層316bと、を有する。20

**【0292】**

なお、導電層316bは、絶縁層312、314に形成された開口部を介して、導電層310eに接続される。30

**【0293】**

(抵抗素子)

抵抗素子114は、基板302と、基板302上に形成された絶縁層305と、絶縁層305上に形成された絶縁層306と、絶縁層306上に形成された半導体層308dと、絶縁層306、及び半導体層308d上に形成された導電層310f、310gと、導電層310f、310g上に形成された絶縁層312と、絶縁層312、導電層310f、310g、及び半導体層308d上に形成された絶縁層314と、を有する。

**【0294】**

本実施の形態に示す表示装置は、先の実施の形態の図9に示す表示装置との違いとして、開口部の形状が異なる。より、具体的には、導電層304b、310c、310e上に形成される開口部は、2回のエッチング工程により形成されることを特徴とする。40

**【0295】**

図24に示すように開口部の形状を変えることによって、以下のよう効果を得ることができる。

**【0296】**

導電層304b、310c、310eの1回目のエッチング工程で形成される開口部の内側に絶縁層314が形成されており、開口部から入り込みうる不純物、例えば、水、アルカリ金属、アルカリ土類金属等が、内部に拡散することを抑制することができる。

**【0297】**

なお、本実施の形態に示す表示装置は、駆動回路部104、及び画素回路部108が有50

するトランジスタと、抵抗素子 114 と、を同時に形成することができる。したがって、製造コスト等を増やさずに抵抗素子 114 を形成することが可能となる。

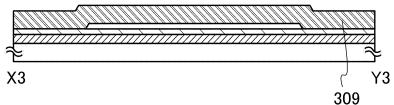

#### 【0298】

次に、図 24 に示す表示装置の作製方法について、図 25 乃至図 29 を用いて、以下説明を行う。

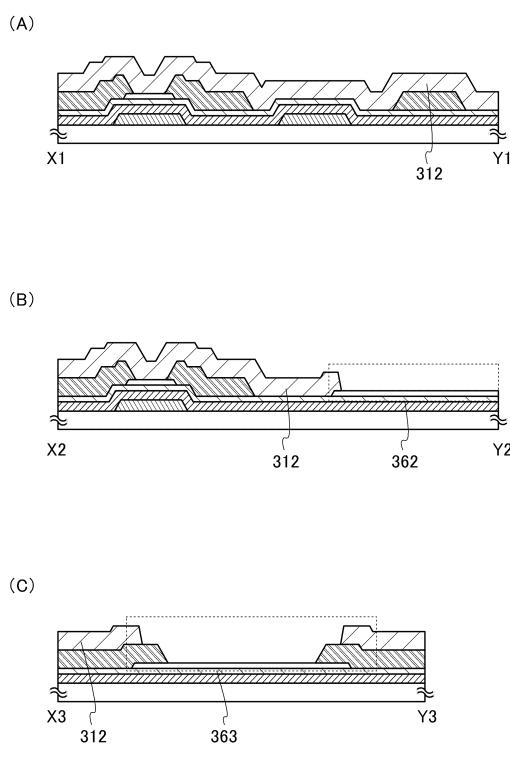

#### 【0299】

なお、駆動回路部 104 の作製方法については、図 25 (A)、図 26 (A)、図 27 (A)、図 28 (A)、及び図 29 (A) に示し、画素回路部 108 の作製方法については、図 25 (B)、図 26 (B)、図 27 (B)、図 28 (B)、及び図 29 (B) に示し、抵抗素子 114 の作製方法については、図 25 (C)、図 26 (C)、図 27 (C)、図 28 (C)、及び図 29 (C) に示す。

10

#### 【0300】

まず、先の実施の形態の図 15 に示す構造まで作製する。つまり、3枚のマスクを用いてパターニング、及びエッチングまで行った基板を作製する。

#### 【0301】

次に、絶縁層 311 を所望の領域に加工することで、開口部 372a、372b、372c、372d、372e を形成する。また、絶縁層 311 は、開口部 372a、372b、372c、372d、372e が形成された絶縁層 312 となる。なお、絶縁層 312、及び開口部 372a、372b、372c、372d、372e の形成は、所望の領域に第 4 のパターニングによるマスクの形成を行い、該マスクに覆われていない領域をエッチングすることで、形成することができる。(図 25 (A)、(B)、(C) 参照)。

20

#### 【0302】

なお、開口部 372a は、絶縁層 305 が露出するように形成する。また、開口部 372b、372c は、それぞれ、導電層 310c、310e が露出するように形成する。また、開口部 372d、372e は、それぞれ、半導体層 308c、308d が露出するように形成する。開口部 372a、372b、372c、372d、372e の形成方法としては、例えば、ドライエッチング法を用いることができる。ただし、開口部 372a、372b、372c、372d、372e の形成方法としては、これに限定されず、ウエットエッチング法、またはドライエッチング法とウエットエッチング法を組み合わせた形成方法としてもよい。

30

#### 【0303】

次に、開口部 372a、372b、372c、372d、372e を覆い、且つ絶縁層 305、312、及び半導体層 308c、308d 上に絶縁層 313 を形成する(図 26 (A)、(B)、(C) 参照)。

#### 【0304】

絶縁層 313 は、外部からの不純物、例えば、水、アルカリ金属、アルカリ土類金属等が、酸化物半導体層へ拡散するのを防ぐ材料で形成される膜であり、更には水素を含む。このため、絶縁層 313 の水素が半導体層 308c、308d に拡散すると、該半導体層 308c、308d において水素は酸素と結合し、キャリアである電子が生成される。この結果、半導体層 308c、308d は、導電性が高くなり透光性を有する導電層となる。

40

#### 【0305】

次に、絶縁層 313 を所望の領域に加工することで、開口部 374a、374b、374c を形成する。また、絶縁層 313 は、開口部 374a、374b、374c が形成された絶縁層 314 となる。なお、絶縁層 314、及び開口部 374a、374b、374c は、所望の領域に第 5 のパターニングによるマスクの形成を行い、該マスクに覆われていない領域をエッチングすることで形成することができる(図 27 (A)、(B)、(C) 参照)。

#### 【0306】

また、開口部 374a は、導電層 304b が露出するように形成する。また、開口部 3

50

74bは、導電層310cが露出するように形成する。また、開口部374cは、導電層310eが露出するように形成する。

#### 【0307】

なお、開口部374a、374b、374cの形成方法としては、例えば、ドライエッチング法を用いることができる。ただし、開口部374a、374b、374cの形成方法としては、これに限定されず、ウェットエッチング法、またはドライエッチング法とウェットエッチング法を組み合わせた形成方法としてもよい。

#### 【0308】

次に、開口部374a、374b、374cを覆うように絶縁層314上に導電層315を形成する(図28(A)、(B)、(C)参照)。

10

#### 【0309】

次に、導電層315を所望の領域に加工することで、導電層316a、316bを形成する。なお、導電層316a、316bの形成は、所望の領域に第6のパターニングによるマスクの形成を行い、該マスクに覆われていない領域をエッチングすることで形成することができる(図29(A)、(B)、(C)参照)。

#### 【0310】

以上の工程でトランジスタを有する駆動回路部104と、トランジスタを有する画素回路部108と、抵抗素子114と、を同一基板上に形成することができる。なお、本実施の形態に示す作製工程においては、第1乃至第6のパターニング、すなわち6枚のマスクでトランジスタ、及び容量素子、及び抵抗素子を同時に形成することができる。

20

#### 【0311】

本実施の形態に示す構成は、他の実施の形態に示す構成と適宜組み合わせて用いることができる。

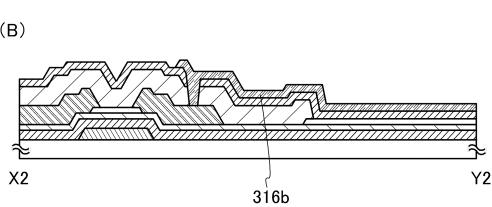

#### 【0312】

##### (実施の形態5)

本実施の形態では、本発明の一態様の表示装置について、図30乃至図35を用いて説明を行う。

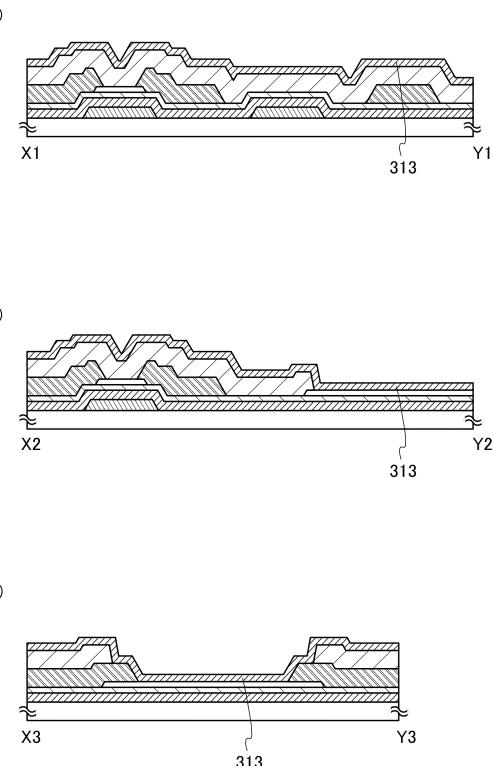

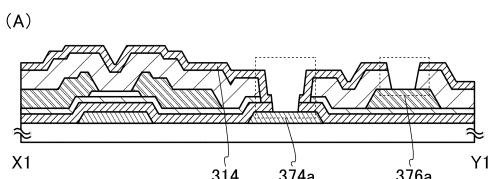

#### 【0313】

図30に示す表示装置は、図9に示す表示装置の変形例であり、図31乃至図35は、図30に示す表示装置の作製方法を示す断面図である。

30

#### 【0314】

なお、図30乃至図35において、先の実施の形態に示す同様の箇所、または同様の機能を有する部分については、同様の符号を付し、その詳細の説明は省略する。

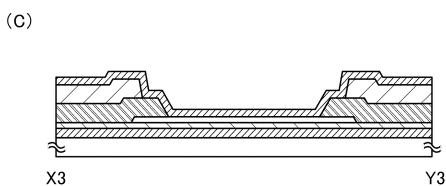

#### 【0315】

図30に示す表示装置は、駆動回路部104と、画素回路部108と、抵抗素子114と、を有する。図30に示す表示装置について、以下説明を行う。

#### 【0316】

##### (駆動回路部)

駆動回路部104は、基板302と、基板302上に形成された導電層304a、304bと、基板302、及び導電層304a、304b上に形成された絶縁層305と、絶縁層305上に形成された絶縁層306と、絶縁層306上に形成され、導電層304aと重畠する位置に形成された半導体層308aと、絶縁層306、及び半導体層308a上に形成された導電層310a、310bと、絶縁層306上に形成された導電層310cと、半導体層308a、及び導電層310a、310b、310cを覆うように形成された絶縁層312と、絶縁層312上に形成された絶縁層314と、絶縁層314上に形成された導電層316aと、を有する。

40

#### 【0317】

なお、導電層316aは、導電層304bと、導電層310cを接続する配線としての機能を有する。導電層304bは、絶縁層305、306、312、314に形成された開口部を介して、導電層310cは、絶縁層312、314に形成された開口部を介して

50

、導電層 316a により接続される。

**【0318】**

(画素回路部)

画素回路部 108 は、基板 302 と、基板 302 上に形成された導電層 304c と、基板 302、及び導電層 304c 上に形成された絶縁層 305 と、絶縁層 305 上に形成された絶縁層 306 と、絶縁層 306 上に形成され、導電層 304c と重畳する位置に形成された半導体層 308b と、絶縁層 306 上に形成された半導体層 308c と、絶縁層 306、及び半導体層 308b 上に形成された導電層 310d、310e と、半導体層 308b、及び導電層 310d、310e を覆うように形成され、且つ半導体層 308c の一部を覆う絶縁層 312 と、絶縁層 312 上に形成され、且つ半導体層 308c 上に形成された絶縁層 314 と、絶縁層 314 上に形成され、且つ導電層 310e に接続された導電層 316b と、を有する。

10

**【0319】**

なお、導電層 316b は、絶縁層 312、314 に形成された開口部を介して、導電層 310e に接続される。

**【0320】**

(抵抗素子)

抵抗素子 114 は、基板 302 と、基板 302 上に形成された絶縁層 305 と、絶縁層 305 上に形成された絶縁層 306 と、絶縁層 306 上に形成された半導体層 308d と、絶縁層 306、及び半導体層 308d 上に形成された導電層 310f、310g と、導電層 310f、310g 上に形成された絶縁層 312 と、絶縁層 312、導電層 310f、310g、及び半導体層 308d 上に形成された絶縁層 314 と、を有する。

20

**【0321】**

本実施の形態に示す表示装置は、先の実施の形態の図 24 に示す表示装置との違いとして、開口部の形状が異なる。より、具体的には、導電層 310c、310e 上に形成される開口部は、図 9 に示す表示装置と同様に 1 回のエッチング工程により形成されることを特徴とする。また、導電層 304b 上に形成される開口部は、2 回のエッチング工程により形成されることを特徴とする。

**【0322】**

図 30 に示すように開口部の形状を変えることによって、以下のような効果を得ることができる。

30

**【0323】**

1 回目のエッチング工程により絶縁層の膜厚を調整することによって、2 回目のエッチング工程により形成される開口の際に、深さ方向の異なる絶縁層のエッチングを好適に行なうことができる。

**【0324】**

なお、本実施の形態に示す表示装置は、駆動回路部 104、及び画素回路部 108 が有するトランジスタと、抵抗素子 114 と、を同時に形成することができる。したがって、製造コスト等を増やさずに抵抗素子 114 を形成することが可能となる。

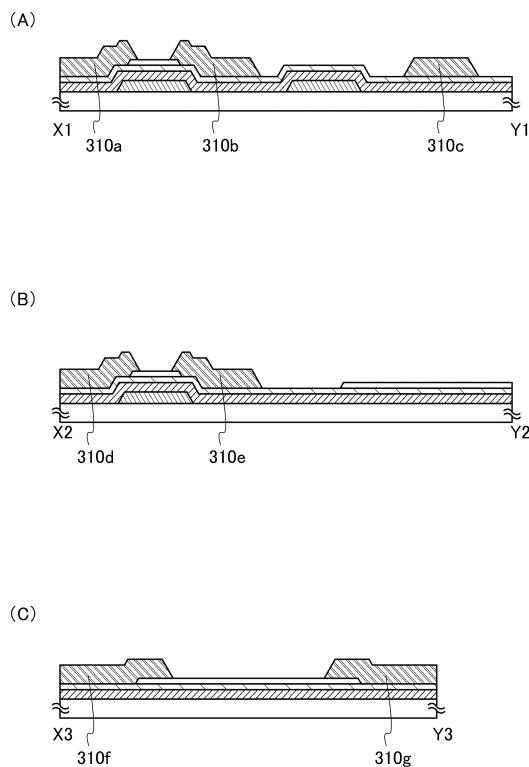

**【0325】**

次に、図 30 に示す表示装置の作製方法について、図 31 乃至図 35 を用いて、以下説明を行う。

40

**【0326】**

なお、駆動回路部 104 の作製方法については、図 31(A)、図 32(A)、図 33(A)、図 34(A)、及び図 35(A) に示し、画素回路部 108 の作製方法については、図 31(B)、図 32(B)、図 33(B)、図 34(B)、及び図 35(B) に示し、抵抗素子 114 の作製方法については、図 31(C)、図 32(C)、図 33(C)、図 34(C)、及び図 35(C) に示す。

**【0327】**

まず、先の実施の形態の図 15 に示す構造まで作製する。つまり、3 枚のマスクを用い

50

てパターニング、及びエッチングまで行った基板を作製する。

#### 【0328】

次に、絶縁層311を所望の領域に加工することで、開口部372a、372d、372eを形成する。また、絶縁層311は、開口部372a、372d、372eが形成された絶縁層312となる。なお、絶縁層312、及び開口部372a、372d、372eの形成は、所望の領域に第4のパターニングによるマスクの形成を行い、該マスクに覆われていない領域をエッチングすることで、形成することができる。(図31(A)、(B)、(C)参照)。

#### 【0329】

なお、開口部372aは、絶縁層305が露出するように形成する。また、開口部372d、372eは、それぞれ、半導体層308c、308dが露出するように形成する。開口部372a、372d、372eの形成方法としては、例えば、ドライエッティング法を用いることができる。ただし、開口部372a、372d、372eの形成方法としては、これに限定されず、ウェットエッティング法、またはドライエッティング法とウェットエッティング法を組み合わせた形成方法としてもよい。

#### 【0330】

次に、開口部372a、372d、372eを覆い、且つ絶縁層305、312、及び半導体層308c、308d上に絶縁層313を形成する(図32(A)、(B)、(C)参照)。

#### 【0331】

絶縁層313は、外部からの不純物、例えば、水、アルカリ金属、アルカリ土類金属等が、酸化物半導体層へ拡散するのを防ぐ材料で形成される膜であり、更には水素を含む。このため、絶縁層313の水素が半導体層308c、308dに拡散すると、該半導体層308c、308dにおいて水素は酸素と結合し、キャリアである電子が生成される。この結果、半導体層308c、308dは、導電性が高くなり透光性を有する導電層となる。

#### 【0332】

次に、絶縁層313を所望の領域に加工することで、開口部374a、376a、376bを形成する。また、絶縁層313は、開口部374a、376a、376bが形成された絶縁層314となる。なお、絶縁層314、及び開口部374a、376a、376bは、所望の領域に第5のパターニングによるマスクの形成を行い、該マスクに覆われていない領域をエッチングすることで形成することができる(図33(A)、(B)、(C)参照)。

#### 【0333】

また、開口部374aは、導電層304bが露出するように形成する。また、開口部376aは、導電層310cが露出するように形成する。また、開口部376bは、導電層310eが露出するように形成する。

#### 【0334】

なお、開口部374a、376a、376bの形成方法としては、例えば、ドライエッティング法を用いることができる。ただし、開口部374a、376a、376bの形成方法としては、これに限定されず、ウェットエッティング法、またはドライエッティング法とウェットエッティング法を組み合わせた形成方法としてもよい。

#### 【0335】

次に、開口部374a、376a、376bを覆うように絶縁層314上に導電層315を形成する(図34(A)、(B)、(C)参照)。

#### 【0336】

次に、導電層315を所望の領域に加工することで、導電層316a、316bを形成する。なお、導電層316a、316bの形成は、所望の領域に第6のパターニングによるマスクの形成を行い、該マスクに覆われていない領域をエッチングすることで形成することができる(図35(A)、(B)、(C)参照)。

10

20

30

40

50

**【0337】**

以上の工程でトランジスタを有する駆動回路部104と、トランジスタを有する画素回路部108と、抵抗素子114と、を同一基板上に形成することができる。なお、本実施の形態に示す作製工程においては、第1乃至第6のパターニング、すなわち6枚のマスクでトランジスタ、容量素子及び抵抗素子を同時に形成することができる。

**【0338】**

本実施の形態に示す構成は、他の実施の形態に示す構成と適宜組み合わせて用いることができる。

**【0339】**

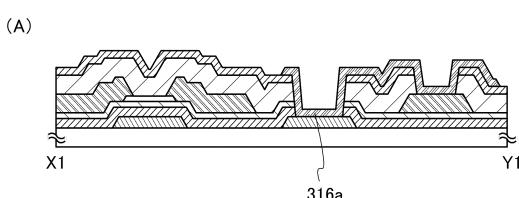

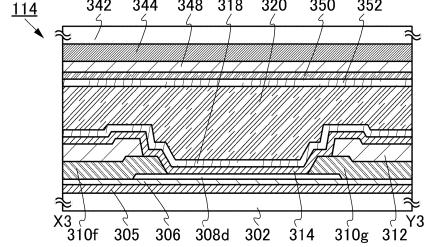

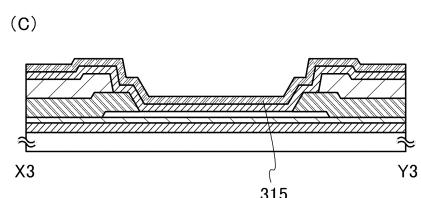

(実施の形態6)

10

本実施の形態では、本発明の一態様の表示装置について、図36乃至図41を用いて説明を行う。

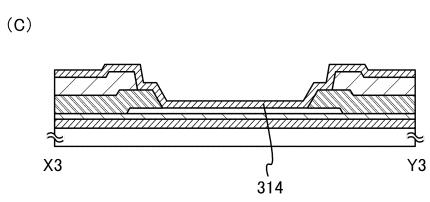

**【0340】**

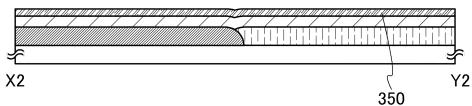

図36に示す表示装置は、図9に示す表示装置の変形例であり、図37乃至図41は、図36に示す表示装置の作製方法を示す断面図である。

**【0341】**

なお、図36乃至図41において、先の実施の形態に示す同様の箇所、または同様の機能を有する部分については、同様の符号を付し、その詳細の説明は省略する。

**【0342】**

図36に示す表示装置は、駆動回路部104と、画素回路部108と、抵抗素子114と、を有する。図36に示す表示装置について、以下説明を行う。

20

**【0343】**

(駆動回路部)

駆動回路部104は、基板302と、基板302上に形成された導電層304a、304bと、基板302、及び導電層304a、304b上に形成された絶縁層305と、絶縁層305上に形成された絶縁層306と、絶縁層306上に形成され、導電層304aと重畠する位置に形成された半導体層308aと、絶縁層306、及び半導体層308a上に形成された導電層310a、310bと、絶縁層306上に形成された導電層310cと、半導体層308a、及び導電層310a、310b、310cを覆うように形成された絶縁層312と、絶縁層312上に形成された絶縁層314と、絶縁層314上に形成された導電層316aと、を有する。

30

**【0344】**

なお、導電層316aは、導電層304bと、導電層310cを接続する配線としての機能を有する。導電層304bは、絶縁層305、306、312、314に形成された開口部を介して、導電層310cは、絶縁層312、314に形成された開口部を介して、導電層316aにより接続される。

**【0345】**

(画素回路部)

画素回路部108は、基板302と、基板302上に形成された導電層304cと、基板302、及び導電層304c上に形成された絶縁層305と、絶縁層305上に形成された絶縁層306と、絶縁層306上に形成され、導電層304cと重畠する位置に形成された半導体層308bと、絶縁層305上に形成された半導体層308cと、絶縁層306、及び半導体層308b上に形成された導電層310d、310eと、半導体層308b、308c及び導電層310d、310eを覆うように形成された絶縁層312と、絶縁層312上に形成された絶縁層314と、絶縁層314上に形成され、且つ導電層310eに接続された導電層316bと、を有する。

40

**【0346】**

なお、導電層316bは、絶縁層312、314に形成された開口部を介して、導電層310eに接続される。

**【0347】**

50

(抵抗素子 114)

抵抗素子 114 は、基板 302 と、基板 302 上に形成された絶縁層 305 と、絶縁層 305 上に形成された絶縁層 306 と、絶縁層 305 上に形成された半導体層 308d と、絶縁層 306、及び半導体層 308d 上に形成された導電層 310f、310g と、半導体層 308d、導電層 310f、310g 上に形成された絶縁層 312 と、絶縁層 312 上に形成された絶縁層 314 と、を有する。

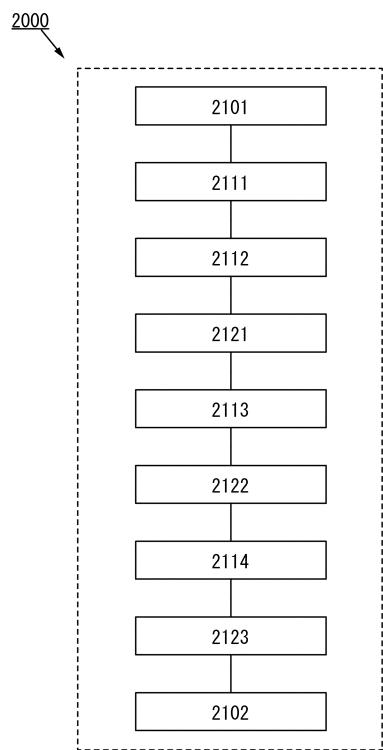

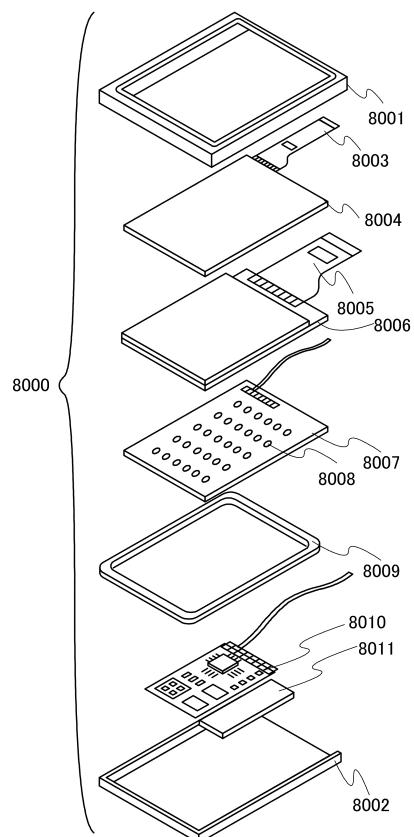

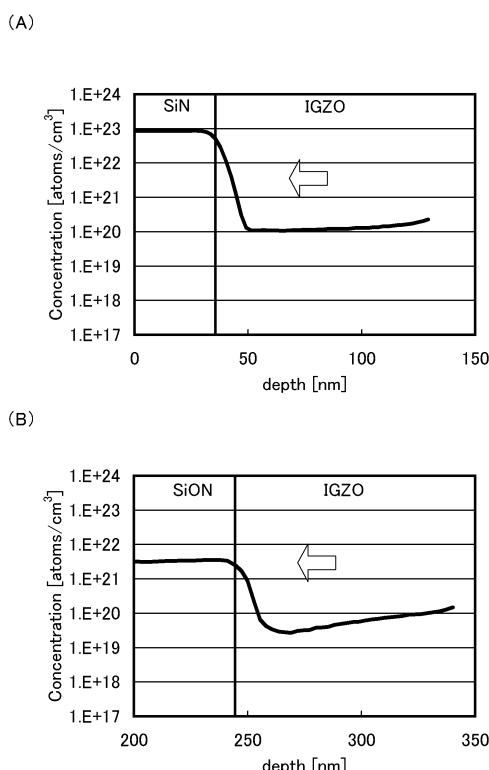

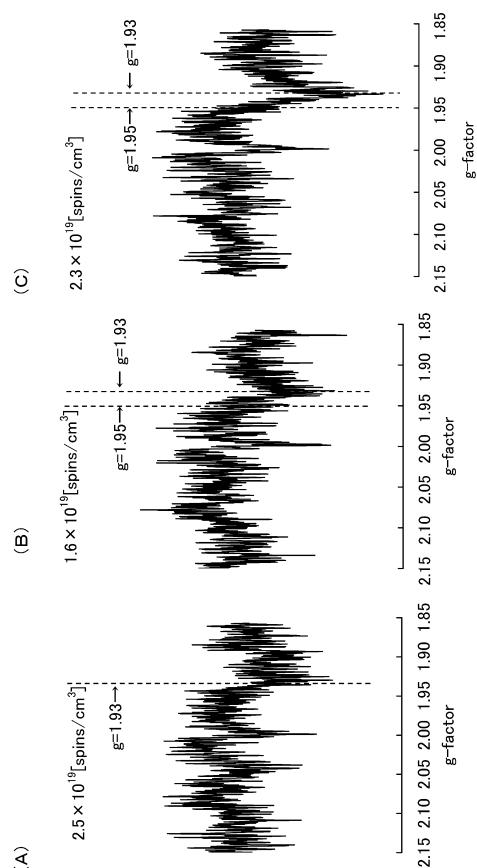

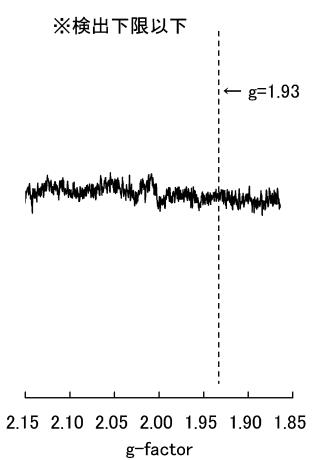

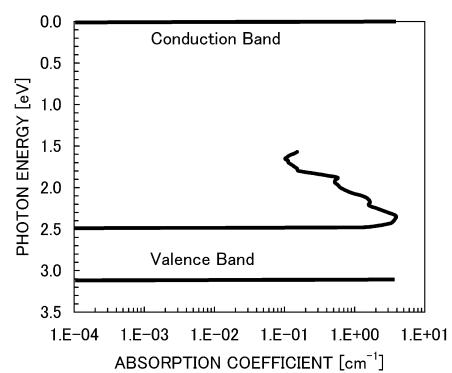

【0348】