(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3626254号

(P3626254)

(45) 発行日 平成17年3月2日(2005.3.2)

(24) 登録日 平成16年12月10日(2004.12.10)

(51) Int.CI.<sup>7</sup>

F 1

G 11 C 29/00

G 11 C 29/00

601B

請求項の数 10 (全 16 頁)

(21) 出願番号 特願平7-224722

(22) 出願日 平成7年8月9日(1995.8.9)

(65) 公開番号 特開平8-96595

(43) 公開日 平成8年4月12日(1996.4.12)

審査請求日 平成14年7月16日(2002.7.16)

(31) 優先権主張番号 94112661.7

(32) 優先日 平成6年8月12日(1994.8.12)

(33) 優先権主張国 オーストリア(AT)

(73) 特許権者 390039413

シーメンス アクチエンゲゼルシャフト

S i e m e n s A k t i e n g e s e l

l s c h a f t

ドイツ連邦共和国 D-80333 ミュ

ンヘン ヴィッテルスバッハーブラツツ

2

(74) 代理人 100075166

弁理士 山口 巍

(72) 発明者 ドミニク サヴィニアク

ドイツ連邦共和国 85737 イスマニ

ング パーンホフシュトラーセ 2

最終頁に続く

(54) 【発明の名称】集積半導体メモリ用の冗長回路装置

## (57) 【特許請求の範囲】

## 【請求項 1】

正規および冗長メモリセルを有し、メモリのメモリセルの任意の群のアドレス(A 0 . . 1 0 ; A ' 0 . . 1 0 )が第1の部分アドレス(A 8 . . 1 0 ; A ' 8 . . 1 0 )および第2の部分アドレス(A 0 . . 7 ; A ' 0 . . 7 )から形成されている集積半導体メモリ用の冗長回路装置において、

M個(ここでM 1)の固定的にプログラム可能なアドレス回路(F S 0 . . F S 7 )を有し、固定的にプログラム可能なアドレス回路(F S 0 . . F S 7 )が第1の部分アドレス(A 8 . . 1 0 ; A ' 8 . . 1 0 )のそれぞれ1つに対応付けられており、各固定的にプログラム可能なアドレス回路(F S 0 . . F S 7 )が能動化された状態において正規メモリセルの置換すべき群の第2の部分アドレス(R 0 . . 7 )と、アドレス回路(F S 0 . . F S 7 )の能動化された状態において、回路装置に与えられる第1の部分アドレス(A 8 . . 1 0 ; A ' 8 . . 1 0 )がアドレス回路(F S i )に対応付けられている第1の部分アドレスと合致するときに、能動化信号(R D A )が与えられる第1の出力端(c 8 )とを有し、

すべてのアドレス回路(F S 0 . . F S 7 )に共通であり、アドレス回路(F S 0 . . F S 7 )が能動化信号(R D A )を与えられた際にこのアドレス回路に記憶されている第2の部分アドレス(R 0 . . 7 )を与えられた第2の部分アドレス(A 0 . . 7 ; A ' 0 . . 7 )と比較するアドレス比較器(A V 1 ; A V 2 )を有し、これらの両第2の部分アドレスが一致する際にレリーズ信号(R S P ; R N O )がアドレス比較器(A V 1 ; A V 2 )の

第1の出力端(20; 20')に与えられ、このレリーズ信号(RSP; RNO)が冗長デコーダ(RRDEC; RCD0)を駆動するのに用いられることを特徴とする集積半導体メモリ用の冗長回路装置。

**【請求項2】**

各アドレス回路(FS0...FS7)がN+1個(Nは第2の部分アドレス(A0..7; A'0..7)のビット幅)の断路可能な接続(F0...F8)によりプログラム可能であることを特徴とする請求項1記載の冗長回路装置。

**【請求項3】**

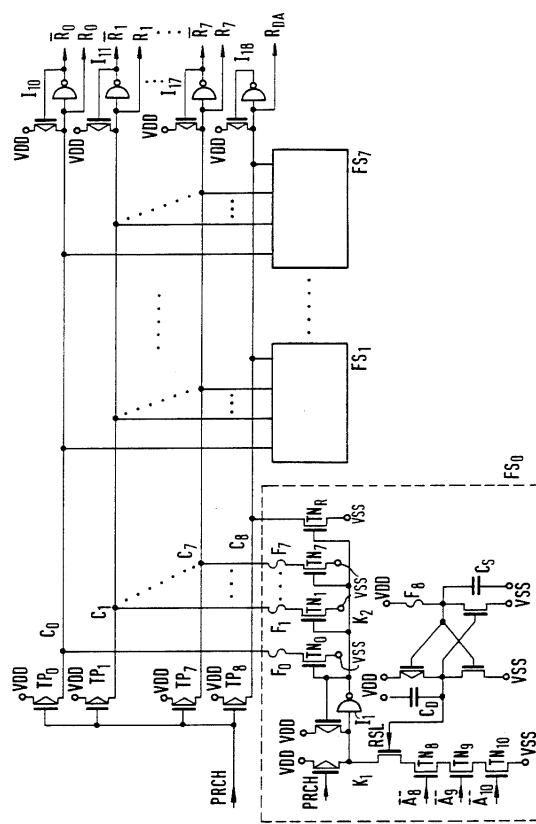

アドレス比較器(AV1; AV2)がローカルなコーディングバス(C0...C8)によりすべてのアドレス回路(FS0...FS7)と接続されており、ローカルなコーディングバスがアドレス回路に記憶されている第2の部分アドレス(A0..7; バーA0..7)および能動化信号(RDA)をアドレス比較器(AV1; AV2)に仲介することを特徴とする請求項1または2記載の冗長回路装置。 10

**【請求項4】**

各アドレス回路(FS0...FS7)がそれぞれ1つの断路可能なヒューズ要素(F0..7)および1つの第1の電界効果トランジスタ(TN0..7)のN個の直列回路を有し、その直列回路がそれぞれ第1の供給電位(VSS)とそのつどの第1の節点(C0...C7)との間に接続されており、第1の節点(C0...C7)および第1の出力端(C8)がローカルなコーディングバスを形成し、アドレス回路の互いに相応するヒューズ要素(F0..7)が同一の節点と接続されており、各第1の節点(C0..7)が第2の供給電位(VDD)および第1のインバータ(I10...I17)のそれぞれ1つの入力端に第2の電界効果トランジスタ(TP0..7)を介して接続されており、第1の電界効果トランジスタ(TN0..7)の制御端子に第1の制御信号(K2)が供給されており、第2の電界効果トランジスタ(TP0..7)の制御端子に第2の制御信号(PCRCH)が供給されており、各第1の節点(C0...C7)が第1のアドレス出力端(R0..7)を形成し、また第1のインバータ(I10...I17)の各出力端がそのつどの第1のアドレス出力端に対して相補性のアドレス出力端(バーR0..7)を形成することを特徴とする請求項2記載の冗長回路装置。 20

**【請求項5】**

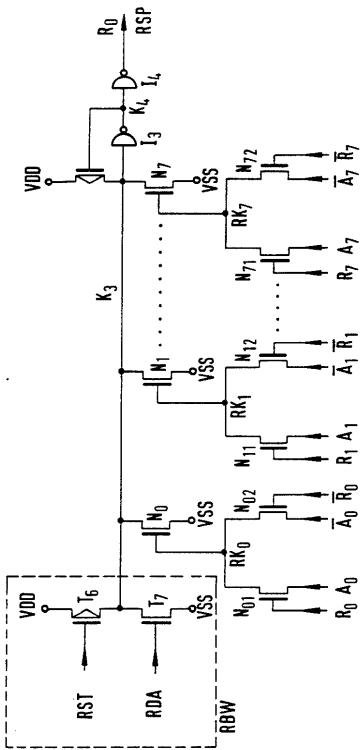

アドレス比較器(AV1; AV2)がN個(Nは第2の部分アドレス(A0..7; A'0..7)のビット幅)の第3の電界効果トランジスタ(N0...N7; N'0...N'7)を有し、第3の電界効果トランジスタ(N0...N7; N'0...N'7)のそのつどの負荷バスが第3の節点(K3; K'3)と第1の供給電位(VSS)との間に接続されており、それらの制御入力端がそれぞれN個の第4の節点(RK0..7; RK'0..7)の1つに接続されており、各第4の節点に第4の電界効果トランジスタ(N01...N71; N'01...N'71)および第5の電界効果トランジスタ(N02...N72; N'02...N'72)が対応付けられており、各第4の電界効果トランジスタ(N01...N71; N'01...N'71)の負荷バスが対応付けられている第4の節点(RK0..7; RK'0..7)と与えられているアドレスの対応付けられているアドレス線(A0..7; A'0..7)との間に接続され、対応する第5の電界効果トランジスタ(N02...N72; N'02...N'72)の負荷バスが対応付けられている第4の節点(RK0..7; RK'0..7)とそのつどの対応付けられているアドレス線(A0..7; A'0..7)に対しても相補性のアドレス線(バーA0..7; バーA'0..7)との間に接続されており、そのつどの第4の電界効果トランジスタ(N01...N71; N'01...N'71)の制御端子にアドレス回路(FS0...FS7)に記憶されている第2の部分アドレスのそのつどのアドレス線(R0..7)が導かれており、そのつどの第5の電界効果トランジスタ(N02...N72; N'02...N'72)の制御端子にアドレス回路に記憶されている第2の部分アドレスのそのつどのアドレス線(バーR0..7)が導かれており、アドレス比較器(AV1; AV2)がホールド段(I3; I'3)を有し、その入 40

力端子が第3の節点( K<sub>3</sub> ; K'<sub>3</sub> )と接続されており、またその出力端子から第1のレリーズ信号( RSP ; RNO )が取り出し可能であり、アドレス比較器( AV1 ; AV2 )が能動化段( RBW ; RBW' )を有し、その出力信号が第3の節点( K<sub>3</sub> ; K'<sub>3</sub> )に与えられていることを特徴とする請求項1ないし4の1つに記載の冗長回路装置。

#### 【請求項6】

能動化段( RBW )が第6および第7の電界効果トランジスタ( T<sub>6</sub> , T<sub>7</sub> )の直列回路から成り、直列回路が第1および第2の基準電位( VS , VDD )の間に接続されており、第6の電界効果トランジスタ( T<sub>6</sub> )の制御端子に第3の制御信号( RST )が供給されており、第7の電界効果トランジスタ( T<sub>7</sub> )の制御端子にアドレス回路( FS0 ... FS7 )の能動化信号( RDA )が供給されており、第6および第7の電界効果トランジスタの負荷バスの間の節点( K )が第3の節点( K<sub>3</sub> )の部分であることを特徴とする請求項5記載の冗長回路装置。 10

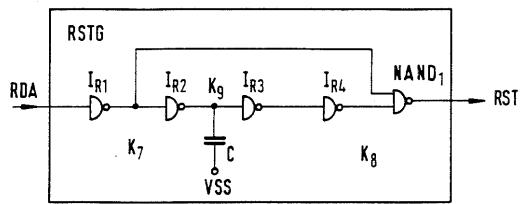

#### 【請求項7】

回路装置が4つの相続くインバータ段( IR1 ... IR4 )の直列回路を有する第3の制御信号( RST )の発生のための回路( RTSG )を有し、直列回路の入力端にアドレス回路( FS0 ... FS7 )の能動化信号( RDA )が供給されており、直列回路の出力端( K<sub>8</sub> )が NAND ゲート( NAND1 )の第1の入力端に接続されており、 NAND ゲートの第2の入力端が第1および第2のインバータ段( IR1 , IR2 )の間の節点( K<sub>7</sub> )に接続されており、 NAND ゲートの出力端から第3の制御信号( RST )が取り出し可能であり、コンデンサ( C )が第1の供給電位( VSS )と第2および第3のインバータ段( IR2 , IR3 )の間の節点( K<sub>9</sub> )との間に接続されていることを特徴とする請求項6記載の冗長回路装置。 20

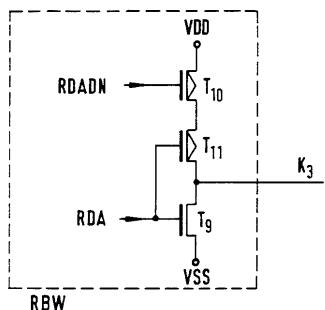

#### 【請求項8】

能動化段( RBW ; RBW' )が第9の電界効果トランジスタ( T<sub>9</sub> , T'<sub>9</sub> )および第10および第11の電界効果トランジスタ( T<sub>10</sub> , T<sub>11</sub> ; T'<sub>10</sub> , T'<sub>11</sub> )の直列回路を有し、この直列回路が第2の供給電位( VDD )と第3の節点( K<sub>3</sub> ; K'<sub>3</sub> )との間に接続されており、第9の電界効果トランジスタ( T<sub>9</sub> ; T'<sub>9</sub> )の負荷バスが第3の節点( K<sub>3</sub> ; K'<sub>3</sub> )と第1の供給電位( VSS )との間に接続されており、第9および第11の電界効果トランジスタ( T<sub>9</sub> , T<sub>11</sub> ; T'<sub>9</sub> , T'<sub>11</sub> )が互いに相補性の導電形式であり、第9および第11の電界効果トランジスタ( T<sub>9</sub> , T<sub>11</sub> ; T'<sub>9</sub> , T'<sub>11</sub> )の制御端子にアドレス回路( FS0 ... FS7 )の能動化信号( RDA )が供給されており、第10の電界効果トランジスタ( T<sub>10</sub> ; T'<sub>10</sub> )の制御端子に第4の制御信号( RDADN ; ATDN )が供給されていることを特徴とする請求項5記載の冗長回路装置。 30

#### 【請求項9】

メモリセルがM個( M = 1 )のメモリブロック( BK0 . . . 7 )のなかに配置されており、メモリブロック( BK0 . . . 7 )がブロックアドレス( A8 . . . 10 ; A'8 . . . 10 )により呼び出し可能であり、メモリブロックの内部のメモリセルが内部ブロックアドレスにより呼び出し可能であり、第1の部分アドレスがブロックアドレスであり、第2の部分アドレスが内部ブロックアドレスであり、各固定的にプログラム可能なアドレス回路( FS0 ... FS7 )がM個のメモリブロック( BK0 . . . 7 )のそれぞれ1つに対応付けられていることを特徴とする請求項1ないし8の1つに記載の冗長回路装置。 40

#### 【請求項10】

半導体メモリがダイナミックな直接アクセス半導体メモリ( DRAM )であることを特徴とする請求項1ないし9の1つに記載の冗長回路装置。

#### 【発明の詳細な説明】

#### 【0001】

#### 【発明の属する技術分野】

本発明は、たとえば米国電気電子学会雑誌・固体回路編（I E E E J o u r n a l o f S o l i d S t a t e C i r c u i t s ） 、第26巻、第1号、1991年1月、第12頁以降またはヨーロッパ特許出願公開第 A - 0 4 7 2 2 0 9 号明細書から知られているような、特にダイナミックメモリ（D R A M ）におけるワード線又はビット線の修理のための集積半導体メモリ用の冗長回路装置に関する。

#### 【 0 0 0 2 】

##### 【 従来の技術 】

各々の新しいメモリ世代におけるラスター寸法の縮小はセル領域の中の故障発生率を高める。従って、採算の合う生産はこのような故障を修理し得る装置をメモリ上に必要とする。一般に、プログラム可能なコーディング要素により故障したセルの代わりに使用される冗長セルが設けられている。

10

#### 【 0 0 0 3 】

より大きい容量のメモリではメモリセルは複数のブロックに分割されている。メモリセルのマトリックス状の配置の故に、冗長セルは同じく行および列の中に配置されなければならない。これらの冗長導線は一般にセル領域の縁に構成されている。それらはそれぞれ与えられたアドレスと関連付けてプログラム可能なアドレス回路により選ばれる。

#### 【 0 0 0 4 】

これらのプログラム可能なアドレス回路はたとえばレーザーにより断路可能なヒューズブロックであってよい。通常の仕方で各々のヒューズブロックは1つまたは複数の導線に固定的に対応付けられている。一般に独立したメモリブロックの数と同数のヒューズブロックおよびアドレス比較器が利用される。

20

#### 【 0 0 0 5 】

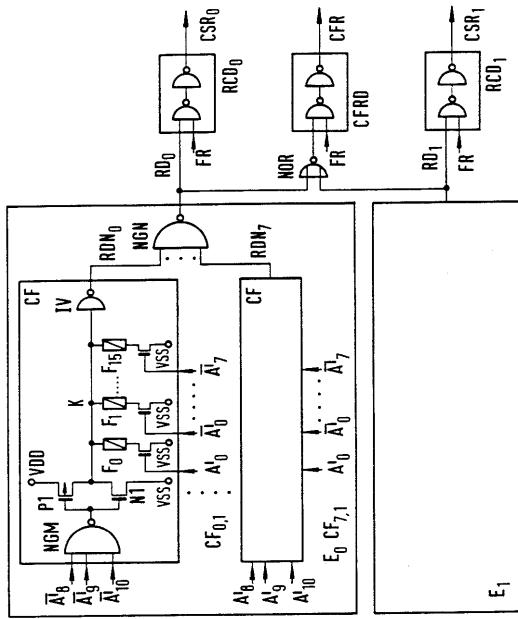

図1には列冗長の際の列アドレスのコーディングのための従来の技術による通常の回路が示されている。例としてメモリセルはここではブロックアドレスA'8、A'9、A'10により呼び出し可能な8つのメモリブロックに分割されている。内部ブロックアドレスA'0...7、すなわち1つのメモリブロックの内部の1つの列のアドレスはここでは8ビット幅である。アドレス回路C F 中のコーディング要素としてここではレーザーにより断路可能なヒューズブロックが使用される。ヒューズブロックあたり内部ブロックアドレスのビット幅の2倍の断路可能な接続要素F 0、…F 15が必要とされる。

30

#### 【 0 0 0 6 】

この例ではメモリブロックあたり2つの冗長列が設けられており、アドレス回路の2つの群E 0、E 1によりコーディングされる。図1には1つのユニットE 0のみが詳細に示されている。このようなユニットは8つの同一のアドレス回路、E 0におけるC F 0, 0 … C F 7, 0 またはE 1におけるC F 0, 1 … C F 7, 1、と8つの入力端R D N 0...7 および1つの出力端、E 0におけるR D 0 またはE 1におけるR D 1、を有する NANDゲートN G N とから成っている。各々のユニットE 0、E 1において各々のアドレス回路C F 0, 0 … C F 7, 0 はそれぞれ8つのメモリブロックの1つに対応付けられている。2つの出力信号R D 0 およびR D 1 は出力端C S R 0 またはC S R 1 を有する各1つの冗長ドライバR C D 0 またはR C D 1 および1つのノアゲートN O R に供給されている。このゲートN O R の出力端はドライバC F R D に接続されており、その出力信号は参照符号C F R を付されている。この信号C F R は正規の列デコーダに供給され、冗長ドライバ（R C D 0 またはR C D 1）が能動化されているならば、正規メモリセルの列デコーダをロックする。3つのドライバR C D 0、R C D 1 およびC F R D にレリーズ信号F R が供給されており、このレリーズ信号F R は論理状態“0”の際に正規および冗長選択線の双方を低いほうの電位、論理“0”、に保つ。このレリーズ信号F R は通常の仕方で同期化目的でチップ上で使用される。

40

#### 【 0 0 0 7 】

メモリはメモリブロックあたりメモリセルの各 $2^8 = 256$ の列を有する $2^3 = 8$ の

50

メモリブロックに編成されている。従って、各々の回路  $C F_{i,j}$  はブロックコーディングのための 3 つの入力端と、 NAND ゲート  $N G N$  の 1 つの入力端と接続されている 1 つの出力端  $R T N_i$  とを有する。

#### 【 0 0 0 8 】

このような回路  $C F_{i,j}$  は 8 つの入力端を有する NAND ゲート  $N G N$  と、その後段に接続されているインバータ  $P_1, N_1$  と、インバータ  $P_1, N_1$  の出力端 A に並列に接続されている各 1 つのヒューズ要素と直列に接続されている  $2 \cdot 8$  の  $n$  チャネルトランジスタと、出力インバータ  $I V$  とから成っている。ブロック選択はたとえば、3 つのブロックアドレス導線バー  $A'_{8,9,10}$  およびそれらの相補性の導線バー  $A'_{8,9,10}$  からの 3 つの導線のすべての可能な組み合わせの 1 つを供給される入力 NAND ゲート  $N G N$  を介して行われる。回路  $C F_{i,j}$  は、この NAND ゲートのすべての入力が論理 “1” であるときに能動化される。その出力はそのときに論理 “0” であり、インバータ  $P_1, N_1$  の出力 K はその結果として論理 “1” である。すべての他の回路  $C F$  では少なくとも 1 つの入力  $A'm$  またはバー  $A'm$  が論理 “0” である。従ってインバータ出力 K も論理 “0” であり、導線  $R D N_n$  は論理 “1” である。

#### 【 0 0 0 9 】

$Y' = 2^N$  の選択線が存在しているならば、 $2 \cdot N'$  の列アドレス線が 1 つの列アドレスのコーディングのために一般的な制限、たとえば  $A'_{0 \dots N-1}$  またはバー  $A'_{0 \dots N-1}$ 、なしに必要とされる。なぜならば、 $n$  チャネルトランジスタおよびレーザーにより断路可能なヒューズ要素の直列回路は論理 “1” を有する入力信号の際にのみ作用を示すからである。

#### 【 0 0 1 0 】

能動化された回路  $C F_{i,j}$ において、相応の列アドレス線が論理 “1” を有する少なくとも 1 つのヒューズ要素が断路されていないならば、節点 K がこのスイッチオンされた  $n$  チャネルトランジスタを介して、出力インバータ  $I V$  が論理 “1” に切換わるような低い電位に保たれる。従って、この場合、すべての導線  $R D N_{0 \dots 7}$  は論理状態 “1” を、また  $N G N$  の出力線  $R D J$  は論理状態 “0” を有する。従って、対応付けられている冗長選択線  $C S R_j$  は信号  $F R$  に無関係に非能動的、すなわち論理 “0” である。このことが両導線  $R D 0$  および  $R D 1$  において該当すると、ゲート  $N O R$  の出力は論理 “1” である。レリーズ信号  $F R$  が能動的になると、信号  $C F R$  は同じく論理状態 “1” をとり、また正規列デコーダをアンロックする。この場合、正規ビット線群が選択される。

#### 【 0 0 1 1 】

それと逆に能動的な回路  $C F_{i,0}$  または  $C F_{i,1}$  においてすべてのヒューズ要素が断路されており、相応の列アドレス線が論理 “1” であれば、節点 K は高い電位に充電された状態にとどまり、また出力インバータ  $I V$  は論理状態 “0” にとどまる。その結果、導線  $R D 1$  または  $R D 2$  が論理状態 “1” をとる。従ってゲート  $N O R$  の出力は論理 “0” である。このことは同じくレリーズ信号  $F R$  に無関係に信号  $C F R$  に対しても当てはまるので、正規列デコーダがロックされる。それに対して冗長選択線  $C S R 0$  または  $C S R 1$  は能動化され、また能動的なメモリブロック  $B K_i$  の中の相応の冗長ビット線群が選択される。

#### 【 0 0 1 2 】

以上に説明した解決策の 1 つの欠点は、プログラムされないアドレスを与える際に、すなわち  $Y'$  の  $Y' - 1$  の場合に、すべての能動的サイクルにおいて横電流が選択された回路  $C F_{i,j}$  のトランジスタ  $P_1$  を経てより低い電位に向かって流れることである。この横電流は場合によっては各々のメモリブロック群  $E_1, E_2$  において 2 回生じ、複数のこののような群を有する具体的な解決策の際に許容できなき高い値をとる。別の欠点は、同じく具体的な場合に、導線  $R D N_{1 \dots N}$  の数とそれにより条件付けられる出力ゲート  $N G N$  の数とが過大であることである。

#### 【 0 0 1 3 】

さらにアドレス回路あたり内部ブロックアドレスのビット幅の 2 倍の多くの断路可能な接

続要素が利用される。冗長アドレスデコーダの構成は2つの欠点を有する。即ち第一に占有場所が大きく、従って円板あたりチップの個数の減少に通じ得る。このようなメモリ世代ではヒューズブロックに対して必要とされる面積が駆動回路の面積と共に冗長メモリセルが必要とする面積とほぼ同様に大きい。第二にこのような回路は、特に列冗長の駆動がすべての能動的サイクルで可能にされている列冗長の際に、高い電流消費に通ずる。出力線がそれにより強く負荷される。

#### 【0014】

ヨーロッパ特許出願公開第 A - 0 4 9 2 0 9 9 号明細書には、置換すべき列または行の内部ブロックアドレスがヒューズブロックの中でプログラムされる冗長回路装置であって、ビット幅と同数の断路可能な接続のみが使用される冗長回路装置が記載されている。これらのアドレスはローカルなバスにより対応付けられている冗長デコーダにメモリのスイッチオン相で書き込まれる。冗長デコーダにおいて、置換すべき列または行のアドレスはフリップフロップ回路により記憶されている。与えられたアドレスと置換すべき列 行のアドレスとの間の比較は各々の冗長デコーダにおいて別々に行われる。従って、断路可能な接続の数の節減は確かに達成されるが、電流消費は高い値にとどまる。

#### 【0015】

##### 【発明が解決しようとする課題】

本発明の課題は、列または行冗長を有する回路装置であって、冗長なアドレス回路の面積需要が最小であり、電流消費が減ぜられており、またアドレス線の負荷が減ぜられている回路装置を提供することである。

10

20

#### 【0016】

##### 【課題を解決するための手段】

上述の課題を解決するため、本発明によれば、正規および冗長メモリセルを有し、メモリのメモリセルの任意の群のアドレスが第1の部分アドレスおよび第2の部分アドレスから形成されている集積半導体メモリ用の冗長回路装置において、M個（ここでM>1）の固定的にプログラム可能なアドレス回路を有し、各固定的にプログラム可能なアドレス回路が第1の部分アドレスのそれぞれ1つに対応付けられており、各固定的にプログラム可能なアドレス回路が能動化された状態において正規メモリセルの置換すべき群の第2の部分アドレスと、アドレス回路の能動化された状態において、回路装置に与えられる第1の部分アドレスがアドレス回路に対応付けられている第1の部分アドレスと合致するときに、能動化信号が与えられる第1の出力端とを有し、すべてのアドレス回路に共通であり、アドレス回路が能動化信号を与えられた際にこのアドレス回路に記憶されている第2の部分アドレスを与えられた第2の部分アドレスと比較するアドレス比較器を有し、これらの両第2の部分アドレスが一致する際にレリーズ信号がアドレス比較器の第1の出力端に与えられ、このレリーズ信号が冗長デコーダを駆動するのに用いられる。

30

#### 【0017】

##### 【実施例】

以下、図面に示されている実施例により本発明を詳細に説明する。

#### 【0018】

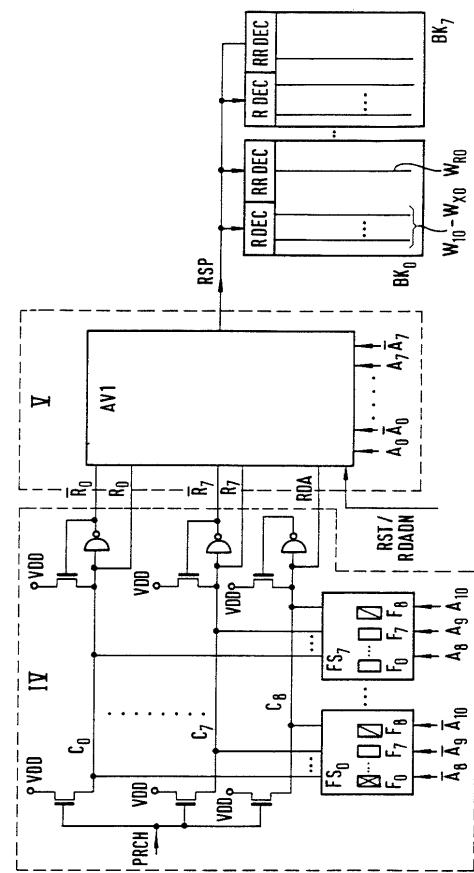

図2は行冗長を有する冗長回路図の本発明による実施例のブロック回路図を示す。破線で囲まれている範囲I VおよびVは図4ないし図10に詳細に示されている。

40

#### 【0019】

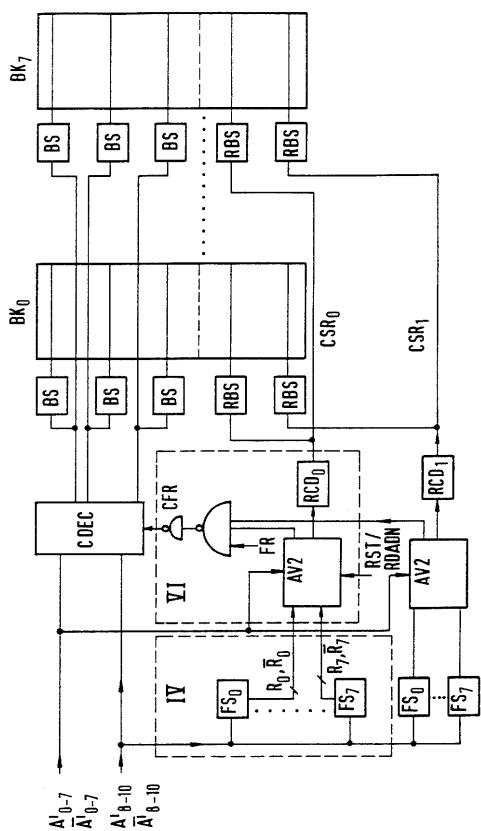

図3は列冗長を有する実施例のブロック回路図である。

#### 【0020】

以下の例では回路はたとえば接地または供給電圧であってよい第1の基準電位(VSS)および第2の基準電位(VDD)に接続されている。

#### 【0021】

置換すべき列または行のアドレスR0-7、バーR0-7は図2による回路においてたとえばローカルなコーディングバスC0-7と、独立したメモリブロックBK0ないしBK7の数aに一致する数のアドレス回路FS0ないしFS7によりプログラムさ

50

れる。図4にアドレス回路F S 0 が詳細に示されている。例としてここには $a = 8$ のメモリブロックB K 0ないしB K 7が選ばれている。内部ブロックアドレス、すなわちメモリブロックB Kの内部の列または行のアドレスはここでは8ビット幅である。それはここではそれぞれ第1の電界効果トランジスタT N 0 . . . 7とコーディングバスの第1の節点との間に接続されている断路可能な接続F 0 ないしF 7によりコーディングされる。補助のヒューズF 8 は、冗長が相応のメモリブロックB Kにおいて使用されるときに断路される。この補助のヒューズF 8 は、アドレス指定のためにここに8つのヒューズF 0 ないしF 7のみが通常の60のヒューズの代わりに必要であることを可能にする。

## 【0022】

一般にメモリは $a$ のメモリブロックを有し、その際に $A = 2^M$ である。メモリブロックB K 0 . . . 7はY'の列およびYの行を有し、その際に $Y = 2^N$ および $Y' = 2^N$ である。この場合、 $N$ ( $N =$ 内部ブロックアドレスのビット幅)のヒューズが行内部ブロックアドレスに対して必要とされる。メモリブロック自体は $2 \cdot M$ のアドレス線によりアドレス指定可能である。以下では行アドレスはAを付されており、また列アドレスはA'を付されている。バーAまたはバーA'はそれに対して相補性の行または列アドレスを示す。

## 【0023】

冗長な導線あたり1つの回路、すなわちこの場合8つの回路が必要とされる図1に示されている回路と異なり、図2に示されている回路は各々のメモリブロックB Kにおいて冗長な導線あたり1つ必要とされる。各々のメモリブロックB Kにおいて2つの冗長な導線が設けられているならば2つの回路が使用される。

## 【0024】

断路可能な接続F 8(図4参照)が断路されていないならば、準備信号R S Lは第1の基準電位V S S(接地)を有する。図4中のアドレス回路F S 0 の2つのキャパシタンスC S およびC D は、断路可能な接続F 8 が断路されているときに、準備信号R S Lを第2の基準電位V D Dに確実にセットする役割をする。

## 【0025】

図2中のアドレス比較器回路A V 1において、与えられた内部ブロックアドレスA 0 - 7が置換すべきアドレスR 0 - 7と比較される。図5にはアドレス比較器A V 1の1つの実施例が示されている。

## 【0026】

アドレス比較が各々の冗長回路C Fにおいて行われる図1に示されている回路と異なり、本発明によれば比較は単一のアドレス比較器A V 1により行われる。しかしアドレス比較は、アドレス指定されたブロックにおいてその付属のアドレス回路F S 0 ないしF S 7がプログラムされており、従って能動化信号R D Aが例えば低いレベルをとるとき、すなわち与えられたアドレスがそのアドレス回路(ヒューズボックスとも呼ばれる)F S 0 ないしF S 7がプログラムされているメモリブロックB Kに該当するときにのみ行われる。それにより内部ブロックアドレス線A 0 - 7、バーA 0 - 7がより少なく負荷され、またすべてのメモリ回路の電流消費が減ぜられる。

## 【0027】

図5のアドレス比較器A V 1は能動化段R B Wにおいて、図6中に示されている回路により能動化信号R D Aから発生可能なパルス信号の形態の第3の制御信号R S Tを使用する。図8には、遅延させられた第4の制御信号R D A D Nをパルス信号R S Tの代わりに利用する能動化段R B Wの1つの回路変形例が示されている。この回路は図5に示されている回路よりも若干速い。このようなパルス信号R S Tまたは遅延させられた信号R D A D Nにより電流消費がさらに減ぜられる。

## 【0028】

図5の能動化段R B Wは第6および第7のF E T T 6、T 7の直列回路から成っており、T 6はpチャネルF E T、T 7はnチャネルF E Tである。信号R D A、R S Tは第7

10

20

30

40

50

のFET T7、第6のFET T6の制御入力端に接続されている。

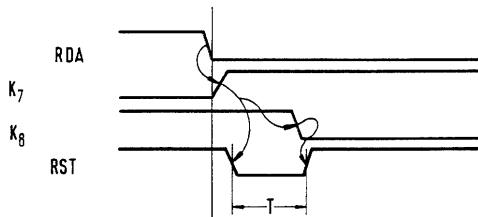

【0029】

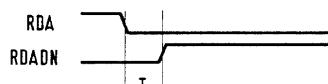

第3の制御信号RSTは図6に示されている回路RSTGから発生可能である。回路RSTGは4つの相続くインバータ段IR1～IR4の直列回路を含んでいる。この直列回路の入力端に能動化信号RDAが供給されており、この直列回路の出力端K8は NANDゲートNAND1に接続されている。第1および第2のインバータ段IR1、IR2の間の節点K7も NANDゲートNAND1に接続されている。コンデンサCが第1の基準電位(接地)と第2および第3のインバータ段の間の節点との間に接続されている。第3の制御信号RSTは NANDゲートNAND1の出力信号である。図7は回路RSTGの時間ダイアグラムを示す。第3の制御信号RSTは、時間間隔Tの間に、能動化信号RDAが論理“0”に移行するときに論理“0”に移行するパルスであり、さもなければ第3の制御信号RSTのレベルは論理“1”的レベルを有する。

10

【0030】

図8には、第3の制御信号RSTの代わりに第4の制御信号RDADNを利用する能動化段RBWの1つの変形例が示されている。RSTのようなパルスの代わりに、RDADNは、RDAが論理“0”に下げられている時間間隔T'の後にレベル論理“1”を駆動する信号である。図8中の能動化段RBWは第9、第10および第11の電界効果トランジスタT9～T11の直列回路を含んでおり、T9はnチャネル形式であり、トランジスタT10およびT11はpチャネル形式である。能動化信号RDAは第9および第11のFET T9、T11の制御入力端に接続されており、また第4の制御信号RDADNは第10のFET T10の制御入力端に接続されている。

20

【0031】

第3の制御信号はたとえば図9に示されている回路RDADNGにより発生可能である。それは3つの相続くインバータ段I'R1～I'R3の直列回路を含んでいる。この直列回路の入力端に能動化信号RDAが供給されており、出力端に第4の制御信号RDADNが生ずる。コンデンサC'が第1の供給電位(接地)と第1および第2のインバータ段I'R1、I'R2の間の節点との間に接続されている。図10は回路RDADNGの時間ダイアグラムを示す。

【0032】

図2が示すように、アドレス比較器AV1の出力信号RSPは冗長の使用の際に冗長行デコーダRRDECを駆動し、また同時に各々のメモリブロックBK0～BK7の正規行デコーダRDECをロックする。従って冗長行WRkがメモリブロックBKkの置換すべき行Wikの代わりにアドレス指定される。

30

【0033】

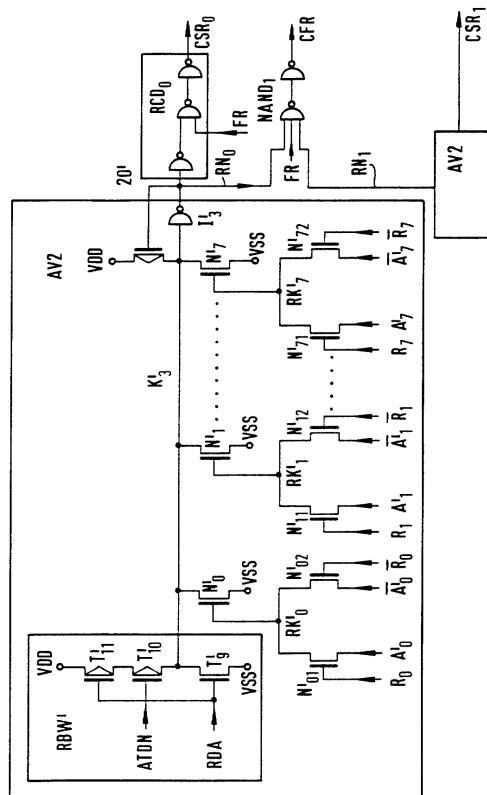

図3は列冗長の際の冗長回路装置の本発明による実施例のプロック回路図を示す。破線で囲まれている範囲IVおよびVIは図4または図11に詳細に説明されている。

【0034】

アドレス比較器AV2の機能は図2および図5に示されているアドレス比較器AV1の機能と同一である。行冗長と比較してここでは第4の制御信号ATDNへのアクセスが行われる。後で一層詳細に説明されるように、第4の制御信号ATDNは、アドレス比較器AV2を通じて横電流を回避する機能を有する。図3中には追加的に、各ブロックにおいて選択線CSR0またはCSR1を有する2つの冗長列デコーダRCDOおよびRCDOが使用されるときに、2組のアドレス回路FS0～FS7および2つのアドレス比較器AV2がどのように互いに接続されるかが示されている。冗長列デコーダRCDOおよびRCDOはメモリブロックBK0～BK7あたり各1つの冗長ビットスイッチRBSを駆動する。信号CFRにより冗長列の選択の際に正規列デコーダCDECがロックされるので、この場合、正規ビットスイッチBBSは駆動されない。

40

【0035】

図5および図11中に示されているアドレス比較器回路AV2では冗長レリーズ信号CSR0は、すべての節点RK'0ないしRK'7が論理“0”であるときに始めて能動

50

化され、すなわち第3の節点K'3が論理“0”である。これらの節点RK'0ないしRK'7の少なくとも1つが論理“1”であれば、節点K'3はスイッチオングされたnチャネルトランジスタN'0ないしN'7を介して、後段に接続されているインバータI3'が出力信号を論理“1”に保つように低い電位にとどまる。

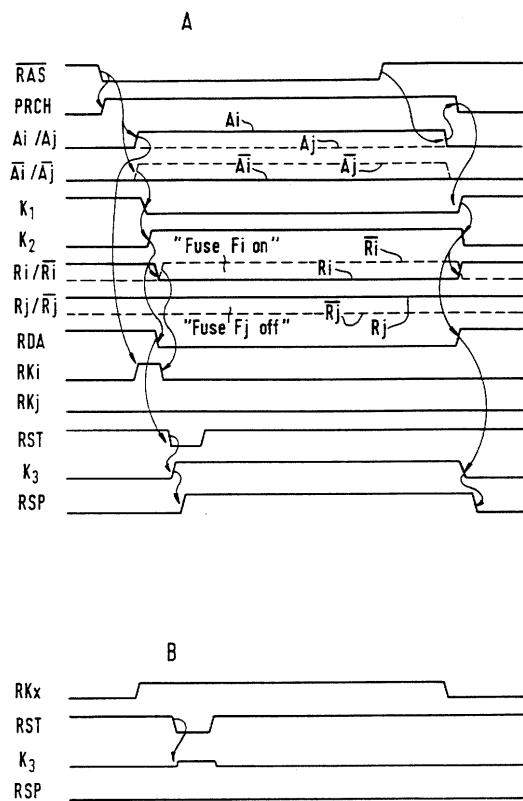

#### 【0036】

図2、図4および図5による回路の機能は図12の時間ダイアグラムにより説明され、その際にそのために必要なメモリ信号のみが示されている。図12aは行冗長を使用するサイクルを示し、図12bは正規の場合、すなわち冗長を使用しない場合を示す。

#### 【0037】

休止相(バーRAS = 論理“1”)ではアドレスA0-7、バーA0-7および第2の制御信号またはロード信号PRCHは論理状態“0”にある。この状態ではすべてのnチャネル形式の第3の電界効果トランジスタN0-7は遮断されており、pチャネル形式の第2の電界効果トランジスタTP0-8は導通している。その結果、節点K1は論理“1”であり、また第1の制御信号を第1のトランジスタTN0-7およびTNRに供給する節点K2は論理“0”である。第1のアドレス出力端R0-7およびローカルなコーディングバスC0ないしC8の第1の出力端RDAはすべて論理“1”であり、他方において第1のアドレス出力端に対して相補性の出力端バーR0-7は論理“0”である。それにより第3の節点K3は論理“0”、またレリーズ信号RSPは論理“0”である。

#### 【0038】

書き込みまたは読み出しサイクルは信号バーRASの立下りにより開始される。第2の制御信号PRCHはバーRASの立下りの後に論理“1”になる。節点K1の論理状態“1”はインバータI1の支援により得られている。その後に出力線A0-10およびバーA0-10の特定の組み合わせが能動的な論理“1”になる。ここでA0-7およびバーA0-7は内部ブロックアドレス、またA8-10およびバーA8-10はブロックアドレスを表す。たとえばバーA8、バーA9およびバーA10がすべて論理“1”であれば、メモリブロックBK0がアドレス指定される。従ってアドレス回路FS0の3つのnチャネルトランジスタTN8ないしTN10が導通する。第4の節点RKiが論理“1”にロードされる。ここでAi = 論理“1”であり、さもなければRKjは論理“0”である。

#### 【0039】

このアドレス回路FS0がコーディングされていると、補助のヒューズF8が断路されている。それによりRSLは論理“1”にある。従って節点K1は論理“0”になり、節点K2は論理“1”になる。図4に示されているアドレス回路の実施例は、断路されたヒューズFj(j=0~7)が論理“1”であり、断路されていないヒューズFiが論理“0”を意味するように接続されている。コーディングバスC0ないしC7により、置換すべき行のアドレスR0-7、バーR0-7が発生される。同時に能動化信号RDAが論理“0”をアドレス回路の第1の出力端C8上に発生する。すべてのRiおよびAiまたはバーRiおよびバーAi(i=0~7)が等しいならば、すべてのRKiは論理“0”になる。従ってすべての第3の電界効果トランジスタ(nチャネル形式)N0ないしN7は遮断状態にある。

#### 【0040】

RDAの立下りにより、時間間隔Tの間論理“0”になるパルスRSTが発生される。すべての第3のnチャネルトランジスタN0-7が遮断しているので、第3の節点K3は論理“1”に上昇する。ここでは保持接続されたインバータI3の形態の保持段I3により、K3はパルスRSTが論理“1”に復帰した後にも論理“1”にとどまる。それにより、冗長デコーダを駆動するためのレリーズ信号RSPが論理“1”になる。

#### 【0041】

正規の場合には、すなわちアドレスA0-7およびR0-7が合致していないならば、少なくとも1つのAnがRnに等しくない。それにより少なくとも1つの第4の節

10

20

30

40

50

点  $R K_n$  が論理 “1” にとどまる。パルス信号  $R S T$  が論理 “0” になると、確かに第 3 の節点  $K_3$  の電位は上昇するが、導通している  $n$  チャネルトランジスタ  $N_n$  により電位は保持接続されたインバータ  $I_3$  を切換えるために十分に上昇しない。従って  $K_3$  はパルス  $R S T$  の後に論理 “0” にとどまり、またレリーズ信号  $R S P$  は論理 “0” にとどまる。

#### 【0042】

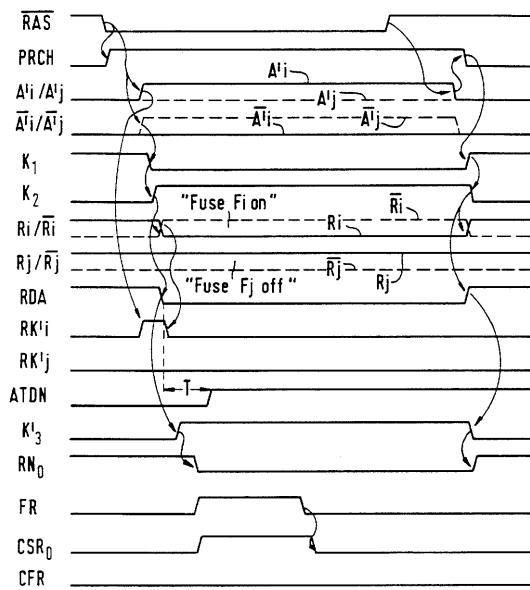

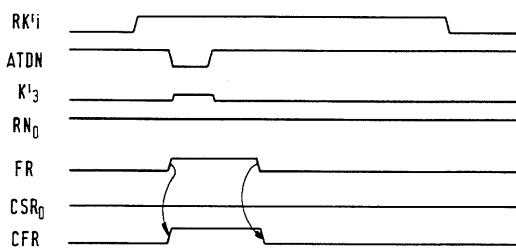

図3、図4および図11中に示されている列冗長に対する冗長回路装置の機能は図13の時間ダイアグラムにより説明され、その際に図3中に示されている時間ダイアグラムとの相違点のみが説明される。図4と比較してここでは第3の制御信号  $R S T$  が、 $R D A D N$  のように能動化信号  $R D A$  から図9による回路により発生され得る第4の制御信号  $A T D N$  により置換される。さらに、メモリのその他の部分回路に既に存在しているデータリーズ信号  $F R$  も利用される。 $C S R_0$  は冗長列デコーダ  $R B S$  に対するレリーズ信号であり、また  $C F R$  は論理状態 “1” で正規列デコーダ  $C D E C$  を遮断する信号である。 $C F R$  は NANDゲートにより信号  $R N_0$ 、 $R N_1$  から発生される。すなわち  $C F R$  は、冗長列デコーダの1つがスイッチオンされると、論理 “1” になる。図13は、図12a、bにおけるように、冗長の際の時間ダイアグラムを示し、また図14は“正規の場合”を示す。

#### 【0043】

休止相（バー  $R A S$  = 論理 “1”）ではアドレス  $A'0 - 7$  およびバー  $A'0 - 7$  および第2の制御信号  $P R C H$  は論理状態 “0” にある。この状態ではすべての  $n$  チャネル形式の第1の電界効果トランジスタ  $N_{0 - 7}$  は遮断されており、また  $p$  チャネル形式の第2の電界効果トランジスタ  $T P_{0 - 8}$  は導通している。その結果、節点  $K_1$  は論理 “1” であり、また第1の制御信号を第1のトランジスタ  $T N_{0 - 7}$  および  $T N R$  に供給する節点  $K_2$  は論理 “0” である。第1のアドレス出力端  $R_{0 - 7}$  およびローカルなコーディングバス  $C_0$  ないし  $C_8$  の第1の出力端  $R D A$  は論理 “1” であり、他方において第1のアドレス出力端に対して相補性のアドレス出力端バー  $R_{0 - 7}$  は論理 “0” である。それにより第3の節点  $K'3$  は論理 “0”、またレリーズ信号  $R N_0$  は論理 “1” である。従って冗長ビットデコーダ  $R C D 0$  はロックされている。制御信号  $C S R_0$  はそれにより論理 “0” にとどまり、また冗長ビット回路  $R B S$  はロックされた状態にとどまる。正規列デコーダ  $C D E C$  も  $C F R =$  論理 “0” によりロックされている。

#### 【0044】

書き込みまたは読み出しサイクルは信号バー  $R A S$  の立下りにより開始される。第2の制御信号  $P R C H$  はバー  $R A S$  の立下りの後に論理 “1” になる。節点  $K_1$  の論理状態 “1” は保持接続されたインバータ  $I_1$  により得られている。

#### 【0045】

その直後に出力線  $A'0 - 10$  およびバー  $A'0 - 10$  の特定の組み合わせが能動的な論理 “1” になる。ここで  $A'0 - 7$  およびバー  $A'0 - 7$  は内部ブロックアドレス、また  $A'8 - 10$  およびバー  $A'8 - 10$  はブロックアドレスを表す。第4の節点  $R K'i$  が論理 “1” にロードされる。ここで  $A'i$  は論理 “1” であり、さもなければ第4の節点  $R K'j =$  論理 “0” である。

#### 【0046】

このアドレス回路がコーディングされていると、補助のヒューズ  $F_8$  が断路されている。それにより  $R S L$  は論理 “1” にある。従って節点  $K_1$  は論理 “0” になり、節点  $K_2$  は論理 “1” になる。コーディングバス  $C_0$  ないし  $C_8$  により、置換すべき行のアドレス  $R_{0 - 7}$ 、バー  $R_{0 - 7}$  が発生される。同時に  $R D A$  が論理 “0” になる。すべての  $R_i$  および  $A'i$  またはバー  $R_i$  ( $i = 0 - 7$ ) が等しいならば、すべての  $R K'i$  は論理 “0” になる。従ってすべての  $n$  チャネルトランジスタ  $N'0$  ないし  $N'7$  は遮断状態にある。

#### 【0047】

10

20

30

40

50

R D A の立下りにより、時間間隔 T' の後に論理 “1” になる第 4 の制御パルス A T D N が発生される。すべての n チャネルトランジスタ N' 0 - 7 が遮断しているので、節点 K' 3 はこの時間間隔 T' において論理 “1” に上昇する。インバータ I' 3 の保持回路により、第 4 の制御信号 A T D N が論理値 “0” に上昇しているならば、この時間間隔中に K' 3 も論理レベル “1” にとどまる。それにより冗長レリーズ信号 R N 0 が論理 “0” になる。レリーズ信号 F R が論理 “1” になると、冗長信号 R C D 0 がスイッチオンし、また冗長ビットスイッチ R B S の制御信号 R S R 0 が論理 “1” になる。同時に C F R が論理 “0” にとどまり、また正規列デコーダ C D E C がロックされた状態にとどまる。

## 【0048】

10

正規の場合には、すなわちアドレス A' 0 - 7 および R 0 - 7 が合致していないならば、少なくとも 1 つの A' i が R i に等しくない。それにより少なくとも 1 つの節点 R K' i が論理 “1” にとどまる。R D A が論理 “0” になり、また第 4 の制御信号 A T D N が論理 “1” になると、確かに節点 K' 3 の電位は上昇するが、導通している n チャネルトランジスタ N' i により電位は保持接続されたインバータ I' 3 を切換えるために十分に上昇しない。従って K' 3 は A T D N の後に論理 “0” にとどまり、また R N 0 は論理 “1” にとどまる。冗長ビットデコーダ R C D 0 はロックされた状態にとどまる。レリーズ信号 F R が論理 “1” になると、C F R は論理 “1” に上昇し、また正規列デコーダ C D E C が能動化される。

## 【0049】

20

例ではそれぞれただ 1 つの行または列が本発明による冗長回路装置により置換可能になるけれども、容易にたとえば 2、4 または 8 の行または列の 1 つの群も同時に置換可能である。この場合、アドレスデコーダ F S 0 ~ F S 7 に記憶される内部ブロックアドレスは 1、2 または 3 ビット短い。従って、上記の実施例は、実施例ではそれぞれただ 1 つの行または列がアドレス指定されているけれども、任意の群の行または列が内部ブロックアドレスによりアドレス指定可能であると理解されるべきである。

## 【0050】

本発明による冗長回路装置はメモリブロックの分割のようなメモリアーキテクチャに無関係に使用され得る。上記の実施例のように各アドレス回路を 1 つのブロックアドレスに対応付ける代わりに、一般に各アドレス回路をメモリセルの 1 つの群の完全なアドレスの第 1 の部分アドレスに対応付けらることもできる。第 2 の部分アドレス、すなわち完全なアドレスの残部は、アドレス回路において例えばレーザーヒューズのような断路可能な接続によりコード化される。例えば 8 つのメモリブロックおよび 4 つのアドレス回路を有するメモリにおいてブロックアドレス A 8、A 9、A 10 のただ 2 つのアドレス線 A 8、A 9 がアドレス回路の選択のために使用されるならば、例えば各アドレス回路がそれぞれ 2 つのメモリブロックに対応付けられ得る。第 3 のブロックアドレス線、例えば A 10、が追加的にアドレスデコーダ F S 0 ~ F S 7 において使用され得る。その際アドレス比較器 A V 1、A V 2 は追加的なアドレス線を得る。こうして単一の能動的なアドレス回路、例えば F S 2 により選択的に 2 つの異なるメモリブロックの中のメモリセルの群が置換可能である。逆に、一種のブロックなしの冗長を実現するため、複数のアドレス回路を 1 つまたは複数のメモリブロックに共通に対応付けることもできる。与えられたアドレスにおいて常にただ 1 つのアドレス回路が能動化される。従って第 1 の部分アドレスのビット幅 n 1 は、アドレス回路の数 M に応じて  $M = 2^{n-1}$  であるように選ばれていなければならない。

30

## 【図面の簡単な説明】

40

【図 1】従来の技術による列冗長の際のアドレス回路およびその駆動のための回路装置の接続図。

【図 2】本発明による行冗長回路装置のブロック接続図。

【図 3】本発明による列冗長回路装置のブロック接続図。

【図 4】本発明によるアドレス回路の 1 つの実施例の接続図。

50

【図 5】本発明による行冗長の際のアドレス比較器の実施例の接続図。

【図 6】本発明による行冗長の際のアドレス比較器の別の実施例の接続図。

【図 7】図 6 による回路の信号の時間ダイアグラム。

【図 8】本発明による能動化段の 1 つの実施例の接続図。

【図 9】本発明による回路の接続図。

【図 10】本発明による回路の信号の時間ダイアグラム。

【図 11】本発明による列冗長の際のアドレス比較器の 1 つの実施例の接続図。

【図 12】図 2、図 4 および図 5 による回路の信号の時間ダイアグラム。

【図 13】図 3、図 4 および図 11 による回路の信号の時間ダイアグラム。

【図 14】図 3、図 4 および図 11 による回路の信号の時間ダイアグラム。 10

【符号の説明】

A 8 . . 1 0 ; A ' 8 . . 1 0 第 1 の部分アドレス

A 0 . . 7 ; A ' 0 . . 7 第 2 の部分アドレス

A V 1 ; A V 2 アドレス比較器

C 0 ... C 8 コーディングバス

c 8 第 1 の出力端

E 0 ; E 1 アドレス回路の群

F 0 ... F 8 ヒューズ

F R レリーズ信号

F S 0 ... F S 7 アドレス回路

N G N ナンドゲート

N O R ノアゲート

R 0 . . 7 置換すべき群の第 2 の部分アドレス

R D A 能動化信号

R R D E C ; R C D 0 冗長デコーダ

R S P ; R N O レリーズ信号

2 0 ; 2 0 ' 第 1 の出力端

10

20

【 図 1 】

【 囮 2 】

【 図 3 】

【 四 4 】

【図5】

【図6】

【図7】

【図8】

【図10】

【図9】

【図11】

【図12】

【図13】

【図14】

---

フロントページの続き

(72)発明者 デイーター ゾンマー

ドイツ連邦共和国 80469 ミュンヘン ウエスター・ミユールシユトラーセ 23

(72)発明者 オリファー キール

ドイツ連邦共和国 80804 ミュンヘン レオポルトシユトラーセ 138

審査官 小松 正

(56)参考文献 特開平04-103099(JP,A)

特開平04-274096(JP,A)

特開平06-060690(JP,A)

特開平06-044795(JP,A)

特開平06-195995(JP,A)

特開平04-307498(JP,A)

(58)調査した分野(Int.Cl.<sup>7</sup>, DB名)

G11C 29/00