(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4955488号

(P4955488)

(45) 発行日 平成24年6月20日(2012.6.20)

(24) 登録日 平成24年3月23日(2012.3.23)

(51) Int.CI.

H01L 23/12 (2006.01)

F 1

H01L 23/12 501P

請求項の数 10 (全 16 頁)

(21) 出願番号 特願2007-230323 (P2007-230323)

(22) 出願日 平成19年9月5日 (2007.9.5)

(65) 公開番号 特開2009-64897 (P2009-64897A)

(43) 公開日 平成21年3月26日 (2009.3.26)

審査請求日 平成22年6月29日 (2010.6.29)

(73) 特許権者 000190688

新光電気工業株式会社

長野県長野市小島田町80番地

(74) 代理人 100091672

弁理士 岡本 啓三

(72) 発明者 高池 英次

長野県長野市小島田町80番地 新光電気

工業株式会社内

審査官 坂本 薫昭

(56) 参考文献 特開平05-110223 (JP, A)

特開2006-073862 (JP, A)

最終頁に続く

(54) 【発明の名称】半導体装置及びその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

デバイスが作り込まれた半導体基板と、

前記半導体基板の前記デバイスが作り込まれている側の表面に形成され、前記デバイスの複数の電極パッドが露出する複数の開口部を有する絶縁層と、

前記絶縁層上の、前記複数の開口部のうち一部の開口部を含む領域に形成され、前記一部の開口部から露出している電極パッドに接続された配線層と、

前記絶縁層上の、ポスト形成領域に対応する部分に形成された外部端子用パッドと、

前記複数の開口部のうち残りの開口部から露出している電極パッドと前記外部端子用パッドとを接続するボンディングワイヤと、

前記配線層の一部によって画定される端子形成部分と前記外部端子用パッド上にそれぞれ形成された導体ポストと、

前記導体ポストが形成されていない領域において前記配線層上的一部を覆う保護膜と、

前記保護膜と異なる材質からなり、前記保護膜で覆われていない残りの領域を、前記保護膜の厚さよりも厚く、かつ前記導体ポストの頂上部を露出させて覆う封止樹脂層と、

前記導体ポストの頂上部に接合された外部接続端子と、を備えたことを特徴とする半導体装置。

## 【請求項 2】

前記ボンディングワイヤの端部が、前記導体ポストに埋め込まれて前記外部端子用パッドに接続されていることを特徴とする請求項 1 に記載の半導体装置。

**【請求項 3】**

前記外部端子用パッドを構成する導体層が下層及び上層の2層構造からなり、前記ボンディングワイヤの端部が前記下層に接続され、かつ前記上層に埋め込まれていることを特徴とする請求項1に記載の半導体装置。

**【請求項 4】**

デバイスが作り込まれた半導体基板と、

前記半導体基板の前記デバイスが作り込まれている側の表面に形成され、前記デバイスの複数の電極パッドが露出する複数の開口部を有する絶縁層と、

前記絶縁層上の、前記複数の開口部のうち一部の開口部を含む領域に形成され、前記一部の開口部から露出している電極パッドに接続された配線層と、

前記絶縁層上の、ポスト形成領域に対応する部分に形成された外部端子用パッドと、

前記配線層の一部によって画定される端子形成部分と前記外部端子用パッド上にそれぞれ形成された導体ポストと、

前記複数の開口部のうち残りの開口部から露出している電極パッドに一方の端部が接続され、他方の端部がフローティング状態で前記導体ポストに埋め込まれたボンディングワイヤと、

前記導体ポストが形成されていない領域において前記配線層上的一部を覆う保護膜と、

前記保護膜と異なる材質からなり、前記保護膜で覆われていない残りの領域を、前記保護膜の厚さよりも厚く、かつ前記導体ポストの頂上部を露出させて覆う封止樹脂層と、

前記導体ポストの頂上部に接合された外部接続端子と、を備えたことを特徴とする半導体装置。

**【請求項 5】**

前記デバイスの複数の電極パッドにそれぞれ一方の端部が接続された複数のボンディングワイヤの各々の他方の端部が、前記導体ポストに電気的に接続されていることを特徴とする請求項1から4のいずれか一項に記載の半導体装置。

**【請求項 6】**

前記保護膜は、ポリイミド樹脂からなることを特徴とする請求項1又は4に記載の半導体装置。

**【請求項 7】**

複数のデバイスが作り込まれた半導体ウエハを用意する工程と、

前記半導体ウエハのデバイスが作り込まれている側の表面に、各デバイスの複数の電極パッドが露出する複数の開口部を有するように絶縁層を形成し、さらに該絶縁層上にシード層を形成する工程と、

前記シード層の、前記複数の開口部のうち一部の開口部を含む領域に配線層を形成すると共に、前記シード層の、ポスト形成領域に対応する部分に外部端子用パッドを形成する工程と、

前記シード層の、前記複数の開口部のうち残りの開口部から露出している電極パッド上の部分と、前記外部端子用パッドとをボンディングワイヤで接続する工程と、

前記配線層の一部によって画定される端子形成部分と前記外部端子用パッド上にそれぞれ導体ポストを形成する工程と、

前記シード層の露出している部分を除去する工程と、

前記導体ポストが形成されていない領域において前記配線層上的一部を覆うように保護膜を形成する工程と、

前記保護膜で覆われていない残りの領域を、前記保護膜の厚さよりも厚く、かつ前記導体ポストの頂上部を露出させて覆うように、前記保護膜と異なる材質からなる封止樹脂で封止する工程と、

前記導体ポストの頂上部に外部接続端子を接合し、該外部接続端子が接合された半導体ウエハを個々のデバイス単位に分割する工程とを含むことを特徴とする半導体装置の製造方法。

**【請求項 8】**

10

20

30

40

50

前記ボンディングワイヤで接続する工程において、前記シード層の前記電極パッド上の部分に一方の端部が接続されたボンディングワイヤの他方の端部を、前記外部端子用パッドの中央部に近い箇所に接続し、

前記導体ポストを形成する工程において、前記ボンディングワイヤの他方の端部が埋め込まれるように当該導体ポストを形成することを特徴とする請求項7に記載の半導体装置の製造方法。

#### 【請求項9】

複数のデバイスが作り込まれた半導体ウエハを用意する工程と、

前記半導体ウエハのデバイスが作り込まれている側の表面に、各デバイスの複数の電極パッドが露出する複数の開口部を有するように絶縁層を形成し、さらに該絶縁層上にシード層を形成する工程と、

前記シード層の、前記複数の開口部のうち一部の開口部から露出している電極パッド上の部分に、一方の端部をフローティング状態としてボンディングワイヤの他方の端部を接続する工程と、

前記シード層の、前記複数の開口部のうち残りの開口部を含む領域に配線層を形成すると共に、前記シード層の、ポスト形成領域に対応する部分に外部端子用パッドを形成する工程と、

前記配線層の一部によって画定される端子形成部分と前記外部端子用パッド上にそれぞれ導体ポストを形成する工程と、

前記シード層の露出している部分を除去する工程と、

前記導体ポストが形成されていない領域において前記配線層上の一部を覆うように保護膜を形成する工程と、

前記保護膜で覆われていない残りの領域を、前記保護膜の厚さよりも厚く、かつ前記導体ポストの頂上部を露出させて覆うように、前記保護膜と異なる材質からなる封止樹脂で封止する工程と、

前記導体ポストの頂上部に外部接続端子を接合し、該外部接続端子が接合された半導体ウエハを個々のデバイス単位に分割する工程とを含むことを特徴とする半導体装置の製造方法。

#### 【請求項10】

前記保護膜を形成する工程において、ポリイミド樹脂を用いて当該保護膜を形成することを特徴とする請求項7又は9に記載の半導体装置の製造方法。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、半導体装置及びその製造方法に関し、特に、複数のデバイスが作り込まれたウエハレベルパッケージにおいて外部接続端子の再配置を効率良く行うのに有用な技術に関する。

##### 【背景技術】

##### 【0002】

近年、電子機器や装置の小型化及び高機能化の要求に伴い、それに用いられるICやLSI等の半導体装置(チップ)は高集積化され大容量化してきている。そして、半導体チップを実装するパッケージについても、小型化(薄型化)、多ピン化、高密度化等が図られている。また、複数の半導体チップを1つの基板上に実装するMCP(マルチチップパッケージ)が実用化され、特にスタックタイプのMCPは一般的に使用されている。さらに、半導体チップの実装においては、CSP(チップサイズパッケージ)のように更なる小型化の技術が要求されている。

##### 【0003】

複数の半導体素子(能動デバイス)を搭載するパッケージにおいては、ウエハレベルパッケージを利用することで微細な配線を形成することができ、高密度化等に寄与することができる。典型的なウエハレベルパッケージにおいては、ウエハのデバイスが作り込まれ

10

20

30

40

50

ている側の表面に保護膜としてのパッシベーション膜やポリイミド樹脂等からなる絶縁膜が形成され、この絶縁膜上に、該絶縁膜の所要の箇所に形成された開口部を介して各デバイスの電極パッド（配線層）をパッケージ外部に連絡するための導体層（再配線層）が形成されており、さらにこの再配線層の端子形成部分に導体ポストが設けられ、この導体ポストが形成されている側の面全体が（ただし、導体ポストの頂上部は露出するように）封止樹脂によって封止され、さらに導体ポストの頂上部に外部接続端子（はんだボール等）が接合されている。

#### 【0004】

上記の従来技術に関する技術としては、例えば、特許文献1に記載されるように、スタッカタイプのMCP（半導体装置）において、半導体チップを封止する基板の絶縁層の表面にリード（ステッチ）あるいは配線を形成し、前記半導体チップ上のパッド電極とボンディングワイヤで接続するステッチの他に余剰のステッチを前記絶縁層の表面に設けるようにしたものがある。また、特許文献2に記載されるように、半導体基板上に形成された絶縁層上に再配線パターンを形成し、この再配線パターン上に導体ポストを介してバンプ電極を形成するとともに、前記絶縁層の開口部から露出するパッドと前記再配線パターンとをボンディングワイヤにより接続し、前記再配線パターン及びボンディングワイヤを絶縁層により封止するようにしたものがある。

【特許文献1】特開2002-237567号公報

【特許文献2】特開2006-73862号公報

#### 【発明の開示】

##### 【発明が解決しようとする課題】

#### 【0005】

上述したように複数の半導体素子を搭載するパッケージにおいては、ウエハレベルパッケージを利用してすることで微細な配線を形成することができるが、ウエハレベル上での再配置（外部接続端子の再配置）をする場合、コスト面を考慮すると、1層の導体部で配線形成（再配線）を行うのが望ましい。

#### 【0006】

しかしながら、導体部は、各素子に所要の電源電圧を供給するための電源ライン、グラウンドライン、データや制御信号等を伝搬させるための信号ラインなど異なる属性の配線に分かれており、さらに、同じ属性の信号ラインでも5V用、3.3V用など供給電圧毎に異なる配線が含まれており、同様に同じ属性の信号ラインでもアナログ信号用、デジタル信号用など信号種別に応じて異なる配線が含まれている。このため、導体部（各配線）の接続情報や設計上等の制約条件（例えば、ライン／スペース等）が重なると、パッケージのピン数（外部接続端子の設置数）にかかわらず導体部の1層で再配線することができない場合が起こり得るといった課題があった。

#### 【0007】

本発明は、かかる従来技術における課題に鑑み創作されたもので、導体部の1層で配線形成を可能とし、ひいてはコストの低減化に寄与することができる半導体装置及びその製造方法を提供することを目的とする。

#### 【課題を解決するための手段】

#### 【0008】

上記の従来技術の課題を解決するため、本発明の一形態によれば、デバイスが作り込まれた半導体基板と、前記半導体基板の前記デバイスが作り込まれている側の表面に形成され、前記デバイスの複数の電極パッドが露出する複数の開口部を有する絶縁層と、前記絶縁層上の、前記複数の開口部のうち一部の開口部を含む領域に形成され、前記一部の開口部から露出している電極パッドに接続された配線層と、前記絶縁層上の、ポスト形成領域に対応する部分に形成された外部端子用パッドと、前記複数の開口部のうち残りの開口部から露出している電極パッドと前記外部端子用パッドとを接続するボンディングワイヤと、

前記配線層の一部によって画定される端子形成部分と前記外部端子用パッド上にそれぞ

10

20

30

40

50

れ形成された導体ポストと、前記導体ポストが形成されていない領域において前記配線層上の一部を覆う保護膜と、前記保護膜と異なる材質からなり、前記保護膜で覆われていない残りの領域を、前記保護膜の厚さよりも厚く、かつ前記導体ポストの頂上部を露出させて覆う封止樹脂層と、前記導体ポストの頂上部に接合された外部接続端子と、を備えたことを特徴とする半導体装置が提供される。

#### 【0009】

この形態に係る半導体装置によれば、半導体基板に作り込まれたデバイスの一部の電極パッドは、ポンディングワイヤを介して導体層の一部分である外部端子用パッド（導体ポスト、外部接続端子）に接続され、残りの電極パッドは、同じ導体層である配線層を介して端子形成部分（導体ポスト、外部接続端子）に接続されている。従って、ウエハレベルパッケージであってもウエハレベル上での外部接続端子の再配置を当該導体層（配線層及び外部端子用パッド）で実現することができる。つまり、1層の導体部で配線形成（再配線）を行うことができるので、コスト面で有利となる。

10

#### 【0010】

また、本発明の他の形態によれば、複数のデバイスが作り込まれた半導体ウエハを用意する工程と、前記半導体ウエハのデバイスが作り込まれている側の表面に、各デバイスの複数の電極パッドが露出する複数の開口部を有するように絶縁層を形成し、さらに該絶縁層上にシード層を形成する工程と、前記シード層の、前記複数の開口部のうち一部の開口部を含む領域に配線層を形成すると共に、前記シード層の、ポスト形成領域に対応する部分に外部端子用パッドを形成する工程と、前記シード層の、前記複数の開口部のうち残りの開口部から露出している電極パッド上の部分と、前記外部端子用パッドとをポンディングワイヤで接続する工程と、前記配線層の一部によって画定される端子形成部分と前記外部端子用パッド上にそれぞれ導体ポストを形成する工程と、前記シード層の露出している部分を除去する工程と、前記導体ポストが形成されていない領域において前記配線層上の一部を覆うように保護膜を形成する工程と、前記保護膜で覆われていない残りの領域を、前記保護膜の厚さよりも厚く、かつ前記導体ポストの頂上部を露出させて覆うように、前記保護膜と異なる材質からなる封止樹脂で封止する工程と、前記導体ポストの頂上部に外部接続端子を接合し、該外部接続端子が接合された半導体ウエハを個々のデバイス単位に分割する工程とを含むことを特徴とする半導体装置の製造方法が提供される。

20

#### 【0011】

30

本発明に係る半導体装置及びその製造方法の他の構成上の特徴及びそれに基づく有利な利点等については、発明の実施の形態を参照しながら説明する。

#### 【発明を実施するための最良の形態】

#### 【0012】

以下、本発明の好適な実施の形態について、添付の図面を参照しながら説明する。

#### 【0013】

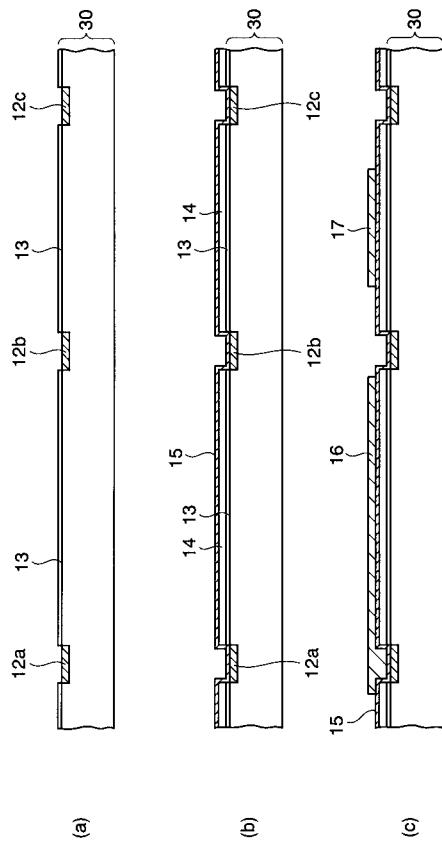

（第1の実施形態…図1～図5参照）

図1～図3は本発明の第1の実施形態に係るCSP構造の半導体装置の製造工程を断面図の形態で示したものである。

#### 【0014】

40

先ず、図3（b）を参照すると、10は本実施形態に係る半導体装置（CSP）、11はデバイスが作り込まれた半導体基板を示し、この半導体基板11は、後述する半導体ウエハを切断（分割）した一部分である。また、12a、12b及び12cはそれぞれデバイス上に形成された導体部の一部の領域によって画定された電極パッド、13は各電極パッド12a、12b、12cが形成されている側の面に形成されたパッシベーション膜、14はパッシベーション膜13上に形成された絶縁膜、15は絶縁膜14上に所要の形状にパターニング形成された金属薄膜、16は金属薄膜15上のー部の領域に形成された再配線層、16Pは再配線層16の端子形成部分、17は金属薄膜15上の他の領域に画定されたパッド、18及び19はそれぞれ電極パッド12b及び12cと金属薄膜15上のパッド17とを接続するポンディングワイヤ、20は再配線層16の端子形成部分16P

50

とパッド17の中央部とにそれぞれ形成された導体ポスト、21は再配線層16を覆って形成された保護膜、22は導体ポスト20が形成されている側の面において保護膜21で覆われていない残りの部分を覆うように（但し、導体ポスト20の頂上部を露出させて）形成された封止樹脂層、23は露出した導体ポスト20の頂上部に接合された外部接続端子を示す。

#### 【0015】

以下の記述において、導体ポスト20が形成されている部分のパッド17を、半導体基板11に作り込まれているデバイスの各電極パッド12a, 12b, 12cと区別する意味で、便宜上、「ポスト側パッド」という。

#### 【0016】

本実施形態では、このポスト側パッド17を電源プレーン又はグランドプレーンとして利用している。従って、各ワイヤ18, 19を介してポスト側パッド17に接続される各電極パッド12b, 12cは、基板11に作り込まれたデバイスの電源用（又はグランド用）の端子として割り当てられている。つまり、2個の電源用（又はグランド用）電極パッド12b, 12cにそれぞれボンディングされた各ワイヤ18, 19が、まとめて一つの電源プレーン（又はグランドプレーン）に接続されている。図示の例では、2本のワイヤ18, 19を電極パッド12b, 12cに接続した場合を示しているが、各電源用（又はグランド用）電極パッドとポスト側パッドとの位置関係によっては、3本もしくはそれ以上のワイヤを接続することも可能である（図4参照）。一方、再配線層16に接続される電極パッド12aは、基板11に作り込まれたデバイスの信号用の端子として割り当てられている。

#### 【0017】

本実施形態に係る半導体装置10は、図3（b）に示すように、基板11に作り込まれたデバイスの各電極パッド12b, 12cにそれぞれ一端が接続されたワイヤ18, 19の各々の他端をポスト側パッド17上で導体ポスト20の外側にそれぞれボンディングしたことを特徴とする。また、本実施形態では、後述するように本装置10を他の半導体装置（チップ）と共にプリント基板等に実装してSIP（システム・イン・パッケージ）を構築するよう意図している。

#### 【0018】

本実施形態の半導体装置10を構成する各部材の材料や形態等については、ここでは省略し、以下に記述する製造方法の中で適宜説明する。

#### 【0019】

以下、本実施形態に係るCSP構造の半導体装置10の製造方法について、図1～図3を参照しながら説明する。

#### 【0020】

先ず最初の工程では（図1（a）参照）、複数のデバイス（図示せず）が作り込まれたウエハ30を用意する。例えば、直径が8インチのシリコン（Si）ウエハ（ $725\mu m$ 程度の厚さ）に対し所要のデバイスプロセスを行った後、ウエハの表面（図示の例では上側の面）に窒化シリコン（SiN）やリンガラス（PSG）等からなる保護膜としてのパッシベーション膜13を形成し、各デバイス上に所要のパターンで多数形成されたアルミニウム（Al）の配線層の一部分によって画定される電極パッド12a, 12b, 12cに対応する部分のパッシベーション膜13を除去する（つまり、当該部分を開口する）。パッシベーション膜13の開口は、例えば、YAGレーザやエキシマレーザ等のレーザ加工によって行われる。これによって、図示のように表面がパッシベーション膜13で覆われ、かつ電極パッド12a, 12b, 12cが露出したウエハ30が作製される。なお、場合によっては、ウエハ表面にパッシベーション膜13を設けずに、次の工程で形成される絶縁膜にパッシベーション膜の機能を兼ねさせてもよい。

#### 【0021】

次の工程では（図1（b）参照）、ウエハ30のパッシベーション膜13上に絶縁膜14を形成し、絶縁膜14が形成されている側の全面にシード層としての金属薄膜15を形

10

20

30

40

50

成する。

#### 【0022】

先ず、フォトリソグラフィにより、ウエハ30の表面にレジストとしての感光性のポリイミド樹脂を塗布し、このポリイミド樹脂（レジスト）のソフトベーク（プリベーク）処理を行った後、マスク（図示せず）を用いて露光及び現像（レジストのパターニング）を行い、更にハードベーク（ポストベーク）処理を行い、図示のように所定の箇所に開口部を有する絶縁膜（ポリイミド樹脂層）14を形成する。この際、レジストのパターニングは、各電極パッド12a, 12b, 12cの形状に従って行う。従って、露光及び現像を行うと、図示のように各電極パッド12a, 12b, 12cに対応する部分のポリイミド樹脂層14が除去されて、それぞれ当該電極パッドに到達する開口部が形成される。

10

#### 【0023】

次いで、絶縁膜（ポリイミド樹脂層）14が形成されている側の全面に、スパッタリングにより、金属薄膜（シード層）15を形成する。この金属薄膜15は、密着金属層を構成するクロム（Cr）層又はチタン（Ti）層と、この上に積層される銅（Cu）層又は金（Au）層の2層構造を有している。金属薄膜15は、全面にCr又はTiをスパッタリングにより堆積させ（密着金属層：Cr層又はTi層）、更にその上にCu又はAuをスパッタリングにより堆積させることにより（Cu層又はAu層）、形成され得る。ここに、上層部分は厚さ数μm程度（Cu層の場合）又は厚さ数十μm程度（Au層の場合）に形成される。このようにして形成された金属薄膜（シード層）15は、後の工程で再配線や導体ポスト等を形成するのに必要な電解めっき処理の際に給電層として機能する。

20

#### 【0024】

なお、本工程では、ウエハ30の表面に形成する絶縁膜14として感光性のポリイミド樹脂を用いているが、絶縁膜14の材料は感光性樹脂に限定されないことはもちろんであり、例えば、非感光性のポリイミド樹脂やエポキシ樹脂等の樹脂を使用してもよい。但しこの場合は、フォトリソグラフィを用いることはできないため、例えば、レーザ加工により必要な開口部を形成することになる。

#### 【0025】

次の工程では（図1（c）参照）、所要の形状にレジストパターンを形成し、電解めっきを施して再配線層16及びポスト側パッド17を形成する。

#### 【0026】

30

先ず、金属薄膜15の表面の脱水ベークを行い、液状のフォトレジストを塗布して乾燥させた後、マスク（図示せず）を用いて露光及び現像（フォトレジストのパターニング）を行い、レジスト層（図示せず）を形成する。このフォトレジストのパターニングは、形成されるべき再配線層16及びポスト側パッド17の形状に従って行う。

#### 【0027】

次いで、金属薄膜（シード層）15を給電層としてその表面に電解銅（Cu）めっきを施し、パターニングされたレジスト層をマスクにして、Cuの再配線層16及びポスト側パッド17を厚さ数十μm程度に形成する。この後、有機溶剤を含む剥離液を用いてフォトレジスト（レジスト層）を除去する。

#### 【0028】

40

なお、本工程では、パターニング材料として液状のフォトレジストを用いているが、感光性のドライフィルムを用いて所要のレジストパターンを形成することもできる。この場合、金属薄膜15の表面（Cu層又はAu層表面）を清浄にした後、ドライフィルム（厚さ100μm程度）を熱圧着により貼り付け、さらに所要の形状にパターニングされたマスク（図示せず）を用いて露光及び現像（ドライフィルムのパターニング）を行い、レジスト層を形成する。そして、再配線層16及びポスト側パッド17を形成した後、水酸化ナトリウムやモノエタノールアミン系等のアルカリ性の薬液を用いてドライフィルム（レジスト層）を剥離し、除去する。

#### 【0029】

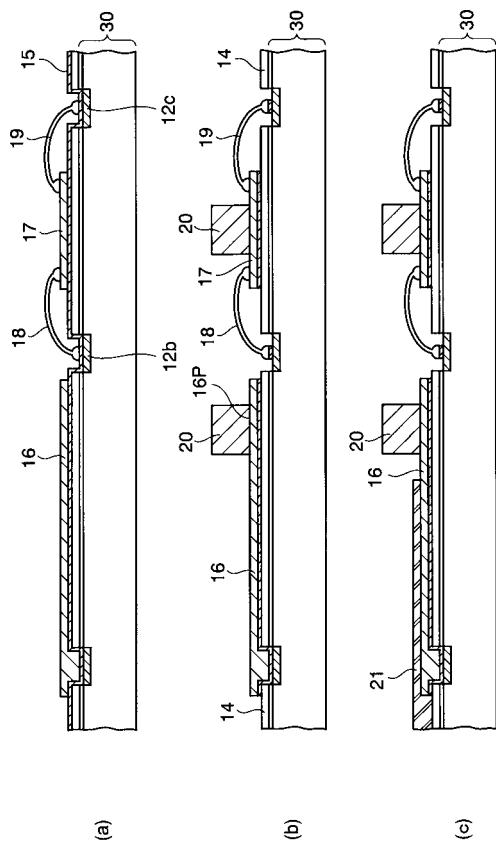

次の工程では（図2（a）参照）、ウエハ30に作り込まれたデバイスの各電極パッド

50

12b, 12c(その上の金属薄膜15)と、この金属薄膜15上のポスト側パッド17とをそれぞれボンディングワイヤ18, 19で接続する。この接続は、ボールボンディング法(超音波を併用した熱圧着法)を用いて行うことができる。先ず、ワイヤボンダーのツール先端(中空部分にボンディング用の金(Au)線又は銅(Cu)線を保持したキャピラリ)を電極パッド12b(又は12c)上の金属薄膜15(接合対象箇所)に接触させ、そのツール先端に溶製されたAuボール又はCuボールを、あらかじめ加熱された当該接合対象箇所に熱と圧力の下で生じる拡散と超音波振動による摩擦により接合させる。このときの加熱温度は、大体150~200程度である。次に、ツール先端をポスト側パッド17上の所定の箇所に接触させ、同様にしてAuボール又はCuボールを接合させる。このときの接合位置(所定の箇所)は、ポスト側パッド17の周辺部に近い箇所に選定される。

#### 【0030】

次の工程では(図2(b)参照)、所要の形状にレジストパターンを形成し、電解めっきを施して導体ポスト20を形成する。さらに、バリヤメタル層の形成、バックグランド処理等も行う。

#### 【0031】

先ず、ワイヤ18, 19がボンディングされている側の表面(金属薄膜15、再配線層16、ポスト側パッド17の各表面)の脱水ペークを行い、液状のフォトレジストを塗布して乾燥させた後、マスク(図示せず)を用いて露光及び現像(フォトレジストのパターニング)を行い、レジスト層(図示せず)を形成する。このフォトレジストのパターニングは、形成されるべき導体ポスト20の形状に従って行う。

#### 【0032】

次いで、金属薄膜(シード層)15を給電層として再配線層16及びポスト側パッド17の表面に電解Cuめっきを施し、パターニングされたレジスト層をマスクにして、再配線層16の端子形成部分16Pとポスト側パッド17の中央部にそれぞれ導体(Cu)ポスト20を高さ50~100μm程度に形成する。

#### 【0033】

さらにCuポスト20の頂上部に、電解めっきによりバリヤメタル層(図示せず)を形成する。このバリヤメタル層は、例えば、シード層15を給電層としてCuポスト20の表面に密着性向上のためのニッケル(Ni)めっきを施し、さらにこのNi層上に導電性向上のためのパラジウム(Pd)めっきを施した後、このPd層上に金(Au)めっきを施すことにより、形成され得る(Ni/Pd/Au)。あるいは、Pd層を設けずにNi層上に直接Au層を形成してもよい(Ni/Au)。この時点で、ワイヤ18, 19がボンディングされている側の面(図示の例では上側の面)は、Cuポスト20(及びバリヤメタル層)の表面とフォトレジスト(レジスト層)の表面によってほぼ平坦な状態となっている。

#### 【0034】

さらに、特に図示はしていないが、周知の研削装置を用いてウエハ裏面(図示の例では下側の面)を研削し、ウエハ30の厚さを250~300μm程度に薄くする(バックグランド処理)。このとき、上側の面はほぼ平坦であるので、研削に先立ってその上側の面を保持(チャック)するのが容易となり、このようにチャックした状態でウエハ30の裏面を所定の厚さに薄くすることができる。

#### 【0035】

この後、有機溶剤を含む剥離液を用いてフォトレジスト(レジスト層)を除去し、さらに、ウェットエッチングにより、露出している金属薄膜(シード層)15を除去する。すなわち、Cuを溶かすエッチング液又はAuを溶かすエッチング液でシード層15の上層部分(Cu層又はAu層)を除去し、次にCr又はTiを溶かすエッチング液で下層部分の密着金属層(Cr層又はTi層)を除去する。これによって、図2(b)に示すように絶縁膜(ポリイミド樹脂層)14が露出する。この後、所定の表面洗浄等を行う。

#### 【0036】

10

20

30

40

50

なお、Cuを溶かすエッチング液を用いた時、再配線層16及びポスト側パッド17を構成するCuも同様に除去されて導体パターンが断線するよう見えるが、実際にはかかる不都合は生じない。その理由は、上述したように、シード層15の上層部分はCu又はAuのスパッタリングにより形成されるためその膜厚は数μm程度の厚さであるのに対し、再配線層16及びポスト側パッド17は電解Cuめっきにより形成されるためその膜厚は数十μm程度の厚さであるので、シード層15のCu又はAuは完全に除去されても、再配線層16及びポスト側パッド17のCuはその表層部分のみが除去される程度であり、導体パターンが断線することはないからである。

#### 【0037】

次の工程では(図2(c)参照)、再配線層16上に保護膜としてのポリイミド樹脂層21を形成する。これは、図1(b)の工程で行った「絶縁膜(ポリイミド樹脂層)14の形成」処理と同様にして、フォトリソグラフィにより形成することができる。図示の例では、再配線層16の一部の領域(Cuポスト20が形成されている部分)については、ポリイミド樹脂層21で覆われていないが、次の工程で同様の保護膜(封止樹脂層)で覆われることになるので、支障はない。

#### 【0038】

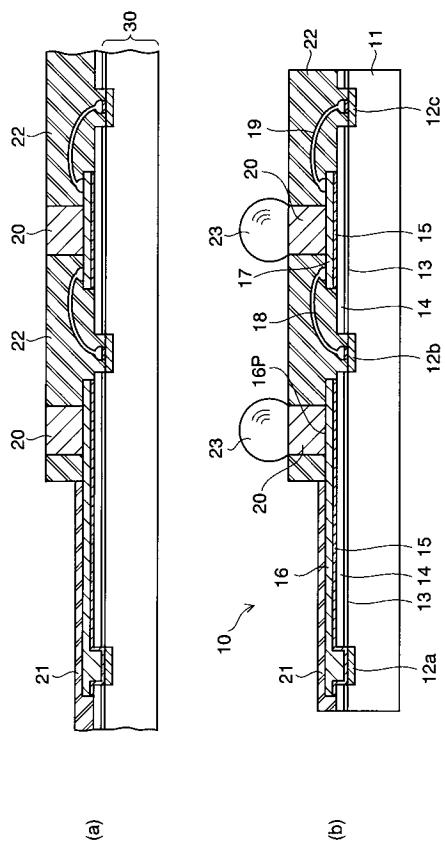

次の工程では(図3(a)参照)、ウエハ30のCuポスト20が形成されている側の面においてポリイミド樹脂層21で覆われていない残りの部分を覆うように(但し、Cuポスト20(バリヤメタル層)の頂上部を露出させて)樹脂で封止する(封止樹脂層22の形成)。これは、例えば以下のようにして行うことができる。

#### 【0039】

先ず、上型と下型に分かれた封止金型を用意し、これを175°C程度に加熱する。次いで上型に樹脂フィルムを吸着させ、下型の凹部内にウエハ30を装着し、さらにこの上に封止樹脂として密着力の高いタブレット状のエポキシ樹脂を載せる。そして、封止金型の熱とプレスによる圧力でエポキシ樹脂を溶融してウエハ全面に広げ、金型内で保持しながらエポキシ樹脂を硬化させる処理(キュア)を行う。この後、金型からウエハ30を取り外す。この時、ウエハ30は樹脂フィルムと一体になっているので、この樹脂フィルムをウエハ30から引き剥がす。これによって、図示のように表面(ポリイミド樹脂層21で覆われている部分を除く)がエポキシ樹脂層22で覆われ、かつ、Cuポスト20(バリヤメタル層)の頂上部が露出したウエハ30が作製される。

#### 【0040】

最後の工程では(図3(b)参照)、露出したCuポスト20(バリヤメタル層)の頂上部に、表面処理剤としてのフラックスを塗布した後、外部接続端子として用いられるはんだボール23を搭載し、240°C~260°C程度の温度でリフローして固定する。その後、表面を洗浄してフラックスを除去する。

#### 【0041】

この後、ダイサー等により、封止樹脂層22及び保護膜21と共にウエハ30を切断して個々の半導体装置(チップ)に分割する。これによって、第1の実施形態に係るCSP構造の半導体装置10が作製されることになる。

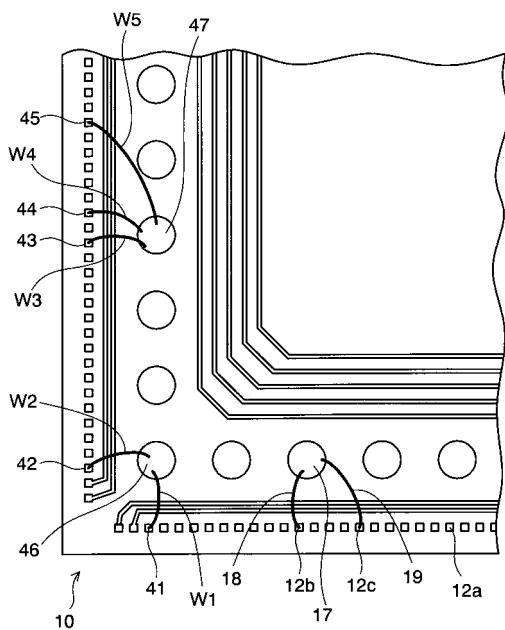

#### 【0042】

図4は、本実施形態に係る半導体装置10の要部の構成を平面図の形態で模式的に示したものであり、図2(a)の工程で行う「ワイヤボンディング」の直後の状態を表している。ウエハに作り込まれたデバイスの各電極パッド12a, 12b, 12cは、図示のように最終的に分割される当該デバイス(半導体装置10)の周辺部に沿って配列されており、これら各電極パッドが形成されている領域の内側には、同様に周辺部に沿って端子形成部分16P及びポスト側パッド17が配列されている。図4には示していないが、端子形成部分16Pは再配線層16の一部の領域に画定された部分であり、この端子形成部分16Pとポスト側パッド17には、それぞれ最終的に導体ポスト20が形成され、さらに各導体ポスト20上に外部接続端子23が接合されるようになっている。つまり、当該デバイス(半導体装置10)は、その周辺部に沿って外部接続端子が配列された「ペリフェ

10

20

30

40

50

ラル型」のパッケージ構造を有している。なお、図示の例では簡単化のため、外部接続端子（端子形成部分 16P、ポスト側パッド 17）を 1 列に配列した場合を示している。

#### 【0043】

また、各電極パッドのうち、電極パッド 12b, 12c は、上述したように電源用又はグランド用の端子として割り当てられ、電極パッド 12a は信号用の端子として割り当てられている。信号用の電極パッド 12a は、再配線層 16（図示せず）を介して端子形成部分 16P に接続され、電源用又はグランド用の電極パッド 12b, 12c は、それぞれボンディングワイヤ 18, 19 を介して共通のポスト側パッド 17 にまとめて接続されている。同様に他の電源用又はグランド用の電極パッド 41, 42, 43, 44, 45 についても、それぞれボンディングワイヤ W1, W2, W3, W4, W5 を介して、近傍のポスト側パッド（電源プレーン又はグランドプレーン）46, 47 にそれぞれまとめて接続されている。10

#### 【0044】

以上説明したように、第 1 の実施形態に係る CSP 構造の半導体装置 10 及びその製造方法によれば（図 1～図 4 参照）、半導体基板 11 に作り込まれたデバイスの各電極パッドのうち一部の電極パッド 12b, 12c は、ボンディングワイヤ 18, 19 を介して導体（Cu）層の一部分であるポスト側パッド 17（Cu ポスト 20、外部接続端子 23）に接続されている。また、残りの電極パッド 12a は、同じ導体（Cu）層である配線層 16 を介して端子形成部分 16P（Cu ポスト 20、外部接続端子 23）に接続されている。これにより、ウエハレベルパッケージであってもウエハレベル上の外部接続端子 23 の再配置を当該導体層（1 層の導体部）で実現することができる。つまり、1 層の導体部で所要の再配線を行うことができるので、コストの低減化を図ることができる。20

#### 【0045】

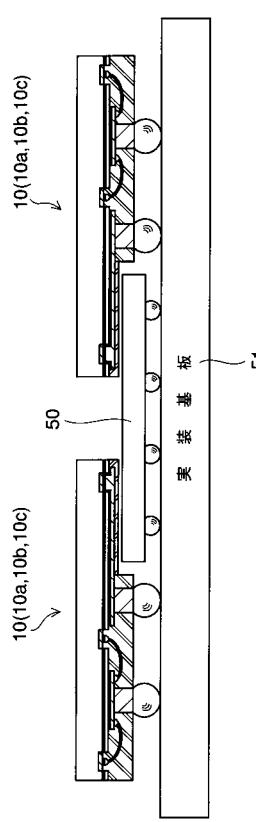

また、本装置（チップ）10 は、封止樹脂層 22 で覆われている部分（外部接続端子が形成されている領域）と比べて保護膜 21 で覆われている部分が「薄く」形成されているので、この「薄く」形成されている部分を有效地に利用することができる。例えば、図 5 に示すようにプリント基板等の実装基板 51 に他の半導体装置（チップ）50 と共に「フェイスダウン」の態様で実装する場合に、この他のチップ 50 を、本装置 10 の「薄く」なっている部分の直下の空所部分に配置することができる。図 5 の例では、本装置 10 を 2 個用意し、各々の「薄く」なっている部分を対向させて配置し、各々の部分の直下の空所部分に他のチップ 50 を配置している。このように実装に際し本装置 10 の「薄く」なっている部分を有效地に利用できるので、単純に 3 個のチップを横方向に並べて配置する場合と比べると、実装基板上に占める面積を小さくすることができる。言い換えると、実装基板 51 の面積が一定であれば、本装置（チップ）10 を含めてより多くのチップを搭載できることになり、MCP（マルチチップパッケージ）としてより一層の高機能化に寄与することができる。30

#### 【0046】

また、このような実装形態（図 5）とすることにより、特許文献 1 に記載されているような、2 つのチップを積み重ねて実装するスタックタイプの MCP と比べると、高さ方向のサイズを小さくすることができる。つまり、薄型化を図ることができる。40

#### 【0047】

また、MCP の一つである SIP（システム・イン・パッケージ）においては、現状、各チップ間を Au ワイヤで接続する技術が主流であるが、この Au ワイヤを介しての配線長は比較的長いため、高速化に適していない。これに対し、図 5 に示すような「フェイスダウン」の態様で実装し、各チップ 10, 50 間をはんだボール（外部接続端子）を介して接続すれば、配線長は相対的に短くなるので、高速化に対応することができる。

#### 【0048】

上述した第 1 の実施形態では（図 3（b）参照）、半導体基板 11 内のデバイスの各電極パッド 12b, 12c にそれぞれ一端が接続されたワイヤ 18, 19 の各々の他端をポスト側パッド 17 上で導体ポスト 20 の外側にそれぞれボンディングしているが、ボンデ50

イングの態様がこれに限定されないことはもちろんであり、他にも種々の接続態様が考えられる。以下、幾つかの接続態様について説明する。

#### 【0049】

(第2の実施形態...図6参照)

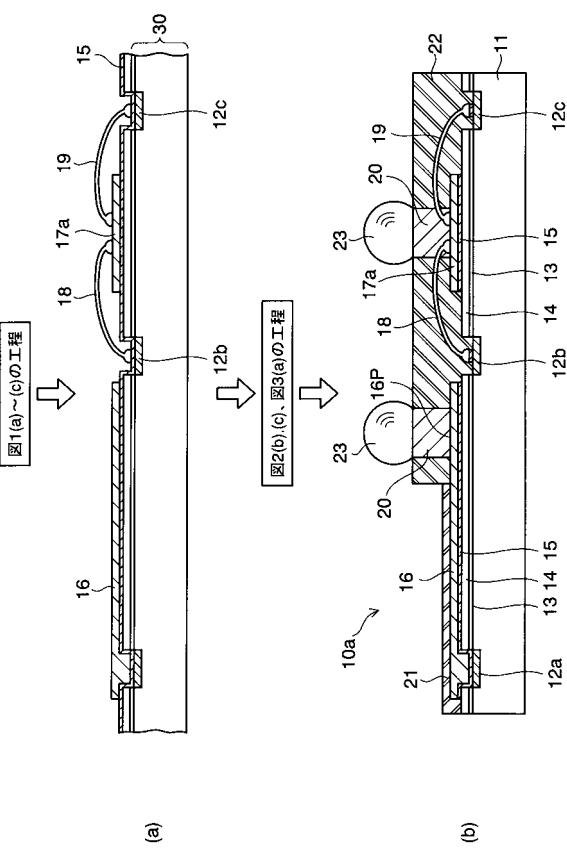

図6は本発明の第2の実施形態に係る半導体装置の製造工程の一部を断面図の形態で示したものである。

#### 【0050】

本実施形態に係る半導体装置10aは、図6(b)に示すように、基板11に作り込まれたデバイスの各電極パッド12b, 12c(その上のシード層15)にそれぞれ一端が接続されたワイヤ18, 19の各々の他端をポスト側パッド17a上で導体ポスト20の内側にそれぞれボンディングしたことを特徴とする。本実施形態の半導体装置10aは、図1(a)~(c)の工程と同じ工程を経た後、図2(a)の工程で行った処理と同様の「ワイヤボンディング」を行い(図6(a)参照)、さらに図2(b), (c)及び図3(a)の工程で行った処理と同様の処理を経た後、図3(b)の工程で行った処理と同様の「はんだボールの接合」及び「ダイシング」を行うことにより(図6(b)参照)、製造される。10

#### 【0051】

なお、図6(a)の工程において各ワイヤ18, 19をボンディングする際、ワイヤボンダーのツール先端をポスト側パッド17a上の所定の箇所に接触させてAuボールを接合させることになるが、このときの接合位置(所定の箇所)は、ポスト側パッド17aの中央部に近い箇所に選定される。これによって、図6(b)に示すようにポスト側パッド17aの中央部に導体ポスト20が形成されたときに各ワイヤ18, 19の接続端部が当該ポスト20に埋め込まれるようになる。20

#### 【0052】

この第2の実施形態によれば、上述した第1の実施形態で得られた効果に加え、さらに以下の利点が得られる。すなわち、基板11の各電極パッド12b, 12cにそれぞれ一端が接続されたワイヤ18, 19の各々の他端が導体ポスト20に埋め込まれてポスト側パッド17aにボンディングされているので、第1の実施形態のように「各ワイヤ18, 19の他端が導体ポスト20の外側でポスト側パッド17にボンディングされた構造」と比べて、ポスト側パッド17aの大きさを小さく形成することができる。つまり、その小さくなつた分だけスペースに余裕ができるので、隣合う導体ポスト20間の配置間隔を狭めることができ、特に高密度化を意図したピン数の多いパッケージに適用する場合に有効である。30

#### 【0053】

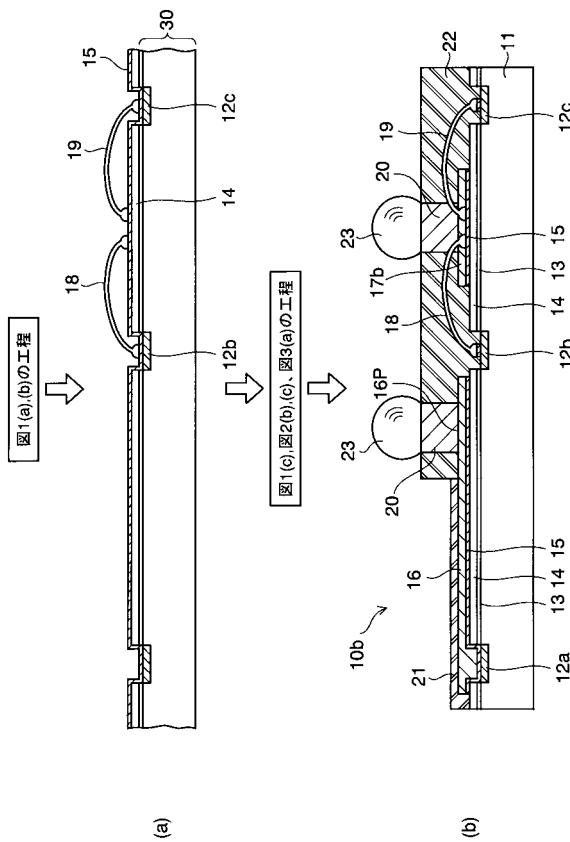

(第3の実施形態...図7参照)

図7は本発明の第3の実施形態に係る半導体装置の製造工程の一部を断面図の形態で示したものである。

#### 【0054】

本実施形態に係る半導体装置10bは、図7(b)に示すように、基板11に作り込まれたデバイスの各電極パッド12b, 12c(その上のシード層15)にそれぞれ一端が接続されたワイヤ18, 19の各々の他端を、シード層15にボンディングすると共に、シード層15上に形成したポスト側パッド17bで埋め込んだことを特徴とする。本実施形態の半導体装置10bは、図1(a), (b)の工程と同じ工程を経た後、図2(a)の工程で行った処理と同様の「ワイヤボンディング」を行い(図7(a)参照)、さらに図1(c)、図2(b), (c)及び図3(a)の工程で行った処理と同様の「はんだボールの接合」及び「ダイシング」を行うことにより(図7(b)参照)、製造される。40

#### 【0055】

ただし、本実施形態では、図7(a)の工程において各ワイヤ18, 19をボンディングする際、ワイヤボンダーのツール先端を絶縁膜14上のシード層15の所定の箇所に接50

触させて A u ボール又は C u ボールを接合させることになるが、このときの接合位置（所定の箇所）は、図 7 ( b ) に示すように導体ポスト 2 0 の内側に対応する箇所に選定される。これによって、上述した第 2 の実施形態の場合と同様に、ポスト側パッド 1 7 b の中央部に導体ポスト 2 0 が形成されたときに各ワイヤ 1 8 , 1 9 の一部が当該ポスト 2 0 に埋め込まれ、かつ各々の接続端部がポスト側パッド 1 7 b に埋め込まれるようになる。

#### 【 0 0 5 6 】

この第 3 の実施形態によれば、上述した第 2 の実施形態の場合と同様の装置構成を有しているので、第 2 の実施形態で得られた効果と同様の効果が得られる。

#### 【 0 0 5 7 】

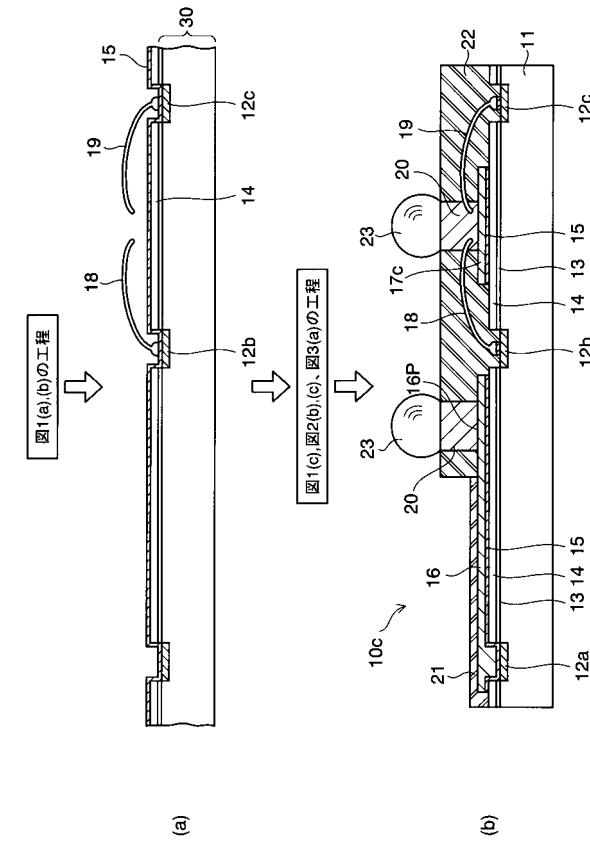

（第 4 の実施形態…図 8 参照）

10

図 8 は本発明の第 4 の実施形態に係る半導体装置の製造工程の一部を断面図の形態で示したものである。

#### 【 0 0 5 8 】

本実施形態に係る半導体装置 1 0 c は、図 8 ( b ) に示すように、基板 1 1 に作り込まれたデバイスの各電極パッド 1 2 b , 1 2 c ( その上のシード層 1 5 ) にそれぞれ一端が接続されたワイヤ 1 8 , 1 9 の各々の他端を、フロー・ティング状態（どこにも接続しない状態）にすると共に、ポスト側パッド 1 7 c 上に形成した導体ポスト 2 0 で埋め込んだことを特徴とする。本実施形態の半導体装置 1 0 c は、図 1 ( a ) , ( b ) の工程と同じ工程を経た後、図 2 ( a ) の工程で行った処理と同様の「ワイヤボンディング」を行い（図 8 ( a ) 参照）、さらに図 1 ( c ) 、図 2 ( b ) , ( c ) 及び図 3 ( a ) の工程で行った処理と同様の処理を経た後、図 3 ( b ) の工程で行った処理と同様の「はんだボールの接合」及び「ダイシング」を行うことにより（図 8 ( b ) 参照）、製造される。

20

#### 【 0 0 5 9 】

ただし、本実施形態では、図 8 ( a ) の工程において各ワイヤ 1 8 , 1 9 をボンディングする際、2 度目のボンディング（絶縁膜 1 4 上のシード層 1 5 への接続）は不要であるが、後の工程でポスト側パッド 1 7 c の中央部に導体ポスト 2 0 が形成されたときに各ワイヤ 1 8 , 1 9 の各々の他端が当該ポスト 2 0 に埋め込まれるような位置に保持しておく必要がある。

#### 【 0 0 6 0 】

この第 4 の実施形態によれば、上述した第 2 、第 3 の実施形態で得られた効果に加え、ワイヤボンディングを行う際に 1 度目のボンディング（電極パッド 1 2 b , 1 2 c 上のシード層 1 5 への接続）のみで済み、2 度目のボンディングは行う必要がないので、ワイヤボンディング処理を簡素化できるというメリットがある。これは、製造コストの低減化に寄与する。

30

#### 【 図面の簡単な説明 】

#### 【 0 0 6 1 】

【 図 1 】本発明の第 1 の実施形態に係る C S P 構造の半導体装置の製造工程を示す断面図である。

【 図 2 】図 1 の製造工程に続く製造工程を示す断面図である。

【 図 3 】図 2 の製造工程に続く製造工程を示す断面図である。

40

【 図 4 】本実施形態に係る半導体装置の要部の構成を模式的に示す平面図である。

【 図 5 】本実施形態に係る半導体装置の実装形態の一例を示す断面図である。

【 図 6 】本発明の第 2 の実施形態に係る半導体装置の製造工程の一部を示す断面図である。

【 図 7 】本発明の第 3 の実施形態に係る半導体装置の製造工程の一部を示す断面図である。

【 図 8 】本発明の第 4 の実施形態に係る半導体装置の製造工程の一部を示す断面図である。

#### 【 符号の説明 】

#### 【 0 0 6 2 】

50

- 10, 10a, 10b, 10c ... 半導体装置 (CSP / チップ)、

11 ... 半導体 (シリコン) 基板、

12a, 12b, 12c, 41 ~ 45 ... 電極パッド、

13 ... パッシベーション膜、

14 ... 絶縁膜 (ポリイミド樹脂層)、

15 ... 金属薄膜 (シード層)、

16 ... 再配線層、

16P ... 端子形成部分、

17, 17a, 17b, 17c, 46, 47 ... ポスト側パッド (外部端子用パッド)、

18, 19, W1 ~ W5 ... ボンディングワイヤ、

20 ... 導体 (Cu) ポスト、

21 ... 保護膜 (ポリイミド樹脂層)、

22 ... 封止樹脂層 (エポキシ樹脂層)、

23 ... 外部接続端子 (はんだボール)、

30 ... 半導体 (シリコン) ウエハ、

50 ... 他の半導体装置 (チップ)、

51 ... 実装基板。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

---

フロントページの続き

(58)調査した分野(Int.Cl., DB名)

H 01 L 23 / 12 , 28

H 01 L 21 / 60

H 01 L 25 / 10