#### (12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

# (19) World Intellectual Property **Organization**

International Bureau

(43) International Publication Date 21 July 2005 (21.07.2005)

## (10) International Publication Number WO 2005/066970 A2

(51) International Patent Classification<sup>7</sup>: 29/00, G06F 11/20

G11C 11/56,

(21) International Application Number:

PCT/US2004/043680

(22) International Filing Date:

22 December 2004 (22.12.2004)

(25) Filing Language:

**English**

(26) Publication Language:

English

(30) Priority Data:

10/750,155 30 December 2003 (30.12.2003) US 13 August 2004 (13.08.2004) 10/917,725

(71) Applicant (for all designated States except US): SAN-DISK CORPORATION [US/US]; 140 Caspian Court, Sunnyvale, California 94089 (US).

- (72) Inventors; and

- (75) Inventors/Applicants (for US only): GOROBETS, Sergey Anatolievich [RU/GB]; 1F1, 92 Blackford Avenue, Edinburgh Midlothian EH9 3ES (GB). BRYCE, Alan Douglas [GB/GB]; Flat 6, Block 7, Allanfield, Edinburgh Midlothian EH7 5YH (GB). BENNETT, Alan David [GB/GB]; 2 Thorburn Road, Edinburgh Midlothian EH13 0BQ (GB).

- (74) Agents: PARSONS, Gerald, P. et al.; Parsons, Hsue & de Runtz LLP, 655 Montgomery Street, Suite 1800, San Francisco, California 94111 (US).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BW, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, HR, HU, ID, IL, IN, IS, JP, KE, KG, KP, KR, KZ, LC, LK, LR, LS, LT, LU, LV, MA, MD, MG, MK, MN, MW, MX, MZ, NA, NI, NO, NZ, OM, PG,

[Continued on next page]

(54) Title: NON-VOLATILE MEMORY AND METHOD WITH CONTROL DATA MANAGEMENT

#### Multistate Page

2<sup>nd</sup> program 1st program

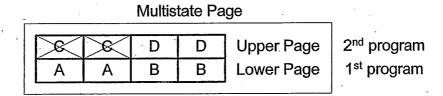

Robust Arrangement of Duplicate Sectors in a Page

(57) Abstract: In a nonvolatile memory with block management system, critical data such as control data for the block management system is maintained in duplicates. Various methods are described for robustly writing and reading two copies of critical data in multi-state memory. In another aspect of the invention, a preemptive garbage collection on memory block containing control data avoids an undesirable situation where a large number of such memory blocks need be garbage collected at the same time.

# WO 2005/066970 A2

PH, PL, PT, RO, RU, SC, SD, SE, SG, SK, SL, SY, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, YU, ZA, ZM, ZW.

(84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HU, IE, IS, IT, LT, LU, MC, NL, PL, PT, RO,

SE, SI, SK, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

#### **Published:**

without international search report and to be republished upon receipt of that report

For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.

# NON-VOLATILE MEMORY AND METHOD WITH CONTROL DATA MANAGEMENT

#### FIELD OF THE INVENTION

[0001] This invention relates generally to non-volatile semiconductor memory and specifically to those having a memory block management system with critical handling of control data

#### BACKGROUND OF THE INVENTION

[0002] Solid-state memory capable of nonvolatile storage of charge, particularly in the form of EEPROM and flash EEPROM packaged as a small form factor card, has recently become the storage of choice in a variety of mobile and handheld devices, notably information appliances and consumer electronics products. Unlike RAM (random access memory) that is also solid-state memory, flash memory is non-volatile, and retaining its stored data even after power is turned off. Also, unlike ROM (read only memory), flash memory is rewritable similar to a disk storage device. In spite of the higher cost, flash memory is increasingly being used in mass storage applications. Conventional mass storage, based on rotating magnetic medium such as hard drives and floppy disks, is unsuitable for the mobile and handheld environment. This is because disk drives tend to be bulky, are prone to mechanical failure and have high latency and high power requirements. These undesirable attributes make disk-based storage impractical in most mobile and portable applications. On the other hand, flash memory, both embedded and in the form of a removable card is ideally suited in the mobile and handheld environment because of its small size, low power consumption, high speed and high reliability features.

[0003] Flash EEPROM is similar to EEPROM (electrically erasable and programmable read-only memory) in that it is a non-volatile memory that can be

erased and have new data written or "programmed" into their memory cells. Both utilize a floating (unconnected) conductive gate, in a field effect transistor structure, positioned over a channel region in a semiconductor substrate, between source and drain regions. A control gate is then provided over the floating gate. The threshold voltage characteristic of the transistor is controlled by the amount of charge that is retained on the floating gate. That is, for a given level of charge on the floating gate, there is a corresponding voltage (threshold) that must be applied to the control gate before the transistor is turned "on" to permit conduction between its source and drain regions. In particular, flash memory such as Flash EEPROM allows entire blocks of memory cells to be erased at the same time.

[0004] The floating gate can hold a range of charges and therefore can be programmed to any threshold voltage level within a threshold voltage window. The size of the threshold voltage window is delimited by the minimum and maximum threshold levels of the device, which in turn correspond to the range of the charges that can be programmed onto the floating gate. The threshold window generally depends on the memory device's characteristics, operating conditions and history. Each distinct, resolvable threshold voltage level range within the window may, in principle, be used to designate a definite memory state of the cell.

[0005] The transistor serving as a memory cell is typically programmed to a "programmed" state by one of two mechanisms. In "hot electron injection," a high voltage applied to the drain accelerates electrons across the substrate channel region. At the same time a high voltage applied to the control gate pulls the hot electrons through a thin gate dielectric onto the floating gate. In "tunneling injection," a high voltage is applied to the control gate relative to the substrate. In this way, electrons are pulled from the substrate to the intervening floating gate. While the term "program" has been used historically to describe writing to a memory by injecting electrons to an initially erased charge storage unit of the memory cell so as to alter the memory state, it has now been used interchangeable with more common terms such as "write" or "record."

[0006] The memory device may be erased by a number of mechanisms. For EEPROM, a memory cell is electrically erasable, by applying a high voltage to the substrate relative to the control gate so as to induce electrons in the floating gate to

tunnel through a thin oxide to the substrate channel region (i.e., Fowler-Nordheim tunneling.) Typically, the EEPROM is erasable byte by byte. For flash EEPROM, the memory is electrically erasable either all at once or one or more minimum erasable blocks at a time, where a minimum erasable block may consist of one or more sectors and each sector may store 512 bytes or more of data.

[0007] The memory device typically comprises one or more memory chips that may be mounted on a card. Each memory chip comprises an array of memory cells supported by peripheral circuits such as decoders and erase, write and read circuits. The more sophisticated memory devices also come with a controller that performs intelligent and higher level memory operations and interfacing.

There are many commercially successful non-volatile solid-state [8000] memory devices being used today. These memory devices may be flash EEPROM or may employ other types of nonvolatile memory cells. Examples of flash memory and systems and methods of manufacturing them are given in United States patents nos. 5,070,032, 5,095,344, 5,315,541, 5,343,063, and 5,661,053, 5,313,421 and 6,222,762. In particular, flash memory devices with NAND string structures are described in United States patent nos. 5,570,315, 5,903,495, 6,046,935. Also nonvolatile memory devices are also manufactured from memory cells with a dielectric layer for storing charge. Instead of the conductive floating gate elements described earlier, a dielectric layer is used. Such memory devices utilizing dielectric storage element have been described by Eitan et al., "NROM: A Novel Localized Trapping, 2-Bit Nonvolatile Memory Cell," IEEE Electron Device Letters, vol. 21, no. 11, November 2000, pp. 543-545. An ONO dielectric layer extends across the channel between source and drain diffusions. The charge for one data bit is localized in the dielectric layer adjacent to the drain, and the charge for the other data bit is localized in the dielectric layer adjacent to the source. For example, United States patents nos. 5,768,192 and 6,011,725 disclose a nonvolatile memory cell having a trapping dielectric sandwiched between two silicon dioxide layers. Multi-state data storage is implemented by separately reading the binary states of the spatially separated charge storage regions within the dielectric.

[0009] In order to improve read and program performance, multiple charge storage elements or memory transistors in an array are read or programmed in

parallel. Thus, a "page" of memory elements are read or programmed together. In existing memory architectures, a row typically contains several interleaved pages or it may constitute one page. All memory elements of a page will be read or programmed together.

[0010] In flash memory systems, erase operation may take as much as an order of magnitude longer than read and program operations. Thus, it is desirable to have the erase block of substantial size. In this way, the erase time is amortized over a large aggregate of memory cells.

[0011] The nature of flash memory predicates that data must be written to an erased memory location. If data of a certain logical address from a host is to be updated, one way is rewrite the update data in the same physical memory location. That is, the logical to physical address mapping is unchanged. However, this will mean the entire erase block contain that physical location will have to be first erased and then rewritten with the updated data. This method of update is inefficient, as it requires an entire erase block to be erased and rewritten, especially if the data to be updated only occupies a small portion of the erase block. It will also result in a higher frequency of erase recycling of the memory block, which is undesirable in view of the limited endurance of this type of memory device.

Another problem with managing flash memory system has to do with system control and directory data. The data is produced and accessed during the course of various memory operations. Thus, its efficient handling and ready access will directly impact performance. It would be desirable to maintain this type of data in flash memory because flash memory is meant for storage and is nonvolatile. However, with an intervening file management system between the controller and the flash memory, the data can not be accessed as directly. Also, system control and directory data tends to be active and fragmented, which is not conducive to storing in a system with large size block erase. Conventionally, this type of data is set up in the controller RAM, thereby allowing direct access by the controller. After the memory device is powered up, a process of initialization enables the flash memory to be scanned in order to compile the necessary system control and directory information to be placed in the controller RAM. This process takes time and requires controller RAM capacity, all the more so with ever increasing flash memory capacity.

[0013] US 6,567,307 discloses a method of dealing with sector updates among large erase block including recording the update data in multiple erase blocks acting as scratch pad and eventually consolidating the valid sectors among the various blocks and rewriting the sectors after rearranging them in logically sequential order. In this way, a block needs not be erased and rewritten at every slightest update.

[0014] W0 03/027828 and W0 00/49488 both disclose a memory system dealing with updates among large erase block including partitioning the logical sector addresses in zones. A small zone of logical address range is reserved for active system control data separate from another zone for user data. In this way, manipulation of the system control data in its own zone will not interact with the associated user data in another zone. Updates are at the logical sector level and a write pointer points to the corresponding physical sectors in a block to be written. The mapping information is buffered in RAM and eventually stored in a sector allocation table in the main memory. The latest version of a logical sector will obsolete all previous versions among existing blocks, which become partially obsolete. Garbage collection is performed to keep partially obsolete blocks to an acceptable number.

[0015] Prior art systems tend to have the update data distributed over many blocks or the update data may render many existing blocks partially obsolete. The result often is a large amount of garbage collection necessary for the partially obsolete blocks, which is inefficient and causes premature aging of the memory. Also, there is no systematic and efficient way of dealing with sequential update as compared to non-sequential update.

[0016] Therefore there is a general need for high capacity and high performance non-volatile memory. In particular, there is a need to have a high capacity nonvolatile memory able to conduct memory operations in large blocks without the aforementioned problems.

#### SUMMARY OF INVENTION

[0017] A non-volatile memory system is organized in physical groups of physical memory locations. Each physical group (metablock) is erasable as a unit and can be used to store a logical group of data. A memory management system allows for update of a logical group of data by allocating a metablock dedicated to recording the update data of the logical group. The update metablock records update data in the order received and has no restriction on whether the recording is in the correct logical order as originally stored (sequential) or not (chaotic). Eventually the update metablock is closed to further recording. One of several processes will take place, but will ultimately end up with a fully filled metablock in the correct order which replaces the original metablock. In the chaotic case, directory data is maintained in the non-volatile memory in a manner that is conducive to frequent updates. The system supports multiple logical groups being updated concurrently.

[0018] One feature of the invention allows data to be updated logical-group by logical-group. Thus, when a logical group is being updated, the distribution of logical units (and also the scatter of memory units that the updates obsolete) are limited in range. This is especially true when the logical group is normally contained within a physical block.

[0019] During updates of the logical group, typically one or two blocks need be assigned to buffer the updated logical units. Thus, garbage collection need only be performed over a relatively fewer number of blocks. Garbage collection of a chaotic block may be performed by either consolidation or compaction.

[0020] The economy of the update process is further evident in the generic treatment of the update blocks so that no additional block need be assigned for chaotic (non-sequential) updates as compared to the sequential ones. All update blocks are allocated as sequential update block, and any update block can change to a chaotic update block. Indeed, the change of an update block from sequential to chaotic is discretionary.

[0021] The efficient use of system resource allows multiple logical groups to be updated concurrently. This further increases efficiency and reduces overheads.

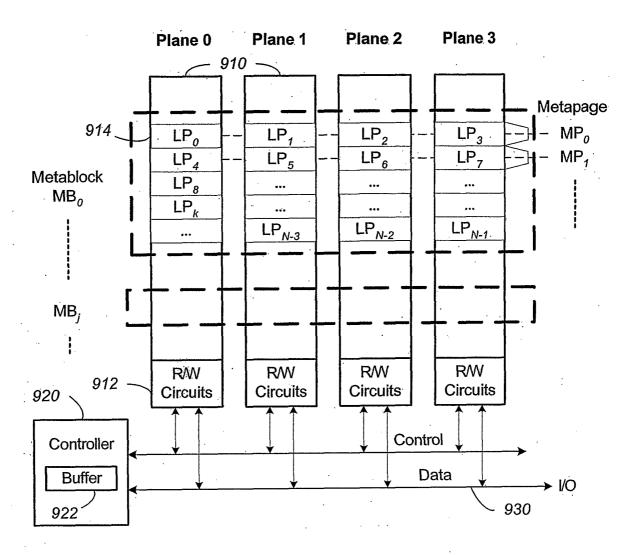

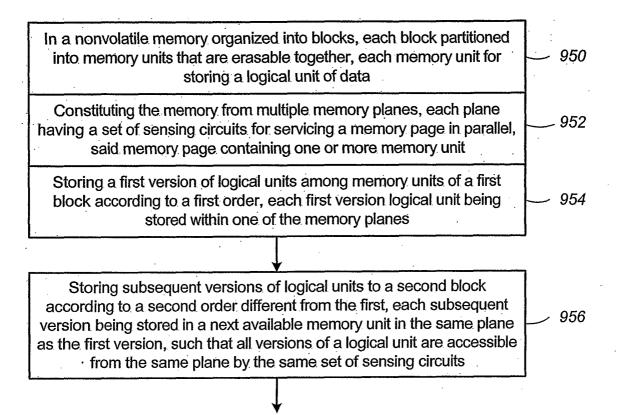

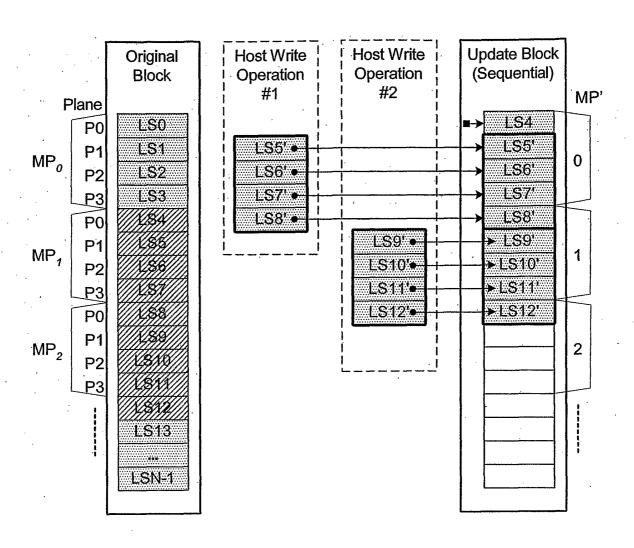

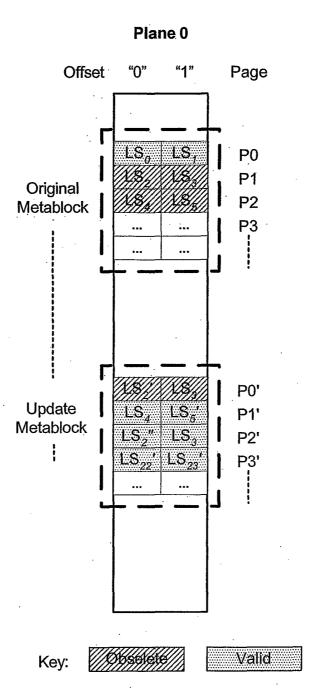

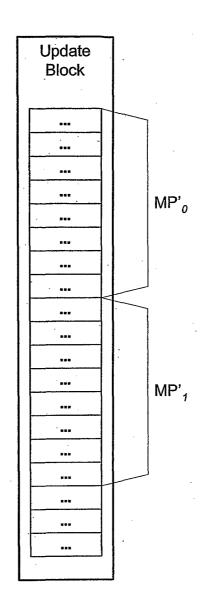

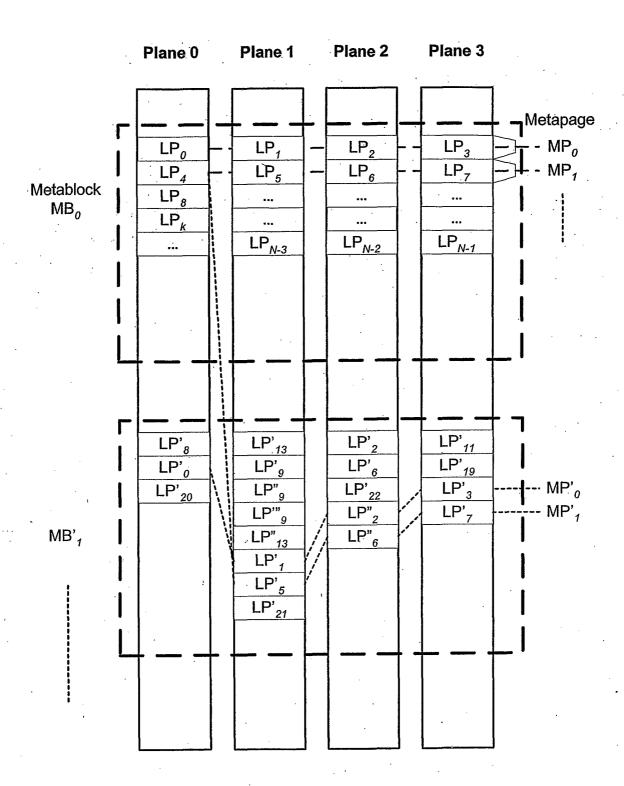

# Alignment For Memory Distributed Over Multiple Memory Planes

[0022] According to another aspect of the invention, for a memory array organized into erasable blocks and constituted from multiple memory planes so that logical units can be read or programmed into the multiple planes in parallel, when an original logical unit of a first block stored in a given memory plane is to be updated, provisions are made to keep the updated logical unit in the same plane as the original. This is accomplished by recording the updated logical unit to the next available location of a second block but in the same plane. Preferably, the logical unit is stored with an identical offset position in the plane as its other versions so that all versions of a given logical units are serviced by an identical set of sensing circuits.

[0023] In a preferred embodiment, any intervening gaps from the last programmed memory unit to the next available plane-aligned memory unit are padded accordingly with the current versions of logical units. The padding is accomplished by filling in a gap with current versions of the logical units that follow logically from the last programmed logical unit, and with current versions of the logical units that precede logically from the logical unit stored in the next available plane-aligned memory unit.

[0024] In this way, all versions of a logical unit are maintained in the same plane with the same offsets as the original so that in a garbage collection operation, the latest version of the logical unit need not be retrieved from a different plane, resulting in reduced performance. In a preferred embodiment, each memory unit across the plane is either updated or padded with the latest versions. Thus a logical unit from each plane could be read out in parallel, which will be in logical sequential order without the need for further rearrangement.

[0025] This scheme reduces the time for consolidation of a chaotic block by allowing on-plane rearrangement of the latest versions of the logical units of a logical group and avoiding having to gather the latest versions from different memory planes. This is of benefit where the performance specification for the host interface defines a maximum latency for completion of a sector write operation by the memory system.

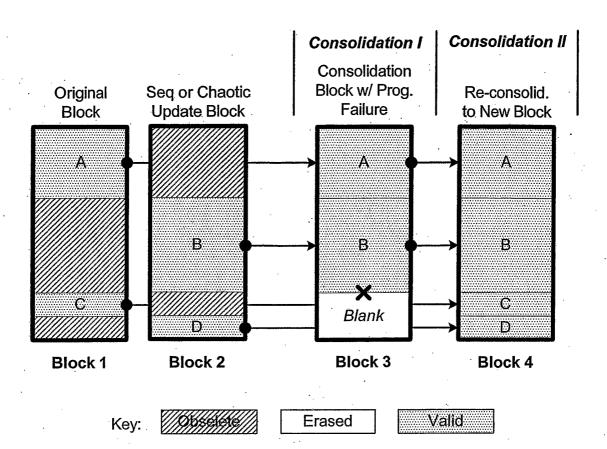

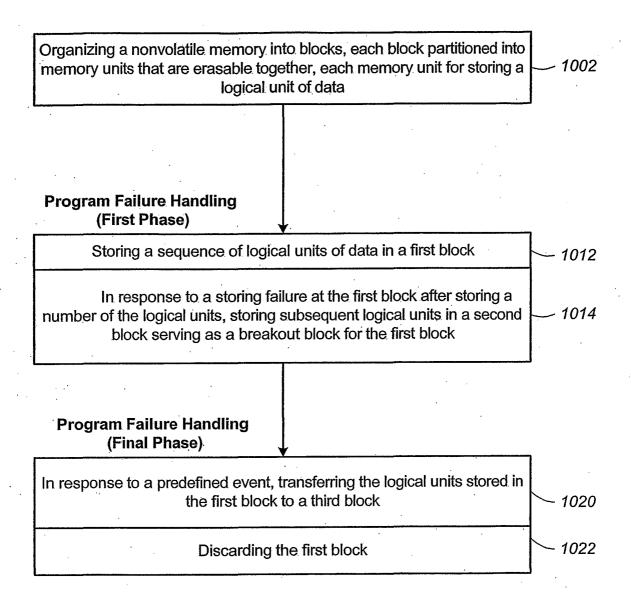

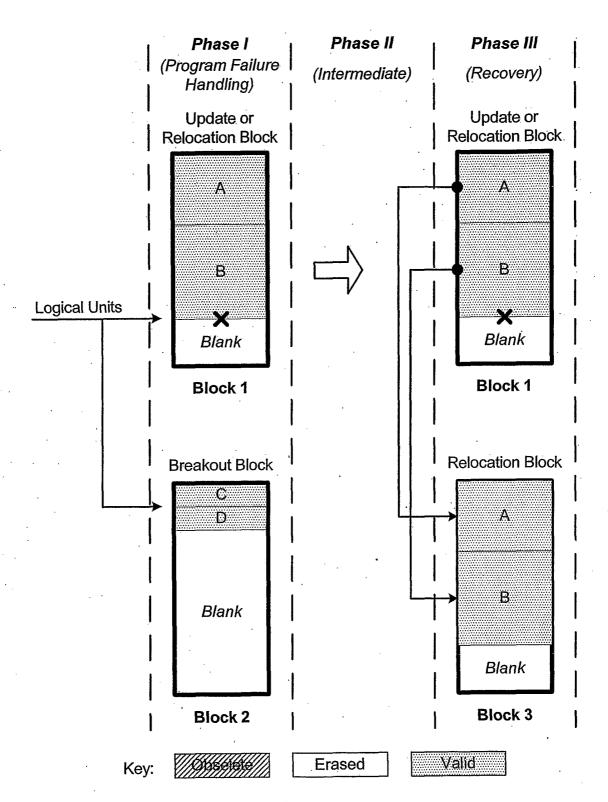

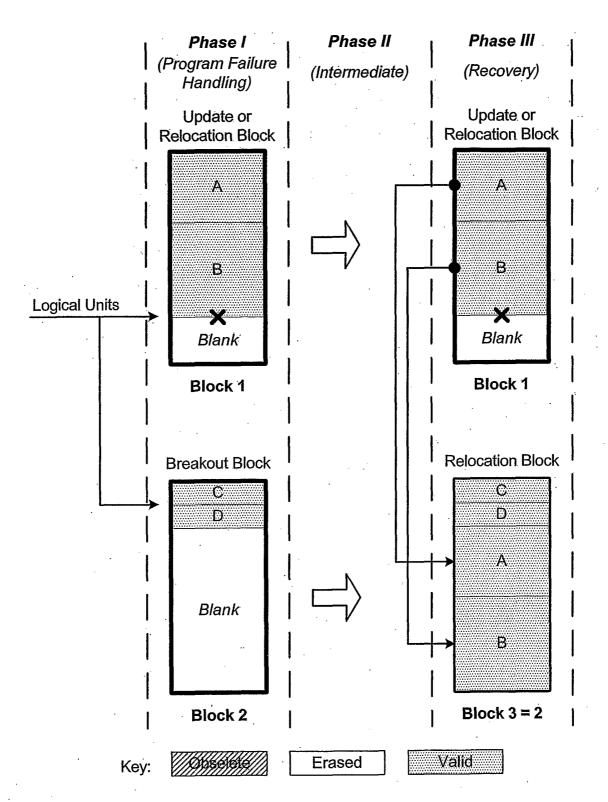

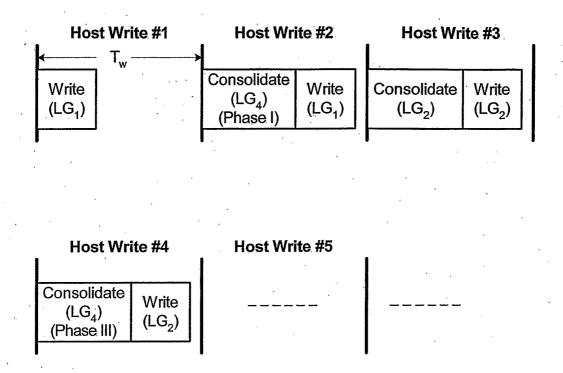

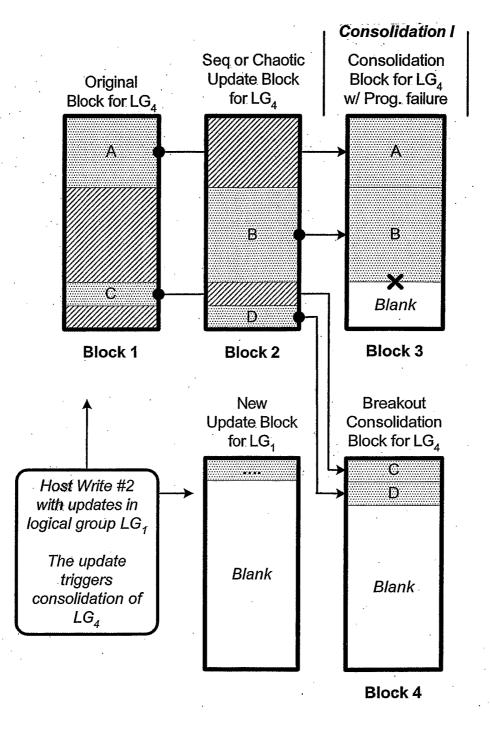

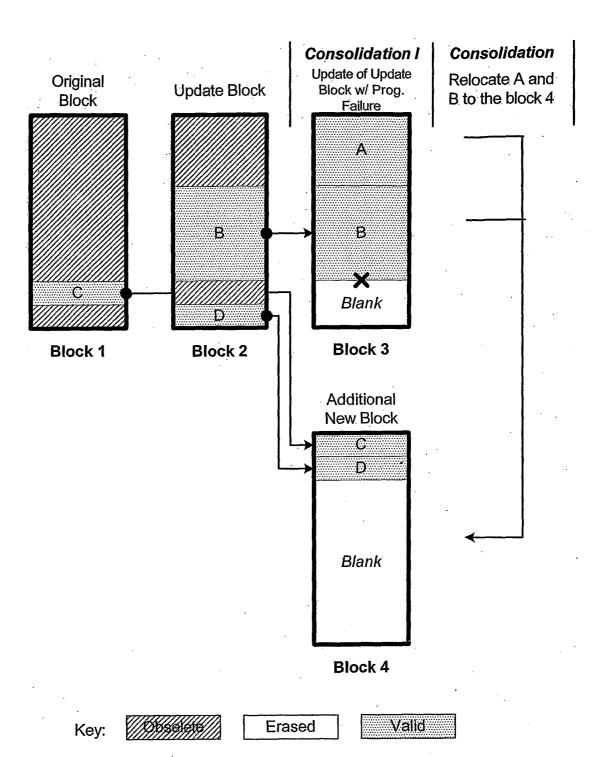

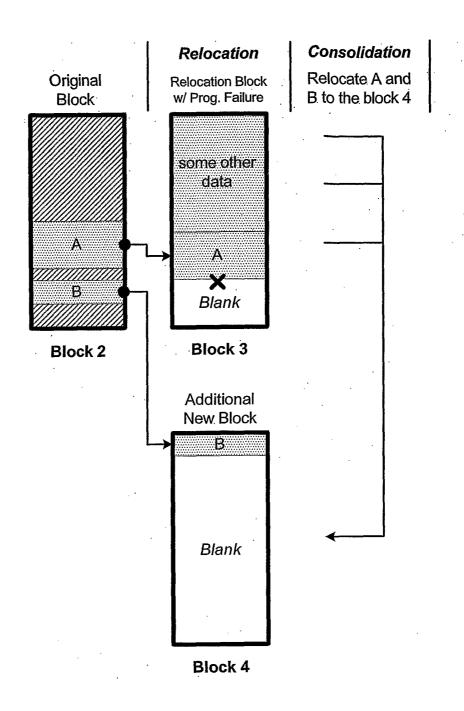

## Phased Program Error Handling

[0026] According to another aspect of the invention, in a memory with block management system, program failure in a block during a time-critical memory operation is handled by continuing the programming operation in a breakout block. Later, at a less critical time, the data recorded in the failed block prior to the interruption is transferred to another block, which could also be the breakout block. The failed block can then be discarded. In this way, when a defective block is encountered, it can be handled without loss of data and without exceeding a specified time limit by having to transfer the stored data in the defective block on the spot. This error handling is especially critical for a garbage collection operation so that the entire operation need not be repeated on a fresh block during a critical time. Subsequently, at an opportune time, the data from the defective block can be salvaged by relocation to another block.

[0027] The program failure handling is especially critical during a consolidation operation. A normal consolidation operation consolidates into a consolidation block the current versions of all logical units of a logical group residing among an original block and an update block. During the consolidation operation, if a program failure occurs in the consolidation block, another block acting as a breakout consolidation block will be provisioned to receive the consolidation of the remaining logical units. In this way, no logical units need be copied more than once and the operation with exception handling can still be completed within a period specified for a normal consolidation operation. At an opportune time, the consolidation operation can be completed by consolidating all outstanding logical units of the group into the breakout block. The opportune time will be during some other period outside the current host write operation when there is time to perform the consolidation. One such opportune time is during another host write where there is an update but no associated consolidation operation.

[0028] Essentially, the consolidation with the program failure handling can be regarded as being implemented in multiple phases. In a first phase, the logical units

are being consolidated into more than one block after a program failure occurs in order to avoid consolidating each logical unit more than once. The final phase is completed at an opportune time, where the logical group is consolidated into one block, preferably by collecting all the logical units into the breakout consolidation block in sequential order.

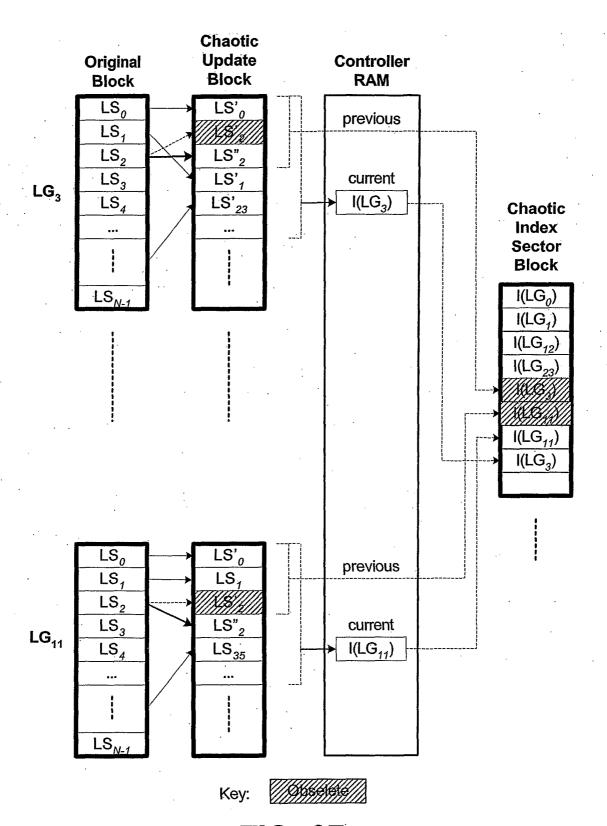

## Non-Sequential Update Block Indexing

[0029] According to another aspect of the invention, in a nonvolatile memory with block management system that supports update blocks with non-sequential logical units, an index of the logical units in a non-sequential update block is buffered in RAM and stored periodically into the non-volatile memory. In one embodiment, the index is stored in a block dedicated for storing indices. In another embodiment, the index is stored in the update block itself. In yet another embodiment, the index is stored in the header of each logical unit. In another aspect, the logical units written after the last index update but before the next have their indexing information stored in the header of each logical unit. In this way, after a power outage, the location of recently written logical units can be determined without having to perform a scanning during initialization. In yet another aspect, a block is managed as partially sequential and partially non-sequential, directed to more than one logical subgroup.

#### Control Data Integrity & Mangement

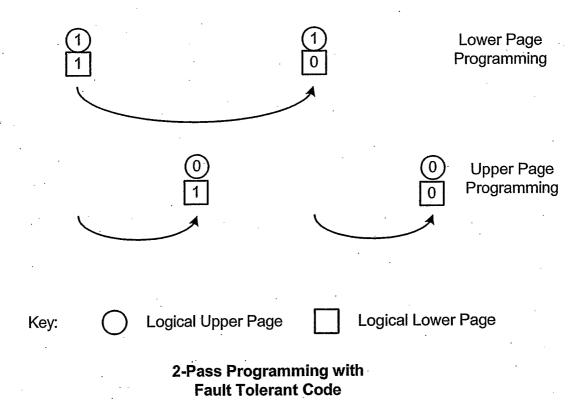

[0030] According to another aspect of the invention, critical data such as some or all of the control data is guaranteed an extra level of reliability if it is maintained in duplicates. The duplication is performed in a manner that for multi-state memory system employing a two-pass programming technique for successively programming the multi-bits of the same set of memory cells, any programming error in the second pass will not corrupt the data established by the first pass. The duplication also helps with detection of write aborts, detection of misdetection (i.e., both copies have good ECC but data are different), and adds an extra level of reliability. Several techniques of data duplication are contemplated.

[0031] In one embodiment, after two copies of a given data have been programmed in an earlier programming pass, a subsequent programming pass avoids programming the memory cells storing at least one of the two copies. In this way, at

least one of the two copies will be unaffected in the event the subsequent programming pass aborts before completion and corrupts the data of the earlier pass.

[0032] In another embodiment, the two copies of a given data are stored in two different blocks where at most one of the two copies have its memory cells programmed in a subsequent programming pass.

[0033] In yet another embodiment, after two copies of a given data have been stored in a programming pass, no further programming will be preformed on the set of memory cells storing the two copies. This is accomplished by programming the two copies in an ultimate programming pass for the set of memory cells.

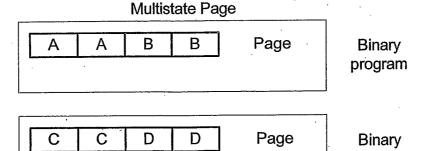

[0034] In yet another embodiment, the two copies of a given data is programmed into a multi-state memory in a binary programming mode, so that no further programming on the programmed memory cells will take place.

[0035] In yet another embodiment, for multi-state memory system employing a two-pass programming technique for successively programming the multi-bits of the same set of memory cells, a fault-tolerant code is employ to code the multiple memory states such that data established by an earlier programming pass is insensitive to errors in subsequent programming pass.

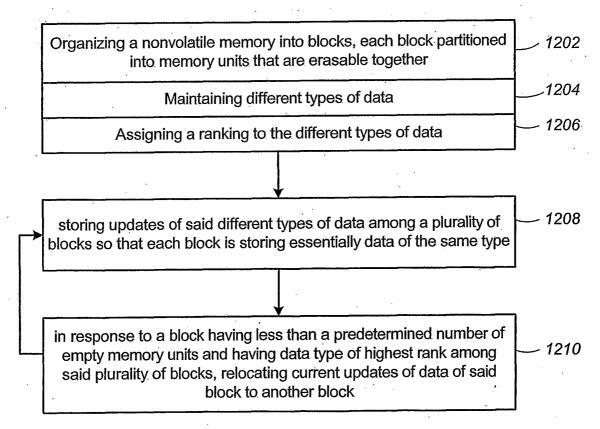

[0036] According to another aspect of the invention, in a nonvolatile memory with a block management system, a "control garbage collection" or preemptive relocation of a memory block is implemented to avoid the situation where a large number of update blocks all happen to need relocation concurrently. For example, this situation can happen when updating control data used for controlling the operation of the block management system. A hierarchy of control data type can exist with varying degree of update frequencies, resulting in their associated update blocks requiring garbage collection or relocation at different rates. There will be certain times that the garbage collection operations of more than one control data types coincide. In the extreme situation, the relocation phases of the update blocks for all control data types could line up, resulting in all of the update blocks requiring relocation at the same time.

[0037] Additional features and advantages of the present invention will be

understood from the following description of its preferred embodiments, which description should be taken in conjunction with the accompanying drawings.

#### BRIEF DESCRIPTION OF THE DRAWINGS

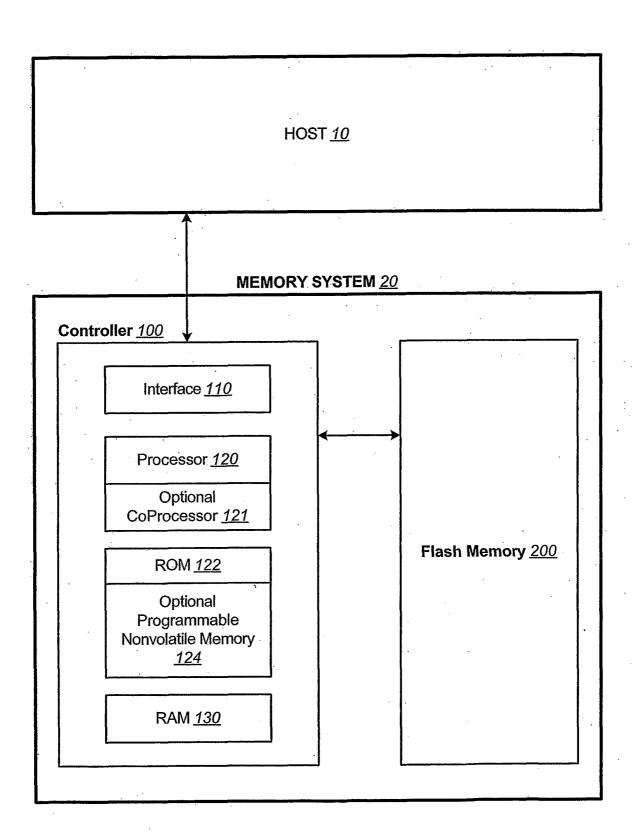

- [0038] FIG. 1 illustrates schematically the main hardware components of a memory system suitable for implementing the present invention.

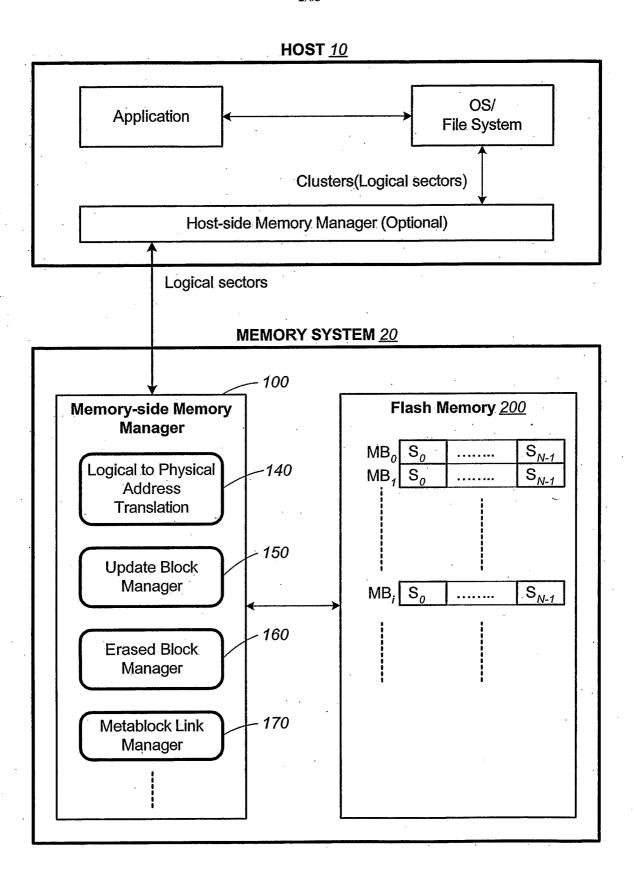

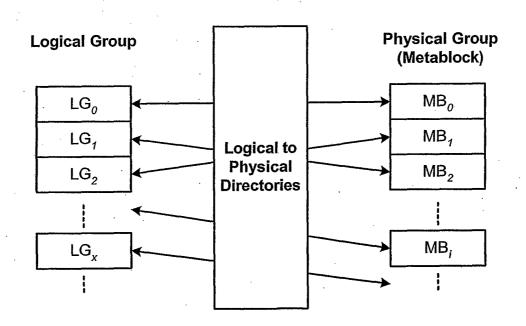

- [0039] FIG. 2 illustrates the memory being organized into physical groups of sectors (or metablocks) and managed by a memory manager of the controller, according to a preferred embodiment of the invention.

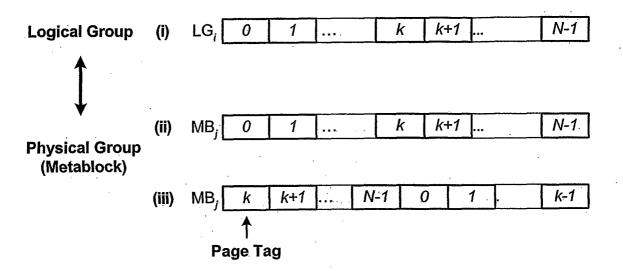

- [0040] FIGs. 3A(i) 3A(iii) illustrate schematically the mapping between a logical group and a metablock, according to a preferred embodiment of the present invention.

- [0041] FIG. 3B illustrates schematically the mapping between logical groups and metablocks.

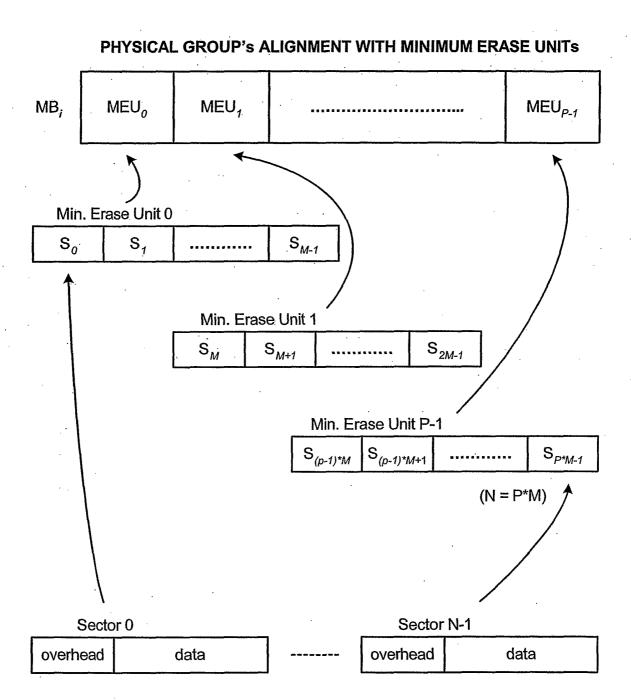

- [0042] FIG. 4 illustrates the alignment of a metablock with structures in physical memory.

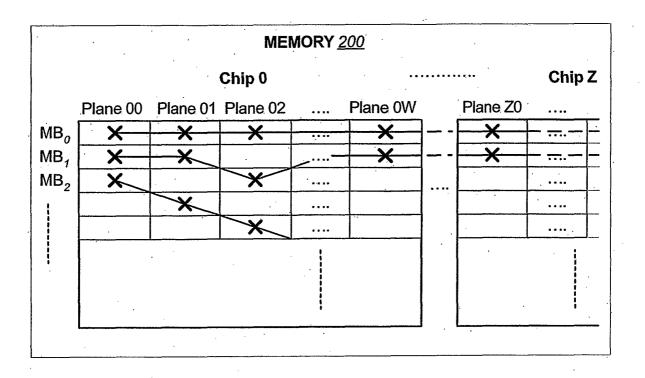

- [0043] FIG. 5A illustrates metablocks being constituted from linking of minimum erase units of different planes.

- [0044] FIG. 5B illustrates one embodiment in which one minimum erase unit (MEU) is selected from each plane for linking into a metablock.

- [0045] FIG. 5C illustrates another embodiment in which more than one MEU are selected from each plane for linking into a metablock.

- [0046] FIG. 6 is a schematic block diagram of the metablock management system as implemented in the controller and flash memory.

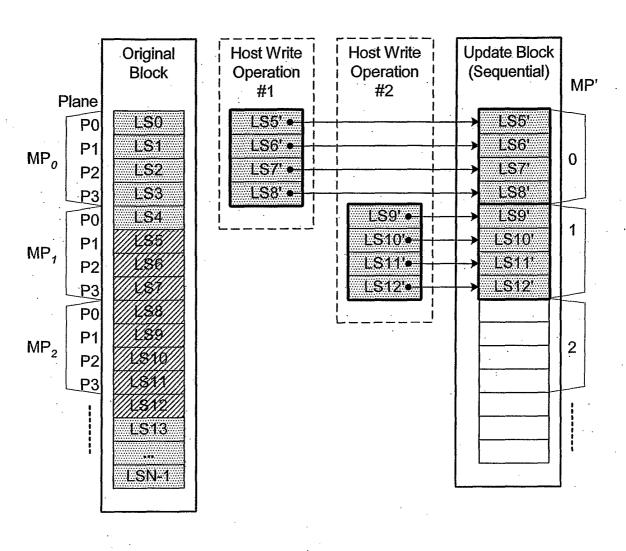

- [0047] FIG. 7A illustrates an example of sectors in a logical group being written in sequential order to a sequential update block.

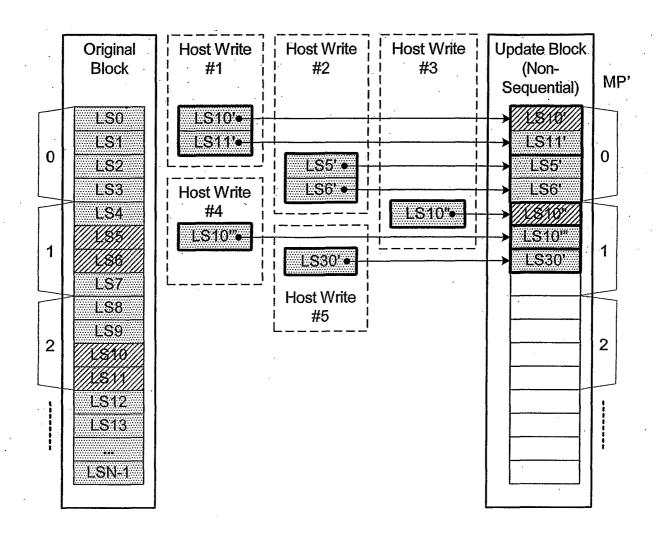

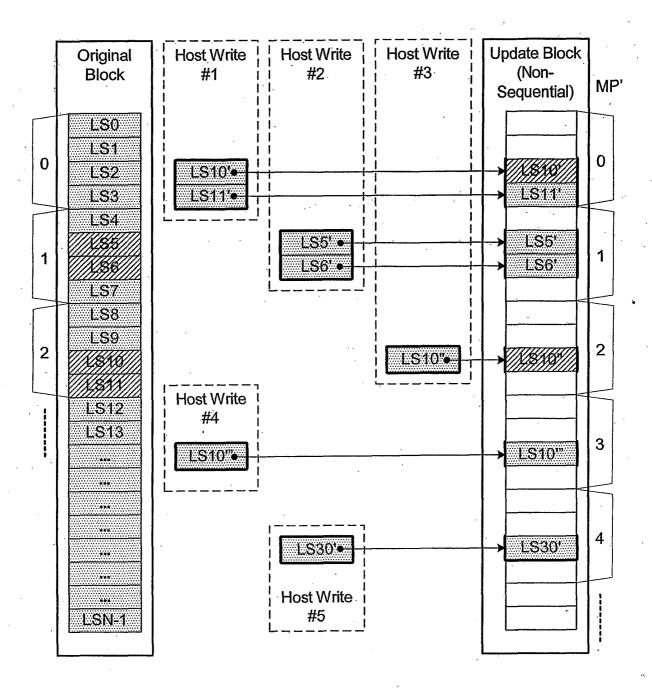

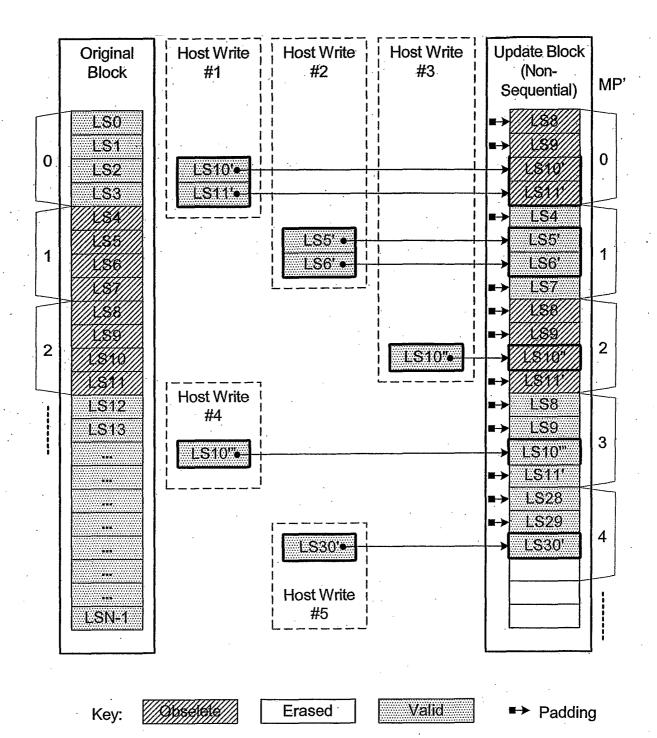

[0048] FIG. 7B illustrates an example of sectors in a logical group being written in chaotic order to a chaotic update block.

- [0049] FIG. 8 illustrates an example of sectors in a logical group being written in sequential order to a sequential update block as a result of two separate host write operations that has a discontinuity in logical addresses.

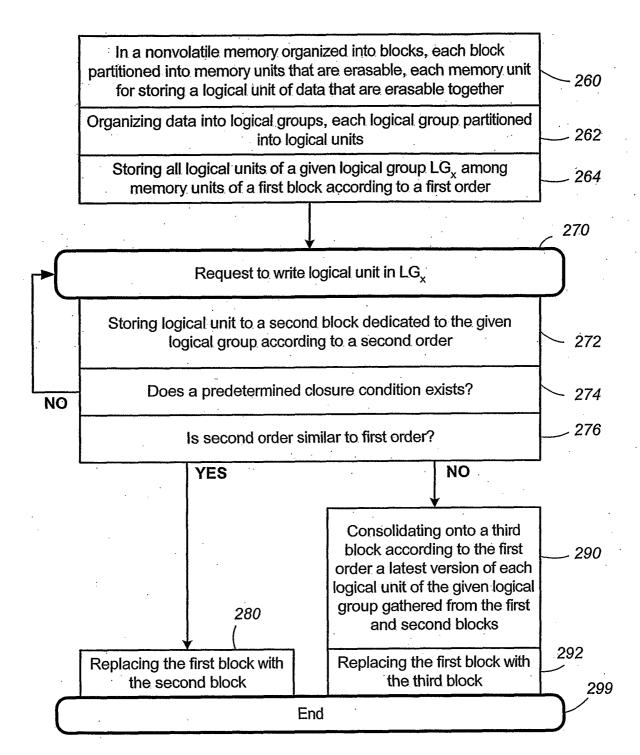

- [0050] FIG. 9 is a flow diagram illustrating a process by the update block manager to update a logical group of data, according a general embodiment of the invention.

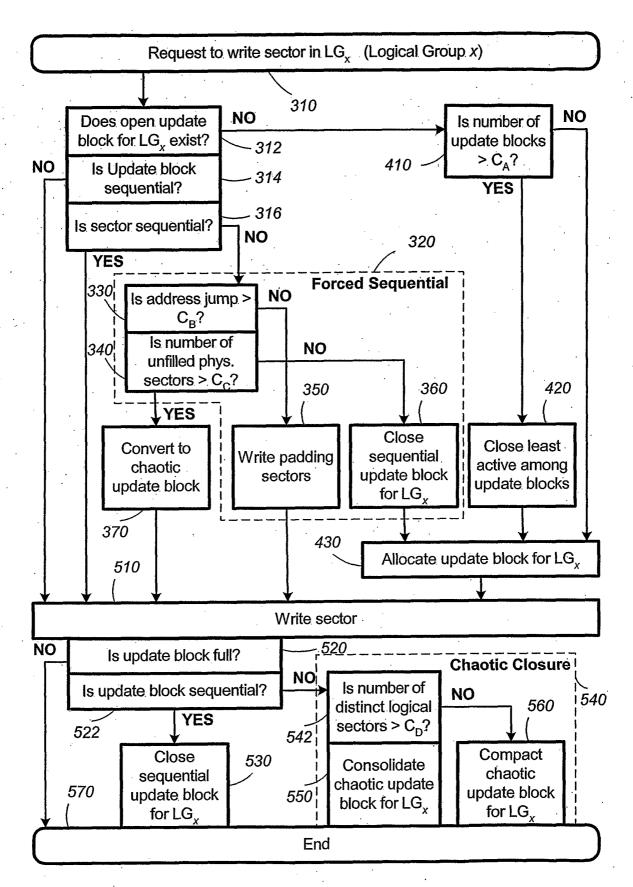

- [0051] FIG. 10 is a flow diagram illustrating a process by the update block manager to update a logical group of data, according a preferred embodiment of the invention.

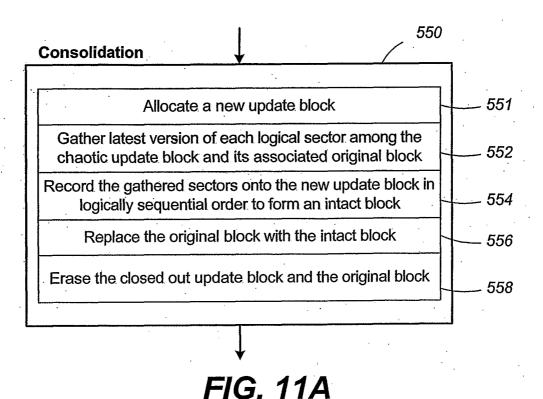

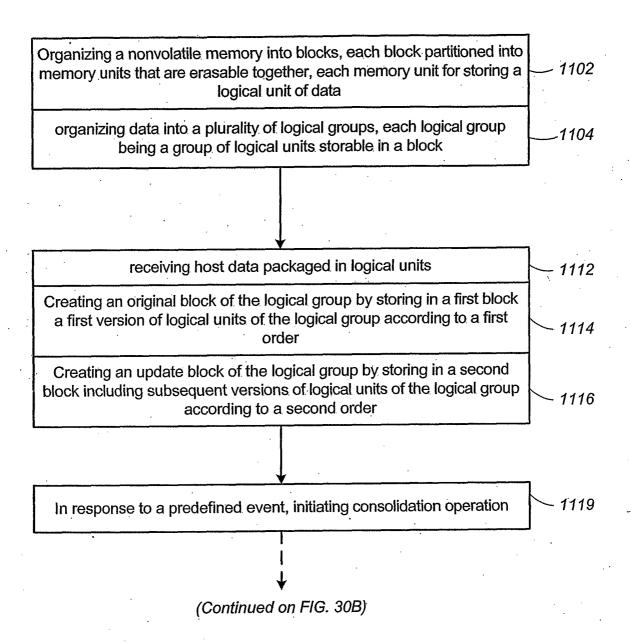

- [0052] FIG. 11A is a flow diagram illustrating in more detail the consolidation process of closing a chaotic update block shown in FIG. 10.

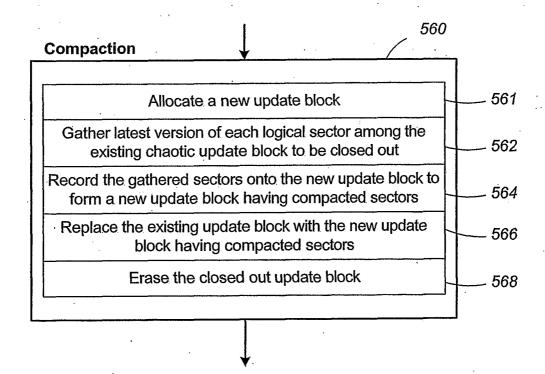

- [0053] FIG. 11B is a flow diagram illustrating in more detail the compaction process for closing a chaotic update block shown in FIG. 10.

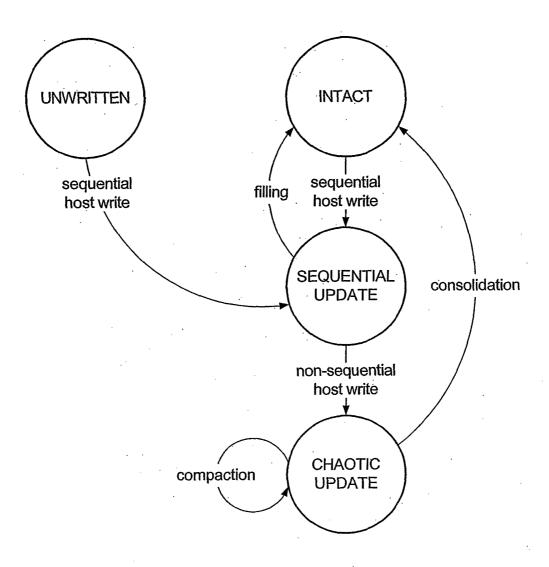

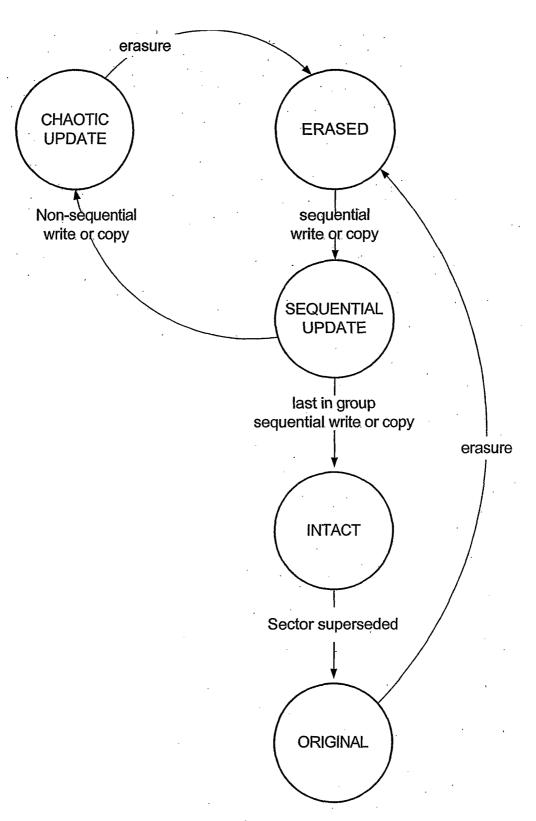

- [0054] FIG. 12A illustrates all possible states of a Logical Group, and the possible transitions between them under various operations.

- [0055] FIG. 12B is a table listing the possible states of a Logical Group.

- [0056] FIG. 13A illustrates all possible states of a metablock, and the possible transitions between them under various operations. A metablock is a Physical Group corresponding to a Logical Group.

- [0057] FIG. 13B is a table listing the possible states of a metablock.

- [0058] FIGs. 14(A) 14(J) are state diagrams showing the effect of various operations on the state of the logical group and also on the physical metablock.

- [0059] FIG. 15 illustrates a preferred embodiment of the structure of an allocation block list (ABL) for keeping track of opened and closed update blocks and erased blocks for allocation.

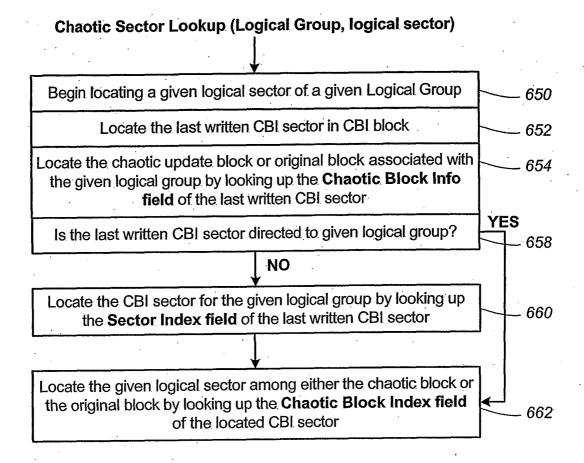

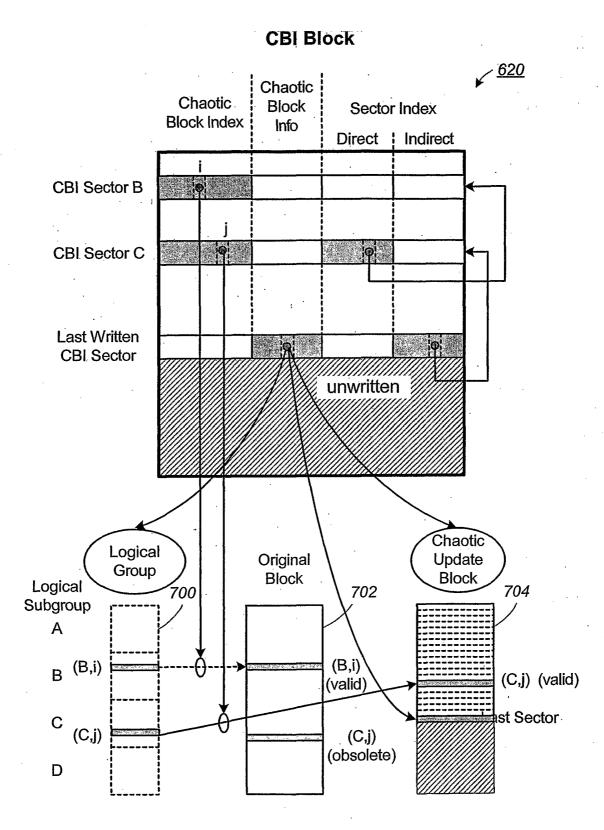

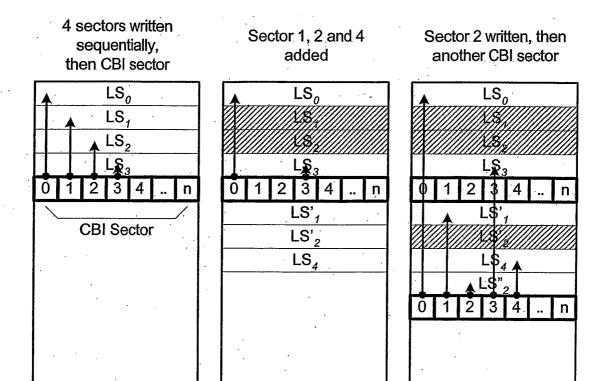

[0060] FIG. 16A illustrates the data fields of a chaotic block index (CBI) sector.

- [0061] FIG. 16B illustrates an example of the chaotic block index (CBI) sectors being recorded in a dedicated metablock.

- [0062] FIG. 16C is a flow diagram illustrating access to the data of a logical sector of a given logical group undergoing chaotic update.

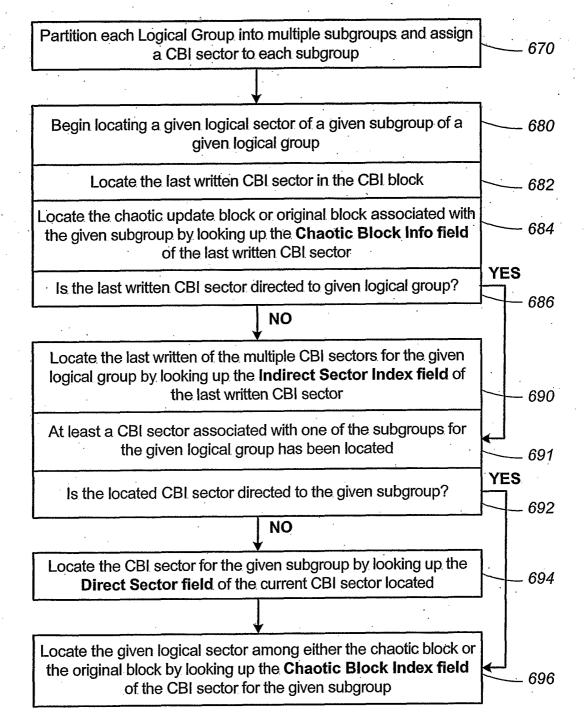

- [0063] FIG. 16D is a flow diagram illustrating access to the data of a logical sector of a given logical group undergoing chaotic update, according to an alternative embodiment in which logical group has been partitioned into subgroups.

- [0064] FIG. 16E illustrates examples of Chaotic Block Indexing (CBI) sectors and their functions for the embodiment where each logical group is partitioned into multiple subgroups.

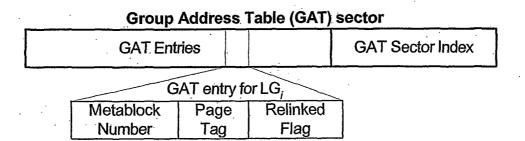

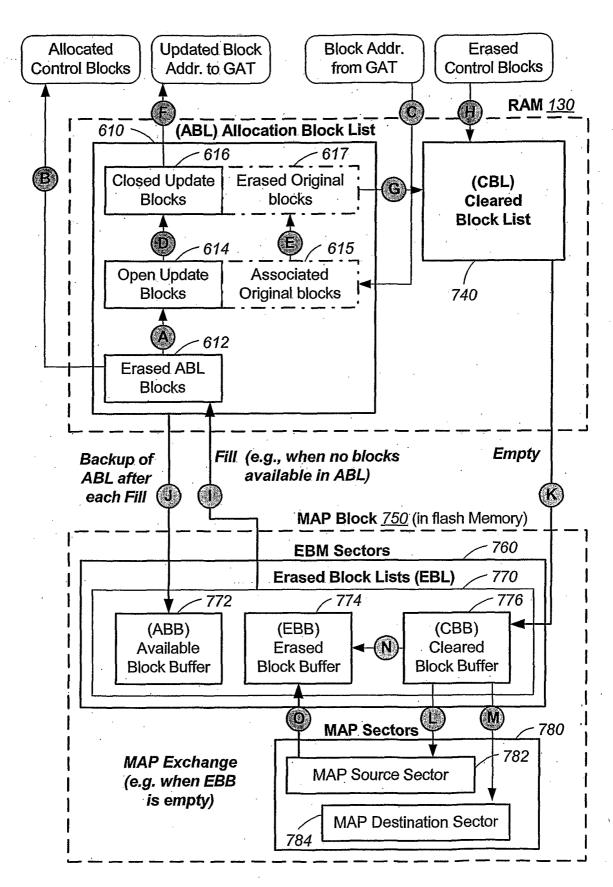

- [0065] FIG. 17A illustrates the data fields of a group address table (GAT) sector.

- [0066] FIG. 17B illustrates an example of the group address table (GAT) sectors being recorded in a GAT block.

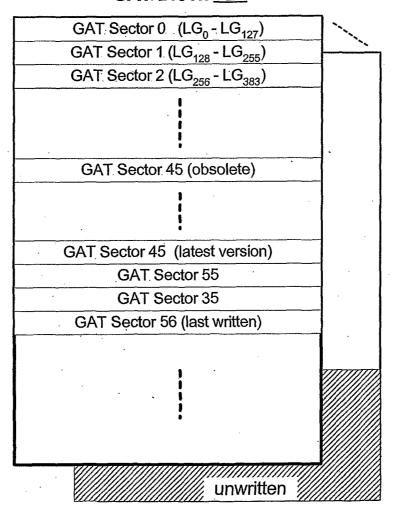

- [0067] FIG. 18 is a schematic block diagram illustrating the distribution and flow of the control and directory information for usage and recycling of erased blocks.

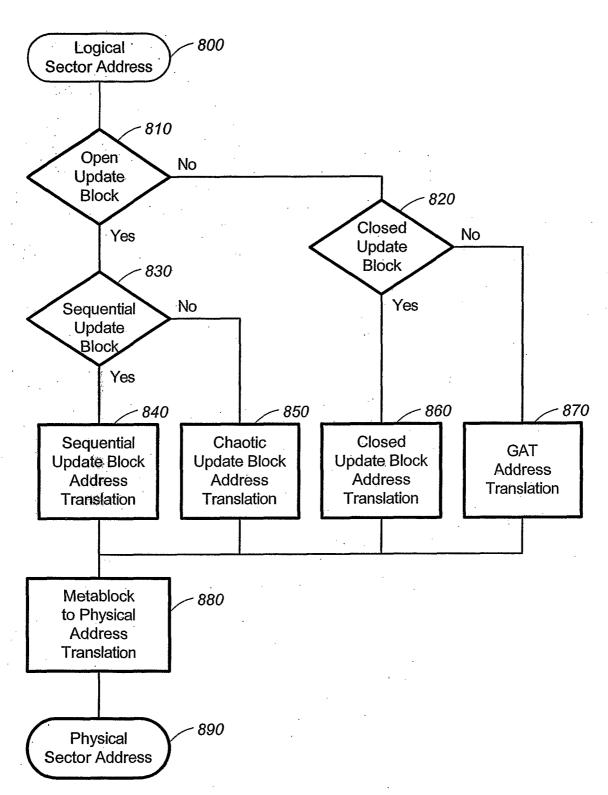

- [0068] FIG. 19 is a flow chart showing the process of logical to physical address translation.

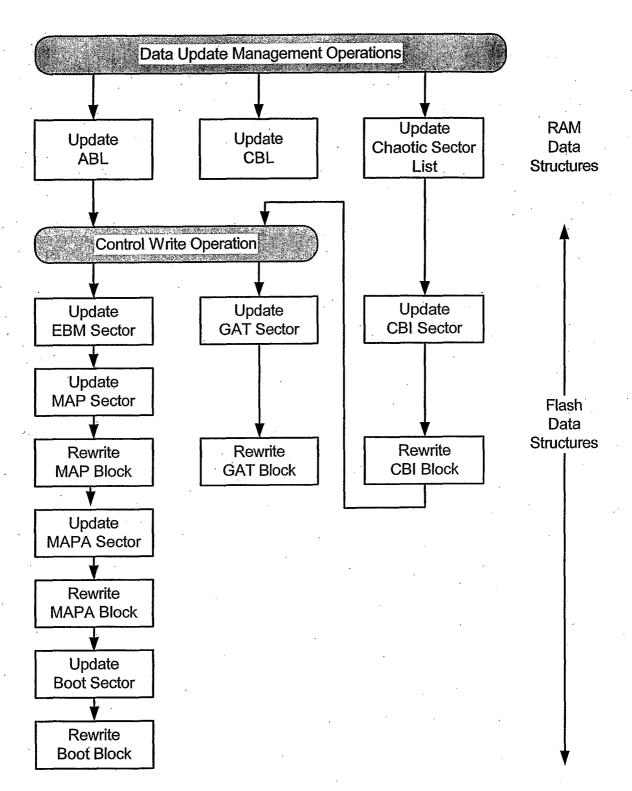

- [0069] FIG. 20 illustrates the hierarchy of the operations performed on control data structures in the course of the operation of the memory management.

- [0070] FIG. 21 illustrates a memory array constituted from multiple memory planes.

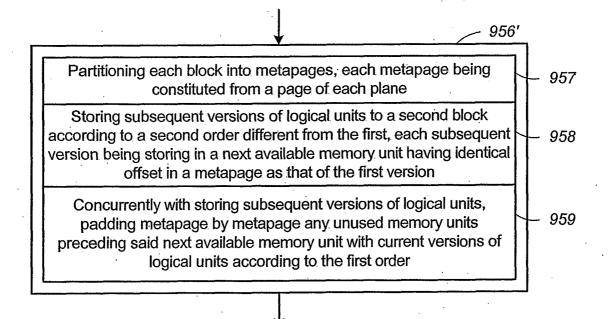

- [0071] FIG. 22A is a flow diagram illustrating a method of update with plane alignment, according to a general implementation of the invention.

- [0072] FIG. 22B illustrates a preferred embodiment of the step of storing

updates in the flow diagram shown in FIG. 22A.

- [0073] FIG. 23A illustrates an example of logical units being written in sequential order to a sequential update block without regard to plane alignment.

- [0074] FIG. 23B illustrates an example of logical units being written in non-sequential order to a chaotic update block without regard to plane alignment.

- [0075] FIG. 24A illustrates the sequential update example of FIG. 23A with plane alignment and padding, according to a preferred embodiment of the invention.

- [0076] FIG. 24B illustrates the chaotic update example of FIG. 23B with plane alignment and with no padding, according to one preferred embodiment of the invention.

- [0077] FIG. 24C illustrates the chaotic update example of FIG. 23B with plane alignment and padding, according to another preferred embodiment of the invention.

- [0078] FIG. 25 illustrates an example memory organization in which each page contains two memory units for storing two logical units, such as two logical sectors.

- [0079] FIG. 26A is similar to the memory structure of FIG. 21 except each page contains two sectors instead of one.

- [0080] FIG. 26B illustrates metablocks shown in FIG. 26A having memory units laid out in a schematic linear fashion.

- [0081] FIG. 27 illustrates an alternative scheme for plane alignment in an update block without padding logical units to be copied from one location to another.

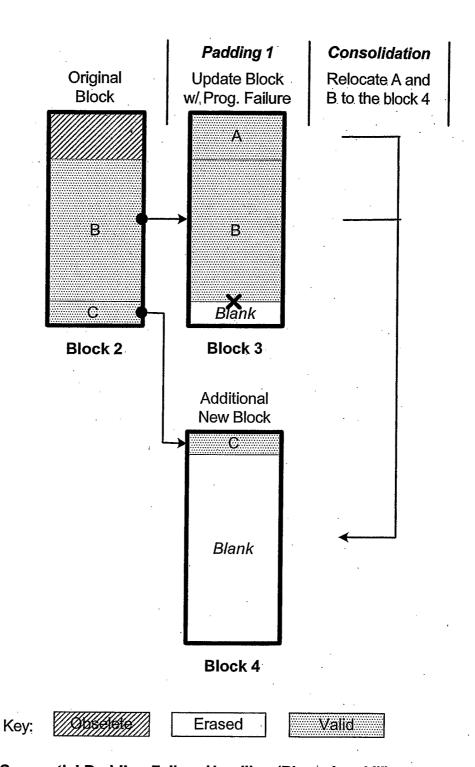

- [0082] FIG. 28 illustrates a scheme in which when a program failure occurs in a defective block during a consolidation operation, the consolidation operation is repeated on another block.

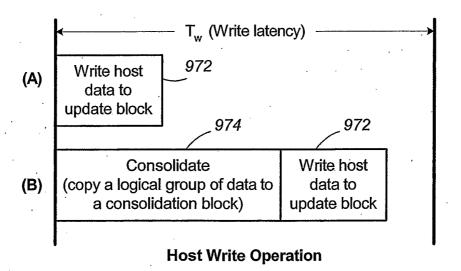

- [0083] FIG. 29 illustrates schematically, a host write operation with a timing or write latency that allows enough time to complete a write (update) operation as

well as a consolidation operation.

[0084] FIG. 30 illustrates a flow chart of the program failure handling according to a general scheme of the invention.

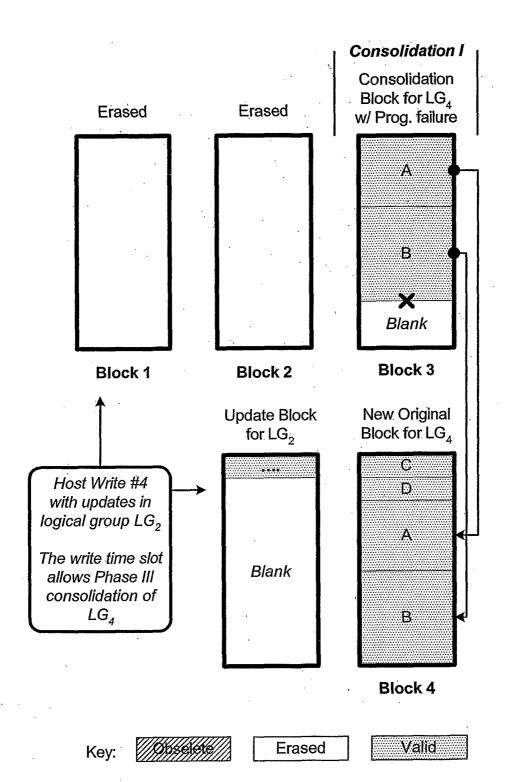

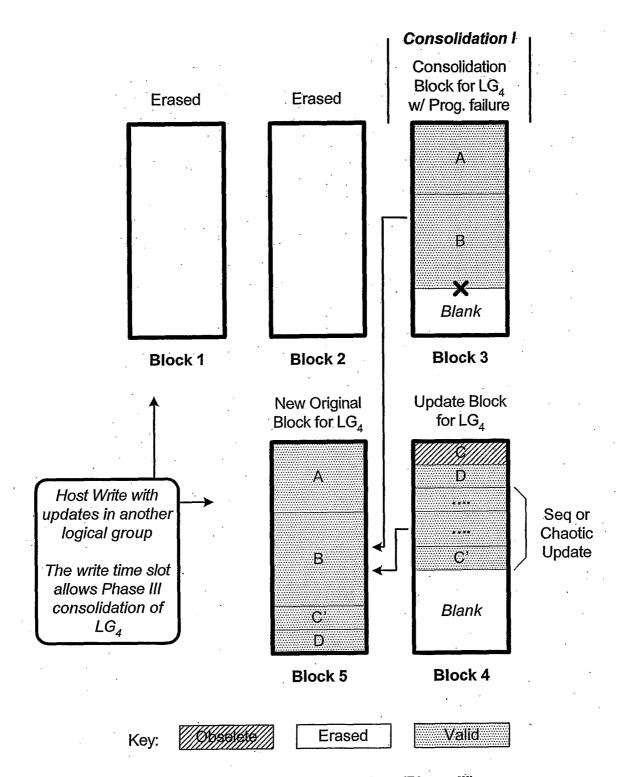

- [0085] FIG. 31A illustrates one embodiment of program failure handling in which the third (final relocation) block is different from the second (breakout) block.

- [0086] FIG. 31B illustrates another embodiment of program failure handling in which the third (final relocation) block is the same as the second (breakout) block.

- [0087] FIG. 32A illustrates a flow chart of initial update operation that results in a consolidation operation.

- [0088] FIG. 32B illustrates a flow chart of the multiple phase consolidation operation, according to a preferred embodiment of the invention.

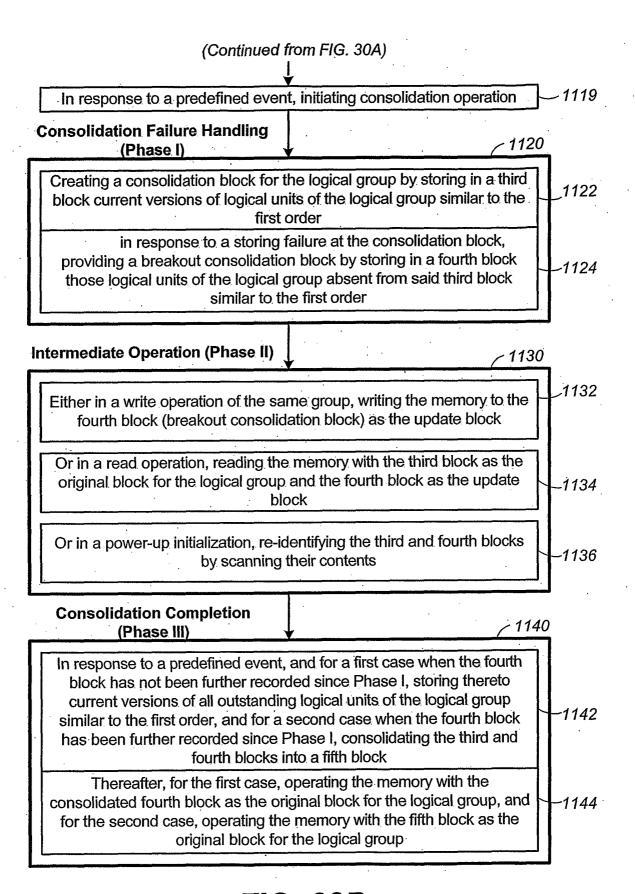

- [0089] FIG. 33 illustrates an example timing of the first and final phases of the multiple phase consolidation operation.

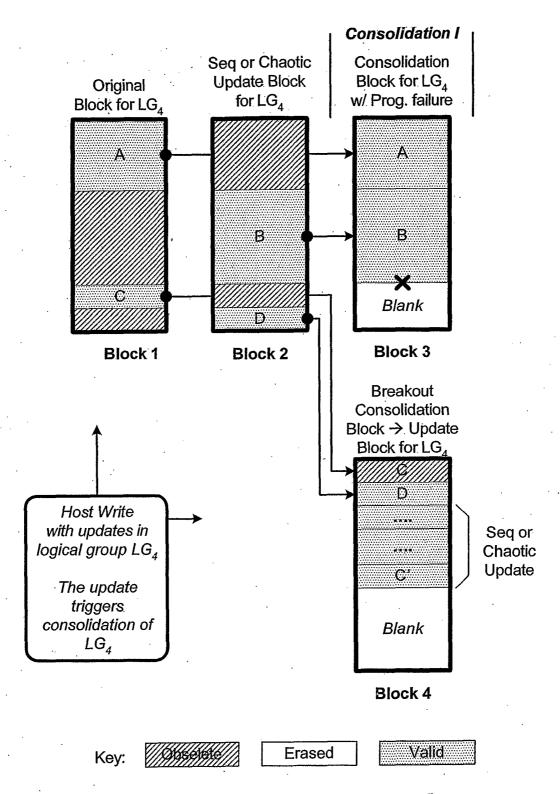

- [0090] FIG. 34A illustrates the case where the breakout consolidation block is not used as an update block but more as a consolidation block whose consolidation operation has been interrupted.

- [0091] FIG. 34B illustrates the third and final phase of the multiple phase consolidation started in FIG. 34A.

- [0092] FIG. 35A illustrates the case where the breakout consolidation block is maintained as an update block to receive host writes rather than as a consolidation block.

- [0093] FIG. 35B illustrates the third and final phase of the multiple phase consolidation started in FIG. 35A for the second case.

- [0094] FIG. 36A illustrates the phased program error handling method as applied to the scenario when the host write triggers the closure of an update block, and the update block is sequential.

- [0095] FIG. 36B illustrates the phased program error handling method as it

can be applied to a (Partial Blocks system) in the case of an Update of Update blocks.

- [0096] FIG. 36C illustrates the phased program error handling the garbage collection operation, or clean-up in a memory block management system that does not support a logical group mapped to a metablock.

- [0097] FIG. 37 illustrates an example of a schedule of writing of a CBI sector to an associated chaotic index sector block after every N sector writes of the same logical group.

- [0098] FIG. 38A illustrates an update block up to the point when a CBI sector is recorded in it after a predetermined number of writes.

- [0099] FIG. 38B illustrates the update block of FIG. 38A to have data pages 1, 2 and 4 further recorded to it after the index sector.

- [00100] FIG. 38C illustrates the update block of FIG. 38B having another logical sector written to trigger the next recording of an index sector.

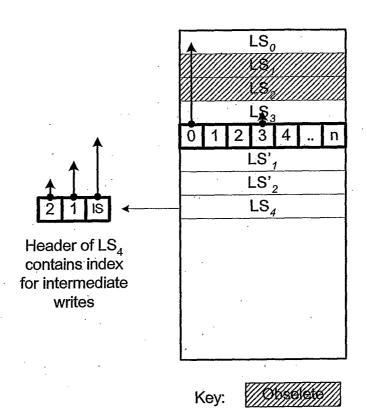

- [00101] FIG. 39A illustrates an intermediate index for the intermediate writes being stored in a header of each data sector in the chaotic update block

- [00102] FIG. 39B illustrates an example of storing an intermediate index for the intermediate writes in the header of each sector written.

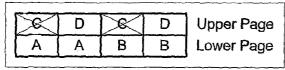

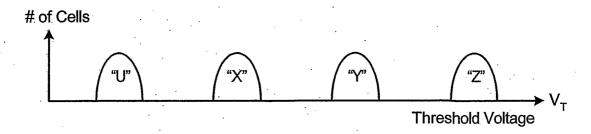

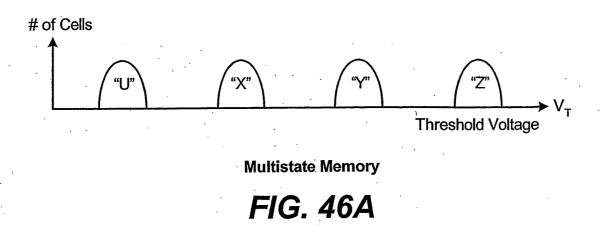

- [00103] FIG. 40 illustrates the information in the chaotic index field being stored in a header of each data sector in the chaotic update block. FIG. 41A illustrates threshold voltage distributions of a 4-state memory array when each memory cell stores two bits of data.

- [00104] FIG. 41A illustrates threshold voltage distributions of a 4-state memory array when each memory cell stores two bits of data.

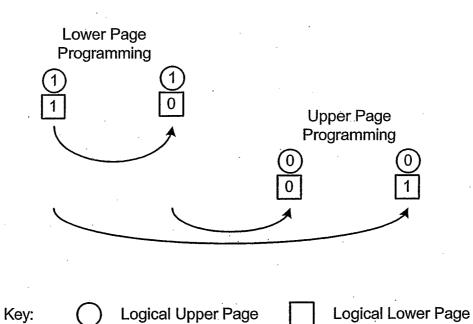

- [00105] FIG. 41B illustrates an existing, 2-pass programming scheme using a Gray code.

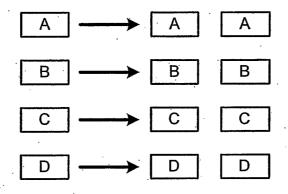

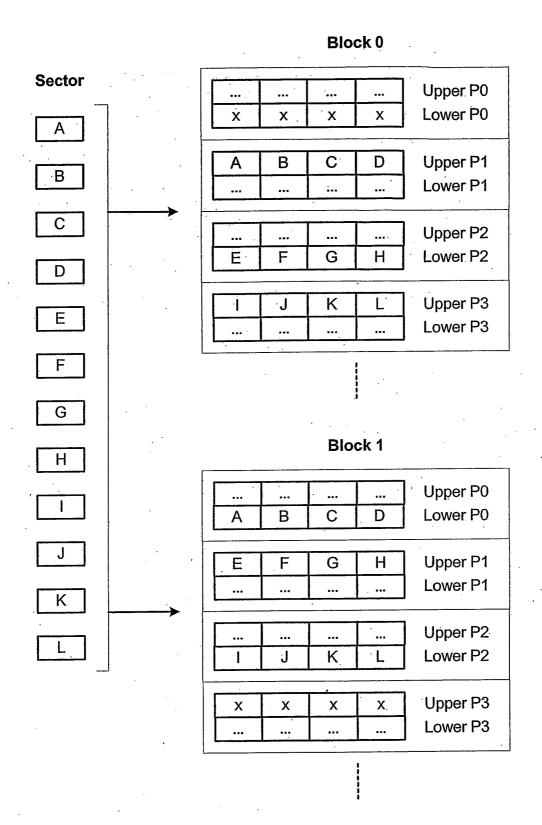

- [00106] FIG. 42 illustrates a way of safe guarding critical data by saving each sector in duplicates. For example, the sectors A, B, C, and D are saved in duplicate

copies. If there is corruption of the data in one sector copy, then the other one can be read instead.

- [00107] FIG. 43 illustrates the non-robustness in which duplicate sectors are typically saved in a multi-state memory.

- [00108] FIG. 44A illustrates one embodiment of saving staggered duplicate copies of critical data to a multi-state memory.

- [00109] FIG. 44B illustrates another embodiment of saving duplicate copies of critical data only to the logical upper page of a multi-state memory.

- [00110] FIG. 44C illustrates yet another embodiment of saving duplicate copies of critical data in binary mode of a multi-state memory.

- [00111] FIG. 45 illustrates yet another embodiment of saving duplicate copies of critical data concurrently to two different metablocks.

- [00112] FIG. 46A is similar to FIG. 41A in illustrating threshold voltage distributions of a 4-state memory array and is shown as a reference for FIG. 46B.

- [00113] FIG. 46B illustrates yet another embodiment of saving duplicate copies of critical data concurrently by the use of a fault-tolerant code.

- [00114] FIG. 47 is a table showing the possible states of the two copies of data, and the validity of the data.

- [00115] FIG. 48 illustrates a flow chart of preemptive relocation of memory block storing control data.

## DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS

FIG. 1 illustrates schematically the main hardware components of a [00116] memory system suitable for implementing the present invention. The memory system 20 typically operates with a host 10 through a host interface. The memory system is typically in the form of a memory card or an embedded memory system. The memory system 20 includes a memory 200 whose operations are controlled by a controller 100. The memory 200 comprises of one or more array of non-volatile memory cells distributed over one or more integrated circuit chip. The controller 100 includes an interface 110, a processor 120, an optional coprocessor 121, ROM 122 (read-only-memory), RAM 130 (random access memory) and optionally programmable nonvolatile memory 124. The interface 110 has one component interfacing the controller to a host and another component interfacing to the memory 200. Firmware stored in nonvolatile ROM 122 and/or the optional nonvolatile memory 124 provides codes for the processor 120 to implement the functions of the controller 100. Error correction codes may be processed by the processor 120 or the optional coprocessor 121. In an alternative embodiment, the controller 100 is implemented by a state machine (not shown.) In yet another embodiment, the controller 100 is implemented within the host.

## LOGICAL AND PHYSICAL BLOCK STRUCTURES

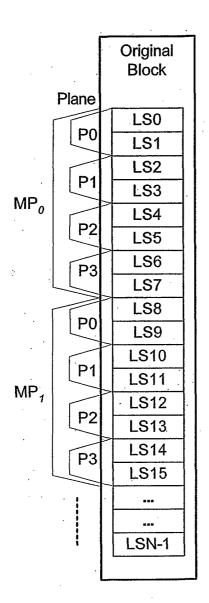

**[00117] FIG. 2** illustrates the memory being organized into physical groups of sectors (or metablocks) and managed by a memory manager of the controller, according to a preferred embodiment of the invention. The memory 200 is organized into metablocks, where each metablock is a group of physical sectors  $S_0, ..., S_{N-1}$  that are erasable together.

[00118] The host 10 accesses the memory 200 when running an application under a file system or operating system. Typically, the host system addresses data in units of logical sectors where, for example, each sector may contain 512 bytes of data. Also, it is usual for the host to read or write to the memory system in unit of logical clusters, each consisting of one or more logical sectors. In some host systems, an optional host-side memory manager may exist to perform lower level memory management at the host. In most cases during read or write operations, the host 10 essentially issues a command to the memory system 20 to read or write a segment

containing a string of logical sectors of data with contiguous addresses.

[00119] A memory-side memory manager is implemented in the controller 100 of the memory system 20 to manage the storage and retrieval of the data of host logical sectors among metablocks of the flash memory 200. In the preferred embodiment, the memory manager contains a number of software modules for managing erase, read and write operations of the metablocks. The memory manager also maintains system control and directory data associated with its operations among the flash memory 200 and the controller RAM 130.

[00120] FIGs. 3A(i) – 3A(iii) illustrate schematically the mapping between a logical group and a metablock, according to a preferred embodiment of the present invention. The metablock of the physical memory has N physical sectors for storing N logical sectors of data of a logical group. FIG. 3A(i) shows the data from a logical group LG<sub>i</sub>, where the logical sectors are in contiguous logical order 0, 1, ..., N-1. FIG. 3A(ii) shows the same data being stored in the metablock in the same logical order. The metablock when stored in this manner is said to be "sequential." In general, the metablock may have data stored in a different order, in which case the metablock is said to be "non-sequential" or "chaotic."

There may be an offset between the lowest address of a logical group and the lowest address of the metablock to which it is mapped. In this case, logical sector address wraps round as a loop from bottom back to top of the logical group within the metablock. For example, in **FIG. 3A(iii)**, the metablock stores in its first location beginning with the data of logical sector k. When the last logical sector N-1 is reached, it wraps around to sector 0 and finally storing data associated with logical sector k-1 in its last physical sector. In the preferred embodiment, a page tag is used to identify any offset, such as identifying the starting logical sector address of the data stored in the first physical sector of the metablock. Two blocks will be considered to have their logical sectors stored in similar order when they only differ by a page tag.

[00122] FIG. 3B illustrates schematically the mapping between logical groups and metablocks. Each logical group is mapped to a unique metablock, except for a small number of logical groups in which data is currently being updated. After a logical group has been updated, it may be mapped to a different metablock. The

mapping information is maintained in a set of logical to physical directories, which will be described in more detail later.

[00123] Other types of logical group to metablock mapping are also comtemplated. For example, metablocks with variable size are disclosed in copending and co-owned United States Patent application, entitled, "Adaptive Metablocks," filed by Alan Sinclair, on the same day as the present application. The entire disclosure of the co-pending application is hereby incorporated herein by reference.

[00124] One feature of the invention is that the system operates with a single logical partition, and groups of logical sectors throughout the logical address range of the memory system are treated identically. For example, sectors containing system data and sectors containing user data can be distributed anywhere among the logical address space.

[00125] Unlike prior art systems, there is no special partitioning or zoning of system sectors (i.e., sectors relating to file allocation tables, directories or subdirectories) in order to localize in logical address space sectors that are likely to contain data with high-frequency and small-size updates. Instead, the present scheme of updating logical groups of sectors will efficiently handle the patterns of access that are typical of system sectors, as well as those typical of file data.

[00126] FIG. 4 illustrates the alignment of a metablock with structures in physical memory. Flash memory comprises blocks of memory cells which are erasable together as a unit. Such erase blocks are the minimum unit of erasure of flash memory or minimum erasable unit (MEU) of the memory. The minimum erase unit is a hardware design parameter of the memory, although in some memory systems that supports multiple MEUs erase, it is possible to configure a "super MEU" comprising more than one MEU. For flash EEPROM, a MEU may comprise one sector but preferably multiple sectors. In the example shown, it has M sectors. In the preferred embodiment, each sector can store 512 bytes of data and has a user data portion and a header portion for storing system or overhead data. If the metablock is constituted from P MEUs, and each MEU contains M sectors, then, each metablock will have N = P\*M sectors.

[00127] The metablock represents, at the system level, a group of memory locations, e.g., sectors that are erasable together. The physical address space of the flash memory is treated as a set of metablocks, with a metablock being the minimum unit of erasure. Within this specification, the terms "metablock" and "block" are used synonymously to define the minimum unit of erasure at the system level for media management, and the term "minimum erase unit" or MEU is used to denote the minimum unit of erasure of flash memory.

## LINKING OF MINIMUM ERASE UNITS (MEUs) TO FORM A METABLOCK

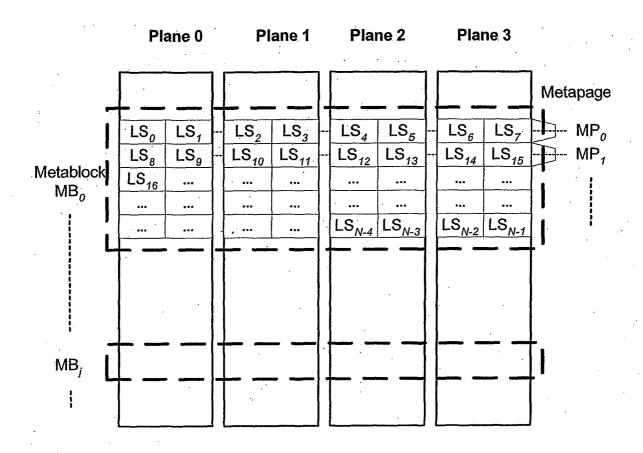

[00128] In order to maximize programming speed and erase speed, parallelism is exploited as much as possible by arranging for multiple pages of information, located in multiple MEUs, to be programmed in parallel, and for multiple MEUs to be erased in parallel.

[00129] In flash memory, a page is a grouping of memory cells that may be programmed together in a single operation. A page may comprise one or more sector. Also, a memory array may be partitioned into more than one plane, where only one MEU within a plane may be programmed or erased at a time. Finally, the planes may be distributed among one or more memory chips.

[00130] In flash memory, the MEUs may comprise one or more page. MEUs within a flash memory chip may be organized in planes. Since one MEU from each plane may be programmed or erased concurrently, it is expedient to form a multiple MEU metablock by selecting one MEU from each plane (see FIG. 5B below.)

[00131] FIG. 5A illustrates metablocks being constituted from linking of minimum erase units of different planes. Each metablock, such as MB0, MB1, ..., is constituted from MEUs from different planes of the memory system, where the different planes may be distributed among one or more chips. The metablock link manager 170 shown in FIG. 2 manages the linking of the MEUs for each metablock. Each metablock is configured during an initial formatting process, and retains its constituent MEUs throughout the life of the system, unless there is a failure of one of the MEUs.

[00132] FIG. 5B illustrates one embodiment in which one minimum erase unit (MEU) is selected from each plane for linking into a metablock.

[00133] FIG. 5C illustrates another embodiment in which more than one MEU are selected from each plane for linking into a metablock. In another embodiment, more than one MEU may be selected from each plane to form a super MEU. For example, a super MEU may be formed from two MEUs. In this case, it may take more than one pass for read or write operation.

[00134] The linking and re-linking of MEUs into metablocks is also disclosed in co-pending and co-owned United States Patent application, entitled "Adaptive Deterministic Grouping of Blocks into Multi-Block Structures," filed by Carlos Gonzales et al, on the same day as the present application. The entire disclosure of the co-pending application is hereby incorporated herein by reference.

## METABLOCK MANAGEMENT

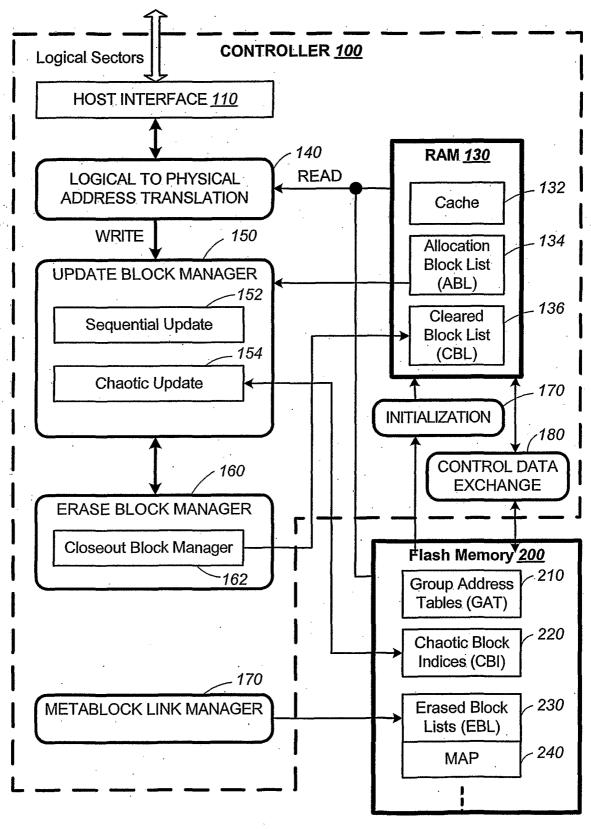

[00135] FIG. 6 is a schematic block diagram of the metablock management system as implemented in the controller and flash memory. The metablock management system comprises various functional modules implemented in the controller 100 and maintains various control data (including directory data) in tables and lists hierarchically distributed in the flash memory 200 and the controller RAM 130. The function modules implemented in the controller 100 includes an interface module 110, a logical-to-physical address translation module 140, an update block manager module 150, an erase block manager module 160 and a metablock link manager 170.

[00136] The interface 110 allows the metablock management system to interface with a host system. The logical to physical address translation module 140 maps the logical address from the host to a physical memory location. The update block Manager module 150 manages data update operations in memory for a given logical group of data. The erased block manager 160 manages the erase operation of the metablocks and their allocation for storage of new information. A metablock link manager 170 manages the linking of subgroups of minimum erasable blocks of sectors to constitute a given metablock. Detailed description of these modules will be given in their respective sections.

During operation the metablock management system generates and [00137] works with control data such as addresses, control and status information. Since much of the control data tends to be frequently changing data of small size, it can not be readily stored and maintained efficiently in a flash memory with a large block structure. A hierarchical and distributed scheme is employed to store the more static control data in the nonvolatile flash memory while locating the smaller amount of the more varying control data in controller RAM for more efficient update and access. In the event of a power shutdown or failure, the scheme allows the control data in the volatile controller RAM to be rebuilt quickly by scanning a small set of control data in the nonvolatile memory. This is possible because the invention restricts the number of blocks associated with the possible activity of a given logical group of data. In this way, the scanning is confined. In addition, some of the control data that requires persistence are stored in a nonvolatile metablock that can be updated sectorby-sector, with each update resulting in a new sector being recorded that supercedes a previous one. A sector indexing scheme is employed for control data to keep track of the sector-by-sector updates in a metablock.

The non-volatile flash memory 200 stores the bulk of control data that are relatively static. This includes group address tables (GAT) 210, chaotic block indices (CBI) 220, erased block lists (EBL) 230 and MAP 240. The GAT 210 keeps track of the mapping between logical groups of sectors and their corresponding metablocks. The mappings do not change except for those undergoing updates. The CBI 220 keeps track of the mapping of logically non-sequential sectors during an update. The EBL 230 keeps track of the pool of metablocks that have been erased. MAP 240 is a bitmap showing the erase status of all metablocks in the flash memory.

[00139] The volatile controller RAM 130 stores a small portion of control data that are frequently changing and accessed. This includes an allocation block list (ABL) 134 and a cleared block list (CBL) 136. The ABL 134 keeps track of the allocation of metablocks for recording update data while the CBL 136 keeps track of metablocks that have been deallocated and erased. In the preferred embodiment, the RAM 130 acts as a cache for control data stored in flash memory 200.

#### UPDATE BLOCK MANAGER

[00140] The update block manager 150 (shown in FIG. 2) handles the update of logical groups. According to one aspect of the invention, each logical group of sectors undergoing an update is allocated a dedicated update metablock for recording the update data. In the preferred embodiment, any segment of one or more sectors of the logical group will be recorded in the update block. An update block can be managed to receive updated data in either sequential order or non-sequential (also known as chaotic) order. A chaotic update block allows sector data to be updated in any order within a logical group, and with any repetition of individual sectors. In particular, a sequential update block can become a chaotic update block, without need for relocation of any data sectors. No predetermined allocation of blocks for chaotic data update is required; a non-sequential write at any logical address is automatically accommodated. Thus, unlike prior art systems, there is no special treatment whether the various update segments of the logical group is in logical sequential or nonsequential order. The generic update block will simply be used to record the various segments in the order they are requested by the host. For example, even if host system data or system control data tends to be updated in chaotic fashion, regions of logical address space corresponding to host system data do not need to be treated differently from regions with host user data.

Data of a complete logical group of sectors is preferably stored in [00141]logically sequential order in a single metablock. In this way, the index to the stored logical sectors is predefined. When the metablock has in store all the sectors of a given logical group in a predefined order it is said to be "intact." As for an update block, when it eventually fills up with update data in logically sequential order, then the update block will become an updated intact metablock that readily replace the original metablock. On the other hand, if the update block fills up with update data in a logically different order from that of the intact block, the update block is a nonsequential or chaotic update block and the out of order segments must be further processed so that eventually the update data of the logical group is stored in the same order as that of the intact block. In the preferred case, it is in logically sequential order in a single metablock. The further processing involves consolidating the updated sectors in the update block with unchanged sectors in the original block into yet another update metablock. The consolidated update block will then be in logically sequential order and can be used to replace the original block. Under some

predetermined condition, the consolidation process is preceded by one or more compaction processes. The compaction process simply re-records the sectors of the chaotic update block into a replacing chaotic update block while eliminating any duplicate logical sector that has been rendered obsolete by a subsequent update of the same logical sector.

[00142] The update scheme allows for multiple update threads running concurrently, up to a predefined maximum. Each thread is a logical group undergoing updates using its dedicated update metablock.

## Sequential data update

[00143] When data belonging to a logical group is first updated, a metablock is allocated and dedicated as an update block for the update data of the logical group. The update block is allocated when a command is received from the host to write a segment of one or more sectors of the logical group for which an existing metablock has been storing all its sectors intact. For the first host write operation, a first segment of data is recorded on the update block. Since each host write is a segment of one or more sector with contiguous logical address, it follows that the first update is always sequential in nature. In subsequent host writes, update segments within the same logical group are recorded in the update block in the order received from the host. A block continues to be managed as a sequential update block whilst sectors updated by the host within the associated logical group remain logically sequential. All sectors updated in this logical group are written to this sequential update block, until the block is either closed or converted to a chaotic update block.

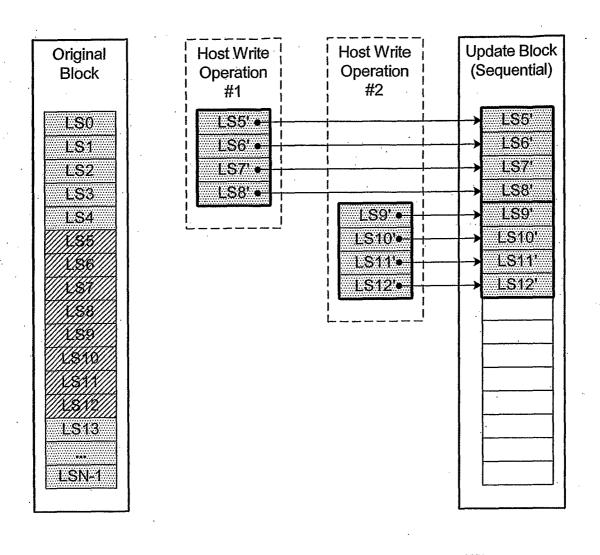

[00144] FIG. 7A illustrates an example of sectors in a logical group being written in sequential order to a sequential update block as a result of two separate host write operations, whilst the corresponding sectors in the original block for the logical group become obsolete. In host write operation #1, the data in the logical sectors LS5-LS8 are being updated. The updated data as LS5'-LS8'are recorded in a newly allocated dedicated update block.

[00145] For expediency, the first sector to be updated in the logical group is recorded in the dedicated update block starting from the first physical sector location. In general, the first logical sector to be updated is not necessarily the logical first

sector of the group, and there may therefore be an offset between the start of the logical group and the start of the update block. This offset is known as page tag as described previously in connection with **FIG. 3A**. Subsequent sectors are updated in logically sequential order. When the last sector of the logical group is written, group addresses wrap around and the write sequence continues with the first sector of the group.

[00146] In host write operation #2, the segment of data in the logical sectors LS9-LS12 are being updated. The updated data as LS9'-LS12' are recorded in the dedicated update block in a location directly following where the last write ends. It can be seen that the two host writes are such that the update data has been recorded in the update block in logically sequential order, namely LS5'-LS12'. The update block is regarded as a sequential update block since it has been filled in logically sequential order. The update data recorded in the update block obsoletes the corresponding ones in the original block.

# Chaotic data update

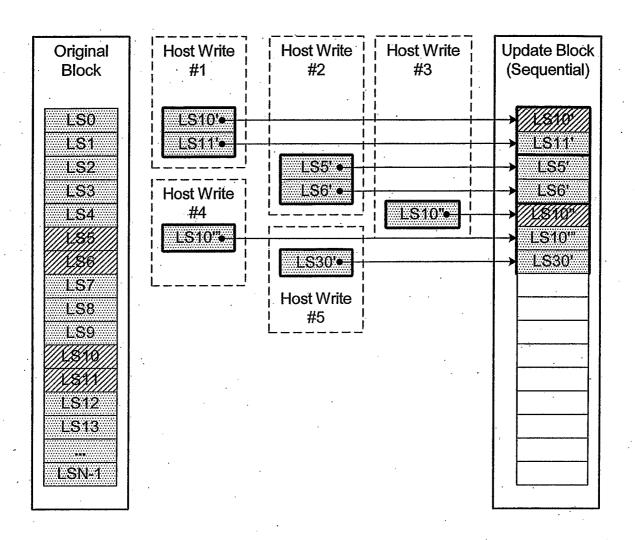

[00147] Chaotic update block management may be initiated for an existing sequential update block when any sector updated by the host within the associated logical group is logically non-sequential. A chaotic update block is a form of data update block in which logical sectors within an associated logical group may be updated in any order and with any amount of repetition. It is created by conversion from a sequential update block when a sector written by a host is logically non-sequential to the previously written sector within the logical group being updated. All sectors subsequently updated in this logical group are written in the next available sector location in the chaotic update block, whatever their logical sector address within the group.

[00148] FIG. 7B illustrates an example of sectors in a logical group being written in chaotic order to a chaotic update block as a result of five separate host write operations, whilst superseded sectors in the original block for the logical group and duplicated sectors in the chaotic update block become obsolete. In host write operation #1, the logical sectors LS10-LS11 of a given logical group stored in an original metablock is updated. The updated logical sectors LS10'-LS11' are stored in

a newly allocated update block. At this point, the update block is a sequential one. In host write operation #2, the logical sectors LS5-LS6 are updated as LS5'-LS6' and recorded in the update block in the location immediately following the last write. This converts the update block from a sequential to a chaotic one. In host write operation #3, the logical sector LS10 is being updated again and is recorded in the next location of the update block as LS10". At this point LS10" in the update block supersedes LS10 in a previous recording which in turns supercedes LS10 in the original block. In host write operation #4, the data in the logical sector LS10 is again updated and is recorded in the next location of the update block as LS10". Thus, LS10" is now the latest and only valid data for the logical sector LS10. In host write operation #5, the data in logical sector LS30 is being updated and recorded in the update block as LS30". Thus, the example illustrates that sectors within a logical group can be written in a chaotic update block in any order and with any repetition.

## Forced Sequential Update

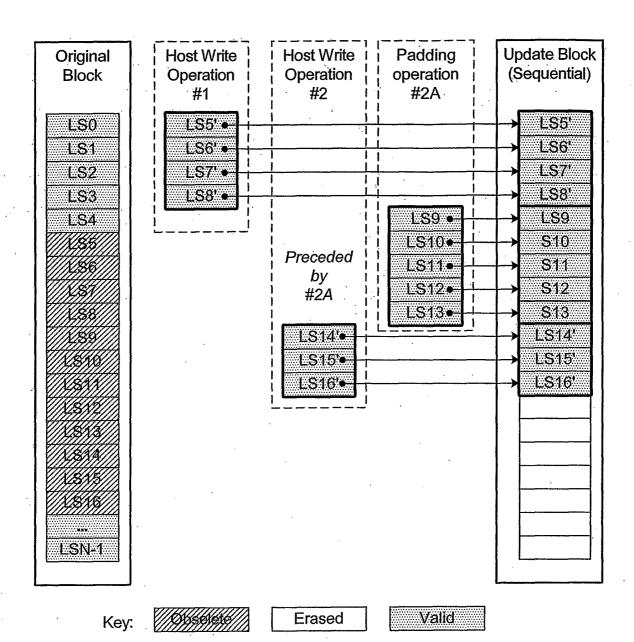

written in sequential order to a sequential update block as a result of two separate host write operations that has a discontinuity in logical addresses. In host write #1, the update data in the logical sectors LS5-LS8 is recorded in a dedicated update block as LS5'-LS8'. In host write #2, the update data in the logical sectors LS14-LS16 is being recorded in the update block following the last write as LS14'-LS16'. However, there is an address jump between LS8 and LS14 and the host write #2 would normally render the update block non-sequential. Since the address jump is not substantial, one option is to first perform a padding operation (#2A) by copying the data of the intervening sectors from the original block to the update block before executing host write #2. In this way, the sequential nature of the update block is preserved.

[00150] FIG. 9 is a flow diagram illustrating a process by the update block manager to update a logical group of data, according a general embodiment of the invention. The update process comprises the following steps:

[00151] STEP 260: The memory is organized into blocks, each block partitioned into memory units that are erasable together, each memory unit for storing

a logical unit of data.

[00152] STEP 262: The data is organized into logical groups, each logical group partitioned into logical units.

- [00153] STEP 264: In the standard case, all logical units of a logical group is stored among the memory units of an original block according to a first prescribed order, preferably, in logically sequential order. In this way, the index for accessing the individual logical units in the block is known.

- [00154] STEP 270: For a given logical group (e.g.,  $LG_X$ ) of data, a request is made to update a logical unit within  $LG_X$ . (A logical unit update is given as an example. In general the update will be a segment of one or more contiguous logical units within  $LG_X$ .)

- [00155] STEP 272: The requested update logical unit is to be stored in a second block, dedicated to recording the updates of  $LG_X$ . The recording order is according to a second order, typically, the order the updates are requested. One feature of the invention allows an update block to be set up initially generic to recording data in logically sequential or chaotic order. So depending on the second order, the second block can be a sequential one or a chaotic one.

- [00156] STEP 274: The second block continues to have requested logical units recorded as the process loops back to STEP 270. The second block will be closed to receiving further update when a predetermined condition for closure materializes. In that case, the process proceeds to STEP 276.

- [00157] STEP 276: Determination is made whether or not the closed, second block has its update logical units recorded in a similar order as that of the original block. The two blocks are considered to have similar order when they recorded logical units differ by only a page tag, as described in connection with FIG. 3A. If the two blocks have similar order the process proceeds to STEP 280, otherwise, some sort of garbage collection need to be performed in STEP 290.

- [00158] STEP 280: Since the second block has the same order as the first block, it is used to replace the original, first block. The update process then ends at STEP 299.

[00159] STEP 290: The latest version of each logical units of the given logical group are gathered from among the second block (update block) and the first block (original block). The consolidated logical units of the given logical group are then written to a third block in an order similar to the first block.

- [00160] STEP 292: Since the third block (consolidated block) has a similar order to the first block, it is used to replace the original, first block. The update process then ends at STEP 299.

- [00161] STEP 299: When a closeout process creates an intact update block, it becomes the new standard block for the given logical group. The update thread for the logical group will be terminated.

- [00162] FIG. 10 is a flow diagram illustrating a process by the update block manager to update a logical group of data, according a preferred embodiment of the invention. The update process comprises the following steps:

- [00163] STEP 310: For a given logical group (e.g.,  $LG_X$ ) of data, a request is made to update a logical sector within  $LG_X$ . (A sector update is given as an example. In general the update will be a segment of one or more contiguous logical sectors within  $LG_X$ .)

- [00164] STEP 312: If an update block dedicated to  $LG_X$  does not already exist, proceed to STEP 410 to initiate a new update thread for the logical group. This will be accomplished by allocating an update block dedicated to recording update data of the logical group. If there is already an update block open, proceed to STEP 314 to begin recording the update sector onto the update block.

- [00165] STEP 314: If the current update block is already chaotic (i.e., non-sequential) then simply proceed to STEP 510 for recording the requested update sector onto the chaotic update block. If the current update block is sequential, proceed to STEP 316 for processing of a sequential update block.

- [00166] STEP 316: One feature of the invention allows an update block to be set up initially generic to recording data in logically sequential or chaotic order. However, since the logical group ultimately has its data stored in a metablock in a logically sequential order, it is desirable to keep the update block sequential as far as

possible. Less processing will then be required when an update block is closed to further updates as garbage collection will not be needed.

[00167] Thus determination is made whether the requested update will follow the current sequential order of the update block. If the update follows sequentially, then proceed to STEP 510 to perform a sequential update, and the update block will remain sequential. On the other hand, if the update does not follow sequentially (chaotic update), it will convert the sequential update block to a chaotic one if no other actions are taken.

[00168] In one embodiment, nothing more is done to salvage the situation and the process proceeds directly to STEP 370 where the update is allowed to turn the update block into a chaotic one.

## Optional Forced Sequential Process

[00169] In another embodiment, a forced sequential process STEP 320 is optionally performed to preserve the sequential update block as far as possible in view of a pending chaotic update. There are two situations, both of which require copying missing sectors from the original block to maintain the sequential order of logical sectors recorded on the update block. The first situation is where the update creates a short address jump. The second situation is to prematurely close out an update block in order to keep it sequential. The forced sequential process STEP 320 comprises the following substeps:

[00170] STEP 330: If the update creates a logical address jump not greater a predetermined amount, C<sub>B</sub>, the process proceeds to a forced sequential update process in STEP 350, otherwise the process proceeds to STEP 340 to consider if it qualifies for a forced sequential closeout.

[00171] STEP 340: If the number of unfilled physical sectors exceeds a predetermined design parameter, C<sub>C</sub>, whose typical value is half of the size of the update block, then the update block is relatively unused and will not be prematurely closed. The process proceeds to STEP 370 and the update block will become chaotic. On the other hand, if the update block is substantially filled, it is considered to have been well utilized already and therefore is directed to STEP 360 for forced sequential

closeout.

[00172] STEP 350: Forced sequential update allows current sequential update block to remain sequential as long as the address jump does not exceed a predetermined amount, C<sub>B</sub>. Essentially, sectors from the update block's associated original block are copied to fill the gap spanned by the address jump. Thus, the sequential update block will be padded with data in the intervening addresses before proceeding to STEP 510 to record the current update sequentially.

[00173] STEP 360: Forced sequential closeout allows the currently sequential update block to be closed out if it is already substantially filled rather than converted to a chaotic one by the pending chaotic update. A chaotic or non-sequential update is defined as one with a forward address transition not covered by the address jump exception described above, a backward address transition, or an address repetition. To prevent a sequential update block to be converted by a chaotic update, the unwritten sector locations of the update block are filled by copying sectors from the update block's associated original partly-obsolete block. The original block is then fully obsolete and may be erased. The current update block now has the full set of logical sectors and is then closed out as an intact metablock replacing the original metablock. The process then proceeds to STEP 430 to have a new update block allocated in its place to accept the recording of the pending sector update that was first requested in STEP 310.

## Conversion to Chaotic Update Block

[00174] STEP 370: When the pending update is not in sequential order and optionally, if the forced sequential conditions are not satisfied, the sequential update block is allowed to be converted to a chaotic one by virtue of allowing the pending update sector, with non-sequential address, to be recorded on the update block when the process proceeds to STEP 510. If the maximum number of chaotic update blocks exist, it is necessary to close the least recently accessed chaotic update block before allowing the conversion to proceed; thus preventing the maximum number of chaotic blocks from being exceeded. The identification of the least recently accessed chaotic update block is the same as the general case described in STEP 420, but is constrained to chaotic update blocks only. Closing a chaotic update block at this time

is achieved by consolidation as described in STEP 550.

## Allocation of New Update Block subject to System Restriction

[00175] STEP 410: The process of allocating an erase metablock as an update block begins with the determination whether a predetermined system limitation is exceeded or not. Due to finite resources, the memory management system typically allows a predetermined maximum number of update blocks,  $C_A$ , to exist concurrently. This limit is the aggregate of sequential update blocks and chaotic update blocks, and is a design parameter. In a preferred embodiment, the limit is, for example, a maximum of 8 update blocks. Also, due to the higher demand on system resources, there may also be a corresponding predetermined limit on the maximum number of chaotic update blocks that can be open concurrently (e.g., 4.)

[00176] Thus, when  $C_A$  update blocks have already been allocated, then the next allocation request could only be satisfied after closing one of the existing allocated ones. The process proceeds to **STEP 420**. When the number of open update blocks is less than  $C_A$ , the process proceeds directly to **STEP 430**.

[00177] STEP 420: In the event the maximum number of update blocks, C<sub>A</sub>, is exceeded, the least-recently accessed update block is closed and garbage collection is performed. The least recently accessed update block is identified as the update block associated with the logical block that has been accessed least recently. For the purpose of determining the least recently accessed blocks, an access includes writes and optionally reads of logical sectors. A list of open update blocks is maintained in order of access; at initialization, no access order is assumed. The closure of an update block follows along the similar process described in connection with STEP 360 and STEP 530 when the update block is sequential, and in connection with STEP 540 when the update block is chaotic. The closure makes room for the allocation of a new update block in STEP 430.

[00178] STEP 430: The allocation request is fulfilled with the allocation of a new metablock as an update block dedicated to the given logical group  $LG_X$ . The process then proceeds to STEP 510.

## Record Update Data onto Update Block

[00179] STEP 510: The requested update sector is recorded onto next available physical location of the update block. The process then proceeds to STEP 520 to determine if the update block is ripe for closeout.

## Update Block Closeout

[00180] STEP 520: If the update block still has room for accepting additional updates, proceed to STEP 570. Otherwise proceed to STEP 522 to closeout the update block. There are two possible implementations of filling up an update block when the current requested write attempts to write more logical sectors than the block has room for. In the first implementation, the write request is split into two portions, with the first portion writing up to the last physical sector of the block. The block is then closed and the second portion of the write will be treated as the next requested write. In the other implementation, the requested write is withheld while the block has it remaining sectors padded and is then closed. The requested write will be treated as the next requested write.

[00181] STEP 522: If the update block is sequential, proceed to STEP 530 for sequential closure. If the update block is chaotic, proceed to STEP 540 for chaotic closure.

#### Sequential Update Block Closeout

[00182] STEP 530: Since the update block is sequential and fully filled, the logical group stored in it is intact. The metablock is intact and replaces the original one. At this time, the original block is fully obsolete and may be erased. The process then proceeds to STEP 570 where the update thread for the given logical group ends.

## Chaotic Update Block Closeout

[00183] STEP 540: Since the update block is non-sequentially filled and may contain multiple updates of some logical sectors, garbage collection is performed to

salvage the valid data in it. The chaotic update block will either be compacted or consolidated. Which process to perform will be determined in STEP 542.

[00184] STEP 542: To perform compaction or consolidation will depend on the degeneracy of the update block. If a logical sector is updated multiple times, its logical address is highly degenerate. There will be multiple versions of the same logical sector recorded on the update block and only the last recorded version is the valid one for that logical sector. In an update block containing logical sectors with multiple versions, the number of distinct logical sectors will be much less than that of a logical group.

[00185] In the preferred embodiment, when the number of distinct logical sectors in the update block exceeds a predetermined design parameter,  $C_D$ , whose typical value is half of the size of a logical group, the closeout process will perform a consolidation in STEP 550, otherwise the process will proceed to compaction in STEP 560.

[00186] STEP 550: If the chaotic update block is to be consolidated, the original block and the update block will be replaced by a new standard metablock containing the consolidated data. After consolidation the update thread will end in STEP 570.

[00187] STEP 560: If the chaotic update block is to be compacted, it will be replaced by a new update block carrying the compacted data. After compaction the processing of the compacted update block will end in STEP 570. Alternatively, compaction can be delayed until the update block is written to again, thus removing the possibility of compaction being followed by consolidation without intervening updates. The new update block will then be used in further updating of the given logical block when a next request for update in  $LG_X$  appears in STEP 502.

[00188] STEP 570: When a closeout process creates an intact update block, it becomes the new standard block for the given logical group. The update thread for the logical group will be terminated. When a closeout process creates a new update block replacing an existing one, the new update block will be used to record the next update requested for the given logical group. When an update block is not closed out, the processing will continue when a next request for update in  $LG_X$  appears in **STEP**

310.

[00189] As can be seen from the process described above, when a chaotic update block is closed, the update data recorded on it is further processed. In particular its valid data is garbage collected either by a process of compaction to another chaotic block, or by a process of consolidation with its associated original block to form a new standard sequential block.

[00190] FIG. 11A is a flow diagram illustrating in more detail the consolidation process of closing a chaotic update block shown in FIG. 10. Chaotic update block consolidation is one of two possible processes performed when the update block is being closed out, e.g., when the update block is full with its last physical sector location written. Consolidation is chosen when the number of distinct logical sectors written in the block exceeds a predetermined design parameter, C<sub>D</sub>. The consolidation process STEP 550 shown in FIG. 10 comprises the following substeps:

[00191] STEP 551: When a chaotic update block is being closed, a new metablock replacing it will be allocated.

[00192] STEP 552: Gather the latest version of each logical sector among the chaotic update block and its associated original block, ignoring all the obsolete sectors.

[00193] STEP 554: Record the gathered valid sectors onto the new metablock in logically sequential order to form an intact block, i.e., a block with all the logical sectors of a logical group recorded in sequential order.

[00194] STEP 556: Replace the original block with the new intact block.

[00195] STEP 558: Erase the closed out update block and the original block.