(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6676536号

(P6676536)

(45) 発行日 令和2年4月8日(2020.4.8)

(24) 登録日 令和2年3月16日(2020.3.16)

(51) Int.Cl.

F 1

H02M 3/155 (2006.01)

H05B 45/00 (2020.01)H02M 3/155

H05B 37/02H

J

請求項の数 15 (全 18 頁)

(21) 出願番号 特願2016-555297 (P2016-555297)

(86) (22) 出願日 平成27年3月5日 (2015.3.5)

(65) 公表番号 特表2017-513447 (P2017-513447A)

(43) 公表日 平成29年5月25日 (2017.5.25)

(86) 國際出願番号 PCT/US2015/019065

(87) 國際公開番号 WO2015/134813

(87) 國際公開日 平成27年9月11日 (2015.9.11)

審査請求日 平成30年2月28日 (2018.2.28)

(31) 優先権主張番号 61/948,175

(32) 優先日 平成26年3月5日 (2014.3.5)

(33) 優先権主張国・地域又は機関

米国(US)

(73) 特許権者 516043960

シグニファイ ホールディング ピー ヴ

イ

S I G N I F Y H O L D I N G B. V

.オランダ国 5656 アーネー アイン

トホーフェン ハイ テク キャンパス

48

H i g h T e c h C a m p u s 4 8

, 5656 AE E i n d h o v e n,

The N e t h e r l a n d s

(74) 代理人 100163821

弁理士 柴田 沙希子

前置審査

最終頁に続く

(54) 【発明の名称】 LEDベースライト用のデジタル制御スイッチモードスタートアップ回路

## (57) 【特許請求の範囲】

## 【請求項 1】

照明コントローラを動作させる出力電圧を供給する電圧調整器と、前記電圧調整器に結合され、且つライン入力から前記電圧調整器に電源電流を供給するパワーFETと、前記パワーFETのゲートに結合され、且つ前記照明コントローラのスタートアップモード中にスイッチングモード電源として前記パワーFETを動作させるゲート駆動回路とを含み、前記パワーFETは、デプレッションモードパワーFETであり、且つ電流パワートレインの一部であり、

前記電流パワートレインは、前記デプレッションモードパワーFETに結合され、且つエンハンストモードパワーFETを有する第2のパワーFETと、前記デプレッションモードパワーFETのソースに結合され、且つ前記エンハンストモードパワーFETのドレインに結合されたダイオードとを有する、装置。

## 【請求項 2】

照明コントローラを動作させる出力電圧を供給する電圧調整器と、前記電圧調整器に結合され、且つライン入力から前記電圧調整器に電源電流を供給するパワーFETと、前記パワーFETのゲートに結合され、且つ前記照明コントローラのスタートアップモード中にスイッチングモード電源として前記パワーFETを動作させるゲート駆動回路とを含み、前記ゲート駆動回路は、前記パワーFETのゲートに結合されたインバータを含み、前記インバータは、電源電圧及び前記パワーFETのソースにおける電圧を含む電圧のうちの大きい方の電圧を供給する、装置。

**【請求項 3】**

前記ゲート駆動回路は、前記照明コントローラのスタートアップ期間中、前記パワーFETを動作させる、請求項1又は2に記載の装置。

**【請求項 4】**

前記ゲート駆動回路は、前記照明コントローラのスタートアップ期間後に前記パワーFETをデジタル的にオフにする、請求項3に記載の装置。

**【請求項 5】**

前記パワーFETのソースに結合された補助出力電圧ノードをモニタリングし、第1閾値電圧にモニタリングされた出力電圧が到達した後に、前記パワーFETのゲートをグランドに結合するよう前記ゲート駆動回路を制御するためのデジタル制御ループを更に有する、請求項1又は2に記載の装置。 10

**【請求項 6】**

前記デジタル制御ループは更に、第2の閾値電圧にモニタリングされた出力電圧が到達した後に、前記パワーFETのゲートを前記電源電圧ノードに結合するよう前記ゲート駆動回路を制御する、請求項5に記載の装置。

**【請求項 7】**

前記デジタル制御ループは、前記電圧調整器の出力電圧と第1の閾値電圧に対応する基準電圧とを比較する比較器を含む、請求項5に記載の装置。

**【請求項 8】**

前記デジタル制御ループは、前記比較器に結合されたロジック回路を含み、前記ロジック回路は、少なくとも部分的に前記比較器の出力に基づいて前記パワーFETのゲートに制御信号を出力する、請求項7に記載の装置。 20

**【請求項 9】**

前記パワーFETと前記ライン入力との間に結合される抵抗を更に有する、請求項1又は2に記載の装置。

**【請求項 10】**

パワーFETにおいてライン電圧を受け取るステップと、前記パワーFETによって、前記パワーFETから電圧調整器に電流供給を提供するステップと、前記電圧調整器によって、前記電流供給から照明コントローラ用の電源電圧を生成するステップと、前記パワーFETのゲートに結合されたゲート駆動回路によって、前記電流供給を提供するためのスイッチングモード電源として前記パワーFETを動作させるステップとを含む方法であって、前記パワーFETを動作させるステップは、前記照明コントローラのスタートアップ段階中に、前記パワーFETをスイッチングモード電源として動作させることを含み、前記パワーFETは、デプレッションモードパワーFETであり、且つ電流パワートレインの一部であり。 30

前記電流パワートレインは、前記デプレッションモードパワーFETに結合され、且つエンハンストモードパワーFETを有する第2のパワーFETと、前記デプレッションモードパワーFETのソースに結合され、且つ前記エンハンストモードパワーFETのドレインに結合されたダイオードとを有する、方法。

**【請求項 11】**

パワーFETにおいてライン電圧を受け取るステップと、前記パワーFETによって、前記パワーFETから電圧調整器に電流供給を提供するステップと、前記電圧調整器によって、前記電流供給から照明コントローラ用の電源電圧を生成するステップと、前記パワーFETのゲートに結合されたゲート駆動回路によって、前記電流供給を提供するためのスイッチングモード電源として前記パワーFETを動作させるステップとを含む方法であって、前記パワーFETを動作させるステップは、前記照明コントローラのスタートアップ段階中に、前記パワーFETをスイッチングモード電源として動作させることを含み、前記ゲート駆動回路は、前記パワーFETのゲートに結合されたインバータを含み、前記インバータは、電源電圧及び前記パワーFETのソースにおける電圧を含む電圧のうちの大きい方の電圧を供給する、方法。 40

**【請求項 1 2】**

前記パワーFETを動作させるステップは、前記照明コントローラのスタートアップ段階後に、前記パワーFETをデジタル的にオフにすることを含む、請求項1 0又は1 1に記載の方法。

**【請求項 1 3】**

デジタル制御ループによって、前記パワーFETに結合された補助出力ノードにおける電圧をモニタリングするステップと、前記デジタル制御ループによって、モニタリングされた前記電圧が第1の閾値に達する時を決定するステップと、前記モニタリングされた電圧が前記第1の閾値に達した後に前記パワーFETをデジタル的にオフにするステップとを更に含む、請求項1 2に記載の方法。

10

**【請求項 1 4】**

前記デジタル制御ループによって、前記モニタリングされた電圧が第2の閾値に達する時を決定するステップと、前記モニタリングされた電圧が前記第2の閾値に達した後に前記パワーFETをデジタル的にオンにするステップとを更に含む、請求項1 3に記載の方法。

**【請求項 1 5】**

前記ゲート駆動回路に結合され、且つ前記照明コントローラの前記スタートアップモード中に前記パワーFETを制御し、且つ調光器互換性を提供するように前記パワーFETを制御するロジック回路を更に含む、請求項1又は2に記載の装置。

20

**【発明の詳細な説明】****【技術分野】****【0 0 0 1】**

関連出願の相互参照

[0001] 本出願は、本明細書に援用される、2014年3月5日に出願された「A Digitally Controlled High Voltage (HV) Startup Circuit for LED Lighting Applications」という名称のErik J. Mentzeらの米国仮特許出願第61/948,175号の優先権の利益を主張する。本出願は、主題に関して、2015年3月5日に出願された「Digitally-Controlled Switch-Mode Start-Up Circuit With Dimmer Compatibility For LED-Based Lights」という名称のErik J. Mentzeらの米国仮特許出願第14/639,925号に関連する。

30

**【0 0 0 2】**

[0002] 本開示は、照明デバイスに関する。より具体的には、本開示は、LED照明内のコントローラ用の電源電圧生成に関する。

**【背景技術】****【0 0 0 3】**

[0003] 白熱電球に取って代わる代替照明デバイスは、エネルギーが光に変換される方法が白熱電球と異なる。白熱電球は、金属フィラメントを含む。電気が金属フィラメントに印加されると、金属フィラメントは熱くなり、且つ白熱し、光を周辺領域に放射する。従来の白熱電球の金属フィラメントは、一般的に、特定の電力要件を有さない。即ち、金属フィラメントが受動デバイスであるため、任意の電圧及び任意の電流を金属フィラメントに印加することができる。電圧及び電流は、金属フィラメントを白熱状態に加熱するのに十分なものである必要はあるが、金属フィラメントに送られるエネルギーの他の特徴は、白熱電球の動作に影響を与えない。従って、殆どの住居及び商業ビルにおける従来のライセン電圧は、白熱電球の動作にとって十分である。

40

**【0 0 0 4】**

[0004] しかしながら、小型蛍光灯(CFL: compact fluorescent light)電球及び発光ダイオード(LED: light emitting diode)ベース電球等の代替照明デバイスは、電球へのエネルギー供給と相互作用する能動素子を含む。これらの代替デバイスは、それらのエネルギー消費の減少に関して好ましいが、代替デバイスは、電球に送られるエネルギーに関して特定の要件を有する。例えば、代替デバイスは、LED、安定器、又は電球

50

の他の構成要素への電力の送出を制御するコントローラ集積回路（コントローラIC）を含む。コントローラICは、同様に低電圧で動作するコンピュータデバイスと同様の構成要素から及び同様の製造技術を用いて作られた低電圧デバイスである。但し、コンピュータデバイスは、コントローラICを動作させるための低電圧を生成するために束ねられたAC/DCアダプタブリックを有するが、電球は、スペースが限られており、従来のAC/DCアダプタを含むことができない。代わりに、LEDベース電球は、高電圧ACライン入力を受け入れて、通常動作中にコントローラICに電力を供給するための、ライン入力よりもはるかに低いDC低電圧出力を提供するように構成された小型スイッチモード電源を含む。LEDベース電球の最初のターンオン中、スイッチモード電源のDC低電圧出力は、コントローラICに電力を供給することができず、システムを開始させ、及び主電源がオンラインになるまで一時的電源を提供するために、スタートアップ回路がスイッチモード電源に付属している。

#### 【0005】

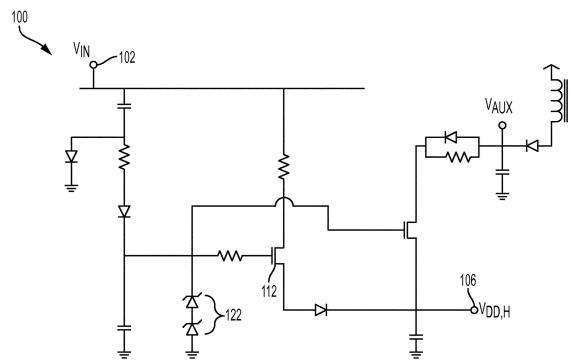

[0005] 図1は、先行技術によるLEDベース電球用の従来のスタートアップ回路100の一例である。回路100は、抵抗113を介してAC電圧入力 $V_{IN}$ ノード102に結合された高電圧パワー電界効果トランジスタ（HVパワーFET）112を含む。HVパワーFET112は、飽和モードにおいてツェナーダイオード122を用いてバイアスがかけられ、ノード106において電源電圧 $V_{DD,H}$ を生成する。回路100は、 $V_{IN}$ ノード102から高ピーク電流を引き出し、補助電圧入力 $V_{AUX}$ ノードがノード106の電圧 $V_{DD,H}$ よりも低い場合に小さい連続電流を引き出し続ける。回路100は、時折非常に高い連続した電流引き出しと、HVパワーFET112のバイアス状態により、HVパワーFET112内で大量の電力を損失させる。HVパワーFET112が、LEDベース電球用の集積回路（IC：integrated circuit）に他の構成要素と共に統合される場合、HVパワーFET112によって生成される熱がICの構築を困難にする。例えば、HVパワーFET112は、最大電力損失規格を超えることなく熱を放散するのに十分な大きさでなければならない。HVパワーFET112のより大きいサイズは、ICのコストを増加させ、及びICを電球に組み込むことを困難にする。

#### 【0006】

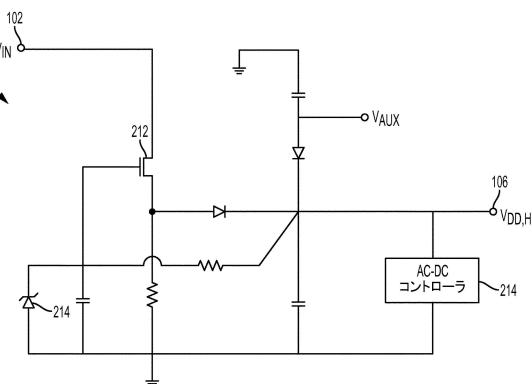

[0006] 図2は、先行技術によるLEDベース電球用の従来のスタートアップ回路200の別の例である。回路200は、AC入力電圧 $V_{IN}$ ノード102に結合されたデプレッショントラブルFET212を含む。デプレッショントラブルFET212は、飽和モードにおいてツェナーダイオード214によってバイアスがかけられて、 $V_{DD,H}$ 供給出力ノード106において低電圧を生成する。電源電圧 $V_{DD,H}$ は、スタートアップ中にコントローラ214を動作させるためにコントローラに供給される。図1の回路100と同様に、回路200は、補助電圧入力 $V_{AUX}$ ノードがノード106の電圧 $V_{DD,H}$ よりも低い場合に、 $V_{IN}$ ノード102から電流を引き出し続ける。デプレッショントラブルFET212は、デプレッショントラブルFET212が電力消費を減少させるための遷移時間中にのみ電力を損失させるが、回路200は、必要とされる負荷電流が約0.5ミリアンペア未満の低電力用途に限られる。負荷電流が0.5ミリアンペアを超えて上昇すると、デプレッショントラブルFET212による電力損失は、図1の回路100において上記に説明した問題と同様の問題を生じさせる。

#### 【0007】

[0007] 図1及び図2を参照して説明された従来のスタートアップ回路の両方において、入力電圧 $V_{IN}$ ノード102は、飽和モードでバイアスをかけられた際のパワーFET112又は212を通して低下される。更に、スタートアップ回路からの出力電流は、最大5ミリアンペア以上を消費するデジタルコントローラをスタートアップさせるのに不十分となる。従って、電力損失を低下させながら、より大きい負荷電流を供給する回路が必要とされる。

#### 【0008】

[0008] ここに記述された欠点は代表的なものに過ぎず、特に照明デバイス及び消費者

10

20

30

40

50

レベルデバイス用の、低電力損失のための改良されたスタートアップ回路に対するニーズが存在することを単に強調するために含まれたものである。ここに記載される実施形態は、幾つかの欠点に対処するが、必ずしもここに記載される又は当該技術分野で知られているあらゆる欠点に対処するものではない。

【発明の概要】

【課題を解決するための手段】

【0009】

[0009] スタートアップ回路による電力消費は、入力電圧に結合されたパワーFETをスイッチとして動作させることによって減少される。デジタル制御は、例えば、パワーFETのゲートをアースに結合させて、パワーFETをオフにすることを含む。パワーFETがオフにされると、スタートアップ回路は、入力電圧から殆ど又は全く電力を消費しないことができる。パワーFETが、オン状態とオフ状態とをデジタル的に切り換えられると、パワーFETがスイッチモードで動作されるため、パワーFET内の電力損失が減少する。一実施形態では、スイッチモード動作パワーFETは、ドレイン端子とソース端子との間のパワーFETの抵抗が増加する飽和モードで動作されることができる。パワーFETは、1つ又は複数の出力電圧を生成する電圧調整器に結合される。パワーFETは、1つ又は複数の電圧調整器出力に基づいてパワーFETをオン及びオフにすることを決定するロジック回路によって生成されるデジタル信号により、オン及びオフにされる。

【0010】

[0010] パワーFETはまた、LEDベース電球の通常動作中に調光器互換性を提供するためにスタートアップ後に動作される。スタートアップ回路に関連するロジック回路は、ホストコントローラICから制御信号を受信する。ホストコントローラICは、調光器互換性を提供するべくパワーFETを構成するようにロジック回路に指示する。

【0011】

[0011] 一実施形態によれば、装置は、以下：1) 照明コントローラを動作させる出力電圧を供給するように構成された電圧調整器；2) 電圧調整器に結合され、且つライン入力から電圧調整器に電源電流を供給するように構成されたパワーFET；及び／又は3) パワーFETのゲートに結合され、且つ照明コントローラのスタートアップモード中にスイッチングモード電源としてパワーFETを動作させるように構成されたゲート駆動回路を含む。

【0012】

[0012] 実施形態によっては、装置は、補助出力電圧ノード $V_{AUX}$ をモニタリングするように構成されたデジタル制御ループも含む。出力電圧ノード $V_{AUX}$ が第1の閾値電圧に達すると、デジタル制御ループは、パワーFETのゲートに結合されたゲート駆動回路に対し、パワーFETのゲートをアースするように信号を送り、その結果、パワーFETをオフにする。出力電圧ノード $V_{AUX}$ が、大きさで第1の閾値電圧を上回る第2の閾値電圧に達すると、デジタル制御ループは、パワーFETのゲートに結合されたゲート駆動回路に対し、パワーFETのゲートに電力を印加するように信号を送り、その結果、パワーFETをオンにする。

【0013】

[0013] 特定の実施形態では、ゲート駆動回路は、照明コントローラのスタートアップ期間中、パワーFETを動作させるように構成され；ゲート駆動回路は、照明コントローラのスタートアップ期間後にパワーFETをデジタル的にオフにするように構成され得；パワーFETは、デプレッションモードパワーFETでもよく、且つデプレッションモードパワーFETに結合された第2のエンハンストモードパワーFETを有し、及びデプレッションモードパワーFETのソースに結合され、且つエンハンストモードパワーFETのドレインに結合されたダイオードを有する電流パワートレインの一部でもよく；ゲート駆動回路は、パワーFETのゲートに結合されたインバータを含み、インバータは、電源電圧及びパワーFETのソースにおける電圧を含む電圧のうちの大きい方の電圧を供給するように構成され；デジタル制御ループは、第2の閾値電圧がモニタリングされた出力電

10

20

30

40

50

圧によって到達された後に、パワーFETのゲートを電源電圧ノードに結合するようにゲート駆動回路を制御するように更に構成され；デジタル制御ループは、電圧調整器の出力電圧及び第1の閾値電圧に対応する基準電圧を比較する比較器を含み；デジタル制御ループは、比較器に結合されたロジック回路を含み、及びロジック回路は、少なくとも部分的に比較器の出力に基づいてパワーFETのゲートに制御信号を出力するように構成され；並びに／又は電圧調整器、パワーFET、及びゲート駆動回路は、集積回路（IC）に統合され、且つ抵抗は、集積回路（IC）に対して外部である。

#### 【0014】

[0014] 別の実施形態によれば、方法は、パワーFETにおいてライン電圧を受け取るステップ；パワーFETによって、パワーFETから電圧調整器に電流供給を提供するステップ；電圧調整器によって、電流供給から照明コントローラ用の電源電圧を生成するステップ；及び／又はパワーFETのゲートに結合されたゲート駆動回路によって、電流供給を提供するためのスイッチングモード電源としてパワーFETを動作させるステップを含む。

10

#### 【0015】

[0015] 実施形態によっては、本方法は、デジタル制御ループによって、パワーFETに結合された補助出力ノードにおける電圧をモニタリングするステップ；デジタル制御ループによって、モニタリングされた電圧が第1の閾値に達する時を決定するステップ；モニタリングされた電圧が第1の閾値に達した後にパワーFETをデジタル的にオフにするステップ；デジタル制御ループによって、モニタリングされた電圧が第2の閾値に達する時を決定するステップ；モニタリングされた電圧が第2の閾値に達した後にパワーFETをデジタル的にオンにするステップ；及び／又はパワーFETに結合された外部抵抗において電力を損失させるステップも含む。

20

#### 【0016】

[0016] 特定の実施形態では、パワーFETを動作させるステップは、照明コントローラのスタートアップ段階中に、パワーFETをスイッチングモード電源として動作させることを含み、及び／又はパワーFETを動作させるステップは、照明コントローラのスタートアップ段階後に、パワーFETをデジタル的にオフにすることを含む。

#### 【0017】

[0017] 更に別の実施形態によれば、装置は、照明コントローラに供給するための出力電圧を生成するように構成された電圧調整器；パワーFETを含み、且つ電圧調整器に結合された電流パワートレイン；パワーFETのゲートに結合されたゲート駆動回路；及び／又はゲート駆動回路に結合され、且つ電界効果トランジスタをスイッチングモード電源として動作させるように構成されたロジック回路を含む。

30

#### 【0018】

[0018] 実施形態によっては、装置は、ロジック回路に結合された比較器も含み、比較器は、補助出力ノード電圧と基準電圧との差に比例する信号をロジック回路に提供するように構成される。

#### 【0019】

[0019] 特定の実施形態では、パワーFETは、高電圧（HV：high-voltage）デブリッシャンモードパワーFETでもよく；電流パワートレインは、低電圧（LV：low-voltage）エンハンストモードパワーFETであって、LVパワーFETのドレインがHVパワーFETのソースに結合される、LVエンハンストモードパワーFETと、LVパワーFETのドレイン及びHVパワーFETのソースに結合されるダイオードとを含み；ゲート駆動回路は、電界効果トランジスタのゲートに結合されたインバータを含み、インバータへの電力供給入力は、パワーFETのソースにおける電圧及び電圧調整器の出力電圧のうちの大きい方でもよく；並びに／又はロジック回路は、比較器の信号に基づいてパワーFETをデジタル的に切り換えるように構成される。

40

#### 【0020】

[0020] 一実施形態によれば、装置は、照明コントローラを動作させるための出力電圧

50

を供給するように構成された電圧調整器；電圧調整器に結合され、且つライン入力から電圧調整器に電源電流を供給するように構成されたパワーFET；及び／又はパワーFETに結合され、且つ照明コントローラのスタートアップ段階中にパワーFETを制御し、及び調光器互換性を提供するようにパワーFETを制御するように構成されたロジック回路を含む。

【0021】

[0021] 実施形態によっては、装置は、電界効果トランジスタのソースに比例する入力信号に結合され、且つ基準信号に結合されたデジタルフィードバックループも含み、ロジック回路は、入力信号が基準信号を下回ることをデジタルフィードバックループが示す場合にパワーFETを導通させ、且つ入力信号が基準信号に達したことをデジタルフィードバックループが示す場合にパワーFETを導通させないように構成され；並びに／又は電界効果トランジスタのソースに比例する入力信号に結合され、且つ基準信号に結合されたデジタルフィードバックループも含み、ロジック回路は、入力信号が基準信号を下回ることをデジタルフィードバックループが示す場合に、電流をダイオードに向けるために、パワーFETを導通させ、及び第2のパワーFETを導通させず、且つ入力信号が基準信号に達したことをデジタルフィードバックループが示す場合に、パワーFETを導通させ、第2のパワーFETを導通させるように構成される。

【0022】

[0022] 特定の実施形態では、ロジック回路は、照明コントローラからモード入力を受信するように構成されたモード入力ノードを含み、ロジック回路は、少なくとも部分的にモード入力に基づいてパワーFETを制御するように構成され得；パワーFETは、電流パワートレインの一部でもよく、電流パワートレインは、第1のパワーFETのソースに結合された第2のパワーFETと、パワーFETのソースに結合され、且つ第2のパワーFETのドレインに結合されたダイオードとを含み；ロジック回路は、照明コントローラのスタートアップ段階中に、照明コントローラ用のスイッチングモード電源としてパワーFETを動作させるようにパワーFETのゲートを制御するように構成され；ロジック回路は、パワーFET及び第2のパワーFETをオフにするために電界効果トランジスタのゲート及び第2のパワーFETのゲートを制御するように構成され；ロジック回路は、パワーFET及び第2のパワーFETをオンにするために電界効果トランジスタのゲート及び第2のパワーFETのゲートを制御するように構成され；ロジック回路は、ダイオードへの駆動電流及び第2の電界効果トランジスタ（パワーFET）への駆動電流をアースへと交互に送るように、電界効果トランジスタのゲート及び第2のパワーFETのゲートを制御するように構成され；パワーFETは、デプレッションモードパワーFETでもよく、及び第2のパワーFETは、エンハンストモードパワーFETでもよく；並びに／又はロジック回路は、制御シーケンスロジックを含む。

【0023】

[0023] 別の実施形態によれば、方法は、パワーFETにおいてライン電圧を受け取るステップ；パワーFETによって、電流供給を電圧調整器に提供するステップ；電圧調整器によって、電流供給から照明コントローラ用の電源電圧を生成するステップ；及び／又はパワーFETのゲートに結合されたゲート駆動回路によって、照明コントローラのスタートアップ段階中及びスタートアップ段階後に、調光器互換性を提供するようにパワーFETを動作させるステップを含む。

【0024】

[0024] 実施形態によっては、本方法は、調光器互換性を提供するようにパワーFETを動作させるためのモード選択を照明コントローラから受信するステップ；パワーFETに結合された出力ノードにおける電圧レベルを示すフィードバック信号を受信するステップであって、パワーFETをスイッチングモード電源として動作させるステップが、少なくとも部分的にフィードバック信号に基づいてパワーFETをデジタル的に切り換えることを含む、ステップ；パワーFETに結合され、且つアースに結合された第2のパワーFETをオンにするステップ；並びに／又はパワーFETに結合された出力ノードにおける

10

20

30

40

50

電圧レベルを示すフィードバック信号を受信するステップであって、交互に行うステップは、少なくとも部分的にフィードバック信号に基づいて、パワーFETを通して駆動電流を電圧調整器に送ること及びパワーFETを通して駆動電流をアースに送ることを交互に行うことを含む、ステップも含むことができる。

【0025】

[0025] 特定の実施形態では、スタートアップ段階中にパワーFETを動作させるステップは、照明コントローラのスタートアップ段階中にパワーFETをスイッチングモード電源として動作させることを含み；スタートアップ段階後にパワーFETを動作させるステップは、パワーFETをオフにすることを含み；スタートアップ段階後にパワーFETを動作させるステップは、電流をライン電圧入力ノードからアースへと導通させるようにパワーFETを制御することを含み；及び／又はスタートアップ段階後にパワーFETを動作させるステップは、パワーFET及びダイオードを通して駆動電流を電圧調整器に送ること及びパワーFETを通して駆動電流をアースに送ることを交互に行うことを含む。

【0026】

[0026] 更に別の実施形態によれば、装置は、照明コントローラに供給するための出力電圧を生成するように構成された電圧調整器；パワーFETを含み、且つ電圧調整器及びライン電圧入力ノードに結合された電流パワートレイン；パワーFETのゲートに結合されたゲート駆動回路；及び／又はゲート駆動回路に結合され、且つ照明コントローラのスタートアップ段階中にパワーFETを制御し、且つ調光器互換性を提供するようにパワーFETを制御するように構成されたロジック回路を含む。

【0027】

[0027] 実施形態によっては、装置は、ロジック回路に結合されたフィードバックループも含み、フィードバックループは、電流パワートレインの出力における電圧と基準電圧との差を示すフィードバック信号を提供し、及びロジック回路は、少なくとも部分的にフィードバック信号に基づいて電流パワートレインを動作させるように構成される。

【0028】

[0028] 特定の実施形態では、電流パワートレインは、パワーFETに結合された第2のパワーFETと、パワーFETのソースに結合され、且つ第2のパワーFETのドレインに結合されたダイオードとを含み得；パワーFETは、デプレッションモードパワーFETでもよく、及び第2のパワーFETは、エンハンストモードパワーFETでもよく；ロジック回路は、照明コントローラからモード入力を受信するように構成されたモード入力ノードを含み、ロジック回路は、少なくとも部分的にモード入に基いて電流パワートレインを制御するように構成され；ロジック回路は、以下のモードの少なくも1つにおいて電流パワートレインを動作させるように構成され；並びに／又はロジック回路は、以下のモード：照明コントローラのスタートアップ段階中に照明コントローラ用のスイッチングモード電源としてパワーFETを動作させる第1のモード、電流パワートレインを停止させる第2のモード、ライン電圧入力ノードからアースへと電流を導通するように電流パワートレインを制御する第3のモード、及び電流パワートレインを通して駆動電流を電圧調整器へと送ること及び電流パワートレインを通して駆動電流をアースへと送ることを交互に行う第4のモードの少なくとも1つにおいて、電流パワートレインを動作させるように構成される。

【0029】

[0029] 上記は、以下に続く詳細な説明をより良く理解することができるよう、本発明の実施形態の特定の特徴及び技術的利点の概要をかなり大まかに述べたものである。本発明の請求項の主題を成す追加の特徴及び利点が、以下に説明される。開示された概念及び具体的な実施形態は、同じ又は類似の目的を実施するための他の構造を変更又は設計するための基礎として容易に利用することが当業者によって認識されるであろう。そのような均等な構造が添付の特許請求の範囲に記載される本発明の趣旨及び範囲から逸脱しないことも、当業者によって理解されるであろう。追加の特徴は、添付の図面に関連して考慮された場合に、以下の説明からより良く理解されるであろう。但し、各図面は、例示及び

10

20

30

40

50

説明目的でのみ提供されることと、本発明を限定することが意図されないことが明確に理解されるものとする。

【0030】

[0030] 開示されるシステム及び方法のより詳細な理解のために、添付の図面と併せて以下の説明がこれより言及される。

【図面の簡単な説明】

【0031】

【図1】[0031] 先行技術によるLEDベース電球用の従来のスタートアップ回路を示す例示的回路図である。

【図2】[0032] 先行技術によるLEDベース電球用の従来のスタートアップ回路を示す別の例示的回路図である。 10

【図3】[0033] 本開示の一実施形態による、コントローラ電源電圧を生成するためのデジタル制御スイッチモードスタートアップ回路を示す例示的ブロック図である。

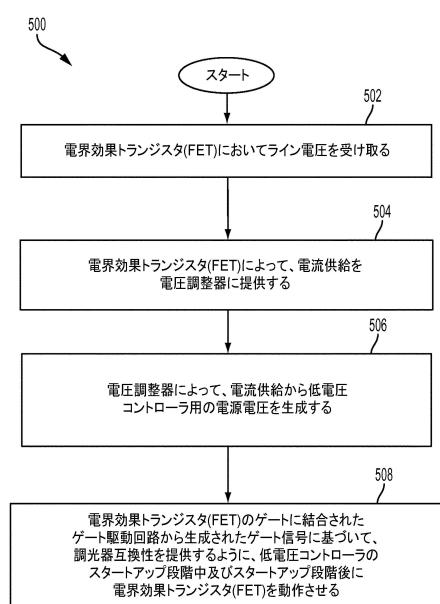

【図4】[0034] 本開示の一実施形態による、コントローラ電源電圧を生成するためのスイッチモードスタートアップ回路を動作させる方法を示す例示的フローチャートである。

【図5】[0035] 本開示の一実施形態による、調光器互換性を提供するようにスタートアップ回路の動作をデジタル的に制御する方法を示す例示的フローチャートである。

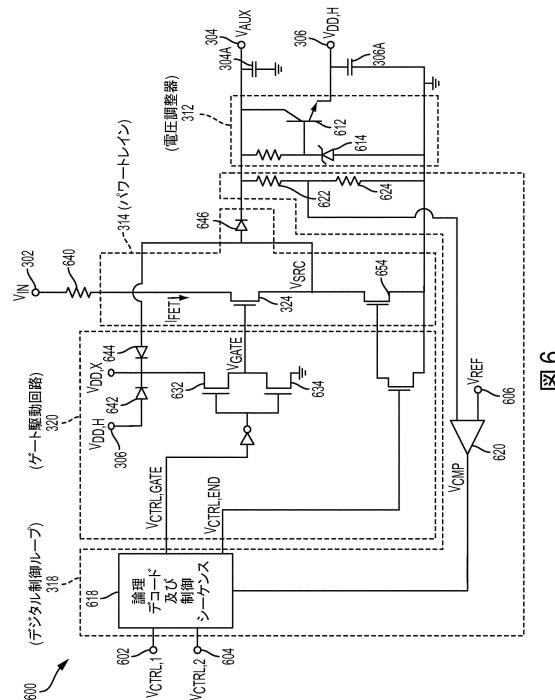

【図6】[0036] 本開示の一実施形態による、コントローラ電源電圧を生成するため及び調光器互換性を提供するためのパワーFETのデジタル制御を示す例示的回路図である。 20

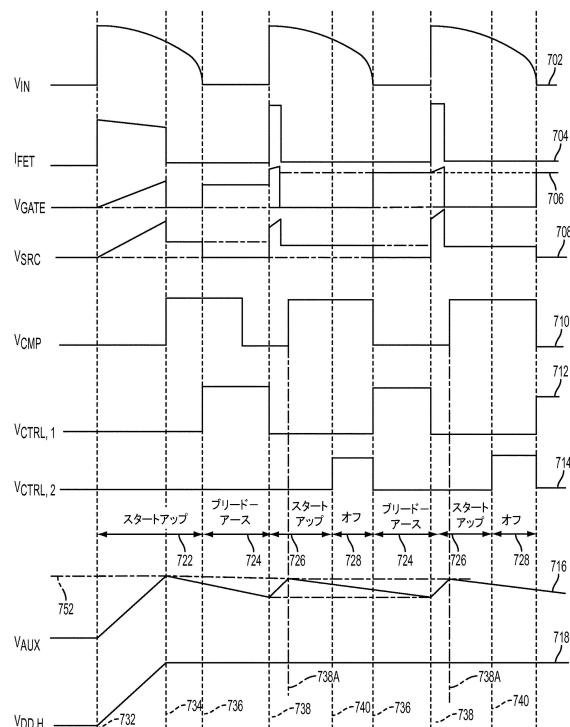

【図7】[0037] 本開示の一実施形態による、LEDベース電球においてスタートアップ及び調光器互換性を提供するための図6の回路の動作を示す例示的グラフである。

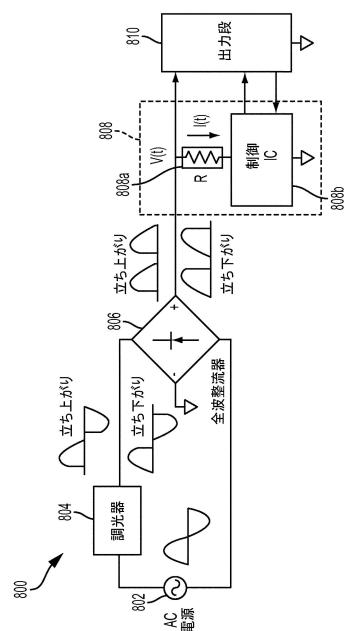

【図8】[0038] 本開示の一実施形態による、デジタル制御スイッチモードスタートアップ回路を備えた発光ダイオード(LED)ベース電球用の調光器システムを示す例示的ブロック図である。

【発明を実施するための形態】

【0032】

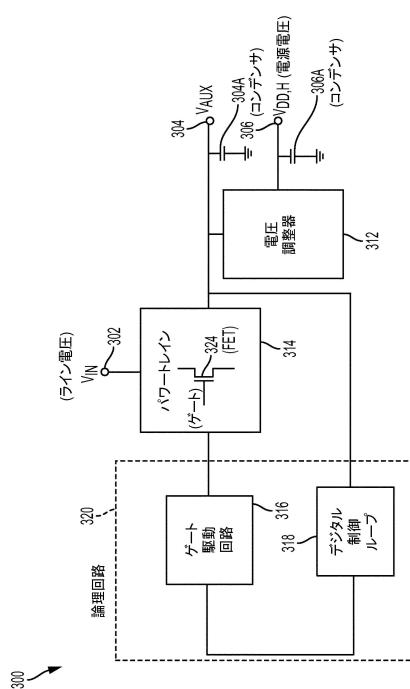

[0039] 図3は、本開示の一実施形態による、コントローラ電源電圧を生成するためのデジタル制御スイッチモードスタートアップ回路を示す例示的ブロック図である。電圧調整器312は、出力ノード304において補助出力電圧 $V_{AUX}$ を間接的に制御することができる、及び出力ノード306において電源電圧 $V_{DD,H}$ を直接的に制御することができる。 $V_{DD,H}$ 電圧は、例えば、コントローラ集積回路(コントローラIC)用の約5~15ボルトの電源電圧でもよく、及び $V_{AUX}$ 電圧より低くてもよい。 $V_{AUX}$ 用の出力ノード306は、スタートアップ回路300がオフの時に電圧調整器312に電流を供給する変圧器(不図示)の巻線に結合される。出力ノード304、306の各々は、それぞれコンデンサ304A、306Aによって、比較的一定に維持することができる。 30

【0033】

[0040] 電圧調整器312は、ライン電圧 $V_{LINE}$ 等の入力電圧 $V_{IN}$ を受け取る入力ノード302からパワートレイン314を経由して電力を受け取ることができる。パワートレイン314は、入力ノード302からの電力を電圧調整器312に印加するトランジスタ324を含む。パワートレイン314は、ゲート駆動回路316及びデジタル制御ループ318を含むロジック回路320によって制御される。ゲート駆動回路316は、トランジスタ324のゲートへの入力用の信号を生成することができる。ゲート駆動回路316によって生成された信号は、例えば、出力ノード304において所望の補助電圧 $V_{AUX}$ レベルを生成するようにトランジスタ324を制御することができる。一実施形態では、パワートレイン314は、ダイオードを介して $V_{AUX}$ ノード304に直接結合する。ゲート駆動回路316は、デジタル制御ループ318を経由して、パワートレイン314の動作に関するフィードバックを受け取ることができる。例えば、デジタル制御ループ318は、出力ノード304における補助電圧 $V_{AUX}$ の電圧レベルに関する情報を提供する。 40

【0034】

[0041] 一実施形態では、トランジスタ324は、高電圧デプレッションモードパワーFETでもよい。パワートレイン314は、低電圧エンハンストモードパワーFET等の他のトランジスタ(不図示)及びブロッキングダイオード等の他の構成要素も含む。スタートアップ時、電流は、入力ノード302からトランジスタ324を経由して出力ノード304用の充電コンデンサ304Aに引き出される。トランジスタ324は、回路300のスタートアップ中に、コンデンサ304AがLEDベース電球の通常動作のためのレベルにまで充電する間、トランジスタ324を「オン」状態に維持するためにブート処理される。

### 【0035】

[0042] ゲート駆動回路316は、トランジスタ324をデジタル的にオン及びオフにすることによってトランジスタ324を制御する。例えば、スタートアップ中に、ゲート駆動回路316は、 $V_{DD,x}$ (不図示)電圧をトランジスタ324のゲートに印加する。 $V_{DD,x}$ 電圧は、トランジスタ324を「オン」状態に維持するために、トランジスタ324のソース電圧をトラッキングする。 $V_{DD,x}$ 電圧は、コンデンサ304Aにおける補助電圧 $V_{AUX}$ が上昇するにつれて上昇する。デジタル制御ループ318は、補助電圧 $V_{AUX}$ レベルをモニタリングし、パワートレイン314の制御のためにゲート駆動回路316にフィードバックを提供することができる。補助電圧 $V_{AUX}$ が第1の閾値レベルに達するか、又は第1の閾値レベルを超えたことをデジタル制御ループ318が検出すると、ゲート駆動回路316は、アースをトランジスタ324のゲートに結合する。トランジスタ324は、その後、トランジスタ324を「オフ」状態に維持するために十分な負のゲート-ソース電圧 $V_{GS}$ が生成された後に、「オフ」状態に遷移する。補助電圧 $V_{AUX}$ レベルが第1の閾値レベルよりも低い第2の閾値レベルにまで低下したことをデジタル制御ループ318が検出すると、ゲート駆動回路316は、トランジスタ324を再び「オン」状態に遷移させるために、トランジスタ324のゲートに $V_{DD,x}$ 電圧を送ることができる。トランジスタ324が「オン」状態に戻ると、コンデンサ304Aは充電を開始し、デジタル制御ループ318が再び第1の閾値レベルの到達を検出するまで補助電圧 $V_{AUX}$ が上昇する。図6に示される一実施形態では、 $V_{DD,x}$ は、ダイオード642及び644(図6に示されるような)によって、出力ノード306における電源電圧 $V_{DD,H}$ 及びトランジスタ324のソース電圧 $V_{SRC}$ のより大きい方から選択される。

### 【0036】

[0043] 上記のようなトランジスタ324による回路300の動作は、トランジスタ324が、トランジスタ324の動作のアクティブ領域においてではなく、「オン」状態又は「オフ」状態のスイッチモードで動作することをもたらす。スイッチとしてトランジスタ324を動作させることは、トランジスタ324による電力損失を最小限に抑え、及びその結果、トランジスタ324のサイズが減少することを可能にする。トランジスタ324のサイズは、回路300によって占有される空間の大部分を表す。従って、トランジスタ324のサイズの減少は、回路300のサイズ及び集積回路(IC)として回路300を製造するコストの大幅な減少を可能にする。

### 【0037】

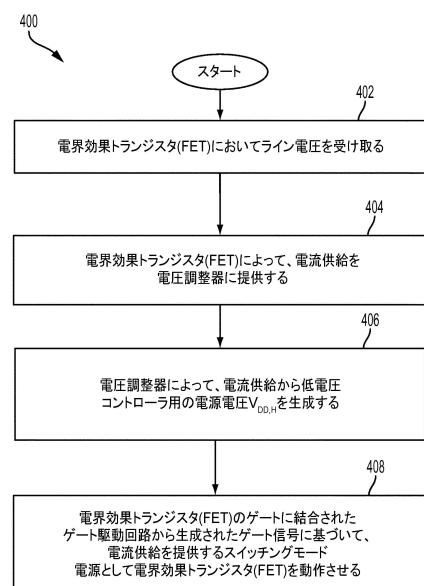

[0044] 上記のように、トランジスタ324は、電源電圧 $V_{DD,H}$ を生成するためにスイッチングモードで動作される。図4は、本開示の一実施形態による、コントローラ電源電圧を生成するためのスイッチングモード電源を動作させる方法を示す例示的フローチャートである。方法400は、ブロック402において、パワーFETでライン電圧を受け取ることで開始する。ブロック404では、電流供給が、パワーFETによって電圧調整器に提供される。ブロック406では、電源電圧 $V_{DD,H}$ が、ブロック404の電流供給から電圧調整器によって生成される。電源電圧 $V_{DD,H}$ は、低電圧コントローラIC用の電源電圧でもよい。ブロック408では、パワーFETのゲートに結合されたゲート駆動回路は、電流供給を電圧調整器に提供するスイッチングモード電源としてパワーFETを動作させることができる。ブロック408は、例えば、 $V_{DD,H}$ 出力ノードに結

10

20

30

40

50

合されたコンデンサにおいて電荷を増加させるためにパワーFETをオンにすること、及びコンデンサにおいて電荷を減少させるためにパワーFETをオフにすることを含む。コンデンサの電荷レベルの変動は、 $V_{DD, H}$ 電圧の比例上昇又は低下をもたらす。従って、パワーFETのスイッチングモード動作は、LEDベース電球のスタートアップ中に、 $V_{DD, H}$ 電圧の電圧レベルをゲート駆動回路が調整することを可能にすることができる。 $V_{DD, H}$ 電圧の変動は、電圧調整器によって及びパワーFETのスイッチングのタイミングを計ることによって減少させることができる。

#### 【0038】

[0045] スタートアップ機能の提供に加えて、トランジスタ324は、調光器互換性を提供するために使用される。図5は、本開示の一実施形態による、調光器互換性を提供するようにスタートアップ回路の動作をデジタル的に制御する方法を示す例示的フローチャートである。方法500のブロック502、504、及び506は、方法400のブロック402、404、及び406と同様でもよい。即ち、ブロック502では、パワーFETにおいてライン電圧が受け取られ得、ブロック504では、電流供給がパワーFETによって電圧調整器に提供され得、及びブロック506では、電流供給から電源電圧 $V_{DD, H}$ が電圧調整器によって生成される。ゲート駆動回路からのパワーFETの動作の制御は、図4のブロック408と比較して、ブロック508では異なる。

10

#### 【0039】

[0046] ブロック508において、パワーFETは、スタートアップ中に、電源電圧 $V_{DD, H}$ を生成するように動作され得、及びLEDベース電球が起動した後に電源電圧 $V_{DD, H}$ を生成することによって、調光器互換性を提供するようにも動作される。一実施形態では、調光器互換性は、調光器の内部時定数が妨げられないように、制御インピーダンスを経由したアースへの経路を設けることによって提供される。例えば、図3及び図6にそれぞれ示されたFET324及び654は、入力ノードにおけるライン電圧 $V_{IN}$ からアースへと制御された量の電流を引き込み得る。抵抗640を経由したアースへのこの経路は、制御インピーダンスを提供することができる。一般的に、LEDベース電球は、オン/オフライツイッチからの動作に限定される。調光器互換性がLEDベース電球に組み込まれる場合、電球は、調光器スイッチで動作して、オフからオンへほぼ連続した動作範囲を可能にすることができる。調光器互換性は、本質的に容量性であるLEDベース電球が、本質的に抵抗性であり、及び常に電流路を提供する従来の電球と共に使用するために設計された、例えば家庭における従来の調光器から動作することを可能にする。しかしながら、従来、そのような調光器互換性は、スタートアップ回路とは別の追加の回路において実現される。

20

#### 【0040】

[0047] ブロック508においてゲート駆動回路は、スタートアップ中及びスタートアップ後に電源電圧 $V_{DD, H}$ を生成するようにパワーFETを制御する。一実施形態では、ゲート駆動回路は、ゲート駆動回路によってパワーFETの動作を修正するために、ホスト制御ICからデジタル入力を受信するように構成される。従って、制御IC内の回路は、スタートアップ中及び調光されたLEDベース電球の動作中、パワーFETを動作させることによって縮小することができる。

30

#### 【0041】

[0048] 図3の回路300は、ホストコントローラICから受信されたデジタル入力によって制御されるように構成される。図6は、本開示の一実施形態による、コントローラ電源電圧を生成するため及び調光器互換性を提供するためのパワーFETのデジタル制御を示す例示的回路図である。トランジスタ(パワーFET)324のゲートは、相補型金属酸化物半導体インバータ(CMOSインバータ)として構成されるトランジスタ632及び634に結合される。デジタル制御ループ318によって生成された制御信号 $V_{CTRL, GATE}$ は、トランジスタ632及び634を制御するためのゲート駆動回路320に提供される。 $V_{CTRL, GATE}$ 制御信号は、 $V_{DD, X}$ とアースとの間で、トランジスタ654の印加ゲート電圧を切り換えることができる。例えば、 $V_{CTRL, GATE}$

40

50

$V_{CTRL, 1}$  信号が高い場合、トランジスタ 632 は、 $V_{DD, X}$  をトランジスタ 654 のゲートに結合するために閉じられることができ、トランジスタ 634 は、トランジスタ 654 のゲートをアースから切り離すために開かれる。別の例では、 $V_{CTRL, GATE}$  信号が低い場合、トランジスタ 632 は、トランジスタ 654 のゲートから  $V_{DD, X}$  を切り離すために開かれることができ、及びトランジスタ 634 は、トランジスタ 324 のゲートをアースに接続するために閉じられ得る。従って、デジタル制御ループ 318 は、ゲート駆動回路 320 によるトランジスタ 324 へのゲート電圧  $V_{GATE}$  の印加を制御することができる。

#### 【0042】

[0049] トランジスタ 324 のゲートパワー FET が  $V_{DD, X}$  に接続されると、トランジスタ 324 は、「オン」状態となることができ、及び電流が入力ノード 302 から抵抗 640 を経由し、トランジスタ 324 を経由し且つブロッキングダイオード 646 を経由して電圧調整器 312 へと流れることができる。更に、電流は、 $V_{AUX}$  コンデンサ 304A に直接流れ得る。電圧調整器 312 は、 $V_{AUX}$  コンデンサ 304A 及び  $V_{DD, H}$  コンデンサ 306A への電流の流れを調整することができる。抵抗 640 は、集積回路包含回路 600 の外側にある。回路 600 では、入力電圧  $V_{IN}$  の大部分は、抵抗 640 を通して低下される。従って、トランジスタ 324 の電力損失を減少させることができる。抵抗 640 の抵抗は、トランジスタ 324 がオンにされた時にトランジスタ 324 を流れる電流を調整するように選択される。電流は、ブロッキングダイオード 646 を経由して電圧調整器 312 に流れる。トランジスタ 612 は、 $V_{AUX}$  及び  $V_{DD, H}$  をそれぞれ生成するように、パワートレイン 314 からコンデンサ 304A 及び 306A へと駆動電流を送る線形調整器として動作することができる。トランジスタ 612 は、ツェナーダイオード 614 によってバイアスをかけられる。

#### 【0043】

[0050]  $V_{CTRL, GATE}$  信号は、デジタル制御ループ 318 のロジックデコード及び制御シーケンスブロック 618 によって生成することができる。制御ループ 318 は、比較器 620、抵抗 622 及び 624、並びに基準電圧  $V_{ref}$  入力ノード 606 も含む。抵抗 622 及び 624 は、抵抗 622 及び 624 の比較抵抗値によって定義される比率に従って、電圧調整器 312 の両端の電圧を分割する。抵抗 624 は、電圧調整器 312 の両端の電圧のごく一部である電圧レベルを比較器 620 に供給するセンス抵抗としても機能することができる。比較器 620 は、抵抗 624 の両端の電圧を基準電圧  $V_{ref}$  と比較することができる。 $V_{ref}$  電圧は、図 3 を参照して上記に説明された第 1 の閾値レベルに一致する。比較器 620 の出力  $V_{CMP}$  は、 $V_{AUX}$  の電圧レベルが第 1 の閾値電圧以上であるか否かに関するフィードバックをロジックブロック 618 に提供する。ロジックブロック 618 は、 $V_{CMP}$  フィードバックに基づいて、トランジスタ 324 をオン及びオフにするために、高と低とで  $V_{CTRL, GATE}$  信号を切り換えることができる。例えば、 $V_{AUX}$  信号が第 1 の閾値レベルに達したことを  $V_{CMP}$  が示すと、トランジスタ 324 をオフにするために、 $V_{CTRL, GATE}$  信号を切り換えることができる。ロジックブロック 618 は、トランジスタ 654 をオフにするために、トランジスタ 654 のゲートをアースに切り換えるように、高と低とで  $V_{CTRL, GND}$  信号を切り換えることもできる。

#### 【0044】

[0051] ロジックブロック 618 は、モード入力ノード 602 及び 604 において、デジタル制御入力  $V_{CTRL, 1}$  及び  $V_{CTRL, 2}$  を受信することもできる。 $V_{CTRL, 1}$  及び  $V_{CTRL, 2}$  入力は、調光器互換性を提供するようにトランジスタ 324 を制御するためのフィードバックとしてホストコントローラ IC によって提供される。一実施形態では、プルダウン抵抗（不図示）は、ロジックブロック 618 をデフォルト設定によりスタートアップ用のモード 0 に設定するために、入力ノード 602 及び 604 並びにアースに結合される。ロジックブロック 618 は、表 1 に記載される制御に基づく  $V_{CTRL, 1}$  及び  $V_{CTRL, 2}$  入力に基づいて、回路 600 を制御することができる。

10

20

30

40

50

【0045】

【表1】

| モード                    | $V_{CTRL,1}$ | $V_{CTRL,2}$ | $V_{CMP}$ | パワー<br>FET 324 | パワー<br>FET 654 |

|------------------------|--------------|--------------|-----------|----------------|----------------|

| 0 (HVS)                | 0            | 0            | 0         | オン             | オフ             |

|                        | 0            | 0            | 1         | オフ             | オフ             |

| 1 (オフ)                 | 0            | 1            | X         | オフ             | オフ             |

| 2 (ブリードーアース)           | 1            | 0            | X         | オン             | オン             |

| 3 (ブリードー補助電圧又は<br>アース) | 1            | 1            | 0         | オン             | オフ             |

|                        | 1            | 1            | 1         | オン             | オン             |

表1. 本開示の一実施形態による、回路600を制御するための制御信号及び調光器互換性のために生じる回路600の動作。

【0046】

[0052] 表1に記載される4つのモードは、調光器互換性を提供するためのトランジスタ324を備えた回路600の構成を可能にすることができる。 $V_{CTRL,1}$ 及び $V_{CTRL,2}$ 入力における低信号によって示されるモード0は、図3を参照して上記に記載されたのと同様の動作を有するスタートアップモードでもよい。モード0では、トランジスタ654は、オフにされ、トランジスタ324は、比較器620の出力に基づいてオン及びオフが切り換えられる。トランジスタ324は、高信号を出力することによって $V_{AUX}$ が第1の閾値レベルを超えることを比較器620が示す場合にオフにされる。トランジスタ324は、低信号を出力することによって $V_{AUX}$ が第1の閾値レベルを下回ることを比較器620が示す場合にオンにされる。低 $V_{CTRL,1}$ 及び高 $V_{CTRL,2}$ 信号によって示されるモード1では、トランジスタ324及び654は、オフにされる。モード2では、電荷がラインからアースへと導通される。モード2は、高 $V_{CTRL,1}$ 及び低 $V_{CTRL,2}$ 信号によって示される。モード2では、トランジスタ324及び654は共に、比較器620の出力とは無関係にオンにされる。モード3では、トランジスタ324は、常にオンでもよく、比較器620の出力は、電荷をコンデンサ304A又はアースに移動させるかを決定する。比較器620の出力が、 $V_{AUX}$ が第1の閾値レベルに達したことを示す高である場合に、トランジスタ654は、アースに電流を放出するためにオンにされる。比較器620の出力が、 $V_{AUX}$ が第1の閾値レベルを下回ることを示す低である場合に、トランジスタ654は、コンデンサ304Aに電流を放出するためにオフにされる。モード3は、ホストコントローラICが低過ぎる電源電圧 $V_{DD,H}$ によって正常に動作しなくなる前に、ホストコントローラICが低電源電圧 $V_{DD,H}$ から回復することを可能にできる。

【0047】

[0053] 図6の回路600を動作させる一方法の例示は、図7に示される信号を用いて示される。図7は、本開示の一実施形態による、LEDベース電球においてスタートアップ及び調光器互換性を提供するための図6の回路の動作を示す例示的グラフを含む。時点732において、回路600は、 $V_{CTRL,1}$ 712及び $V_{CTRL,2}$ 714が低いスタートアップモード722に入る。入力電圧702は、調光器によって生成される立ち上がり(LE: leading edge)ライン電圧を示す。スタートアップモード722では、トランジスタ324のゲートがトランジスタ324のソースに結合される。従って、電圧 $V_{GATE,706}$ 及び電圧 $V_{SRC,708}$ が共に上昇する。トランジスタ324を流れる電

流  $I_{FET}$  は、ライン 704 に示され、及びトランジスタ 324 がオンの間、ラインの入力電圧  $V_{IN}$  702 に追従する。補助電圧  $V_{AUX}$  及び電源電圧  $V_{DD, H}$  は、コンデンサ 304A 及び 306A が電流  $I_{FET}$  から充電されるにつれて上昇する。時点 734 では、ライン 710 の比較器 620 の出力  $V_{CMP}$  は、補助電圧  $V_{AUX}$  716 が第1の閾値 752 に達すると高に切り換わる。ロジックブロック 618 は、次に、トランジスタ 324 をオフにするために、 $V_{GATE}$  706 をアースに切り換える。補助電圧  $V_{AUX}$  716 は、次に、時点 734 の後、コンデンサ 304A が放電するにつれて低下する。ライン 718 における電源電圧  $V_{DD, H}$  は、スタートアップモード 722 の開始後、比較的一定に維持される。

## 【0048】

10

[0054] スタートアップモード 722 の後、ロジックブロック 618 は、調光器互換性を提供するためにホストコントローラ IC から  $V_{CTRL, 1}$  及び  $V_{CTRL, 2}$  に関するモード入力を受信し、これは、LED ベース電球の通常動作中、回路 600 が電源電圧  $V_{DD, H}$  718 を供給し続けることを可能にすることができる。時点 736 では、ホストコントローラ IC は、高  $V_{CTRL, 1}$  712 及び低  $V_{CTRL, 2}$  714 信号を生成することによって、ブリード - アースモード 724 を示す。時点 736 の後、トランジスタ 324 及び 654 はオンにされ、且つ電流が入力ノード 302 からアースへと放出される。時点 738 では、ホストコントローラ IC は、低  $V_{CTRL, 1}$  712 及び低  $V_{CTRL, 2}$  714 信号を生成することによって、スタートアップモード 726 を示す。時点 738 の後、トランジスタ 324 はオンにされ、トランジスタ 654 はオフにされ、及び電流は、コンデンサ 304A を充電するために再び電圧調整器 312 に供給される。時点 738A では、ライン 710 の比較器 620 の出力  $V_{CMP}$  は、補助電圧  $V_{AUX}$  が第1の閾値レベル 752 に達したことを示す高に切り換わる。ロジックブロック 618 は、次に、トランジスタ 324 をオフにし、コンデンサ 304A は、再び放電を開始する。時点 740 では、ホストコントローラ IC は、低  $V_{CTRL, 1}$  信号 712 及び高  $V_{CTRL, 2}$  信号 714 を生成することによって、オフモード 728 を示す。ロジックブロック 618 は、オフモード 728 においてトランジスタ 324 及び 654 をオフにする。ホストコントローラ IC は、LED ベース電球の通常動作の間、モード 724、726、及び 728 を周期的に繰り返し続ける。ホストコントローラ IC が周期的に繰り返し続けるため、各モードのタイミング持続時間は、 $V_{DD, H}$  の所望の電圧レベルを維持するために必要に応じて入力電圧 702 の周期によって変動する。

20

## 【0049】

30

[0055] 上記のスタートアップ回路は、調光器互換性を照明デバイスに提供するために、調光器回路に組み込むことができる。図 8 は、本開示の一実施形態による、デジタル制御スイッチモードスタートアップ回路を備えた発光ダイオード (LED) ベース電球用の調光器システムを示す例示的ブロック図である。システム 800 は、可変抵抗デバイス 808a 及び制御集積回路 (IC) 808b を備えた調光器互換性回路 808 を含む。調光器互換性回路 808 は、調光器 804 及び整流器 806 を有する入力段を、発光ダイオード (LED) を含む出力段 810 と結合させる。システム 800 は、交流 (AC : alternating current) 電源ライン 802 から入力を受け取り得る。出力段 810 は、上記のようなスタートアップ回路を備えた電力段を含む。例えば、出力段 810 は、図 3 及び / 又は図 6 を参照して上記に説明されたデジタル制御スタートアップ回路を含む。

40

## 【0050】

[0056] フームウェア及び / 又はソフトウェアにおいて実施される場合、図 4 及び図 5 を参照して記載された機能性等の上記の機能は、コンピュータ可読媒体上に 1つ又は複数の命令又はコードとして保存される。例は、データ構造を用いてコード化された非一時的コンピュータ可読媒体及びコンピュータプログラムを用いてコード化されたコンピュータ可読媒体を含む。コンピュータ可読媒体は、物理的コンピュータストレージ媒体を含む。ストレージ媒体は、コンピュータによってアクセスされることが可能な任意の利用可能な媒体でよい。限定ではなく、一例として、このようなコンピュータ可読媒体は、ランダ

50

ムアクセスメモリ (RAM : random access memory) 、読み取り専用メモリ (ROM : read-only memory) 、電気的消去書き込み可能ROM (EEPROM : electrically erasable programmable read-only memory) 、コンパクトディスク読み取り専用メモリ (CD-ROM : compact disc-read memory) 、又は他の光ディスクストレージ、磁気ディスクストレージ若しくは他の磁気ストレージデバイス、又は命令若しくはデータ構造の形式の所望のプログラムコードを保存するために使用することができ、及びコンピュータによってアクセスすることができる任意の他の媒体を含む。ディスク (disk) 及びディスク (disc) は、コンパクトディスク (CD : compact disc) 、レーザーディスク (登録商標) 、光ディスク、デジタル多用途ディスク (DVD : digital versatile disc) 、フロッピーディスク及びブルーレイディスクを含む。一般的に、ディスク (disk) は、データを磁気的に再生し、及びディスク (disc) は、データを光学的に再生する。上記の組み合わせもコンピュータ可読媒体の範囲内に含まれるものとする。

【0051】

[0057] コンピュータ可読媒体への保存に加えて、命令及び / 又はデータは、通信装置に含まれる伝送媒体上の信号として提供される。例えば、通信装置は、命令及びデータを表す信号を有する送受信器を含む。命令及びデータは、1つ又は複数のプロセッサにクレームに概要が示される機能を実施させるように構成される。

【0052】

[0058] 本開示及び特定の代表的利点を詳細に説明したが、添付の特許請求の範囲によつて定義される本開示の趣旨及び範囲から逸脱することなく、様々な変更、置換、及び修正を本明細書において行うことができることを理解されたい。例えば、コントローラによつて生成される信号は、全体を通して、「高」又は「低」として記載されるが、信号は、「低」信号がスイッチをオンにする及び「高」信号がスイッチをオフにするように反転される。また、本出願の範囲は、本明細書に記載されたプロセス、機械、製品、組成物、手段、方法及びステップの特定の実施形態に限定されるものではない。当業者が本開示から容易に理解する様に、本明細書に記載された対応する実施形態と実質的に同じ機能を行う又は実質的に同じ結果を得る、既存の又は後に開発されるプロセス、機械、製品、組成物、手段、方法、又はステップが利用される。従つて、添付の特許請求の範囲は、その範囲に、そのようなプロセス、機械、製品、組成物、手段、方法、又はステップを包含するものとする。

10

20

30

【図1】

図1

先行技術

【図2】

図2

先行技術

【図3】

図3

【図4】

図4

【図5】

5

【図6】

6

〔 7 〕

义 7

〔 8 〕

8

---

フロントページの続き

(72)発明者 メンツェ エリック ジェイ .

アメリカ合衆国 78703 テキサス州 オースティン ナンバー4 ウォーターストン アベ

ニュー 1816

(72)発明者 トムソン カール

アメリカ合衆国 78109 テキサス州 コンバース オータム ダウン 9934

審査官 柳下 勝幸

(56)参考文献 特開2006-115611(JP, A)

特開2012-109211(JP, A)

実開平04-055610(JP, U)

特表2013-509683(JP, A)

(58)調査した分野(Int.Cl., DB名)

H02M 3/155

H05B 45/00