WO 2013/023656 A2

(12) NACH DEM VERTRAG ÜBER DIE INTERNATIONALE ZUSAMMENARBEIT AUF DEM GEBIET DES

PATENTWESENS (PCT) VERÖFFENTLICHTE INTERNATIONALE ANMELDUNG

(19) Weltorganisation für geistiges

Eigentum

Internationales Büro

(43) Internationales

Veröffentlichungsdatum

21. Februar 2013 (21.02.2013)

(10) Internationale Veröffentlichungsnummer

**WO 2013/023656 A2**

- (51) Internationale Patentklassifikation: Nicht klassifiziert

- (21) Internationales Aktenzeichen: PCT/DE2012/200054

- (22) Internationales Anmeldedatum: 16. August 2012 (16.08.2012)

- (25) Einreichungssprache: Deutsch

- (26) Veröffentlichungssprache: Deutsch

- (30) Angaben zur Priorität:

10 2011 052 764.8

16. August 2011 (16.08.2011) DE

- (71) Anmelder (für alle Bestimmungsstaaten mit Ausnahme von US): SILICON LINE GMBH [DE/DE]; Elsenheimerstr. 48 / II, 80687 München (DE).

- (72) Erfinder; und

- (75) Erfinder/Anmelder (nur für US): BLON, Thomas [DE/DE]; c/o Silicon Line GmbH, Elsenheimerstr. 48 / II, 80687 München (DE). JANSEN, Florian [DE/DE]; c/o Silicon Line GmbH, Elsenheimerstr. 48 / II, 80687 München (DE). HOELTKE, Holger [DE/DE]; Am Blütenanger 54C, 80995 München (DE).

- (74) Anwälte: HOFMANN, Andreas et al.; Sendlinger Str. 2 / III, 80331 München, P.O. Box/Postfach 330211, 80062 München (DE).

- (81) Bestimmungsstaaten (soweit nicht anders angegeben, für jede verfügbare nationale Schutzrechtsart): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

- (84) Bestimmungsstaaten (soweit nicht anders angegeben, für jede verfügbare regionale Schutzrechtsart): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, SZ, TZ, UG, ZM, ZW), eurasisches (AM, AZ, BY, KG, KZ, RU, TJ, TM), europäisches (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE,

[Fortsetzung auf der nächsten Seite]

(54) Title: CIRCUIT ARRANGEMENT AND METHOD FOR TRANSMITTING SIGNALS

(54) Bezeichnung : SCHALTUNGSANORDNUNG UND VERFAHREN ZUM ÜBERTRAGEN VON SIGNALEN

**Fig. 1A**

(57) Abstract: The invention relates to a circuit arrangement (S, E) and to a corresponding method, using single-ended signals based on logic levels and differential, in particular common mode based signals, in which it is possible to further reduce the size of tools, which are associated with said type of circuit arrangement (S, E) and said type of method.

(57) Zusammenfassung: Es werden auf Basis von single-ended, auf Logikpegeln basierenden Signalen sowie von differentiellen, insbesondere auf common mode basierenden, Signalen eine Schaltungsanordnung (S, E) sowie ein entsprechendes Verfahren vorgeschlagen, bei denen eine weitere Miniaturisierung von Gerätschaften, denen eine derartige Schaltungsanordnung (S, E) sowie ein derartiges Verfahren zugeordnet sind, ermöglicht wird.

# WO 2013/023656 A2

SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA,

GN, GQ, GW, ML, MR, NE, SN, TD, TG).

## Veröffentlicht:

- ohne internationalen Recherchenbericht und erneut zu veröffentlichten nach Erhalt des Berichts (Regel 48 Absatz 2 Buchstabe g)

**SCHALTUNGSAORDNUNG UND VERFAHREN ZUM UEBERTRAGEN VON SIGNALEN****Technisches Gebiet**

Die vorliegende Erfindung betrifft eine Schaltungsanordnung gemäß dem Oberbegriff des Anspruchs 1 sowie ein Verfahren gemäß dem Oberbegriff des Anspruchs 13.

5

**Stand der Technik, insbesondere dessen Nachteile und technische Probleme**

Die Bitübertragungsschicht oder physikalische Schicht (PHY) ist die unterste Schicht im O[pen]S[ystems]I[nterconnection]-Schichtenmodell, das auch OSI-Referenzmodell genannt wird und ein Schichtenmodell der Internationalen Organisation für Normung (ISO) bezeichnet, das wiederum als Designgrundlage von Kommunikationsprotokollen in Rechnernetzen dient.

Die Physical Layer (PHY) ist für Combining, F[orward]Error C[orrection], Modulation, Power Control, Spreading (C[ode]D[ivision]M[ultiple]A[ccess]) und dergleichen zuständig und kennt weder Daten noch Anwendungen, sondern nur Nullen und Einsen. PHY stellt der darüber liegenden Sicherungsschicht (D[ata]L[inke]L[ayer]), insbesondere einer Teilschicht namens M[edia]A[ccess]C[ontrol]-Layer, logische Kanäle zur Verfügung (Transportkanäle bei U[niversal]M[obile]T[elecommunications]S[ystem]).

20 D-PHY ermöglicht grundsätzlich eine flexible, kostengünstige und schnelle serielle Schnittstelle für Kommunikationsverbindungen zwischen Komponenten innerhalb einer mobilen Vorrichtung.

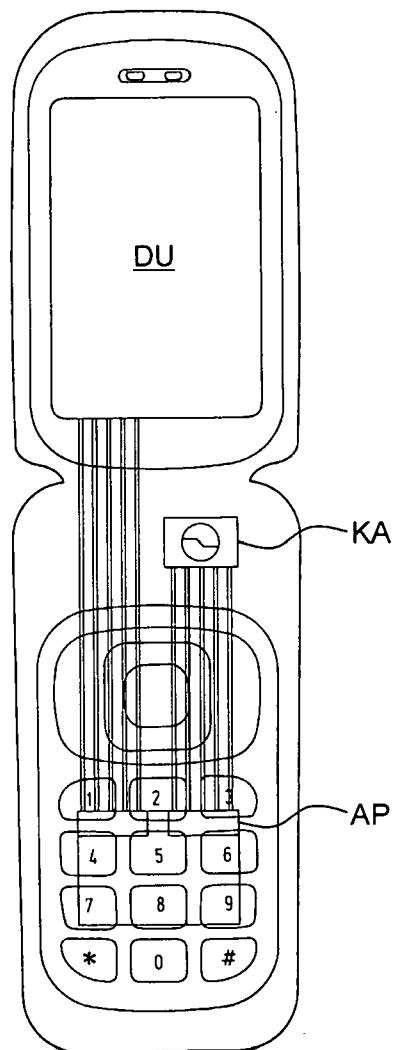

Wie anhand Fig. 3A veranschaulicht, stellt in modernen Mobiltelefonen eine Datenquelle, zum Beispiel ein Applikationsprozessor, am M[obile]I[ndustry]P[rocessor]I[nterface]-D[isplay]S[erial]I[nterface] Bilddaten als D-PHY-Signale für die Darstellung an einer angeschlossenen Datensenke, zum Beispiel an einem angeschlossenen Display, zur Verfügung. Auch kann eine Datensenke, zum Beispiel ein Applikationsprozessor, über ein MIPI-C[amera]S[erial]I[nterface] Bilddaten von einer angeschlossenen Datenquelle, zum Beispiel von einer angeschlossenen Kamera, im D-PHY-Format empfangen.

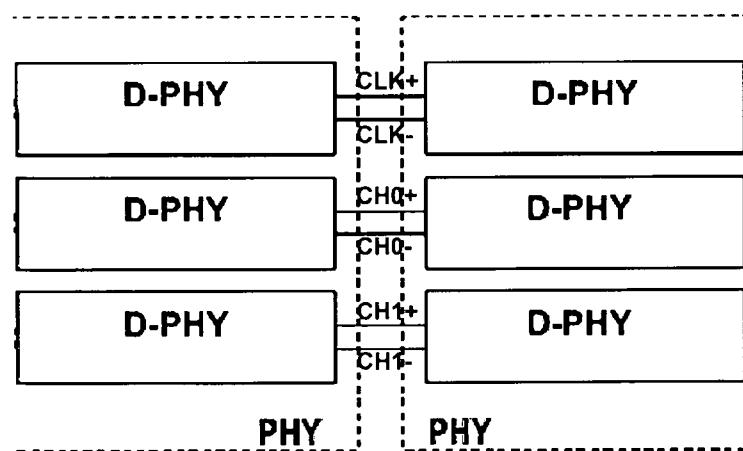

35 Ein auf dem D-PHY-Protokoll basierendes DSI oder DSI-2 oder CSI oder CSI-2 oder CSI-3 umfasst bis zu vier differentielle Datenleitungen und eine differentielle Takteleitung, die den Applikationsprozessor elektrisch mittels Kupferkabel mit dem Display und/oder mit der Kamera verbinden. Die Datenrate pro differentieller Datenleitung beträgt bis zu 1,5 Gbps (Gigabit pro Sekunde).

Dieses konventionelle Versenden und Empfangen der D-PHY-DSI- oder D-PHY-CSI-Signale über ein bis vier differentielle Datensignale und eine differentielle Takteleitung ist in der D-PHY-Schnittstellenkonfiguration der Fig. 3B anhand zweier Datenkanäle (= sogenannte data lanes CH0+, CH0- und CH1+, CH1-) und einer Takteleitung (= sogenannte clock lane CLK+, CLK-) zwischen den Modulen der Master-Seite (= Datenquelle, zum Beispiel Kamera und/oder Applikationsprozessor) und den Modulen der Slave-Seite (= Datensenke, zum Beispiel Applikationsprozessor und/oder Anzeigeeinheit) exemplarisch veranschaulicht.

Wie in diesem Zusammenhang aus Fig. 3A ersichtlich ist, werden pro angeschlossenem Display oder pro angeschlossener Kamera bis zu zehn Kupferleitungen zur Datenübertragung benötigt (zum Beispiel viermal zwei Datenleitungen und einmal zwei Takteleitungen).

Mit zunehmender Auflösung von Displays und Kameras steigen auch die Datenraten vom Applikationsprozessor zum Display bzw. von der Kamera zum Applikationsprozessor. Die hierbei während der Datenübertragung erzeugten hochfrequenten elektromagnetischen Felder stören die empfindlichen benachbarten Empfänger von hochfrequenten Nutzsignalen, wie zum Beispiel den Bluetooth-, G[lobal]P[ositioning]S[ystem]-, U[niversal]M[obile]T[elecommunications]S[ystem]- oder Wi-Fi-Empfänger, und beeinträchtigen damit deren Funktion erheblich.

Umfangreiche und somit kostenaufwändige Abschirmmaßnahmen an den Übertragungskabeln sind notwendig, um einen störungsfreien Betrieb der vorgenannten Empfänger sicherzustellen.

Mit zunehmender Anzahl an Displays und an Kameras in modernen Mobiltelefonen oder vergleichbaren Geräten können die Kabelbaumgrößen in derartigen Geräten leicht auf bis zu sechzig Leitungen ansteigen, die nur für die Übertragung von Bilddaten benötigt werden. Diese Kabelbaumgrößen verhindern nachteiligerweise eine weitere Miniaturisierung derartiger Geräte.

### **Darstellung der vorliegenden Erfindung: Aufgabe, Lösung, Vorteile**

Ausgehend von den vorstehend dargelegten Nachteilen und Unzulänglichkeiten sowie unter Würdigung des umrissten Standes der Technik liegt der vorliegenden Erfindung die Aufgabe zugrunde, eine Schaltungsanordnung der eingangs genannten Art sowie ein Verfahren der eingangs genannten Art so weiterzuentwickeln, dass eine weitere

Miniaturisierung von Gerätschaften, denen eine derartige Schaltungsanordnung sowie ein derartiges Verfahren zugeordnet sind, ermöglicht wird.

Diese Aufgabe wird durch eine Schaltungsanordnung mit den Merkmalen des Anspruchs 1 sowie durch ein Verfahren mit den Merkmalen des Anspruchs 13 gelöst. Vorteilhafte Ausgestaltungen und zweckmäßige Weiterbildungen der vorliegenden Erfindung sind in den jeweiligen Unteransprüchen gekennzeichnet.

Erfindungsgemäß wird also zum einen eine Sendeanordnung vorgeschlagen, mittels derer

- die single-ended, auf Logikpegeln basierenden Signalen entsprechenden H[igh]S[peed]-Daten und

- die differentiellen, insbesondere auf common mode basierenden, Signalen entsprechenden L[ow]P[ower]-Daten

zu einem gemeinsamen Signalstrom serialisiert werden.

Des Weiteren wird erfindungsgemäß eine Empfangsanordnung vorgeschlagen, mittels derer dieser gemeinsame Signalstrom wieder

- in die single-ended, auf Logikpegeln basierenden Signalen entsprechenden H[igh]S[peed]-Daten und

- die differentiellen, insbesondere auf common mode basierenden, Signalen entsprechenden L[ow]P[ower]-Daten

deserialisiert werden.

Hierbei können die verschiedenen Signale für den zwischen der Sendeanordnung und der Empfangsanordnung erfolgenden Transport über mindestens ein optisches Medium, insbesondere über mindestens einen optischen Wellenleiter, zum Beispiel über mindestens eine Glasfaser und/oder über mindestens eine Plastikfaser, zum gemeinsamen Signalstrom aufbereitet, insbesondere sendeseitig gebündelt oder serialisiert und empfangsseitig entbündelt oder deserialisiert, werden.

In einer bevorzugten Weiterbildung der vorliegenden Erfindung können unter Berücksichtigung der Besonderheiten des D-PHY-Protokolls auf Seiten der Sendeanordnung mindestens eine, insbesondere bis zu vier, differentielle Datenleitungen und mindestens eine, insbesondere genau eine, differentielle Taktleitung des D[isplay]S[erial]I[nterface], auch in der Spezifikation DSI-2, und/oder des C[amera]S[erial]I[nterface], auch in den Spezifikationen CSI-2 und/oder CSI-3, serialisiert werden, insbesondere durch Serialisieren der differentiellen Datenleitungen und der differentiellen Taktleitung des

D[isplay]S[erial]I[nterface] und/oder des C[amera]S[erial]I[nterface].

In entsprechend bevorzugter Weiterbildung der vorliegenden Erfindung kann unter Berücksichtigung der Besonderheiten des D-PHY-Protokolls ein gemäß vorstehend dargelegter Sendeanordnung gebündelter oder serialisierter gemeinsamer Signalstrom auf Seiten der Empfangsanordnung aufgenommen werden, um daraus die mindestens eine, insbesondere die bis zu vier, differentiellen Datenleitungen und die mindestens eine, insbesondere die genau eine, differentielle Taktleitung für das DSI, auch in der Spezifikation DSI-2, und/oder für das CSI, auch in den Spezifikationen CSI-2 und/oder CSI-3, zurückzugewinnen, insbesondere durch Entbündeln.

Im Ergebnis bietet die vorliegende Erfindung eine Möglichkeit,

- single-ended, auf Logikpegeln basierende Daten- und Taktsignale und

- differentielle, insbesondere auf common mode basierende, Daten- und Taktsignale

gemeinsam optisch zu übertragen, insbesondere in der Ausgestaltung als D-PHY-Signale, und hierbei zum Beispiel in der Ausgestaltung als MIPI-D-PHY-Signale.

Durch die optische Übertragung werden keine hochfrequenten elektromagnetischen Felder erzeugt, die empfindliche benachbarte Empfänger von hochfrequenten Nutzsignalen, wie zum Beispiel Bluetooth-, G[lobal]P[ositioning]S[ytem]-, U[niversal]M[obile]T[elecommunications]S[ytem]- oder Wi-Fi-Empfänger stören könnten. Damit wird deren Funktion auch nicht beeinträchtigt.

Vorteilhafterweise entfallen also umfangreiche, kostenaufwändige Abschirmungsmaßnahmen an den Übertragungsmedien. Die Anzahl an Übertragungskanälen kann auf einen optischen Wellenleiter pro Display und/oder pro Kamera reduziert werden.

Exemplarisch lässt sich die vorliegende Erfindung beim gleichzeitigen seriellen und/oder gebündelten, insbesondere CSI-protokollbasierten und/oder CSI-2-protokollbasierten und/oder CSI-3-protokollbasierten und/oder DSI-protokollbasierten und/oder DSI-2-protokollbasierten, Übertragen sowohl von single-ended, auf Logikpegeln basierenden Daten- und Taktignalen als auch von differentiellen, insbesondere auf common mode basierenden, Daten- und Taktignalen, insbesondere von D-PHY-Datensignalen und D-PHY-Taktsignalen, zum Beispiel von bis zu vier Bit breiten MIPI-D-PHY-Datensignalen und MIPI-D-PHY-Taktsignalen, zwischen mindestens einer Datenquelle, insbesondere mindestens einer, zum Beispiel hochauflösenden und/oder zum Beispiel als Bildquelle fungierenden,

Kamera und/oder mindestens einem Applikationsprozessor, und mindestens einer Datensenke, insbesondere mindestens einem Applikationsprozessor und/oder mindestens einer, zum Beispiel hochauflösenden und/oder zum Beispiel als Bildsenke fungierenden, Anzeigeeinheit, zum Beispiel mindestens einem Display oder mindestens einem Monitor,

5 anwenden.

### **Kurze Beschreibung der Zeichnungen**

Wie bereits vorstehend erörtert, gibt es verschiedene Möglichkeiten, die Lehre der vorliegenden Erfindung in vorteilhafter Weise auszugestalten und weiterzubilden. Hierzu wird einerseits auf die dem Anspruch 1 sowie dem Anspruch 13 nachgeordneten Ansprüche verwiesen, andererseits werden weitere Ausgestaltungen, Merkmale und Vorteile der vorliegenden Erfindung nachstehend unter Anderem anhand der durch Fig. 1A bis Fig. 2B veranschaulichten Ausführungsbeispiele näher erläutert.

15 Es zeigt:

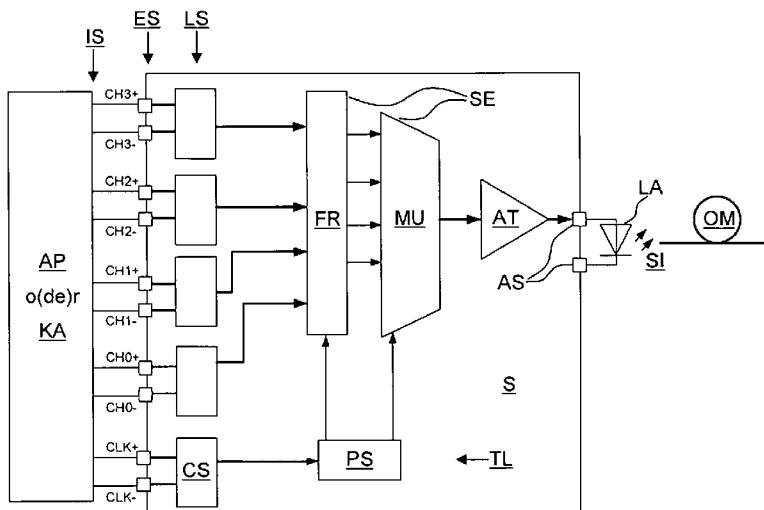

Fig. 1A in konzeptuell-schematischer Darstellung ein Ausführungsbeispiel des ersten Teils, nämlich der gemäß der vorliegenden Erfindung ausgebildeten Sendeanordnung einer Schaltungsanordnung, die nach dem Verfahren gemäß der vorliegenden Erfindung arbeitet;

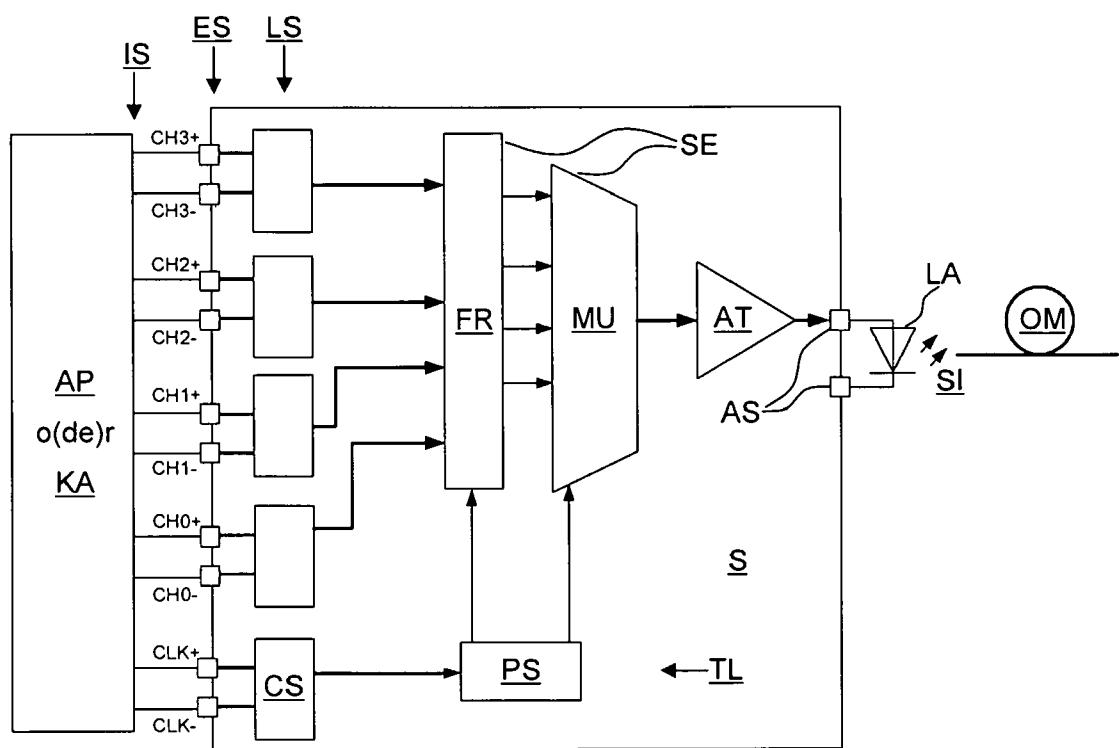

20 Fig. 1B in konzeptuell-schematischer Detaildarstellung ein Ausführungsbeispiel des Framers der Sendeanordnung aus Fig. 1A;

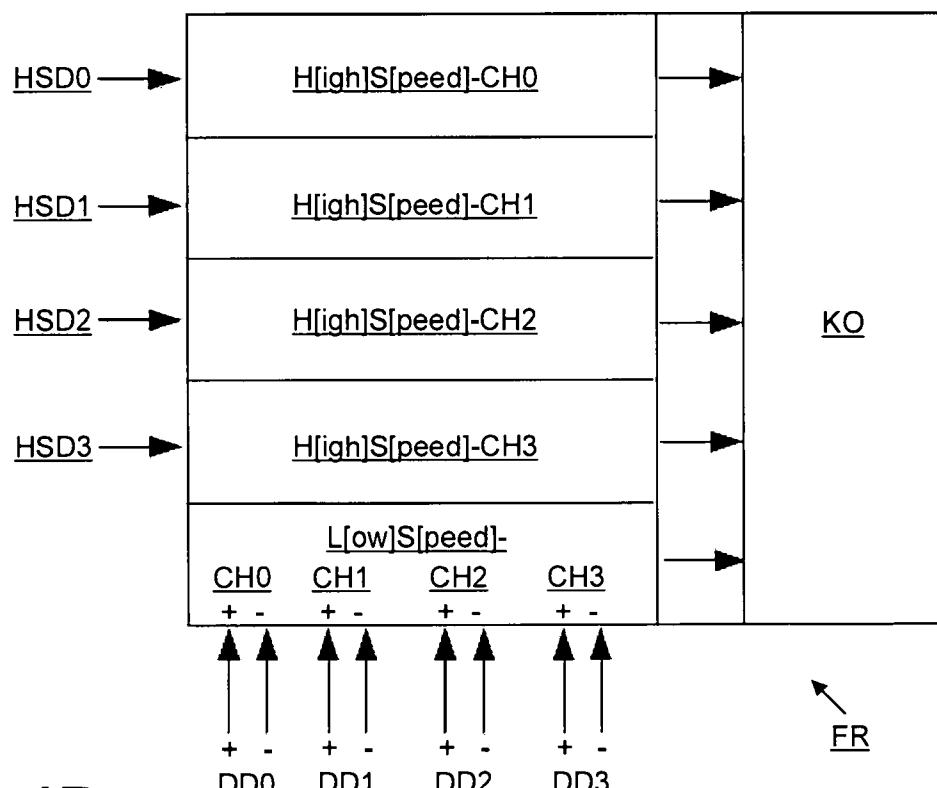

25 Fig. 2A in konzeptuell-schematischer Darstellung ein Ausführungsbeispiel des zweiten Teils, nämlich der gemäß der vorliegenden Erfindung ausgebildeten Empfangsanordnung einer Schaltungsanordnung, die nach dem Verfahren gemäß der vorliegenden Erfindung arbeitet;

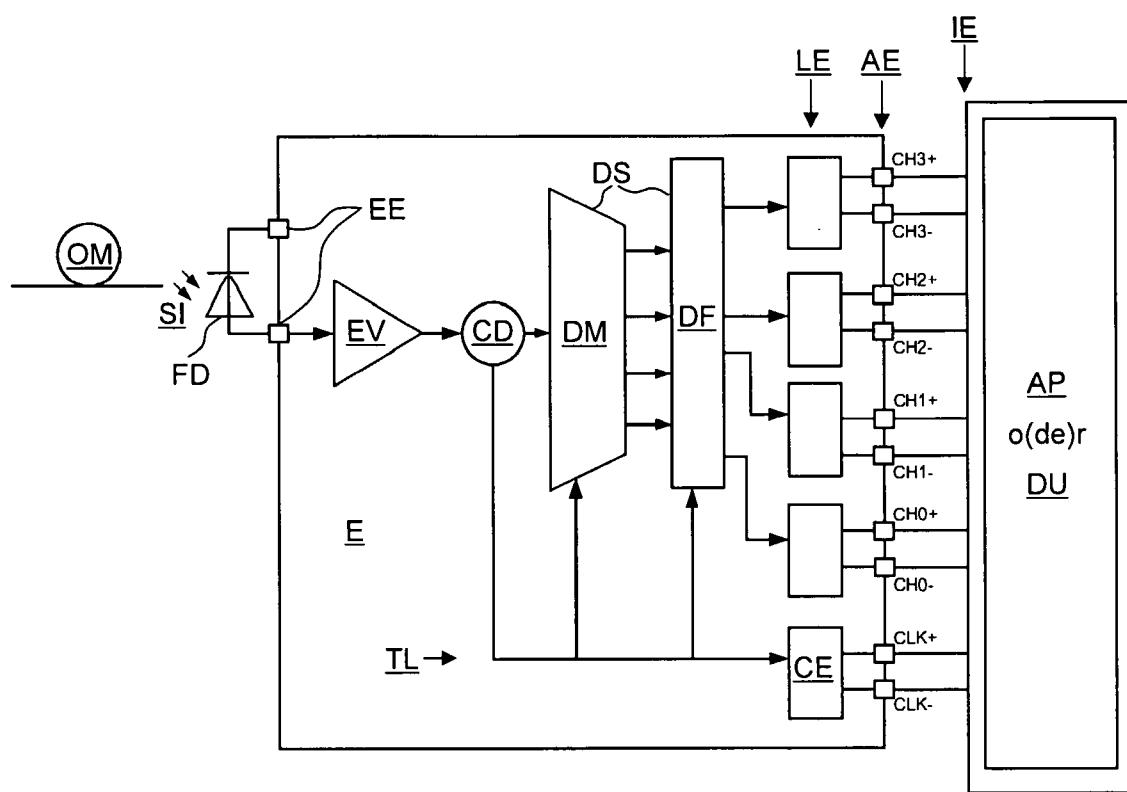

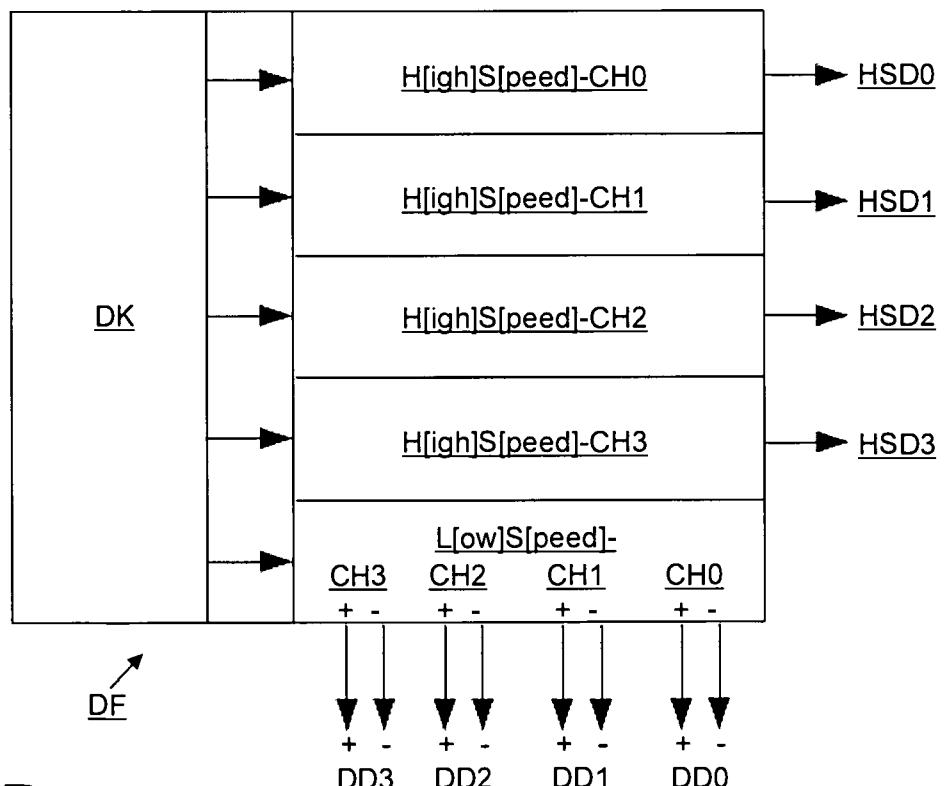

30 Fig. 2B in konzeptuell-schematischer Detaildarstellung ein Ausführungsbeispiel des Deframers der Empfangsanordnung aus Fig. 2A;

35 Fig. 3A in konzeptuell-schematischer Darstellung ein Beispiel einer Anordnung aus dem Stand der Technik; und

Fig. 3B in konzeptuell-schematischer Darstellung ein Beispiel einer der Anordnung aus

Fig. 3A zugrunde liegenden Schnittstellenkonfiguration mit zwei Datenkanälen und mit einer Takteleitung.

5 Gleiche oder ähnliche Ausgestaltungen, Elemente oder Merkmale sind in Fig. 1A bis Fig. 3B mit identischen Bezugszeichen versehen.

### Bester Weg zur Ausführung der vorliegenden Erfindung

- Mittels des anhand Fig. 1A veranschaulichten Ausführungsbeispiels einer Sendeanordnung S gemäß der vorliegenden Erfindung und

- mittels des anhand Fig. 2A veranschaulichten Ausführungsbeispiels einer Empfangsanordnung E gemäß der vorliegenden Erfindung,

durch die zusammen ein Ausführungsbeispiel einer Schaltungsanordnung S, E (vgl. Fig. 1A, Fig. 2A) gemäß der vorliegenden Erfindung gebildet wird (im Rahmen der vorliegenden Erfindung ist es möglich, die Sendeanordnung S und die Empfangsanordnung E unabhängig voneinander zu realisieren und zu betreiben), ist es grundsätzlich möglich, eine kabelbasierte Verbindung

- gemultiplext und mithin serialisiert auf optischer Basis, insbesondere auf Basis mindestens eines optischen Mediums, zum Beispiel auf Basis mindestens eines optischen Wellenleiters OM (vgl. hierzu im Detail Fig. 1A, Fig. 2A), wie etwa auf Basis mindestens einer Glasfaser und/oder auf Basis mindestens einer Plastikfaser, und/oder

- nicht gemultiplext auf elektrischer oder galvanischer Basis, insbesondere auf Basis mindestens einer elektrischen oder galvanischen Verbindung, zum Beispiel auf Basis mindestens eines Kupferkabels und/oder auf Basis mindestens einer, etwa auf Basis einer Leiterplatte angeordneten, elektrischen Leitung,

- zu realisieren und zu betreiben.

Fig. 1A zeigt ein Ausführungsbeispiel für den prinzipiellen Aufbau einer Sendeanordnung S zum Anschluss an eine D[isplay]S[erial]I[nterface]-Datenübertragungsschnittstelle IS oder 30 auch an eine C[amera]S[erial]I[nterface]-Datenübertragungsschnittstelle IS.

Die im Applikationsprozessor AP oder in der Kamera KA generierten Bilddaten werden auf vier Datenleitungen oder Kanälen CH0+, CH0-, CH1+, CH1-, CH2+, CH2-, CH3+, CH3- als D-PHY-Signale an der bis zu vier Bit breiten Datenübertragungsschnittstelle IS zusammen 35 mit D-PHY-korrekt Taktsignalen CLK+, CLK- zur Verfügung gestellt.

Die Sendeanordnung S nimmt diese Signale an einer integrierten Interface-Logik LS auf,

deren Blöcke jeweils mindestens einen Zustandsautomaten zur richtigen Interpretation der D-PHY-Logiksignale und zur Unterscheidung zwischen hochfrequenten Datenströmen (sogenannten H[igh]S[peed]-Daten) und niederfrequenten Datenströmen (sogenannten L[ow]S[peed]-Daten) aufweisen können.

5

Ein in der Sendeanordnung S folgender Framer FR (vgl. hierzu detaillierter Fig. 1B) stellt die D[irect]CURRENT-Balancierung des Eingangssignals sicher und erzeugt einen auf der Empfangsseite (vgl. Fig. 2A) wiedererkennbaren Rahmen, der es der Empfangsanordnung E (vgl. Fig. 2A) ermöglicht, die empfangenen Daten den richtigen Ausgangsdatenleitungen oder Ausgangskanälen CH0+, CH0-, CH1+, CH1-, CH2+, CH2-, CH3+, CH3- wieder zuzuordnen.

Im Detail kann der Framer FR gemäß Fig. 1B sowohl mit den single-ended, auf Logikpegeln basierenden Datensignalen HSD0, HSD1, HSD2, HSD3 als auch mit den differentiellen Datensignalen DD0+, DD0-, DD1+, DD1-, DD2+, DD2-, DD3+, DD3- beaufschlagen werden. Mittels seines als 5b/6b-Kodierblock ausgebildeten Kodierers KObettet der Framer FR gemäß Fig. 1B diese differentiellen Datensignale DD0+, DD0-, DD1+, DD1-, DD2+, DD2-, DD3+, DD3- in den Strom der single-ended, auf Logikpegeln basierenden Datensignale HSD0, HSD1, HSD2, HSD3 ein.

10

15

Ein sich dem Framer FR anschließender Multiplexer MU, insbesondere H[igh]S[peed]-Mux, erzeugt mit Hilfe eines als Phase-Locked-Loop, insbesondere als C[lock]M[ultiplier]U[nit], ausgebildeten Taktgenerators PS das hochfrequente serielle oder gebündelte Sendesignal, das dem Ausgang AS der Sendeanordnung S mittels eines Ausgangstreiber AT zur Verfügung gestellt wird. Der Framer FR und der Multiplexer MU bilden zusammen den Serialisierer SE.

20

25

Hierbei dient das über den Taktport CLK+, CLK- und über das Taktmodul CS der Interface-Logik LS mittels des Taktgenerators PS bereit gestellte D-PHY-Taktsignal als (Takt-)Referenz für den Serialisierer SE, insbesondere für dessen Multiplexer MU, und wird im seriellen Datenstrom, also im serialisierten Ausgangssignal eingebettet. Hierdurch entsteht der gemeinsame Signalstrom SI, der an die Empfangsanordnung E (vgl. Fig. 2A) übermittelt wird.

30

35

Wie der Darstellung gemäß Fig. 1A des Weiteren entnehmbar ist, ist der Ausgangstreiber AT als integrierter Lasertreiber zur Ansteuerung mindestens eines direkt angeschlossenen Lasers LA, insbesondere zur Ansteuerung mindestens einer direkt angeschlossener

V[ertical]C[avity]S[urface]E[mitting]L[aserdiode], ausgeführt.

Fig. 2A zeigt ein Ausführungsbeispiel für den prinzipiellen Aufbau einer Empfangsanordnung E zum Anschluss an eine D[isplay]S[erial]I[nterface]-Datenübertragungsschnittstelle IE oder auch an eine C[amera]S[erial]I[nterface]-Datenübertragungsschnittstelle IE.

Die von der Sendeanordnung S (vgl. Fig. 1A) ausgesandten seriellen oder gebündelten Daten werden über einen Eingangsverstärker EV der Empfangsanordnung E aufgenommen und einer integrierten Takt- und Datenrückgewinnung CD zugeführt.

Diese integrierte Takt- und Datenrückgewinnung CD regeneriert aus dem gemeinsamen Signalstrom SI den ursprünglichen D-PHY-Takt, der über das Taktmodul CE der Interface-Logik LE direkt dem D[isplay]S[erial]I[nterface] oder dem C[amera]S[erial]I[nterface] wieder zur Verfügung gestellt wird. Der verbleibende serielle Datenstrom wird über einen Demultiplexer DM entbündelt sowie parallelisiert und an einen Deframer DF (vgl. hierzu detaillierter Fig. 2B) übergeben, der grundsätzlich spiegelbildlich zum Framer FR gemäß Fig. 1B aufgebaut ist. Der Demultiplexer DM und der Deframer DF bilden zusammen den Deserialisierer DS.

Im Detail kann der Deframer FR gemäß Fig. 2B mittels seines als 6b/5b-Dekodierblock ausgebildeten Dekodierers DK die differentiellen Datensignale DD0+, DD0-, DD1+, DD1-, DD2+, DD2-, DD3+, DD3- von den single-ended, auf Logikpegeln basierenden Datensignalen HSD0, HSD1, HSD2, HSD3 separieren und die reparallelisierten Datensignale den jeweils zutreffenden Datenleitungen CH0+, CH0-, CH1+, CH1-, CH2+, CH2-, CH3+, CH3- wieder zuordnen.

Die in der Empfangsanordnung E dargestellten Interface-Logik-Blöcke LE können jeweils mindestens einen Zustandsautomaten zur richtigen Interpretation der D-PHY-Logiksignale und zur Unterscheidung zwischen hochfrequenten Datenströmen und niederfrequenten Datenströmen aufweisen.

Wie der Darstellung gemäß Fig. 2A des Weiteren entnehmbar ist, ist der Eingangsverstärker EV als integrierter Transimpedanzverstärker ausgeführt, der es ermöglicht, eine Photodiode FD direkt an die Empfangsanordnung E anzuschließen.

Auf diese Weise ist es bei der Schaltungsanordnung S, E (vgl. Fig. 1A, Fig. 2A) gemäß der

vorliegenden Erfindung möglich, die kabelbasierte gemultiplexte Verbindung zwischen der Sendeanordnung S (vgl. Fig. 1A) und der Empfangsanordnung E (vgl. Fig. 2A) auf optischer Basis, nämlich mittels eines, zum Beispiel in Form einer Glasfaser und/oder in Form einer Plastikfaser ausgebildeten, optischen Wellenleiters OM zu realisieren und zu betreiben.

5

### Bezugszeichenliste

|    |      |                                                                                                                         |

|----|------|-------------------------------------------------------------------------------------------------------------------------|

|    | E    | Empfangsanordnung                                                                                                       |

|    | S    | Sendeanordnung                                                                                                          |

| 10 | AE   | Ausgang der Empfangsanordnung E                                                                                         |

|    | AP   | Applikationsprozessor                                                                                                   |

|    | AS   | Ausgang der Sendeanordnung S                                                                                            |

|    | AT   | Ausgangstreiber, insbesondere Lasertreiber                                                                              |

|    | CD   | Takt- und Datenrückgewinnungseinheit                                                                                    |

| 15 | CE   | Taktmodul der Empfangs-Schnittstellen-Logik LE                                                                          |

|    | CH0± | erste Datenleitung oder erster Kanal                                                                                    |

|    | CH1± | zweite Datenleitung oder zweiter Kanal                                                                                  |

|    | CH2± | dritte Datenleitung oder dritter Kanal                                                                                  |

|    | CH3± | vierte Datenleitung oder vierter Kanal                                                                                  |

| 20 | CLK± | Taktleitung oder Taktkanal                                                                                              |

|    | CS   | Taktmodul der Sende-Schnittstellen-Logik LS                                                                             |

|    | DD0± | differentielles, insbesondere auf common mode basierendes, Datensignal auf erster Datenleitung oder erstem Kanal CH0±   |

|    | DD1± | differentielles, insbesondere auf common mode basierendes, Datensignal auf zweiter Datenleitung oder zweitem Kanal CH1± |

| 25 | DD2± | differentielles, insbesondere auf common mode basierendes, Datensignal auf dritter Datenleitung oder drittem Kanal CH2± |

|    | DD3± | differentielles, insbesondere auf common mode basierendes, Datensignal auf vierter Datenleitung oder viertem Kanal CH3± |

| 30 | DF   | Deframer                                                                                                                |

|    | DK   | Dekodierer, insbesondere 6b/5b-Dekodierblock, des Deframers DF                                                          |

|    | DM   | Demultiplexer                                                                                                           |

|    | DS   | Deserialisierungselement oder Deserialisierer                                                                           |

|    | DU   | Anzeigeeinheit                                                                                                          |

| 35 | EE   | Eingang der Empfangsanordnung E                                                                                         |

|    | ES   | Eingang der Sendeanordnung S                                                                                            |

|    | EV   | Eingangsverstärker, insbesondere Transimpedanzverstärker                                                                |

|    |      |                                                                                                        |

|----|------|--------------------------------------------------------------------------------------------------------|

|    | FD   | Fotodiode                                                                                              |

|    | FR   | Framer                                                                                                 |

|    | HSD0 | single-ended, auf Logikpegeln basierendes Datensignal auf erster Datenleitung oder erstem Kanal CH0±   |

| 5  | HSD1 | single-ended, auf Logikpegeln basierendes Datensignal auf zweiter Datenleitung oder zweitem Kanal CH1± |

|    | HSD2 | single-ended, auf Logikpegeln basierendes Datensignal auf dritter Datenleitung oder drittem Kanal CH2± |

|    | HSD3 | single-ended, auf Logikpegeln basierendes Datensignal auf vierter Datenleitung oder viertem Kanal CH3± |

| 10 | IE   | datensenkenbezogene CSI- und/oder CSI-2- und/oder CSI-3- und/oder DSI- und/oder DSI-2-Schnittstelle    |

|    | IS   | datenquellenbezogene CSI- und/oder CSI-2- und/oder CSI-3- und/oder DSI- und/oder DSI-2-Schnittstelle   |

| 15 | KA   | Kamera                                                                                                 |

|    | KO   | Kodierer, insbesondere 5b/6b-Kodierblock, des Framers FR                                               |

|    | LA   | Laser                                                                                                  |

|    | LE   | Empfangs-Schnittstellen-Logik                                                                          |

|    | LS   | Sende-Schnittstellen-Logik                                                                             |

| 20 | MU   | Multiplexer                                                                                            |

|    | OM   | optisches Medium, insbesondere optischer Wellenleiter, zum Beispiel Glasfaser und/oder Plastikfaser    |

|    | PS   | Taktgenerator, insbesondere Phase-Locked-Loop, zum Beispiel Clock Multiplier Unit                      |

| 25 | SE   | Serialisierungselement oder Serialisierer                                                              |

|    | SI   | gemeinsamer Signalstrom                                                                                |

|    | TL   | Taktleitung                                                                                            |

**Ansprüche**

1. Schaltungsanordnung (S, E)

- mit mindestens einer Sendeanordnung (S), die beaufschlagbar ist:

- mit auf mindestens einer Datenleitung (CH0+, CH0-, CH1+, CH1-, CH2+, CH2-, CH3+, CH3-) transportierbaren Datensignalen, wobei auf jeder der Datenleitungen (CH0+, CH0-, CH1+, CH1-, CH2+, CH2-, CH3+, CH3-)

- 5 --- sowohl single-ended, auf Logikpegeln basierende Datensignale (HSD0, HSD1, HSD2, HSD3)

- als auch differentielle, insbesondere auf common mode basierende, Datensignale (DD0+, DD0-, DD1+, DD1-, DD2+, DD2-, DD3+, DD3-)

- 10 anliegen, und

- mit auf mindestens einer Takteleitung (CLK+, CLK-) transportierbaren Taktsignalen, wobei auf jeder der Takteleitungen (CLK+, CLK-)

- sowohl single-ended, auf Logikpegeln basierende Taktsignale

- als auch differentielle, insbesondere auf common mode basierende, Taktsignale

- 15 anliegen,

- und mit mindestens einer Empfangsanordnung (E), die ausgibt:

- auf mindestens einer Datenleitung (CH0+, CH0-, CH1+, CH1-, CH2+, CH2-, CH3+, CH3-) transportierbare Datensignale, wobei auf jeder der Datenleitungen (CH0+, CH0-, CH1+, CH1-, CH2+, CH2-, CH3+, CH3-)

- 20 --- sowohl single-ended, auf Logikpegeln basierende Datensignale (HSD0, HSD1, HSD2, HSD3)

- als auch differentielle, insbesondere auf common mode basierende, Datensignale (DD0+, DD0-, DD1+, DD1-, DD2+, DD2-, DD3+, DD3-)

- anliegen, und

- 25 -- auf mindestens einer Takteleitung (CLK+, CLK-) transportierbare Taktsignale, wobei auf jeder der Takteleitungen (CLK+, CLK-)

- sowohl single-ended, auf Logikpegeln basierende Taktsignale

- als auch differentielle, insbesondere auf common mode basierende, Taktsignale

- anliegen,

- 30 **d a d u r c h g e k e n n z e i c h n e t ,**

- dass die Sendeanordnung (S) die single-ended, auf Logikpegeln basierenden Daten- sowie Taktsignale und die differentiellen Daten- sowie Taktsignale zu einem gemeinsamen Signalstrom (SI) serialisiert und

- dass die Empfangsanordnung (E) diesen gemeinsamen Signalstrom (SI) wieder in die single-ended, auf Logikpegeln basierenden Daten- sowie Taktsignale und in die

- 35

differentiellen Daten- sowie Taktsignale deserialisiert.

2. Schaltungsanordnung gemäß Anspruch 1, dadurch gekennzeichnet,

- dass die Sendeanordnung (S) mindestens einer Datenquelle, insbesondere mindestens einer Kamera (KA) und/oder mindestens einem Applikationsprozessor (AP), nachgeschaltet ist,

- dass die Empfangsanordnung (E) mindestens einer Datensenke, insbesondere mindestens einem Applikationsprozessor (AP) und/oder mindestens einer Anzeigeeinheit (DU), vorgeschaltet ist und

- dass die Datensignale, insbesondere in Form von D-PHY-Datensignalen, und die Taktsignale, insbesondere in Form von D-PHY-Taktsignalen, zwischen der Datenquelle und der Datensenke protokollbasiert, insbesondere auf Basis des CSI-Protokolls und/oder auf Basis des CSI-2-Protokolls und/oder auf Basis des CSI-3-Protokolls und/oder auf Basis des DSI-Protokolls und/oder auf Basis des DSI-2-Protokolls, übertragbar sind.

3. Schaltungsanordnung gemäß Anspruch 1 oder 2, dadurch gekennzeichnet, dass die Sendeanordnung (S) aufweist:

- mindestens einen Eingang (ES) für die Datensignale und Taktsignale,

- mindestens eine dem Eingang (ES) nachgeschaltete Sende-Schnittstellen-Logik (LS) zum Aufnehmen der Datensignale und Taktsignale,

- mindestens einen der Sende-Schnittstellen-Logik (LS) nachgeschalteten Serialisierer (SE) zum Erzeugen des gemeinsamen Signalstroms (SI),

- mindestens einen mindestens einem Taktmodul (CS) der Sende-Schnittstellen-Logik (LS) nachgeschalteten, dem Serialisierer (SE) vorgeschalteten und zum Erzeugen mindestens eines Referenztakts vorgesehenen Taktgenerator (PS), insbesondere Phase-Locked-Loop, zum Beispiel Clock Multiplier Unit,

- mindestens einen dem Serialisierer (SE) nachgeschalteten Ausgangstreiber (AT) und

- mindestens einen dem Ausgangstreiber (AT) nachgeschalteten Ausgang (AS) zum Übertragen des gemeinsamen Signalstroms (SI) an die Empfangsanordnung (E).

4. Schaltungsanordnung gemäß Anspruch 3, dadurch gekennzeichnet, dass der Serialisierer (SE) aufweist:

- mindestens einen der Sende-Schnittstellen-Logik (LS) nachgeschalteten Framer (FR) zum Erzeugen mindestens eines in der Empfangsanordnung (E) wiedererkennbaren Rahmens für den gemeinsamen Signalstrom (SI) sowie

- mindestens einen dem Framer (FR) nachgeschalteten Multiplexer (MU) zum Erzeugen

des gemeinsamen Signalstroms (SI).

5. Schaltungsanordnung gemäß Anspruch 4, dadurch gekennzeichnet, dass der Framer (FR) sowohl mit den single-ended, auf Logikpegeln basierenden Datensignalen (HSD0, HSD1, HSD2, HSD3) als auch mit den differentiellen Datensignalen (DD0+, DD0-, DD1+, DD1-, DD2+, DD2-, DD3+, DD3-) beaufschlagbar ist und mittels mindestens eines Kodierers (KO), insbesondere mittels mindestens eines 5b/6b-Kodierblocks, die differentiellen Datensignale (DD0+, DD0-, DD1+, DD1-, DD2+, DD2-, DD3+, DD3-) in den Strom der single-ended, auf Logikpegeln basierenden Datensignale (HSD0, HSD1, HSD2, HSD3) einbettet.

10. Schaltungsanordnung gemäß mindestens einem der Ansprüche 3 bis 5, dadurch gekennzeichnet, dass der Ausgangstreiber (AT) als mindestens ein Lasertreiber ausgebildet ist, mittels dessen mindestens ein dem Ausgang (AS) nachgeschalteter Laser (LA), insbesondere mindestens eine V[ertical]C[avity]S[urface]E[mitting]L[aserdiode], ansteuerbar ist.

15. Schaltungsanordnung gemäß mindestens einem der Ansprüche 1 bis 6, dadurch gekennzeichnet, dass die Empfangsanordnung (E) aufweist:

- mindestens einen Eingang (EE) für den von der Sendeanordnung (S) übertragenen gemeinsamen Signalstrom (SI),

- mindestens einen Eingangsverstärker (EV) zum Aufnehmen des gemeinsamen Signalstroms (SI),

- mindestens eine Takt- und Datenrückgewinnungseinheit (CD) zum Wiederherstellen der Datensignale und Taktsignale aus dem gemeinsamen Signalstrom (SI),

- mindestens ein der Takt- und Datenrückgewinnungseinheit (CD) nachgeschaltetes Taktmodul (CE) mindestens einer Empfangs-Schnittstellen-Logik (LE),

- mindestens einen der Takt- und Datenrückgewinnungseinheit (CD) nachgeschalteten Deserialisierer (DS) zum Reparallelisieren der Datensignale und zum Zuordnen der reparallelisierten Datensignale auf die Empfangs-Schnittstellen-Logik (LE) und

- mindestens einen der Empfangs-Schnittstellen-Logik (LE) nachgeschalteten Ausgang (AE) für die Datensignale und Taktsignale.

20. Schaltungsanordnung gemäß Anspruch 7, dadurch gekennzeichnet, dass der Deserialisierer (DS) aufweist:

- mindestens einen der Takt- und Datenrückgewinnungseinheit (CD) nachgeschalteten Demultiplexer (DM) zum Reparallelisieren der Datensignale sowie

25. Schaltungsanordnung gemäß Anspruch 7, dadurch gekennzeichnet, dass der Deserialisierer (DS) aufweist:

- mindestens einen der Takt- und Datenrückgewinnungseinheit (CD) nachgeschalteten Demultiplexer (DM) zum Reparallelisieren der Datensignale sowie

30. Schaltungsanordnung gemäß Anspruch 7, dadurch gekennzeichnet, dass der Deserialisierer (DS) aufweist:

- mindestens einen der Takt- und Datenrückgewinnungseinheit (CD) nachgeschalteten Demultiplexer (DM) zum Reparallelisieren der Datensignale sowie

35. Schaltungsanordnung gemäß Anspruch 7, dadurch gekennzeichnet, dass der Deserialisierer (DS) aufweist:

- mindestens einen der Takt- und Datenrückgewinnungseinheit (CD) nachgeschalteten Demultiplexer (DM) zum Reparallelisieren der Datensignale sowie

- mindestens einen dem Demultiplexer (DM) nachgeschalteten Deframer (DF) zum Zuordnen der reparallelisierten Datensignale auf die Empfangs-Schnittstellen-Logik (LE).

9. Schaltungsanordnung gemäß Anspruch 8, dadurch gekennzeichnet, dass der

5 Deframer (DF) mittels mindestens eines Dekodierers (DK), insbesondere mittels mindestens eines 6b/5b-Dekodierblocks, die differentiellen Datensignale (DD0+, DD0-, DD1+, DD1-, DD2+, DD2-, DD3+, DD3-) von den single-ended, auf Logikpegeln basierenden Datensignalen (HSD0, HSD1, HSD2, HSD3) separiert und die reparallelisierten Datensignale den jeweiligen Datenleitungen (CH0+, CH0-, CH1+, CH1-, CH2+, CH2-, CH3+, CH3-) zuordnet.

10. Schaltungsanordnung gemäß mindestens einem der Ansprüche 7 bis 9, dadurch

gekennzeichnet, dass der Eingangsverstärker (EV) als mindestens ein

Transimpedanzverstärker ausgebildet ist, dem mindestens eine dem Eingang (EE)

15 vorgeschaltete Fotodiode (FD) zugeordnet ist.

11. Schaltungsanordnung gemäß Anspruch 6 und/oder 10, dadurch gekennzeichnet, dass

der gemeinsame Signalstrom (SI) zwischen der Sendeanordnung (S) und der

Empfangsanordnung (E) optisch, insbesondere über mindestens ein optisches

20 Medium (OM), zum Beispiel über mindestens einen optischen Wellenleiter, wie etwa

über mindestens eine Glasfaser und/oder über mindestens eine Plastikfaser,

übertragbar ist.

12. Schaltungsanordnung gemäß mindestens einem der Ansprüche 1 bis 11, dadurch

25 gekennzeichnet,

- dass die Datenquelle mindestens eine, insbesondere bis zu vier Bit breite, CSI- und/oder CSI-2- und/oder CSI-3- und/oder DSI- und/oder DSI-2-Schnittstelle (IS) für die ausgehenden Datensignale aufweist und/oder

- dass die Datensenke mindestens eine, insbesondere bis zu vier Bit breite, CSI- und/oder CSI-2- und/oder CSI-3- und/oder DSI- und/oder DSI-2-Schnittstelle (IE) für die eingehenden Datensignale aufweist.

13. Verfahren,

- wobei mindestens eine Sendeanordnung (S) beaufschlagt wird:

- mit auf mindestens einer Datenleitung (CH0+, CH0-, CH1+, CH1-, CH2+, CH2-, CH3+, CH3-) transportierbaren Datensignalen, wobei auf jeder der Datenleitungen (CH0+, CH0-, CH1+, CH1-, CH2+, CH2-, CH3+, CH3-)

--- sowohl single-ended, auf Logikpegeln basierende Datensignale (HSD0, HSD1, HSD2, HSD3)

--- als auch differentielle, insbesondere auf common mode basierende, Datensignale (DD0+, DD0-, DD1+, DD1-, DD2+, DD2-, DD3+, DD3-) anliegen, und

-- mit auf mindestens einer Taktleitung (CLK+, CLK-) transportierbaren Taktsignalen, wobei auf jeder der Taktleitungen (CLK+, CLK-)

--- sowohl single-ended, auf Logikpegeln basierende Taktsignale

--- als auch differentielle, insbesondere auf common mode basierende, Taktsignale anliegen,

- und wobei mindestens eine Empfangsanordnung (E) ausgibt:

-- auf mindestens einer Datenleitung (CH0+, CH0-, CH1+, CH1-, CH2+, CH2-, CH3+, CH3-) transportierbare Datensignale, wobei auf jeder der Datenleitungen (CH0+, CH0-, CH1+, CH1-, CH2+, CH2-, CH3+, CH3-)

--- sowohl single-ended, auf Logikpegeln basierende Datensignale (HSD0, HSD1, HSD2, HSD3)

--- als auch differentielle, insbesondere auf common mode basierende, Datensignale (DD0+, DD0-, DD1+, DD1-, DD2+, DD2-, DD3+, DD3-) anliegen, und

-- auf mindestens einer Taktleitung (CLK+, CLK-) transportierbare Taktsignale, wobei auf jeder der Taktleitungen (CLK+, CLK-)

--- sowohl single-ended, auf Logikpegeln basierende Taktsignale

--- als auch differentielle, insbesondere auf common mode basierende, Taktsignale anliegen,

**dadurch gekennzeichnet,**

- dass die Sendeanordnung (S) die single-ended, auf Logikpegeln basierenden Daten- sowie Taktsignale und die differentiellen Daten- sowie Taktsignale zu einem gemeinsamen Signalstrom (SI) serialisiert und

- dass die Empfangsanordnung (E) diesen gemeinsamen Signalstrom (SI) wieder in die single-ended, auf Logikpegeln basierenden Daten- sowie Taktsignale und in die differentiellen Daten- sowie Taktsignale deserialisiert.

14. Verfahren gemäß Anspruch 13, dadurch gekennzeichnet, dass der gemeinsame Signalstrom (SI) zwischen der Sendeanordnung (S) und der Empfangsanordnung (E) optisch, insbesondere über mindestens ein optisches Medium (OM), zum Beispiel über mindestens einen optischen Wellenleiter, wie etwa über mindestens eine Glasfaser und/oder über mindestens eine Plastikfaser, übertragen wird.

15. Verwendung mindestens einer Schaltungsanordnung (S, E) gemäß mindestens einem der Ansprüche 1 bis 12 und/oder eines Verfahrens gemäß Anspruch 13 oder 14 zum gleichzeitigen seriellen und/oder gebündelten, insbesondere CSI-protokollbasierten und/oder CSI-2-protokollbasierten und/oder CSI-3-protokollbasierten und/oder DSI-protokollbasierten und/oder DSI-2-protokollbasierten, Übertragen sowohl von single-ended, auf Logikpegeln basierenden Daten- und Taktsignalen als auch von differentiellen, insbesondere auf common mode basierenden, Daten- und Taktsignalen, insbesondere von D-PHY-Datensignalen und D-PHY-Taktsignalen, zum Beispiel von bis zu vier Bit breiten MIPI-D-PHY-Datensignalen und MIPI-D-PHY-Taktsignalen, zwischen mindestens einer Datenquelle, insbesondere mindestens einer, zum Beispiel hochauflösenden und/oder zum Beispiel als Bildquelle fungierenden, Kamera (KA) und/oder mindestens einem Applikationsprozessor (AP), und mindestens einer Datensenke, insbesondere mindestens einem Applikationsprozessor (AP) und/oder mindestens einer, zum Beispiel hochauflösenden und/oder zum Beispiel als Bildsenke fungierenden, Anzeigeeinheit (DU), zum Beispiel mindestens einem Display oder mindestens einem Monitor.

**Fig. 1A****Fig. 1B**

**Fig. 2A****Fig. 2B**

**Fig. 3A** (= prior art = Stand der Technik)

**Fig. 3B** (= prior art = Stand der Technik)