(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6110769号

(P6110769)

(45) 発行日 平成29年4月5日(2017.4.5)

(24) 登録日 平成29年3月17日(2017.3.17)

|               |           |

|---------------|-----------|

| (51) Int.Cl.  | F 1       |

| HO 1 L 25/065 | (2006.01) |

| HO 1 L 25/07  | (2006.01) |

| HO 1 L 25/18  | (2006.01) |

| HO 1 L 23/50  | (2006.01) |

| HO 1 L 21/60  | (2006.01) |

| HO 1 L        | 25/08     |

| HO 1 L        | 25/08     |

| HO 1 L        | 23/50     |

| HO 1 L        | 21/60     |

|               | 3 O 1 A   |

請求項の数 14 (全 22 頁)

(21) 出願番号 特願2013-198300 (P2013-198300)

(22) 出願日 平成25年9月25日 (2013.9.25)

(65) 公開番号 特開2015-65296 (P2015-65296A)

(43) 公開日 平成27年4月9日 (2015.4.9)

審査請求日 平成28年2月2日 (2016.2.2)

(73) 特許権者 302062931

ルネサスエレクトロニクス株式会社

東京都江東区豊洲三丁目2番24号

(74) 代理人 100110928

弁理士 速水 進治

(74) 代理人 100127236

弁理士 天城 聰

(72) 発明者 内田 慎一

神奈川県川崎市中原区下沼部1753番地

ルネサスエレクトロニクス株式会社内

(72) 発明者 西川 健次

神奈川県川崎市中原区下沼部1753番地

ルネサスエレクトロニクス株式会社内

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

表面、第1長辺、前記第1長辺とは反対側であって凹部を有する第2長辺、前記第1および第2長辺と交差する第1短辺、並びに前記第1および第2長辺と交差し、且つ前記第1短辺とは反対側の第2短辺を有するダイパッドと、

第1主面、前記第1主面とは反対側の第1裏面、第1辺、前記第1辺とは反対側の第2辺、前記第1および第2辺と交差する第3辺、前記第3辺とは反対側の第4辺、前記第1主面上に形成された複数の第1電極パッド、並びに前記第1主面上に形成された複数の第1インダクタを有しており、前記第1裏面が前記ダイパッドの表面に対向するように前記ダイパッドの上に搭載される矩形状の第1半導体チップと、

第2主面、前記第2主面とは反対側の第2裏面、第5辺、前記第5辺とは反対側の第6辺、前記第5および第6辺と交差する第7辺、前記第7辺とは反対側の第8辺、前記第2主面上に形成された複数の第2電極パッド、並びに前記第2主面上に形成された複数の第2インダクタを有しており、前記第2主面が前記第1半導体チップの前記第1主面に対向するように前記第1半導体チップの上に絶縁用のシートを介して搭載される矩形状の第2半導体チップと、

前記ダイパッドの前記第1長辺に沿って配置された複数の第1リードと、

前記ダイパッドの前記第2長辺に沿って配置された複数の第2リードと、

前記複数の第1リードと前記第1半導体チップの前記複数の第1電極パッドを接続する複数の第1ボンディングワイヤと、

10

20

前記複数の第2リードと前記第2半導体チップの前記複数の第2電極パッドを接続する複数の第2ポンディングワイヤと、

前記ダイパッド、前記第1および第2半導体チップ、前記複数の第1リードのそれぞれの一部、並びに前記複数の第2リードのそれぞれの一部を樹脂で封止する封止体と、

を備え、

平面視において、前記第1半導体チップの前記第1および第2辺、並びに前記第2半導体チップの前記第5および第6辺、並びに前記ダイパッドの前記第1および2長辺のそれは、第1方向に沿って平行に配置されており、

平面視において、前記第1半導体チップの前記第3および第4辺、前記第2半導体チップの前記第7および第8辺、並びに前記ダイパッドの前記第1および第2短辺のそれは、前記第1方向に直交する第2方向に沿って平行に配置されており、 10

平面視において、前記第1半導体チップの前記第1辺は、前記ダイパッドの第2長辺より前記第1長辺の近くに配置されており、

平面視において、前記第1半導体チップの前記第1および第2辺は、前記ダイパッドの第1長辺と第2長辺の間に位置しており、

平面視において、前記第2半導体チップの前記第6辺は、前記ダイパッドの第1長辺より前記第2長辺の近くに配置されており、

平面視において、前記第1半導体チップの前記複数の第1電極パッドは、前記第1方向に沿って配置され、且つ前記第2辺より前記第1辺の近くに配置されており、

平面視において、前記第2半導体チップの前記複数の第2電極パッドは、前記第1方向に沿って配置され、且つ前記第5辺より前記第6辺の近くに配置されており、 20

平面視において、前記第1半導体チップの前記複数の第1インダクタは、前記第1方向に沿って配置され、且つ前記第1辺より前記第2辺の近くに配置されており、

平面視において、前記第2半導体チップの前記複数の第2インダクタは、前記第1方向に沿って配置され、且つ前記第6辺より前記第5辺の近くに配置されており、

平面視において、前記第1半導体チップの前記複数の第1インダクタのそれは、前記第2半導体チップの前記複数の第2インダクタのそれと重なっており、

前記ダイパッドは、平面視において前記第1半導体チップより大きく、

前記第1半導体チップは、平面視において前記第2半導体チップより大きく、

前記第1半導体チップの前記第2辺は、平面視において前記第2半導体チップの前記第5辺と前記第6辺の間に位置しており、 30

前記第1半導体チップの前記複数の第1電極パッドは、平面視において前記第2半導体チップと重なっておらず、

前記第2半導体チップの前記複数の第2電極パッドは、平面視において前記第1半導体チップと重なっておらず、

前記ダイパッドの前記凹部は、平面視において前記第1半導体チップの前記複数の第1電極パッドと重なっておらず、

前記ダイパッドの前記凹部は、平面視において前記第2半導体チップの前記複数の第2電極パッドと重なっており、

平面視において、前記第1半導体チップの前記第1辺の長さは、前記第1方向において前記凹部の開口側の幅よりも大きく、 40

平面視において、前記凹部の前記開口側の幅は、前記第1方向において前記第2半導体チップの前記第6辺の長さよりも大きい半導体装置。

### 【請求項2】

請求項1に記載の半導体装置において、

平面視において、前記第2半導体チップの前記第5辺から前記凹部までの距離は、前記第2方向において前記第2半導体チップの前記第5辺から前記第6辺までの距離の1/2より大きい半導体装置。

### 【請求項3】

請求項1に記載の半導体装置において、

前記ダイパッドの前記凹部は、平面視において前記ダイパッドの前記第1短辺から前記第2短辺までの間に位置し、且つ前記ダイパッドの第1長辺から第2長辺の間に位置している半導体装置。

**【請求項4】**

請求項1に記載の半導体装置において、

平面視において、前記凹部の前記開口側の端部にはテーパが形成されている半導体装置。

。

**【請求項5】**

請求項1に記載の半導体装置において、

前記第1半導体チップは、電力制御用の半導体チップであり、

10

前記第2半導体チップは、前記第1半導体チップを制御するマイクロコントローラ若しくはマイクロプロセッサである半導体装置。

**【請求項6】**

請求項1に記載の半導体装置において、

平面視において、前記複数の第2リードから前記ダイパッドの前記第2長辺までの距離は、前記第2方向に沿って前記複数の第1リードから前記ダイパッドの第1長辺までの距離よりも大きい半導体装置。

**【請求項7】**

請求項1に記載の半導体装置において、

前記第1半導体チップは、前記第2半導体チップとは電気的に接続されてない半導体装置。

20

**【請求項8】**

請求項7に記載の半導体装置において、

前記第2半導体チップは、前記ダイパッドと電気的に接続されていない半導体装置。

**【請求項9】**

請求項8に記載の半導体装置において、

前記ダイパッドは、前記複数の第2リードと電気的に接続されていない半導体装置。

**【請求項10】**

請求項1に記載の半導体装置において、

前記第2半導体チップは、前記第1半導体チップよりも厚い半導体装置。

30

**【請求項11】**

請求項1に記載の半導体装置において、

前記第2半導体チップの前記第2裏面に設けられた保護層を備える半導体装置。

**【請求項12】**

請求項5に記載の半導体装置において、

前記第1半導体チップに形成された電力制御素子を備えている半導体装置。

**【請求項13】**

請求項1に記載の半導体装置において、

前記シートの一部は前記第2半導体チップの側面の上に位置しており、

前記シートの他の一部は、前記第1半導体チップの側面のうち前記第2半導体チップと重なっている領域の上に位置している半導体装置。

40

**【請求項14】**

請求項1に記載の半導体装置において、

前記第1半導体チップの前記第1主面及び前記第2半導体チップの前記第2主面のいずれか一方に形成された凸部と、

前記第1半導体チップの前記第1主面及び前記第2半導体チップの前記第2主面の他方に形成された切欠部と、

を備え、

平面視において、前記凸部の外形と前記切欠部の外形は同様の形状を有しており、かつ前記凸部と前記切欠部は重なっている半導体装置。

50

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、半導体装置に関し、例えば2つの半導体チップを積層させた半導体装置に適用可能な技術である。

**【背景技術】****【0002】**

半導体装置には、第1半導体チップと第2半導体チップの素子形成面を互いに対向させた状態で、これら2つの半導体チップを積層したものがある（例えば特許文献1）。特許文献1に記載の技術は、第1半導体チップと第2半導体チップの間で信号を送受信させるものである。具体的には、第1半導体チップと第2半導体チップのそれぞれにインダクタを形成し、これらのインダクタを互いに対向させている。そして、これらのインダクタの間で信号を送受信することにより、第1半導体チップと第2半導体チップの間で信号の送受信を行っている。

**【0003】**

また特許文献1には、リードフレームの素子搭載部の上に第1半導体チップを搭載し、さらにこの第1半導体チップの上に第2半導体チップを搭載した半導体装置が記載されている。この半導体装置において、第2半導体チップの素子形成面の一部は第1の半導体チップからみ出している。そして第2半導体チップとリード端子は、ボンディングワイヤを用いて接続されている。

**【先行技術文献】****【特許文献】****【0004】****【特許文献1】特開2011-54800号公報****【発明の概要】****【発明が解決しようとする課題】****【0005】**

本発明者は、リードフレームの素子搭載部の上に第1半導体チップを搭載し、この第1半導体チップの上に第2半導体チップを、素子形成面を第1半導体チップに向けて搭載し、さらにボンディングワイヤで第2半導体チップとリード端子を接続することを検討した。この場合において、半導体装置を小型化すると、本発明者が検討した結果、ボンディングワイヤを第2半導体チップに接続するボンディングヘッドが、素子搭載部と干渉する可能性がでてくる、と考えた。その他の課題と新規な特徴は、本明細書の記述及び添付図面から明らかになるであろう。

**【課題を解決するための手段】****【0006】**

一実施の形態によれば、半導体装置は、チップ搭載部、第1半導体チップ、及び第2半導体チップを有している。第1半導体チップは第1主面がチップ搭載部に対向する向きに、チップ搭載部に搭載されている。第2半導体チップは、第3主面が第1半導体チップに對向する向きに、第1半導体チップの上に一部が搭載されている。素子搭載部は切欠部を有している。第2半導体チップの一部は切欠部と重なっている。第2半導体チップの第3主面のうち切欠部と重なっている領域には、第2電極パッドが設けられている。第1半導体チップの第1電極パッドには第1ボンディングワイヤが接続しており、第2電極パッドには第2ボンディングワイヤが接続している。

**【発明の効果】****【0007】**

前記一実施の形態によれば、ボンディングワイヤを第2半導体チップに接続するボンディングヘッドが、素子搭載部と干渉することを抑制できる。

**【図面の簡単な説明】****【0008】**

10

20

30

40

50

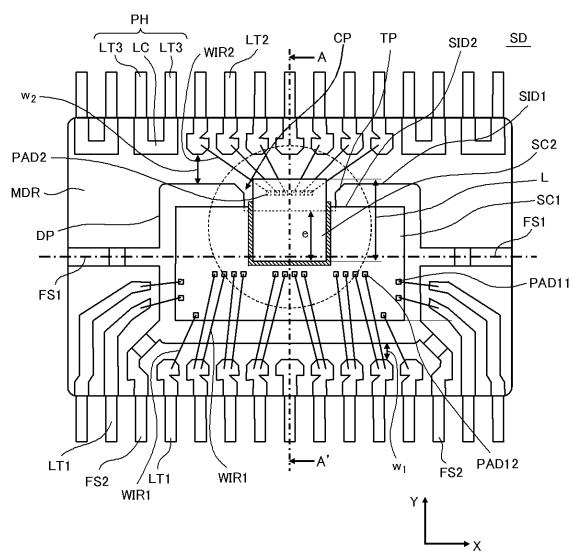

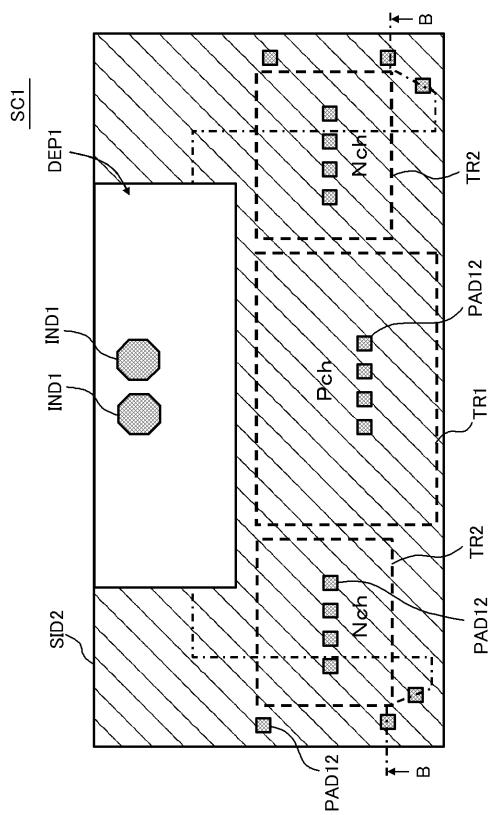

【図1】実施形態に係る半導体装置の構成を示す平面図である。

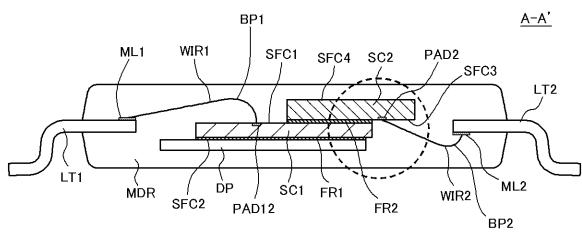

【図2】図1のA-A'断面図である。

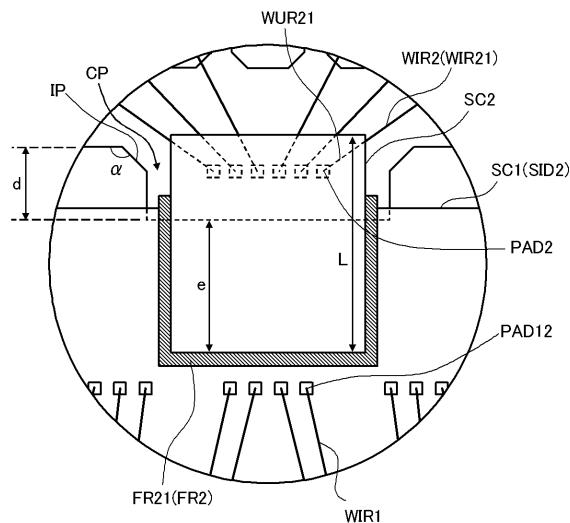

【図3】図1の点線で囲んだ領域を拡大した図である。

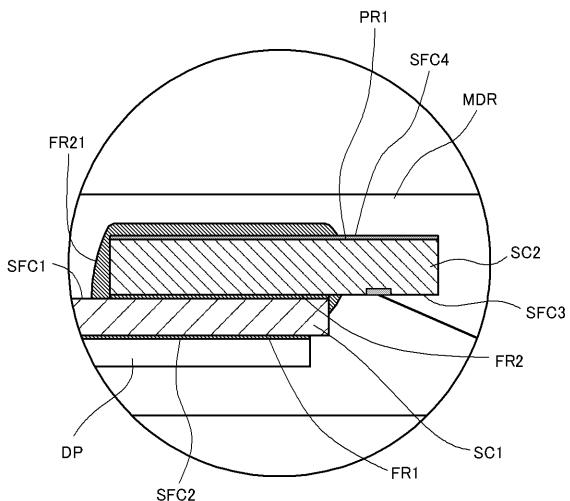

【図4】図2の点線で囲んだ領域を拡大した図である。

【図5】第1半導体チップの構造の一例を示す平面図である。

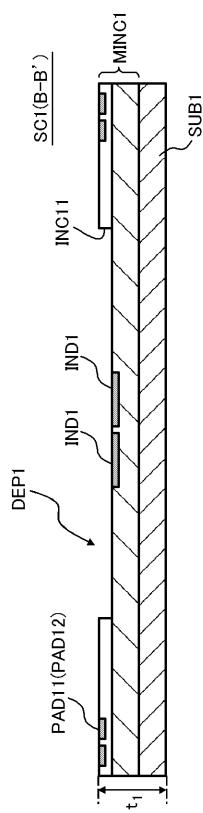

【図6】図5のB-B'断面図である。

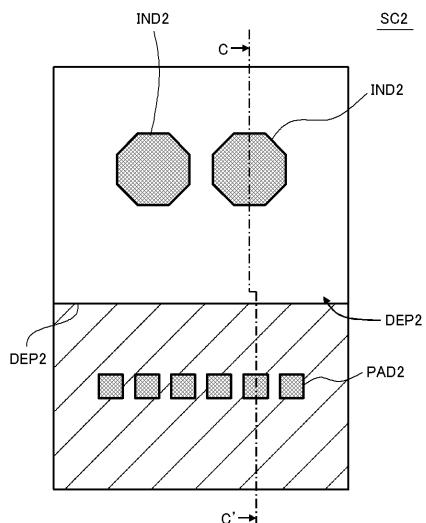

【図7】第2半導体チップの構造の一例を示す平面図である。

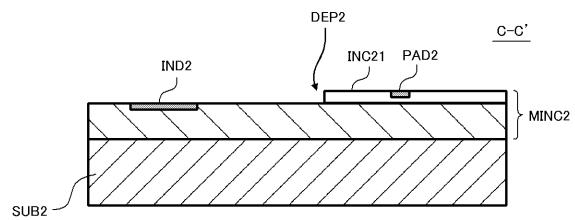

【図8】図7のC-C'断面図である。

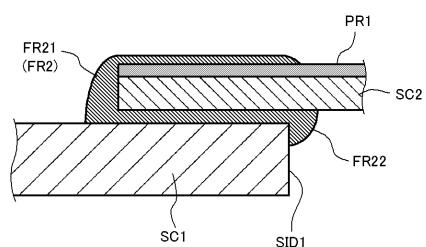

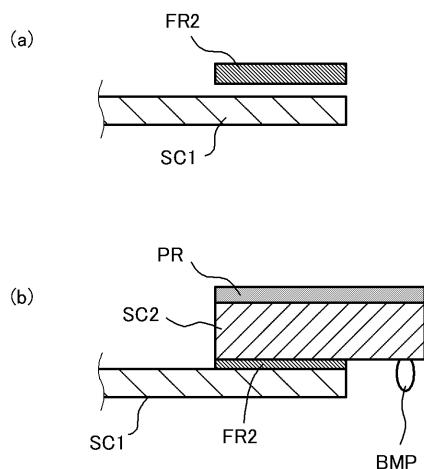

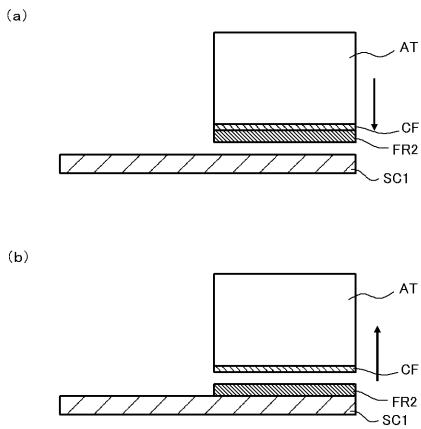

【図9】固定層の形状の第1例を示す断面図である。

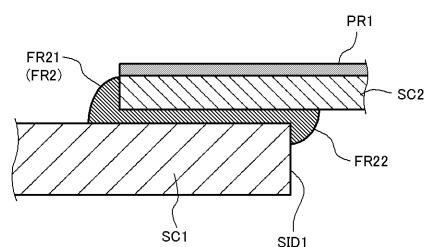

【図10】固定層の形状の第2例を示す断面図である。

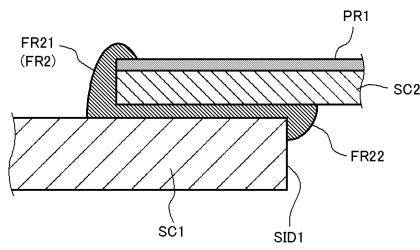

10

【図11】固定層の形状の第3例を示す断面図である。

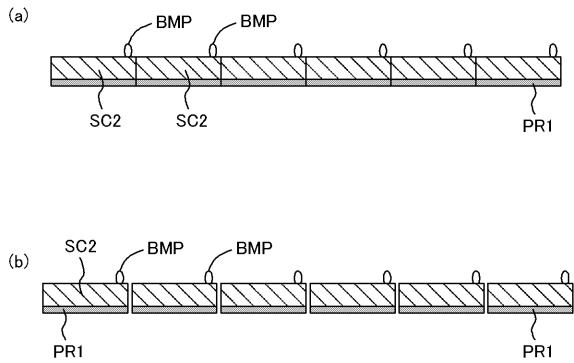

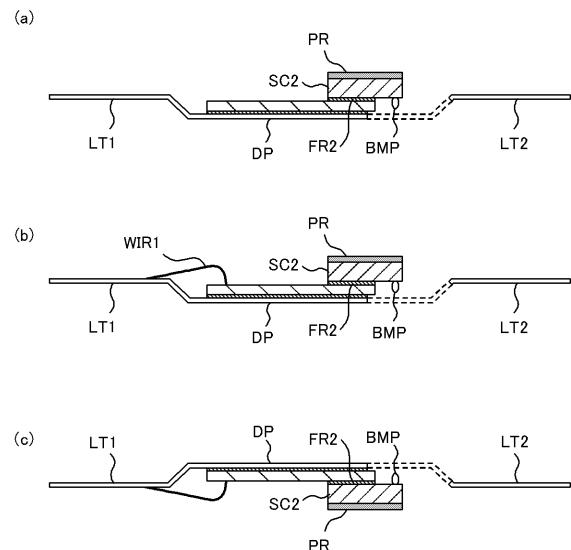

【図12】半導体装置の製造方法を説明するための断面図である。

【図13】半導体装置の製造方法を説明するための断面図である。

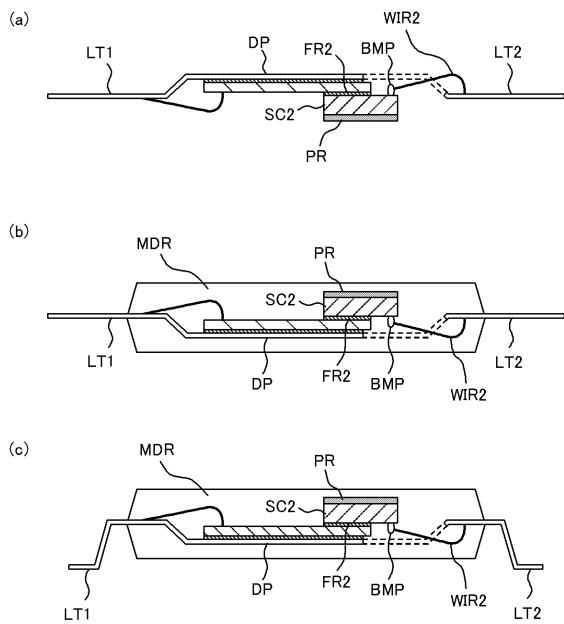

【図14】半導体装置の製造方法を説明するための断面図である。

【図15】半導体装置の製造方法を説明するための断面図である。

【図16】図13(a)及び(b)に示した工程の詳細を示すフローチャートである。

【図17】図13(a)及び(b)に示した工程の詳細を示すフローチャートである。

【図18】変形例に係る第1半導体チップの平面図である。

【図19】変形例に係る第2半導体チップの平面図である。

【発明を実施するための形態】

20

【0009】

以下、実施の形態について、図面を用いて説明する。尚、すべての図面において、同様な構成要素には同様の符号を付し、適宜説明を省略する。

【0010】

(実施形態)

図1は、実施形態に係る半導体装置SDの構成を示す平面図である。図2は、図1のA-A'断面図である。図3は、図1の点線で囲んだ領域を拡大した図である。図4は、図2の点線で囲んだ領域を拡大した図である。実施形態に係る半導体装置SDは、チップ搭載部DP、第1半導体チップSC1、及び第2半導体チップSC2を備えている。第1半導体チップSC1はチップ搭載部DPの上に搭載されており、第2半導体チップSC2は第1半導体チップSC1の上に一部が搭載されている。

30

【0011】

詳細には、図2に示すように、第1半導体チップSC1は第1主面SFC1及び第2主面SFC2を有している。第2主面SFC2は第1主面SFC1の反対側の面である。第1半導体チップSC1は、第2主面SFC2がチップ搭載部DPに対向する向きに、チップ搭載部DPに搭載されている。

【0012】

また、図2に示すように、第2半導体チップSC2は第3主面SFC3及び第4主面SFC4を有している。第4主面SFC4は第3主面SFC3の反対側の面である。そして第2半導体チップSC2は、第3主面SFC3が第1主面SFC1に対向する向きに、第1半導体チップSC1の上に一部が搭載されている。

40

【0013】

図1及び図3に示すように、平面図において、チップ搭載部DPは切欠部CPを有している。第2半導体チップSC2の一部は切欠部CPと重なっている。また、第1半導体チップSC1の第1主面SFC1のうち第2半導体チップSC2と重なっていない部分には、第1電極パッドPAD11, PAD12が設けられており、第2半導体チップSC2の第3主面SFC3のうち切欠部CPと重なっている領域には、第2電極パッドPAD2が設けられている。そして半導体装置SDは、第1ボンディングワイヤWIR1及び第2ボンディングワイヤWIR2を備えている。第1ボンディングワイヤWIR1の一端は第1電極パッドPAD11(又は第1電極パッドPAD12)に接続しており、第2ボンディ

50

ングワイヤWIR2の一端は第2電極パッドPAD2に接続している。以下、詳細に説明する。

#### 【0014】

第1半導体チップSC1は、例えば電力制御用の半導体チップであり、電力制御用のパワートランジスタ、及びこのパワートランジスタを制御する制御回路を有している。第1半導体チップSC1は、さらにロジック回路を有していてもよい。第2半導体チップSC2は、例えばマイコン（マイクロコントローラ（MCU：Micro Control Unit）またはマイクロプロセッサ（MPU：Micro-Processing Unit）などである。そして、第1半導体チップSC1は、第2半導体チップSC2よりも大きい。この場合、本実施形態に示すように、第1半導体チップSC1を第2半導体チップSC2の下に位置させることで、半導体装置SDの構造は安定する。ただし、第1半導体チップSC1は、第2半導体チップSC2と同じ程度の大きさであっても良い。10

#### 【0015】

また、第2半導体チップSC2は、第1半導体チップSC1よりも厚くなっている。例えば第1半導体チップSC1の厚さは100μm以上300μm以下であり、第2半導体チップSC2の厚さは300μm以上500μm以下である。

#### 【0016】

図1及び図2に示す例において、チップ搭載部DPはリードフレームのダイパッドであり、略多角形、例えば矩形である。そして、切欠部CPは、チップ搭載部DPの辺SID1に設けられている。平面視かつ辺SID1に直交する方向において第2半導体チップSC2の長さをL（図1，3参照）とした場合、第2半導体チップSC2のうち第1半導体チップSC1上に位置する部分の端から切欠部CPまでの距離e（図1，3参照）は、L/2以上となっている。図1に示す例において、チップ搭載部DPは略長方形であり、辺SID1はチップ搭載部DPの長辺である。そしてチップ搭載部DPの残りの3辺のうち辺SID1に交わる2辺のそれぞれには、支持部FS1（例えば吊りリード）の一端が接続している。図1に示す例では、支持部FS1はチップ搭載部DPの短辺のほぼ中央に接続している。20

#### 【0017】

また、チップ搭載部DPには支持部FS2も接続している。支持部FS2も吊りリードであり、リードフレームのリード端子の間に位置している。言い換えると、支持部FS2は、リード端子のうち第1半導体チップSC1及び第2半導体チップSC2のいずれにも接続していない端子を吊りリードとしたものである。このため、支持部FS2のうちチップ搭載部DPに接続していない側の端部は、封止樹脂MDR（後述）の外部に延在している。支持部FS2が設けられることにより、チップ搭載部DPの位置及び向きは安定する。また、リード端子を支持部FS2として流用しているため、新たに吊りリードを追加する場合と比較して、リードフレームが大型化することを抑制できる。30

#### 【0018】

図1に示す例では、チップ搭載部DPの辺SID1に面する側には、複数の第2リード端子LT2が設けられている。そして、平面視においてチップ搭載部DPを挟んで第2リード端子LT2と逆側には、複数の第1リード端子LT1が設けられている。第2リード端子LT2には、第2ボンディングワイヤWIR2の他端が接続しており、第1リード端子LT1には第1ボンディングワイヤWIR1の他端が接続している。そして支持部FS2は、複数の第1リード端子LT1の間に設けられている。具体的には、支持部FS2は2つ設けられている。2つの支持部FS2は、それぞれ、チップ搭載部DPの4つの角のうち辺SID1に繋がっていない2つの角に接続している。なお、一部の第1リード端子LT1の第1ボンディングワイヤWIR1に接続する側の端部は、チップ搭載部DPの短辺に対向している。40

#### 【0019】

また、第1リード端子LT1のうち第1ボンディングワイヤWIR1が接続している面（図2に示す例では第1半導体チップSC1の第1主面SFC1とは逆側の面）と、第250

リード端子 L T 2 のうち第 2 ボンディングワイヤ W I R 2 が接続している面（図 2 に示す例では第 2 半導体チップ S C 2 の第 3 主面 S F C 3 とは逆側の面）は、互いに逆となっている。そして、第 1 リード端子 L T 1 のワイヤ接続側の端部のうち第 1 ボンディングワイヤ W I R 1 が接続する面には、金属層 M L 1 が形成されており、第 2 リード端子 L T 2 のワイヤ接続側の端部のうち第 2 ボンディングワイヤ W I R 2 が接続する面には、金属層 M L 2 が形成されている。言い換えると、第 2 リード端子 L T 2 のうち金属層 M L 2 が形成されている面は、第 1 リード端子 L T 1 のうち金属層 M L 1 が形成されている面とは逆になっている。金属層 M L 1 , M L 2 は、ボンディングワイヤと接合しやすい金属によって形成されている。ボンディングワイヤが金ワイヤの場合、金属層 M L 1 , M L 2 は、例えば錫銀メッキなどによって形成されている。

10

#### 【 0 0 2 0 】

なお、チップ搭載部 D P の上には第 1 半導体チップ S C 1 が搭載されているため、チップ搭載部 D P の電位は、第 1 半導体チップ S C 1 の基板電位と一致しているのが好ましい。第 1 半導体チップ S C 1 が電力制御用の素子である場合、第 1 半導体チップ S C 1 の基板電位と第 2 半導体チップ S C 2 の基板電位には大きな差が生じる。このため、チップ搭載部 D P と第 2 リード端子 L T 2 を近づけると、これらの間の絶縁が確保できなくなる可能性が出てくる。これに対して図 1 に示す例では、平面視において、第 2 リード端子 L T 2 からチップ搭載部 D P までの距離 w<sub>2</sub> は、第 1 リード端子 L T 1 からチップ搭載部 D P までの距離 w<sub>1</sub> よりも大きい。このため、チップ搭載部 D P と第 2 リード端子 L T 2 の間の絶縁を確保できる。

20

#### 【 0 0 2 1 】

図 2 に示すように、半導体装置 S D の厚さ方向において、第 1 ボンディングワイヤ W I R 1 及び第 2 ボンディングワイヤ W I R 2 は、いずれも屈曲点を有している。

#### 【 0 0 2 2 】

そして、平面視において、第 1 リード端子 L T 1 から第 1 ボンディングワイヤ W I R 1 の屈曲点 B P<sub>1</sub> までの距離は、第 1 半導体チップ S C 1 の第 1 電極パッド P A D 1 1 ( 又は第 1 電極パッド P A D 1 2 ) から屈曲点 B P<sub>1</sub> までの距離よりも、長い。そして、第 1 ボンディングワイヤ W I R 1 の他端 ( 第 1 リード端子 L T 1 に接続している側の端部 ) の第 1 リード端子 L T 1 に対する角度は、第 1 ボンディングワイヤ W I R 1 の一端 ( 第 1 半導体チップ S C 1 に接続している側の端部 ) の第 1 半導体チップ S C 1 に対する角度よりも小さくなっている。これは、第 1 ボンディングワイヤ W I R 1 の一端を第 1 電極パッド P A D 1 1 ( 又は第 1 電極パッド P A D 1 2 ) に接続してから第 1 ボンディングワイヤ W I R 1 の他端を第 2 リード端子 L T 2 に接続しているためである。

30

#### 【 0 0 2 3 】

これに対して、平面視において、第 2 リード端子 L T 2 から第 2 ボンディングワイヤ W I R 2 の屈曲点 B P<sub>2</sub> までの距離は、第 2 半導体チップ S C 2 の第 2 電極パッド P A D 2 から屈曲点 B P<sub>2</sub> までの距離よりも、短い。そして、第 2 ボンディングワイヤ W I R 2 の他端 ( 第 2 リード端子 L T 2 に接続している側の端部 ) の第 2 リード端子 L T 2 に対する角度は、第 2 ボンディングワイヤ W I R 2 の一端 ( 第 2 半導体チップ S C 2 に接続している側の端部 ) の第 2 半導体チップ S C 2 に対する角度よりも大きくなっている。これは、第 2 ボンディングワイヤ W I R 2 の他端を第 2 リード端子 L T 2 に接続してから第 2 ボンディングワイヤ W I R 2 の一端を第 2 電極パッド P A D 2 に接続しているためである。

40

#### 【 0 0 2 4 】

また、半導体装置 S D は、樹脂保持部 P H を備えている。樹脂保持部 P H は、隣り合う 2 つの第 3 リード端子 L T 3 及び一つの端子接続部 L C からなる。端子接続部 L C は第 3 リード端子 L T 3 のうち封止樹脂 M D R の内側に位置している端部を互いに接続している。端子接続部 L C は、第 3 リード端子 L T 3 と一体に形成されている。図 1 に示す例では、第 3 リード端子 L T 3 は第 2 リード端子 L T 2 と並んで配置されているが、ボンディングワイヤには接続されていない。また、端子接続部 L C にもボンディングワイヤは接続されていない。そして辺 S I D 1 が延在する方向 ( 図 1 における X 方向 ) において、樹脂保

50

持部 P H は、複数の第 2 リード端子 L T 2 の両側のそれぞれに設けられている。言い換えると、第 1 の樹脂保持部 P H と第 2 の樹脂保持部 P H の間に複数の第 2 リード端子 L T 2 が設けられている。樹脂保持部 P H は、封止樹脂 M D R から端子接続部 L C が抜けることを抑制するために設けられている。

#### 【 0 0 2 5 】

なお、図 1 に示す例において、第 2 リード端子 L T 2 の数は第 1 リード端子 L T 1 の数よりも少ない。このため、樹脂保持部 P H は第 2 リード端子 L T 2 と並んで配置されている。ただし、第 1 リード端子 L T 1 の数が第 2 リード端子 L T 2 の数よりも少ない場合、樹脂保持部 P H は第 1 リード端子 L T 1 と並んで配置されていても良い。

#### 【 0 0 2 6 】

第 1 半導体チップ S C 1 は、チップ搭載部 D P の中心と重なるように配置されている。これに対して第 2 半導体チップ S C 2 は第 1 半導体チップ S C 1 よりも小さく、このため、チップ搭載部 D P の辺 S I D 1 側に寄っている。そして第 2 半導体チップ S C 2 の一部は、平面視で第 1 半導体チップ S C 1 から食み出しており、この食み出している部分がチップ搭載部 D P に設けられた切欠部 C P に重なっている。

#### 【 0 0 2 7 】

図 1 に示す例において、辺 S I D 1 が延在する方向（図 1 における X 方向）において、切欠部 C P の幅は第 2 半導体チップ S C 2 の幅よりも大きくなっている。このため、図 1 の X 方向において、第 2 半導体チップ S C 2 の全体が切欠部 C P の内側に位置している。ただし、図 1 の X 方向において、第 2 半導体チップ S C 2 の端部はチップ搭載部 D P と重なっていても良い。

#### 【 0 0 2 8 】

また、平面視において、切欠部 C P のうち開口側の端部 T P にはテーパが形成されている。このテーパは、外側に行くにつれて切欠部 C P の幅が広がる方向を向いている。辺 S I D 1 に対する端部 T P の角度（図 3 参照）は、例えば 135° 以上 180° 以下であるが、この範囲に限定されない。

#### 【 0 0 2 9 】

第 1 半導体チップ S C 1 のうち切欠部 C P に面している辺 S I D 2 の幅は、切欠部 C P の幅よりも広い。このため、辺 S I D 2 が延在する方向において、第 1 半導体チップ S C 1 のうち辺 S I D 2 の近傍に位置する部分の両端は、チップ搭載部 D P によって支持される。従って、辺 S I D 2 に直交する方向におけるチップ搭載部 D P の幅を小さくした場合と比較して、第 1 半導体チップ S C 1 の安定性は向上する。なお、平面視において、辺 S I D 2 の一部は切欠部 C P と重なっている。

#### 【 0 0 3 0 】

第 1 半導体チップ S C 1 は、第 1 主面 S F C 1 に半導体素子及び第 1 多層配線層 M I N C 1（後述）を有している。第 1 電極パッド P A D 1 1 , 第 1 電極パッド P A D 1 2 は第 1 多層配線層 M I N C 1 に形成されている。図 1 に示す例において、第 1 電極パッド P A D 1 1 は第 1 半導体チップ S C 1 の縁に沿って配置されており、第 1 電極パッド P A D 1 2 は第 1 電極パッド P A D 1 1 よりも第 1 半導体チップ S C 1 の内側に配置されている。このため、第 1 電極パッド P A D 1 2 から第 2 半導体チップ S C 2 までの距離は、第 1 電極パッド P A D 1 1 から第 2 半導体チップ S C 2 までの距離よりも、短い。第 1 電極パッド P A D 1 2 は第 1 半導体チップ S C 1 が有するパワートランジスタに接続しており、第 1 電極パッド P A D 1 1 は、このパワートランジスタの制御回路及びロジック回路の一方に接続している。

#### 【 0 0 3 1 】

第 2 半導体チップ S C 2 は、第 3 主面 S F C 3 に半導体素子及び第 2 多層配線層 M I N C 2（後述）を有している。第 2 電極パッド P A D 2 は第 2 多層配線層 M I N C 2 に形成されている。

#### 【 0 0 3 2 】

そして、図 4 に詳細を示すように、第 1 半導体チップ S C 1 は固定層 F R 1 を用いてチ

10

20

30

40

50

チップ搭載部 D P に固定されている。チップ搭載部 D P は、例えば導電性のペースト材、例えば銀ペーストである。

#### 【 0 0 3 3 】

また、図 1 及び図 4 に詳細を示すように、第 2 半導体チップ S C 2 は、第 2 多層配線層 M I N C 2 が第 1 半導体チップ S C 1 の第 1 多層配線層 M I N C 1 と対向する向きに、固定層 F R 2 を用いて第 1 半導体チップ S C 1 上に固定されている。固定層 F R 2 は、例えば N C F (Non Conductive Film) を用いて形成されている。そして図 3 及び図 4 に示すように、固定層 F R 2 の一部は、第 2 半導体チップ S C 2 の側面のうち第 1 半導体チップ S C 1 の上に位置している部分を這い上がり、フィレット F R 2 1 を形成している。

#### 【 0 0 3 4 】

なお、第 2 半導体チップ S C 2 の第 4 主面 S F C 4 は、保護層 P R 1 によって覆われている。図 4 に示す例において、保護層 P R 1 は、第 4 主面 S F C 4 の全面を覆っている。保護層 P R 1 は、例えば D A F (Die Attachment Film) であり、第 2 半導体チップ S C 2 を第 1 半導体チップ S C 1 上に搭載する際に、第 2 半導体チップ S C 2 を保護するため 10 に設けられている。なお、保護層 P R 1 は設けられていなくても良い。

#### 【 0 0 3 5 】

また、第 1 半導体チップ S C 1 の第 1 多層配線層 M I N C 1 には第 1 インダクタ I N D 1 (後述) が形成されており、第 2 半導体チップ S C 2 の第 2 多層配線層 M I N C 2 には第 2 インダクタ I N D 2 が形成されている。平面視において、第 1 インダクタ I N D 1 と第 2 インダクタ I N D 2 は重なっており、互いに電気的に結合 (例えば誘導結合) する。そして、第 2 半導体チップ S C 2 が生成したパワートランジスタ制御用の信号は、第 2 インダクタ I N D 2 及び第 1 インダクタ I N D 1 を介して、第 1 半導体チップ S C 1 のパワートランジスタ制御用の回路に入力される。

#### 【 0 0 3 6 】

さらに、図 1 及び図 2 に示すように、半導体装置 S D は、封止樹脂 M D R を有している。封止樹脂 M D R は、チップ搭載部 D P 、第 1 半導体チップ S C 1 、第 2 半導体チップ S C 2 、第 1 ボンディングワイヤ W I R 1 、第 2 ボンディングワイヤ W I R 2 、第 1 リード端子 L T 1 のうち第 1 ボンディングワイヤ W I R 1 との接続部、第 2 リード端子 L T 2 のうち第 2 ボンディングワイヤ W I R 2 との接続部、端子接続部 L C 、第 3 リード端子 L T 3 のうち端子接続部 L C との接続部、及び支持部 F S 2 の一部を封止している。図 2 に示す例では、チップ搭載部 D P の裏面は封止樹脂 M D R の内側に位置している。なお、図 1 及び図 2 は半導体装置 S D の封止構造の一例を示したものであるため、半導体装置 S D の封止構造は図 1 及び図 2 に示す例に限定されない。

#### 【 0 0 3 7 】

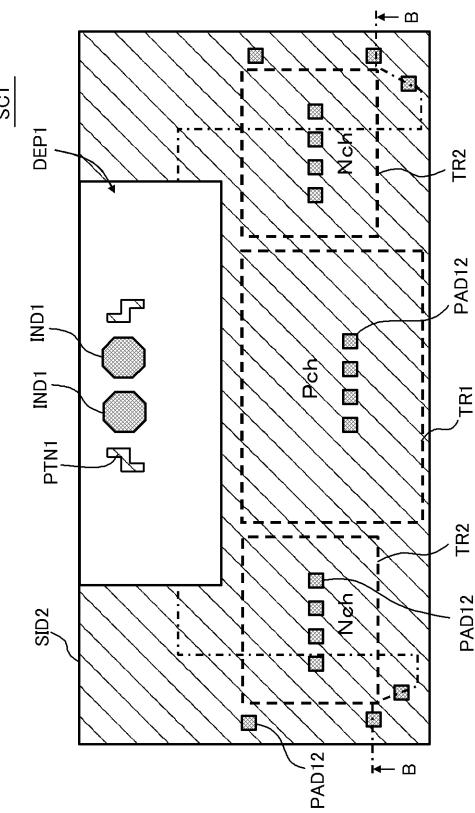

図 5 は、第 1 半導体チップ S C 1 の構造の一例を示す平面図である。図 6 は、図 5 の B - B' 断面図である。図 5 に示すように、第 1 半導体チップ S C 1 は、電力制御用の素子として、複数のトランジスタ (本図に示す例では、第 1 トランジスタ T R 1 及び 2 つの第 2 トランジスタ T R 2 ) を有している。第 1 トランジスタ T R 1 は第 1 導電型 (例えば p チャネル型) のトランジスタであり、第 2 トランジスタ T R 2 は第 2 導電型 (例えば n チャネル型) のトランジスタである。第 1 トランジスタ T R 1 及び 2 つの第 2 トランジスタ T R 2 は、第 1 半導体チップ S C 1 のうち辺 S I D 2 とは逆側の辺に沿って配置されている。そして第 1 トランジスタ T R 1 は、2 つの第 2 トランジスタ T R 2 の間に位置している。第 1 トランジスタ T R 1 及び第 2 トランジスタ T R 2 の上には、それぞれ、そのトランジスタに接続する第 1 電極パッド P A D 1 2 が形成されている。

#### 【 0 0 3 8 】

また、第 1 半導体チップ S C 1 は、少なくとも一つの第 1 インダクタ I N D 1 (本図に示す例では 2 つ) を有している。第 1 インダクタ I N D 1 は、平面視で第 2 半導体チップ S C 2 と重なる領域に位置している。図 6 に示すように、第 1 インダクタ I N D 1 は、第 1 多層配線層 M I N C 1 を用いて形成されている。言い換えると、第 1 インダクタ I N D 1 と同一層には、配線 (図示せず) またはビアが形成されている。第 1 多層配線層 M I N

10

20

30

40

50

C 1 は、第 1 基板 S U B 1 上に形成されている。第 1 基板 S U B 1 は、例えばシリコン基板などの半導体基板である。なお、第 1 基板 S U B 1 には、第 1 トランジスタ T R 1 及び第 2 トランジスタ T R 2 が形成されている。また、第 1 インダクタ I N D 1 の巻軸は、第 1 基板 S U B 1 に交わる方向（例えば垂直な方向）を向いている。

#### 【 0 0 3 9 】

なお、図 5 及び図 6 に示すように、第 1 半導体チップ S C 1 のうち平面視で第 2 半導体チップ S C 2 と重なる領域には、第 1 凹部 D E P 1 が形成されている。第 1 凹部 D E P 1 の幅は、第 2 半導体チップ S C 2 の幅よりも大きい。このため、第 1 半導体チップ S C 1 と第 2 半導体チップ S C 2 を重ねたとき、第 2 半導体チップ S C 2 は第 1 凹部 D E P 1 に嵌る。なお、第 2 半導体チップ S C 2 の一部は辺 S I D 2 から第 1 半導体チップ S C 1 の外側に食み出す必要があるため、第 1 凹部 D E P 1 は、辺 S I D 2 に繋がっている。10

#### 【 0 0 4 0 】

第 1 凹部 D E P 1 は、第 1 半導体チップ S C 1 が有する第 1 多層配線層 M I N C 1 のうち、第 1 インダクタ I N D 1 が形成されている層よりも上に位置する配線層の少なくとも一層（第 1 電極パッド P A D 1 1 及び第 1 電極パッド P A D 1 2 が形成されている層を含む）を部分的に形成しないことによって、形成されている。これにより、第 1 インダクタ I N D 1 と、後述する第 2 インダクタ I N D 2 の距離を近くして、これらの間の通信の精度を高めることができる。なお、第 1 半導体チップ S C 1 は第 1 凹部 D E P 1 を有していないなくても良い。

#### 【 0 0 4 1 】

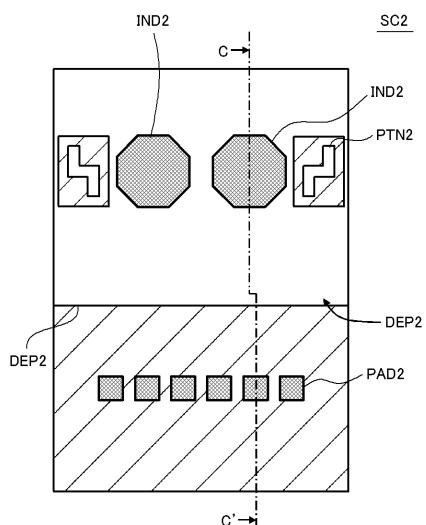

図 7 は、第 2 半導体チップ S C 2 の構造の一例を示す平面図である。図 8 は、図 7 の C - C' 断面図である。第 2 半導体チップ S C 2 は、少なくとも一つの第 2 インダクタ I N D 2（本図に示す例では 2 つ）を有している。第 2 インダクタ I N D 2 の数は、第 1 インダクタ I N D 1 の数と同じである。第 2 インダクタ I N D 2 は、第 2 半導体チップ S C 2 が第 1 半導体チップ S C 1 の上に配置されたときに、第 1 インダクタ I N D 1 と重なる位置に形成されている。これにより、第 2 半導体チップ S C 2 は、第 1 半導体チップ S C 1 と絶縁した状態で、第 2 インダクタ I N D 2 及び第 1 インダクタ I N D 1 を介して、第 2 半導体チップ S C 2 と通信することができる。

#### 【 0 0 4 2 】

図 8 に示すように、第 2 インダクタ I N D 2 は、第 2 多層配線層 M I N C 2 を用いて形成されている。第 2 多層配線層 M I N C 2 は、第 2 基板 S U B 2 上に形成されている。第 2 基板 S U B 2 は、例えばシリコン基板などの半導体基板である。第 2 基板 S U B 2 には、回路を形成している素子（例えばM O S トランジスタ）が形成されている。また、第 2 インダクタ I N D 2 の中心軸は、第 2 基板 S U B 2 に交わる方向（例えば垂直な方向）を向いている。30

#### 【 0 0 4 3 】

なお、図 7 及び図 8 に示すように、第 2 半導体チップ S C 2 のうち平面視で第 1 半導体チップ S C 1 と重なる領域には、第 2 凹部 D E P 2 が形成されている。第 2 凹部 D E P 2 は、第 2 半導体チップ S C 2 の 3 辺に繋がっている。

#### 【 0 0 4 4 】

第 2 凹部 D E P 2 は、第 2 半導体チップ S C 2 が有する第 2 多層配線層 M I N C 2 のうち、第 2 インダクタ I N D 2 が形成されている層よりも上に位置する配線層の少なくとも一層（第 2 電極パッド P A D 2 が形成されている層を含む）を部分的に形成しないことによって、形成されている。これにより、第 2 インダクタ I N D 2 と第 1 インダクタ I N D 1 の距離を近くして、これらの間の通信の精度を高めることができる。なお、第 2 半導体チップ S C 2 は第 2 凹部 D E P 2 を有しなくてもよい。

#### 【 0 0 4 5 】

また、第 2 基板 S U B 2 の厚さは、第 1 基板 S U B 1 よりも厚い。これにより、第 2 半導体チップ S C 2 は第 1 半導体チップ S C 1 よりも厚くなっている。第 2 基板 S U B 2 の厚さは、例えば 3 0 0  $\mu$ m 以上 5 0 0  $\mu$ m 以下であり、第 1 基板 S U B 1 の厚さは、例え50

ば 100 μm 以上 300 μm 以下である。

**【0046】**

図9は、固定層FR2の形状の第1例を示す断面図である。本図に示す例において、フィレットFR21は、第2半導体チップSC2の保護層PR1よりも高くなっている。また、固定層FR2の一部は、第1半導体チップSC1の辺SID2側の側面に食み出し、フィレットFR22を形成している。このように、固定層FR2がフィレットFR22も形成しているため、第1半導体チップSC1に対する第2半導体チップSC2の固着力は大きくなる。これにより、後述するように、第2ポンディングワイヤWIR2を第2半導体チップSC2に取り付ける工程において、第2半導体チップSC2が第1半導体チップSC1から外れることを抑制できる。また、フィレットFR21, FR22が形成されることにより、第2半導体チップSC2が応力に起因して反ることを抑制できる。

10

**【0047】**

また、第2半導体チップSC2と第1半導体チップSC1の間で絶縁破壊が生じることも抑制できる。詳細には、第2半導体チップSC2と第1半導体チップSC1の間の絶縁破壊の起点は、第2半導体チップSC2の第1半導体チップSC1との距離が短い部分である。本実施形態では、第2半導体チップSC2の側面のうち第1半導体チップSC1の上に位置する部分を、フィレットFR21によって覆っている。このため、第2半導体チップSC2の側面を起点として第1半導体チップSC1と第2半導体チップSC2の間で絶縁破壊が生じることを、抑制できる。

**【0048】**

図10は、固定層FR2の形状の第2例を示す断面図である。本図に示す例は、フィレットFR21が保護層PR1に達していない点を除いて、図9に示した例と同様である。

**【0049】**

図11は、固定層FR2の形状の第3例を示す断面図である。本図に示す例は、フィレットFR21の一部は保護層PR1よりも高くなっているが、フィレットFR21の残りの部分が保護層PR1に達していない点を除いて、図9に示した例と同様である。

**【0050】**

図12～図15の各図は、半導体装置SDの製造方法を説明するための断面図である。まず、第1半導体チップSC1及び第2半導体チップSC2を製造する。第1半導体チップSC1及び第2半導体チップSC2は、例えば以下のようにして製造される。

30

**【0051】**

まず、ウェハ状態の第1基板SUB1（又は第2基板SUB2）に素子分離膜を形成する。これにより、素子形成領域が分離される。素子分離膜は、例えばSTI法を用いて形成されるが、LOCOS法を用いて形成されても良い。次いで、素子形成領域に位置する半導体基板に、ゲート絶縁膜及びゲート電極を形成する。ゲート絶縁膜は酸化シリコン膜であってもよいし、酸化シリコン膜よりも誘電率が高い高誘電率膜（例えばハフニウムシリケート膜）であってもよい。ゲート絶縁膜が酸化シリコン膜である場合、ゲート電極はポリシリコン膜により形成される。またゲート絶縁膜が高誘電率膜である場合、ゲート電極は、金属膜（例えばTiN）とポリシリコン膜の積層膜により形成される。また、ゲート電極がポリシリコンにより形成される場合、ゲート電極を形成する工程において、素子分離膜上にポリシリコン抵抗を形成しても良い。

40

**【0052】**

次いで、素子形成領域に位置する半導体基板に、ソース及びドレインのエクステンション領域を形成する。次いでゲート電極の側壁にサイドウォールを形成する。次いで、素子形成領域に位置する半導体基板に、ソース及びドレインとなる不純物領域を形成する。このようにして、半導体基板上にMOSトランジスタが形成される。

**【0053】**

また、第1半導体チップSC1の製造工程においては、上記した工程の少なくとも一部を用いることにより、第1トランジスタTR1及び第2トランジスタTR2が形成される。

50

## 【0054】

次いで、素子分離膜上及びMOSトランジスタ上に、第1多層配線層MINC1（または第2多層配線層MINC2）を形成する。最上層の配線層には、第1電極パッドPAD11, PAD12（又は第2電極パッドPAD2）が形成される。次いで、多層配線層上に、保護絶縁膜（パッシベーション膜）を形成する。保護絶縁膜には、電極パッド上に位置する開口が形成される。

## 【0055】

その後、第1半導体チップSC1となるウェハを個片化することにより、第1半導体チップSC1が形成される。

## 【0056】

また、第2半導体チップSC2となるウェハについては、図12(a)に示すように、ウェハのうち第2半導体チップSC2の第4正面SFC4となる面に、保護層PR1を貼り付ける。また、第2電極パッドPAD2のそれぞれの上に、バンプBMPを形成する。バンプBMPは、例えは金など、第2ボンディングワイヤWIR2と接合しやすい金属を用いて形成されている。

## 【0057】

次いで、図12(b)にしめすように、第2半導体チップSC2となるウェハを、保護層PR1とともに個片化する。これにより、第2半導体チップSC2が、保護層PR1が設けられた状態で製造される。

## 【0058】

なお、第1半導体チップSC1を個片化する前に、必要に応じて第1半導体チップSC1の第1基板SUB1を研磨して薄くする。同様に、第2半導体チップSC2に保護層PR1を設ける前に、必要に応じて第2半導体チップSC2の第2基板SUB2を研磨して薄くする。

## 【0059】

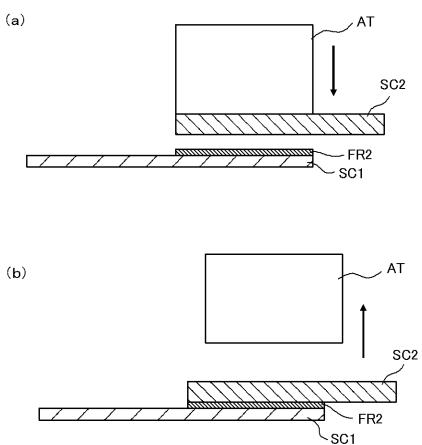

次いで、図13(a)に示すように、第1半導体チップSC1の第1正面SFC1うち第2半導体チップSC2が搭載される領域の上に、固定層FR2を設ける。次いで、図13(b)に示すように、第1半導体チップSC1の上に第2半導体チップSC2を搭載する。このとき、第2半導体チップSCの第3正面SFC3を、固定層FR2に対向するようとする。また、このとき、第2半導体チップSC2のバンプBMPが第1半導体チップSC1又は固定層FR2で覆われないようにする。

## 【0060】

次いで、図14(a)に示すように、リードフレームのチップ搭載部DPに、固定層FR1を用いて、第1半導体チップSC1及び第2半導体チップSC2の積層体を搭載する。このとき、チップ搭載部DPの切欠部CPと第2半導体チップSC2のバンプBMPが重なるようにする。

## 【0061】

次いで、図14(b)に示すように、第1ボンディングワイヤWIR1を用いて、第1半導体チップSC1の第1電極パッドPAD11及び第1電極パッドPAD12を、第1リード端子LT1に接続する。このとき、第1ボンディングワイヤWIR1の一端を第1電極パッドPAD11（又は第1電極パッドPAD12）に固定してから、第1ボンディングワイヤWIR1の他端を第1リード端子LT1に固定する。

## 【0062】

その後、図14(c)に示すように、リードフレームの上下を逆にする。

## 【0063】

次いで、図15(a)に示すように、第2ボンディングワイヤWIR2を用いて、第2半導体チップSC2の第2電極パッドPAD2を第2リード端子LT2に接続する。このとき、第2ボンディングワイヤWIR2の他端を第2リード端子LT2に固定してから、第2ボンディングワイヤWIR2の一端をバンプBMP（すなわち第2電極パッドPAD2）に固定する。なお、この工程を行うためには、リードフレームを保持するステージに

10

20

30

40

50

も、切欠部 C P と同様の切り欠きを設ける必要がある。

【 0 0 6 4 】

この工程において、第 2 電極パッド P A D 2 の上には予めバンプ B M P が形成されている。このため、第 2 ボンディングワイヤ W I R 2 の一端を第 2 電極パッド P A D 2 に強く押し付けなくても、第 2 ボンディングワイヤ W I R 2 の一端を第 2 電極パッド P A D 2 に接続することができる。従って、第 2 ボンディングワイヤ W I R 2 を第 2 電極パッド P A D 2 に固定するときに、第 2 半導体チップ S C 2 が第 1 半導体チップ S C 1 から外れることを抑制できる。

【 0 0 6 5 】

また、第 2 ボンディングワイヤ W I R 2 の一端を第 2 電極パッド P A D 2 に取り付けてから第 2 ボンディングワイヤ W I R 2 の他端を第 2 リード端子 L T 2 に取り付ける場合、第 2 ボンディングワイヤ W I R 2 を第 2 電極パッド P A D 2 に取り付けてから第 2 リード端子 L T 2 に取り付けるまでの間に、第 2 ボンディングワイヤ W I R 2 を介して第 2 半導体チップ S C 2 に力が加わる可能性が出てくる。この場合、第 2 半導体チップ S C 2 が第 1 半導体チップ S C 1 から外れる可能性が出てくる。本実施形態では、第 2 ボンディングワイヤ W I R 2 を第 2 リード端子 L T 2 に取り付けてから第 2 電極パッド P A D 2 に取り付けているため、このような問題が生じることを抑制できる。10

【 0 0 6 6 】

また、第 2 半導体チップ S C 2 は第 1 半導体チップ S C 1 よりも厚くなっている。従って、第 2 半導体チップ S C 2 に第 2 ボンディングワイヤ W I R 2 を取り付けるときに、第 2 半導体チップ S C 2 が破損することを抑制できる。20

【 0 0 6 7 】

その後、図 15 ( b ) に示すように、リードフレームの上下を逆にする。これにより、リードフレームの搬送は容易になる。次いで、封止用の金型を用いて、封止樹脂 M D R を形成する。

【 0 0 6 8 】

次いで、図 15 ( c ) に示すように、第 1 リード端子 L T 1 及び第 2 リード端子 L T 2 のうち封止樹脂 M D R の外に位置している部分を変形し、端子とする。

【 0 0 6 9 】

なお、第 1 半導体チップ S C 1 をチップ搭載部 D P 上に搭載した後に、第 2 半導体チップ S C 2 を第 1 半導体チップ S C 1 に搭載しても良い。30

【 0 0 7 0 】

図 16 及び図 17 は、図 13 ( a ) 及び ( b ) に示した工程の詳細を示すフローチャートである。まず、図 16 ( a ) に示すように、組立装置 A T を用いて、所定の形状にカットされたシート状の固定層 F R 2 を保持（例えば吸着）する。この状態において、固定層 F R 2 のうち組立装置 A T によって保持される面には、カバーフィルム C F が設けられている。次いで、組立装置 A T を用いて、固定層 F R 2 を第 1 半導体チップ S C 1 のうち第 2 半導体チップ S C 2 が搭載される領域に押し付ける。

【 0 0 7 1 】

次いで、図 16 ( b ) に示すように、組立装置 A T を、カバーフィルム C F を吸着した状態で上昇させる。これにより、固定層 F R 2 からカバーフィルム C F が外される。40

【 0 0 7 2 】

次いで、図 17 ( a ) に示すように、組立装置 A T に第 2 半導体チップ S C 2 を保持させる。組立装置 A T は、例えば第 2 半導体チップ S C 2 の第 4 主面 S F C 4 を吸着する。このとき、第 4 主面 S F C 4 は保護層 P R 1 によって覆われているため、第 4 主面 S F C 4 には傷が付かない。

【 0 0 7 3 】

次いで、組立装置 A T を用いて、第 2 半導体チップ S C 2 を固定層 F R 2 に押し付ける。これにより、第 2 半導体チップ S C 2 は第 1 半導体チップ S C 1 上に固定される。またこのとき、固定層 F R 2 には、フィレット F R 2 1 , F R 2 2 が形成される。50

**【 0 0 7 4 】**

その後、図17(b)に示すように、組立装置ATから第2半導体チップSC2を離す。

**【 0 0 7 5 】**

次に、本実施形態の効果について説明する。本実施形態において、チップ搭載部DPには切欠部CPが形成されている。そして平面視において、第2半導体チップSC2の第2電極パッドPAD2は、切欠部CPと重なっている。従って、第2電極パッドPAD2に第2ボンディングワイヤWIR2の一端を取り付けるときに、ボンディングツールとチップ搭載部DPが干渉することを抑制できる。

**【 0 0 7 6 】**

また、複数の第2ボンディングワイヤWIR2のうち端に位置する第2ボンディングワイヤWIR21(例えは図3において右端に位置する第2ボンディングワイヤWIR2及び左端に位置する第2ボンディングワイヤWIR2)は、チップ搭載部DPの辺SID1に対して斜めに延在している。このため、第2ボンディングワイヤWIR21またはこれを取り付けるためのボンディングツールは、切欠部CPの端部TPに接触する可能性が出てくる。これに対して本実施形態では、切欠部CPの端部TPにはテーパが設けられている。従って、第2ボンディングワイヤWIR21またはこれを取り付けるためのボンディングツールが、切欠部CPの端部TPに接触することを抑制できる。

**【 0 0 7 7 】****(変形例)**

図18は、変形例に係る第1半導体チップSC1の平面図であり、図19は、変形例に係る第2半導体チップSC2の平面図である。本変形例に係る半導体装置SDは、第1半導体チップSC1の第1主面SFC1に凸部PTN1が形成されており、第2半導体チップSC2の第2主面SFC2に凹部PTN2が形成されている点を除いて、実施形態に係る半導体装置SDと同様の構成である。

**【 0 0 7 8 】**

凸部PTN1は第1半導体チップSC1の第1多層配線層MINC1、又はその上の保護絶縁膜を用いて形成されており、凹部PTN2は第2半導体チップSC2の第2多層配線層MINC2、又はその上の保護絶縁膜を用いて形成されている。具体的には、凸部PTN1は、第1半導体チップSC1の最表層の少なくとも一層において、凸部PTN1の周囲に位置する部分を除去することによって、形成されている。また、凹部PTN2は、第1半導体チップSC1の最表層の少なくとも一層において、凹部PTN2となる領域を除去することによって、形成されている。

**【 0 0 7 9 】**

凹部PTN2の平面形状は凸部PTN1の平面形状と同様である。そして、第1半導体チップSC1と第2半導体チップSC2を重ねた状態において、凸部PTN1は凹部PTN2と重なっている。凸部PTN1の少なくとも上部は、凹部PTN2に嵌っていても良い。

**【 0 0 8 0 】**

本変形例によても、実施形態と同様の効果が得られる。また、凸部PTN1と凹部PTN2の位置を重ねることにより、第1半導体チップSC1と第2半導体チップSC2の相対位置の精度を高めることができる。これによって、第1インダクタIND1と第2インダクタIND2の間で通信エラーが生じることを抑制できる。特に、凸部PTN1の少なくとも上部が凹部PTN2に嵌るようにした場合、第1半導体チップSC1と第2半導体チップSC2の相対位置の精度は特に高くなる。

**【 0 0 8 1 】**

なお、第1半導体チップSC1の第1主面SFC1に凹部が形成され、第2半導体チップSC2の第3主面SFC3に凸部が形成されている場合でも、本変形例と同様の効果が得られる。

**【 0 0 8 2 】**

10

20

30

40

50

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

## 【符号の説明】

## 【0083】

|           |          |    |

|-----------|----------|----|

| A T       | 組立装置     |    |

| B M P     | バンプ      |    |

| B P 1     | 屈曲点      |    |

| B P 2     | 屈曲点      |    |

| C F       | カバーフィルム  | 10 |

| C P       | 切欠部      |    |

| D E P 1   | 第1凹部     |    |

| D E P 2   | 第2凹部     |    |

| D P       | チップ搭載部   |    |

| D P       | 素子搭載部    |    |

| F R 1     | 固定層      |    |

| F R 2     | 固定層      |    |

| I N D 1   | 第1インダクタ  |    |

| I N D 2   | 第2インダクタ  |    |

| L C       | 端子接続部    | 20 |

| L T 1     | 第1リード端子  |    |

| L T 2     | 第2リード端子  |    |

| L T 3     | 第3リード端子  |    |

| M D R     | 封止樹脂     |    |

| M I N C 1 | 第1多層配線層  |    |

| M I N C 2 | 第2多層配線層  |    |

| M L 1     | 金属層      |    |

| M L 2     | 金属層      |    |

| P A D 1 1 | 第1電極パッド  |    |

| P A D 1 2 | 第1電極パッド  | 30 |

| P A D 2   | 第2電極パッド  |    |

| P H       | 樹脂保持部    |    |

| P R 1     | 保護層      |    |

| F R 2     | 固定層      |    |

| F R 2 1   | フィレット    |    |

| F R 2 2   | フィレット    |    |

| P T N 1   | 凸部       |    |

| P T N 2   | 凹部       |    |

| S I D 1   | 辺        |    |

| S I D 2   | 辺        | 40 |

| S C 1     | 第1半導体チップ |    |

| S C 2     | 第2半導体チップ |    |

| S D       | 半導体装置    |    |

| S F C 1   | 第1主面     |    |

| S F C 2   | 第2主面     |    |

| S F C 3   | 第3主面     |    |

| S F C 4   | 第4主面     |    |

| S U B 1   | 第1基板     |    |

| S U B 2   | 第2基板     |    |

| T P       | 端部       | 50 |

T R 1 第1トランジスタ

T R 2 第2トランジスタ

W I R 1 第1ボンディングワイヤ

W I R 2 第2ボンディングワイヤ

W I R 2 1 第2ボンディングワイヤ

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

---

フロントページの続き

(72)発明者 菅野 正人

神奈川県川崎市中原区下沼部1753番地 ルネサスエレクトロニクス株式会社内

(72)発明者 米澤 美香

神奈川県川崎市中原区下沼部1753番地 ルネサスエレクトロニクス株式会社内

(72)発明者 帰山 隼一

神奈川県川崎市中原区下沼部1753番地 ルネサスエレクトロニクス株式会社内

(72)発明者 清原 俊範

神奈川県川崎市中原区下沼部1753番地 ルネサスエレクトロニクス株式会社内

審査官 梅本 章子

(56)参考文献 特開2011-054800(JP,A)

特開2000-156464(JP,A)

特開平08-130284(JP,A)

特開2003-068975(JP,A)

米国特許第06476474(US,B1)

特開2008-091627(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/60 - 21/607

H01L 23/12 - 23/15

H01L 23/50

H01L 25/00 - 25/18