(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6843550号

(P6843550)

(45) 発行日 令和3年3月17日(2021.3.17)

(24) 登録日 令和3年2月26日(2021.2.26)

(51) Int.Cl.

F 1

G09G 3/36 (2006.01)

G09G 3/36

G02F 1/133 (2006.01)

G02F 1/133 505

G09G 3/20 (2006.01)

G09G 3/20 612L

G09G 3/20 612P

G09G 3/20 621A

請求項の数 18 (全 24 頁) 最終頁に続く

(21) 出願番号

特願2016-161390 (P2016-161390)

(22) 出願日

平成28年8月19日(2016.8.19)

(65) 公開番号

特開2018-28640 (P2018-28640A)

(43) 公開日

平成30年2月22日(2018.2.22)

審査請求日

平成30年8月8日(2018.8.8)

審判番号

不服2019-13031 (P2019-13031/J1)

審判請求日

令和1年10月1日(2019.10.1)

(73) 特許権者 308017571

シナプティクス・ジャパン合同会社

東京都中野区中野四丁目10番2号

(74) 代理人 100205350

弁理士 狩野 芳正

(72) 発明者 黒岩 剛史

東京都中野区中野4丁目10番2号 シナ

プティクス・ジャパン合同会社内

## 合議体

審判長 中塚 直樹

審判官 濱野 隆

審判官 岸 智史

最終頁に続く

(54) 【発明の名称】表示ドライバ及び表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

表示パネルを駆動する表示ドライバであって、

当該表示ドライバの外部から供給され、垂直同期期間の開始を指示する垂直同期期間開始指示に応答して垂直同期ソース信号を生成するように構成された同期抽出回路と、

前記垂直同期ソース信号に応答して内部垂直同期信号を生成するタイミング生成回路と、

前記内部垂直同期信号に同期して前記表示パネルを駆動する駆動回路とを具備し、

前記タイミング生成回路は、前記垂直同期ソース信号のアサートに応答して前記内部垂直同期信号をアサートするように構成され、

前記同期抽出回路は、前記垂直同期期間開始指示を検出したときに前記垂直同期ソース信号をアサートするように構成され、且つ、

前記同期抽出回路は、前記垂直同期ソース信号の前回のアサートの後、前記垂直同期期間開始指示を検出しないとき、所定時間が経過した場合に、前記垂直同期ソース信号をアサートするように構成された

表示ドライバ。

## 【請求項 2】

請求項 1 に記載の表示ドライバであって、

前記同期抽出回路は、

10

20

前記垂直同期期間開始指示を検出して垂直同期期間開始指示検出信号を生成するよう

に構成された垂直同期期間開始指示検出部と、

カウント動作を行うカウンタを備えると共に、前記カウンタが保持するカウント値に

応じて垂直同期疑似信号を生成するように構成された垂直同期疑似信号生成部と、

前記垂直同期期間開始指示検出信号と前記垂直同期疑似信号とに応じて前記垂直同期

ソース信号を生成する論理回路部

とを備える

表示ドライバ。

#### 【請求項 3】

請求項 2 に記載の表示ドライバであって、

前記垂直同期期間開始指示検出部は、前記垂直同期期間開始指示を検出すると前記垂直

同期期間開始指示検出信号をアサートするように構成され、

前記カウンタは、前記カウント値をカウントアップするように構成され、

前記垂直同期疑似信号生成部は、前記カウント値の所定の上限値への到達に応答して前記

垂直同期疑似信号をアサートするように構成され、

前記論理回路部は、前記垂直同期期間開始指示検出信号のアサートと前記垂直同期疑似

信号のアサートとに応答して前記垂直同期ソース信号をアサートするように構成され、

前記カウンタは、前記垂直同期期間開始指示検出信号のアサートに応答して前記所定の

リセット値にリセットされると共に、前記垂直同期疑似信号のアサートに応答して前記カ

ウント値が前記リセット値より大きい所定値にセットされるように構成された

表示ドライバ。

#### 【請求項 4】

請求項 3 に記載の表示ドライバであって、

前記論理回路部は、前記カウント値が所定の下限値に到達していない場合、前記垂直

同期ソース信号をアサートしない

表示ドライバ。

#### 【請求項 5】

請求項 2 に記載の表示ドライバであって、

前記垂直同期期間開始指示検出部は、前記垂直同期期間開始指示を検出すると前記垂直

同期期間開始指示検出信号をアサートするように構成され、

前記カウンタは、前記カウント値をカウントダウンするように構成され、

前記垂直同期疑似信号生成部は、前記カウント値の所定の下限値への到達に応答して前記

垂直同期疑似信号をアサートするように構成され、

前記論理回路部は、前記垂直同期期間開始指示検出信号のアサートと前記垂直同期疑似

信号のアサートとに応答して前記垂直同期ソース信号をアサートするように構成され、

前記カウンタは、前記垂直同期期間開始指示検出信号のアサートに応答して前記所定の

リセット値にリセットされると共に、前記垂直同期疑似信号のアサートに応答して前記カ

ウント値が前記リセット値より小さい所定値にセットされるように構成された

表示ドライバ。

#### 【請求項 6】

請求項 5 に記載の表示ドライバであって、

前記論理回路部は、前記カウント値が所定の上限値に到達していない場合、前記垂直

同期ソース信号をアサートしない

表示ドライバ。

#### 【請求項 7】

請求項 3 又は 4 に記載の表示ドライバであって、

更に、

前記上限値を保持する上限値レジスタを備える

表示ドライバ。

#### 【請求項 8】

10

20

30

40

50

請求項 7 に記載の表示ドライバであって、

前記上限値レジスタに保持されている前記上限値が、当該表示ドライバの外部から書き

換え可能である

表示ドライバ。

## 【請求項 9】

請求項 1 乃至 8 のいずれかに記載の表示ドライバであって、

前記垂直同期期間開始指示は、当該表示ドライバに供給される垂直同期パケットを含む

表示ドライバ。

## 【請求項 10】

請求項 1 に記載の表示ドライバであって、

前記同期抽出回路は、当該表示ドライバの外部から供給され、水平同期期間の開始を指

示する水平同期期間開始指示に応答して水平同期ソース信号を生成するように構成され、

前記タイミング生成回路は、前記水平同期ソース信号に応答して内部水平同期信号を生

成するように構成され、

前記駆動回路は、前記内部水平同期信号に同期して前記表示パネルを駆動し、

前記タイミング生成回路は、前記水平同期ソース信号のアサートに応答して前記内部水

平同期信号をアサートするように構成され、

前記同期抽出回路は、前記水平同期期間開始指示を検出したときに前記水平同期ソース

信号をアサートするように構成されると共に、前記水平同期ソース信号の前回のアサート

の後、前記水平同期期間開始指示を検出しないとき、所定時間が経過した場合に、前記水

平同期ソース信号をアサートするように構成された

表示ドライバ。

## 【請求項 11】

表示パネルを駆動する表示ドライバであって、

当該表示ドライバの外部から供給され、水平同期期間の開始を指示する水平同期期間開

始指示に応答して水平同期ソース信号を生成するように構成された同期抽出回路と、

前記水平同期ソース信号に応答して内部水平同期信号を生成するタイミング生成回路と

、

前記内部水平同期信号に同期して前記表示パネルを駆動する駆動回路

とを具備し、

前記タイミング生成回路は、前記水平同期ソース信号のアサートに応答して前記内部水

平同期信号をアサートするように構成され、

前記同期抽出回路は、前記水平同期期間開始指示を検出したときに前記水平同期ソース

信号をアサートするように構成されると共に、前記水平同期ソース信号の前回のアサート

の後、前記水平同期期間開始指示を検出しないとき、所定時間が経過した場合に、前記水

平同期ソース信号をアサートするように構成された

表示ドライバ。

## 【請求項 12】

請求項 1 に記載の表示ドライバであって、

前記同期抽出回路は、

前記水平同期期間開始指示を検出して水平同期期間開始指示検出信号を生成するよう

に構成された水平同期期間開始指示検出部と、

カウント動作を行うカウンタを備えると共に、前記カウンタが保持するカウント値に

応じて水平同期疑似信号を生成するように構成された水平同期疑似信号生成部と、

前記水平同期期間開始指示検出信号と前記水平同期疑似信号とに応じて前記水平同期

ソース信号を生成する論理回路部

とを備える

表示ドライバ。

## 【請求項 13】

請求項 1 に記載の表示ドライバであって、

10

20

30

40

50

前記水平同期期間開始指示検出部は、前記水平同期期間開始指示を検出すると前記水平同期期間開始指示検出信号をアサートするように構成され、

前記カウンタは、前記カウント値をカウントアップするように構成され、

前記水平同期疑似信号生成部は、前記カウント値の所定の上限値への到達に応答して前記水平同期疑似信号をアサートするように構成され、

前記論理回路部は、前記水平同期期間開始指示検出信号のアサートと前記水平同期疑似信号のアサートとに応答して前記水平同期ソース信号をアサートするように構成され、

前記カウンタは、前記水平同期期間開始指示検出信号のアサートに応答して前記所定のリセット値にリセットされると共に、前記水平同期疑似信号のアサートに応答して前記カウント値が前記リセット値より大きい所定値にセットされるように構成された

10

表示ドライバ。

#### 【請求項 1 4】

請求項 1 3 に記載の表示ドライバであって、

前記論理回路部は、前記カウント値が所定の下限値に到達していない場合、前記水平同期ソース信号をアサートしない

表示ドライバ。

#### 【請求項 1 5】

請求項 1 2 に記載の表示ドライバであって、

前記水平同期期間開始指示検出部は、前記水平同期期間開始指示を検出すると前記水平同期期間開始指示検出信号をアサートするように構成され、

20

前記カウンタは、前記カウント値をカウントダウンするように構成され、

前記水平同期疑似信号生成部は、前記カウント値の所定の下限値への到達に応答して前記水平同期疑似信号をアサートするように構成され、

前記論理回路部は、前記水平同期期間開始指示検出信号のアサートと前記水平同期疑似信号のアサートとに応答して前記水平同期ソース信号をアサートするように構成され、

前記カウンタは、前記水平同期期間開始指示検出信号のアサートに応答して前記所定のリセット値にリセットされると共に、前記水平同期疑似信号のアサートに応答して前記カウント値が前記リセット値より小さい所定値にセットされるように構成された

表示ドライバ。

#### 【請求項 1 6】

30

請求項 1 5 に記載の表示ドライバであって、

前記論理回路部は、前記カウント値が所定の上限値に到達していない場合、前記水平同期ソース信号をアサートしない

表示ドライバ。

#### 【請求項 1 7】

請求項 1 1 乃至 1 6 のいずれかに記載の表示ドライバであって、

前記水平同期期間開始指示は、当該表示ドライバに供給される水平同期パケットを含む表示ドライバ。

#### 【請求項 1 8】

請求項 1 乃至 1 7 のいずれかに記載の表示ドライバと、

40

表示パネル

とを具備する

表示装置。

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0 0 0 1】

本発明は、表示ドライバ及び表示装置に関し、特に、表示ドライバ及び表示装置の同期（例えば、垂直同期及び水平同期）のための技術に関する。

#### 【背景技術】

#### 【0 0 0 2】

50

表示装置（例えば、液晶表示装置やO L E D（organic light emitting diode）表示装置）では、一般に、同期の確立、より具体的には、垂直同期及び水平同期の確立が求められる。垂直同期及び水平同期を確立する最も伝統的な方法は、垂直同期信号及び水平同期信号を使用する方法である。このアーキテクチャでは、垂直同期信号によって垂直同期期間の開始が指示され、水平同期信号によって水平同期信号の開始が指示される。例えば、パネル表示装置については、表示パネルを駆動する表示ドライバに垂直同期信号及び水平同期信号を供給し、該表示ドライバが垂直同期信号及び水平同期信号に同期して動作することで、垂直同期及び水平同期が確立される。

#### 【0003】

近年の表示装置では、垂直同期期間及び水平同期期間の開始を指示するために、特定のパケットを該表示ドライバに送信するアーキテクチャがしばしば採用される。例えば、M I P I D S I（Mobile Industry Processor Interface Display Serial Interface）は、このようなアーキテクチャを採用する典型的な規格である。M I P I D S Iでは、V s y n c パケット（Vsync packet）が垂直同期期間の開始を指示するパケットとして規定され、H s y n c パケット（Hsync packet）が水平同期期間の開始を指示するパケットとして規定される。本願においては、垂直同期期間の開始を指示するパケットを垂直同期パケットと呼び、本願においては、水平同期期間の開始を指示するパケットを水平同期パケットと呼ぶことがある。最も典型的な構成では、表示ドライバの内部において内部垂直同期信号が垂直同期パケットに応じて生成され、内部水平同期信号が水平同期パケットに応じて生成される。表示ドライバの各回路は、生成された内部垂直同期信号及び内部水平同期信号に同期して動作する。

10

20

#### 【0004】

このようなアーキテクチャには、信号線の数を低減できる利点がある。垂直同期信号及び水平同期信号を供給する構成では、垂直同期信号及び水平同期信号を供給するための専用の信号線が必要となり、信号線の数が増大する。垂直同期信号及び水平同期信号の代わりに、垂直同期期間及び水平同期期間の開始タイミングを示す垂直同期パケット及び水平同期パケットをデータインターフェースによって伝送することで、専用の信号線を設ける必要性が無くなり、信号線の数を低減できる。

#### 【0005】

表示装置における同期の確立において生じ得る問題の一つは、同期の確立に関する信号線にノイズが印加されると、同期の確立が妨げられる可能性があることである。

30

#### 【0006】

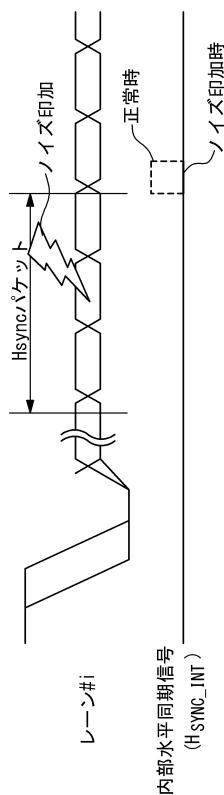

例えば、図1は、水平同期パケットを用いて水平同期を確立するアーキテクチャを採用する表示装置、より具体的には、M I P I D S Iに準拠したシリアルインターフェースを用いた表示装置において、レーン# iによって水平同期パケットを伝送する場合の動作の一例を示すタイミングチャートである。

#### 【0007】

水平同期期間の開始時に水平同期パケットが表示ドライバに伝送される。表示装置が正常に動作している場合、水平同期パケットが表示ドライバに供給されると、表示ドライバの内部では、該水平同期パケットに同期して内部水平同期信号がアサートされる。表示ドライバの各回路は、内部水平同期信号のアサートに応答して所定の動作を行う。

40

#### 【0008】

しかしながら、例えばレーン# iに高電圧のノイズが印加されることによって表示ドライバが水平同期パケットの受信に失敗すると、内部水平同期信号が適切なタイミングでアサートされなくなり、水平同期の確立が妨げられる。垂直同期パケットについても同様である。表示ドライバが垂直同期パケットの受信に失敗すると、垂直同期の確立が妨げられる。

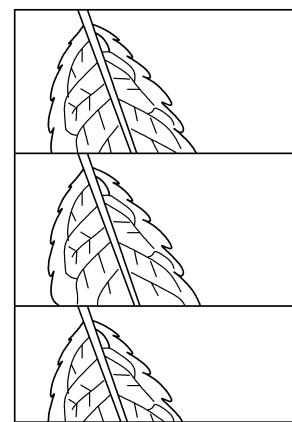

#### 【0009】

垂直同期パケット及び／又は水平同期パケットの受信に失敗し、垂直同期及び／又は水平同期の確立が妨げられると、表示パネルに表示される画像に乱れが発生することがある

50

。図2は、垂直同期及び水平同期の確立に失敗したときの表示画面の一例を示している。画像データパケットの受信に失敗した場合は、画像の乱れは、受信に失敗した画像データパケットに対応する画素に限定されるが、垂直同期パケット及び／又は水平同期パケットの受信の失敗の影響は表示画面の全体に及ぶことがあり、好ましくない。

#### 【0010】

垂直同期信号や水平同期信号を用いて垂直同期及び水平同期を確立するアーキテクチャについても同様である。垂直同期信号や水平同期信号を供給する信号線にノイズが印加されると、垂直同期及び水平同期の確立に失敗することがある。

#### 【0011】

以上から理解されるように、同期の確立の失敗に起因する表示の乱れの発生を抑制することには技術的ニーズが存在する。 10

#### 【0012】

なお、コマンドに応じた垂直同期信号の生成については、例えば、特開2014-115391号公報に開示されている。

#### 【先行技術文献】

#### 【特許文献】

#### 【0013】

#### 【特許文献1】特開2014-115391号公報

#### 【発明の概要】

#### 【発明が解決しようとする課題】 20

#### 【0014】

したがって、本発明の目的の一つは、同期の確立の失敗に起因する表示の乱れの発生を抑制することにある。本発明の他の目的は、下記の開示から当業者には理解されるであろう。

#### 【課題を解決するための手段】

#### 【0015】

本発明の一の観点では、表示パネルを駆動する表示ドライバが、当該表示ドライバの外部から供給され、垂直同期期間の開始を指示する垂直同期期間開始指示に応答して垂直同期ソース信号を生成するように構成された同期抽出回路と、垂直同期ソース信号に応答して内部垂直同期信号を生成するタイミング生成回路と、内部垂直同期信号に同期して表示パネルを駆動する駆動回路とを具備する。タイミング生成回路は、垂直同期ソース信号のアサートに応答して内部垂直同期信号をアサートするように構成される。同期抽出回路は、垂直同期期間開始指示を検出したときに垂直同期ソース信号をアサートするように構成されると共に、垂直同期ソース信号の前回のアサートの後、所定時間が経過した場合には垂直同期期間開始指示を検出しない場合でも垂直同期ソース信号をアサートするように構成されている。 30

#### 【0016】

本発明の他の観点では、表示パネルを駆動する表示ドライバが、当該表示ドライバの外部から供給され、水平同期期間の開始を指示する水平同期期間開始指示に応答して水平同期ソース信号を生成するように構成された同期抽出回路と、水平同期ソース信号に応答して内部水平同期信号を生成するタイミング生成回路と、内部水平同期信号に同期して表示パネルを駆動する駆動回路とを具備する。タイミング生成回路は、水平同期ソース信号のアサートに応答して内部水平同期信号をアサートするように構成される。同期抽出回路は、水平同期期間開始指示を検出したときに水平同期ソース信号をアサートするように構成されると共に、水平同期ソース信号の前回のアサートの後、所定時間の経過に応じて水平同期ソース信号をアサートするように構成されている。 40

#### 【0017】

このように構成された表示ドライバは、表示装置に好適に使用される。

#### 【発明の効果】

#### 【0018】

50

20

30

40

50

本発明によれば、同期の失敗に起因する表示の乱れの発生を抑制することができる。

**【図面の簡単な説明】**

**【0019】**

【図1】M I P I D S Iに準拠したシリアルインターフェースを用いた表示システムにおいて水平同期パケットを伝送する場合の動作の一例を示すタイミングチャートである。

【図2】垂直同期及び水平同期の確立に失敗したときの表示画面の一例を示している。

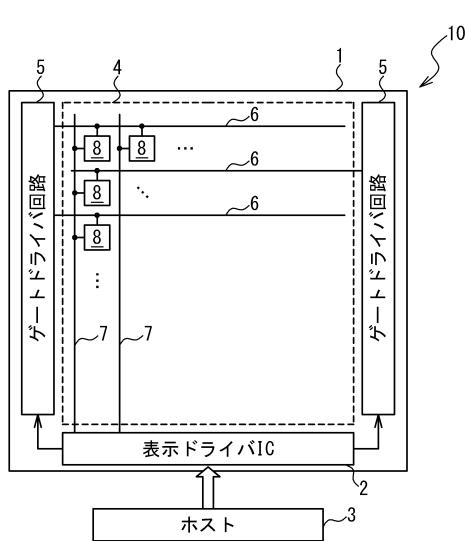

【図3】一実施形態における表示装置の構成を概略的に示すブロック図である。

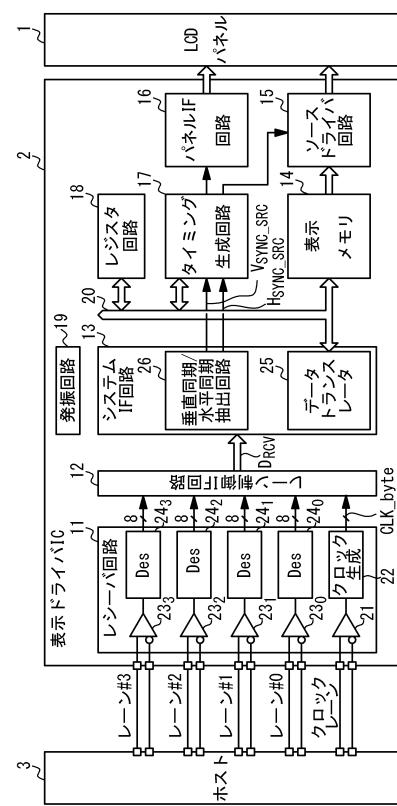

【図4】本実施形態における表示ドライバI Cの構成を概略的に示すブロック図である。

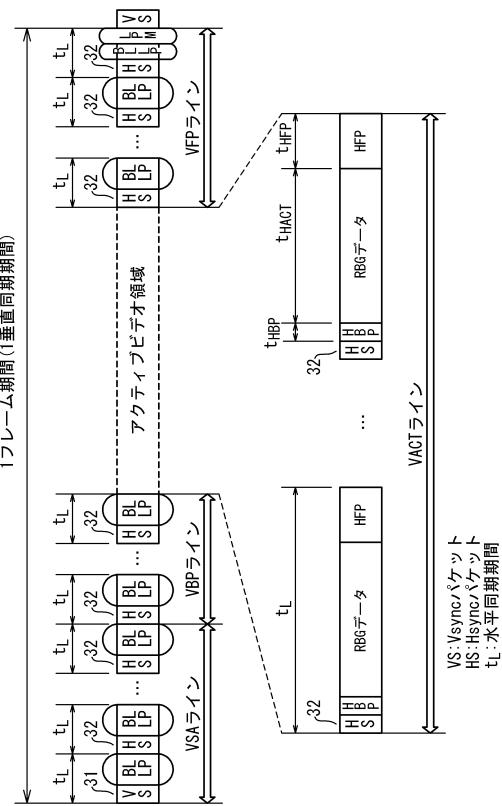

【図5】本実施形態における、ホストから表示ドライバI Cへの通信におけるデータストリームのフォーマットを示す図である。 10

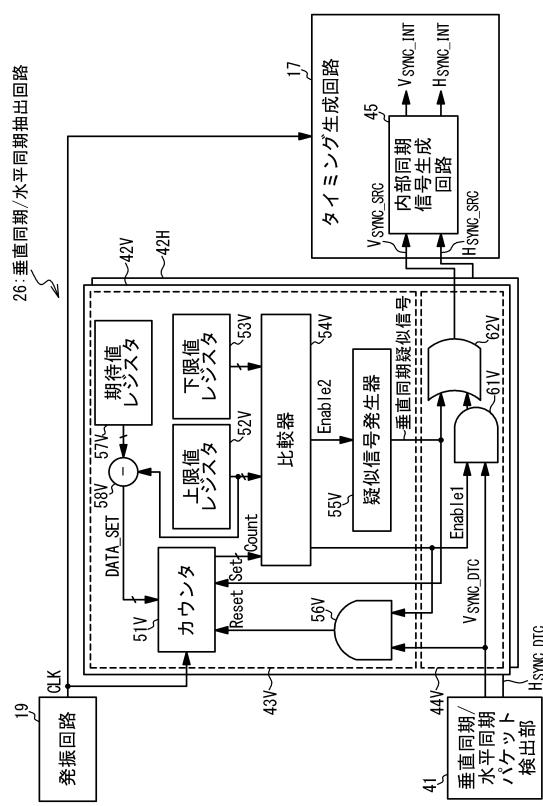

【図6】本実施形態における、垂直同期／水平同期抽出回路の垂直同期ソース信号生成部の構成を示すブロック図である。

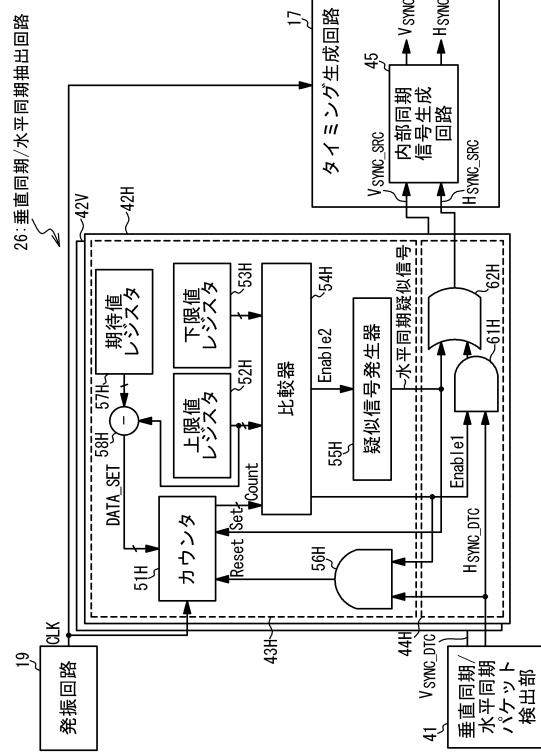

【図7】本実施形態の垂直同期／水平同期抽出回路の水平同期ソース信号生成部の構成を示すブロック図である。 10

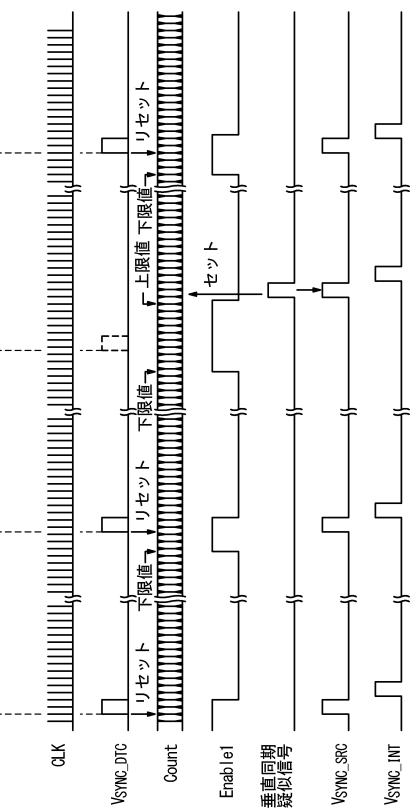

【図8】本実施形態における垂直同期ソース信号生成部の動作を示すタイミングチャートである。

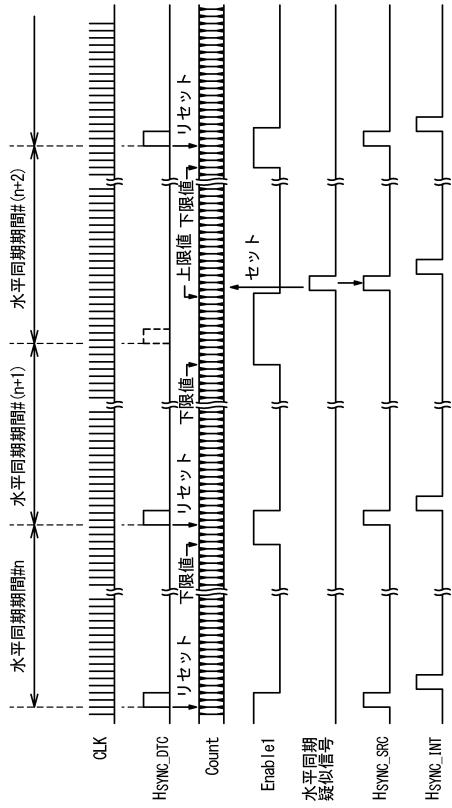

【図9】本実施形態における水平同期ソース信号生成部の動作を示すタイミングチャートである。 10

**【発明を実施するための形態】**

**【0020】**

以下、添付図面を参照しながら実施形態を説明する。以下の説明において、同一又は対応する構成要素が、同一又は対応する参照符号によって参照されることがあることに留意されたい。 20

**【0021】**

図3は、一実施形態における表示装置10の構成を概略的に示すブロック図である。表示装置10は、液晶表示装置として構成されており、LCD (liquid crystal display) パネル1と、表示ドライバI C2とを備えている。表示装置10は、ホスト3から画像データ及び制御データを受け取り、受け取った画像データ及び制御データに応じてLCDパネル1に画像を表示するように構成されている。 30

**【0022】**

LCDパネル1は、表示領域4とゲートドライバ回路5とを備えている。表示領域4には、複数のゲート線6と複数のソース線7と複数の画素8とが配置される。画素8は、行列に配置されており、各画素8は、対応するゲート線6とソース線7とが交差する位置に設けられている。ゲートドライバ回路5は、表示ドライバI C2から受け取った制御信号に応じてゲート線6を駆動する。本実施形態では、表示領域4の左右に一対のゲートドライバ回路5が設けられている。ゲートドライバ回路5は、C o G (Circuit-on-Glass) 技術によってLCDパネル1に集積化されている。 30

**【0023】**

表示ドライバI C2は、ホスト3から受け取った画像データ及び制御データに応じてLCDパネル1のソース線7を駆動する。表示ドライバI C2は、更に、ゲート制御信号をゲートドライバ回路5に供給してゲートドライバ回路5を制御する。 40

**【0024】**

図4は、本実施形態における表示ドライバI C2の構成を概略的に示すブロック図である。本実施形態では、表示ドライバI C2とホスト3の間の通信が、M I P I D S Iに準拠したシリアルインターフェースによって行われる。より具体的には、本実施形態では、表示ドライバI C2とホスト3が、クロックレーンと4つのデータレーン：レーン#0～#3によって接続されている。クロックレーンは、差動クロック信号をホスト3から表示ドライバI C2に供給するために用いられ、レーン#0～#3は、差動データ信号をホスト3から表示ドライバI C2に送信するために用いられる。 50

**【0025】**

図5は、本実施形態における、ホスト3から表示ドライバIC2への通信におけるデータストリームのフォーマットを示す図である。各フレーム期間（垂直同期期間）は、VSAライン(vertical sync active lines)と、VBPライン(vertical back porch lines)と、VACTライン(video active lines)と、VFPライン(vertical front porch lines)とを含んでいる。各フレーム期間が開始されるときに垂直同期パケット31（即ち、Vsyncパケット）がホスト3から表示ドライバIC2に送信され、各ライン（各水平同期期間）が開始されるときに、水平同期パケット32（即ち、Hsyncパケット）がホスト3から表示ドライバIC2に送信される。本実施形態では、垂直同期パケット31が、各フレーム期間、即ち、垂直同期期間の開始を指示する垂直同期期間開始指示として用いられ、水平同期パケット32が、各ライン、即ち、水平同期期間の開始を指示する水平同期期間開始指示として用いられる。10

#### 【0026】

図4に戻り、表示ドライバIC2は、レシーバ回路11と、レーン制御インターフェース回路12と、システムインターフェース回路13と、表示メモリ14と、ソースドライバ回路15と、パネルインターフェース回路16と、タイミング生成回路17と、レジスタ回路18と、発振回路19とを備えている。

#### 【0027】

レシーバ回路11は、レシーバ21、クロック生成回路22と、レシーバ $23_0 \sim 23_3$ と、デシリアルライザ $24_0 \sim 24_3$ とを備えている。レシーバ21は、ホスト3からクロックレーンを介して送信される差動クロック信号をシングルエンドのクロック信号に変換する。クロック生成回路22は、レシーバ21から出力されるクロック信号から、レシーバ回路11において用いられるドットクロック信号（図示されない）、及び、レーン制御インターフェース回路12によって用いられるバイトクロック信号CLK\_byteを生成する。20

#### 【0028】

レシーバ $23_0 \sim 23_3$ は、それぞれ、ホスト3からレーン#0～#3を介して送信される差動データ信号をシングルエンド信号に変換する。デシリアルライザ $24_0 \sim 24_3$ は、ドットクロック信号に同期して動作し、それぞれレシーバ $23_0 \sim 23_3$ から受け取ったシングルエンド信号に対してデシリアルライズ(deserialize)を行う。本実施形態では、デシリアルライザ $24_0 \sim 24_3$ は、デシリアルライズされたデータを8ビットのデータ幅で出力する。30

#### 【0029】

レーン制御インターフェース回路12は、バイトクロック信号CLK\_byteに同期してデシリアルライザ $24_0 \sim 24_3$ からデータを受け取り、受け取ったデータを統合して受信データ列D<sub>R\_cv</sub>を生成する。受信データ列D<sub>R\_cv</sub>は、システムインターフェース回路13に供給される。

#### 【0030】

システムインターフェース回路13は、データトランスレータ25によって受信データ列D<sub>R\_cv</sub>に含まれるデータの内容を識別し、受信データ列D<sub>R\_cv</sub>に含まれる様々なデータ（例えば、画像データ（LCDパネル1の各画素8の階調を示すデータ）や、表示ドライバIC2の制御に用いられるコマンド、パラメータ）に対し、データの種類に応じた様々な処理を行う。例えば、システムインターフェース回路13は、受信データ列D<sub>R\_cv</sub>のうち画像データを表示メモリ14に転送し、また、表示ドライバIC2の制御に用いられるコマンド及びパラメータを、バス20を介してタイミング生成回路17又はレジスタ回路18に転送する。40

#### 【0031】

表示メモリ14は、システムインターフェース回路13から受け取った画像データを一時的に保存し、ソースドライバ回路15に転送する。

#### 【0032】

ソースドライバ回路15は、表示メモリ14から受け取った画像データに応じてLCD50

パネル 1 のソース線 7 を駆動する。

**【 0 0 3 3 】**

パネルインターフェース回路 16 は、LCD パネル 1 のゲートドライバ回路 5 に供給するゲート制御信号を生成する。

**【 0 0 3 4 】**

タイミング生成回路 17 は、システムインターフェース回路 13 及びレジスタ回路 18 から受け取ったコマンド及びパラメータに応じて、表示ドライバ IC 2 に含まれる各回路の動作タイミングの制御を行う。より具体的には、タイミング生成回路 17 は、表示ドライバ IC 2 の内部で用いられる内部垂直同期信号及び内部水平同期信号を生成する。上述のソースドライバ回路 15 及びパネルインターフェース回路 16 は、生成された内部垂直同期信号及び内部水平同期信号に同期して動作する。即ち、ソースドライバ回路 15 は、内部垂直同期信号及び内部水平同期信号に同期して LCD パネル 1 のソース線 7 を駆動し、パネルインターフェース回路 16 は、内部垂直同期信号及び内部水平同期信号に同期してゲート制御信号を生成する。10

**【 0 0 3 5 】**

レジスタ回路 18 は、表示ドライバ IC 2 の制御に用いられるコマンド及びパラメータを保持する。

**【 0 0 3 6 】**

発振回路 19 は、表示ドライバ IC 2 の内部で用いられるクロック信号を発生する。

**【 0 0 3 7 】**

本実施形態の表示ドライバ IC 2 では、表示ドライバ IC 2 の内部で用いられる内部垂直同期信号及び内部水平同期信号が、ホスト 3 から送られる垂直同期期間開始指示及び水平同期期間開始指示に同期して、より具体的には、ホスト 3 から送られる垂直同期パケット及び水平同期パケットに同期して生成される。詳細には、垂直同期パケット及び水平同期パケットは、レーン # 0 ~ # 3 のいずれかを用いてホスト 3 から表示ドライバ IC 2 に送信される。垂直同期パケットが表示ドライバ IC 2 によって正常に受信されると、内部垂直同期信号がタイミング生成回路 17 によってアサートされ、水平同期パケットが表示ドライバ IC 2 によって正常に受信されると、内部水平同期信号がタイミング生成回路 17 によってアサートされる。20

**【 0 0 3 8 】**

このような動作を行うために、本実施形態では、システムインターフェース回路 13 が垂直同期 / 水平同期抽出回路 26 を含んでいる。垂直同期 / 水平同期抽出回路 26 は、ホスト 3 から送られる垂直同期期間開始指示及び水平同期期間開始指示を検出する機能、本実施形態では受信データ列  $D_{RCV}$  に含まれる垂直同期パケット及び水平同期パケットを検出する機能を有しており、垂直同期ソース信号  $V_{SYNC\_SRC}$  及び水平同期ソース信号  $H_{SYNC\_SRC}$  を生成する。垂直同期ソース信号  $V_{SYNC\_SRC}$  及び水平同期ソース信号  $H_{SYNC\_SRC}$  は、それぞれ、タイミング生成回路 17 における内部垂直同期信号及び内部水平同期信号の生成に用いられる信号である。垂直同期 / 水平同期抽出回路 26 は、垂直同期期間開始指示を検出すると、即ち、受信データ列  $D_{RCV}$  において垂直同期パケットを検出すると、垂直同期ソース信号  $V_{SYNC\_SRC}$  をアサートする。また、垂直同期 / 水平同期抽出回路 26 は、水平同期期間開始指示を検出すると、即ち、受信データ列  $D_{RCV}$  において水平同期パケットを検出すると、水平同期ソース信号  $H_{SYNC\_SRC}$  をアサートする。タイミング生成回路 17 は、垂直同期ソース信号  $V_{SYNC\_SRC}$  がアサートされると内部垂直同期信号をアサートし、水平同期ソース信号  $H_{SYNC\_SRC}$  がアサートされると、内部水平同期信号をアサートする。40

**【 0 0 3 9 】**

ここで、本実施形態においては、垂直同期 / 水平同期抽出回路 26 が、垂直同期パケットが表示ドライバ IC 2 に送信されることが期待される期間に表示ドライバ IC 2 が垂直同期パケットを受信しない場合にも、垂直同期ソース信号  $V_{SYNC\_SRC}$  の前回のアサートの後、所定時間が経過したときに垂直同期ソース信号  $V_{SYNC\_SRC}$  をアサー50

トするように構成される。同様に、垂直同期 / 水平同期抽出回路 26 は、水平同期パケットが表示ドライバ I C 2 に送信されることが期待される間に表示ドライバ I C 2 が水平同期パケットを受信しない場合にも、水平同期ソース信号 H<sub>S Y N C \_ S R C</sub> の前回のアサートの後、所定時間が経過したときに水平同期ソース信号 H<sub>S Y N C \_ S R C</sub> をアサートするように構成される。

#### 【 0 0 4 0 】

垂直同期 / 水平同期抽出回路 26 のこのような動作により、本実施形態の表示ドライバ I C 2 は、一時的に垂直同期パケット又は水平同期パケットの受信に失敗しても、表示の乱れの発生を抑制することができる。以下では、垂直同期 / 水平同期抽出回路 26 の構成及び動作の詳細について説明する。

10

#### 【 0 0 4 1 】

図 6、図 7 は、本実施形態の垂直同期 / 水平同期抽出回路 26 の構成の一例を示すブロック図である。垂直同期 / 水平同期抽出回路 26 は、垂直同期 / 水平同期パケット検出部 41 と、垂直同期ソース信号生成部 42V と、水平同期ソース信号生成部 42H とを備えている。なお、垂直同期ソース信号生成部 42V の構成が図 6 に図示されており、水平同期ソース信号生成部 42H の構成が図 7 に図示されている。

#### 【 0 0 4 2 】

垂直同期 / 水平同期パケット検出部 41 は、垂直同期パケット及び水平同期パケットを検出するように構成されており、検出結果に応じて垂直同期パケット検出信号 V<sub>S Y N C \_ D T C</sub> 及び水平同期パケット検出信号 H<sub>S Y N C \_ D T C</sub> を生成する。詳細には、垂直同期 / 水平同期パケット検出部 41 は、受信データ列 D<sub>R C V</sub> において垂直同期パケットを検出すると、垂直同期パケット検出信号 V<sub>S Y N C \_ D T C</sub> をアサートし、水平同期パケットを検出すると、水平同期パケット検出信号 H<sub>S Y N C \_ D T C</sub> をアサートする。

20

#### 【 0 0 4 3 】

垂直同期ソース信号生成部 42V は、垂直同期パケット検出信号 V<sub>S Y N C \_ D T C</sub> から垂直同期ソース信号 V<sub>S Y N C \_ S R C</sub> を生成する。詳細には、図 6 に図示されているように、垂直同期ソース信号生成部 42V は、垂直同期疑似信号生成部 43V と、論理回路部 44V とを備えている。

#### 【 0 0 4 4 】

垂直同期疑似信号生成部 43V は、カウンタ 51V を備えており、カウンタ 51V が保持するカウント値 C<sub>o u n t</sub> に応じて垂直同期疑似信号を生成する。詳細には、垂直同期疑似信号生成部 43V は、カウンタ 51V に加え、上限値レジスタ 52V と、下限値レジスタ 53V と、比較器 54V と、疑似信号発生器 55V と、AND ゲート 56V と、期待値レジスタ 57V と、減算器 58V とを備えている。

30

#### 【 0 0 4 5 】

カウンタ 51V は、発振回路 19 からクロック信号 C L K を受け取り、受け取ったクロック信号 C L K に同期してカウント動作を行う。本実施形態では、カウンタ 51V は、カウント値 C<sub>o u n t</sub> をカウントアップする（1ずつ増加させる）動作を行う。カウンタ 51V のリセット端子には、AND ゲート 56V の出力信号が入力され、カウンタ 51V のセット端子には、疑似信号発生器 55V から出力される垂直同期疑似信号が入力される。また、カウンタ 51V のデータ端子には、減算器 58V から出力される設定値 D A T A \_ S E T が入力される。リセット端子がアサートされると、カウンタ 51V のカウント値 C<sub>o u n t</sub> が所定のリセット値（典型的には“0”）にリセットされる。また、セット端子がアサートされると、カウンタ 51V のカウント値 C<sub>o u n t</sub> が設定値 D A T A \_ S E T にセットされる。

40

#### 【 0 0 4 6 】

上限値レジスタ 52V は、所定の上限値を保持する。後述されるように、上限値レジスタ 52V に保持される上限値は、カウンタ 51V がカウント動作を行っているときに垂直同期疑似信号をアサートするカウント値 C<sub>o u n t</sub> の値を示している。

#### 【 0 0 4 7 】

50

下限値レジスタ 53V は、所定の下限値を保持する。後述されるように、下限値レジスタ 53V に保持される下限値は、カウンタ 51V がカウント動作を行っているときに垂直同期ソース信号  $V_{SYNC\_SRC}$  のアサートを禁止するカウント値 Count の値の範囲を示している。下限値レジスタ 53V に保持されている下限値は、上限値レジスタ 52V に保持されている上限値よりも小さい。

#### 【0048】

比較器 54V は、カウンタ 51V のカウント値 Count を、上限値レジスタ 52V に保持される上限値及び下限値レジスタ 53V に保持される下限値と比較し、その比較結果に応じてイネーブル信号 Enable1、Enable2 を生成する。ここで、イネーブル信号 Enable1 は、垂直同期ソース信号  $V_{SYNC\_SRC}$  のアサートを許可する信号であり、イネーブル信号 Enable2 は、垂直同期疑似信号のアサートを許可する信号である。

#### 【0049】

詳細には、比較器 54V は、カウント値 Count が下限値レジスタ 53V に保持される下限値よりも小さい場合、イネーブル信号 Enable1、Enable2 の両方をネゲートする。また、比較器 54V は、カウント値 Count がカウントアップされて下限値レジスタ 53V に保持される下限値に到達すると、イネーブル信号 Enable1 をアサートする。このとき、イネーブル信号 Enable2 は、ネゲートされたままで維持される。カウント値 Count が更にカウントアップされて上限値レジスタ 52V に保持される上限値に到達すると、イネーブル信号 Enable2 を一定期間アサートする。イネーブル信号 Enable2 を一定期間アサートした後、比較器 54V は、イネーブル信号 Enable1、Enable2 をネゲートする。

#### 【0050】

疑似信号発生器 55V は、比較器 54V から受け取ったイネーブル信号 Enable2 に応じて垂直同期疑似信号を生成する。詳細には、疑似信号発生器 55V は、イネーブル信号 Enable2 がアサートされると、垂直同期疑似信号を一定期間アサートする。

#### 【0051】

AND ゲート 56V は、一方の入力に垂直同期パケット検出信号  $V_{SYNC\_DTC}$  が入力され、他方の入力にイネーブル信号 Enable1 が入力される。AND ゲート 56V は、垂直同期パケット検出信号  $V_{SYNC\_DTC}$  とイネーブル信号 Enable1 の論理積を示す出力信号を出力する。上述のように、AND ゲート 56V の出力信号は、カウンタ 51V のリセットに用いられる。

#### 【0052】

期待値レジスタ 57V は、1 フレーム期間（1 垂直同期期間）の期待される長さに対応する値である期待値を保持する。

#### 【0053】

減算器 58V は、上限値レジスタ 52V に保持されている上限値から期待値レジスタ 57V に保持されている期待値を減じて得られる値をカウンタ 51V に設定すべき設定値 DATA\_SET として算出する。

#### 【0054】

なお、表示ドライバ I C 2 は、上限値レジスタ 52V に設定される上限値が外部から（例えば、ホスト 3 から）書き換え可能であるように構成されることが好ましい。例えば、ホスト 3 から上限値レジスタ 52V に設定されるべき上限値を記述したパケットが表示ドライバ I C 2 に送信されると、該パケットは、受信データ列  $D_{RCV}$  として、レーン制御インターフェース回路 12 からシステムインターフェース回路 13 に送られる。該パケットに記述された上限値は、上限値レジスタ 52V に書き込まれる。同様に、表示ドライバ I C 2 は、下限値レジスタ 53V に設定される下限値及び期待値レジスタ 57V に設定される期待値が、外部から（例えば、ホスト 3 から）書き換え可能であるように構成されることが好ましい。

#### 【0055】

10

20

30

40

50

論理回路部 44V は、垂直同期 / 水平同期パケット検出部 41 から受け取った垂直同期パケット検出信号  $V_{SYNC\_DT_C}$  と、垂直同期疑似信号生成部 43V から受け取ったイネーブル信号  $Enable_1$  及び垂直同期疑似信号から、タイミング生成回路 17 に供給すべき垂直同期ソース信号  $V_{SYNC\_SRC}$  を生成する。

#### 【0056】

詳細には、論理回路部 44V は、AND ゲート 61V と OR ゲート 62V を備えている。AND ゲート 61V の一方の入力には垂直同期 / 水平同期パケット検出部 41 から受け取った垂直同期パケット検出信号  $V_{SYNC\_DT_C}$  が入力され、他方の入力には比較器 54V から受け取ったイネーブル信号  $Enable_1$  が入力される。AND ゲート 61V の出力信号は、OR ゲート 62V の一方の入力に入力される。OR ゲート 62V の他方の入力には、垂直同期疑似信号生成部 43V から受け取った垂直同期疑似信号が入力される。

10

#### 【0057】

このように構成された論理回路部 44V は、次のように動作する。

(1) イネーブル信号  $Enable_1$  がアサートされている状態で垂直同期パケット検出信号  $V_{SYNC\_DT_C}$  がアサートされると、論理回路部 44V は、垂直同期ソース信号  $V_{SYNC\_SRC}$  をアサートする。

(2) 垂直同期疑似信号がアサートされると、論理回路部 44V は、垂直同期ソース信号  $V_{SYNC\_SRC}$  をアサートする。

#### 【0058】

ここで、イネーブル信号  $Enable_1$  がネゲートされている状態では、垂直同期パケット検出信号  $V_{SYNC\_DT_C}$  がアサートされても垂直同期ソース信号  $V_{SYNC\_SRC}$  がアサートされないことに留意されたい。

20

#### 【0059】

図 7 を参照して、水平同期ソース信号生成部 42H は、垂直同期パケット検出信号  $V_{SYNC\_DT_C}$  の代わりに水平同期パケット検出信号  $H_{SYNC\_DT_C}$  が入力され、水平同期パケット検出信号  $H_{SYNC\_DT_C}$  に応じて水平同期ソース信号  $H_{SYNC\_SRC}$  を生成することを除けば、垂直同期ソース信号生成部 42V と同様の構成を有しており、同様に動作する。

#### 【0060】

水平同期ソース信号生成部 42H は、水平同期疑似信号生成部 43H と、論理回路部 44H とを備えている。水平同期疑似信号生成部 43H は、カウンタ 51H を備えており、カウンタ 51H が保持するカウント値  $Count$  に応じて水平同期疑似信号を生成する。水平同期疑似信号生成部 43H の構成は、垂直同期疑似信号生成部 43V と同様であり、カウンタ 51H に加え、上限値レジスタ 52H と、下限値レジスタ 53H と、比較器 54H と、疑似信号発生器 55H と、AND ゲート 56H と、期待値レジスタ 57H と、減算器 58H を備えている。

30

#### 【0061】

論理回路部 44H は、垂直同期 / 水平同期パケット検出部 41 から受け取った水平同期パケット検出信号  $H_{SYNC\_DT_C}$  と、水平同期疑似信号生成部 43H から受け取ったイネーブル信号  $Enable_1$  及び水平同期疑似信号から、タイミング生成回路 17 に供給すべき水平同期ソース信号  $H_{SYNC\_SRC}$  を生成する。論理回路部 44H の構成は、垂直同期ソース信号生成部 42V の論理回路部 44V と同一であり、AND ゲート 61H と OR ゲート 62H を備えている。

40

#### 【0062】

表示ドライバ IC 2 は、上限値レジスタ 52H に設定される上限値が外部から（例えば、ホスト 3 から）書き換え可能であるように構成されることが好ましい。同様に、表示ドライバ IC 2 は、下限値レジスタ 53H に設定される下限値及び期待値レジスタ 57H に設定される期待値が、外部から（例えば、ホスト 3 から）書き換え可能であるように構成されることが好ましい。

50

## 【0063】

垂直同期ソース信号生成部42Vの論理回路部44Vから出力された垂直同期ソース信号 $V_{SYNC\_SRC}$ と、水平同期ソース信号生成部42Hの論理回路部44Hから出力された水平同期ソース信号 $H_{SYNC\_SRC}$ とは、タイミング生成回路17に供給される。タイミング生成回路17は、内部同期信号生成回路45を備えている。内部同期信号生成回路45は、垂直同期ソース信号 $V_{SYNC\_SRC}$ と水平同期ソース信号 $H_{SYNC\_SRC}$ とに応じて内部垂直同期信号 $V_{SYNC\_INT}$ 及び内部水平同期信号 $H_{SYNC\_INT}$ を生成する。内部同期信号生成回路45は、垂直同期ソース信号 $V_{SYNC\_SRC}$ のアサートに応じて内部垂直同期信号 $V_{SYNC\_INT}$ をアサートし、水平同期ソース信号 $H_{SYNC\_SRC}$ のアサートに応じて内部水平同期信号 $H_{SYNC\_INT}$ をアサートする。

10

## 【0064】

タイミング生成回路17の内部同期信号生成回路45によって生成された内部垂直同期信号 $V_{SYNC\_INT}$ 及び内部水平同期信号 $H_{SYNC\_INT}$ は、表示ドライバIC2の各回路の動作タイミングの制御、例えば、ソースドライバ回路15及びパネルインターフェース回路16の動作タイミングの制御に用いられる。ソースドライバ回路15は、内部垂直同期信号 $V_{SYNC\_INT}$ 及び内部水平同期信号 $H_{SYNC\_INT}$ のアサートに同期してソース線7を駆動する。パネルインターフェース回路16は、内部垂直同期信号 $V_{SYNC\_INT}$ 及び内部水平同期信号 $H_{SYNC\_INT}$ のアサートに同期してゲートドライバ回路5に供給すべきソース制御信号を生成する。

20

## 【0065】

続いて、本実施形態の表示ドライバIC2の動作、特に、垂直同期／水平同期抽出回路26の動作について詳細に説明する。

## 【0066】

図8、図9は、本実施形態における垂直同期／水平同期抽出回路26の動作を示すタイミングチャートである。より具体的には、図8は、垂直同期／水平同期抽出回路26の垂直同期ソース信号生成部42Vの動作を示しており、図9は、水平同期ソース信号生成部42Hの動作を示している。以下では、まず、垂直同期ソース信号生成部42Vの動作について説明する。

## 【0067】

30

図8は、3つのフレーム期間#m～#(m+2)における垂直同期ソース信号生成部42Vの動作を示している。図8におけるフレーム期間#m～#(m+2)(垂直同期期間#m～#(m+2))は、ホスト3が垂直同期パケットを表示ドライバIC2に送信する時刻を基準として定義されている。以下では、フレーム期間#(m+1)及びそれ以前のフレーム期間において開始時に表示ドライバIC2が垂直同期パケットを正常に受信する一方で、フレーム期間#(m+2)においては表示ドライバIC2が垂直同期パケットを正常に受信できなかった場合における垂直同期ソース信号生成部42Vの動作を説明する。

## 【0068】

フレーム期間#mの開始時に垂直同期パケットが表示ドライバIC2によって正常に受信されると、垂直同期／水平同期パケット検出部41によって垂直同期パケットが検出され、垂直同期パケット検出信号 $V_{SYNC\_DTC}$ がアサートされる。垂直同期パケット検出信号 $V_{SYNC\_DTC}$ がアサートされると、垂直同期ソース信号 $V_{SYNC\_SRC}$ も論理回路部44Vによってアサートされる。後の説明から理解されるように、前のフレーム期間において垂直同期パケットが表示ドライバIC2によって正常に受信された場合には各フレーム期間の開始時にイネーブル信号Enableがアサートされていることに留意されたい。

40

## 【0069】

タイミング生成回路17では、垂直同期ソース信号 $V_{SYNC\_SRC}$ のアサートに同期して、内部垂直同期信号 $V_{SYNC\_INT}$ が内部同期信号生成回路45によってアサ

50

ートされる。本実施形態では、垂直同期ソース信号  $V_{SYNC\_SRC}$  のアサートの後、所定時間だけ遅れて内部垂直同期信号  $V_{SYNC\_INT}$  がアサートされる。

#### 【0070】

一方で、垂直同期パケット検出信号  $V_{SYNC\_DTC}$  がアサートされると、カウンタ 51V のリセット端子がアサートされ、カウンタ 51V が所定のリセット値（典型的には“0”）にリセットされる（ここでも、イネーブル信号  $E_{nab1e1}$  がアサートされていることに留意されたい）。カウンタ 51V がリセットされると、カウンタ 51V のカウント値が下限値レジスタ 53V に保持されている下限値より小さくなるので、イネーブル信号  $E_{nab1e1}$  が比較器 54V によってネゲートされる。イネーブル信号  $E_{nab1e1}$  がネゲートされるので、垂直同期ソース信号  $V_{SYNC\_SRC}$  も論理回路部 44V によってネゲートされる。10

#### 【0071】

その後、カウンタ 51V のカウント値がカウントアップされる。カウンタ 51V のカウント値が下限値レジスタ 53V に保持されている下限値に到達するまでは、イネーブル信号  $E_{nab1e1}$  がネゲートに維持される。イネーブル信号  $E_{nab1e1}$  がネゲートに維持されるので、誤動作によって垂直同期 / 水平同期パケット検出部 41 が垂直同期パケットを検出したと認識して垂直同期パケット検出信号  $V_{SYNC\_DTC}$  がアサートされても垂直同期ソース信号  $V_{SYNC\_SRC}$  はアサートされず、ネゲートされた状態に維持される。このような動作は、表示ドライバ I C 2 の動作の信頼性を向上させるために有効である。20

#### 【0072】

カウンタ 51V のカウント値がカウントアップされ、カウンタ 51V のカウント値が下限値レジスタ 53V に保持されている下限値に到達すると、比較器 54V によってイネーブル信号  $E_{nab1e1}$  がアサートされる。これにより、垂直同期ソース信号生成部 42V は、以後に垂直同期パケットが検出されたときに垂直同期ソース信号  $V_{SYNC\_SRC}$  をアサートする状態に設定されることになる。

#### 【0073】

その後、フレーム期間 # ( $m + 1$ ) の開始時に垂直同期パケットが表示ドライバ I C 2 によって正常に受信されると、垂直同期 / 水平同期パケット検出部 41 によって垂直同期パケットが検出され、フレーム期間 #  $m$  の開始時と同様の動作が実行される。詳細には、垂直同期パケット検出信号  $V_{SYNC\_DTC}$  が垂直同期 / 水平同期パケット検出部 41 によってアサートされ、垂直同期ソース信号  $V_{SYNC\_SRC}$  も論理回路部 44V によってアサートされる。タイミング生成回路 17 では、垂直同期ソース信号  $V_{SYNC\_SRC}$  のアサートの後、所定時間だけ遅れて内部垂直同期信号  $V_{SYNC\_INT}$  がアサートされる。更に、垂直同期パケット検出信号  $V_{SYNC\_DTC}$  のアサートに応じてカウンタ 51V のリセット端子がアサートされ、カウンタ 51V がリセットされる。カウンタ 51V がリセットされると、イネーブル信号  $E_{nab1e1}$  がネゲートされ、更に、垂直同期ソース信号  $V_{SYNC\_SRC}$  も論理回路部 44V によってネゲートされる。30

#### 【0074】

その後、カウンタ 51V のカウント値がカウントアップされる。カウンタ 51V のカウント値が下限値レジスタ 53V に保持されている下限値に到達すると、イネーブル信号  $E_{nab1e1}$  がアサートされる。40

#### 【0075】

ここで、フレーム期間 # ( $m + 1$ ) に続くフレーム期間 # ( $m + 2$ ) の開始時において表示ドライバ I C 2 が垂直同期パケットの受信に失敗したとする。この場合、フレーム期間 # ( $m + 2$ ) の開始時に垂直同期パケット検出信号  $V_{SYNC\_DTC}$  はアサートされず、カウンタ 51V のカウント値のカウントアップが継続される。

#### 【0076】

カウンタ 51V のカウント値が上限値レジスタ 52V に保持されている上限値に到達すると、比較器 54V によってイネーブル信号  $E_{nab1e2}$  がアサートされる。イネーブル信号  $E_{nab1e2}$  がアサートされると、カウンタ 51V のカウント値がリセットされる。50

ル信号 E n a b l e 2 のアサートに応じて疑似信号発生器 5 5 V は、垂直同期疑似信号をアサートする。垂直同期疑似信号がアサートされるので、O R ゲート 6 2 V から出力される垂直同期ソース信号 V<sub>S Y N C \_ S R C</sub> がアサートされる。その結果、垂直同期ソース信号 V<sub>S Y N C \_ S R C</sub> のアサートから所定時間だけ遅れて内部垂直同期信号 V<sub>S Y N C \_ I N T</sub> がアサートされる。

#### 【 0 0 7 7 】

このような動作によれば、前回の垂直同期ソース信号 V<sub>S Y N C \_ S R C</sub> がアサートされた後、上限値レジスタ 5 2 V に設定された上限値に対応する時間が経過すると、垂直同期パケットが正常に受信されなくても垂直同期ソース信号 V<sub>S Y N C \_ S R C</sub> がアサートされ、更に、内部垂直同期信号 V<sub>S Y N C \_ I N T</sub> がアサートされる。このような動作によれば、垂直同期パケットがノイズ等の原因によって正常に受信できなくても内部垂直同期信号 V<sub>S Y N C \_ I N T</sub> がアサートされるので、画像の乱れを抑制することができる。10

#### 【 0 0 7 8 】

留意すべきことは、垂直同期パケットの受信に失敗したフレーム期間 # ( m + 2 ) においては、垂直同期パケットの受信に成功したフレーム期間 # m 、 # ( m + 1 ) と比較すると、垂直同期ソース信号 V<sub>S Y N C \_ S R C</sub> が相対的に遅れてアサートされることである。このため、フレーム期間 # ( m + 2 ) においては、垂直同期ソース信号 V<sub>S Y N C \_ S R C</sub> がアサートされてからイネーブル信号 E n a b l e 1 がアサートされるまでの時間は短く設定されるべきである。また、フレーム期間 # ( m + 2 ) において垂直同期ソース信号 V<sub>S Y N C \_ S R C</sub> がアサートされてから、フレーム期間 # ( m + 2 ) の次のフレーム期間において垂直同期パケットの受信に失敗した場合に垂直同期疑似信号（又はイネーブル信号 E n a b l e 2 ）をアサートするまでの時間も短く設定されるべきである。20

#### 【 0 0 7 9 】

上記を鑑み、本実施形態では、カウンタ 5 1 V が、垂直同期疑似信号のアサートに応じて設定値 D A T A \_ S E T に設定される。カウンタ 5 1 V がカウント値 C o u n t をカウントアップする本実施形態では、設定値 D A T A \_ S E T は、リセット値（典型的には“0”）よりも大きな値に設定される。このような設定によれば、垂直同期パケットの受信に失敗したフレーム期間において垂直同期ソース信号 V<sub>S Y N C \_ S R C</sub> のアサートが遅れても、適正なタイミングでイネーブル信号 E n a b l e 1 及び垂直同期疑似信号（又はイネーブル信号 E n a b l e 2 ）をアサートすることができる。30

#### 【 0 0 8 0 】

本実施形態では、設定値 D A T A \_ S E T は、上限値レジスタ 5 2 V に設定された上限値から期待値レジスタ 5 7 V に設定された期待値を減じて算出される。期待値レジスタ 5 7 V には、期待されるフレーム期間の長さに対応する値が期待値として設定される。上限値レジスタ 5 2 V に設定される上限値は、あるフレーム期間において垂直同期パケットが正常に受信されてから次のフレーム期間において垂直同期パケットの受信に失敗したときに垂直同期疑似信号（又はイネーブル信号 E n a b l e 2 ）がアサートされるまでの時間に対応するので、結果として、設定値 D A T A \_ S E T は、垂直同期パケットの受信に失敗したフレーム期間における垂直同期パケットの受信に失敗したフレーム期間のアサートの遅れを補償するような値に設定されることになる。40

#### 【 0 0 8 1 】

ただし、設定値 D A T A \_ S E T は、上限値レジスタ 5 2 V に設定された上限値から期待値レジスタ 5 7 V に設定された期待値を減じて得られる値に限定されない。例えば、設定値 D A T A \_ S E T は、無条件に、固定の特定値に設定されてもよい。

#### 【 0 0 8 2 】

なお、カウンタ 5 1 V が、カウント値 C o u n t をカウントダウンする（例えば、1ずつ減少させる）ように構成されてもよい。この場合、比較器 5 4 V は、カウント値 C o u n t が減少して上限値レジスタ 5 2 V に設定された上限値に到達したときにイネーブル信号 E n a b l e 1 をアサートし、その後、垂直同期パケットが正常に受信されずに下限値レジスタ 5 3 V に設定された下限値に到達したときに垂直同期疑似信号（及びイネーブル50

信号 E n a b l e 2 ) をアサートするように構成される。設定値 D A T A \_ S E T は、下限値レジスタ 5 3 V に設定された下限値に、期待値レジスタ 5 7 V に設定された期待値を加算することで算出される。この場合も、設定値 D A T A \_ S E T は、下限値レジスタ 5 3 V に設定された下限値から期待値レジスタ 5 7 V に設定された期待値を加算して得られる値に限定されない。例えば、設定値 D A T A \_ S E T は、無条件に、固定の特定値に設定されてもよい。カウンタ 5 1 V がカウント値 C o u n t をカウントダウンする場合にも、比較器 5 4 V の動作を変更することで、垂直同期ソース信号生成部 4 2 V は、カウンタ 5 1 V がカウント値 C o u n t をカウントアップする場合と同様に動作する。

#### 【 0 0 8 3 】

図 9 を参照して、水平同期ソース信号生成部 4 2 H の動作は、垂直同期パケット検出信号 V S Y N C \_ D T C の代わりに水平同期パケット検出信号 H S Y N C \_ D T C が入力され、水平同期パケット検出信号 H S Y N C \_ D T C に応じて水平同期ソース信号 H S Y N C \_ S R C を生成することを除けば、垂直同期ソース信号生成部 4 2 V の動作と同一である。

#### 【 0 0 8 4 】

図 9 は、3 つの水平同期期間 # n ~ # ( n + 2 ) における水平同期ソース信号生成部 4 2 H の動作を示している。図 9 における水平同期期間 # n ~ # ( n + 2 ) は、ホスト 3 が水平同期パケットを表示ドライバ I C 2 に送信する時刻を基準として定義されている。以下では、水平同期期間 # ( n + 1 ) 及びそれ以前の水平同期期間において開始時に表示ドライバ I C 2 が水平同期パケットを正常に受信する一方で、水平同期期間 # ( n + 2 ) においては表示ドライバ I C 2 が水平同期パケットを正常に受信できなかった場合における水平同期ソース信号生成部 4 2 H の動作を説明する。

#### 【 0 0 8 5 】

水平同期期間 # n の開始時に水平同期パケットが表示ドライバ I C 2 によって正常に受信されると、垂直同期 / 水平同期パケット検出部 4 1 によって水平同期パケットが検出され、水平同期パケット検出信号 H S Y N C \_ D T C がアサートされる。水平同期パケット検出信号 H S Y N C \_ D T C がアサートされると、水平同期ソース信号 H S Y N C \_ S R C も論理回路部 4 4 H によってアサートされる。後の説明から理解されるように、前の水平同期期間において水平同期パケットが表示ドライバ I C 2 によって正常に受信された場合には各水平同期期間の開始時にイネーブル信号 E n a b l e 1 がアサートされていることに留意されたい。

#### 【 0 0 8 6 】

タイミング生成回路 1 7 では、水平同期ソース信号 H S Y N C \_ S R C のアサートに同期して、内部水平同期信号 H S Y N C \_ I N T が内部同期信号生成回路 4 5 によってアサートされる。本実施形態では、水平同期ソース信号 H S Y N C \_ S R C のアサートの後、所定時間だけ遅れて内部水平同期信号 H S Y N C \_ I N T がアサートされる。

#### 【 0 0 8 7 】

一方で、水平同期パケット検出信号 H S Y N C \_ D T C がアサートされると、カウンタ 5 1 H のリセット端子がアサートされ、カウンタ 5 1 H が所定のリセット値（典型的には“ 0 ”）にリセットされる（ここでも、イネーブル信号 E n a b l e 1 がアサートされていることに留意されたい）。カウンタ 5 1 H がリセットされると、カウンタ 5 1 H のカウント値が下限値レジスタ 5 3 H に保持されている下限値より小さくなるので、イネーブル信号 E n a b l e 1 が比較器 5 4 H によってネゲートされる。イネーブル信号 E n a b l e 1 がネゲートされるので、水平同期ソース信号 H S Y N C \_ S R C も論理回路部 4 4 H によってネゲートされる。

#### 【 0 0 8 8 】

その後、カウンタ 5 1 H のカウント値がカウントアップされる。カウンタ 5 1 H のカウント値が下限値レジスタ 5 3 H に保持されている下限値に到達するまでは、イネーブル信号 E n a b l e 1 がネゲートに維持される。イネーブル信号 E n a b l e 1 がネゲートに維持されるので、誤動作によって垂直同期 / 水平同期パケット検出部 4 1 が水平同期パケ

10

20

30

40

50

ットを検出したと認識して水平同期パケット検出信号  $H_{SYNC\_DT_C}$  がアサートされても水平同期ソース信号  $H_{SYNC\_SRC}$  はネゲートされた状態に維持される。このような動作は、表示ドライバ I C 2 の動作の信頼性を向上させるために有効である。

#### 【0089】

カウンタ 51H のカウント値がカウントアップされ、カウンタ 51H のカウント値が下限値レジスタ 53H に保持されている下限値に到達すると、比較器 54H によってイネーブル信号  $E_{nable1e1}$  がアサートされる。これにより、水平同期ソース信号生成部 42H は、以後に水平同期パケットが検出されたときに水平同期ソース信号  $H_{SYNC\_SRC}$  をアサートする状態に設定されることになる。

#### 【0090】

その後、水平同期期間 # (n + 1) の開始時に水平同期パケットが表示ドライバ I C 2 によって正常に受信されると、垂直同期 / 水平同期パケット検出部 41 によって水平同期パケットが検出され、水平同期期間 # n の開始時と同様の動作が実行される。詳細には、水平同期パケット検出信号  $H_{SYNC\_DT_C}$  が垂直同期 / 水平同期パケット検出部 41 によってアサートされ、水平同期ソース信号  $H_{SYNC\_SRC}$  も論理回路部 44H によってアサートされる。タイミング生成回路 17 では、水平同期ソース信号  $H_{SYNC\_SRC}$  のアサートの後、所定時間だけ遅れて内部水平同期信号  $H_{SYNC\_INT}$  がアサートされる。更に、水平同期パケット検出信号  $H_{SYNC\_DT_C}$  のアサートに応じてカウンタ 51H のリセット端子がアサートされ、カウンタ 51H がリセットされる。カウンタ 51H がリセットされると、イネーブル信号  $E_{nable1e1}$  がネゲートされ、更に、水平同期ソース信号  $H_{SYNC\_SRC}$  も論理回路部 44H によってネゲートされる。

10

#### 【0091】

その後、カウンタ 51H のカウント値がカウントアップされる。カウンタ 51H のカウント値が下限値レジスタ 53H に保持されている下限値に到達すると、イネーブル信号  $E_{nable1e1}$  がアサートされる。

#### 【0092】

ここで、水平同期期間 # (n + 1) に続く水平同期期間 # (n + 2) の開始時において表示ドライバ I C 2 が水平同期パケットの受信できなかったとする。この場合、水平同期期間 # (n + 2) の開始時に水平同期パケット検出信号  $H_{SYNC\_DT_C}$  はアサートされず、カウンタ 51H のカウント値のカウントアップが継続される。

30

#### 【0093】

カウンタ 51H のカウント値が上限値レジスタ 52H に保持されている上限値に到達すると、比較器 54H によってイネーブル信号  $E_{nable2e2}$  がアサートされる。イネーブル信号  $E_{nable2e2}$  のアサートに応じて疑似信号発生器 55H は、水平同期疑似信号をアサートする。水平同期疑似信号がアサートされるので、OR ゲート 62H から出力される水平同期ソース信号  $H_{SYNC\_SRC}$  がアサートされる。その結果、水平同期ソース信号  $H_{SYNC\_SRC}$  のアサートから所定時間だけ遅れて内部水平同期信号  $H_{SYNC\_INT}$  がアサートされる。

#### 【0094】

このような動作によれば、前回の水平同期ソース信号  $H_{SYNC\_SRC}$  がアサートされた後、上限値レジスタ 52H に設定された上限値に対応する時間が経過すると、水平同期パケットが正常に受信されなくとも水平同期ソース信号  $H_{SYNC\_SRC}$  がアサートされ、更に、内部水平同期信号  $H_{SYNC\_INT}$  がアサートされる。このような動作によれば、水平同期パケットがノイズ等の原因によって正常に受信できなくても内部水平同期信号  $H_{SYNC\_INT}$  がアサートされるので、画像の乱れを抑制することができる。

40

#### 【0095】

水平同期パケットの受信に失敗した水平同期期間 # (n + 2) においては、水平同期パケットの受信に成功した水平同期期間 # n、# (n + 1) と比較すると、水平同期ソース信号  $H_{SYNC\_SRC}$  が相対的に遅れてアサートされる。よって、水平同期期間 # (n + 2) においては、水平同期ソース信号  $H_{SYNC\_SRC}$  がアサートされてからイネ-

50

ブル信号 E n a b l e 1 がアサートされるまでの時間は短く設定されるべきである。また、水平同期期間 # ( n + 2 ) において水平同期ソース信号 H S Y N C \_ S R C がアサートされてから、水平同期期間 # ( n + 2 ) の次の水平同期期間において水平同期パケットの受信に失敗した場合に水平同期疑似信号（又はイネーブル信号 E n a b l e 2 ）をアサートするまでの時間も短く設定されるべきである。

#### 【 0 0 9 6 】

上記を鑑み、本実施形態では、カウンタ 5 1 H が、水平同期疑似信号のアサートに応じて設定値 D A T A \_ S E T に設定される。カウンタ 5 1 H がカウント値 C o u n t をカウントアップする本実施形態では、設定値 D A T A \_ S E T は、リセット値（典型的には“0”）よりも大きな値に設定される。このような設定によれば、水平同期パケットの受信に失敗した水平同期期間において水平同期ソース信号 H S Y N C \_ S R C のアサートが遅れても、適正なタイミングでイネーブル信号 E n a b l e 1 及び水平同期疑似信号（又はイネーブル信号 E n a b l e 2 ）をアサートすることができる。10

#### 【 0 0 9 7 】

本実施形態では、設定値 D A T A \_ S E T は、上限値レジスタ 5 2 H に設定された上限値から期待値レジスタ 5 7 H に設定された期待値を減じて算出される。期待値レジスタ 5 7 H には、期待される水平同期期間の長さに対応する値が期待値として設定される。上限値レジスタ 5 2 H に設定される上限値は、ある水平同期期間において水平同期パケットが正常に受信されてから次の水平同期期間において水平同期パケットの受信に失敗したときに水平同期疑似信号（又はイネーブル信号 E n a b l e 2 ）がアサートされるまでの時間に対応するので、結果として、設定値 D A T A \_ S E T は、水平同期パケットの受信に失敗した水平同期期間における水平同期パケットの受信に失敗した水平同期期間のアサートの遅れを補償するような値に設定されることになる。20

#### 【 0 0 9 8 】

ただし、設定値 D A T A \_ S E T は、上限値レジスタ 5 2 H に設定された上限値から期待値レジスタ 5 7 H に設定された期待値を減じて得られる値に限定されない。例えば、設定値 D A T A \_ S E T は、無条件に、固定の特定値に設定されてもよい。

#### 【 0 0 9 9 】

なお、カウンタ 5 1 H が、カウント値 C o u n t をカウントダウンする（例えば、1ずつ減少させる）ように構成されてもよい。この場合、比較器 5 4 H は、カウント値 C o u n t が減少して上限値レジスタ 5 2 H に設定された上限値に到達したときにイネーブル信号 E n a b l e 1 をアサートし、その後、水平同期パケットが正常に受信されずに下限値レジスタ 5 3 H に設定された下限値に到達したときに水平同期疑似信号（及びイネーブル信号 E n a b l e 2 ）をアサートするように構成される。設定値 D A T A \_ S E T は、下限値レジスタ 5 3 H に設定された下限値に、期待値レジスタ 5 7 H に設定された期待値を加算することで算出される。この場合も、設定値 D A T A \_ S E T は、下限値レジスタ 5 3 H に設定された下限値から期待値レジスタ 5 7 H に設定された期待値を加算して得られる値に限定されない。例えば、設定値 D A T A \_ S E T は、無条件に、固定の特定値に設定されてもよい。カウンタ 5 1 H がカウント値 C o u n t をカウントダウンする場合にも、比較器 5 4 H の動作を変更することで、水平同期ソース信号生成部 4 2 H は、カウンタ 5 1 H がカウント値 C o u n t をカウントアップする場合と同様に動作する。3040

#### 【 0 1 0 0 】

以上に説明されているように、本実施形態では、垂直同期パケットが表示ドライバ I C 2 に送信されることが期待される期間に表示ドライバ I C 2 が垂直同期パケットを受信しない場合にも、垂直同期ソース信号 V S Y N C \_ S R C の前回のアサートの後、所定時間が経過したときに垂直同期ソース信号 V S Y N C \_ S R C がアサートされる。同様に、水平同期パケットが表示ドライバ I C 2 に送信されることが期待される期間に表示ドライバ I C 2 が水平同期パケットを受信しない場合にも、水平同期ソース信号 H S Y N C \_ S R C の前回のアサートの後、所定時間が経過したときに水平同期ソース信号 H S Y N C \_ S R C がアサートされる。このような動作により、本実施形態の表示ドライバ I C 2 は、50

時的に垂直同期パケット又は水平同期パケットの受信に失敗しても、表示の乱れの発生を抑制することができる。

#### 【0101】

以上には、本発明の実施形態が具体的に記述されているが、本発明は、上記の実施形態に限定されると解釈してはならない。本発明が様々な変更と共に実施され得ることは、当業者には自明的であろう。

#### 【0102】

例えば、上記の実施形態では、表示装置10がLCDパネル1に画像を表示するように構成されているが、本発明は、他の表示パネル（例えば、OLED（organic light emitting diode）表示パネル）に画像を表示するように構成された表示装置にも適用可能である。10

#### 【0103】

また、上記の実施形態では、垂直同期パケットの受信に失敗した場合及び水平同期パケットの受信に失敗した場合の両方に対応した垂直同期／水平同期抽出回路26の構成が記述されているが、垂直同期／水平同期抽出回路26が、一方の場合にのみ対応するように構成されてもよい。例えば、垂直同期／水平同期抽出回路26が垂直同期パケットの受信に失敗にのみ対応するように構成される場合、水平同期ソース信号生成部42Hは設けられず、水平同期パケット検出信号H<sub>S Y N C \_ D T C</sub>が、そのまま、水平同期ソース信号H<sub>S Y N C \_ S R C</sub>として用いられる。また、垂直同期／水平同期抽出回路26が水平同期パケットの受信に失敗にのみ対応するように構成される場合、垂直同期ソース信号生成部42Vは設けられず、垂直同期パケット検出信号V<sub>S Y N C \_ D T C</sub>が、そのまま、垂直同期ソース信号V<sub>S Y N C \_ S R C</sub>として用いられる。20

#### 【0104】

また、上記では、垂直同期パケットが垂直同期期間の開始を指示する垂直同期期間開始指示として用いられる実施形態が開示されているが、ホスト3から表示ドライバIC2に供給される外部垂直同期信号が垂直同期期間開始指示として用いられてもよい。この場合、表示ドライバIC2の各回路（例えば、垂直同期／水平同期抽出回路26）は、外部垂直同期信号のアサートを検出した場合に、上記の実施形態において垂直同期パケットの受信を検出した場合の動作を行う。

#### 【0105】

同様に、上記では、水平同期パケットが水平同期期間の開始を指示する水平同期期間開始指示として用いられる実施形態が開示されているが、ホスト3から表示ドライバIC2に供給される外部水平同期信号が水平同期期間開始指示として用いられてもよい。この場合、この場合、表示ドライバIC2の各回路（例えば、垂直同期／水平同期抽出回路26）は、外部水平同期信号のアサートを検出した場合に、上記の実施形態において水平同期パケットの受信を検出した場合の動作を行う。

#### 【0106】

このような構成によれば、垂直同期信号や水平同期信号を供給する信号線にノイズが印加され、垂直同期及び水平同期の確立に失敗しても、表示の乱れの発生を抑制することができる。40

#### 【符号の説明】

#### 【0107】

- 1 : LCDパネル

- 2 : 表示ドライバIC

- 3 : ホスト

- 4 : 表示領域

- 5 : ゲートドライバ回路

- 6 : ゲート線

- 7 : ソース線

- 8 : 画素

10

20

30

40

50

|               |                      |    |

|---------------|----------------------|----|

| 1 0           | : 表示装置               |    |

| 1 1           | : レシーバ回路             |    |

| 1 2           | : レーン制御インターフェース回路    |    |

| 1 3           | : システムインターフェース回路     |    |

| 1 4           | : 表示メモリ              |    |

| 1 5           | : ソースドライバ回路          |    |

| 1 6           | : パネルインターフェース回路      |    |

| 1 7           | : タイミング生成回路          |    |

| 1 8           | : レジスタ回路             | 10 |

| 1 9           | : 発振回路               |    |

| 2 0           | : バス                 |    |

| 2 1           | : レシーバ               |    |

| 2 2           | : クロック生成回路           |    |

| 2 3 0 ~ 2 3 3 | : レシーバ               |    |

| 2 4 0 ~ 2 4 3 | : デシリアルライザ           |    |

| 2 5           | : データトランスレータ         |    |

| 2 6           | : 垂直同期 / 水平同期抽出回路    |    |

| 3 1           | : 垂直同期パケット           |    |

| 3 2           | : 水平同期パケット           |    |

| 4 1           | : 垂直同期 / 水平同期パケット検出部 | 20 |

| 4 2 H         | : 水平同期ソース信号生成部       |    |

| 4 2 V         | : 垂直同期ソース信号生成部       |    |

| 4 3 H         | : 水平同期疑似信号生成部        |    |

| 4 3 V         | : 垂直同期疑似信号生成部        |    |

| 4 4 V、4 4 H   | : 論理回路部              |    |

| 4 5           | : 内部同期信号生成回路         |    |

| 5 1 V、5 1 H   | : カウンタ               |    |

| 5 2 V、5 2 H   | : 上限値レジスタ            |    |

| 5 3 V、5 3 H   | : 下限値レジスタ            |    |

| 5 4 V、5 4 H   | : 比較器                | 30 |

| 5 5 V、5 5 H   | : 疑似信号発生器            |    |

| 5 6 V、5 6 H   | : ANDゲート             |    |

| 5 7 V、5 7 H   | : 期待値レジスタ            |    |

| 5 8 V、5 8 H   | : 減算器                |    |

| 6 1 V、6 1 H   | : ANDゲート             |    |

| 6 2 V、6 2 H   | : ORゲート              |    |

【 四 1 】

【図2】

【図3】

【図4】

【 四 5 】

【 四 6 】

【 义 7 】

【 四 8 】

【図9】

---

フロントページの続き

(51)Int.Cl.

| F I     |      |         |

|---------|------|---------|

| G 0 9 G | 3/20 | 6 3 1 V |

| G 0 9 G | 3/20 | 6 3 3 D |

| G 0 9 G | 3/20 | 6 3 3 E |

| G 0 9 G | 3/20 | 6 7 0 F |

(56)参考文献 特開2008-152023(JP,A)

特開平09-270937(JP,A)

特開2007-093695(JP,A)

特開昭55-080814(JP,A)

特開平06-232738(JP,A)

(58)調査した分野(Int.Cl., DB名)

G09G 3/00-5/42

H04N 5/66-5/74