(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5869811号

(P5869811)

(45) 発行日 平成28年2月24日(2016.2.24)

(24) 登録日 平成28年1月15日(2016.1.15)

(51) Int.Cl.

F 1

H01L 29/786 (2006.01)

H01L 51/50 (2006.01)H01L 29/78 617N

H01L 29/78 618B

H01L 29/78 612B

H01L 29/78 616T

H05B 33/14 A

請求項の数 4 (全 34 頁)

(21) 出願番号 特願2011-198077 (P2011-198077)

(22) 出願日 平成23年9月12日 (2011.9.12)

(65) 公開番号 特開2012-84864 (P2012-84864A)

(43) 公開日 平成24年4月26日 (2012.4.26)

審査請求日 平成26年9月1日 (2014.9.1)

(31) 優先権主張番号 特願2010-207009 (P2010-207009)

(32) 優先日 平成22年9月15日 (2010.9.15)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 井上 聖子

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 三宅 博之

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 豊高 耕平

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 市川 武宣

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

絶縁表面上の、第1のゲート電極及び第2のゲート電極と、

ゲート絶縁膜を介して、前記第1のゲート電極と重なる第1の領域と、前記第2のゲート電極と重なる第2の領域と、前記第1のゲート電極及び第2のゲート電極と重ならず前記第1の領域及び前記第2の領域の間にある第3の領域と、を有する酸化物半導体膜と、

前記第1のゲート電極の一部及び前記酸化物半導体膜の一部と重なるソース電極と、

前記第2のゲート電極の一部及び前記酸化物半導体膜の一部と重なるドレイン電極と、

前記ゲート絶縁膜、前記第1のゲート電極、前記第2のゲート電極、前記酸化物半導体膜、前記ソース電極、及び前記ドレイン電極上の、絶縁膜と、

を有し、

前記絶縁膜は、前記第3の領域と接することを特徴とする半導体装置。

## 【請求項 2】

絶縁表面上の、第1のトランジスタ及び第2のトランジスタを有する半導体装置であり、

前記第1のトランジスタは、

前記絶縁表面上の、第1のゲート電極及び第2のゲート電極と、

ゲート絶縁膜を介して、前記第1のゲート電極と重なる第1の領域と、前記第2のゲート電極と重なる第2の領域と、前記第1のゲート電極及び第2のゲート電極と重ならず前記第1の領域及び前記第2の領域の間にある第3の領域と、を有する第1の酸化物半導体

10

20

膜と、

前記第1のゲート電極の一部及び前記第1の酸化物半導体膜の一部と重なる第1のソース電極と、

前記第2のゲート電極の一部及び前記第1の酸化物半導体膜の一部と重なる第1のドレイン電極と、

前記ゲート絶縁膜、前記第1のゲート電極、前記第2のゲート電極、前記第1の酸化物半導体膜、前記第1のソース電極、及び第1のドレイン電極上の、絶縁膜と、

を有し、

前記第2のトランジスタは、

前記絶縁表面上の、第3のゲート電極と、

10

前記ゲート絶縁膜を介して、前記第3のゲート電極と重なる領域を有する第2の酸化物半導体膜と、

前記第3のゲート電極の一部及び前記第2の酸化物半導体膜の一部と重なる第2のソース電極及び第2のドレイン電極と、

前記ゲート絶縁膜、前記第3のゲート電極、前記第2の酸化物半導体膜、前記第2のソース電極、及び前記第2のドレイン電極上の、前記絶縁膜と、

を有し、

前記絶縁膜は、前記第3の領域と接することを特徴とする半導体装置。

#### 【請求項3】

請求項2において、

20

前記絶縁表面上に、複数の画素を有する画素部、及び、前記画素部を駆動する駆動回路を有し、

前記複数の画素はそれぞれ、発光素子と、前記発光素子の電流を制御する電流制御素子と、前記電流制御素子のオン及びオフを制御するスイッチング素子とを有し、

前記第1のトランジスタは、前記電流制御素子としての機能を有することを特徴とする半導体装置。

#### 【請求項4】

請求項2において、

前記絶縁表面上に、複数の画素を有する画素部、及び、前記画素部を駆動する駆動回路を有し、

30

前記複数の画素はそれぞれ前記第1のトランジスタを有し、

前記駆動回路は前記第2のトランジスタを有することを特徴とする半導体装置。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

開示される発明の一態様は、半導体装置、表示装置、及びそれらの作製方法に関する。

##### 【背景技術】

##### 【0002】

近年、マトリクス状に配置された表示画素毎に薄膜トランジスタ（Thin Film Transistor：TFT）からなるスイッチング素子や電流制御素子を設けたアクティブマトリクス型の表示装置（発光表示装置や電気泳動式表示装置等）が盛んに開発されている。このような発光表示装置の一つとして、例えば、エレクトロルミネッセンス（Electro Luminescence：EL）表示装置が挙げられる。

40

##### 【0003】

また、チャネル形成領域に酸化物半導体膜を用いるトランジスタ（以下「酸化物半導体トランジスタ」と呼ぶ）を、透光性を有する基板上に形成し、表示装置のスイッチング素子などに用いる技術が研究されている（特許文献1参照）。

##### 【0004】

酸化物半導体トランジスタは、チャネル形成領域にアモルファスシリコン膜を用いたトランジスタに比べ、移動度が高いため、オン電流が高いという利点がある。また酸化物半導

50

体トランジスタのオフ電流は、チャネル形成領域にアモルファスシリコン膜を用いたトランジスタに比べて低いという利点がある。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2010-56539号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

ところが、発光表示装置の画素に設けられるトランジスタとして、酸化物半導体トランジスタを用いると、酸化物半導体トランジスタのオン電流が高すぎる恐れがある。オン電流が高すぎるトランジスタは、トランジスタの駆動電圧の小さな変動でドレイン電流が大きく変動してしまう。トランジスタのドレイン電流が大きく変動すると、発光表示装置の輝度が大きく変動するという問題が生じる。

【0007】

そのため画素に設けられる酸化物半導体トランジスタは、オン電流を調節する必要がある。酸化物半導体トランジスタのオン電流を下げるためには、酸化物半導体トランジスタのチャネル長を長く設ければよい。

【0008】

しかしながら、酸化物半導体トランジスタのチャネル長が長くなると、酸化物半導体トランジスタの占有面積が増大してしまうという恐れがある。

【0009】

ところで、高精細の表示装置は、一つの画素の占有面積が小さい。

【0010】

そのため、当該占有面積が小さい画素に、当該占有面積が大きいトランジスタを用いると、表示装置の開口率が小さくなるという恐れがある。

【0011】

以上を鑑みて、開示される発明の一態様では、占有面積を増大させることなくオン電流を低減できる酸化物半導体トランジスタを得ることを課題の一とする。

【0012】

また開示される発明の一態様では、開口率を減少させることなく、オン電流が低減された酸化物半導体トランジスタを画素に用いた表示装置を得ることを課題の一とする。

【0013】

また酸化物半導体トランジスタは、上述のようにオン電流が高いため、ゲートドライバやソースドライバのような駆動回路に用いることができる。

【0014】

オン電流が低い酸化物半導体トランジスタとオン電流が高い酸化物半導体トランジスタを同一基板上に作製すると、酸化物半導体トランジスタの作製工程が削減でき、作製コストを抑制することができる。

【0015】

以上を鑑み、開示される発明の一態様では、同一基板上に、オン電流が低い酸化物半導体トランジスタ及びオン電流が高い酸化物半導体トランジスタを作製することを課題の一とする。

【0016】

また表示装置の作製において、同一基板上に、画素にオン電流が低い酸化物半導体トランジスタを作製し、かつ駆動回路にオン電流が高い酸化物半導体トランジスタを作製すると、表示装置の作製工程が削減でき、作製コストを抑制することができる。

【0017】

よって、開示される発明の一態様では、同一基板上に、画素にオン電流が低い酸化物半導体トランジスタを用い、かつ駆動回路にオン電流が高い酸化物半導体トランジスタを用い

10

20

30

40

50

た表示装置を得ることを課題の一とする。

### 【課題を解決するための手段】

【 0 0 1 8 】

酸化物半導体トランジスタのソース電極側及びドレイン電極側それぞれに、第1のゲート電極及び第2のゲート電極を設ける。

【 0 0 1 9 】

これにより、酸化物半導体膜と第1のゲート電極が重畠している領域と、酸化物半導体膜と第2のゲート電極が重畠している領域との間に、酸化物半導体膜とゲート電極が重畠しない領域が生じる。本明細書では、当該ゲート電極が重畠しない酸化物半導体膜の領域を $L_{off}$ 領域と呼ぶ。当該 $L_{off}$ 領域を設けることにより、酸化物半導体トランジスタのオン電流を減少させることができる。

【 0 0 2 0 】

以上の様にして作製された酸化物半導体トランジスタを画素に用いることにより、酸化物半導体トランジスタの占有面積を増大させずに、オン電流を低減させることができる。

【 0 0 2 1 】

また、上記のオン電流を低減させた酸化物半導体トランジスタを用いた画素を有する表示装置では、開口率が減少するのを抑制することができる。

【 0 0 2 2 】

また、 $L_{\text{off}}$  領域を設けない酸化物半導体トランジスタは、上述のようにオン電流が高い。そこでオン電流が低い酸化物半導体トランジスタと、オン電流が高い酸化物半導体トランジスタを同一基板上に作製することができる。

〔 0 0 2 3 〕

このように、オン電流が低い酸化物半導体トランジスタ及びオン電流が高い酸化物半導体トランジスタを同一基板上に作製すると、作製工程が削減でき、作製コストを抑制することができる。

〔 0 0 2 4 〕

また、 $L_{ff}$  領域を設けない酸化物半導体トランジスタ（オン電流が高い酸化物半導体トランジスタ）を駆動回路を構成するトランジスタ、 $L_{ff}$  領域を設けた酸化物半導体トランジスタ（オン電流が低い酸化物半導体トランジスタ）を、画素を構成するトランジスタとして用いると、画素と駆動回路の酸化物半導体トランジスタを同一基板上に作製することができる。

[ 0 0 2 5 ]

このように、同一基板上に、画素にオン電流が低い酸化物半導体トランジスタを作製し、かつ駆動回路にオン電流が高い酸化物半導体トランジスタを作製すると、表示装置の作製工程が削減でき、作製コストを抑制することができる。

[ 0 0 2 6 ]

開示される発明の一態様は、絶縁表面上に設けられ、互いに離れて配置された第1のゲート電極及び第2のゲート電極と、ゲート絶縁膜を介して、当該第1のゲート電極及び第2のゲート電極と重畳する領域、並びに当該第1のゲート電極及び第2のゲート電極と重畳しない領域を有する酸化物半導体膜と、当該第1のゲート電極の一部及び当該酸化物半導体膜の一部と重畳するソース電極又はドレイン電極の一方と、当該第2のゲート電極の一部及び当該酸化物半導体膜の一部と重畳するソース電極又はドレイン電極の他方と、当該ゲート絶縁膜、当該第1のゲート電極、当該第2のゲート電極、当該酸化物半導体膜、並びに、当該ソース電極及びドレイン電極を覆い、当該酸化物半導体膜と直接接觸している絶縁膜とを有することを特徴とする半導体装置に関する。

〔 0 0 2 7 〕

開示される発明の一態様は、絶縁表面上に設けられた第1のトランジスタ及び第2のトランジスタを有する半導体装置であり、当該絶縁表面上に設けられ、互いに離れて配置された第1のゲート電極及び第2のゲート電極と、ゲート絶縁膜を介して、当該第1のゲート電極及び第2のゲート電極と重複する領域、及び当該第1のゲート電極及び第2のゲート

電極と重畠しない領域を有する第1の酸化物半導体膜と、当該第1のゲート電極の一部及び当該第1の酸化物半導体膜の一部と重畠する第1のソース電極又はドレイン電極の一方と、当該第2のゲート電極の一部及び当該第1の酸化物半導体膜の一部と重畠する第1のソース電極又はドレイン電極の他方と、当該ゲート絶縁膜、当該第1のゲート電極、当該第2のゲート電極、当該第1の酸化物半導体膜、及び、当該第1のソース電極及びドレイン電極を覆い、当該第1の酸化物半導体膜と直接接觸している絶縁膜とを有する当該第1のトランジスタと、当該絶縁表面上に設けられた第3のゲート電極と、当該ゲート絶縁膜を介して、当該第3のゲート電極と重畠する第2の酸化物半導体膜と、当該第3のゲート電極の一部及び当該第2の酸化物半導体膜の一部と重畠する第2のソース電極及びドレイン電極と、当該ゲート絶縁膜、当該第3のゲート電極、当該第2の酸化物半導体膜、及び、当該第2のソース電極及びドレイン電極を覆い、当該第2の酸化物半導体膜と直接接觸している当該絶縁膜とを有する当該第2のトランジスタと、を有することを特徴とする半導体装置に関する。 10

#### 【0028】

開示される発明の一態様は、絶縁表面上に、複数の画素を有する画素部、及び、当該画素部を駆動する駆動回路を有する表示装置であり、当該複数の画素はそれぞれ、発光素子と、当該発光素子の電流を制御する電流制御素子と、当該電流制御素子のオン及びオフを制御するスイッチング素子とを有し、当該電流制御素子は、当該絶縁表面上に設けられ、互いに離れて配置された第1のゲート電極及び第2のゲート電極と、ゲート絶縁膜を介して、当該第1のゲート電極及び第2のゲート電極と重畠する領域、及び当該第1のゲート電極及び第2のゲート電極と重畠しない領域を有する酸化物半導体膜と、当該第1のゲート電極の一部及び当該酸化物半導体膜の一部と重畠するソース電極又はドレイン電極の一方と、当該第2のゲート電極の一部及び当該酸化物半導体膜の一部と重畠するソース電極又はドレイン電極の他方と、当該ゲート絶縁膜、当該第1のゲート電極、当該第2のゲート電極、当該酸化物半導体膜、及び、当該ソース電極及びドレイン電極を覆い、当該酸化物半導体膜と直接接觸している絶縁膜とを有するトランジスタを有することを特徴とする表示装置に関する。 20

#### 【0029】

開示される発明の一態様は、絶縁表面上に、複数の画素を有する画素部、及び、当該画素部を駆動する駆動回路を有する表示装置であり、当該複数の画素はそれぞれ、当該絶縁表面上に設けられ、互いに離れて配置された第1のゲート電極及び第2のゲート電極と、ゲート絶縁膜を介して、当該第1のゲート電極及び第2のゲート電極と重畠する領域、及び当該第1のゲート電極及び第2のゲート電極と重畠しない領域を有する第1の酸化物半導体膜と、当該第1のゲート電極の一部及び当該第1の酸化物半導体膜の一部と重畠する第1のソース電極又はドレイン電極の一方と、当該第2のゲート電極の一部及び当該第1の酸化物半導体膜の一部と重畠する第1のソース電極又はドレイン電極の他方と、当該ゲート絶縁膜、当該第1のゲート電極、当該第2のゲート電極、当該第1の酸化物半導体膜、及び、当該第1のソース電極及びドレイン電極を覆い、当該第1の酸化物半導体膜と直接接觸している絶縁膜とを有する当該第1のトランジスタを有し、当該駆動回路は、当該絶縁表面上に設けられた第3のゲート電極と、当該ゲート絶縁膜を介して、当該第3のゲート電極と重畠する第2の酸化物半導体膜と、当該第3のゲート電極の一部及び当該第2の酸化物半導体膜の一部と重畠する第2のソース電極及びドレイン電極と、当該ゲート絶縁膜、当該第3のゲート電極、当該第2の酸化物半導体膜、及び、当該第2のソース電極及びドレイン電極を覆い、当該第2の酸化物半導体膜と直接接觸している絶縁膜とを有する当該第2のトランジスタを有することを特徴とする表示装置に関する。 40

#### 【0030】

開示される発明の一態様において、当該複数の画素はそれぞれ発光素子を有することを特徴とする。

#### 【0031】

開示される発明の一態様は、絶縁表面上に、複数の画素を有する画素部、及び、当該画素 50

部を駆動する駆動回路を有する表示装置であり、当該複数の画素はそれぞれ、発光素子と、当該発光素子の電流を制御する電流制御素子と、当該電流制御素子のオン及びオフを制御するスイッチング素子とを有し、当該電流制御素子は、当該絶縁表面上に設けられ、互いに離れて配置された第1のゲート電極及び第2のゲート電極と、ゲート絶縁膜を介して、当該第1のゲート電極及び第2のゲート電極と重畳する領域、及び当該第1のゲート電極及び第2のゲート電極と重畳しない領域を有する第1の酸化物半導体膜と、当該第1のゲート電極の一部及び当該第1の酸化物半導体膜の一部と重畳する第1のソース電極又はドレイン電極の一方と、当該第2のゲート電極の一部及び当該第1酸化物半導体膜の一部と重畳する第1のソース電極又はドレイン電極の他方と、当該ゲート絶縁膜、当該第1のゲート電極、当該第2のゲート電極、当該第1の酸化物半導体膜、及び、当該第1のソース電極及びドレイン電極を覆い、当該第1の酸化物半導体膜と直接接觸している絶縁膜とを有する当該第1のトランジスタを有し、当該駆動回路は、当該絶縁表面上に設けられた第3のゲート電極と、当該ゲート絶縁膜を介して、当該第3のゲート電極と重畳する第2の酸化物半導体膜と、当該第3のゲート電極の一部及び当該第2の酸化物半導体膜の一部と重畳する第2のソース電極又はドレイン電極と、当該ゲート絶縁膜、当該第3のゲート電極、当該第2の酸化物半導体膜、及び、当該第2のソース電極及びドレイン電極を覆い、当該第2の酸化物半導体膜と直接接觸している絶縁膜とを有する当該第2のトランジスタを有することを特徴とする表示装置に関する。 10

#### 【0032】

開示される発明の一態様において、当該駆動回路は、ソースドライバ及びゲートドライバであることを特徴とする。 20

#### 【発明の効果】

#### 【0033】

開示される発明の一態様により、占有面積を増大することなくオン電流を低減できる酸化物半導体トランジスタを得ることができる。

#### 【0034】

また開示される発明の一態様により、開口率を減少させることなく、オン電流が低減された酸化物半導体トランジスタを画素に用いた表示装置を得ることができる。

#### 【0035】

さらに、開示される発明の一態様により、同一基板上に、オン電流が低い酸化物半導体トランジスタ及びオン電流が高い酸化物半導体トランジスタを作製することができる。 30

#### 【0036】

オン電流が低い酸化物半導体トランジスタとオン電流が高い酸化物半導体トランジスタを同一基板上に作製すると、酸化物半導体トランジスタの作製工程が削減でき、作製コストを抑制することができる。

#### 【0037】

また、開示される発明の一態様により、同一基板上に、画素にオン電流が低い酸化物半導体トランジスタを用い、かつ駆動回路にオン電流が高い酸化物半導体トランジスタを用いた表示装置を得ることができる。

#### 【0038】

同一基板上に、画素にオン電流が低い酸化物半導体トランジスタを作製し、かつ駆動回路にオン電流が高い酸化物半導体トランジスタを作製すると、表示装置の作製工程が削減でき、作製コストを抑制することができる。 40

#### 【図面の簡単な説明】

#### 【0039】

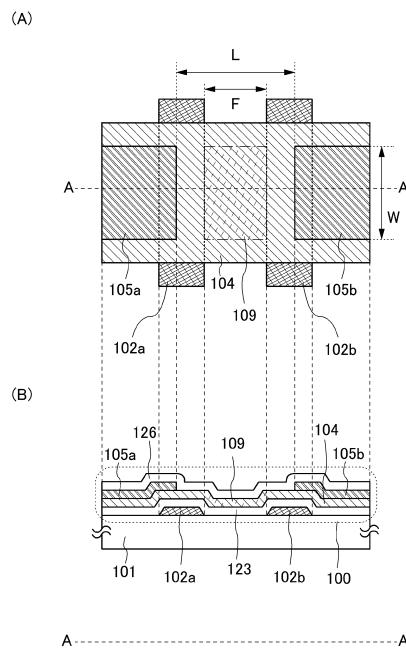

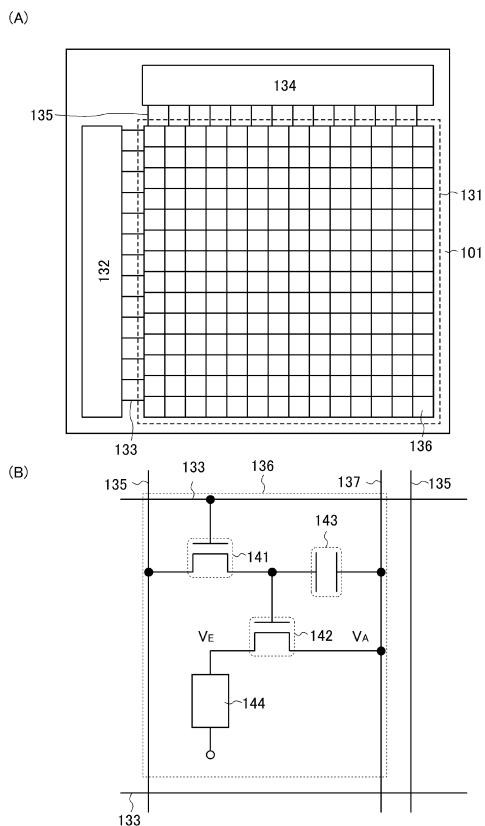

【図1】半導体装置の上面図及び断面図。

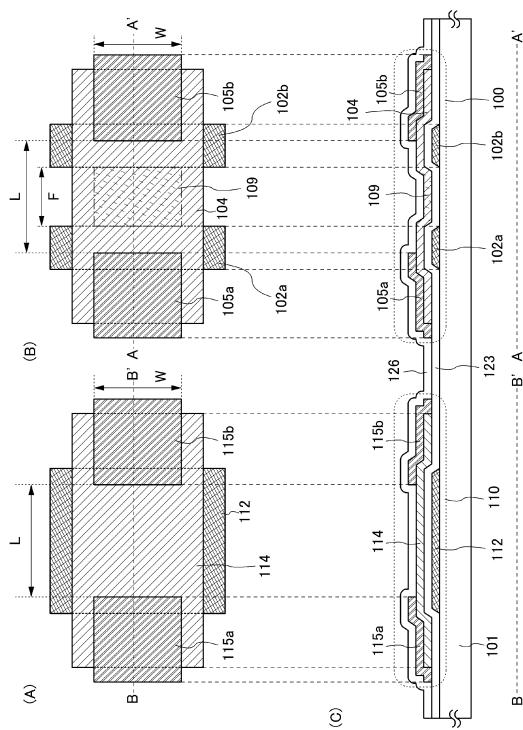

【図2】半導体装置の上面図及び断面図。

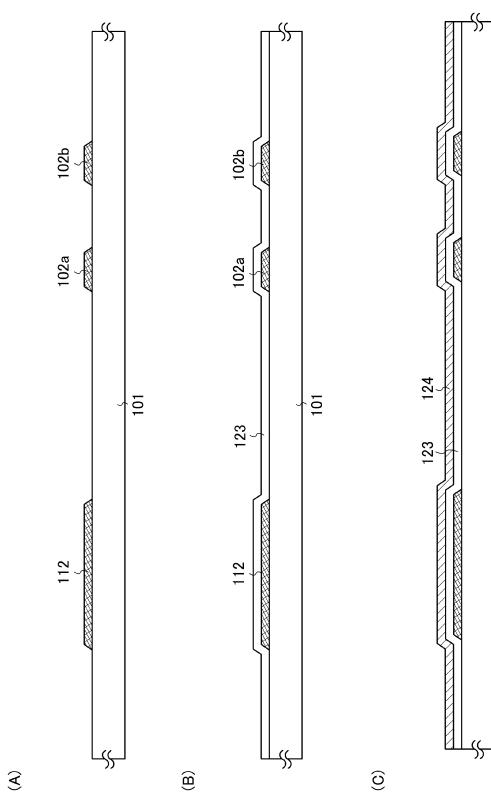

【図3】半導体装置の作製工程を示す断面図。

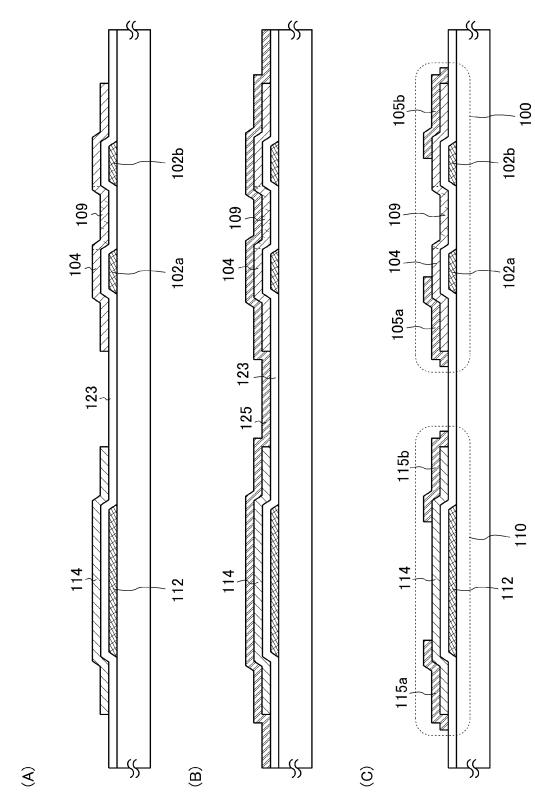

【図4】半導体装置の作製工程を示す断面図。

【図5】表示装置のブロック図及び画素の回路図。 50

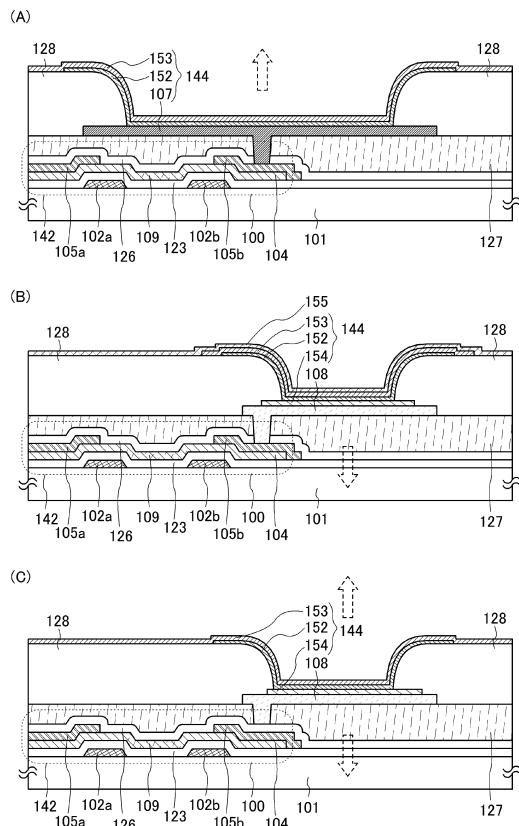

【図6】表示装置の断面図。

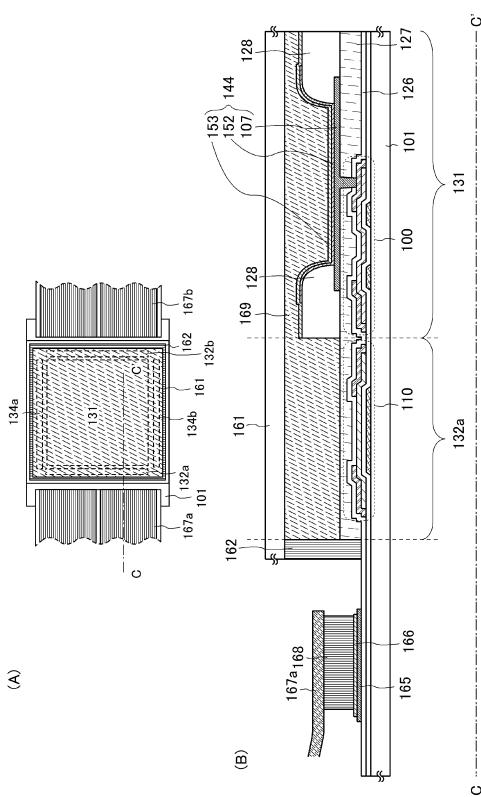

【図7】表示パネルの上面図及び断面図。

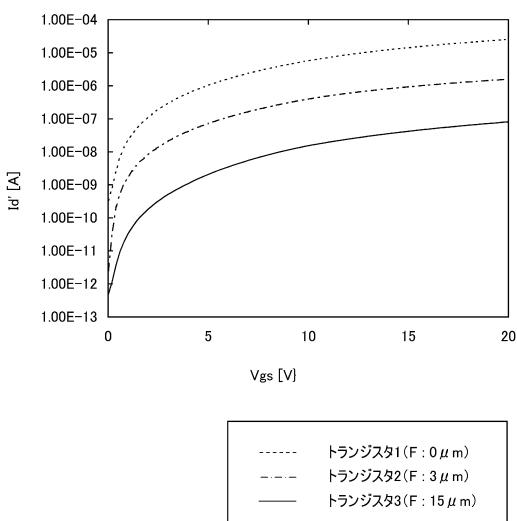

【図8】酸化物半導体トランジスタの $V_{g_s}$ - $I_d$ 特性を示す図。

【図9】チャネル長の異なるトランジスタの特性を示す図。

【図10】半導体装置の上面図及び断面図。

【図11】酸化物材料の構造を説明する図。

【図12】酸化物材料の構造を説明する図。

【図13】酸化物材料の構造を説明する図。

【発明を実施するための形態】

【0040】

10

以下、本明細書に開示された発明の実施の態様について、図面を参照して説明する。但し、本明細書に開示された発明は多くの異なる態様で実施することが可能であり、本明細書に開示された発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本実施の形態の記載内容に限定して解釈されるものではない。なお、以下に示す図面において、同一部分又は同様な機能を有する部分には同一の符号を付し、その繰り返しの説明は省略する。

【0041】

なお本明細書に開示された発明において、半導体装置とは、半導体を利用することで機能する素子及び装置全般を指し、電子回路、表示装置、発光装置等を含む電気装置およびその電気装置を搭載した電子機器をその範疇とする。

20

【0042】

<L<sub>off</sub>領域を有する酸化物半導体トランジスタ>

図1(B)に示す酸化物半導体トランジスタ100は、絶縁表面を有する基板101上に形成されている。酸化物半導体トランジスタ100は、第1のゲート電極であるゲート電極102a、第2のゲート電極であるゲート電極102b、ゲート絶縁膜123、第1の酸化物半導体膜である酸化物半導体膜104、ソース電極又はドレイン電極の一方である電極105a、ソース電極又はドレイン電極の他方である電極105bを有している。

【0043】

基板101は、バリウムホウケイ酸ガラス、アルミノホウケイ酸ガラス、若しくはアルミニシリケートガラスなど、フュージョン法やフロート法で作製される無アルカリガラス基板、セラミック基板の他、本作製工程の処理温度に耐えうる耐熱性を有するプラスチック基板等を用いることができる。また、ステンレス合金などの金属基板の表面に絶縁膜を設けた基板を適用しても良い。

30

【0044】

基板101上に設けられたゲート電極102a及びゲート電極102bは、互いに離れて配置されている。また、ゲート電極102a及びゲート電極102bの間には、ゲート絶縁膜123が配置されている。

【0045】

第1のゲート電極であるゲート電極102a、及び第2のゲート電極であるゲート電極102bは、それぞれチタン(Ti)、モリブデン(Mo)、クロム(Cr)、タンタル(Ta)、タングステン(W)、アルミニウム(Al)、銀(Ag)、金(Au)、銅(Cu)のいずれかを含む導電膜である。

40

【0046】

また、ゲート電極102a及びゲート電極102bはそれぞれ、上記の元素のいずれかを含む導電膜を用いた単層構造であってもよく、又上記の元素のいずれかを含む導電膜の積層構造であってもよい。

【0047】

なお、ゲート電極102a及びゲート電極102bそれぞれの上には、半導体膜や導電膜が形成される。そのため、半導体膜や導電膜の段切れ防止のため、ゲート電極102a及びゲート電極102bそれぞれの端部は、テーパ状になるように加工することが望ましい

50

。

**【0048】**

ゲート絶縁膜123は、ゲート電極102a及びゲート電極102bを覆って設けられている。

**【0049】**

ゲート絶縁膜123は、酸化珪素膜、酸化窒化珪素膜、窒化酸化珪素膜、窒化珪素膜を用いた単層構造、或いはこれらの膜を積層した積層構造を用いてもよい。

**【0050】**

本実施の形態において、酸化窒化珪素膜とは、その組成において、窒素(N)よりも酸素(O)の含有量が多いものであって、ラザフォード後方散乱法(RBS: Rutherford Backscattering Spectrometry)及び水素前方散乱法(HFS: Hydrogen Forward Scattering)を用いて測定した場合に、濃度範囲として酸素(O)が55~70原子%、窒素(N)が0.5~15原子%、珪素(Si)が25~35原子%、水素(H)が0.1~10原子%の範囲で含まれるものという。10

**【0051】**

また、窒化酸化珪素膜とは、その組成において、酸素(O)よりも窒素(N)の含有量が多いものであって、濃度範囲として酸素(O)が5~30原子%、窒素(N)が20~55原子%、珪素(Si)が25~35原子%、水素(H)が10~30原子%の範囲で含まれるものという。20

**【0052】**

但し、酸化窒化珪素または窒化酸化珪素を構成する原子の合計を100原子%としたとき、窒素(N)、酸素(O)、珪素(Si)、及び水素(H)の含有比率が上記の範囲内に含まれるものとする。

**【0053】**

また、ゲート絶縁膜123として、アルミニウム(A1)、イットリウム(Y)、マグネシウム(Mg)、又はハフニウム(Hf)の酸化物、アルミニウム(A1)、イットリウム(Y)、マグネシウム(Mg)、又はハフニウム(Hf)窒化物、アルミニウム(A1)、イットリウム(Y)、マグネシウム(Mg)、又はハフニウム(Hf)酸化窒化物、又はアルミニウム(A1)、イットリウム(Y)、マグネシウム(Mg)、又はハフニウム(Hf)窒化酸化物のいずれかを用いることができる。また当該酸化物、窒化物、酸化窒化物、窒化酸化物の少なくとも2種以上を含む化合物を用いることもできる。30

**【0054】**

また酸化物半導体トランジスタ100は、ゲート絶縁膜123上に形成され、チャネル形成領域が形成される酸化物半導体膜104を有している。酸化物半導体トランジスタ100は、連続した面を有する酸化物半導体膜104を有しているので、キャリアの移動に障壁がなく好適である。

**【0055】**

酸化物半導体膜104と第1のゲート電極102aが重畳している領域と、酸化物半導体膜104と第2のゲート電極102bが重畳している領域との間に、酸化物半導体膜104とゲート電極が重畳しない領域が生じる。上述のように、本明細書では、当該ゲート電極102a及びゲート電極102bが重畳しない酸化物半導体膜104の領域をL<sub>ff</sub>領域109と呼ぶ。40

**【0056】**

酸化物半導体膜104は、以下の酸化物半導体の薄膜を用いる。

**【0057】**

本実施の形態で用いる酸化物半導体としては、少なくともインジウム(In)あるいは亜鉛(Zn)を含むことが好ましい。特にInとZnを含むことが好ましい。また、該酸化物半導体を用いたトランジスタの電気特性のばらつきを減らすためのスタビライザーとして、それらに加えてガリウム(Ga)を有することが好ましい。また、スタビライザーと50

してスズ( Sn )を有することが好ましい。また、スタビライザーとしてハフニウム( Hf )を有することが好ましい。また、スタビライザーとしてアルミニウム( Al )を有することが好ましい。

#### 【0058】

また、他のスタビライザーとして、ランタノイドである、ラントン( La )、セリウム( Ce )、プラセオジム( Pr )、ネオジム( Nd )、サマリウム( Sm )、ユウロピウム( Eu )、ガドリニウム( Gd )、テルビウム( Tb )、ジスプロシウム( Dy )、ホルミウム( Ho )、エルビウム( Er )、ツリウム( Tm )、イッテルビウム( Yb )、ルテチウム( Lu )のいずれか一種あるいは複数種を有してもよい。

#### 【0059】

例えば、酸化物半導体として、酸化インジウム、酸化スズ、酸化亜鉛、二元系金属の酸化物である In - Zn 系酸化物、 Sn - Zn 系酸化物、 Al - Zn 系酸化物、 Zn - Mg 系酸化物、 Sn - Mg 系酸化物、 In - Mg 系酸化物、 In - Ga 系酸化物、三元系金属の酸化物である In - Ga - Zn 系酸化物( IGZO とも表記する )、 In - Al - Zn 系酸化物、 In - Sn - Zn 系酸化物、 Sn - Ga - Zn 系酸化物、 Al - Ga - Zn 系酸化物、 Sn - Al - Zn 系酸化物、 In - Hf - Zn 系酸化物、 In - La - Zn 系酸化物、 In - Ce - Zn 系酸化物、 In - Pr - Zn 系酸化物、 In - Nd - Zn 系酸化物、 In - Sm - Zn 系酸化物、 In - Eu - Zn 系酸化物、 In - Gd - Zn 系酸化物、 In - Tb - Zn 系酸化物、 In - Dy - Zn 系酸化物、 In - Ho - Zn 系酸化物、 In - Er - Zn 系酸化物、 In - Tm - Zn 系酸化物、 In - Yb - Zn 系酸化物、 In - Lu - Zn 系酸化物、四元系金属の酸化物である In - Sn - Ga - Zn 系酸化物、 In - Hf - Ga - Zn 系酸化物、 In - Al - Ga - Zn 系酸化物、 In - Sn - Al - Zn 系酸化物、 In - Sn - Hf - Zn 系酸化物、 In - Hf - Al - Zn 系酸化物を用いることができる。

#### 【0060】

なお、ここで、例えば、 In - Ga - Zn 系酸化物とは、 In と Ga と Zn を主成分として有する酸化物という意味であり、 In と Ga と Zn の比率は問わない。また、 In と Ga と Zn 以外の金属元素が入っていてもよい。

#### 【0061】

また、酸化物半導体として、  $InMO_3 (ZnO)_m$  ( $m > 0$  、且つ、  $m$  は整数でない) で表記される材料を用いてもよい。なお、 M は、 Ga 、 Fe 、 Mn 及び Co から選ばれた一の金属元素または複数の金属元素を示す。また、酸化物半導体として、  $In_2SnO_5 (ZnO)_n$  ( $n > 0$  、且つ、  $n$  は整数) で表記される材料を用いてもよい。

#### 【0062】

例えば、  $In : Ga : Zn = 1 : 1 : 1$  (= 1 / 3 : 1 / 3 : 1 / 3 ) あるいは  $In : Ga : Zn = 2 : 2 : 1$  (= 2 / 5 : 2 / 5 : 1 / 5 ) の原子比の In - Ga - Zn 系酸化物やその組成の近傍の酸化物を用いることができる。あるいは、  $In : Sn : Zn = 1 : 1 : 1$  (= 1 / 3 : 1 / 3 : 1 / 3 ) 、  $In : Sn : Zn = 2 : 1 : 3$  (= 1 / 3 : 1 / 6 : 1 / 2 ) あるいは  $In : Sn : Zn = 2 : 1 : 5$  (= 1 / 4 : 1 / 8 : 5 / 8 ) の原子比の In - Sn - Zn 系酸化物やその組成の近傍の酸化物を用いるとよい。

#### 【0063】

しかし、これらに限られず、必要とする半導体特性( 移動度、しきい値、ばらつき等 ) に応じて適切な組成のものを用いればよい。また、必要とする半導体特性を得るために、キャリア密度や不純物濃度、欠陥密度、金属元素と酸素の原子数比、原子間結合距離、密度等を適切なものとすることが好ましい。

#### 【0064】

例えば、 In - Sn - Zn 系酸化物では比較的容易に高い移動度が得られる。しかしながら、 In - Ga - Zn 系酸化物でも、バルク内欠陥密度を下げるにより移動度を上げることができる。

#### 【0065】

10

20

30

40

50

なお、例えば、In、Ga、Znの原子数比がIn : Ga : Zn = a : b : c (a + b + c = 1)である酸化物の組成が、原子数比がIn : Ga : Zn = A : B : C (A + B + C = 1)の酸化物の組成の近傍であるとは、a、b、cが、(a - A)<sup>2</sup> + (b - B)<sup>2</sup> + (c - C)<sup>2</sup> / r<sup>2</sup>を満たすことをいい、rは、例えば、0.05とすればよい。他の酸化物でも同様である。

#### 【0066】

酸化物半導体は単結晶でも、非単結晶でもよい。後者の場合、アモルファスでも、多結晶でもよい。また、アモルファス中に結晶性を有する部分を含む構造でも、非アモルファスでもよい。

#### 【0067】

アモルファス状態の酸化物半導体は、比較的容易に平坦な表面を得ることができるため、これを用いてトランジスタを作製した際の界面散乱を低減でき、比較的容易に、比較的高い移動度を得ることができる。

#### 【0068】

また、結晶性を有する酸化物半導体では、よりバルク内欠陥を低減することができ、表面の平坦性を高めればアモルファス状態の酸化物半導体以上の移動度を得ることができる。表面の平坦性を高めるためには、平坦な表面上に酸化物半導体を形成することができる。具体的には、平均面粗さ(Ra)が1nm以下、好ましくは0.3nm以下、より好ましくは0.1nm以下の表面上に形成するとよい。

#### 【0069】

なお、Raは、JIS B 0601で定義されている中心線平均粗さを面に対して適用できるよう三次元に拡張したものであり、「基準面から指定面までの偏差の絶対値を平均した値」と表現でき、以下の式にて定義される。

#### 【0070】

#### 【数1】

$$Ra = \frac{1}{S_0} \int_{y_1}^{y_2} \int_{x_1}^{x_2} |f(x, y) - Z_0| dx dy$$

20

30

#### 【0071】

なお、上記において、S<sub>0</sub>は、測定面(座標(x<sub>1</sub>, y<sub>1</sub>)(x<sub>1</sub>, y<sub>2</sub>)(x<sub>2</sub>, y<sub>1</sub>)(x<sub>2</sub>, y<sub>2</sub>)で表される4点によって囲まれる長方形の領域)の面積を指し、Z<sub>0</sub>は測定面の平均高さを指す。Raは原子間力顕微鏡(AFM: Atomic Force Microscope)にて評価可能である。

#### 【0072】

ここで酸化物半導体が結晶性を有する場合として、c軸配向し、かつab面、表面または界面の方向から見て三角形状または六角形状の原子配列を有し、c軸においては金属原子が層状または金属原子と酸素原子とが層状に配列しており、ab面においてはa軸またはb軸の向きが異なる(c軸を中心に回転した)結晶(CAAC: C Axis Aligned Crystalともいう)を含む酸化物について説明する。

40

#### 【0073】

CAACを含む酸化物とは、広義に、非単結晶であって、そのab面に垂直な方向から見て、三角形、六角形、正三角形または正六角形の原子配列を有し、かつc軸方向に垂直な方向から見て、金属原子が層状、または金属原子と酸素原子が層状に配列した相を含む酸化物をいう。

#### 【0074】

CAACは単結晶ではないが、非晶質のみから形成されているものでもない。また、CAACは結晶化した部分(結晶部分)を含むが、1つの結晶部分と他の結晶部分の境界を明確に判別できないこともある。

50

**【 0 0 7 5 】**

C A A C に酸素が含まれる場合、酸素の一部は窒素で置換されてもよい。また、C A A C を構成する個々の結晶部分のc 軸は一定の方向（例えば、C A A C を支持する基板面、C A A C の表面などに垂直な方向）に揃っていてもよい。または、C A A C を構成する個々の結晶部分のa b 面の法線は一定の方向（例えば、C A A C を支持する基板面、C A A C の表面などに垂直な方向）を向いていてもよい。

**【 0 0 7 6 】**

C A A C は、その組成などに応じて、導体であったり、半導体であったり、絶縁体であったりする。また、その組成などに応じて、可視光に対して透明であったり不透明であったりする。

10

**【 0 0 7 7 】**

このようなC A A C の例として、膜状に形成され、膜表面または支持する基板面に垂直な方向から観察すると三角形または六角形の原子配列が認められ、かつその膜断面を観察すると金属原子または金属原子および酸素原子（または窒素原子）の層状配列が認められる結晶を挙げることもできる。

**【 0 0 7 8 】**

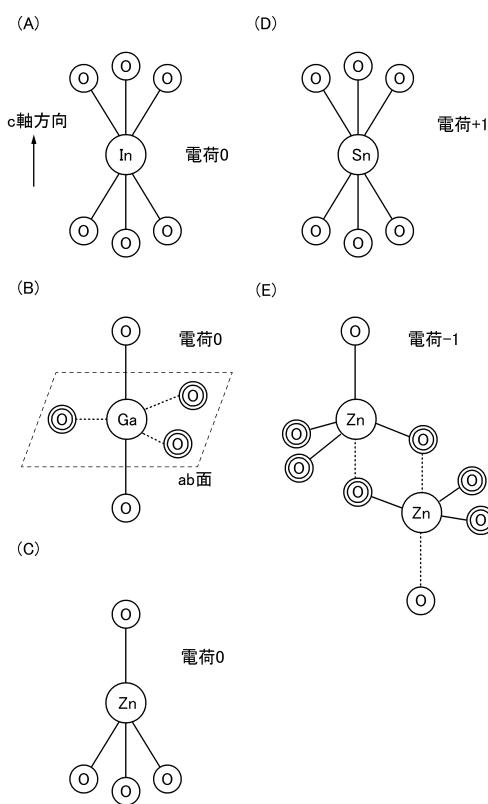

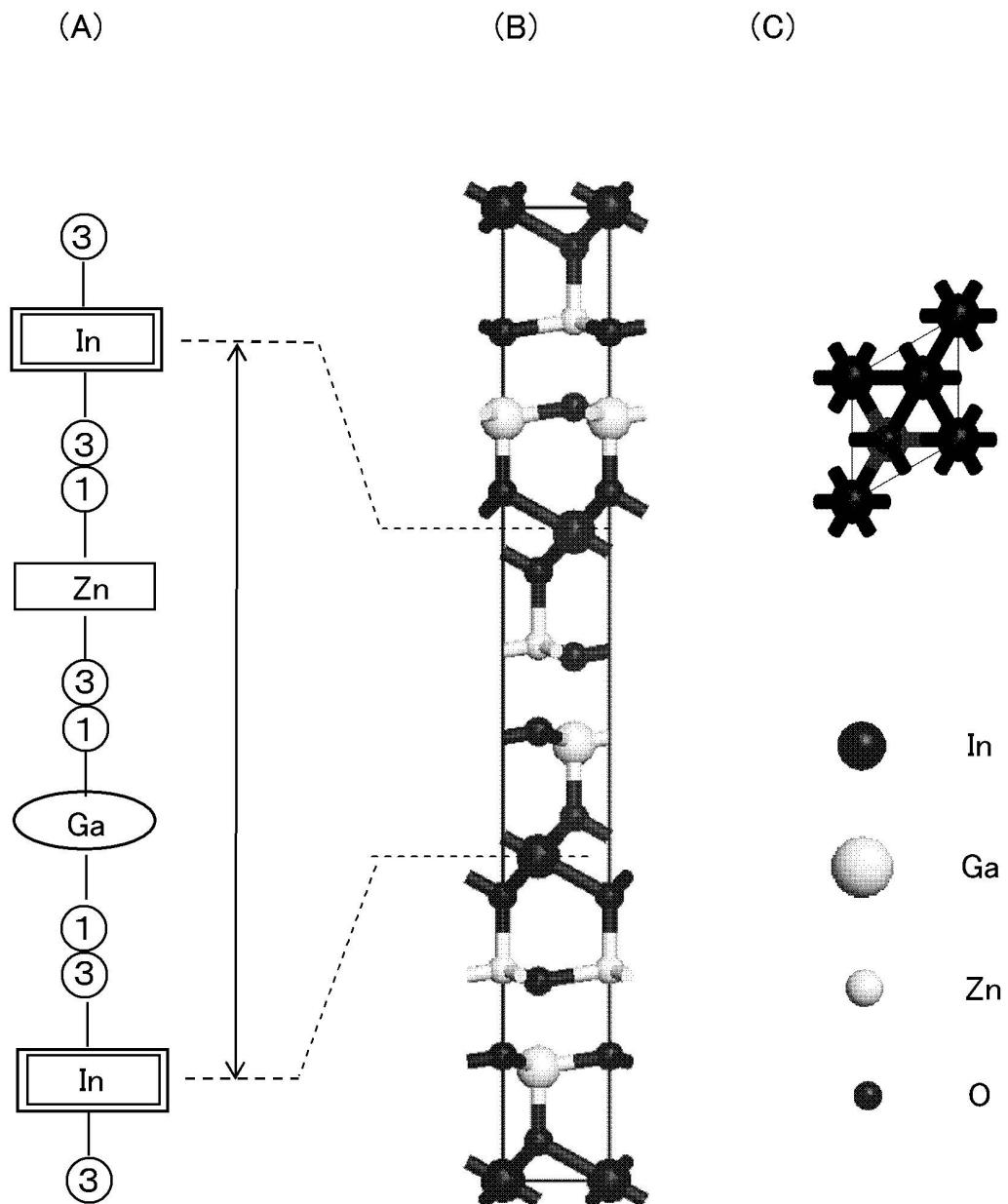

C A A C に含まれる結晶構造の一例について図11乃至図13を用いて詳細に説明する。なお、特に断りがない限り、図11乃至図13は上方向をc 軸方向とし、c 軸方向と直交する面をa b 面とする。なお、単に上半分、下半分という場合、a b 面を境にした場合の上半分、下半分をいう。また、図11において、丸で囲まれたOは4配位のOを示し、二重丸で囲まれたOは3配位のOを示す。

20

**【 0 0 7 9 】**

図11(A)に、1個の6配位のInと、Inに近接の6個の4配位の酸素原子（以下4配位のO）と、を有する構造を示す。ここでは、金属原子が1個に対して、近接の酸素原子のみ示した構造を小グループと呼ぶ。図11(A)の構造は、八面体構造をとるが、簡単のため平面構造で示している。なお、図11(A)の上半分および下半分にはそれぞれ3個ずつ4配位のOがある。図11(A)に示す小グループは電荷が0である。

**【 0 0 8 0 】**

図11(B)に、1個の5配位のGaと、Gaに近接の3個の3配位の酸素原子（以下3配位のO）と、Gaに近接の2個の4配位のOと、を有する構造を示す。3配位のOは、いずれもa b 面に存在する。図11(B)の上半分および下半分にはそれぞれ1個ずつ4配位のOがある。また、Inも5配位をとるため、図11(B)に示す構造をとりうる。図11(B)に示す小グループは電荷が0である。

30

**【 0 0 8 1 】**

図11(C)に、1個の4配位のZnと、Znに近接の4個の4配位のOと、を有する構造を示す。図11(C)の上半分には1個の4配位のOがあり、下半分には3個の4配位のOがある。または、図11(C)の上半分に3個の4配位のOがあり、下半分に1個の4配位のOがあつてもよい。図11(C)に示す小グループは電荷が0である。

**【 0 0 8 2 】**

図11(D)に、1個の6配位のSnと、Snに近接の6個の4配位のOと、を有する構造を示す。図11(D)の上半分には3個の4配位のOがあり、下半分には3個の4配位のOがある。図11(D)に示す小グループは電荷が+1となる。

40

**【 0 0 8 3 】**

図11(E)に、2個のZnを含む小グループを示す。図11(E)の上半分には1個の4配位のOがあり、下半分には1個の4配位のOがある。図11(E)に示す小グループは電荷が-1となる。

**【 0 0 8 4 】**

ここでは、複数の小グループの集合体を中グループと呼び、複数の中グループの集合体を大グループ（ユニットセルともいう。）と呼ぶ。

**【 0 0 8 5 】**

50

ここで、これらの小グループ同士が結合する規則について説明する。図11(A)に示す6配位のInの上半分の3個のOは、下方向にそれぞれ3個の近接Inを有し、下半分の3個のOは、上方向にそれぞれ3個の近接Inを有する。5配位のGaの上半分の1個のOは、下方向に1個の近接Gaを有し、下半分の1個のOは、上方向に1個の近接Gaを有する。4配位のZnの上半分の1個のOは下方向に1個の近接Znを有し、下半分の3個のOは、上方向にそれぞれ3個の近接Znを有する。この様に、金属原子の上方向の4配位のOの数と、そのOの下方向にある近接金属原子の数は等しく、同様に金属原子の下方向の4配位のOの数と、そのOの上方向にある近接金属原子の数は等しい。Oは4配位なので、下方向にある近接金属原子の数と、上方向にある近接金属原子の数の和は4になる。従って、金属原子の上方向にある4配位のOの数と、別の金属原子の下方向にある4配位のOの数との和が4個のとき、金属原子を有する二種の小グループ同士は結合することができる。例えば、6配位の金属原子(InまたはSn)が下半分の4配位のOを介して結合する場合、4配位のOが3個であるため、5配位の金属原子(GaまたはIn)、または4配位の金属原子(Zn)のいずれかと結合することになる。

#### 【0086】

これらの配位数を有する金属原子は、c軸方向において、4配位のOを介して結合する。また、このほかにも、層構造の合計の電荷が0となるように複数の小グループが結合して中グループを構成する。

#### 【0087】

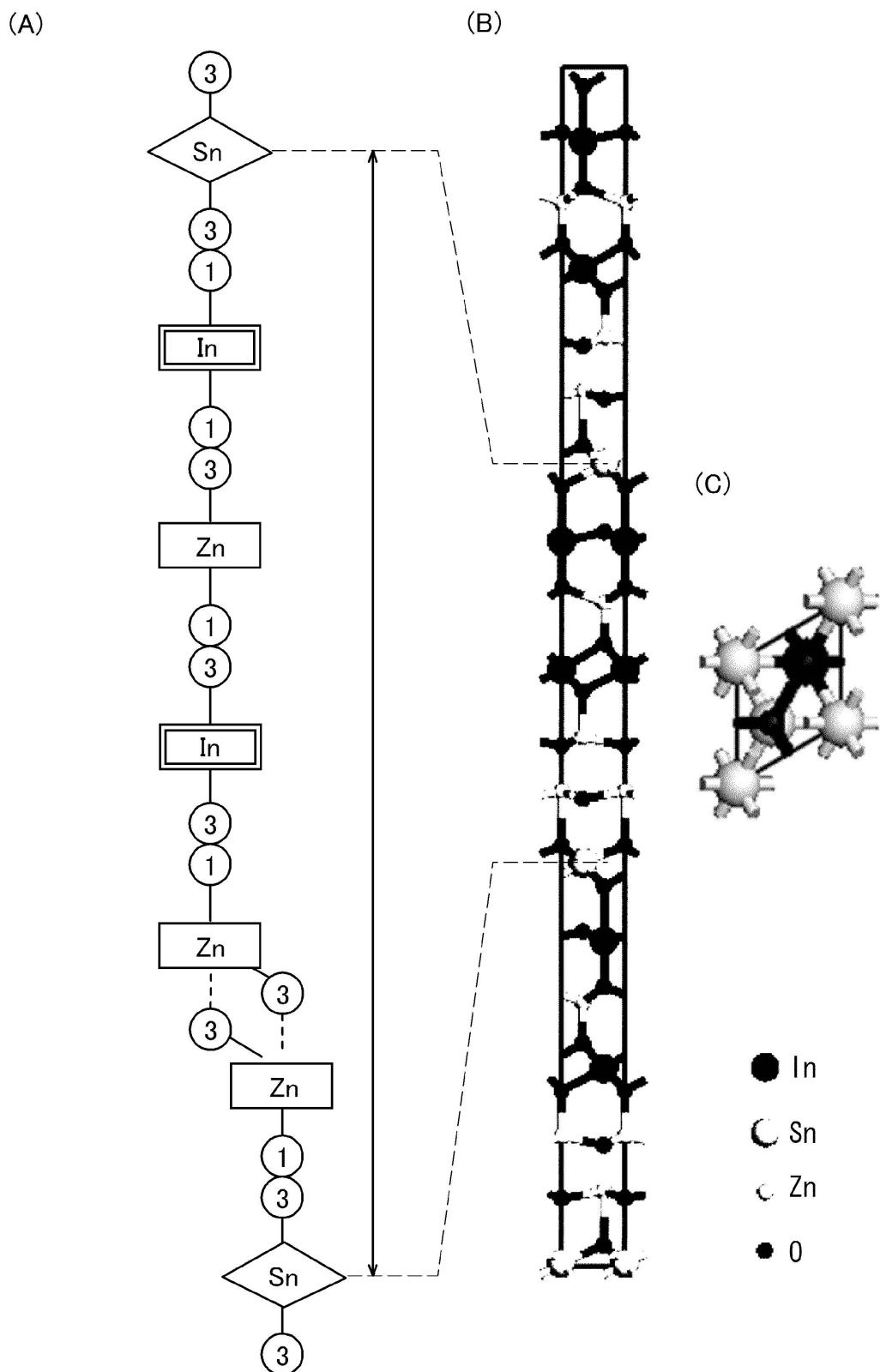

図12(A)に、In-Sn-Zn-O系の層構造を構成する中グループのモデル図を示す。図12(B)に、3つの中グループで構成される大グループを示す。なお、図12(C)は、図12(B)の層構造をc軸方向から観察した場合の原子配列を示す。

#### 【0088】

図12(A)においては、簡単のため、3配位のOは省略し、4配位のOは個数のみ示し、例えば、Snの上半分および下半分にはそれぞれ3個ずつ4配位のOがあることを丸枠の3として示している。同様に、図12(A)において、Inの上半分および下半分にはそれぞれ1個ずつ4配位のOがあり、丸枠の1として示している。また、同様に、図12(A)において、下半分には1個の4配位のOがあり、上半分には3個の4配位のOがあるZnと、上半分には1個の4配位のOがあり、下半分には3個の4配位のOがあるZnとを示している。

#### 【0089】

図12(A)において、In-Sn-Zn-O系の層構造を構成する中グループは、上から順に4配位のOが3個ずつ上半分および下半分にあるSnが、4配位のOが1個ずつ上半分および下半分にあるInと結合し、そのInが、上半分に3個の4配位のOがあるZnと結合し、そのZnの下半分の1個の4配位のOを介して4配位のOが3個ずつ上半分および下半分にあるInと結合し、そのInが、上半分に1個の4配位のOがあるZn2個からなる小グループと結合し、この小グループの下半分の1個の4配位のOを介して4配位のOが3個ずつ上半分および下半分にあるSnと結合している構成である。この中グループが複数結合して大グループを構成する。

#### 【0090】

ここで、3配位のOおよび4配位のOの場合、結合1本当たりの電荷はそれれ-0.667、-0.5と考えることができる。例えば、In(6配位または5配位)、Zn(4配位)、Sn(5配位または6配位)の電荷は、それぞれ+3、+2、+4である。従って、Snを含む小グループは電荷が+1となる。そのため、Snを含む層構造を形成するためには、電荷+1を打ち消す電荷-1が必要となる。電荷-1をとる構造として、図11(E)に示すように、2個のZnを含む小グループが挙げられる。例えば、Snを含む小グループが1個に対し、2個のZnを含む小グループが1個あれば、電荷が打ち消されるため、層構造の合計の電荷を0とすることができる。

#### 【0091】

具体的には、図12(B)に示した大グループが繰り返されることで、In-Sn-Zn

10

20

30

40

50

- O 系の結晶 ( $In_2SnZn_3O_8$ ) を得ることができる。なお、得られる In - Sn - Zn - O 系の層構造は、 $In_2SnZn_2O_7$  ( $ZnO$ )<sub>m</sub> (m は 0 または自然数。) とする組成式で表すことができる。

#### 【0092】

また、このほかにも、四元系金属の酸化物である In - Sn - Ga - Zn 系酸化物や、三元系金属の酸化物である In - Ga - Zn 系酸化物 (IGZOとも表記する。)、In - Al - Zn 系酸化物、Sn - Ga - Zn 系酸化物、Al - Ga - Zn 系酸化物、Sn - Al - Zn 系酸化物や、In - Hf - Zn 系酸化物、In - La - Zn 系酸化物、In - Ce - Zn 系酸化物、In - Pr - Zn 系酸化物、In - Nd - Zn 系酸化物、In - Sm - Zn 系酸化物、In - Eu - Zn 系酸化物、In - Gd - Zn 系酸化物、In - Tb - Zn 系酸化物、In - Dy - Zn 系酸化物、In - Ho - Zn 系酸化物、In - Er - Zn 系酸化物、In - Tm - Zn 系酸化物、In - Yb - Zn 系酸化物、In - Lu - Zn 系酸化物や、二元系金属の酸化物である In - Zn 系酸化物、Sn - Zn 系酸化物、Al - Zn 系酸化物、Zn - Mg 系酸化物、Sn - Mg 系酸化物、In - Mg 系酸化物や、In - Ga 系酸化物などを用いた場合も同様である。

10

#### 【0093】

例えば、図 13 (A) に、In - Ga - Zn - O 系の層構造を構成する中グループのモデル図を示す。

#### 【0094】

図 13 (A) において、In - Ga - Zn - O 系の層構造を構成する中グループは、上から順に 4 配位の O が 3 個ずつ上半分および下半分にある In が、4 配位の O が 1 個上半分にある Zn と結合し、その Zn の下半分の 3 個の 4 配位の O を介して、4 配位の O が 1 個ずつ上半分および下半分にある Ga と結合し、その Ga の下半分の 1 個の 4 配位の O を介して、4 配位の O が 3 個ずつ上半分および下半分にある In と結合している構成である。この中グループが複数結合して大グループを構成する。

20

#### 【0095】

図 13 (B) に 3 つの中グループで構成される大グループを示す。なお、図 13 (C) は、図 13 (B) の層構造を c 軸方向から観察した場合の原子配列を示している。

#### 【0096】

ここで、In (6 配位または 5 配位)、Zn (4 配位)、Ga (5 配位) の電荷は、それぞれ +3、+2、+3 であるため、In、Zn および Ga のいずれかを含む小グループは、電荷が 0 となる。そのため、これらの小グループの組み合わせであれば中グループの合計の電荷は常に 0 となる。

30

#### 【0097】

また、In - Ga - Zn - O 系の層構造を構成する中グループは、図 13 (A) に示した中グループに限定されず、In、Ga、Zn の配列が異なる中グループを組み合わせた大グループも取りうる。

#### 【0098】

また、In - Sn - Zn 系酸化物は、ITZO と呼ぶことができ、用いるターゲットの組成比は、In : Sn : Zn が原子数比で、1 : 2 : 2、2 : 1 : 3、1 : 1 : 1、または 20 : 45 : 35 などとなる酸化物ターゲットを用いる。

40

#### 【0099】

なお本明細書の酸化物半導体膜において、二次イオン質量分析法 (SIMS : Secondary Ion Mass Spectroscopy) によって測定されたナトリウム (Na) の濃度は、 $5 \times 10^{16} \text{ cm}^{-3}$  以下、好ましくは  $1 \times 10^{16} \text{ cm}^{-3}$  以下、さらに好ましくは  $1 \times 10^{15} \text{ cm}^{-3}$  以下が好適である。また本明細書の酸化物半導体膜において、SIMS によって測定されたリチウム (Li) の濃度は、 $5 \times 10^{15} \text{ cm}^{-3}$  以下、好ましくは  $1 \times 10^{15} \text{ cm}^{-3}$  以下が好適である。また本明細書の酸化物半導体膜において、SIMS によって測定されたカリウム (K) の濃度は、 $5 \times 10^{15} \text{ cm}^{-3}$  以下、好ましくは  $1 \times 10^{15} \text{ cm}^{-3}$  以下が好適である。

50

## 【0100】

当該酸化物半導体膜中において、ナトリウム（Na）、リチウム（Li）、カリウム（K）等のアルカリ金属、並びに、アルカリ土類金属の濃度が高い場合、トランジスタ特性の劣化及びトランジスタ特性のばらつきをもたらす恐れがある。そのため、トランジスタ特性の劣化及びトランジスタ特性のばらつきを抑制するために、酸化物半導体膜中のアルカリ金属及びアルカリ土類金属は、上述の濃度範囲であることが好適である。

## 【0101】

特に、酸化物半導体膜に接する絶縁膜が酸化物絶縁膜である場合、ナトリウム（Na）は、当該絶縁膜中に拡散し、ナトリウムイオン（Na<sup>+</sup>）となる。また、ナトリウム（Na）は、酸化物半導体膜中において、金属と酸素の結合を分断し、あるいは結合中に割り込む恐れがある。10

## 【0102】

ナトリウム（Na）が絶縁膜中でナトリウムイオン（Na<sup>+</sup>）となる場合、ナトリウム（Na）が酸化物半導体膜中において、金属と酸素の結合を分断し、或いは、ナトリウム（Na）が酸化物半導体膜中において、結合中に割り込む場合、トランジスタ特性の劣化（例えば、ノーマリオン化（しきい値の負へのシフト）、移動度の低下等）の原因となる恐れがある。さらに、このようなナトリウム（Na）の振る舞いは、トランジスタ特性のばらつきの原因ともなる。

## 【0103】

上述のアルカリ金属及びアルカリ土類金属に起因するトランジスタ特性の劣化及びトランジスタ特性のばらつきは、特に酸化物半導体膜中の水素の濃度が十分に低い場合において顕著となる。従って、酸化物半導体膜中の水素の濃度が、 $5 \times 10^{19} \text{ cm}^{-3}$  以下、特に  $5 \times 10^{18} \text{ cm}^{-3}$  以下である場合には、アルカリ金属の濃度を上述の値にすることが好適である。20

## 【0104】

またソース電極又はドレイン電極の一方である電極105aは、ゲート電極102aの一部及び酸化物半導体膜104の一部と重畳している。また、ソース電極又はドレイン電極の他方である電極105bは、ゲート電極102bの一部及び酸化物半導体膜104の一部と重畳している。

## 【0105】

電極105a及び電極105bそれぞれは、アルミニウム（Al）、クロム（Cr）、タンタル（Ta）、チタン（Ti）、モリブデン（Mo）、タンクステン（W）から選ばれた元素を含む導電膜、上述した元素を成分とする合金膜、或いは上述した元素を組み合わせた合金膜等を用いる。30

## 【0106】

なお、アルミニウム（Al）単体のアルミニウム膜は、耐熱性が劣り、また腐蝕しやすい等の問題点がある。そのため、電極105a及び電極105bそれぞれをアルミニウム（Al）を用いて形成する場合は、アルミニウム（Al）と耐熱性導電性材料を組み合わせて形成する。

## 【0107】

アルミニウム（Al）と組み合わせる耐熱性導電性材料としては、チタン（Ti）、タンタル（Ta）、タンクステン（W）、モリブデン（Mo）、クロム（Cr）、ネオジム（Nd）、スカンジウム（Sc）から選ばれた元素を含む材料、または上述した元素を成分とする合金材料、上述した元素を組み合わせた合金材料、または上述した元素を成分とする窒化物を用いる。40

## 【0108】

また第1のゲート電極であるゲート電極102a、第2のゲート電極であるゲート電極102b、ゲート絶縁膜123、酸化物半導体膜104、ソース電極又はドレイン電極の一方である電極105a、ソース電極又はドレイン電極の他方である電極105bを覆って、絶縁膜126が形成されている。絶縁膜126は、酸化物半導体膜104に直接接触し50

て設けられている絶縁膜であり、酸化物半導体膜 104 を保護する保護膜である。

【0109】

絶縁膜 126 は、ゲート絶縁膜 123 と同様に、酸化珪素膜、酸化窒化珪素膜、窒化酸化珪素膜、窒化珪素膜を用いた単層構造、或いはこれらの膜を積層した積層構造を用いてもよい。保護膜は、大気中に浮遊する有機物や金属物、水蒸気などの汚染不純物の侵入を防ぐためのものであり、緻密な膜が好ましい。

【0110】

図 1 (A) は、酸化物半導体トランジスタ 100 の上面図であり、図 1 (A) の A - A' の断面図が、図 1 (B) となる。

【0111】

酸化物半導体膜 104 中の電極 105a 及び電極 105b (ソース電極及びドレイン電極)との間の領域が、チャネル形成領域となる。よって図 1 (A) に示すように、電極 105a の端部及び電極 105b の端部との間の距離が、チャネル長 L となる。また電極 105a 又は電極 105b のチャネル長と垂直な一辺の長さが、チャネル幅 W となる。

【0112】

よって当該チャネル形成領域、かつ、酸化物半導体膜 104 がゲート電極 102a 及びゲート電極 102b に重畠しない領域が、 $L_{\text{off}}$  領域 109 となる。 $L_{\text{off}}$  領域 109 のチャネル長方向の長さを長さ F とする。

【0113】

$L_{\text{off}}$  領域 109 のチャネル長方向の長さである長さ F は、短すぎるとオン電流低減の効果が望めず、長すぎるとチャネル形成領域の抵抗が増大する。よって、 $L_{\text{off}}$  領域 109 のチャネル長方向の長さである長さ F は、1 μm 以上 20 μm 以下が好適である。

【0114】

$L_{\text{off}}$  領域 109 を設けることにより、酸化物半導体トランジスタ 100 のオン電流を低減することができる。よって、占有面積を増大することなくオン電流を低減できる酸化物半導体トランジスタ 100 を得ることができる。

【0115】

このように  $L_{\text{off}}$  領域 109 を設けることによってオン電流が低減された酸化物半導体トランジスタ 100 は、表示装置の画素に用いることができる。画素に酸化物半導体トランジスタ 100 を用いた表示装置については、後述する。

【0116】

なお本実施の形態では、酸化物半導体トランジスタ 100 として、ボトムゲート構造を有するトランジスタについて説明したが、開示される発明の一態様はこれに限定されない。第 1 のゲート電極と第 2 のゲート電極が互いに離れており、ゲート絶縁膜を介して、当該第 1 のゲート電極と第 2 のゲート電極に重畠する領域と重畠しない領域を有する酸化物半導体トランジスタは、トップゲート構造であってもオン電流低減の効果が望めるので好適である。

【0117】

<同一基板上に設けられた  $L_{\text{off}}$  領域を設けない酸化物半導体トランジスタ及び  $L_{\text{off}}$  領域を設けた酸化物半導体トランジスタ>

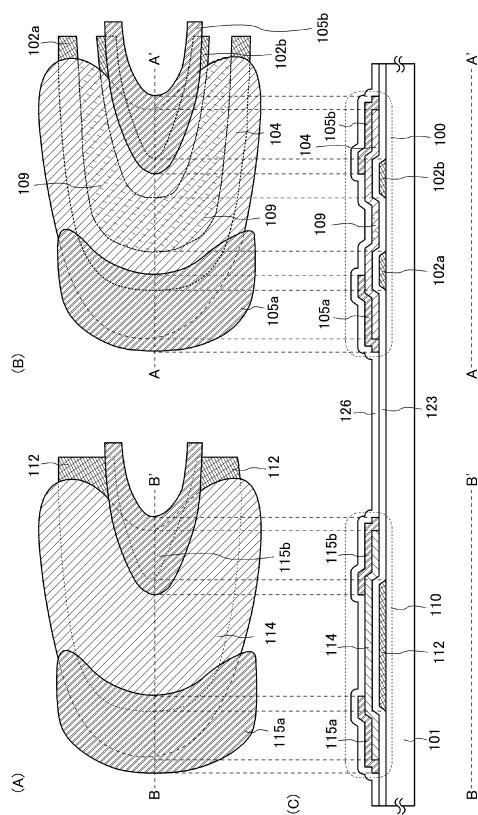

図 2 (A) ~ 図 2 (C) に、 $L_{\text{off}}$  領域を設けない酸化物半導体トランジスタ 110 及び  $L_{\text{off}}$  領域 109 を設けた酸化物半導体トランジスタ 100 の上面図と断面図を示す。

【0118】

図 2 (C)において、A - A' の断面図が図 2 (B)に対応し、B - B' の断面図が図 2 (A)に対応する。なお、図 2 (B) は図 1 (A) と同じ図面であり、図 2 (C) の A - A' の断面図は、図 1 (B) と同じ図面である。図 2 (B) 及び図 2 (C) に示される酸化物半導体トランジスタ 100 の詳細な説明については、上述したので割愛する。

【0119】

図 2 (A) 及び図 2 (C) で示す酸化物半導体トランジスタ 110 は、絶縁表面を有する

10

20

30

40

50

基板 101 上に形成されている。

**【0120】**

酸化物半導体トランジスタ 110 は、基板 101 上に設けられ、第 3 のゲート電極であるゲート電極 112、及びゲート絶縁膜 123 を有している。ゲート電極 112 の材料は、ゲート電極 102a 及びゲート電極 102b と同様である。

**【0121】**

また酸化物半導体トランジスタ 110 は、ゲート電極 112 上にゲート絶縁膜 123 を介して設けられ、チャネル形成領域が形成される第 2 の酸化物半導体膜である酸化物半導体膜 114 を有している。酸化物半導体膜 114 の材料は、酸化物半導体膜 104 と同様である。

10

**【0122】**

また酸化物半導体トランジスタ 110 は、ゲート電極 112 の一部及び酸化物半導体膜 114 の一部と重畳し、ソース電極又はドレイン電極の一方である電極 115a、及び、ゲート電極 112 の一部及び酸化物半導体膜 114 の一部と重畳し、ソース電極又はドレイン電極の他方である電極 115b を有している。電極 115a 及び電極 115b の材料は、電極 105a 及び電極 105b と同様である。

**【0123】**

また酸化物半導体トランジスタ 100 と同様に、酸化物半導体トランジスタ 110 において、ゲート電極 112、ゲート絶縁膜 123、酸化物半導体膜 114、ソース電極又はドレイン電極の一方である電極 115a、ソース電極又はドレイン電極の他方である電極 115b を覆って、絶縁膜 126 が形成されている。絶縁膜 126 は、酸化物半導体膜 114 に直接接触して設けられている絶縁膜であり、酸化物半導体膜 114 を保護する保護膜である。

20

**【0124】**

酸化物半導体トランジスタ 110 は、 $L_{ff}$  領域が設けられていないので、オン電流が高い。このようなオン電流の高い酸化物半導体トランジスタ 110 は、表示装置の駆動回路に用いることができる。酸化物半導体トランジスタ 110 を駆動回路に用いた表示装置については、後述する。

**【0125】**

なお図 2(A) ~ 図 2(C)においては、酸化物半導体トランジスタ 100 のゲート電極 102a、ゲート電極 102b、酸化物半導体膜 104、電極 105a、及び、電極 105b、並びに、酸化物半導体トランジスタ 110 のゲート電極 112、酸化物半導体膜 114、電極 115a、及び、電極 115b を矩形としたが、本実施の形態はこれに限定されない。酸化物半導体トランジスタ 100 及び酸化物半導体トランジスタ 110 を構成するゲート電極、酸化物半導体膜、ソース電極及びドレイン電極を、図 10(A) ~ 図 10(C)に示すように、湾曲形状を有するように形成してもよい。ゲート電極、酸化物半導体膜、ソース電極及びドレイン電極が湾曲形状を有する酸化物半導体トランジスタにおいても、 $L_{ff}$  領域が形成された酸化物半導体トランジスタは、オン電流が低いという点において好適である。また $L_{ff}$  領域が形成されない酸化物半導体トランジスタは、オン電流が高いので駆動回路に用いることが可能である。

30

**【0126】**

また本実施の形態では、酸化物半導体トランジスタ 100 及び酸化物半導体トランジスタ 110 として、ボトムゲート構造を有するトランジスタについて説明したが、本実施の形態はこれに限定されない。トップゲート構造の酸化物半導体トランジスタにおいても、 $L_{ff}$  領域が形成された酸化物半導体トランジスタは、オン電流が低いという点において好適である。また $L_{ff}$  領域が形成されない酸化物半導体トランジスタは、オン電流が高いので駆動回路に用いることが可能である。

40

**【0127】**

同一基板 101 上に、 $L_{ff}$  領域を設けない酸化物半導体トランジスタ 110、及び $L_{ff}$  領域 109 を設けた酸化物半導体トランジスタ 100 の作製方法について、以下に

50

述べる。

**【0128】**

まず絶縁表面を有する基板101上に、ゲート電極112、ゲート電極102a、及びゲート電極102bを作製する(図3(A)参照)。

**【0129】**

ゲート電極112、ゲート電極102a、及びゲート電極102bは、スパッタリング法や真空蒸着法で、導電膜を形成し、当該導電膜をエッチングすることによって形成する。あるいは、導電性ナノペーストを用い、インクジェット法により吐出し焼成することにより、ゲート電極112、ゲート電極102a、及びゲート電極102bを形成してもよい。

**【0130】**

次いで、基板101、ゲート電極112、ゲート電極102a、及びゲート電極102bを覆って、ゲート絶縁膜123を形成する(図3(B)参照)。

**【0131】**

ゲート絶縁膜123を覆って、酸化物半導体膜124を形成する(図3(C)参照)。酸化物半導体膜124は、上述した酸化物半導体膜104の材料をターゲットとして用い、スパッタ法にて形成すればよい。

**【0132】**

次いで酸化物半導体膜124をエッチングにて加工し、ゲート電極112上にゲート絶縁膜123を介して酸化物半導体膜114、並びに、ゲート電極102a及びゲート電極102b上にゲート絶縁膜123を介して酸化物半導体膜104が形成される(図4(A)参照)。これにより、酸化物半導体トランジスタ110のチャネル形成領域である酸化物半導体膜である114、及び酸化物半導体トランジスタ100のチャネル形成領域である酸化物半導体膜104を、同じ材料及び同じ工程で形成することができる。

**【0133】**

図4(A)において、酸化物半導体膜104中の領域で、ゲート電極102a及びゲート電極102bの間の領域、すなわちゲート電極と酸化物半導体膜104が重畠しない領域が、 $L_{ff}$ 領域109となる。 $L_{ff}$ 領域109が存在することにより、酸化物半導体トランジスタ100のオン電流が低減される。

**【0134】**

ゲート絶縁膜123、酸化物半導体膜114、及び酸化物半導体膜104を覆って、導電膜125を形成する(図4(B)参照)。導電膜125は、上述した電極105a及び電極105bの材料をターゲットとして用い、スパッタ法にて形成すればよい。

**【0135】**

次いで、導電膜125をエッチングして、酸化物半導体トランジスタ110のソース電極及びドレイン電極である電極115a及び電極115b、並びに、酸化物半導体トランジスタ100のソース電極及びドレイン電極である電極105a及び電極105bを形成する。以上により、酸化物半導体トランジスタ110及び酸化物半導体トランジスタ100が作製される(図4(C)参照)。

**【0136】**

次いで、酸化物半導体トランジスタ110及び酸化物半導体トランジスタ100を覆って、保護膜として機能する絶縁膜126を形成する(図2(C)参照)。

**【0137】**

酸化物半導体トランジスタ110は、 $L_{ff}$ 領域が形成されないため、オン電流が高い。一方、酸化物半導体トランジスタ100は、 $L_{ff}$ 領域109が設けられているため、オン電流が低減される。

**【0138】**

以上のようにして、同一基板101上に、オン電流が低い酸化物半導体トランジスタ100及びオン電流が高い酸化物半導体トランジスタ110を作製することができる。

**【0139】**

なお、本実施の形態においては、酸化物半導体膜124をエッチングして酸化物半導体膜

10

20

30

40

50

114 及び酸化物半導体膜 104 を形成した後、導電膜 125 を形成し、導電膜 125 をエッティングすることにより電極 115a、電極 115b、電極 105a、及び電極 105b を形成する。しかし本実施の形態は、上述の作製工程に限定されない。酸化物半導体膜 124 及び導電膜 125 を形成し、酸化物半導体膜 124 及び導電膜 125 を、同じマスクを用いてエッティングしてもよい。酸化物半導体膜 124 及び導電膜 125 を、同じマスクを用いてエッティングすると、マスク数を減らすことができ、作製工程を減らすことが可能である。

#### 【0140】

このように、オン電流が低い酸化物半導体トランジスタ 100 とオン電流が高い酸化物半導体トランジスタ 110 を同一基板 101 上に作製すると、酸化物半導体トランジスタの作製工程が削減でき、作製コストを抑制することができる。10

#### 【0141】

なお本実施の形態では、オン電流が低い酸化物半導体トランジスタ 100 及びオン電流が高い酸化物半導体トランジスタ 110 として、ボトムゲート構造のトランジスタを作製する例について述べたが、開示される発明の一態様はこれに限定されない。酸化物半導体トランジスタ 100 及び酸化物半導体トランジスタ 110 としてトップゲート構造を有するトランジスタを用いた場合においても、同一基板上にそれぞれのトランジスタを同時に作製することが可能である。これにより、酸化物半導体トランジスタの作製工程が削減でき、作製コストを抑制することができる。

#### 【0142】

##### <表示装置>

本実施の形態では、本発明の一態様に係る表示装置として、発光表示装置の例を示す。表示装置の有する表示素子としては、ここではエレクトロルミネッセンスを利用する発光素子を用いて示す。エレクトロルミネッセンスを利用する発光素子は、発光材料が有機化合物であるか、無機化合物であるかによって区別され、一般的に、前者は有機EL素子、後者は無機EL素子と呼ばれている。

#### 【0143】

有機EL素子は、発光素子に電圧を印加することにより、一対の電極から電子および正孔がそれぞれ発光性の有機化合物を含む層に注入され、電流が流れる。そして、それらキャリア（電子および正孔）が再結合することにより、発光性の有機化合物が励起状態を形成し、その励起状態が基底状態に戻る際に発光する。このようなメカニズムから、このような発光素子は、電流励起型の発光素子と呼ばれる。30

#### 【0144】

無機EL素子は、その素子構成により、分散型無機EL素子と薄膜型無機EL素子とに分類される。分散型無機EL素子は、発光材料の粒子をバインダ中に分散させた発光層を有するものであり、発光メカニズムはドナー準位とアクセプター準位を利用するドナー-アクセプター再結合型発光である。薄膜型無機EL素子は、発光層を誘電体層で挟み込み、さらにそれを電極で挟んだ構造であり、発光メカニズムは金属イオンの内殻電子遷移を利用する局在型発光である。なお、ここでは、発光素子として有機EL素子を用いて説明する。40

#### 【0145】

図 5 (A) に、本発明の一態様に係る発光表示装置の一例として、アクティブマトリクス型EL表示装置を示す。図 5 (A) に示す発光表示装置は、絶縁表面を有する基板 101 上に、複数の画素 136 を有する画素部 131、並びに、画素部 131 を駆動する駆動回路であるゲートドライバ 132 及びソースドライバ 134 を有する。

#### 【0146】

画素部 131 は、ソースドライバ 134 から伸張して配置された複数のソース線 135 により、ソースドライバ 134 と接続されている。また画素部 131 は、ゲートドライバ 132 から伸張して配置された複数のゲート線 133 によりゲートドライバ 132 と接続されている。また画素部 131 は、ソース線 135 及びゲート線 133 に対応して、マトリ50

クス状に配置された複数の画素 136 を有する。

【0147】

各画素 136 は、トランジスタ 141、トランジスタ 142、発光素子 144、容量素子 143、ソース線 135、ゲート線 133、電源線 137 を含む（図 5（B）参照）。

【0148】

トランジスタ 141 のソース又はドレインの一方は、ソース線 135 に電気的に接続されている。トランジスタ 141 のソース又はドレインの他方は、容量素子 143 の一方の端子、及びトランジスタ 142 のゲートに電気的に接続されている。トランジスタ 141 のゲートは、ゲート線 133 に電気的に接続されている。トランジスタ 141 は、トランジスタ 142 のオン及びオフを制御するスイッチング素子として機能する。

10

【0149】

トランジスタ 142 のソース又はドレインの一方は、発光素子 144 に電気的に接続されている。トランジスタ 142 のソース又はドレインの他方は、容量素子 143 の他方の端子、及び電源線 137 に電気的に接続されている。トランジスタ 142 のゲートは、トランジスタ 141 のソース又はドレインの他方、及び容量素子 143 の一方の端子に電気的に接続されている。トランジスタ 142 は、発光素子 144 に流す電流の制御を行う電流制御素子として機能する。

【0150】

容量素子 143 の一方の端子は、トランジスタ 141 のソース又はドレインの他方、及びトランジスタ 142 のゲートに電気的に接続されている。容量素子 143 の他方の端子は、トランジスタ 142 のソース又はドレインの他方、及び電源線 137 に電気的に接続されている。

20

【0151】

発光素子 144 は、トランジスタ 142 のソース又はドレインの一方電気的に接続されている。

【0152】

画素 136 に用いられるトランジスタ 141 及びトランジスタ 142 はそれぞれ、図 1（A）～図 1（B）及び図 2（B）～図 2（C）で説明された酸化物半導体トランジスタ 100 を用いることができる。

30

【0153】

画素 136 に用いるトランジスタ 141 及びトランジスタ 142 として、 $L_{\text{off}}$  領域 109 を有する酸化物半導体トランジスタ 100 を用いると、占有面積を増大させずに、オン電流が低減されたトランジスタ 141 及びトランジスタ 142 を得ることができる。

【0154】

以上説明したように、オン電流が低減された酸化物半導体トランジスタを画素 136 に用いた発光表示装置は、発光表示装置の開口率が減少するのを抑制することができる。

【0155】

また、発光素子 144 の電流制御用トランジスタであるトランジスタ 142 として、オン電流が低減されたトランジスタを用いると、トランジスタ 142 の駆動電圧が変化してもドレイン電流の変化量が小さいという点で特に好適である。その理由を以下に説明する。

40

【0156】

本実施の形態の発光表示装置の輝度は、発光素子 144 及びトランジスタ 142 の電流に依存する。そのため、発光素子 144 及びトランジスタ 142 の特性が発光表示装置の輝度にとっては重要である。

【0157】

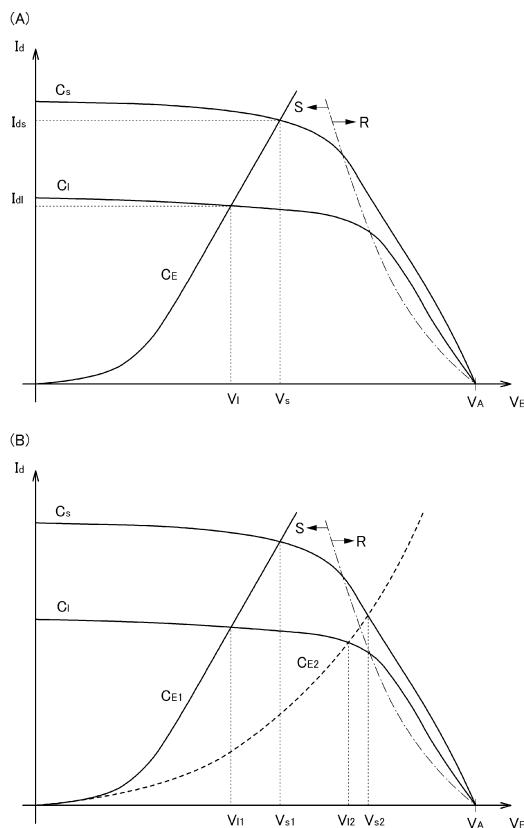

図 5 に示すトランジスタ 142 として、チャネル長が長いことによりオン電流が低いトランジスタを用いた場合と、チャネル長が短いことによりオン電流が高いトランジスタを用いた場合の特性の違いを、図 9（A）及び図 9（B）を用いて説明する。

【0158】

まず図 5において、トランジスタ 142 のソース又はドレインのうち、電源線 137 と接

50

続されている側の電圧を $V_A$ 、またトランジスタ142のソース又はドレインのうち、発光素子144と接続されている側の電圧を電圧 $V_E$ とする。

【0159】

図9(A)及び図9(B)は、オン電流が低い(チャネル長が長い)トランジスタ及びオン電流が高い(チャネル長が短い)トランジスタそれぞれにおいて、電圧 $V_E$ 及びドレン電流 $I_d$ 特性(以下「 $V_E - I_d$ 特性」ともいう)、並びに、発光素子144の電圧特性を示す。なおこのとき、オン電流が低い(チャネル長が長い)トランジスタ及びオン電流が高い(チャネル長が短い)トランジスタのゲート及びソース間電圧 $V_{gs}$ は等しいものとする。

【0160】

図9(A)において、発光素子144の電圧特性の曲線を曲線 $C_E$ とする。

【0161】

また、オン電流が低い(チャネル長が長い)トランジスタの $V_E - I_d$ 特性の曲線を曲線 $C_1$ 、曲線 $C_1$ が曲線 $C_E$ と交わる点の電圧を電圧 $V_1$ 、及び、曲線 $C_1$ が曲線 $C_E$ と交わる点の電流を $I_{d1}$ とする。

【0162】

また、オン電流が高い(チャネル長が短い)トランジスタの $V_E - I_d$ 特性の曲線を曲線 $C_s$ 、曲線 $C_s$ が曲線 $C_E$ と交わる点の電圧を電圧 $V_s$ 、及び、曲線 $C_s$ が曲線 $C_E$ と交わる点の電流を $I_{ds}$ とする。

【0163】

曲線 $C_1$ 及び曲線 $C_s$ はそれぞれ、電圧 $V_E$ に対してドレン電流 $I_d$ がほぼ変化しない領域である飽和領域S、及び、電圧 $V_E$ に対してドレン電流 $I_d$ に対して線形に変化する線形領域Rを有する。

【0164】

電圧 $V_1$ はオン電流が低い(チャネル長が長い)トランジスタの駆動電圧、電圧 $V_s$ はオン電流が高い(チャネル長が短い)トランジスタの駆動電圧となる。

【0165】

ここで図9(B)に、発光素子144が劣化し、発光素子144に流せる電流が低くなつた場合の電圧特性を示す。

【0166】

図9(B)においては、劣化前の発光素子144の電圧特性の曲線 $C_E$ を曲線 $C_{E1}$ とし、劣化後の発光素子144の電圧特性の曲線 $C_E$ を曲線 $C_{E2}$ とする。

【0167】

また、オン電流が低い(チャネル長が長い)トランジスタの $V_E - I_d$ 特性の曲線 $C_1$ が、曲線 $C_{E1}$ と交わる点の電圧を駆動電圧 $V_{11}$ とする。オン電流が高い(チャネル長が短い)トランジスタの $V_E - I_d$ 特性の曲線 $C_s$ が、曲線 $C_{E1}$ と交わる点の電圧を駆動電圧 $V_{s1}$ とする。

【0168】

同様に、オン電流が低い(チャネル長が長い)トランジスタの $V_E - I_d$ 特性の曲線 $C_1$ が、曲線 $C_{E2}$ と交わる点の電圧を駆動電圧 $V_{12}$ とする。オン電流が高い(チャネル長が短い)トランジスタの $V_E - I_d$ 特性の曲線 $C_s$ が、曲線 $C_{E2}$ と交わる点の電圧を駆動電圧 $V_{s2}$ とする。

【0169】

発光素子144が劣化し、発光素子144に流せる電流が低くなると、発光素子144に印加する電圧を増加させなければならない。そのため、駆動電圧 $V_{11}$ 及び駆動電圧 $V_{s1}$ よりも、駆動電圧 $V_{12}$ 及び駆動電圧 $V_{s2}$ の方が電圧値が高くなる。さらに、駆動電圧 $V_{12}$ 及び駆動電圧 $V_{s2}$ が高くなると、駆動電圧 $V_{12}$ 及び駆動電圧 $V_{s2}$ が線形領域Rに入る恐れがある。

【0170】

図9(B)では、オン電流が高い(チャネル長が短い)トランジスタを用いた場合の駆動

10

20

30

40

50

電圧  $V_{S2}$  が線形領域 R に入った場合を示している。駆動電圧が線形領域 R に入ると、駆動電圧の小さな変化でドレンイン電流が大きく変化してしまう恐れがある。

【0171】

一方、オン電流が低い（チャネル長が長い）トランジスタを用いた場合の駆動電圧  $V_{12}$  は、線形領域 R に入らず、飽和領域 S に存在する。

【0172】

そのためオン電流が低い（チャネル長が長い）トランジスタでは、駆動電圧が変化してもドレンイン電流の変化量が小さいという効果を奏する。

【0173】

よって、トランジスタ 142 としてオン電流が低い（チャネル長の長い）トランジスタを用いると、トランジスタ 142 の駆動電圧が変化してもドレンイン電流の変化量が小さいという点で特に好適である。10

【0174】

また当該複数の画素 136 を有する画素部 131 を駆動するゲートドライバ 132 及びソースドライバ 134 に用いるトランジスタとして、図 2 (A) 及び図 2 (C) で説明された酸化物半導体トランジスタ 110 を用いることができる。

【0175】

ゲートドライバ 132 及びソースドライバ 134 に用いるトランジスタとして酸化物半導体トランジスタ 110 を用いると、オン電流が高い酸化物半導体トランジスタ 110 と、上記オン電流が低い酸化物半導体トランジスタ 100 を、同一基板 101 上に作製することができる。20

【0176】

オン電流が高い酸化物半導体トランジスタ 110 とオン電流が低い酸化物半導体トランジスタ 100 を同一基板 101 上に作製すると、酸化物半導体トランジスタ 110 及び酸化物半導体トランジスタ 100 の作製工程が削減でき、作製コストを抑制することができる。

【0177】

よって、本実施の形態により、同一基板 101 上に、画素 136 にオン電流が低い酸化物半導体トランジスタ 100 を用い、かつ駆動回路（ゲートドライバ 132 及びソースドライバ 134）にオン電流が高い酸化物半導体トランジスタ 110 を用いた表示装置を得ることができる。30

【0178】

よって、複数の画素 136 を有する画素部 131、及び駆動回路（ゲートドライバ 132 及びソースドライバ 134）に用いられるトランジスタとして、それぞれ酸化物半導体トランジスタ 100 及び酸化物半導体トランジスタ 110 を同一基板 101 上に作製することができる。これにより、発光表示装置の作製において、作製工程が削減でき、作製コストを抑制することが可能となる。

【0179】

図 6 (A) ~ 図 6 (C) に、トランジスタ 142 として用いた酸化物半導体トランジスタ 100、及び発光素子 144 の断面を示す。40

【0180】

図 6 (A) に示す発光表示装置は、基板 101、トランジスタ 142 として酸化物半導体トランジスタ 100、絶縁膜 126、絶縁膜 127、隔壁 128、電極 107、発光層 152、電極 153 を有している。電極 107 は、酸化物半導体トランジスタ 100 のソース電極又はドレンイン電極の他方に電気的に接続されている。また、電極 107、発光層 152、及び電極 153 で、発光素子 144 を形成する。

【0181】

発光素子 144 は、発光を取り出すために、少なくとも陽極又は陰極の一方が透光性を有すればよい。そして、基板上にトランジスタ及び発光素子を形成し、基板とは逆側の面から発光を取り出す上面射出や、基板側の面から発光を取り出す下面射出や、基板側及び基50

板とは反対側の面から発光を取り出す両面射出構造の発光素子があり、本発明の一態様に係る画素構成はどの射出構造の発光素子にも適用することができる。

【0182】

図6(A)では、上面射出構造の発光素子144について説明する。

【0183】

絶縁膜127は、アクリル、ポリイミド、ポリアミドなどの有機樹脂、またはシリコサンを用いて形成することが好ましい。

【0184】

本実施の形態では、画素136のトランジスタ142(酸化物半導体トランジスタ100)がn型である。そのため、電極107を陰極として用いることが望ましい。具体的には、陰極としては、仕事関数が小さい材料、例えば、Ca、Al、CaF、MgAg、AlLi等の金属材料を用いることができる。

10

【0185】

隔壁128は、有機樹脂膜、無機絶縁膜、又は有機ポリシリコサンを用いて形成する。特に感光性の材料を用い、電極107上に開口部を形成し、その開口部の側壁が連続した曲率を持って形成される傾斜面となるように形成することが好ましい。

【0186】

発光層152は、単数の層で構成されていても、複数の層が積層されるように構成されていてもどちらでも良い。

【0187】

発光層152を覆うように、陽極として電極153を形成する。電極153は、透光性を有する導電性材料を用いた透光性導電膜で形成することができる。

20

【0188】

透光性を有する導電性材料として、例えば、酸化タンクス滕を含むインジウム酸化物、酸化タンクス滕を含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム錫酸化物、インジウム亜鉛酸化物、酸化ケイ素を添加したインジウム錫酸化物等が挙げられる。

【0189】

電極107、発光層152、及び電極153が重畠することにより、発光素子144が形成されている。また、発光素子144に酸素、水素、水分、二酸化炭素等が侵入しないように、電極153及び隔壁128を覆って保護膜を形成してもよい。保護膜としては、窒化珪素膜、窒化酸化珪素膜、 DLC 膜等を形成することができる。

30

【0190】

図6(A)に示した発光素子144の場合、陰極である電極107が遮光性を有する金属材料、陽極である電極153が透光性を有する導電性材料を用いて形成されている。そのため、図6(A)に示した発光素子144から発せられる光は、矢印で示すように電極153側に射出する。よって、図6(A)に示す発光素子144は、上面射出構造の発光素子である。

【0191】

なお図6(A)に示す発光素子が上面射出構造の発光素子のため、発光表示装置の開口率を上げることは難しい。しかしながら、本実施の形態により、トランジスタ142のオン電流の最適化が行われているので好適である。

40

【0192】

図6(B)では、下面射出構造の発光素子144について説明する。

【0193】

図6(B)では、画素136のトランジスタ142(酸化物半導体トランジスタ100)に電気的に接続された電極108を、上述の透光性を有する導電性材料を用いて形成する。

【0194】

透光性を有する電極108上に、発光素子144の陰極である電極154が成膜されてお

50

り、電極 154 上に発光層 152、陽極である電極 153 が順に積層されている。

【0195】

陰極である電極 154 は、図 6 (A) に示す電極 107 と同様に、仕事関数が小さい導電性材料であれば様々な材料を用いることができる。ただしその膜厚は、光を透過する程度（好ましくは、5 nm ~ 30 nm 程度）とする。例えば 20 nm の膜厚を有するアルミニウム膜を、電極 154 として用いることができる。

【0196】

陽極である電極 153 が透光性を有する場合、電極 153 を覆うように、光を反射または遮蔽するための遮蔽膜 155 を形成する。遮蔽膜 155 は、例えば光を反射する金属等を用いることができるが、金属膜に限定されない。例えば黒の顔料添加した樹脂等を用いることもできる。

10

【0197】

電極 154、発光層 152、及び電極 153 が重畳することにより、発光素子 144 が形成されている。また、発光素子 144 に酸素、水素、水分、二酸化炭素等が侵入しないように、遮蔽膜 155 及び隔壁 128 を覆って保護膜を形成してもよい。保護膜としては、窒化珪素膜、窒化酸化珪素膜、DLC 膜等を形成することができる。

【0198】

図 6 (B) に示した発光素子 144 の場合、陰極である電極 154 は光を透過する程度に薄い。また電極 154 の下方には、透光性を有する電極 108 が設けられている。また、陽極である電極 153 を覆って遮蔽膜 155 が形成されている。

20

【0199】

そのため、図 6 (B) に示した発光素子 144 から発せられる光は、矢印で示すように電極 154 側に射出する。よって、図 6 (B) に示す発光素子 144 は、下面射出構造の発光素子である。

【0200】

図 6 (B) に示す発光素子は、上面射出構造の発光素子のため、本実施の形態により発光表示装置の開口率を上げることができる。さらに、本実施の形態により、トランジスタ 142 のオン電流の最適化が行われているので好適である。

【0201】

図 6 (C) では、両面射出構造の発光素子 144 について説明する。

30

【0202】

図 6 (C) では、図 6 (B) と同様に、画素 136 のトランジスタ 142 (酸化物半導体トランジスタ 100) に電気的に接続された電極 108 を、上述の透光性を有する導電性材料を用いて形成する。

【0203】

また図 6 (C) に示す発光素子 144 において、図 6 (B) と同様に、透光性を有する電極 108 上に、発光素子 144 の陰極である電極 154 が成膜されており、電極 154 上に発光層 152、陽極である電極 153 が順に積層されている。

【0204】

陰極である電極 154 は、図 6 (A) に示す電極 107 と同様に、仕事関数が小さい導電性材料であれば様々な材料を用いることができる。ただしその膜厚は、光を透過する程度（好ましくは、5 nm ~ 30 nm 程度）とする。例えば 20 nm の膜厚を有するアルミニウム膜を、電極 154 として用いることができる。

40

【0205】

電極 154、発光層 152、及び電極 153 が重畳することにより、発光素子 144 が形成されている。また、発光素子 144 に酸素、水素、水分、二酸化炭素等が侵入しないように、電極 153 及び隔壁 128 を覆って保護膜を形成してもよい。保護膜としては、窒化珪素膜、窒化酸化珪素膜、DLC 膜等を形成することができる。

【0206】

図 6 (C) に示した発光素子 144 の場合、陰極である電極 154 は光を透過する程度に

50

薄い。また電極 154 の下方には、透光性を有する電極 108 が設けられている。また、陽極である電極 153 も透光性を有する導電材料を用いて形成されている。

#### 【0207】

そのため、図 6 (C) に示した発光素子 144 から発せられる光は、矢印で示すように電極 154 側及び電極 153 側の両方に射出する。よって、図 6 (C) に示す発光素子 144 は、両面射出構造の発光素子である。

#### 【0208】

さらに、以上のようにして作製された発光素子 144 を、さらに外気に曝されないように気密性が高く、脱ガスの少ない保護フィルム（貼り合わせフィルム、紫外線硬化樹脂フィルム等）やカバー材でパッケージング（封入）することが好ましい。

10

#### 【0209】

なお、ここでは、発光素子 144 として有機 EL 素子について述べたが、発光素子 144 として無機 EL 素子を設けることも可能である。

#### 【0210】

また、酸化物半導体トランジスタ 100 において、必要であれば、 $L_{ff}$  領域 109 を遮光する遮光膜、更に或いは酸化物半導体トランジスタ 100 全体を遮光する遮光膜を設けてもよい。このような遮光膜を設けることにより、光の取り出し効率を高めることができる。

#### 【0211】

<表示パネル>

20

図 7 (A) 及び図 7 (B) は、本実施の形態の表示装置の一形態である表示パネルの上面図及び断面図である。図 7 (B) は、図 7 (A) の C-C' の断面図に相当する。

#### 【0212】

第 1 の基板 101 上に設けられた画素部 131、ゲートドライバ 132a、ゲートドライバ 132b、ソースドライバ 134a、及びソースドライバ 134b を囲むようにして、シール材 162 が設けられている。また画素部 131、ゲートドライバ 132a、ゲートドライバ 132b、ソースドライバ 134a、及びソースドライバ 134b の上に第 2 の基板 161 が設けられている。画素部 131、ゲートドライバ 132a、ゲートドライバ 132b、ソースドライバ 134a、及びソースドライバ 134b は、第 1 の基板 101、第 2 の基板 161、及びシール材 162 によって、充填材 169 と共に密封されている。

30

#### 【0213】

第 1 の基板 101 上に設けられた画素部 131 に用いられるトランジスタとして、上述のように、図 1 (A) ~ 図 1 (B) 及び図 2 (B) ~ 図 2 (C) で説明された酸化物半導体トランジスタ 100 を用いることができる。

#### 【0214】

画素部 131 に用いられるトランジスタとして、 $L_{ff}$  領域 109 を有する酸化物半導体トランジスタ 100 を用いると、画素部 131 に用いられるトランジスタは、占有面積を増大させることなくオン電流を低減することができる。

#### 【0215】

このような酸化物半導体トランジスタ 100 を画素部 131 に用いた表示パネルは、表示パネルの開口率が減少するのを抑制することができる。

40

#### 【0216】

また、ゲートドライバ 132a、ゲートドライバ 132b、ソースドライバ 134a、及びソースドライバ 134b にトランジスタとして、上述のように、図 2 (A) 及び図 2 (C) で説明された酸化物半導体トランジスタ 110 を用いることができる。

#### 【0217】

よって、同一基板 101 上に、画素部 131 にオン電流が低い酸化物半導体トランジスタ 100 を用い、かつゲートドライバ 132a、ゲートドライバ 132b、ソースドライバ 134a、及びソースドライバ 134b にオン電流が高い酸化物半導体トランジスタ 110 を用いることができる。

50

0を用いた表示パネルを得ることができる。これにより、表示パネルの作製において、作製工程が削減でき、作製コストを抑制することができる。

【0218】

ゲートドライバ132a、ゲートドライバ132b、ソースドライバ134a、及びソースドライバ134bに与えられる各種信号及び電位は、FPC167a及びFPC167bから供給されている。

【0219】

図7(B)に示す表示パネルでは、発光素子144として図6(A)に示す上方射出構造の発光素子を用いる。当該表示パネルにおいて、接続端子165が、電極107と同じ導電膜から形成され、配線166は、発光素子144が有する電極153と同じ導電膜から形成されている。

10

【0220】

ただし発光素子144として、図6(A)に示す上方射出構造の発光素子のみならず、図6(B)に示す下方射出構造の発光素子、図6(C)に示す両面射出構造の発光素子を用いてもよい。

【0221】

図7(B)に示す表示パネルに図6(B)に示す下方射出構造の発光素子を用いる場合には、接続端子165として電極108又は電極154と同じ導電膜、配線166として電極153と同じ導電膜を用いることができる。

【0222】

図7(B)に示す表示パネルに図6(C)に示す両面射出構造の発光素子を用いる場合には、接続端子165として電極108又は電極154と同じ導電膜、配線166として電極153と同じ導電膜を用いることができる。

20

【0223】

接続端子165は、FPC167aが有する端子と、異方性導電膜168を介して電気的に接続されている。

【0224】

発光素子144として、図6(A)に示す上方射出構造の発光素子、又は図6(C)に示す両面射出構造の発光素子を用いる場合には、発光素子144からの光の取り出し方向に位置する第2の基板161は透光性でなければならない。その場合には、ガラス板、プラスチック板、ポリエチルフィルムまたはアクリルフィルムのような透光性を有する材料を用いる。

30

【0225】

また、充填材169としては窒素やアルゴンなどの不活性な気体の他に、紫外線硬化樹脂または熱硬化樹脂を用いることができ、PVC(ポリビニルクロライド)、アクリル、ポリイミド、エポキシ樹脂、シリコーン樹脂、PVB(ポリビニルブチラル)またはEVA(エチレンビニルアセテート)を用いることができる。本実施の形態は充填材169として窒素を用いた。

【0226】

また、必要であれば、発光素子144の射出面に偏光板、又は円偏光板(楕円偏光板を含む)、位相差板(1/4板、1/2板)、カラーフィルタなどの光学フィルムを適宜設けてよい。また、偏光板又は円偏光板に反射防止膜を設けてよい。例えば、表面の凹凸により反射光を拡散し、映り込みを低減できるアンチグレア処理を施すことができる。

40

【0227】

以上述べたように、本実施の形態により、オン電流が低減され、かつ、占有面積の増大が抑制された酸化物半導体トランジスタを得ることができる。

【0228】

また本実施の形態により、オン電流が低減された酸化物半導体トランジスタを画素に用いた表示装置において、表示装置の開口率が減少するのを抑制することができる。

【0229】

10

20

30

40

50

また本実施の形態により、同一基板上に、オン電流が低い酸化物半導体トランジスタ及びオン電流が高い酸化物半導体トランジスタを作製することができる。

#### 【0230】

さらに、本実施の形態により、同一基板上に、画素にオン電流が低い酸化物半導体トランジスタを用い、かつ駆動回路にオン電流が高い酸化物半導体トランジスタを用いた表示装置を得ることができる。

#### 【実施例】

##### 【0231】

本実施例では、 $L_{\text{off}}$ 領域109のチャネル長方向の長さFを変えた場合において、酸化物半導体トランジスタの特性の変化について述べる。より具体的には、ゲート-ソース間電圧 $V_{gs}$ 及びドレイン電流 $I_d$ 特性（以後「 $V_{gs}$ - $I_d$ 特性」ともいう）の長さFとの依存性について述べる。

10

##### 【0232】

図8に、長さFを変えた酸化物半導体トランジスタの $V_{gs}$ - $I_d$ 特性を示す。本実施例における酸化物半導体トランジスタとして、実施の形態で述べた酸化物半導体トランジスタ100を用いた。また、長さFが0 μm、すなわち $L_{\text{off}}$ 領域が存在しない酸化物半導体トランジスタの構造は、実施の形態の酸化物半導体トランジスタ110と同様である。なお本実施例では、酸化物半導体トランジスタ100の酸化物半導体膜104、及び酸化物半導体トランジスタ110の酸化物半導体膜114の材料として、酸化インジウムと酸化ガリウムと酸化亜鉛からなる酸化物（IGZO：Indium Gallium Zinc Oxide）を用いた。

20

##### 【0233】

ただし、本実施例で測定した酸化物半導体トランジスタは、それぞれチャネル長L及びチャネル幅Wが異なる酸化物半導体トランジスタであった。ドレイン電流 $I_d$ は、チャネル長L及びチャネル幅Wに依存して変化してしまう。そのため、本実施例では、チャネル長L及びチャネル幅Wの比に基づいて、ドレイン電流 $I_d$ の規格化を行った。

##### 【0234】

まず $L_{\text{off}}$ 領域が存在しない酸化物半導体トランジスタをトランジスタ1、トランジスタ1のチャネル長Lをチャネル長 $L_1$ 、トランジスタ1のチャネル幅Wを $W_1$ とする。

30

##### 【0235】

$L_{\text{off}}$ 領域109のチャネル長方向の長さFが3 μmの酸化物半導体トランジスタを、トランジスタ2とする。トランジスタ2のチャネル長Lをチャネル長 $L_2$ 、トランジスタ2のチャネル幅Wを $W_2$ 、及びトランジスタ2の測定されたドレイン電流 $I_d$ を $I_{d2}$ とする。同様に、チャネル長方向の長さFが10 μmの酸化物半導体トランジスタをトランジスタ3とし、トランジスタ3のチャネル長L、チャネル幅W、測定されたドレイン電流 $I_d$ をそれぞれ、チャネル長 $L_3$ 、チャネル幅 $W_3$ 、ドレイン電流 $I_{d3}$ とする（表1参照）。

##### 【0236】

##### 【表1】

|         | チャネル長L |        | チャネル幅W |        | F  | ドレイン電流 $I_d$ |             |             |

|---------|--------|--------|--------|--------|----|--------------|-------------|-------------|

|         | 名前     | 長さ(μm) |        | 長さ(μm) |    | 長さ(μm)       | 測定された $I_d$ | 規格化後の $I_d$ |

| トランジスタ1 | $L_1$  | 20     | $W_1$  | 10     | 0  |              |             |             |

| トランジスタ2 | $L_2$  | 9      | $W_2$  | 11     | 3  | $I_{d2}$     | $I_{d2}'$   |             |

| トランジスタ3 | $L_3$  | 21     | $W_3$  | 11     | 15 | $I_{d3}$     | $I_{d3}'$   |             |

##### 【0237】

トランジスタ2のドレイン電流 $I_{d2}$ 及びトランジスタ3のドレイン電流 $I_{d3}$ を、トランジスタ1のチャネル長 $L_1$ とチャネル幅 $W_1$ の比 $L_1/W_1$ によって規格化した。

##### 【0238】

10

20

30

40

50

トランジスタ2において、測定されたドレイン電流 $I_d$ をドレイン電流 $I_{d_2}$ 、規格化後のドレイン電流をドレイン電流 $I_{d_2}'$ とする。測定されたドレイン電流 $I_{d_2}$ を $L_1/W_1$ によって規格化するには、 $I_{d_2}': I_{d_2} = W_2/L_2 : W_1/L_1$ が成り立つ。これにより、 $I_{d_2}' = I_{d_2} \times (W_2/L_2) \times (L_1/W_1)$ となる。またトランジスタ3においても同様の規格化を行った(表1参照)。

#### 【0239】

図8に、トランジスタ1、並びに、規格化後のトランジスタ2及びトランジスタ3の $V_{g_s} - I_d$ 特性を示す。図8において、トランジスタ1の $V_{g_s} - I_d$ 特性は点線、トランジスタ2の $V_{g_s} - I_d$ 特性は一点鎖線、トランジスタ3の $V_{g_s} - I_d$ 特性は実線で示されている。

10

#### 【0240】

図8に示されるように、 $L_{o_{ff}}$ 領域109のチャネル長方向の長さFが長くなるにつれて、規格化後のドレイン電流 $I_d'$ が低くなつた。

#### 【0241】

以上本実施例により、 $L_{o_{ff}}$ 領域109によるオン電流低減の効果が確認できた。

#### 【0242】

このように、開示される発明の一態様により、占有面積を増大することなくオン電流を低減できる酸化物半導体トランジスタを得ることができる。

#### 【0243】

また開示される発明の一態様により、開口率を減少させることなく、オン電流が低減された酸化物半導体トランジスタを画素に用いた表示装置を得ることができる。

20

#### 【0244】

さらに、開示される発明の一態様により、同一基板上に、オン電流が低い酸化物半導体トランジスタ及びオン電流が高い酸化物半導体トランジスタを作製することができる。

#### 【0245】

オン電流が低い酸化物半導体トランジスタとオン電流が高い酸化物半導体トランジスタを同一基板上に作製すると、酸化物半導体トランジスタの作製工程が削減でき、作製コストを抑制することができる。

#### 【0246】

また、開示される発明の一態様により、同一基板上に、画素にオン電流が低い酸化物半導体トランジスタを用い、かつ駆動回路にオン電流が高い酸化物半導体トランジスタを用いた表示装置を得ることができます。

30

#### 【0247】

同一基板上に、画素にオン電流が低い酸化物半導体トランジスタを作製し、かつ駆動回路にオン電流が高い酸化物半導体トランジスタを作製すると、表示装置の作製工程が削減でき、作製コストを抑制することができる。

#### 【符号の説明】

#### 【0248】

|       |                 |

|-------|-----------------|

| 100   | 酸化物半導体トランジスタ    |

| 101   | 基板              |

| 102 a | ゲート電極           |

| 102 b | ゲート電極           |

| 104   | 酸化物半導体膜         |

| 105 a | 電極              |

| 105 b | 電極              |

| 107   | 電極              |

| 108   | 電極              |

| 109   | $L_{o_{ff}}$ 領域 |

| 110   | 酸化物半導体トランジスタ    |

| 112   | ゲート電極           |

10

20

30

40

50

|         |         |    |

|---------|---------|----|

| 1 1 4   | 酸化物半導体膜 |    |

| 1 1 5 a | 電極      |    |

| 1 1 5 b | 電極      |    |

| 1 2 3   | ゲート絶縁膜  |    |

| 1 2 4   | 酸化物半導体膜 |    |

| 1 2 5   | 導電膜     |    |

| 1 2 6   | 絶縁膜     |    |

| 1 2 7   | 絶縁膜     |    |

| 1 2 8   | 隔壁      |    |

| 1 3 1   | 画素部     | 10 |

| 1 3 2   | ゲートドライバ |    |

| 1 3 2 a | ゲートドライバ |    |

| 1 3 2 b | ゲートドライバ |    |

| 1 3 3   | ゲート線    |    |

| 1 3 4   | ソースドライバ |    |

| 1 3 4 a | ソースドライバ |    |

| 1 3 4 b | ソースドライバ |    |

| 1 3 5   | ソース線    |    |

| 1 3 6   | 画素      |    |

| 1 3 7   | 電源線     | 20 |

| 1 4 1   | トランジスタ  |    |

| 1 4 2   | トランジスタ  |    |

| 1 4 3   | 容量素子    |    |

| 1 4 4   | 発光素子    |    |

| 1 5 2   | 発光層     |    |

| 1 5 3   | 電極      |    |

| 1 5 4   | 電極      |    |

| 1 5 5   | 遮蔽膜     |    |

| 1 6 1   | 基板      |    |

| 1 6 2   | シール材    | 30 |

| 1 6 5   | 接続端子    |    |

| 1 6 6   | 配線      |    |

| 1 6 7 a | F P C   |    |

| 1 6 7 b | F P C   |    |

| 1 6 8   | 異方性導電膜  |    |

| 1 6 9   | 充填材     |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【 四 6 】

【図7】

【 义 8 】

【図9】

【図10】

【図11】

【図 1 2】

【図13】

---

フロントページの続き

(56)参考文献 特開2009-021612(JP,A)

特開2005-227618(JP,A)

特開2010-080952(JP,A)

特開平07-030116(JP,A)

特開平02-135780(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 29/786

H01L 51/50