(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6061937号

(P6061937)

(45) 発行日 平成29年1月18日(2017.1.18)

(24) 登録日 平成28年12月22日(2016.12.22)

(51) Int.Cl.

H01L 25/065 (2006.01)

F 1

H01L 25/08

E

H01L 25/07 (2006.01)

H01L 25/18 (2006.01)

請求項の数 30 (全 16 頁)

(21) 出願番号 特願2014-537171 (P2014-537171)

(86) (22) 出願日 平成24年10月17日 (2012.10.17)

(65) 公表番号 特表2014-531134 (P2014-531134A)

(43) 公表日 平成26年11月20日 (2014.11.20)

(86) 國際出願番号 PCT/US2012/060585

(87) 國際公開番号 WO2013/059297

(87) 國際公開日 平成25年4月25日 (2013.4.25)

審査請求日 平成27年10月16日 (2015.10.16)

(31) 優先権主張番号 13/277,330

(32) 優先日 平成23年10月20日 (2011.10.20)

(33) 優先権主張国 米国(US)

(73) 特許権者 309034272

インヴェンサンス・コーポレイション

アメリカ合衆国 カリフォルニア州 95

134、サン・ホセ、オーチャード・パー

クウェイ 3025

(74) 代理人 100099623

弁理士 奥山 尚一

(74) 代理人 100096769

弁理士 有原 幸一

(74) 代理人 100107319

弁理士 松島 鉄男

(74) 代理人 100114591

弁理士 河村 英文

(74) 代理人 100125380

弁理士 中村 純子

最終頁に続く

(54) 【発明の名称】積層された超小型電子装置を有する超小型電子パッケージ及びその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

複数の第1のチップコンタクトを有する半導体チップと、前記半導体チップの端に接する封止層と、前記封止層の表面に露出し前記第1のチップコンタクトと電気的に接続された複数の第1の装置コンタクトとを含む第1の超小型電子装置と、

複数の第2のチップコンタクトを表面に有する半導体チップと、前記半導体チップの端に接し前記端から延びる表面を有する封止層とを含む第2の超小型電子装置であって、該第2の超小型電子装置の前記半導体チップの前記表面と前記封止層の前記表面は該第2の超小型電子装置の外面を形成する第2の超小型電子装置と、

前記第1の装置コンタクトと電気的に接続された複数の結合線と、

前記第2の超小型電子装置の前記外面に位置する複数のパッケージ端子であって、(i)前記第1の装置コンタクトに前記結合線を介して電気的に接続されたパッケージ端子と(ii)前記第2のチップコンタクトに接して形成された金属被覆されたビアと配線とを介して前記第2のチップコンタクトに電気的に接続されたパッケージ端子とを備えてなり、

前記第1の超小型電子装置は、前記第1の超小型電子装置の外面に露出した複数の第1のチップコンタクトを有する第1の半導体チップと、前記第1の超小型電子装置の前記封止層を貫通する導電性ビアを介して第1のチップコンタクトが前記第1の装置コンタクトに接続された第2の半導体チップとを含むことを特徴とする超小型電子パッケージ。

## 【請求項 2】

10

20

前記第1の超小型電子装置はメモリ記憶アレイ機能を主に提供するよう構成されていることを特徴とする請求項1に記載の超小型電子パッケージ。

【請求項3】

前記第2の超小型電子装置は論理機能を主に提供するよう構成されていることを特徴とする請求項2に記載の超小型電子パッケージ。

【請求項4】

前記第2の半導体チップの前記第1のチップコンタクトのうち少なくとも1つは、前記第1の超小型電子装置の前記封止層の貫通孔において露出していることを特徴とする請求項1に記載の超小型電子パッケージ。

【請求項5】

前記第1及び第2の半導体チップはメモリ記憶アレイ機能を主に提供するよう構成されていることを特徴とする請求項1に記載の超小型電子パッケージ。

【請求項6】

前記第2の半導体チップが前記第1の半導体チップを部分的に覆うことで、前記第2の半導体チップの前記第1のチップコンタクトが前記第1の半導体チップの端を超えて配置されることを特徴とする請求項5に記載の超小型電子パッケージ。

【請求項7】

前記第1及び第2の半導体チップの前記第1のチップコンタクトは、それぞれ前記第1及び第2の半導体チップの端に隣接して配置されていることを特徴とする請求項5に記載の超小型電子パッケージ。

【請求項8】

前記パッケージ端子に結合された導電性の結合部を更に備えることを特徴とする請求項1に記載の超小型電子パッケージ。

【請求項9】

前記複数の結合線の少なくとも幾つかは、前記第2の超小型電子装置の端を回って延びていることを特徴とする請求項1に記載の超小型電子パッケージ。

【請求項10】

複数の第1のチップコンタクトを有する半導体チップと、前記半導体チップの端に接する封止層と、前記封止層の表面に露出し前記第1のチップコンタクトと電気的に接続された複数の第1の装置コンタクトとを含む第1の超小型電子装置と、

複数の第2のチップコンタクトを表面に有する半導体チップと、前記半導体チップの端に接し前記端から延びる表面を有する封止層とを含む第2の超小型電子装置であって、該第2の超小型電子装置の前記半導体チップの前記表面と前記封止層の前記表面は該第2の超小型電子装置の外面を形成する第2の超小型電子装置と、

前記第1の装置コンタクトと電気的に接続された複数の結合線と、

前記第2の超小型電子装置の前記外面に位置する複数のパッケージ端子であって、(i)前記第1の装置コンタクトに前記結合線を介して電気的に接続されたパッケージ端子と、(ii)前記第2のチップコンタクトに接して形成された金属被覆されたビアと配線とを介して前記第2のチップコンタクトに電気的に接続されたパッケージ端子とを備えてなり、

前記複数の結合線の少なくとも幾つかは、前記第2の超小型電子装置の前記封止層の貫通孔を通って延びていることを特徴とする超小型電子パッケージ。

【請求項11】

前記複数のパッケージ端子の少なくとも幾つかは、前記貫通孔と前記第2の超小型電子装置の端との間に配置されていることを特徴とする請求項10に記載の超小型電子パッケージ。

【請求項12】

前記複数のパッケージ端子の前記少なくとも幾つかは、電源及び接地端子のうち少なくとも1つを含むことを特徴とする請求項11に記載の超小型電子パッケージ。

【請求項13】

10

20

30

40

50

前記複数のパッケージ端子の少なくとも幾つかは、前記貫通孔と前記第2の超小型電子装置の前記半導体チップの端との間に配置されていることを特徴とする請求項10に記載の超小型電子パッケージ。

【請求項14】

前記第1の超小型電子装置の前記封止層は、前記半導体チップの、前記第1のチップコンタクトが配置された表面と反対側の表面を覆っていることを特徴とする請求項1に記載の超小型電子パッケージ。

【請求項15】

前記第2の超小型電子装置の前記封止層は、前記半導体チップの、前記第2のチップコンタクトが配置された表面と反対側の表面を覆っていることを特徴とする請求項1に記載の超小型電子パッケージ。 10

【請求項16】

前記第1及び第2の超小型電子装置のうち少なくとも1つは、前記第1及び第2の超小型電子装置を備える該超小型電子パッケージの形成の前に機能テストが可能であることを特徴とする請求項1に記載の超小型電子パッケージ。

【請求項17】

前記第1及び第2の超小型電子装置のそれぞれは、前記第1及び第2の超小型電子装置を備える該超小型電子パッケージの形成の前に機能テストが可能であることを特徴とする請求項1に記載の超小型電子パッケージ。

【請求項18】

第1の超小型電子装置を第2の超小型電子装置の上に積層するステップであって、前記第1の超小型電子装置は、複数の第1のチップコンタクトを有する半導体チップと、前記半導体チップの端に接する封止層と、前記封止層の表面に露出し前記第1のチップコンタクトと電気的に接続された複数の第1の装置コンタクトとを含み、

前記第2の超小型電子装置は、複数の第2のチップコンタクトを表面に有する半導体チップと、前記第2の超小型電子装置の前記半導体チップの端に接し、前記端から延びる表面を有する封止層とを含み、前記第2の超小型電子装置の前記半導体チップの前記表面と前記封止層の前記表面は前記第2の超小型電子装置の外面を形成している、ステップと、

次いで前記第1の装置コンタクトを前記第2の超小型電子装置の前記外面に位置する複数のパッケージ端子に電気的に接続する複数の結合線を形成するステップであって、前記パッケージ端子は前記第2のチップコンタクトに接して形成された金属被覆されたビアと配線とを介して前記第2のチップコンタクトに電気的に接続されている、ステップとを含んでなり。

前記第1の超小型電子装置は、前記第1の超小型電子装置の外面に露出した複数の第1のチップコンタクトを有する第1の半導体チップと、前記第1の超小型電子装置の前記封止層を貫通する導電性ビアを介して第1のチップコンタクトが前記第1の装置コンタクトに接続された第2の半導体チップとを含むことを特徴とする超小型電子パッケージの製造方法。

【請求項19】

前記ビアと配線は堆積されることを特徴とする請求項18に記載の方法。 40

【請求項20】

前記第1の超小型電子装置はメモリ記憶アレイ機能を主に提供するよう構成されていることを特徴とする請求項18に記載の方法。

【請求項21】

前記第2の超小型電子装置は論理機能を主に提供するよう構成されていることを特徴とする請求項18に記載の方法。

【請求項22】

前記第1及び第2の半導体チップはメモリ記憶アレイ機能を主に提供するよう構成されていることを特徴とする請求項18に記載の方法。

【請求項23】

10

20

30

40

50

前記第2の半導体チップが前記第1の半導体チップを部分的に覆うことで、前記第2の半導体チップの前記第1のチップコンタクトが前記第1の半導体チップの端を越えて配置されることを特徴とする請求項18に記載の方法。

【請求項24】

前記複数の結合線を形成するステップは、前記複数の結合線の少なくとも幾つかが前記第2の超小型電子装置の端を回って延びるよう形成することを特徴とする請求項18に記載の方法。

【請求項25】

第1の超小型電子装置を第2の超小型電子装置の上に積層するステップであって、

前記第1の超小型電子装置は、複数の第1のチップコンタクトを有する半導体チップと

、前記半導体チップの端に接する封止層と、前記封止層の表面に露出し前記第1のチップ

コンタクトと電気的に接続された複数の第1の装置コンタクトとを含み、

前記第2の超小型電子装置は、複数の第2のチップコンタクトを表面に有する半導体チップと、前記第2の超小型電子装置の前記半導体チップの端に接し、前記端から延びる表面を有する封止層とを含み、前記第2の超小型電子装置の前記半導体チップの前記表面と前記封止層の前記表面は前記第2の超小型電子装置の外面を形成している、ステップと、

次いで前記第1の装置コンタクトを前記第2の超小型電子装置の前記外面に位置する複数のパッケージ端子に電気的に接続する複数の結合線を形成するステップであって、前記パッケージ端子は前記第2のチップコンタクトに接して形成された金属被覆されたビアと配線とを介して前記第2のチップコンタクトに電気的に接続されている、ステップと

を含んでなり、

前記複数の結合線を形成するステップは、前記複数の結合線の少なくとも幾つかが前記第2の超小型電子装置の前記封止層の貫通孔を通って延びるよう形成することを特徴とする方法。

【請求項26】

前記第2の超小型電子装置の前記封止層の前記貫通孔は、前記第2の超小型電子装置の前記半導体チップの周りに前記封止層を成形する間に形成されることを特徴とする請求項25に記載の方法。

【請求項27】

前記貫通孔と同じ構成を有する要素が、前記成形時、前記貫通孔を形成することを特徴とする請求項26に記載の方法。

【請求項28】

前記第1及び第2の超小型電子装置のうち少なくとも1つを前記積層するステップの前に機能テストすることを更に含んでいることを特徴とする請求項18に記載の方法。

【請求項29】

前記第1及び第2の超小型電子装置のそれぞれを前記積層するステップの前に機能テストすることを更に含んでいることを特徴とする請求項18に記載の方法。

【請求項30】

前記第1及び第2の超小型電子装置のうち少なくとも1つは、再構成されたウェハ又は回路パネルであることを特徴とする請求項18に記載の方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、積層された超小型電子装置を含む超小型電子パッケージ及びそのパッケージの製造方法に関する。

【0002】

【関連出願の相互参照】

本出願は、2011年10月20日に出願された米国特許出願第13/277,330号の継続出願である。この出願の開示内容を引用することにより本明細書の一部をなすものとする。

10

20

30

40

50

## 【背景技術】

## 【0003】

半導体チップは表の面上に配置されチップ自体の内部電気回路に接続されたコンタクトを有する平板体である。半導体チップは通常、パッケージに入れられてパッケージのコンタクトに電気的に接続された複数の端子を有する超小型電子パッケージを構成する。次に、パッケージの端子は外部の超小型電子部品、例えば回路パネルに接続されてもよい。

## 【0004】

複数の超小型電子パッケージを、「積層」配置してパッケージに入れることがしばしば望ましい。この積層配置では超小型電子パッケージはそれぞれ1つ以上の半導体チップを含み、積み重ねられてスペースを節約する。積層チップパッケージ構造体又はパッケージ・オン・パッケージ（P o P）においては、複数のパッケージのそれぞれのチップは積み重ねられてその表面積は全チップの総表面積より小さい。このP o Pのチップの低減された面積によって、P o Pのチップが取り付けられる印刷回路基板（PCB）上の領域を非常に効率的に利用することが出来る。

10

## 【0005】

通常、P o Pに含まれる複数の超小型電子パッケージは、積層状態で結合されP o Pを構成する前に、個々のパッケージのチップのチップコンタクトにおけるテストを可能にするのに十分大きなサイズを有する。また、幾つかのP o Pでは、導電性構造体が複数のパッケージのそれぞれのチップのチップコンタクト同士を電気的に相互接続する。このような導電性構造体はパッケージ間に高い寄生成分を発生させる長さを有し、望ましくない。

20

## 【0006】

従って、超小型電子パッケージの外部の超小型電子部品に接続可能な半導体チップ等の超小型電子素子をそれぞれ備え積層された超小型電子装置を含む超小型電子パッケージを製造する技術の更なる改善が望ましい。

## 【発明の概要】

## 【0007】

本開示の1つの実施形態によれば、超小型電子パッケージは、複数の第1のチップコンタクトを有する半導体チップと、前記半導体チップの端に接する封止層と、前記封止層の表面に露出し前記第1のチップコンタクトと電気的に接続された複数の第1の装置コンタクトとを含む第1の超小型電子装置を備えてよい。本パッケージは、複数の第2のチップコンタクトを表面に有する半導体チップと、前記半導体チップの端に接し前記端から延びる表面を有する封止層とを含む第2の超小型電子装置であって、該第2の超小型電子装置の前記半導体チップの前記表面と前記封止層の前記表面は該第2の超小型電子装置の外面を形成する第2の超小型電子装置を備えてよい。本パッケージは前記第1の装置コンタクトと電気的に接続された複数の結合線も備えてよい。本パッケージは、前記第2の超小型電子装置の前記外面に位置する複数のパッケージ端子であって、(i)前記第1の装置コンタクトに前記結合線を介して電気的に接続されたパッケージ端子と(ii)前記第2のチップコンタクトに接して形成された金属被覆されたビアと配線とを介して前記第2のチップコンタクトに電気的に接続されたパッケージ端子とを更に備えてよい。

30

## 【0008】

本開示の別の実施形態では、超小型電子パッケージの製造方法は、第1の超小型電子装置を第2の超小型電子装置の上に積層することを備えてよい。前記第1の超小型電子装置は、複数の第1のチップコンタクトを有する半導体チップと、前記半導体チップの端に接する封止層と、前記封止層の表面に露出し前記第1のチップコンタクトと電気的に接続された複数の第1の装置コンタクトとを含んでよい。前記第2の超小型電子装置は、複数の第2のチップコンタクトを表面に有する半導体チップと、前記第2の超小型電子装置の前記半導体チップの端に接し前記端から延びる表面を有する封止層とを含み、前記第2の超小型電子装置の前記半導体チップの前記表面と前記封止層の前記表面は前記第2の超小型電子装置の外面を形成する。本方法は、前記第1の装置コンタクトを前記第2の超小型電子装置の外面に位置する複数のパッケージ端子に電気的に接続する複数の結合線を形成す

40

50

ることを更に備えてよい。前記パッケージ端子は前記第2のチップコンタクトに接して形成された金属被覆されたビアと配線とを介して前記第2のチップコンタクトに電気的に接続されている。

【図面の簡単な説明】

【0009】

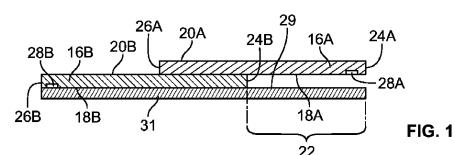

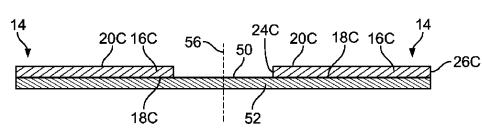

【図1】本開示の1つの実施形態に係る垂直方向に積層された超小型電子素子を含む超小型電子装置の製造方法の1段階を例示する概略断面図である。

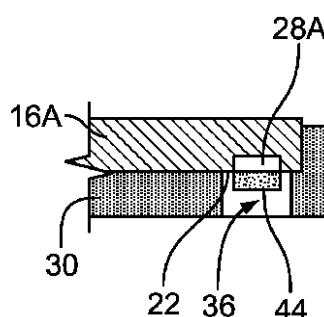

【図2】本開示の1つの実施形態に係る垂直方向に積層された超小型電子素子を含む超小型電子装置の製造方法の1段階を例示する概略断面図である。

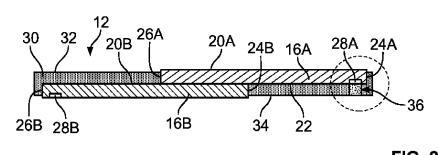

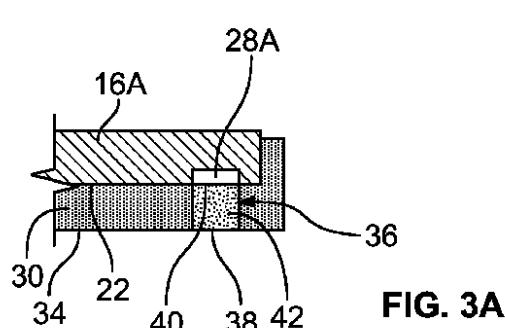

【図3】図3Aは、本開示の1つの実施形態に係る垂直方向に積層された超小型電子素子を含む超小型電子装置の一部の概略断面図である。図3Bは、本開示の別の実施形態に係る垂直方向に積層された超小型電子素子を含む超小型電子装置の一部の概略断面図である。

10

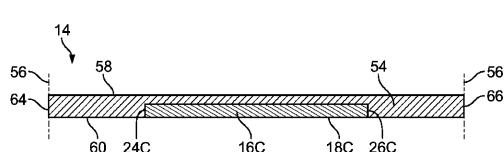

【図4】本開示の1つの実施形態に係るパッケージ端子を有する超小型電子装置の製造方法の1段階を例示する概略断面図である。

【図5】本開示の1つの実施形態に係るパッケージ端子を有する超小型電子装置の製造方法の1段階を例示する概略断面図である。

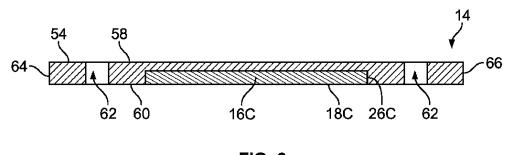

【図6】本開示の1つの実施形態に係るパッケージ端子を有する超小型電子装置の製造方法の1段階を例示する概略断面図である。

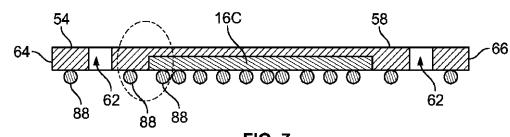

【図7】本開示の1つの実施形態に係るパッケージ端子を有する超小型電子装置の製造方法の1段階を例示する概略断面図である。

20

【図8】本開示の1つの実施形態に係るパッケージ端子を有する超小型電子装置の製造方法の1段階を例示する概略断面図である。

【図9】本開示の1つの実施形態に係る図1～図3及び図4～図8の方法を使用して形成された超小型電子装置が積層された超小型電子パッケージの製造方法の1段階を例示する概略断面図である。

【図10】本開示の1つの実施形態に係る図1～図3及び図4～図8の方法を使用して形成された超小型電子装置が積層された超小型電子パッケージの製造方法の1段階を例示する概略断面図である。

30

【図11】本開示の1つの実施形態に係る図1～図3及び図4～図8の方法を使用して形成された超小型電子装置が積層された超小型電子パッケージの製造方法の1段階を例示する概略断面図である。

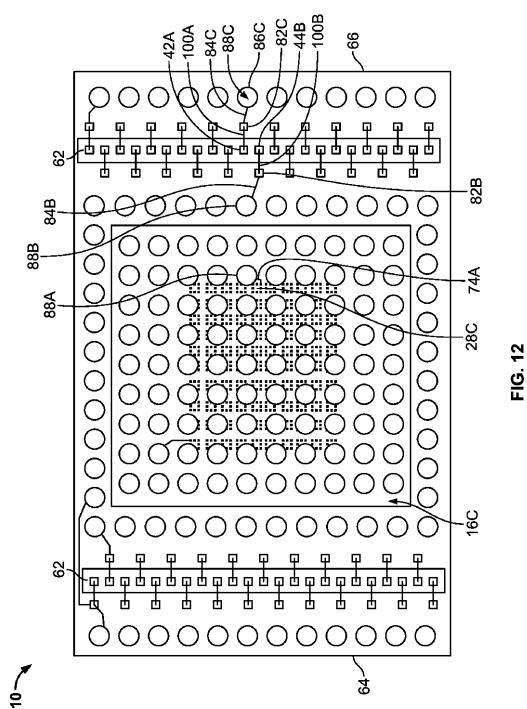

【図12】図11のパッケージの底面図である。

【図13】本開示の別の実施形態に係る超小型電子パッケージの概略断面図である。

【図14】本開示の別の実施形態に係る超小型電子パッケージの概略断面図である。

【図15】本開示の1つの実施形態に係るシステムの概略図である。

【発明を実施するための形態】

【0010】

超小型電子素子をそれぞれ備え積層された超小型電子装置12及び14を含む超小型電子パッケージ10は、図1～図11に示す本開示の実施形態に従って製造されてもよい。前記各超小型電子素子は半導体チップ又はウェハなどであってよい。チップは複数の能動素子（例えば、トランジスタ、ダイオードなど）、複数の受動素子（例えば、抵抗、コンデンサ、インダクタなど）、又は能動素子と受動素子の両方を含む。通常、少なくとも1つのチップが能動素子、又は能動素子と受動素子の両方を含む。各チップは超小型電子装置内の他のチップと同じ種類であってもよいし、異なる種類であってもよい。

40

【0011】

特定の実施形態では、パッケージ10内の超小型電子装置のうち1つ以上、例えば超小型電子装置14は、論理チップとして主要な機能を有するよう構成されたチップ、例えばプログラマブル汎用又は専用プロセッサ、マイクロコントローラ、書替え可能ゲートアレイ（FPGA）デバイス、特定用途集積回路（ASIC）、ディジタル信号プロセッサな

50

どを含んでよい。このような実施形態では、パッケージ 10 内の超小型電子装置のうち 1 つ以上、例えば超小型電子装置 12 は、論理チップ以外の主要な機能を有するチップを含んでよい。例えば、1 つ以上の論理チップを有する装置 14 は、主要なメモリ機能を有する 1 つ以上の記憶アレイチップをそれぞれ含む 1 つ以上の装置 12 と結合されてもよい。このようなメモリ記憶アレイチップは、揮発性メモリ記憶領域、例えば動的ランダムアクセスメモリ (DRAM)、静的ランダムアクセスメモリ (SRAM)、又は不揮発性メモリ記憶アレイ、例えばフラッシュメモリ又は磁気ランダムアクセスメモリ (MRAM)、又は揮発性記憶アレイと不揮発性記憶アレイとの組み合わせを含んでもよい。特定の実施形態では、パッケージ 10 の超小型電子装置のうち 1 つ以上は、論理機能と他の重要な機能、例えば重要なメモリ機能と同じチップ上で結合したチップを含んでもよい。

10

#### 【0012】

図 1、図 2 を参照すると、超小型電子装置 12 は垂直方向に積層されたチップ 16 A 及び 16 B を含んでもよい。各チップ 16 は表の面 18 と表の面 18 と反対側の裏面 20 とを有してよい。超小型電子装置 12 は 1 つのチップの表の面が他のチップの裏面と対面するよう構成されていてもよいし、超小型電子装置 12 は垂直方向に積層された 2 つを超える数のチップ 16 を含んでもよい。これらのチップ 16 は対面する面において接着剤の層 (不図示) により接合され、積層されたチップの底のチップ、例えば積層されたチップ 16 A と 16 B のうちのチップ 16 B も、台板 31 の表面 29 に接着剤の層 (不図示) により接合されてよい。台板 31 は誘電材料又はガラスでできてもよい。接着層はダイ取付け接着剤を含んでもよく、コンプライアンス、熱伝導性、水分又は他の汚染物質に対する不透過性などの特性、又はこれら特性の組み合わせを有するものを選択してもよい。接着層は、チップ 16 の表の面又は裏面を覆うよう塗布された、例えば流動性の接着剤又は粘着性の (部分的に硬化した) 接着剤であってよい。塗布後、例えばピックアンドプレースツールを使用して他のチップが該接着層に接合される。或いは、接着層は液体として剥離可能な裏材上に堆積されるか、部分的に硬化した接着層として剥離可能な裏材に接合されてもよい。その後、チップ 16 が該接着層に接合される。剥離可能な裏材を除去した後、該接着層は他のチップ又は台板 31 と整列され接合されうる。

20

#### 【0013】

本開示で使用されているように、「上方へ」、「下方へ」、「垂直に」、及び「水平に」等の用語は指定された構成要素の基準系を指すと理解されるべきであり、通常の重力基準系に合致する必要はない。また、参照の容易さのために、本開示において、方向は超小型電子パッケージ 10 内で超小型電子装置 14 上に積層された超小型電子装置 12 の表の面 (例えば図 1 に示すチップ 16 B の表面 18 B) を基準として指定される。通常、「上向きの」又は「から上方への」と称される方向は超小型電子装置 12 の表の面に直交し離れる方向を指す。「下向きの」と称される方向は超小型電子装置 12 の表の面に直交し上向き方向と反対の方向を指す。「垂直な」方向は超小型電子装置 12 の表の面に直交する方向を指す。基準点の「上方」という用語はその基準点の上方の点を指し、基準点の「下方」という用語はその基準点の下方の点を指す。任意の個々の構成要素の「最上部」はその構成要素の上向き方向に最も遠い点又は点群を指し、任意の構成要素の「底部」という用語はその構成要素の下向き方向に最も遠い点又は点群を指す。

30

#### 【0014】

超小型電子装置 12 において、チップ 16 B は、チップ 16 B の端 24 B からチップ 16 A の端 24 A まで延びる表面部 22 を除くチップ 16 A の表の面 18 A を覆う。両方のチップ 16 の端 24 の反対側の端 26 同士は垂直に整列されている場合も、そうでない場合もある。1 つの実施形態では、チップ 16 A 及び 16 B は、チップ 16 A の表の面 18 A の両部分 22 がそれぞれチップ 16 B の端 24 B と 26 B を超えて延びるよう構成され積層されていてもよい。

40

#### 【0015】

チップ 16 内の回路又は他の導電性要素 (不図示) に電気的に接続された複数の素子 / チップコンタクト 28 が、積層されたチップのうちチップ 16 A の表の面 18 A の部分 2

50

2及びチップ16Bの表の面18Bにおいて露出していてよい。

【0016】

本開示で使用されているように、電気的に伝導性の部分は、表面、例えば半導体チップの上面を形成する誘電体層の表面において、該金属製部分が該表面に塗布されたコンタクト又はボンディング材料に接触可能な場合、「露出している」と考えることが出来る。従って、誘電体の表面から突出するか又は誘電体の表面と同じ高さの金属製部分は、該表面に露出している。一方、誘電体内の誘電体の表面まで延在する穴の中に配置又は整列された引っ込んだ導電性部分も該表面に露出している。

【0017】

例えば半導体チップ上のコンタクト28は、アルミニウム又は銅を含み、サブミクロン寸法の露出した表の面を有する。コンタクト28の表の面は、コンタクト28を後の処理の間、例えば後述するようにチップの表の面を覆う誘電材料にレーザ光をあてる際に発生しうる損傷から保護する金属又は他の導電材料で覆われ、一方、該コンタクトはパッケージの他の電気的に伝導性の材料又は要素に該コンタクトを覆う該導電材料を介して電気的に接続される。2011年8月1日に出願された米国特許出願第13/195,187号を参照されたい。この出願を引用することにより本明細書の一部となすものとする。

10

【0018】

図2を参照すると、超小型電子装置12の製造の一段階において、封止剤の層30が、表面18Aのチップ16Bの端26Aから延びる非被覆部分22と、チップ16A及び16Bの端24及び26と、チップ16Bの裏面20Bの非被覆部分とを覆って形成されてよい。外部環境から被封止要素を保護する封止層は誘電材料又は樹脂を含んでもよい。1つの実施形態では、封止層は成形プロセスにより形成されてよい。この成形プロセスはチップ16Aの裏面20Aから同一平面上を延びる封止層30の平らな上面32を形成する。また、該封止層はチップ16Bの表の面18Bから同一平面上を延びる平らな裏面34を形成してもよい。台板31は、封止層の形成の次に、例えば研磨、エッチング、又は類似の手法で除去されてもよい。これにより封止層で覆われ露出した面を有する積層されたチップ16を備えた超小型電子装置12が得られる。

20

【0019】

封止層30がチップ16Aのコンタクト28Aを覆って形成された1つの実施形態では、製造の次の段階は、裏面34から封止層30を貫通してチップ16Aの表の面の部分22に向かう穴36の形成を含む。チップ12Aの表の面18Aの部分22においてコンタクト28Aを覆う導電材料は穴36内で露出している。

30

【0020】

穴36はチップから離れる垂直又は概ね垂直な軸に沿って延在する。図3Aを参照すると、穴36は裏面34において略円形の上端38とチップ16Aのコンタクト28Aに隣接した略円形の下端40とを有する略円錐形又は円筒形をしていてもよい。別の実施形態では、穴36は約25ミクロンの平均直径又は幅を有してもよい。この穴の上端の直径又は幅と下端の直径又は幅との差は約5~10ミクロンであってよい。幾つかの例では、穴の下端の幅は上端の幅より小さくてもよい。別の例では、穴の下端の幅は上端の幅と同じであってよい。

40

【0021】

別の実施形態では、穴36は超小型電子装置12のチップの表の面に概ね平行に延びるスロットの形態であってもよい。

【0022】

1つの実施形態では、穴36は、例えばレーザ、打ち抜き、又はエッチングを使用する除去により封止層に形成されてもよい。

【0023】

別の実施形態では、封止層30はチップ16A、16Bの端の形状と、チップ16Aの表の面の非被覆部及びチップ16Bの裏面の非被覆部とを有するよう予め形成され、チップ16Aの露出した素子コンタクト28Aに適合するよう予形成された穴を備えてもよい

50

。封止層 30 は軟化した状態で、積層されたチップを取り付け、又は押し付けられて、該穴は垂直方向にコンタクト 28A と整列される。1つの実施形態では、このような場合の封止層は、積層されたチップに取り付ける時、部分的に硬化した、例えば「Bステージ」材料であってもよい。

【0024】

製造の次の段階では、図 3A を参照すると、超小型電子装置コンタクトは、裏面 34 から穴 36 を通ってコンタクト 28A へ延びる金属被覆されたビア 42 として形成されてもよい。例えば、ビア 42 は裏面 34 からコンタクト 28A を覆う隆起又は柱（不図示）まで延びてもよい。ビア 42 はエッキング可能な導電材料、望ましくは銅、銅系合金、アルミニウム、ニッケル、金等の金属を含んでよい。

10

【0025】

1つの実施形態では、ビア 42 は堆積、例えば電解金属めっき又は無電解金属めっき、導電材料又は導電性基質材料の蒸着、又はステンシルを使用して導電性ペーストを選択的に穴内に印刷して導電性ビアを形成することで、形成されてよい。別の実施形態では、導電性シード層（不図示）を、導電性ビア 42 を形成する前に穴 36 内に形成してもよい。

【0026】

別の実施形態では、封止層 30 はチップ 16A 及び 16B の表の面と裏面との非被覆部とチップ 16 の端とを覆うよう成形プロセスにより成形されてよい。この成形プロセスでは、金型の構造要素又は別の要素、例えばピンが垂直方向にコンタクト 28A と整列され穴 36 を形成する。図 3B を参照すると、封止層の形成の後に、導電材料が穴 36 内に堆積され導電性パッド 44 を表面部 22 に形成してもよい。パッド 44 はチップコンタクト 28A に電気的に接続された超小型電子装置 12 の装置コンタクトとして働きうる。

20

【0027】

上記の様々な製造工程を、例えば台板上に配列された複数のチップ積層体に対して実行し、複数の超小型電子装置 12 を形成するのが望ましい。複数の装置 12 の個々は、該台板の除去前又は後に装置 12 間の封止層をダイシングラインに沿って切断することで得られる。超小型電子装置 12 は、完成時に該 1 つ以上のチップを支持するためのパッケージ基板を必要とせずに構築されるのが望ましい。

【0028】

図 4 ~ 図 8 を参照すると、超小型電子装置 14 を形成するために、複数の半導体チップ 16C はそれらの表の面 18C において接着剤の層（不図示）により台板 52 の表面 50 に接合されてよい。台板 52 と接着剤とは超小型電子装置 12 の形成について上述したのと類似の材料から形成されてよい。

30

【0029】

図 5 を参照すると、封止剤の層 54 が、複数のチップ 16C の裏面 20C と端 24C 及び 26C とを覆って形成されてよい。封止層 54 は超小型電子装置 12 について上述したのと同様にして類似の材料で成形により形成され、その後、台板 52 は除去されてもよい。個々の超小型電子装置 14 はそれぞれチップ 16C を備え、両端 64 及び 66 を有し、封止層をダイシングライン 56 に沿って、例えばソーイング又はスクライビングで切断することで得られる。別の実施形態では、個々のパッケージを得るために、台板 52 を除去する前に切断されてよい。

40

【0030】

1つの実施形態では、封止層 54 は成形プロセスにより形成され、端 64 と端 66 との間を延びる平らな上面 58 と、チップ 16C の表の面 18C と同一の面でチップ 16C の端 26C と端 66 との間及びチップ 16C の端 24C と端 64 との間を延びる平らな裏面 60 とが形成される。

【0031】

図 6 を参照すると、穴 62 が封止層 54 を貫通して形成され、全厚みを通って裏面 60 から上面 58 まで延びている。穴 62 は表面 58 及び 60 に沿って所定の位置にあり、導電性要素がその中を通り、超小型電子装置 14 のコンタクトを別の超小型電子装置、例え

50

ば下記に詳述するように超小型電子装置 14 上に積層されてパッケージ 10 を構成する超小型電子装置 12 の装置コンタクトに電気的に接続することができる。穴 62 は直径約 400 ミクロン～1 mm の円筒形スロットの形態であってよい。1 つの実施形態では、複数の穴 62 は、端 26C と端 66 との間の穴と端 24C と端 64 との間の穴とを含む。別の実施形態では、穴 62 は概ね水平に超小型電子装置 14 内を延びるスロットとして構成されてもよい。穴 62 は穴 36 の形成について上述したのと同様なプロセスを使用して形成されてよい。

【 0032 】

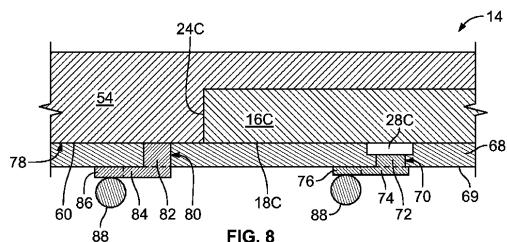

図 7 と、表の面 18C において露出したチップ 16C のコンタクト 28C を含む装置 14 の部分の拡大図を例示する図 8 とを参照すると、誘電材料の層 68 がチップ 16C の表の面 18C と、表の面 18C から穴 62 まで延びる封止層 54 の裏面 60 と、2 つの穴 62 から端 64、66 まで延びる裏面 60 とを覆って形成されてもよい。次に、誘電層 68 を貫通してコンタクト 28C に向かって延びる穴 70 が形成されてコンタクト 28C を覆う導電材料（不図示）を露出させてよい。次に、電気的に伝導性の部分が表の面 18C に形成されてよい。該導電性の部分は、誘電層 68 の裏面 69 から穴 70 を通ってコンタクト 28C を覆う導電材料まで延びる導電性のビア 72 と、ビア 72 から表面 69 に沿って延びる導電性配線 74 と、表面 69 にあり望ましくは配線 74 から延び電気的に接続された端子 76 とを含む。端子 76 は超小型電子装置 14 の裏面 78 に露出し、コンタクト 28C に配線 74 及びビア 70 を介して電気的に接続される。

【 0033 】

他の実施形態では、一連の蒸着処理が封止された組立体に対して実行されて、金属被覆されたビアと導電性配線の 1 つ以上の層と誘電材料の複数の層とを備える導電性構造体が作製される。

【 0034 】

また、誘電層 68 を貫通して装置 14 の封止層 54 の裏面 60 まで延びる穴 80 が形成されてもよい。図示していないが、穴 80 は表面 60 の長さに沿ってこれと平行に装置 14 の別の電気要素、例えば電源（不図示）の正又は負の接地端子まで延びていてもよい。次に、導電性の部分が装置 14 の表面 78 に形成されてよい。該導電性の部分は、誘電層 68 の裏面 69 から穴 80 を通って封止層 54 の裏面 60 まで延びる導電性のビア 82 と、ビア 82 から表面 69 に沿って延びる導電性配線 84 と、表面 69 にあり望ましくは配線 84 から延び電気的に接続された端子 86 とを含む。1 つの実施形態では、ビア 82 の導電材料は裏面 60 に沿って延びて、電源（不図示）の正及び負の端子を構成する外部コネクタに接続されてもよい。

【 0035 】

装置 14 の封止層の裏面 60 にある配線、ビア、及び端子を構成する導電性部分は、超小型電子装置 12 の装置コンタクトを形成するのに使用されるのと同じ上述した材料を含み、フォトリソグラフィ又は類似のプロセスで形成されてもよい。配線は任意の適切な金属堆積手法で形成されてよい。この堆積手法は例えばスパッタリング、無電解又は電解めつき、又は導電性ペースト又は導電性基質材料の印刷又はステンシル印刷を含む。

【 0036 】

半田レジスト層（不図示）で誘電層 68 の裏面 69 の非被覆部を覆い、パターン形成して配線 74、84 を覆ってもよい。これにより端子 76、86 が表面 69 に露出される。

【 0037 】

また、半田レジスト層の形成の次に、ボンドメタル、半田、導電性ペースト、導電性基質材料などの導電材料の塊 88 からなる結合部が、導電性部分の外面の露出部（端子 74、84 として働く）上に形成されてよい。塊 88 の幾つかは端子 76、導電性配線 74、及びビア 72 を介してチップ 16C のコンタクト 28C に電気的に接続されてよい。また、塊 88 の幾つかは端子 86、配線 84、及びビア 82 を介して、例えば装置 14 に含まれるか関連する他の電子回路に電気的に接続されてもよい。塊 88 はボンドメタル、例えば半田、金、スズ、又はインジウムを含んでよい。塊 88 の形成の次に、半田レジスト層

10

20

30

40

50

は除去されてもよい。

【0038】

超小型電子装置14は超小型電子装置12と同様に、完成時に該1つ以上のチップを支持するためのパッケージ基板を必要とせずに構築されるのが望ましい。

【0039】

従って、上記のように形成された装置12、14はテスト可能な装置を構成し、それ含まれるチップの所望の電気的機能性及び動作性を確認するためにテストを実行することが出来る。例えば装置12のチップ16Aは、装置コンタクトとの接続を介して機能テストを実行でき、チップ16Bは、露出したコンタクト28Bとの接続を介して機能テストを実行できる。また、超小型電子装置14の端子はチップ16Cの機能テストに適切である。従って、各超小型電子装置12、14内のチップは、装置を積層し組み立てる前に、必要に応じて他の超小型電子装置と共に機能をテストできるので、下記に説明するパッケージ10などの共通パッケージを形成できる。

【0040】

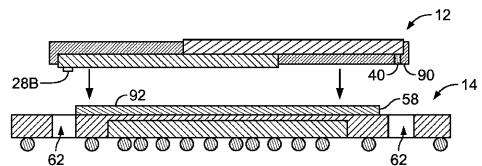

図9～図11を参照すると、超小型電子装置12は望ましくはテスト後、超小型電子装置14（望ましくはテスト後の）に垂直積層配置で取り付けられてパッケージ10を形成する。装置12は裏面34、18Bからなる裏面90において装置14の封止層54の上面58に、接着剤の層92により取り付けられる。接着剤92は上述した装置12のチップを互いに接合するのに使用した接着剤に類似していてよい。装置12、14は、装置14の穴62が装置12の装置コンタクト、例えばビア42と露出したチップコンタクト28Bとに垂直に整列された状態で互いに接合される。

【0041】

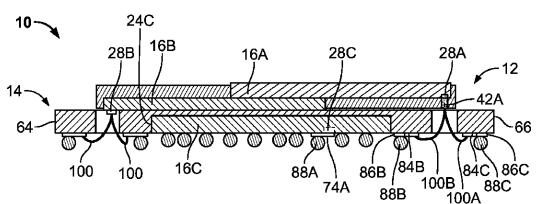

図10を参照すると、積層された装置12及び14からなるパッケージ10は、配線84の露出部に一端が接続し、他端が超小型電子装置12のチップの装置コンタクト又はチップコンタクトに接続された結合線100を有してもよい。例えば、導電性要素間の電気的接続が概略的に例示されたパッケージ10の底面図である図12を参照すると、結合線100Aは、端子86C及び塊88Cに電気的に接続された配線84Cを、装置12のチップ16Aのコンタクト28Aに電気的に接続されたビア42Aに接続する。また、結合線100Bは、端子86B及び塊88Bに電気的に接続された配線84Cを、超小型電子装置コンタクト、例えば装置12のチップ16Aの別のコンタクト28Aに電気的に接続されたパッド（不図示）に接続する。また、装置14の形成に関して上記説明したように、チップ16Cのコンタクト28Cは塊88Aに導電性ビア72A（図12において不図示）、配線74A、及び端子76A（図12において不図示）を介して電気的に接続される。1つの実施形態では、穴62と超小型電子装置14の近接する端64又は66との間に位置する端子86と電気的に互いに接続された関連する配線、ビア、及び塊88とは、結合線100が接続される電源及び接地端子を構成してもよい。一方、穴62と超小型電子装置14のチップの近接する端24又は26との間に位置する端子86と電気的に互いに接続された関連する配線、ビア、及び塊88とは、接続された結合線100を介して超小型電子装置12のチップとのデータ交換を可能にする。

【0042】

1つの実施形態では、結合線100は、細線の端に露出したワイヤー（通常、金、銅、又は銅合金製）の端を加熱してボールボンドを形成するよう軟化させることで、装置コンタクト、例えばビア42及び配線84に圧着により接合され、ベース（不図示）を形成することができる。

【0043】

或いは、結合線をウエッジ接合により形成できる。ウエッジ接合はワイヤーの端に近い部分を加熱し装置14の裏面の装置コンタクト及び配線に沿って加圧しながら引っ張ることで形成される。アルミニウム結合線をこの方法で形成できる。このようなプロセスは米国特許第7,391,121号により詳しく記載されている。この特許の開示内容全体を引用することにより本明細書の一部となすものとする。

10

20

30

40

50

## 【0044】

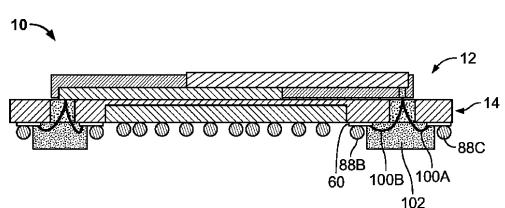

図11を参照すると、封止層102が、穴62内と穴62に隣接した封止層54の裏面60の非被覆部を覆って形成され、結合線100を封止してもよい。封止層102はエポキシ材料を含んでもよい。

## 【0045】

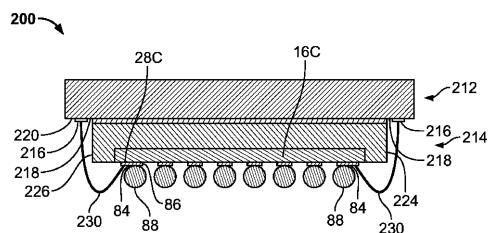

別の実施形態では、図13を参照すると、超小型電子パッケージ200は装置14と類似の構成を有する超小型電子装置214と装置12と類似の構成を有する超小型電子装置212とを含み、装置214の上に垂直方向に装置212が積層されていてよい。パッケージ200において、装置212は、裏面220の装置214の両端224、226から伸びる両部分218上に露出したチップコンタクト216を有する。装置214は中を結合線が通る貫通する穴を有していない。上述したパッケージ10と同様に、結合線230は装置212のコンタクト216を覆う導電材料(不図示)から端226、224を回って配線84まで伸び、配線84は端子86を装置214内の半導体チップ16Cのチップコンタクト28Cに電気的に接続する。

10

## 【0046】

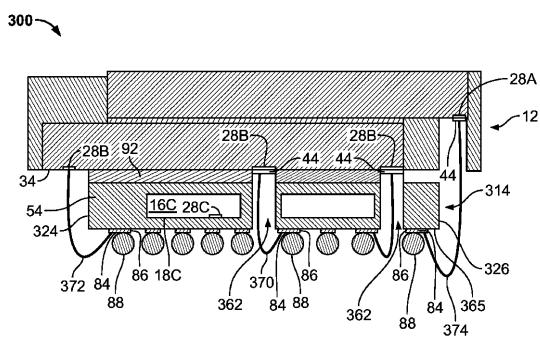

別の実施形態では、図14を参照すると、超小型電子パッケージ300は超小型電子装置314の上に垂直方向に積層された上述した超小型電子装置12を含んでもよい。封止層54の裏面が装置314の裏面365を形成し、封止剤がチップコンタクト28Cが配置されたチップ16の表の面18Cから装置314の裏面365に伸びている点を除いて、装置314は上述した超小型電子装置14と類似の構成を有する。この実施形態では、穴362が裏面365から装置314の厚みを貫通して装置12の表面34まで伸び、上側の装置12のチップ16Bのコンタクト28Bに垂直に整列されている。結合線370は装置12の装置コンタクト44から穴362を通って装置314の裏面365にある配線84まで伸びている。また、結合線372はコンタクト28Bから装置314の端324を回って装置314の裏面上の配線84まで伸び、端子86をチップコンタクト28Bに電気的に接続する。また、結合線374はコンタクト28Aに電気的に接続された装置コンタクト44から装置314の端326を回って伸び、装置314の裏面上の配線84に接続することで、端子86をコンタクト28Aに電気的に接続する。

20

## 【0047】

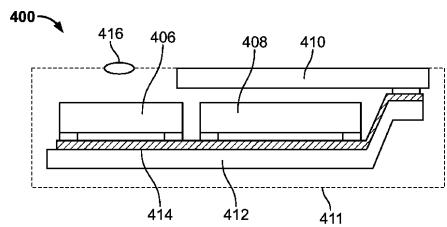

上記した超小型電子パッケージは、図15に示すように様々な電子システムの構成において使用できる。例えば、本開示の別の実施形態に係るシステム400は、上記の超小型電子パッケージ406と他の電子部品408及び410とを含む。この図の例では、部品408は半導体チップであり、一方、部品410は表示画面であるが、任意の他の部品を使用できる。図15では図の明確さのために追加の部品が2つだけ描かれているが、勿論、システムは任意の数の部品を含んでよい。電子パッケージ又は組立体406は上記のパッケージ又は組立体のいずれでもよい。別の変形例では、任意の数の超小型電子パッケージ又は組立体が使用される。超小型電子パッケージ又は組立体406と部品408及び410は破線で概略描いた共通のハウジング411に実装され、適宜互いに電気的に接続されて所望の回路を形成する。図に示した代表的なシステムでは、該システムはフレキシブル印刷回路基板等の回路パネル412を含み、該回路パネルは部品を互いに接続する多数の導体414(図15では1つだけ描かれている)を含む。しかし、これは単に代表例であり、電気的接続のための任意の適切な構造体を使用できる。ハウジング411は、例えば携帯電話又は携帯情報端末で使用可能な種類の携帯ハウジングとして描かれており、表示画面410はハウジングの表面に露出している。構造体406が撮像チップ等の光感應素子を含む場合、レンズ416又は他の光学素子も該構造体に光を導くために設けてよい。図15に示す簡略化したシステムは単に代表例であり、通常、固定構造体と見なされるシステム、例えば卓上型コンピュータ、ルーター等を含む他のシステムを上記の構造体を使用して作製することが出来る。

30

## 【0048】

従って、本開示の実施形態は、テスト可能な複数の超小型電子装置を共通のパッケージ

40

50

内に組み立てる方法を提供する。この共通のパッケージは、回路パネル、回路基板、フレキシブル回路パネル等の外部部品に接続するための共通のパッケージ端子群を有する。各超小型電子装置は1つ以上の半導体チップを含み、超小型電子装置群のうち第1の超小型電子装置の表面に露出する装置コンタクトは、第1の超小型電子装置の1つ以上のチップのチップコンタクト及び第2の超小型電子装置の外面にあるパッケージ端子に電気的に接続される。各超小型電子装置は、完成時に該1つ以上のチップを支持するためのパッケージ基板を必要とせずに構築されうる。装置コンタクトは第1の装置の半導体チップのチップコンタクトから第1の装置の露出した面に沿って少なくとも一方向に離すことができる。該パッケージの超小型電子装置は、ウェハレベル・チップスケールパッケージ (WLCSP) 又はファンアウト・ウェハレベルパッケージ (FO-WLP) の特徴、ワイヤーボンド可能なパッド等の装置コンタクトは、導電材料を1つ以上の半導体チップを含む封止された組立体上に堆積させることで形成される、に類似の特徴を有する可能性がある。例えば、超小型電子装置は再構成されたウェハ又は回路パネルの一部であってもよい。

## 【0049】

装置コンタクトは各第1の超小型電子装置における1つ以上の半導体チップの機能テストに適しており、端子は各第2の超小型電子装置における1つ以上の半導体チップの機能テストに適しているので、共通のパッケージ内に1つ以上の第1の超小型電子装置と1つ以上の第2の超小型電子装置とを更に組み立てる前に、第1と第2の超小型電子装置のそれぞれのチップを機能テストすることが出来る。

## 【0050】

本発明を特定の実施形態について説明したが、これらの実施形態は本発明の原理と用途を単に例示していることは理解されるべきである。従って、これらの実施形態に多数の変更が加えられる可能性があり、添付の請求項により定義される本発明の思想及び範囲から逸脱することなく他の構成が想到される可能性があることは理解されるべきである。

【図1】

【図3B】

FIG. 3B

【図2】

【図3A】

FIG. 3A

【図4】

FIG. 4

【図5】

FIG. 5

【図6】

FIG. 6

【図7】

FIG. 7

【図8】

FIG. 8

【図9】

FIG. 9

【図10】

FIG. 10

【図11】

FIG. 11

【図12】

FIG. 12

【図13】

FIG. 13

【図14】

FIG. 14

【図15】

FIG. 15

---

フロントページの続き

(74)代理人 100142996

弁理士 森本 聰二

(74)代理人 100154298

弁理士 角田 恭子

(74)代理人 100166268

弁理士 田中 祐

(74)代理人 100170379

弁理士 徳本 浩一

(74)代理人 100161001

弁理士 渡辺 篤司

(74)代理人 100179154

弁理士 駿玉 真衣

(74)代理人 100180231

弁理士 水島 亜希子

(74)代理人 100184424

弁理士 増屋 徹

(72)発明者 キャスキー, テレンス

アメリカ合衆国カリフォルニア州 95134, サン・ノゼ, オーチャード・パークウェイ 302

5

(72)発明者 モハメッド, イリヤス

アメリカ合衆国カリフォルニア州 95050, サンタ・クララ, ボハノン・ドライヴ 2377

審査官 秋山 直人

(56)参考文献 米国特許出願公開第 2007/0252256 (U.S., A1)

特開平 11-135713 (JP, A)

特開 2005-353837 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 25/065

H 01 L 25/07

H 01 L 25/18