(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2016년04월20일

(11) 등록번호 10-1614106

(24) 등록일자 2016년04월14일

(51) 국제특허분류(Int. Cl.)

H01L 33/46 (2010.01) H01L 33/40 (2010.01)

H01L 33/44 (2010.01)

(21) 출원번호 10-2012-7004141

(22) 출원일자(국제) 2010년06월10일

심사청구일자 2015년02월02일

(85) 번역문제출일자 2012년02월16일

(65) 공개번호 10-2012-0052327

(43) 공개일자 2012년05월23일

(86) 국제출원번호 PCT/EP2010/058160

(87) 국제공개번호 WO 2011/006719

국제공개일자 2011년01월20일

(30) 우선권주장

10 2009 033 686.9 2009년07월17일 독일(DE)

(56) 선행기술조사문현

WO2009084670 A1\*

JP05235406 A\*

US20090101919 A1\*

\*는 심사관에 의하여 인용된 문헌

(73) 특허권자

오스람 옵토 세미컨덕터스 게엠베하

독일 레겐스부르크 라이브니츠슈트라쎄 4 ( 우:93055)

(72) 발명자

회펠, 루츠

독일 93087 알테크로프스하임 래씽슈트라쎄 1

본 말, 노르빈

독일 93152 니텐도르프-툼하우젠 슈톡로어 슈트라쎄 8

(74) 대리인

특허법인 남앤드남

전체 청구항 수 : 총 13 항

심사관 : 한상일

(54) 발명의 명칭 광전자 반도체 소자 그리고 무기 광전자 반도체를 제조하기 위한 방법

**(57) 요 약**

본 발명은 캐리어(2) 및 적어도 하나의 반도체 층 시퀀스(3)를 포함하는 광전자 반도체 소자(1)와 관련이 있다. 반도체 층 시퀀스(3)는 적어도 하나의 활성층(30)을 구비한다. 반도체 층 시퀀스(3)는 또한 캐리어(2)에도 적용되어 있다. 광전자 반도체 소자(1)는 또한 캐리어(2)와 반도체 층 시퀀스(3) 사이에 있는 금속 미리(4)도 포함한다. 캐리어(2) 및 반도체 층 시퀀스(3)는 금속 미리(4) 위로 가로 방향으로 돌출한다. 또한, 금속 미리(4)는 방사선을 통과시키는 캡슐화 층(5)에 의해서 가로 방향으로 직접 둘러싸여 있다.

**대 표 도** - 도1a

## 명세서

### 청구범위

#### 청구항 1

광전자 반도체 소자(1)로서,

캐리어(2)를 포함하며,

하나 이상의 활성층(30)을 갖는 하나 이상의 반도체 층 시퀀스(3)를 포함하며, 이때 상기 반도체 층 시퀀스(3)는 캐리어(2)에 설치되어 있으며, 이때 상기 반도체 층 시퀀스(3)는 하나 또는 다수의 활성층(30)을 갖고, 상기 활성층들은 전자기 방사선을 방출할 목적으로 설치되어 있으며, 그리고

상기 캐리어(2)와 상기 반도체 층 시퀀스(3) 사이에 있는 금속 미러(4)를 포함하며,

상기 캐리어(2) 및 상기 반도체 층 시퀀스(3)는 상기 금속 미러(4) 위로 가로 방향으로 돌출하며,

상기 금속 미러(4)는 가로 방향으로 캡슐화 층(5)에 의해서 직접 둘러싸이고,

상기 캡슐화 층(5)의 재료는 둘레에서 상기 금속 미러(4)의 재료에 직접 접합으로써, 결과적으로 상기 캐리어(2) 또는 상기 반도체 층 시퀀스(3) 쪽을 향하고 있지 않은 금속 미러(4)의 모든 제한 면은 상기 캡슐화 층(5)에 의해서 덮여 있고, 마찬가지로 금속 미러(4)에 의해서 덮이지 않았고 상기 캐리어(2) 쪽을 향하고 있는 상기 반도체 층 시퀀스(3)의 하부 면도 상기 캡슐화 층(5)에 의해서 덮여 있으며,

상기 캡슐화 층(5)은 횡단면 상으로 볼 때 U자 모양으로 형성됨으로써, 결과적으로 U자의 레그들은 상기 금속 미러(4)로부터 멀어지는 방향을 향하고 있고,

상기 캡슐화 층(5)의 두께는 20 nm 이상 100 nm 이하이며,

상기 캡슐화 층(5) 상에 보호층(50)이 적어도 국부적으로 제공되어 있으며, 상기 보호층의 두께는 100 nm 이상 400 nm 이하이고,

상기 금속 미러(4) 위로 돌출하는 상기 반도체 층 시퀀스(3)의 가로 돌출부(L)는 100 nm 이상 2.0 μm 이하이며,

상기 캡슐화 층(5)은 전기 절연성이고, 방사선을 통과시키며, 그리고

상기 반도체 층 시퀀스(3)로부터 성장된 한 부분 층 및 제 2 미러 층(6)으로부터 성장된 상기 캡슐화 층(5)의 한 부분 층이 서로 접촉하여 심(8)을 형성하고, U자의 레그들은 상기 캡슐화 층(5)을 형성하는,

광전자 반도체 소자.

#### 청구항 2

제 1 항에 있어서,

상기 캡슐화 층(5)의 두께는 30 nm 이상 70 nm 이하이고, 상기 캡슐화 층(5)의 결합 밀도는 mm<sup>2</sup>당 최고 0.1 결합이며,

이때 상기 캡슐화 층(5)은

상기 반도체 층 시퀀스(3)의 측벽들(32)을 부분적으로 또는 완전히 덮으며, 그리고

상기 반도체 층 시퀀스(3) 쪽을 향하고 있는 그리고 방사선 통과 면(35)에 대한 평면도를 통해서 볼 때 상기 반도체 층 시퀀스(3)에 의해서 겹쳐진 상기 캐리어(2)의, 상기 제 2 미러 층(6)의 그리고 납땜 결합 층(22)의 제한 면을 부분적으로 또는 완전히 덮는,

광전자 반도체 소자.

#### 청구항 3

제 2 항에 있어서,

상기 캡슐화 층(5)이 텅스텐, SiO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub> 및/또는 ZrO<sub>2</sub>을 포함하는 재료들 중에 한 가지 재료를 포함하거나 또는 상기 재료로 이루어지는,

광전자 반도체 소자.

#### 청구항 4

제 1 항에 있어서,

상기 캡슐화 층(5)의 재료는 0.1 μm의 재료 두께에 대하여 산출했을 때 물 및 산소에 대하여 최고  $10^{-5}$  g/(m<sup>2</sup> d)의 고유 확산 상수를 갖는,

광전자 반도체 소자.

#### 청구항 5

제 1 항 내지 제 4 항 중 어느 한 항에 있어서,

상기 금속 미러(4)는 100 nm 이상 200 nm 이하의 두께를 갖는,

광전자 반도체 소자.

#### 청구항 6

제 1 항 내지 제 4 항 중 어느 한 항에 있어서,

상기 캡슐화 층(5)이 두 가지 이상의 상이한 재료로 이루어진 일련의 개별 층들(5a, 5b)을 포함하며, 이때 상기 캡슐화 층(5)은 총 네 개 이상의 개별 층(5a, 5b)을 포함하고, 상기 개별 층들(5a, 5b)의 두께는 각각 2 nm 이상 8 nm 이하인,

광전자 반도체 소자.

#### 청구항 7

제 1 항 내지 제 4 항 중 어느 한 항에 있어서,

상기 캡슐화 층(5)은 투명하게 보이고, 상기 활성층(30)에 의해서 발생되는 또는 수신될 통과 방사선을 최고 3.0 %까지 흡수하는,

광전자 반도체 소자.

#### 청구항 8

제 1 항 내지 제 4 항 중 어느 한 항에 있어서,

상기 광전자 반도체 소자가 상기 제 2 미러 층(6)을 포함하며, 상기 제 2 미러 층은 상기 금속 미러(4)와 상기 캐리어(2) 사이에 있고, 가로 방향으로 상기 반도체 층 시퀀스(3) 위로 돌출하며, 이때 상기 제 2 미러 층(6)은 상기 캡슐화 층(5)을 통과하는 그리고 활성층(30) 내에서 발생하는 방사선을 반사할 목적으로 설치된,

광전자 반도체 소자.

#### 청구항 9

제 1 항 내지 제 4 항 중 어느 한 항에 있어서,

상기 금속 미러(4)의 면적과 상기 반도체 층 시퀀스(3)의 면적 비율이 적어도 95 %인,

광전자 반도체 소자.

#### 청구항 10

제 1 항 또는 제 4 항에 있어서,

상기 반도체 층 시퀀스(3)의 방사선 통과 면(35)에는 상기 캡슐화 층(5)이 없는,

광전자 반도체 소자.

### 청구항 11

제 1 항에 따른 광전자 반도체 소자를 제조하는 방법으로서,

상기 방법이

캐리어(2), 반도체 층 시퀀스(3) 및 금속 미러(4)를 준비하는 단계를 포함하며, 이때 상기 금속 미러(4)는 상기 캐리어(2)와 상기 반도체 층 시퀀스(3) 사이에 있고, 상기 캐리어 및 상기 반도체 층 시퀀스가 상기 금속 미러(4) 위로 가로 방향으로 돌출하며, 그리고

캡슐화 층(5)을 가로 방향으로 상기 금속 미러(4)에 직접 제공하는 단계를 포함하며, 이때 상기 캡슐화 층(5)은 원자 층 중착을 통해서 형성되는,

광전자 반도체 소자를 제조하는 방법.

### 청구항 12

제 11 항에 있어서,

100 nm 이상 400 nm 이하의 두께를 갖는 상기 보호층(50)이 기상 중착을 통해서 상기 캡슐화 층(5) 상에 제공되 는,

광전자 반도체 소자를 제조하는 방법.

### 청구항 13

제 11 항 또는 제 12 항에 있어서,

상기 반도체 층 시퀀스(3) 및 상기 금속 미러(4)의 패턴화는 에칭에 의해서 그리고 동일한 마스크에 의해서 이 루어지는,

광전자 반도체 소자를 제조하는 방법.

### 청구항 14

삭제

### 청구항 15

삭제

## 발명의 설명

### 기술 분야

본 발명은 광전자 반도체 소자와 관련이 있다. 더 나아가 본 발명은 무기 광전자 반도체를 제조하기 위한 방법 과도 관련이 있다.

### 발명의 내용

본 발명의 해결 과제는, 광 방출 효율이 높은 광전자 반도체 소자를 제공하는 것이다. 한 가지 추가의 해결 과제는, 상기와 같이 광 방출 효율이 높은 광전자 반도체 소자를 제조하기 위한 방법을 제시하는 것이다.

광전자 반도체 소자의 적어도 한 가지 실시 예에 따라, 상기 광전자 반도체 소자는 하나 이상의 반도체 층 시퀀스를 구비한다. 바람직하게 무기 반도체 층 시퀀스로서는 발광 다이오드, 레이저 다이오드 또는 포토 다이오드 가 사용될 수 있다. 상기 반도체 층 시퀀스는 바람직하게 예를 들어 간행물 DE 10 2007 004 304 A1호에 기재된 박막 층 시퀀스이며, 반도체 층 시퀀스 및 반도체 층 시퀀스를 제조하기 위한 방법과 관련하여 상기 간행물에

공개된 내용은 인용의 방식으로 본 출원서에 수용된다. 상기 반도체 층 시퀀스는 하나 또는 다수의 활성층을 갖는다. '활성'이라는 표현은 상응하는 층이 전자기 방사선을 방출할 목적으로 또는 흡수할 목적으로 설치되어 있다는 것을 의미한다.

광전자 반도체 소자의 적어도 한 가지 실시 예에 따라, 상기 광전자 반도체 소자는 하나의 캐리어를 구비한다. 상기 캐리어는 바람직하게 반도체 층 시퀀스를 지탱할 목적으로 그리고 기계적으로 지지할 목적으로 설치되어 있다. 캐리어로서는 특히 상기 반도체 소자의 용도에 따른 작동 중에 발생하는 부하 범위 안에서 휨에 안정적인 강성의 고체가 사용된다. 예를 들어 캐리어는 게르마늄 혹은 규소와 같은 반도체 재료, Cu, Ni, Ag 혹은 Mo 와 같은 금속 또는  $\text{Al}_2\text{O}_3$ ,  $\text{AlN}$  혹은  $\text{SiN}_x$ 와 같은 전기 절연 재료를 포함하거나 또는 이와 같은 재료로 이루어진다. 상기 캐리어는 반도체 층 시퀀스의 성장 기관과 상이할 수 있다.

광전자 반도체 소자의 적어도 한 가지 실시 예에 따라, 상기 반도체 층 시퀀스는 캐리어에 적용되어 있다. 이와 같은 내용이 의미하는 바는, 반도체 층 시퀀스와 캐리어 사이에 하나 또는 다수의 층이 있고, 상기 하나 또는 다수의 층을 통해서 반도체 층 시퀀스와 캐리어 간의 접착 촉진 및 견고한 결합이 보증된다는 것이다. 특히 캐리어 재료와 반도체 층 시퀀스 간에는 직접적인 접촉이 이루어지지 않는다.

광전자 반도체 소자의 적어도 한 가지 실시 예에 따라, 상기 광전자 반도체 소자는 금속 미러를 포함한다. 상기 금속 미러는 캐리어와 반도체 층 시퀀스 사이에 있다. 바람직하게 전체 금속 미러는 이 금속 미러가 완전히 반도체 층 시퀀스와 캐리어 사이에 존재하도록 배치되어 있다. 금속 미러는 활성층에 의해서 방출될 또는 수신될 방사선을 반사할 목적으로 설치되어 있다. '금속 미러'란 이 미러가 주로 또는 완전히 금속 또는 금속 합금으로 이루어진다는 것을 의미한다. 예를 들어 금속 미러는 은 미러다. 캐리어와 반도체 층 시퀀스 간의 전기 접속은 바람직하게 도전성 금속 미러를 통해서 이루어질 수 있다. 이와 같은 금속 미러는 반도체 층 시퀀스에 집적 접촉한다.

특히 금속 미러는 예컨대 은과 같이 산소 또는 물의 영향에 의해서 화학적으로 손상되는 재료를 포함하거나 또는 이와 같은 재료로 이루어진다. 또한, 금속 미러의 재료는 - 예컨대 은도 마찬가지로 - 특별히 습기 및/또는 전기적인 전압의 영향에 의해서 이동(migration)하는 경향을 가질 수도 있다.

광전자 반도체 소자의 적어도 한 가지 실시 예에 따라, 상기 캐리어 및 반도체 층 시퀀스는 금속 미러 위로 가로 방향으로 돌출한다. 이 가로 방향은 예컨대 캐리어의 주 연장 방향을 따라서 평행하게 뻗는 방향이다. 특히 모든 가로 방향으로 캐리어뿐만 아니라 반도체 층 시퀀스도 금속 미러 위로 돌출한다. 다른 말로 표현하자면, 캐리어뿐만 아니라 반도체 층 시퀀스도 가로 방향으로 바람직하게는 둘레에서 또는 모든 면에서 금속 미러 위로 돌출한다.

광전자 반도체 소자의 적어도 한 가지 실시 예에 따라, 상기 금속 미러는 반도체 층 시퀀스에 의해서 방출될 또는 수신될 방사선을 통과시키는 그리고 전기 절연성의 또는 도전성의 캡슐화 층에 의해서 직접 가로 방향으로 둘러싸여 있다. 다른 말로 표현하자면, 상기 캡슐화 층의 재료는 특히 둘레에서 상기 금속 미러의 재료에, 예컨대 캐리어 또는 반도체 층 시퀀스 쪽을 향하고 있지 않은 금속 미러의 모든 경계면에 직접 접한다.

광전자 반도체 소자의 적어도 한 가지 실시 예에 따라, 상기 광전자 반도체 소자는 하나의 캐리어 및 적어도 하나의 반도체 층 시퀀스를 구비한다. 상기 반도체 층 시퀀스는 적어도 하나의 활성층을 갖는다. 반도체 층 시퀀스는 또한 캐리어에도 적용되어 있다. 반도체 소자는 또한 캐리어와 반도체 층 시퀀스 사이에 있는 금속 미러도 포함한다. 캐리어 및 반도체 층 시퀀스는 금속 미러 위로 가로 방향으로 돌출한다. 또한, 금속 미러는 방사선을 통과시키는 그리고 전기 절연성의 또는 도전성의 캡슐화 층에 의해서 가로 방향으로 직접 둘러싸여 있다.

금속 미러가 캡슐화 층에 의해서 가로 방향으로 특히 완전히 둘러싸임으로써, 결과적으로 반도체 층 시퀀스 또는 캐리어 쪽을 향하는 상기 금속 미러의 경계면은 노출되지 않으며, 금속 미러는 예를 들어 산화에 의한 손상으로부터 보호될 수 있다. 또한, 금속 미러의 구성 성분으로부터 예컨대 반도체 층 시퀀스의 가로 경계면들로의 이동 현상도 상기 캡슐화 층에 의해서 방지될 수 있거나 또는 현저하게 줄어들 수 있다. 방사선을 통과시키는 캡슐화 층을 사용함으로써, 예를 들어 반도체 소자 내에서 발생하는 방사선의 방출 효율이 증가할 수 있는데, 그 이유는 상기 캡슐화 층에 의해서 실제로 방사선이 전혀 흡수되지 않기 때문이며, 그리고 특히 캡슐화 층 아래에 놓인 추가 층들에 의해서 방사선의 효율적인 반사 및 편향이 이루어질 수 있기 때문이다.

광전자 반도체 소자의 적어도 한 가지 실시 예에 따라, 상기 캡슐화 층의 재료는 물 및/또는 산소에 대하여 최

대  $10^{-5}$  g/(m<sup>2</sup> d)의 고유 확산 상수를 갖는다. 이때 상기 고유 확산 상수는 특히 0.1 μm의 재료 두께에 대하여 산출되었다. 상기 확산 상수는 바람직하게 최고  $5 \times 10^{-6}$  g/(m<sup>2</sup> d), 특히 최고  $10^{-6}$  g/(m<sup>2</sup> d)이다. 이와 같은 캡슐화 층 재료에 의해서는 상기 캡슐화 층의 두께가 얇게 선택될 수 있다. 또한, 상기와 같은 캡슐화 층 재료에 의해서는 반도체 층 시퀀스의 수명 안에서 금속 미러의 두드러진 부식 작용 또는 화학적인 파괴 현상이 방지될 수 있다.

광전자 반도체 소자의 적어도 한 가지 실시 예에 따라, 상기 캡슐화 층은 규소 산화물, 알루미늄 산화물 및/또는 지르코늄 산화물(예를 들어, ZrO<sub>2</sub>)을 포함하거나 또는 이와 같은 산화물로 이루어진다. 또한, 캡슐화 층은 다음과 같은 재료들 중에 한 가지 재료를 포함하거나 또는 이와 같은 재료로 이루어질 수도 있다: TiO<sub>2</sub>, HfO<sub>2</sub>, SnO<sub>2</sub>, SiC, Zr(SiO<sub>4</sub>), Pb<sub>3</sub>(Si<sub>2</sub>O<sub>7</sub>), Na(AlSiO<sub>4</sub>), Si<sub>3</sub>N<sub>4</sub>, AlN, GaN. 투명하고 습기에 안정적인 다른 산화물, 탄화물 및/또는 질화물도 캡슐화 층을 위해서 사용될 수 있다.

광전자 반도체 소자의 적어도 한 가지 실시 예에 따라, 상기 금속 미러는 100 nm(100 nm 포함) 내지 200 nm, 특히 100 nm(100 nm 포함) 내지 150 nm의 두께를 갖는다.

광전자 반도체 소자의 적어도 한 가지 실시 예에 따라, 상기 캡슐화 층의 두께는 20 nm(20 nm 포함) 내지 100 nm, 특히 35 nm(35 nm 포함) 내지 70 nm이다. 이때 캡슐화 층의 두께는 특히 상기 캡슐화 층의 성장 방향에 대하여 평행인 방향으로 측정되어야 한다. 상기 캡슐화 층이 함께 성장된 다수의 부분 영역을 가지면, 특히 개별 부분 영역들 각각에 대한 두께는 예컨대 개별 부분 영역들이 상호 인접하게 되는 심(seam)까지 포함해서 결정되어야만 한다.

광전자 반도체 소자의 적어도 한 가지 실시 예에 따라, 상기 광전자 반도체 소자는 금속 미러와 캐리어 사이에 있는 제 2 미러 층을 포함한다. 이 경우에는 제 2 미러 층이 바람직하게 금속 미러에 직접 접함으로써, 결과적으로 상기 제 2 미러 층의 재료는 금속 미러의 재료와 물리적으로 접촉하게 된다. 제 2 미러 층은 바람직하게도 전성이고, 예를 들어 마찬가지로 적어도 하나의 금속으로부터 형성되었다. 상기 제 2 미러 층의 재료는 예를 들어 Cr 또는 Cr-합금이다. 제 2 미러 층을 위해서 가능한 추가의 재료들은 Ti, Ti<sub>3</sub>N<sub>4</sub>, TiW, TiW(N), Au, Pt, Pd 및/또는 Ni이다. 제 2 미러 층의 재료는 바람직하게 습기 및/또는 산소의 영향하에서 이동 및 부식의 경향을 갖지 않거나 또는 캡슐화 층의 재료보다 적어도 덜 강한 이동 및 부식의 경향을 갖는다.

광전자 반도체 소자의 적어도 한 가지 실시 예에 따라, 상기 제 2 미러 층은 가로 방향으로, 바람직하게는 둘레에서 금속 미러 위로 돌출한다. 그와 마찬가지로 제 2 미러 층은 바람직하게 가로 방향으로, 특히 둘레에서 캡슐화 층 위로도 돌출한다.

상기 제 2 미러 층은 특히 캡슐화 층을 통과한, 활성층 내에서 발생한 전자기 방사선을 반사할 목적으로 설치되었다. 다른 말로 표현하자면, 캡슐화 층에 입사되는 방사선은 적어도 부분적으로 특별히 캡슐화 층을 통과하고, 제 2 미러 층에 의해서 반사되어 예컨대 반도체 층 시퀀스의 방사선 통과 면 쪽으로 향한다. 상기 방사선 통과 면은 예컨대 캐리어로부터 떨어져서 마주한 상기 반도체 층 시퀀스의 제한 면이다.

광전자 반도체 소자의 적어도 한 가지 실시 예에 따라, 상기 광전자 반도체 소자는 캐리어로부터 떨어져서 마주한 방사선 통과 면에서 방사선의 대부분을, 예컨대 방사선의 50 % 이상 또는 80 % 이상의 부분을 방출한다. 다른 말로 표현하자면, 반도체 소자 내에서 발생하는 방사선의 주 방사 방향은 활성층의 주 연장 방향들에 의해서 설정된 평면에 대하여 수직으로, 더 상세하게 말하자면 특히 반도체 층 시퀀스가 그 위에 제공되어 있는 캐리어 기판의 한 측면에 대하여 수직으로 또는 반도체 층 시퀀스의 성장 방향에 대하여 평행하게 방향 설정될 수 있다.

광전자 반도체 소자의 적어도 한 가지 실시 예에 따라, 상기 캡슐화 층은 횡단면 상으로 볼 때 U자 모양으로 형성되었다. U자의 레그들은 바람직하게 금속 미러로부터 떨어지는 방향을 향하고 있는데, 다시 말하자면 U자의 개방된 측이 금속 미러로부터 떨어져서 마주하고 있다. 다른 말로 표현하자면, 상기 캡슐화 층에 의해서는 특히 반도체 층 시퀀스 및 캐리어가 금속 미러 위로 가로로 돌출하는 영역에 일종의 중공 그루우브(hollow groove)가 형성된다. 다시 말해서 캡슐화 층은 금속 미러 위로 돌출하는 상기 반도체 층 시퀀스의 그리고 캐리어의 또는 제 2 미러 층의 또는 납땜 결합 층의 영역들에 그리고 상기 금속 미러의 가로 제한 면들에 밀착되어, 이 경우 상기 돌출 영역에서는 공동부가 가로 방향에 대하여 수직인 방향으로 상기 캡슐화 층에 의해서 제한되어 있다.

광전자 반도체 소자의 적어도 한 가지 실시 예에 따라, 상기 캡슐화 층은 일련의 개별 층들을 포함하며, 이 경우 두 개 이상의 개별 층들은 서로 상이한 재료를 포함한다. 예를 들어 캡슐화 층은 두 가지 이상의 상이한 재료로 이루어진 개별 층들이 교대로 제공된 시퀀스를 갖는다. 바람직하게 상기 캡슐화 층은 네 개 이상의 개별 층, 특히 열두 개 이상의 개별 층, 특히 열두 개 이상의 개별 층을 포함한다.

광전자 반도체 소자의 적어도 한 가지 실시 예에 따라, 상기 개별 층들의 두께는 각각 2 nm(2 nm 포함) 내지 8 nm, 특히 3 nm(3 nm 포함) 내지 6 nm이다.

광전자 반도체 소자의 적어도 한 가지 실시 예에 따라, 금속 미러 위로 돌출하는 상기 반도체 층 시퀀스의 가로 돌출부는 50 nm(50 nm 포함) 내지 2.0  $\mu\text{m}$ 이다. 상기 가로 돌출부는 바람직하게 100 nm(100 nm 포함) 내지 1.0  $\mu\text{m}$ , 특히 100 nm(100 nm 포함) 내지 500 nm이다.

광전자 반도체 소자의 적어도 한 가지 실시 예에 따라, 상기 캡슐화 층은 투명하다. 캡슐화 층을 통과하는 가시 방사선은 특히 최고 3.0 %까지 흡수되고, 바람직하게는 최고 2.0 %까지 흡수된다. 다른 말로 표현하자면, 상기 캡슐화 층은 높은 투명도를 갖는다. 이와 같은 경우는 반도체 소자의 작동 중에 반도체 층 시퀀스에 의해 전자기 방사선이 발생되는 스펙트럼 범위에 바람직하다.

광전자 반도체 소자의 적어도 한 가지 실시 예에 따라, 상기 반도체 소자에 대한 평면도를 통해서 볼 때 금속 미러의 면적과 반도체 층 시퀀스의 면적 비율은 적어도 95 %, 바람직하게는 적어도 97 %, 특히 적어도 98.5 %이다. 다른 말로 표현하자면, 실제로 캐리어 쪽을 향하고 있는 상기 반도체 층 시퀀스의 전체 면이 금속 미러에 의해서 덮여 있다.

광전자 반도체 소자의 적어도 한 가지 실시 예에 따라, 상기 반도체 층 시퀀스의 방사선 통과 면에는 캡슐화 층이 없다.

광전자 반도체 소자의 적어도 한 가지 실시 예에 따라, 상기 반도체 층 시퀀스의 방사선 통과 면은 캡슐화 층에 의해서 덮여 있다. 예컨대 방사선 통과 면은 단독으로 또는 상기 방사선 통과 면에 접촉하는 전기 접촉점과 함께 캡슐화 층에 의해서 완전히 덮여 있다. 이때 상기 캡슐화 층의 재료는  $\text{SiO}_2$ 가 바람직하다.

광전자 반도체 소자의 적어도 한 가지 실시 예에 따라, 상기 캡슐화 층은 금속 미러의 모든 가로 제한 면들, 캐리어 쪽을 향하고 있고 금속 미러 위로 돌출하는 상기 반도체 층 시퀀스의 하나의 제한 면, 상기 반도체 층 시퀀스의 측벽들, 그리고 반도체 층 시퀀스 쪽을 향하고 있고 방사선 통과 면에 대한 평면도 상으로 볼 때 상기 반도체 층 시퀀스에 의해서 덮인 상기 캐리어의, 제 2 미러 층의 그리고/또는 납땜 결합 층의 한 제한 면을 부분적으로 또는 바람직하게는 완전히 덮는다.

더 나아가 무기 광전자 반도체 소자를 제조하기 위한 방법이 제시된다. 예를 들면 전술된 실시 예들 중에 한 가지 실시 예 또는 다수의 실시 예와 연관하여 기술된 방법에 의해서 반도체 소자가 제조될 수 있다. 그렇기 때문에 광전자 반도체 소자의 특징들은 이하에서 기술될 방법에 대해서도 개시된 것이며, 그 역도 마찬가지로 가능하다.

무기 광전자 반도체 소자를 제조하기 위한 방법의 적어도 한 가지 실시 예에서, 상기 제조 방법은 다음과 같은 단계들을 포함한다:

- 캐리어, 반도체 층 시퀀스 및 금속 미러를 준비하는 단계로서, 이 경우에는 금속 미러가 캐리어와 반도체 층 시퀀스 사이에 있고, 상기 캐리어 및 반도체 층 시퀀스가 금속 미러 위로 가로 방향으로 돌출하며,

- 방사선을 통과시키는 전기 절연성의 또는 도전성의 캡슐화 층을 가로 방향으로 금속 미러에 직접 제공하는 단계로서, 이 경우 상기 캡슐화 층은 원자 층 증착을 통해서 형성되며, 그리고

- 광전자 반도체 소자를 완성하는 단계.

상기 반도체 층 시퀀스는 예를 들어 성장 기판상에서 이루어지는 에피택셜 성장(epitaxial growth)에 의해서 형성된다. 캐리어는 바람직하게는 성장 기판과 상이하다.

상기 캡슐화 층은 원자 층 증착을 통해서 간행물 US 4,058,430 A호에 기재된 바와 유사하게 형성될 수 있다. 상기 간행물의 공개 내용은 인용의 방식으로 본 출원서에 수용된다.

상기 캡슐화 층이 원자 층 증착(영어: Atomic Layer Deposition; 간략히 ALD)을 통해서 형성됨으로써, 특히 균일하게 형성되었고 단지 비교적 적은 오염물 및 결함만을 가지며, 그렇기 때문에 특히 확산에 안정적인 층이 형

성될 수 있다.

무기 광전자 반도체 소자를 제조하기 위한 방법의 적어도 한 가지 실시 예에 따라, 하나의 보호층이 기상 증착을 통해서 상기 캡슐화 층 상에, 특히 상기 캐리어, 반도체 층 시퀀스, 제 2 미러 층 및/또는 납땜 결합 층에 접하지 않는 상기 캡슐화 층의 제한 면들 상에 완전히 또는 국부적으로 제공된다. 기상 증착으로서는 소위 화학 기상 증착(Chemical Vapour Deposition, 간략히 CVD) 또는 물리 기상 증착(Physical Vapour Deposition, 간략히 PVD)이 이용될 수 있다.

무기 광전자 반도체 소자를 제조하기 위한 방법의 적어도 한 가지 실시 예에 따라, 100 nm(100 nm 포함) 내지 500 nm의 두께를 갖는 보호층이 형성된다. 상기 보호층에 의해서는 특히 기계적인 부하 및 손상에 대하여 캡슐화 층이 보호될 수 있거나 또는 캡슐화 층의 재료에 대해서 반응하는 화학 약품들에 대하여도 캡슐화 층이 보호될 수 있다.

무기 광전자 반도체 소자를 제조하기 위한 방법의 적어도 한 가지 실시 예에 따라, 반도체 층 시퀀스 및 금속 미러의 패턴화는 동일한 마스크에 의해서 그리고 특히 에칭에 의해서 이루어진다. 반도체 층 시퀀스 상에는 예를 들어 포토 리소그래피 방법을 통해서 마스크가 제공된다. 그 다음에 반도체 층 시퀀스의 측벽들, 다시 말해 반도체 층 시퀀스의 가로 제한 면들이 형성된다. 그 후에 마스크를 제거하지 않고 특히 제 1 에칭 단계와 상이한 후속하는 제 2 에칭 단계에서 금속 미러가 패턴화되며, 이때에 반도체 층 시퀀스가 가로 방향으로 금속 미러 위로 들출하여 조절될 수 있다. 두 가지 패턴화 프로세스가 동일한 마스크로 이루어짐으로써, 금속 미러의 성형에 대하여 상대적으로 반도체 층 시퀀스의 성형과 관련된 높은 조절 정확성이 보증된다.

이하에서는 본 발명에 따른 광전자 반도체 소자 그리고 무기 광전자 반도체 소자를 제조하기 위한 방법이 실시 예를 인용하는 도면을 참조해서 상세하게 설명된다. 동일한 도면 부호들은 개별 도면에서 동일한 소자들을 지시한다. 하지만, 도면은 척도에 맞게 도시되지 않았으며, 오히려 개별 소자들은 이해를 돋기 위하여 과도하게 크게 도시될 수 있다.

### 도면의 간단한 설명

도 1a, 도 1b, 도 2, 도 4 내지 도 7은 본 발명에 따른 광전자 반도체 소자의 실시 예들의 개략적인 단면도이며, 그리고

도 3은 광전자 반도체 소자의 한 가지 변형 예의 개략적인 단면도이다.

### 발명을 실시하기 위한 구체적인 내용

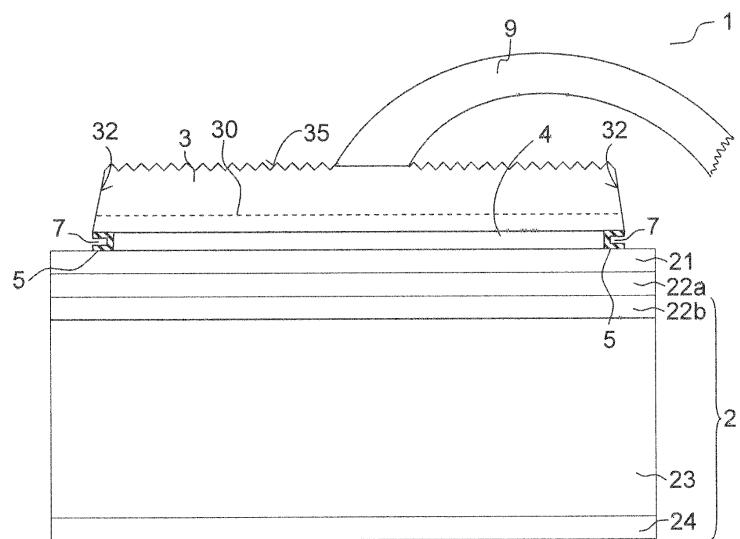

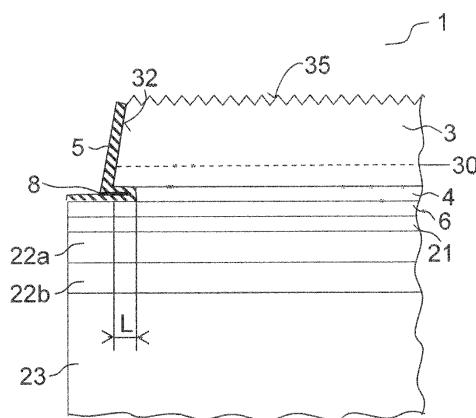

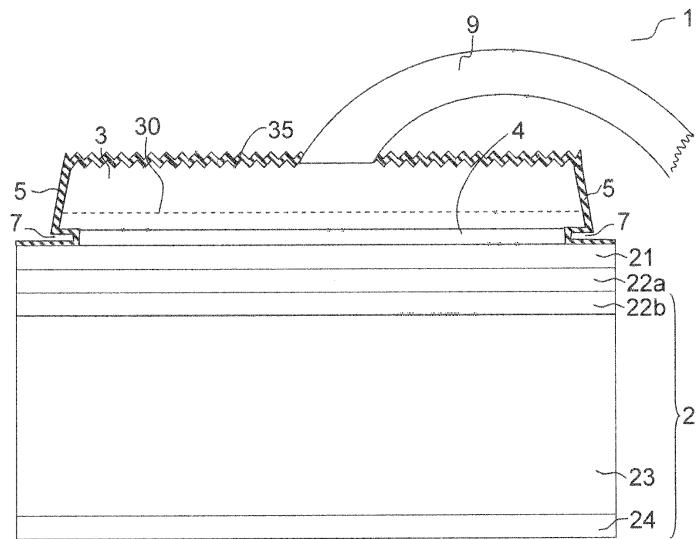

도 1a에는 광전자 반도체 소자의 한 가지 실시 예가 단면도로서 도시되어 있다. 반도체 소자(1)는 활성층(30)을 갖는 반도체 층 시퀀스(3)를 포함한다. 반도체 층 시퀀스(3)의 방사선 통과 면(35)은 반도체 층 시퀀스(3)로부터의 광 방출을 개선하기 위한 표면 주름을 보여준다.

예를 들어 반도체 층 시퀀스(3)의 활성층(30)은 반도체 소자(1)의 작동 중에 자외선, 근접 적외선 또는 가시 광선, 특히 청색 광을 방출할 목적으로 설치되었다. 반도체 층 시퀀스(3)는 GaN, InGaN, AlGaN, GaP, InGaAlP, InGaAs 또는 GaAs에 기반을 둘 수 있다.

방사선 통과 면(35)으로부터 떨어져서 마주한 상기 반도체 층 시퀀스(3)의 한 면에는 금속 미러(4)가 있다. 금속 미러(4)는 예컨대 은 미러이고, 반도체 층 시퀀스(3)와 직접 접촉한다.

또한, 반도체 소자(1)는 캐리어(2)도 포함한다. 캐리어(2)는 예를 들어 금속, 세라믹으로부터 제조되었거나 또는 규소 혹은 게르마늄으로부터 제조된 캐리어 기판(23)을 구비한다. 반도체 층 시퀀스(3)를 향하는 방향으로 캐리어 기판(23)에는 납땜 결합 층(22a, 22b)이 접한다. 상기 두 개의 납땜 결합 층(22a, 22b) 중에 적어도 하나의 납땜 결합 층이 캐리어(2)에 의해 둘러싸여서 캐리어 기판(23) 상에 제공된다. 특히 납땜 결합 층(22a)은 반도체 층 시퀀스(3)에서 형성될 수 있고/형성될 수 있거나 반도체 층 시퀀스(3)에 제공될 수 있다. 반도체 층 시퀀스(3)로부터 떨어져서 마주한 상기 캐리어 기판(23)의 한 면에는 또한 금속 층(24)이 있다. 상기 금속 층(24)을 통해서 반도체 소자(1)는 예를 들어 표면 장착 공정으로 도면에 도시되지 않은 외부 조립 캐리어에 납땜될 수 있다.

납땜 결합 층(22a)과 반도체 층 시퀀스(3) 사이에는 또한 캡슐화 중간층(21)이 있다. 상기 캡슐화 중간층(21)을 통해서는 예컨대 납땜 결합 층(22a, 22b)의 구성 성분들이 반도체 층 시퀀스(3) 내부로 이동하는 현상이 저지될 수 있다. 예를 들어 캡슐화 중간층(21)은 TiWN을 포함하거나 또는 TiWN으로 이루어진다. 금속 미러(4)와

캡슐화 중간층(21) 사이에는 또한 제 2 미러 층(6)이 있으며, 상기 제 2 미러 층은 도전성이고, 예를 들어 크롬으로부터 형성되었다.

캐리어(2) 뿐만 아니라 반도체 층 시퀀스(3)도 가로 방향으로, 바람직하게는 둘레에서 금속 미러(4) 위로 돌출한다. 다른 말로 표현하자면, 반도체 층 시퀀스(3) 및 캐리어(2)는 측면에서 금속 미러(4) 위로 돌출한다. 금속 미러(4)의 가로 제한 면들에, 반도체 층 시퀀스(3) 쪽을 향하고 있고 금속 미러(4)에 의해서 덮이지 않은 상기 제 2 미러 층(6)의 상부 면에, 선택적으로 반도체 층 시퀀스(3)의 가로 제한 면들을 형성하는 상기 반도체 층 시퀀스(3)의 측벽들(32)에 그리고 금속 미러(4)에 의해서 덮이지 않았고 캐리어 기판(23) 쪽을 향하고 있는 상기 반도체 층 시퀀스(3)의 하부 면에는 캡슐화 층(5)이 있다. 캡슐화 층(5)은 원자 층 증착 방법을 통해서 제조되고, 바람직하게는 전기 절연성이다.

상기 캡슐화 층(5)에 입사되는 방사선의 대부분을 전반사(total reflection)를 통해서 반사하기 위하여, 캡슐화 층(5)의 재료는 바람직하게 적은 굴절 지수를 갖는다. '적은 굴절 지수'란 캡슐화 층(5)의 굴절 지수 또는 평균 굴절 지수가 최고 1.7, 바람직하게는 최고 1.6이라는 것을 의미한다. 특히 캡슐화 층(5)의 평균 굴절 지수는 반도체 층 시퀀스(3)의 평균 굴절 지수보다 적어도 35 %만큼 더 작다.

반도체 소자의 구성 부품들은 개별적으로 또는 조합된 형태로 이하에 기술되는 바와 같이 형성될 수 있다. 반도체 층 시퀀스(3)의 두께는 바람직하게 3  $\mu\text{m}$ (3  $\mu\text{m}$  포함) 내지 15  $\mu\text{m}$ , 특히 4  $\mu\text{m}$ (4  $\mu\text{m}$  포함) 내지 6  $\mu\text{m}$ 이다. 금속 미러(4)는 바람직하게 100 nm(100 nm 포함) 내지 150 nm의 두께를 갖는다. 도 1에 따라 캡슐화 층(5)의 두께가 금속 미러(4) 두께의 절반보다 더 작음으로써, 결과적으로 캡슐화 층(5)에 의해서는 상기 반도체 층 시퀀스(3) 및 캐리어(2)가 금속 미러(4) 위로 가로로 돌출하는 영역에 중공 그루우브(7)가 형성된다. 이때 캡슐화 층(5)의 두께는 바람직하게 30 nm(30 nm 포함) 내지 70 nm이다.

제 2 미러 층(6)의 두께는 바람직하게 50 nm(50 nm 포함) 내지 250 nm이다. 캡슐화 중간층(21)의 두께는 예를 들어 200 nm(200 nm 포함) 내지 1.5  $\mu\text{m}$ 이다. 요약하자면, 납땜 결합 층들(22a, 22b)은 예컨대 1  $\mu\text{m}$ (1  $\mu\text{m}$  포함) 내지 6  $\mu\text{m}$ 의 두께를 갖고, 특히 Au, Zn, Ni 및/또는 In으로부터 형성되거나 또는 이들로 이루어진다. 캐리어 기판(23)은 바람직하게 50  $\mu\text{m}$ (50  $\mu\text{m}$  포함) 내지 500  $\mu\text{m}$ , 특히 75  $\mu\text{m}$ (75  $\mu\text{m}$  포함) 내지 200  $\mu\text{m}$ 의 두께를 갖는다. 예를 들어 Au 또는 Au-합금으로 이루어진 금속 접촉 층들(24)은 예컨대 50 nm(50 nm 포함) 내지 300 nm의 두께를 갖는다.

반도체 소자(1)는 다음과 같이 제조될 수 있다: 도면에 도시되지 않은 성장 기판상에서 반도체 층 시퀀스(3)가 예를 들어 에피택셜 성장된다. 또한, 상기 성장 기판으로부터 떨어져서 마주한 상기 반도체 층 시퀀스(3)의 한 측에서 금속 미러(4) 및 제 2 미러 층(6)이 예를 들어 임프린팅(imprinting) 되고, 진공 증착되거나 또는 갈바닉 전기 방법을 통해서 증착된다. 또한, 제 2 미러 층(6)에 캡슐화 중간층(21)이 제공되고, 상기 캡슐화 중간 층에서 재차 납땜 결합 층(22a)이 형성된다.

계속해서 납땜 결합 층(22b), 캐리어 기판(23) 및 금속 접촉 층(24)을 갖는 캐리어(2)가 준비된다. 도면에 도시되지 않은 성장 기판으로부터 반도체 층 시퀀스(3)를 분리하기 전에 또는 분리한 후에도 납땜 결합 층들(22a, 22b)이 서로 납땜 됨으로써, 캐리어(2)는 반도체 층 시퀀스(3)와 단단히 결합 된다. 마찬가지로 캐리어(2)도 반도체 층 시퀀스(3)에 갈바닉 전기 방법으로 제공될 수 있다.

특히 반도체 층 시퀀스(3)로부터 성장 기판을 제거한 후에는 도면에 도시되지 않은, 예를 들어 포토 레커의 형태로 형성된 마스크가 반도체 층 시퀀스(3) 상에 제공된다. 그 다음에 예컨대 에칭을 통해서 반도체 층 시퀀스(3)의 측벽들(32)이 형성되고, 상기 반도체 층 시퀀스(3)가 자신의 가로 연장부들 내에서 패턴화된다. 도면에 도시되지 않은 마스크를 제거하지 않고 바람직하게는 연이어서 다른 에칭 방법으로 금속 미러(4)가 패턴화되고, 상기 금속 미러의 가로 치수가 결정된다. 이와 같은 패턴화 공정에 의해서 금속 미러(4) 위로 돌출하는 반도체 층 시퀀스(3)의 돌출부가 형성된다. 더 상세하게 말하자면, 반도체 층 시퀀스(3)의 그리고 금속 미러(4)의 패턴화는 바람직하게 동일한 마스크를 통해서 연속하는 에칭 단계들로 이루어진다. 그 다음에 예컨대 도면에 도시되지 않은 마스크를 제거한 후에 방사선 통과 면(35)에서 패턴화가 이루어질 수 있다.

방사선 통과 면(35)에서 패턴화가 이루어지기 전에 또는 패턴화가 이루어진 후에도 원자 층 증착을 통해서 캡슐화 층(5)이 형성된다. 이때 방사선 통과 면(35)에는 바람직하게 캡슐화 층(5)이 없다. 캡슐화 층(5)은 이산화 규소 및/또는 산화알루미늄을 갖거나 이와 같은 물질로 이루어진 그리고 도면에 도시되지 않은 하나 또는 다수의 개별 층을 포함하며, 이 경우 상기 층들은 각각 바람직하게 2 nm(2 nm 포함) 내지 8 nm의 두께를 갖고, 캡슐화 층(5)의 전체 두께는 바람직하게 30 nm(30 nm 포함) 내지 70 nm이다. 예를 들면  $\text{SiO}_2$  그리고  $\text{Al}_2\text{O}_3$ 로 이루어

진 개별 층들이 교대로 배치되어 있다.

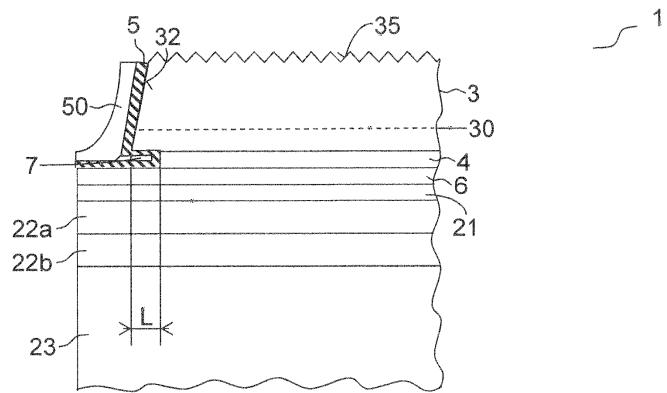

금속 미러(4) 위로 돌출하는 반도체 층 시퀀스(3)의 가로 돌출부(L)는 바람직하게 100 nm(100 nm 포함) 내지 5  $\mu\text{m}$ 이다. 바람직하게 상기 가로 돌출부(L)는 1  $\mu\text{m}$ 보다 작거나 또는 0.5  $\mu\text{m}$ 보다 작다. 이와 같이 크기가 작은 돌출부(L)는 도면에 도시되지 않은 동일한 마스크에 의해서 반도체 층 시퀀스(3)의 그리고 금속 미러(4)의 패턴화가 이루어지고, 그 결과 상기 금속 미러의 그리고 반도체 층 시퀀스(3)의 패턴화가 서로 상대적으로 정확하게 이루어짐으로써 구현된다.

또한, 캡슐화 층(5)은 바람직하게 투명하고, 예컨대 반도체 층 시퀀스(3) 내에서 발생하는 전자기 방사선을 흡수하지 않거나 또는 단지 무시할 수 있을 정도만 흡수한다. 방사선을 발생하기 위하여 활성층이 설치되면, 상기 활성층(30) 내에서 발생하는 방사선의 일부분이 캡슐화 층(5)을 손실 없이 통과하여 제 2 미러 층(6)에서 역으로, 예컨대 방사선 통과 면(35)의 방향으로 반사될 수 있다. 그럼으로써, 반도체 소자(1)로부터 방출되는 방사선의 방출 효율이 증가하게 된다.

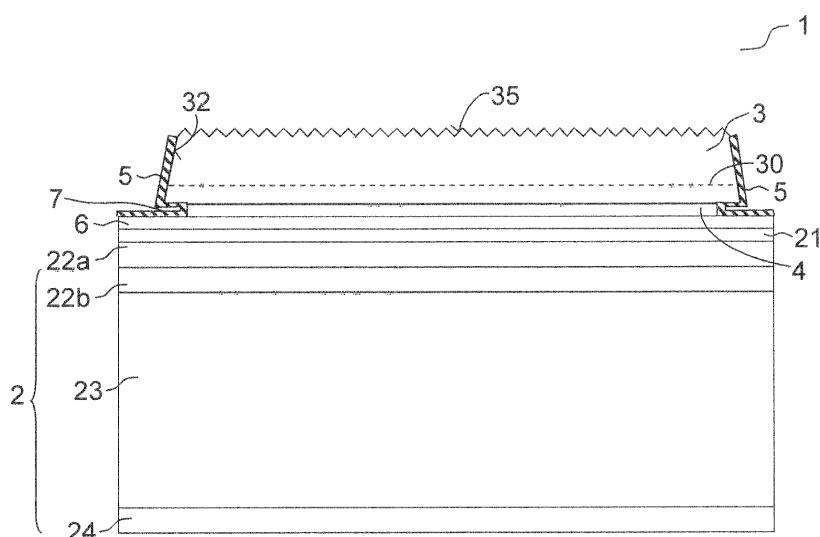

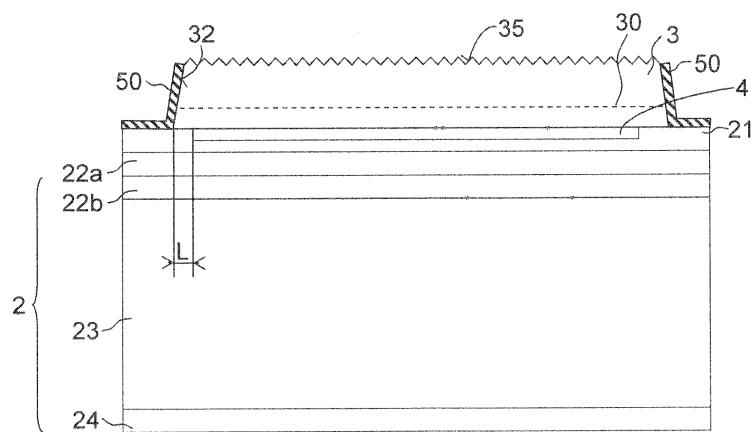

도 1b에는 캡슐화 층(5)의 상세도가 도시되어 있다. 또한, 도 1b에 따른 실시 예에서 캡슐화 층(5)에는 보호층(50)이 제공되어 있다. 보호층(50)의 두께는 예를 들어 100 nm(100 nm 포함) 내지 400 nm이다.

원자 층 중착(간략히 ALD)에 의해서 형성되는 캡슐화 층(5)과 달리 상기 보호층(50)은 예를 들어 CVD 또는 PVD를 통해서 제조된다. 캡슐화 층(5)을 제조할 때에 이용되는 방법인 ALD와 달리 CVD 또는 PVD 방법에서는 일반적인 경우에 중공 그루우브(7)를 재료로 완전히 채울 수가 없다. 그럼으로써, 반도체 층 시퀀스(3) 및 캐리어(2)가 가로로 금속 미러(4) 위로 돌출하는 영역에는 캡슐화 층(5) 및 보호층(50)에 의해서 둘러싸인 공동부가 남게 된다.

또한, ALD에 의해서 제조된 캡슐화 층(5) 및 CVD 혹은 PVD를 통해서 형성된 보호층(50)은 상기 ALD-캡슐화 층(5)의 결함 밀도가 통상적으로  $\text{mm}^2$ 당 0.1 결함보다 더 작은 반면에 CVD- 혹은 PVD-보호층(50)은  $\text{mm}^2$ 당 수백 결함의 결함 밀도를 갖는다는 점에서 서로 상이하다. 이와 같은 사실은 예를 들어 투과 전자 현미경(간략히 TEM; Transmission Electron Microscope)을 통해서 입증될 수 있다. ALD-캡슐화 층(5)의 비교적 적은 결함 밀도로 인해 에칭률(etching rate)도 CVD- 혹은 PVD-보호층(50)에 비해 줄어들었다. 특히 이와 같은 상황은 캡슐화 층(5) 및 보호층(50)이 산화알루미늄으로 이루어지거나 또는 산화알루미늄을 포함하는 경우에 해당한다. 예를 들어 결함 밀도 및/또는 에칭률을 통해서는 상기 층들(5, 50) 중에 어느 층이 어떤 방식을 통해서 형성되었는지를 확인할 수 있다.

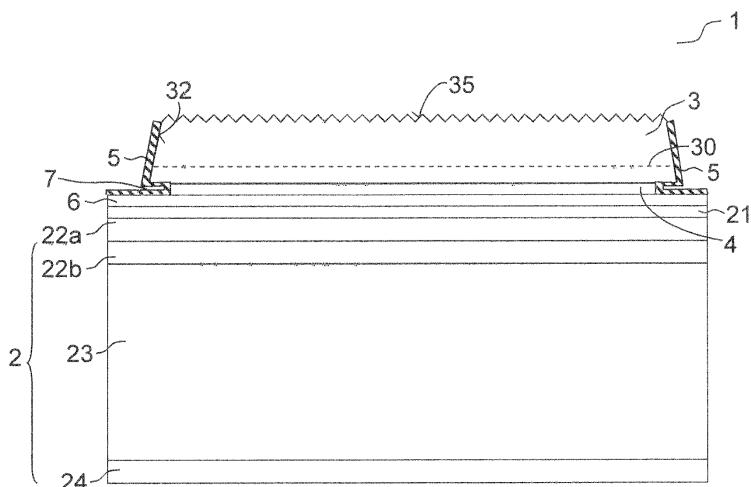

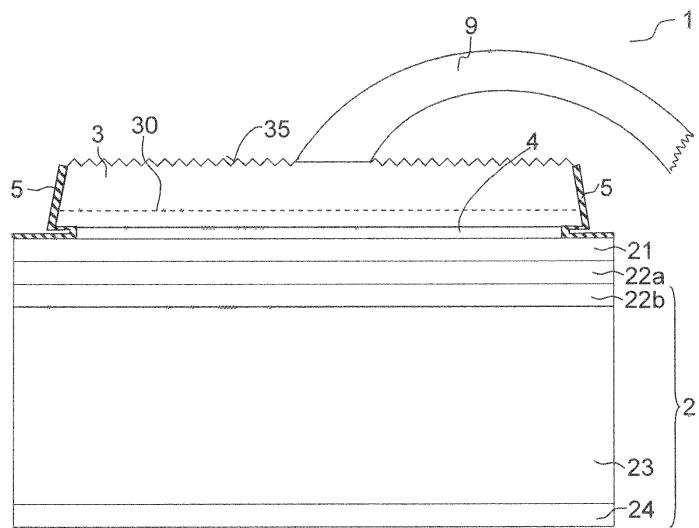

도 2에 따른 실시 예에서는 반도체 층 시퀀스(3)로부터 성장된 한 부분 층 및 제 2 미러 층(6)으로부터 성장된 상기 캡슐화 층(5)의 한 부분 층이 서로 접촉하여 심(8)을 형성할 수 있을 정도의 두께로 캡슐화 층(5)이 ALD 방식을 통해서 성장한다. 그럼으로써, 산소 및/또는 물에 대한 금속 미러(4)의 특히 효율적인 캡슐화가 보증된다.

도 3에는 반도체 소자의 한 변형 예의 단면도가 도시되어 있다. 이와 같은 종래의 구조에서는 금속 미러(4)가 가로 방향으로도 캡슐화 중간층(21)에 의해서 둘러싸여 있다. 캡슐화 중간층(21)이 예컨대 검은색 혹은 갈색의 착색 상태를 보이는 TiWN으로 이루어지면, 반도체 층 시퀀스(3) 내에서 발생하는 방사선은 상기 캡슐화 중간층(21)에서 대부분 흡수되어 반도체 소자로부터 방출되지 않는다. 반도체 층 시퀀스(3)의 가로 연장부가 수백  $\mu\text{m}$ 의 범위 안에 있고, 가로 돌출부(L)가 수  $\mu\text{m}$ 의 범위 안에 있으면, 상기 캡슐화 중간층(21)에 의해서는 활성층(30) 내에서 발생한 방사선의 방사선 비율이 수 %의 크기로 흡수된다. 도 1 또는 도 2에 따른 반도체 소자(1)의 효율은 도 3에 따른 소자에 비해 거의 상기 방사선 비율만큼 증가할 수 있다.

도 4에 따른 실시 예에 따라 방사선 통과 면(35)에는 본딩 와이어(9)가 설치되어 있다. 더 상세하게 말하자면, 반도체 소자(1)에 대한 전력 공급은 금속 접촉 층(24)을 통해서 그리고 본딩 와이어(9)를 통해서 이루어진다.

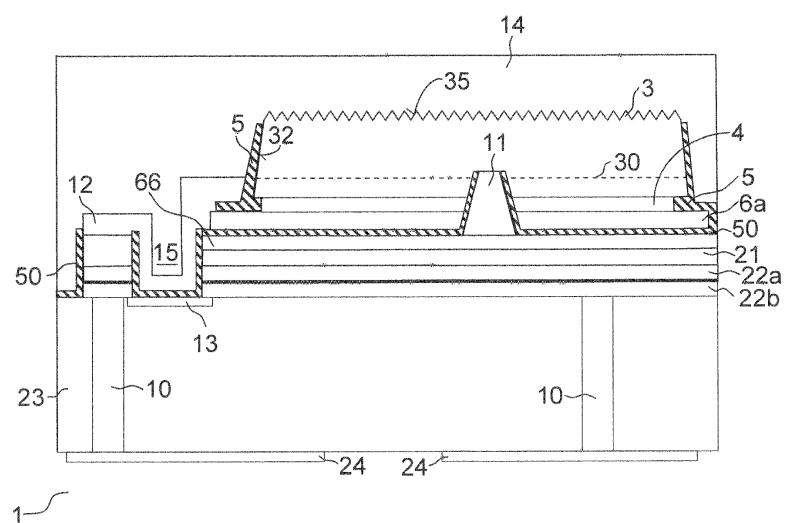

도 5에 따른 실시 예에서 반도체 소자(1)는 두 개의 금속 접촉 층(24)을 포함하며, 상기 두 개의 접촉 층은 각각 전기적인 관통 플레이트 결합부(10)를 통해서 반도체 층 시퀀스(3) 쪽을 향하고 있는 상기 캐리어 기판(23)의 한 측으로 가이드 된다. 캐리어 기판(23) 쪽을 향하고 있는 상기 반도체 층 시퀀스(3)의 한 측의 전기적인 콘택팅은 또한, 전기 브리지(12)를 통해서 이루어지며, 상기 전기 브리지는 납땜 결합 층들(22a, 22b) 안에 있는 그리고 캡슐화 중간층(21) 안에 있는 리세스(15)를 연결한다. 캐리어 기판(23)으로부터 떨어져서 마주한 상기 반도체 층 시퀀스의 한 측은 예컨대 구리로 채워진 브레이크쓰루(11)(breakthrough)를 통해서 전기적으로 접속된다. 캡슐화 층(5)은 예를 들어 도 1b 또는 도 2에 도시된 바와 같이 실현된다.

다른 모든 실시 예들에서도 마찬가지로 반도체 층 시퀀스(3)는 소켓팅(14)(socketing)에 의해서 둘러싸일 수 있다. 소켓팅(14)에는 적어도 하나의 변환 수단, 적어도 하나의 확산 수단 및/또는 적어도 하나의 필터링 수단이 첨가될 수 있다. 다른 실시 예들에서도 마찬가지로 캐리어 기판(23)에는 선택적으로 전기 기능 소자(13)가 접속될 수 있는데, 상기 전기 기능 소자는 예를 들어 정전기 방전으로부터 보호 장치로서 구현되었다.

도 6에 따라, 캡슐화 층(5)은 특히 선택적으로 존재하는 본딩 와이어(9)용 접속 영역을 제외하고 방사선 관통면(35)을 완전히 또는 거의 완전히 덮는다. 이와 같은 형상에서 캡슐화 층(5)은 반도체 층 시퀀스(3) 내에서 발생하는 방사선의 적어도 일부분을 통과시키는 재료로 이루어지거나 또는 이와 같은 재료를 포함한다. 이때 캡슐화 층(5)은 예컨대 이산화규소를 포함하거나 또는 이산화규소로 이루어지며, 이 경우 상기 이산화규소는 도핑될 수 있다. 도핑은 특히 바람직하게 최고 1000 ppm 또는 최고 100 ppm의 도펀트 농도를 갖는 알루미늄을 사용해서 이루어지며, 이 경우 ppm은 parts per million의 약자이다.

도 7에 따른 실시 예에서 캡슐화 층(5)은 오로지 중공 그루우브(7)까지만 또는 실제로 중공 그루우브(7)까지 연장된다. 도 7에 도시된 바와 달리 캡슐화 층(5)이 부분적으로 반도체 층 시퀀스(3)의 측벽들(32)까지 연장될 수도 있지만, 이 경우에는 캡슐화 층(5)이 활성층(30)에 도달하지 않거나 또는 캐리어 기판(23)으로부터 멀어지는 방향으로 활성층(30)을 초과하지 않는다. 그와 마찬가지로 중공 그루우브(7) 외부에 놓인 상기 캡슐화 층(21)의 부분들도 캡슐화 층(5)에 의해서 덮일 수 있다.

캡슐화 층(5)이 특히 상기와 같이 형성된 경우에는 상기 캡슐화 층(5)을 위해서 도전성 재료들을 사용하는 것이 가능하다. 예컨대 캡슐화 층(5)은 다음과 같은 재료들 중에 한 가지 재료로 이루어지거나 또는 다음과 같은 재료들 중에 하나 또는 다수의 재료를 포함한다: 산화인듐주석과 같은 투명한 전도성 산화물, 텉스텐과 같은 순수한 금속.

도 7에 도시된 바와 같은 캡슐화 층(5)은 상기 캡슐화 층(5)을 위한 재료가 도 6에 따른 실시 예에서와 유사하게 특히 전체 반도체 층 시퀀스(3) 상에 제공된 다음에 상기 재료가 국부적으로 제거됨으로써 형성될 수 있다.

본 발명은 실시 예들을 참조하는 상세한 설명에 의해서 제한되지 않는다. 오히려 본 발명은 각각의 새로운 특징 그리고 각각의 특징 조합을 포함하며, 상기 특징 또는 상기 특징 조합 자체가 특히청구범위 또는 실시 예에 명시적으로 기재되어 있지 않더라도 특히 각각의 특징 조합은 특히청구범위에 포함된 것으로 간주된다.

본 특허 출원서는 독일 특허 출원서 10 2009 033 686.9호를 우선권으로 주장하며, 상기 우선권 서류의 공개 내용은 인용의 방식으로 본 출원서에 수용된다.

## 도면

### 도면 1a

## 도면1b

## 도면2

## 도면3

도면4

도면5

도면6

도면7