(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11) 特許番号

特許第6489757号 (P6489757)

(45) 発行日 平成31年3月27日 (2019.3.27)

(24) 登録日 平成31年3月8日(2019.3.8)

(51) Int.Cl. F 1

HO4N 1/00 C (2006, 01)H04N 1/00 HO3K 19/173 (2006, 01)нозк 19/173 130 B41J 29/38 (2006.01) B 4 1 J 29/38  $\mathbf{Z}$

請求項の数 17 (全 27 頁)

(21) 出願番号 特願2014-79726 (P2014-79726) (22) 出願日 平成26年4月8日 (2014.4.8)

(65) 公開番号 特開2015-201766 (P2015-201766A)

(43) 公開日 平成27年11月12日 (2015.11.12) 審査請求日 平成29年4月6日 (2017.4.6) (73)特許権者 000001007 キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74)代理人 100076428

弁理士 大塚 康徳

||(74)代理人 100112508

弁理士 高柳 司郎

(74)代理人 100115071

弁理士 大塚 康弘

(74)代理人 100116894

弁理士 木村 秀二

(74) 代理人 100130409

弁理士 下山 治

|(74)代理人 100134175

弁理士 永川 行光 最終頁に続く

(54) 【発明の名称】画像処理装置、その制御方法及びプログラム

### (57)【特許請求の範囲】

## 【請求項1】

画像を読み取る読取手段と、

シートに画像を印刷する印刷手段と、を有し、

前記読取手段により読み取られた画像を前記印刷手段がシートに印刷するコピージョブと、外部の装置から入力された印刷データから生成される画像を前記印刷手段がシートに印刷する印刷ジョブとを実行可能であり、前記コピージョブの実行に必要な画像処理の一部と前記印刷ジョブの実行に必要な画像処理の一部が共通する画像処理装置において、

回路の構成を変えることのできる再構成回路と、

前記コピージョブと前記印刷ジョブのいずれかのジョブの実行が指示された後、実行が 指示された前記ジョブを実行するための処理と、前記再構成回路に構成された回路が実行 する処理に違いがあることを判定手段と、

<u>前記判定手段による判定結果に基づいて、前記ジョブを実行するために必要な画像処理</u>を行う回路を前記再構成回路にコンフィグレーションする再構成手段と、を有し、

前記再構成手段は、前記再構成回路に構成されている回路のうち、前記コピージョブと前記印刷ジョブで共通する画像処理を実行する回路をコンフィグレーションすることなく、前記コピージョブと前記印刷ジョブで共通しない画像処理を実行する回路をコンフィグレーションすることを特徴とする画像処理装置。

## 【請求項2】

前記再構成手段は、前記再構成回路の前記コピージョブと前記印刷ジョブで共通する画

像処理を実行するための回路が構成されている領域と異なる領域に前記コピージョブと前記印刷ジョブで共通しない画像処理を実行するための回路をコンフィグレーションすることを特徴とする請求項1に記載の画像処理装置。

### 【請求項3】

前記コピージョブと前記印刷ジョブで共通する画像処理とは、前記印刷手段に入力する 画像を生成するための画像処理であることを特徴とする請求項1または2に記載の画像処 理装置。

## 【請求項4】

前記共通する画像処理は、色空間変換処理、ガンマ補正処理、ハーフトーン処理の少なくとも一つを含むことを特徴とする請求項3に記載の画像処理装置。

## 【請求項5】

前記コピージョブを実行するために必要な画像処理であり、前記コピージョブと前記印刷ジョブで共通していない画像処理とは、前記読取手段に読み取られた画像から前記コピージョブと前記印刷ジョブで共通した画像処理を実行するための回路に入力される画像を生成する処理であることを特徴とする請求項1乃至4のいずれか一項に記載の画像処理装置。

### 【請求項6】

前記コピージョブを実行するために必要な画像処理であり、前記コピージョブと前記印刷ジョブで共通していない画像処理とは、少なくとも像域分離処理を含むことを特徴とする請求項 5 に記載の画像処理装置。

### 【請求項7】

前記印刷ジョブを実行するために必要な画像処理であり、前記コピージョブと前記印刷ジョブで共通していない画像処理とは、前記外部の装置から入力された画像から前記コピージョブと前記印刷ジョブで共通した画像処理を実行するための回路に入力される画像を生成する処理であることを特徴とする請求項1乃至6のいずれか一項に記載の画像処理装置。

## 【請求項8】

前記印刷ジョブを実行するために必要な画像処理であり、前記コピージョブと前記印刷 ジョブで共通していない画像処理とは、前記外部の装置から入力された画像のレンダリン グ処理を含むことを特徴とする請求項7に記載の画像処理装置。

### 【請求項9】

前記再構成回路に、複数の画像処理のそれぞれを実行するための回路をコンフィグレーションするための回路構成データを記憶する記憶手段をさらに有し、

前記再構成手段は、前記記憶手段に記憶された回路構成データに基づいて、前記コピー ジョブと前記印刷ジョブで共通していない画像処理を実行するための回路をコンフィグレ ーションすることを特徴とする請求項1乃至8のいずれか一項に記載の画像処理装置。

## 【請求項10】

前記再構成回路は回路の構成を変えることのできる領域を複数有し、前記再構成手段は 前記領域ごとに回路をコンフィグレーションすることを特徴とする請求項1乃至9のいず れか一項に記載の画像処理装置。

## 【請求項11】

前記再構成手段は、前記コピージョブと前記印刷ジョブを実行するために必要な画像処理のうち、前記コピージョブと前記印刷ジョブで共通する処理を実行する回路が前記再構成回路に構成されていない場合、前記コピージョブと前記印刷ジョブで共通する処理を実行する回路を前記再構成回路にコンフィグレーションすることを特徴とする請求項1乃至10のいずれか一項に記載の画像処理装置。

#### 【請求項12】

前記再構成手段は、前記再構成回路をコンフィグレーションする際の制約条件があるか 否かを判断する判断手段をさらに備え、

前記再構成手段は、前記判断手段によって判断された前記制約条件に従って、前記再構

20

10

30

40

成回路に画像処理を実行する回路をコンフィグレーションすることを特徴とする請求項 1 乃至 1 1 のいずれか一項に記載の画像処理装置。

#### 【請求項13】

前記制約条件は、少なくとも前記再構成回路の回路規模、書き換え回数のいずれかに関する条件であることを特徴とする請求項12に記載の画像処理装置。

## 【請求項14】

前記再構成手段は、前記再構成回路の各領域において、各領域に構成されている画像処理の処理形式に従ってコンフィグレーションする回路を決定することを特徴とする請求項13に記載の画像処理装置。

## 【請求項15】

前記処理形式は、画像データをラインごとに処理するライン処理形式と、画像データを 矩形ごとに処理する矩形処理形式を含むことを特徴とする請求項14に記載の画像処理装 置。

## 【請求項16】

画像を読み取る読取手段と、

シートに画像を印刷する印刷手段と、

回路の構成を変えることのできる再構成回路と、

## を有し、

前記読取手段により読み取られた画像を前記印刷手段がシートに印刷するコピージョブと、外部の装置から入力された印刷データから生成される画像を前記印刷手段がシートに印刷する印刷ジョブとを実行可能であり、前記コピージョブの実行に必要な画像処理の一部と前記印刷ジョブの実行に必要な画像処理の一部が共通する画像処理装置の制御方法において、

前記コピージョブと前記印刷ジョブのいずれかのジョブの実行が指示された後、実行が 指示された前記ジョブを実行するための処理と、前記再構成回路に構成された回路が実行 する処理に違いがあることを判定する判定工程と、

前記判定工程における判定結果に基づいて、前記ジョブを実行するために必要な画像処理を行う回路を前記再構成回路に<u>コンフィグレーションする再構成工程と、を有し、</u>

前記再構成工程において、前記再構成回路に構成されている回路のうち、前記コピージョブと前記印刷ジョブで共通する画像処理を実行する回路をコンフィグレーションすることなく、前記コピージョブと前記印刷ジョブで共通しない画像処理を実行する回路をコンフィグレーションすることを特徴とする画像処理装置の制御方法。

#### 【請求項17】

請求項1乃至15のいずれか一項に記載の画像処理装置としてコンピュータを機能させるための該コンピュータで読み取り可能なプログラム。

【発明の詳細な説明】

#### 【技術分野】

## [0001]

本発明は、画像処理装置、その制御方法及びプログラムに関する。

#### 【背景技術】

## [0002]

論理回路の構成を変更可能なPLD(Programmable Logic Device)やFPGA(Field Programmable Gate Array)などの再構成可能回路が良く知られている。一般的に、PLDやFPGAの論理回路の変更は、起動時に、ROM等の不揮発性メモリに格納された回路構成情報を、PLDやFPGA内部の揮発性メモリであるコンフィグレーションメモリへ書き込むことで実現される。また、コンフィグレーションメモリの情報は電源遮断時にクリアされるため、電源投入時に、再度、ROMに記憶している回路構成情報をコンフィグレーションメモリに書き込む必要がある。このように、電源が供給されている状態で、一度だけPLDやFPGAの論理回路を構成する方法を静的再構成という。これに対して、論理回路が動作中に、その

10

20

30

00

40

(4)

論理回路の構成を動的に変更できるFPGA等が開発されており、このように動的に論理回路を変更する方法を動的再構成という。

#### [0003]

また、FPGAには、FPGAのチップ全体の回路構成でなく、特定の領域の回路構成だけを書き換えることが可能なものがあり、このような書き換えを部分再構成という。特に、動作中の回路の動作を停止させずに、それ以外の他の回路構成を変更することを動的部分再構成という。動的部分再構成では、動的再構成時に、コンフィグレーションメモリを体を書き換えるのではなく、コンフィグレーションメモリの一部の領域のみを書き換えることで、FPGAの論理回路を部分的に再構成することができる。このような動的部分再構成を用いることで、例えばFPGAのある領域に、時分割で複数の論理回路を切り替えて実装できる。この結果、少ないハードウェアリソースで、用途に合わせた様々な機能を、ハードウェアによる高速の演算性能を保ったままで柔軟に実現できる。

#### [0004]

ただし、動作中に回路構成を変更できるといっても、回路構成の変更(書き換え)に要する時間は長く、その時間はコンフィグレーションメモリに書き込む論理回路構成情報のサイズに比例する。また、回路構成の変更箇所が多く、それぞれの変更箇所の回路を単独で回路の変更を行えば、それだけ変更のためのコンフィグレーション回数が必要となり、全体での回路の再構成を完了するのに要する書き換え時間が増える。特許文献1には、書き換え時間を低減するための技術として、画像処理中に次に処理する可能性の高い処理を予測し、予測した処理を実現するためのコンフィグデータを高速なコンフィギュレーションメモリに先行してロードすることが開示されている。高速なコンフィギュレーションメモリに先行ロードすることにより、画像処理中の回路構成データのロード時間を短縮でき、画像処理速度の高速化を図ることができる。

#### [0005]

また、MFP(MULTI FUNCTION PRINTER)等の画像処理装置は、ユーザーからの要求に応じた複数のジョブ(コピージョブ、プリントジョブ、SENDジョブ等)を選択可能である。各処理に応じた画像処理は、ハードウェア又はソフトウェアにより実現される。近年のMFPはユーザーからの機能要望へ対応するために、多様なに対応した大規模な画像処理用ハードウェアを搭載しており、さまざまなジョブ内をに応じた細かな設定を受け付けて多様な機能を実現することが可能である。しかしながら、多様なジョブの内容に応じて画像処理用ハードウェアの機能拡張による画像処理用のドウェアのコストアップに繋がっている。それだけでなく、多様なジョブ内容に応したでいる。そのため、ジョブの実行処理が開始されるまでの時間が増大している。したがって、MFPの画像処理装置に対して、再構成可能な回路を用い、多様なジョブ内容に対って、MFPの画像処理装置に対して、再構成可能な回路を用い、多様なジョブにのみ対応する機能を再構成可能な回路で実現する必要がある。

【先行技術文献】

【特許文献】

[0006]

【特許文献1】特開2012-234337号公報

【発明の概要】

【発明が解決しようとする課題】

## [0007]

しかしながら、上記従来技術には以下に記載する問題がある。例えば、上記従来技術における再構成技術を画像処理装置の画像処理部に適用した場合、動作中に回路構成を変更できるといっても、変更する処理回路部は、その処理回路部に接続されている周辺回路とのインターフェースが一致していなければならない。特に、インターフェースにおけるデータの処理方式が一致していなければならない。例えば、回路構成の書き換えを行いたい処理回路部のみを変更して、周辺回路とのデータの処理方式が一致していなければ、書き

10

20

30

40

換えを行った処理回路部は正常に動作することができない。

#### [0008]

書き換えを行う処理回路部のデータの処理単位が矩形状のデータを取り扱う矩形処理である場合を考える。当然、その処理回路部と接続されている周辺回路のデータの単位も同じ矩形データを取り扱わなければならない。例えば、書き換えを行う処理回路部が、ライン状のデータを取り扱うライン処理になった場合は、その処理回路部と接続されている周辺回路とのデータの処理方式が異なり、処理データの受け渡しが一致しなくなる。そのため、書き換えを行う回路に対して、変更を行う必要な範囲を判断して再構成を行なわなければ、再構成した回路を正しく実行できないという課題がある。

#### [0009]

さらに、回路構成の変更(書き換え)に要する時間に対しても、書き換えに掛かる実行時間が長くなれば、それだけ画像処理装置で実行するジョブを完了させるまでの時間が長くなってしまう課題がある。回路構成の変更に掛かる時間は、再構成可能な回路におけるコンフィギュレーションメモリに書き込むコンフィグデータのサイズに比例する。また、回路構成の変更箇所が多く、それぞれの変更箇所の回路を単独で回路の変更を行えば、それだけ変更のためのコンフィグレーション回数が必要となり、全体での回路の再構成を完了するのに要する書き換え時間が増える。従来技術におけるコンフィグデータの書き換え時間を高速化する方法では、先行してコンフィグデータをロードしても、処理回路の書き換え回数や、コンフィグデータのサイズが大きければ、全体に掛かる書き換え時間を短縮することはできない。

#### [0010]

本発明は、上述の問題に鑑みて成されたものであり、部分再構成が可能な再構成部において、新たに書き換えた機能ブロックが書き換えていない部分の他の機能ブロックと連携して動作可能であるとともに、当該再構成に掛かる書き換え時間を短縮する仕組みを提供することを目的とする。

【課題を解決するための手段】

## [0011]

本発明は、画像を読み取る読取手段と、シートに画像を印刷する印刷手段と、を有し、前記読取手段により読み取られた画像を前記印刷手段がシートに印刷するコピージョブと、外部の装置から入力された印刷データから生成される画像を前記印刷手段がシートに印刷する印刷ジョブとを実行可能であり、前記コピージョブの実行に必要な画像処理の一部と前記印刷ジョブの実行に必要な画像処理の一部が共通する画像処理装置において、回路の構成を変えることのできる再構成回路と、前記コピージョブと前記印刷ジョブのいずれかのジョブの実行が指示された後、実行が指示された前記ジョブを実行するための処理と、前記再構成回路に構成された回路が実行する処理に違いがあることを判定手段と、前記判定手段による判定結果に基づいて、前記ジョブを実行するために必要な画像処理を行う回路を前記再構成回路にコンフィグレーションする再構成手段と、を有し、前記再構成手段は、前記再構成回路に構成されている回路のうち、前記コピージョブと前記印刷ジョブで共通しない画像処理を実行する回路をコンフィグレーションすることなく、前記コピージョブと前記印刷ジョブで共通しない画像処理を実行する回路をコンフィグレーションすることを特徴とする。

#### 【発明の効果】

## [0012]

本発明によれば、部分再構成が可能な再構成部において、新たに書き換えた機能ブロックが書き換えていない部分の他の機能ブロックと連携して動作可能であるとともに、当該再構成に掛かる書き換え時間を短縮することができる。

### 【図面の簡単な説明】

### [0013]

【図1】第1の実施形態に係る画像処理装置の構成の一例を示すプロック図。

【図2】第1の実施形態に係る画像処理装置のユーザーからのジョブを受け付ける操作部

10

20

30

40

を表す図。

- 【図3】第1の実施形態に係る画像処理装置で受け付けるジョブと、対応する処理機能との関係を説明する図。

- 【図4】第1の実施形態に係る画像処理装置の設定変更時における画像処理部の再構成制御を表すフローチャート。

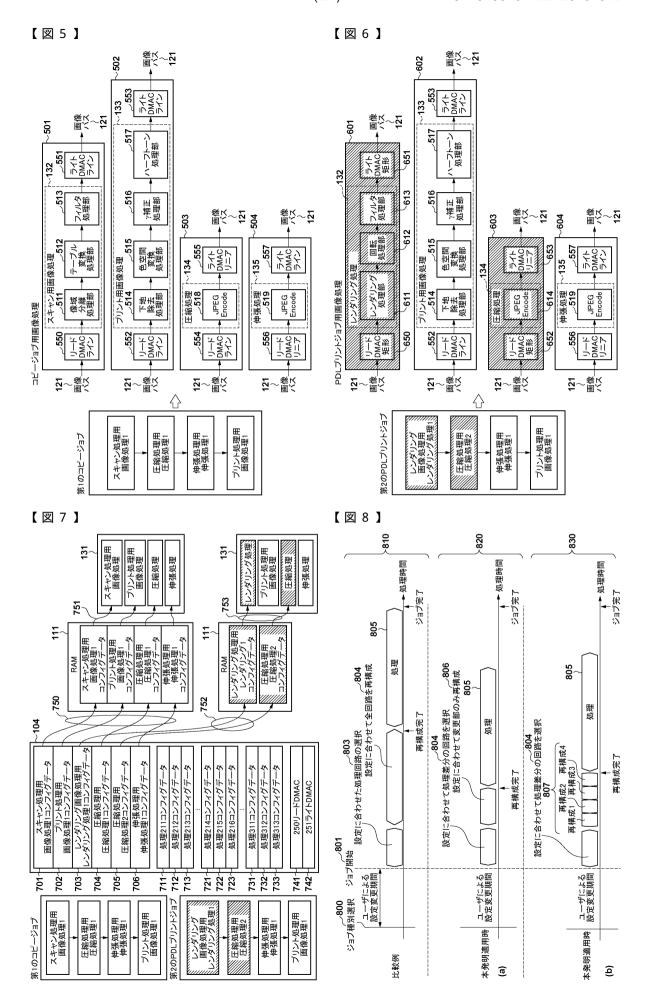

- 【図5】第1の実施形態に係る画像処理装置の機能と、再構成部に構成される画像処理機能を説明する図。

- 【図 6 】第 1 の実施形態に係る画像処理装置の機能と、再構成部に構成される画像処理機能を説明する図。

- 【図7】第1の実施形態に係る画像処理装置におけるコンフィグデータの遷移を説明する図。

- 【図8】第1の実施形態に係る本発明適用時のジョブ実行までの時間短縮効果を表すタイミングチャート。

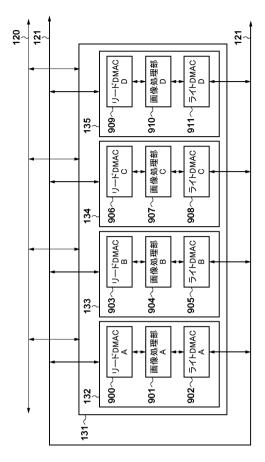

- 【図9】第2の実施形態に係る再構成部に構成される画像処理構成を表すブロック図。

- 【図10】第2の実施形態に係る画像処理装置で受け付けるジョブと、それに対応する処理機能の関係を説明する図。

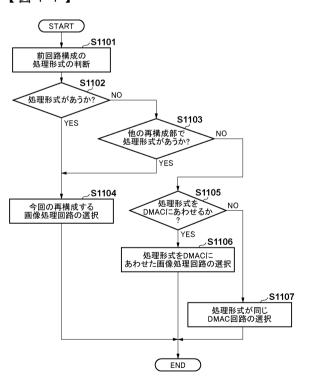

- 【図11】第2の実施形態に係る画像処理装置の設定変更時における画像処理部の再構成制御を表すフローチャート。

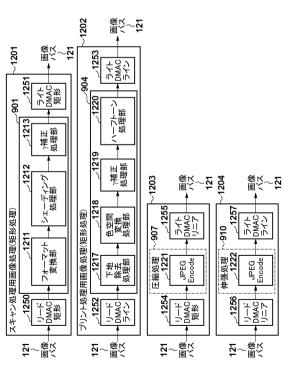

- 【図12】第2の実施形態に係る画像処理装置の機能と再構成部に構成される画像処理機能を説明する図。

- 【図13】第2の実施形態に係る画像処理装置の機能と、再構成部に構成される画像処理 機能を説明する図。

- 【図14】第3の実施形態に係る画像処理装置の設定変更時における画像処理部の再構成制御を表すフローチャート。

- 【図15】第3の実施形態に係る画像処理装置の機能と、再構成部に構成される画像処理 部の構成例を説明する図。

- 【図16】第4の実施形態に係る画像処理装置の設定変更時における画像処理部の再構成制御を表すフローチャート。

【発明を実施するための形態】

[0014]

以下、添付図面を参照して本発明の実施形態を詳しく説明する。なお、以下の実施形態は特許請求の範囲に係る本発明を限定するものでなく、また本実施形態で説明されている特徴の組み合わせの全てが本発明の解決手段に必須のものとは限らない。

[0015]

<第1の実施形態>

<画像処理装置の構成>

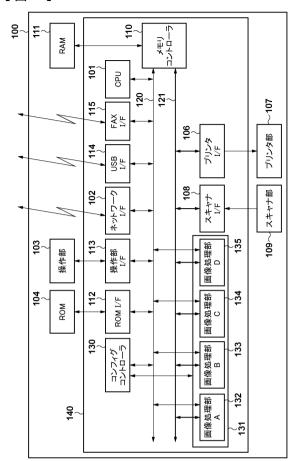

以下では、図1乃至図8を参照して、本発明の第1の実施形態について説明する。まず、図1を参照して、本発明の実施形態に関わる画像処理装置の装置構成を説明するブロック図である。本実施形態において、画像処理装置100は、スキャナ部やプリンタ部を有する複合機(多機能処理装置)の場合で説明する。

[0016]

画像処理装置100は、画像処理装置100を使用するユーザーが各種の操作を行うための操作部103と、原稿の画像情報を読み取るスキャナ部109と、画像データに基づいて用紙に画像を印刷するプリンタ部107とを有する。スキャナ部109は、スキャナ部109を制御するCPU(不図示)や原稿の読取を行うための照明ランプや走査ミラー(いずれも不図示)などを有する。プリンタ部107は、当該プリンタ部107の制御を行うCPU(不図示)や、画像の形成(印刷)や定着を行うための感光体ドラムや定着器(いずれも不図示)等を有する。操作部103は、節電キー(不図示)を持ち、節電キーの押下により、省電力状態への移行、復帰を行う。

[0017]

10

20

30

40

10

20

30

40

50

また、画像処理装置100は、画像処理装置100の制御を行うコントローラとして、動的再構成部を備えるFPGA140を有する。この例では、FPGA140が、画像処理装置100の動作を統括的に制御するCPU101を備える。このCPU101が、FPGA140や再構成を制御するコンフィグコントローラ130等を制御するためのプログラムを実行する。なお、FPGA140がCPU101を備えていることはあくまで一例にすぎず、FPGA140の外部にCPUを設けてもよい。

#### [0018]

また、画像処理装置100は、CPU101が実行するブートプログラム、及び、FPGA140をコンフィグレーションする為の論理回路構成情報が格納されているROM(第1記憶手段)104を有する。また、画像処理装置100は、CPU101が動作するためのシステムワークメモリであり、かつ画像データを一時記憶するための画像メモリでもあるRAM(第2記憶手段)111を有する。また、RAM111は、ROM104に格納された論理回路構成情報を複製し格納して高速に読み出すためのメモリでもある。

## [0019]

FPGA140は、CPU101、ネットワークI/F102、プリンタI/F106、スキャナI/F108、メモリコントローラ110、ROMI/F112、操作部I/F113、USBI/F114、FAXI/F115、コンフィグコントローラ130、及び動的な再構成部(再構成回路)131を備える。再構成部131は、再構成が可能な高建回路で構成された回路群であり、動的に再構成が可能かつ部分的な再構成書が可能な回路群である。すなわち、再構成部131の一部に再構成された回路が動作している間に、その回路が占める部分とは重ならない別の部分に別の回路を再構成することができる。再構成部131には、各種画像処理を行うための論理回路が部分的に再構成できる画像処理部A132、画像処理部B133、画像処理部C134、画像処理部D135を有する。なお、本実施形態では再構成部131に構成される画像処理部の数が4つの場合の形態を示しているが、再構成部131に構成される画像処理部の数が4つの場合の形態を示しているが、再構成部131に構成される画像処理部は複数個あり、個数は4つに限定されるものではない。コンフィグコントローラ130は、再構成部131の回路構成(コンフィグレーション)を制御する。

#### [0020]

スキャナ I / F 1 0 8 は、スキャナ部 1 0 9 から画像データが入力される。プリンタ I / F 1 0 6 は、プリンタへ画像データを出力する。再構成部 1 3 1、及びスキャナ I / F 1 0 8、プリンタ I / F 1 0 6 は、処理される画像データを転送するための画像バス 1 2 1 に接続される。

#### [0021]

てPU101は、画像処理装置100の動作を統括的に制御し、ネットワークI/F(ネットワークインターフェース)102を介し、ネットワーク上の汎用コンピュータ(不図示)と通信(送受信)を行う。また、CPU101は、USBI/F(USBインターフェース)114を介し、画像処理装置100と接続された汎用コンピュータ(不図示)と通信(送受信)を行う。また、CPU101は、FAXI/F(ファクシミリインターフェース)115を介し、公衆回線網と接続し、他の画像処理装置(不図示)やファクシミリ装置と通信(送受信)を行う。FAXI/F115には、公衆回線網からの呼出信号(CI信号:Call Indicator)を検知するCI検知回路(不図示)がある。ROMI/F112は、CPU101が実行するブートプログラム、及び、再構成部131をコンフィグレーションするための論理回路構成情報(コンフィグレーションデータ)が格納されているROM104への書き込み、読み出し動作を制御する。

### [0022]

また、FPGA140は、CPU101、ネットワークI/F102、操作部103、 ROMI/F112、コンフィグコントローラ130、再構成部131を相互に接続する システムバス120を有する。CPU101は、再構成部131内にコンフィギュレーションされた各画像処理部(132、133、134、135)と、スキャナI/F108 、プリンタI/F106のパラメータ設定を、システムバス120を介して行う。RAM

10

20

30

40

50

1 1 1 は、 C P U 1 0 1 が動作するためのシステムワークメモリであり、かつ画像データを一時記憶するための画像メモリでもあり、かつ R O M 1 0 4 に格納された論理回路構成情報を複製し格納して高速に読み出すためのメモリでもある。メモリコントローラ 1 1 0 は、 R A M 1 1 1 への書き込み、読み出し動作を制御する。メモリコントローラ 1 1 0 は、システムバス 1 2 0 及び画像バス 1 2 1 に接続され、画像バス 1 2 1 に接続されたバスマスタの R A M 1 1 1 アクセスとを、排他的に切り替える。

## [0023]

< 操作部 >

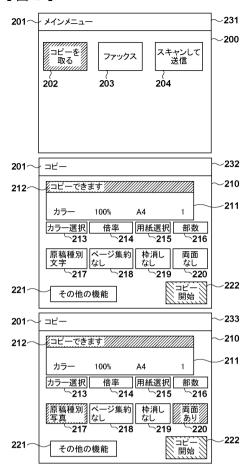

次に、図2を参照して、本実施形態に係る画像処理装置100の操作部103における表示項目及びユーザーによる設定項目変更に伴う表示項目の遷移について説明する。本実施形態では、操作部103は、液晶画面及びタッチパネルを用いて構成される。本発明はこれに限定されず、当然、操作部103はその他の代替構成が適用されていてもよい。

[0024]

図2の231は、画像処理装置100の電源投入後、或いは省電力のためのスリープ状態から、ユーザーによる復帰操作が行われたときに操作部103に表示されるUI(ユーザーインターフェース)画面を示す。通常、電源投入後又はスリープ復帰後にはメインメニュー画面200には、現在のメニュー階層をユーザーに示すための階層表示部201が表示される。また、メインメニュー画面200には画像処理装置100が実行することのできるジョブを選択するための、ジョブ選択アイコン202~204はそれぞれ、コピージョブ、ファックスジョブ、SENDジョブを表す。なお、画像処理装置100が処理することのできるジョブは、231に示す例に限定されるわけではない。

[0025]

図2の232は、メインメニュー画面200において、ユーザーがコピージョブのジョブ選択アイコン202を選択した後に表示される、コピー設定画面210を示す。コピー設定画面210には、現在の基本的な設定値を一覧で表示する設定値表示部211が表示される。設定値表示部211には、画像処理装置100が、現在、ジョブを開始することが可能かどうかをユーザーに通知する状態通知部212が表示される。また、設定値表示部211には、基本的な設定値として、原稿をカラー又はモノクロで読み取るかどうかや、倍率、用紙サイズ、コピーを出力する部数などが一覧で表示される。コピー設定画面210には、よく使用される各種設定値を変更するための、設定変更アイコン213~220が表示される。当該アイコンには、原稿読み取りカラー選択アイコン213、倍率を変更する倍率アイコン214、用紙種類を変更する用紙選択アイコン215、及び部数を変更する部数アイコン216が含まれる。

[0026]

また、コピー設定画面 2 1 0 には、原稿の種類を写真のみか、写真と文字が含まれるか、文字のみかを設定する原稿種別設定アイコンが表示される。また、コピー設定画面 2 1 0 には、スキャナ部 1 0 9 で読み取った複数の原稿を 1 ページにまとめて出力する設定を行うページ集約設定アイコンが表示される。また、コピー設定画面 2 1 0 には、原稿の余白に含まれる不要な領域を削除する枠けし設定アイコン 3 1 9 が表示される。また、コピー設定画面 2 1 0 には、プリンタ部 1 0 7 で画像を紙の裏と表の両方に印字するかどうかを切り替える両面設定アイコン 2 2 0 が含まれる。また、コピー設定画面 2 1 0 には、画面内に表示しきれないその他の設定項目を変更するためのその他の機能設定アイコン 2 2 1 が表示される。また、画像処理装置 1 0 0 に対してコピー動作開始を<u>指示</u>するコピー開始アイコン 2 2 2 2 が表示される。

[0027]

なお、本実施形態において、コピージョブの設定項目及び、コピー設定画面 2 1 0 に表示される設定変更アイコン 2 1 3 ~ 2 2 1 は、 2 3 2 に限定されるわけではない。 2 3 2 に示すように、メインメニュー画面 2 0 0 においてコピージョブ選択アイコン 2 0 2 が選

択された直後には、コピージョブのデフォルト設定として、最もよく使われる設定値がすでに設定されている。なお、ここで示すデフォルト設定値は232に限定されるわけではない。

#### [0028]

図2の233は、232のコピー設定画面210において、ユーザーによる各設定変更後の操作部103に表示される画面を示す。233の例では、倍率が80%に、原稿種別が写真に、両面印刷がありにそれぞれ設定変更されている。設定変更された設定変更アイコン214、217、220は、設定値が変わっていることをユーザーに通知するために、アイコンの表示色等が変更される。この状態において、コピー開始アイコン222を選択することにより、ユーザーによって設定された値に基づいて、画像処理装置100はコピージョブを開始する。

#### [0029]

本実施形態においては、231においてコピージョブ選択アイコン202が選択されると、コピージョブのデフォルト設定の画像処理機能である、図2の201の構成が、再構成部131へ構成される。すなわち、ROM104に格納された201の画像処理機能の構成を実現するためのコンフィグデータが適宜、コンフィグコントローラ130によって再構成部131へ転送され、コンフィグレーション(構成)される。なお、コンフィグデータはROM104から直接読み出すのではなく、RAM111へ事前に複製したものを読み出してもよい。

## [0030]

図2の233で、コピージョブの処理が実行された後、ネットワークよりPDLプリント処理のジョブが画像処理装置100へ要求された場合には、即時に、画像処理部132に構成されていたスキャン用画像処理が、レンダリング用画像処理に再構成される。その他にも、コピージョブに限らず、画像処理装置100が受け付けるジョブの実行設定が変更されると、随時、対応した図示しない画像処理部が再構成部131へ再構成される。ジョブの処理内容の変更による再構成は、前に受け付けたジョブの処理内容の構成と変更がない部分については、再構成部131の各画像処理構成部の回路構成はそのまま保持されている。

## [0031]

## <ジョブに対する処理関係>

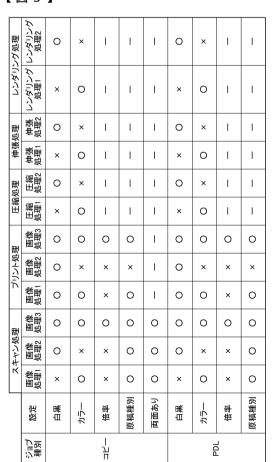

次に、図3を参照して、画像処理装置100が操作部103で受け付けた各種ジョブと、それに対応する再構成部131で実行する処理の関係について説明する。図3に示す各種ジョブと設定は、図2における操作部103で設定されたジョブの種類とジョブの設定に対応する。各ジョブに対応できる処理群(機能ブロック)を大きく、スキャン処理、プリント処理、圧縮処理、伸張処理と分けている。当然、それ以外にも処理はあり、同様に各設定により再構成を行う処理回路が用意される。

## [0032]

図3に示した各処理群に対して、さらに、設定により対応できる処理が分かれる。スキャン処理には、スキャン処理用の画像処理1、画像処理2、画像処理3の3つの処理構成が用意される。図3に示す丸で示した処理が、選択されたジョブ内容に対応できる処理にあたる。

## [0033]

図2で選択された例では、コピージョブを最初に受付けたときに、図3に示すジョブ種別内にあるコピー処理に対応する各機能が再構成部131で選択されうる処理群になる。次に、コピージョブのうち、コピー設定画像210で設定される各設定に従って、図3に示す設定の項目に対応する処理群が選択される。例えば、コピー設定画面210でのカラー選択213が操作された場合は、図3に示すカラーの設定項目に対応し、当該カラーの設定項目に対応できる処理群(丸)が再構成部131で選択可能な処理構成となる。なお、図3に示す表の内容を定義したテーブルがROM104等に予め記憶されていることが望ましい。つまり、画像処理装置100は、操作部103を介して入力された選択や設定

10

20

30

40

10

20

30

40

50

に応じて、ROM 1 0 4 に格納された上記テーブルを参照し、さらには後述する制御に従って、再構成する機能ブロックを決定することができる。

### [0034]

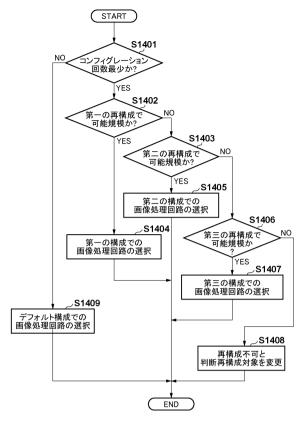

< 再構成制御シーケンス >

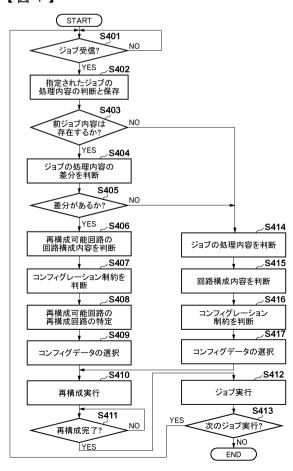

次に、図4を参照して、操作部103で受け付けたジョブに応じて、再構成部131の再構成を行う処理手順について説明する。以下で説明する処理は、CPU101がROM104に格納された制御プログラムをRAM111で実行することによって実現される。

## [0035]

S401で、CPU101は、受付手段として機能し、操作部103においてジョブの受け付けがあったか否かを判断する。ジョブを受け付けた場合はS402へ移行する。S402で、CPU101は、S401で指定されたジョブの処理内容をRAM111に記憶し、且つ、そのジョブで要求されている処理内容を判断する。例えば、コピージョブ選択アイコン202が選択された場合は、CPU101は、コピー処理に必要なスキャン画像処理、及びプリント画像処理の各処理とその各処理に必要な設定パラメータを判断する

#### [0036]

次に、S403で、CPU101は、受け付けたジョブの前に操作部103から受け付けたジョブが存在するか否かを判断する。前のジョブの受け付けが存在するか否かの判断は、CPU101が、RAM111に記憶されている前のジョブの内容を確認することで実現する。CPU101が RAM111に記憶されている前のジョブの内容を確認することでスして、前ジョブのデータが存在すれば、S404に移行する。前ジョブのデータが記憶されていなければ、電源投入後又はスリープ復帰後の最初に受けたジョブであると判断し、S414に移行する。

#### [0037]

S404で、CPU101は、前のジョブの処理内容と現在受け付けたジョブの処理内容との差分を判断する。前のジョブから、どの処理が変更になったかをCPU101が判断し、変更、追加、削除された処理内容を抽出する。続いて、S405で、CPU101は、S404の判断結果から変更になった処理内容があるか否かを判断する。変更になった処理内容がある場合にはS406に移行し、変更差分がない場合には同じジョブの処理内容と判断し、S414に移行する。

### [0038]

S406で、CPU101は、前述のジョブの差分処理の内容から画像処理構成部132、133、134、135で再構成を行う回路構成を特定する。CPU101は、ジョブの差分となる処理に対応する回路構成を判断する。変更に必要な回路構成を判断した後、S407で、CPU101は、再構成を行う上での制約条件があるか否かを判断する。例えば、ジョブ間の画像処理装置100の処理パフォーマンスを重視し、再構成を行う回路への再構成に掛かる時間を最小限にする場合、回路構成の書き換え回数を最小限にする。或いは、書き換え時間を最小限にすることが選択される。

## [0039]

S408で、CPU101は、S407で判断した制約条件に従って、再構成を行うための回路構成を特定する。CPU101は、ジョブを実行する上で必要となる回路構成であり、且つ、再構成を行う上での上記制約条件を満たす回路構成を決定する。続いて、S409で、コンフィグコントローラ130は、ROM104又はRAM111等に予め記憶しているコンフィグデータから、再構成すべき回路構成に従って、細かい処理単位で加コンフィグデータを複数選択することで1つの再構成を実行してもよい。或いは、より再構成を行う処理単位を大きく設定し、コンフィグデータの数をより少なく構成して1つの再構成を実行してもよい。つまり、再構成を行うモジュール単位を機能ブロックに相当する1つのモジュールとしてもよいし、機能ブロックを分割した単位のモジュールとしてもよい。この再構成を行うための、コンフィグデータの選択は、上記S407及びS40

8における制約条件の中に含まれる。

### [0040]

次に、S410で、コンフィグコントローラ130は、S409で選択したコンフィグデータを用いて、再構成部131を再構成する。再構成は、コンフィグデータに従って、再構成部131の各画像処理構成部(132,133、134、135)の回路を再度、書き換えることで実現する。再構成部131への再構成が完了すると、S411で、コンフィグコントローラ130は、再構成完了の割り込み通知を行う。S412で、CPU101は、S411の再構成完了の割り込み通知を受けて、受け付けたジョブを実行する。ジョブ実行後は、S413で、CPU101は、次のジョブの受け付け判断を行い、次のジョブの受け付けが発生すると、S401に移行して、ジョブ処理を行う。

## [0041]

一方、S403で前のジョブの内容が記憶されていないと判断するか、又は、S405で差分がないと判断するとS414に移行する。S414で、CPU101は、ジョブの処理内容を判断し、ジョブを実行するために必要な処理を全て選択する。続いて、S415で、CPU101は、S414で選択した処理内容に従って、画像処理構成部(132、133、134、135)で構成する回路構成を特定する。S416で、CPU101は、必要な回路構成を判断した後、構成を行う上での制約条件があるか否かを判断する。続いて、S417で、コンフィグコントローラ130は、ROM104又はRAM111等に予め記憶されているコンフィグデータから、再構成すべき回路構成に対応するコンフィグデータを抽出する。その後、S410に移行し、再構成を実行する。以降の処理は、上述した内容と同様であるため説明を省略する。

#### [0042]

<再構成部に構成される画像処理回路の構成例>

次に、図5及び図6を参照して、本実施形態にかかる画像処理装置100に係るジョブ内容に応じて切り替わる再構成部131に構成される画像処理機能(機能ブロック)とコンフィグデータとの関係について説明する。画像処理装置100は、スキャナ部109で読み取られた原稿を複写する機能(コピージョブ)、外部のプリンタドライバから送付された印刷データを印刷する機能(PDLプリントジョブ)を有する。また、FAXI/F115より受信したFAXデータを印刷する機能(FAXジョブ)を有する。また、スキャナ部109で読み取られた原稿を画像データとしてネットワークI/F102を介して外部の汎用コンピュータへ送信するSENDジョブを有する。動的再構成技術を適用した画像処理システムの場合、ユーザーにより選択された機能及び変更された設定項目に応じて必要な画像処理機能を再構成部131に構成して実際の処理を行う。

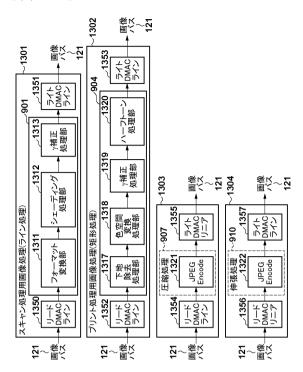

### [0043]

図5は、第1のジョブを受け付けて、ジョブを処理するために再構成部131に構成される画像処理機能の状態を示す。図5では、第1のジョブとしてコピージョブを操作部103から受け付けた場合を示す。コピージョブを受け付けた場合の再構成部131で行う処理内容としては、原稿を読み取った際の処理としてスキャン用の画像処理と、印刷出力するための画像処理としてプリント用の画像処理とが必要になる。また、スキャン用画像処理を行った画像データに対して圧縮処理(デコード処理)と、プリント用画像処理を実行する前に圧縮データを伸張する伸張処理(エンコード処理)とが必要になる。

## [0044]

コピージョブとしては、スキャナ部109で読み取った原稿の画像データをスキャンI/F108を介して画像バス121からRAM111へ格納する。続いて、リードダイレクトアクセスメモリコントローラ(DMAC:Direct Access Memory Controller)550によって、RAM111に格納された画像データは、画像バス121を介して読み出される。読み出された画像データには、スキャン用の画像処理が行われ、その処理結果の画像データがRAM111に対してライトDMAC551によって書き戻される。上記処理内容を実現する画像処理機能が、図5の501に示す回路構成に相当する。ここで、リードDMAC550、ライトDMAC551、スキャン用

10

20

30

40

の画像処理のデータ処理形式は、全てライン処理になる。

## [0045]

次に、リードDMAC554によって、RAM111に格納されたスキャン用の画像処理を行った画像データを読み出し、圧縮処理を行う。圧縮処理が行われたデータは、ライン画像のデータとは異なり圧縮した連続データの形式になる。ここでは、この連続したデータの形式をリニア処理と表現する。ライトDMAC555は、圧縮処理を行ったリニア処理データをRAM111に書き戻す。上記処理内容を実現する画像処理機能が、図5の503に示す回路構成に相当する。

### [0046]

次に、リードDMAC556によって、RAM111に格納された圧縮データが読み出され、伸張処理が行われる。伸張処理が行われたデータは、ライン状の画像のデータとして出力され、ライン処理形式になる。ライトDMAC557は、伸張処理を行ったリニア処理データをRAM111に書き戻す。上記処理内容を実現する画像処理機能が、図5の504に示す回路構成に相当する。

#### [0047]

次に、リードDMAC552によって、RAM111に格納されたライン処理の画像データは、画像バス121を介して読み出される。読み出された画像データに対してプリント用の画像処理が行われ、その処理結果の画像データが、RAM111にライトDMAC553によって書き戻される。最後に、RAM111に格納された画像データは、画像バス121を介してプリンタIF106によって、プリンタ部107に出力される。上記処理内容を実現する画像処理機能が、図5の502に示す回路構成に相当する。

#### [0048]

各画像処理構成部132、133、134、135は、このリードDMAC、ライトDMACと、各画像データをジョブ内容に従って画像処理を行う処理機能を有する。図5の例では、第1のジョブを受けて画像処理構成部132は、リードDMAC550、ライトDMAC551、及びスキャン用画像処理の処理回路を構成する。画像処理構成部133は、リードDMAC552、ライトDMAC553、及びプリント用画像処理の処理回路を構成する。画像処理構成部134は、リードDMAC554、ライトDMAC555、及び圧縮処理の処理回路518を構成する。画像処理構成部135は、前記リードDMAC556、ライトDMAC557、伸張処理の処理回路519を構成する。

### [0049]

スキャン用画像処理は、像域分離処理部511、テーブル変換処理部512、及びフィルタ処理部513を含む。プリント用画像処理は、下地除去処理部514、色空間変換処理部515、補正処理部516、及びハーフトーン処理部517を含む。像域分離処理部511は、入力画像から文字部を検出することにより、像域を判定し、その後の画像型に利用する像域信号を生成する。テーブル変換処理部512は、読み取った輝度データである画像データを濃度データに変換するために、テーブル変換を行う。フィルタ処理部513は、例えばエッジ強調などの目的に従ったデジタル空間フィルタで演算処理を行う。下地除去処理部514は、背景に薄い色がある原稿を読み取った画像データが送られてきた場合に背景色を除去する処理を行う。色空間変換処理部515は、RGBデータを画像処理装置の出力特性に合わせてCMYK変換を行う。補正処理部516では、画像で一タの濃度変換を行う。ハーフトーン処理部517は、入力画像データを所定の閾値と比較することにより、N値化を行い、その際の入力画像データと閾値との差分を以降にN値化処理する周囲画素に対して拡散する。

## [0050]

以上の画像処理が終了した画像データは、画像バス121を介して、プリンタェ/F106に転送され、プリンタ部107から出力される。上述したフローは一例であり、他の画像処理機能を再構成部131に構成して処理を実施することも可能である。

## [0051]

50

10

20

30

(13)

画像処理装置100が受ける第2のジョブとして、PDLプリント処理を受け付けた場合について説明する。第2のジョブは、第1のジョブを再構成部131で処理を実行した後、操作部103より受け付けた次のジョブになる。図6は、第2のジョブを処理するために、再構成部131に構成される画像処理機能の状態を示す。

### [0052]

PDLプリント処理を受け付けた場合の再構成部131で行う処理内容としては、PDL用のレンダリング画像処理と、印刷出力するための画像処理としてプリント用の画像処理とが必要になる。また、PDL用のレンダリング画像処理を行った画像データに対して圧縮処理(デコード処理)と、プリント用画像処理を実行する前に圧縮データを伸張する伸張処理(エンコード処理)とが必要になる。

#### [0053]

PDLプリント処理のジョブを受けて、ネットワークI/F102より受け付けたPDLデータは、RAM111に格納される。続いて、リードDMAC650によって、RAM111に格納された画像データは、画像バス121を介して読み出される。読み出されたPDLデータは、レンダリング処理、印刷方向に従った回転処理、及びフィルタ処理がなされ、その処理結果の画像データが、RAM111にライトDMAC651によって書き戻される。上記処理内容を実現する画像処理機能が、図6の601に示す回路構成に相当する。ここで、リードDMAC650、ライトDMAC651、レンダリング用の画像処理のデータ処理形式は、全て矩形処理になる。

## [0054]

次に、リードDMAC652によって、RAM111に格納されたレンダリング用の画像処理を行った画像データが読み出され、圧縮処理が行われる。圧縮処理が行われたデータは、矩形状の画像データとは異なり圧縮したリニア処理形式になる。ライトDMAC563は、圧縮処理を行ったリニア処理データをRAM111に書き戻す。上記処理内容を実現する画像処理機能が、図6の603に示す回路構成に相当する。

### [0055]

次に、リードDMAC556によって、RAM111に格納された圧縮データが読み出され、伸張処理が行われ。伸張処理が行われたデータは、ライン状の画像のデータとして出力されライン処理形式になる。ライトDMAC557は、伸張処理を行ったリニア処理データをRAM111に書き戻す。上記処理内容を実現する画像処理機能が、図6の604に示す回路構成に相当する。

## [0056]

次に、リードDMAC552によって、RAM111に格納された画像データは、画像バス121を介して読み出される。読み出された画像データは、プリント用の画像処理がなされ、その処理結果の画像データが、RAM111にライトDMAC553によって書き戻される。最後に、RAM111に格納された画像データは、プリンタI/F106によってプリンタ部107に出力される。上記処理内容を実現する画像処理機能が、図6の602に示す回路構成に相当する。

## [0057]

各画像処理構成部132、133は、このリードDMAC650、ライトDMAC65 1と、画像データをジョブ内容に従って画像処理を行う処理機能を有する。図6の例では、第2のジョブを受けて画像処理構成部132には、リードDMAC650、ライトDMAC651、及びレンダリング用画像処理の処理回路が構成される。画像処理構成部13 3には、リードDMAC552、ライトDMAC553、プリント用画像処理の処理回路が構成される。なお、以下で説明するように、図6の例では、画像処理構成部133は、前ジョブの回路構成をそのまま流用している。

### [0058]

図6に示す処理構成は、第1のジョブから第2のジョブのジョブ処理の差分を判断した結果から、画像処理構成部132、133、134、135を再構成したものである。図5の構成と比較して、スキャン用画像処理の処理構成をしていた画像処理構成部132が

10

20

30

40

、レンダリング処理用の画像処理構成に再構成されている。また、圧縮処理をしている画像構成部134の処理形式が、ライン処理入力から矩形処理入力に変わる。それに対して、プリント用画像処理構成をしていた画像処理構成部133と、伸張処理を行っている画像処理構成部135は、処理変更が必要ないため再構成されていない。

#### [0059]

レンダリング処理用の画像処理は、レンダリング処理部611、回転処理部612、及びフィルタ処理部613を含む。レンダリング処理部611は、PDLデータから画像データを生成する。回転処理部612は、生成した画像データを印刷方向の設定に応じて画像回転を行う。フィルタ処理部613は、その画像データに対してフィルタ処理を行う。

### [0060]

本実施形態では、第1のジョブと第2のジョブの処理差分である、レンダリング処理用の画像処理の回路構成と、圧縮処理の回路構成を構成部131内で再構成を行っている。第2のジョブ内容でも必要なプリント用の画像処理と伸張処理は、画像処理構成部133、135の回路構成を維持することで実現している。それに対して、スキャン用画像処理は第2のジョブでは必要としない。そのため、スキャン用画像処理をレンダリング処理用の画像処理に構成を書き換える。また、第1と第2のジョブで圧縮処理の処理形式が矩形処理とライン処理で異なるため、DMACと圧縮処理の構成を書き換える。このように、第1のジョブと第2のジョブとの処理の差分のみを、構成部131で再構成することで、再構成を行う処理時間を低減している。

## [0061]

本実施形態によれば、図5及び図6を用いて説明した画像処理機能を再構成部131に適宜構成することにより画像処理を実施することとなる。なお、画像処理装置100が処理することのできるジョブは、図5及び図6に示すものに限定されるわけではない。また、画像処理の処理単位は、図5及び図6に示すものに限定されるわけではなく、各画像処理に含まれている処理単位を、さらに細かい粒度(コンポーネント)に分割し、回路構成することも可能である。

## [0062]

#### <コンフィグデータの構成>

次に、図7を参照して、コンフィグデータ(構成データ)の構成について説明する。再構成を行うためのコンフィグデータは、図5及び図6に記載した各処理単位で構成してもよいし、他の単位で構成してもよい。例えば、リードDMAC、各種画像処理部、ライトDMACをすべて含んで1つのコンフィグデータとして用意することもできる。また、各ライトDMAC、リードDMAC、各画像処理部を別々のコンフィグデータとして用意することもできる。スキャン用画像処理に係る画像処理部511~513を個々に分けたコンフィグデータを用意することもできる。プリント用画像処理に係る画像処理部514~517も同様である。レンダリング処理に係る画像処理部611~613も同様である。コンフィグデータを別々に用意した場合に、各ジョブを実行するには、上記それぞれ別々コンフィグデータを再構成部131に部分再構成することにより、ジョブの実行に必要な回路を構成することができる。

### [0063]

本実施形態によれば、ROM104内に再構成部131で構成する回路のコンフィグデータを予め記憶しておく。コンフィグデータの構成単位として、コンフィグデータ701、702、703、704、705、706は、前述した、リードDMACとそれに対応する各種画像処理部と、ライトDMACを含んだ1つの構成を有する。コンフィグデータ711~742は、前述したより細かな粒度である各種画像処理部211~219、311~314、リードDMAC550、ライトDMAC551を別々に有する構成である。

#### [0064]

図 7 に示すように、第 1 のジョブを受け付けて、コンフィグコントローラ 1 3 0 は、 S 4 0 9 で、図 7 (a)に示す 7 0 1、 7 0 2、 7 0 4、 7 0 6 のコンフィグデータを R O M 1 0 4 から R A M 1 1 1 にプリロードさせる(図 7 の 7 5 0)。次に、コンフィグコン

10

20

30

40

トローラ 1 3 0 は、 S 4 1 0 で再構成を実行する際に、再構成部 1 3 1 にプリロードした 7 0 1、 7 0 2、 7 0 4、 7 0 6 のコンフィグデータを用いて再構成を実行する(図 7 の 7 5 1)。

#### [0065]

次に、画像処理装置100が第2のジョブを受け付けると、CPU101は、S406で受け付けた第1と第2のジョブの処理差分を特定する。特定した処理差分に従って、コンフィグコントローラ130は、S409でジョブの処理差分となる703のレンダリング処理用画像処理1コンフィグデータと、705の圧縮処理用の圧縮処理2コンフィグデータをRAM111にプリロードする(図7の752)。

#### [0066]

コンフィグコントローラ 1 3 0 は、S 4 1 0 で再構成を実行する際に、再構成部 1 3 1 に R A M 1 1 1 にプリロードした 7 0 3 のコンフィグデータと、 7 0 5 の圧縮処理用の圧縮処理 2 コンフィグデータとを用いて再構成を実行する(図 7 の 7 5 3 )。この時、再構成部 1 3 1 は、スキャン用画像処理に変わってレンダリング処理用の画像処理機能と、圧縮処理のライン処理入力から矩形処理入力のデータ処理構成に再構成する。

#### [0067]

< 再構成処理のタイミングチャート >

次に、図8を参照して、本実施形態に係る本発明適用時の再構成処理のタイミングチャートについて説明する。図8の上部は、比較例となる手法の適用時の処理のタイミングチャートを示し、図8の820、830は本発明適用時の処理のタイミングチャートを示す。図8のジョブ種別選択800は、メインメニュー画面200においてジョブ選択アイコン202~204のいずれかを選択することで、ジョブ種別が決定した段階を示す。

#### [0068]

ジョブ種別選択800からジョブ開始要求がなされるジョブ開始801の段階までの間が、ユーザーによる設定変更期間である。ジョブ開始801の後、比較例810では、803に示すジョブの設定を実装する全回路を選択する。その後、804にて、全ての処理会を再構成した後、ジョブ実行805を行う。

#### [0069]

一方、820で示す804、805では、ジョブの内容を判断し、前回実行したジョブとの差分のみを選択し、変更する回路部のみの再構成を行う。そのため、全ての処理回路を再構成する場合(810)と比較し、再構成する回路規模が小さいため、再構成に要する期間は短い。804、805での処理は、前述のようにCPU101によって判断し、コンフィグレーションコントローラ130で再構成を実施する。再構成が完了した後、805でCPU101によってジョブの実行が行われる。

### [0070]

また、830に示すように、再構成を行う処理単位をより細かな処理回路にした場合には、再構成を行う回数が分割した再構成の処理数に応じて複数回実行される。ただし、再構成を行う処理単位の回路がより小規模の回路のため、807の個々の再構成時間は820に示す806の再構成時間がより短くなる。再構成を完了する期間807全体では、先の複数回の再構成を実施するために、820の場合の再構成時間よりも長くなる場合があるものの、比較例810よりは短くなる。

#### [0071]

以上説明したように、本実施形態に係る画像処理装置100は、受け付けたジョブを処理するための回路構成と、再構成回路に構成されている回路構成との差分を抽出し、当該差分から、再構成回路に再構成する機能ブロックを選択し、記憶手段から必要な構成データを読み出して再構成回路を再構成する。また、本画像処理装置100は、所定の制約条件に従って機能ブロックを選択することができる。これにより、本画像処理装置100は、新たに書き換えた機能ブロックが書き換えていない部分の他の機能ブロックと連携して動作可能であるとともに、当該再構成に掛かる書き換え時間を短縮することができる。

## [0072]

10

20

30

#### <第2の実施形態>

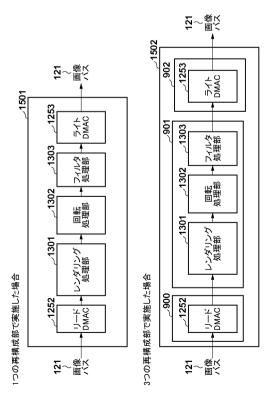

以下では、図9乃至図13を用いて、本発明の第2の実施形態について説明する。上記第1の実施形態では、再構成部131に用意する画像処理構成部を132、133、134、135と少数の再構成部を持つ場合を示した。第1の実施形態では、各画像処理構成部にDMACとそれに接続される画像処理部を1つの画像処理構成部に実装していた。本実施形態では、再構成部131に、多数の画像処理再構成部を有する場合に、より細かな処理回路に分けて再構成する場合について説明する。本実施形態で示すケースとして、DMACとそれに接続される各画像処理部を別々の画像処理構成部として実装する。

## [0073]

## <再構成部の構成>

まず、図9を参照して、本実施形態における再構成部131の構成について説明する。 再構成部131の内部に構成されている画像処理構成部は、各画像処理を行う再構成可能 な回路901、904、907、910の回路で構成される。また、リードDMAC90 0、903、906、909の回路、及び、ライトDMAC902、905、908、9 11の回路で構成される。

#### [0074]

〈ジョブに対する処理関係〉

次に、図10を参照して、画像処理装置100が操作部103で受け付けた各種ジョブと、それに対する再構成部131で実行する処理の関係について説明する。図10に示す処理関係は、図3で示した処理関係から、本実施形態で示すデータの処理形式(矩形処理、ライン処理、リニア処理)の関係を考慮したものである。

#### [0075]

図10中の各種ジョブと設定は、図2における操作部103で設定されたジョブの種別とジョブの設定に対応する。各ジョブに対応できる処理群を大きく、スキャン処理、プリント処理、圧縮処理、及び伸張処理と分けている。さらに、CPU101が選択する処理は、データの転送を行うライトDMACとリードDMACとの処理も追加される。当然、それ以外にも処理はあり、同様に各設定により再構成を行う処理回路が用意される。

#### [0076]

< 再構成制御シーケンス >

次に、図11を参照して、CPU101の再構成実施時の再構成回路の特定(図4のS408)処理の手順について説明する。他の処理フローのステップは、上記第1の実施形態で示した図4の処理フローに従う。以下で説明する処理は、CPU101がROM104に格納された制御プログラムをRAM111で実行することによって実現される。

### [0077]

S 1 1 0 1 で、 C P U 1 0 1 は、第 1 のジョブで構成される再構成部 1 3 1 での各画像処理の処理形式を判断する。ここでは、ライン処理を行っているか、矩形処理を行っているかを判断する。続いて、S 1 1 0 2 で、C P U 1 0 1 は、処理形式が一致するか否かを判定する。一致する場合には S 1 1 0 4 に移行し、一致しない場合には S 1 1 0 3 に移行する。 S 1 1 0 4 で、 C P U 1 0 1 は、処理形式が一致すると判断し、再構成される画像処理回路を選択する。

## [0078]

処理形式が一致しない場合には、S 1 1 0 3 で、他の画像処理部で処理形式が一致するものが存在するか否かを判断する。例えば、再構成前のリード D M A C、ライト D M A C の処理形式がライン処理であり、再構成を行う画像処理の処理形式が矩形処理であった場合に、他に再構成可能な矩形処理を行うリード D M A C、ライト D M A C があるか、C P U 1 0 1 が判断する。S 1 1 0 3 で、他に処理形式が一致するものが存在すると判定された場合には、S 1 1 0 4 に移行する。

### [0079]

一方、S1103で、他に処理形式が一致するものが無ければ、S1105に移行する。S1105で、CPU101は、処理形式をDMACで行っている処理形式に一致させ

10

20

30

40

10

20

30

40

50

るか否かを判断する。例えば、リードDMAC、ライトDMACの処理形式がライン処理でありDMACの処理形式に一致させると判断した場合には、S1106で、CPU101は、画像処理をDMACの処理形式に合わせるように、ライン処理の回路で構成するように選択する。一方、S1105でDMACの処理形式を一致させないと判断した場合、CPU101は、S1107でリードDMAC及びライトDMACが矩形処理の回路で構成されるように選択する。

#### [080]

<再構成部に構成される画像処理回路の構成例>

図12及び図13を参照して、本実施形態に係る画像処理装置における、ジョブの内容によって再構成部131に構成される画像処理機能とコンフィグデータとの関係について説明する。図12は、第1のジョブを受け付けて、ジョブを処理するために再構成部131に構成される画像処理機能の状態を示す。

#### [0081]

第1のジョブとして、白黒画像のコピージョブを操作部103を介して受け付けた場合について説明する。白黒画像のコピージョブを受け付けた場合の再構成部131で行う処理内容としては、原稿を読み取った際の処理としてスキャン用の白黒画像処理と、印刷出力するための画像処理としてプリント用の画像処理とが必要になる。また、スキャン用の白黒画像処理を行った画像データに対して圧縮処理(デコード処理)と、プリント用画像処理を実行する前に圧縮データを伸張する伸張処理(エンコード処理)とが必要になる。

## [0082]

コピージョブとしては、スキャナ部109で読み取った原稿の画像データがスキャンI / F108を介して画像バス121からRAM111へ格納される。続いて、リードDMAC1250によって、RAM111に格納された画像データは、画像バス121を介して読み出される。読み出された画像データに対して、白黒画像のスキャン用画像処理が行われ、その処理結果の画像データがRAM111にライトDMAC1251によって書き戻される。ここでは、白黒画像の第1のスキャン用画像処理は、矩形処理で行う画像処理とする。同様に、ライトDMAC1251も、スキャン用画像処理で実行した矩形処理に対応して矩形処理を行うDMA制御の回路である(図12の1201)。第1のスキャン用画像処理は、1211の画像データのフォーマット変換を行い、1212のシェーディング補正の処理を行い、1213で 補正の処理を行う。その処理結果を、先のライトDMAC1251で画像バス121に出力する。リードDMAC1250は、900でライトDMAC1251は902で構成される。他の各画像処理は、1211、1212、1213が画像処理部901で構成される。

### [0083]

次に、リードDMAC1254によって、RAM111に格納されたスキャン用の画像処理を行った画像データが読み出され、圧縮処理が行われる。ライトDMAC1255は、圧縮処理を行ったリニア処理データをRAM111に書き戻す。上記処理内容を実現する画像処理機能が、図12の1203に示す回路構成に相当する。

## [0084]

次に、リードDMAC1256によって、RAM111に格納された圧縮データが読み出され、伸張処理が行われる。伸張処理が行われたデータは、ライン状の画像のデータとして出力されライン処理形式になる。ライトDMAC1257は、伸張処理が行われたライン処理データをRAM111に書き戻す。上記処理内容を実現する画像処理機能が、図12の1204に示す回路構成に相当する。

#### [0085]

次に、プリント処理を行うためのプリント用画像処理について説明する。プリント用画像処理は、ライン処理を処理単位とするプリント用の画像処理を行う。リードDMAC1252、及びライトDMAC1253は、ライン処理を行うDMA制御を行う回路である(図12の1202)。プリント用画像処理は、1217で背景となる下地を除去する処理を行い、1218でRGBデータを画像処理装置の出力特性に合わせてCMYKの色空

間変換を行う。1219で画像データの 補正が行われる。1220でハーフトーン処理が行われる。その処理結果が、先のライトDMAC1253によって画像バス121に出力される(図12の1202)。リードDMAC1252は、903、ライトDMAC1253は、905、プリント画像処理(1217~1220)は、画像処理部904で構成される。

## [0086]

次に、画像処理装置100が受け付ける第2のジョブとして、カラー画像のコピージョブ処理を受け付けた場合について説明する。第2のジョブは、第1のジョブを再構成部131で処理した後に、操作部103から受け付けた次のジョブとなる。図13は、第2のジョブを処理するために再構成部131に構成される画像処理機能の状態を示す。

## [0087]

第2のカラー画像のコピージョブを受け付けた場合の再構成部で行う処理内容としては、原稿を読み取った際の処理としてスキャン用のカラー画像処理と、印刷出力するための画像処理としてプリント用の画像処理とが必要になる。また、スキャン用のカラー画像処理を行った画像データに対して圧縮処理(デコード処理)と、プリント用画像処理を実行する前に圧縮データを伸張する伸張処理(エンコード処理)とが必要になる。

### [0088]

第1のジョブに対して、差分の処理となるのは、スキャナ用画像処理と、スキャナ用画像処理の処理形式に伴う、圧縮処理になる。スキャナ用画像処理は、白黒画像処理での矩形データの読み込みから、カラー画像処理のラインデータの読み込みに処理形式が変わる

#### [0089]

第2のジョブで変更となるカラー画像のスキャン用画像処理は、リードDMAC1350でRAM111から読み出した画像データをスキャン用画像処理し、その処理結果の画像データをRAM111にライトDMAC1351で書き戻す。ここでは、カラー画像のスキャン用画像処理は、ライン処理で行う画像処理とする。同様に、ライトDMAC1351も、リードDMAC1350もライン処理を行うDMA制御の回路になる(図13の1301)。カラー画像のスキャン用画像処理は、1311で画像データのフォーマット変換を行い、1312のシェーディング補正の処理を行い、1313で 補正の処理を行う。その処理結果を、先のライトDMAC1351で画像バス121に出力する。リードDMAC1350は900で、ライトDMAC1351は902で再構成される。他の各画像処理は、1311、1312、1313が画像処理部901で再構成される。

#### [0090]

次に、リードDMAC1354によって、RAM111に格納されたスキャン用の画像処理を行った画像データが読み出され、圧縮処理が行われる。リードDMAC1354ではライン処理が行われる。ライトDMAC1355は、圧縮処理が行われたリニア処理データをRAM111に書き戻す。上記処理内容を実現する画像処理機能が、図13の1303に示す回路構成に相当する。リードDMAC1354は906で、ライトDMAC1355は908で再構成される。圧縮処理1321は、907で再構成される。

#### [0091]

次に、リードDMAC1356によって、RAM111に格納された圧縮データが読み出され、伸張処理が行われる。伸張処理が行われたデータは、ライン状の画像のデータとして出力されライン処理形式となる。ライトDMAC1357は、伸張処理が行われたライン処理データをRAM111に書き戻す。上記処理内容を実現する画像処理機能が、図13の1304に示す回路構成に相当する。この伸張処理は、第1のジョブと同じ処理でよいため、再構成は行われない。

### [0092]

次に、プリント処理を行うためのプリント用画像処理について説明する。プリント用画像処理も、第1のジョブと同じ処理でよいため、再構成は行われない。そのため各処理も第1のジョブで実行した処理と同じになる(図13の1302)。

10

20

30

40

#### [0093]

次に、第1のジョブと第2のジョブを受けて、再構成を行う再構成の判断処理について説明する。第1のジョブと第2のジョブのジョブ内容の差分をCPU101が判断し、差分の処理内容を構成する再構成回路の特定を行う。その際に、再構成を行う回路を最小限にするための回路構成をコンフィグレーション制約としている。図4のS407及びS408で、CPU101は、コンフィグレーションを実行する場合、再構成するターゲットの画像処理部とその周辺の処理の方式が同じで、且つ、より少なく再構成を行う回数となる構成を優先的に選択する。これは、再構成を行うターゲットである画像処理部が少なければ、より再構成のためのコンフィグレーションの回数が少なくなる。その結果、前述した再構成に掛かる実行時間が短くなるためである。

[0094]

以上説明したように、本実施形態では、まず、リードDMACとライトDMACの処理形式を判断している。DMACのデータ処理の形式はライン処理、リニア処理、矩形処理と考えられ、各画像処理で取り扱う処理形式と合わせる必要がある。図13で示すように、第2のジョブを実施するための再構成の選択肢として、まず再構成が必要な画像処理を選択し、その画像処理のデータ転送に必要なリードDMACとライトDMACの処理形式が一致しているかを判断し、同じ処理形式の組みを選択する。当然、画像処理の処理データの形式(ここでは、ライン処理形式と矩形処理形式)を画像処理内容とDMACとを合わせなければ、正しい処理が行えない。そこで、本実施形態に係るCPU101は、各画像処理を構成する際に、処理データの転送を担うリードDMAC及びライトDMACの処理形式を判断している。

[0095]

<第3の実施形態>

以下では、図14及び図15を参照して、本発明の第3の実施形態について説明する。上記第2の実施形態では、再構成部131に、多数の画像処理再構成部を有する場合で、処理形式が一致しない場合の再構成の判断について説明した。一方、本実施形態では、上記第2の実施形態と同様に多数の画像処理再構成部を有する場合であって、再構成に対して回路規模とコンフィグレーション回数を判断基準とした例について説明する。再構成部131は、第2の実施形態での再構成部131に従う。

[0096]

< 再構成制御シーケンス >

まず、図14を参照して、本実施形態における処理手順について説明する。再構成部131における再構成制御のシーケンスは、上記第1の実施形態における図4の再構成制御シーケンスに従う。このシーケンス内の再構成実施時の再構成回路の特定(図4のS408)部の処理ステップを以下で詳細に説明する。以下で説明する処理は、CPU101がROM104に格納された制御プログラムをRAM111で実行することによって実現される。

[0097]

S1401で、CPU101は、第2のジョブで要求される再構成の制約でコンフィグレーション回数を最小にするか否かを判断する。即ち、再構成に掛かる時間の要因の一つとなるコンフィグレーション回数を最小にすることで、再構成に掛かる時間を抑える場合である。この場合、ユーザーにとっては、ジョブを受け付けて画像処理装置100の処理が開始されるまでの待ち時間を抑える効果がある。なお、S1401の判断は、前もってユーザー入力された設定情報を参照することによって行われてもよいし、画像処理装置100の機種情報として製品出荷時に格納された情報を参照することによって行われてもよい。前者の場合は、ユーザー入力を受け付けるユーザーインターフェースが必要となり、ジョブの入力時に行ってもよいし、他の任意のタイミングで前もって行われてもよい。

[0098]

S 1 4 0 1 でコンフィグレーション回数を最小にする制約があれば、 S 1 4 0 2 に移行し、制約が無い場合には S 1 4 0 9 に移行する。 S 1 4 0 9 で、 C P U 1 0 1 は、コンフ

10

20

30

40

ィグレーション回数に対する制約が無いため、デフォルトの構成(ここでは、4つの再構成部を用いる構成)で再構成する画像処理回路を選択し、処理を終了する。

#### [0099]

一方、S1402で、CPU101は、コンフィグレーション回数を最小にする場合の構成を判断し、その構成で回路規模として再構成可能か否かを判断する。画像処理部133に構成できる回路規模が、PDLプリント処理を全て構成できる範囲であれば、S1404に進み、CPU101は、画像処理部133に再構成を行う回路を選択し、処理を終了する。この回路構成を第1の再構成とする。

### [0100]

S1402で回路規模が第1の再構成を超えると判断された場合には、S1403に進み、CPU101は、第2の再構成で再構成可能か否かを判断する。第2の再構成の回路規模で再構成可能と判断すると、S1405に進み、CPU101は、画像処理部133、136、142に再構成を行う回路構成を選択し、処理を終了する。一方、第2の再構成で回路規模が超えると判断した場合はS1406に進み、CPU101は、第3の再構成で再構成可能な否かを判断する。

#### [0101]

超えると判断した場合には、S1408に進み、CPU101は、再構成対象を変更し、より広範囲な画像処理構成を判断して、回路規模が入る再構成を選択し、処理を終了する。一方、第3の再構成の回路規模で再構成可能と判断すると、S1407に進み、CPU101は、画像処理部133、136、139、142に再構成を行う回路を選択し、処理を終了する。

#### [0102]

<再構成部に構成される画像処理回路の構成例>

次に、図15を参照して、本実施形態での再構成を、上記第1の実施形態で示した第2のジョブ処理を行うための再構成例であるPDLプリント処理部(図6の601)に対する再構成部131での回路構成例を使って説明する。PDLプリント処理を行うために必要な処理構成は、レンダリング用画像処理、矩形処理のリードDMAC及び矩形処理のライトDMACである。これらを再構成する構成パターンとして2パターンの例を図15に示す。

## [0103]

図15の1501に示す構成は、第1の実施形態での、上記3つの処理構成を1つの画像処理構成部132で実現していた構成例である。この場合には、132の再構成1回で処理を完了する。一方、図15の1502で示す構成は、第2の実施形態で示した再構成部131(図9)に基づく、上記3つの処理構成をそれぞれ900、901、902の構成部で実現した構成例である。この場合には、3回の再構成処理が発生する。つまり、900に対するライトDMACの再構成、901に対する画像処理部の再構成、902に対するリードDMACの再構成である。例えば、再構成を行う構成部の回路規模が、再構成を行う処理回路の規模より大きければ再構成を行える。したがって、1501に示す回路構成が可能であれば、より再構成に掛かるコンフィグレーション回数を低減することができる。

## [0104]

本実施形態によれば、再構成を行う構成で、再構成を行う処理内容は、一度に再構成できる回路規模を条件に入れて判断する。再構成を行う画像処理部を大きな回路規模の領域に割り当てると、再構成を行う処理内容によっては、使用していない回路が画像処理部により多く存在してしまう。一方で、再構成を行う画像処理部をより細かな回路規模の領域に割り当てると、その画像処理部に再構成時に入りきらない場合が発生してしまう。この場合には、CPU101が判断した再構成の処理内容をより細かに分解して、再構成を行う必要がある。この場合には、再構成を行う画像処理部が多数存在することになり、コンフィグレーション回数が、その分増加することになる。このように、コンフィグレーション回数と回路規模とはトレードオフの関係にある。従って、本実施形態では、再構成に掛

10

20

30

40

かる時間のコンフィグレーション回数と、再構成を行う画像処理部の回路規模との関係を考慮し、CPU101にて、その再構成を実施するコンフィグレーション制約のもとで再構成範囲を調整する。

#### [0105]

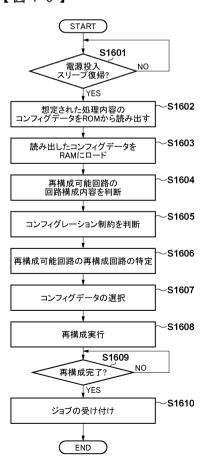

<第4の実施形態>

以下では、図16を参照して、本発明の第4の実施形態について説明する。本実施形態では、画像処理装置100が、電源投入後又はスリープ復帰後に再構成を行う場合の一例について説明する。電源投入後又はスリープ復帰後の再構成の処理シーケンス部以外は、上記第1の実施形態に従うため説明を省略する。

#### [0106]

本実施形態に係る画像処理装置100は、電源投入後、又はスリープ復帰後の最初のジョブの処理完了時間をより早くするために、予測される最初のジョブ内容を再構成部131に前もって構成する。再構成部131に予測される処理の回路を前もって構成しておくことで、最初のジョブを受け付けた際に、当該ジョブに必要な回路構成と、予め構成した回路構成との処理差分のみを再構成することで、最初のジョブを実行するまでの処理時間をより低減できる。本実施形態では、画像処理装置100が最初に実行するジョブに関して、前もって構成する回路構成について説明する。

#### [0107]

CPU101は、電源投入後又はスリープ復帰後において、ROM104から、予測される処理内容の回路構成を示すコンフィグデータをRAM111にプリロードする。このタイミングでは、まだジョブを受け付けていないことを想定している。その後、CPU101は、コンフィグコントローラ130を介して、再構成部131に対して構成を行う。これにより、画像処理装置100は、電源投入後又はスリープ復帰後において、最初のジョブ処理をより高速に処理することが可能となり、ユーザーに処理待ち時間を短縮することができる。なお、電源投入後又はスリープ復帰後のタイミングでジョブを受け付けている場合は、当該ジョブに合わせた回路構成に対応するコンフィグデータを使用する。また、ROM104には、画像処理装置100が起動する要因、例えば、電源投入やネットワークアクセスによるスリープ復帰に対応して定義された最初に構成する回路構成を示すコンフィグデータが格納されていることが望ましい。

## [0108]

< 再構成制御シーケンス >

次に、図16を参照して、電源投入後又はスリープ復帰後の再構成部131における再構成制御のシーケンスについて説明する。本制御フローは、電源投入後もしくはスリープ復帰後に開始される。以下で説明する処理は、CPU101がROM104に格納された制御プログラムをRAM111で実行することによって実現される。

#### [0109]

S1601で、CPU101は、電源投入又はスリープ復帰が実施されたか否かを判断する。電源投入又はスリープ復帰が実施されればS1602へ移行する。S1602で、CPU101は、画像処理装置100が復帰後、予測されるジョブの内容をROM104から読み込む。上述したように、ROM104には、復帰後に予測される処理内容のコンフィグデータが予め格納されている。S1603で、CPU101は、読み出したコンフィグデータをRAM111に記憶する。例えば、コピージョブが予測されている場合には、CPU101は、コピー処理に必要なスキャン画像処理、及びプリント画像処理の各処理のコンフィグデータとその各処理に必要な設定パラメータを読み込む。

#### [0110]

次に、S1604で、CPU101は、S1603でロードしたコンフィグデータから 再構成部131で再構成を行う回路構成を特定する。S1605で、CPU101は、コンフィグデータを元に、再構成を行う上での制約条件があるか否か判断する。例えば、最初のジョブとなるため再構成を行う回路への再構成に掛かる時間を最小限にするための条件となる。 10

20

30

#### [0111]

S1606で、CPU101は、S1605での制約判断に従って、再構成を行うための回路構成を特定する。続いて、S1607で、コンフィグコントローラ130は、RAM111に記憶したコンフィグデータから再構成を行う回路を実現するコンフィグデータを抽出する。このコンフィグデータは、再構成を行う回路構成に従って、細かい処理単位でのコンフィグデータを複数選択することで1つの再構成を実行することもできる。或いは、より再構成を行う処理単位を大きくし、コンフィグデータの数をより少なく構成して1つの再構成を実行することもできる。

## [0112]

次に、S1608で、コンフィグコントローラ130は、先のS1607で選択したコンフィグデータを用いて、再構成部131を再構成する。再構成は、先のコンフィグデータから再構成部131へ回路を再度、書き換えることで実現する。再構成部131への再構成が完了すると、S1609で、コンフィグコントローラ130は、CPU101にて再構成完了の割り込み通知を行う。S1610で、CPU101は、当該再構成完了の割り込み通知を受けて、ジョブの受け付けを行い、当該フローチャートの処理を終了する。【0113】

本実施形態によれば、画像処理装置100は、電源投入後又はスリープ復帰後において、実行が予想されるジョブに対応するコンフィグデータを用いて再構成を実施する。これにより、ジョブを受け付けた後に再構成を実施するよりも、ジョブを受け付けてから当該ジョブを開始するまでの時間を短縮することができる。画像処理装置100の電源投入後又はスリープ復帰後の最初のジョブ例としては、コピージョブ、プリントジョブなどが予測される。画像処理装置100の予測される最初のジョブは変更することも可能で、CPU101によってROM104からコンフィグデータを選択することで実現できる。なお、最初のジョブを受け付けた後の処理シーケンスは、第1の実施形態で示した図5の処理シーケンスに従う。最初のジョブを受け付けた際には、電源投入後又はスリープ復帰後に予め予測した処理回路と、最初のジョブとの差分があったとしても、当該差分となる理のみ再構成部131で再構成を行えばよい。これによって、画像処理装置100は、電源投入後又はスリープ復帰後の最初に受け付けるジョブの処理を実行する際の処理時間を低減することができる。

## [0114]

## <その他の実施形態>

また、本発明は、以下の処理を実行することによっても実現される。即ち、上述した実施形態の機能を実現するソフトウェア(プログラム)を、ネットワーク又は各種記憶媒体を介してシステム或いは装置に供給し、そのシステム或いは装置のコンピュータ(又はCPUやMPU等)がプログラムを読み出して実行する処理である。

## 【符号の説明】

## [0115]

1 0 0 : 画像処理装置、1 0 1 : C P U、1 0 4 : R O M、1 1 1 : R A M、1 2 0 : システムバス、1 2 1 : 画像バス、1 3 0 : コンフィグコントローラ、1 3 1 : 再構成部

10

20

【図2】

【図3】

【図4】

【図10】

|               | А.ш.              |        |     |    |    |       |     |              |   |      |

|---------------|-------------------|--------|-----|----|----|-------|-----|--------------|---|------|

| の処理           | リニア処理             | ×      | ×   | 1  | I  | I     | ×   | ×            | 1 | I    |

| リードDMAC処理     | 是<br>是<br>用       | 0      | ×   | 1  | -1 | ı     | 0   | 0            | 1 | ı    |

| ライトDMAC処理 リート | アカツ理              | ×      | 0   | ı  | I  | Ι     | 0   | ×            | 1 | ı    |

|               | リニア<br>処理         | ×      | ×   | I  | I  | _     | ×   | ×            | I | I    |

|               | 短别<br>開業          | 0      | ×   | ı  | 1  | ı     | 0   | 0            | 1 | ı    |

| レンダリング<br>処理  | ライン<br>処理         | ×      | 0   | 1  | 1  | _     | ×   | 0            | 1 | I    |

|               | レンダ<br>リング<br>処理2 | 0      | ×   | I  | 1  | _     | 0   | ×            | 1 | 1    |

| 伸張処理 レンダ      | レンダ<br>リング<br>処理1 | ×      | 0   | I  | 1  | -     | ×   | 0            | 1 | ı    |

|               | 伸張<br>処理2         | 0      | ×   | 1  | -1 | -     | 0   | ×            | 1 | 1    |

| 圧縮処理 伸張       | 伸張<br>処理1         | ×      | 0   | 1  | -1 | Ι     | ×   | 0            | 1 | 1    |

|               | 圧縮<br>処理2         | 0      | ×   | 1  | I  | ı     | 0   | ×            | 1 | ı    |

| プリント処理 圧縮     | 圧縮<br>処理1         | ×      | 0   | 1  | 1  | -     | ×   | 0            | 1 | 1    |

|               | 画像<br>処理3         | 0      | 0   | 0  | 0  | Ι     | 0   | 0            | 0 | 0    |

|               | 画像<br>処理2         | 0      | ×   | ×  | ×  | I     | 0   | ×            | × | ×    |

| スキャン処理 プリ     | 画像<br>処理1         | 0      | 0   | ×  | 0  | I     | 0   | 0            | × | 0    |

|               | 画像<br>処理3         | 0      | 0   | 0  | 0  | 0     | 0   | 0            | 0 | 0    |

|               | 画像<br>処理2         | 0      | ×   | ×  | 0  | 0     | 0   | ×            | × | 0    |

| X             | 画像<br>処理1         | ×      | 0   | ×  | 0  | 0     | ×   | 0            | × | 0    |

|               | 設定                | 計      | カラー | 和科 | 原稿 | 両面をかり | 黒   | <del>1</del> | 和 | 原稿種別 |

|               | ジョブ種別             | Н<br>1 |     |    |    |       | PDL |              |   |      |

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

## フロントページの続き

## (72)発明者 山本 直宏

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

## 審査官 宮島 潤

(56)参考文献 特開2005-25599(JP,A)

特開2002-181897(JP,A)

特開2008-242850(JP,A)

(58)調査した分野(Int.CI., DB名)

H 0 4 N 1 / 0 0

B 4 1 J 5 / 0 0 - 5/52

B 4 1 J 2 9 / 0 0 - 2 9 / 7 0 G 0 6 T 1 / 0 0 - 1 / 4 0

H03K 19/098 - 19/23