(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5008334号

(P5008334)

(45) 発行日 平成24年8月22日(2012.8.22)

(24) 登録日 平成24年6月8日(2012.6.8)

(51) Int.Cl.

F 1

G09G 5/00 (2006.01)

G09G 5/00 550M

G09G 5/39 (2006.01)

G09G 5/36 530D

H04N 1/21 (2006.01)

H04N 1/21

請求項の数 4 (全 14 頁)

(21) 出願番号 特願2006-110048 (P2006-110048)

(22) 出願日 平成18年4月12日 (2006.4.12)

(65) 公開番号 特開2006-330700 (P2006-330700A)

(43) 公開日 平成18年12月7日 (2006.12.7)

審査請求日 平成21年3月16日 (2009.3.16)

(31) 優先権主張番号 特願2005-133742 (P2005-133742)

(32) 優先日 平成17年4月28日 (2005.4.28)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 傅保 洋樹

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 居島 一仁

最終頁に続く

(54) 【発明の名称】 画像出力装置

## (57) 【特許請求の範囲】

## 【請求項 1】

データバスに接続されたバスコントローラと、

前記バスコントローラに接続されたメモリコントローラと、

前記メモリコントローラに接続された映像記憶メモリ及び一時記憶メモリと、

前記一時記憶メモリに接続された表示コントローラと、

前記表示コントローラに接続された表示装置と、を有し、

前記バスコントローラは、前記映像記憶メモリに書き込みまたは前記映像記憶メモリから読み出しを切り替える機能を有し、

前記メモリコントローラは、前記表示コントローラからの信号に基づき、前記一時記憶メモリと前記映像記憶メモリとが接続されるか、前記バスコントローラと前記映像記憶メモリとが接続されるかを切り替える機能を有し、

前記一時記憶メモリと前記映像記憶メモリとが接続される場合、前記映像記憶メモリの画像データが前記一時記憶メモリにコピーされ、

前記映像記憶メモリと前記バスコントローラとが接続される場合、前記映像記憶メモリへの画像データの書き込み、又は前記映像記憶メモリからの画像データの読み出しが行われ、且つ前記一時記憶メモリの画像データが前記表示装置に出力されることを特徴とする画像出力装置。

## 【請求項 2】

請求項 1 において、

10

前記表示コントローラは、前記一時記憶メモリと前記表示装置とが接続されるか否かを切り替える機能を有し、

前記映像記憶メモリと前記バスコントローラとが接続される場合、前記一時記憶メモリと前記表示装置とが接続されることを特徴とする画像出力装置。

**【請求項 3】**

請求項 1 又は請求項 2 において、

前記表示コントローラは、R G B 変換回路と、D / A 変換回路と、を有し、

前記一時記憶メモリの画像データは、前記 R G B 変換回路及び D / A 変換回路を介して前記表示装置に出力されることを特徴とする画像出力装置。

**【請求項 4】**

10

請求項 1 乃至請求項 3 のいずれか一項において、

前記メモリコントローラと前記表示コントローラとの間には、複数の前記一時記憶メモリが並列接続されていることを特徴とする画像出力装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0 0 0 1】**

本発明はデータバス上に接続された画像出力装置に関し、特に映像記憶メモリ、一時記憶メモリを有する画像出力装置に関する。

**【背景技術】**

**【0 0 0 2】**

20

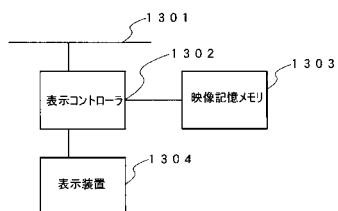

図 13 は、データバスに接続する従来の画像出力装置の一例を示すブロック図である。画像出力装置は、データバス 1301、表示コントローラ 1302、映像記憶メモリ 1303、表示装置 1304 を有する。データバス 1301 から入力された画像データは、表示コントローラ 1302 によって映像記憶メモリ 1303 に書き込まれ、表示コントローラ 1302 によって表示装置 1304 に出力される（特許文献 1 参照）。

**【特許文献 1】特開平 5 - 122474 号公報**

**【発明の開示】**

**【発明が解決しようとする課題】**

**【0 0 0 3】**

30

上記画像出力装置においては、画像を表示するために映像記憶メモリ 1303 から表示コントローラ 1302 を介して表示装置 1304 へ画像データを出力している際に、表示コントローラ 1302 はデータバス 1301 から映像記憶メモリ 1303 へ画像データの書き込みができない。

**【0 0 0 4】**

そこで本発明は、データバスの使用効率を向上させ、画像出力装置の処理速度を向上させることを目的とする。

**【課題を解決するための手段】**

**【0 0 0 5】**

上記課題を鑑み本発明は、一時記憶メモリ、メモリコントローラ、バスコントローラを使用することで、データバスの動作状態をもとに、画像出力装置の動作制御を行うことを特徴とする。また映像記憶メモリに加えて、一時記憶メモリを設けたことにより、映像記憶メモリに書き込みを行なながら、一時記憶メモリからの映像信号を表示装置へ出力することができる。

40

**【0 0 0 6】**

以下に、具体的な本発明の形態を示す。

**【0 0 0 7】**

本発明の一形態は、データバスに接続されたバスコントローラと、バスコントローラに接続されたメモリコントローラと、メモリコントローラに接続された映像記憶メモリ及び一時記憶メモリと、一時記憶メモリに接続された表示コントローラと、表示コントローラに接続された表示装置と、を有することを特徴とする画像出力装置である。

50

## 【0008】

本発明の別形態は、データバスに接続されたバスコントローラと、バスコントローラに接続されたメモリコントローラと、メモリコントローラに接続された映像記憶メモリ及び一時記憶メモリと、一時記憶メモリに接続された表示コントローラと、表示コントローラに接続された表示装置と、を有し、バスコントローラは、メモリコントローラに接続されたアドレスデコーダ、書き込み用デコーダ、読み出し用デコーダ、及びコマンド判定回路を有し、コマンド判定回路からの信号に基づき、書き込み用データデコーダ又は読み出し用データデコーダのいずれかを選択するスイッチを有することを特徴とする画像出力装置である。

## 【0009】

本発明の別形態は、データバスに接続されたバスコントローラと、バスコントローラに接続されたメモリコントローラと、メモリコントローラに接続された映像記憶メモリ及び一時記憶メモリと、一時記憶メモリに接続された表示コントローラと、表示コントローラに接続された表示装置と、を有し、表示コントローラは、アドレスカウンタ、表示アドレスカウンタ、遙倍回路、表示タイミング信号生成回路、基準クロック発信器、RGB変換回路、D/A変換回路を有し、基準クロック発信器からの信号が遙倍回路、表示アドレスカウンタ、及び表示タイミング信号生成回路に入力され、表示タイミング信号生成回路からの信号に基づき、アドレスカウンタ又は表示アドレスカウンタのいずれかを選択するスイッチを有することを特徴とする画像出力装置である。

## 【0010】

本発明の別形態は、データバスに接続されたバスコントローラと、バスコントローラに接続されたメモリコントローラと、メモリコントローラに接続された映像記憶メモリ及び一時記憶メモリと、一時記憶メモリに接続された表示コントローラと、表示コントローラに接続された表示装置と、を有し、メモリコントローラは、メモリ動作判定回路を有し、表示コントローラからの信号に基づき、一時記憶メモリ又は映像記憶メモリの接続を切り替えるスイッチを有することを特徴する画像出力装置である。

## 【0011】

このような画像出力装置において、メモリコントローラを介して映像記憶メモリに映像が記録されるとき、一時記憶メモリから表示コントローラを介して表示装置に画像を出力することができる。

## 【発明の効果】

## 【0012】

本発明によれば映像出力期間中に画像データを映像記憶メモリに書き込むことが可能になることによって、電子計算機上のデータバスの使用効率が向上し、バス占有時間に無駄がない電子計算機システムを提供することができる。

## 【発明を実施するための最良の形態】

## 【0013】

以下に、本発明の実施の形態を図面に基づいて説明する。但し、本発明は多くの異なる態様で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本実施の形態の記載内容に限定して解釈されるものではない。なお、実施の形態を説明するための全図において、同一部分又は同様な機能を有する部分には同一の符号を付し、その繰り返しの説明は省略する。

## 【0014】

## (実施の形態1)

本実施の形態では、本発明に係る画像出力装置の一態様を、図面を参照しながら説明する。

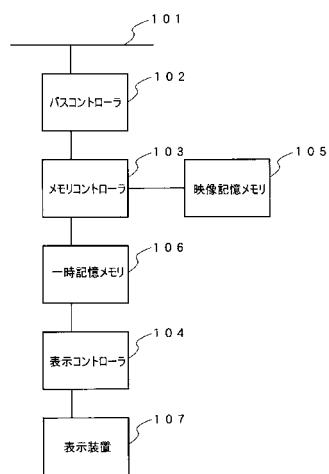

## 【0015】

図1には、本発明にかかる画像出力装置の構成が示されている。本画像出力装置は、データバス101、バスコントローラ102、メモリコントローラ103、表示コントロー

10

20

30

40

50

ラ 1 0 4、映像記憶メモリ 1 0 5、一時記憶メモリ 1 0 6、表示装置 1 0 7 で構成される。データバス 1 0 1 は、バスコントローラ 1 0 2 が接続され、バスコントローラ 1 0 2 にはメモリコントローラ 1 0 3 が接続されている。また、メモリコントローラ 1 0 3 には、映像記憶メモリ 1 0 5 及び一時記憶メモリ 1 0 6 が接続されている。また一時記憶メモリ 1 0 6 には、表示コントローラ 1 0 4 を介して表示装置 1 0 7 が接続され、表示装置において所定の映像を表示することができる。

【 0 0 1 6 】

このような画像出力装置によって、データバス 1 0 1 からの映像に関するデータバス信号を映像記憶メモリ 1 0 5 に書き込みながら、一時記憶メモリ 1 0 6 に記録された映像を表示装置 1 0 7 に表示することができる。

10

【 0 0 1 7 】

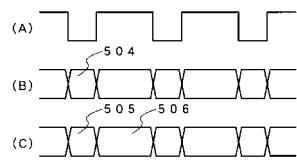

このような画像出力装置において、データバス 1 0 1 を流れるデータバス信号の波形を図 5 に示す。

【 0 0 1 8 】

データバス信号には、データバスフレーム信号、データバスコマンド信号、データバスアドレスデータ信号がある。

【 0 0 1 9 】

データバスフレーム信号は、データバス 1 0 1 からバスコントローラ 1 0 2 へのアクセスが発生したときに L o w になる。また、データバスコマンド信号には、メモリコントローラ 1 0 3 に対する命令コード 5 0 4 が含まれている。データバスアドレスデータ信号には、映像記憶メモリ 1 0 5 に対するアドレスコード 5 0 5 、画像データコード 5 0 6 の値を有する。

20

【 0 0 2 0 】

バスコントローラ 1 0 2 は、データバス 1 0 1 とメモリコントローラ 1 0 3 の間にあり、双方の信号を適した形に変換する機能を有する。

【 0 0 2 1 】

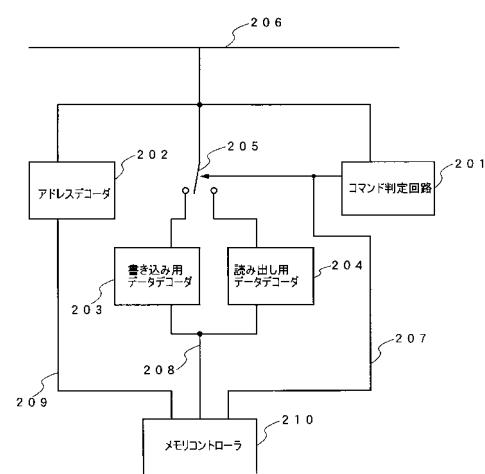

次にバスコントローラ 1 0 2 の機能を説明する。図 2 は、バスコントローラ 1 0 2 の機能を示すブロック図である。

【 0 0 2 2 】

バスコントローラ 1 0 2 は、コマンド判定回路 2 0 1 、アドレスデコーダ 2 0 2 、書き込み用データデコーダ 2 0 3 、読み出し用データデコーダ 2 0 4 、バス切り替えスイッチ 2 0 5 を有する。メモリコントローラ 2 1 0 は、図 1 のメモリコントローラ 1 0 3 に相当する。データバス 2 0 6 は、図 1 のデータバス 1 0 1 に相当する。

30

【 0 0 2 3 】

データバス 2 0 6 からの信号は、アドレスデコーダ 2 0 2 又はコマンド判定回路 2 0 1 に入力される。コマンド判定回路 2 0 1 は、データバス 2 0 6 から受け取ったデータバスコマンド信号に含まれた命令コードを判別し、ライトイネーブル信号が出力される配線（ライトイネーブル用配線）2 0 7 を介して、メモリコントローラ 2 1 0 、バス切り替えスイッチ 2 0 5 へ出力する。ここで、命令コードが書き込み命令であれば、ライトイネーブル信号は L o w となり、メモリコントローラ 1 0 3 を介して L o w が映像記憶メモリ 1 0 5 に入力され、映像記憶メモリ 1 0 5 が書き込み可能な状態となる。また命令コードが読み出し命令であれば、ライトイネーブル信号は H i g h となり、メモリコントローラ 1 0 3 を介して H i g h が映像記憶メモリ 1 0 5 に入力され、映像記憶メモリ 1 0 5 が書き込み不可能な状態となる。

40

【 0 0 2 4 】

またバス切り替えスイッチ 2 0 5 は、コマンド判定回路 2 0 1 から受け取ったライトイネーブル信号に基づき、データバス 2 0 6 と書き込み用データデコーダ 2 0 3 と読み出し用データデコーダ 2 0 4 の接続を切り替える機能を有する。

【 0 0 2 5 】

ライトイネーブル信号に基づくバス切り替えスイッチ 2 0 5 の動作を表 1 に示す。

50

## 【表1】

| ライトイネーブル信号 | 接続状態                           |

|------------|--------------------------------|

| H i g h    | 読み出し用<br>データバス206 ⇔ データデコーダ204 |

| L o w      | 書き込み用<br>データバス206 ⇔ データデコーダ203 |

## 【0026】

書き込み用データデコーダ203は、データバス206から受け取ったデータバスアドレスデータ信号に含まれる画像データコード506をメモリコントローラデータバス信号へ変換し、変換されたメモリコントローラデータバス信号が入力される配線（メモリコントローラデータバス用配線）208を介してメモリコントローラ210へ出力する。 10

## 【0027】

読み出し用データデコーダ204は、メモリコントローラ210から受け取ったメモリコントローラデータバス信号を、画像データコード506を含むデータバスアドレスデータ信号に変換しデータバス206へ出力する。

## 【0028】

アドレスデコーダ202は、データバス206から受け取ったデータバスアドレスデータ信号に含まれるアドレスコード505をメモリコントローラアドレスバス信号へ変換し、変換されたメモリコントローラアドレスバス信号は配線（メモリコントローラアドレスバス用配線）209を介してメモリコントローラ210へ出力する。 20

## 【0029】

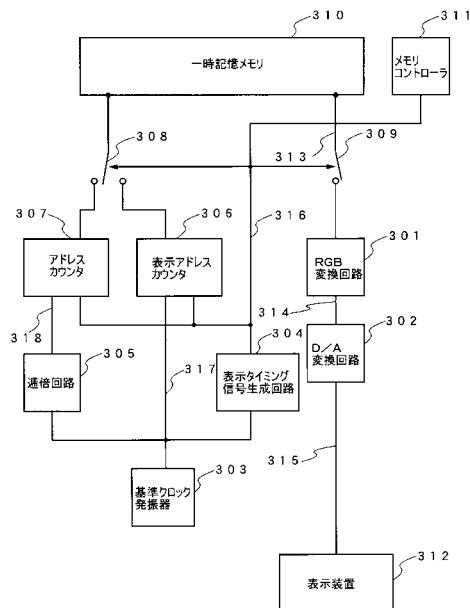

次に表示コントローラ104の機能を説明する。図3は、表示コントローラ104の機能を示すブロック図である。

## 【0030】

表示コントローラ104は、RGB変換回路301とD/A変換回路302、基準クロック発振器303、表示タイミング信号生成回路304、倍倍回路305、表示アドレスカウンタ306、アドレスカウンタ（読み出しアドレスカウンタ）307、アドレスバススイッチ308、データバススイッチ309を有する。一時記憶メモリ310は、図1に示す一時記憶メモリ106に相当する。メモリコントローラ311は、図1に示すメモリコントローラ103に相当する。表示装置312は、図1に示す表示装置107に相当する。 30

## 【0031】

このような表示コントローラ104は、一時記憶メモリ106と表示装置107の間にあり、一時記憶メモリ106に格納された画像データを表示装置107に適した信号に変換し出力する機能を有する。

## 【0032】

またRGB変換回路301は、一時記憶メモリ310から受け取った一時記憶メモリデータ信号をR、G、B各色の色データとして分離し、配線（一時記憶メモリデータ用配線）313に出力され、デジタルRGB信号として配線（デジタルRGB用配線）314を介してD/A変換回路302へ渡す。 40

## 【0033】

D/A変換回路302は、RGB変換回路301より受け取ったデジタルRGB信号をアナログRGB信号に変換し、変換されたアナログRGB信号を配線（アナログRGB用配線）315から表示装置312へ出力する機能を有する。

## 【0034】

基準クロック発振器303は、表示装置312のドットクロックと同じクロックを発信することができる。

## 【0035】

表示タイミング信号生成回路 304 は、基準クロック発振器 303 から表示タイミング信号を作り出し、当該表示タイミング信号を配線（表示タイミング用配線）316 から、メモリコントローラ 311、表示装置 312、表示アドレスカウンタ 306、アドレスカウンタ 307、アドレスバススイッチ 308、及びデータバススイッチ 309 へ出力する機能を有する。

【0036】

表示アドレスカウンタ 306 は、表示タイミング信号が High になった瞬間から基準クロック発振器 303 より受け取ったクロック信号をカウントし、カウントした値を配線（クロック用配線）317 から一時記憶メモリ 310 へ出力する。

【0037】

アドレスカウンタ 307 は、表示タイミング信号が Low になった瞬間から基準クロック発振器 303 を通じ回路 305 によって n 倍に高速化したクロック信号をもとに、カウントし、カウントされた値を配線（n 倍クロック用配線）318 から一時記憶メモリ 310 へ出力する。

【0038】

このとき表示アドレスカウンタ 306 とアドレスカウンタ 307 の出力は、アドレスバススイッチ 308 によってスイッチングされ、一時記憶メモリアドレスバス信号として、配線（一時記憶メモリアドレスバス用配線）から一時記憶メモリ 310 へ出力される。

【0039】

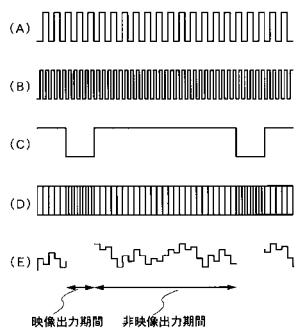

図 6 の (A) から (E) には、表示コントローラ 104 で使用する各種信号の挙動が示されている。

【0040】

図 6 (A) には基準クロック信号の波形を示す。基準クロックはクロック信号と同じ信号の波形を用いることができる。

【0041】

図 6 (B) には n 倍基準クロックの波形を示す。n 倍基準クロックはクロック信号と同じ信号を用いることができる。

【0042】

図 6 (C) には表示タイミング信号の波形を示す。

【0043】

図 6 (D) には一時記憶メモリアドレスバス信号の波形を示す。一時記憶メモリアドレスバス信号は基準クロック信号をカウントした値と、n 倍基準クロックをカウントした値とを、表示タイミング信号のタイミングに基づきアドレスバススイッチ 308 で切り替えて出力したものである。

【0044】

図 6 (E) には表示出力信号の波形を示す。表示出力信号はアナログ RGB 信号と同じ信号の波形を用いることができる。

【0045】

表示タイミング信号は、基準クロック発振器 303 が発信する基準クロックから表示タイミング信号生成回路 304 によって生成される。表示タイミング信号が High のときだけ、データバススイッチ 309 がオンとなり、一時記憶メモリデータ信号が配線 313 を経由し、RGB 変換回路 301、D/A 変換回路 302 を経て表示出力信号が表示装置 312 へ出力される。このとき、表示タイミング信号が High の期間を映像出力期間 606、Low の期間を非映像出力期間 607 とする。

【0046】

表示装置 312 は、アナログ RGB 信号である表示出力信号と、表示タイミング信号とによって描画を行うため、アナログ駆動方式の液晶ディスプレイ、CRT などに対応できる。

【0047】

メモリコントローラ 103 は、表示コントローラ 104 が出力する表示タイミング信号

10

20

30

40

50

とバスコントローラ 102 が出力するライトイネーブル信号を元に、映像記憶メモリ 105 と一時記憶メモリ 106、映像記憶メモリ 105 とバスコントローラ 102 の接続を切り替える。

【0048】

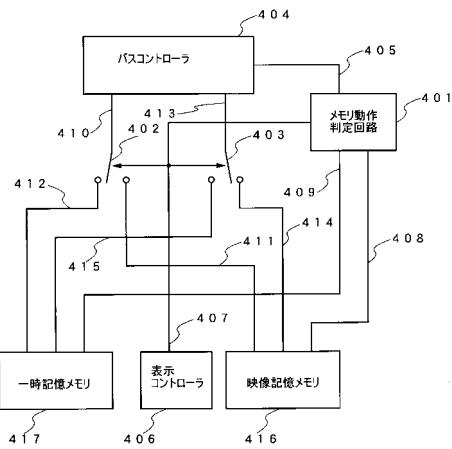

次にメモリコントローラ 103 の機能を説明する。図 4 は、メモリコントローラ 103 の機能を示すブロック図である。

【0049】

メモリコントローラ 103 は、メモリ動作判定回路 401、アドレスバス切り替えスイッチ 402、データバス切り替えスイッチ 403 を有する。一時記憶メモリ 417 は、図 1 の一時記憶メモリ 106 に相当する。映像記憶メモリ 416 は、図 1 の映像記憶メモリ 105 に相当する。表示コントローラ 406 は、図 1 の表示コントローラ 104 に相当する。バスコントローラ 404 は、図 1 のバスコントローラ 102 に相当する。

【0050】

メモリ動作判定回路 401 は、バスコントローラ 404 からライトイネーブル信号を、配線（ライトイネーブル用配線）405 を介して受け取る。さらにメモリ動作判定回路 401 は、表示コントローラ 406 から表示タイミング信号を、配線（表示タイミング用配線）407 を介して受け取る。そして配線 407 を経由する当該表示タイミング信号をもとに、配線 408 を経由する映像記憶メモリライトイネーブル信号、配線 409 を経由する一時記憶メモリライトイネーブル信号を、映像記憶メモリ 416、一時記憶メモリ 417 へそれぞれ出力する。

【0051】

上記、メモリ動作判定回路 401 の動作を表 2 に示す。

【表 2】

| 表示タイミング信号 | ライトイネーブル信号 | 映像記憶メモリライトイネーブル信号 | 一時記憶メモリライトイネーブル信号 |

|-----------|------------|-------------------|-------------------|

| High      | High       | High              | High              |

| High      | Low        | Low               | High              |

| Low       | High       | High              | Low               |

| Low       | Low        | High              | Low               |

10

20

30

【0052】

アドレスバス切り替えスイッチ 402 は、表示コントローラ 406 から受け取った表示タイミング信号をもとに、メモリコントローラアドレスバス 410 と映像記憶メモリアドレスバス 411 と一時記憶メモリアドレスバス 412 を切り替える。

【0053】

上記、アドレスバス切り替えスイッチ 402 の動作を表 3 に示す。

【表 3】

| 表示タイミング信号 | 接続状態                |                   |

|-----------|---------------------|-------------------|

| High      | メモリコントローラアドレスバス 410 | 映像記憶メモリアドレスバス 411 |

| Low       | 一時記憶メモリアドレスバス 412   | 映像記憶メモリアドレスバス 411 |

40

【0054】

また、データバス切り替えスイッチ 403 は、表示コントローラ 406 から受け取った表示タイミング信号をもとに、メモリコントローラデータバス 413 と映像記憶メモリデータバス 414 と一時記憶メモリデータバス 415 を切り替える。

【0055】

50

上記、データバス切り替えスイッチ 403 の動作を表 4 に示す。

【表 4】

| 表示タイミング信号 | 接続状態                   |                           |

|-----------|------------------------|---------------------------|

| H i g h   | メモリコントローラ<br>データバス 413 | 映像記憶メモリ<br>データバス 414<br>↔ |

| L o w     | 一時記憶メモリ<br>データバス 415   | 映像記憶メモリ<br>データバス 414<br>↔ |

【0056】

10

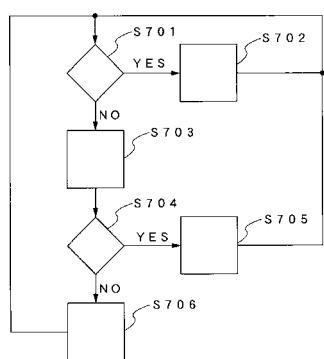

次に、メモリコントローラの動作をフローチャートとして図 7 に示す。

【0057】

メモリコントローラ 103 は、表示コントローラ 104 より表示タイミング信号を受け (S701)、L であれば (YES)、一時記憶メモリデータバス 415 と映像記憶メモリデータバス 414 を接続し画像データをコピー (S702) し、H であれば (NO)、映像記憶メモリデータバス 414 とメモリコントローラデータバス 413 を接続する (S703)。

【0058】

表示タイミング信号が H であるときに、メモリコントローラ 103 は、バスコントローラ 102 よりライトイネーブル信号を受け (S704)、L であれば (YES)、メモリコントローラデータバス 413 と映像記憶メモリデータバス 414 を接続し映像記憶メモリ 105 へ画像データを書き込み (S705)、H であれば (NO)、映像記憶メモリ 105 からメモリコントローラデータバス 413 へ画像データを読み出す (S706)。

20

【0059】

以下に、本実施形態における画像出力装置のメリットを示す。

【0060】

1) 一時記憶メモリと映像記憶メモリを異なった速度で動作させることによって、電子計算機上のデータバスの動作速度に依存しない描画タイミングで画像を出力する画像出力装置を提供することが出来る。

30

【0061】

2) 映像記憶メモリ、一時記憶メモリとして高価なデュアルポートメモリを使用することなく、画像出力装置を構成することが可能になることで、製造コストを下げられる。

【0062】

(実施の形態 2)

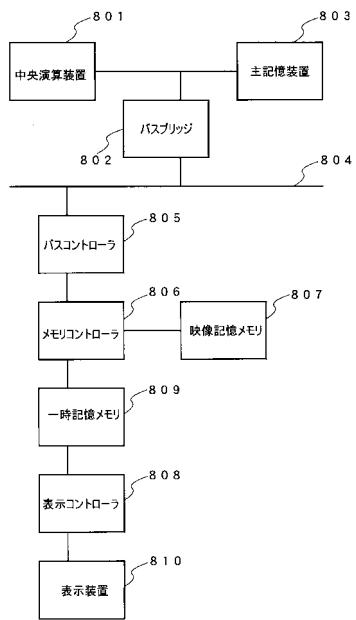

図 8 は、図 1 に示す画像出力装置を有する応用例として電子計算機システムを示す。

【0063】

図 8 において、電子計算機システムは、中央演算装置 801、バスブリッジ 802、主記憶装置 803、データバス 804、バスコントローラ 805、メモリコントローラ 806、映像記憶メモリ 807、一時記憶メモリ 809、表示コントローラ 808、表示装置 810 を有する。中央演算装置 801、バスブリッジ 802、主記憶装置 803 は互いに接続されている。バスブリッジ 802 はデータバス 804 を介してバスコントローラ 805 に接続され、メモリコントローラ 806 を介して映像記憶メモリ 807、一時記憶メモリ 809 に接続されている。また一時記憶メモリ 809 は、表示コントローラ 808 を介して表示装置 810 に接続されている。そして主記憶装置 803 に格納されている画像表示プログラムを元に、電子計算機システムが制御される。

40

【0064】

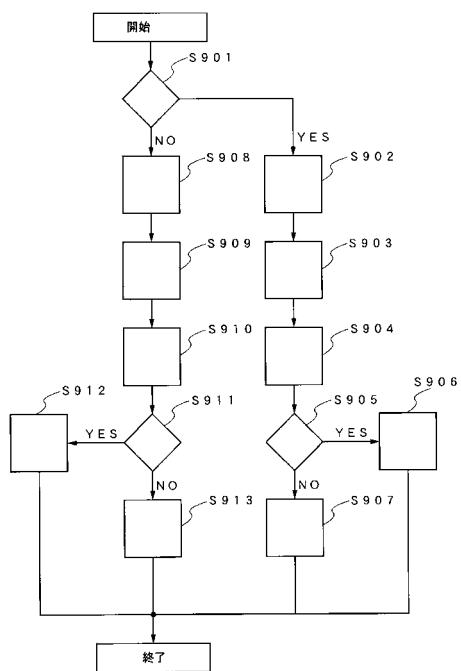

図 9 には、主記憶装置 803 に記録された画像データを画像出力装置に書き込む処理、画像出力装置に記録された画像データを主記憶装置 803 に読み出す処理のフローチャートを示す。

【0065】

50

中央演算装置 801 は主記憶装置 803 より読み込んだプログラムを実行する。

【0066】

中央演算装置 801 はプログラムの命令を解釈し (S901)、画像出力要求であれば (YES)、主記憶装置 803 内の画像データと書き込み命令をバスブリッジ 802 へ送る (S902)。

【0067】

バスブリッジ 802 はデータバス 804 を介してバスコントローラ 805 へ画像データを書き込み命令とともに出力する (S903)。

【0068】

バスコントローラ 805 は書き込み命令を受け、メモリコントローラ 806 へ画像データとともに書き込み信号を送る (S904)。 10

【0069】

メモリコントローラ 806 は書き込み信号を受け、映像出力期間であるかどうか判定し (S905)、映像出力期間であれば (YES)、映像記憶メモリ 807 へ書き込みを行い (S906)、非映像出力期間であれば (NO)、映像出力期間になるまで待ち、書き込み処理を行う (S907)。

【0070】

また、中央演算装置 801 がプログラムの命令を解釈したときに (S901)、画像読み出し要求であれば (NO)、読み出し命令をバスブリッジ 802 へ送る (S908)。 20

【0071】

バスブリッジ 802 はデータバス 804 を介してバスコントローラ 805 へ読み出し命令を出力する (S909)。

【0072】

バスコントローラ 805 は読み出し命令を受け、メモリコントローラ 806 へ読み出し信号を送る。 (S910)。

【0073】

メモリコントローラ 806 は読み出し信号を受け、映像出力期間であるかどうか判定し (S911)、映像出力期間であれば (YES)、映像記憶メモリ 807 から読み出しを行い (S912)、非映像出力期間であれば (NO)、映像出力期間になるまで待ち、読み出し処理を行う (S913)。 30

【0074】

(実施の形態 3)

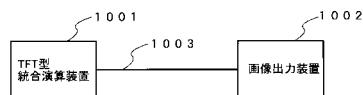

図 10 は、図 1 に示す画像出力装置を有する応用例である TFT (薄膜トランジスタ) 型統合演算処理システムを示す。

【0075】

図 10においては、TFT 型統合演算装置 1001 が接続されており、画像出力装置 1002 が制御される。TFT 型統合演算装置とは、TFT によって構成された演算装置である。そして、格納されている画像表示プログラムを元に、画像出力装置 1002 が制御される。

【0076】

なお TFT 型統合演算装置 1001 は、高密度プラズマ CVD 装置で成膜したゲート絶縁膜等の絶縁膜を有する TFT を有することができる。 40

【0077】

(実施の形態 4)

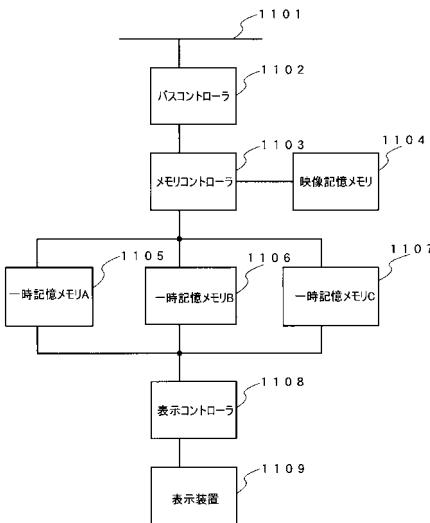

図 11 は図 1 に示した本発明実施の形態の構成の変形例を示す図である。

【0078】

図 11 は一時記憶メモリの並列接続例を有する画像出力装置である。図 11 に示す画像出力装置は、データバス 1101 に接続されたバスコントローラ 1102、メモリコントローラ 1103、映像記憶メモリ 1104、一時記憶メモリ A1105、一時記憶メモリ B1106、一時記憶メモリ C1107、表示コントローラ 1108、表示装置 1109

を有する。バスコントローラ 1102 は、メモリコントローラ 1103 に接続され、メモリコントローラ 1103 は映像記憶メモリ 1104 に接続される。またメモリコントローラ 1103 は、一時記憶メモリ A 1105、一時記憶メモリ B 1106、一時記憶メモリ C 1107 にそれぞれ接続されている。また一時記憶メモリ A 1105、一時記憶メモリ B 1106、一時記憶メモリ C 1107 は、それぞれ表示コントローラ 1108 に接続され、表示コントローラ 1108 は表示装置 1109 に接続されている。

【0079】

この変形例は、一時記憶メモリが並列接続しているため、画像出力装置によって特定の連続パターンを表示する用途に適用可能で、データバスを全く使用することなく、画像出力装置のみで連続パターンを表示できる。

10

【0080】

(実施の形態 5)

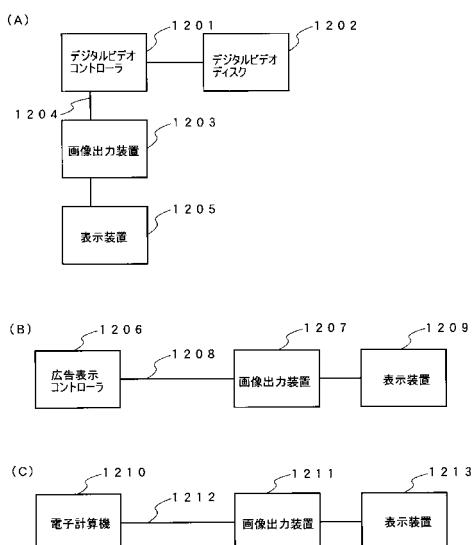

図 12 (A)、(B)、(C) は、図 1 に示す画像出力装置の最終製品レベルである電子機器を示す。

【0081】

図 12 (A) は、デジタルビデオ再生装置を示す。デジタルビデオ再生装置は、デジタルビデオコントローラ 1201、デジタルビデオディスク 1202、画像出力装置 1203、表示装置 1205 を有する。デジタルビデオコントローラ 1201 は、デジタルビデオディスク 1202 及び画像出力装置 1203 に接続され、画像出力装置 1203 は表示装置 1205 に接続されている。このようなデジタルビデオ再生装置は、ユーザーが娯楽用途もしくは学習用途向けのデジタルビデオを鑑賞するために使用することができる。

20

【0082】

図 12 (B) は、街頭広告装置を示す。街頭広告装置は、広告表示コントローラ 1206、画像出力装置 1207、データバス 1208、表示装置 1209 を有する。広告表示コントローラ 1206 は、データバス 1208 を介して画像出力装置 1207 に接続され、画像出力装置 1207 は表示装置 1209 が接続されている。このような街頭広告装置は、広告主が宣伝用途において商品画像などを広告するために使用することができる。

【0083】

図 12 (C) は、電子計算機装置を示す。電子計算機装置は、電子計算機 1210、データバス 1212、画像出力装置 1211、表示装置 1213 を有する。電子計算機 1210 はデータバス 1212 を介して画像出力装置 1211 に接続され、画像出力装置 1211 は表示装置 1213 に接続されている。

30

このような電子計算機装置は、ユーザーが計算結果を確認するために使用することができる。

【図面の簡単な説明】

【0084】

【図 1】本発明にかかる画像出力装置の実施の形態を示すブロック図である。

【図 2】バスコントローラ 102 のブロック図である。

【図 3】表示コントローラ 104 のブロック図である。

【図 4】メモリコントローラ 103 のブロック図である。

40

【図 5】データバス 101 を流れるデータ信号である。

【図 6】表示コントローラ 104 で使用する各種信号のタイミングチャートである。

【図 7】メモリコントローラ 103 の動作を示すフローチャートである。

【図 8】画像出力装置の実施の応用例である電子計算機システムを示すブロック図である。

【図 9】電子計算機システムの動作を示すフローチャートである。

【図 10】画像出力装置の実施の変形例を示すブロック図である。

【図 11】画像出力装置の最終製品レベルでの実施の形態を示すブロック図である。

【図 12】本発明の画像出力装置を用いた電子機器を示す図である。

【図 13】従来の画像出力装置の一例を示すブロック図である。

50

## 【符号の説明】

## 【0085】

- 101 データバス

- 102 バスコントローラ

- 103 メモリコントローラ

- 104 表示コントローラ

- 105 映像記憶メモリ

- 106 一時記憶メモリ

- 107 表示装置

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図8】

【図7】

【図9】

【図11】

【図10】

【図12】

【図13】

---

フロントページの続き

(56)参考文献 特開平11-352951(JP, A)

特開平10-105154(JP, A)

特開2002-202881(JP, A)

特開2000-035778(JP, A)

特開2004-317536(JP, A)

特開平3-107895(JP, A)

(58)調査した分野(Int.Cl., DB名)

G 09 G 3 / 00 - 5 / 42