(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2017년06월21일

(11) 등록번호 10-1749583

(24) 등록일자 2017년06월15일

(51) 국제특허분류(Int. Cl.)

H03M 1/50 (2006.01) H03M 1/00 (2006.01)

(21) 출원번호 10-2011-0051105

(22) 출원일자 2011년05월30일

심사청구일자 2016년05월26일

(65) 공개번호 10-2012-0132772

(43) 공개일자 2012년12월10일

(56) 선행기술조사문현

US20050018780 A1

US20050062513 A1

US20120159226 A1

US20120200435 A1

(73) 특허권자

삼성전자주식회사

경기도 수원시 영통구 삼성로 129 (매탄동)

(72) 발명자

김성진

울산광역시 중구 화진4길 92, 남운파크 601호 (태화동)

김지현

경기도 화성시 동탄중앙로 189, 342동 1002호 (반송동, 동탄시범다은마을 월드메르디앙반도유보라아파트)

(74) 대리인

박영우

전체 청구항 수 : 총 20 항

심사관 : 유선중

(54) 발명의 명칭 시간차 가산기, 시간차 누산기, 시그마-델타 타임 디지털 변환기, 디지털 위상 고정 루프 및 온도 센서

**(57) 요 약**

시간차 가산기, 시간차 누산기, 시그마-델타 타임 디지털 변환기, 디지털 위상 고정 루프 및 온도 센서가 개시된다. 시간차 가산기는 제1 레지스터부 및 제2 레지스터부를 포함한다. 제1 레지스터부는, 제1 입력 신호 및 제2 입력 신호를 수신하고, 제1 신호에 응답하여 제1 출력 신호를 생성한다. 제2 레지스터부는, 제3 입력 신호 및 제4 입력 신호를 수신하고, 제1 신호에 응답하여 제1 출력 신호에 대하여 제1 및 제2 입력 신호들간의 제1 시간차와 제3 및 제4 입력 신호들간의 제2 시간차의 합에 상응하는 시간차를 가지는 제2 출력 신호를 생성한다.

**대 표 도** - 도1

## 명세서

### 청구범위

#### 청구항 1

제1 시간차를 가지는 제1 입력 신호 및 제2 입력 신호를 수신하고, 제1 신호에 응답하여 제1 출력 신호를 생성하는 제1 레지스터부; 및

제2 시간차를 가지는 제3 입력 신호 및 제4 입력 신호를 수신하고, 상기 제1 신호에 응답하여 상기 제1 출력 신호에 대하여 상기 제1 시간차와 상기 제2 시간차의 합에 상응하는 시간차를 가지는 제2 출력 신호를 생성하는 제2 레지스터부를 포함하는 것을 특징으로 하는 시간차 가산기를 포함하는 시스템-온-칩.

#### 청구항 2

제1 항에 있어서, 상기 제1 레지스터부는,

상기 제2 입력 신호를 오프셋 시간만큼 지연시켜 제1 홀드 신호를 생성하는 제1 오프셋 지연기; 및

상기 제1 입력 신호를 수신하는 제1 입력 단자, 상기 제1 홀드 신호를 수신하는 제1 홀드 단자, 상기 제1 신호를 수신하는 제1 어웨이크 단자, 및 상기 제1 출력 신호를 출력하는 제1 출력 단자를 가지는 제1 시간 레지스터를 포함하고,

상기 제2 레지스터부는,

상기 제3 입력 신호를 상기 오프셋 시간만큼 지연시켜 제2 홀드 신호를 생성하는 제2 오프셋 지연기; 및

상기 제4 입력 신호를 수신하는 제2 입력 단자, 상기 제2 홀드 신호를 수신하는 제2 홀드 단자, 상기 제1 신호를 수신하는 제2 어웨이크 단자, 및 상기 제2 출력 신호를 출력하는 제2 출력 단자를 가지는 제2 시간 레지스터를 포함하는 것을 특징으로 하는 시간차 가산기를 포함하는 시스템-온-칩.

#### 청구항 3

제2 항에 있어서,

상기 제1 시간 레지스터는, 상기 제1 신호의 상승 에지로부터 디스차지 시간에서 상기 오프셋 시간 및 상기 제1 시간차가 감산된 시간 후 상승 에지를 가지는 상기 제1 출력 신호를 출력하고,

상기 제2 시간 레지스터는, 상기 제1 신호의 상기 상승 에지로부터 상기 디스차지 시간에서 상기 오프셋 시간이 감산되고 상기 제2 시간차가 가산된 시간 후 상승 에지를 가지는 상기 제2 출력 신호를 출력하는 것을 특징으로 하는 시간차 가산기를 포함하는 시스템-온-칩.

#### 청구항 4

제3 항에 있어서, 상기 제1 시간 레지스터 및 상기 제2 시간 레지스터는 제1 커패시터 및 제2 커패시터를 각각 포함하고, 상기 제1 커패시터 및 상기 제2 커패시터는 동일한 커패시턴스를 가지며, 상기 디스차지 시간은 상기 동일한 커패시턴스에 따라 결정되는 것을 특징으로 하는 시간차 가산기를 포함하는 시스템-온-칩.

#### 청구항 5

제2 항에 있어서, 상기 제1 시간 레지스터는,

상기 제1 입력 신호를 반전시키는 제1 인버터;

상기 제1 홀드 신호에 응답하여 상기 제1 인버터를 비활성화시키고, 상기 제1 신호에 응답하여 상기 제1 인버터를 활성화시키는 인버터 제어부;

상기 제1 인버터의 출력 신호에 응답하여 충전 또는 방전되는 커패시터; 및

상기 커패시터의 전압에 기초하여 상기 제1 출력 신호를 생성하는 제2 인버터를 포함하는 것을 특징으로 하는 시간차 가산기를 포함하는 시스템-온-칩.

#### 청구항 6

제5 항에 있어서, 상기 커패시터는, 상기 제1 입력 신호와 상기 제1 홀드 신호 사이의 시간차에 상응하는 시간 동안 방전됨으로써, 상기 제1 입력 신호와 상기 제1 홀드 신호 사이의 상기 시간차에 대한 정보를 저장하는 것을 특징으로 하는 시간차 가산기를 포함하는 시스템-온-칩.

#### 청구항 7

제5 항에 있어서, 상기 커패시터의 방전은, 상기 제1 입력 신호의 상승 에지에 응답하여 시작되고, 상기 제1 홀드 신호의 상승 에지에 응답하여 중지되며, 상기 제1 신호의 상승 에지에 응답하여 재개되는 것을 특징으로 하는 시간차 가산기를 포함하는 시스템-온-칩.

#### 청구항 8

제5 항에 있어서, 상기 제1 인버터는,

상기 제1 입력 신호가 인가되는 게이트, 상기 인버터 제어부를 통하여 전원 전압에 연결된 소스, 및 중간 노드에 연결된 드레인을 포함하는 제1 PMOS 트랜지스터; 및

상기 제1 입력 신호가 인가되는 게이트, 상기 인버터 제어부를 통하여 접지 전압에 연결된 소스, 및 상기 중간 노드에 연결된 드레인을 포함하는 제1 NMOS 트랜지스터를 포함하고,

상기 인버터 제어부는,

상기 전원 전압과 상기 제1 PMOS 트랜지스터 사이에 연결된 제2 PMOS 트랜지스터;

상기 접지 전압과 상기 제1 NMOS 트랜지스터 사이에 연결된 제2 NMOS 트랜지스터;

상기 제2 PMOS 트랜지스터의 게이트에 연결된 출력 단자, 상기 제2 NMOS 트랜지스터의 게이트에 연결된 반전 출력 단자, 상기 반전 출력 단자에 연결된 테이터 단자, 및 클록 단자를 포함하는 D-플립플롭; 및

상기 D-플립플롭의 상기 반전 출력 단자에서 출력되는 반전 출력 신호에 응답하여 상기 D-플립플롭의 상기 클록 단자에 상기 제1 홀드 신호 또는 상기 제1 신호를 선택적으로 출력하는 선택기를 포함하며,

상기 커패시터는 상기 중간 노드와 상기 접지 전압 사이에 연결되고,

상기 제2 인버터는,

상기 중간 노드에 연결된 게이트, 상기 전원 전압에 연결된 소스, 및 상기 제1 출력 신호가 출력되는 드레인을 포함하는 제3 PMOS 트랜지스터; 및

상기 중간 노드에 연결된 게이트, 상기 접지 전압에 연결된 소스, 및 상기 제1 출력 신호가 출력되는 드레인을 포함하는 제3 NMOS 트랜지스터를 포함하는 것을 특징으로 하는 시간차 가산기를 포함하는 시스템-온-칩.

#### 청구항 9

제2 항에 있어서, 상기 제1 시간 레지스터는,

상기 제1 입력 신호를 반전시키는 제1 인버터;

상기 제1 홀드 신호에 응답하여 상기 제1 인버터를 비활성화시키고, 상기 제1 신호에 응답하여 상기 제1 인버터를 활성화시키는 인버터 제어부;

상기 제1 인버터의 출력 신호에 응답하여 충전 또는 방전되는 커패시터; 및

상기 커패시터의 전압을 기준 전압과 비교하여 상기 제1 출력 신호를 생성하는 비교기를 포함하는 것을 특징으로 하는 시간차 가산기를 포함하는 시스템-온-칩.

#### 청구항 10

삭제

### 청구항 11

삭제

### 청구항 12

제1 시간차를 가지는 제1 입력 신호 및 제2 입력 신호를 수신하고, 제1 신호에 응답하여 제1 출력 신호를 생성하는 제1 레지스터부; 및

제2 시간차를 가지는 제3 입력 신호 및 제4 입력 신호를 수신하고, 상기 제1 신호에 응답하여 상기 제1 출력 신호에 대하여 상기 제1 시간차와 상기 제2 시간차의 합에 상응하는 시간차를 가지는 제2 출력 신호를 생성하는 제2 레지스터부를 포함하고,

상기 제1 레지스터부는,

상기 제1 입력 신호를 수신하는 제1 입력 단자, 상기 제2 입력 신호를 수신하는 제1 홀드 단자, 상기 제1 신호를 수신하는 제1 어웨이크 단자, 및 상기 제1 출력 신호를 출력하는 제1 출력 단자를 가지는 제1 시간 레지스터를 포함하고,

상기 제2 레지스터부는,

상기 제4 입력 신호를 수신하는 제2 입력 단자, 상기 제3 입력 신호를 수신하는 제2 홀드 단자, 상기 제1 신호를 수신하는 제2 어웨이크 단자, 및 상기 제2 출력 신호를 출력하는 제2 출력 단자를 가지는 제2 시간 레지스터를 포함하는 것을 특징으로 하는 시간차 가산기를 포함하는 시스템-온-칩.

### 청구항 13

삭제

### 청구항 14

제1 시간차를 가지는 제1 입력 신호 및 제2 입력 신호를 수신하고, 제1 신호에 응답하여 제1 출력 신호를 생성하는 제1 레지스터부; 및

제2 시간차를 가지는 제3 입력 신호 및 제4 입력 신호를 수신하고, 상기 제1 신호에 응답하여 상기 제1 출력 신호에 대하여 상기 제1 시간차와 상기 제2 시간차의 합에 상응하는 시간차를 가지는 제2 출력 신호를 생성하는 제2 레지스터부를 포함하고,

상기 제1 레지스터부는,

상기 제2 입력 신호를 오프셋 시간만큼 지연시켜 제1 홀드 신호를 생성하는 제1 오프셋 지연기; 및

상기 제1 입력 신호를 수신하는 제1 입력 단자, 상기 제1 홀드 신호를 수신하는 제1 홀드 단자, 제2 신호를 수신하는 제1 프리차지 단자, 상기 제1 신호를 수신하는 제1 어웨이크 단자, 및 상기 제1 출력 신호를 출력하는 제1 출력 단자를 가지는 제1 시간 레지스터를 포함하고,

상기 제2 레지스터부는,

상기 제3 입력 신호를 상기 오프셋 시간만큼 지연시켜 제2 홀드 신호를 생성하는 제2 오프셋 지연기; 및

상기 제4 입력 신호를 수신하는 제2 입력 단자, 상기 제2 홀드 신호를 수신하는 제2 홀드 단자, 상기 제2 신호를 수신하는 제2 프리차지 단자, 상기 제1 신호를 수신하는 제2 어웨이크 단자, 및 상기 제2 출력 신호를 출력하는 제2 출력 단자를 가지는 제2 시간 레지스터를 포함하는 것을 특징으로 하는 시간차 가산기를 포함하는 시스템-온-칩.

### 청구항 15

삭제

**청구항 16**

삭제

**청구항 17**

삭제

**청구항 18**

제1 시간차를 가지는 제1 입력 신호 및 제2 입력 신호를 수신하고, 제1 신호에 응답하여 제1 출력 신호를 생성하는 제1 레지스터부; 및

제2 시간차를 가지는 제3 입력 신호 및 제4 입력 신호를 수신하고, 상기 제1 신호에 응답하여 상기 제1 출력 신호에 대하여 상기 제1 시간차와 상기 제2 시간차의 합에 상응하는 시간차를 가지는 제2 출력 신호를 생성하는 제2 레지스터부를 포함하고,

상기 제1 레지스터부는,

상기 제1 입력 신호를 수신하는 제1 입력 단자, 상기 제2 입력 신호를 수신하는 제1 홀드 단자, 제2 신호를 수신하는 제1 프리차지 단자, 상기 제1 신호를 수신하는 제1 어웨이크 단자, 및 상기 제1 출력 신호를 출력하는 제1 출력 단자를 가지는 제1 시간 레지스터를 포함하고,

상기 제2 레지스터부는,

상기 제4 입력 신호를 수신하는 제2 입력 단자, 상기 제3 입력 신호를 수신하는 제2 홀드 단자, 상기 제2 신호를 수신하는 제2 프리차지 단자, 상기 제1 신호를 수신하는 제2 어웨이크 단자, 및 상기 제2 출력 신호를 출력하는 제2 출력 단자를 가지는 제2 시간 레지스터를 포함하는 것을 특징으로 하는 시간차 가산기를 포함하는 시스템-온-칩.

**청구항 19**

제1 입력 신호와 제2 입력 신호간의 제1 시간차 및 제1 이전 출력 신호와 제2 이전 출력 신호간의 제2 시간차를 가산하여 상기 제1 시간차와 상기 제2 시간차의 합에 상응하는 제3 시간차를 가지는 제1 출력 신호 및 제2 출력 신호를 생성하는 제1 시간차 가산기; 및

상기 제1 출력 신호와 상기 제2 출력 신호간의 상기 제3 시간차 및 동일한 신호들간의 시간차를 가산하여 상기 제3 시간차를 가지는 상기 제1 이전 출력 신호 및 상기 제2 이전 출력 신호를 생성하는 제2 시간차 가산기를 포함하는 것을 특징으로 하는 시간차 누산기를 포함하는 시스템-온-칩.

**청구항 20**

삭제

**청구항 21**

제1 입력 신호와 제2 입력 신호간의 제1 시간차 및 제1 이전 출력 신호와 제2 이전 출력 신호간의 제2 시간차를 가산하여 상기 제1 시간차와 상기 제2 시간차의 합에 상응하는 제3 시간차를 가지는 제1 출력 신호 및 제2 출력 신호를 생성하는 시간차 가산기;

상기 제1 출력 신호를 소정의 시간만큼 지연시켜 상기 제1 이전 출력 신호를 생성하는 제1 지연기; 및

상기 제2 출력 신호를 상기 소정의 시간만큼 지연시켜 상기 제2 이전 출력 신호를 생성하는 제2 지연기를 포함하는 것을 특징으로 하는 시간차 누산기를 포함하는 시스템-온-칩.

**청구항 22**

제1 입력 신호와 제2 입력 신호간의 제1 시간차에서 제1 피드백 신호와 제2 피드백 신호간의 제2 시간차를 감산하여 상기 제1 시간차에서 상기 제2 시간차가 감산된 제3 시간차를 가지는 제1 가산 신호 및 제2 가산 신호를 생성하는 시간차 가산기;

상기 제1 가산 신호와 상기 제2 가산 신호간의 상기 제3 시간차를 누산하여 제1 누산 신호 및 제2 누산 신호를 생성하는 시간차 누산기;

상기 제1 누산 신호와 상기 제2 누산 신호간의 시간차를 디지털 출력 신호로 변환하는 시간 도메인 양자화기; 및

상기 디지털 출력 신호를 상기 제1 피드백 신호 및 상기 제2 피드백 신호로 변환하는 디지털 타임 변환기를 포함하는 시그마-델타 타임 디지털 변환기.

### 청구항 23

제1 입력 신호, 제2 입력 신호 및 디지털 출력 신호를 수신하고, 상기 디지털 출력 신호에 기초하여 상기 제1 입력 신호 또는 상기 제2 입력 신호를 상기 디지털 출력 신호에 상응하는 지연 시간만큼 지연시킴으로써 제1 가산 신호 및 제2 가산 신호를 생성하는 시간차 조절부;

상기 제1 가산 신호와 상기 제2 가산 신호간의 시간차를 누산하여 제1 누산 신호 및 제2 누산 신호를 생성하는 시간차 누산기; 및

상기 제1 누산 신호와 상기 제2 누산 신호간의 시간차를 상기 디지털 출력 신호로 변환하는 시간 도메인 양자화기를 포함하는 시그마-델타 타임 디지털 변환기.

### 청구항 24

삭제

### 청구항 25

기준 입력 신호와 피드백 신호간의 제1 시간차에 상응하는 디지털 시간차 신호를 생성하는 위상 검출기;

상기 디지털 시간차 신호를 필터링하여 디지털 제어 신호를 생성하는 디지털 루프 필터;

상기 디지털 제어 신호에 응답하여 출력 신호를 생성하는 디지털 제어 발진기; 및

상기 출력 신호를 분주하여 상기 피드백 신호를 생성하는 분주기를 포함하고,

상기 위상 검출기는,

상기 기준 입력 신호와 상기 피드백 신호간의 상기 제1 시간차에서 제1 내부 피드백 신호와 제2 내부 피드백 신호간의 제2 시간차를 감산하여 상기 제1 시간차에서 상기 제2 시간차가 감산된 제3 시간차를 가지는 제1 가산 신호 및 제2 가산 신호를 생성하는 시간차 가산기;

상기 제1 가산 신호와 상기 제2 가산 신호간의 상기 제3 시간차를 누산하여 제1 누산 신호 및 제2 누산 신호를 생성하는 시간차 누산기;

상기 제1 누산 신호와 상기 제2 누산 신호간의 시간차를 상기 디지털 시간차 신호로 변환하는 시간 도메인 양자화기; 및

상기 디지털 시간차 신호를 상기 제1 내부 피드백 신호 및 상기 제2 내부 피드백 신호로 변환하는 디지털 타임 변환기를 포함하는 것을 특징으로 하는 디지털 위상 고정 루프.

### 청구항 26

기준 입력 신호와 피드백 신호간의 시간차에 상응하는 디지털 시간차 신호를 생성하는 위상 검출기;

상기 디지털 시간차 신호를 필터링하여 디지털 제어 신호를 생성하는 디지털 루프 필터;

상기 디지털 제어 신호에 응답하여 출력 신호를 생성하는 디지털 제어 발진기; 및

상기 출력 신호를 분주하여 상기 피드백 신호를 생성하는 분주기를 포함하고,

상기 위상 검출기는,

상기 디지털 시간차 신호에 기초하여 상기 기준 입력 신호 또는 상기 피드백 신호를 상기 디지털 시간차 신호에 상응하는 지연 시간만큼 지연시킴으로써 제1 가산 신호 및 제2 가산 신호를 생성하는 시간차 조절부;

상기 제1 가산 신호와 상기 제2 가산 신호간의 시간차를 누산하여 제1 누산 신호 및 제2 누산 신호를 생성하는 시간차 누산기; 및

상기 제1 누산 신호와 상기 제2 누산 신호간의 시간차를 상기 디지털 시간차 신호로 변환하는 시간 도메인 양자화기를 포함하는 것을 특징으로 하는 디지털 위상 고정 루프.

### 청구항 27

온도를 감지하여 상기 온도에 상응하는 제1 시간차를 가지는 제1 입력 신호 및 제2 입력 신호를 생성하는 센싱부; 및

상기 제1 입력 신호와 상기 제2 입력 신호간의 상기 제1 시간차에 상응하는 디지털 출력 신호를 생성하는 시그마-델타 타임 디지털 변환기를 포함하고,

상기 시그마-델타 타임 디지털 변환기는,

상기 제1 입력 신호와 상기 제2 입력 신호간의 상기 제1 시간차에서 제1 피드백 신호와 제2 피드백 신호간의 제2 시간차를 감산하여 상기 제1 시간차에서 상기 제2 시간차가 감산된 제3 시간차를 가지는 제1 가산 신호 및 제2 가산 신호를 생성하는 시간차 가산기;

상기 제1 가산 신호와 상기 제2 가산 신호간의 상기 제3 시간차를 누산하여 제1 누산 신호 및 제2 누산 신호를 생성하는 시간차 누산기;

상기 제1 누산 신호와 상기 제2 누산 신호간의 시간차를 상기 디지털 출력 신호로 변환하는 시간 도메인 양자화기; 및

상기 디지털 출력 신호를 상기 제1 피드백 신호 및 상기 제2 피드백 신호로 변환하는 디지털 타임 변환기를 포함하는 것을 특징으로 하는 온도 센서.

### 청구항 28

삭제

### 청구항 29

온도를 감지하여 상기 온도에 상응하는 시간차를 가지는 제1 입력 신호 및 제2 입력 신호를 생성하는 센싱부; 및

상기 제1 입력 신호와 상기 제2 입력 신호간의 상기 시간차에 상응하는 디지털 출력 신호를 생성하는 시그마-델타 타임 디지털 변환기를 포함하고,

상기 시그마-델타 타임 디지털 변환기는,

상기 디지털 출력 신호에 기초하여 상기 제1 입력 신호 또는 상기 제2 입력 신호를 상기 디지털 출력 신호에 상응하는 지연 시간만큼 지연시킴으로써 제1 가산 신호 및 제2 가산 신호를 생성하는 시간차 조절부;

상기 제1 가산 신호와 상기 제2 가산 신호간의 시간차를 누산하여 제1 누산 신호 및 제2 누산 신호를 생성하는 시간차 누산기; 및

상기 제1 누산 신호와 상기 제2 누산 신호간의 시간차를 상기 디지털 출력 신호로 변환하는 시간 도메인 양자화기를 포함하는 것을 특징으로 하는 온도 센서.

## 발명의 설명

### 기술 분야

[0001] 본 발명은 신호 처리에 관한 것으로서, 더욱 상세하게는 시간차 가산기를 포함하는 시스템-온-칩(System-on-Chip; SOC), 시간차 누산기를 포함하는 시스템-온-칩, 시그마-델타 타임 디지털 변환기, 디지털 위상 고정 루프 및 온도 센서에 관한 것이다.

### 배경 기술

[0002] 타임 디지털 변환기(Time-to-Digital Converter; TDC)는 입력 신호들간의 시간차(Time Difference)를 디지털 신호로 변환하는 장치이다. 한편, 디자인 룰(Design Rule; DR)이 감소되고 전원 전압이 낮아짐에 따라, 전압 신호의 신호 대 잡음 비(Signal-to-Noise Ratio; SNR)가 낮아지고, 전압 신호를 디지털 신호로 변환하는 아날로그-디지털 변환기(Analog-to-Digital Converter; ADC)의 성능이 악화될 수 있다. 이에 따라, 아날로그-디지털 변환기가 시간차를 디지털 신호로 변환하는 타임 디지털 변환기로 대체될 수 있다.

### 발명의 내용

#### 해결하려는 과제

[0003] 본 발명의 일 목적은 입력 신호들간의 시간차들을 가산하는 시간차 가산기(Time Difference Adder)를 포함하는 시스템-온-칩을 제공하는 것이다.

[0004] 본 발명의 다른 목적은 입력 신호들간의 시간차들을 누산하는 시간차 누산기(Time Difference Accumulator)를 포함하는 시스템-온-칩을 제공하는 것이다.

[0005] 본 발명의 또 다른 목적은 시그마-델타 방식으로 입력 신호들간의 시간차를 디지털 신호로 변환하는 시그마-델타 시간-디지털 변환기(Sigma-Delta Time-to-Digital Converter)를 제공하는 것이다.

[0006] 본 발명의 또 다른 목적은 시그마-델타 시간-디지털 변환기를 포함하는 디지털 위상 고정 루프(Digital Phase Locked Loop; DPLL)를 제공하는 것이다.

[0007] 본 발명의 또 다른 목적은 시그마-델타 시간-디지털 변환기를 포함하는 온도 센서를 제공하는 것이다.

#### 과제의 해결 수단

[0008] 상기 일 목적을 달성하기 위해, 본 발명의 실시예들에 따른 시스템-온-칩에 포함된 시간차 가산기는 제1 레지스터부 및 제2 레지스터부를 포함한다. 상기 제1 레지스터부는 제1 시간차를 가지는 제1 입력 신호 및 제2 입력 신호를 수신하고, 제1 신호에 응답하여 제1 출력 신호를 생성한다. 상기 제2 레지스터부는 제2 시간차를 가지는 제3 입력 신호 및 제4 입력 신호를 수신하고, 상기 제1 신호에 응답하여 상기 제1 출력 신호에 대하여 상기 제1 시간차와 상기 제2 시간차의 합에 상응하는 시간차를 가지는 제2 출력 신호를 생성한다.

[0009] 일 실시예에서, 상기 제1 레지스터부는, 상기 제2 입력 신호를 오프셋 시간만큼 지연시켜 제1 홀드 신호를 생성하는 제1 오프셋 지연기, 및 상기 제1 입력 신호를 수신하는 제1 입력 단자, 상기 제1 홀드 신호를 수신하는 제1 홀드 단자, 상기 제1 신호를 수신하는 제1 어웨이크 단자, 및 상기 제1 출력 신호를 출력하는 제1 출력 단자를 가지는 제1 시간 레지스터를 포함할 수 있다. 상기 제2 레지스터부는, 상기 제3 입력 신호를 상기 오프셋 시간만큼 지연시켜 제2 홀드 신호를 생성하는 제2 오프셋 지연기, 및 상기 제4 입력 신호를 수신하는 제2 입력 단자, 상기 제2 홀드 신호를 수신하는 제2 홀드 단자, 상기 제1 신호를 수신하는 제2 어웨이크 단자, 및 상기 제2 출력 신호를 출력하는 제2 출력 단자를 가지는 제2 시간 레지스터를 포함할 수 있다.

[0010] 일 실시예에서, 상기 제1 시간 레지스터는, 상기 제1 신호의 상승 에지로부터 디스차지 시간에서 상기 오프셋 시간 및 상기 제1 시간차가 감산된 시간 후 상승 에지를 가지는 상기 제1 출력 신호를 출력하고, 상기 제2 시간 레지스터는, 상기 제1 신호의 상기 상승 에지로부터 상기 디스차지 시간에서 상기 오프셋 시간이 감산되고 상기 제2 시간차가 가산된 시간 후 상승 에지를 가지는 상기 제2 출력 신호를 출력할 수 있다.

[0011] 일 실시예에서, 상기 제1 시간 레지스터 및 상기 제2 시간 레지스터는 제1 커패시터 및 제2 커패시터를 각각 포함하고, 상기 제1 커패시터 및 상기 제2 커패시터는 실질적으로 동일한 커패시턴스를 가지며, 상기 디스차지 시간은 상기 실질적으로 동일한 커패시턴스에 따라 결정될 수 있다.

[0012] 일 실시예에서, 상기 제1 시간 레지스터는, 상기 제1 입력 신호를 반전시키는 제1 인버터, 상기 제1 홀드 신호에 응답하여 상기 제1 인버터를 비활성화시키고, 상기 제1 신호에 응답하여 상기 제1 인버터를 활성화시키는 인버터 제어부, 상기 제1 인버터의 출력 신호에 응답하여 충전 또는 방전되는 커패시터, 및 상기 커패시터의 전압에 기초하여 상기 제1 출력 신호를 생성하는 제2 인버터를 포함할 수 있다.

[0013] 일 실시예에서, 상기 커패시터는, 상기 제1 입력 신호와 상기 제1 홀드 신호 사이의 시간차에 상응하는 시간 동안 방전됨으로써, 상기 제1 입력 신호와 상기 제1 홀드 신호 사이의 상기 시간차에 대한 정보를 저장할 수 있다.

- [0014] 일 실시예에서, 상기 커패시터의 방전은, 상기 제1 입력 신호의 상승 에지에 응답하여 시작되고, 상기 제1 홀드 신호의 상승 에지에 응답하여 중지되며, 상기 제1 신호의 상승 에지에 응답하여 재개될 수 있다.

- [0015] 일 실시예에서, 상기 제1 인버터는, 상기 제1 입력 신호가 인가되는 게이트, 상기 인버터 제어부를 통하여 전원 전압에 연결된 소스, 및 중간 노드에 연결된 드레인을 포함하는 제1 PMOS 트랜지스터, 및 상기 제1 입력 신호가 인가되는 게이트, 상기 인버터 제어부를 통하여 접지 전압에 연결된 소스, 및 상기 중간 노드에 연결된 드레인을 포함하는 제1 NMOS 트랜지스터를 포함할 수 있다. 상기 인버터 제어부는, 상기 전원 전압과 상기 제1 PMOS 트랜지스터 사이에 연결된 제2 PMOS 트랜지스터, 상기 접지 전압과 상기 제1 NMOS 트랜지스터 사이에 연결된 제2 NMOS 트랜지스터, 상기 제2 PMOS 트랜지스터의 게이트에 연결된 출력 단자, 상기 제2 NMOS 트랜지스터의 게이트에 연결된 반전 출력 단자, 상기 반전 출력 단자에 연결된 테이터 단자, 및 클록 단자를 포함하는 D-플립플롭, 및 상기 D-플립플롭의 상기 반전 출력 단자에서 출력되는 반전 출력 신호에 응답하여 상기 D-플립플롭의 상기 클록 단자에 상기 제1 홀드 신호 또는 상기 제1 신호를 선택적으로 출력하는 선택기를 포함할 수 있다. 상기 커패시터는 상기 중간 노드와 상기 접지 전압 사이에 연결될 수 있다. 상기 제2 인버터는, 상기 중간 노드에 연결된 게이트, 상기 전원 전압에 연결된 소스, 및 상기 제1 출력 신호가 출력되는 드레인을 포함하는 제3 PMOS 트랜지스터, 및 상기 중간 노드에 연결된 게이트, 상기 접지 전압에 연결된 소스, 및 상기 제1 출력 신호가 출력되는 드레인을 포함하는 제3 NMOS 트랜지스터를 포함할 수 있다.

- [0016] 일 실시예에서, 상기 제1 시간 레지스터는, 상기 제1 입력 신호를 반전시키는 제1 인버터, 상기 제1 홀드 신호에 응답하여 상기 제1 인버터를 비활성화시키고, 상기 제1 신호에 응답하여 상기 제1 인버터를 활성화시키는 인버터 제어부, 상기 제1 인버터의 출력 신호에 응답하여 충전 또는 방전되는 커패시터, 및 상기 커패시터의 전압을 기준 전압과 비교하여 상기 제1 출력 신호를 생성하는 비교기를 포함할 수 있다.

- [0017] 일 실시예에서, 상기 제1 신호는, 상기 제1 입력 신호, 상기 제2 입력 신호, 상기 제3 입력 신호 또는 상기 제4 입력 신호 중 어느 하나의 신호를 지연 또는 반전시켜 생성된 어웨이크 신호일 수 있다.

- [0018] 상기 일 목적을 달성하기 위해, 본 발명의 실시예들에 따른 시스템-온-칩에 포함된 시간차 가산기는 제1 레지스터부 및 제2 레지스터부를 포함한다. 상기 제1 레지스터부는 제1 시간차를 가지는 제1 입력 신호 및 제2 입력 신호를 수신하고, 제1 신호에 응답하여 제1 출력 신호를 생성한다. 상기 제2 레지스터부는 제2 시간차를 가지는 제3 입력 신호 및 제4 입력 신호를 수신하고, 상기 제1 신호에 응답하여 상기 제1 출력 신호에 대하여 상기 제1 시간차와 상기 제2 시간차의 합에 상응하는 시간차를 가지는 제2 출력 신호를 생성한다. 상기 제1 레지스터부는, 상기 제2 입력 신호를 오프셋 시간만큼 지연시켜 제1 홀드 신호를 생성하는 제1 오프셋 지연기, 및 상기 제1 입력 신호를 수신하는 제1 입력 단자, 상기 제1 홀드 신호를 수신하는 제1 홀드 단자, 상기 제1 신호를 수신하는 제1 어웨이크 단자, 및 상기 제1 출력 신호를 출력하는 제1 출력 단자를 가지는 제1 시간 레지스터를 포함한다. 상기 제2 레지스터부는, 상기 제3 입력 신호를 상기 오프셋 시간만큼 지연시켜 제2 홀드 신호를 생성하는 제2 오프셋 지연기, 및 상기 제4 입력 신호를 수신하는 제2 입력 단자, 상기 제2 홀드 신호를 수신하는 제2 홀드 단자, 상기 제1 신호를 수신하는 제2 어웨이크 단자, 및 상기 제2 출력 신호를 출력하는 제2 출력 단자를 가지는 제2 시간 레지스터를 포함한다.

- [0019] 상기 일 목적을 달성하기 위해, 본 발명의 실시예들에 따른 시스템-온-칩에 포함된 시간차 가산기는 제1 레지스터부 및 제2 레지스터부를 포함한다. 상기 제1 레지스터부는 제1 시간차를 가지는 제1 입력 신호 및 제2 입력 신호를 수신하고, 제1 신호에 응답하여 제1 출력 신호를 생성한다. 상기 제2 레지스터부는 제2 시간차를 가지는 제3 입력 신호 및 제4 입력 신호를 수신하고, 상기 제1 신호에 응답하여 상기 제1 출력 신호에 대하여 상기 제1 시간차와 상기 제2 시간차의 합에 상응하는 시간차를 가지는 제2 출력 신호를 생성한다. 상기 제1 레지스터부는, 상기 제1 입력 신호를 수신하는 제1 입력 단자, 상기 제2 입력 신호를 수신하는 제1 홀드 단자, 상기 제1 신호를 수신하는 제1 어웨이크 단자, 및 상기 제1 출력 신호를 출력하는 제1 출력 단자를 가지는 제1 시간 레지스터를 포함하고, 상기 제2 레지스터부는, 상기 제4 입력 신호를 수신하는 제2 입력 단자, 상기 제3 입력 신호를 수신하는 제2 홀드 단자, 상기 제1 신호를 수신하는 제2 어웨이크 단자, 및 상기 제2 출력 신호를 출력하는 제2 출력 단자를 가지는 제2 시간 레지스터를 포함한다.

- [0020] 일 실시예에서, 상기 제1 시간 레지스터는, 상기 제1 신호의 상승 에지로부터 디스차지 시간에서 상기 제1 시간 차가 감산된 시간 후 상승 에지를 가지는 상기 제1 출력 신호를 출력하고, 상기 제2 시간 레지스터는, 상기 제1 신호의 상기 상승 에지로부터 상기 디스차지 시간에 상기 제2 시간차가 가산된 시간 후 상승 에지를 가지는 상기 제2 출력 신호를 출력할 수 있다.

- [0021] 상기 일 목적을 달성하기 위해, 본 발명의 실시예들에 따른 시스템-온-칩에 포함된 시간차 가산기는 제1 레지스

터부 및 제2 레지스터부를 포함한다. 상기 제1 레지스터부는 제1 시간차를 가지는 제1 입력 신호 및 제2 입력 신호를 수신하고, 제1 신호에 응답하여 제1 출력 신호를 생성한다. 상기 제2 레지스터부는 제2 시간차를 가지는 제3 입력 신호 및 제4 입력 신호를 수신하고, 상기 제1 신호에 응답하여 상기 제1 출력 신호에 대하여 상기 제1 시간차와 상기 제2 시간차의 합에 상응하는 시간차를 가지는 제2 출력 신호를 생성한다. 상기 제1 레지스터부는, 상기 제2 입력 신호를 오프셋 시간만큼 지연시켜 제1 홀드 신호를 생성하는 제1 오프셋 지연기, 및 상기 제1 입력 신호를 수신하는 제1 입력 단자, 상기 제1 홀드 신호를 수신하는 제1 홀드 단자, 제2 신호를 수신하는 제1 프리차지 단자, 상기 제1 신호를 수신하는 제1 어웨이크 단자, 및 상기 제1 출력 신호를 출력하는 제1 출력 단자를 가지는 제1 시간 레지스터를 포함한다. 상기 제2 레지스터부는, 상기 제3 입력 신호를 상기 오프셋 시간만큼 지연시켜 제2 홀드 신호를 생성하는 제2 오프셋 지연기, 및 상기 제4 입력 신호를 수신하는 제2 입력 단자, 상기 제2 홀드 신호를 수신하는 제2 홀드 단자, 상기 제2 신호를 수신하는 제1 프리차지 단자, 상기 제1 신호를 수신하는 제2 어웨이크 단자, 및 상기 제2 출력 신호를 출력하는 제2 출력 단자를 가지는 제2 시간 레지스터를 포함한다.

[0022] 일 실시예에서, 상기 제1 시간 레지스터는, 중간 노드와 접지 전압 사이에 연결된 커패시터, 상기 중간 노드와 상기 전원 전압 사이에 연결되고, 상기 제2 신호에 응답하여 상기 커패시터를 충전시키는 폴-업 트랜지스터, 상기 중간 노드와 상기 접지 전압 사이에 연결된 폴-다운 트랜지스터, 상기 제1 입력 신호에 응답하여 상기 폴-다운 트랜지스터를 턴-온시키고, 상기 홀드 신호에 응답하여 상기 폴-다운 트랜지스터를 턴-오프시키며, 상기 제1 신호에 응답하여 상기 폴-다운 트랜지스터를 턴-온시키는 폴-다운 트랜지스터 제어부, 및 상기 커패시터의 전압에 기초하여 상기 제1 출력 신호를 생성하는 출력부를 포함할 수 있다.

[0023] 일 실시예에서, 상기 폴-다운 트랜지스터 제어부는, 상기 제1 입력 신호를 수신하는 셋 단자, 상기 제1 홀드 신호를 수신하는 리셋 단자, 및 출력 단자를 포함하는 셋-리셋 래치, 및 상기 셋-리셋 래치의 상기 출력 단자에서 출력된 출력 신호 및 상기 제1 신호에 OR 연산을 수행하고, 상기 폴-다운 트랜지스터의 게이트에 연결된 출력 단자를 포함하는 OR 게이트를 포함할 수 있다.

[0024] 일 실시예에서, 상기 시간차 가산기는 상기 제1 신호 및 상기 제2 신호를 생성하는 제어부를 더 포함할 수 있다. 상기 제어부는, 상기 제1 입력 신호를 반전시켜 상기 제1 입력 신호의 반전 신호를 생성하는 제1 인버터, 상기 제1 입력 신호의 상기 반전 신호를 지연시키는 어웨이크 지연기, 상기 제1 입력 신호의 상기 반전 신호를 수신하는 셋 단자, 상기 어웨이크 지연기의 출력 신호를 수신하는 리셋 단자, 및 상기 제1 신호를 출력하는 출력 단자를 가지는 제1 셋-리셋 래치, 상기 어웨이크 지연기의 상기 출력 신호를 지연시키는 프리차지 지연기, 상기 어웨이크 지연기의 상기 출력 신호를 수신하는 셋 단자, 상기 프리차지 지연기의 출력 신호를 수신하는 리셋 단자, 및 출력 단자를 가지는 제2 셋-리셋 래치, 및 상기 제2 셋-리셋 래치의 출력 신호를 반전시켜 상기 제2 신호를 생성하는 제2 인버터를 포함할 수 있다.

[0025] 상기 일 목적을 달성하기 위해, 본 발명의 실시예들에 따른 시스템-온-칩에 포함된 시간차 가산기는 제1 레지스터부 및 제2 레지스터부를 포함한다. 상기 제1 레지스터부는 제1 시간차를 가지는 제1 입력 신호 및 제2 입력 신호를 수신하고, 제1 신호에 응답하여 제1 출력 신호를 생성한다. 상기 제2 레지스터부는 제2 시간차를 가지는 제3 입력 신호 및 제4 입력 신호를 수신하고, 상기 제1 신호에 응답하여 상기 제1 출력 신호에 대하여 상기 제1 시간차와 상기 제2 시간차의 합에 상응하는 시간차를 가지는 제2 출력 신호를 생성한다. 상기 제1 레지스터부는, 상기 제1 입력 신호를 수신하는 제1 입력 단자, 상기 제2 입력 신호를 수신하는 제1 홀드 단자, 제2 신호를 수신하는 제1 프리차지 단자, 상기 제1 신호를 수신하는 제1 어웨이크 단자, 및 상기 제1 출력 신호를 출력하는 제1 출력 단자를 가지는 제1 시간 레지스터를 포함하고, 상기 제2 레지스터부는, 상기 제4 입력 신호를 수신하는 제2 입력 단자, 상기 제3 입력 신호를 수신하는 제2 홀드 단자, 상기 제2 신호를 수신하는 제1 프리차지 단자, 상기 제1 신호를 수신하는 제2 어웨이크 단자, 및 상기 제2 출력 신호를 출력하는 제2 출력 단자를 가지는 제2 시간 레지스터를 포함할 수 있다.

[0026] 상기 다른 목적을 달성하기 위해, 본 발명의 실시예들에 따른 시스템-온-칩에 포함된 시간차 누산기는 제1 시간차 가산기 및 제2 시간차 가산기를 포함한다. 상기 제1 시간차 가산기는 제1 입력 신호와 제2 입력 신호간의 제1 시간차 및 제1 이전 출력 신호와 제2 이전 출력 신호간의 제2 시간차를 가산하여 상기 제1 시간차와 상기 제2 시간차의 합에 상응하는 제3 시간차를 가지는 제1 출력 신호 및 제2 출력 신호를 생성한다. 상기 제2 시간차 가산기는 상기 제1 출력 신호와 상기 제2 출력 신호간의 상기 제3 시간차 및 실질적으로 동일한 신호들간의 시간차를 가산하여 상기 제3 시간차를 가지는 상기 제1 이전 출력 신호 및 상기 제2 이전 출력 신호를 생성한다.

[0027] 일 실시예에서, 상기 실질적으로 동일한 신호들은 상기 제1 출력 신호, 상기 제2 출력 신호, 상기 제1 출력 신

호의 반전 신호, 또는 상기 제2 출력 신호의 반전 신호 중 어느 하나일 수 있다.

[0028] 상기 다른 목적을 달성하기 위해, 본 발명의 실시예들에 따른 시스템-온-칩에 포함된 시간차 누산기는 시간차 가산기, 제1 지연기 및 제2 지연기를 포함한다. 상기 시간차 가산기는 제1 입력 신호와 제2 입력 신호간의 제1 시간차 및 제1 이전 출력 신호와 제2 이전 출력 신호간의 제2 시간차를 가산하여 상기 제1 시간차와 상기 제2 시간차의 합에 상응하는 제3 시간차를 가지는 제1 출력 신호 및 제2 출력 신호를 생성한다. 상기 제1 지연기는 상기 제1 출력 신호를 소정의 시간만큼 지연시켜 상기 제1 이전 출력 신호를 생성한다. 상기 제2 지연기는 상기 제2 출력 신호를 상기 소정의 시간만큼 지연시켜 상기 제2 이전 출력 신호를 생성한다.

[0029] 상기 또 다른 목적을 달성하기 위해, 본 발명의 실시예들에 따른 시그마-델타 타임 디지털 변환기는 시간차 가산기, 시간차 누산기, 시간 도메인 양자화기 및 디지털 타임 변환기를 포함한다. 상기 시간차 가산기는 제1 입력 신호와 제2 입력 신호간의 제1 시간차에서 제1 피드백 신호와 제2 피드백 신호간의 제2 시간차를 감산하여 상기 제1 시간차에서 상기 제2 시간차가 감산된 제3 시간차를 가지는 제1 가산 신호 및 제2 가산 신호를 생성한다. 상기 시간차 누산기는 상기 제1 가산 신호와 상기 제2 가산 신호간의 상기 제3 시간차를 누산하여 제1 누산 신호 및 제2 누산 신호를 생성한다. 상기 시간 도메인 양자화기는 상기 제1 누산 신호와 상기 제2 누산 신호간의 시간차를 디지털 출력 신호로 변환한다. 상기 디지털 타임 변환기는 상기 디지털 출력 신호를 상기 제1 피드백 신호 및 상기 제2 피드백 신호로 변환한다.

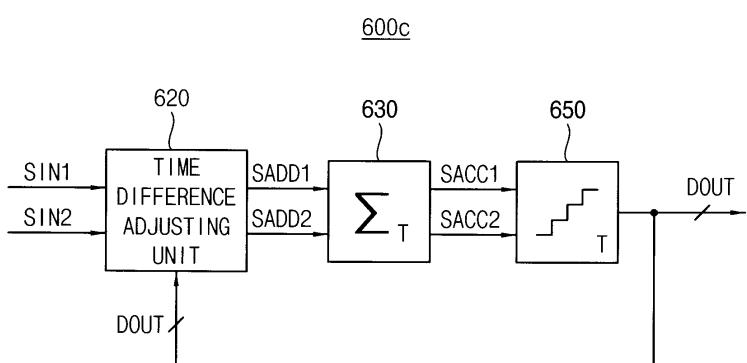

[0030] 상기 또 다른 목적을 달성하기 위해, 본 발명의 실시예들에 따른 시그마-델타 타임 디지털 변환기는 시간차 조절부, 시간차 누산기 및 시간 도메인 양자화기를 포함한다. 상기 시간차 조절부는 제1 입력 신호, 제2 입력 신호 및 디지털 출력 신호를 수신하고, 상기 디지털 출력 신호에 기초하여 상기 제1 입력 신호 또는 상기 제2 입력 신호를 상기 디지털 출력 신호에 상응하는 지연 시간만큼 지연시킴으로써 제1 가산 신호 및 제2 가산 신호를 생성한다. 상기 시간차 누산기는 상기 제1 가산 신호와 상기 제2 가산 신호간의 시간차를 누산하여 제1 누산 신호 및 제2 누산 신호를 생성한다. 상기 시간 도메인 양자화기는 상기 제1 누산 신호와 상기 제2 누산 신호간의 시간차를 상기 디지털 출력 신호로 변환한다.

[0031] 일 실시예에서, 상기 시간차 조절부는, 상기 제1 입력 신호 또는 상기 제2 입력 신호 중 적어도 하나의 신호를 지연시키는 적어도 하나의 지연기, 및 상기 디지털 출력 신호에 응답하여 상기 지연기에 의해 지연되지 않은 상기 적어도 하나의 신호 또는 상기 지연기에 의해 지연된 상기 지연기의 출력 신호를 선택적으로 출력하는 적어도 하나의 선택기를 포함할 수 있다.

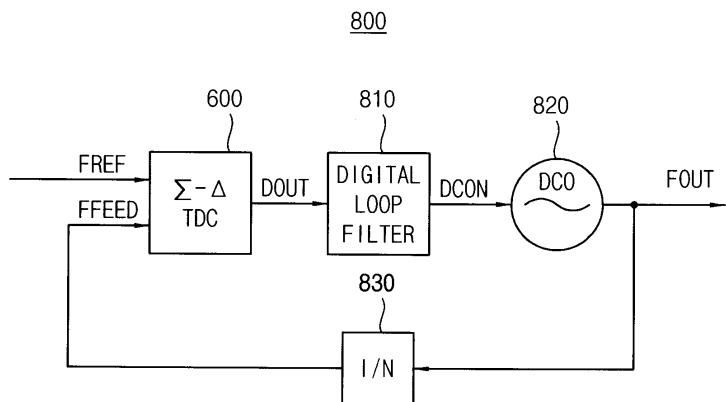

[0032] 상기 또 다른 목적을 달성하기 위해, 본 발명의 실시예들에 따른 디지털 위상 고정 루프는 위상 검출기, 디지털 루프 필터, 디지털 제어 발진기 및 분주기를 포함한다. 상기 위상 검출기는 기준 입력 신호와 피드백 신호간의 제1 시간차에 상응하는 디지털 시간차 신호를 생성한다. 상기 디지털 루프 필터는 상기 디지털 시간차 신호를 필터링하여 디지털 제어 신호를 생성한다. 상기 디지털 제어 발진기는 상기 디지털 제어 신호에 응답하여 출력 신호를 생성한다. 상기 분주기는 상기 출력 신호를 분주하여 상기 피드백 신호를 생성한다. 상기 위상 검출기는, 상기 기준 입력 신호와 상기 피드백 신호간의 상기 제1 시간차에서 제1 내부 피드백 신호와 제2 내부 피드백 신호간의 제2 시간차를 감산하여 상기 제1 시간차에서 상기 제2 시간차가 감산된 제3 시간차를 가지는 제1 가산 신호 및 제2 가산 신호를 생성하는 시간차 가산기, 상기 제1 가산 신호와 상기 제2 가산 신호간의 상기 제3 시간차를 누산하여 제1 누산 신호 및 제2 누산 신호를 생성하는 시간차 누산기, 상기 제1 누산 신호와 상기 제2 누산 신호간의 시간차를 상기 디지털 시간차 신호로 변환하는 시간 도메인 양자화기, 및 상기 디지털 시간차 신호를 상기 제1 내부 피드백 신호 및 상기 제2 내부 피드백 신호로 변환하는 디지털 타임 변환기를 포함한다.

[0033] 상기 또 다른 목적을 달성하기 위해, 본 발명의 실시예들에 따른 디지털 위상 고정 루프는 위상 검출기, 디지털 루프 필터, 디지털 제어 발진기 및 분주기를 포함한다. 상기 위상 검출기는 기준 입력 신호와 피드백 신호간의 시간차에 상응하는 디지털 시간차 신호를 생성한다. 상기 디지털 루프 필터는 상기 디지털 시간차 신호를 필터링하여 디지털 제어 신호를 생성한다. 상기 디지털 제어 발진기는 상기 디지털 제어 신호에 응답하여 출력 신호를 생성한다. 상기 분주기는 상기 출력 신호를 분주하여 상기 피드백 신호를 생성한다. 상기 위상 검출기는, 상기 디지털 시간차 신호에 기초하여 상기 기준 입력 신호 또는 상기 피드백 신호를 상기 디지털 시간차 신호에 상응하는 지연 시간만큼 지연시킴으로써 제1 가산 신호 및 제2 가산 신호를 생성하는 시간차 조절부, 상기 제1 가산 신호와 상기 제2 가산 신호간의 시간차를 누산하여 제1 누산 신호 및 제2 누산 신호를 생성하는 시간차 누산기, 및 상기 제1 누산 신호와 상기 제2 누산 신호간의 시간차를 상기 디지털 시간차 신호로 변환하는 시간 도메인 양자화기를 포함한다.

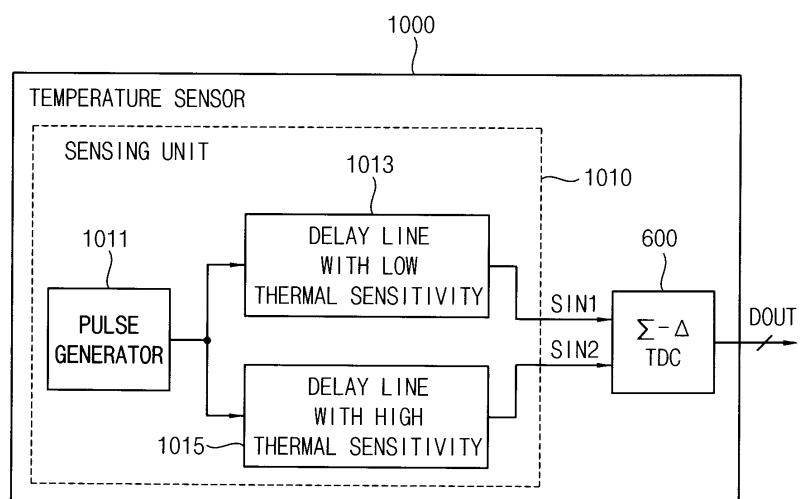

[0034] 상기 또 다른 목적을 달성하기 위해, 본 발명의 실시예들에 따른 온도 센서는 센싱부 및 시그마-델타 타임 디지털 변환기를 포함한다. 상기 센싱부는 온도를 감지하여 상기 온도에 상응하는 제1 시간차를 가지는 제1 입력 신호 및 제2 입력 신호를 생성한다. 상기 시그마-델타 타임 디지털 변환기는 상기 제1 입력 신호와 상기 제2 입력 신호간의 상기 제1 시간차에 상응하는 디지털 출력 신호를 생성한다. 상기 시그마-델타 타임 디지털 변환기는, 상기 제1 입력 신호와 상기 제2 입력 신호간의 상기 제1 시간차에서 제1 피드백 신호와 제2 피드백 신호간의 제2 시간차를 감산하여 상기 제1 시간차에서 상기 제2 시간차가 감산된 제3 시간차를 가지는 제1 가산 신호 및 제2 가산 신호를 생성하는 시간차 가산기, 상기 제1 가산 신호와 상기 제2 가산 신호간의 상기 제3 시간차를 누산하여 제1 누산 신호 및 제2 누산 신호를 생성하는 시간차 누산기, 상기 제1 누산 신호와 상기 제2 누산 신호간의 시간차를 상기 디지털 출력 신호로 변환하는 시간 도메인 양자화기, 및 상기 디지털 출력 신호를 상기 제1 피드백 신호 및 상기 제2 피드백 신호로 변환하는 디지털 타임 변환기를 포함한다.

[0035] 일 실시예에서, 상기 센싱부는, 펠스를 생성하는 펠스 생성기, 상기 펠스를 실질적으로 일정한 제1 지연 시간만큼 지연시켜 상기 제1 입력 신호로서 출력하는 온도 둔감 지연 라인, 및 상기 펠스를 온도에 따라 변경되는 제2 지연 시간만큼 지연시켜 상기 제2 입력 신호로서 출력하는 온도 민감 지연 라인을 포함할 수 있다.

[0036] 상기 또 다른 목적을 달성하기 위해, 본 발명의 실시예들에 따른 온도 센서는 센싱부 및 시그마-델타 타임 디지털 변환기를 포함한다. 상기 센싱부는 온도를 감지하여 상기 온도에 상응하는 시간차를 가지는 제1 입력 신호 및 제2 입력 신호를 생성한다. 상기 시그마-델타 타임 디지털 변환기는 상기 제1 입력 신호와 상기 제2 입력 신호간의 상기 시간차에 상응하는 디지털 출력 신호를 생성한다. 상기 시그마-델타 타임 디지털 변환기는, 상기 디지털 출력 신호에 기초하여 상기 제1 입력 신호 또는 상기 제2 입력 신호를 상기 디지털 출력 신호에 상응하는 지연 시간만큼 더욱 지연시킴으로써 제1 가산 신호 및 제2 가산 신호를 생성하는 시간차 조절부, 상기 제1 가산 신호와 상기 제2 가산 신호간의 시간차를 누산하여 제1 누산 신호 및 제2 누산 신호를 생성하는 시간차 누산기, 및 상기 제1 누산 신호와 상기 제2 누산 신호간의 시간차를 상기 디지털 출력 신호로 변환하는 시간 도메인 양자화기를 포함한다.

### 발명의 효과

[0037] 본 발명의 실시예들에 따른 시간차 가산기를 포함하는 시스템-온-칩은 입력 신호들간의 시간차들을 정확하게 가산할 수 있다.

[0038] 또한, 본 발명의 실시예들에 따른 시간차 누산기를 포함하는 시스템-온-칩은 입력 신호들간의 시간차들을 정확하게 누산할 수 있다.

[0039] 또한, 본 발명의 실시예들에 따른 시그마-델타 타임 디지털 변환기는 입력 신호들간의 시간차를 고해상도(High Resolution)를 가지는 디지털 신호로 변환할 수 있다.

[0040] 또한, 본 발명의 실시예들에 따른 디지털 위상 고정 루프는 상기 시그마-델타 타임 디지털 변환기를 포함하여 낮은 전원 전압 환경에서도 원하는 주파수를 가지는 신호를 정확하게 출력할 수 있다.

[0041] 또한, 본 발명의 실시예들에 따른 온도 센서는 상기 시그마-델타 타임 디지털 변환기를 포함하여 낮은 전원 전압 환경에서도 온도를 정확하게 감지할 수 있다.

### 도면의 간단한 설명

[0042] 도 1은 본 발명의 실시예들에 따른 시간차 가산기를 나타내는 도면이다.

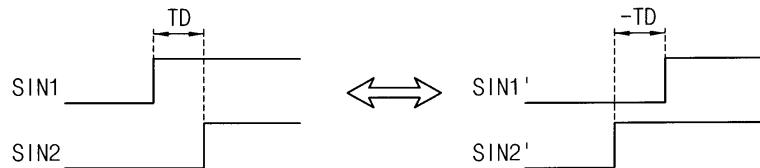

도 2a 및 도 2b는 도 1의 시간차 가산기에서 수행되는 시간차 가산의 항등원 및 역원을 나타내는 도면들이다.

도 3은 본 발명의 일 실시예에 따른 시간차 가산기를 나타내는 블록도이다.

도 4는 도 3의 시간차 가산기에 포함된 시간 레지스터의 일 예를 나타내는 회로도이다.

도 5는 도 4의 시간 레지스터의 동작을 설명하기 위한 타이밍도이다.

도 6은 도 3의 시간차 가산기에 포함된 시간 레지스터의 다른 예를 나타내는 회로도이다.

도 7은 도 3의 시간차 가산기에 포함된 시간 레지스터의 또 다른 예를 나타내는 회로도이다.

도 8은 도 3의 시간차 가산기에 포함된 시간 레지스터의 또 다른 예를 나타내는 회로도이다.

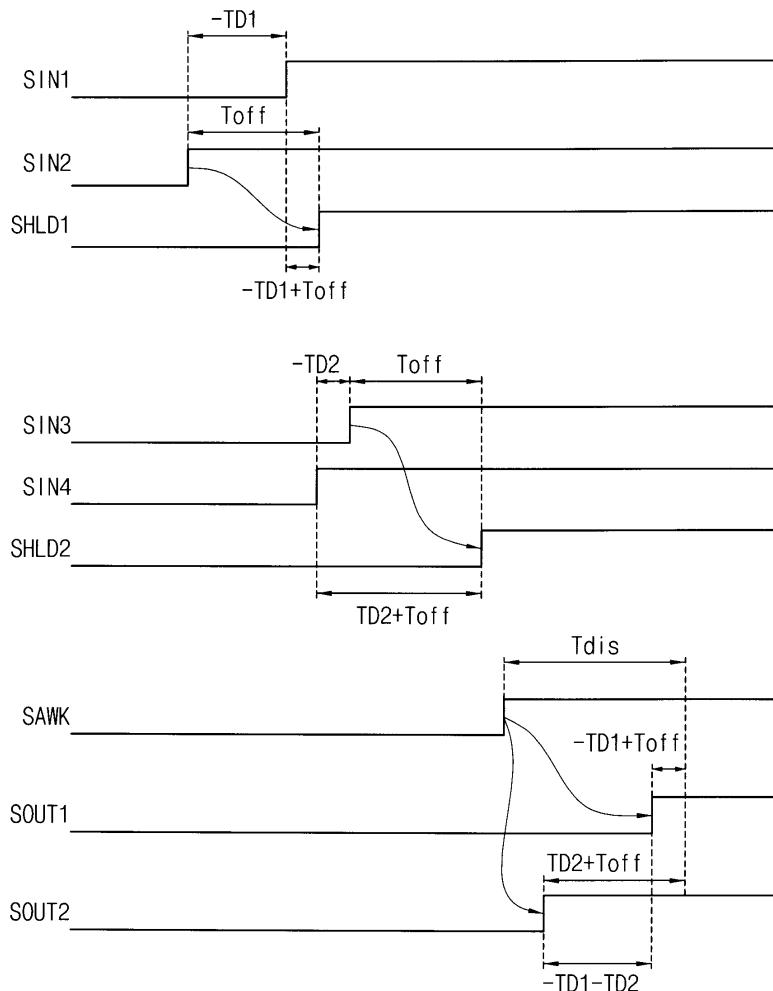

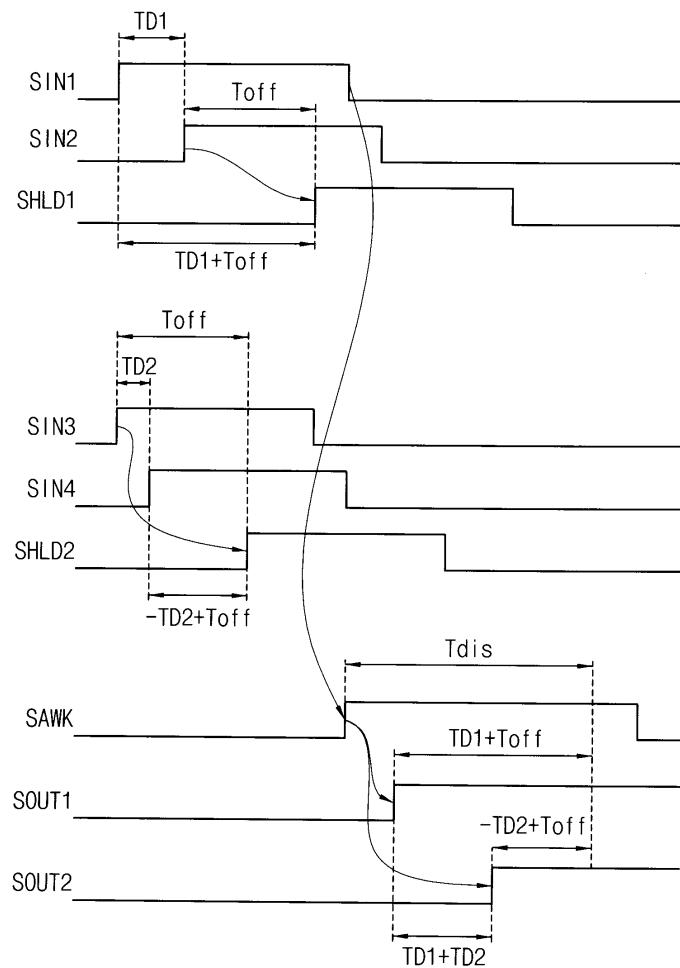

도 9a는 도 3의 시간차 가산기의 동작의 일 예를 설명하기 위한 타이밍도이다.

도 9b는 도 3의 시간차 가산기의 동작의 다른 예를 설명하기 위한 타이밍도이다.

도 10은 본 발명의 다른 실시예에 따른 시간차 가산기를 나타내는 블록도이다.

도 11은 도 10의 시간차 가산기의 동작의 일 예를 설명하기 위한 타이밍도이다.

도 12는 본 발명의 또 다른 실시예에 따른 시간차 가산기를 나타내는 블록도이다.

도 13은 도 12의 시간차 가산기에 포함된 시간 레지스터의 일 예를 나타내는 회로도이다.

도 14는 도 12의 시간차 가산기에 포함된 제어부의 일 예를 나타내는 회로도이다.

도 15는 도 13의 시간 레지스터의 동작을 설명하기 위한 타이밍도이다.

도 16은 도 12의 시간차 가산기에 포함된 시간 레지스터의 다른 예를 나타내는 회로도이다.

도 17은 도 12의 시간차 가산기의 동작의 일 예를 설명하기 위한 타이밍도이다.

도 18은 본 발명의 또 다른 실시예에 따른 시간차 가산기를 나타내는 블록도이다.

도 19는 본 발명의 실시예들에 따른 시간차 누산기를 나타내는 도면이다.

도 20은 본 발명의 일 실시예에 따른 시간차 누산기를 나타내는 블록도이다.

도 21은 본 발명의 다른 실시예에 따른 시간차 누산기를 나타내는 블록도이다.

도 22는 도 21의 시간차 누산기에 포함된 지연부의 일 예를 나타내는 회로도이다.

도 23은 도 22의 지연부에 포함된 트랜지스터들의 배치의 일 예를 설명하기 위한 도면이다.

도 24는 본 발명의 일 실시예에 따른 시그마-델타 타임 디지털 변환기를 나타내는 블록도이다.

도 25는 도 24의 시그마-델타 타임 디지털 변환기에서 수행되는 노이즈 쉐이핑을 설명하기 위한 도면이다.

도 26은 도 24의 시그마-델타 타임 디지털 변환기에 포함된 시간 도메인 양자화기의 일 예를 나타내는 블록도이다.

도 27은 도 24의 시그마-델타 타임 디지털 변환기에 포함된 시간 도메인 양자화기의 다른 예를 나타내는 블록도이다.

도 28은 도 24의 시그마-델타 타임 디지털 변환기에 포함된 디지털 타임 변환기의 일 예를 나타내는 블록도이다.

도 29는 도 24의 시그마-델타 타임 디지털 변환기에 포함된 디지털 타임 변환기의 다른 예를 나타내는 블록도이다.

도 30은 본 발명의 다른 실시예에 따른 시그마-델타 타임 디지털 변환기를 나타내는 블록도이다.

도 31은 본 발명의 또 다른 실시예에 따른 시그마-델타 타임 디지털 변환기를 나타내는 블록도이다.

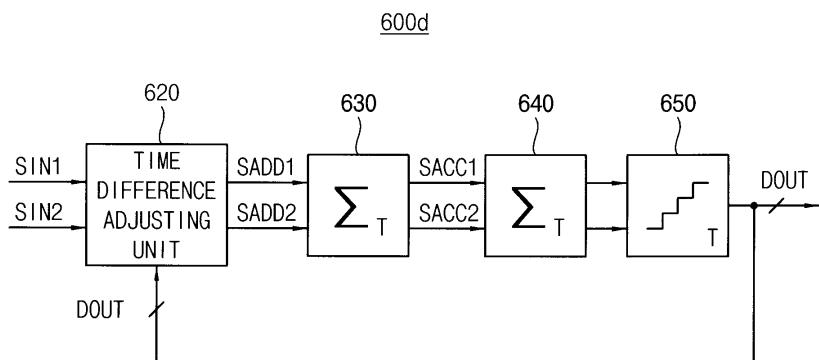

도 32는 도 31의 시그마-델타 타임 디지털 변환기의 일 예를 나타내는 블록도이다.

도 33은 도 31의 시그마-델타 타임 디지털 변환기의 다른 예를 나타내는 블록도이다.

도 34는 본 발명의 또 다른 실시예에 따른 시그마-델타 타임 디지털 변환기를 나타내는 블록도이다.

도 35는 본 발명의 실시예들에 따른 디지털 위상 고정 루프를 나타내는 블록도이다.

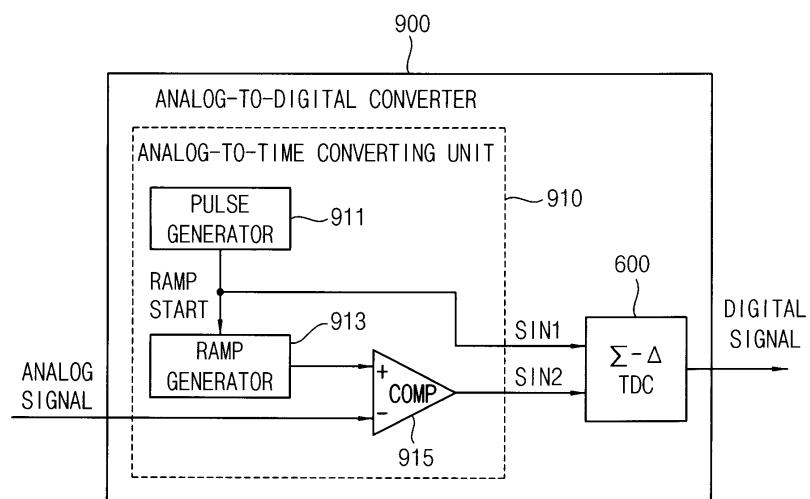

도 36은 본 발명의 실시예들에 따른 시그마-델타 타임 디지털 변환기를 포함하는 아날로그 디지털 변환기를 나타내는 블록도이다.

도 37은 본 발명의 실시예들에 따른 시그마-델타 타임 디지털 변환기를 포함하는 센서를 나타내는 블록도이다.

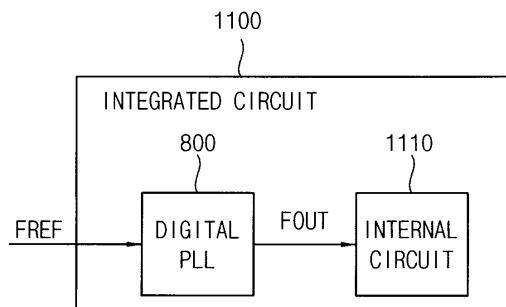

도 38은 본 발명의 실시예들에 따른 디지털 위상 고정 루프를 포함하는 집적 회로를 나타내는 블록도이다.

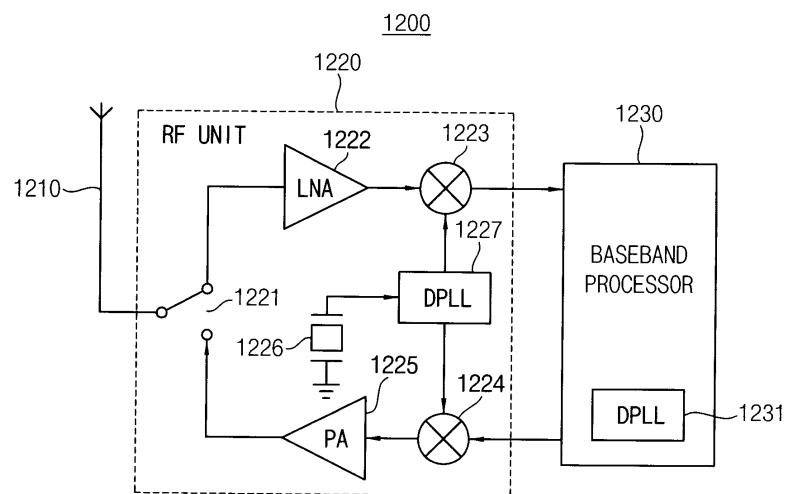

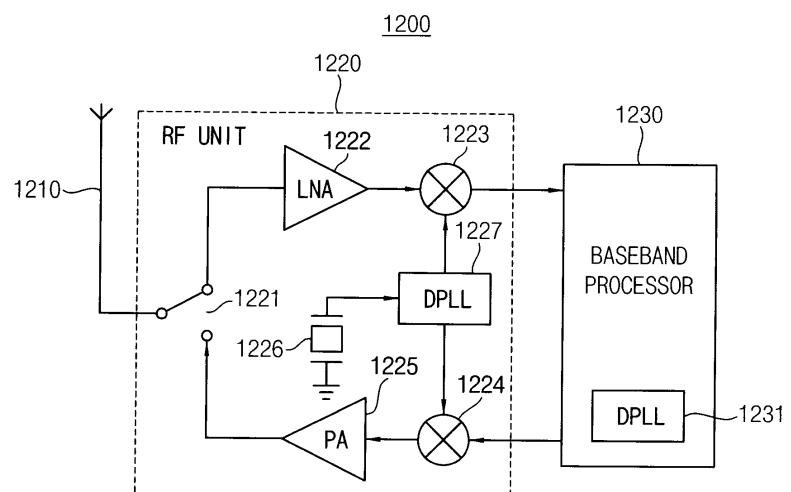

도 39는 본 발명의 실시예들에 따른 디지털 위상 고정 루프를 포함하는 송수신기를 나타내는 블록도이다.

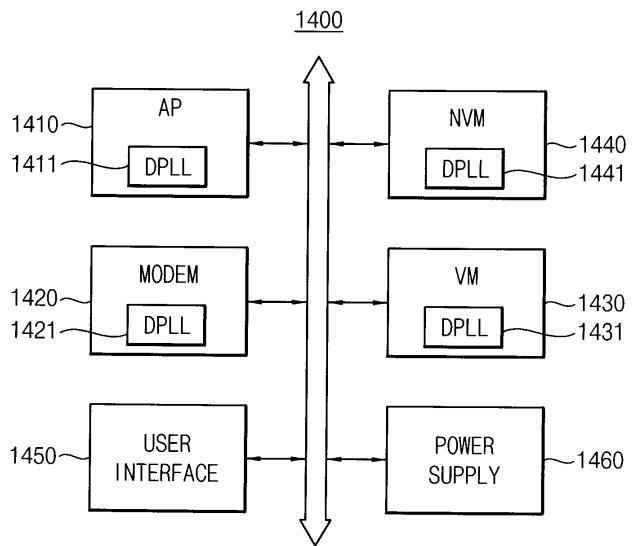

도 40은 본 발명의 실시예들에 따른 디지털 위상 고정 루프를 포함하는 메모리 장치를 나타내는 블록도이다.

도 41은 본 발명의 실시예들에 따른 디지털 위상 고정 루프를 모바일 시스템에 응용한 예를 나타내는 블록도이다.

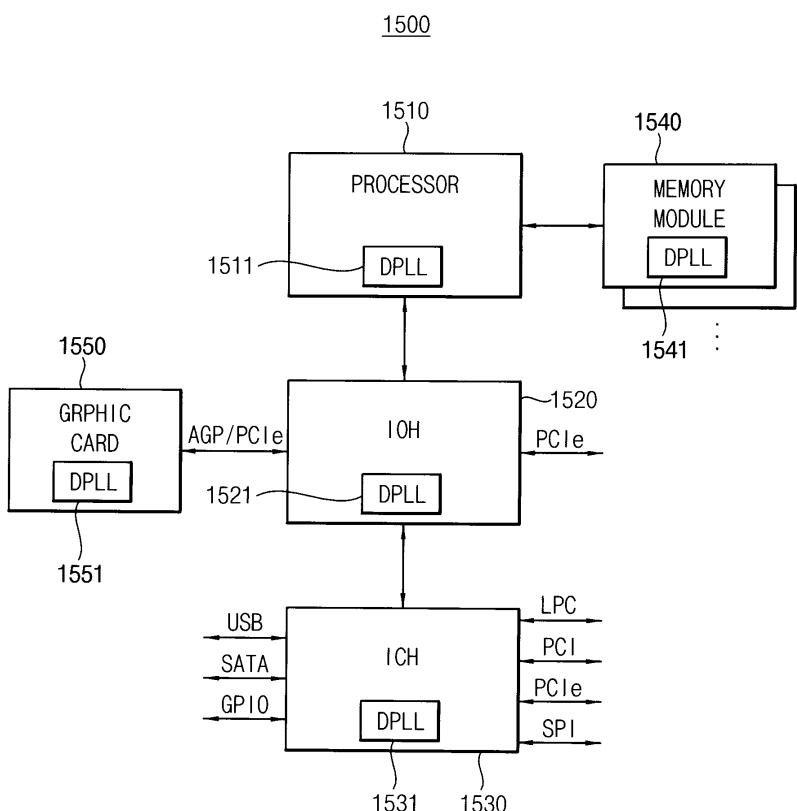

도 42는 본 발명의 실시예들에 따른 디지털 위상 고정 루프를 컴퓨팅 시스템에 응용한 예를 나타내는 블록도이다.

### 발명을 실시하기 위한 구체적인 내용

[0043]

본문에 개시되어 있는 본 발명의 실시예들에 대해서, 특정한 구조적 내지 기능적 설명들은 단지 본 발명의 실시예를 설명하기 위한 목적으로 예시된 것으로, 본 발명의 실시예들은 다양한 형태로 실시될 수 있으며 본문에 설명된 실시예들에 한정되는 것으로 해석되어서는 아니 된다.

[0044]

본 발명은 다양한 변경을 가할 수 있고 여러 가지 형태를 가질 수 있는바, 특정 실시예들을 도면에 예시하고 본문에 상세하게 설명하고자 한다. 그러나 이는 본 발명을 특정한 개시 형태에 대해 한정하려는 것이 아니며, 본 발명의 사상 및 기술 범위에 포함되는 모든 변경, 균등물 내지 대체물을 포함하는 것으로 이해되어야 한다.

[0045]

제1, 제2 등의 용어는 다양한 구성 요소들을 설명하는데 사용될 수 있지만, 상기 구성요소들은 상기 용어들에 의해 한정되어서는 안 된다. 상기 용어들은 하나의 구성요소를 다른 구성 요소로부터 구별하는 목적으로 사용될 수 있다. 예를 들어, 본 발명의 권리 범위로부터 이탈되지 않은 채 제1 구성 요소는 제2 구성 요소로 명명될 수 있고, 유사하게 제2 구성 요소도 제1 구성 요소로 명명될 수 있다.

[0046]

어떤 구성 요소가 다른 구성 요소에 "연결되어" 있다거나 "접속되어" 있다고 언급된 때에는, 그 다른 구성 요소에 직접적으로 연결되어 있거나 또는 접속되어 있을 수도 있지만, 중간에 다른 구성 요소가 존재할 수도 있다고 이해되어야 할 것이다. 반면에, 어떤 구성 요소가 다른 구성 요소에 "직접 연결되어" 있다거나 "직접 접속되어" 있다고 언급된 때에는, 중간에 다른 구성요소가 존재하지 않는 것으로 이해되어야 할 것이다. 구성 요소들 간의 관계를 설명하는 다른 표현들, 즉 "~사이에"와 "바로 ~사이에" 또는 "~에 이웃하는"과 "~에 직접 이웃하는" 등도 마찬가지로 해석되어야 한다.

[0047]

본 출원에서 사용한 용어는 단지 특정한 실시예를 설명하기 위해 사용된 것으로, 본 발명을 한정하려는 의도가 아니다. 단수의 표현은 문맥상 명백하게 다르게 뜻하지 않는 한, 복수의 표현을 포함한다. 본 출원에서, "포함하다" 또는 "가지다" 등의 용어는 실시된 특징, 숫자, 단계, 동작, 구성요소, 부분품 또는 이들을 조합한 것이 존재함을 지정하려는 것이지, 하나 또는 그 이상의 다른 특징들이나 숫자, 단계, 동작, 구성요소, 부분품 또는 이들을 조합한 것들의 존재 또는 부가 가능성을 미리 배제하지 않는 것으로 이해되어야 한다.

[0048]

다르게 정의되지 않는 한, 기술적이거나 과학적인 용어를 포함해서 여기서 사용되는 모든 용어들은 본 발명이 속하는 기술분야에서 통상의 지식을 가진 자에 의해 일반적으로 이해되는 것과 동일한 의미이다. 일반적으로 사용되는 사전에 정의되어 있는 것과 같은 용어들은 관련 기술의 문맥상 가지는 의미와 일치하는 의미인 것으로 해석되어야 하며, 본 출원에서 명백하게 정의하지 않는 한, 이상적이거나 과도하게 형식적인 의미로 해석되지 않는다.

[0049]

이하, 첨부한 도면들을 참조하여, 본 발명의 실시예들을 보다 상세하게 설명하고자 한다. 도면상의 동일한 구성요소에 대해서는 동일하거나 유사한 참조 부호를 사용한다.

[0050]

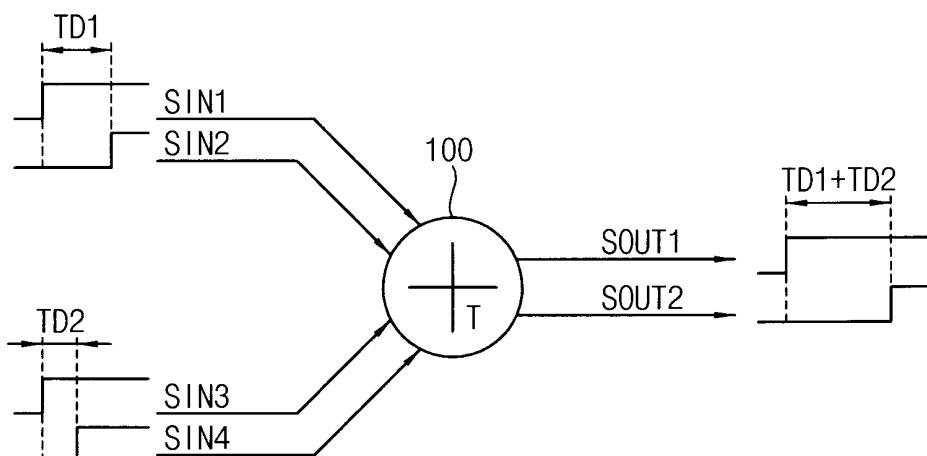

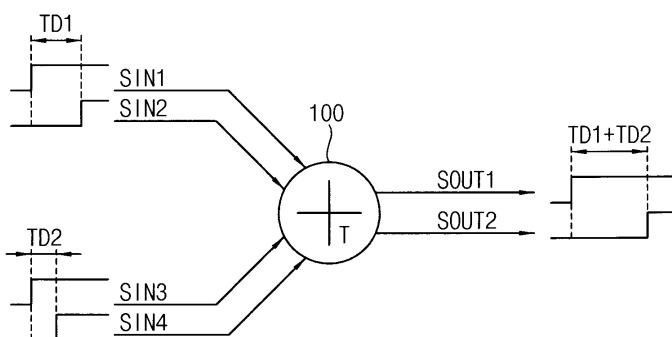

도 1은 본 발명의 실시예들에 따른 시간차 가산기를 나타내는 도면이고, 도 2a 및 도 2b는 도 1의 시간차 가산기에서 수행되는 시간차 가산의 항등원 및 역원을 나타내는 도면들이다.

[0051]

도 1을 참조하면, 시간차 가산기(100)는 제1 입력 신호(SIN1), 제2 입력 신호(SIN2), 제3 입력 신호(SIN3) 및 제4 입력 신호(SIN4)에 응답하여 제1 출력 신호(SOUT1) 및 제2 출력 신호(SOUT2)를 생성한다. 시간차 가산기(100)는 제1 입력 신호(SIN1)와 제2 입력 신호(SIN2)간의 제1 시간차(TD1) 및 제3 입력 신호(SIN3)와 제4 입력 신호(SIN4)간의 제2 시간차(TD2)를 가산함으로써 제1 시간차(TD1)와 제2 시간차(TD2)의 합에 상응하는 시간차(TD1+TD2)를 가지는 제1 출력 신호(SOUT1) 및 제2 출력 신호(SOUT2)를 출력한다.

[0052]

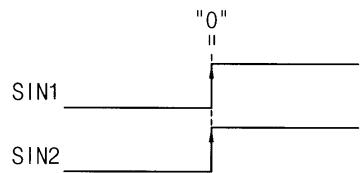

도 2a 및 도 2b에 도시된 바와 같이, 임의의 시간차(TD)를 가지는 신호들에 대하여 시간차 가산기(100)에서 수행되는 시간차 가산(예를 들어, 연산자 "+" )의 항등원 및 역원이 정의될 수 있다. 즉, 임의의 시간차(TD)를 가지는 신호들에 대하여 [수학식 1]을 만족하는 상기 시간차 가산의 항등원 "0"이 존재한다.

[0053] [수학식 1]

$$TD + 0 = 0 + TD = TD$$

[0055] 또한, 임의의 시간차(TD)를 가지는 신호들에 대한 상기 시간차 가산에서, [수학식 2]를 만족하는 임의의 시간차(TD)의 역원(-TD)가 존재한다.

[0056] [수학식 2]

$$TD + (-TD) = (-TD) + TD = 0$$

[0058] 이와 같이, 본 발명의 실시예들에 따른 시간차 가산기(100)는, 임의의 시간차(TD)를 가지는 신호들이 닫혀있는 시간차 가산을 수행할 수 있다.

[0059] 한편, 반도체 장치에 대한 디자인 룰(Design Rule; DR)이 감소됨에 따라, 전원 전압 또는 동작 전압이 낮아지고, 이에 따라 전압 도메인에서의 신호 대 잡음 비(Signal-to-Noise Ratio; SNR)가 감소된다. 그러나, 전원 전압 또는 동작 전압이 낮아짐에 따라 전압 신호의 로우 레벨에서 하이 레벨로의 천이 시간 또는 하이 레벨에서 로우 레벨로의 천이 시간은 감소된다. 이에 따라, 시간 도메인에서의 신호 대 잡음 비는 증가될 수 있다. 따라서, 낮은 전원 전압 환경에서, 전자 회로들 및 장치들은 시간 도메인에서 신호 처리를 수행함으로써 성능을 향상시킬 수 있다. 즉, 낮은 전원 전압 환경에서, 본 발명의 실시예들에 따른 시간차 가산기(100) 및/또는 시간 차 누산기가 시간 도메인에서 신호 처리를 수행함으로써 시간차 가산기(100) 및/또는 시간차 누산기를 포함하는 다양한 전자 회로들 및 장치의 성능이 향상될 수 있다.

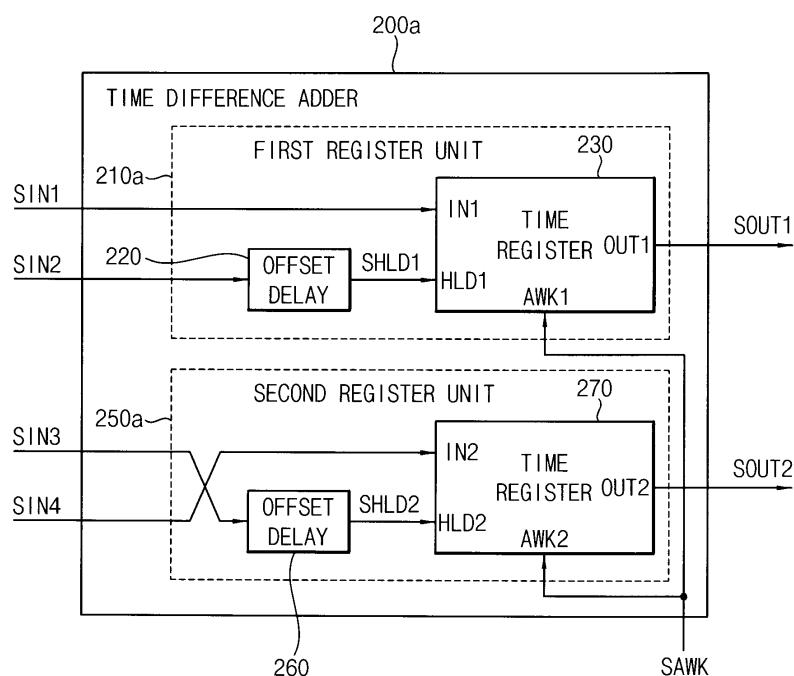

[0060] 도 3은 본 발명의 일 실시예에 따른 시간차 가산기를 나타내는 블록도이다.

[0061] 도 3을 참조하면, 시간차 가산기(200a)는 제1 레지스터부(210a) 및 제2 레지스터부(250a)를 포함한다.

[0062] 제1 레지스터부(210a)는 제1 입력 신호(SIN1) 및 제2 입력 신호(SIN2)를 수신하고, 어웨이크 신호(SAWK)에 응답하여 제1 출력 신호(SOUT1)를 생성한다. 제1 레지스터부(210a)는 제1 오프셋 지연기(220) 및 제1 시간 레지스터(230)를 포함할 수 있다. 제1 오프셋 지연기(220)는 제2 입력 신호(SIN2)를 오프셋 시간만큼 지연시켜 제1 홀드 신호(SHLD1)를 생성할 수 있다. 제1 시간 레지스터(230)는, 제1 입력 신호(SIN1)를 수신하는 제1 입력 단자(IN1), 제1 홀드 신호(SHLD1)를 수신하는 제1 홀드 단자(HLD1), 어웨이크 신호(SAWK)를 수신하는 제1 어웨이크 단자(AWK1), 및 제1 출력 신호(SOUT1)를 출력하는 제1 출력 단자(OUT1)를 가질 수 있다.

[0063] 제2 레지스터부(250a)는 제3 입력 신호(SIN3) 및 제4 입력 신호(SIN4)를 수신하고, 어웨이크 신호(SAWK)에 응답하여 제2 출력 신호(SOUT2)를 생성한다. 제2 레지스터부(250a)는 제2 오프셋 지연기(260) 및 제2 시간 레지스터(270)를 포함할 수 있다. 제2 오프셋 지연기(260)는 제3 입력 신호(SIN3)를 상기 오프셋 시간만큼 지연시켜 제2 홀드 신호(SHLD2)를 생성할 수 있다. 제2 시간 레지스터(270)는, 제4 입력 신호(SIN4)를 수신하는 제2 입력 단자(IN2), 제2 홀드 신호(SHLD2)를 수신하는 제2 홀드 단자(HLD2), 어웨이크 신호(SAWK)를 수신하는 제2 어웨이크 단자(AWK2), 및 제2 출력 신호(SOUT2)를 출력하는 제2 출력 단자(OUT2)를 가질 수 있다.

[0064] 실시예에 따라, 어웨이크 신호(SAWK)는 외부의 회로 또는 장치에서 수신되거나, 시간차 가산기(200a)가 어웨이크 신호(SAWK)를 생성하는 회로를 포함할 수 있다. 예를 들어, 시간차 가산기(200a)는 제1 입력 신호(SIN1), 제2 입력 신호(SIN2), 제3 입력 신호(SIN3) 또는 제4 입력 신호(SIN4) 중 어느 하나의 신호를 지연 또는 반전시켜 어웨이크 신호(SAWK)를 생성할 수 있다.

[0065] 제1 시간 레지스터(230)는, 어웨이크 신호(SAWK)에 응답하여, 어웨이크 신호(SAWK)의 상승 에지로부터, 디스차지 시간에서 상기 오프셋 시간이 감산되고 제1 입력 신호(SIN1)와 제2 입력 신호(SIN2)간의 제1 시간차가 감산된 시간 후, 상승 에지를 가지는 제1 출력 신호(SOUT1)를 출력할 수 있다. 즉, 어웨이크 신호(SAWK)와 제1 출력 신호(SOUT1)간의 시간차는 상기 디스차지 시간에서 상기 오프셋 시간이 감산되고 상기 제1 시간차가 더욱 감산된 시간에 상응할 수 있다.

[0066] 또한, 제2 시간 레지스터(270)는, 어웨이크 신호(SAWK)에 응답하여, 어웨이크 신호(SAWK)의 상기 상승 에지로부터, 상기 디스차지 시간에서 상기 오프셋 시간이 감산되고 제3 입력 신호(SIN3)와 제4 입력 신호(SIN4)간의 제2 시간차가 가산된 시간 후, 상승 에지를 가지는 제2 출력 신호(SOUT2)를 출력할 수 있다. 즉, 어웨이크 신호(SAWK)와 제2 출력 신호(SOUT2)간의 시간차는 상기 디스차지 시간에서 상기 오프셋 시간이 감산되고 상기 제2 시간차가 가산된 시간에 상응할 수 있다.

[0067] 제1 오프셋 지연기(220)의 상기 오프셋 시간과 제2 오프셋 지연기(260)의 상기 오프셋 시간은 실질적으로 동일

할 수 있다. 실시예에 따라, 상기 오프셋 시간은 시간차 가산기(200a)에 입력되는 시간차들의 범위에 상응하도록 설정될 수 있다. 예를 들어, 상기 오프셋 시간은 시간차 가산기(200a)에 입력되는 음의 시간차의 최대값 이상으로 설정될 수 있다.

[0068] 또한, 제1 시간 레지스터(230)의 상기 디스차지 시간과 제2 시간 레지스터(270)의 상기 디스차지 시간은 실질적으로 동일할 수 있다. 한편, 상기 디스차지 시간은 제1 시간 레지스터(230) 및 제2 시간 레지스터(270)의 각각에 포함된 커패시터의 커패시턴스에 따라 결정될 수 있고, 제1 시간 레지스터(230)에 포함된 커패시터의 커패시턴스와 제2 시간 레지스터(270)에 포함된 커패시터의 커패시턴스는 실질적으로 동일할 수 있다. 실시예에 따라, 상기 디스차지 시간은 상기 오프셋 시간 및 시간차 가산기(200a)에 입력되는 시간차들의 범위에 상응하도록 설정될 수 있다. 예를 들어, 상기 디스차지 시간은 상기 오프셋 시간과 시간차 가산기(200a)에 입력되는 양의 시간차의 최대값의 합 이상으로 설정될 수 있다. 또한, 실시예에 따라, 상기 디스차지 시간은 제1 내지 제4 입력 신호들(SIN1, SIN2, SIN3, SIN4) 중 하나의 펄스 폭보다 작도록 설정될 수 있다.

[0069] 제1 출력 신호(SOUT1)와 제2 출력 신호(SOUT2)간의 시간차는, 제2 출력 신호(SOUT2)의 상승 에지가 발생되는 시간에서 제1 출력 신호(SOUT1)의 상승 에지가 발생되는 시간을 감산한 시간으로서, 어웨이크 신호(SAWK)와 제2 출력 신호(SOUT2)간의 시간차에서 어웨이크 신호(SAWK)와 제1 출력 신호(SOUT1)간의 시간차가 감산된 시간에 상응한다. 따라서, 제1 오프셋 지연기(220) 및 제2 오프셋 지연기(260)가 실질적으로 동일한 상기 오프셋 시간을 가지고, 제1 시간 레지스터(230) 및 제2 시간 레지스터(270)가 실질적으로 동일한 상기 디스차지 시간을 가지고, 제1 출력 신호(SOUT1)와 제2 출력 신호(SOUT2)간의 시간차는 상기 제1 시간차와 상기 제2 시간차의 합에 상응할 수 있다.

[0070] 이와 같이, 본 발명의 일 실시예에 따른 시간차 가산기(200a)는 상기 제1 시간차와 상기 제2 시간차의 합에 상응하는 시간차를 가지는 제1 출력 신호(SOUT1) 및 제2 출력 신호(SOUT2)를 출력할 수 있다.

[0071] 실시예에 따라, 제1 레지스터부(210a)의 적어도 일부의 구성요소들(예를 들어, 트랜지스터들)과 제2 레지스터부(250a)의 적어도 일부의 구성요소들(예를 들어, 트랜지스터들)은 서로 교번하여 배치될 수 있다. 이에 따라, 공정, 전압, 온도(Process, Voltage, Temperature; PVT) 변화(Variation)에도 제1 레지스터부(210a)와 제2 레지스터부(250a)간의 미스매치가 최소화될 수 있다.

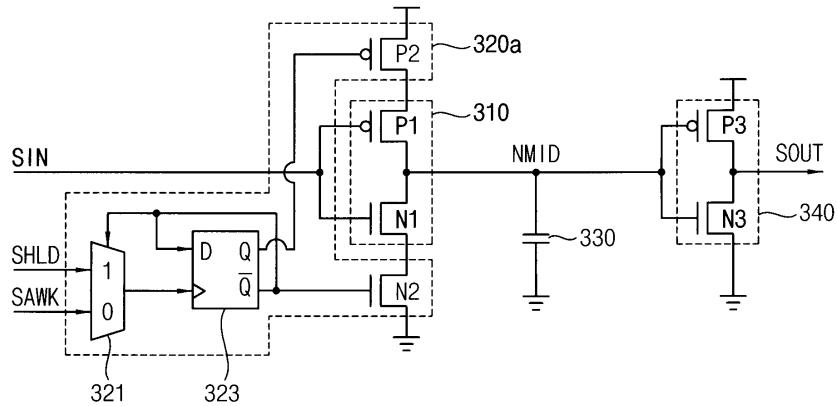

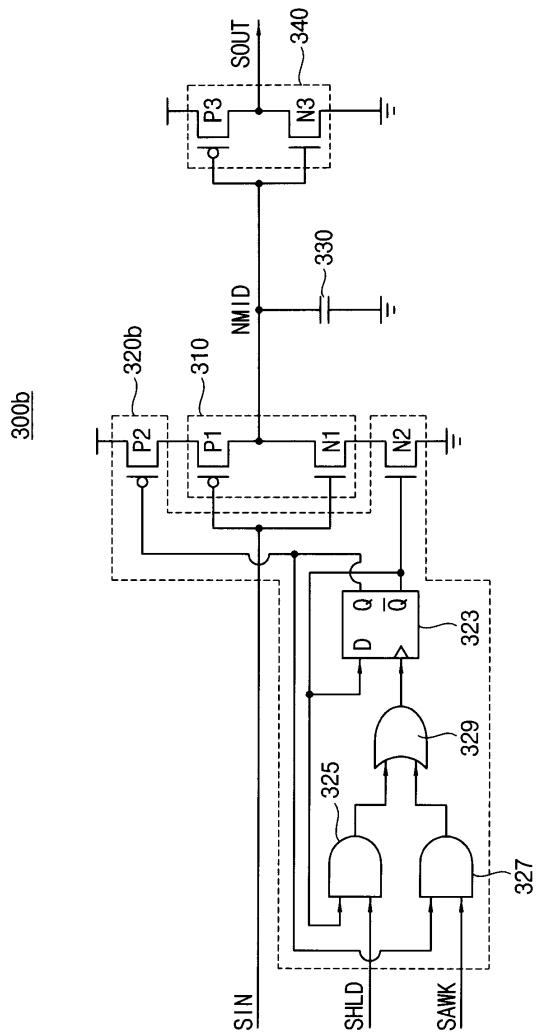

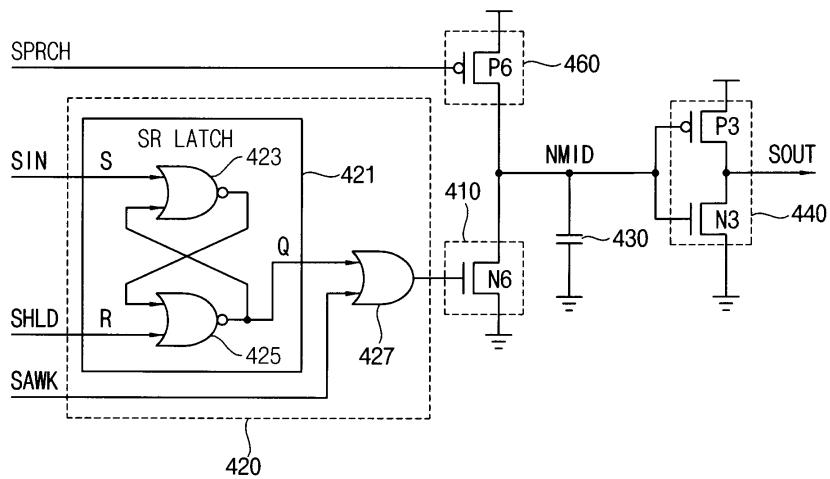

[0072] 도 4는 도 3의 시간차 가산기에 포함된 시간 레지스터의 일 예를 나타내는 회로도이다.

[0073] 도 4를 참조하면, 시간 레지스터(300a)는 제1 인버터(310), 인버터 제어부(320a), 커패시터(330) 및 출력부(340)를 포함한다. 일 실시예에서, 도 3의 제1 시간 레지스터(230) 및 제2 시간 레지스터(270)는 시간 레지스터(300a)와 같이 구현될 수 있다. 예를 들어, 시간 레지스터(300a)가 도 3의 제1 시간 레지스터(230)인 경우, 입력 신호(SIN)는 도 3의 제1 입력 신호(SIN1)이고, 홀드 신호(SHLD)는 도 3의 제1 홀드 신호(SHLD1)이며, 출력 신호(SOUT)는 도 3의 제1 출력 신호(SOUT1)일 수 있다. 또한, 시간 레지스터(300a)가 도 3의 제2 시간 레지스터(270)인 경우, 입력 신호(SIN)는 도 3의 제4 입력 신호(SIN4)이고, 홀드 신호(SHLD)는 도 3의 제2 홀드 신호(SHLD2)이며, 출력 신호(SOUT)는 도 3의 제2 출력 신호(SOUT2)일 수 있다.

[0074] 제1 인버터(310)는 입력 신호(SIN)를 반전시킨다. 제1 인버터(310)는 제1 PMOS 트랜지스터(P1) 및 제1 NMOS 트랜지스터(N1)을 포함할 수 있다. 제1 PMOS 트랜지스터(P1)는, 입력 신호(SIN)가 인가되는 게이트, 인버터 제어부(320a)를 통하여 전원 전압에 연결된 소스, 및 중간 노드(NMID)에 연결된 드레인을 포함할 수 있다. 또한, 제1 NMOS 트랜지스터(N1)는, 입력 신호(SIN)가 인가되는 게이트, 인버터 제어부(320a)를 통하여 접지 전압에 연결된 소스, 및 중간 노드(NMID)에 연결된 드레인을 포함할 수 있다.

[0075] 인버터 제어부(320a)는 홀드 신호(SHLD)에 응답하여 제1 인버터(310)를 비활성화시키고, 어웨이크 신호(SAWK)에 응답하여 제1 인버터(310)를 활성화시킬 수 있다. 인버터 제어부(320a)는 제2 PMOS 트랜지스터(P2), 제2 NMOS 트랜지스터(N2), D-플립플롭(323) 및 선택기(321)를 포함할 수 있다.

[0076] 제2 PMOS 트랜지스터(P2)는 상기 전원 전압과 제1 PMOS 트랜지스터(P1) 사이에 연결될 수 있다. 예를 들어, 제2 PMOS 트랜지스터(P2)는, D-플립플롭(323)의 출력 단자(Q)에 연결된 게이트, 상기 전원 전압에 연결된 소스, 및 제1 PMOS 트랜지스터(P1)의 소스에 연결된 드레인을 포함할 수 있다. 제2 NMOS 트랜지스터(N2)는 상기 접지 전압과 제1 NMOS 트랜지스터(N1) 사이에 연결될 수 있다. 예를 들어, 제2 NMOS 트랜지스터(N2)는, D-플립플롭(323)의 반전 출력 단자(/Q)에 연결된 게이트, 상기 접지 전압에 연결된 소스, 및 제1 NMOS 트랜지스터(N1)의 소스에 연결된 드레인을 포함할 수 있다. 제2 PMOS 트랜지스터(P2) 및 제2 NMOS 트랜지스터(N2)는 상기 전원 또는 접지 전압들과 제1 인버터(310)의 연결을 제어할 수 있다. 예를 들어, 제2 PMOS 트랜지스터(P2) 및 제2 NMOS

트랜지스터(N2)가 턴-온되면, 제1 인버터(310)가 상기 전원 전압 또는 상기 접지 전압에 전기적으로 연결되고, 제2 PMOS 트랜지스터(P2) 및 제2 NMOS 트랜지스터(N2)가 턴-오프되면, 제1 인버터(310)가 상기 전원 전압 또는 상기 접지 전압으로부터 전기적으로 차단될 수 있다.

[0077] D-플립플롭(323)은 제2 PMOS 트랜지스터(P2)의 게이트에 연결된 출력 단자(Q), 제2 NMOS 트랜지스터(N2)의 게이트에 연결된 반전 출력 단자(/Q), 반전 출력 단자(/Q)에 연결된 데이터 단자(D), 및 선택기(321)의 출력 신호가 인가되는 클록 단자를 포함할 수 있다. 한편, 데이터 단자(D)에 반전 출력 단자(/Q)가 연결되므로, D-플립플롭(323)의 출력 단자(Q)에서 출력되는 출력 신호 및 반전 출력 단자(/Q)에서 출력되는 반전 출력 신호는, 상기 클록 단자에 인가되는 선택기(321)의 상기 출력 신호가 상승 에지를 가질 때마다 토글될 수 있다.

[0078] 선택기(321)는 반전 출력 단자(/Q)에서 출력되는 상기 반전 출력 신호에 응답하여 상기 클록 단자에 홀드 신호(SHLD) 또는 어웨이크 신호(SAWK)를 선택적으로 출력할 수 있다. 예를 들어, 선택기(321)는 멀티플렉서(321)로 구현될 수 있다. 멀티플렉서(321)는, 홀드 신호(SHLD)를 수신하는 제1 입력 단자, 어웨이크 신호(SAWK)를 수신하는 제2 입력 단자, 상기 반전 출력 신호를 선택 신호로서 수신하는 선택 단자, 및 상기 선택 신호에 응답하여 홀드 신호(SHLD) 또는 어웨이크 신호(SAWK)를 선택적으로 출력하는 출력 단자를 포함할 수 있다.

[0079] 커패시터(330)는 제1 인버터(310)의 출력 신호에 응답하여 충전 또는 방전될 수 있다. 또한, 커패시터(330)는 중간 노드(NMID)에 연결된 제1 단자 및 상기 접지 전압에 연결된 제2 단자를 가질 수 있다. 예를 들어, 제1 인버터(310)의 상기 출력 신호가 로직 하이 레벨을 가지는 경우, 즉, 제1 PMOS 트랜지스터(P1) 및 제2 PMOS 트랜지스터(P2)가 턴-온된 경우, 커패시터(330)의 상기 제1 단자는 제1 PMOS 트랜지스터(P1) 및 제2 PMOS 트랜지스터(P2)를 통하여 상기 전원 전압에 전기적으로 연결되고, 커패시터(330)가 충전될 수 있다. 또한, 제1 인버터(310)의 상기 출력 신호가 로직 로우 레벨을 가지는 경우, 즉, 제1 NMOS 트랜지스터(N1) 및 제2 NMOS 트랜지스터(N2)가 턴-온된 경우, 커패시터(330)의 상기 제1 단자는 제1 NMOS 트랜지스터(N1) 및 제2 NMOS 트랜지스터(N2)를 통하여 상기 접지 전압에 전기적으로 연결되고, 커패시터(330)가 방전될 수 있다.

[0080] 출력부(340)는 커패시터(330)의 전압(즉, 중간 노드(NMID)의 전압)에 기초하여 출력 신호(SOUT)를 생성할 수 있다. 예를 들어, 출력부(340)는 제2 인버터(340)를 포함할 수 있다. 제2 인버터(340)는 제3 PMOS 트랜지스터(P3) 및 제3 NMOS 트랜지스터(N3)를 포함할 수 있다. 예를 들어, 제3 PMOS 트랜지스터(P3)는, 중간 노드(NMID)에 연결된 게이트, 상기 전원 전압에 연결된 소스, 및 출력 신호(SOUT)가 출력되는 드레인을 포함할 수 있다. 또한, 제3 NMOS 트랜지스터(N3)는, 중간 노드(NMID)에 연결된 게이트, 상기 접지 전압에 연결된 소스, 및 출력 신호(SOUT)가 출력되는 드레인을 포함할 수 있다. 제2 인버터(340)는, 커패시터(330)의 전압이 소정의 문턱 전압 이하일 때, 로직 하이 레벨을 가지는 출력 신호(SOUT)를 출력할 수 있다. 즉, 커패시터(330)의 전압이 제3 PMOS 트랜지스터(P3)의 문턱 전압 이하일 때, 제3 PMOS 트랜지스터(P3)가 턴-온되고, 제2 인버터(340)는 로직 하이 레벨을 가지는 출력 신호(SOUT)를 출력할 수 있다.

[0081] 커패시터(330)는, 입력 신호(SIN)와 홀드 신호(SHLD)간의 시간차에 상응하는 시간 동안 방전됨으로써, 입력 신호(SIN)와 홀드 신호(SHLD)간의 상기 시간차에 대한 정보를 저장할 수 있다. 즉, 커패시터(330)의 방전이 입력 신호(SIN)의 상승 에지에 응답하여 시작되고, 커패시터(330)의 방전이 홀드 신호(SHLD)의 상승 에지에 응답하여 중지됨으로써, 커패시터(330)는 입력 신호(SIN)와 홀드 신호(SHLD)간의 상기 시간차에 상응하는 시간 동안 방전될 수 있다. 또한, 커패시터(330)의 방전은 어웨이크 신호(SAWK)의 상승 에지에 응답하여 재개될 수 있다. 이에 따라, 커패시터(330)의 전압은, 어웨이크 신호(SAWK)의 상승 에지로부터 소정의 시간 후, 상기 소정의 문턱 전압(예를 들어, 제3 PMOS 트랜지스터(P3)의 문턱 전압) 이하로 낮아질 수 있고, 상기 소정의 시간은 입력 신호(SIN)와 홀드 신호(SHLD)간의 상기 시간차에 따라 결정될 수 있다. 예를 들어, 상기 시간 차가 증가되는 경우, 상기 소정의 시간은 감소되고, 상기 시간 차가 감소되는 경우, 상기 소정의 시간은 증가될 수 있다. 또한, 출력부(340)는, 커패시터(330)의 전압이 상기 소정의 문턱 전압 이하로 낮아질 때, 로직 하이 레벨을 가지는 출력 신호(SOUT)를 출력할 수 있다. 이에 따라, 출력 신호(SOUT)는, 어웨이크 신호(SAWK)의 상승 에지로부터 상기 시간차에 따라 결정되는 상기 소정의 시간 후, 상승 에지를 가질 수 있다. 즉, 출력 신호(SOUT)가 상승 에지를 가지는 시점은 입력 신호(SIN)와 홀드 신호(SHLD)간의 상기 시간차에 따라 결정될 수 있다.

[0082] 예를 들어, 제1 인버터(310)는, 커패시터(330)의 방전이 시작되도록, 입력 신호(SIN)의 상승 에지에 응답하여 커패시터(330)를 상기 접지 전압에 전기적으로 연결할 수 있다. 이 후, 인버터 제어부(320a)는, 커패시터(330)의 방전이 중지되도록, 홀드 신호(SHLD)의 상승 에지에 응답하여 제1 인버터(310)를 비활성화시킬 수 있다. 이어서, 인버터 제어부(320a)는, 커패시터(330)의 방전이 재개되도록, 어웨이크 신호(SAWK)의 상승 에지에 응답하여 제1 인버터(310)를 활성화시킬 수 있다. 커패시터(330)의 방전이 재개된 후, 커패시터(330)의 전압, 즉, 중

간 노드(NMID)의 전압이 상기 소정의 문턱 전압 이하로 낮아질 때, 출력부(340)는 로직 하이 레벨을 가지는 출력 신호(SOUT)를 출력할 수 있다.

[0083] 이에 따라, 시간 레지스터(300a)는 어웨이크 신호(SAWK)에 응답하여 입력 신호(SIN)와 홀드 신호(SHLD)간의 시간차에 따라 결정되는 시점에서 상승 에지를 가지는 출력 신호(SOUT)를 출력할 수 있다.

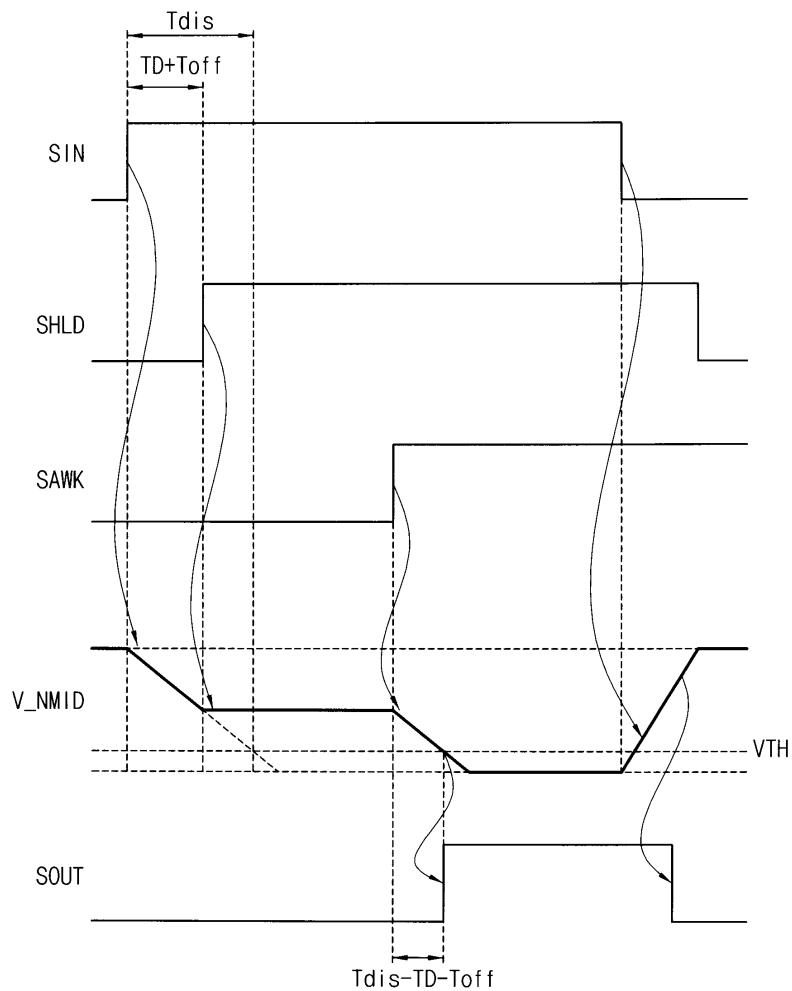

[0084] 도 5는 도 4의 시간 레지스터의 동작을 설명하기 위한 타이밍도이다.

[0085] 도 4 및 도 5를 참조하면, 제1 인버터(310)는 입력 신호(SIN)의 상승 에지에 응답하여 로직 로우 레벨의 출력 신호를 출력할 수 있다. 한편, 입력 신호(SIN)가 상기 상승 에지를 가지는 동안, D-플립플롭(323)은 출력 단자(Q)에서 로직 로우 레벨의 출력 신호를 출력하고, 반전 출력 단자(/Q)에서 로직 하이 레벨의 반전 출력 신호를 출력할 수 있다. 이에 따라, 제1 NMOS 트랜지스터(N1)가 입력 신호(SIN)의 상승 에지에 응답하여 턴-온되고, 제2 NMOS 트랜지스터(N2)가 상기 로직 하이 레벨의 반전 출력 신호에 응답하여 턴-온될 수 있다. 제1 NMOS 트랜지스터(N1) 및 제2 NMOS 트랜지스터(N2)가 턴-온되면, 중간 노드(NMID), 즉 커페시터(330)의 제1 단자는 제1 NMOS 트랜지스터(N1) 및 제2 NMOS 트랜지스터(N2)를 통하여 접지 전압에 연결되고, 커페시터(330)는 방전될 수 있다. 이와 같이, 입력 신호(SIN)의 상승 에지에 응답하여 커페시터(330)가 방전되고, 커페시터(330)의 전압, 즉 중간 노드(NMID)의 전압(V\_NMID)이 감소될 수 있다.

[0086] 인버터 제어부(320a)는 홀드 신호(SHLD)의 상승 에지에 응답하여 제1 인버터(310)를 비활성화시킨다. 예를 들어, 선택기(321)는 반전 출력 단자(/Q)에서 출력된 상기 로직 하이 레벨의 반전 출력 신호에 응답하여 클록 단자에 홀드 신호(SHLD)를 출력하고, D-플립플롭(323)은 출력 단자(Q)에서 로직 하이 레벨의 출력 신호를 출력하고, 반전 출력 단자(/Q)에서 로직 로우 레벨의 반전 출력 신호를 출력할 수 있다. 이에 따라, 제2 PMOS 트랜지스터(P2)가 상기 로직 하이 레벨의 출력 신호에 응답하여 턴-오프되고, 제2 NMOS 트랜지스터(N2)가 상기 로직 로우 레벨의 반전 출력 신호에 응답하여 턴-오프될 수 있다. 제2 NMOS 트랜지스터(N2)가 턴-오프되면, 커페시터(330)의 방전이 중지될 수 있다. 이와 같이, 홀드 신호(SHLD)의 상승 에지에 응답하여 커페시터(330)의 방전이 중지되고, 커페시터(330)의 전압, 즉 중간 노드(NMID)의 전압(V\_NMID)이 감소가 중지될 수 있다.

[0087] 인버터 제어부(320a)는 어웨이크 신호(SAWK)의 상승 에지에 응답하여 제1 인버터(310)를 활성화시킨다. 예를 들어, 선택기(321)는 반전 출력 단자(/Q)에서 출력된 상기 로직 로우 레벨의 반전 출력 신호에 응답하여 클록 단자에 어웨이크 신호(SHLD)를 출력하고, D-플립플롭(323)은 출력 단자(Q)에서 로직 로우 레벨의 출력 신호를 출력하고, 반전 출력 단자(/Q)에서 로직 하이 레벨의 반전 출력 신호를 출력할 수 있다. 이에 따라, 제2 PMOS 트랜지스터(P2)가 상기 로직 로우 레벨의 출력 신호에 응답하여 턴-온되고, 제2 NMOS 트랜지스터(N2)가 상기 로직 하이 레벨의 반전 출력 신호에 응답하여 턴-온될 수 있다. 또한, 제1 NMOS 트랜지스터(N1)는 로직 하이 레벨의 입력 신호(SIN)에 응답하여 턴-온될 수 있다. 제1 NMOS 트랜지스터(N1) 및 제2 NMOS 트랜지스터(N2)가 턴-온되면, 중간 노드(NMID)는 제1 NMOS 트랜지스터(N1) 및 제2 NMOS 트랜지스터(N2)를 통하여 상기 접지 전압에 연결되고, 커페시터(330)의 방전이 재개될 수 있다. 이와 같이, 어웨이크 신호(SAWK)의 상승 에지에 응답하여 커페시터(330)의 방전이 재개되고, 커페시터(330)의 전압, 즉 중간 노드(NMID)의 전압(V\_NMID)이 다시 감소될 수 있다.

[0088] 출력부(340)는 커페시터(330)의 전압, 즉 중간 노드(NMID)의 전압(V\_NMID)에 기초하여 출력 신호(SOUT)를 출력한다. 출력부(340)는, 중간 노드(NMID)의 전압(V\_NMID)이 소정의 문턱 전압(VTH) 이하인 경우, 로직 하이 레벨의 출력 신호(SOUT)를 출력할 수 있다. 예를 들어, 문턱 전압(VTH)은 제3 PMOS 트랜지스터(P3)의 문턱 전압일 수 있다. 즉, 중간 노드(NMID)의 전압(V\_NMID)이 제3 PMOS 트랜지스터(P3)의 문턱 전압 이하로 낮아지는 경우, 제3 PMOS 트랜지스터(P3)가 턴-온되고, 출력 신호(SOUT)는 로직 하이 레벨을 가질 수 있다.

[0089] 한편, 출력 신호(SOUT)는 어웨이크 신호(SAWK)의 상승 에지로부터, 소정의 디스차지 시간(Tdis)에서 입력 신호(SIN)와 홀드 신호(SHLD)간의 시간차(TD+Toff)가 감산된 시간(Tdis-TD-Toff) 후, 상승 에지를 가질 수 있다. 예를 들어, 입력 신호(SIN)가 도 3의 제1 입력 신호(SIN1)이고, 홀드 신호(SHLD)가 도 3의 제1 오프셋 지연기(220)에서 출력된 제1 홀드 신호(SHLD1)인 경우, 입력 신호(SIN)와 홀드 신호(SHLD)간의 시간차(TD+Toff)는 제1 입력 신호(SIN1)와 제2 입력 신호(SIN2)간의 시간차(TD)와 제1 오프셋 지연기(220)의 오프셋 시간(Toff)의 합에 상응할 수 있다. 이 경우, 출력 신호(SOUT)는 어웨이크 신호(SAWK)의 상승 에지로부터 디스차지 시간(Tdis)에서 제1 입력 신호(SIN1)와 제2 입력 신호(SIN2)간의 시간차(TD)와 제1 오프셋 지연기(220)의 오프셋 시간(Toff)이 감산된 시간(Tdis-TD-Toff) 후 상승 에지를 가질 수 있다.

[0090] 여기서, 디스차지 시간(Tdis)은 커페시터(330)의 전압, 즉 중간 노드(NMID)의 전압(V\_NMID)이 하이 레벨에서 소

정의 문턱 전압(VTH) 이하로 감소될 때까지의 시간으로서, 제1 및 제2 NMOS 트랜지스터들(N1, N2)의 전류 구동 능력 및 커패시터(330)의 커패시턴스에 의해 결정될 수 있다. 즉, 제1 및 제2 NMOS 트랜지스터들(N1, N2)의 전류 구동 능력이 일정한 경우, 디스차지 시간(Tdis)은 커패시터(330)의 커패시턴스에 의해 결정될 수 있다. 한편, 도 3의 제1 시간 레지스터(230)에 포함된 커패시터와 도 3의 제2 시간 레지스터(270)에 포함된 커패시터가 실질적으로 동일한 커패시턴스를 가짐으로써, 제1 시간 레지스터(230) 및 제2 시간 레지스터(270)는 실질적으로 동일한 디스차지 시간(Tdis)을 가질 수 있다. 또한, 도 3의 제1 오프셋 지연기(220)와 제2 오프셋 지연기(260)는 실질적으로 동일한 오프셋 시간(Toff)을 가질 수 있다.

[0091] 이에 따라, 도 3의 제1 출력 신호(SOUT1)와 제2 출력 신호(SOUT2)간의 시간차(즉, 제1 출력 신호(SOUT1)가 상승 예지를 가지는 시점과 제2 출력 신호(SOUT2)가 상승 예지를 가지는 시점간의 차이)는 제1 입력 신호(SIN1)와 제2 입력 신호(SIN2)간의 제1 시간차 및 제3 입력 신호(SIN3)와 제4 입력 신호(SIN4)간의 제2 시간차에 의해 결정될 수 있다.

[0092] 출력부(340)에서 로직 하이 레벨의 출력 신호(SOUT)가 출력된 후, 제1 인버터(310)는 입력 신호(SIN)의 하강 예지에 응답하여 로직 로우 레벨의 출력 신호를 출력할 수 있다. 예를 들어, 제1 PMOS 트랜지스터(P1)가 입력 신호(SIN)의 하강 예지에 응답하여 턴-온되고, 제2 PMOS 트랜지스터(P2)가 로직 로우 레벨의 반전 출력 신호에 응답하여 턴-온될 수 있다. 제1 PMOS 트랜지스터(P1) 및 제2 PMOS 트랜지스터(P2)가 턴-온되면, 중간 노드(NMID), 즉 커패시터(330)의 제1 단자는 제1 PMOS 트랜지스터(P1) 및 제2 PMOS 트랜지스터(P2)를 통하여 전원 전압에 연결되고, 커패시터(330)는 다시 충전될 수 있다.

[0093] 다른 실시예에서, 어웨이크 신호(SAWK)는 입력 신호(SIN)의 반전 신호이고, 입력 신호(SIN)와 제1 인버터(310) 사이에, 입력 신호(SIN)가 하강 예지를 가지더라도 제1 인버터(310)에 일정 시간 동안 로직 하이 레벨의 입력 신호를 인가하기 위한 논리 게이트들이 위치할 수 있다. 이 경우, 제1 인버터(310)는 상기 논리 게이트들의 출력 신호에 응답하여 커패시터(330)를 충전할 수 있다.

[0094] 도 6은 도 3의 시간차 가산기에 포함된 시간 레지스터의 다른 예를 나타내는 회로도이다.

[0095] 도 6을 참조하면, 시간 레지스터(300b)는 제1 인버터(310), 인버터 제어부(320b), 커패시터(330) 및 출력부(340)를 포함한다. 시간 레지스터(300b)는, 인버터 제어부(320b)에 포함된 선택기(325, 327, 329)의 구성 및 동작을 제외하고 도 4의 시간 레지스터(300a)와 실질적으로 유사한 구성을 가지고, 실질적으로 유사한 동작을 수행할 수 있다.

[0096] 인버터 제어부(320b)는 홀드 신호(SHLD)에 응답하여 제1 인버터(310)를 비활성화시키고, 어웨이크 신호(SAWK)에 응답하여 제1 인버터(310)를 활성화시킬 수 있다. 인버터 제어부(320b)는 제2 PMOS 트랜지스터(P2), 제2 NMOS 트랜지스터(N2), D-플립플롭(323) 및 선택기(325, 327, 329)를 포함할 수 있다.

[0097] 선택기(325, 327, 329)는 로직 게이트들(325, 327, 329)로 구현될 수 있다. 예를 들어, 선택기(325, 327, 329)는 제1 AND 게이트(325), 제2 AND 게이트(327) 및 OR 게이트(329)를 포함할 수 있다. 제1 AND 게이트(325)는 홀드 신호(SHLD) 및 반전 출력 단자(/Q)에서 출력된 반전 출력 신호에 AND 연산을 수행할 수 있다. 제2 AND 게이트(327)는 어웨이크 신호(SAWK) 및 출력 단자(Q)에서 출력된 출력 신호에 AND 연산을 수행할 수 있다. 또한, OR 게이트(329)는 제1 AND 게이트(325)의 출력 신호 및 제2 AND 게이트(327)의 출력 신호에 OR 연산을 수행할 수 있다. 상기 반전 출력 신호가 로직 하이 레벨을 가지고, 상기 출력 신호가 로직 로우 레벨을 가진 경우, 로직 게이트들(325, 327, 329)은 홀드 신호(SHLD)를 출력하고, 상기 반전 출력 신호가 로직 로우 레벨을 가지고, 상기 출력 신호가 로직 하이 레벨을 가진 경우, 로직 게이트들(325, 327, 329)은 어웨이크 신호(SAWK)를 출력할 수 있다.

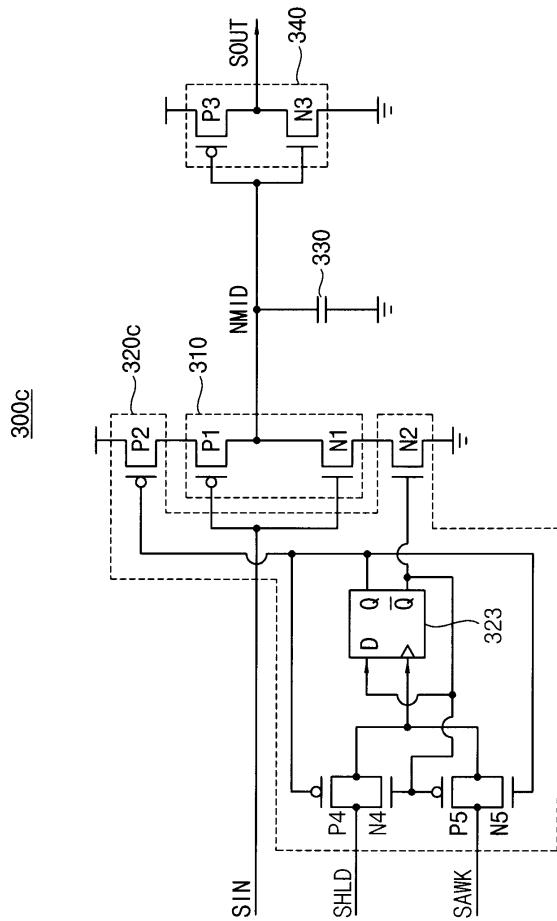

[0098] 도 7은 도 3의 시간차 가산기에 포함된 시간 레지스터의 또 다른 예를 나타내는 회로도이다.

[0099] 도 7을 참조하면, 시간 레지스터(300c)는 제1 인버터(310), 인버터 제어부(320c), 커패시터(330) 및 출력부(340)를 포함한다. 시간 레지스터(300c)는, 인버터 제어부(320c)에 포함된 선택기(P4, N4, P5, N5)의 구성 및 동작을 제외하고 도 4의 시간 레지스터(300a)와 실질적으로 유사한 구성을 가지고, 실질적으로 유사한 동작을 수행할 수 있다.

[0100] 인버터 제어부(320c)는 홀드 신호(SHLD)에 응답하여 제1 인버터(310)를 비활성화시키고, 어웨이크 신호(SAWK)에 응답하여 제1 인버터(310)를 활성화시킬 수 있다. 인버터 제어부(320c)는 제2 PMOS 트랜지스터(P2), 제2 NMOS 트랜지스터(N2), D-플립플롭(323) 및 선택기(P4, N4, P5, N5)를 포함할 수 있다.

- [0101] 선택기(P4, N4, P5, N5)는 전송 게이트들(P4, N4, P5, N5)로 구현될 수 있다. 예를 들어, 선택기(P4, N4, P5, N5)는 제1 전송 게이트(P4, N4) 및 제2 전송 게이트(P5, N5)를 포함할 수 있다. 제1 전송 게이트(P4, N4)는, 반전 출력 단자(/Q)에서 출력된 반전 출력 신호가 로직 하이 레벨을 가지고, 출력 단자(Q)에서 출력된 출력 신호가 로직 로우 레벨을 가진 경우, 헬드 신호(SHLD)를 출력할 수 있다. 제1 전송 게이트(P4, N4)는, 출력 단자(Q)에 연결된 게이트를 가지는 제4 PMOS 트랜지스터(P4), 및 반전 출력 단자(/Q)에 연결된 게이트를 가지는 제4 NMOS 트랜지스터(N4)를 포함할 수 있다. 제2 전송 게이트(P5, N5)는, 반전 출력 단자(/Q)에서 출력된 상기 반전 출력 신호가 로직 로우 레벨을 가지고, 출력 단자(Q)에서 출력된 상기 출력 신호가 로직 하이 레벨을 가진 경우, 어웨이크 신호(SAWK)를 출력할 수 있다. 제2 전송 게이트(P5, N5)는, 반전 출력 단자(/Q)에 연결된 게이트를 가지는 제5 PMOS 트랜지스터(P5), 및 출력 단자(Q)에 연결된 게이트를 가지는 제5 NMOS 트랜지스터(N5)를 포함할 수 있다.

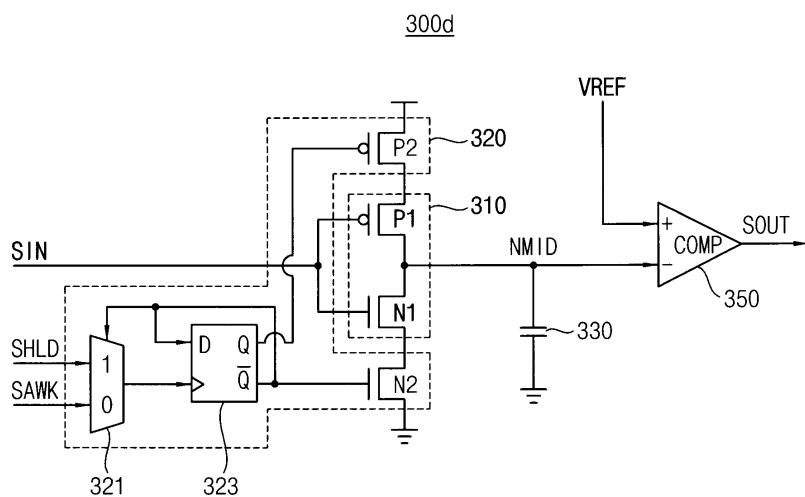

- [0102] 도 8은 도 3의 시간차 가산기에 포함된 시간 레지스터의 또 다른 예를 나타내는 회로도이다.

- [0103] 도 8을 참조하면, 시간 레지스터(300d)는 제1 인버터(310), 인버터 제어부(320), 커패시터(330) 및 출력부(350)를 포함한다. 시간 레지스터(300d)는, 출력부(350)의 구성 및 동작을 제외하고 도 4의 시간 레지스터(300a)와 실질적으로 유사한 구성을 가지고, 실질적으로 유사한 동작을 수행할 수 있다. 실시예에 따라, 인버터 제어부(320)는 도 4의 인버터 제어부(320a), 도 6의 인버터 제어부(320b), 도 7의 인버터 제어부(320c) 또는 이와 유사한 구성의 인버터 제어부로 구현될 수 있다.

- [0104] 출력부(350)는 커패시터(330)의 전압(즉, 중간 노드(NMID)의 전압)에 기초하여 출력 신호(SOUT)를 생성할 수 있다. 예를 들어, 출력부(350)는 비교기(350)를 포함할 수 있다. 비교기(350)는 기준 전압(VREF)을 수신하는 반전 입력 단자, 커패시터(330)의 전압을 수신하는 반전 입력 단자, 및 출력 신호(SOUT)를 출력하는 출력 단자를 포함할 수 있다. 비교기(350)는, 기준 전압(VREF)이 커패시터(330)의 전압보다 높은 경우, 즉, 커패시터(330)의 전압이 기준 전압(VREF) 이하로 낮아지는 경우, 로직 하이 레벨의 출력 신호(SOUT)를 생성할 수 있다. 실시예에 따라, 기준 전압(VREF)은 외부의 회로 또는 장치에서 수신되거나, 시간 레지스터(300d)가 기준 전압(VREF)을 생성하는 회로를 포함할 수 있다. 기준 전압(VREF)은 전원 전압보다 낮을 수 있다. 예를 들어, 기준 전압(VREF)은 상기 전원 전압의 약 0.2배일 수 있다.

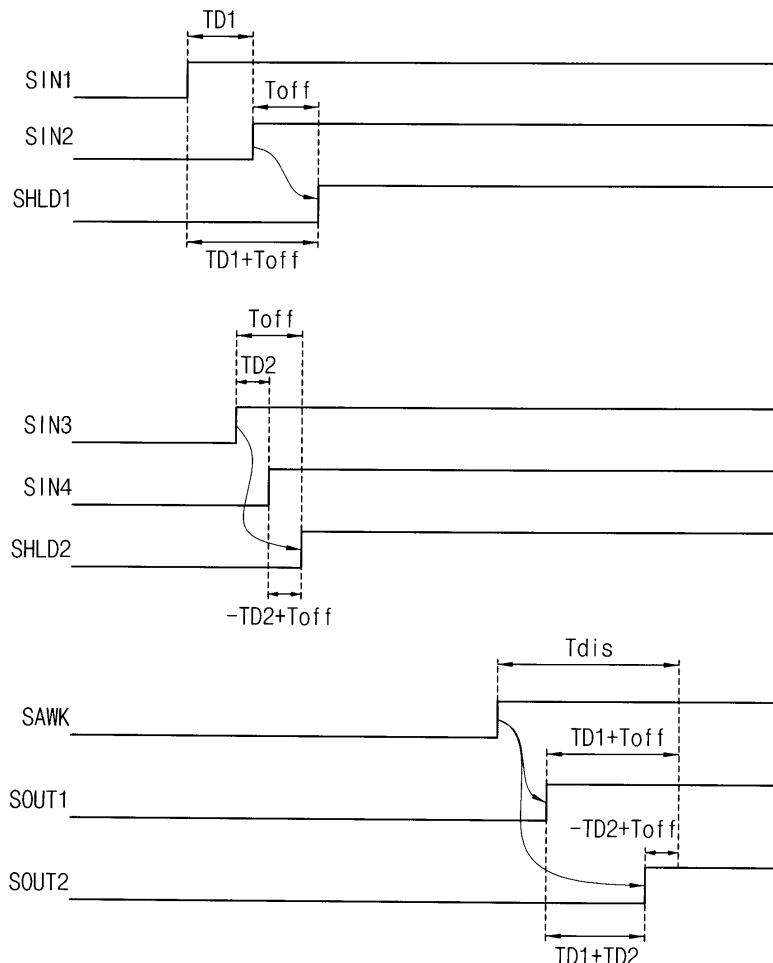

- [0105] 도 9a는 도 3의 시간차 가산기의 동작의 일 예를 설명하기 위한 타이밍도이다. 도 9a에는 제1 입력 신호(SIN1) 및 제2 입력 신호(SIN2)가 양의 제1 시간차(TD1)를 가지고, 제3 입력 신호(SIN3) 및 제4 입력 신호(SIN4)가 양의 제2 시간차(TD2)를 가진 예가 도시되어 있다.

- [0106] 도 3 및 도 9a를 참조하면, 제1 입력 신호(SIN1)는 제1 시간 레지스터(230)의 제1 입력 단자(IN1)에 인가되고, 제2 입력 신호(SIN2)는 제1 오프셋 지연기(220)에 의해 오프셋 시간(Toff)만큼 지연되어 제1 헬드 신호(SHLD1)로서 제1 시간 레지스터(230)의 제1 헬드 단자(HLD1)에 인가된다. 이에 따라, 제1 입력 신호(SIN1) 및 제1 헬드 신호(SHLD1)는 제1 입력 신호(SIN1)와 제2 입력 신호(SIN2)간의 제1 시간차(TD1)와 오프셋 시간(Toff)의 합에 상응하는 시간차(TD1+Toff)를 가질 수 있다.

- [0107] 제4 입력 신호(SIN4)는 제2 시간 레지스터(270)의 제2 입력 단자(IN2)에 인가되고, 제3 입력 신호(SIN3)는 제2 오프셋 지연기(260)에 의해 오프셋 시간(Toff)만큼 지연되어 제2 헬드 신호(SHLD2)로서 제2 시간 레지스터(270)의 제2 헬드 단자(HLD2)에 인가된다. 이에 따라, 제4 입력 신호(SIN4) 및 제2 헬드 신호(SHLD2)는 오프셋 시간(Toff)에서 제3 입력 신호(SIN1)와 제4 입력 신호(SIN2)간의 제2 시간차(TD2)가 감산된 시간에 상응하는 시간차(-TD2+Toff)를 가질 수 있다.

- [0108] 제1 시간 레지스터(230)는, 어웨이크 신호(SAWK)에 응답하여, 어웨이크 신호(SAWK)의 상승 에지로부터, 디스차지 시간(Tdis)에서 제1 입력 신호(SIN1)와 제1 헬드 신호(SHLD1)간의 시간차(TD1+Toff)가 감산된 시간(Tdis-TD1-Toff) 후, 상승 에지를 가지는 제1 출력 신호(SOUT1)를 출력할 수 있다. 즉, 어웨이크 신호(SAWK) 및 제1 출력 신호(SOUT1)는 디스차지 시간(Tdis)에서 제1 입력 신호(SIN1)와 제1 헬드 신호(SHLD1)간의 시간차(TD1+Toff)가 감산된 시간에 상응하는 시간차(Tdis-TD1-Toff)를 가질 수 있다.

- [0109] 제2 시간 레지스터(270)는, 어웨이크 신호(SAWK)에 응답하여, 어웨이크 신호(SAWK)의 상승 에지로부터, 디스차지 시간(Tdis)에서 제4 입력 신호(SIN4)와 제2 헬드 신호(SHLD2)간의 시간차(-TD2+Toff)가 감산된 시간(Tdis-TD2-Toff) 후, 상승 에지를 가지는 제2 출력 신호(SOUT2)를 출력할 수 있다. 즉, 어웨이크 신호(SAWK) 및 제2 출력 신호(SOUT2)는 디스차지 시간(Tdis)에서 제4 입력 신호(SIN4)와 제2 헬드 신호(SHLD2)간의 시간차(-TD2+Toff)가 감산된 시간에 상응하는 시간차(Tdis-TD2-Toff)를 가질 수 있다.

- [0110] 한편, 제1 오프셋 지연기(220)와 제2 오프셋 지연기(260)는 실질적으로 동일한 오프셋 시간(Toff)을 가지고, 제1 시간 레지스터(230)와 제2 시간 레지스터(270)는 실질적으로 동일한 디스차지 시간(Tdis)를 가질 수 있다. 이에 따라, 제1 출력 신호(SOUT1)와 제2 출력 신호(SOUT2)간의 시간차는, 어웨이크 신호(SAWK)와 제2 출력 신호(SOUT2)간의 시간차(Tdis+TD2-Toff)에서 어웨이크 신호(SAWK)와 제1 출력 신호(SOUT1)간의 시간차(Tdis-TD1-Toff)가 감산된 시간((Tdis+TD2-Toff) - (Tdis-TD1-Toff)) = TD2 + TD1에 상응하고, 따라서, 제1 입력 신호(SIN1)와 제2 입력 신호(SIN2)간의 제1 시간차(TD1) 및 제3 입력 신호(SIN3)와 제4 입력 신호(SIN4)간의 제2 시간차(TD2)의 합(TD1+TD2)에 상응할 수 있다.

- [0111] 이와 같이, 본 발명의 일 실시예에 따른 시간차 가산기(200a)는 입력 신호들(SIN1, SIN2, SIN3, SIN4)간의 시간차들(TD1, TD2)을 정확하게 가산할 수 있다.

- [0112] 도 9b는 도 3의 시간차 가산기의 동작의 다른 예를 설명하기 위한 타이밍도이다. 도 9b에는 제1 입력 신호(SIN1) 및 제2 입력 신호(SIN2)가 음의 제1 시간차(-TD1)를 가지고, 제3 입력 신호(SIN3) 및 제4 입력 신호(SIN4)가 음의 제2 시간차(-TD2)를 가진 예가 도시되어 있다.

- [0113] 도 3 및 도 9b를 참조하면, 제1 입력 신호(SIN1)는 제1 시간 레지스터(230)의 제1 입력 단자(IN1)에 인가되고, 제2 입력 신호(SIN2)는 제1 오프셋 지연기(220)에 의해 오프셋 시간(Toff)만큼 지연되어 제1 홀드 신호(SHLD1)로서 제1 시간 레지스터(230)의 제1 홀드 단자(HLD1)에 인가된다. 이에 따라, 제1 입력 신호(SIN1) 및 제1 홀드 신호(SHLD1)는 제1 입력 신호(SIN1)와 제2 입력 신호(SIN2)간의 제1 시간차(-TD1)와 오프셋 시간(Toff)의 합에 상응하는 시간차(-TD1+Toff)를 가질 수 있다.

- [0114] 제4 입력 신호(SIN4)는 제2 시간 레지스터(270)의 제2 입력 단자(IN2)에 인가되고, 제3 입력 신호(SIN3)는 제2 오프셋 지연기(260)에 의해 오프셋 시간(Toff)만큼 지연되어 제2 홀드 신호(SHLD2)로서 제2 시간 레지스터(270)의 제2 홀드 단자(HLD2)에 인가된다. 이에 따라, 제4 입력 신호(SIN4) 및 제2 홀드 신호(SHLD2)는 오프셋 시간(Toff)에서 제3 입력 신호(SIN1)와 제4 입력 신호(SIN2)간의 제2 시간차(-TD2)가 감산된 시간에 상응하는 시간차(TD2+Toff)를 가질 수 있다.

- [0115] 제1 시간 레지스터(230)는, 어웨이크 신호(SAWK)에 응답하여, 어웨이크 신호(SAWK)의 상승 에지로부터, 디스차지 시간(Tdis)에서 제1 입력 신호(SIN1)와 제1 홀드 신호(SHLD1)간의 시간차(-TD1+Toff)가 감산된 시간((Tdis+TD1-Toff)) 후, 상승 에지를 가지는 제1 출력 신호(SOUT1)를 출력할 수 있다. 즉, 어웨이크 신호(SAWK) 및 제1 출력 신호(SOUT1)는 디스차지 시간(Tdis)에서 제1 입력 신호(SIN1)와 제1 홀드 신호(SHLD1)간의 시간차(-TD1+Toff)가 감산된 시간에 상응하는 시간차(Tdis+TD1-Toff)를 가질 수 있다.

- [0116] 제2 시간 레지스터(270)는, 어웨이크 신호(SAWK)에 응답하여, 어웨이크 신호(SAWK)의 상승 에지로부터, 디스차지 시간(Tdis)에서 제4 입력 신호(SIN4)와 제2 홀드 신호(SHLD2)간의 시간차(TD2+Toff)가 감산된 시간((Tdis-TD2-Toff)) 후, 상승 에지를 가지는 제2 출력 신호(SOUT2)를 출력할 수 있다. 즉, 어웨이크 신호(SAWK) 및 제2 출력 신호(SOUT2)는 디스차지 시간(Tdis)에서 제4 입력 신호(SIN4)와 제2 홀드 신호(SHLD2)간의 시간차(TD2+Toff)가 감산된 시간에 상응하는 시간차(Tdis-TD2-Toff)를 가질 수 있다.

- [0117] 한편, 제1 오프셋 지연기(220)와 제2 오프셋 지연기(260)는 실질적으로 동일한 오프셋 시간(Toff)을 가지고, 제1 시간 레지스터(230)와 제2 시간 레지스터(270)는 실질적으로 동일한 디스차지 시간(Tdis)를 가질 수 있다. 이에 따라, 제1 출력 신호(SOUT1)와 제2 출력 신호(SOUT2)간의 시간차는, 어웨이크 신호(SAWK)와 제2 출력 신호(SOUT2)간의 시간차(Tdis-TD2-Toff)에서 어웨이크 신호(SAWK)와 제1 출력 신호(SOUT1)간의 시간차(Tdis+TD1-Toff)가 감산된 시간((Tdis-TD2-Toff) - (Tdis+TD1-Toff)) = -TD2-TD1에 상응하고, 따라서, 제1 입력 신호(SIN1)와 제2 입력 신호(SIN2)간의 제1 시간차(-TD1) 및 제3 입력 신호(SIN3)와 제4 입력 신호(SIN4)간의 제2 시간차(-TD2)의 합(-TD1-TD2)에 상응할 수 있다.

- [0118] 이와 같이, 본 발명의 일 실시예에 따른 시간차 가산기(200a)는 입력 신호들(SIN1, SIN2, SIN3, SIN4)간의 시간차들(TD1, TD2)을 정확하게 가산할 수 있다.

- [0119] 한편, 도 9a 및 도 9b에는 제1 입력 신호(SIN1)의 상승 에지와 제2 입력 신호(SIN2)의 상승 에지 사이의 제1 시간차 및 제3 입력 신호(SIN3)의 상승 에지와 제4 입력 신호(SIN4)의 상승 에지 사이의 제2 시간차를 가산하여 상기 제1 시간차와 상기 제2 시간차의 합에 상응하는 시간차를 가지는 제1 출력 신호(SOUT1) 및 제2 출력 신호(SOUT2)를 생성하는 시간차 가산기의 시간차 가산의 예들이 도시되어 있으나, 실시예에 따라, 시간차 가산기는 제1 입력 신호(SIN1)의 하강 에지와 제2 입력 신호(SIN2)의 하강 에지 사이의 제3 시간차 및 제3 입력 신호(SIN3)의 하강 에지와 제4 입력 신호(SIN4)의 하강 에지 사이의 제4 시간차를 가산하여 상기 제3 시간차와 상기

제4 시간차의 합에 상응하는 시간차를 가지는 제1 출력 신호(SOUT1) 및 제2 출력 신호(SOUT2)를 생성할 수 있다. 또한, 다른 실시예에서, 시간차 가산기는 상기 상승 에지들에 대한 시간차 가산 및 상기 하강 에지들에 대한 시간차 가산을 모두 수행할 수 있다.

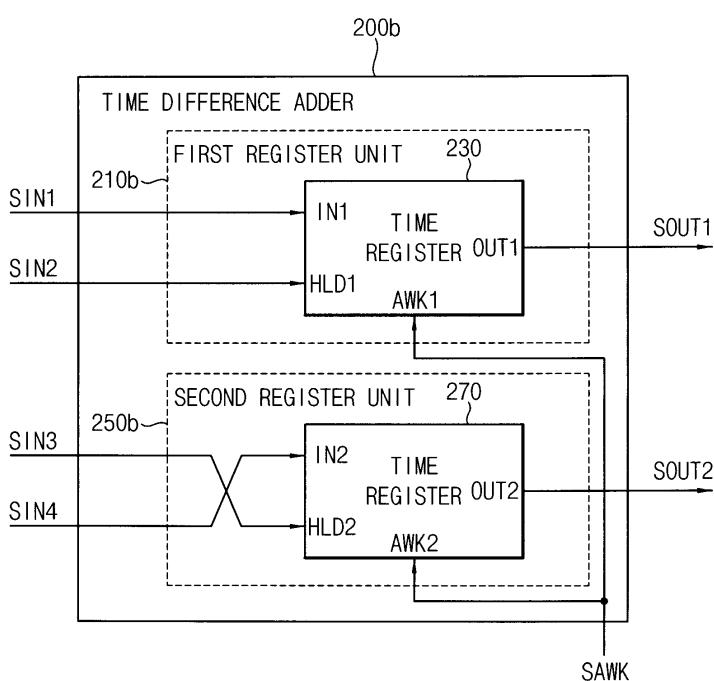

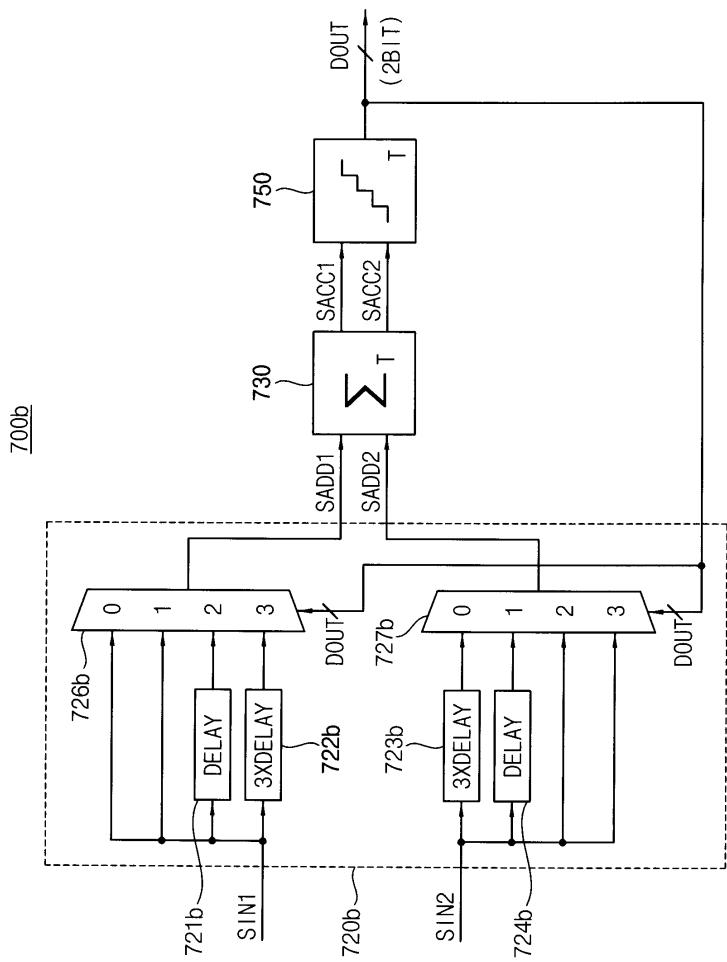

[0120] 도 10은 본 발명의 다른 실시예에 따른 시간차 가산기를 나타내는 블록도이다.

[0121] 도 10을 참조하면, 시간차 가산기(200b)는 제1 레지스터부(210b) 및 제2 레지스터부(250b)를 포함한다. 시간차 가산기(200b)는, 도 3의 시간차 가산기(200a)와 비교하여, 도 3의 제1 오프셋 지연기(220) 및 제2 오프셋 지연기(260)를 포함하지 않을 수 있다. 실시예에 따라, 시간차 가산기(200b)에는 양의 시간차를 가지는 제1 입력 신호(SIN1) 및 제2 입력 신호(SIN2)가 인가되고, 음의 시간차를 가지는 제3 입력 신호(SIN3) 및 제4 입력 신호(SIN4)가 인가될 수 있다.

[0122] 제1 레지스터부(210b)는 제1 입력 신호(SIN1) 및 제2 입력 신호(SIN2)를 수신하고, 어웨이크 신호(SAWK)에 응답하여 제1 출력 신호(SOUT1)를 생성한다. 제1 레지스터부(210b)는 제1 시간 레지스터(230)를 포함할 수 있다. 제1 시간 레지스터(230)는, 제1 입력 신호(SIN1)를 수신하는 제1 입력 단자(IN1), 제2 입력 신호(SIN2)를 수신하는 제1 홀드 단자(HLD1), 어웨이크 신호(SAWK)를 수신하는 제1 어웨이크 단자(AWK1), 및 제1 출력 신호(SOUT1)를 출력하는 제1 출력 단자(OUT1)를 가질 수 있다.

[0123] 제2 레지스터부(250b)는 제3 입력 신호(SIN3) 및 제4 입력 신호(SIN4)를 수신하고, 어웨이크 신호(SAWK)에 응답하여 제2 출력 신호(SOUT2)를 생성한다. 제2 레지스터부(250b)는 제2 시간 레지스터(270)를 포함할 수 있다. 제2 시간 레지스터(270)는, 제4 입력 신호(SIN4)를 수신하는 제2 입력 단자(IN2), 제3 입력 신호(SIN3)를 수신하는 제2 홀드 단자(HLD2), 어웨이크 신호(SAWK)를 수신하는 제2 어웨이크 단자(AWK2), 및 제2 출력 신호(SOUT2)를 출력하는 제2 출력 단자(OUT2)를 가질 수 있다.

[0124] 실시예에 따라, 제1 시간 레지스터(230) 및 제2 시간 레지스터(270) 각각은 도 4의 시간 레지스터(300a), 도 6의 시간 레지스터(300b), 도 7의 시간 레지스터(300c), 도 8의 시간 레지스터(300d), 또는 이와 유사한 구성을 가지는 시간 레지스터로 구현될 수 있다.

[0125] 제1 시간 레지스터(230)는, 어웨이크 신호(SAWK)에 응답하여, 어웨이크 신호(SAWK)의 상승 에지로부터, 디스차지 시간에서 제1 입력 신호(SIN1)와 제2 입력 신호(SIN2)간의 제1 시간차가 감산된 시간 후, 상승 에지를 가지는 제1 출력 신호(SOUT1)를 출력할 수 있다. 즉, 어웨이크 신호(SAWK)와 제1 출력 신호(SOUT1)간의 시간차는 상기 디스차지 시간에서 상기 제1 시간차가 감산된 시간에 상응할 수 있다.

[0126] 또한, 제2 시간 레지스터(270)는, 어웨이크 신호(SAWK)에 응답하여, 어웨이크 신호(SAWK)의 상기 상승 에지로부터, 상기 디스차지 시간에 제3 입력 신호(SIN3)와 제4 입력 신호(SIN4)간의 제2 시간차가 가산된 시간 후, 상승 에지를 가지는 제2 출력 신호(SOUT2)를 출력할 수 있다. 즉, 어웨이크 신호(SAWK)와 제2 출력 신호(SOUT2)간의 시간차는 상기 디스차지 시간에 상기 제2 시간차가 가산된 시간에 상응할 수 있다.

[0127] 제1 시간 레지스터(230)의 상기 디스차지 시간과 제2 시간 레지스터(270)의 상기 디스차지 시간은 실질적으로 동일할 수 있다. 이에 따라, 어웨이크 신호(SAWK)와 제2 출력 신호(SOUT2)간의 시간차에서 어웨이크 신호(SAWK)와 제1 출력 신호(SOUT1)간의 시간차가 감산된 시간에 상응하는 제1 출력 신호(SOUT1)와 제2 출력 신호(SOUT2)간의 시간차는, 상기 제1 시간차와 상기 제2 시간차의 합에 상응할 수 있다.

[0128] 이와 같이, 본 발명의 다른 실시예에 따른 시간차 가산기(200b)는 상기 제1 시간차와 상기 제2 시간차의 합에 상응하는 시간차를 가지는 제1 출력 신호(SOUT1) 및 제2 출력 신호(SOUT2)를 출력할 수 있다.

[0129] 도 11은 도 10의 시간차 가산기의 동작의 일 예를 설명하기 위한 타이밍도이다. 도 11에는 제1 입력 신호(SIN1) 및 제2 입력 신호(SIN2)가 양의 제1 시간차(TD1)를 가지고, 제3 입력 신호(SIN3) 및 제4 입력 신호(SIN4)가 음의 제2 시간차(-TD2)를 가진 예가 도시되어 있다.

[0130] 도 10 및 도 11을 참조하면, 제1 입력 신호(SIN1)는 제1 시간 레지스터(230)의 제1 입력 단자(IN1)에 인가되고, 제2 입력 신호(SIN2)는 제1 시간 레지스터(230)의 제1 홀드 단자(HLD1)에 인가된다. 또한, 제4 입력 신호(SIN4)는 제2 시간 레지스터(270)의 제2 입력 단자(IN2)에 인가되고, 제3 입력 신호(SIN3)는 제2 시간 레지스터(270)의 제2 홀드 단자(HLD2)에 인가된다.

[0131] 제1 시간 레지스터(230)는, 어웨이크 신호(SAWK)에 응답하여, 어웨이크 신호(SAWK)의 상승 에지로부터, 디스차지 시간(Tdis)에서 제1 입력 신호(SIN1)와 제2 입력 신호(SIN2)간의 제1 시간차(TD1)가 감산된 시간(Tdis-TD1) 후, 상승 에지를 가지는 제1 출력 신호(SOUT1)를 출력할 수 있다. 즉, 어웨이크 신호(SAWK) 및 제1 출력 신호

(SOUT1)는 디스차지 시간(Tdis)에서 제1 시간차(TD1)가 감산된 시간에 상응하는 시간차(Tdis-TD1)를 가질 수 있다.

[0132] 제2 시간 레지스터(270)는, 어웨이크 신호(SAWK)에 응답하여, 어웨이크 신호(SAWK)의 상승 에지로부터, 디스차지 시간(Tdis)에 제3 입력 신호(SIN3)와 제4 입력 신호(SIN4)간의 시간차(-TD2)가 가산된 시간(Tdis-TD2) 후, 상승 에지를 가지는 제2 출력 신호(SOUT2)를 출력할 수 있다. 즉, 어웨이크 신호(SAWK) 및 제2 출력 신호(SOUT2)는 디스차지 시간(Tdis)에 제2 시간차(-TD2)가 가산된 시간에 상응하는 시간차(Tdis-TD2)를 가질 수 있다.

[0133] 한편, 제1 시간 레지스터(230)와 제2 시간 레지스터(270)는 실질적으로 동일한 디스차지 시간(Tdis)을 가질 수 있다. 이에 따라, 제1 출력 신호(SOUT1)와 제2 출력 신호(SOUT2)간의 시간차는, 어웨이크 신호(SAWK)와 제2 출력 신호(SOUT2)간의 시간차(Tdis-TD2)에서 어웨이크 신호(SAWK)와 제1 출력 신호(SOUT1)간의 시간차(Tdis-TD1)가 감산된 시간((Tdis-TD2) - (Tdis-TD1) = -TD2 + TD1)에 상응하고, 따라서, 제1 입력 신호(SIN1)와 제2 입력 신호(SIN2)간의 제1 시간차(TD1) 및 제3 입력 신호(SIN3)와 제4 입력 신호(SIN4)간의 제2 시간차(-TD2)의 합(TD1-TD2)에 상응할 수 있다.

[0134] 이와 같이, 본 발명의 다른 실시예에 따른 시간차 가산기(200b)는 입력 신호들(SIN1, SIN2, SIN3, SIN4)간의 시간차들(TD1, TD2)을 정확하게 가산할 수 있다.

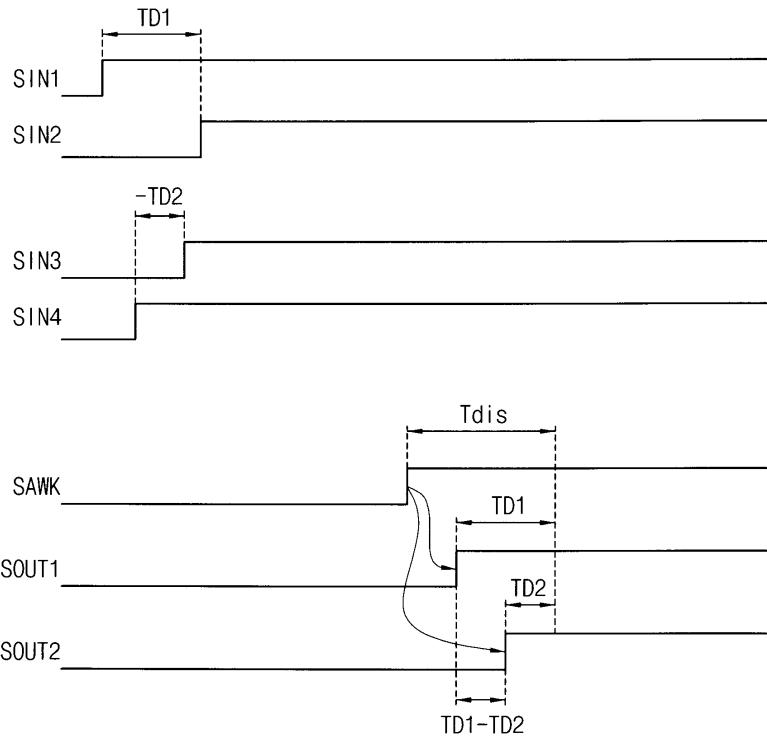

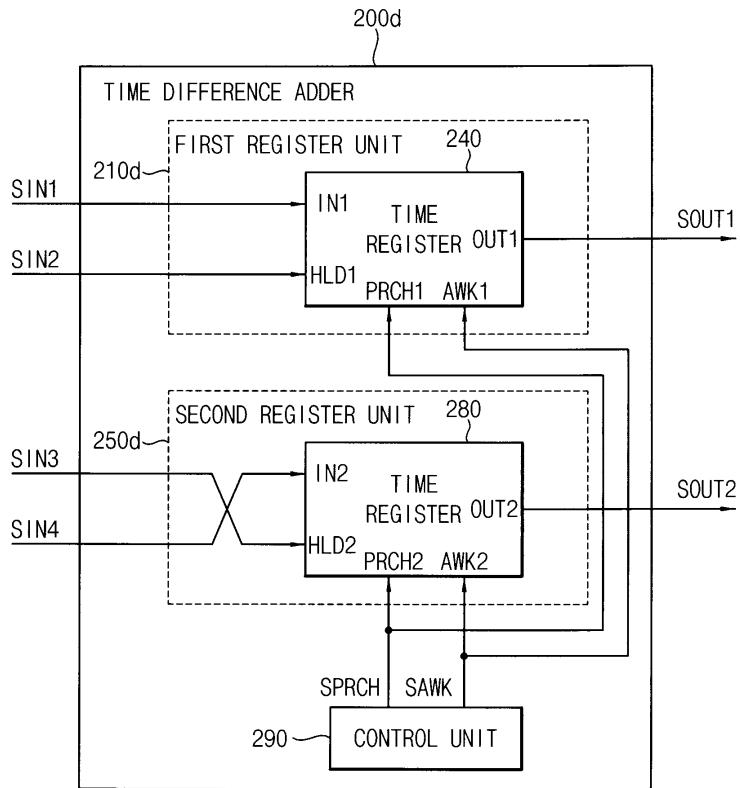

[0135] 도 12는 본 발명의 또 다른 실시예에 따른 시간차 가산기를 나타내는 블록도이다.

[0136] 도 12를 참조하면, 시간차 가산기(200c)는 제1 레지스터부(210c), 제2 레지스터부(250c) 및 제어부(290)를 포함한다.

[0137] 제1 레지스터부(210c)는 제1 입력 신호(SIN1) 및 제2 입력 신호(SIN2)를 수신하고, 어웨이크 신호(SAWK)에 응답하여 제1 출력 신호(SOUT1)를 생성한다. 제1 레지스터부(210c)는 제1 오프셋 지연기(220) 및 제1 시간 레지스터(240)를 포함할 수 있다. 제1 오프셋 지연기(220)는 제2 입력 신호(SIN2)를 오프셋 시간만큼 지연시켜 제1 홀드 신호(SHLD1)를 생성할 수 있다. 제1 시간 레지스터(240)는, 제1 입력 신호(SIN1)를 수신하는 제1 입력 단자(IN1), 제1 홀드 신호(SHLD1)를 수신하는 제1 홀드 단자(HLD1), 프리차지 신호(SPRCH)를 수신하는 제1 프리차지 단자(PRCH1), 어웨이크 신호(SAWK)를 수신하는 제1 어웨이크 단자(AWK1), 및 제1 출력 신호(SOUT1)를 출력하는 제1 출력 단자(OUT1)를 가질 수 있다.

[0138] 제2 레지스터부(250c)는 제3 입력 신호(SIN3) 및 제4 입력 신호(SIN4)를 수신하고, 어웨이크 신호(SAWK)에 응답하여 제2 출력 신호(SOUT2)를 생성한다. 제2 레지스터부(250c)는 제2 오프셋 지연기(260) 및 제2 시간 레지스터(280)를 포함할 수 있다. 제2 오프셋 지연기(260)는 제3 입력 신호(SIN3)를 상기 오프셋 시간만큼 지연시켜 제2 홀드 신호(SHLD2)를 생성할 수 있다. 제2 시간 레지스터(280)는, 제4 입력 신호(SIN4)를 수신하는 제2 입력 단자(IN2), 제2 홀드 신호(SHLD2)를 수신하는 제2 홀드 단자(HLD2), 프리차지 신호(SPRCH)를 수신하는 제2 프리차지 단자(PRCH2), 어웨이크 신호(SAWK)를 수신하는 제2 어웨이크 단자(AWK2), 및 제2 출력 신호(SOUT2)를 출력하는 제2 출력 단자(OUT2)를 가질 수 있다.

[0139] 제어부(290)는 프리차지 신호(SPRCH) 및 어웨이크 신호(SAWK)를 생성한다. 예를 들어, 제어부(290)는 제1 입력 신호(SIN1), 제2 입력 신호(SIN2), 제3 입력 신호(SIN3) 또는 제4 입력 신호(SIN4) 중 어느 하나의 신호를 지연 및/또는 반전시켜 프리차지 신호(SPRCH) 및 어웨이크 신호(SAWK)를 생성할 수 있다. 일 실시예에서, 제어부(290)는 어웨이크 신호(SAWK)가 상승 에지를 가진 후 프리차지 신호(SPRCH)가 상승 에지를 가지도록 프리차지 신호(SPRCH) 및 어웨이크 신호(SAWK)를 생성할 수 있다.

[0140] 제1 시간 레지스터(240)는, 어웨이크 신호(SAWK)에 응답하여, 어웨이크 신호(SAWK)의 상승 에지로부터, 디스차지 시간에서 상기 오프셋 시간이 감산되고 제1 입력 신호(SIN1)와 제2 입력 신호(SIN2)간의 제1 시간차가 감산된 시간 후, 상승 에지를 가지는 제1 출력 신호(SOUT1)를 출력할 수 있다. 즉, 어웨이크 신호(SAWK)와 제1 출력 신호(SOUT1)간의 시간차는 상기 디스차지 시간에서 상기 오프셋 시간이 감산되고 상기 제1 시간차가 더욱 감산된 시간에 상응할 수 있다.

[0141] 또한, 제2 시간 레지스터(280)는, 어웨이크 신호(SAWK)에 응답하여, 어웨이크 신호(SAWK)의 상기 상승 에지로부터, 상기 디스차지 시간에서 상기 오프셋 시간이 감산되고 제3 입력 신호(SIN3)와 제4 입력 신호(SIN4)간의 제2 시간차가 가산된 시간 후, 상승 에지를 가지는 제2 출력 신호(SOUT2)를 출력할 수 있다. 즉, 어웨이크 신호(SAWK)와 제2 출력 신호(SOUT2)간의 시간차는 상기 디스차지 시간에서 상기 오프셋 시간이 감산되고 상기 제2

시간차가 가산된 시간에 상응할 수 있다.

[0142] 제1 오프셋 지연기(220)의 상기 오프셋 시간과 제2 오프셋 지연기(260)의 상기 오프셋 시간은 실질적으로 동일 할 수 있다. 또한, 제1 시간 레지스터(240)의 상기 디스차지 시간과 제2 시간 레지스터(280)의 상기 디스차지 시간은 실질적으로 동일할 수 있다. 이에 따라, 어웨이크 신호(SAWK)와 제2 출력 신호(SOUT2)간의 시간차에서 어웨이크 신호(SAWK)와 제1 출력 신호(SOUT1)간의 시간차가 감산된 시간에 상응하는 제1 출력 신호(SOUT1)와 제2 출력 신호(SOUT2)간의 시간차는, 상기 제1 시간차와 상기 제2 시간차의 합에 상응할 수 있다.

[0143] 제1 시간 레지스터(240) 및 제2 시간 레지스터(280)는 프리차지 신호(SPRCH)에 응답하여 각각에 포함된 커패시터를 충전할 수 있다.

[0144] 상술한 바와 같이, 본 발명의 또 다른 실시예에 따른 시간차 가산기(200c)는 상기 제1 시간차와 상기 제2 시간 차의 합에 상응하는 시간차를 가지는 제1 출력 신호(SOUT1) 및 제2 출력 신호(SOUT2)를 출력할 수 있다.

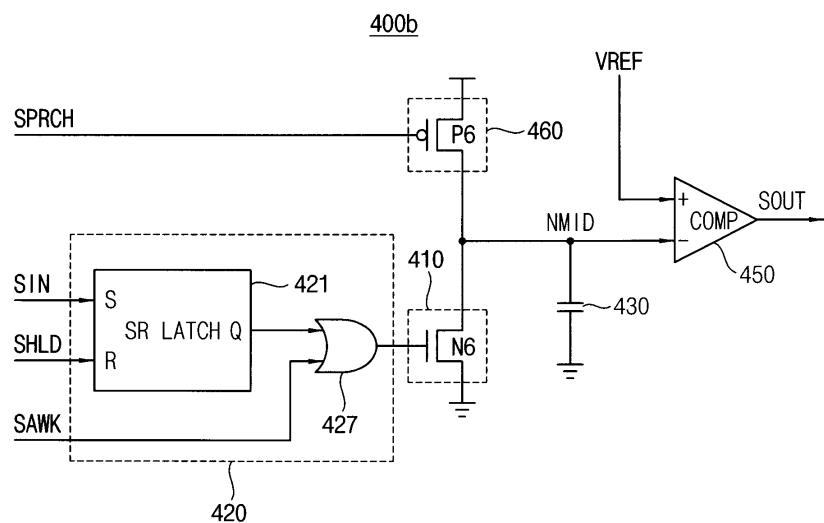

[0145] 도 13은 도 12의 시간차 가산기에 포함된 시간 레지스터의 일 예를 나타내는 회로도이다.

[0146] 도 13을 참조하면, 시간 레지스터(400a)는 풀-다운 트랜지스터(410), 풀-업 트랜지스터(460), 풀-다운 트랜지스터 제어부(420), 커패시터(430) 및 출력부(440)를 포함한다. 일 실시예에서, 도 12의 제1 시간 레지스터(240) 및 제2 시간 레지스터(280)는 시간 레지스터(400a)와 같이 구현될 수 있다.

[0147] 풀-다운 트랜지스터(410)는 중간 노드(NMID)와 접지 전압 사이에 연결되고, 커패시터(430)를 방전시키도록 풀-다운 트랜지스터 제어부(420)에 의해 제어될 수 있다. 예를 들어, 풀-다운 트랜지스터(410)는, 풀-다운 트랜지스터 제어부(420)의 출력 신호가 인가되는 게이트, 상기 접지 전압에 연결된 소스, 및 중간 노드(NMID)에 연결된 드레인을 가지는 NMOS 트랜지스터(N6)를 포함할 수 있다.

[0148] 풀-업 트랜지스터(460)는 중간 노드(NMID)와 전원 전압 사이에 연결되고, 프리차지 신호(SPRCH)에 응답하여 커 패시터(430)를 충전시킬 수 있다. 예를 들어, 풀-업 트랜지스터(460)는, 프리차지 신호(SPRCH)가 인가되는 게이 트, 상기 전원 전압에 연결된 소스, 및 중간 노드(NMID)에 연결된 드레인을 가지는 PMOS 트랜지스터(P6)를 포함 할 수 있다.

[0149] 풀-다운 트랜지스터 제어부(420)는, 입력 신호(SIN)에 응답하여 풀-다운 트랜지스터(410)를 턴-온시키고, 홀드 신호(SHLD)에 응답하여 풀-다운 트랜지스터(410)를 턴-오프시키며, 어웨이크 신호(SAWK)에 응답하여 풀-다운 트 랜지스터(410)를 턴-온시킬 수 있다. 풀-다운 트랜지스터 제어부(420)는 셋-리셋 래치(421) 및 OR 게이트(427)를 포함할 수 있다.

[0150] 셋-리셋 래치(421)는 입력 신호(SIN)를 수신하는 셋 단자(S), 홀드 신호(SHLD)를 수신하는 리셋 단자(R), 및 출력 신호를 출력하는 출력 단자(Q)를 포함할 수 있다. 셋-리셋 래치(421)는 제1 NOR 게이트(423) 및 제2 NOR 게이트(425)를 포함할 수 있다. 제1 NOR 게이트(423)는 입력 신호(SIN) 및 제2 NOR 게이트(425)의 출력 신호에 NOR 연산을 수행하고, 제2 NOR 게이트(425)는 홀드 신호(SHLD) 및 제1 NOR 게이트(423)의 출력 신호에 NOR 연 산을 수행할 수 있다.

[0151] 셋-리셋 래치(421)는, 입력 신호(SIN)가 로직 하이 레벨을 가지고, 홀드 신호(SHLD)가 로직 로우 레벨을 가질 때, 로직 하이 레벨의 출력 신호를 생성할 수 있다. 또한, 셋-리셋 래치(421)는, 홀드 신호(SHLD)가 로직 하이 레벨을 가질 때, 입력 신호(SIN)의 로직 레벨과 무관하게 로직 로우 레벨의 출력 신호를 생성할 수 있다. 또한, 셋-리셋 래치(421)는, 입력 신호(SIN) 및 홀드 신호(SHLD)가 모두 로직 로우 레벨을 가질 때, 이전 출력 신호의 로직 레벨과 동일한 로직 레벨을 가지는 출력 신호를 생성할 수 있다.

[0152] OR 게이트(427)는 셋-리셋 래치(421)의 출력 단자(Q)에서 출력된 상기 출력 신호 및 어웨이크 신호(SAWK)에 OR 연산을 수행한다. OR 게이트(427)의 출력 단자는 풀-다운 트랜지스터(410)의 게이트에 연결되고, 풀-다운 트랜지스터(410)는 OR 게이트(427)의 출력 신호에 의하여 제어될 수 있다.

[0153] 커패시터(430)는 풀-업 트랜지스터(460)에 의하여 충전되고, 풀-다운 트랜지스터(410)에 의하여 방전될 수 있다. 또한, 커패시터(430)는 중간 노드(NMID)에 연결된 제1 단자 및 상기 접지 전압에 연결된 제2 단자를 가질 수 있다. 예를 들어, 풀-업 트랜지스터(460)가 턴-온된 경우, 커패시터(430)의 상기 제1 단자는 풀-업 트랜지스터(460)를 통하여 상기 전원 전압에 전기적으로 연결되고, 커패시터(430)가 충전될 수 있다. 또한, 풀-다운 트랜지스터(410)가 턴-온된 경우, 커패시터(430)의 상기 제1 단자는 풀-다운 트랜지스터(410)를 통하여 상기 접지 전압에 전기적으로 연결되고, 커패시터(430)가 방전될 수 있다.

- [0154] 출력부(440)는 커패시터(430)의 전압(즉, 중간 노드(NMID)의 전압)에 기초하여 출력 신호(SOUT)를 생성할 수 있다. 예를 들어, 출력부(440)는 인버터(440)를 포함할 수 있다. 인버터(440)는 PMOS 트랜지스터(P3) 및 NMOS 트랜지스터(N3)를 포함할 수 있다. 인버터(440)는, 커패시터(430)의 전압이 소정의 문턱 전압 이하일 때, 로직 하이 레벨을 가지는 출력 신호(SOUT)를 출력할 수 있다. 즉, 커패시터(430)의 전압이 PMOS 트랜지스터(P3)의 문턱 전압 이하일 때, PMOS 트랜지스터(P3)가 터-온되고, 인버터(440)는 로직 하이 레벨을 가지는 출력 신호(SOUT)를 출력할 수 있다.

- [0155] 커패시터(430)는, 입력 신호(SIN)와 홀드 신호(SHLD)간의 시간차에 상응하는 시간 동안 방전됨으로써, 입력 신호(SIN)와 홀드 신호(SHLD)간의 상기 시간차에 대한 정보를 저장할 수 있다. 즉, 커패시터(430)의 방전이 입력 신호(SIN)의 상승 에지에 응답하여 시작되고, 커패시터(430)의 방전이 홀드 신호(SHLD)의 상승 에지에 응답하여 중지됨으로써, 커패시터(430)는 입력 신호(SIN)와 홀드 신호(SHLD)간의 상기 시간차에 상응하는 시간 동안 방전될 수 있다. 또한, 커패시터(430)의 방전은 어웨이크 신호(SAWK)의 상승 에지로부터 소정의 시간 후, 상기 소정의 문턱 전압(예를 들어, PMOS 트랜지스터(P3)의 문턱 전압) 이하로 낮아질 수 있고, 상기 소정의 시간은 입력 신호(SIN)와 홀드 신호(SHLD)간의 상기 시간차에 따라 결정될 수 있다. 또한, 출력부(440)는, 커패시터(430)의 전압이 상기 소정의 문턱 전압 이하로 낮아질 때, 로직 하이 레벨을 가지는 출력 신호(SOUT)를 출력할 수 있다. 이에 따라, 출력 신호(SOUT)는, 어웨이크 신호(SAWK)의 상승 에지로부터 상기 시간차에 따라 결정되는 상기 소정의 시간 후, 상승 에지를 가질 수 있다. 즉, 출력 신호(SOUT)가 상승 에지를 가지는 시점은 입력 신호(SIN)와 홀드 신호(SHLD)간의 상기 시간차에 따라 결정될 수 있다.

- [0156] 예를 들어, 셋-리셋 래치(421)는 입력 신호(SIN)의 상승 에지에 응답하여 로직 하이 레벨의 출력 신호를 생성하고, OR 게이트(427)는 셋-리셋 래치(421)의 상기 로직 하이 레벨의 출력 신호에 응답하여 로직 하이 레벨의 출력 신호를 생성할 수 있다. 풀-다운 트랜지스터(410)는 OR 게이트(427)의 상기 로직 하이 레벨의 출력 신호에 응답하여 터-온되고, 터-온된 풀-다운 트랜지스터(410)에 의하여 커패시터(430)의 방전이 시작될 수 있다. 이후, 셋-리셋 래치(421)는 홀드 신호(SHLD)의 상승 에지에 응답하여 로직 로우 레벨의 출력 신호를 생성하고, OR 게이트(427)는 셋-리셋 래치(421)의 상기 로직 로우 레벨의 출력 신호 및 로직 로우 레벨의 어웨이크 신호(SAWK)에 응답하여 로직 로우 레벨의 출력 신호를 생성할 수 있다. 풀-다운 트랜지스터(410)는 OR 게이트(427)의 상기 로직 로우 레벨의 출력 신호에 응답하여 터-오프되고, 터-오프된 풀-다운 트랜지스터(410)에 의하여 커패시터(430)의 방전이 중지될 수 있다. 이어서, OR 게이트(427)는 어웨이크 신호(SAWK)의 상승 에지에 응답하여 로직 하이 레벨의 출력 신호를 생성할 수 있다. 풀-다운 트랜지스터(410)는 OR 게이트(427)의 상기 로직 하이 레벨의 출력 신호에 응답하여 터-온되고, 터-온된 풀-다운 트랜지스터(410)에 의하여 커패시터(430)의 방전이 재개될 수 있다. 커패시터(430)의 방전이 재개된 후, 커패시터(430)의 전압, 즉, 중간 노드(NMID)의 전압이 상기 소정의 문턱 전압 이하로 낮아질 때, 출력부(440)는 로직 하이 레벨을 가지는 출력 신호(SOUT)를 출력할 수 있다.

- [0157] 이에 따라, 시간 레지스터(400a)는 어웨이크 신호(SAWK)에 응답하여 입력 신호(SIN)와 홀드 신호(SHLD)간의 시간차에 따라 결정되는 시점에서 상승 에지를 가지는 출력 신호(SOUT)를 출력할 수 있다.

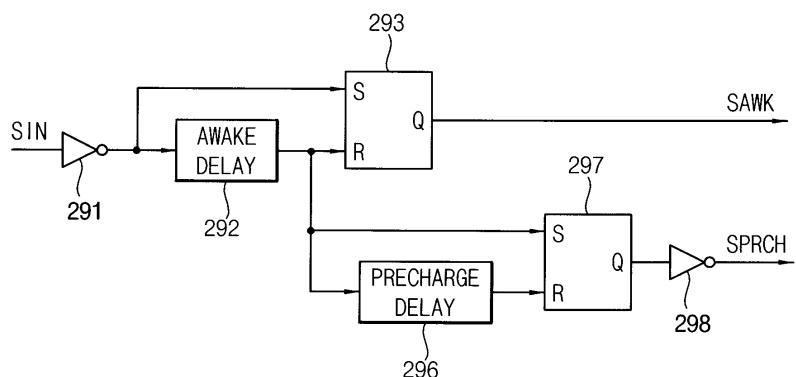

- [0158] 도 14는 도 12의 시간차 가산기에 포함된 제어부의 일 예를 나타내는 회로도이다.

- [0159] 도 14를 참조하면, 제어부(290)는 제1 인버터(291), 어웨이크 지연기(292), 제1 셋-리셋 래치(293), 프리차지 지연기(296), 제2 셋-리셋 래치(297) 및 제2 인버터(298)를 포함한다.

- [0160] 제1 인버터(291)는 입력 신호(SIN)를 반전시켜 입력 신호(SIN)의 반전 신호를 생성한다. 실시예에 따라, 입력 신호(SIN)는 도 12의 제1 입력 신호(SIN1), 제2 입력 신호(SIN2), 제3 입력 신호(SIN3), 제4 입력 신호(SIN4), 또는 다른 신호일 수 있다. 제1 인버터(291)는 입력 신호(SIN)의 상기 반전 신호를 어웨이크 지연기(292) 및 제1 셋-리셋 래치(293)에 제공할 수 있다.

- [0161] 어웨이크 지연기(292) 및 제1 셋-리셋 래치(293)는 어웨이크 펄스 생성기를 구성할 수 있다. 어웨이크 지연기(292)는 입력 신호(SIN)의 상기 반전 신호를 소정의 지연 시간만큼 지연시킨다. 실시예에 따라, 어웨이크 지연기(292)의 상기 지연 시간은 시간 레지스터의 디스차지 시간 이상이 되도록 설정될 수 있다.

- [0162] 제1 셋-리셋 래치(293)는, 입력 신호(SIN)의 상기 반전 신호를 수신하는 셋 단자(S), 어웨이크 지연기(292)의 출력 신호를 수신하는 리셋 단자(R), 및 어웨이크 신호(SAWK)를 출력하는 출력 단자(Q)를 포함할 수 있다. 제1 셋-리셋 래치(293)는, 어웨이크 신호(SAWK)가 입력 신호(SIN)의 상기 반전 신호(즉, 어웨이크 지연기(292)의 입

력 신호)의 상승 에지에 응답하여 상승 에지를 가지고, 어웨이크 지연기(292)의 상기 출력 신호의 상승 에지에 응답하여 하강 에지를 가지고록, 어웨이크 신호(SAWK)를 생성할 수 있다. 이에 따라, 어웨이크 신호(SAWK)의 상기 상승 에지와 상기 하강 에지의 간격인 어웨이크 신호(SAWK)의 펄스 폭은, 어웨이크 지연기(292)의 상기 출력 신호의 상승 에지와 어웨이크 지연기(292)의 상기 출력 신호의 상승 에지의 간격, 즉 어웨이크 지연기(292)의 상기 지연 시간에 상응할 수 있다.

[0163] 프리차지 지연기(296) 및 제2 셋-리셋 래치(297)는 프리차지 펄스 생성기를 구성할 수 있다. 프리차지 지연기(296)는 어웨이크 지연기(292)의 상기 출력 신호를 소정의 지연 시간만큼 지연시킨다. 실시예에 따라, 프리차지 지연기(296)의 상기 지연 시간은 시간 레지스터에 포함된 커패시터가 실질적으로 완전히 충전되기 위한 시간 이상으로 설정될 수 있다.

[0164] 제2 셋-리셋 래치(297)는, 어웨이크 지연기(292)의 상기 출력 신호를 수신하는 셋 단자(S), 프리차지 지연기(296)의 출력 신호를 수신하는 리셋 단자(R), 및 출력 신호를 출력하는 출력 단자(Q)를 포함할 수 있다. 또한, 제2 인버터(298)는 제2 셋-리셋 래치(297)의 상기 출력 신호를 반전시켜 프리차지 신호(SPRCH)를 생성할 수 있다.

[0165] 제2 셋-리셋 래치(297) 및 제2 인버터(298)는, 프리차지 신호(SPRCH)가 어웨이크 지연기(292)의 상기 출력 신호(즉, 프리차지 지연기(296)의 입력 신호)의 상승 에지에 응답하여 하강 에지를 가지고, 프리차지 지연기(296)의 상기 출력 신호의 상승 에지에 응답하여 상승 에지를 가지고록, 프리차지 신호(SPRCH)를 생성할 수 있다. 이에 따라, 프리차지 신호(SPRCH)의 상기 하강 에지와 상기 상승 에지의 간격은, 프리차지 지연기(296)의 상기 입력 신호의 상승 에지와 프리차지 지연기(296)의 상기 출력 신호의 상승 에지의 간격, 즉 프리차지 지연기(296)의 상기 지연 시간에 상응할 수 있다.

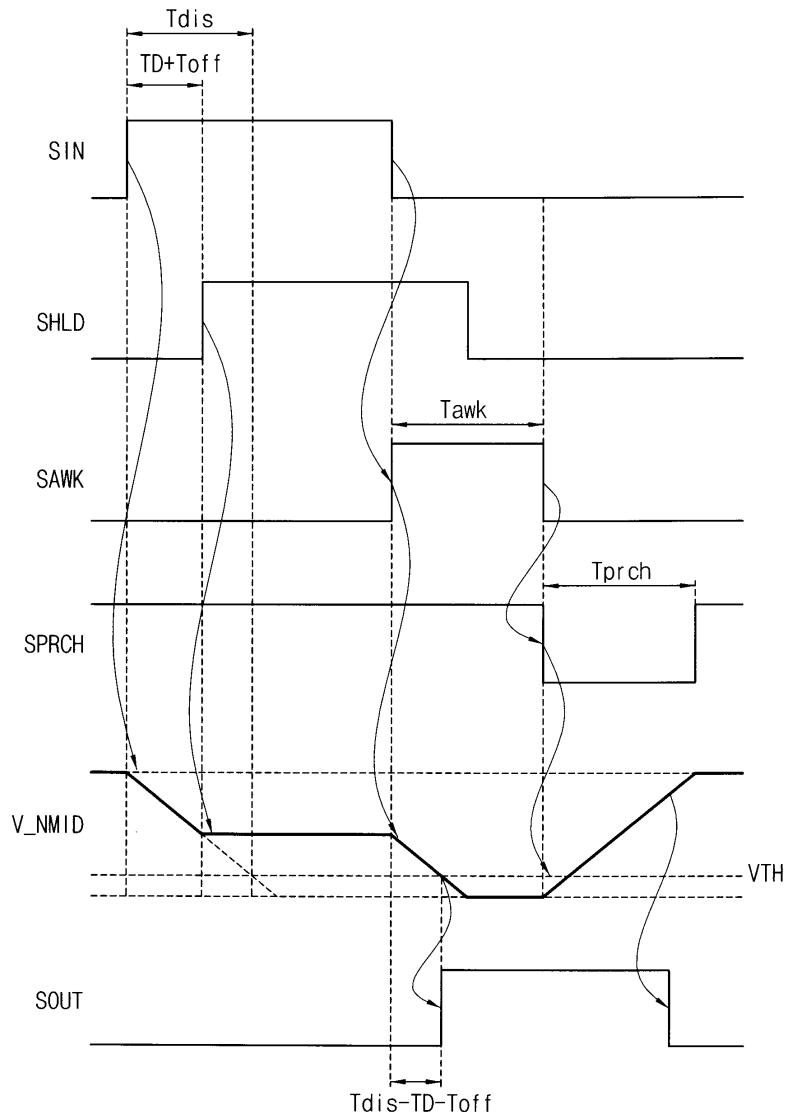

[0166] 도 15는 도 13의 시간 레지스터의 동작을 설명하기 위한 타이밍도이다.

[0167] 도 13, 도 14 및 도 15를 참조하면, 풀-다운 트랜지스터 제어부(420)는 입력 신호(SIN)의 상승 에지에 응답하여 로직 하이 레벨의 출력 신호를 생성할 수 있다. 예를 들어, 셋-리셋 래치(421)는 입력 신호(SIN)의 상승 에지에 응답하여 출력 단자(Q)에서 로직 하이 레벨의 출력 신호를 생성하고, OR 게이트(427)는 셋-리셋 래치(421)의 상기 로직 하이 레벨의 출력 신호에 응답하여 로직 하이 레벨의 출력 신호를 생성할 수 있다. 풀-다운 트랜지스터(410)의 NMOS 트랜지스터(N6)는 OR 게이트(427)의 상기 로직 하이 레벨의 출력 신호에 응답하여 턴-온될 수 있다. 풀-다운 트랜지스터(410)의 NMOS 트랜지스터(N6)가 턴-온되면, 중간 노드(NMID), 즉 커패시터(430)의 제1 단자는 NMOS 트랜지스터(N6)를 통하여 접지 전압에 연결되고, 커패시터(430)는 방전될 수 있다. 이와 같이, 입력 신호(SIN)의 상승 에지에 응답하여 커패시터(430)가 방전되고, 커패시터(430)의 전압, 즉 중간 노드(NMID)의 전압(V\_NMID)이 감소될 수 있다.

[0168] 풀-다운 트랜지스터 제어부(420)는 홀드 신호(SHLD)의 상승 에지에 응답하여 로직 로우 레벨의 출력 신호를 생성할 수 있다. 예를 들어, 셋-리셋 래치(421)는 홀드 신호(SHLD)의 상승 에지에 응답하여 출력 단자(Q)에서 로직 로우 레벨의 출력 신호를 생성하고, OR 게이트(427)는 셋-리셋 래치(421)의 상기 로직 로우 레벨의 출력 신호 및 로직 로우 레벨의 어웨이크 신호(SAWK)에 응답하여 로직 로우 레벨의 출력 신호를 생성할 수 있다. 풀-다운 트랜지스터(410)의 NMOS 트랜지스터(N6)는 OR 게이트(427)의 상기 로직 로우 레벨의 출력 신호에 응답하여 턴-오프될 수 있다. 풀-다운 트랜지스터(410)의 NMOS 트랜지스터(N6)가 턴-오프되면, 커패시터(430)의 방전이 중지될 수 있다. 이와 같이, 홀드 신호(SHLD)의 상승 에지에 응답하여 커패시터(430)의 방전이 중지되고, 커패시터(430)의 전압, 즉 중간 노드(NMID)의 전압(V\_NMID)의 감소가 중지될 수 있다.

[0169] 제어부(290)는 입력 신호(SIN)의 하강 에지에 응답하여 로직 하이 레벨의 어웨이크 신호(SAWK)를 생성할 수 있다. 어웨이크 신호(SAWK)는 시간 레지스터(400a)의 디스차지 시간(Tdis) 이상의 로직 하이 구간(Tawk)을 가질 수 있다. 어웨이크 신호(SAWK)의 펄스 폭, 즉 로직 하이 구간(Tawk)은 어웨이크 지연기(292)의 지연 시간에 상응할 수 있다.

[0170] 풀-다운 트랜지스터 제어부(420)는 어웨이크 신호(SAWK)의 상승 에지에 응답하여 로직 하이 레벨의 출력 신호를 생성할 수 있다. 예를 들어, OR 게이트(427)는 어웨이크 신호(SAWK)의 상승 에지에 응답하여 로직 하이 레벨의 출력 신호를 생성할 수 있다. 풀-다운 트랜지스터(410)의 NMOS 트랜지스터(N6)는 OR 게이트(427)의 상기 로직 하이 레벨의 출력 신호에 응답하여 턴-온될 수 있다. 풀-다운 트랜지스터(410)의 NMOS 트랜지스터(N6)가 턴-온되면, 중간 노드(NMID)는 NMOS 트랜지스터(N6)를 통하여 상기 접지 전압에 연결되고, 커패시터(430)의 방전이 재개될 수 있다. 이와 같이, 어웨이크 신호(SAWK)의 상승 에지에 응답하여 커패시터(430)의 방전이 재개되고,

커패시터(430)의 전압, 즉 중간 노드(NMID)의 전압(V\_NMID)이 다시 감소될 수 있다.

[0171] 출력부(440)는 커패시터(430)의 전압, 즉 중간 노드(NMID)의 전압(V\_NMID)에 기초하여 출력 신호(SOUT)를 출력한다. 출력부(440)는, 중간 노드(NMID)의 전압(V\_NMID)이 소정의 문턱 전압(VTH) 이하인 경우, 로직 하이 레벨의 출력 신호(SOUT)를 출력할 수 있다. 예를 들어, 문턱 전압(VTH)은 출력부(440)의 PMOS 트랜지스터(P3)의 문턱 전압일 수 있다. 즉, 중간 노드(NMID)의 전압(V\_NMID)이 PMOS 트랜지스터(P3)의 문턱 전압 이하로 낮아지는 경우, PMOS 트랜지스터(P3)가 턴-온되고, 출력 신호(SOUT)는 로직 하이 레벨을 가질 수 있다.

[0172] 한편, 출력 신호(SOUT)는 어웨이크 신호(SAWK)의 상승 에지로부터, 소정의 디스차지 시간(Tdis)에서 입력 신호(SIN)와 홀드 신호(SHLD)간의 시간차(TD+Toff)가 감산된 시간(Tdis-TD-Toff) 후, 상승 에지를 가질 수 있다. 즉, 출력 신호(SOUT)가 상승 에지를 가지는 시점은 입력 신호(SIN)와 홀드 신호(SHLD)간의 시간차(TD+Toff)에 따라 결정될 수 있다.

[0173] 제어부(290)는 어웨이크 신호(SAWK)의 하강 에지에 응답하여 로직 로우 레벨의 프리차지 신호(SPRCH)를 생성할 수 있다. 프리차지 신호(SPRCH)는 커패시터(430)가 실질적으로 완전히 충전되기 위한 시간 이상의 로직 로우 구간(Tprch)을 가질 수 있다. 프리차지 신호(SPRCH)의 로직 로우 구간(Tprch)은 프리차지 지연기(296)의 지연 시간에 상응할 수 있다.

[0174] 풀-업 트랜지스터(460)의 PMOS 트랜지스터(P6)는 프리차지 신호(SPRCH)의 하강 에지에 응답하여 턴-온될 수 있다. 풀-업 트랜지스터(460)의 PMOS 트랜지스터(P6)가 턴-온되면, 중간 노드(NMID), 즉 커패시터(430)의 제1 단자는 PMOS 트랜지스터(P6)를 통하여 전원 전압에 연결되고, 커패시터(430)는 다시 충전될 수 있다.

[0175] 도 16은 도 12의 시간차 가산기에 포함된 시간 레지스터의 다른 예를 나타내는 회로도이다.

[0176] 도 16을 참조하면, 시간 레지스터(400b)는 풀-다운 트랜지스터(410), 풀-업 트랜지스터(460), 풀-다운 트랜지스터 제어부(420), 커패시터(430) 및 출력부(450)를 포함한다. 시간 레지스터(400b)는, 출력부(450)의 구성 및 동작을 제외하고 도 13의 시간 레지스터(400a)와 실질적으로 유사한 구성을 가지고, 실질적으로 유사한 동작을 수행할 수 있다.

[0177] 출력부(450)는 커패시터(430)의 전압(즉, 중간 노드(NMID)의 전압)에 기초하여 출력 신호(SOUT)를 생성할 수 있다. 예를 들어, 출력부(450)는 비교기(450)를 포함할 수 있다. 비교기(450)는 기준 전압(VREF)을 수신하는 비반전 입력 단자, 커패시터(430)의 전압을 수신하는 반전 입력 단자, 및 출력 신호(SOUT)를 출력하는 출력 단자를 포함할 수 있다. 실시예에 따라, 기준 전압(VREF)은 외부의 회로 또는 장치에서 수신되거나, 시간 레지스터(400b)가 기준 전압(VREF)을 생성하는 회로를 포함할 수 있다. 기준 전압(VREF)은 전원 전압보다 낮을 수 있다.

[0178] 도 17은 도 12의 시간차 가산기의 동작의 일 예를 설명하기 위한 타이밍도이다. 도 17에는 제1 입력 신호(SIN1) 및 제2 입력 신호(SIN2)가 양의 제1 시간차(TD1)를 가지고, 제3 입력 신호(SIN3) 및 제4 입력 신호(SIN4)가 양의 제2 시간차(TD2)를 가진 예가 도시되어 있다.

[0179] 도 12 및 도 17을 참조하면, 제1 입력 신호(SIN1)는 제1 시간 레지스터(240)의 제1 입력 단자(IN1)에 인가되고, 제2 입력 신호(SIN2)는 제1 오프셋 지연기(220)에 의해 오프셋 시간(Toff)만큼 지연되어 제1 홀드 신호(SHLD1)로서 제1 시간 레지스터(240)의 제1 홀드 단자(HLD1)에 인가된다. 이에 따라, 제1 입력 신호(SIN1) 및 제1 홀드 신호(SHLD1)는 제1 입력 신호(SIN1)와 제2 입력 신호(SIN2)간의 제1 시간차(TD1)와 오프셋 시간(Toff)의 합에 상응하는 시간차(TD1+Toff)를 가질 수 있다.

[0180] 제4 입력 신호(SIN4)는 제2 시간 레지스터(280)의 제2 입력 단자(IN2)에 인가되고, 제3 입력 신호(SIN3)는 제2 오프셋 지연기(260)에 의해 오프셋 시간(Toff)만큼 지연되어 제2 홀드 신호(SHLD2)로서 제2 시간 레지스터(280)의 제2 홀드 단자(HLD2)에 인가된다. 이에 따라, 제4 입력 신호(SIN4) 및 제2 홀드 신호(SHLD2)는 오프셋 시간(Toff)에서 제3 입력 신호(SIN1)와 제4 입력 신호(SIN2)간의 제2 시간차(TD2)가 감산된 시간에 상응하는 시간차(-TD2+Toff)를 가질 수 있다.

[0181] 제1 시간 레지스터(240)는, 어웨이크 신호(SAWK)에 응답하여, 어웨이크 신호(SAWK)의 상승 에지로부터, 디스차지 시간(Tdis)에서 제1 입력 신호(SIN1)와 제1 홀드 신호(SHLD1)간의 시간차(TD1+Toff)가 감산된 시간(Tdis-TD1-Toff) 후, 상승 에지를 가지는 제1 출력 신호(SOUT1)를 출력할 수 있다. 즉, 어웨이크 신호(SAWK) 및 제1 출력 신호(SOUT1)는 디스차지 시간(Tdis)에서 제1 입력 신호(SIN1)와 제1 홀드 신호(SHLD1)간의 시간차(TD1+Toff)가 감산된 시간에 상응하는 시간차(Tdis-TD1-Toff)를 가질 수 있다.

[0182] 제2 시간 레지스터(280)는, 어웨이크 신호(SAWK)에 응답하여, 어웨이크 신호(SAWK)의 상승 에지로부터, 디스차

지 시간(Tdis)에서 제4 입력 신호(SIN4)와 제2 홀드 신호(SHLD2)간의 시간차(-TD2+Toff)가 감산된 시간(Tdis+TD2-Toff) 후, 상승 에지를 가지는 제2 출력 신호(SOUT2)를 출력할 수 있다. 즉, 어웨이크 신호(SAWK) 및 제2 출력 신호(SOUT2)는 디스차지 시간(Tdis)에서 제4 입력 신호(SIN4)와 제2 홀드 신호(SHLD2)간의 시간차(-TD2+Toff)가 감산된 시간에 상응하는 시간차(Tdis+TD2-Toff)를 가질 수 있다.

[0183] 한편, 제1 오프셋 지연기(220)와 제2 오프셋 지연기(260)는 실질적으로 동일한 오프셋 시간(Toff)을 가지고, 제1 시간 레지스터(240)와 제2 시간 레지스터(280)는 실질적으로 동일한 디스차지 시간(Tdis)를 가질 수 있다. 이에 따라, 제1 출력 신호(SOUT1)와 제2 출력 신호(SOUT2)간의 시간차는, 어웨이크 신호(SAWK)와 제2 출력 신호(SOUT2)간의 시간차(Tdis+TD2-Toff)에서 어웨이크 신호(SAWK)와 제1 출력 신호(SOUT1)간의 시간차(Tdis-TD1-Toff)가 감산된 시간((Tdis+TD2-Toff) - (Tdis-TD1-Toff) = TD2 + TD1)에 상응하고, 따라서, 제1 입력 신호(SIN1)와 제2 입력 신호(SIN2)간의 제1 시간차(TD1) 및 제3 입력 신호(SIN3)와 제4 입력 신호(SIN4)간의 제2 시간차(TD2)의 합(TD1+TD2)에 상응할 수 있다.

[0184] 이와 같이, 본 발명의 또 다른 실시예에 따른 시간차 가산기(200c)는 입력 신호들(SIN1, SIN2, SIN3, SIN4)간의 시간차들(TD1, TD2)을 정확하게 가산할 수 있다.

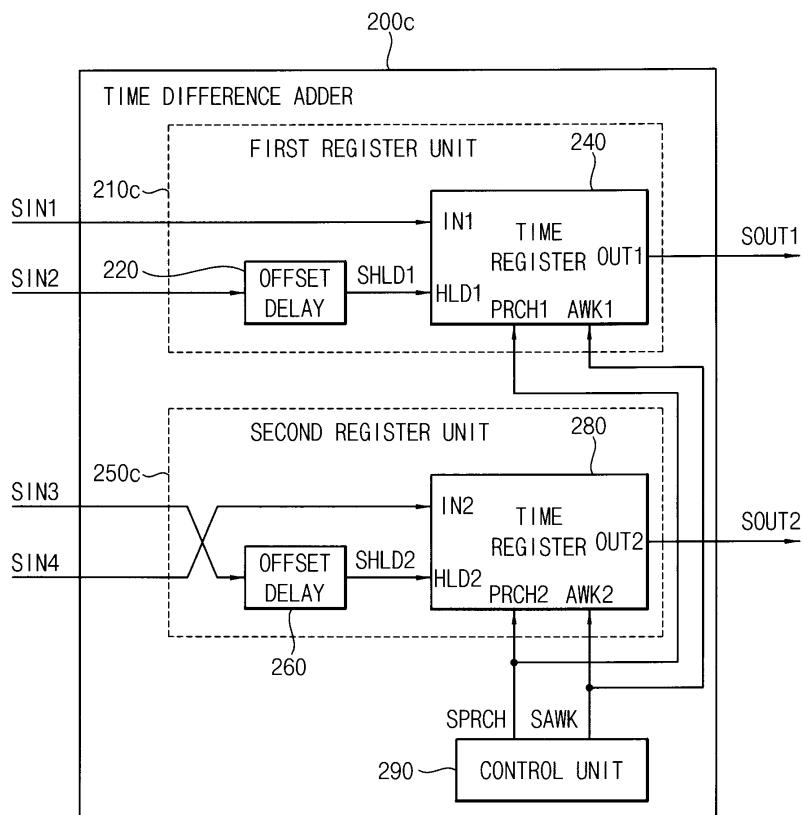

[0185] 도 18은 본 발명의 또 다른 실시예에 따른 시간차 가산기를 나타내는 블록도이다.

[0186] 도 18을 참조하면, 시간차 가산기(200d)는 제1 레지스터부(210d), 제2 레지스터부(250d) 및 제어부(290)를 포함한다. 시간차 가산기(200d)는, 도 12의 시간차 가산기(200c)와 비교하여, 제1 오프셋 지연기(220) 및 제2 오프셋 지연기(260)를 포함하지 않을 수 있다. 실시예에 따라, 시간차 가산기(200d)에는 양의 시간차를 가지는 제1 입력 신호(SIN1) 및 제2 입력 신호(SIN2)가 인가되고, 음의 시간차를 가지는 제3 입력 신호(SIN3) 및 제4 입력 신호(SIN4)가 인가될 수 있다.

[0187] 제1 레지스터부(210d)는 제1 입력 신호(SIN1) 및 제2 입력 신호(SIN2)를 수신하고, 어웨이크 신호(SAWK)에 응답하여 제1 출력 신호(SOUT1)를 생성한다. 제1 레지스터부(210d)는 제1 시간 레지스터(240)를 포함할 수 있다. 제1 시간 레지스터(240)는, 제1 입력 신호(SIN1)를 수신하는 제1 입력 단자(IN1), 제2 입력 신호(SIN2)를 수신하는 제1 홀드 단자(HLD1), 프리차지 신호(SPRCH)를 수신하는 제1 프리차지 단자(PRCH1), 어웨이크 신호(SAWK)를 수신하는 제1 어웨이크 단자(AWK1), 및 제1 출력 신호(SOUT1)를 출력하는 제1 출력 단자(OUT1)를 가질 수 있다.

[0188] 제2 레지스터부(250d)는 제3 입력 신호(SIN3) 및 제4 입력 신호(SIN4)를 수신하고, 어웨이크 신호(SAWK)에 응답하여 제2 출력 신호(SOUT2)를 생성한다. 제2 레지스터부(250d)는 제2 시간 레지스터(280)를 포함할 수 있다. 제2 시간 레지스터(280)는, 제4 입력 신호(SIN4)를 수신하는 제2 입력 단자(IN2), 제3 입력 신호(SIN3)를 수신하는 제2 홀드 단자(HLD2), 프리차지 신호(SPRCH)를 수신하는 제2 프리차지 단자(PRCH2), 어웨이크 신호(SAWK)를 수신하는 제2 어웨이크 단자(AWK2), 및 제2 출력 신호(SOUT2)를 출력하는 제2 출력 단자(OUT2)를 가질 수 있다.

[0189] 실시예에 따라, 제1 시간 레지스터(240) 및 제2 시간 레지스터(280) 각각은 도 13의 시간 레지스터(400a), 도 16의 시간 레지스터(400b), 또는 이와 유사한 구성을 가지는 시간 레지스터로 구현될 수 있다.

[0190] 제어부(290)는 프리차지 신호(SPRCH) 및 어웨이크 신호(SAWK)를 생성한다. 예를 들어, 제어부(290)는 제1 입력 신호(SIN1), 제2 입력 신호(SIN2), 제3 입력 신호(SIN3) 또는 제4 입력 신호(SIN4) 중 어느 하나의 신호를 지연 및/또는 반전시켜 프리차지 신호(SPRCH) 및 어웨이크 신호(SAWK)를 생성할 수 있다.

[0191] 제1 시간 레지스터(240)는, 어웨이크 신호(SAWK)에 응답하여, 어웨이크 신호(SAWK)의 상승 에지로부터, 디스차지 시간에서 제1 입력 신호(SIN1)와 제2 입력 신호(SIN2)간의 제1 시간차가 감산된 시간 후, 상승 에지를 가지는 제1 출력 신호(SOUT1)를 출력할 수 있다. 즉, 어웨이크 신호(SAWK)와 제1 출력 신호(SOUT1)간의 시간차는 상기 디스차지 시간에서 상기 제1 시간차가 감산된 시간에 상응할 수 있다.

[0192] 또한, 제2 시간 레지스터(280)는, 어웨이크 신호(SAWK)에 응답하여, 어웨이크 신호(SAWK)의 상기 상승 에지로부터, 상기 디스차지 시간에 제3 입력 신호(SIN3)와 제4 입력 신호(SIN4)간의 제2 시간차가 가산된 시간 후, 상승 에지를 가지는 제2 출력 신호(SOUT2)를 출력할 수 있다. 즉, 어웨이크 신호(SAWK)와 제2 출력 신호(SOUT2)간의 시간차는 상기 디스차지 시간에 상기 제2 시간차가 가산된 시간에 상응할 수 있다.

[0193] 제1 시간 레지스터(240)의 상기 디스차지 시간과 제2 시간 레지스터(280)의 상기 디스차지 시간은 실질적으로 동일할 수 있다. 이에 따라, 어웨이크 신호(SAWK)와 제2 출력 신호(SOUT2)간의 시간차에서 어웨이크 신호(SAWK)와 제1 출력 신호(SOUT1)간의 시간차가 감산된 시간에 상응하는 제1 출력 신호(SOUT1)와 제2 출력 신호(SOUT2)간의 시간차는, 상기 제1 시간차와 상기 제2 시간차의 합에 상응할 수 있다.

- [0194] 이와 같이, 본 발명의 또 다른 실시예에 따른 시간차 가산기(200d)는 상기 제1 시간차와 상기 제2 시간차의 합에 상응하는 시간차를 가지는 제1 출력 신호(SOUT1) 및 제2 출력 신호(SOUT2)를 출력할 수 있다.

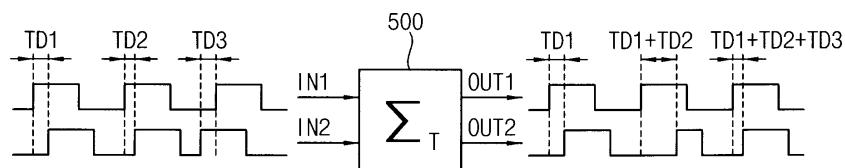

- [0195] 도 19는 본 발명의 실시예들에 따른 시간차 누산기를 나타내는 도면이다.

- [0196] 도 19를 참조하면, 시간차 누산기(500)는 제1 입력 신호(IN1) 및 제2 입력 신호(IN2)에 응답하여 제1 출력 신호(OUT1) 및 제2 출력 신호(OUT2)를 생성한다. 시간차 누산기(500)는 제1 입력 신호(IN1)와 제2 입력 신호(IN2)간의 시간차를 누산하여 누적된 시간차를 가지는 제1 및 제2 출력 신호들(OUT1, OUT2)을 생성할 수 있다. 예를 들어, 제1 시간차(TD1)를 가지는 제1 입력 신호(IN1) 및 제2 입력 신호(IN2)가 입력된 경우, 시간차 누산기(500)는 제1 시간차(TD1)를 가지는 제1 및 제2 출력 신호들(OUT1, OUT2)을 생성할 수 있다. 이어서, 제2 시간차(TD2)를 가지는 제1 입력 신호(IN1) 및 제2 입력 신호(IN2)가 입력된 경우, 시간차 누산기(500)는 제1 시간차(TD1)와 제2 시간차(TD2)의 합을 가지는 제1 및 제2 출력 신호들(OUT1, OUT2)을 생성할 수 있다. 또한, 이어서, 제2 시간차(TD3)를 가지는 제1 입력 신호(IN1) 및 제2 입력 신호(IN2)가 입력된 경우, 시간차 누산기(500)는 제1 시간차(TD1), 제2 시간차(TD2) 및 제3 시간차(TD3)의 합을 가지는 제1 및 제2 출력 신호들(OUT1, OUT2)을 생성할 수 있다.

- [0197] 도 20은 본 발명의 일 실시예에 따른 시간차 누산기를 나타내는 블록도이다.

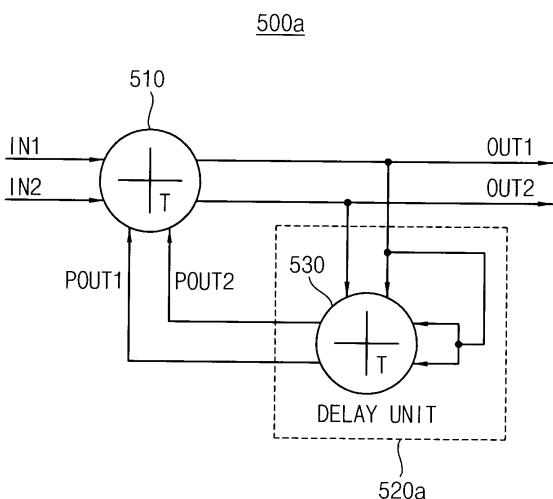

- [0198] 도 20을 참조하면, 시간차 누산기(500a)는 제1 시간차 가산기(510) 및 지연부(520a)를 포함한다.

- [0199] 제1 시간차 가산기(510)는 제1 입력 신호(IN1), 제2 입력 신호(IN2), 제1 이전 출력 신호(POUT1) 및 제2 이전 출력 신호(POUT2)에 응답하여 제1 출력 신호(OUT1) 및 제2 출력 신호(OUT2)를 생성한다. 제1 시간차 가산기(510)는, 제1 입력 신호(IN1)와 제2 입력 신호(IN2)간의 제1 시간차 및 제1 이전 출력 신호(POUT1)와 제2 이전 출력 신호(POUT2)간의 제2 시간차를 가산하여 상기 제1 시간차와 상기 제2 시간차의 합에 상응하는 시간차를 가지는 제1 출력 신호(OUT1) 및 제2 출력 신호(OUT2)를 생성할 수 있다. 여기서, 제1 이전 출력 신호(POUT1)와 제2 이전 출력 신호(POUT2)는 제1 시간차 가산기(510)가 직전에 시간차 가산을 수행하여 출력한 제1 출력 신호(OUT1) 및 제2 출력 신호(OUT2)를 나타낸다.

- [0200] 실시예에 따라, 제1 시간차 가산기(510)는 도 3의 시간차 가산기(200a), 도 10의 시간차 가산기(200b), 도 12의 시간차 가산기(200c), 도 18의 시간차 가산기(200d), 또는 이와 유사한 구성의 시간차 가산기로 구현될 수 있다.

- [0201] 지연부(520a)는 제1 출력 신호(OUT1) 및 제2 출력 신호(OUT2)를 지연시켜 제1 이전 출력 신호(POUT1) 및 제2 이전 출력 신호(POUT2)를 생성한다. 지연부(520a)는 제2 시간차 가산기(530)를 포함할 수 있다. 실시예에 따라, 제2 시간차 가산기(530)는 도 3의 시간차 가산기(200a), 도 10의 시간차 가산기(200b), 도 12의 시간차 가산기(200c), 도 18의 시간차 가산기(200d), 또는 이와 유사한 구성의 시간차 가산기로 구현될 수 있다.

- [0202] 제2 시간차 가산기(530)는 제1 출력 신호(OUT1), 제2 출력 신호(OUT2) 및 두 개의 실질적으로 동일한 신호들에 응답하여 제1 이전 출력 신호(POUT1) 및 제2 이전 출력 신호(POUT2)를 생성한다. 제2 시간차 가산기(530)는, 제1 출력 신호(OUT1)와 제2 출력 신호(OUT2)간의 제3 시간차, 및 상기 실질적으로 동일한 신호들의 제4 시간차를 가산하여 상기 제3 시간차와 상기 제4 시간차의 합에 상응하는 시간차를 가지는 제1 이전 출력 신호(POUT1) 및 제2 이전 출력 신호(POUT2)를 생성한다. 상기 실질적으로 동일한 신호들은 실질적으로 동일한 시점에서 상승 에지들을 가지고, 상기 제4 시간차는 시간차 가산의 항등원인 “0”일 수 있다. 이에 따라, 제1 이전 출력 신호(POUT1)와 제2 이전 출력 신호(POUT2)간의 시간차는 제1 출력 신호(OUT1)와 제2 출력 신호(OUT2)간의 상기 제3 시간차와 실질적으로 동일할 수 있다. 즉, 제2 시간차 가산기(530)는 제1 출력 신호(OUT1) 및 제2 출력 신호(OUT2)를 시간차의 변경 없이 서로 동일한 지연 시간만큼 지연시켜 제1 이전 출력 신호(POUT1) 및 제2 이전 출력 신호(POUT2)를 생성할 수 있다.

- [0203] 한편, 도 20에는 상기 실질적으로 동일한 신호들로서 제1 출력 신호(OUT1)를 이용한 예가 도시되어 있으나, 실시예에 따라, 상기 실질적으로 동일한 신호들은 제2 출력 신호(OUT2), 제1 출력 신호(OUT1)의 반전 신호, 제2 출력 신호(OUT2)의 반전 신호, 또는 다른 신호 중 어느 하나일 수 있다.

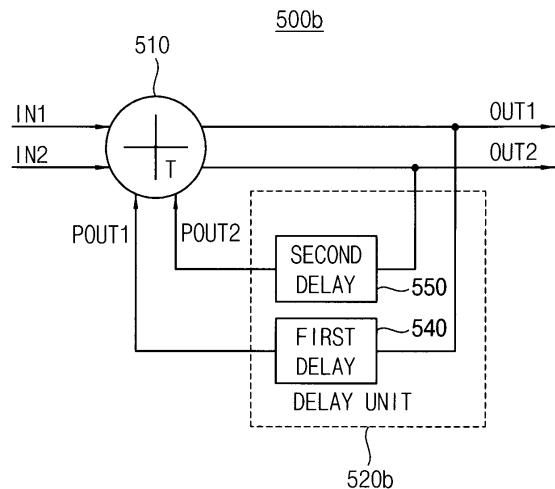

- [0204] 도 21은 본 발명의 다른 실시예에 따른 시간차 누산기를 나타내는 블록도이다.

- [0205] 도 21을 참조하면, 시간차 누산기(500b)는 제1 시간차 가산기(510) 및 지연부(520b)를 포함한다. 시간차 누산기(500b)는, 지연부(520b)의 구성을 제외하고 도 20의 시간차 누산기(500a)와 실질적으로 유사한 구성을 가지고, 실질적으로 유사한 동작을 수행할 수 있다.

- [0206] 지연부(520b)는 제1 출력 신호(OUT1) 및 제2 출력 신호(OUT2)를 지연시켜 제1 이전 출력 신호(POUT1) 및 제2 이전 출력 신호(POUT2)를 생성한다. 지연부(520b)는 제1 지연기(540) 및 제2 지연기(550)를 포함할 수 있다.

- [0207] 제1 지연기(540)는 제1 출력 신호(OUT1)를 지연시켜 제1 이전 출력 신호(POUT1)를 생성하고, 제2 지연기(550)는 제2 출력 신호(OUT2)를 지연시켜 제2 이전 출력 신호(POUT2)를 생성할 수 있다. 제1 지연기(540) 및 제2 지연기(550)는 실질적으로 동일한 지연 시간을 가질 수 있다. 이에 따라, 제1 지연기(540) 및 제2 지연기(550)는 제1 출력 신호(OUT1) 및 제2 출력 신호(OUT2)는 서로 동일한 지연 시간만큼 지연시켜 제1 이전 출력 신호(POUT1) 및 제2 이전 출력 신호(POUT2)를 생성할 수 있다.

- [0208] 도 22는 도 21의 시간차 누산기에 포함된 지연부의 일 예를 나타내는 회로도이고, 도 23은 도 22의 지연부에 포함된 트랜지스터들의 배치의 일 예를 설명하기 위한 도면이다.

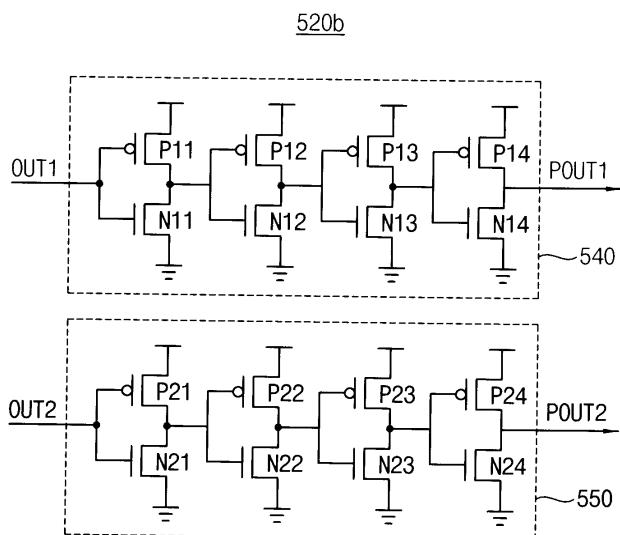

- [0209] 도 22를 참조하면, 지연부(520b)는 제1 지연기(540) 및 제2 지연기(550)를 포함한다. 제1 지연기(540)는 복수의 PMOS 트랜지스터들(P11, P12, P13, P14) 및 복수의 NMOS 트랜지스터들(N11, N12, N13, N14)로 구성된 복수의 인버터들을 포함할 수 있다. 또한, 제2 지연기(550)는 복수의 PMOS 트랜지스터들(P21, P22, P23, P24) 및 복수의 NMOS 트랜지스터들(N21, N22, N23, N24)로 구성된 복수의 인버터들을 포함할 수 있다. 제1 지연기(540) 및 제2 지연기(550)는 서로 동일한 수의 인버터들을 포함함으로써 서로 동일한 지연 시간을 가질 수 있다.

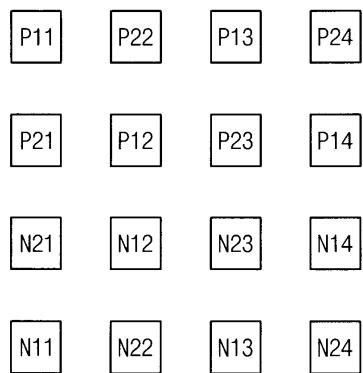

- [0210] 도 23에 도시된 바와 같이, 제1 지연기(540)의 복수의 트랜지스터들(P11, P12, P13, P14, N11, N12, N13, N14) 및 제2 지연기(550)의 복수의 트랜지스터들(P21, P22, P23, P24, N21, N22, N23, N24)은 서로 교변하여 배치될 수 있다. 예를 들어, 제1 지연기(540)의 제1 PMOS 트랜지스터(P11)와 제1 NMOS 트랜지스터(N11) 사이에 제2 지연기(550)의 제1 PMOS 및 NMOS 트랜지스터들(P21, N21)이 배치되고, 제2 지연기(550)의 제2 PMOS 트랜지스터(P22)와 제2 NMOS 트랜지스터(N22) 사이에 제1 지연기(540)의 제2 PMOS 및 NMOS 트랜지스터들(P12, N12)이 배치될 수 있다. 이와 같이, 제1 지연기(540)와 제2 지연기(550)의 트랜지스터들이 서로 교변하여 배치됨으로써, 공정, 전압, 온도(Process, Voltage, Temperature; PVT) 변화(Variation)에도 제1 지연기(540)와 제2 지연기(550)간의 미스매치가 최소화될 수 있다.

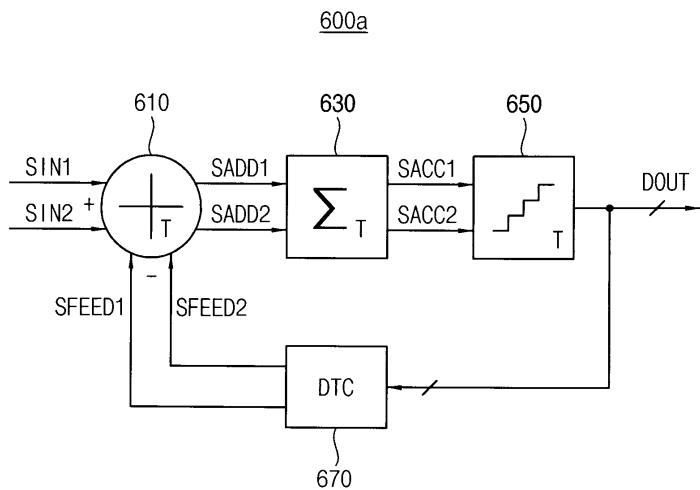

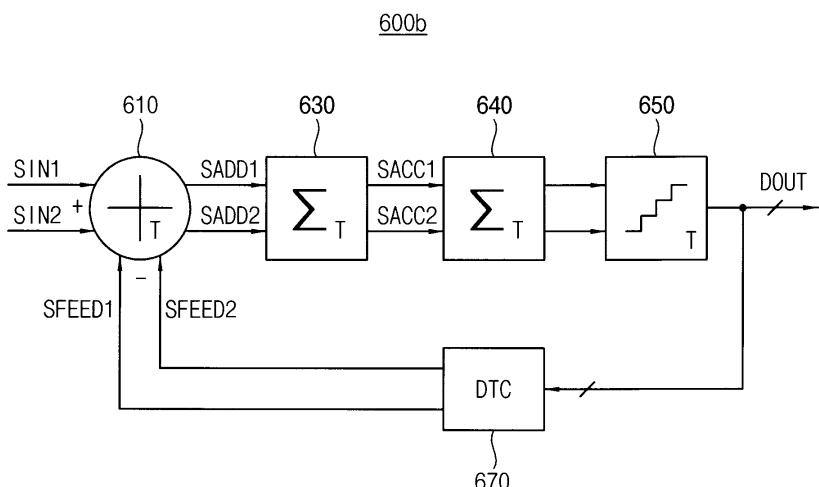

- [0211] 도 24는 본 발명의 일 실시예에 따른 시그마-델타 타임 디지털 변환기를 나타내는 블록도이다.

- [0212] 도 24를 참조하면, 시그마-델타 타임 디지털 변환기(600a)는 시간차 가산기(610), 시간차 누산기(630), 시간 도메인 양자화기(650) 및 디지털 타임 변환기(670)를 포함한다.

- [0213] 시간차 가산기(610)는 제1 입력 신호(SIN1)와 제2 입력 신호(SIN2)간의 제1 시간차에서 제1 피드백 신호(SFEED1)와 제2 피드백 신호(SFEED2)간의 제2 시간차를 감산하여 상기 제1 시간차에서 상기 제2 시간차가 감산된 제3 시간차를 가지는 제1 가산 신호(SADD1) 및 제2 가산 신호(SADD2)를 생성한다. 실시예에 따라, 시간차 가산기(610)는 도 3의 시간차 가산기(200a), 도 10의 시간차 가산기(200b), 도 12의 시간차 가산기(200c), 도 18의 시간차 가산기(200d), 또는 이와 유사한 구성의 시간차 가산기로 구현될 수 있다. 예를 들어, 시간차 가산기(610)는 도 3의 시간차 가산기(200a)로 구현된 경우, 제1 입력 신호(SIN1)는 도 3의 제1 시간 레지스터(230)의 제1 입력 단자(IN1)에 인가되고, 제2 입력 신호(SIN2)는 도 3의 제1 오프셋 지연기(220)에 인가되며, 제1 피드백 신호(SFEED1)는 도 3의 제2 시간 레지스터(270)의 제2 입력 단자(IN2)에 인가되고, 제2 피드백 신호(SFEED2)는 도 3의 제2 오프셋 지연기(260)에 인가될 수 있다. 즉, 제1 피드백 신호(SFEED1)는 도 3의 제4 입력 신호(SIN4)에 상응하고, 제2 피드백 신호(SFEED2)는 도 3의 제3 입력 신호(SIN3)에 상응할 수 있다.

- [0214] 시간차 누산기(630)는 제1 가산 신호(SADD1)와 제2 가산 신호(SADD2)간의 상기 제3 시간차를 누산하여 제1 누산 신호(SACC1) 및 제2 누산 신호(SACC2)를 생성한다. 실시예에 따라, 시간차 누산기(630)는 도 20의 시간차 누산기(500a), 도 21의 시간차 누산기(500b), 또는 이와 유사한 구성의 시간차 누산기로 구현될 수 있다.

- [0215] 시간 도메인 양자화기(650)는 제1 누산 신호(SACC1)와 제2 누산 신호(SACC2)간의 시간차를 디지털 출력 신호(DOUT)로 변환한다. 실시예에 따라, 디지털 출력 신호(DOUT)는 2-레벨을 가지는 한 비트의 신호이거나, 3-레벨 이상을 가지는 2 이상의 비트들의 신호일 수 있다.

- [0216] 디지털 타임 변환기(670)는 디지털 출력 신호(DOUT)를 제1 피드백 신호(SFEED1) 및 제2 피드백 신호(SFEED2)로 변환한다. 예를 들어, 디지털 타임 변환기(670)는 디지털 출력 신호(DOUT)의 값이 증가할수록 제1 피드백 신호(SFEED1)와 제2 피드백 신호(SFEED2)간의 상기 제2 시간차를 증가시킬 수 있다.

- [0217] 본 발명의 일 실시예에 따른 시그마-델타 타임 디지털 변환기(600a)에서, 시간차 가산기(610)가 상기 제1 시간차와 상기 제2 시간차의 차(즉, 델타(Delta))를 출력하고, 시간차 누산기(630)가 이러한 차를 누산(즉, 시그마-

(Sigma)하며, 시간 도메인 양자화기(650)가 누산된 신호를 디지털 값으로 변환하고, 디지털 타임 변환기(670)는 상기 디지털 값을 시간차로 변환하여 시간차 가산기(610)에 제공한다. 즉, 시그마-델타 타임 디지털 변환기(600a)는 시간차 가산기(610), 시간차 누산기(630), 시간 도메인 양자화기(650) 및 디지털 타임 변환기(670)를 포함함으로써 시그마-델타 방식을 채용할 수 있다. 이에 따라, 본 발명의 일 실시예에 따른 시그마-델타 타임 디지털 변환기(600a)는 고해상도(High Resolution)를 가질 수 있다.

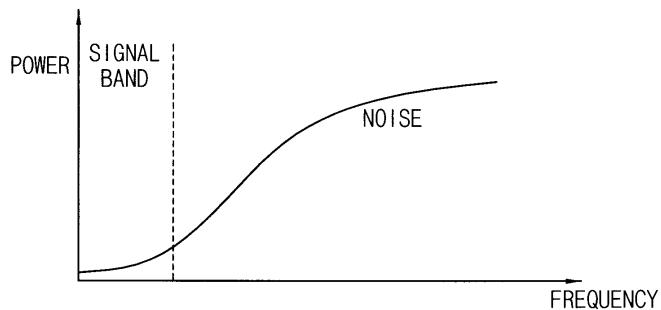

[0218] 도 25는 도 24의 시그마-델타 타임 디지털 변환기에서 수행되는 노이즈 쉐이핑을 설명하기 위한 도면이다.

[0219] 도 25를 참조하면, 본 발명의 실시예들에 따른 시그마-델타 타임 디지털 변환기는 오버샘플링(Over-Sampling) 및 노이즈 쉐이핑(Noise Shaping)을 수행할 수 있다. 상기 시그마-델타 타임 디지털 변환기가 오버샘플링을 수행함으로써, 양자화 잡음(Quantization Noise)이 넓은 대역으로 확산되고, 신호 대역에서 상기 양자화 잡음이 실질적으로 감소될 수 있다. 또한, 상기 시그마-델타 타임 디지털 변환기가 노이즈 쉐이핑을 수행함으로써, 상기 양자화 잡음을 사용하지 않는 대역으로 이동시킬 수 있다. 즉, 상기 시그마-델타 타임 디지털 변환기가 양자화 잡음에 대하여 하이 패스 필터(High Pass Filter)의 역할을 수행하여 상기 양자화 잡음을 이동시킬 수 있다.

[0220] 이에 따라, 본 발명의 실시예들에 따른 시그마-델타 타임 디지털 변환기는 노이즈를 최소화할 수 있고, 고해상도를 가질 수 있다.

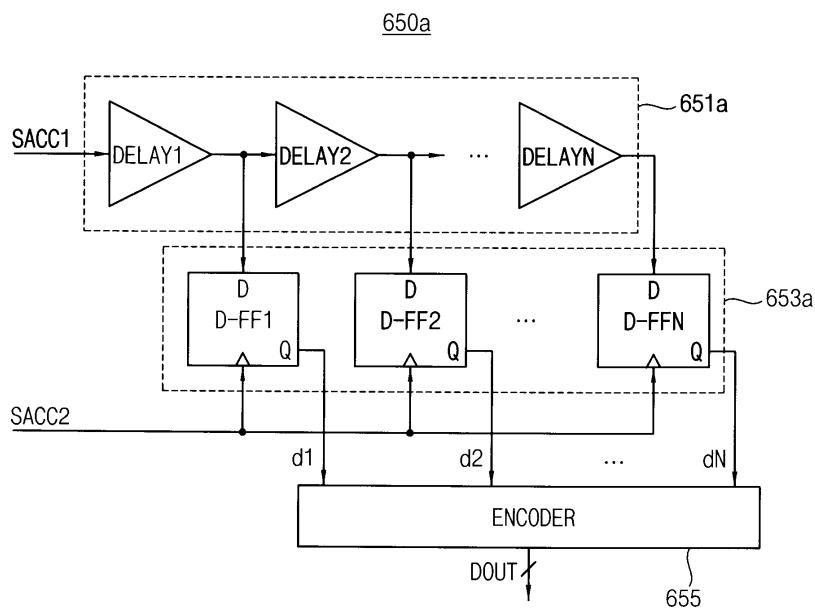

[0221] 도 26은 도 24의 시그마-델타 타임 디지털 변환기에 포함된 시간 도메인 양자화기의 일 예를 나타내는 블록도이다.

[0222] 도 26을 참조하면, 시간 도메인 양자화기(650a)는 지연 라인(651a), 복수의 D-플립플롭들(653a) 및 인코더(655)를 포함한다.

[0223] 지연 라인(651a)은 제1 누산 신호(SACC1)를 순차적으로 지연시키는 N개(N은 1 이상의 자연수)의 지연 셀들을 포함할 수 있다. 상기 지연 셀들에서 출력된 신호들은 N개의 D-플립플롭들(653a)에 각각 인가될 수 있다. D-플립플롭들(653a)은 제2 누산 신호(SACC2)의 상승 에지에 응답하여 N개의 출력 신호들(d1, d2, ..., dn)을 출력할 수 있다. 이에 따라, D-플립플롭들(653a)은 제1 누산 신호(SACC1)와 제2 누산 신호(SACC2)간의 시간차에 따라 “1”의 값을 가지는 출력 신호들(d1, d2, ..., dn)을 출력할 수 있다.

[0224] 인코더(655)는 D-플립플롭들(653a)의 출력 신호들(d1, d2, ..., dn)에 기초하여 디지털 출력 신호(DOUT)를 생성할 수 있다. 예를 들어, 인코더(655)는 온도계 코드(Thermometer Code)인 D-플립플롭들(653a)의 출력 신호들(d1, d2, ..., dn)을 이진 코드(Binary Code)인 디지털 출력 신호(DOUT)로 변환할 수 있다.

[0225] 이에 따라, 시간 도메인 양자화기(650a)는 제1 누산 신호(SACC1)와 제2 누산 신호(SACC2)간의 시간차에 상응하는 디지털 출력 신호(DOUT)를 생성할 수 있다.

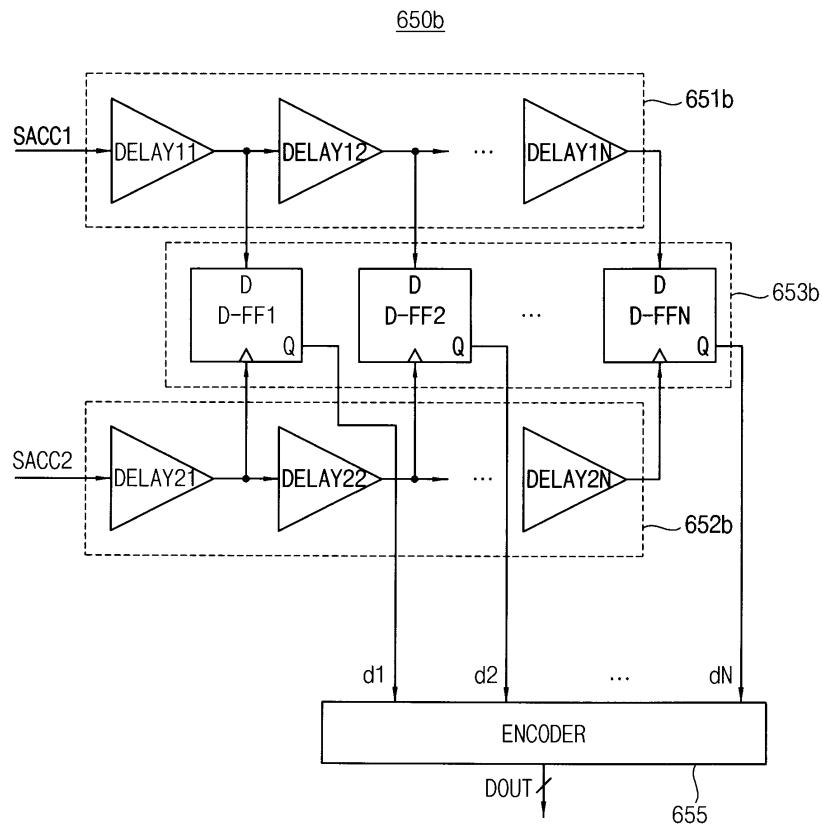

[0226] 도 27은 도 24의 시그마-델타 타임 디지털 변환기에 포함된 시간 도메인 양자화기의 다른 예를 나타내는 블록도이다.

[0227] 도 27을 참조하면, 시간 도메인 양자화기(650b)는 제1 지연 라인(651b), 제2 지연 라인(652b), 복수의 D-플립플롭들(653b) 및 인코더(655)를 포함한다.

[0228] 제1 지연 라인(651b)은 제1 누산 신호(SACC1)를 순차적으로 지연시키는 N개(N은 1 이상의 자연수)의 제1 지연 셀들을 포함하고, 제2 지연 라인(652b)은 제2 누산 신호(SACC2)를 순차적으로 지연시키는 N개의 제2 지연 셀들을 포함할 수 있다. 상기 제1 지연 셀들에서 출력된 신호들은 N개의 D-플립플롭들(653b)의 데이터 단자들(D)에 각각 인가되고, 상기 제2 지연 셀들에서 출력된 신호들은 상기 D-플립플롭들(653b)의 클록 단자들에 각각 인가될 수 있다. 이에 따라, D-플립플롭들(653b)은 상기 제2 지연 셀들에서 출력된 신호들에 응답하여 N개의 출력 신호들(d1, d2, ..., dn)을 출력할 수 있다. 이에 따라, D-플립플롭들(653b)은 제1 누산 신호(SACC1)와 제2 누산 신호(SACC2)간의 시간차에 따라 “1”의 값을 가지는 출력 신호들(d1, d2, ..., dn)을 출력할 수 있다.

[0229] 한편, 상기 제1 지연 셀들 각각의 지연 시간은 상기 제2 지연 셀들 각각의 지연 시간보다 길 수 있다. 이에 따라, 시간 도메인 양자화기(650b)는 각 지연 셀의 최소 지연 시간보다 작은 단위로 시간차를 디지털 값으로 변환할 수 있다.

[0230] 인코더(655)는 D-플립플롭들(653b)의 출력 신호들(d1, d2, ..., dn)에 기초하여 디지털 출력 신호(DOUT)를 생성할 수 있다.

[0231] 이에 따라, 시간 도메인 양자화기(650b)는 제1 누산 신호(SACC1)와 제2 누산 신호(SACC2)간의 시간차에 상응하

는 디지털 출력 신호(DOUT)를 생성할 수 있다.

[0232] 한편, 도 26 및 도 27에는 본 발명의 실시예들에 따른 시그마-델타 타임 디지털 변환기에 포함된 시간 도메인 양자화기의 예들이 도시되어 있으나, 본 발명의 실시예들에 따른 시그마-델타 타임 디지털 변환기는 다양한 구성을 가지는 시간 도메인 양자화기를 포함할 수 있다.

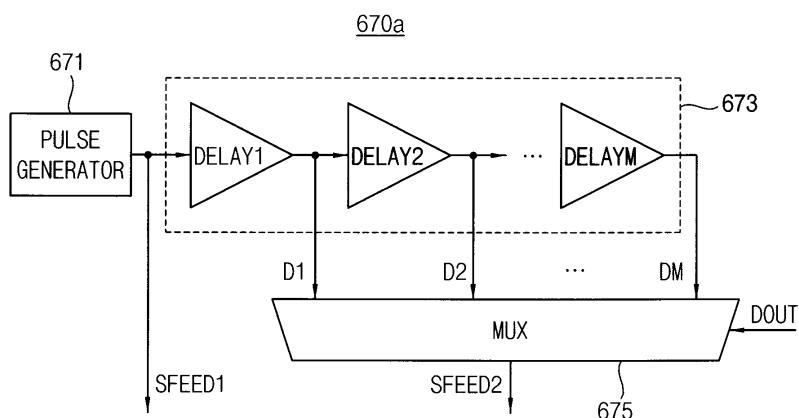

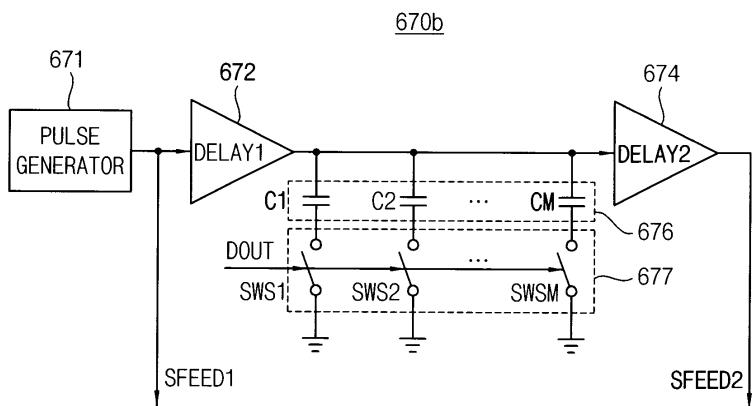

[0233] 도 28은 도 24의 시그마-델타 타임 디지털 변환기에 포함된 디지털 타임 변환기의 일 예를 나타내는 블록도이다.

[0234] 도 28을 참조하면, 디지털 타임 변환기(670a)는 펠스 생성기(671), 지연 라인(673) 및 멀티플렉서(675)를 포함한다.

[0235] 펠스 생성기(671)는 펠스를 생성하고, 상기 펠스를 제1 피드백 신호(SFEED1)로서 출력할 수 있다. 지연 라인(673)은 상기 펠스를 순차적으로 지연시키는 M개(M은 1이상의 자연수)의 지연 셀들을 포함할 수 있다. 멀티플렉서(675)는 디지털 출력 신호(DOUT)에 응답하여 상기 지연 셀들에서 출력된 M개의 순차적으로 지연된 신호들(D1, D2, …, DM) 중 하나의 신호를 제2 피드백 신호(SFEED2)로서 출력할 수 있다. 이에 따라, 디지털 타임 변환기(670a)는 디지털 출력 신호(DOUT)에 상응하는 시간차를 가지는 제1 피드백 신호(SFEED1) 및 제2 피드백 신호(SFEED2)를 생성할 수 있다.

[0236] 도 29는 도 24의 시그마-델타 타임 디지털 변환기에 포함된 디지털 타임 변환기의 다른 예를 나타내는 블록도이다.