(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6891528号

(P6891528)

(45) 発行日 令和3年6月18日(2021.6.18)

(24) 登録日 令和3年5月31日(2021.5.31)

(51) Int.Cl.

G04F 10/04 (2006.01)

F 1

G 04 F 10/04

C

請求項の数 12 (全 26 頁)

(21) 出願番号 特願2017-27463 (P2017-27463)

(22) 出願日 平成29年2月17日 (2017.2.17)

(65) 公開番号 特開2018-132461 (P2018-132461A)

(43) 公開日 平成30年8月23日 (2018.8.23)

審査請求日 令和1年11月15日 (2019.11.15)

(73) 特許権者 000002369

セイコーエプソン株式会社

東京都新宿区新宿四丁目1番6号

(74) 代理人 100104710

弁理士 竹腰 昇

(74) 代理人 100090479

弁理士 井上 一

(74) 代理人 100124682

弁理士 黒田 泰

(72) 発明者 羽田 秀生

長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内

審査官 岩本 太一

最終頁に続く

(54) 【発明の名称】回路装置、物理量測定装置、電子機器及び移動体

## (57) 【特許請求の範囲】

## 【請求項 1】

第1の信号が入力され、基準クロック信号と前記第1の信号の位相差を表す第1の位相差信号を出力する第1の位相差信号出力部と、

第2の信号が入力され、前記基準クロック信号と前記第2の信号の位相差を表す第2の位相差信号を出力する第2の位相差信号出力部と、

前記第1の位相差信号と前記第2の位相差信号に基づいて、前記第1の信号と前記第2の信号の時間差を測定する測定部と、

を含み、

前記第1の位相差信号出力部は、

10

前記第1の信号に基づいて、前記基準クロック信号のパルス幅に対応するパルス幅の第1のパルス信号を生成する第1のパルス信号生成部を有し、

前記第2の位相差信号出力部は、

前記第2の信号に基づいて、前記基準クロック信号の前記パルス幅に対応するパルス幅の第2のパルス信号を生成する第2のパルス信号生成部を有することを特徴とする回路装置。

## 【請求項 2】

請求項1に記載の回路装置において、

前記第1の位相差信号出力部は、

前記基準クロック信号と前記第1の信号に基づく積分処理を行って、前記第1の位相差

20

信号を出力し、

前記第2の位相差信号出力部は、

前記基準クロック信号と前記第2の信号に基づく積分処理を行って、前記第2の位相差信号を出力することを特徴とする回路装置。

**【請求項3】**

請求項1又は2に記載の回路装置において、

前記第1のパルス信号生成部は、

第1の遅延回路を有し、

前記第1の位相差信号出力部は、

前記第1の遅延回路の遅延時間を、前記基準クロック信号の前記パルス幅に対応する遅延時間に設定する第1の遅延制御回路を有し、

前記第2のパルス信号生成部は、

第2の遲延回路を有し、

前記第2の位相差信号出力部は、

前記第2の遲延回路の遲延時間を、前記基準クロック信号の前記パルス幅に対応する遲延時間に設定する第2の遲延制御回路を有することを特徴とする回路装置。 10

**【請求項4】**

請求項3に記載の回路装置において、

前記第1の位相差信号出力部は、

パルス幅測定モードでは、前記第1の遲延回路に前記基準クロック信号を出力し、位相差検出モードでは、前記第1のパルス信号生成部に前記第1の信号を出力する第1のセレクターを有し、

前記第2の位相差信号出力部は、

前記パルス幅測定モードでは、前記第2の遲延回路に前記基準クロック信号を出力し、前記位相差検出モードでは、前記第2のパルス信号生成部に前記第2の信号を出力する第2のセレクターを有することを特徴とする回路装置。 20

**【請求項5】**

第1の信号が入力され、基準クロック信号と前記第1の信号の位相差を表す第1の位相差信号を出力する第1の位相差信号出力部と、

第2の信号が入力され、前記基準クロック信号と前記第2の信号の位相差を表す第2の位相差信号を出力する第2の位相差信号出力部と、

前記第1の位相差信号と前記第2の位相差信号に基づいて、前記第1の信号と前記第2の信号の時間差を測定する測定部と、

を含み、

前記第1の位相差信号出力部は、

前記第1の信号に基づいて、所定パルス幅の第1のパルス信号を生成する第1のパルス信号生成部と、

前記基準クロック信号と前記第1のパルス信号に基づく積分処理を行う第1の積分処理部と、

を有し、

前記第2の位相差信号出力部は、

前記第2の信号に基づいて、前記所定パルス幅の第2のパルス信号を生成する第2のパルス信号生成部と、

前記基準クロック信号と前記第2のパルス信号に基づく積分処理を行う第2の積分処理部と、

を有することを特徴とする回路装置。 40

**【請求項6】**

請求項5に記載の回路装置において、

前記所定パルス幅は、前記基準クロック信号のパルス幅に対応するパルス幅であることを特徴とする回路装置。 50

**【請求項 7】**

第1の信号が入力され、基準クロック信号と前記第1の信号の位相差を表す第1の位相差信号を出力する第1の位相差信号出力部と、

第2の信号が入力され、前記基準クロック信号と前記第2の信号の位相差を表す第2の位相差信号を出力する第2の位相差信号出力部と、

前記第1の位相差信号と前記第2の位相差信号に基づいて、前記第1の信号と前記第2の信号の時間差を測定する測定部と、

前記基準クロック信号に基づいて、互いに位相が異なる第1～第nのクロック信号（nは2以上の整数）を生成するクロック信号生成部と、

を含み、

10

前記第1の位相差信号出力部は、

前記第1～第nのクロック信号と前記第1の信号に基づく積分処理を行う第1～第nの積分器を有し、

前記第2の位相差信号出力部は、

前記第1～第nのクロック信号と前記第2の信号に基づく積分処理を行う第n+1～第2nの積分器を有することを特徴とする回路装置。

**【請求項 8】**

請求項7に記載の回路装置において、

前記測定部は、

前記第1～第nの積分器の出力信号及び前記第n+1～第2nの積分器の出力信号のいずれかを選択するセレクターと、

20

前記セレクターからの信号をA/D変換するA/D変換回路と、

A/D変換された前記第1～第nの積分器の出力信号及び前記第n+1～第2nの積分器の出力信号に基づいて、前記時間差を求める処理部と、

を有することを特徴とする回路装置。

**【請求項 9】**

請求項1乃至8のいずれか一項に記載の回路装置において、

前記第1の信号がアクティブになってから、前記第2の信号がアクティブになるまでの前記基準クロック信号のクロック数をカウントするカウンターを含み、

前記測定部は、

30

前記カウンターのカウント値と前記第1の位相差信号と前記第2の位相差信号に基づいて、前記第1の信号と前記第2の信号の前記時間差を測定することを特徴とする回路装置。

**【請求項 10】**

請求項1乃至9のいずれか一項に記載の回路装置を含むことを特徴とする物理量測定装置。

**【請求項 11】**

請求項1乃至9のいずれか一項に記載の回路装置を含むことを特徴とする電子機器。

**【請求項 12】**

請求項1乃至9のいずれか一項に記載の回路装置を含むことを特徴とする移動体。

40

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、回路装置、物理量測定装置、電子機器及び移動体等に関する。

**【背景技術】****【0002】**

送信信号と受信信号の位相差を検出し、その位相差に基づいてT.O.F (Time Of Flight) の測定等を行う位相差検出方式の時間デジタル変換器が知られている。従来の位相差検出方式では、送信信号と受信信号の位相差をセンサーで電荷に変換（位相差の積分値に相当する電荷量を蓄積）し、その電荷に基づいて位相差を検出している。

50

**【 0 0 0 3 】**

例えば特許文献 1 ~ 3 には、測定対象に向けて発光し、測定対象物からの反射光をセンサーで受光し、発光タイミングと受光タイミングの位相差に対応する電荷量がセンサーに蓄積され、センサーから読み出した電荷量に基づいて測定対象の距離を測定する手法が開示されている。

**【先行技術文献】****【特許文献】****【 0 0 0 4 】**

【特許文献 1】特開 2012 - 93256 号公報

【特許文献 2】特開 2008 - 164496 号公報

10

【特許文献 3】特開 2011 - 53216 号公報

**【発明の概要】****【発明が解決しようとする課題】****【 0 0 0 5 】**

上述した従来技術では、発光タイミングを基準として得られた受光信号をセンサーで電荷（積分値）に変換して距離を測定するため、時間デジタル変換器が送信信号を自発する必要がある。そのため、時間デジタル変換回路の外部から任意のタイミングで入力された2つの信号の間の時間を測定することができなかった。

**【課題を解決するための手段】****【 0 0 0 6 】**

20

本発明は、上記の課題の少なくとも一部を解決するためになされたものであり、以下の形態又は態様として実現することが可能である。

**【 0 0 0 7 】**

本発明の一態様は、第1の信号が入力され、基準クロック信号と前記第1の信号の位相差を表す第1の位相差信号を出力する第1の位相差信号出力部と、第2の信号が入力され、前記基準クロック信号と前記第2の信号の位相差を表す第2の位相差信号を出力する第2の位相差信号出力部と、前記第1の位相差信号と前記第2の位相差信号に基づいて、前記第1の信号と前記第2の信号の時間差を測定する測定部と、を含む回路装置に関する。

**【 0 0 0 8 】**

30

本発明の一態様によれば、基準クロック信号と第1の信号の位相差を表す第1の位相差信号が出力され、基準クロック信号と第2の信号の位相差を表す第2の位相差信号が出力される。これにより、基準クロック信号に対して任意のタイミングで入力される（いわゆる自発でない）第1の信号に基づいて、基準クロック信号と第1の信号の位相差を検出でき、基準クロック信号に対して任意のタイミングで入力される第2の信号に基づいて、基準クロック信号と第2の信号の位相差を検出できる。そして、これらの位相差を表す第1の位相差信号と第2の位相差信号に基づいて、第1の信号と第2の信号の時間差を測定できる。このようにして本発明の一態様では、自発でない2つの信号の間の時間を測定できる。

**【 0 0 0 9 】**

40

また本発明の一態様では、前記第1の位相差信号出力部は、前記基準クロック信号と前記第1の信号に基づく積分処理を行って、前記第1の位相差信号を出力し、前記第2の位相差信号出力部は、前記基準クロック信号と前記第2の信号に基づく積分処理を行って、前記第2の位相差信号を出力してもよい。

**【 0 0 1 0 】**

このようにすれば、基準クロック信号と第1の信号に基づく積分処理を行うことで、基準クロック信号と第1の信号の位相差を表す第1の位相差信号を出力できる。また、基準クロック信号と第2の信号に基づく積分処理を行うことで、基準クロック信号と第2の信号の位相差を表す第2の位相差信号を出力できる。

**【 0 0 1 1 】**

50

また本発明の一態様では、前記第1の位相差信号出力部は、前記第1の信号に基づいて、前記基準クロック信号のパルス幅に対応するパルス幅の第1のパルス信号を生成する第1のパルス信号生成部を有し、前記第2の位相差信号出力部は、前記第2の信号に基づいて、前記基準クロック信号の前記パルス幅に対応するパルス幅の第2のパルス信号を生成する第2のパルス信号生成部を有してもよい。

#### 【0012】

このようにすれば、第1のパルス信号により規定される積分期間において基準クロック信号を積分することが可能になり、その積分値により第1の位相差信号を生成できるようになる。また第2のパルス信号により規定される積分期間において基準クロック信号を積分することが可能になり、その積分値により第2の位相差信号を生成できるようになる。10 即ち、第1の信号から第1のパルス信号を生成し、第2の信号から第2のパルス信号を生成することで、第1の信号及び第2の信号が任意のタイミングで入力される場合であっても、積分処理が可能となり、位相差を検出できる。

#### 【0013】

また本発明の一態様では、前記第1の位相差信号出力部は、前記基準クロック信号と前記第1のパルス信号に基づく積分処理を行う第1の積分処理部を有し、前記第2の位相差信号出力部は、前記基準クロック信号と第2のパルス信号に基づく積分処理を行う第2の積分処理部を有してもよい。

#### 【0014】

このようにすれば、第1の積分処理部が基準クロック信号と第1のパルス信号に基づく積分処理を行うことで、基準クロック信号と第1の信号の位相差を表す第1の位相差信号を出力できる。また、第2の積分処理部が基準クロック信号と第2のパルス信号に基づく積分処理を行うことで、基準クロック信号と第2の信号の位相差を表す第2の位相差信号を出力できる。20

#### 【0015】

また本発明の一態様では、前記第1のパルス信号生成部は、第1の遅延回路を有し、前記第1の位相差信号出力部は、前記第1の遅延回路の遅延時間を、前記基準クロック信号の前記パルス幅に対応する遅延時間に設定する第1の遅延制御回路を有し、前記第2のパルス信号生成部は、第2の遅延回路を有し、前記第2の位相差信号出力部は、前記第2の遅延回路の遅延時間を、前記基準クロック信号の前記パルス幅に対応する遅延時間に設定する第2の遅延制御回路を有してもよい。30

#### 【0016】

このようにすれば、基準クロック信号のパルス幅に対応する遅延時間に設定された第1の遅延回路を用いて、基準クロック信号のパルス幅に対応するパルス幅の第1のパルス信号を生成できる。また、基準クロック信号のパルス幅に対応する遅延時間に設定された第2の遅延回路を用いて、基準クロック信号のパルス幅に対応するパルス幅の第2のパルス信号を生成できる。

#### 【0017】

また本発明の一態様では、前記第1の位相差信号出力部は、パルス幅測定モードでは、前記第1の遅延回路に前記基準クロック信号を出力し、位相差検出モードでは、前記第1のパルス信号生成部に前記第1の信号を出力する第1のセレクターを有し、前記第2の位相差信号出力部は、前記パルス幅測定モードでは、前記第2の遅延回路に前記基準クロック信号を出力し、前記位相差検出モードでは、前記第2のパルス信号生成部に前記第2の信号を出力する第2のセレクターを有してもよい。40

#### 【0018】

このようにすれば、パルス幅測定モードにおいて第1の遅延回路と第1の遅延制御回路により第1の遅延回路の遅延時間を設定し、第2の遅延回路と第2の遅延制御回路により第2の遅延回路の遅延時間を設定できる。そして、位相差検出モードにおいて第1のパルス信号生成部が第1の遅延回路を用いて第1の信号から第1のパルス信号を生成し、第2のパルス信号生成部が第2の遅延回路を用いて第2の信号から第2のパルス信号を生成し50

、これらのパルス信号に基づいて位相差を検出できる。

**【0019】**

また本発明の一態様では、回路装置は、前記基準クロック信号に基づいて、互いに位相が異なる第1～第nのクロック信号（nは2以上の整数）を生成するクロック信号生成部を含み、前記第1の位相差信号出力部は、前記第1～第nのクロック信号と前記第1の信号に基づく積分処理を行う第1～第nの積分器を有し、前記第2の位相差信号出力部は、前記第1～第nのクロック信号と前記第2の信号に基づく積分処理を行う第n+1～第2nの積分器を有してもよい。

**【0020】**

このようにすれば、互いに位相が異なる第1～第nの積分値の特性が得られる。これにより、入力位相差に対して、位相が異なるn個の特性に基づくn個の積分値が得られる。積分処理は積分器の特性ばらつき等によって非線形性を有する可能性があり、それによって入力位相差と出力位相差の間に非線形性が生じる可能性がある。この点、本発明の一態様によれば、n個の積分値を例えば平均して位相差を求めることで、入力位相差と出力位相差の間に非線形性を低減できる。

10

**【0021】**

また本発明の一態様では、前記測定部は、前記第1～第nの積分器の出力信号及び前記第n+1～第2nの積分器の出力信号のいずれかを選択するセレクターと、前記セレクターからの信号をA/D変換するA/D変換回路と、A/D変換された前記第1～第nの積分器の出力信号及び前記第n+1～第2nの積分器の出力信号に基づいて、前記時間差を求める処理部と、を有してもよい。

20

**【0022】**

このようにすれば、第1～第nの積分器の出力信号及び第n+1～第2nの積分器の出力信号を時分割にA/D変換できる。これにより、回路規模を節約できる。また、このようなA/D変換を行うことで、デジタル信号処理により積分器の出力信号（積分値）に基づいて時間差を求めることができる。

**【0023】**

また本発明の一態様では、回路装置は、前記第1の信号がアクティブになってから、前記第2の信号がアクティブになるまでの前記基準クロック信号のクロック数をカウントするカウンターを含み、前記測定部は、前記カウンターのカウント値と前記第1の位相差信号と前記第2の位相差信号に基づいて、前記第1の信号と前記第2の信号の時間差を測定してもよい。

30

**【0024】**

従来の位相差検出方式ではセンサーで積分処理を行うため、ダイナミックレンジを広げることが困難である。この点、本発明の一態様によれば、第1の信号がアクティブになってから、第2の信号がアクティブになるまでの基準クロック信号のクロック数がカウントされ、そのカウント値を用いて第1の信号と第2の信号の時間差が測定される。これにより、第1の信号と第2の信号の位相差が基準クロック信号の1周期より大きい場合であっても、位相差を検出できる。これにより、広いダイナミックレンジの測定が可能になる。

40

**【0025】**

また本発明の他の態様は、上記のいずれかに記載の回路装置を含む物理量測定装置に関係する。

**【0026】**

また本発明の更に他の態様は、上記のいずれかに記載の回路装置を含む電子機器に関係する。

**【0027】**

また本発明の更に他の態様は、上記のいずれかに記載の回路装置を含む移動体に関係する。

**【図面の簡単な説明】**

**【0028】**

50

- 【図 1】本実施形態の回路装置の第 1 の構成例。

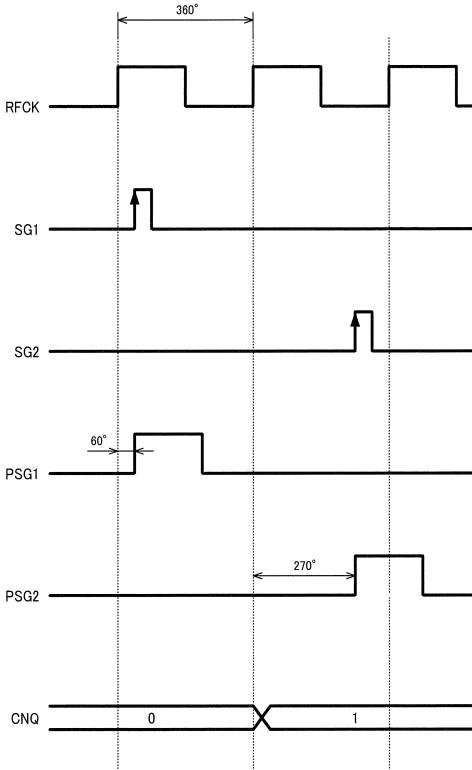

- 【図 2】本実施形態における時間差測定の手法を説明する図。

- 【図 3】第 1 の位相差信号出力部の動作を説明するタイミングチャート。

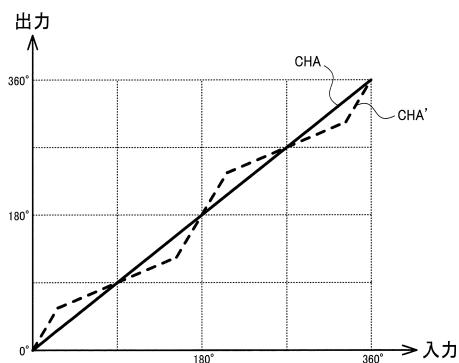

- 【図 4】積分値の特性を示す図。

- 【図 5】本実施形態の回路装置の第 2 の構成例。

- 【図 6】第 2 の構成例の回路装置の動作を説明するタイミングチャート。

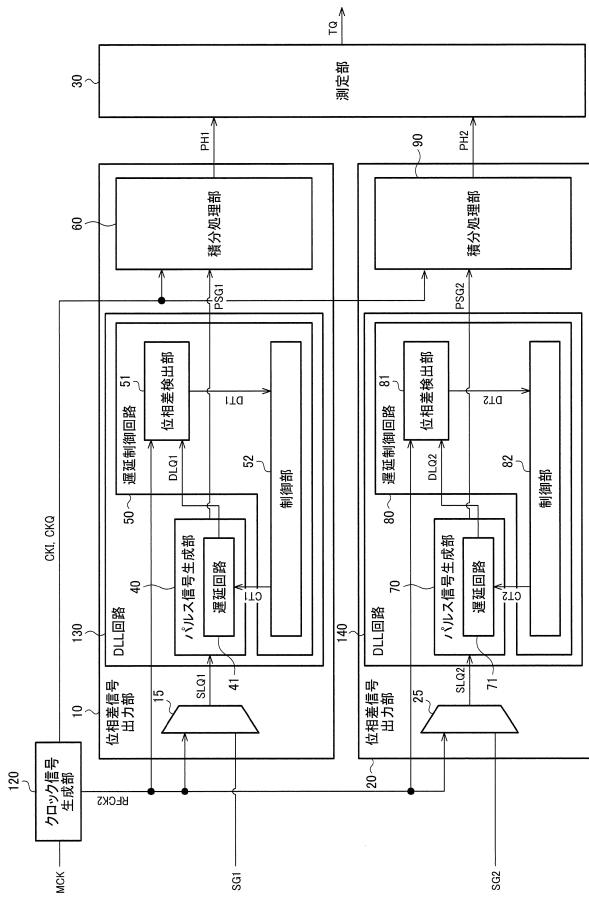

- 【図 7】本実施形態の回路装置の詳細な構成例。

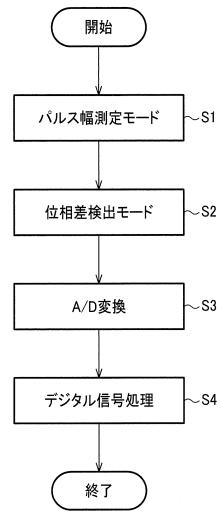

- 【図 8】詳細な構成例の回路装置の動作を説明するフローチャート。

- 【図 9】パルス幅測定モードにおける第 1 の位相差信号出力部の動作を説明する図。

- 【図 10】位相差検出モードにおける第 1 の位相差信号出力部の動作を説明する図。 10

- 【図 11】第 1 の積分処理部の詳細な構成例。

- 【図 12】クロック信号生成部が生成するクロック信号のタイミングチャート。

- 【図 13】多相クロックによる積分処理の積分値の特性を示す図。

- 【図 14】多相クロックによる積分処理の積分値の特性を示す図。

- 【図 15】多相クロックによる積分処理の積分値の特性を示す図。

- 【図 16】測定部の詳細な構成例。

- 【図 17】積分器の詳細な構成例。

- 【図 18】積分器の動作を説明するタイミングチャート。

- 【図 19】積分器間における積分値の特性のばらつきを説明する図。

- 【図 20】入力位相差に対する出力位相差の特性例。 20

- 【図 21】積分器のばらつき補正を説明する図。

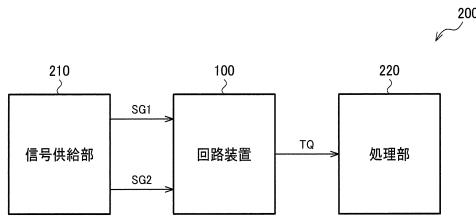

- 【図 22】物理量測定装置の構成例。

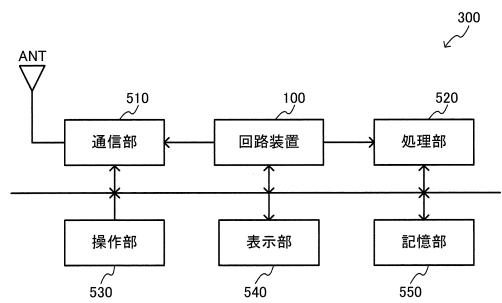

- 【図 23】電子機器の構成例。

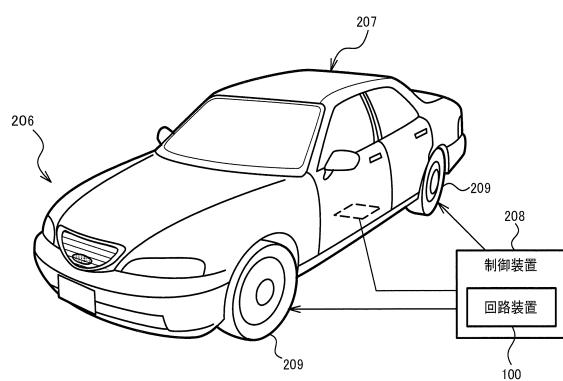

- 【図 24】移動体の構成例。

- 【発明を実施するための形態】**

- 【0029】**

以下、本発明の好適な実施の形態について詳細に説明する。なお以下に説明する本実施形態は特許請求の範囲に記載された本発明の内容を不当に限定するものではなく、本実施形態で説明される構成の全てが本発明の解決手段として必須であるとは限らない。

- 【0030】** 30

### 1. 第 1 の構成例

上述したように、従来の位相差検出方式では信号の積分がセンサーで行われており、センサーの出力信号が位相差信号となっている。この方式は、例えば 3 次元計測等に利用されている。即ち、2 次元センサーを用いて各画素での測距を行い、測定対象の 3 次元情報を取得する。

- 【0031】**

位相差検出方式は、送信信号と受信信号の位相差（時間差）を測定するので、一種の時間デジタル変換器と考えられる。しかしながら、送信信号を自発する必要があることや、センサーで位相差に変換していることから、時間デジタル変換器として用途が限られている。例えば、2 つの信号経路の遅延差や、PLL における位相差検出等の、自発でない 2 つの信号の時間差を測定することは、従来の位相差検出方式では困難である。 40

- 【0032】**

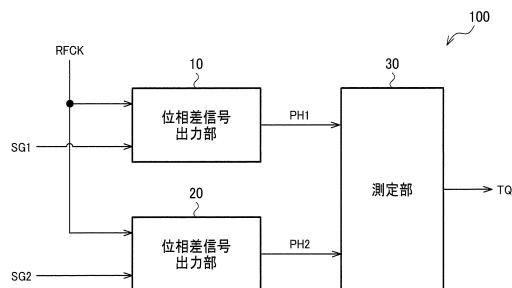

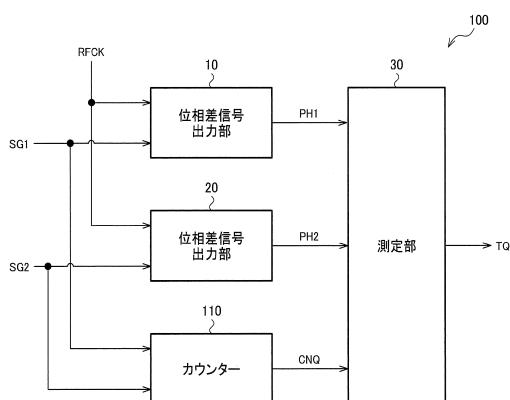

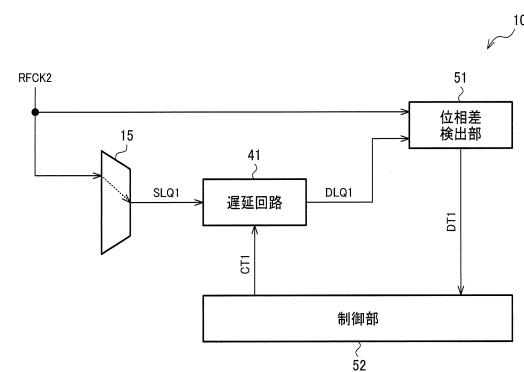

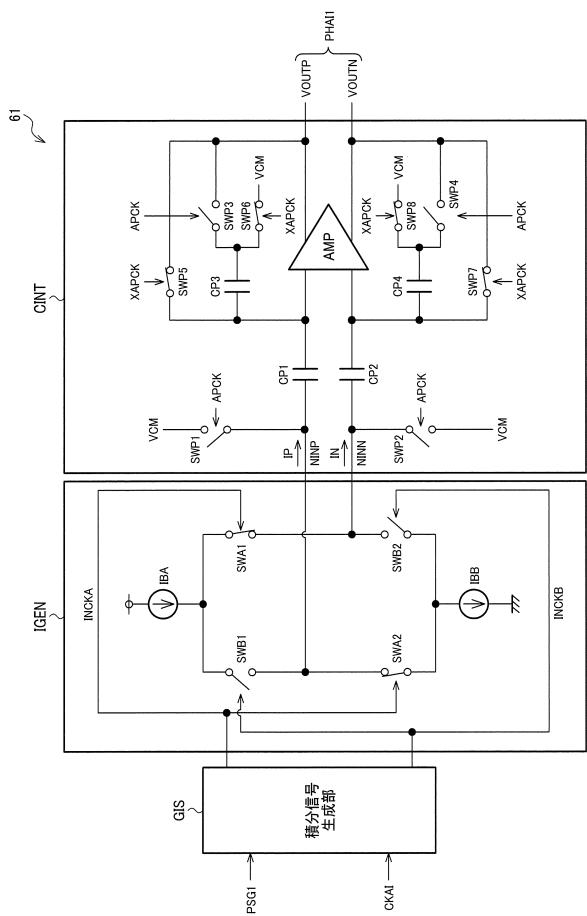

図 1 は、本実施形態の回路装置の第 1 の構成例である。回路装置 100 は、第 1 の位相差信号出力部 10（第 1 の位相差信号出力回路）、第 2 の位相差信号出力部 20（第 2 の位相差信号出力回路）、測定部 30（測定回路）を含む。なお、本実施形態は図 1 の構成に限定されず、その構成要素の一部を省略したり、他の構成要素を追加したりする等の種々の変形実施が可能である。例えば、図 1 では基準クロック信号 R F C K が位相差信号出力部 10、20 に入力されているが、これに限定されず、基準クロック信号 R F C K を位相又は周波数の基準として生成されたクロック信号が位相差信号出力部 10、20 に入力されてもよい。

**【 0 0 3 3 】**

図1の回路装置100は、第1の信号SG1と第2の信号SG2の遷移タイミングの時間差をデジタル値（時間差データTQ）に変換する時間デジタル変換回路である。

**【 0 0 3 4 】**

具体的には、第1の位相差信号出力部10は、第1の信号SG1が入力され、基準クロック信号RFCKと第1の信号SG1の位相差を表す第1の位相差信号PH1を出力する。第2の位相差信号出力部20は、第2の信号SG2が入力され、基準クロック信号RFCKと第2の信号SG2の位相差を表す第2の位相差信号PH2を出力する。測定部30は、第1の位相差信号PH1と第2の位相差信号PH2に基づいて、第1の信号SG1と第2の信号SG2の遷移タイミングの時間差を測定する。測定部30は、測定された時間差を表す時間差データTQを出力する。10

**【 0 0 3 5 】**

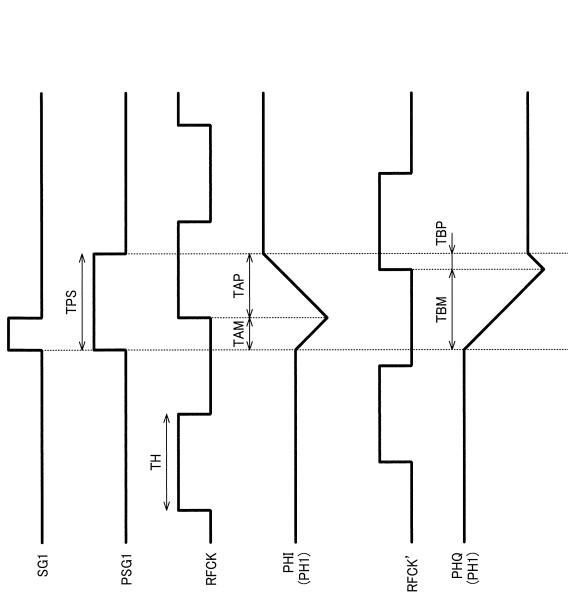

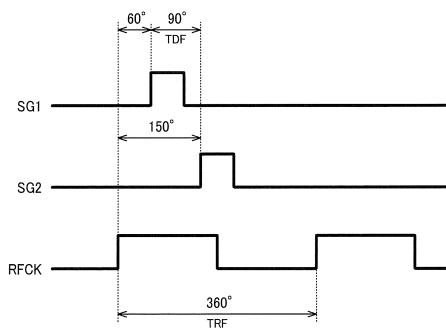

図2は、本実施形態における時間差測定の手法を説明する図である。なお以下では、各信号の遷移タイミングが信号の立ち上がりエッジである場合を例に説明するが、信号の遷移タイミングはこれに限定されない。即ち、遷移タイミングは信号レベルが変化するタイミングであればよい。

**【 0 0 3 6 】**

第1の位相差信号出力部10は、基準クロック信号RFCKの立ち上がりエッジと第1の信号SG1の立ち上がりエッジの間の位相差に対応する第1の位相差信号PH1を生成する。例えば、基準クロック信号RFCKの1周期を360度として、位相差が60度だったとする。第2の位相差信号出力部20は、基準クロック信号RFCKの立ち上がりエッジと第2の信号SG2の立ち上がりエッジの間の位相差に対応する第2の位相差信号PH2を生成する。例えば、位相差が150度だったとする。測定部30は、2つの位相差信号PH1、PH2から、第1の信号SG1の立ち上がりエッジと第2の信号SG2の立ち上がりエッジの間の位相差を求める。具体的には、第1の位相差信号PH1から位相差(60度)を求め、第2の位相差信号PH2から位相差(150度)を求め、2つの位相差の差分 $150\text{度} - 60\text{度} = 90\text{度}$ を求める。例えば、測定部30は、位相差90度を表すデジタル値を時間差データTQとして出力する。或いは、基準クロック信号RFCKの1周期をTRFとした場合に、位相差90度を時間差 $TDF = (90\text{度} / 360\text{度}) \times TRF$ に変換し、その時間差TDFを表す時間差データTQを出力する。2030

**【 0 0 3 7 】**

第1の信号SG1と第2の信号SG2としては種々の信号を想定できる。例えば、信号SG1、SG2は、TOF方式の測距センサーにおけるスタート信号とストップ信号であってもよい。この場合、先に入力される第1の信号SG1(スタート信号)から、後に入力される第2の信号SG2(ストップ信号)までの時間を測定することになる。或いは、信号SG1、SG2は、基準信号(例えば基準クロック、時刻パルス等)と、その基準信号に同期すべき信号(例えば、基準クロック又は時刻パルスに同期するタイミング信号、クロック信号等)であってもよい。或いは、第1の信号経路を通過した信号(遅延信号)と、第2の信号経路を通過した信号(遅延信号)であってもよい。これらの例では、第1の信号SG1と第2の信号SG2の前後関係は決まっていない。例えば、第1の信号SG1、第2の信号SG2の順に入力された場合には正の値の時間差TDFを出力し、第2の信号SG2、第1の信号SG1の順に入力された場合には負の値の時間差TDFを出力する。40

**【 0 0 3 8 】**

位相差信号(PH1、PH2の各々)は、信号値が0度～360度の位相差に対応した信号であり、例えば信号値と0度～360度の位相差が1対1に対応する信号である。例えば、位相差信号は、位相差のサインとコサインの組み合わせ、又はそれらに類似した信号の組み合わせ(例えば図4のPHQ、PHI)である。なお、位相差信号はこれに限定されず、位相差信号から位相差を特定できる信号であればよい。

**【 0 0 3 9 】**1020304050

本実施形態によれば、基準クロック信号 R F C K と第 1 の信号 S G 1 の位相差が検出され、基準クロック信号 R F C K と第 2 の信号 S G 2 の位相差が検出され、それらの位相差に基づいて、第 1 の信号 S G 1 と第 2 の信号 S G 2 の遷移タイミングの時間差が測定される。これにより、第 1 の信号 S G 1 ( 例えばスタート信号 ) を時間デジタル変換回路が自発しない場合であっても、第 1 の信号 S G 1 と第 2 の信号 S G 2 の遷移タイミングの時間差を測定できる。また、従来の位相差検出方式のように T O F 方式の測距センサーに限らず、2 つの信号の時間差を測定する時間デジタル変換回路として種々の用途に適用できるようになる。

#### 【 0 0 4 0 】

また本実施形態では、第 1 の位相差信号出力部 1 0 は、基準クロック信号 R F C K と第 1 の信号 S G 1 に基づく積分処理を行って、第 1 の位相差信号 P H 1 を出力する。第 2 の位相差信号出力部 2 0 は、基準クロック信号 R F C K と第 2 の信号 S G 2 に基づく積分処理を行って、第 2 の位相差信号 P H 2 を出力する。10

#### 【 0 0 4 1 】

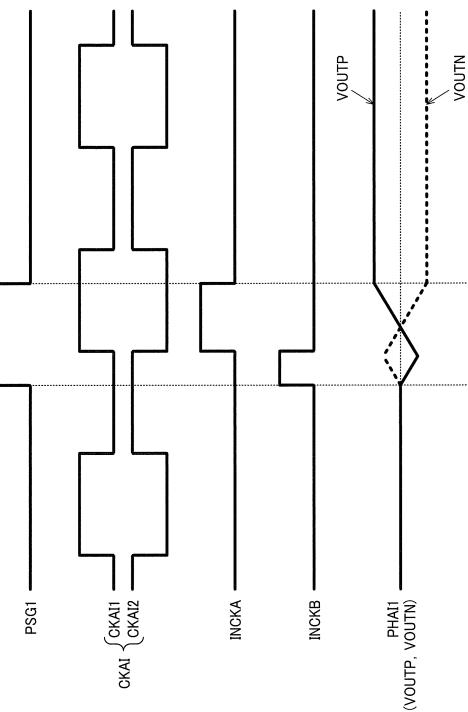

図 3 は、第 1 の位相差信号出力部の動作を説明するタイミングチャートである。なお、ここでは第 1 の位相差信号出力部 1 0 を例に説明するが、第 2 の位相差信号出力部 2 0 についても同様な動作を行う。

#### 【 0 0 4 2 】

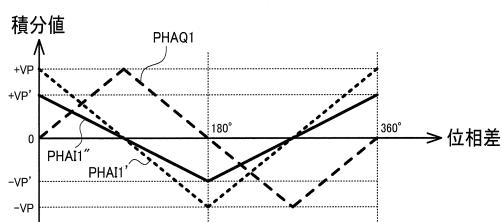

第 1 の位相差信号出力部 1 0 は、第 1 の信号 S G 1 から第 1 のパルス信号 P S G 1 を生成する。第 1 の信号 S G 1 と第 1 のパルス信号 P S G 1 の立ち上がりエッジ ( 遷移タイミング ) は、同じタイミングであり、第 1 のパルス信号 P S G 1 のパルス幅 T P S は、基準クロック信号 R F C K のパルス幅 T H ( ハイレベルの期間 ) と同じである。第 1 の位相差信号出力部 1 0 は、第 1 のパルス信号 P S G 1 がアクティブ ( ハイレベル、第 1 の論理レベル ) である積分期間において基準クロック信号 R F C K を積分する。具体的には、積分期間において基準クロック信号 R F C K がローレベルの期間 T A M では負の信号レベルを積分し、基準クロック信号 R F C K がハイレベルの期間 T A P では正の信号レベルを積分し、その積分値 P H I ( 信号 ) を出力する。積分される負の信号レベルと正の信号レベルは絶対値が同じ信号レベルである。また第 1 の位相差信号出力部 1 0 は、基準クロック信号 R F C K と位相が 90 度異なるクロック信号 R F C K ' を積分期間において積分する。具体的には、積分期間においてクロック信号 R F C K ' がローレベルの期間 T B M では負の信号レベルを積分し、クロック信号 R F C K ' がハイレベルの期間 T B P では正の信号レベルを積分し、その積分値 P H Q ( 信号 ) を出力する。第 1 の位相差信号出力部 1 0 は、積分値 P H I 、 P H Q を第 1 の位相差信号 P H 1 として出力する。20

#### 【 0 0 4 3 】

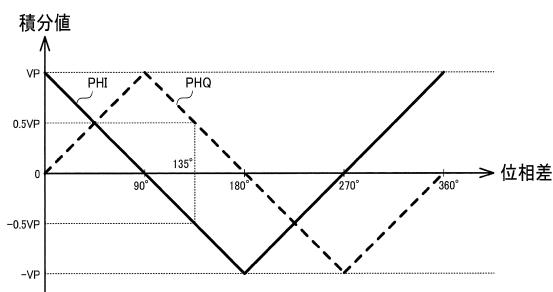

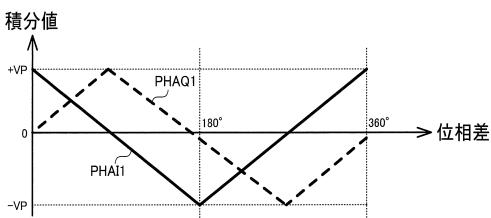

図 4 は、積分値の特性を示す図である。積分値が変化する範囲の上限を + V P とし、下限を - V P とする。積分値 P H I は疑似的なコサイン波の特性を有する。具体的には、コサイン波と同位相の三角波であり、コサイン波の頂点 ( 0 度、 180 度、 360 度 ) とゼロクロス点 ( 90 度、 270 度 ) の間を直線補間 ( 直線近似 ) した波形である。また積分値 P H Q は疑似的なサイン波の特性を有する。具体的には、サイン波と同位相の三角波であり、サイン波のゼロクロス点 ( 0 度、 180 度、 360 度 ) と頂点 ( 90 度、 270 度 ) の間を直線補間 ( 直線近似 ) した波形である。サインとコサインの値に対して、 0 度 ~ 360 度の範囲で角度 ( 位相差 ) を一意に決めることができるので、積分値 P H I 、 P H Q から位相差を決定できる。例えば、図 4 に示すように積分値 ( P H I , P H Q ) = ( - V P / 2, + V P / 2 ) の場合、位相差は 135 度と決定できる。30

#### 【 0 0 4 4 】

このように、基準クロック信号 R F C K と第 1 の信号 S G 1 に基づく積分処理を行うことで、基準クロック信号 R F C K と第 1 の信号 S G 1 の位相差を表す第 1 の位相差信号 P H 1 を出力できる。同様に、基準クロック信号 R F C K と第 2 の信号 S G 2 に基づく積分処理を行うことで、基準クロック信号 R F C K と第 2 の信号 S G 2 の位相差を表す第 2 の位相差信号 P H 2 を出力できる。40

**【 0 0 4 5 】**

また本実施形態では、第1の位相差信号出力部10は、第1の信号SG1に基づいて、基準クロック信号RFCKのパルス幅THに対応するパルス幅TPSの第1のパルス信号PSG1を生成する第1のパルス信号生成部(図7の第1のパルス信号生成部40)を有する。第2の位相差信号出力部20は、第2の信号SG2に基づいて、基準クロック信号RFCKのパルス幅THに対応するパルス幅の第2のパルス信号PSG2を生成する第2のパルス信号生成部(図7の第2のパルス信号生成部70)を有する。

**【 0 0 4 6 】**

このようにすれば、第1のパルス信号PSG1により規定される積分期間(図3のTPS)において基準クロック信号RFCKを積分することで、第1の位相差信号PH1を生成できるようになる。また第2のパルス信号PSG2により規定される積分期間において基準クロック信号RFCKを積分することで、第2の位相差信号PH2を生成できるようになる。即ち、第1の信号SG1から第1のパルス信号PSG1を生成し、第2の信号SG2から第2のパルス信号PSG2を生成することで、第1の信号SG1及び第2の信号SG2が外部から入力される場合であっても、積分処理が可能となり、位相差を検出できる。

10

**【 0 0 4 7 】**

また本実施形態では、第1の位相差信号出力部10は、基準クロック信号RFCKと第1のパルス信号PSG1に基づく積分処理を行う第1の積分処理部(図7の第1の積分処理部60)を有する。第2の位相差信号出力部20は、基準クロック信号RFCKと第2のパルス信号PSG2に基づく積分処理を行う第2の積分処理部(図7の第2の積分処理部90)を有する。

20

**【 0 0 4 8 】**

このようにすれば、基準クロック信号RFCKと第1のパルス信号PSG1に基づく積分処理を行って、基準クロック信号RFCKと第1の信号SG1の位相差を表す第1の位相差信号PH1を出力できる。また、基準クロック信号RFCKと第2のパルス信号PSG2に基づく積分処理を行って、基準クロック信号RFCKと第2の信号SG2の位相差を表す第2の位相差信号PH2を出力できる。

**【 0 0 4 9 】**

また本実施形態では、第1のパルス信号生成部は、第1の遅延回路(図7の第1の遅延回路41)を有する。第1の位相差信号出力部10は、第1の遅延回路の遅延時間を、基準クロック信号RFCKのパルス幅THに対応する遅延時間に設定する第1の遅延制御回路(図7の第1の遅延制御回路50)を有する。そして、第1の遅延回路と第1の遅延制御回路を含んで第1のDLL(Delay Locked Loop)回路(図7の第1のDLL回路130)が構成される。第2のパルス信号生成部は、第2の遅延回路(図7の第2の遅延回路71)を有する。第2の位相差信号出力部20は、第2の遅延回路の遅延時間を、基準クロック信号RFCKのパルス幅THに対応する遅延時間に設定する第2の遅延制御回路(図7の第2の遅延制御回路80)を有する。そして、第2の遅延回路と第2の遅延制御回路を含んで第2のDLL(Delay Locked Loop)回路(図7の第2のDLL回路140)が構成される。

30

**【 0 0 5 0 】**

このようにすれば、基準クロック信号RFCKのパルス幅THに対応する遅延時間に設定された第1の遅延回路により、基準クロック信号RFCKのパルス幅THに対応するパルス幅TPSの第1のパルス信号PSG1を生成できる。また、基準クロック信号RFCKのパルス幅THに対応する遅延時間に設定された第2の遅延回路により、基準クロック信号RFCKのパルス幅THに対応するパルス幅の第2のパルス信号PSG2を生成できる。

40

**【 0 0 5 1 】**

また本実施形態では、第1の位相差信号出力部10は第1のセレクター(図7の第1のセレクター15)を有する。第1のセレクターは、パルス幅測定モード(図8のステップ

50

S 1、図9)では、第1の遅延回路に基準クロック信号R F C Kを出力し、位相差検出モード(図8のステップS 2、図10)では、第1のパルス信号生成部に第1の信号S G 1を出力する。第2の位相差信号出力部2 0は第2のセレクター(図7の第2のセレクター2 5)を有する。第2のセレクターは、パルス幅測定モードでは、第2の遅延回路に基準クロック信号R F C Kを出力し、位相差検出モードでは、第2のパルス信号生成部に第2の信号S G 2を出力する。

#### 【0052】

例えば、パルス幅測定モードは間欠的に設定される。即ち、パルス幅測定モードが設定される第1の期間と、位相差検出モードが設定される第2の期間が交互に繰り返され、第2の期間において位相差の検出(時間差の測定)が行われる。第2の期間は第1の信号S G 1と第2の信号S G 2の入力を待機する待機期間に相当する。この待機期間中に第1の信号S G 1と第2の信号S G 2が入力されると、時間差が測定される。1つの第2の期間中に1回の測定が行われてもよいし、複数回の測定が行われてもよい。

#### 【0053】

このようにすれば、パルス幅測定モードにおいて第1の遅延回路と第1の遅延制御回路により第1の遅延回路の遅延時間を設定し、第2の遅延回路と第2の遅延制御回路により第2の遅延回路の遅延時間を設定できる。そして、位相差検出モードにおいて第1のパルス信号生成部が第1の信号S G 1に基づいて第1のパルス信号P S G 1を生成し、第2のパルス信号生成部が第2の信号S G 2に基づいて第2のパルス信号P S G 2を生成し、これらのパルス信号に基づいて位相差を検出(時間差を測定)できる。

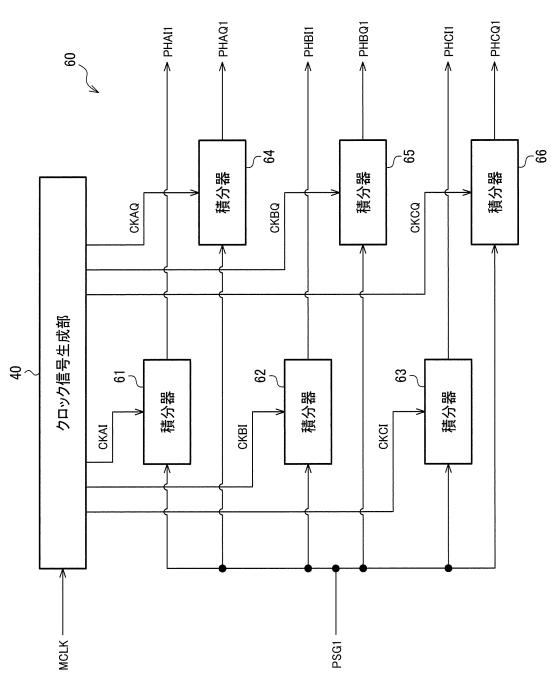

#### 【0054】

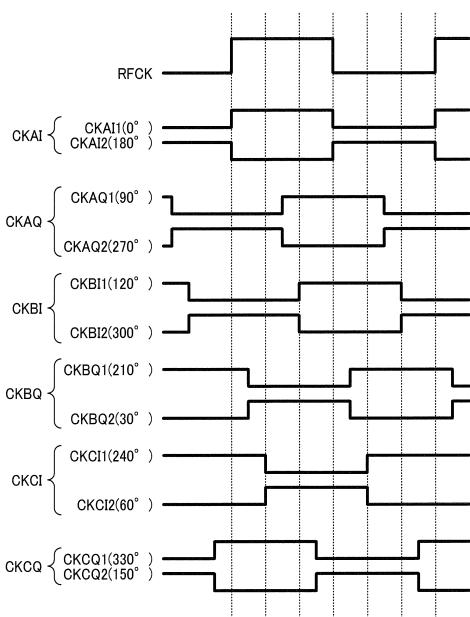

また本実施形態では、回路装置100は、基準クロック信号R F C Kに基づいて、互いに位相が異なる第1～第nのクロック信号(図12のクロック信号C K A I 1、C K B I 1、C K C I 1)を生成するクロック信号生成部(図7のクロック信号生成部120)を含む。第1の位相差信号出力部1 0は、第1～第nのクロック信号と第1の信号S G 1に基づく積分処理を行う第1～第nの積分器(図11の積分器6 1～6 3)を有する。第2の位相差信号出力部2 0は、第1～第nのクロック信号と第2の信号S G 2に基づく積分処理を行う第n+1～第2nの積分器を有する。

#### 【0055】

具体的には、第1～第nのクロック信号の位相は、基準クロック信号R F C Kを基準として360度/n刻みである。例えば、図12ではn=3であり、第1～第3のクロック信号(C K A I 1、C K B I 1、C K C I 1)の位相は360度/3=120度刻みである。なお、第1～第3のクロック信号(C K A I 1、C K B I 1、C K C I 1)と位相が90度異なるクロック信号(C K A Q 1、C K B Q 1、C K C Q 1)、それらと位相が180度異なるクロック信号(C K A I 2、C K B I 2、C K C I 2、C K A Q 2、C K B Q 2、C K C Q 2)を加えると、360度/12=30度の多相クロックになっている。

#### 【0056】

このようにすれば、図13～図15で後述するように、互いに位相が異なる第1～第nの積分値の特性(P H A I 1、P H B I 1、P H C I 1)が得られる。これにより、入力位相差に対して、位相が異なるn個の特性に基づくn個の積分値が得られる。積分処理は積分器の特性ばらつき等によって非線形性を有する可能性があり、それによって入力位相差と出力位相差の間に非線形性が生じる可能性がある。この点、本実施形態によれば、n個の積分値を例えば平均して位相差を求めてことで、入力位相差と出力位相差の間に非線形性を低減できる。

#### 【0057】

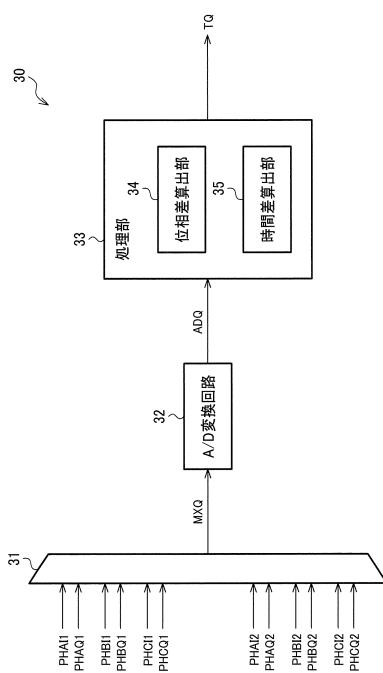

また本実施形態では、測定部3 0は、第1～第nの積分器の出力信号及び第n+1～第2nの積分器の出力信号のいずれかを選択するセレクター(図16のセレクター3 1)と、セレクターからの信号をA/D変換するA/D変換回路(図16のA/D変換回路3 2)と、A/D変換された第1～第nの積分器の出力信号及び第n+1～第2nの積分器の出力信号に基づいて、時間差を求める処理部(図16の処理部3 3)と、を有する。

10

20

30

40

50

**【 0 0 5 8 】**

このようにすれば、第1～第nの積分器の出力信号及び第n+1～第2nの積分器の出力信号を時分割にA/D変換できる。これにより、回路規模を節約できる。また、このようなA/D変換を行うことで、デジタル信号処理により積分器の出力信号（積分値）に基づいて時間差を求めることができる。また、デジタル信号処理において、例えば、図19～図21で後述する積分器のばらつき補正等の種々の処理を簡素な構成で実現できる。

**【 0 0 5 9 】****2 . 第2の構成例**

図5は、本実施形態の回路装置の第2の構成例である。図5では、回路装置100が更にカウンター110を含む。

10

**【 0 0 6 0 】**

カウンター110は、第1の信号SG1がアクティブになってから、第2の信号SG2がアクティブになるまでの基準クロック信号RFCKのクロック数をカウントする。そして、測定部30は、カウンター110のカウント値CNQと第1の位相差信号PH1と第2の位相差信号PH2に基づいて、第1の信号SG1と第2の信号SG2の時間差を測定する。

**【 0 0 6 1 】**

図6は、第2の構成例の回路装置の動作を説明するタイミングチャートである。カウンター110は、第1の信号SG1がアクティブになったことを検出してカウント動作を開始し、第2の信号SG2がアクティブになったことを検出してカウント動作を停止する。図6の例では、第1の信号SG1の立ち上がりエッジから第2の信号SG2の立ち上がりエッジまでの間に基準クロック信号RFCKが1クロック入力されるので、カウント値CNQ=1となる。

20

**【 0 0 6 2 】**

なお、第1のパルス信号PSG1がアクティブになったことを検出してカウント動作を開始し、第2のパルス信号PSG2がアクティブになったことを検出してカウント動作を停止してもよい。

**【 0 0 6 3 】**

図6に示すように、第1の信号SG1と基準クロック信号RFCKの位相差が60度と検出され、第2の信号SG2と基準クロック信号RFCKの位相差が270度と検出されたとする。この場合、測定部30は、第1の信号SG1と第2の信号SG2の位相差を、 $-60\text{度} + (CNQ \times 360\text{度}) + 270\text{度}$ と求める。図6ではCNQ=1なので、位相差は570度となる。

30

**【 0 0 6 4 】**

第2の信号SG2が第1の信号SG1よりも前に入力された場合には、カウンター110は、第2の信号SG2がアクティブになったことを検出してカウント動作を開始し、第1の信号SG1がアクティブになったことを検出してカウント動作を停止する。この場合、カウント値CNQの符号を負にする。

**【 0 0 6 5 】**

従来の位相差検出方式ではセンサーで積分処理を行うため、ダイナミックレンジ（測定できる位相差や距離、時間のレンジ）を広げることが困難である。この点、本実施形態によれば、第1の信号SG1と第2の信号SG2の位相差が360度より大きい（時間差が基準クロック信号RFCKの1周期より大きい）場合であっても、位相差を検出できる。これにより、広いダイナミックレンジの測定が可能になる。

40

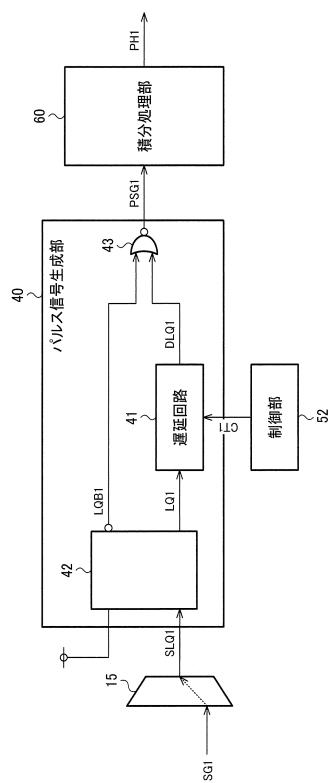

**【 0 0 6 6 】****3 . 詳細な構成例**

図7は、本実施形態の回路装置の詳細な構成例である。回路装置100は、第1の位相差信号出力部10、第2の位相差信号出力部20、測定部30、クロック信号生成部120（クロック信号生成回路）を含む。なお、本実施形態は図7の構成に限定されず、その構成要素の一部を省略したり、他の構成要素（例えば図5のカウンター110）を追加し

50

たりする等の種々の変形実施が可能である。

#### 【0067】

クロック信号生成部120は、クロック信号MCK(マスタークロック信号)からクロック信号RFCK2、CKI、CKQを生成する。クロック信号RFCK2は、基準クロック信号RFCKの2倍の周波数を有するクロック信号である。クロック信号CKI、CKQは、基準クロック信号RFCKから位相がシフトされたクロック信号(多相クロック信号)である。クロック信号MCKは、基準クロック信号RFCKよりも周波数が高いクロック信号であり、回路装置100の内部で生成されるクロック信号、又は回路装置100の外部から供給されるクロック信号である。例えば、クロック信号生成部120は分周器等から構成される。

10

#### 【0068】

第1の位相差信号出力部10は、第1のセレクター15、第1のDLL回路130、第1の積分処理部60(第1の積分処理回路)を含む。第1のDLL回路130は、第1のパルス信号生成部40(第1のパルス信号生成回路)、第1の遅延制御回路50を含む。

#### 【0069】

第1のセレクター15は、第1の信号SG1とクロック信号RFCK2のいずれかを選択し、その選択した信号SLQ1を出力する。第1のパルス信号生成部40は、第1の遅延回路41を含み、パルス幅が第1の遅延回路41の遅延時間で設定される第1のパルス信号PSG1を生成する。第1の遅延制御回路50は、第1の遅延回路41の遅延時間を制御する制御信号CT1を出力し、その遅延時間が基準クロック信号RFCKのパルス幅となるように制御する。例えば、第1の遅延回路41は、複数の遅延素子が直列に接続された回路である。遅延素子は、例えばインバーターと、インバーターの出力に設けられた可変容量キャパシター(負荷容量)である。そして可変容量キャパシターの容量値が制御信号CT1により制御され、第1の遅延回路41の遅延時間が制御される。第1の遅延制御回路50は、第1の遅延回路41の出力信号DLQ1とクロック信号RFCK2との位相差を検出して信号DT1を出力する位相差検出部51(位相差検出回路)と、信号DT1に基づいて制御信号CT1を出力する制御部52(制御回路)とを含む。第1の積分処理部60は、第1のパルス信号PSG1とクロック信号CKI、CKQに基づいて積分処理を行い、第1の位相差信号PH1を出力する。

20

#### 【0070】

第2の位相差信号出力部20は、第2のセレクター25、第2のDLL回路140、第2の積分処理部90(第2の積分処理回路)を含む。第2のDLL回路140は、第2のパルス信号生成部70(第2のパルス信号生成回路)、第2の遅延制御回路80を含む。

30

#### 【0071】

第2のセレクター25は、第2の信号SG2とクロック信号RFCK2のいずれかを選択し、その選択した信号SLQ2を出力する。第2のパルス信号生成部70は、第2の遅延回路71を含み、パルス幅が第2の遅延回路71の遅延時間で設定される第2のパルス信号PSG2を生成する。第2の遅延制御回路80は、第2の遅延回路71の遅延時間を制御する制御信号CT2を出力し、その遅延時間が基準クロック信号RFCKのパルス幅となるように制御する。第2の遅延回路71は第1の遅延回路41と同様な構成である。第2の遅延制御回路80は、第2の遅延回路71の出力信号DLQ2とクロック信号RFCK2との位相差を検出して信号DT2を出力する位相差検出部81(位相差検出回路)と、信号DT2に基づいて制御信号CT2を出力する制御部82(制御回路)とを含む。第2の積分処理部90は、第2のパルス信号PSG2とクロック信号CKI、CKQに基づいて積分処理を行い、第2の位相差信号PH2を出力する。

40

#### 【0072】

図8は、詳細な構成例の回路装置の動作を説明するフローチャートである。動作を開始すると測定部30(図16の処理部33)はパルス幅測定モードを設定する(S1)。パルス幅測定モードでは、第1の位相差信号出力部10及び第2の位相差信号出力部20は、基準クロック信号RFCKのパルス幅を測定して遅延回路の遅延時間(遅延量)を設定

50

(ロック)するパルス幅測定モードを設定する(S1)。

**【0073】**

図9は、パルス幅測定モードにおける第1の位相差信号出力部の動作を説明する図である。ここでは第1の位相差信号出力部10を例に説明するが、第2の位相差信号出力部20の動作も同様である。なお、図9では動作に関わる構成要素を図示し、他の構成要素は図示を省略する。

**【0074】**

パルス幅測定モードでは、第1のセレクター15は、クロック信号R F C K 2を選択し、信号S L Q 1として出力する。遅延回路41は、信号S L Q 1(=R F C K 2)を遅延させた信号D L Q 1を出力する。位相差検出部51は、クロック信号R F C K 2と信号D L Q 1の位相差を検出し、その検出された位相差を表す信号D T 1を出力する。制御部52は、信号D T 1に基づいて、クロック信号R F C K 2と信号D L Q 1の位相差がゼロとなるように制御信号C T 1を生成する。クロック信号R F C K 2の周波数は、基準クロック信号R F C Kの周波数の2倍なので、第1の遅延回路41の遅延時間は、基準クロック信号R F C Kの半周期(基準クロック信号R F C Kのデューティーが50%の場合において基準クロック信号R F C Kのハイパルスの幅)にロックされる。

**【0075】**

図8に示すように、測定部30は位相差検出モードを設定する(S2)。位相差検出モードでは、第1の位相差信号出力部10及び第2の位相差信号出力部20は、第1の信号S G 1と第2の信号S G 2の位相差を検出する。

**【0076】**

図10は、位相差検出モードにおける第1の位相差信号出力部の動作を説明する図である。ここでは第1の位相差信号出力部10を例に説明するが、第2の位相差信号出力部20の構成及び動作も同様である。なお、図10では動作に関わる構成要素を図示し、他の構成要素は図示を省略する。

**【0077】**

第1のパルス信号生成部40は、第1の遅延回路41、ラッチ回路42、N O R回路43を含む。位相差検出モードでは、第1のセレクター15は、第1の信号S G 1を選択し、信号S L Q 1として出力する。ラッチ回路42は、信号S L Q 1(=S G 1)の立ち上がりエッジでハイレベルを取り込み、信号L Q 1をローレベルからハイレベルに変化させ、信号L Q B 1(L Q 1の論理反転信号)をハイレベルからローレベルに変化させる。第1の遅延回路41は、制御信号C T 1で設定される遅延時間で信号L Q 1を遅延させ、信号D L Q 1を出力する。制御信号C T 1は、パルス幅測定モードで設定された値が維持されている。N O R回路43は、信号L Q B 1と信号D L Q 1の否定論理和信号を第1のパルス信号P S G 1として出力する。制御信号C T 1は、パルス幅測定モードで設定された値が維持されており、第1のパルス信号P S G 1のパルス幅は基準クロック信号R F C Kのパルス幅と同じになる。第1の積分処理部60は、第1のパルス信号P S G 1に基づいて積分処理を行い、第1の位相差信号P H 1を出力する。

**【0078】**

図8に示すように、測定部30は、位相差検出モードにおいて出力される第1の位相差信号P H 1と第2の位相差信号P H 2を第1の位相差データと第2の位相差データにA/D変換する(S3)。次に、測定部30は、デジタル信号処理により第1の位相差データと第2の位相差データから第1の信号S G 1と第2の信号S G 2の遷移タイミングの時間差を求める(S4)。

**【0079】**

4. 積分処理部

図11は、第1の積分処理部の詳細な構成例である。第1の積分処理部60は、積分器61～66(複数の積分器、第1～第6の積分器)を含む。なお、ここでは第1の積分処理部60を例に説明するが、第2の積分処理部90も同様に複数の積分器(第7～第12の積分器)を含み、同様に動作により第2のパルス信号P S G 2に基づく積分処理を行う

10

20

30

40

50

。

### 【0080】

クロック信号生成部120は、クロック信号CKAI、CKBI、CKCI、CKAQ、CKBQ、CKCQを生成し、積分器61、62、63、64、65、66に供給する。クロック信号CKAI、CKBI、CKCIは図7のクロック信号CKIに対応し、クロック信号CKAQ、CKBQ、CKCQは図7のクロック信号CKQに対応する。積分器61、62、63、64、65、66は、供給されるクロック信号と第1のパルス信号PSG1に基づいて積分処理を行い、積分値PHAI1、PHBI1、PHCI1、PHAQ1、PHBQ1、PHCQ1を出力する。積分値PHAI1、PHBI1、PHCI1、PHAQ1、PHBQ1、PHCQ1は、図7の第1の位相差信号PH1に対応する

10

。

### 【0081】

図12は、クロック信号生成部が生成するクロック信号のタイミングチャートである。

### 【0082】

クロック信号CKAI、CKBI、CKCI、CKAQ、CKBQ、CKCQの各々は、位相が反転した（位相が180度異なる）2つのクロック信号の組み合わせである。例えば、クロック信号CKAIは、クロック信号CKAI1、CKAI2から構成される。そして、これら12個のクロック信号は、基準クロック信号RFCKに対して30度（=360度/12）ずつ位相がずれた多相クロック信号になっている。

### 【0083】

20

具体的には、クロック信号CKAI1は基準クロック信号RFCKと同位相であり、クロック信号CKBI1、CKCI1は、基準クロック信号RFCKに対して位相が120度、240度だけ遅れている。クロック信号CKAQ1、CKBQ1、CKCQ1は、クロック信号CKAI1、CKBI1、CKCI1に対して位相が90度だけ遅れている。そしてクロック信号CKAI2、CKBI2、CKCI2、CKAQ2、CKBQ2、CKCQ2は、クロック信号CKAI1、CKBI1、CKCI1、CKAQ1、CKBQ1、CKCQ1に対して位相が反転されている（位相が180度異なっている）。

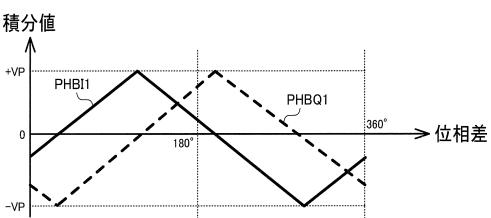

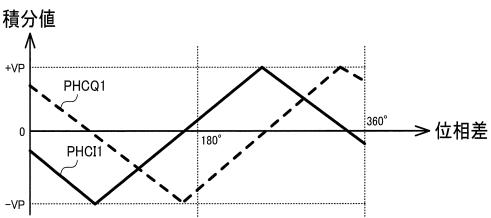

### 【0084】

図13～図15は、多相クロックによる積分処理の積分値の特性を示す図である。横軸の位相差は、基準クロック信号RFCKと第1の信号SG1の位相差である。図12で説明したように、基準クロック信号RFCKを基準としてクロック信号CKAI、CKBI、CKCIの位相は0度、120度、240度になっている。そのため、図13～図15に示すように、積分値PHAI1の特性に対して、積分値PHBI1、PHCI1の特性は120度、240度ずれている。同様に、積分値PHAQ1の特性に対して、積分値PHBQ1、PHCQ1の特性は120度、240度ずれている。

30

### 【0085】

測定部30は、積分値PHAI1、PHAQ1から第1の位相差を求め、積分値PHBI1、PHBQ1から第2の位相差を求め、積分値PHCI1、PHCQ1から第3の位相差を求める。そして、第1～第3の位相差の平均値を、第1の信号SG1と基準クロック信号RFCKの位相差として求める。

40

### 【0086】

理想的には、積分値PHAI1、PHAQ1の組だけでも、入力位相差に対して線形な特性の出力位相差が得られる。入力位相差は、入力された基準クロック信号RFCKと第1の信号SG1の位相差であり、出力位相差は、積分処理に基づく位相差である。しかしながら、積分器の誤差（例えば積分値のフルスケール誤差やオフセット等）によって、入力位相差と出力位相差が線形にならない可能性がある。

### 【0087】

この点、本実施形態では、位相を異ならせた多相クロックで積分処理を行って複数の位相差（第1～第3の位相差）を求め、その複数の位相差を平均するので、入力位相差と出力位相差の間の非線形性を平均化できる。例えば、入力位相差が180度の場合、図13

50

において積分値 P H A I 1 の特性が - V P で折り返す点になっている。このような特性が折り返す点では非線形性が出やすくなる。しかし、図 14、図 15 では、位相差 180 度における積分値 P H B I 1、P H C I 1 の特性は直線になっている。このため、第 1 ~ 第 3 の位相差を平均することで、非線形性を低減できる。

#### 【0088】

##### 5. 測定部

図 16 は、測定部の詳細な構成例である。測定部 30 は、セレクター 31（マルチプレクサー）、A / D 変換回路 32、処理部 33（デジタル信号処理部、処理回路、ロジック回路）を含む。

#### 【0089】

セレクター 31 には、第 1 の位相差信号出力部 10 から積分値 P H A I 1、P H A Q 1、P H B I 1、P H B Q 1、P H C I 1、P H C Q 1 が入力され、第 2 の位相差信号出力部 20 から積分値 P H A I 2、P H A Q 2、P H B I 2、P H B Q 2、P H C I 2、P H C Q 2 が入力される。セレクター 31 は、これらの信号を 1 つずつ時分割に選択し、その選択した信号を信号 M X Q として出力する。A / D 変換回路 32 は、信号 M X Q として入力される積分値 P H A I 1、P H A Q 1、P H B I 1、P H B Q 1、P H C I 1、P H C Q 1、P H A I 2、P H A Q 2、P H B I 2、P H B Q 2、P H C I 2、P H C Q 2 を時分割に A / D 変換し、その A / D 変換された積分値（積分データ）をデータ A D Q として出力する。処理部 33 は、デジタル信号処理により、データ A D Q に基づいて時間差データ T Q を求める。

#### 【0090】

具体的には、処理部 33 は、位相差算出部 34 と時間差算出部 35 を含む。位相差算出部 34 は、積分値 P H A I 1、P H A Q 1 から第 1 の位相差を求め、積分値 P H B I 1、P H B Q 1 から第 2 の位相差を求め、積分値 P H C I 1、P H C Q 1 から第 3 の位相差を求める。また積分値 P H A I 2、P H A Q 2 から第 4 の位相差を求め、積分値 P H B I 2、P H B Q 2 から第 5 の位相差を求め、積分値 P H C I 2、P H C Q 1 から第 6 の位相差を求める。位相差算出部 34 は、第 1 ~ 第 3 の位相差を平均して、第 1 の信号 S G 1 と基準クロック信号 R F C K の位相差を求め、第 4 ~ 第 6 の位相差を平均して、第 2 の信号 S G 2 と基準クロック信号 R F C K の位相差を求める。時間差算出部 35 は、第 1 の信号 S G 1 と基準クロック信号 R F C K の位相差と、第 2 の信号 S G 2 と基準クロック信号 R F C K の位相差とから、第 1 の信号 S G 1 と第 2 の信号 S G 2 の位相差を求め、その位相差に基づいて時間差データ T Q を出力する。位相差を時間差に変換する手法は、図 2 等で説明した手法と同様である。

#### 【0091】

##### 6. 積分器

図 17 は、積分器の詳細な構成例である。また図 18 は、積分器の動作を説明するタイミングチャートである。なお、ここでは図 11 の積分器 61 を例に説明するが、他の積分器（図 11 の積分器 62 ~ 66、第 2 の積分処理部 90 の積分器）も同様の構成である。

#### 【0092】

図 17 に示すように、積分器 61 は、積分信号生成部 G I S、電流生成部 I G E N、積分部 C I N T を含む。

#### 【0093】

積分信号生成部 G I S は、第 1 のパルス信号 P S G 1 とクロック信号 C K A I ( C K A I 1、C K A I 2 ) から積分信号 I N C K A、I N C K B を生成する。図 18 に示すように、第 1 のパルス信号 P S G 1 とクロック信号 C K A I 1 の論理積を積分信号 I N C K A として出力し、第 1 のパルス信号 P S G 1 とクロック信号 C K A I 2 の論理積を積分信号 I N C K B として出力する。

#### 【0094】

電流生成部 I G E N は、積分信号 I N C K A、I N C K B に基づいて電流 I P、I N を生成し、その電流 I P、I N を積分部 C I N T の入力ノード N I N P、N I N N に供給す

10

20

30

40

50

る。具体的には、積分信号 INC KA がハイレベル（アクティブ）であり、積分信号 INC KB がローレベル（非アクティブ）である場合には、スイッチ素子 SWA 1、SWA 2 がオンになり、スイッチ素子 SWB 1、SWB 2 がオフになる。そして、電流源 IBB から一定電流値の負電流が電流 IP としてノード NINP に供給され、電流源 IBA から一定電流値の正電流が電流 IN としてノード NINN に供給され、 $IP - IN < 0$  となる。一方、積分信号 INC KA がローレベル（非アクティブ）であり、積分信号 INC KB がハイレベル（アクティブ）である場合には、スイッチ素子 SWA 1、SWA 2 がオフになり、スイッチ素子 SWB 1、SWB 2 がオンになる。そして、電流源 IBA から一定電流値の正電流が電流 IP としてノード NINP に供給され、電流源 IBB から一定電流値の負電流が電流 IN としてノード NINN に供給され、 $IP - IN > 0$  となる。

10

#### 【0095】

積分部 CINT は、差動入力された電流 IP、IN を積分し、その積分値を電圧 VOUT、VOUTN として差動出力する。即ち、電流 IP、IN により供給される電荷を電圧 VOUTP、VOUTN に変換する電荷電圧変換を行う。積分部 CINT は、負の入力電荷を正の電圧に変換する反転増幅を行う。即ち、積分信号 INC KA がハイレベルであり、積分信号 INC KB がローレベルである場合、上述のように  $IP - IN < 0$  なので、図 18 に示すように VOUTP - VOUTN が増加する方向に電圧 VOUTP、VOUTN が変化する。一方、積分信号 INC KA がローレベルであり、積分信号 INC KB がハイレベルである場合、上述のように  $IP - IN > 0$  なので、図 18 に示すように VOUTP - VOUTN が減少する方向に電圧 VOUTP、VOUTN が変化する。このようにして第 1 のパルス信号 PSG 1 が積分値 PHAI 1 に変換され、図 13 に示す積分値 PHAI 1 の特性が得られる。

20

#### 【0096】

積分部 CINT において、制御信号 APC K（クロック信号）がローレベル（非アクティブ）であり、制御信号 APC K の論理反転信号である制御信号 XAPC K（クロック信号）がハイレベル（アクティブ）である場合、スイッチ素子 SWP 1 ~ SWP 4 がオフになり、スイッチ素子 SWP 5 ~ SWP 8 がオンになる。この場合、キャパシター CP 1 ~ CP 4、アンプ回路 AMP により差動の積分回路（差動の電荷電圧変換回路）が構成され、上述の積分動作が行われる。一方、制御信号 APC K がハイレベル（アクティブ）であり、制御信号 XAPC K がローレベル（非アクティブ）である場合、スイッチ素子 SWP 1 ~ SWP 4 がオンになり、スイッチ素子 SWP 5 ~ SWP 8 がオフになる。この場合、入力ノード NINP、NINN がコモン電圧 VCM に設定され、入力電荷がリセットされ、電圧 VOUTP、VOUTN がコモン電圧 VCM にリセットされる。

30

#### 【0097】

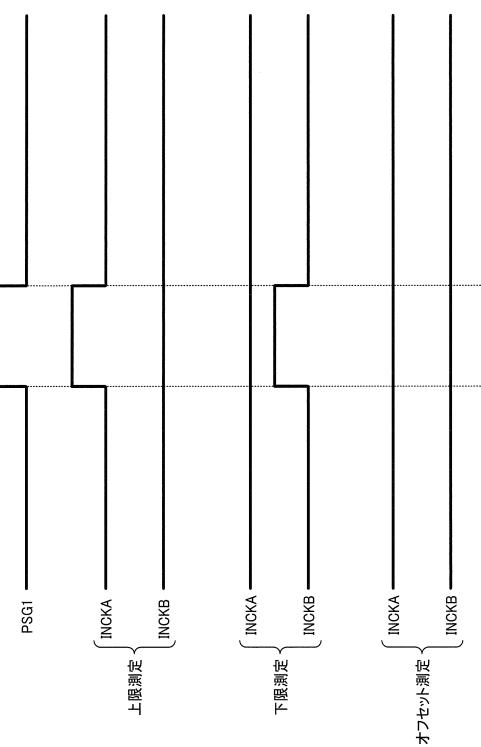

##### 7. 積分器のばらつき補正

図 19 は、積分器間における積分値の特性のばらつきを説明する図である。図 20 は、入力位相差に対する出力位相差の特性例である。

#### 【0098】

図 19 に示すように、積分値 PHAQ 1 の変化範囲の上限が + VP であり、下限が - VP であるとする。即ち、積分値 PHAQ 1 のフルスケール（出力フルスケール）が 2 VP であるとする。このとき、積分値 PHAI 1' のように、積分値 PHAI 1 も同一のフルスケール 2 VP であることが理想である。この理想の場合には、図 20 の特性 CHA のように、入力位相差に対して出力位相差が線形な特性となる。

40

#### 【0099】

しかしながら、図 19 に示す積分値 PHAI 1' のように、積分値 PHAI 1 のフルスケールが 2 VP' 2 VP となる可能性がある。例えば、図 17 において電流源 IBA、IBB が output する電流の大きさが積分器間でばらつくことで、積分器間でのフルスケールのばらつきが生じる。このようなフルスケールのばらつきが生じた場合、図 20 の特性 CHA' のように、入力位相差に対して出力位相差が非線形な特性となる。

#### 【0100】

50

またフルスケールのばらつきだけでなく、オフセットのばらつきが生じる可能性がある。オフセットのばらつきによっても、入力位相差に対して出力位相差が非線形な特性となる可能性がある。

#### 【0101】

図21は、積分器のばらつき補正を説明する図である。なお、図21では参考に第1のパルス信号PSG1を図示しているが、ばらつき補正時には第1のパルス信号PSG1は積分器に供給されなくてよい。

#### 【0102】

図21に示すように、回路装置100は各積分器について上限測定、下限測定、オフセツト測定を行う。これらの測定は、第1の信号SG1と第2の信号SG2の時間差を測定する前に行っておく。例えば回路装置100の電源投入時などに行う。

10

#### 【0103】

上限測定時には、積分信号生成部GISが、第1のパルス信号PSG1と同じパルス幅でハイレベルになる積分信号INCKAを出力し、ローレベルの積分信号INCKBを出力する。これは積分値の上限を測定することに相当するので、例えば図19では+VP'が積分値として得られる。下限測定時には、積分信号生成部GISが、ローレベルの積分信号INCKAを出力し、第1のパルス信号PSG1と同じパルス幅でハイレベルになる積分信号INCKBを出力する。これは積分値の下限を測定することに相当するので、例えば図19では-VP'が積分値として得られる。オフセット測定時には、積分信号生成部GISが、ローレベルの積分信号INCKA、INCKBを出力する。これは積分値のオフセットを測定することに相当するので、例えば図19では0が積分値として得られる。

20

#### 【0104】

上記の測定で得られた積分値の上限をIMAXとし、下限をIMINとし、オフセットをIOFとし、フルスケールの期待値をFLSとする。また、第1の信号SG1と第2の信号SG2の時間差を測定した際に得られた積分値をMESとする。測定部30の処理部33は、補正された積分値MES'を例えれば $MES' = (FLS / (IMAX - IMIN)) \times (MES - IOF)$ により求める。例えば図19の例では $MES' = (VP / VP') \times MES$ となる。このような補正を、各積分器について行う。そして、この補正された積分値に基づいて位相差を求め、その位相差に基づいて時間差を求める。

30

#### 【0105】

なお、オフセット測定を行わず、上限と下限の測定値で積分値を補正してもよい。この場合、 $MES' = (FLS / (IMAX - IMIN)) \times MES$ である。

#### 【0106】

### 8. 物理量測定装置、電子機器、移動体

図22は、本実施形態の回路装置100を含む物理量測定装置の構成例である。物理量測定装置200は、信号供給部210(信号供給回路)、回路装置100、処理部220(処理回路、処理装置)を含む。なお、本実施形態は図22の構成に限定されず、その構成要素の一部(例えば信号供給部)を省略したり、他の構成要素を追加したりする等の種々の変形実施が可能である。

40

#### 【0107】

図22の物理量測定装置200は、時間デジタル変換の結果に基づいて種々の物理量を測定する装置である。例えば、測定される物理量は時間や距離等であるが、これらに限定されない。

#### 【0108】

信号供給部210は、回路装置100に対して第1の信号SG1と第2の信号SG2を供給する。例えば物理量測定装置200が測距センサーである場合、信号供給部210は、発光部、受光部、制御部を含む。そして、制御部が送信信号により発光部を発光させると共に送信信号を第1の信号SG1として回路装置100に供給する。また制御部は、受光部からの受光信号を波形成して受信信号を生成し、その受信信号を第2の信号SG2

50

として回路装置 100 に供給する。或いは物理量測定装置 200 が時間デジタル変換器である場合、信号供給部 210 は、外部から入力される 2 つの信号を波形成形して第 1 の信号 SG1、第 2 の信号 SG2 として出力する。或いは、外部から入力される 2 つの信号をバッファリングして第 1 の信号 SG1、第 2 の信号 SG2 として出力する。或いは、信号供給部 210 は、外部から第 1 の信号 SG1、第 2 の信号 SG2 を入力するケーブル等を接続するコネクターであってもよい。

#### 【0109】

回路装置 100 は、第 1 の信号 SG1 と第 2 の信号 SG2 の時間差を測定し、時間差データ TQ を出力する。処理部 220 は、時間差データ TQ に基づいて種々のデジタル信号処理を行う。例えば、処理部 220 は、時間差データ TQ を物理量に変換する処理を行い、その物理量のデータを出力する。10

#### 【0110】

図 23 は、本実施形態の回路装置 100 を含む電子機器の構成例である。電子機器 300 は、回路装置 100、アンテナ ANT、通信部 510（通信装置）、処理部 520（処理装置）を含む。また操作部 530（操作装置）、表示部 540（表示装置）、記憶部 550（メモリー）を含むことができる。例えば回路装置 100 と処理部 520 により物理量測定装置が構成される。なお電子機器 300 は図 23 の構成に限定されず、これらの一部の構成要素（例えばアンテナ ANT、通信部 510 等）を省略したり、他の構成要素を追加するなどの種々の変形実施が可能である。

#### 【0111】

図 23 の電子機器 300 としては、例えば、ECU (Electronic Control Unit) 等の車載の電子装置や、医療用又は工業用の超音波検査装置等の超音波測定装置や、電波や超音波を用いたレーダーを想定できる。また、電子機器 300 として、ゲーム装置や、デジタルカメラ又はビデオカメラ等の映像機器や、スマートフォン、携帯電話機、携帯型ゲーム装置、ノート PC 又はタブレット PC 等の携帯情報端末（移動端末）や、コンテンツを配信するコンテンツ提供端末や、或いは基地局又はルーター等のネットワーク関連機器などの種々の機器を想定できる。20

#### 【0112】

通信部 510（無線回路）は、アンテナ ANT を介して外部からデータを受信したり、外部にデータを送信する処理を行う。処理部 520 は、電子機器 300 の制御処理や、通信部 510 を介して送受信されるデータの種々のデジタル処理、回路装置 100 が出力する時間差データを用いたデジタル処理などを行う。この処理部 520 の機能は、例えばマイクロコンピューターなどのプロセッサーにより実現できる。操作部 530 は、ユーザーが入力操作を行うためのものであり、操作ボタンやタッチパネルディスプレイをなどにより実現できる。表示部 540 は、各種の情報を表示するものであり、液晶や有機 EL などのディスプレイにより実現できる。なお操作部 530 としてタッチパネルディスプレイを用いる場合には、このタッチパネルディスプレイが操作部 530 及び表示部 540 の機能を兼ねることになる。記憶部 550 は、データを記憶するものであり、その機能は RAM や ROM などの半導体メモリーや HDD（ハードディスクドライブ）などにより実現できる。30

#### 【0113】

図 24 は、本実施形態の回路装置を含む移動体の例を示す。本実施形態の回路装置 100（物理量測定装置）は、例えば、車、飛行機、バイク、自転車、或いは船舶等の種々の移動体に組み込むことができる。移動体は、例えばエンジンやモーター等の駆動機構、ハンドルや舵等の操舵機構、各種の電子機器（車載機器）を備えて、地上や空や海上を移動する機器・装置である。図 24 は移動体の具体例としての自動車 206 を概略的に示している。自動車 206 には、本実施形態の回路装置 100 を有する物理量測定装置（不図示）が組み込まれる。制御装置 208 は、この物理量測定装置により生成された物理量に基づいて動作する。例えば、制御装置 208 は、自動車 206 と物体との距離に応じて運転アシスト制御や自動運転制御を行う ECU であってもよい。なお本実施形態の回路装置や40

物理量測定装置が組み込まれる機器は、このような制御装置 208 には限定されず、自動車 206 等の移動体に設けられる種々の機器（車載機器）に組み込むことが可能である。

#### 【0114】

なお、上記のように本実施形態について詳細に説明したが、本発明の新規事項および効果から実体的に逸脱しない多くの変形が可能であることは当業者には容易に理解できるであろう。従って、このような変形例はすべて本発明の範囲に含まれるものとする。例えば、明細書又は図面において、少なくとも一度、より広義または同義な異なる用語と共に記載された用語は、明細書又は図面のいかなる箇所においても、その異なる用語に置き換えることができる。また本実施形態及び変形例の全ての組み合わせも、本発明の範囲に含まれる。また回路装置、物理量測定装置、電子機器、移動体の構成・動作等も、本実施形態で説明したものに限定されず、種々の変形実施が可能である。

10

#### 【符号の説明】

#### 【0115】

10 ... 第 1 の位相差信号出力部、15 ... 第 1 のセレクター、

20 ... 第 2 の位相差信号出力部、25 ... 第 2 のセレクター、30 ... 測定部、

31 ... セレクター、32 ... A / D 変換回路、33 ... 処理部、34 ... 位相差算出部、

35 ... 時間差算出部、40 ... 第 1 のパルス信号生成部、41 ... 遅延回路、

41 ... 第 1 の遅延回路、42 ... ラッチ回路、43 ... N O R 回路、

50 ... 第 1 の遅延制御回路、51 ... 位相差検出部、52 ... 制御部、

60 ... 第 1 の積分処理部、61 ~ 66 ... 積分器、70 ... 第 2 のパルス信号生成部、

71 ... 第 2 の遅延回路、80 ... 第 2 の遅延制御回路、81 ... 位相差検出部、

82 ... 制御部、90 ... 第 2 の積分処理部、100 ... 回路装置、110 ... カウンター、

120 ... クロック信号生成部、130 ... 第 1 のD L L 回路、

140 ... 第 2 のD L L 回路、200 ... 物理量測定装置、206 ... 自動車（移動体）、

208 ... 制御装置、210 ... 信号供給部、220 ... 処理部、300 ... 電子機器、

510 ... 通信部、520 ... 処理部、530 ... 操作部、540 ... 表示部、550 ... 記憶部、

P H 1 ... 第 1 の位相差信号、P H 2 ... 第 2 の位相差信号、P S G 1 ... 第 1 のパルス信号、

P S G 2 ... 第 2 のパルス信号、R F C K ... 基準クロック信号、S G 1 ... 第 1 の信号、

S G 2 ... 第 2 の信号、T D F ... 時間差、T H ... パルス幅、T P S ... パルス幅、

T Q ... 時間差データ

20

30

【図1】

【図3】

【図2】

【図4】

【図6】

【図5】

【図7】

【図8】

【図9】

【図10】

【図 1 1】

【図 1 2】

【図 1 3】

【図 1 4】

【図 1 5】

【図 1 6】

【図17】

【図18】

【図19】

【図21】

【図20】

【図22】

【図24】

【図23】

---

フロントページの続き

(56)参考文献 特開昭63-309888(JP,A)

特開昭62-095487(JP,A)

特開昭62-299786(JP,A)

特開平11-281744(JP,A)

米国特許出願公開第2007/0005288(US,A1)

(58)調査した分野(Int.Cl., DB名)

G 01 C 3 / 00 - 3 / 32

G 01 S 7 / 48 - 7 / 51

G 01 S 17 / 00 - 17 / 95

G 04 F 7 / 00 - 13 / 06