Europäisches Patentamt

European Patent Office

Office européen des brevets

⑪ Publication number:

0 238 097 B1

⑫

## EUROPEAN PATENT SPECIFICATION

⑬ Date of publication of patent specification: 13.05.92 ⑮ Int. Cl. 5: H04Q 7/02, H04B 5/04,

H04B 1/16, G08B 3/10

⑯ Application number: 87104408.7

⑰ Date of filing: 31.08.81

⑯ Publication number of the earlier application in

accordance with Art.76 EPC: 0 061 462

⑭ Multi-system paging device with power conservation.

⑯ Priority: 01.10.80 US 192779

⑯ Date of publication of application:

23.09.87 Bulletin 87/39

⑯ Publication of the grant of the patent:

13.05.92 Bulletin 92/20

⑯ Designated Contracting States:

AT DE FR GB NL SE

⑯ References cited:

|                 |                 |

|-----------------|-----------------|

| DE-A- 2 738 887 | GB-A- 2 024 567 |

| US-A- 4 019 142 | US-A- 4 181 893 |

| US-A- 4 194 153 | US-A- 4 197 526 |

⑯ Proprietor: MOTOROLA, INC.

1303 East Algonquin Road

Schaumburg, IL 60196(US)

⑯ Inventor: Davis, Walter Lee

10948 N.W. 3rd Street

Coral Springs Florida 33065(US)

Inventor: Raghunathan, Kupuswamy

12311 Scribe Drive

Austin Texas 78759(US)

⑯ Representative: Ibbotson, Harold et al

Motorola Ltd Jays Close Viables Industrial

Estate

Basingstoke Hants RG22 4PD(GB)

EP 0 238 097 B1

Note: Within nine months from the publication of the mention of the grant of the European patent, any person may give notice to the European Patent Office of opposition to the European patent granted. Notice of opposition shall be filed in a written reasoned statement. It shall not be deemed to have been filed until the opposition fee has been paid (Art. 99(1) European patent convention).

Rank Xerox (UK) Business Services

(3.08/2.19/2.0)

Rank Xerox

Rank Xerox

Rank Xerox

**Description****Background of the Invention****5 1. Field of the Invention**

This invention relates generally to the field of portable paging systems and in particular to a portable paging device in which the signal processing is performed by a decoder operating in real time to provide multiple scheme decoding and energy-saving routines.

**10 2. Description of the Prior Art**

15 Pagers are generally small, portable, battery-operated radio receivers designed to be carried on the person of the user in a pocket or clipped to a belt. A typical user might be a medical doctor or maintenance person. The technique used in paging systems is referred to as selective calling in which transmissions intended for a particular receiver will cause a response only in that receiver. The selective calling capability is achieved by assigning to each pager one or more unique address codes which are encoded and modulated on the carrier wave. Each pager includes a decoding portion which is designed to cause a response only to its assigned address codes. If one of the assigned address codes is detected, the pager is 20 activated to produce a corresponding alert signal. Normally, none of the other pagers in the communications system will be activated by that transmission unless the system has a group call operation.

25 Pager communication systems are well known in the art and operate with many types of coding schemes including single or multi-tone signals, selected combination of tone and voice signals and digitally encoded signals. Typically there are wide area paging services capable of transmitting throughout a metropolitan area and local paging services which transmit in a much smaller service area as, for example, a specific building complex or other facility. The range of operation of the various systems is generally determined by the power of the transmitter used.

30 If a pager carrier is required to receive signals within the boundaries of several facilities, he could require a separate local pager for each such facility. The occurrence of such problems can be frequent, as 35 is the case with doctors who may be on the staff of several hospitals and are required to visit patients in several hospital locations. Moreover, changing location, such as traveling to a nearby city having a different wide area service system, would render an original wide area pager and all of the several local pagers useless and require an entirely new set of pagers. Thus, it would be advantageous to have a paging device which can function to provide decoding and alert signaling for more than one pager communications system. Then the difficulty of changing pager addresses on a specific device or physically changing pagers or altering circuitry to change address codes when a pager is carried from one message service area to another could be eliminated.

40 While there are several tone only and tone and voice signal decoding systems, the decoding of such information is generally not as difficult or as demanding as decoding those systems which employ digitally encoded signals. Such digital systems are capable of a high volume of messages transmitted per unit time because of the faster information rate they can transmit for addressing individual paging devices.

45 The digital information which is sent out in a digital communications system normally comprises a binary signal train which includes level transitions from a first level to a second level. These levels indicate the distinction between a binary 0 and a binary 1. There must also be a specific time duration which corresponds to a bit interval. The non-return-to-zero (NRZ) binary coding system generally used does not delineate bit intervals. It therefore is necessary to ascertain when an information bit begins or ends and this applies to both synchronous and asynchronous systems. Because of the variability of the nature of the information in an NRZ serial binary pulse train, several bit intervals could pass without the occurrence of a transition in the signal levels. Thus it is generally not obvious simply from the information received at a 50 receiver precisely when a bit interval begins or ends.

55 There are two general types of digital systems and they are distinguishable by the time relationships between transmitter and receiver. In synchronous systems, the transmitter and receiver must be in synchronization so that bit address sequences and frames delineating information words can be correctly decoded. By contrast, asynchronous systems normally decode a preliminary information word which constitutes part of an address and, when identified, causes the establishment of a time window in anticipation of the subsequent detection of digital information related to the remaining portion of the address of an individual paging device. With either synchronous or asynchronous systems, the difficulties of

providing decoding for more than one encoding system are complex. Moreover, the presence of a multi-system capability in a pager demands some sort of prioritizing to insure proper function when more than one system can be detected by the pager.

The prior art signal processing circuitry for pager communication devices generally comprise custom integrated circuits or custom hybrid circuits which perform the specific high speed decoding functions for a single signal decoding system. A multi-system pager by utilizing the present IC and hybrid decoding technology is prohibitive from the view of cost, design complexity and power consumption. In addition, there exist present and proposed pager communications systems which, because of total unit market volume, could not support the initial tooling and engineering costs associated with the development of the custom circuitry presently required and are therefore prevented from being established. However, the economy offered by a multi-system pager would make it possible to profitably manufacture relatively small numbers of single system pagers by adapting a high unit volume, multi-system pager to decode one specific decoding scheme.

A critical requirement for any signal decoder for a paging system is that it must process signals in real time so that decoding does not fall so far behind that information is lost. The concept of real time processing is well known in the art and is associated with the actual time during which physical events take place. With respect to real time signal processing by a decoder, the operations performed by the decoder which relate to a detection and decoding process must be sufficiently rapid so that the results obtained are useful in controlling the device without the loss of information. Thus the operational speed of a multi-system decoder which is to perform digital signal processing is directly related to the information rate at which the pager communication system operates. The digital information transmission rate may vary from system to system and it is clear that faster rates are preferred because more information may be handled by an entire system in a given unit of time. Clearly, the faster the information rate the greater the processing speed demand on a multi-system decoder.

The high clock rate for a multi-system decoder performing signal processing in real time increases both the voltage required and power consumed by the system and thus can adversely affect the operating economics of a pager and could affect both the size and weight of the device. In general, the greater the power consumption, the larger the mass of the batteries which must be carried to provide for the operation.

GB-A-2024567 describes a digital display pager which has a display device for caller identification and other purposes, and which is controllable by a single multi-position slide-push switch. The display device is actuated for power saving only when the page storage is interrogated.

US-A-4,181,893 describes a battery saver circuit for a tone coded personalized radio pager device which controls the supply of power to the receiver apparatus 12.

### 35 Summary of the Invention

The present invention provides a portable communications system message receiving device as defined in claim 1.

In one preferred embodiment, the device has a multi-scheme signal decoding capability for portable applications such that it is capable of processing a detected signals in accordance with any one of a plurality of decoding schemes. Coding scheme selection means may be provided, coupled to the receiver and the decoder, and responsive to predetermined characteristics of the detected encoded signals for selecting which of the plurality of decoding schemes will be utilized for processing the detected encoded signals. A code memory, coupled to an accessed by the decoder, contains information corresponding to each one of the plurality of decoding schemes including a predetermined sequence of encoded signals in the selected scheme, the reception of which will cause an individual decoder to respond by signalling. The decoder has an equivalent embodiment which comprises a microcomputer.

A code memory is preferably provided, coupled to and accessed by the decoder, containing predetermined information, the reception of which will cause an individual decoder to respond by signalling. The decoder has an equivalent embodiment which comprises a microcomputer.

### Brief Description of the Drawings

The invention itself together with its further objects and advantages thereof, may be best understood by reference to the following description, when taken in conjunction with the accompanying drawings, in which:

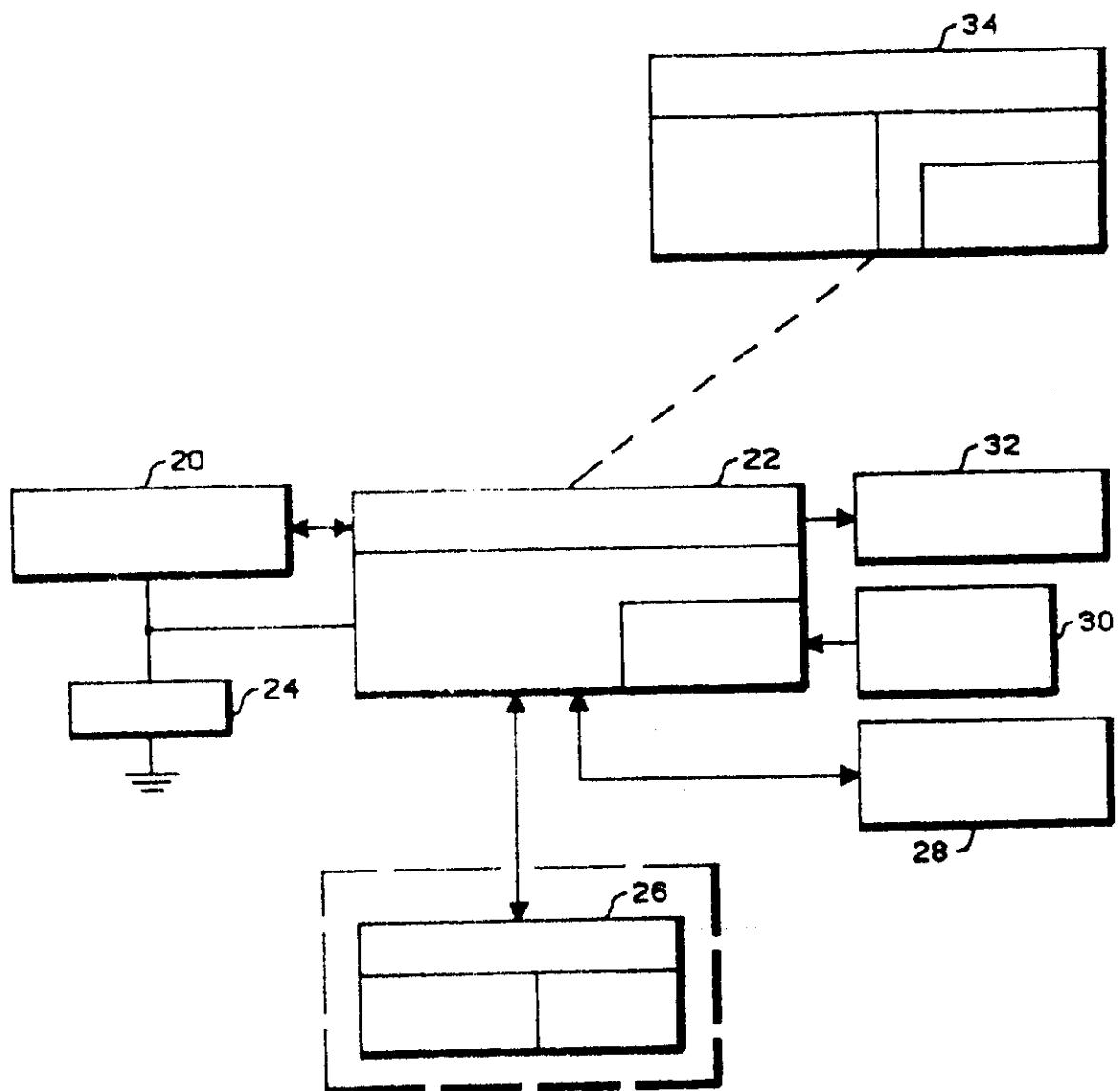

Fig. 1 is a functional block diagram of the present invention showing equivalent preferred embodiments.

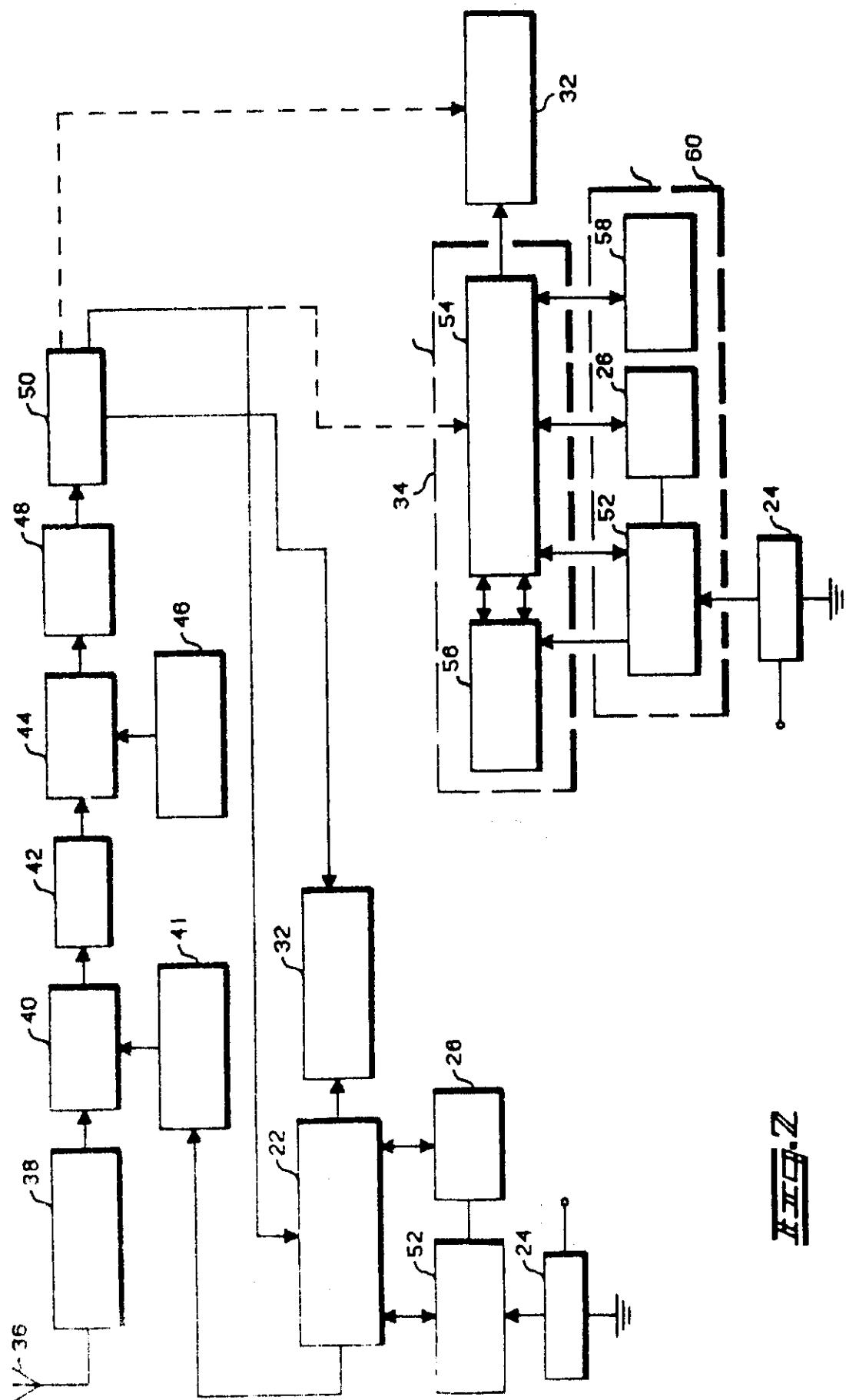

Fig. 2 is a more detailed functional block diagram of the present invention showing equivalent preferred embodiments.

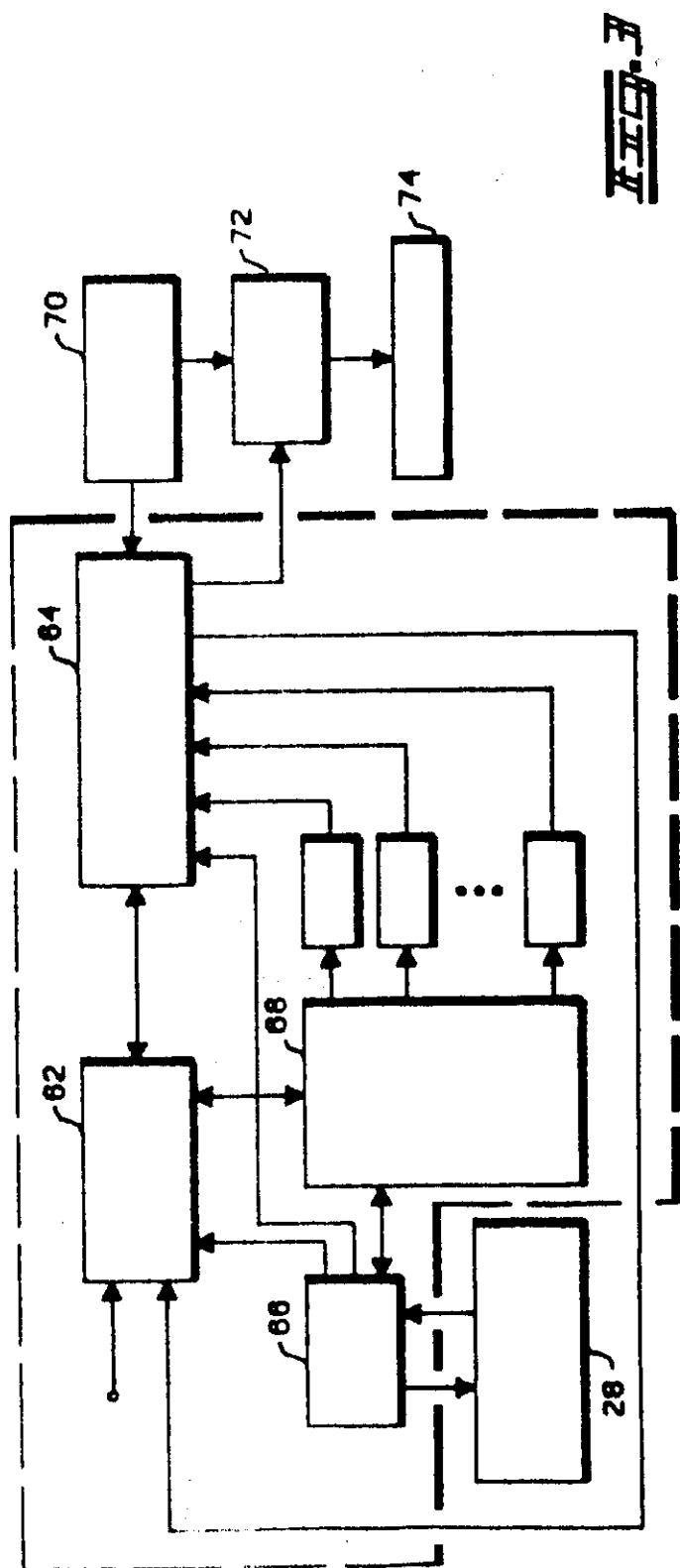

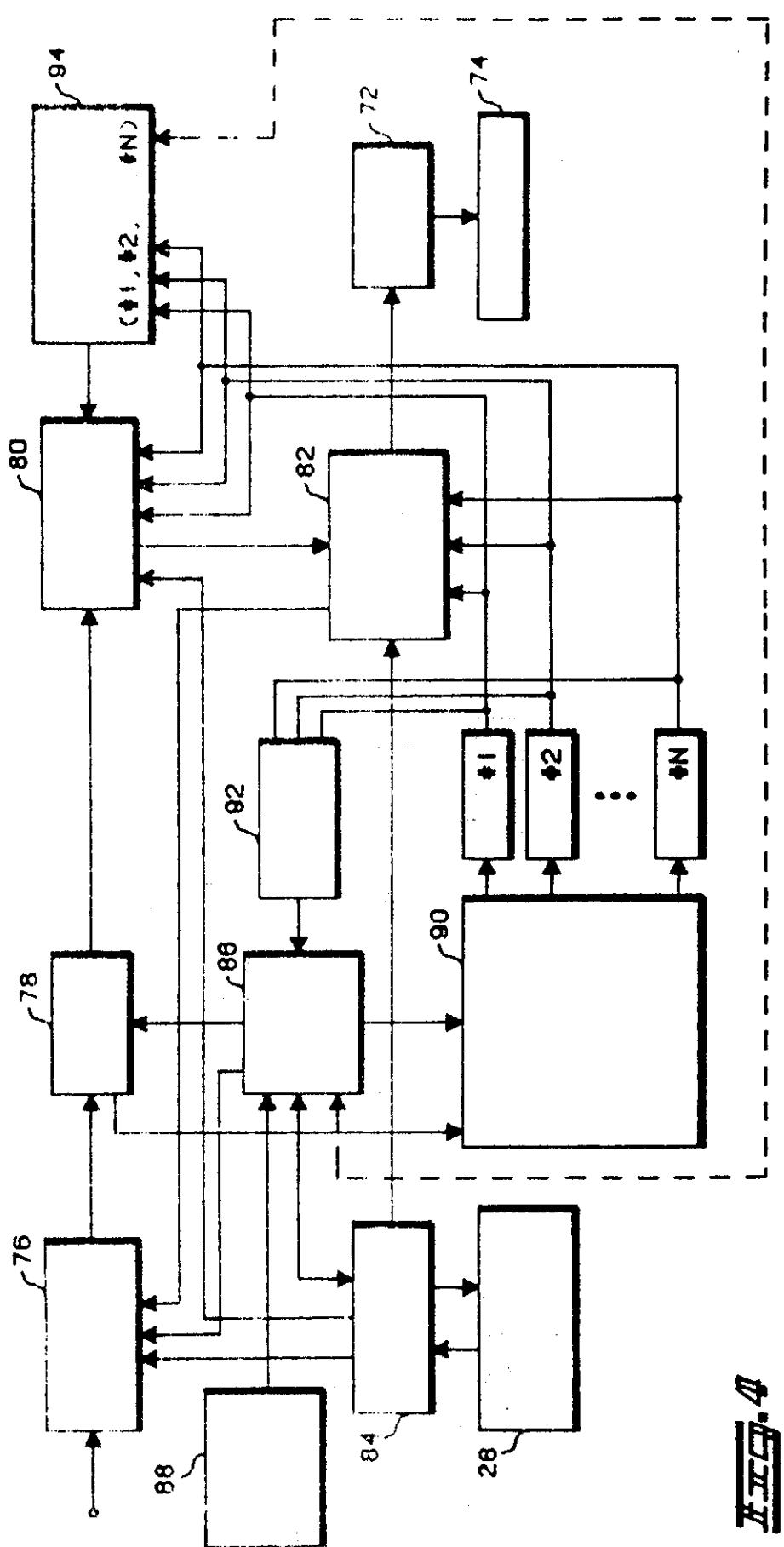

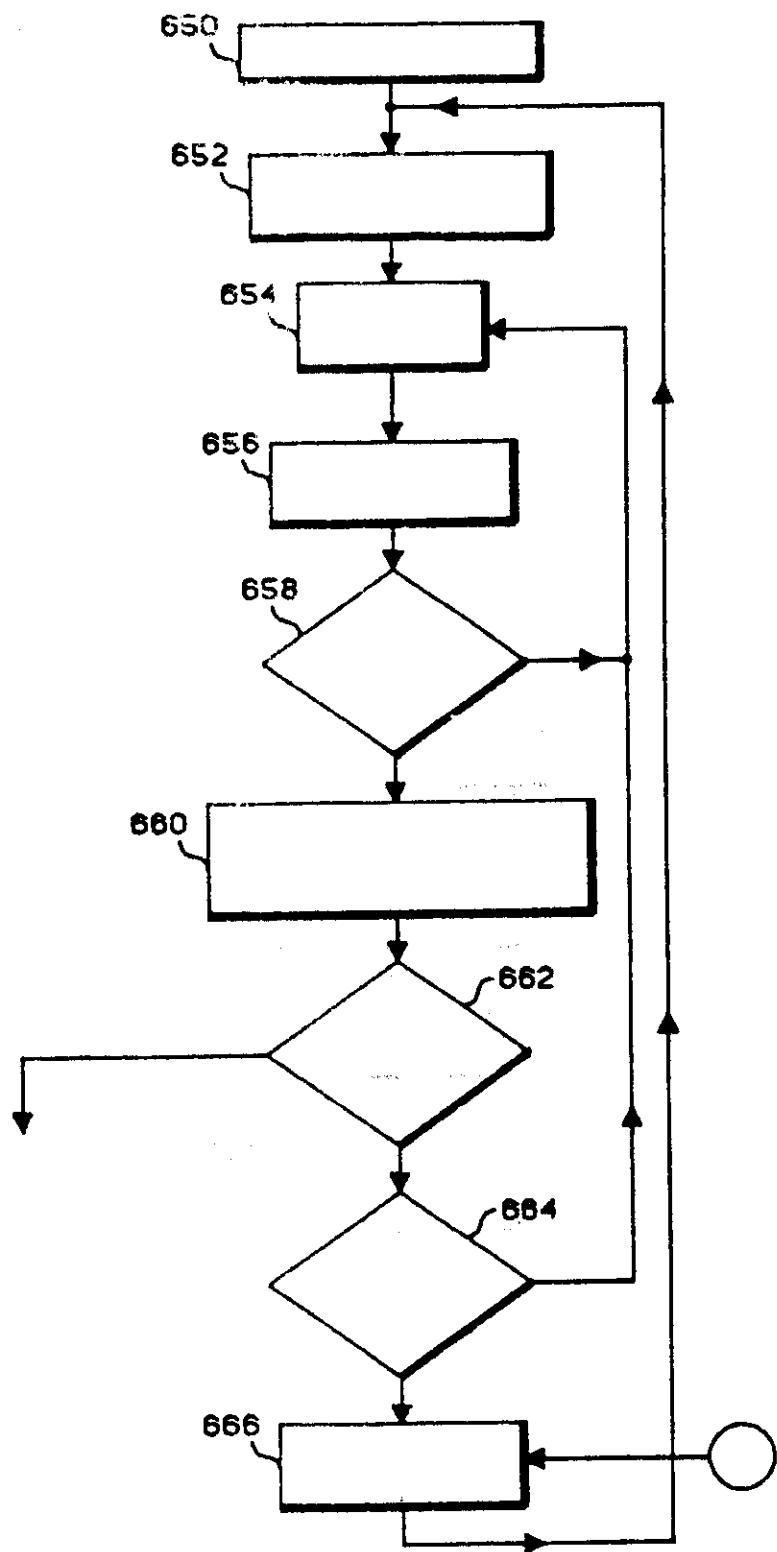

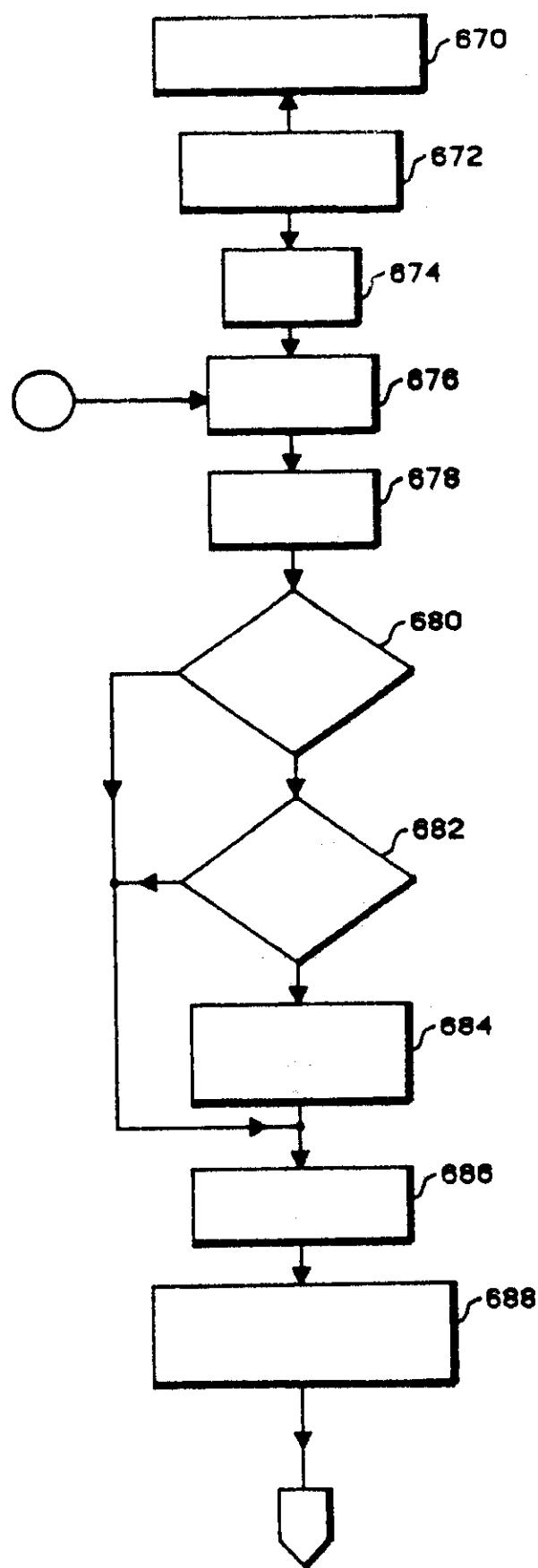

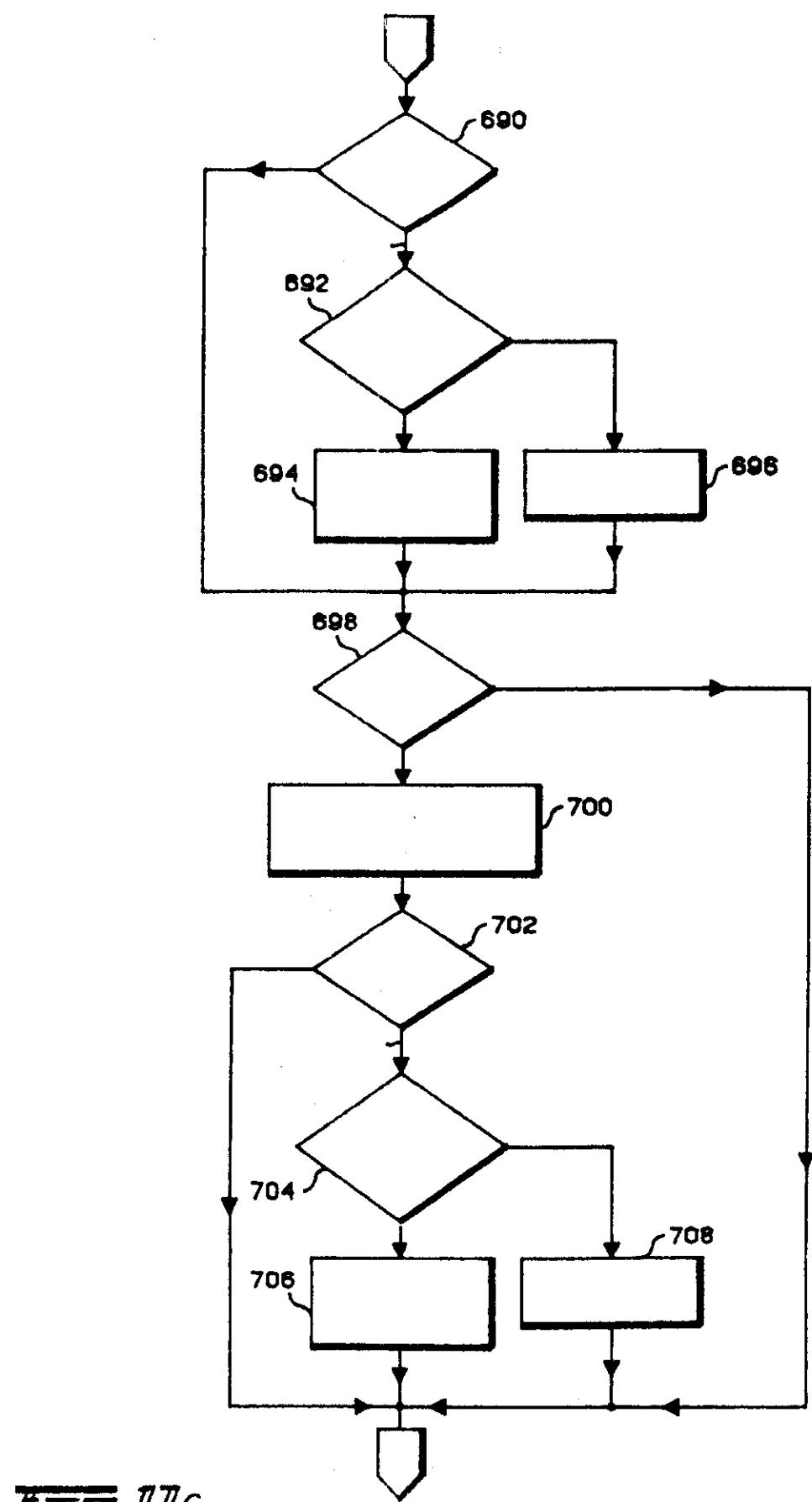

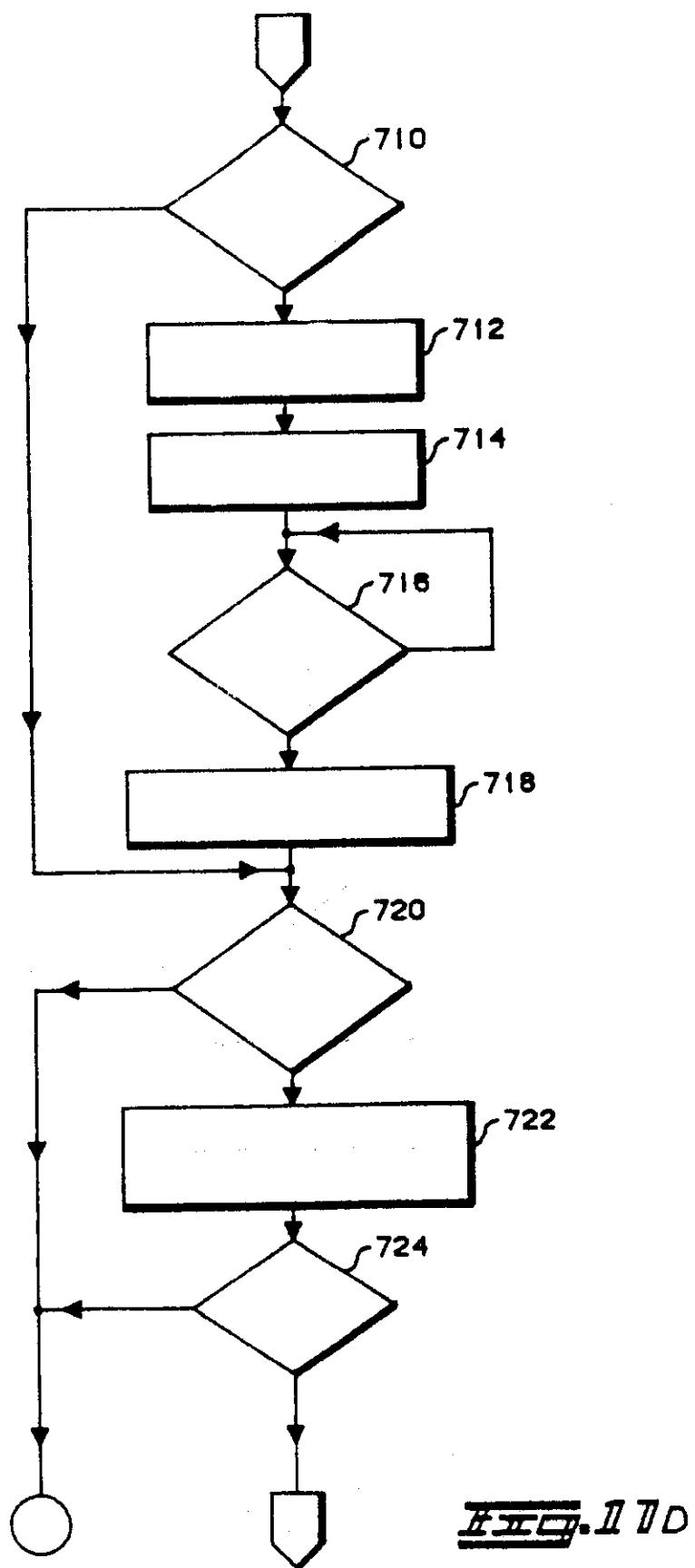

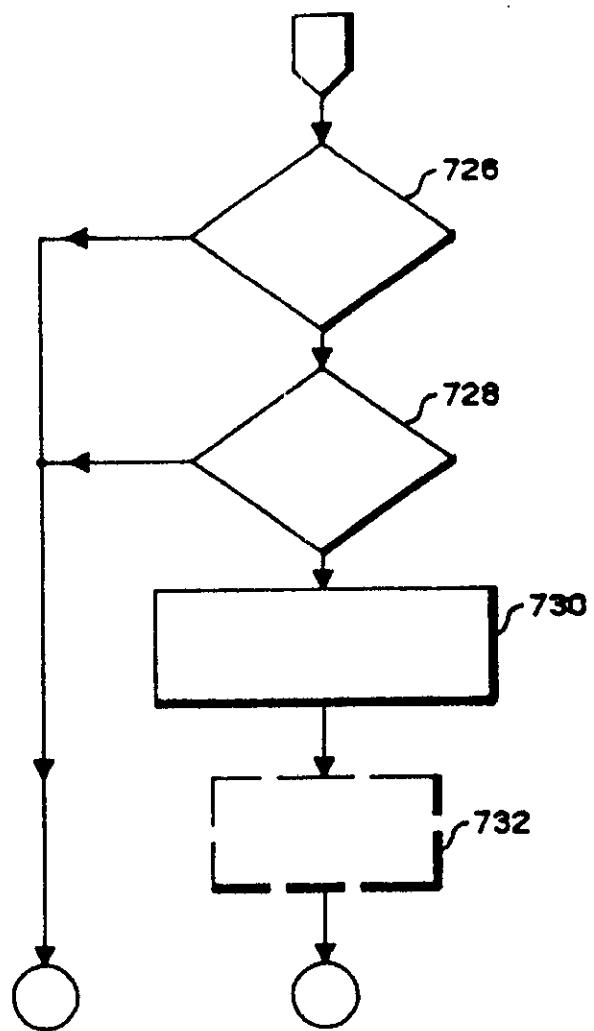

Fig. 3 is a functional block diagram showing the common infrastructure of the preferred embodiments. Fig. 4 is a more detailed block diagram of the common functional infrastructure of the preferred embodiments. Fig. 5 is a combination functional and schematic diagram of the microcomputer embodiment of the invention. Figs. 6A, 6B and 6C comprise a descriptive diagram for one of a first data encoding systems for the preferred embodiments of the invention. Figs. 7A and 7B comprise a descriptive diagram for the second data encoding system for the preferred embodiments of the invention. Fig. 8 is a detailed functional diagram of the common infrastructure of the preferred embodiments. Fig. 9 shows an electrical schematic for the equivalent data sampling and sequencing operations of the preferred embodiments. Figs. 10A through 10J show various timing diagrams for the operation of the schematic of Fig. 9. Figs. 11A and 11B show the detailed electrical schematic of a multiplexer portion of the schematic of Fig. 8. Figs. 12A through 12M show various timing diagrams for the schematic of Figs. 11A and 11B. Fig. 13 shows the detailed electrical schematic for the Exclusive OR array portion of Fig. 8. Fig. 14 shows the detailed electrical schematic for the adder/accumulator portion of Fig. 8. Fig. 15 shows the detailed electrical schematic for an error comparator portion of Fig. 8. Figs. 16A and 16B show a detailed schematic for the bit rate detection portion of Fig. 8. Figs. 17A through 17E comprise a detailed flowchart of the microcomputer implementation of the preferred embodiments of the invention.

#### Description of the Preferred Embodiments

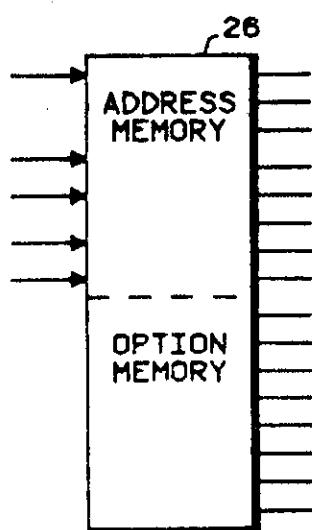

Fig. 1 shows a functional block diagram applicable to both a first and second embodiment of the present invention. A communication receiver 20 is connected to an adaptive signal decoder 22. Decoder 22 contains a region designated Decoding Schemes which serves to indicate that it contains information to decode more than one decoding scheme. A battery 24 is shown connected to communication receiver 20 and decoder 22. Decoder 22 is additionally connected to a code memory 26 shown enclosed with a broken line. Code memory 26 further contains regions designated Function Select and Pager ID. The enclosure of code memory 26 with a broken line indicates the possibility that such a device can be made removable and therefore separable from the rest of the system. Also interconnected with decoder 22 is an energy conservation means 28. A decoding selection means 30 is coupled to the Decoding Schemes region of signal decoder 22. An output of signal decoder 22 is coupled to an annunciation transducer 32.

A microcomputer 34 is shown interconnected with adaptive signal decoder 22 by a broken line. This interconnection indicates that adaptive signal decoder 22 may be replaced entirely by microcomputer 34. Microcomputer 34 is shown to be further comprised of a microprocessor and a read-only memory, with the read-only memory portion including a section designated as Decoding Schemes. Microcomputer 34 will have the identical interconnections as does decoder 22. The replacement of adaptive signal decoder 22 by microcomputer 34 would also provide the exact same signal decoding functions and the resulting system function would be indistinguishable to a pager user. Thus, the function of the two alternative embodiments are indistinguishable within a device.

The operation of the system shown in Fig. 1 is such that the communication receiver is capable of receiving messages in any of several message formats. Adaptive signal decoder 22 responds to the received signals to analyze the data and select one of several decoding schemes for appropriately decoding the incoming information received by communication receiver 20. As with all paging devices, the resulting decoded signal is tested for comparison with a designated pager address contained in code memory 26. Upon detecting correspondence between the received and decoded signal and the address in code memory 26, an output signal is produced indicating to the pager carrier that a message has been received. In particular, the output signal from decoder 22 is supplied to annunciation transducer 32 to produce a signal indicative of the receipt of a message.

Because of the requirements for high speed, real time adaptive signal decoding and the requirement of preserving and extending the useful life of the battery contained in a paging device, energy conservation means 28 functions in cooperation with adaptive signal decoder 22 to conserve battery 24. It may also be appreciated that decoding selection means 30 provides an exterior selector to the pager operator to designate only some of the possible decoding schemes. This selective function may also be supplied by the code memory or may be factory preset independently of the code memory. It may also be appreciated

that code memory 26 may contain several addresses, each one corresponding to the appropriately selected decoding scheme which is determined by the decoder 22 in response to the signals received by receiver 20.

5 In addition, code memory 26 includes a function select region which is used to select the various features of the pager device. It is advantageous to build in the circuitry for all functions and then provide information in code memory 26 which identifies the address of the pager and designates various combinations of the possible function and annunciation features of the system.

10 The replacement of adaptive signal decoder 22 by microcomputer 34 containing its microprocessor and the decoding schemes contained within the read-only memory region provides the same diagram with block 22 removed and replaced in its entirety by block 34. The difference is in the internal function of the microcomputer in that, instead of the hardware adaptive signal decoder responding to the received communication signal, the microcomputer uses a microprocessor for processing the received signals in real time according to the same predetermined search routine. After identification by the same process, the microprocessor accesses the Decoding Scheme region of the read-only memory to determine the correct 15 instructions contained in that memory for processing the decoding scheme. The microprocessor will access the code memory just as the adaptive signal decoder does and will respond to the external decoding selection means.

20 Again, the energy conservation means interacts with the microprocessor and ROM to conserve the battery for the system. When the microprocessor has detected the reception of a signal which corresponds to a pager identification contained in the code memory, microcomputer 34 connects with annunciation transducer 32 to produce a signal so that the pager carrier is made aware that a message has been received in one of the possible decoding schemes. For either the decoder or microcomputer, the form of the alert signaling pattern provided to the pager carrier may be a function of which of the various decoding 25 schemes is detected. The decoding scheme may provide for both emergency and non-emergency calls with corresponding signals supplied to the annunciation transducer so that the pager carrier receives a distinct signal and can respond accordingly.

25 Fig. 2 shows a more detailed block diagram of the embodiments of the present invention. An antenna 36 is connected to a radio frequency amplifier and selectivity device 38 which is connected to a first mixer 40. A first oscillator 41 is also connected to first mixer 40. The output of first mixer 40 is coupled through filter 42 to a second mixer 44. A second oscillator 46 is also connected to second mixer 44. The output of second mixer 44 is connected through an intermediate frequency (IF) gain device 48 to a detector 50. The first portion of Fig. 2 comprises a more detailed description of communication receiver 20.

30 The output of detector 50 is connected to adaptive signal decoder 22. Signal decoder 22 is connected to first oscillator 41. As in Fig. 1, the output of adaptive signal decoder 22 is connected to annunciation transducer 32. Detector 50 is shown connected to annunciation transducer 32 which is a normal connection for tone and voice paging system. Battery 24 is shown as providing power to the communication receiver and is also connected to a DC to DC converter 52. DC to DC converter 52 is also interconnected with adaptive signal decoder 22 and with code memory 26. Code memory 26, as before, is interconnected with decoder 22.

35 Fig. 2 shows in phantom line the complete replacement of the adaptive signal decoder 22 with the corresponding microcomputer 34 and peripheral devices. In particular, microcomputer 34 is shown as comprised of a microprocessor 54 multiply interconnected with a read-only memory 56. Read-only memory 56 is interconnected with DC to DC converter 52. Microprocessor 54 is interconnected with DC to DC converter 52 and with code memory 26. Code memory 26 and DC to DC converter 52 are also 40 interconnected. Microprocessor 54 is also shown interconnected with a deadman timer 58. The three peripheral devices, the DC to DC converter 52, code memory 26 and deadman timer 58, are shown 45 interconnected by a broken line and are designated as a support module 60. Although not shown when microcomputer 34 replaces decoder 22, first oscillator 41 is connected to microprocessor 54. Detector 50 is shown connected in phantom with annunciation transducer 32 as is customary for tone and voice page 50 systems. Battery 24 is shown connected with DC to DC converter 52 as before and supplying power to the communication receiver portion.

55 As is customary with radio receivers, the antenna receives a radio frequency signal which is suitably amplified and selected. Using a superheterodyne technique, the first local oscillator 41 beats with the incoming signal frequency in mixer 40 the output of which is supplied to filter 42. The output of filter 42 is supplied to a second mixer 44 where the signal is mixed with the output of second oscillator 46 and the output supplied to the intermediate frequency gain circuit 48. The output of the gain circuit 48 is supplied to

detector 50 which recovers the encoded signal from the modulated IF output. While a specific super-heterodyne radio system has been described, it should be apparent to those skilled in the art that many other forms of communications receivers may be utilized.

The detector output is supplied to the adaptive signal decoder which may include multi-scheme decoding. The adaptive signal decoder is adaptive in the sense that it performs various characteristic measurements upon the incoming signal in an effort to identify which of several possible schemes should be applied for decoding. When a suitable scheme has been identified, the data is then decoded according to that format and the code memory is interrogated to see if the paging device has been addressed. In the event that the paging device has indeed been addressed, annunciation transducer 32, as before, produces a detect signal to the pager carrier.

It has been tacitly assumed that the various decoding schemes would all function on the same communications channel. The multi-scheme decoding of adaptive signal decoder 22 includes searching and detecting paging message schemes which may not operate at the same frequency. The function of the control line from decoder 22 to first oscillator 41 is to show that decoder 22 can, by the well-known process of frequency synthesis, control the frequency at which it receives signals for decoding. Consistent with the equivalent function of the embodiments, the same control can be exercised by microcomputer 34. Thus the multi-scheme decoding encompasses a plurality of different decoding schemes operating at different frequencies.

The battery 24 is interconnected through a DC to DC converter which supplies power to the adaptive signal decoder 22. The DC to DC converter is also responsive to the adaptive signal decoder 22 and comprises the energy conservation means. When the adaptive signal decoder identifies the decoding scheme it also specifies those periods during which full power may not be required to determine if the pager has been addressed. Such time periods are established by the organization of the message scheme transmission format. Moreover, the DC to DC converter can provide any additional voltage necessary to operate the adaptive signal decoder at higher voltage levels to support the high speed real time operation.

For the second embodiment of Fig. 2, as in Fig. 1, adaptive signal decoder 22 is now entirely replaced with microcomputer 34 and the interconnected peripheral devices. The DC to DC converter 52 supplies power to read-only memory 56 and is responsive to microprocessor 54. Again, according to the determined coding scheme, at various times appropriate for the message formatting of the detected coding format, DC to DC converter 52 can reduce the power supplied to the system thereby conserving the battery energy. Deadman timer 58 functions to ensure that there are no runaway execution conditions. In particular, microprocessor 54 is designed to provide a signal to deadman timer 58 on regular intervals. In the event that the deadman timer does not receive these signals at regular intervals, it will force a reinitialization of the program routine in microprocessor 54 to cause initialization of the searching to identify the decoding scheme being received.

The detected signals will also be processed according to the detected decoding scheme and the resulting information compared with the pager address information contained in code memory 26. The functioning of the signal detection device whether it contains a microcomputer or an adaptive signal decoder is completely indistinguishable from the point of view of the pager carrier.

Fig. 3 shows a block diagram corresponding to Fig. 1 emphasizing the common functional infrastructure of adaptive signal decoder 22 and microcomputer 34. This diagram is equally applicable to both the hardware adaptive signal decoder system and the firmware microcomputer system of the two embodiments. The signal from detector 50 of Fig. 2 labeled Input is applied to a data and sampling storage circuit 62. The output of the data sampling and storage circuit 62 is supplied to a data sequence window comparator 64. The data sampling circuit receives timing signals from a clock 66 which is capable of supplying multiphase clock timing signals. Clock 66 also supplies timing signals to a coding system search and detect circuit 68. Data sampling and storage circuit 62 is interconnected with coding system search and detect circuit 68. The output of coding system search and detect circuit 68 is a plurality of signals, each one of which designates that one of the several possible decoding systems has been detected. These signals are connected to data sequence window comparator 64 so that the proper decoding may proceed. Data sequence window comparator 64 is also connected to clock 66. Clock 66 is also interconnected with coding system search and detect circuit 68. Energy conservation means 28 is interconnected with clock 66 to provide periods of lessened power drain.

Data sequence window comparator 64 is connected to a pager address circuit 70 which is normally contained in code memory 26. The output of data sequence window comparator 64 is coupled to an alert pattern circuit 72. Alert pattern circuit 72 is connected to be responsive to pager address circuit 70. The output of alert pattern circuit 72 is connected to an annunciator device 74 which corresponds to annunciation transducer 32 previously described.

When detector 50 (Fig. 2) contained in the communication receiver provides an input to the data sampling and storage circuit 62, clock 66 provides for sampling the data in a regular pattern as will be shown and described in more detail later. At the time the data is received, a decoding system search routine is initiated to determine, based on the characteristics of the detected code, which of the several possible decoding schemes should be utilized for decoding the data. This is accomplished by applying the various parameters to the detection system corresponding to each of the possible systems and testing the data for identifying characteristics. Once the decoding system has been identified, the proper limits are applied to data sequence window comparator 64 and the sampled and stored data is then appropriately processed to decode the information. An advantage of the technique of sampling and storing the data is that little if any sampled data is lost during the scheme identification process so that a high degree of confidence may be maintained in determining whether the pager has been addressed. Moreover, this process occurs in real time so that all of the received data may be used to both confirm the decoding system received and to apply the decoding to the detected signal to ascertain whether or not the pager has been addressed. The output of the data sequence window comparator 64 is fed back to data sampling and storage circuit 62 to initiate taking additional samples or to continue the sampling technique according to the scheme of the detected coding system.

The function of the interconnection between data sequence window comparator 64 and data sampling and storage circuit 62 is to continue sampling where necessary according to the selected scheme. This may be two or more sequential address words or it may be additional batches of encoded signals which must be processed according to the position of a signal within a batch of coded messages. For single address word systems the interconnection would not be utilized.

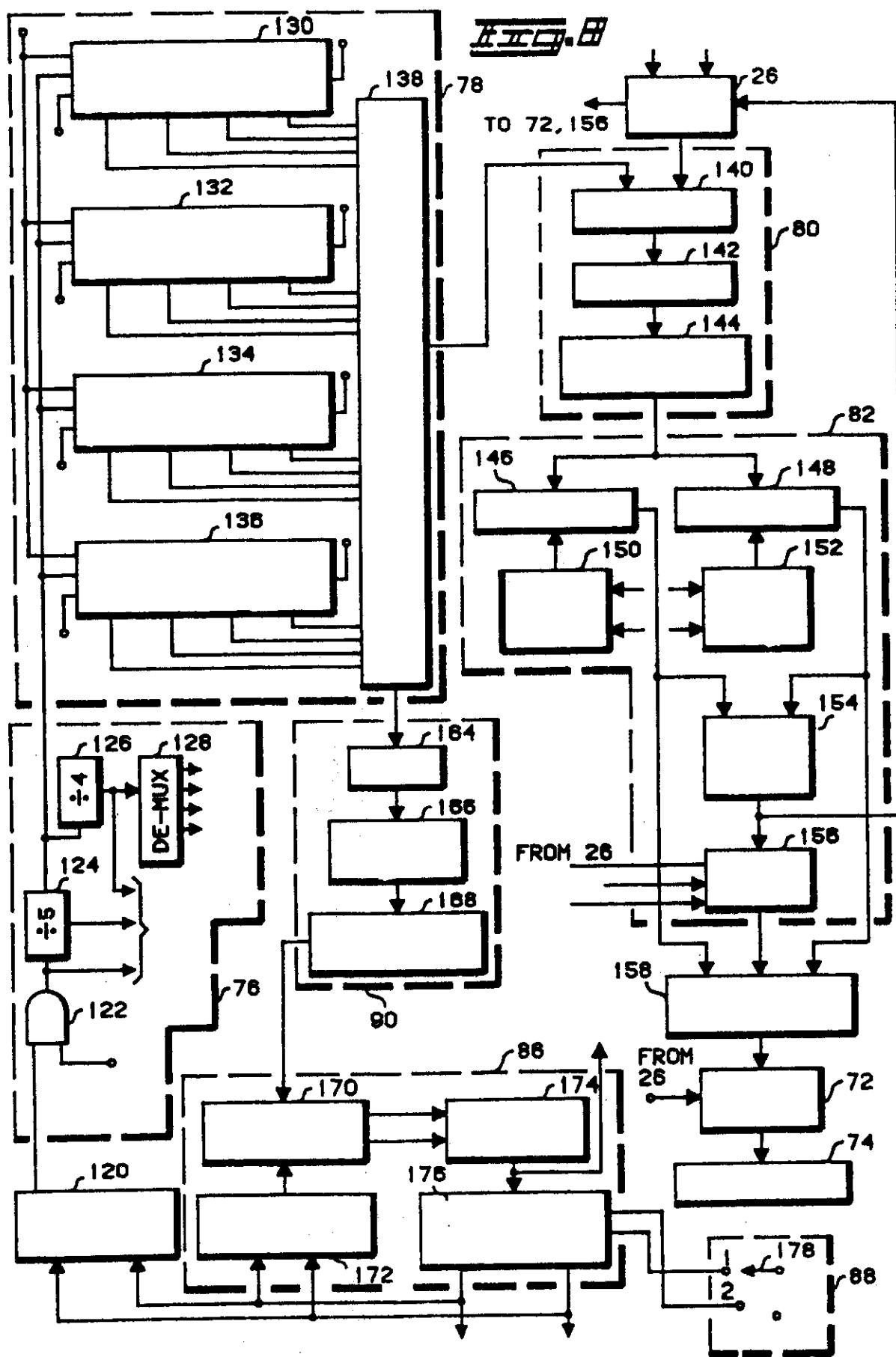

Fig. 4 shows, in additional detail, the diagram for either system containing an adaptive signal decoder or microcomputer and includes the interconnection of an external selector similar to the decoding selection means 30 shown in Fig. 1. An input signal which is the output of detector 50 is applied to a data sampling and sequencing circuit 76. The output of data sampling and sequencing device 76 is supplied to a sample storage device 78. Data sampling and sequencing device 76 and sample storage 78 comprise the data sampling and storage block 62 shown in Fig. 3. The output of sample storage device 78 is supplied to a data sequence comparator 80 which is also connected with a comparator error window limit device 82. The data sequence comparator 80 and comparator error window device 82 comprise the data sequence window comparator 64 of Fig. 3. A multiphase clock 84, which corresponds to clock 66 in Fig. 3, supplies timing signals to data sampling and sequencing device 76 and to data sequence comparator 80. Multiphase clock 84 is also interconnected with energy conservation means 28 to allow for reduced operation periods of the system to conserve battery energy.

Multiphase clock 84 is also interconnected to a coding systems search control 86, which is also connected to be responsive to an external system subset selector 88. Coding systems search control is connected to data sampling and sequencing device 76 and sample storage device 78. An additional output of coding systems search control 86 is connected to a systems characteristic detector 90 which is also connected to sample storage device 78. The outputs of system characteristic detector 90 are a series of lines indicative of the detection of and identification of one of the several possible decoding systems. Shown are N lines indicating system 1, system 2 through system N. Each of the outputs of system characteristic detector 90 is connected through a priority control device 92 to provide an input signal to coding systems search control 86. The outputs of system characteristic detector 90 are also supplied to the inputs of comparator error window limit device 82, to data sequence comparator 80 and to a pager address memory 94. The output of comparator error window limit device 82 is connected to alert pattern circuit 72 which is connected to annunciator 74. Alert pattern circuit 72 is connected to be responsive to pager address memory 94. Pager address memory 94 is shown interconnected by a broken line to coding systems search control 86. An additional output of comparator error window limit 82, labeled as a signal Next Word, is supplied to data sampling and sequencing device 76.

When the pager decoding system is actuated, the various parameters for one of the possible coding system are inserted into the various registers and counters, and the input signal to data sampling and sequencing device 76 from detector 50 is sampled according to a corresponding predetermined time sequence. The samples are stored for processing by data sequence comparator 80 and for analysis by the coding systems search control 86. The function of coding systems search control 86 is to organize the temporarily stored data for processing by the system characteristic detector 90 to determine from the received information the selected one of the several possible decoding schemes which should be employed to decode the received data. In the event that a wrong choice has been made, new parameters of the next coding system are input and another decoding system tested.

When system characteristic detector 90 activates one of the output lines indicating that the system has been detected, priority control 92 is actuated to disrupt the normal searching operation of coding systems search control 86 and to lock into the detected decoding system until such time as a message is received addressing the paging device or until it is determined that no more information is being received in that system. At such subsequent time, coding systems search control 86 will resume its searching operation to scan the incoming signals for the occurrence of messages broadcast in any of the possible decoding systems.

The output of system characteristic detector 90 is also supplied to comparator error window limit device 82 to alter the acceptable error limits for the various decoding systems and to pager addresses memory 94. The data in data sequence comparator 80 is tested for the window limits in comparator 82 with the proper pager address corresponding to the detected coding system. Comparator error window limit device 82 provides an output signal to alert pattern 72 and to actuate annunciator 74 to signal the pager carrier that a message has been received. A signal from pager address memory 94 determines which signaling pattern is supplied by alert pattern circuit 72 to annunciator 74.

Since several of the systems have sequential word coding formats or have multiple batch coding formats, there is an output from comparator error window limit device 82 back to the data sampling and sequencing device 76. This signal is labeled Next Word and provides additional sampling to decode the next serial word or for the next batch of messages within a given system.

The functioning of external system subset selector 88 is to eliminate searching through all possible coding systems and limit that search to only those systems which are receivable within a specific area or those systems to which the pager operator chooses to respond at any given time. It should be clear that this restriction may be provided by code memory 26 or could be independently hard-wired at the time of manufacture. This allows full flexibility for the pager to decode any of the N possible decoding systems and for the pager carrier to override the maximum number of possible decoding systems and concentrate his responses only to selected systems.

It may be appreciated that code memory 26, shown connected in phantom, can affect the coding systems search control as the code memory itself may contain certain limitations on which coding systems are accessible by the search control 86. This, in combination with the enabling of various functions of the pager, gives a complete versatility to a product line. Pager address memory 94 is also shown interconnected in phantom to coding systems search control 86. This line shows that control 86 can access the address words of the individual pager within each of the possible encoding systems.

It should be clear that when a pager is manufactured, or the time that the firmware is established, the pager address in various systems would ordinarily not be the same and to maintain uniqueness each pager unit must have a different address. Therefore, it is advantageous to subsequently designate several pager addresses corresponding to the various possible decoding systems. In addition, certain message systems use multiple addresses so that different types of signaling functions may be supplied to the carriers of their paging devices. An example would be a pager having two distinct addresses, the first designating an emergency message with a corresponding alert signaling pattern and a second indicating a non-emergency message with a substantially different alert signaling pattern.

Consistent with this type of operation, both embodiments of the present invention allow full capability to have several designated addresses within each of several possible decoding systems. Moreover, as has been described, the code memory or factory setting can restrict the availability of the functioning of the systems search routine which would reduce the number of decodable systems available to the carrier of a paging device.

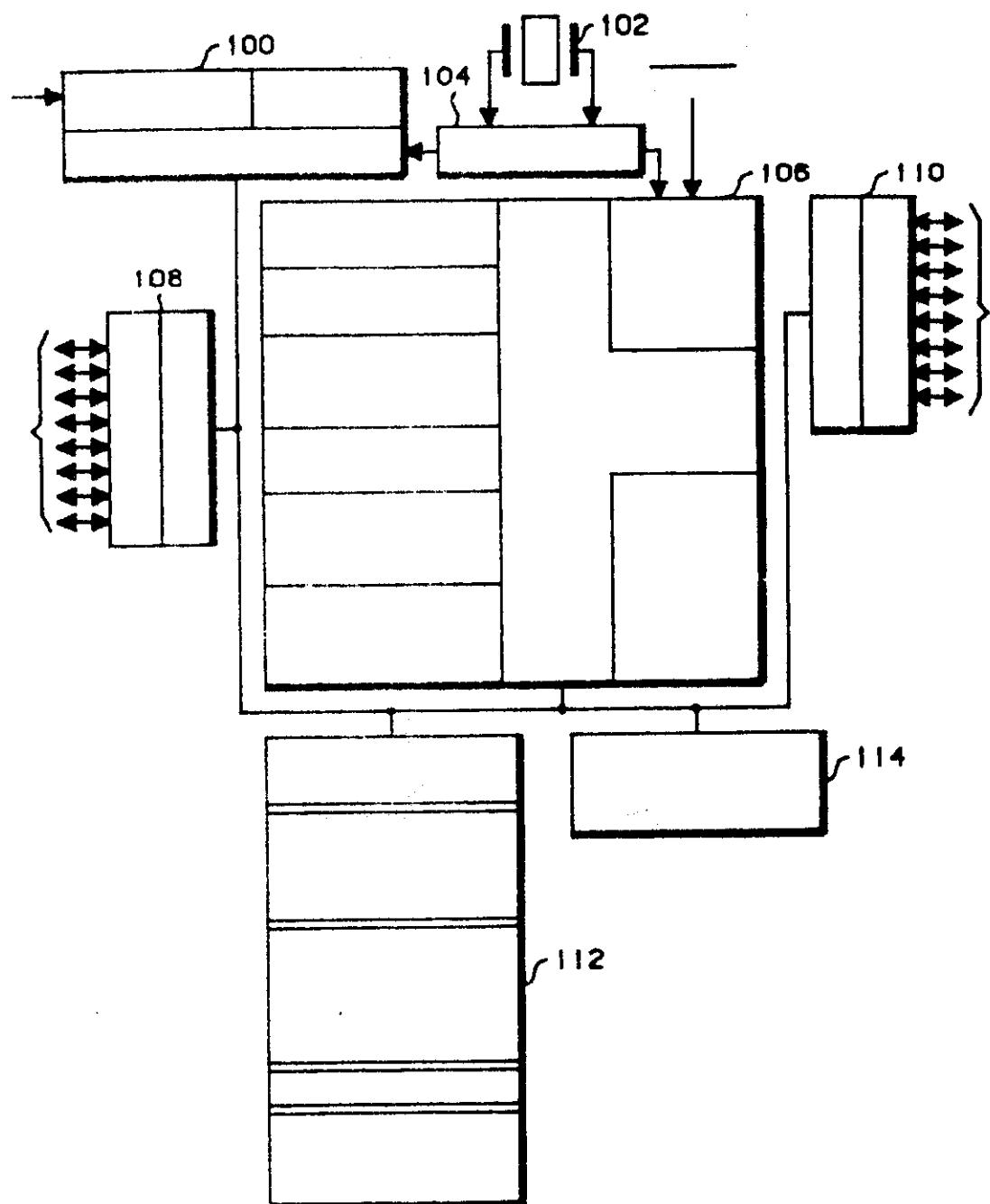

Fig. 5 shows a combination functional and schematic block diagram of a microcomputer of the type suitable for containing a firmware implementation of the functional block diagram of the multi-scheme decoding pager having energy conservation shown as one embodiment in Figs. 1-4. Although the microcomputer embodiment should not be so limited, it is preferred that the microcomputer be of the Motorola 146805 type. A timer signal for actuation is supplied to a timer control unit 100 containing a prescaler and a timer and counter. A crystal 102 is coupled to an oscillator circuit 104 which is also connected to timer control 100.

Oscillator 104 is also connected to a central processing unit 106 which contains the central processing unit control circuit, an arithmetic logic unit designated ALU, an accumulator, index register, condition code register, stack pointer, program counter high and program counter low modules. Also connected to the central processing unit are data directional input/output registers 108 and 110 having a plurality of input/output lines. In particular, eight lines are shown for each of two input/output parts. Also interfacing with the central processing unit are a read-only-memory (ROM) 112 and a random access memory (RAM) 114. As is characteristic of the Motorola 146805 family, the on-chip RAM permits the microcomputer to operate

without an external RAM memory. The parallel input/output capability includes programmable pins indicating whether it is to be an input or an output. The timer/counter is normally an eight bit counter with a programmable prescaler which can be used as an event counter to generate interrupt signals at certain software-selected events or can be used for timing keeping. In the case of the Motorola CMOS version 5 MC146805, this timer can be set to wake up the microprocessor from a software-actuated command to establish a power-saving wait mode.

Fig. 5 also shows the arrangement of major firmware modules stored in the ROM and the corresponding addresses at which the modules begin. The choice and arrangement of this module is a function of the specific program of one of the embodiments of the present invention. It is sufficient to describe the major 10 program modules and their address origination points so that with the core dump of the operating software program for the alternative embodiment, one can ascertain where the various subroutines begin. The use of RAM 114 is principally to contain variables accessed during the program and as a scratch-pad storage. The use of the Motorola 146805 is not a necessary requirement for the alternative embodiment, however, it is a convenient one. All of the subsequently disclosed coding is written to be compatible with the 146805 coding 15 format.

The 146805 microprocessor and its associated architecture and internal instruction set have been described in detail in the following filed U.S. patent applications: U.S. Serial No. 054,093, filed July 2, 1979, entitled "Low Current Input Buffers"; U.S. Serial No. 065,292, filed August 9, 1979, entitled "Method for Reducing Power Consumed by a Static Microprocessor"; U.S. Serial No. 065,293, filed August 9, 1979, 20 entitled "Apparatus for Reducing Power Consumed by a Static Microprocessor"; U.S. Serial No. 065,294, filed August 9, 1979, entitled "CMOS Microprocessor Architecture"; U.S. Serial No. 065,295, filed August 9, 1979, entitled "Incrementor/Decrementor Circuit"; and U.S. Serial No. 079,766, filed September 28, 1979, entitled "A Single Step System for a Microcomputer", all of the above six applications being commonly assigned to the assignee of the present invention. The six designated applications are hereby incorporated 25 by reference for a more complete description of the MC146805 microcomputer.

The microcomputer embodiment of the present invention functions in a manner which is identical to a hardware embodiment. Fig. 5 shows a specific implementation for the microcomputer embodiment. Although not shown, it should be clear that the signal from detector 50 is coupled to one of the input/output ports as are the code memory and the alert pattern device.

30 While the present invention may be applied to any number of pager coding schemes and message formats, for the purposes of describing the preferred embodiments, two subtly different systems have been selected. It will be clear to those skilled in the art how to combine additional systems using a coding system search control and a coding system characteristic detector to be described in greater detail later. One is a binary paging system employing asynchronous detection of serial address words of fixed length and 35 transmission rate. The other is a binary system employing synchronous transmission of fixed length truncated address words systematically arranged into fixed duration batches and transmitted at a different rate. For simplicity both systems employ binary coding which makes differentiation more difficult but the embodiments are more easily understood. It should be clear that any mixture of signal tones, tone and voice or digital signals may be combined. Such systems have such remarkably different characteristics that 40 differentiation between such systems is an easier task.

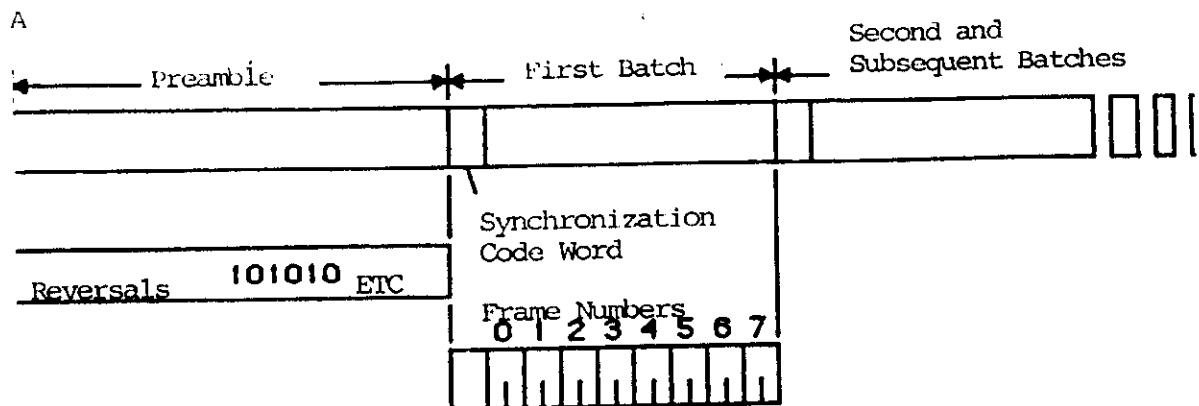

The standard message coding format for the national paging system of the British Post Office is 45 commonly known as POCSAG and has the following coding format. Each transmission is at a bit rate of 512 bits per second and consists of a preamble portion followed by one or more batches of selectively arranged code words. As shown in Fig. 6A, the preamble is a series of reversal logic states 1-0, etc. which has a duration of at least 576 bits. A code word is a 32 bit data sequence which contains information either for synchronization or for addressing an individual pager. Each batch begins with a 32 bit synchronization code word which is an invariant predetermined binary sequence. A batch comprises one synchronization code word and sixteen address code words which are subdivided into eight separate frames each containing two address code words. Subsequent batches in any message transmission contain the same format of a 32 bit 50 synchronization word followed by eight frames, each containing two address code words each for a total of 16 address code words in a batch.

The address code words are grouped into eight frames numbered 0 to 7. The entire pager address population is similarly divided into eight possible groups. Each pager address is allocated to one of the corresponding eight frames according to the three least significant bits of its 21 bit code word identity. 55 Thus, all pagers having addresses which end in 000 would be positioned in frame 0, and similarly, all pagers having an address code word ending in 111 would be in frame 7.

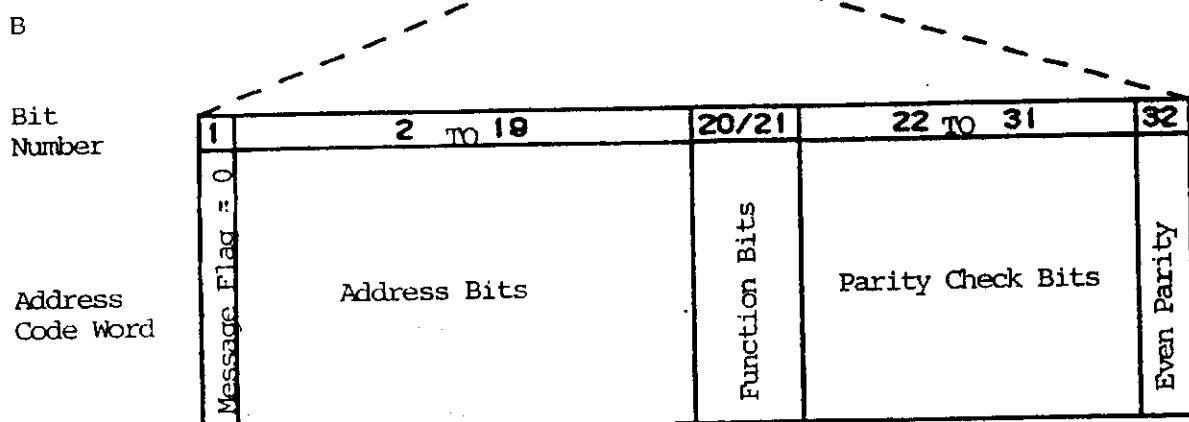

Address code words have a 32 bit structure and bit 1 of an address code word is always 0 as shown in Fig. 6B. Bits 2-19 are the address bits corresponding to the 18 most significant bits of the 21 bit identity sequence assigned to an individual pager. The three least significant bits are not transmitted since they merely serve to define the frame in which the address code word must be transmitted and are therefore derivable from the frame position in a batch. Bits 20 and 21 are two function bits which are used to select the required addresses from the four possible addresses assigned to the pager. Bits 22 to 31 are parity check bits and the final bit, bit 32, is chosen to give even parity. The decoding system will only examine address code words in a designated frame, and therefore, each pager's address code words must only be transmitted in the frame that is allocated to that code word format.

Each code word, whether it is a synchronization code word or an address code word, follows the same 32 bit format in which the most significant bit is transmitted first. The synchronization code word is shown in Fig. 6C with the most significant bit in bit position 1, and least significant bit in bit position 32.

Thus the 21 bit binary sequence for pager identity in this coding system allows for over two million combinations of possible addresses for pagers. The addition of two function bits provide a total of eight million message combinations comprising batch signaling functions and pager addresses.

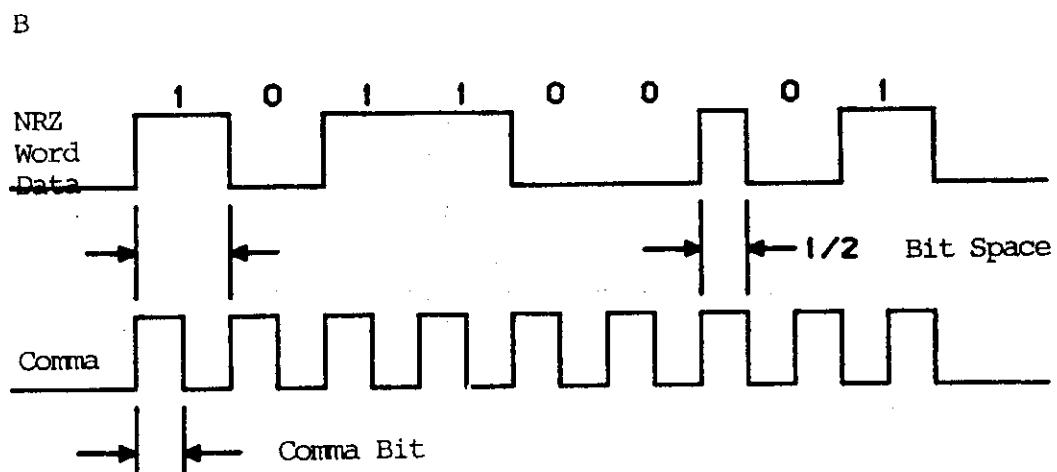

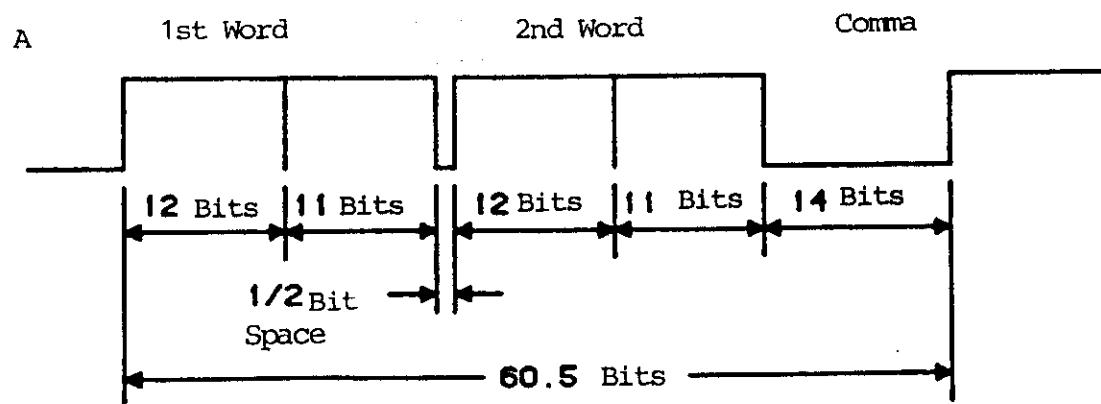

A binary message paging system developed by Motorola, Inc. and commonly known as ECHO transmits information at 300 bits per second and employs two sequential binary words for each pager address. A word for this system is a sequence of 23 binary bits. The logic convention used in this system requires that binary logic 1 correspond to the most positive voltage and that binary logic 0 correspond to the most negative voltage. As shown in Fig. 7A, each paging address in the ECHO system consists of two 23 bit binary words separated by a one-half bit interval and followed by a 14 bit duration comma. Two 23 bit paging address words follow each other serially to constitute the address of a pager and a comma or pause interval of a specified duration is transmitted between each pair of 23 bit addresses to form an interaddress gap. The total addressing data length is then 60.5 bits.

Each word of this dual-word addressing system is generated from 12 information bits. The sum of the information plus parity bits comprises the 23 bit word length. Parity bits are data bits which are added to the information bits to allow errors to occur and yet still ensure that one will not be mistaken for another word. It is conventional in this system that the logic level of the one-half bit space between sequential address words is always opposite of the logic level of the first bit of the second word in the two word address series. Thus, if the first bit of the second word is at a 1 level then the one-half bit space would be at a 0 level.

Fig. 7B shows that the comma or interpage interval consists of a repetitive 1-0 pattern that occurs at twice the bit rate of the normal message transmission for a duration equal to 14 normal 300 second bits. The bit rate of the interaddress gap is at 600 bits per second. The starting logic level of the comma must also be the same logic level as the first bit of the following word.

The use of 12 binary bits to designate the address of the pager allows for 4,096 unique combinations and adding a second word to additionally specify the address would ordinarily result in nearly 17 million unique pager addresses. However, the usual method for decoding ECHO message systems operates asynchronously for the first word in each sequence. This usual decoding apparatus is sensitive to cyclic variations of the address patterns resulting in possible false detections in the first word producing an incorrect identification of the pager address. To eliminate this problem which is due principally to the decoding hardware, two serial address words that are cyclically related are not used as the first word of the two 23-bit word address system since this could lead to a probability of a false word 1 detection. It is possible to provide only 178 different 23-bit binary words where each cyclic variation of any one would be different from any other of the 178 binary words or their cyclic variation by at least seven binary bits. It has additionally been observed that frame synchronization accuracy for the normal ECHO decoding apparatus may be improved by only utilizing those first words which have 12 or more cyclic transitions. This further restricts the number of available coding permutations in the first address word to 118. Thus, the first address word in combination with the 4,095 possible second words provide in excess of 480,000 addresses for the ECHO system.

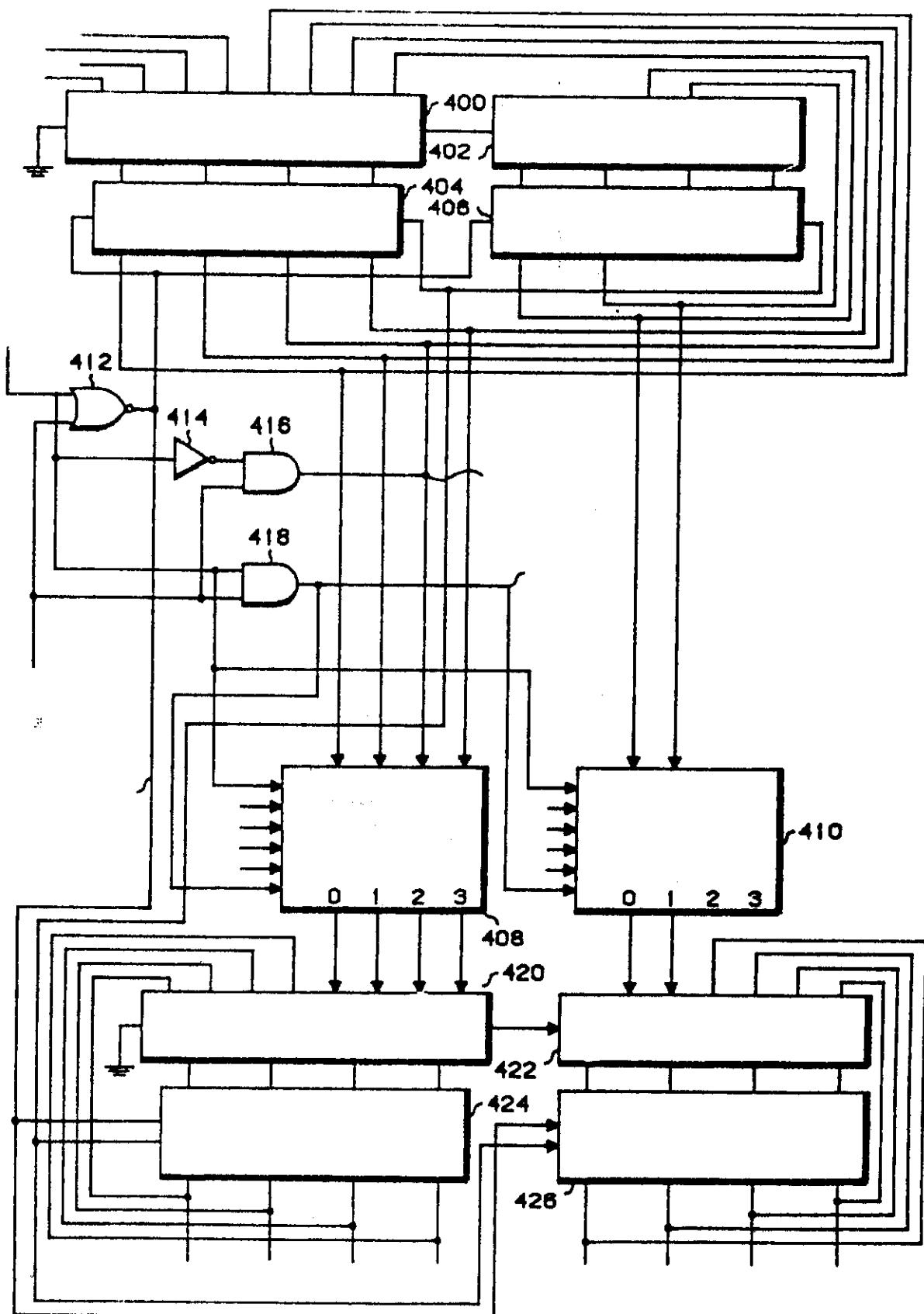

Fig. 8 shows a more detailed structural diagram for the preferred embodiments which comprise in the alternative an adaptive signal decoder or functional equivalent of a microcomputer implementation. For convenience only, one interconnected line is shown between various modules. However, it is to be understood that such a line is to represent as many as eight binary input lines. An adjustable multi-phase clock 120 is connected to the first input of an AND gate 122. A power-up signal from the energy conservation means 28 is connected to the second input of AND 122. The output of AND 122 is connected to a divide-by-five counter 124 which is connected to a divide-by-four counter 126. The outputs of AND 122, divide-by-five counter 124 and divide-by-four counter 126 are variously defined as timing signals as will be

described in more detail later. In addition, the output of counter 126 is connected to a demultiplexer 128 having four output signals designated RE1, RE2, RE3 and RE4. AND 122, the counters 124 and 126 and demultiplexer 128 are shown enclosed by a broken line to enhance the comparison with data sampling and sequencing device 76 shown in Fig. 4. The output of counter 124 is coupled directly to each of the clock 5 inputs of multiple bit serial shift registers 130, 132, 134 and 136. Register enable signals RE1, RE2, RE3 and RE4 are connected respectively to enable terminals of registers 130, 132, 134 and 136. The output of the communication receiver 20 labeled Input is connected to the data terminals of each of registers 130, 132, 134 and 136.

Each of registers 130, 132, 134 and 136 is multiply connected to a multiplexer 138. Four lines are 10 shown interconnecting each register with multiplexer 138. Each of these four interconnect lines represents eight separate lines since preferably the serial shift registers are composed of a series arrangement of four eight-bit serial shift registers as will be described in greater detail later. The serial shift registers and multiplexer 138 are shown enclosed by a broken line to enhance comparison with the data storage device 78 of Fig. 4.

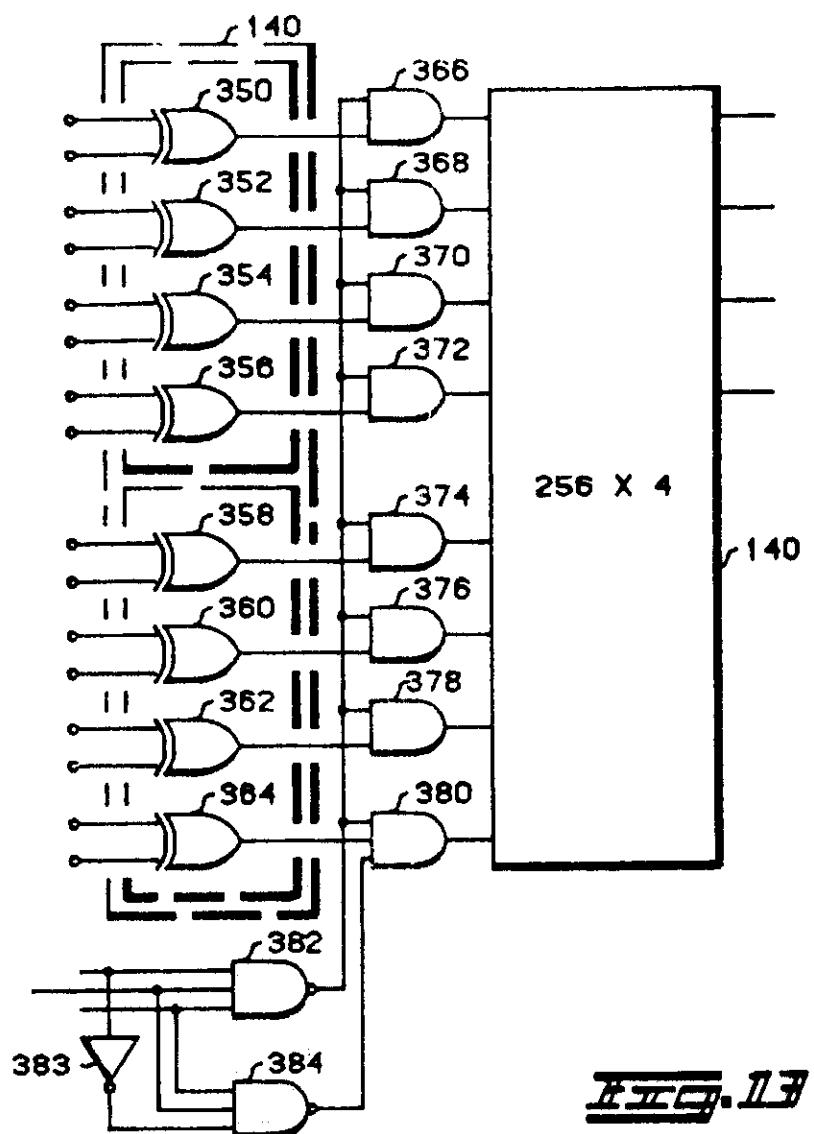

15 The output of multiplexer 138 is connected to an Exclusive OR array 140 preferably containing eight devices. Code memory 26 is connected to a second input of Exclusive OR array 140. The Exclusive OR array 140 is connected to an error read-only memory (ROM) 142. Error ROM 142 is connected to an error adder and accumulator 144. Exclusive OR array 140, error ROM 142 and error accumulator 144 are shown enclosed with a broken line to enhance the comparison with data sequence comparator 80.

20 The output of error accumulator 144 is connected to a comparator 146 and a comparator 148. Comparator 148 is connected to a lower error limit 150 and comparator 148 is connected to an upper error limit 152. Error limit circuits 150 and 152 each receive the S1 and S2 system select signals which will be described in detail later. Comparators 146 and 148 are connected to a word 1 detect memory 154. The word 1 detect memory 154 is connected back to code memory 26 and to a window timer 156. Window 25 timer 156 also receives signals S1 and S2 which will be described later. Window timer 156 also receives a signal from code memory 26. Comparators 146 and 148 and window timer 156 are connected to alert detect latch 158. Alert detect latch 158 is connected to alert pattern circuit 72 which is connected to annunciator 74. Alert pattern circuit 72 is also connected to be responsive to code memory 26. Comparators 146, 148, lower error limit 150, upper error limit 152, word one detect memory 154 and window timer 156 30 are shown enclosed by a broken line to enhance the comparison comparator error window limits circuit 82.

An additional output terminal of multiplexer 138 is connected to a multiplexer 164. Multiplexer 164 is connected to a bit rate ROM 166 which is connected to an adder/accumulator 168. Multiplexer 164, bit rate 35 ROM 166 and adder/accumulator 168 are shown enclosed by a broken line to enhance the comparison with system characteristic detector 90. Accumulator 168 is also connected to a comparator 170. Comparator 170 is connected to be responsive to a bit rate error limit device 172. Bit rate error limit 172 is responsive to system select signals S1 and S2. Two outputs of comparator 170, designated as Pass and Fail, are connected respectively to the reset and count terminals of a Fail Counter 174. Fail Counter 174 is connected to the count terminal of a scheme counter 176. The output of Fail Counter 174 designated as a signal "to R" is to be connected to each of the reset terminals of serial shift registers 130, 132, 134 and 40 136. Comparator 170, bit rate error limit 172, Fail Counter 174 and scheme counter 176 are shown enclosed by a broken line to enhance the comparison with coding systems search control 86.

A three position switch having center terminal 178 connected to B+ is shown with a first terminal designated "1" connected to the S terminal of scheme counter 176; a second terminal designated "2" is connected to the reset terminal of scheme counter 176; and a third terminal designated "both" is 45 unconnected. The switch with its associated terminals are shown enclosed by a broken line to enhance the comparison with external system subset selector 83. Two outputs of scheme counter 176 are designated S1 and S2 and are connected to adjustable multi-phase clock 120, to code memory 26; to window timer 156 and error bit rate limit 172.

For the decoding system containing either the adaptive signal decoder or the microcomputer 50 implementation, when initiated, counter 176 activates one output which is supplied to adjustable clock 120 to establish a timing operation for the bit rate detection procedure. This is the equivalent of selecting one of the two possible decoding schemes to determine if the correct message bit rate is being received. At a time appropriately determined by energy conservation means 28, the signals from adjustable clock 120 are provided to serially enable the registers 130, 132, 134 and 136. In particular, the output of counter 124 55 causes shifting or advancement of the data at the input line to each of the registers. During each sample clock pulse output from counter 124, one sample of the information from communication receiver 20 is applied to the one serial shift register which has been enabled. Demultiplexer 128 enables the shift registers serially so that the first sample of a derived incoming bit pattern would be stored in register 130, a second

sample in register 132, a third sample in 134 and the fourth sample in 136. It is preferable that adjustable clock 120 be operated at 20 times the anticipated bit rate so that the output of counter 124 is precisely four times the bit rate which is the desired sampling rate.

At the time when the system is actuated Fail Counter 174 resets the serial shift registers to clear all of the information which may remain. In addition, scheme counter 176 selects the address information corresponding to the selected decoding scheme from code memory 26 and the correct limits for window timer 156 so that when sufficient sampling data has been supplied to Exclusive OR array 140, the process of confirming whether the address of the specific pager has been detected may continue.

As may be recalled by reviewing the coding formats for the ECHO and POCSAG systems, the word lengths in the various systems are respectively 23 and 32 bits. For an example of the operation of the diagram of Fig. 8, it is convenient to assume that the ECHO system has been selected so that the desired word length is then 23 bits. Each sampling of an incoming bit is applied in sequence to the serial shift registers so that at the time period which is equivalent to acquiring 92 samples serial shift registers 130, 132, 134 and 136 have been filled with the data required for ECHO. This information is supplied through multiplexer 164 where it is reorganized and supplied to bit rate ROM 168. This bit rate ROM compares the individual bit patterns in the shift registers to determine the degree of correspondence and thereby to confirm whether the bit rate of the input signal has been confirmed. The correspondence determination for the data in the shift registers is accomplished by marking a sample position by corresponding sample position comparison and using the bit rate ROM which contains a table of errors corresponding to the various bit values of the position patterns. For each sample and for each enabling of any of the registers, accumulator 168 determines a total error for the reorganized data. This information is supplied to comparator 170 for comparison to a limit appropriate for the chosen scheme from bit rate error limit circuit 172. The outputs of comparator 170 are two signals designated Pass and Fail. In the event that the bit rate has been correctly determined and that information is being received in the ECHO system, the counter 174 is reset. This reset operation prioritizes the searching routine by ensuring that Fail Counter 174 cannot advance scheme counter 176 to select the next scheme. In the event that the error exceeds the maximum limits, the output of comparator 170 will activate the fail signal. If no system has been detected in four consecutive sample attempts, Fail Counter 174 will cause advancement of scheme counter 176 and establish a new timing period for adjustable multi-phase clock 120 and clearing all of the shift registers.

For the POCSAG scheme the data sample accumulation is 128 samples which are supplied through multiplexer 138 into multiplexer 164 for comparison as to whether that assumed bit rate produces an acceptable error in accumulator 168. Again, the output of accumulator 168 is supplied to comparator 170 which would now have a new error limit corresponding to the POCSAG system. In the event that the POCSAG system was correctly identified again, Fail Counter 174 would be reset thus prioritizing and locking the decoding into that scheme.

An advantage in having a separate multiplexer 164 coupled to multiplexer 138 is that the bit rate determination procedure can be achieved by carefully reorganizing the data and once the scheme has been correctly identified the same information contained in serial shift registers 130, 132, 134 and 136 may be used to identify whether the individual pager has been addressed.

At an appropriate time, as designated by the various timing signals, the Exclusive OR array receives the appropriate eight bits from each portion of each serial shift register for comparison with the information in code memory 26. Since for the POCSAG system all 32 bits are processed for the comparison, then all of the information contained in serial shift registers 130, 132, 134 and 136 is processed through Exclusive OR array 140 eight bits at a time. The output of Exclusive OR array 140 is connected to an error ROM 142. As before, this ROM has the advantage of allowing rapid processing to determine the number of errors by simply addressing the memory and having stored at that location the number corresponding to the number of errors difference in the two patterns. This error difference is supplied to error accumulator 144 for each of the eight samples tested. On a sample-by-sample basis, the output of error accumulator 144 is supplied to comparators 146 and 148 to test whether the number of errors is less than the lower acceptable limit or greater than the upper acceptable limit. The outputs of comparators 146 and 148 are supplied to a word 1 detect memory. It will be recalled that the ECHO system uses two serially related 23-bit words while the POCSAG system uses a single 32-bit word at a predetermined position in a batch message format. However, each POCSAG batch contains a synchronization word and it has been found to be advantageous for the POCSAG scheme decoding to let word 1 in the detection scheme correspond to this synchronization word. Once word 1 has been detected, a window timer is established which is required for the asynchronous detection of the ECHO system second word but is also advantageous for the POCSAG system since the window timer can establish the beginning and end of the frame period during which a proper POCSAG pager address word may be found. If the address word is not found, the system continues to

sample until such time as the bit rate detector, which has continued to operate, has a sufficient number of Fail signals to indicate that the bit rate assumption is an error. This would indicate the termination of the broadcast of either system or its replacement by the other.

On the other hand, assuming that the first word of the address has been correctly identified for either system, then the normal search routine is established for the second word which is identical to the word 1 comparator error identification and when that word has been correctly detected, the alert detect latch is activated so that the alert pattern may be supplied to the annunciator to indicate to the pager carrier the receipt of a message.

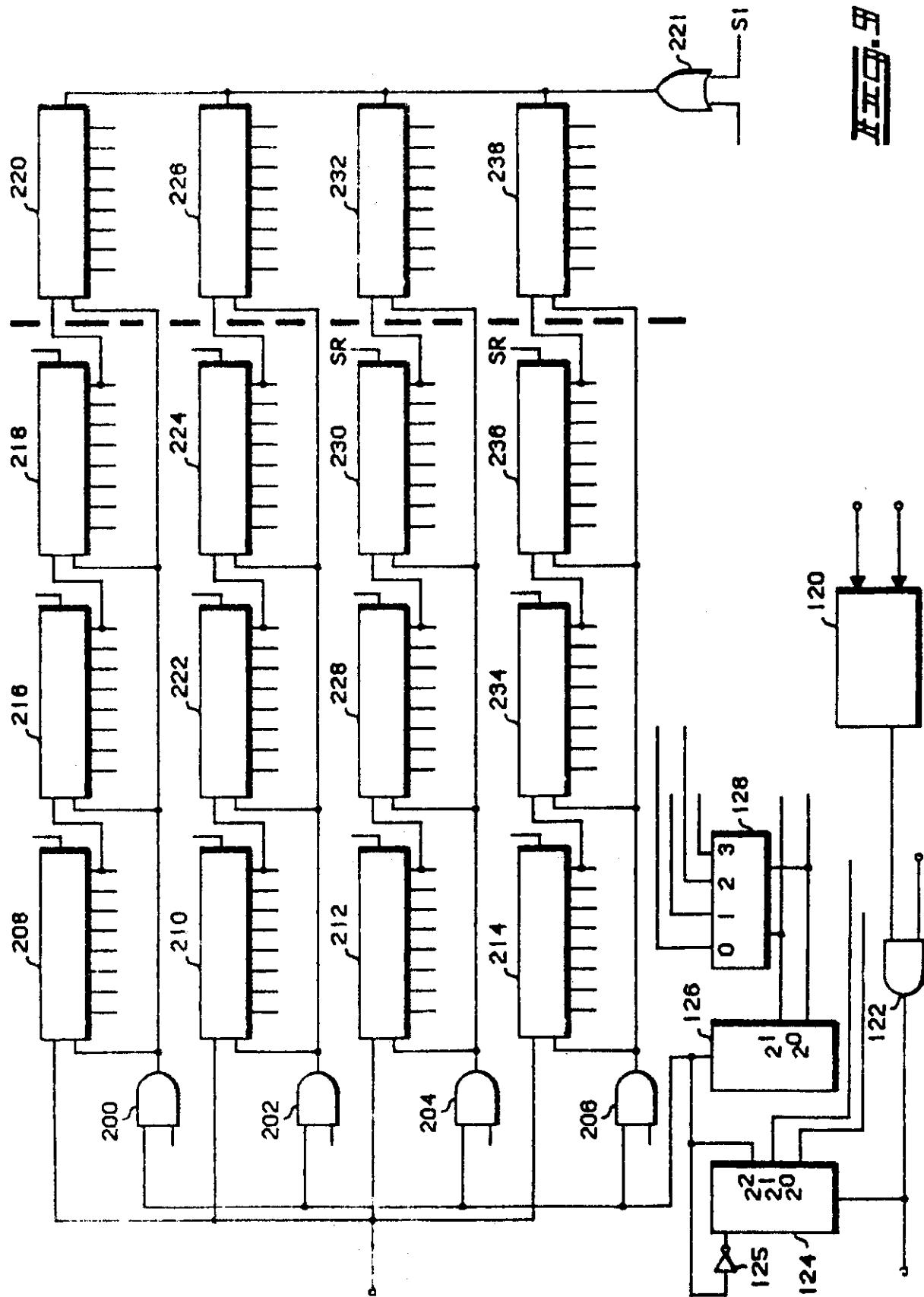

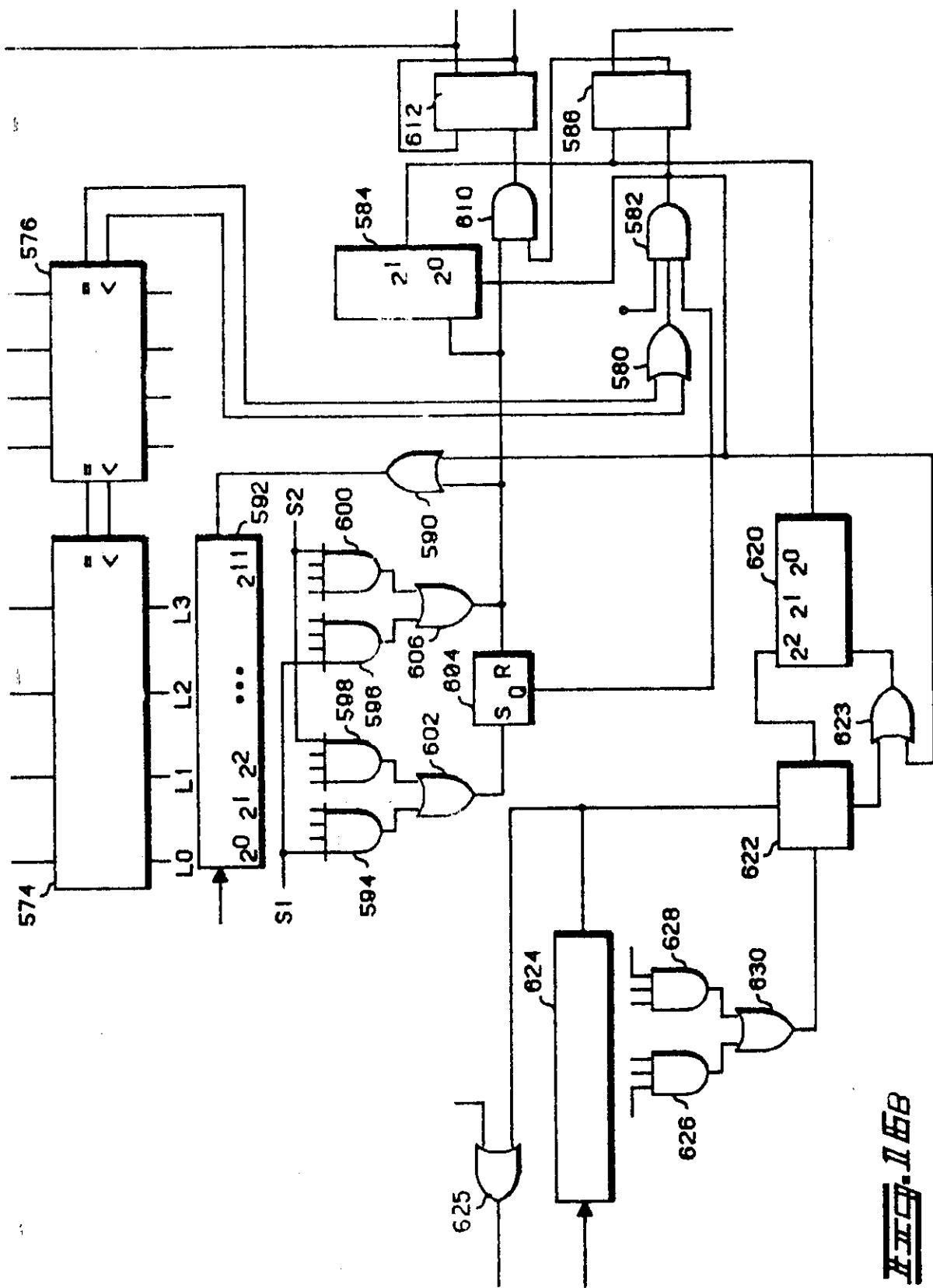

Fig. 9 shows the electrical schematic for data sampling and sequencing circuit 76 and sample storage circuit 78. It therefore is applicable to both the adaptive decoder and microcomputer embodiments. As described for Fig. 8, adjustable clock 120 is connected through AND 122 which is enabled by a Power-Up signal. The output of AND 122 is a gated clock signal and is supplied to the clock input terminal of counter 124. At the 2<sup>0</sup> terminal of counter 124 is a signal BA and at the 2<sup>1</sup> terminal is a signal labeled BB. The 2<sup>2</sup> terminal of counter 124 is connected to the clock terminal of counter 126 and through an inverter 125 to its own R reset terminal. The 2<sup>2</sup> terminal of divide-by-five counter 124 is also connected to the first inputs of AND gates 200, 202, 204 and 206.

At the 2<sup>0</sup> terminal of counter 126 is a signal designated RA which is also connected to the A input terminal of a binary one of four decoder/demultiplexer 128. At the 2<sup>1</sup> terminal of counter 126 is a signal designated RB which is also connected to the B input terminal of demultiplexer 128. At the four terminal outputs of demultiplexer 128 are signals which are designated RE1, RE2, RE3 and RE4. Signal RE1 is connected to the second input of AND 200, RE2 is connected to the second input of AND 202, RE3 is connected to the second input of AND 204 and RE4 is connected to the second input of AND 206.

The signal from communication receiver 20 designated as Input is supplied to the data input terminals of shift registers 208, 210, 212 and 214. Each of registers 208, 210, 212 and 214 bears an additional alphabetic identification A, D, G and K, respectively. The output of AND 200 is connected to the clock terminal of shift register 208 and to the clock terminals of registers 216, 218 and 220. The eight output terminals of register 208 are designated A1 through A8. The A8 terminal of register 208 is connected to the data input terminal of register 216. Register 216 bears the additional alphabetic designation B and the eight output terminals of register 216 are designated B1 through B8. The B8 terminal of register 216 is connected to the data input terminal of register 218. Register 218 bears the additional alphabetic designation C and the eight output terminals of register 218 are designated C1 through C8. The C8 output terminal of register 218 is connected to the data input terminal of register 220. Register 220 bears the additional alphabetic designation N and the eight output terminals are designated as N1 through N8. The signal designated S1 from scheme counter 176 is supplied to the first input of an OR gate 221. The output of OR 221 is supplied to the reset terminal of register 220. The Sampling Reset signal from Fail Counter 174 is supplied to the second input of OR 221. The Sampling Reset signal is also supplied to the reset terminals of registers 208, 216 and 218.

The output of AND 202 is applied to the clock terminals of registers 210, 222, 224 and 226. The eight output terminals of register 210 are designated D1 through D8. The D8 terminal of register 210 is connected to the data input terminal of register 222. Register 222 bears the additional designation E and the eight output terminals are labeled E1 through E8. The E8 output terminal of register 222 is connected to the data input terminal of register 224. Register 224 bears the additional alphabetic designation F and the eight output terminals are designated F1 through F8. The F8 output terminal of register 224 is connected to the data input terminal of register 226. Register 226 bears the additional alphabetic designation O and the eight output terminals are designated O1 through O8. The output of OR 221 is connected to the reset terminal of register 226. The Sampling Reset signal from Fail Counter 174 is supplied to the reset terminals of each of registers 210, 222 and 224.

The output of AND 204 is connected to the clock terminal of registers 212, 228, 230 and 232. Register 212 also has the alphabetic designation G and the eight output terminals of register 212 are designated G1 through G8. The G8 output terminal of register 212 is connected to the data input terminal of register 228. Register 228 bears the additional alphabetic designation H and the eight output terminals are designated H1 through H8. The H8 output terminal of register 228 is connected to the data input terminal of register 230. Register 230 bears the additional alphabetic designation J and the eight output terminals are designated J1 through J8. The J8 output terminal of register 230 is connected to the data input terminal of register 232. Register 232 bears the additional alphabetic designation P and the eight output terminals are designated P1 through P8. The output of OR 221 is connected to the reset terminal of register 232. The Sampling Reset signal from Fail Counter 174 is supplied to each of reset terminals of registers 212, 228 and 230.

The output of AND 206 is connected to the clock terminals of shift registers 214, 234, 236 and 238. Register 215 also bears the alphabetic designation K the eight output terminals of register 214 are designated K1 through K8. The K8 output terminal of shift register 214 is connected to the data input terminal of register 234. Register 234 bears the additional alphabetic designation L and the eight output terminals are designated L1 through L8. The L8 output terminal of register 234 is connected to the data input terminal of register 236. Register 236 bears the additional alphabetic designation M and the output terminals are designated M1 through M8. The M8 output terminal of register 236 is connected to the data input terminal of register 238. Register 238 bears the additional alphabetic designation Q and the eight output terminals are designated Q1 through Q8. The output of OR 221 is connected to the reset terminal of register 238. The Sampling Reset signal from Fail Counter 174 is supplied to each of the reset terminals of registers 214, 234 and 236.

In operation adjustable clock 120 operates at 20 times the anticipated bit rate and this rate is adjusted depending upon which of the two sampling systems of the preferred embodiments have been selected. This output is supplied at times determined by energy conservation means 28 through AND gate 122 to counter 124. The timing diagrams for the BA and BB signal outputs of counter 124 will be shown in Fig. 10. The 20 times the bit rate signal is divided by five to produce a regularly occurring pulse signal at four times the bit rate which is the sampling rate. This sampling rate is supplied to counter 126 and is also supplied to enable AND's 200, 202, 204 and 206 for each sampling period.

At the outputs of counter 126 are signals RA and RB which will be shown in greater detail in Fig. 10 and are supplied to the input terminals of multiplexer 128. Multiplexer 128 serially selects which of the horizontal rows of 16 shift registers will be enabled for each serial sampling period. Although all four AND gates are enabled by the sampling signal, the enabling signal from multiplexer 128 selectively enables the various rows of shift registers through the AND gates.

Each row corresponds to one sampling period for as many as 32 possible bits. This capacity was chosen for the maximum word length which, for the two systems of the preferred embodiments, is 32 bits. It may also be seen that the functioning of signal S1 from scheme counter 176 operating through OR 221 will cause a resetting of shift registers 220, 226, 232 and 238 for all sampling intervals during which system 1 has been selected, thus allowing only a maximum of 24 bits of storage for the data. Moreover, whenever Fail Counter 174 causes a clocking of scheme counter 176, at the same time counter 176 advances to designate a new scheme select output, all of the shift registers are reset including registers 220, 226, 232 and 238 through OR 221.

During each sample interval, the data is advanced into one of the shift register rows and, correspondingly, the shift registers are clocked to accept and store that data. During the sampling intervals, as for the case of ECHO, after 92 such sample intervals, the 12 shift registers A, B, C, D, E, F, G, H, J, K, L and M will be nearly filled with data, the only exception being the last position of shift registers designated C, F, J and M since sufficient shift register positions have been allotted for the possibility of a 24-bit word. However, as will be described in detail later for the operation of the Exclusive OR array, only the first 23 bits of information will be utilized. To more fully understand the operation of the data sampling and sequencing circuit 76, it is convenient to refer to Fig. 10.

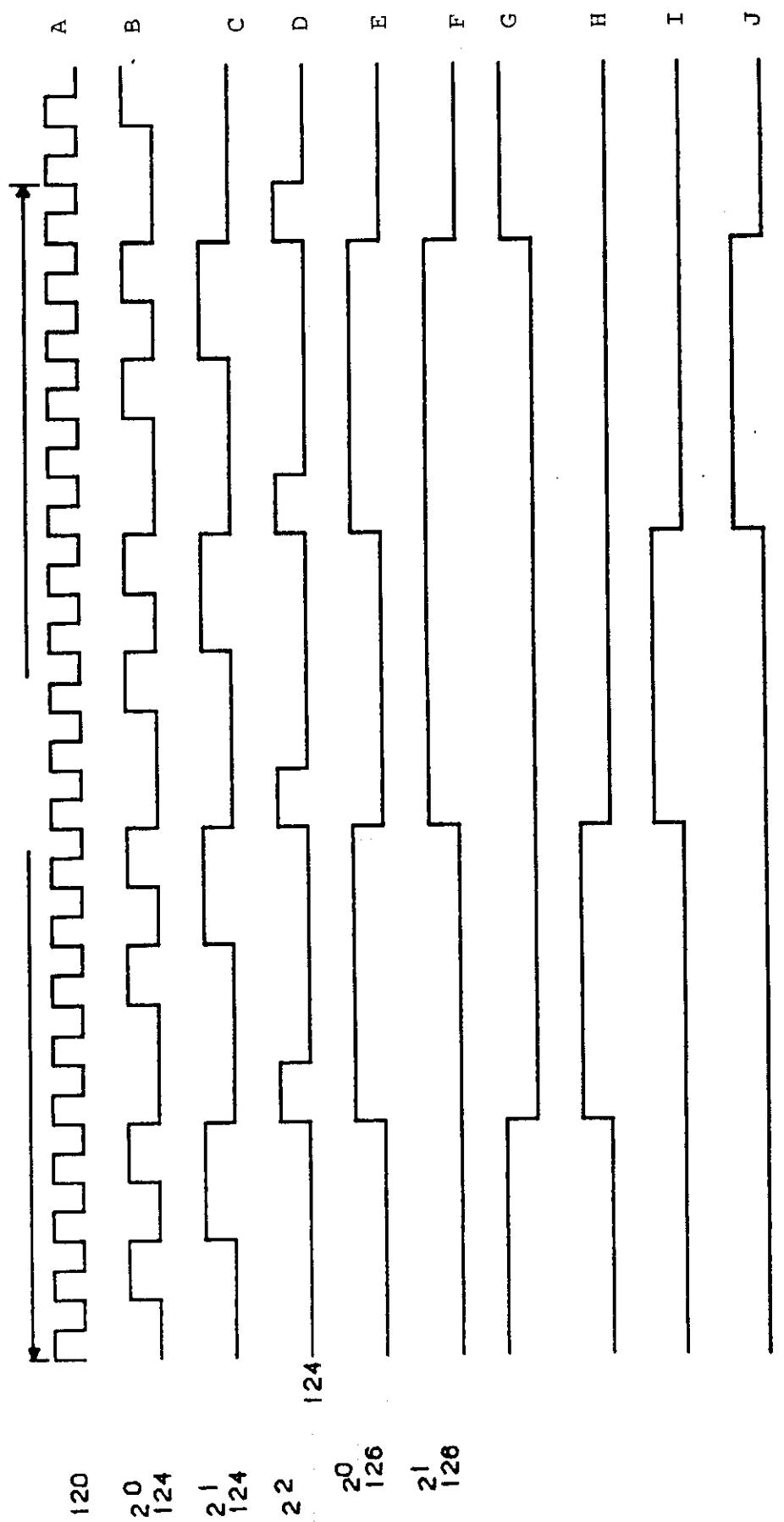

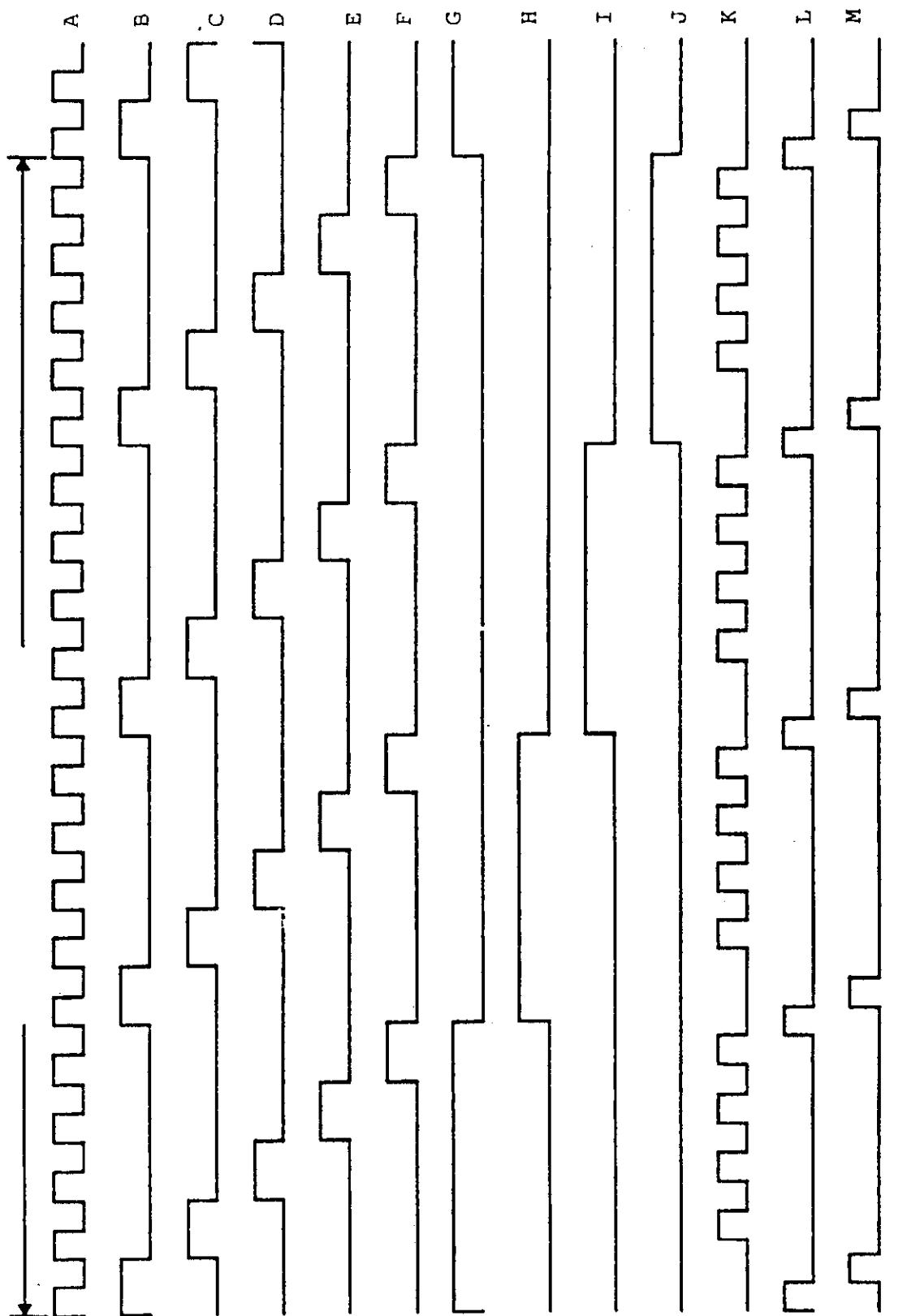

Fig. 10 shows 10 timing diagrams variously identified as 10A through 10J which are useful in understanding more completely the operation of the data sampling and sequencing circuit. Fig. 10A shows the output waveform for adjustable clock 120 which is a square wave operating at a frequency to produce 20 pulses for each anticipated bit interval. Signals BA and BB are shown respectively in Figs. 10B and 10C. Signal BA is operated at the  $2^0$  output of counter 124 and BB is generated at the  $2^1$  terminal of counter 124.

Fig. 10D shows the signal generated at the  $2^2$  terminal of counter 124. It may be seen that the signal generated at the  $2^2$  output of counter 124 is a regularly occurring pulse train at four times the anticipated bit period. This is the sampling clock signal for the circuit. The relative positions in time with respect to the sampling interval for the various outputs of counter 124 are shown in Figs. 10B, 10C and 10D.

Figs. 10E and 10F show, respectively, the signals generated at the  $2^0$  and  $2^1$  output terminals of counter 126. These correspond to output signals designated RA and RB. Figs. 10G, H, I and J correspond to the register enable signals which are the outputs of multiplexer 128. In particular, Fig. 10G shows RE1, Fig. 10H shows RE2; Fig. 10I shows RE3; and Fig. 10J shows RE4.

The operation of data sampling and sequencing circuit 76 may now be explained in terms of the timing of the various control signals. During each sample signal interval as designated by Fig. 10D, one and only one of signals RE1, RE2, RE3 and RE4 are at a positive logic state to enable the appropriate AND gate to allow the sampling signal to clock in the information contained on the input signal which is applied to the data terminal of the selected shift register. As may be seen from the comparison of Figs. 10G, H, I and J with Fig. 10D, for each succeeding sample signal interval, one of RE1 through RE4 becomes positive, thus

enabling the next row of shift registers to accept during the sample interval the input signal at its data terminal. With each subsequent combination of sampling signal intervals and register enabling, the data constituting four measurements for each bit of the multi-bit words, are clocked into the various registers. Registers A, B, C and N contain serial information for the first of the four sample clock phases; registers D, E, F and O contain all of the second clock phase samples; registers G, H, J and P contain all of the third clock phase samples; and registers K, L, M and Q contain all of the fourth clock phase samples.

5 The Sampling Reset signal from Fail Counter 174 and the Scheme Select line S1 from scheme counter 176 operate through OR 221 to selectively cause resetting of shift registers N, O, P and Q. The purpose for this operation is that, during the measurement of the data for the ECHO system, the 32-bit word length is 10 not necessary so that during the times when the ECHO system is either being tested or decoded, serial shift registers N, O, P and Q are constantly reset to 0 and held in that state.

The information at the output terminals of all of the serial shift registers are appropriately identified and are supplied to multiplexer 138.

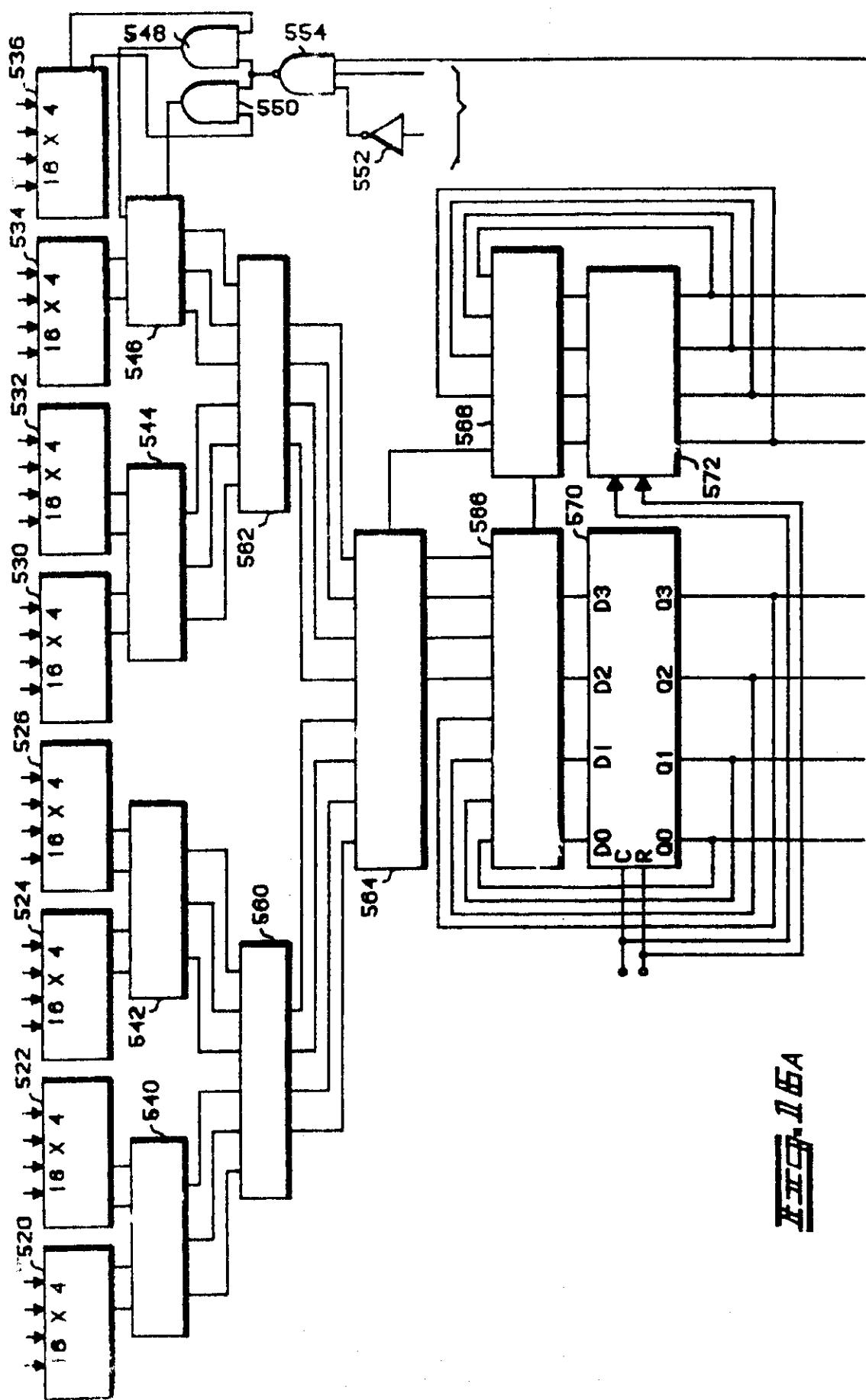

While any of a number of various devices could be used to build the first embodiment shown in Fig. 9, 15 It has been found advantageous to use CMOS devices of the Motorola 14000 series. Counter 124 is preferably of the type MC14163B which is a synchronous programmable four-bit counter. The choice of such a device results in the correspondence of clock terminal with pin 2, the reset R, terminal with pin 1, the  $2^0$ ,  $2^1$  and  $2^2$  terminals correspond to pins 14, 13 and 12, respectively. It may be appreciated by those skilled in the art that the use of such counters may require additional interconnection as is designated by 20 the data notes for the device. Divide-by-four counter 126 is also of the same general type as counter 124 with the corresponding pin and terminal identification. Demultiplexer 128 is preferably of the type MC14555B, which is a dual binary to one of four decoder demultiplexers. Either of the dual devices in the package would be sufficient for the decoding. In particular, the A terminal may be identified with pin 2, the B terminal with pin 3, the corresponding outputs for RE1 through RE4 would be identified as pins 4, 5, 6 25 and 7.

The sixteen serial shift registers designated with the alphabetic characters A, B, C, D, E, F, G, H, J, K, L, M, N, O, P and Q are all preferably of the type MC14015B. These are dual four-bit static shift registers which may be suitably interconnected to form eight-bit shift registers. When such a choice is made, the data terminal would correspond to pin 7; the clock terminals should be interconnected and they are pins 9 30 and 1; and the reset terminals similarly should be interconnected and they correspond to pins 6 and 14; the first four output terminals correspond to pins 5, 4, 3 and 10 and pin 10 should be interconnected with pin 15 which is the data input terminal for the second four bit device. The remaining four of the eight output terminals correspond to pins 13, 12, 11 and 2. With this choice of device, the corresponding outputs designated as 1-8 in Fig. 9 may be identified with the following sequence of pins: 5, 4, 3, 10, 13, 12, 11 35 and 2. As with the choice of all such devices, a review of the data sheet will indicate to those skilled in the art that other pin connections must be made for suitable power and ground.

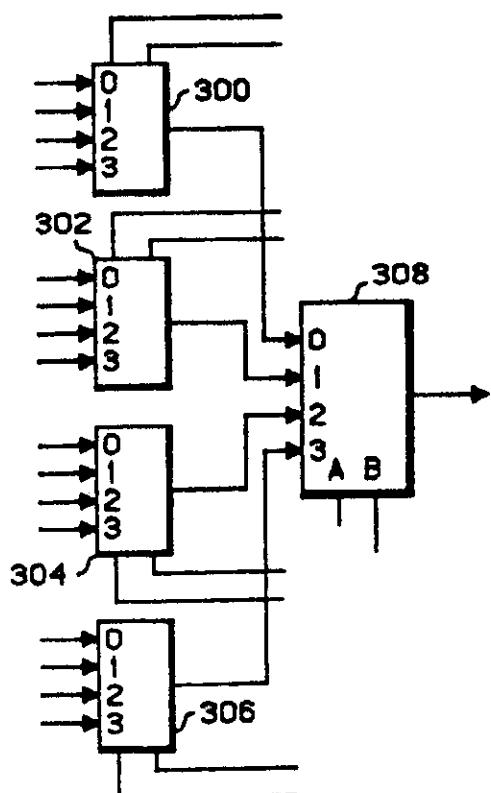

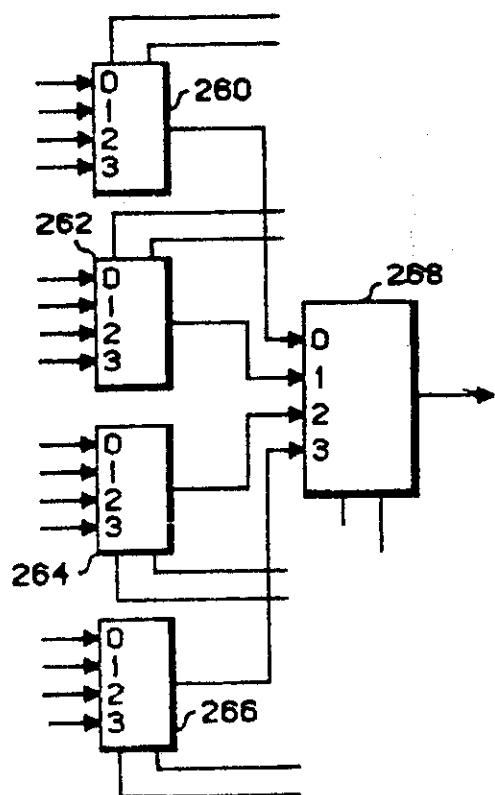

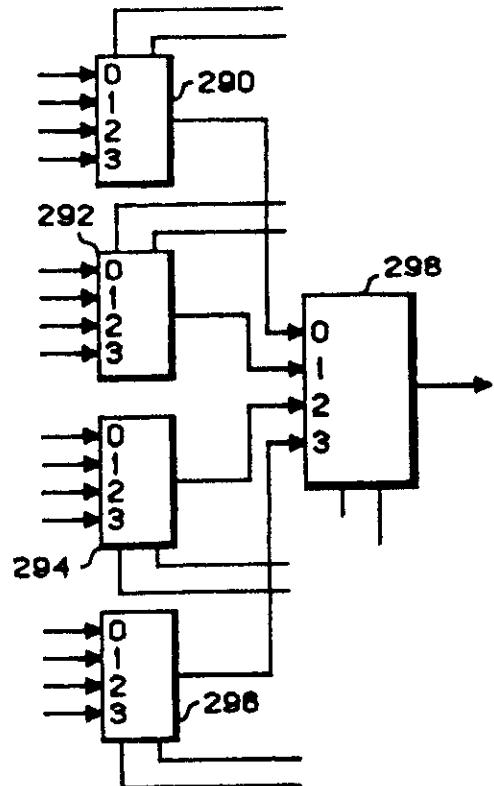

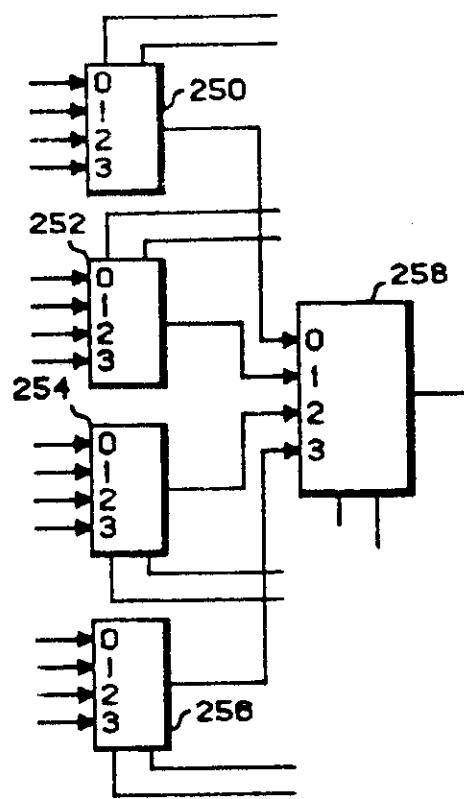

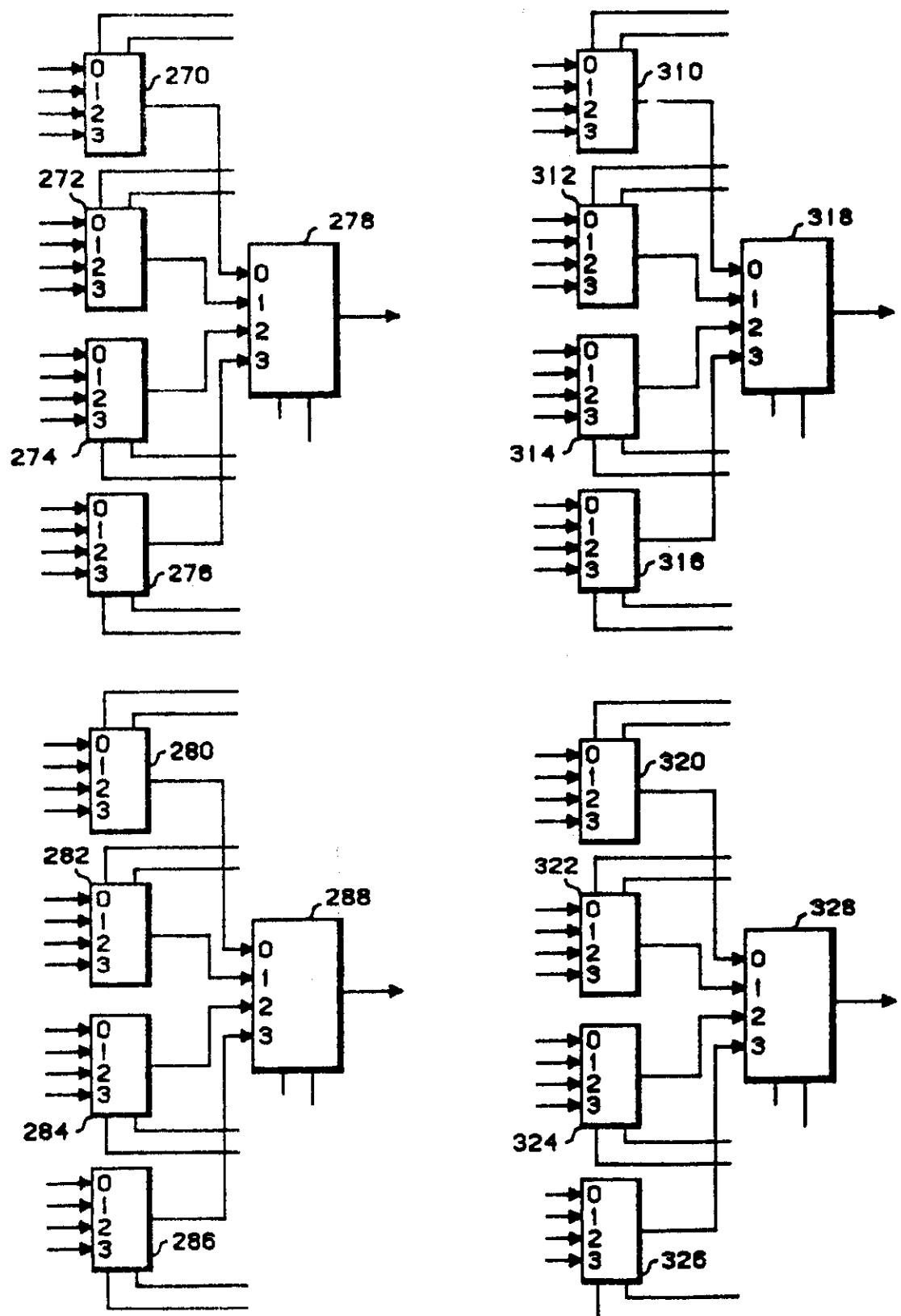

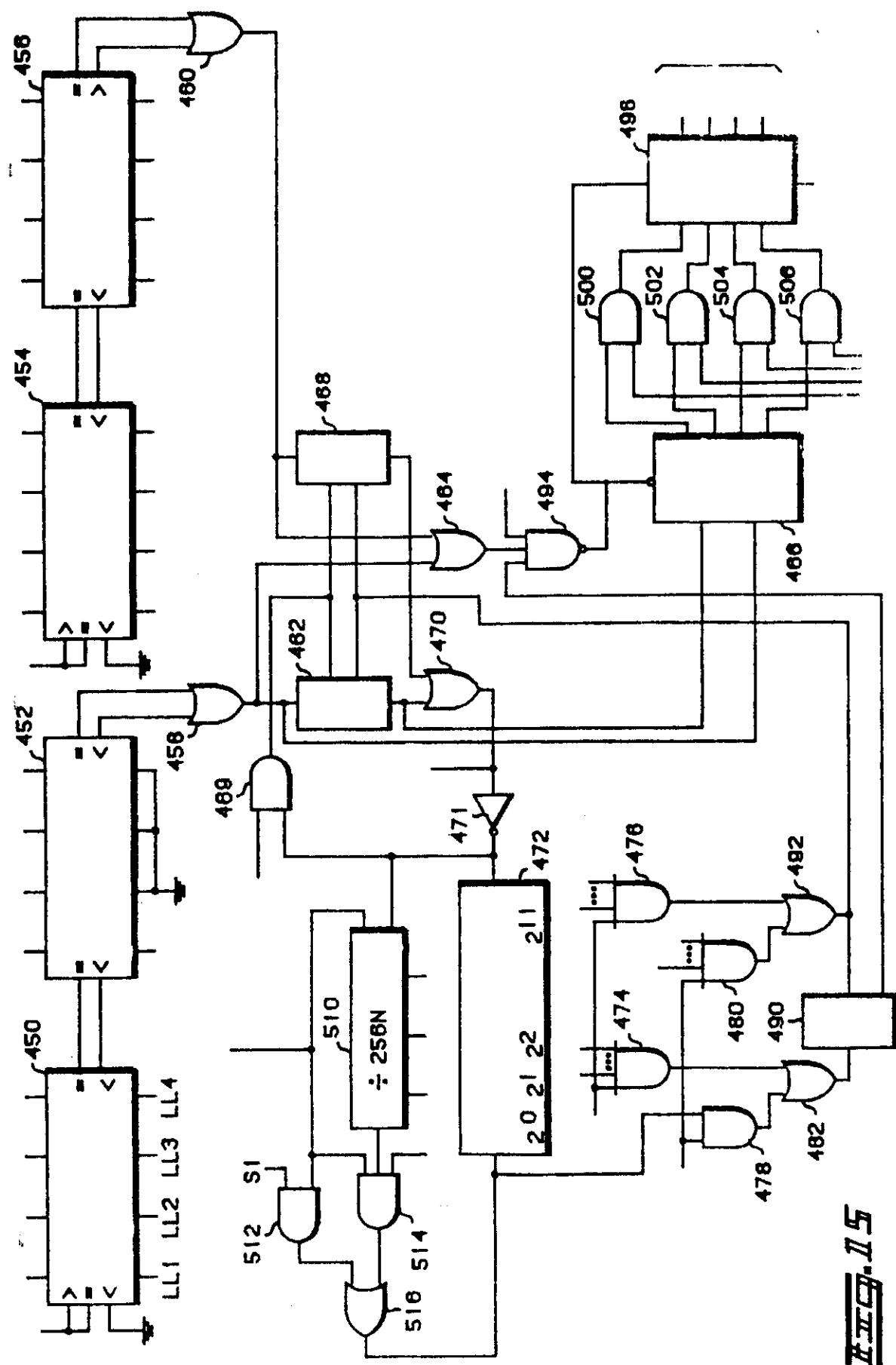

40 Figs. 11A and 11B show the detailed infrastructure of multiplexer 138 in Fig. 8. In the description of this figure, the terminals of the serial shift registers will be described by the two character alphanumeric designation given to each of these terminals in Fig. 9. Terminals A1, B1, C1 and N1 are connected respectively to the 0-3 input terminals of a multiplexer 250. Terminals D1, E1, F1 and O1 are connected 45 respectively to the 0-3 input terminals of a multiplexer 252. Terminals G1, H1, J1 and P1 are connected respectively to the 0-3 input terminals of a multiplexer 254 and terminals K1, L1, M1 and Q1 are connected respectively to the 0-3 input terminals of a multiplexer 256. Each of multiplexers 250, 252, 254 and 256 receive the BA and BB select input signals from the designated output terminals of divide-by-five counter 50 124 as shown in Fig. 9. Each of signals BA and BB are supplied to multiplexers 250, 252, 254 and 256 at corresponding input terminals. The output terminals of multiplexers 250, 252, 254 and 256 are connected respectively to the 0-3 input terminals of a multiplexer 258. At the output terminals of multiplexers 250, 252, 254 and 256 are signals MT1, MT2, MT3 and MT4 respectively. Multiplexer 258 also receives at input terminals designated A and B respectively, signals RA and RB which are the output signals from designated 55 terminals of counter 126. At the output of multiplexer 258 is a signal designated SM1.

Terminals A2, B2, C2 and N2 are connected respectively to the 0-3 input terminals of a multiplexer 260. Terminals D2, E2, F2 and O2 are connected respectively to the 0-3 input terminals of a multiplexer 262. Terminals G2, H2, J2 and P2 are connected respectively to the 0-3 input terminals of a multiplexer 264 and terminals K2, L2, M2 and Q2 are connected respectively to the 0-3 input terminals of a multiplexer 266. 55 Each of multiplexers 260, 262, 264 and 266 receive signals BA and BB at corresponding input terminals. The output of multiplexers 260, 262, 264 and 266 are connected respectively to the 0-3 input terminals of a

multiplexer 268. At the output terminals of multiplexers 260, 262, 264 and 266 are signals MT5, MT6, MT7 and MT8 respectively. Multiplexer 268 also receives signals RA and RB at A and B input terminals respectively. The output of multiplexer 268 is a signal designated as SM2.

Terminals A3, B3, C3 and N3 are connected respectively to the  $\emptyset$ -3 input terminals of a multiplexer 270.