(19) **日本国特許庁(JP)**

(51) Int. Cl.

# (12) 特 許 公 報(B2)

(11)特許番号

特許第6526361号 (P6526361)

(45) 発行日 令和1年6月5日(2019.6.5)

(24) 登録日 令和1年5月17日(2019.5.17)

HO2M 7/48 (2007.01)

HO2M 7/48

FL

Z

請求項の数 6 (全 13 頁)

(21) 出願番号 特願2018-564056 (P2018-564056) (86) (22) 出願日 平成29年1月27日 (2017.1.27)

(86) 国際出願番号 PCT/JP2017/003032 (87) 国際公開番号 W02018/138889

(87) 国際公開日 平成30年8月2日 (2018.8.2) 審査請求日 平成31年2月8日 (2019.2.8)

早期審查対象出願

(73)特許権者 000006013

三菱電機株式会社

東京都千代田区丸の内二丁目7番3号

|(74)代理人 100118762

弁理士 高村 順

(72) 発明者 中嶋 幸夫

東京都千代田区丸の内二丁目7番3号 三

菱電機株式会社内

(72) 発明者 三木 隆義

東京都千代田区丸の内二丁目7番3号 三

菱電機株式会社内

審査官 麻生 哲朗

最終頁に続く

## (54) 【発明の名称】電力変換装置

### (57)【特許請求の範囲】

### 【請求項1】

直列接続された一対の半導体スイッチング素子を具備する半導体モジュールを用いた電力変換装置であって、

4以上且つ偶数の前記半導体モジュールを備え、

前記半導体モジュールは、第1端子、第2端子、及び第3端子を表面に有し、

前記第1端子、前記第2端子及び前記第3端子には複数の締結点が設けられ、

正側スイッチング素子の正極が前記第1端子に電気的に接続され、

負側スイッチング素子の負極が前記第2端子に電気的に接続され、

前記正側スイッチング素子の負極と前記負側スイッチング素子の正極とが前記第3端子に電気的に接続され、

4以上且つ偶数の前記半導体モジュールのうちで同一相の半導体モジュール群を構成する2つの半導体モジュールの第1端子同士、第2端子同士又は第3端子同士は向かい合わせて配置され、

複数の前記半導体モジュール群は、前記半導体モジュール群内の2つの半導体モジュールの配列方向に直交する方向に配列されている

ことを特徴とする電力変換装置。

### 【請求項2】

前記半導体モジュールの数は6であり、6つの前記半導体モジュールを用いて、各相が2並列で接続された3相インバータ回路が構成されることを特徴とする請求項1に記載の

20

### 電力变換装置。

## 【請求項3】

前記半導体モジュールの数は4であり、4つの前記半導体モジュールを用いて、各相が2並列で接続されたコンバータ回路が構成されることを特徴とする請求項1に記載の電力変換装置。

## 【請求項4】

前記半導体モジュールの数は6であり、6つの前記半導体モジュールを用いて、2つの3相インバータ回路が構成されることを特徴とする請求項1に記載の電力変換装置。

#### 【請求項5】

前記第1端子は正極直流端子であり、

前記第2端子は負極直流端子であり、

前記第3端子は交流端子である

ことを特徴とする請求項1から4の何れか1項に記載の電力変換装置。

## 【請求項6】

前記第1端子における複数の前記締結点は、モジュール筐体における一方側の短辺部において、前記モジュール筐体の長手方向に直交する方向に配列され、

前記第2端子における複数の前記締結点は、前記第1端子における複数の前記締結点の 並びと平行で、且つ、前記第1端子よりも前記モジュール筐体の内方側に配列され、

前記第3端子における複数の前記締結点は、前記モジュール筐体における他方側の短辺部において、前記モジュール筐体の長手方向に直交する方向に配列されている

ことを特徴とする請求項1から5の何れか1項に記載の電力変換装置。

### 【発明の詳細な説明】

### 【技術分野】

### [0001]

本発明は、直列接続された正極側及び負極側の一対の半導体スイッチング素子を具備する半導体モジュールを用いた電力変換装置に関する。

## 【背景技術】

#### [00002]

近年、半導体技術の進歩により、大容量の半導体モジュールが実現され、インバータ1相分である上下アームを構成する正極側及び負極側の一対の半導体スイッチング素子を一体化した半導体モジュールが広く普及している。この種の半導体モジュールは、2 i n 1 モジュールと呼ばれている。

### [0003]

また、更なる大容量化のため、1相分のモジュールを構成するために2in1モジュールを並列化して構成する場合がある。この場合、3相のモータを駆動するための2つのインバータ、すなわち2つの3相インバータを用いて電力変換装置を構成するには、6つの2in1モジュールを配置する必要がある。

### [0004]

上記のような技術的背景の下、下記特許文献1には、2つの3相インバータを1台の筐体に収容した構成が開示されている。

【先行技術文献】

#### 【特許文献】

### [0005]

【特許文献1】特開2015-89244号公報

### 【発明の概要】

【発明が解決しようとする課題】

### [0006]

特許文献1は、小型化及び設置面積を低減することを目的としている。しかしながら、 特許文献1では、2並列で構成する一方の半導体モジュールと、他方の半導体モジュール との間の接続にバスバーを用いた上で、当該バスバーを半導体モジュールの端子にねじ止 10

20

30

30

40

めする構造を採用している。このため、2並列で配列する半導体モジュール間の間隔を十 分に小さくすることができず、小型化に関する更なる改善の余地が認められる。

### [0007]

本発明は、上記に鑑みてなされたものであって、2並列で配列する半導体モジュール間 の間隔を小さくして、更なる小型化を図ることができる電力変換装置を得ることを目的と する。

【課題を解決するための手段】

### [0008]

上述した課題を解決し、目的を達成するために、本発明は、直列接続された一対の半導 体スイッチング素子を具備する半導体モジュールを用いた電力変換装置であって、4以上 且つ偶数の前記半導体モジュールを備え、前記半導体モジュールは、第1端子、第2端子 、及び第3端子を表面に有し、正側スイッチング素子の正極が前記第1端子に電気的に接 続され、負側スイッチング素子の負極が前記第2端子に電気的に接続され、前記正側スイ ッチング素子の負極と前記負側スイッチング素子の正極とが前記第3端子に電気的に接続 され、4以上且つ偶数の前記半導体モジュールのうちで同一相の半導体モジュール群を構 成する2つの半導体モジュールの第1端子同士、第2端子同士又は第3端子同士は向かい 合わせて配置され、複数の前記半導体モジュール群は、前記半導体モジュール群内の2つ の半導体モジュールの配列方向に直交する方向に配列されている。

## 【発明の効果】

## [0009]

本発明によれば、2並列で配列する半導体モジュール間の間隔を小さくして、更なる小 型化を図ることができる、という効果を奏する。

【図面の簡単な説明】

[0010]

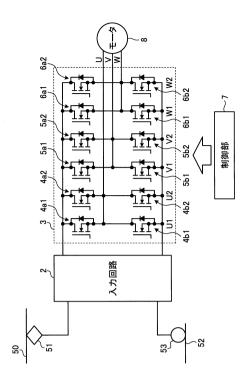

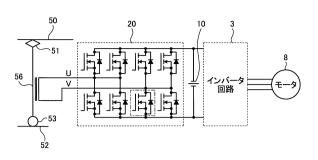

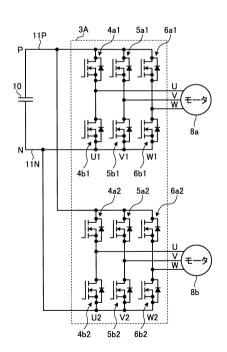

- 【図1】実施の形態1に係る電力変換装置の構成例を示す回路図

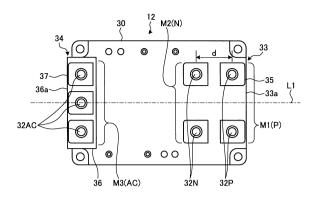

- 【図2】実施の形態1に係る電力変換装置に用いる半導体モジュールにおける各端子の配

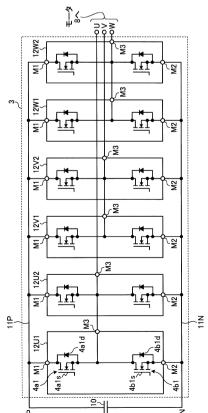

- 【図3】図2に示した半導体モジュールを図1に示したインバータ回路に適用した回路図

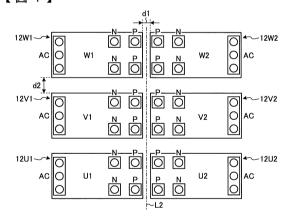

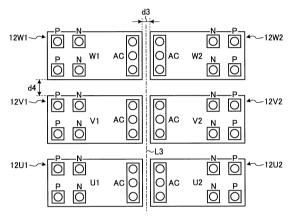

- 【図4】実施の形態1の電力変換装置における6つの半導体モジュールの配置例を模式的 に示す図

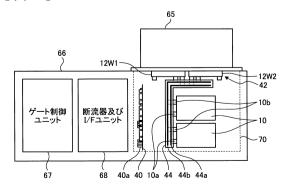

- 【図5】実施の形態1に係る電力変換装置を鉄道車両に搭載した場合の構成例を示す図

- 【図6】ラミネートブスバーと半導体モジュールとの接続状態を示す平面図

- 【図7】実施の形態2の電力変換装置における6つの半導体モジュールの配置例を模式的 に示す図

- 【図8】実施の形態3に係る電力変換装置の構成例を示す図

- 【図9】実施の形態4に係る電力変換装置で用いるインバータ回路の回路構成を示す図 【発明を実施するための形態】

- [0011]

以下に、本発明の実施の形態に係る電力変換装置を図面に基づいて詳細に説明する。な お、以下の実施の形態により、本発明が限定されるものではない。

[0012]

#### 実施の形態1.

図1は、実施の形態1に係る電力変換装置の構成例を示す回路図である。図1において 実施の形態1に係る電力変換装置は、少なくともスイッチ、フィルタコンデンサ、フィ ルタリアクトルを含む入力回路2と、スイッチング素子4a1,4a2,5a1,5a2 , 6 a 1 , 6 a 2 , 4 b 1 , 4 b 2 , 5 b 1 , 5 b 2 , 6 b 1 , 6 b 2 を具備し、少なく とも1台のモータ8を接続してなるインバータ回路3と、スイッチング素子4a1,4a 2,5a1,5a2,6a1,6a2,4b1,4b2,5b1,5b2,6b1,6b 2 を制御するための P W M 信号を生成して出力する制御部 7 を備える。インバータ回路 3 に接続されるモータ8の一例は、誘導電動機又は同期電動機である。

10

20

30

40

20

30

40

50

#### [0013]

また、図1において、入力回路2の一端は集電装置51を介して架線50に接続され、他端は車輪53を介して大地電位を与えるレール52に接続されている。架線50から供給される直流電力または交流電力は、集電装置51を介して入力回路2の入力端に供給されると共に、入力回路2の出力端に生じた電力がインバータ回路3に供給される。

### [0014]

インバータ回路3において、正側スイッチング素子であるスイッチング素子4a1と、 負側スイッチング素子であるスイッチング素子4b1とは直列に接続されてU相の第1レ グを構成し、正側スイッチング素子であるスイッチング素子4a2と、負側スイッチング 素子であるスイッチング素子4b2とは直列に接続されてU相の第2レグを構成する。正 側スイッチング素子は正側アーム又は上側アームとも称され、負側スイッチング素子は負 側アーム又は下側アームとも称される。また、U相の第1レグをU1で表し、U相の第2 レグをU2で表す。

## [0015]

V相及びW相のレグも同様である。以下同様に説明すると、スイッチング素子5a1とスイッチング素子5b1とが直列に接続されてV相の第1レグを構成し、スイッチング素子5a2とスイッチング素子5b2とが直列に接続されてV相の第2レグを構成する。また、スイッチング素子6a1とスイッチング素子6b1とが直列に接続されてW相の第1レグを構成し、スイッチング素子6a2とスイッチング素子6b2とが直列に接続されてW相の第2レグを構成する。なお、U相と同様に、V相の第1レグをV1で表し、V相の第2レグをV2で表し、W相の第1レグをW1で表し、W相の第2レグをW2で表す。

#### [0016]

このようにして、インバータ回路 3 は、各相におけるそれぞれの第 1 レグ及び第 2 レグが並列に接続された 3 相インバータ回路を構成する。なお、スイッチング素子 4 a 1 , 4 a 2 , 5 a 1 , 5 a 2 , 6 a 1 , 6 a 2 , 4 b 1 , 4 b 2 , 5 b 1 , 5 b 2 , 6 b 1 , 6 b 2 には、逆並列ダイオードが内蔵された M O S F E T (Metal-Oxide-Semiconductor Field-Effect Transistor) 又は I G B T (Insulated Gate Bipolar Transistor) が好適である。

## [0017]

制御部7は、PWM (Pulse Width Modulation)信号によってインバータ回路3のスイッチング素子4a1,4a2,5a1,5a2,6a1,6a2,4b1,4b2,5b1,5b2,6b1,6b2をPWM制御する。制御部7のPWM制御により、インバータ回路3は、入力回路2から印加された直流電圧を任意周波数及び任意電圧の交流電圧に変換してモータ8を駆動する。

# [0018]

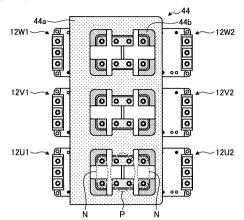

図2は、実施の形態1に係る電力変換装置に用いる半導体モジュール12における各端子の配置を示す平面図であり、図3は、図2に示した半導体モジュール12を図1に示したインバータ回路3に適用した回路図である。

### [0019]

実施の形態 1 に係る電力変換装置に用いる半導体モジュール 1 2 は、図 2 では図示していないが、モジュール筐体であるパッケージ 3 0 の内部に、直列接続された一対の半導体スイッチング素子を具備している。

### [0020]

図 2 に示すように、パッケージ 3 0 における一方の表面側には、第 1 端子 M 1、第 2 端子 M 2 及び第 3 端子 M 3 が設けられている。第 1 端子 M 1 は半導体モジュール 1 2 における正極端子 P を構成し、第 2 端子 M 2 は半導体モジュール 1 2 における負極端子 N を構成し、第 3 端子 M 3 は、半導体モジュール 1 2 における交流端子 A C を構成する。

### [0021]

図 3 において、U 1 相に適用される半導体モジュール 1 2 U 1 は、トランジスタ素子の例示であるMOSFET4a1sと、いわゆるフライホイールダイオード (Free Wheeli

20

30

40

50

ng Diode: FWD)として動作するダイオード(以下「FWD」と表記)4a1dとが逆並列に接続されたスイッチング素子4a1と、MOSFET4b1sとFWD4b1dとが逆並列に接続されたスイッチング素子4b1とを有する。スイッチング素子4a1とスイッチング素子4b1とは直列に接続され、モジュール筐体であるパッケージ30内に収容され、半導体モジュール12U1におけるスイッチング素子対を構成している。U2相に適用される半導体モジュール12U2も、半導体モジュール12U1と同様に構成される。また、V1相及びV2相、並びにW1相及びW2相のそれぞれに適用される半導体モジュール12V1、12W2も、半導体モジュール12U1と同様に構成される。このように、半導体モジュール12U1、12U2、12V1、12V2、12W1、12W2のそれぞれは、直列接続された2つのスイッチング素子が収容された2in1モジュールである。

[0022]

また、MOSFET4a1sの正極であるドレインは第1端子M1に電気的に接続され、MOSFET4b1sの負極であるソースは第2端子M2に電気的に接続され、MOSFET4a1sの負極であるソース及びMOSFET4b1sの正極であるドレインは第3端子M3に電気的に接続される。半導体モジュール12U1,12U2,12V1,12V2,12W1,12W2の第1端子M1は、フィルタコンデンサ10の正極端子Pから引き出された正極側母線11Pに電気的に接続され、半導体モジュール12U1,12U2,12V1,12W2の第2端子M2は、フィルタコンデンサ10の負極端子Nから引き出された負極側母線11Nに電気的に接続される。なお、フィルタコンデンサ10は、電力変換に必要な直流電力を蓄積するコンデンサであり、電力変換装置における電力供給源である。

[0023]

また、半導体モジュール12 U 1 の第3 端子M 3 と半導体モジュール12 U 2 の第3 端子M 3 とは電気的に接続されて U 相交流端子を構成し、モータ8 の U 相に電気的に接続される。半導体モジュール12 V 1 の第3 端子M 3 と半導体モジュール12 V 2 の第3 端子M 3 とは電気的に接続されて V 相交流端子を構成し、モータ8 の V 相に電気的に接続される。半導体モジュール12 W 1 の第3 端子M 3 と半導体モジュール12 W 2 の第3 端子M 3 とは電気的に接続されて W 相交流端子を構成し、モータ8 の W 相に電気的に接続される

[0024]

なお、図 3 では、半導体モジュール 1 2 U 1 に搭載されるスイッチング素子 4 a , 4 b として、MOSFETを例示しているが、MOSFET以外であってもよい。MOSFET以外のスイッチング素子としは、IGBT又はIPM (Intelligent Power Module)が例示される。

[0025]

図2に戻り、半導体モジュール12における各端子の構成について説明する。半導体モジュール12のパッケージ30は、横長形状に形成されている。第1端子M1には2つの締結点32Pが設けられ、第2端子M2には2つの締結点32Nが設けられ、第3端子M3には3つの締結点32ACが設けられている。このように、第1端子M1、第2端子M2及び第3端子M3には、複数の締結点が設けられているので、モジュール内でのチップ間の分流がよくなり、モジュール内での発熱の偏りを小さくできるという利点がある。なお、図2では、第1端子M1における締結点32Pの数、及び第2端子M2における締結点32Nの数を2とし、第3端子M3における締結点32ACの数を3としているが、これらの締結点の数は電流容量に応じて変更してもよい。すなわち、第1端子M1における締結点32P及び第2端子M2における締結点32Nの数は、それぞれが3以上であってもよい。また、第3端子M3における締結点32ACの数は、2であってもよいし、4以上であってもよい。

[0026]

第1端子M1における2つの締結点32Pは、パッケージ30における一方側の短辺部

3 3 において、配列がパッケージ 3 0 の長手方向に直交する方向に並ぶように配列されている。第 2 端子 M 2 における 2 つの締結点 3 2 N は、第 1 端子 M 1 における 2 つの締結点 3 2 P の並びと平行で、且つ、第 1 端子 M 1 よりもパッケージ 3 0 の内方側すなわち中央部側に配列されている。第 3 端子 M 3 における 3 つの締結点 3 2 A C は、パッケージ 3 0 における他方側の短辺部 3 4 において、配列がパッケージ 3 0 の長手方向に直交する方向に並ぶように配列されている。これらの配列により、第 1 端子 M 1、第 2 端子 M 2 及び第 3 端子 M 3 における各締結点は、パッケージ 3 0 の長手方向に平行な短辺同士を結ぶ中心線 L 1 に対して、線対称の位置に配置される。

### [0027]

第1端子M1における1つの締結点32Pと、第2端子M2における1つの締結点32Nとは、距離 d だけ離間して配置されている。距離 d は絶縁に必要な距離である。距離 d は、第1端子M1に印加される電圧と第2端子M2に印加される電圧との差、すなわち第1端子M1と第2端子M2との間の電位差に応じて定めることができる。

## [0028]

第1端子M1における2つの締結点32Pは、締結点32Pにおける外方側の一辺35が、パッケージ30の一方側の短辺部33における一辺33aに沿うように、当該一辺33a側に目一杯寄せられて配置されている。さらに、パッケージ30の他方側の短辺部34では、第3端子M3における3つの締結点32ACを搭載するための台座部36が設けられている。第3端子M3における3つの締結点32ACは、締結点32ACにおける外方側の一辺37が、台座部36における長手方向の一辺36aに沿うように、当該一辺36a側に目一杯寄せられて配置されている。

#### [0029]

第1端子M1における2つの締結点32P及び第3端子M3における3つの締結点32ACを上記のように構成することにより、半導体モジュール12の筐体であるパッケージ30が大きくなるのを抑制しつつ、パッケージ30内に収容する半導体素子の搭載面積を確保することが可能となる。

### [0030]

なお、図2では、第1端子M1をパッケージ30の外方側に配置し、第2端子M2をパッケージ30の内方側に配置しているが、これらの関係を逆にしてもよい。すなわち、第2端子M2をパッケージ30の外方側に配置し、第1端子M1をパッケージ30の内方側に配置してもよい。

## [0031]

次に、実施の形態 1 の電力変換装置における 6 つの半導体モジュールの配置について、図 4 を参照して説明する。図 4 は、実施の形態 1 の電力変換装置における 6 つの半導体モジュールの配置例を模式的に示す図である。

### [0032]

実施の形態1の電力変換装置における6つの半導体モジュールの配置に関する特徴は、以下の通りである。なお、以下の説明では、第1端子M1(P)を正極直流端子、第2端子M2(N)を負極直流端子、第3端子M3(AC)を交流端子と称する。

### [0033]

- (1)同一相の半導体モジュールを構成する2つの半導体モジュールにおける正極直流 端子同士を向かい合わせて配置している。

- (2)同一相の半導体モジュールを構成する2つの半導体モジュールを半導体モジュール群とするときに、3つの半導体モジュール群を半導体モジュール群内の2つの半導体モジュールの配列方向に直交する方向に配列している。

- (3)半導体モジュール群におけるそれぞれの正極直流端子、負極直流端子及び交流端子は、各半導体モジュールの短辺に平行に引いた中心線 L 2 に対して、線対称の位置に配置される。

- (4)同一相の半導体モジュールにおける正極直流端子同士が接近して配置されており、同一相の半導体モジュールにおけるモジュール間の間隔 d 1 が、半導体モジュール群間

10

20

30

40

の間隔すなわち異なる相の半導体モジュールにおけるモジュール間の間隔 d 2 よりも小さくなっている。

### [0034]

上記の特徴について補足する。図4において、W2相を構成する半導体モジュール12W2は、W1相を構成する半導体モジュール12W1を配置面に直交する軸に対して180度回転したものに相当する。すなわち、半導体モジュール12W1と半導体モジュール12W2とは、回転対称の関係にある。また、半導体モジュール12W1と半導体モジュール12W2とは、中心線L2に対して鏡像の関係にある。すなわち、半導体モジュール12W1と半導体モジュール12W2とは、線対称の関係にある。

### [0035]

上記のような、回転対称且つ線対称の関係が満たされるのは、上述したように、第1端子M1、第2端子M2及び第3端子M3における各締結点が、図2に示すように、パッケージ30の中心線L1に対して線対称となるように配置されているからである。これにより、同一相の半導体モジュールにおける正極直流端子同士が向かい合う関係になる。正極直流端子同士は、半導体モジュール12が同相であるか異相であるかに拘わらず、同電位で変動する端子であり、インバータ回路3が電力変換動作を行う場合の電位も同電位で変動する。このため、端子間の電位差が理論的には零となり、向かい合う正極直流端子同士を近づけることができる。これにより、モジュール間の間隔d1を縮めることが可能となる。

## [0036]

なお、上述の効果は、負極直流端子を辺部に配置し、負極直流端子同士を向かい合わせ て配置した場合も同様に得られる。

## [0037]

図5は、実施の形態1に係る電力変換装置を鉄道車両に搭載した場合の構成例を示す図であり、鉄道車両に搭載される電力変換装置の内部を車両上部側からレール側に向けて視認したときの正視図である。図6は、ラミネートブスバーと半導体モジュールとの接続状態を示す平面図である。

#### [0038]

図5に示すように、電力変換装置は、放熱器65、ゲート制御ユニット67、断流器及びI/Fユニット68、並びにインバータ装置70を備えて構成される。また、インバータ装置70は、ゲート駆動回路基板40、フィルタコンデンサ10、素子部42及びラミネートブスバー44を有している。なお、実際の車両搭載状態では、放熱器65を除く、ゲート制御ユニット67、断流器及びI/Fユニット68、並びにインバータ装置70は、筐体66の内部に収容されて外気から遮蔽される。一方、放熱器65は、外気に触れるように筐体66の外部に取り付けられ、冷却風にて冷却可能に構成される。

### [0039]

素子部42は、図2に示した半導体モジュール12を複数含む構成部である。図5では、素子部42として、半導体モジュール12W1,12W2が図示されている。ゲート駆動回路基板40は、素子部42の半導体モジュール12をPWM駆動するのに必要な駆動信号を生成するゲート駆動回路40aを搭載した基板である。断流器及びェノFユニット68は、インバータ装置70に流れる電流を遮断する機能、及びゲート制御ユニット67とゲート駆動回路40aとの間の信号授受を行う機能を有する構成部である。

### [0040]

フィルタコンデンサ 1 0 と、素子部 4 2 を構成する半導体モジュール 1 2 とは、 L 字形状に形成されたラミネートブスバー 4 4 によって結ばれる。ラミネートブスバー 4 4 は、薄板金属板と絶縁物とがラミネート材で一体に被覆されている部品である。図 5 では、薄板金属板を成す第 1 導体部 4 4 a と、第 2 導体部 4 4 b とを示している。なお、ラミネートブスバー 4 4 に代えて、ラミネート材で被覆されていない積層ブスバーを用いてもよい

10

20

40

30

50

[0041]

20

30

40

図 6 に示すように、ラミネートブスバー 4 4 における第 1 導体部 4 4 a は、半導体モジュール 1 2 U 1 , 1 2 U 2 , 1 2 V 1 , 1 2 V 2 , 1 2 W 1 , 1 2 W 2 の正極直流端子に電気的に接続され、第 2 導体部 4 4 b は、半導体モジュール 1 2 U 1 , 1 2 U 2 , 1 2 V 1 , 1 2 V 2 , 1 2 W 1 , 1 2 W 2 の負極直流端子に電気的に接続される。

### [0042]

また、図 5 に示すように、ラミネートブスバー 4 4 における第 1 導体部 4 4 a は、フィルタコンデンサ 1 0 の正極端子 1 0 a に電気的に接続され、ラミネートブスバー 4 4 における第 2 導体部 4 4 b は、フィルタコンデンサ 1 0 の負極端子 1 0 b に電気的に接続される。これらの接続により、素子部 4 2 を構成する半導体モジュール 1 2 U 1 , 1 2 U 2 , 1 2 V 1 , 1 2 V 2 , 1 2 W 1 , 1 2 W 2 のそれぞれと、フィルタコンデンサ 1 0 との間が電気的に接続される。

[0043]

なお、図5及び図6では図示していないが、図1及び図3に示す回路構成とするには、同一相の半導体モジュールにおける交流端子AC同士を電気的に接続すればよい。この場合、図5及び図6に示したラミネートブスバー44の構成を変更して用いてもよいし、ラミネートブスバー44とは異なるラミネートブスバー又は導体バーを用いてもよい。

### [0044]

以上説明したように、実施の形態1に係る電力変換装置によれば、6つの半導体モジュールのうちで同一相の半導体モジュールを構成する2つの半導体モジュールからなる半導体モジュール群において、2つの半導体モジュールの第1端子同士又は第2端子同士を向かい合わせて配置すると共に、3つの半導体モジュール群を半導体モジュール群内の2つの半導体モジュールの配列方向に直交する方向に配列したので、2並列で配置される半導体モジュール間の間隔を小さくすることができ、インバータ回路を含む電力変換装置の更なる小型化を図ることが可能となる。

#### [0045]

実施の形態2.

図7は、実施の形態2の電力変換装置における6つの半導体モジュールの配置例を模式的に示す図である。実施の形態1では、図4に示すように、同一相の半導体モジュールを構成する2つの半導体モジュールにおける正極直流端子同士を向かい合わせて配置していた。これに対し、実施の形態2では、図7に示すように、同一相の半導体モジュールを構成する2つの半導体モジュールにおける交流端子同士を向かい合わせて配置している。その他の構成については、実施の形態1と同一又は同等であり、同一又は同等の構成部には同一符号を付して、重複する説明は省略する。

## [0046]

上述した特徴に加え、実施の形態2の構成では、以下の特徴を有する。

- (1)実施の形態1の構成と同様に、3つの半導体モジュール群を半導体モジュール群内の2つの半導体モジュールの配列方向に直交する方向に配列している。

- (2)半導体モジュール群におけるそれぞれの正極直流端子、負極直流端子及び交流端子は、各半導体モジュールの短辺に平行に引いた中心線L3に対して、線対称の位置に配置される。

(3)同一相の半導体モジュールにおける交流端子同士が接近して配置されており、同一相の半導体モジュールにおけるモジュール間の間隔d3が、半導体モジュール群間の間隔すなわち異なる相の半導体モジュールにおけるモジュール間の間隔d4よりも小さくなっている。

#### [0047]

実施の形態2の構成において、同一相の交流端子同士は、同電位で変動する端子であり、インバータ回路3が電力変換動作を行う場合の電位も同電位で変動する。このため、端子間の電位差が理論的には零となり、向かい合う交流端子同士を近づけることができる。これにより、モジュール間の間隔d3を縮めることが可能となる。

## [0048]

以上説明したように、実施の形態 2 に係る電力変換装置によれば、 6 つの半導体モジュールのうちで同一相の半導体モジュールを構成する 2 つの半導体モジュールからなる半導体モジュール群において、 2 つの半導体モジュールの第 3 端子同士を向かい合わせて配置すると共に、 3 つの半導体モジュール群を半導体モジュール群内の 2 つの半導体モジュールの配列方向に直交する方向に配列したので、 2 並列で配置される半導体モジュール間の間隔を小さくすることができ、インバータ回路を含む電力変換装置の更なる小型化を図ることが可能となる。

### [0049]

#### 実施の形態3.

実施の形態1,2では、図2に示す半導体モジュール12をインバータ回路3に適用した場合の実施の形態について説明したが、実施の形態3では、図2に示す半導体モジュール12をコンバータ回路に適用した場合の実施の形態について説明する。

#### [0050]

図8は、実施の形態3に係る電力変換装置の構成例を示す図である。図8に示す実施の 形態3に係る電力変換装置は、交流入力の電気車に適用される電力変換装置の一構成例で あり、コンバータ回路20、フィルタコンデンサ10及びインバータ回路3を有して構成 される。

## [0051]

図8において、架線50から集電装置51を介して集電された交流電圧は、変圧器56によって降圧された後に、コンバータ回路20によって直流電圧に変換される。変換された直流電圧は、フィルタコンデンサ10を介し、インバータ回路3によって任意周波数及び任意電圧の交流電圧に変換されてモータ8に印加され、モータ8が駆動される。

## [0052]

ここで、図8に示されるコンバータ回路20も、実施の形態1と同様に、各相は、正側スイッチング素子と負側スイッチング素子とが直列に接続されたレグを2組有する構成である。このため、図4又は図7の構成において、4つの半導体モジュール12U1,12U2,12V1,12V2を使用してコンバータ回路20を構成すれば、コンバータ回路20の小型化を図ることができる。

### [0053]

以上説明したように、実施の形態3に係る電力変換装置によれば、4つの半導体モジュールのうちで同一相の半導体モジュールを構成する2つの半導体モジュールからなる半導体モジュール群において、2つの半導体モジュールの第1端子同士、第2端子同士又は第3端子同士を向かい合わせて配置すると共に、2つの半導体モジュール群を半導体モジュール群内の2つの半導体モジュールの配列方向に直交する方向に配列したので、2並列で配置される半導体モジュール間の間隔を小さくすることができ、コンバータ回路を含む電力変換装置の更なる小型化を図ることが可能となる。

## [0054]

### 実施の形態4.

実施の形態1,2のインバータ回路3では、各相におけるそれぞれの第1レグ及び第2レグが並列に接続された3相インバータ回路を使用して1又は複数のモータ8を駆動する実施の形態について説明したが、実施の形態4では、第1レグ及び第2レグを並列に接続せずに構成した2つの3相インバータ回路を使用して1又は複数のモータ8を駆動する実施の形態について説明する。

## [0055]

図9は、実施の形態4に係る電力変換装置で用いるインバータ回路3Aの回路構成を示す図である。図1又は図3に示す実施の形態1と同一又は同等の構成部には同一符号を付して示している。

### [0056]

図 9 に示すインバータ回路 3 A では、スイッチング素子 4 a 1 , 4 a 2 , 5 a 1 , 5 a 2 , 6 a 1 , 6 a 2 , 4 b 1 , 4 b 2 , 5 b 1 , 5 b 2 , 6 b 1 , 6 b 2を具備する点は

10

20

30

40

20

30

図1又は図3に示すインバータ回路3と同様であるが、各相におけるそれぞれの第1レグ 及び第2レグが並列に接続されない点が相違点である。

### [0057]

なお、図9では、インバータ回路3Aを構成する一方の3相インバータ回路がモータ8aを駆動し、インバータ回路3Aを構成する他方の3相インバータ回路がモータ8bを駆動する構成を示しているが、モータ8a,8bは1台であっても複数台であってもよい。実施の形態1の構成でもインバータ回路3が駆動するモータ8は、1台であっても複数台であってもよく、この点は共通している。

### [0058]

図9に示すインバータ回路3Aの構成であっても、図4又は図7に示される配置例を採用することができる。また、この場合、図9の回路図に示されるように、正極側のスイッチング素子のドレインが正極側母線11Pに電気的に接続され、負極側のスイッチング素子のソースが負極側母線11Nに電気的に接続される回路構成となる。このため、図5及び図6に示すラミネートブスバー44を用いて、半導体モジュール12とフィルタコンデンサ10との間を接続することが可能となる。

#### [0059]

なお、以上の実施の形態に示した構成は、本発明の内容の一例を示すものであり、別の公知の技術と組み合わせることも可能であるし、本発明の要旨を逸脱しない範囲で、構成の一部を省略、変更することも可能である。

## 【符号の説明】

### [0060]

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図8】

# 【図7】

【図9】

## フロントページの続き

(56)参考文献 特開2015-89245(JP,A)

特開2003-18863(JP,A)

特開2015-142472(JP,A)

特開2015-104248(JP,A)

(58)調査した分野(Int.CI., DB名)

H 0 2 M 7 / 4 8