등록특허 10-2403113

(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2022년05월30일

(11) 등록번호 10-2403113

(24) 등록일자 2022년05월24일

- (51) 국제특허분류(Int. Cl.)

*H03M 13/11* (2006.01) *H03M 13/00* (2017.01)

*H04L 1/00* (2006.01)

- (52) CPC특허분류

*H03M 13/11* (2013.01)

*H03M 13/1102* (2013.01)

- (21) 출원번호 10-2021-0030403(분할)

- (22) 출원일자 2021년03월08일

심사청구일자 2021년03월08일

- (65) 공개번호 10-2021-0030324

- (43) 공개일자 2021년03월17일

- (62) 원출원 특허 10-2020-0059390

원출원일자 2020년05월18일

심사청구일자 2020년09월28일

- (30) 우선권주장

62/115,810 2015년02월13일 미국(US)

(뒷면에 계속)

- (56) 선행기술조사문현

KR1020130024704 A

KR1020120096154 A

- (73) 특허권자

삼성전자주식회사

경기도 수원시 영통구 삼성로 129 (매탄동)

- (72) 발명자

정홍실

경기도 수원시 영통구 삼성로 129(매탄동)

김경중

경기도 수원시 영통구 삼성로 129(매탄동)

명세호

경기도 수원시 영통구 삼성로 129(매탄동)

- (74) 대리인

정홍식, 김태현

전체 청구항 수 : 총 7 항

심사관 : 조춘근

## (54) 발명의 명칭 송신 장치 및 그의 부가 패리티 생성 방법

**(57) 요약**

송신 장치가 개시된다. 본 송신 장치는 아우터 인코딩된 비트들을 포함하는 입력 비트들을 인코딩하여 패리티 비트들을 생성하는 LDPC 인코더, 상기 패리티 비트들에서 일부 비트들을 평처링하는 평처링부 및 패리티 비트들에서 적어도 일부의 비트들을 선택하여, 이전 프레임에서 전송되는 부가 패리티 비트들을 생성하는 부가 패리티 생성부를 포함하며, 부가 패리티 비트들의 수는 현재 프레임에서 전송되는 아우터 인코딩된 비트들의 수 및 상기 평처링 이후 남은 패리티 비트들의 수에 기초하여 결정된다.

**대 표 도 - 도1**

(52) CPC특허분류

*H03M 13/6362* (2013.01)

*H04L 1/0041* (2013.01)

(30) 우선권주장

62/120,543 2015년02월25일 미국(US)

62/202,304 2015년08월07일 미국(US)

---

## 명세서

### 청구범위

#### 청구항 1

송신 방법에 있어서,

입력 비트들을 포함하는 정보어 비트들을 인코딩하여 생성된 패리티 비트들 중 하나 또는 그 이상의 비트들을 상기 정보어 비트들 및 상기 패리티 비트들 사이에 부가(append)하는 단계;

상기 패리티 비트들 중 하나 또는 그 이상의 비트들을 평처링하는 단계; 및

추가 패리티 비트들의 수를 산출하고, 상기 산출된 수에 대응되는 패리티 비트들을 선택하여 추가 패리티 비트들을 생성하는 단계;를 포함하며,

상기 부가된 하나 또는 그 이상의 비트들의 수는, 상기 입력 비트들의 수에 기초하여 결정되고,

상기 추가 패리티 비트들의 수는, 상기 입력 비트들의 수, 상기 평처링된 하나 또는 그 이상의 비트들의 수 및 상기 부가된 하나 또는 그 이상의 비트들의 수에 기초하여 결정되고,

상기 추가 패리티 비트들은, 제1 프레임에서 전송되고,

상기 부가된 하나 또는 그 이상의 비트들은, 제2 프레임에서 전송되고,

상기 제1 프레임은, 상기 제2 프레임 이전에 전송되는, 송신 방법.

#### 청구항 2

제1항에 있어서,

변조 차수에 기초하여 상기 추가 패리티 비트들을 변조하는 단계;를 더 포함하는 것을 특징으로 하는 송신 방법.

#### 청구항 3

제2항에 있어서,

상기 추가 패리티 비트들의 수는,

하기의 수학식에 기초하여 산출되는 것을 특징으로 하는 송신 방법:

$$N_{AP} = \left\lfloor \frac{N_{AP\_temp}}{n_{MOD}} \right\rfloor \times n_{MOD}$$

여기에서,  $N_{AP}$ 는 상기 추가 패리티 비트들의 수이고,  $N_{AP\_temp}$ 는 추가 패리티 비트들의 임시적인 수이고,  $n_{MOD}$ 는 변조 차수이다.

#### 청구항 4

제3항에 있어서,

상기 추가 패리티 비트들의 임시적인 수는,

하기의 수학식에 기초하여 산출되는 것을 특징으로 하는 송신 방법:

$$N_{AP\_temp} = \min \left\{ \begin{array}{l} 0.5 \times K \times (N_{outer} + N_{ldpc\_parity} - N_{punc} + N_{repeat}), \\ (N_{ldpc\_parity} + N_{punc} + N_{repeat}) \end{array} \right\}, K=0,1,2$$

$$\min(a,b) = \begin{cases} a, & \text{if } a \leq b \\ b, & \text{if } b < a \end{cases}$$

여기에서,  $N_{AP\_temp}$ 는 상기 추가 패리티 비트들의 임시적인 수이고, 이고,

$N_{ldpc\_parity}$ 는 상기 패리티 비트들의 수,  $N_{punc}$ 는 상기 평처링된 패리티 비트들의 수,  $N_{outer}$ 는 상기 입력 비트들의 수,  $N_{repeat}$ 는 상기 부가된 하나 또는 그 이상의 비트들의 수이고, K는 기 설정된 상수로 0,1,2 중 어느 하나의 값이다.

## 청구항 5

복수의 모드 중 하나의 모드에서 동작하는 수신 장치의 수신 방법에 있어서,

송신 장치로부터 수신된 제1 프레임을 복조하여 상기 제1 프레임의 값들을 생성하고, 상기 송신 장치로부터 수신된 제2 프레임을 복조하여 상기 제2 프레임의 값들을 생성하는 단계;

상기 송신 장치에서 평처링된 상기 제1 프레임의 비트 수에 기초하여 기 설정된 값들을 상기 제1 프레임의 값들에 삽입하는 단계;

상기 삽입된 제1 프레임의 값들 중 제1 값들을 상기 삽입된 제1 프레임의 값들 중 상기 제1 값들과 연관된 제2 값들과 합산하고, 상기 제2 프레임의 값들 중 제3 값들을 상기 삽입된 제1 프레임의 값들 중 상기 제3 값들과 연관된 제4 값들과 합산하는 단계;

상기 제1 및 제2 값들이 합산된 값들, 상기 제3 및 제4 값들이 합산된 값들 및 상기 삽입된 제1 프레임의 값들 중 나머지 값들 중에서 하나 또는 그 이상의 값들을 디인터리빙하여, 상기 하나 또는 그 이상의 값들이 디인터리빙된 값들을 제공하는 단계; 및

LDPC(low density parity check) 코드에 기초하여 상기 제공된 값들을 디코딩하는 단계;를 포함하며,

상기 나머지 값들은, 상기 삽입된 제1 프레임의 값들 중에서 상기 제1 값들, 상기 제2 값들 및 상기 제4 값들을 제외한 값들이고,

상기 제1 프레임은, 상기 송신 장치의 모드가 기 설정된 모드인 경우, 정보어 비트들 및 패리티 비트들 사이에 부가된 하나 또는 그 이상의 패리티 비트들에 대응되는 값들을 포함하고,

상기 제2 프레임은, 추가 패리티 비트들에 대응되는 값들을 포함하고,

상기 추가 패리티 비트들의 수는, 상기 부가된 패리티 비트들의 수에 기초하여 결정되고,

상기 제1 값들은, 상기 부가된 패리티 비트들에 대응되고,

상기 제3 값들은, 상기 추가 패리티 비트들에 대응되고,

상기 제2 프레임은, 상기 제1 프레임 이전에 수신되는 수신 방법.

## 청구항 6

제5항에 있어서,

상기 추가 패리티 비트들의 수는,

하기의 수학식에 기초하여 산출되는 것을 특징으로 하는 수신 방법:

$$N_{AP} = \left\lfloor \frac{N_{AP\_temp}}{n_{MOD}} \right\rfloor \times n_{MOD}$$

여기에서,  $N_{AP}$ 는 상기 추가 패리티 비트들의 수이고,  $N_{AP\_temp}$ 는 추가 패리티 비트들의 임시적인 수이고,  $n_{MOD}$ 는 변조 차수이다.

### 청구항 7

제6항에 있어서,

상기 추가 패리티 비트들의 임시적인 수는,

하기의 수학식에 기초하여 산출되는 것을 특징으로 하는 수신 방법:

$$N_{AP\_temp} = \min \left\{ \frac{0.5 \times K \times (N_{outer} + N_{ldpc\_parity} - N_{punc} + N_{repeat}),}{(N_{ldpc\_parity} + N_{punc} + N_{repeat})} \right\}, K=0,1,2$$

$$\min(a,b) = \begin{cases} a, & \text{if } a \leq b \\ b, & \text{if } b < a \end{cases}$$

여기에서,  $N_{AP\_temp}$ 는 상기 추가 패리티 비트들의 임시적인 수이고,  $N_{ldpc\_parity}$ 는 상기 패리티 비트들의 수,  $N_{punc}$ 는 상기 평처링된 패리티 비트들의 수,  $N_{outer}$ 는 상기 정보어 비트들에 포함된 입력 비트들의 수,  $N_{repeat}$ 는 상기 부가된 패리티 비트들의 수이고,  $K$ 는 기 설정된 상수로 0,1,2 중 어느 하나의 값이다.

## 발명의 설명

### 기술 분야

[0001]

본 발명은 송신 장치 및 그의 부가 패리티 생성 방법에 관한 것으로, 더욱 상세하게는 부가 패리티 비트들을 생성하여 전송하는 본 발명은 송신 장치 및 그의 부가 패리티 생성 방법에 관한 것이다.

### 배경 기술

[0002]

21세기 정보화 사회에서 방송 통신 서비스는 본격적인 디지털화, 다채널화, 광대역화, 고품질화의 시대를 맞이하고 있다. 특히, 최근에 고화질 디지털 TV 및 휴대방송 기기 보급이 확대됨에 따라 디지털 방송 서비스도 다양한 수신방식 지원에 대한 요구가 증대되고 있다.

[0003]

이러한 요구에 따라 표준 그룹에서는 다양한 표준을 제정하여, 사용자의 니즈를 만족시킬 수 있는 다양한 서비스를 제공하고 있다. 이에 따라, 보다 우수한 성능을 통해 보다 나은 서비스를 사용자에게 제공하기 위한 방안의 모색이 요청된다.

### 발명의 내용

### 해결하려는 과제

[0004]

본 발명은 상술한 필요성에 따른 것으로, 본 발명의 목적은 패리티 비트들을 이용하여 부가 패리티 비트들을 생성하여 전송하는 본 발명은 송신 장치 및 그의 부가 패리티 생성 방법에 관한 것이다.

## 과제의 해결 수단

- [0005] 이상과 같은 목적을 달성하기 위한 본 발명의 일 실시 예에 따른 송신 장치는 아우터 인코딩된 비트들을 포함하는 입력 비트들을 인코딩하여 패리티 비트들을 생성하는 LDPC 인코더, 상기 패리티 비트들에서 일부 비트들을 평처링하는 평처링부 및 상기 패리티 비트들에서 적어도 일부의 비트들을 선택하여, 이전 프레임에서 전송되는 부가 패리티 비트들을 생성하는 부가 패리티 생성부를 포함하며, 상기 부가 패리티 비트들의 수는 현재 프레임에서 전송되는 아우터 인코딩된 비트들의 수 및 상기 평처링 이후 남은 패리티 비트들의 수에 기초하여 결정된다.

- [0006] 여기에서, 상기 입력 비트들 및 상기 패리티 비트들로 구성된 LDPC 코드워드의 적어도 일부의 비트들이 상기 현재 프레임에서 리피티션되어 전송되도록, 상기 LDPC 코드워드의 적어도 일부의 비트들을 상기 LDPC 코드워드에서 리피티션하는 리피티션부를 더 포함할 수 있다.

- [0007] 그리고, 상기 부가 패리티 비트들의 수는 상기 리피티션이 수행되는 경우, 상기 현재 프레임에서 전송되는 아우터 인코딩된 비트들의 수, 상기 평처링 이후 남은 패리티 비트들의 수 및 상기 현재 프레임에서 리피티션되는 비트들의 수에 기초하여 결정될 수 있다.

- [0008] 또한, 상기 부가 패리티 비트들의 수는 수학식 8에 기초하여 산출된 부가 패리티 비트들의 임시적인 수  $N_{AP\_temp}$ 에 기초하여 산출될 수 있다.

- [0009] 여기에서, 상기 부가 패리티 비트들의 수는 수학식 10에 기초하여 산출될 수 있다.

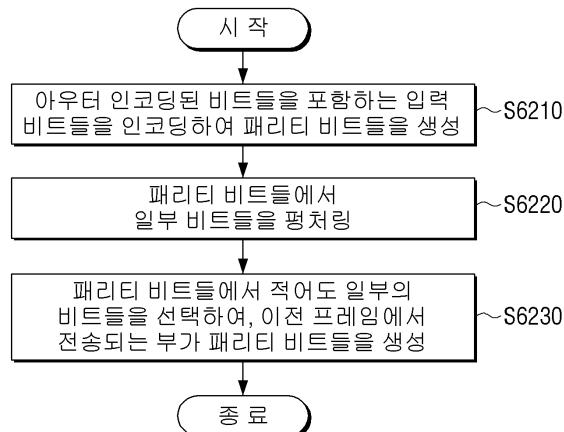

- [0010] 한편, 본 발명의 일 실시 예에 따른 송신 장치의 부가 패리티 생성 방법은 아우터 인코딩된 비트들을 포함하는 입력 비트들을 인코딩하여 패리티 비트들을 생성하는 단계, 상기 패리티 비트들에서 일부 비트들을 평처링하는 단계 및 상기 패리티 비트들에서 적어도 일부의 비트들을 선택하여, 이전 프레임에서 전송되는 부가 패리티 비트들을 생성하는 단계를 포함하며, 상기 부가 패리티 비트들의 수는 현재 프레임에서 전송되는 아우터 인코딩된 비트들의 수 및 상기 평처링 이후 남은 패리티 비트들의 수에 기초하여 결정된다.

- [0011] 여기에서, 상기 입력 비트들 및 상기 패리티 비트들로 구성된 LDPC 코드워드의 적어도 일부의 비트들이 상기 현재 프레임에서 리피티션되어 전송되도록, 상기 LDPC 코드워드의 적어도 일부의 비트들을 상기 LDPC 코드워드에서 리피티션하는 단계를 더 포함할 수 있다.

- [0012] 또한, 상기 부가 패리티 비트들의 수는 상기 리피티션이 수행되는 경우, 상기 현재 프레임에서 전송되는 아우터 인코딩된 비트들의 수, 상기 평처링 이후 남은 패리티 비트들의 수 및 상기 현재 프레임에서 리피티션되는 비트들의 수에 기초하여 결정될 수 있다.

- [0013] 한편, 상기 부가 패리티 비트들의 수는 수학식 8에 기초하여 산출된 부가 패리티 비트들의 임시적인 수  $N_{AP\_temp}$ 에 기초하여 산출될 수 있다.

- [0014] 여기에서, 상기 부가 패리티 비트들의 수는 하기의 수학식 10에 기초하여 산출될 수 있다.

## 발명의 효과

- [0015] 이상과 같은 본 발명의 다양한 실시 예에 따르면, 패리티 비트들 중 일부 비트들이 추가적으로 전송될 수 있어, 부호어 이득을 얻음과 동시에 다이버시티 이득도 얻을 수 있게 된다.

## 도면의 간단한 설명

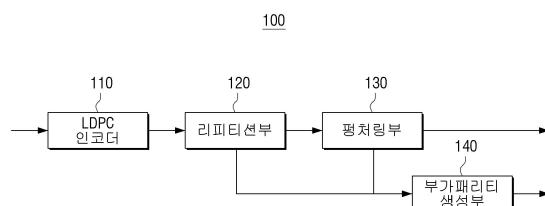

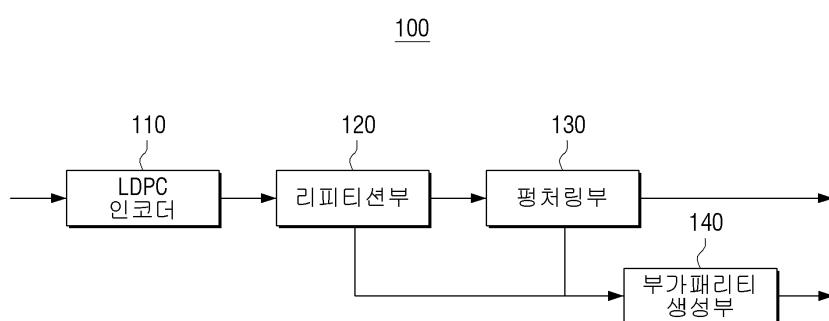

- [0016] 도 1은 본 발명의 일 실시 예에 따른 송신 장치의 구성을 설명하기 위한 블록도,

도 2 및 도 3은 본 발명의 일 실시 예에 따른 패리티 검사 행렬을 설명하기 위한 도면들,

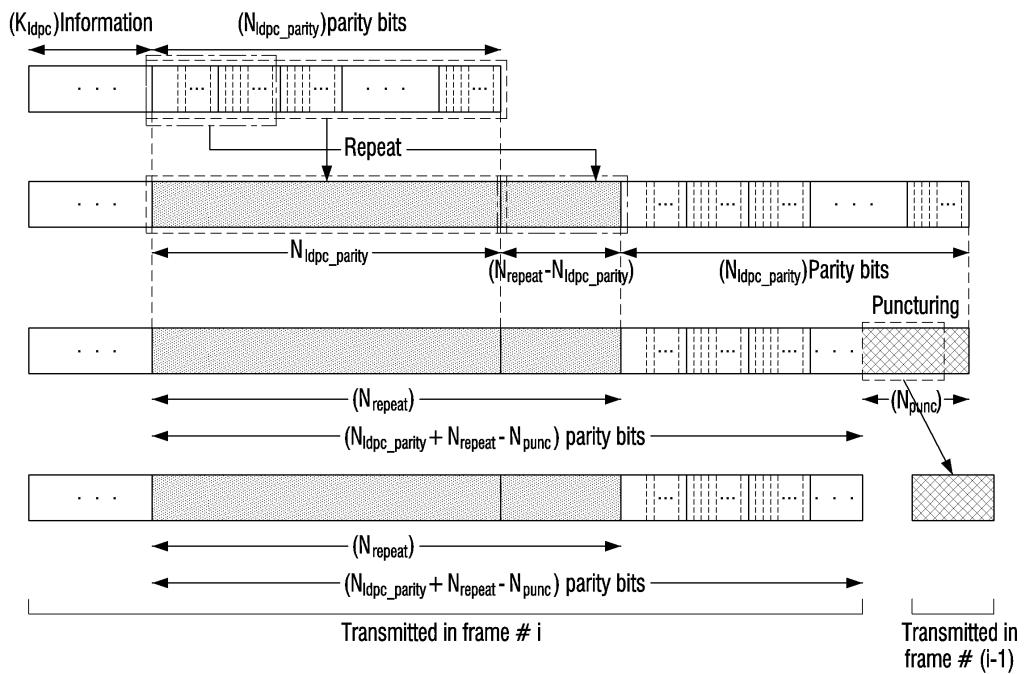

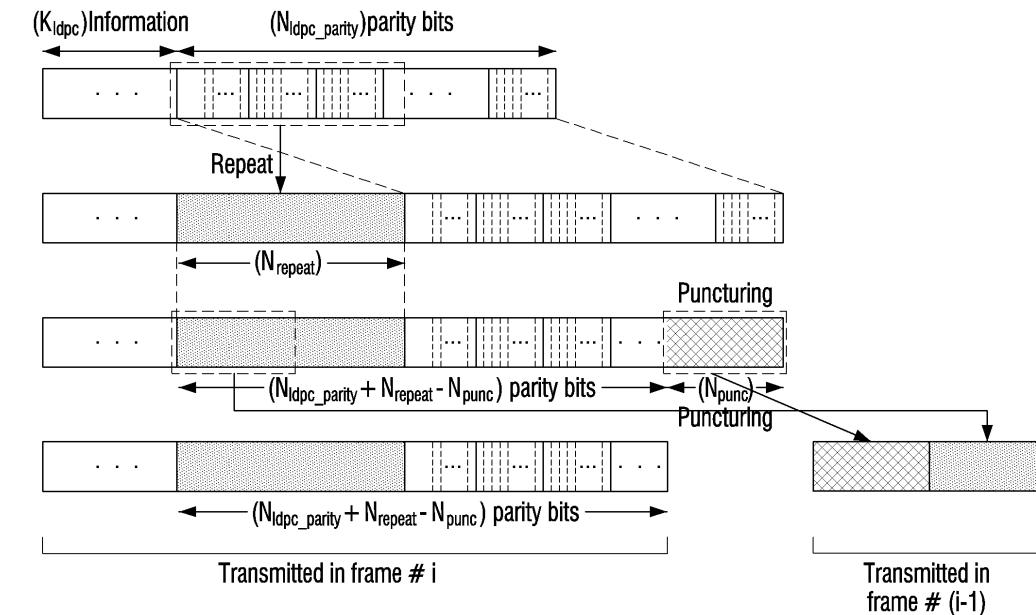

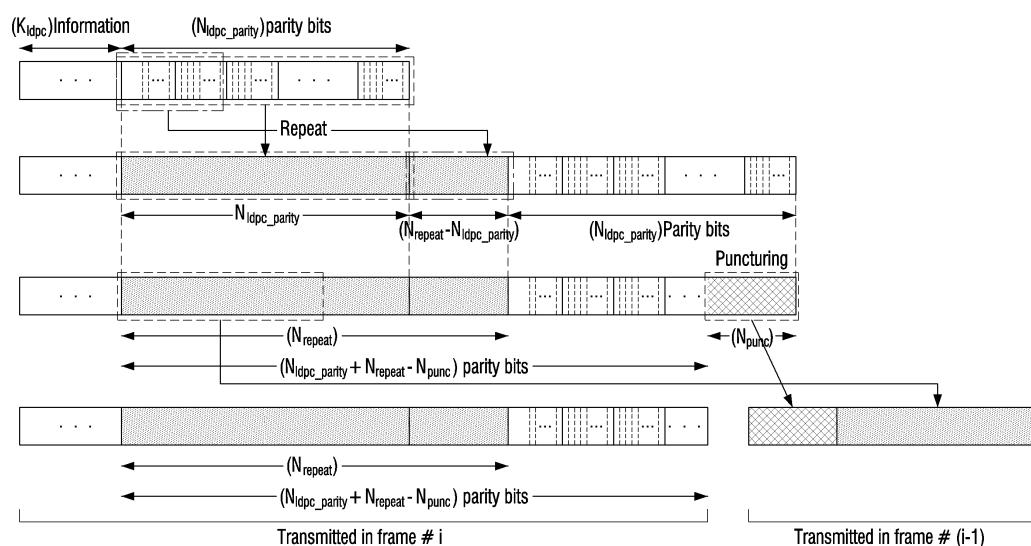

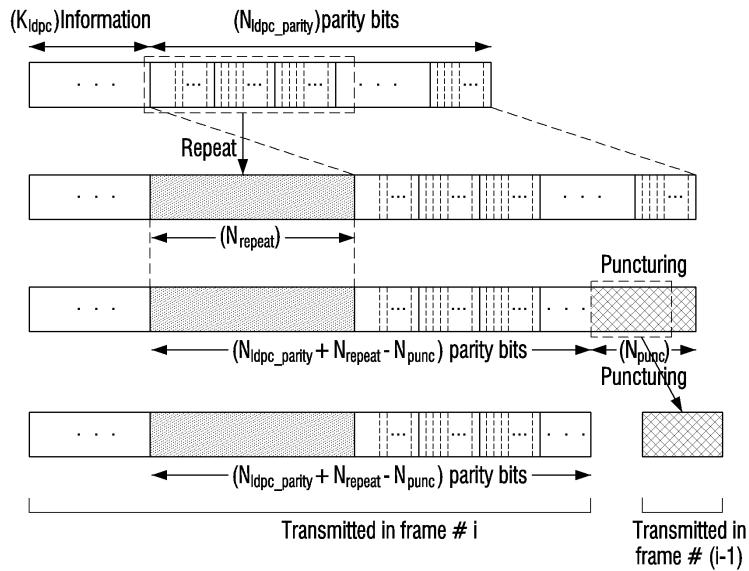

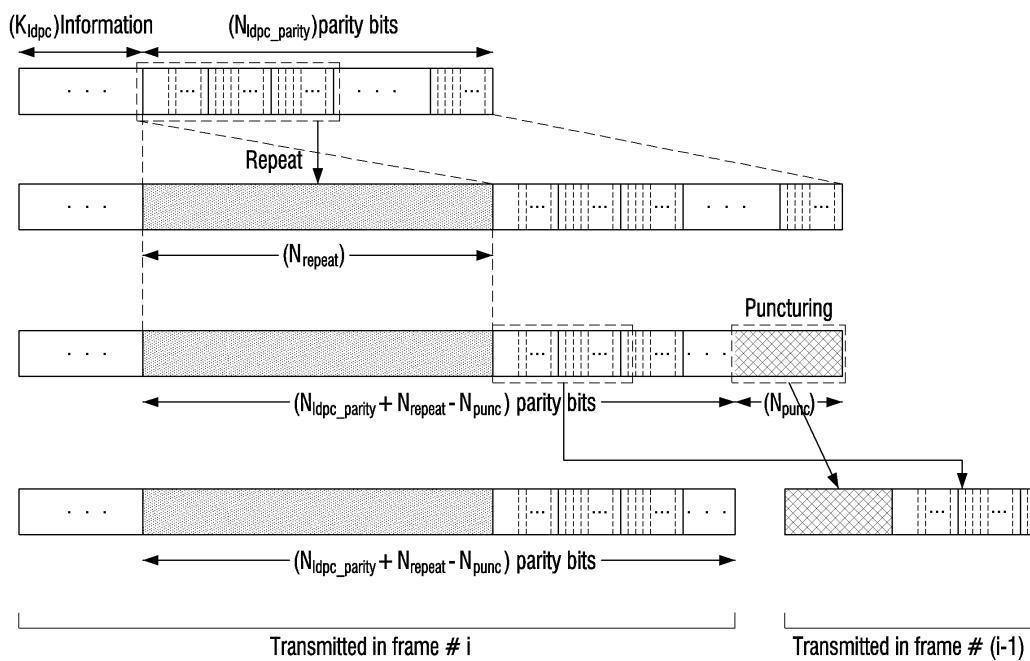

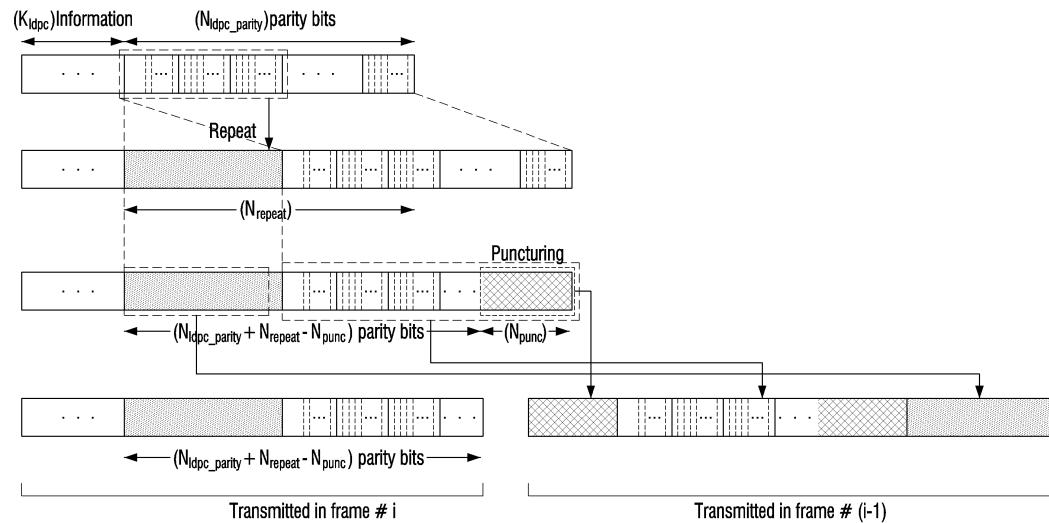

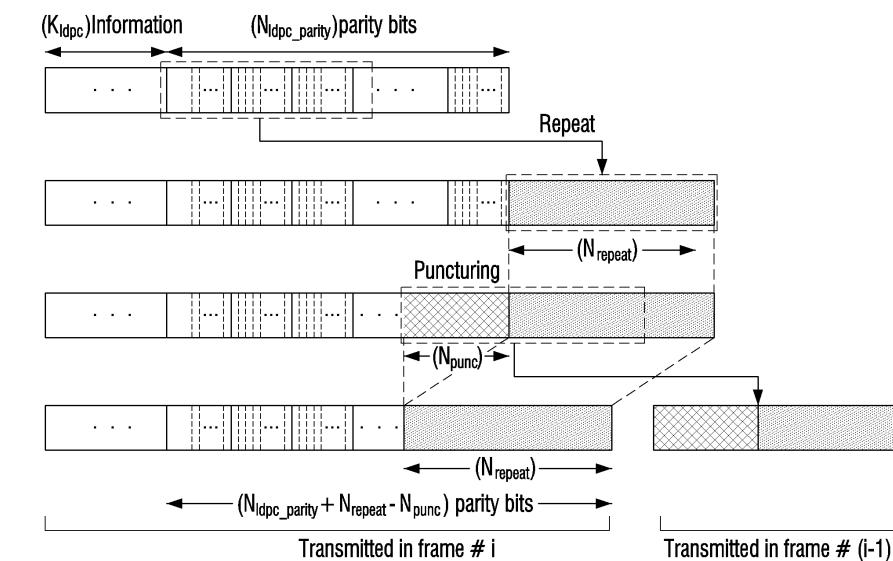

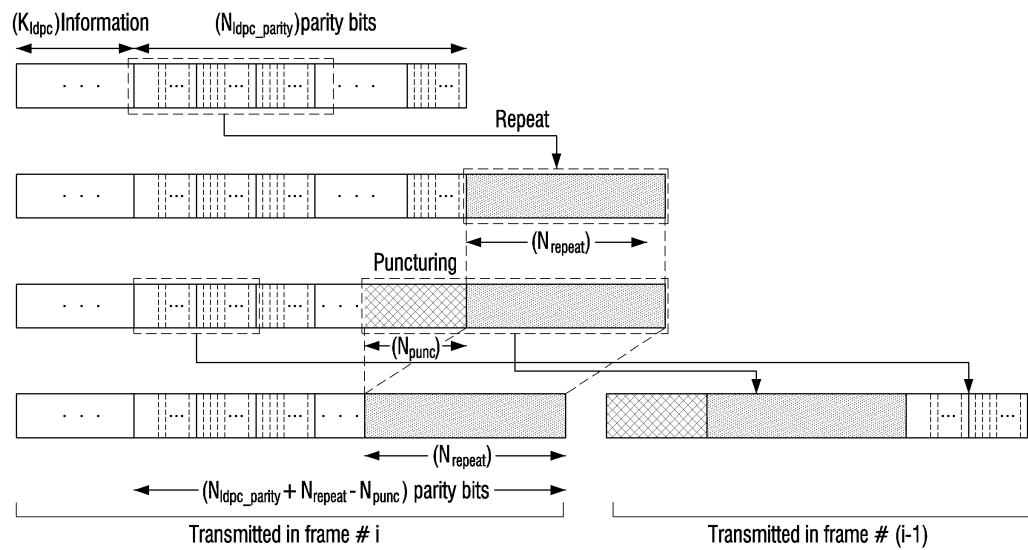

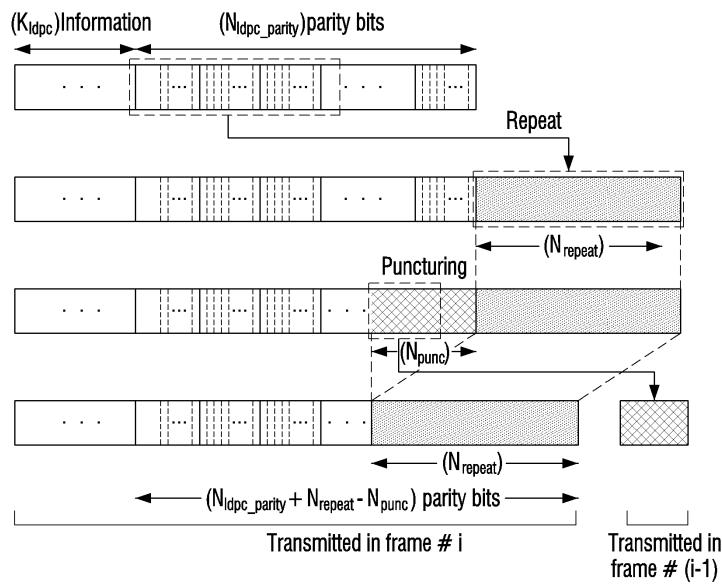

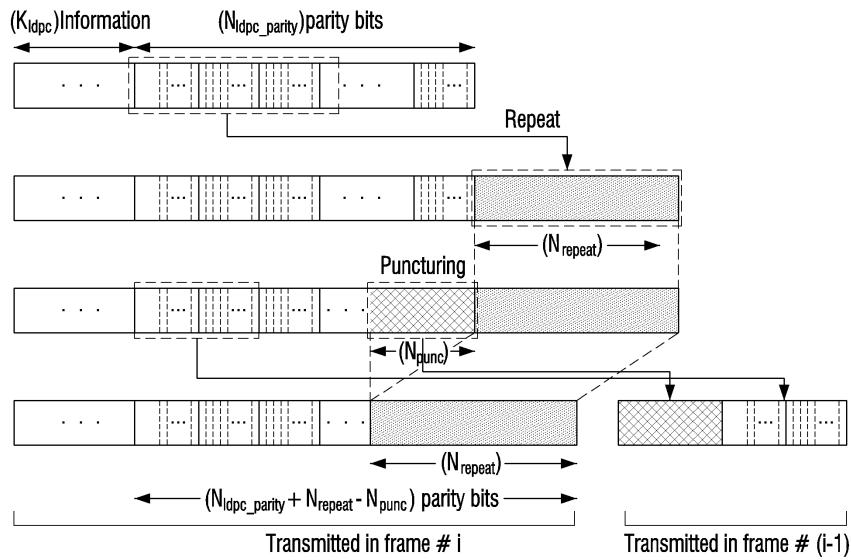

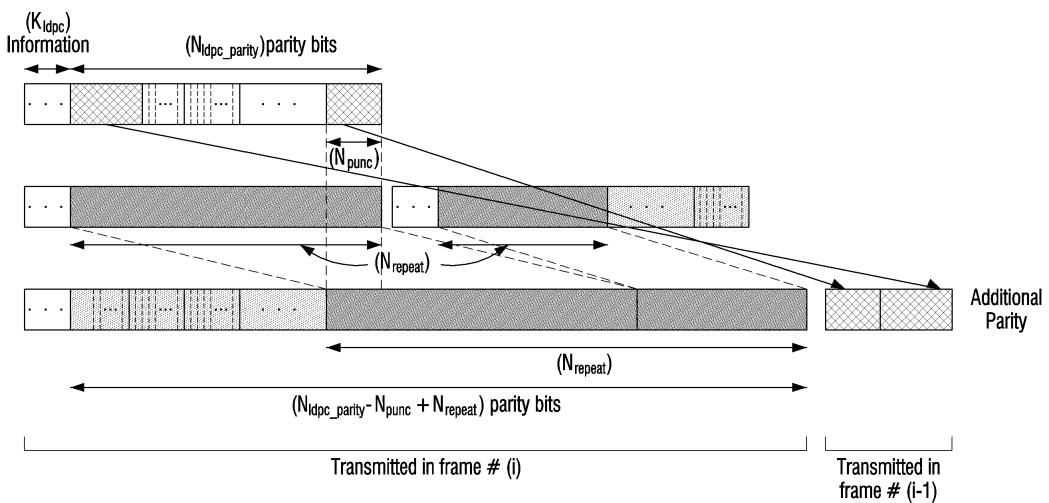

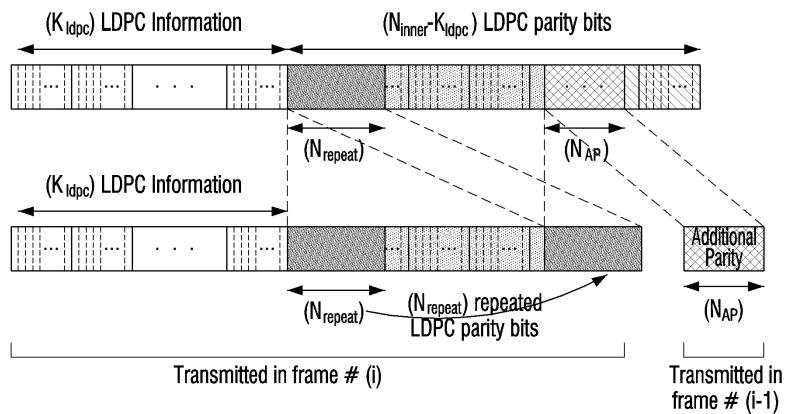

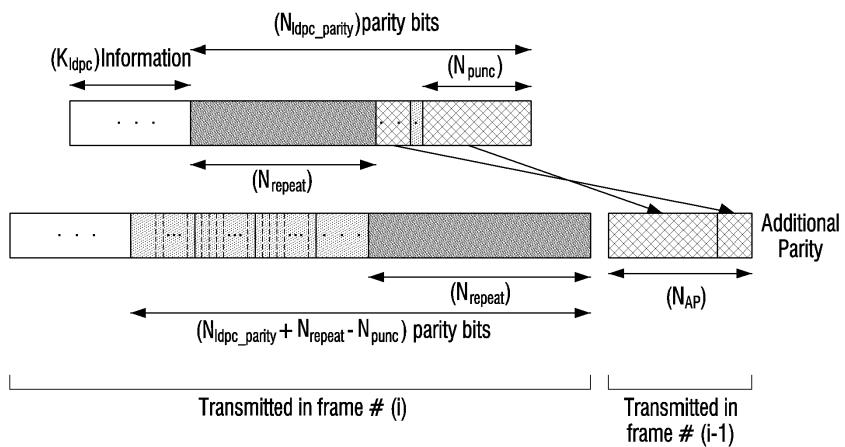

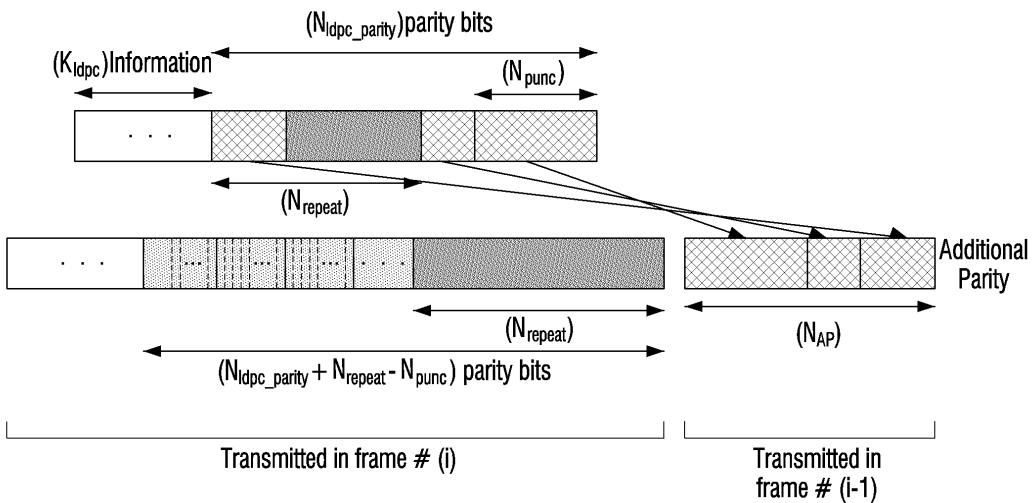

도 4 내지 도 7은 본 발명의 일 실시 예에 따른 리피티션을 설명하기 위한 블록도,

도 8 내지 도 11은 본 발명의 일 실시 예에 따른 평처링을 설명하기 위한 블록도,

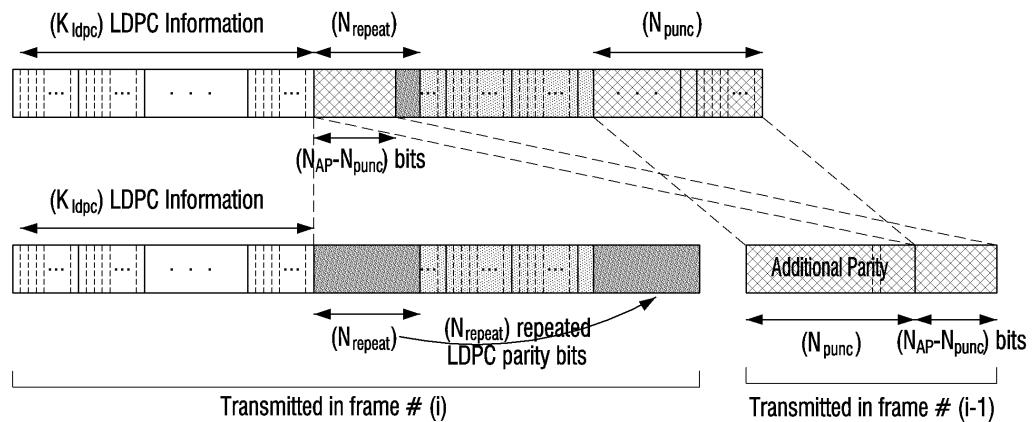

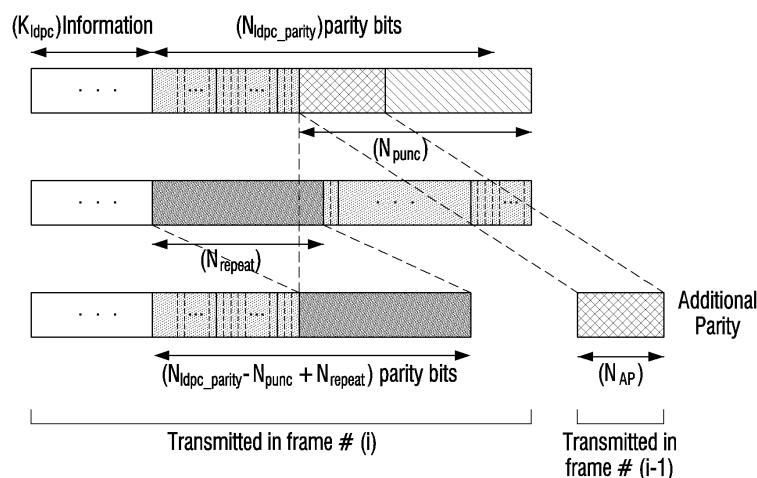

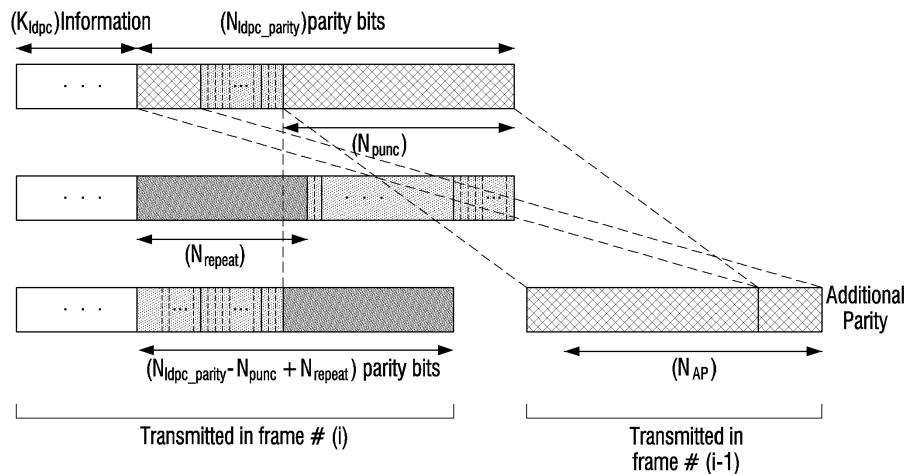

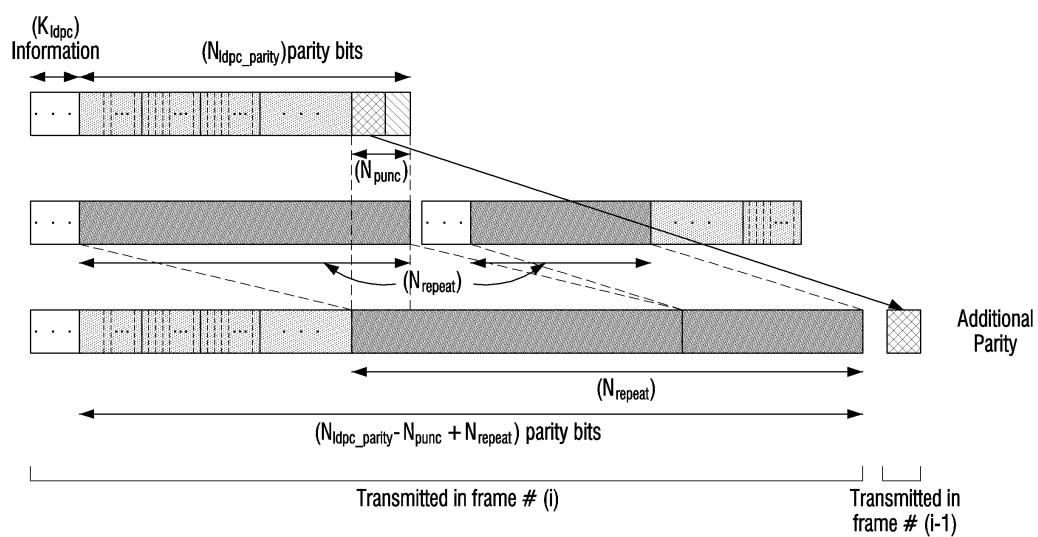

도 12 내지 도 40은 본 발명의 일 실시 예에 따른 부가 패리티 비트들을 생성하는 방법을 설명하기 위한 도면들,

도 41은 본 발명의 일 실시 예에 따른 프레임 구조를 설명하기 위한 도면,

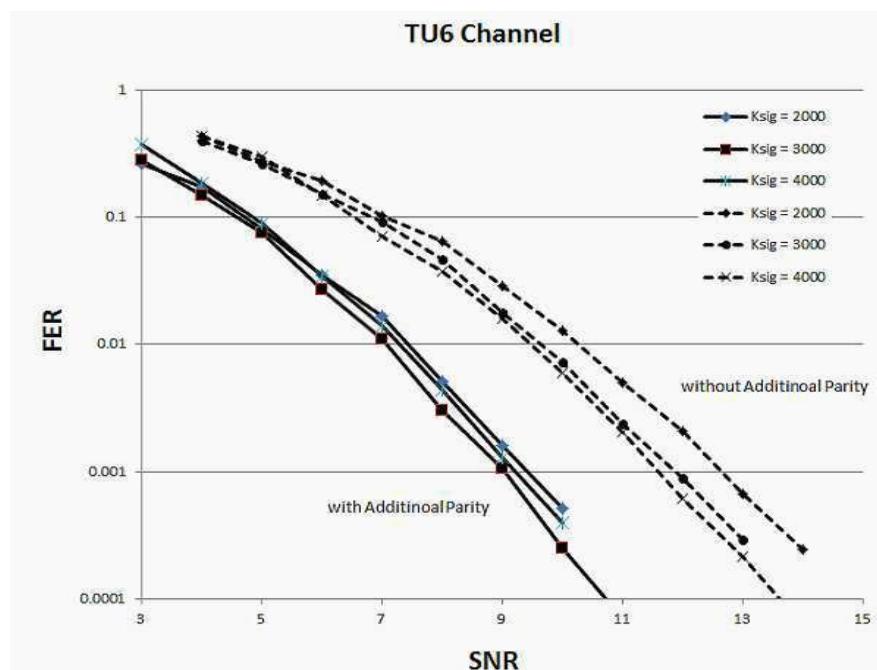

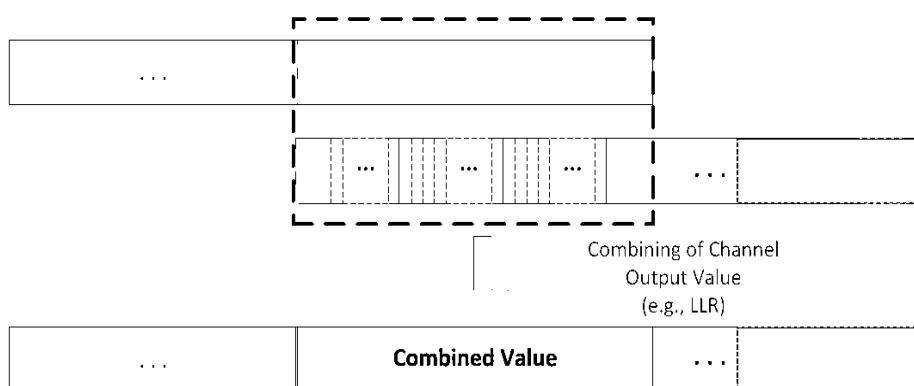

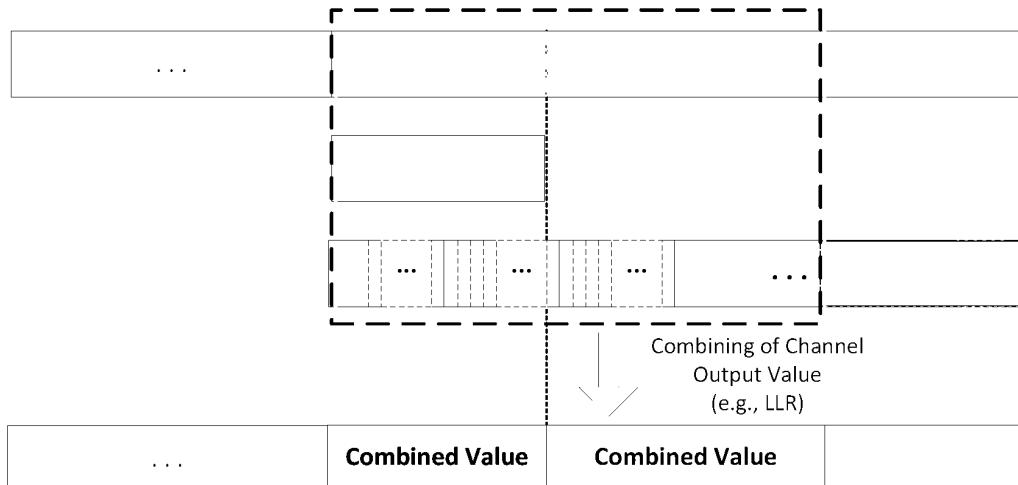

도 42 및 도 43은 본 발명의 일 실시 예에 따른 송신 장치의 세부 구성을 설명하기 위한 블록도들, 도 44 내지 도 57은 본 발명의 일 실시 예에 따라 시그널링을 처리하는 방법을 설명하기 위한 도면들, 도 58 및 도 59는 본 발명의 일 실시 예에 따른 수신 장치의 구성을 설명하기 위한 블록도, 도 60 및 도 61은 본 발명의 일 실시 예에 따른 수신 장치의 LLR 값을 컴비인하는 예를 설명하기 위한 도면들, 도 62는 본 발명의 일 실시 예에 따른 L1 시그널의 길이에 대한 정보가 제공되는 예를 나타낸 도면, 도 63은 본 발명의 일 실시 예에 따른 부가 패리티 생성 방법을 설명하기 위한 흐름도, 그리고 도 64는 본 발명의 일 실시 예에 따른 부가 패리티를 사용할 경우 얻을 수 있는 부호 이득과 다이버시트 이득을 설명하기 위한 도면이다.

### 발명을 실시하기 위한 구체적인 내용

- [0017] 이하에서는 첨부된 도면을 참조하여 본 발명을 더욱 상세하게 설명한다.

- [0018] 도 1은 본 발명의 일 실시 예에 따른 송신 장치의 구성을 나타내는 블록도이다. 도 1을 참조하면, 송신 장치(100)는 LDPC 인코더(110), 리퍼티션부(120), 평처링부(130) 및 부가 패리티 생성부(140)를 포함한다.

- [0019] LDPC 인코더(110)는 입력 비트들을 인코딩 즉, LDPC(Low density parity check) 인코딩하여 패리티 비트들 즉, LDPC 패리티 비트들을 생성한다.

- [0020] 구체적으로, 입력 비트들은 LDPC 인코딩을 위한 LDPC 정보어 비트들로, 정보어 비트들(information bits) 및 정보어 비트들이 아우터 인코딩되어 생성된 패리티 비트들(또는, 패리티 체크 비트들)을 포함하는 아우터 인코딩된 비트들 및, 제로 비트들(zero bits)(즉, 0 값을 갖는 비트들)을 포함할 수 있다.

- [0021] 여기에서, 정보어 비트들은 시그널링(signaling)일 수 있다. 예를 들어, 정보어 비트들은 송신 장치(100)가 전송하는 데이터(예를 들어, 방송 데이터)를 처리하기 위해 요구되는 정보를 포함할 수 있다.

- [0022] 또한, 아우터 코드(outer code)는 연접 코드(concatenated code)에서 이너 코드(inner code) 이전에 수행되는 코드로, BCH(Bose, Chaudhuri, Hocquenghem), CRC(cyclic redundancy check) 등 다양한 인코딩 방식이 이용될 수 있다. 이 경우, 이너 코드는 LDPC 코드가 될 수 있다.

- [0023] 구체적으로, LDPC 코드의 경우, 코드 레이트(code rate) 및 코드 길이(code length)에 따라 일정한 수의 LDPC 정보어 비트들이 요구된다. 따라서, 정보어 비트들이 아우터 인코딩되어 생성된 아우터 인코딩된 비트들의 수가 요구되는 LDPC 정보어 비트들의 수보다 작은 경우, 요구되는 LDPC 정보어 비트들의 수를 맞추기 위해 적절한 수의 제로 비트들이 패딩된다. 이에 따라, 아우터 인코딩된 비트들 및 패딩된 제로 비트들이 LDPC 인코딩에 요구되는 비트 수만큼의 LDPC 정보어 비트들을 구성할 수 있다.

- [0024] 한편, 패딩된 제로 비트들은 LDPC 인코딩을 위한 일정한 비트 수를 맞추는데만 필요한 비트들이므로, LDPC 인코딩된 이후 수신 장치(200)로 전송되지 않게 된다. 이와 같이, 제로 비트들을 패딩하는 절차 또는 제로 비트들을 패딩하고 LDPC 인코딩 후 수신 장치(200)로 전송하지 않는 절차를 쇼트닝이라 할 수 있다. 이 경우, 패딩된 제로 비트들을 쇼트닝 비트들(또는, 쇼트닝된 비트들(shortened bits))이라 할 수 있다.

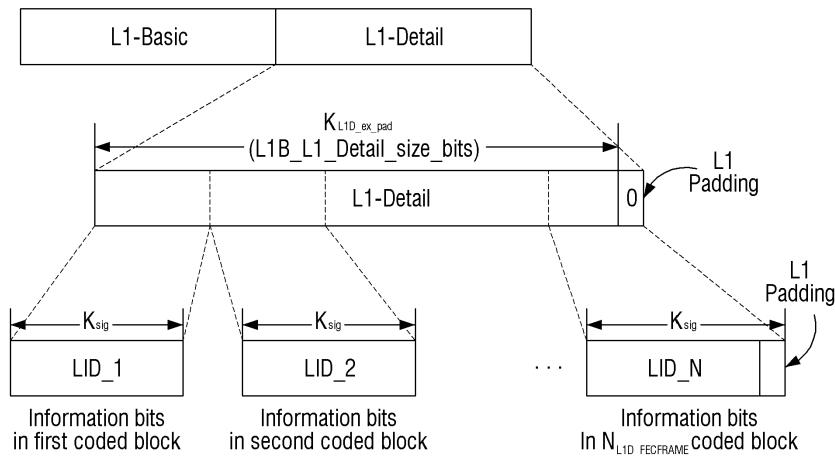

- [0025] 예를 들어, 정보어 비트들의 수가  $K_{sig}$ 이고, 아우터 인코딩에 의해  $M_{outer}$  개의 패리티 비트들이 정보어 비트들에 부가된 경우의 비트들의 수 즉, 정보어 비트들 및 패리티 비트들을 포함하는 아우터 인코딩된 비트들의 수가  $N_{outer} (=K_{sig}+M_{outer})$ 인 경우를 가정한다.

- [0026] 이 경우, 아우터 인코딩된 비트들의 수  $N_{outer}$ 가 LDPC 정보어 비트들의 수  $K_{ldpc}$ 보다 작은 경우,  $K_{ldpc}-N_{outer}$  개의 제로 비트들이 패딩되어, 아우터 인코딩된 비트들 및 패딩된 제로 비트들이 함께 LDPC 정보어 비트들을 구성할 수 있다.

- [0027] 한편, 상술한 예에서는 제로 비트들이 패딩되는 것으로 설명하였으나, 이는 일 예에 불과하다.

- [0028] 예를 들어, 정보어 비트들은 데이터에 대한 시그널링이라는 점에서, 데이터의 양에 따라 정보어 비트들의 길이는 가변적일 수 있다. 따라서, 정보어 비트들의 수가 LDPC 인코딩에 요구되는 LDPC 정보어 비트들의 수보다 큰 경우, 정보어 비트들은 일정한 값 이하로 세그먼테이션될 수 있다.

- [0029] 이에 따라, 정보어 비트들 또는 세그먼트된 정보어 비트들의 수가 LDPC 정보어 비트들의 수에서 아우터 인코딩에 의해 생성되는 패리티 비트들의 수(즉,  $M_{outer}$ )를 뺀 수보다 작은 경우, LDPC 정보어 비트들의 수에서 아우터 인코딩된 비트들 수를 뺀 수만큼의 제로 비트들이 패딩되어, LDPC 정보어 비트들은 아우터 인코딩된 비트들 및 패딩된 제로 비트들로 구성될 수 있다.

- [0030] 하지만, 정보어 비트들 또는 세그먼트된 정보어 비트들의 수가 LDPC 정보어 비트들의 수에서 아우터 인코딩에 의해 생성되는 패리티 비트들의 수를 뺀 수와 동일한 경우, LDPC 정보어 비트들은 패딩되는 제로 비트들이 없이 아우터 인코딩된 비트들만으로 구성될 수 있다.

- [0031] 또한, 상술한 예에서는 정보어 비트들이 아우터 인코딩되는 것으로 설명하였으나 이는 일 예에 불과하다. 즉, 정보어 비트들은 아우터 인코딩되지 않으며, 정보어 비트들의 수에 따라 패딩된 제로 비트와 함께 LDPC 정보어 비트들을 구성하거나, 별도의 패딩 없이 정보어 비트들만으로 LDPC 정보어 비트들을 구성할 수도 있다.

- [0032] 한편, 이하에서는 설명의 편의를 위해, 아우터 인코딩은 BCH 코드에 의해 수행되는 것으로 상정하여 설명하도록 한다.

- [0033] 구체적으로, 입력 비트들은 정보어 비트들 및 정보어 비트들이 BCH 인코딩되어 생성된 BCH 패리티 체크 비트들 (BCH parity-check bits)(또는, BCH 패리티 비트들)을 포함하는 BCH 인코딩된 비트들 및, 제로 비트들(zero bits)을 포함하는 것으로 상정하여 설명하도록 한다.

- [0034] 즉, 정보어 비트들의 수가  $K_{sig}$ 이고, BCH 인코딩에 의해  $M_{outer}$  개의 BCH 패리티 체크 비트들이 정보어 비트들에 부가된 경우의 비트들의 수 즉, 정보어 비트들 및 BCH 패리티 체크 비트들을 포함하는 BCH 인코딩된 비트들의 수가  $N_{outer} (=K_{sig}+M_{outer})$ 인 경우를 상정하여 설명하도록 한다. 여기에서,  $M_{outer}=168$ 이다.

- [0035] 또한, 상술한 예에서는 쇼트닝을 위해 제로 비트들이 패딩되는 것으로 설명하였으나 이는 일 예에 불과하다. 즉, 쇼트닝은 LDPC 정보어 비트들 중 일부 비트들이 수신 장치(200)로 실질적으로 전송하고자 하는 정보를 포함하는 비트들(즉, 정보어 비트들)로 채워진 경우, 나머지 비트들은 실질적인 정보를 전송하지 않도록 하기 위해, 나머지 비트들에 송수신 장치 사이에 기설정된 비트 값을 채우는 것이라는 점에서, 쇼트닝을 위해 제로 비트 외에 송수신 장치에서 기설정된 값(예를 들어, 1)을 갖는 비트가 패딩될 수도 있다.

- [0036] LDPC 인코더(110)는 LDPC 정보어 비트들을 시스템에 허가(technically) 인코딩하여 LDPC 패리티 비트들을 생성하고, LDPC 정보어 비트들과 LDPC 패리티 비트들로 구성된 LDPC 코드워드(또는, LDPC 인코딩된 비트들)를 출력할 수 있다. 즉, LDPC 코드는 시스템에 허가 코드(systematic code)라는 점에서, LDPC 코드워드는 인코딩 전의 LDPC 정보어 비트들과 인코딩에 의해 생성된 LDPC 패리티 비트들로 구성될 수 있다.

- [0037] 예를 들어, LDPC 인코더(110)는  $K_{ldpc}$  개의 LDPC 정보어 비트들  $I=(i_0, i_1, \dots, i_{K_{ldpc}-1})$ 을 LDPC 인코딩하여  $N_{ldpc\_parity}$  개의 LDPC 패리티 비트들  $(p_0, p_1, \dots, p_{N_{ldpc\_parity}-1})$ 을 생성하고,  $N_{inner} (=K_{ldpc}+N_{ldpc\_parity})$  개의 비트들로 구성된 LDPC 코드워드  $\Lambda=(c_0, c_1, \dots, c_{N_{inner}-1})=(i_0, i_1, \dots, i_{K_{ldpc}-1}, p_0, p_1, \dots, p_{N_{inner}-1})$ 을 출력할 수 있다.

- [0038] 이 경우, LDPC 인코더(110)는 다양한 코드 레이트로 입력 비트들을 LDPC 인코딩하여, 일정한 길이를 갖는 LDPC 코드워드를 생성할 수 있다.

- [0039] 예를 들어, LDPC 인코더(110)는 3/15의 코드 레이트로 3240 개의 입력 비트들을 LDPC 인코딩하여 16200 개의 비트들로 구성된 LDPC 코드워드를 생성할 수 있다. 다른 예로, LDPC 인코더(110)는 6/15의 코드 레이트로 6480 개의 입력 비트들을 LDPC 인코딩하여 16200 개의 비트들로 구성된 LDPC 코드워드를 생성할 수 있다.

- [0040] 한편, LDPC 부호화를 수행하는 과정은  $H \cdot C^T = 0$ 을 만족하도록 LDPC 코드워드를 생성하는 과정이라는 점에서, LDPC 인코더(110)는 패리티 검사 행렬(parity check matrix)을 이용하여 LDPC 인코딩을 수행할 수 있다. 여기에서,  $H$ 는 패리티 검사 행렬을 나타내고,  $C$ 는 LDPC 코드워드를 나타낸다.

- [0041] 이하에서는 첨부된 도면을 참조하여, 본 발명의 다양한 실시 예에 따른 패리티 검사 행렬의 구조에 대해 설명하도록 한다. 패리티 검사 행렬에서 1을 제외한 부분의 원소는 0이다.

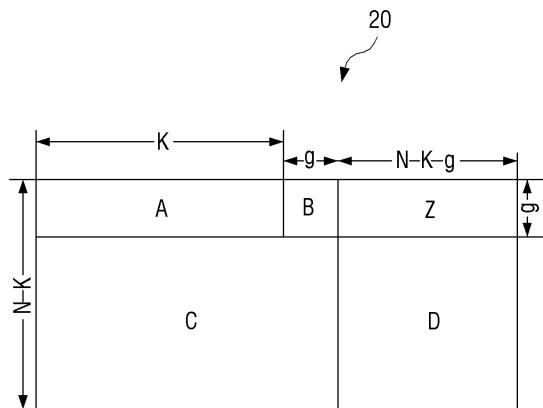

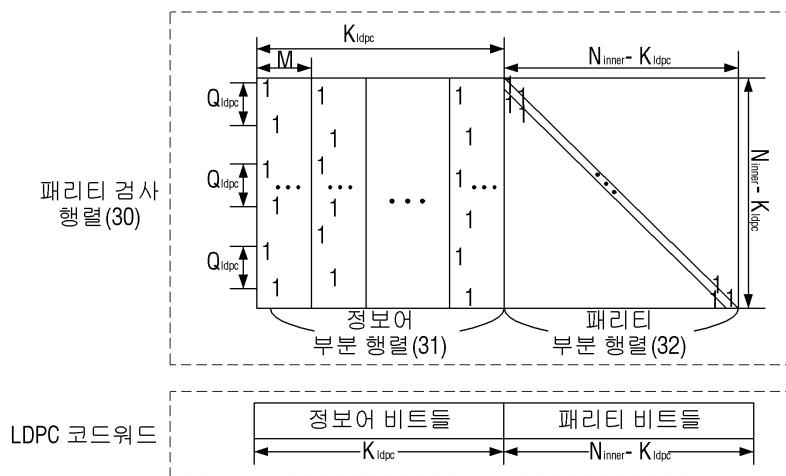

- [0042] 일 예로, 본 발명의 일 실시 예에 따른 패리티 검사 행렬은 도 2와 같은 구조를 가질 수 있다.

- [0043] 도 2를 참조하면, 패리티 검사 행렬(20)은 5 개의 행렬(A, B, C, Z, D)로 구성될 수 있으며, 이하에서는 패리티 검사 행렬(20)의 구조에 대해 설명하기 위해 각 행렬의 구조에 대해 설명하도록 한다.

- [0044] 행렬 A는 K 개의 열(column)과 g 개의 행(row)으로 구성되며, 행렬 C는 K+g 개의 열과 N-K-g 개의 행으로 구성된다. 여기에서, K(또는,  $K_{ldpc}$ )는 LDPC 정보어 비트들의 길이이고, N(또는,  $N_{inner}$ )은 LDPC 코드워드의 길이이다.

- [0045] 그리고, 행렬 A와 행렬 C에서 i 번째 열 그룹(column group)의 0 번째 열에서 1이 위치한 행의 인덱스들은 LDPC 코드워드의 길이가 16200이고, 코드 레이트가 3/15인 경우, 하기의 표 1에 기초하여 정의될 수 있다. 한편, 동일한 열 그룹에 속하는 열의 개수는 360이 될 수 있다.

## 표 1

|                                                          |

|----------------------------------------------------------|

| 8 372 841 4522 5253 7430 8542 9822 10550 11896 11988     |

| 80 255 667 1511 3549 5239 5422 5497 7157 7854 11267      |

| 257 406 792 2916 3072 3214 3638 4090 8175 8892 9003      |

| 80 150 346 1883 6838 7818 9482 10366 10514 11468 12341   |

| 32 100 978 3493 6751 7787 8496 10170 10318 10451 12561   |

| 504 803 856 2048 6775 7631 8110 8221 8371 9443 10990     |

| 152 283 696 1164 4514 4649 7260 7370 11925 11986 12092   |

| 127 1034 1044 1842 3184 3397 5931 7577 11898 12339 12689 |

| 107 513 979 3934 4374 4658 7286 7809 8830 10804 10893    |

| 2045 2499 7197 8887 9420 9922 10132 10540 10816 11876    |

| 2932 6241 7136 7835 8541 9403 9817 11679 12377 12810     |

| 2211 2288 3937 4310 5952 6597 9692 10445 11064 11272     |

- [0046] [0047] 이하에서는, 표 1을 일 예로, 행렬 A와 행렬 C에서 1이 존재하는 행의 위치에 대해 구체적으로 설명하도록 한다.

- [0048] 한편, LDPC 코드워드의 길이가 16200이고, 코드 레이트가 3/15인 경우, 패리티 검사 행렬(200)에 기초한 코딩 파라미터  $M_1$ ,  $M_2$ ,  $Q_1$ ,  $Q_2$ 는 각각 1080, 11880, 3, 33이다.

- [0049] 여기에서,  $Q_1$ 은 행렬 A에서 동일한 열 그룹 내에 속한 열들이 시클릭 쉬프트(cyclic shift)되는 크기이고,  $Q_2$ 는 행렬 C에서 동일한 열 그룹 내에 속한 열들이 시클릭 쉬프트되는 크기이다.

- [0050] 그리고,  $Q_1=M_1/L$ ,  $Q_2=M_2/L$ ,  $M_1=g$ ,  $M_2=N-K-g$ 이고, L은 행렬 A, C 각각에서 열의 패턴이 반복되는 간격 즉, 동일한 열 그룹에 속하는 열의 개수로 일 예로, 360이 될 수 있다.

- [0051] 한편, 행렬 A, C 각각에서 1이 위치하는 행의 인덱스는  $M_1$  값에 기초하여 결정될 수 있다.

- [0052] 예를 들어, 표 1의 경우  $M_1=1080$ 이라는 점에서, 행렬 A에서 i 번째 열 그룹의 0 번째 열에서 1이 존재하는 행의 위치는 표 1의 인덱스 값들 중에서 1080 보다 작은 값들에 기초하여 결정될 수 있으며, 행렬 C에서 i 번째 열 그룹의 0 번째 열에서 1이 존재하는 행의 위치는 표 1의 인덱스 값들 중에서 1080 이상인 값들에 기초하여 결정될 수 있다.

- [0053] 구체적으로, 표 1에서 0 번째 열 그룹에 대응되는 수열은 "8 372 841 4522 5253 7430 8542 9822 10550 11896 11988"이다. 따라서, 행렬 A의 0 번째 열 그룹의 0 번째 열의 경우, 8 번째 행, 372 번째 행, 841 번째 행에 각각 1이 위치할 수 있고, 행렬 C의 0 번째 열 그룹의 0 번째 열의 경우 4522 번째 행, 5253 번째 행, 7430 번째 행, 8542 번째 행, 9822 번째 행, 10550 번째 행, 11896 번째 행, 11988 번째 행에 각각 1이 위치할 수 있다.

- [0054] 한편, 행렬 A의 경우 각 열 그룹의 0 번째 열에서 1의 위치가 정의되면 이를  $Q_1$  만큼 시클릭 쉬프트하여 각 열 그룹의 다른 열에서 1이 존재하는 행의 위치가 정의될 수 있고, 행렬 C의 경우 각 열 그룹의 0 번째 열에서 1의 위치가 정의되면 이를  $Q_2$  만큼 시클릭 쉬프트하여 각 열 그룹의 다른 열에서 1이 존재하는 행의 위치가 정의될 수 있다.

- [0055] 상술한 예에서, 행렬 A의 0 번째 열 그룹의 0 번째 열의 경우, 8 번째 행, 372 번째 행, 841 번째 행에 1이 존재한다. 이 경우,  $Q_1=3$ 이므로, 0 번째 열 그룹의 1 번째 열에서 1이 위치한 행의 인덱스는  $11(=8+3)$ ,  $375(=372+3)$ ,  $844(=841+3)$ 이고, 0 번째 열 그룹의 2 번째 열에서 1이 위치한 행의 인덱스는  $14(=11+3)$ ,  $378(=375+3)$ ,  $847(=844+3)$ 이 될 수 있다.

[0056] 한편, 행렬 C의 0 번째 열 그룹의 0 번째 열의 경우, 4522 번째 행, 5253 번째 행, 7430 번째 행, 8542 번째 행, 9822 번째 행, 10550 번째 행, 11896 번째 행, 11988 번째 행에 1이 존재한다. 이 경우,  $Q_2=33$ 이므로, 0 번째 열 그룹의 1 번째 열에서 1이 위치한 행의 인덱스는  $4555 (=4522+33)$ ,  $5286 (=5253+33)$ ,  $7463 (=7430+33)$ ,  $8575 (=8542+33)$ ,  $9855 (=9822+33)$   $10583 (=10550+33)$ ,  $11929 (=11896+33)$ ,  $12021 (=11988+33)$ 이고, 0 번째 열 그룹의 2 번째 열에서 1이 위치한 행의 인덱스는  $4588 (=4555+33)$ ,  $5319 (=5286+33)$ ,  $7496 (=7463+33)$ ,  $8608 (=8575+33)$ ,  $9888 (=9855+33)$ ,  $10616 (=10583+33)$ ,  $11962 (=11929+33)$ ,  $12054 (=12021+33)$ 가 될 수 있다.

[0057] 이와 같은 방식에 따라 행렬 A 및 행렬 C의 모든 열 그룹에서 1이 존재하는 행의 위치가 정의될 수 있다.

[0058] 한편, 행렬 B는 이중 대각 행렬(dual diagonal matrix)이고, 행렬 D는 항등 행렬(identity matrix)이고, 행렬 Z는 영 행렬(zero matrix)이다.

[0059] 결국, 상술한 바와 같은 구조를 갖는 행렬 A, B, C, D, Z에 의해 도 2와 같은 패리티 검사 행렬(20)의 구조가 정의될 수 있게 된다.

[0060] 이하에서는 LDPC 인코더(110)가 도 2와 같은 패리티 검사 행렬(20)에 기초하여 LDPC 인코딩을 수행하는 방법에 대해 설명하도록 한다.

[0061] LDPC 코드는 정보어 블록  $S=(s_0, s_1, \dots, s_{K-1})$ 을 인코딩하기 위해 이용될 수 있다. 이 경우,  $N=K+M_1+M_2$ 의 길이를 갖는 LDPC 코드워드  $\Lambda=(\lambda_0, \lambda_1, \dots, \lambda_{N-1})$ 를 생성하기 위해, 정보어 블록  $S$ 로부터 패리티 비트들

$$P_{M_1+M_2-1} = (p_0, p_1, \dots, p_{M_1+M_2-1})$$

이 시스템에 페리티 인코딩될 수 있다.

[0062] 이에 따라, LDPC 코드워드는  $\Lambda=(s_0, s_1, \dots, s_{K-1}, p_0, p_1, \dots, p_{M_1+M_2-1})$ 가 될 수 있다.

[0063] 여기에서,  $M_1$  및  $M_2$  각각은 이중 대각 행렬 B 및 항등 행렬 D 각각에 대응되는 패리티 행렬의 사이즈를 나타내며,  $M_1=g$ ,  $M_2=N-K-g$ 가 될 수 있다.

[0064] 한편, 패리티 비트를 산출하는 과정은 다음과 같이 나타낼 수 있다. 이하에서는 설명의 편의를 위해, 패리티 검사 행렬(20)이 표 1과 같이 정의되는 경우를 일 예로 설명하도록 한다.

[0065] 단계 1)  $\lambda_i=s_i$  ( $i=0, 1, \dots, K-1$ ),  $p_j=0$  ( $j=0, 1, \dots, M_1+M_2-1$ )로 초기화한다.

[0066] 단계 2) 표 1의 첫 번째 행에서 정의되는 패리티 비트 어드레스에 첫 번째 정보어 비트  $\lambda_0$ 을 누적한다.

[0067] 단계 3) 다음  $L-1$  개의 정보어 비트  $\lambda_m$  ( $m=1, 2, \dots, L-1$ )에 대해,  $\lambda_m$ 를 하기와 같은 수학식 1에 기초하여 산출되는 패리티 비트 어드레스에 누적한다.

## 수학식 1

$$(x + m \times Q_1) \bmod M_1 \quad (\text{if } x < M_1)$$

$$M_1 + \{(x - M_1 + m \times Q_2) \bmod M_2\} \quad (\text{if } x \geq M_1)$$

[0068]

[0069] 여기에서, x는 첫 번째 정보어 비트  $\lambda_0$ 에 대응되는 패리티 비트 누적기의 어드레스이다.

[0070] 그리고,  $Q_1=M_1/L$ ,  $Q_2=M_2/L$ 이다. 이 경우, LDPC 코드워드의 길이가 16200이고, 코드 레이트가 3/15이므로,  $M_1=1080$ ,  $M_2=11880$ ,  $Q_1=3$ ,  $Q_2=33$ ,  $L=360$ 이 될 수 있다.

[0071] 단계 4) L 번째 정보어 비트  $\lambda_L$ 에 대해 표 1의 두 번째 행과 같은 패리티 비트의 어드레스가 주어진다는 점에

서, 상술한 방식과 유사하게, 이후의  $L-1$  개 정보어 비트  $\lambda_m$  ( $m=L+1, L+2, \dots, 2L-1$ )에 대한 패리티 비트의 어드레스를 단계 3에서 설명한 방식을 이용하여 산출한다. 이 경우,  $x$ 는 정보어 비트  $\lambda_L$ 에 대응되는 패리티 비트 누적기의 어드레스로, 표 1의 두 번째 행에 기초하여 얻어질 수 있다.

[0072] 단계 5) 각 그룹의  $L$  개의 새로운 정보어 비트들에 대해, 표 1의 새로운 행들을 패리티 비트 누적기의 어드레스로 하여 상술한 과정을 반복한다.

[0073] 단계 6) 코드워드 비트  $\lambda_0$ 부터  $\lambda_{K-1}$ 까지 상술한 과정이 반복된 이후,  $i=1$ 부터 순차적으로 하기의 수학식 2에 대한 값을 산출한다.

## 수학식 2

$$P_i = P_i \oplus P_{i-1} \quad (i=1, 2, \dots, M_1-1)$$

[0074] 단계 7) 이중 대각 행렬  $B$ 에 대응되는 패리티 비트  $\lambda_K$ 부터  $\lambda_{K+M_1-1}$  까지를 하기의 수학식 3에 기초하여 산출한다.

## 수학식 3

$$\lambda_{K+L+s} = p_{Q_1 \times s+t} \quad (0 \leq s < L, 0 \leq t < Q_1)$$

[0075] 단계 8) 각 그룹의  $L$  개의 새로운 코드워드 비트  $\lambda_K$ 부터  $\lambda_{K+M_1-1}$  까지에 대한 패리티 비트 누적기의 어드레스는 표 1의 새로운 행 및 수학식 1에 기초하여 산출한다.

[0076] 단계 9) 코드워드 비트  $\lambda_K$ 부터  $\lambda_{K+M_1-1}$  까지 적용된 이후, 대각 행렬  $D$ 에 대응되는 패리티 비트  $\lambda_{K+M_1}$ 부터  $\lambda_{K+M_1+M_2-1}$  까지를 하기의 수학식 4에 기초하여 산출한다.

## 수학식 4

$$\lambda_{K+M_1+L+s} = p_{M_1+Q_2 \times s+t} \quad (0 \leq s < L, 0 \leq t < Q_2)$$

[0077] 결국, 이와 같은 방식에 따라 패리티 비트들을 산출할 수 있게 된다. 다만, 이는 일 예일 뿐이며, 도 2와 같은 패리티 검사 행렬에 기초하여 패리티 비트들을 산출하는 방식은 다양하게 정의될 수 있음을 물론이다.

[0078] 이와 같이, LDPC 인코더(110)는 표 1에 기초하여 LDPC 인코딩을 수행하여, LDPC 코드워드를 생성할 수 있다.

[0079] 구체적으로, LDPC 인코더(110)는 표 1에 기초하여 3/15의 코드 레이트로 3240 개의 입력 비트들 즉, LDPC 정보어 비트들을 LDPC 인코딩하여 12960 개의 LDPC 패리티 비트들을 생성하고, LDPC 패리티 비트들 및 LDPC 패리티 비트들로 구성된 LDPC 코드워드를 출력할 수 있다. 이 경우, LDPC 코드워드는 16200 개의 비트들로 구성될 수 있다.

- [0083] 다른 예로, 본 발명의 일 실시 예에 따른 패리티 검사 행렬은 도 3과 같은 구조를 가질 수 있다.

- [0084] 도 3을 참조하면, 패리티 검사 행렬(30)은 정보어 비트들(즉, LDPC 정보어 비트들)에 대응되는 부분 행렬인 정보어 부분 행렬(31)과 패리티 비트들(즉, LDPC 패리티 비트들)에 대응되는 부분 행렬인 패리티 부분 행렬(32)로 구성된다.

- [0085] 정보어 부분 행렬(31)은  $K_{ldpc}$  개의 열을 포함하고, 패리티 부분 행렬(32)은  $N_{ldpc\_parity}=N_{inner}-K_{ldpc}$  개의 열을 포함한다. 한편, 패리티 검사 행렬(30)의 행의 개수는 패리티 부분 행렬(32)의 열의 개수  $N_{ldpc\_parity}=N_{inner}-K_{ldpc}$ 와 동일하다.

- [0086] 또한, 패리티 검사 행렬(30)에서  $N_{inner}$ 는 LDPC 코드워드의 길이,  $K_{ldpc}$ 는 정보어 비트들의 길이,  $N_{ldpc\_parity}=N_{inner}-K_{ldpc}$ 는 패리티 비트들의 길이를 나타낸다.

- [0087] 이하에서는 정보어 부분 행렬(31)과 패리티 부분 행렬(32)의 구조에 대해 살펴보도록 한다.

- [0088] 정보어 부분 행렬(31)은  $K_{ldpc}$  개의 열(즉, 0 번째 열부터  $K_{ldpc}-1$  번째 열)을 포함하는 행렬로, 다음과 같은 규칙을 따른다.

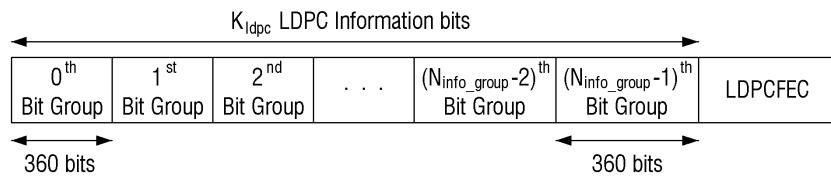

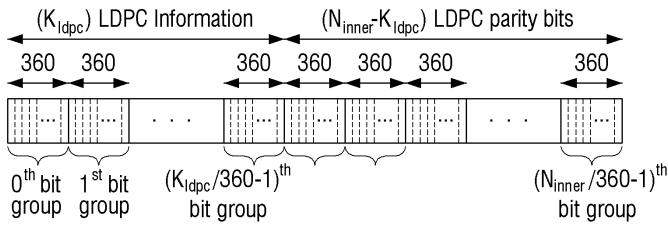

- [0089] 첫째, 정보어 부분 행렬(31)을 구성하는  $K_{ldpc}$  개의 열들은  $M$  개씩 동일한 그룹에 속하며, 총  $K_{ldpc}/M$  개의 열 그룹들로 구분된다. 동일한 열 그룹 내에 속한 열들은 서로  $Q_{ldpc}$  만큼 시클릭 쉬프트된 관계를 가진다. 즉,  $Q_{ldpc}$ 는 패리티 검사 행렬(30)을 구성하는 정보어 부분 행렬의 열 그룹 내에서 열들에 대한 시클릭 쉬프트 파라미터 값으로 볼 수 있다.

- [0090] 여기에서,  $M$ 은 정보어 부분 행렬(31)에서 열의 패턴이 반복되는 간격(일 예로,  $M=360$ )이고,  $Q_{ldpc}$ 는 정보어 부분 행렬(31)에서 각 열이 시클릭 쉬프트되는 크기이다.  $M$ 은  $N_{inner}$ 와  $K_{ldpc}$ 의 공약수(common divisor)이며,  $Q_{ldpc}=(N_{inner}-K_{ldpc})/M$  성립하도록 결정된다. 여기에서,  $M$  및  $Q_{ldpc}$ 는 정수이고,  $K_{ldpc}/M$ 도 정수가 된다. 한편,  $M$  및  $Q_{ldpc}$ 는 LDPC 코드워드의 길이와 코드 레이트에 따라 다양한 값을 가질 수 있다.

- [0091] 예를 들어,  $M=360$ 이고 LDPC 부호어의 길이  $N_{inner}$ 가 16200이고, 코드 레이트가 6/15인 경우,  $Q_{ldpc}$ 는 27이 될 수 있다.

- [0092] 둘째,  $i$  번째 ( $i=0, 1, \dots, K_{ldpc}/M-1$ ) 열 그룹의 0 번째 열의 차수(degree)(여기에서, 차수는 열에 존재하는 1 값의 개수로, 동일한 열 그룹에 속하는 모든 열들의 차수는 동일하다)를  $D_i$ 라 하고,  $i$  번째 열 그룹의 0 번째 열에서 1이 있는 각 행의 위치(또는, 인덱스)를  $R_{i,0}^{(0)}, R_{i,0}^{(1)}, \dots, R_{i,0}^{(D_i-1)}$ 이라 하면,  $i$  번째 열 그룹 내의  $j$  번째 열에서  $k$  번째 1이 위치한 행의 인덱스  $R_{i,j}^{(k)}$ 는 하기의 수학식 5와 같이 결정된다.

## 수학식 5

$$R_{i,j}^{(k)} = R_{i,(j-1)}^{(k)} + Q_{ldpc} \bmod (N_{inner} - K_{ldpc})$$

- [0093] 여기에서,  $k=0, 1, 2, \dots, D_i-1$ ,  $i=0, 1, \dots, K_{ldpc}/M-1$ ,  $j=1, 2, \dots, M-1$ 이다.

- [0094] 한편, 수학식 5는 하기의 수학식 6과 같이 동일하게 표현될 수 있다.

## 수학식 6

$$R_{i,j}^{(k)} = (R_{i,0}^{(k)} + (j \bmod M) \times Q_{ldpc}) \bmod (N_{inner} - K_{ldpc})$$

[0096]

[0097] 여기에서,  $k=0,1,2,\dots,D_i-1$ ,  $i=0,1,\dots,K_{ldpc}/M-1$ ,  $j=1,2,\dots,M-1$ 이다. 여기에서,  $j=1,2,\dots,M-1$ 이기 때문에  $(j \bmod M)$ 은  $j$ 로 볼 수 있다.

[0098] 이를 수학식에서,  $R_{i,j}^{(k)}$ 는  $i$  번째 열 그룹 내의  $j$  번째 열에서  $k$  번째 1이 위치한 행의 인덱스,  $N_{inner}$ 는 LDPC 부호어의 길이,  $K_{ldpc}$ 는 정보어 비트들의 길이,  $D_i$ 는  $i$  번째 열 그룹에 속하는 열들의 차수,  $M$ 은 하나의 열 그룹에 속하는 열의 개수,  $Q_{ldpc}$ 는 각 열이 시클릭 쉬프트되는 크기를 의미한다.

[0099] 결국, 이를 수학식을 참조하면  $R_{i,0}^{(k)}$  값만을 알면  $i$  번째 열 그룹 내의  $j$  번째 열에서  $k$  번째 1이 있는 행의 인덱스  $R_{i,j}^{(k)}$ 를 알 수 있게 된다. 그러므로, 각각의 열 그룹 내의 0 번째 열에서  $k$  번째 1이 있는 행의 인덱스 값을 저장하면, 도 3의 구조를 갖는 패리티 검사 행렬(30)(즉, 패리티 검사 행렬(30)의 정보어 부분 행렬(31))에서 1이 있는 열과 행의 위치가 파악될 수 있다.

[0100] 상술한 규칙들에 따르면,  $i$  번째 열 그룹에 속하는 열들의 차수는 모두  $D_i$ 로 동일하다. 따라서, 상술한 규칙들에 따라 패리티 검사 행렬에 대한 정보를 저장하고 있는 LDPC 부호는 다음과 같이 간략하게 표현될 수 있다.

[0101] 예를 들어,  $N_{inner}$ 가 30,  $K_{ldpc}$ 가 15,  $Q_{ldpc}$ 가 3인 경우, 3 개의 열 그룹의 0 번째 열에서 1이 위치한 행의 위치 정보는 하기의 수학식 7과 같은 수열들로 표현될 수 있으며, 이는 '무게-1 위치 수열(weight-1 position sequence)'이라 지칭될 수 있다.

## 수학식 7

$$\begin{aligned} R_{1,0}^{(1)} &= 1, R_{1,0}^{(2)} = 2, R_{1,0}^{(3)} = 8, R_{1,0}^{(4)} = 10, \\ R_{2,0}^{(1)} &= 0, R_{2,0}^{(2)} = 9, R_{2,0}^{(3)} = 13, \\ R_{3,0}^{(1)} &= 0, R_{3,0}^{(2)} = 14. \end{aligned}$$

[0102]

[0103] 여기에서,  $R_{i,j}^{(k)}$ 는  $i$  번째 열 그룹 내의  $j$  번째 열에서  $k$  번째 1이 있는 행의 인덱스를 의미한다.

[0104]

각 열 그룹의 0 번째 열에서 1이 위치한 행의 인덱스를 나타내는 수학식 7과 같은 무게-1 위치 수열들은 보다 간략하게 하기의 표 2와 같이 표현될 수 있다.

## 표 2

|   |    |    |    |

|---|----|----|----|

| 1 | 2  | 8  | 10 |

| 0 | 9  | 13 |    |

| 0 | 14 |    |    |

[0105]

[0106] 표 2는 패리티 검사 행렬에서 1 값을 가지는 원소의 위치를 나타낸 것으로서,  $i$  번째 무게-1 위치 수열은  $i$  번

째 열 그룹에 속한 0 번째 열에서 1이 있는 행의 인덱스들로 표현된다.

[0107] 상술한 내용에 기초하여 본 발명의 일 실시 예에 다른 패리티 검사 행렬의 정보어 부분 행렬(31)은 하기의 표 3에 의해 정의될 수 있다.

[0108] 여기에서, 표 3은 정보어 부분 행렬(31)의 i 번째 열 그룹의 0 번째 열에서 1이 위치한 행의 인덱스들을 나타낸다. 즉, 정보어 부분 행렬(31)은 각각 M 개의 열을 포함하는 복수의 열 그룹으로 구성되며, 복수의 열 그룹 각각의 0 번째 열에서 1의 위치는 표 3에 의해 정의될 수 있다.

[0109] 일 예로, LDPC 부호어의 길이  $N_{inner}$ 가 16200, 부호율이 6/15, M이 360인 경우, 정보어 부분 행렬(31)의 i 번째 열 그룹의 0 번째 열에서 1이 위치한 행의 인덱스들은 하기의 표 3과 같다.

### 표 3

|                                                                                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------|

| 27 430 519 828 1897 1943 2513 2600 2640 3310 3415 4266 5044 5100 5328 5483 5928 6204 6392 6416 6602 7019 7415 7623 8112 8485 8724 8994 9445 9667 |

| 27 174 188 631 1172 1427 1779 2217 2270 2601 2813 3196 3582 3895 3908 3948 4463 4955 5120 5809 5988 6478 6604 7096 7673 7735 7795 8925 9613 9670 |

| 27 370 617 852 910 1030 1326 1521 1606 2118 2248 2909 3214 3413 3623 3742 3752 4317 4694 5300 5687 6039 6100 6232 6491 6621 6860 7304 8542 8634  |

| 990 1753 7635 8540                                                                                                                               |

| 933 1415 5666 8745                                                                                                                               |

| 27 6567 8707 9216                                                                                                                                |

| 2341 8692 9580 9615                                                                                                                              |

| 260 1092 5839 6080                                                                                                                               |

| 352 3750 4847 7726                                                                                                                               |

| 4610 6580 9506 9597                                                                                                                              |

| 2512 2974 4814 9348                                                                                                                              |

| 1461 4021 5060 7009                                                                                                                              |

| 1796 2883 5553 8306                                                                                                                              |

| 1249 5422 7057                                                                                                                                   |

| 3965 6968 9422                                                                                                                                   |

| 1498 2931 5092                                                                                                                                   |

| 27 1090 6215                                                                                                                                     |

| 26 4232 6354                                                                                                                                     |

[0110]

[0111] 한편, 상술한 표 3에서 각 i 번째 열 그룹에 대응되는 수열 내의 숫자들의 순서가 바뀌어도 동일한 부호의 패리티 검사 행렬이라는 점에서, 표 3에서 각 i 번째 열 그룹에 대응되는 수열 내의 순서가 바뀐 경우도 본 발명에서 고려하는 부호의 한 가지 일 예가 될 수 있다.

[0112] 또한, 표 3에서 각 열 그룹에 대응되는 수열들의 나열 순서가 바뀌어도 부호의 그래프 상의 사이클 특성 및 차수 분포 등의 대수적 특성이 바뀌지 않기 때문에, 표 3에 나타난 수열들의 나열 순서가 바뀐 경우도 한 가지 일 예가 될 수 있다.

[0113] 또한, 표 3에서 임의의 열 그룹에 대응되는 수열들에 대해 모두 동일하게  $Q_{ldpc}$ 의 배수를 더한 결과 또한 부호의 그래프 상의 사이클 특성이나 차수 분포 등의 대수적 특성이 바뀌지 않기 때문에, 표 3에 나타난 수열들에 대해 모두 동일하게  $Q_{ldpc}$ 의 배수를 더한 결과도 한 가지 일 예가 될 수 있다. 여기에서 주의해야 할 점은 주어진 수열에  $Q_{ldpc}$  배수만큼 더했을 경우 그 값이  $(N_{inner}-K_{ldpc})$  이상의 값이 나올 경우에는 그 값에  $(N_{inner}-K_{ldpc})$ 에 대한 모듈로(modulo) 연산을 적용한 값으로 바꾸어 적용해야 한다는 것이다.

[0114] 한편, 표 3과 같이 정보어 부분 행렬(31)의 i 번째 열 그룹의 0 번째 열에서 1이 존재하는 행의 위치가 정의되면, 이를  $Q_{ldpc}$ 만큼 시클릭 쉬프트하여 각 열 그룹의 다른 열에서 1이 존재하는 행의 위치가 정의될 수 있다.

[0115] 예를 들어, 표 3의 경우, 정보어 부분 행렬(31)의 0 번째 열 그룹의 0 번째 열에 대응되는 시퀀스는 "27 430 519 828 1897 1943 2513 2600 2640 3310 3415 4266 5044 5100 5328 5483 5928 6204 6392 6416 6602 7019 7415 7623 8112 8485 8724 8994 9445 9667"이므로, 정보어 부분 행렬(31)의 0 번째 열 그룹의 0 번째 열의 경우, 27 번째 행, 430 번째 행, 519 번째 행,...에 1이 존재한다.

[0116] 이 경우,  $Q_{ldpc}=(N_{inner}-K_{ldpc})/M=(16200-6480)/360=27$ 이므로, 0 번째 열 그룹의 1 번째 열에서 1이 위치한 행의 인덱스는 54( $=27+27$ ), 457( $=430+27$ ), 546( $=519+27$ ),...이고, 81( $=54+27$ ), 484( $=457+27$ ), 573( $=546+27$ ),...이 될 수 있다.

[0117] 이와 같은 방식에 의해, 각 열 그룹의 모든 행에서 1이 위치한 행의 인덱스가 정의될 수 있다.

[0118] 이하에서는 도 3과 같은 패리티 검사 행렬(30)에 기초하여 LDPC 인코딩을 수행하는 방법에 대해 설명하도록 한다.

[0119] 먼저, 인코딩되는 정보어 비트들을  $i_0, i_1, \dots, i_{K_{ldpc}-1}$ 이라 하고, 산출되는 코드 비트들을

$c_0, c_1, \dots, c_{N_{ldpc}-1}$ 이라 한다.

[0120] 그리고, LDPC 코드가 시스템에 허다는 점에서,  $k(0 \leq k < K_{ldpc}-1)$ 에 대해,  $c_k$ 를  $i_k$ 로 설정한다. 한편, 나머지 코

드 비트들의 경우,  $p_k := c_{k+K_{ldpc}}$ 로 설정한다.

[0121] 이하에서는 이러한 패리티 비트를  $p_k$ 를 산출하는 방법에 대해 설명하도록 한다.

[0122] 이하에서  $q(i, j, 0)$ 은 표 3과 같은 인덱스를 리스트(indicies list)에서  $i$  번째 행(row)의  $j$  번째 엔트리(entry)를 나타내고,  $q(i, j, 1)$ 은  $0 < i < 360$ 에 대해  $q(i, j, 1) = q(i, j, 0) + Q_{ldpc} \times 1 \pmod{N_{inner} - K_{ldpc}}$ 라 한다. 한편, 모든 누적 연산(accumulation)은 GF(Galois Field)(2)에서의 덧셈 연산(additions)에 의해 실현될 수 있다. 그리고, 표 3의 경우 LDPC 코드워드의 길이가 16200이고, 코드 레이트가 6/15이므로,  $Q_{ldpc}$ 는 27이다.

[0123] 한편,  $q(i, j, 0)$  및  $q(i, j, 1)$ 이 상기와 같이 정의될 때, 패리티 비트를 산출하는 과정은 하기와 같다.

[0124] 단계 1) 패리티 비트들을 '0'으로 초기화한다. 즉,  $p_k = 0$  for  $0 \leq k < N_{inner} - K_{ldpc}$

[0125] 단계 2)  $0 \leq k < K_{ldpc}$ 의 모든  $k$  값에 대하여  $i$ 와  $1$ 을  $i := \lfloor k/360 \rfloor$ ,  $1 := k \pmod{360}$ 로 설정한다. 여기에서,  $x$ 는  $x$ 보다 크지 않는 최대 정수이다.

[0126] 이후, 모든  $i$ 에 대해,  $i_k$ 를  $p_{q(i, j, 1)}$ 에 누적한다. 즉,  $p_{q(i, j, 1)} = p_{q(i, j, 1)} + i_k$ 를 산출한다.

[0127] 여기에서,  $w(i)$ 는 표 3과 같은 인덱스를 리스트에서  $i$  번째 행의 값들(elements)의 개수이며, 패리티 검사 행렬에서  $i_k$ 에 대응되는 열의 1의 개수를 의미한다. 또한, 표 3에서  $i$  번째 행의  $j$  번째 엔트리인  $q(i, j, 0)$ 은 패리티 비트의 인덱스이며, 패리티 검사 행렬에서  $i_k$ 에 대응되는 열에서 1이 존재하는 행의 위치를 나타낸다.

[0128] 구체적으로, 표 3에서  $i$  번째 행의  $j$  번째 엔트리인  $q(i, j, 0)$ 은 LDPC 부호의 패리티 검사 행렬에서  $i$  번째 열 그룹 내의 첫 번째(즉, 0 번째) 열에서 1이 존재하는 행의 위치를 나타낸다.

[0129]  $q(i, j, 0)$ 은 모든  $i$ 에 대해,  $i_k$ 를  $p_{q(i, j, 1)}$ 에 누적하는 방식을 실제 장치에서 구현(implementation)하는 방법에 따라 LDPC 부호화에 의해 생성되어야 할 패리티 비트의 인덱스로 간주될 수도 있고, 다른 부호화 방법을 구현할 경우에는 또 다른 형태의 인덱스로 간주될 수도 있다. 하지만, 이는 하나의 일 예일 뿐이며, 어떠한 부호화 방식을 적용하더라도 기본적으로는 표 3의  $q(i, j, 0)$  값들에 기초하여 생성할 수 있는 LDPC 부호의 패리티 검사 행렬로부터 얻을 수 있는 LDPC 부호화 결과와 동일한(equivalent) 결과를 얻어야 함은 자명하다.

[0130] 단계 3)  $0 < k < N_{inner} - K_{ldpc}$ 를 만족하는 모든  $k$ 에 대해  $p_k = p_k + p_{k-1}$ 를 산출하여 패리티 비트  $p_k$ 를 산출하게 된다.

[0131] 이에 따라, 모든 코드 비트들  $c_0, c_1, \dots, c_{N_{ldpc}-1}$ 이 얻어질 수 있다.

[0132] 결국, 이와 같은 방식에 따라 패리티 비트들을 산출할 수 있게 된다. 다만, 이는 일 예일 뿐이며, 도 3과 같은 패리티 검사 행렬에 기초하여 패리티 비트들을 산출하는 방식은 다양하게 정의될 수 있음을 물론이다.

[0133] 이와 같이, LDPC 인코더(110)는 표 3에 기초하여 LDPC 인코딩을 수행하여, LDPC 코드워드를 생성할 수 있다.

- [0134] 구체적으로, LDPC 인코더(110)는 표 3에 기초하여 6/15의 코드 레이트로 6480 개의 입력 비트들 즉, LDPC 정보어 비트들을 LDPC 인코딩하여 9720 개의 LDPC 패리티 비트들을 생성하고, LDPC 패리티 비트들 및 LDPC 패리티 비트들로 구성된 LDPC 코드워드를 출력할 수 있다. 이 경우, LDPC 코드워드는 16200 개의 비트들로 구성될 수 있다.

- [0135] 상술한 바와 같이, LDPC 인코더(110)는 다양한 코드 레이트로 입력 비트들을 인코딩하여 입력 비트들 및 LDPC 패리티 비트들로 구성된 LDPC 코드워드를 생성할 수 있다.

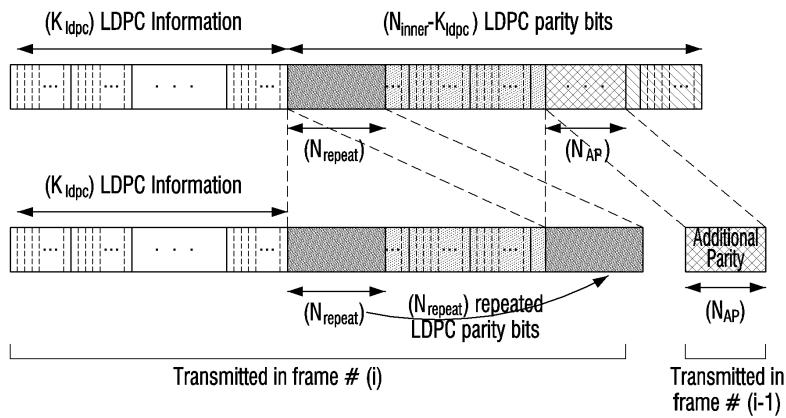

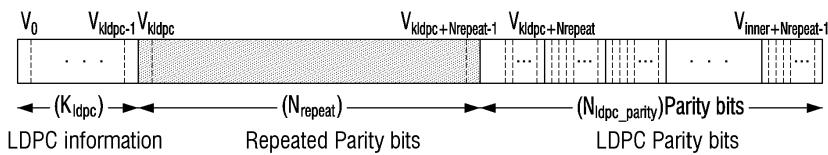

- [0136] 리피티션부(120)는 입력 비트들 및 LDPC 패리티 비트들로 구성된 LDPC 코드워드의 적어도 일부 비트들이 현재 프레임에서 리피티션되어 전송되도록, LDPC 코드워드의 적어도 일부 비트들을 LDPC 코드워드에서 리피티션한다. 그리고, 리피티션부(120)는 리피티션된 LDPC 코드워드(즉, 리피티션된 비트들을 포함하는 LDPC 코드워드 비트들로, 리피티션 이후의 LDPC 코드워드(LDPC codeword with repetition)라 할 수도 있다)을 평처링부(130)로 출력할 수 있다. 또한, 리피티션부(120)는 리피티션 이후의 LDPC 코드워드를 부가 패리티 생성부(140)로 출력하고, 리피티션 비트들에 대한 정보(가령, 리피티션 비트들의 개수 및 위치 등)를 부가 패리티 생성부(140)로 제공할 수 있다.

- [0137] 구체적으로, 리피티션부(120)는 특정한 수의 LDPC 코드워드 비트들(예를 들어,  $N_{repeat}$  개의 LDPC 패리티 비트들)을 LDPC 코드워드 내에서 특정한 위치에 리피티션할 수 있다. 이 경우, 리피티션 비트들의 수는 시스템에 따라 다양한 값을 가질 수 있다.

- [0138] 예를 들어, 리피티션부(120)는 특정한 수의 LDPC 패리티 비트들을 LDPC 정보어 비트들 및 LDPC 패리티 비트들을 포함하는 LDPC 코드워드 내에서 LDPC 정보어 비트들 이후에 부가할 수 있다. 즉, 리피티션부(120)는 패리티 비트들의 적어도 일부 비트들을 입력 비트들 즉, LDPC 정보어 비트들 이후에 부가할 수 있다.

- [0139] 또한, 리피티션부(120)는 특정한 수의 LDPC 패리티 비트들을 LDPC 패리티 비트들 이후에 부가하거나, LDPC 정보어 비트들 사이의 특정한 위치에 부가하거나, LDPC 패리티 비트들 사이의 특정한 위치에 부가할 수도 있다.

- [0140] 이에 따라, 리피티션 이후의 LDPC 코드워드 내에서 특정한 수의 LDPC 패리티 비트들은 반복되며, 수신 장치(200)로 추가적으로 전송될 수 있다는 점에서, 상술한 동작을 리피티션(repetition)이라 할 수 있다. 그리고, 리피티션 이후의 LDPC 코드워드에서 리피티션되는 비트들을 리피티션 비트들(repetition bits)(또는, 리피티션된 비트들(repeated bits))이라 할 수 있다.

- [0141] 이하에서는 도면을 참조하여, 본 발명의 다양한 실시 예에 따라 비트들이 리피티션되는 일 예를 설명하도록 한다.

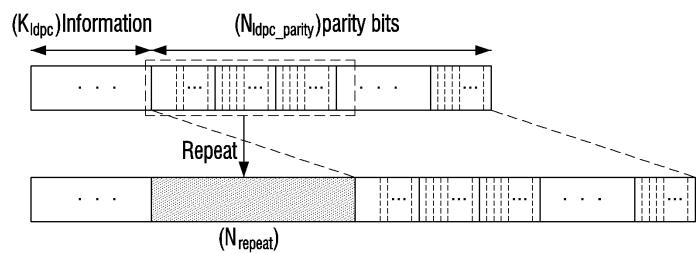

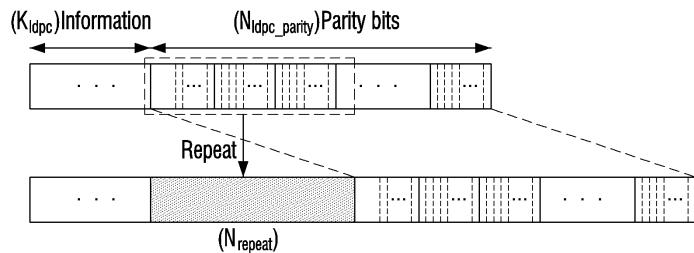

- [0142] 리피티션부(120)는 리피티션 비트들의 수  $N_{repeat}$  가 LDPC 패리티 비트들의 수보다 작거나 같은 경우, 첫 번째 LDPC 패리티 비트부터  $N_{repeat}$  개의 비트들을 LDPC 정보어 비트들 이후에 부가할 수 있다.

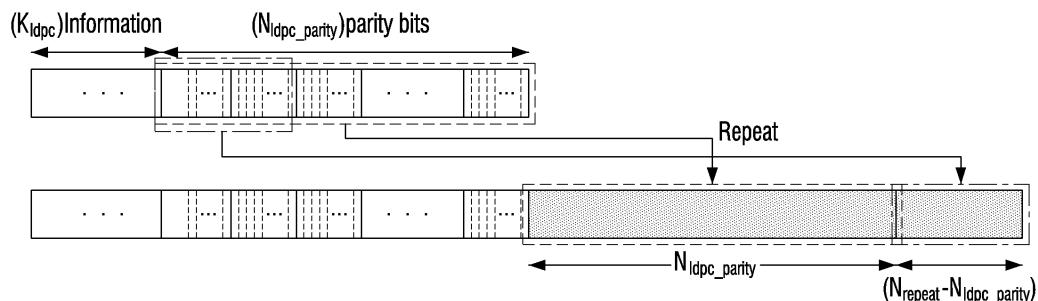

- [0143] 예를 들어,  $N_{repeat} \leq N_{ldpc\_parity}$  보다 작거나 같은 경우, 즉,  $N_{repeat} \leq N_{ldpc\_parity}$ 인 경우, 리피티션부(120)는 도 4와 같이, LDPC 패리티 비트들  $(p_0, p_1, \dots, p_{N_{ldpc} - K_{ldpc} - 1})$ 의 처음  $N_{repeat}$  개의 비트들  $(p_0, p_1, \dots, p_{N_{repeat}-1})$ 을 LDPC 정보어 비트들  $(i_0, i_1, \dots, i_{K_{ldpc}-1})$  다음에 부가할 수 있다.

- [0144] 이에 따라, LDPC 패리티 비트들 중 첫 번째 비트부터  $N_{repeat}$  번째 비트는 LDPC 정보어 비트들 이후에 부가되며,  $(i_0, i_1, \dots, i_{K_{ldpc}-1}, p_0, p_1, \dots, p_{N_{repeat}-1}, p_0, p_1, \dots, p_{N_{ldpc} - K_{ldpc} - 1})$ 와 같이  $N_{repeat}$  개의 비트들은 LDPC 정보어 비트들과 LDPC 패리티 비트들 사이에 위치하게 된다.

- [0145] 한편, 리피티션부(120)는 리피티션 비트들의 수  $N_{repeat}$  가 LDPC 패리티 비트들의 수보다 큰 경우, LDPC 패리티 비트들 전체를 LDPC 정보어 비트들 이후에 부가하고, 첫 번째 LDPC 패리티 비트부터 리피티션 비트들의 수에서 LDPC 패리티 비트들의 수를 뺀 수만큼의 비트들을 먼저 부가된 LDPC 패리티 비트들 이후에 추가적으로 부가할 수 있다.

- [0146] 이 경우, 리피티션부(120)는 리피티션된 LDPC 패리티 비트들이 아닌, 기존의 LDPC 패리티 비트들 즉, 인코딩에 의해 생성된 LDPC 패리티 비트들 중 첫 번째 비트부터 리피티션 비트들의 수에서 LDPC 패리티 비트들의 수를 뺀

수만큼의 비트들을 먼저 부가된 LDPC 패리티 비트들 이후에 추가적으로 부가할 수 있다.

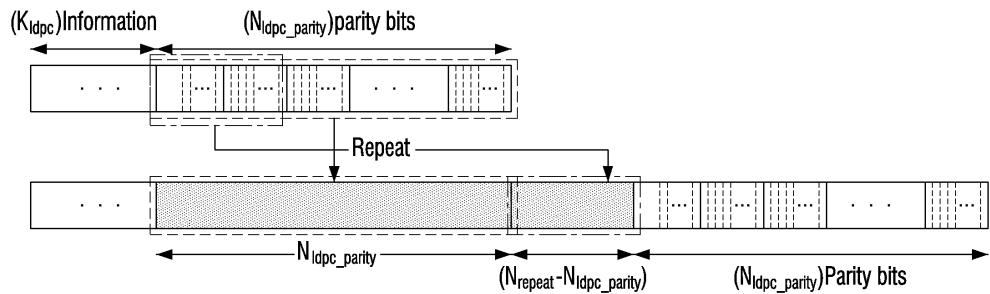

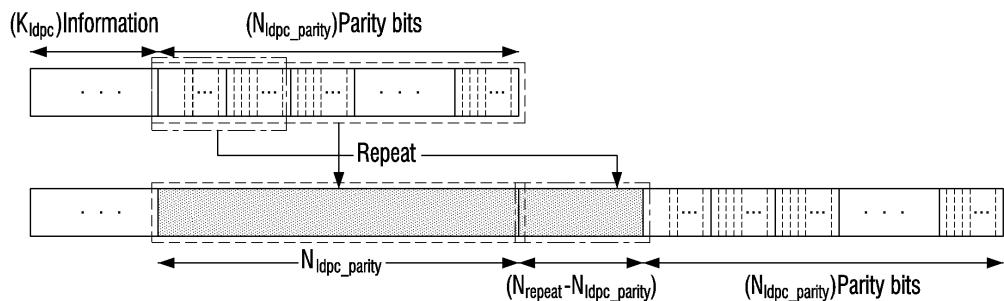

[0147] 예를 들어,  $N_{repeat} \leq N_{ldpc\_parity}$  보다 큰 경우, 즉,  $N_{repeat} > N_{ldpc\_parity}$ 인 경우, 리피티션부(120)는 도 5과 같이,

$N_{ldpc\_parity}$  개의 LDPC 패리티 비트들  $(p_0, p_1, \dots, \overset{P}{p}_{N_{ldpc}-K_{ldpc}-1})$ 을 LDPC 정보어 비트들  $(i_0, i_1, \dots, \overset{i}{i}_{K_{ldpc}-1})$  다음에 부가한다. 그리고, 리피티션부(120)는 LDPC 패리티 비트들의 처음  $N_{repeat}-N_{ldpc\_parity}$  개의 비트들

$(p_0, p_1, \dots, \overset{P}{p}_{N_{repeat}-N_{ldpc\_parity}-1})$ 을 먼저 부가된  $N_{ldpc\_parity}$  개의 LDPC 패리티 비트들 다음에 추가적으로 부가할 수 있다.

[0148] 이에 따라,  $N_{ldpc\_parity}$  개의 LDPC 패리티 비트들이 LDPC 정보어 비트들 이후에 부가되고, LDPC 패리티 비트들의 처음  $N_{repeat}-N_{ldpc\_parity}$  개의 비트들이 먼저 부가된  $N_{ldpc\_parity}$  개의 LDPC 패리티 비트들 이후에 추가적으로 부가될 수 있다.

[0149] 따라서,  $(i_0, i_1, \dots, \overset{i}{i}_{K_{ldpc}-1}, p_0, p_1, \dots, \overset{P}{p}_{N_{ldpc}-K_{ldpc}-1}, p_0, p_1, \dots, \overset{P}{p}_{N_{repeat}-N_{ldpc\_parity}-1}, p_0, p_1, \dots, \overset{P}{p}_{N_{ldpc}-K_{ldpc}-1})$ 와 같아  $N_{repeat}$  개의 비트들은 LDPC 정보어 비트들과 LDPC 패리티 비트들 사이에 위치하게 된다.

[0150] 한편, 상술한 예에서는 리피티션 비트들이 LDPC 정보어 비트들 이후에 부가되는 것으로 설명하였으나, 이는 일 예에 불과하며, 리피티션부(120)는 리피티션 비트들을 LDPC 패리티 비트들 이후에 부가할 수도 있다.

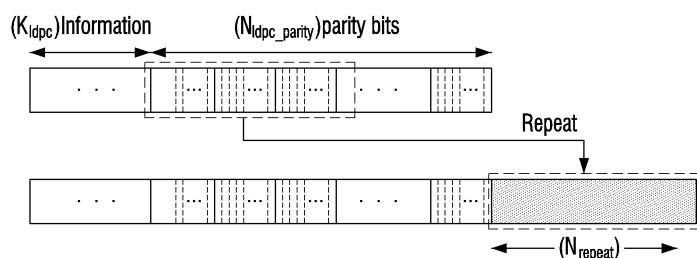

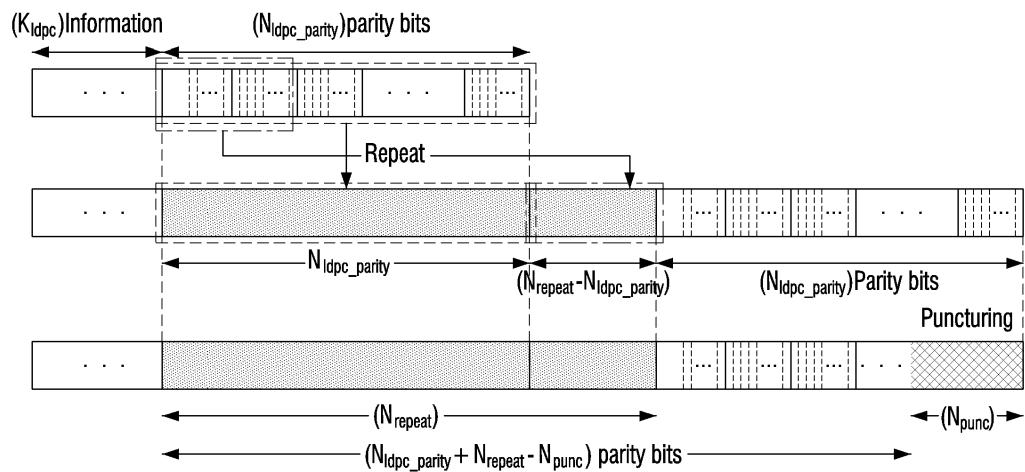

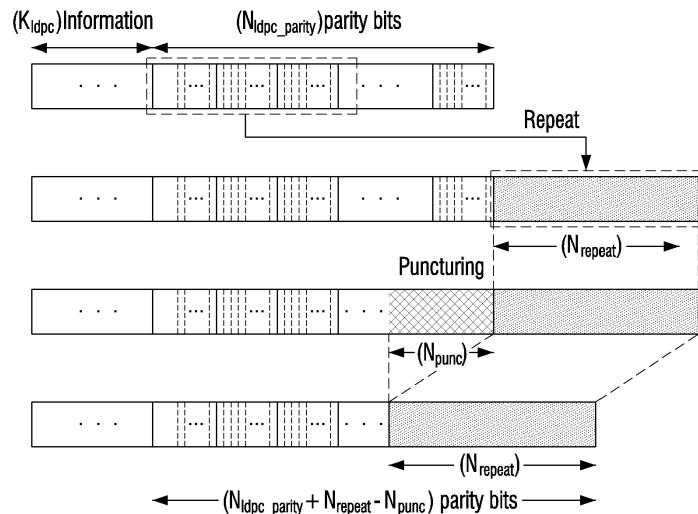

[0151] 예를 들어,  $N_{repeat} \leq N_{ldpc\_parity}$  보다 작거나 같은 경우, 즉,  $N_{repeat} \leq N_{ldpc\_parity}$ 인 경우, 리피티션부(120)는 도 6과 같이, LDPC 패리티 비트들  $(p_0, p_1, \dots, \overset{P}{p}_{N_{ldpc}-K_{ldpc}-1})$ 의 처음  $N_{repeat}$  개의 비트들  $(p_0, p_1, \dots, \overset{P}{p}_{N_{repeat}-1})$ 을 LDPC 패리티 비트들 다음에 부가할 수 있다.

[0152] 이에 따라, LDPC 패리티 비트들 중 첫 번째 비트부터  $N_{repeat}$  번째 비트는 LDPC 패리티 비트들 이후에 부가되며,  $(i_0, i_1, \dots, \overset{i}{i}_{K_{ldpc}-1}, p_0, p_1, \dots, \overset{P}{p}_{N_{ldpc}-K_{ldpc}-1}, p_0, p_1, \dots, \overset{P}{p}_{N_{repeat}-1})$ 와 같이  $N_{repeat}$  개의 비트들은 LDPC 패리티 비트들 이후에 위치하게 된다.

[0153] 그리고,  $N_{repeat} \leq N_{ldpc\_parity}$  보다 큰 경우, 즉,  $N_{repeat} > N_{ldpc\_parity}$ 인 경우, 리피티션부(120)는 도 7과 같이,  $N_{ldpc\_parity}$  개의 LDPC 패리티 비트들  $(p_0, p_1, \dots, \overset{P}{p}_{N_{ldpc}-K_{ldpc}-1})$ 을 LDPC 패리티 비트들 다음에 부가할 수 있다. 그리고, 리피티션부(120)는 LDPC 패리티 비트들의 처음  $N_{repeat}-N_{ldpc\_parity}$  개의 비트들  $(p_0, p_1, \dots, \overset{P}{p}_{N_{repeat}-N_{ldpc\_parity}-1})$ 을 먼저 부가된  $N_{ldpc\_parity}$  개의 LDPC 패리티 비트들 다음에 추가적으로 부가할 수 있다.

[0154] 이에 따라,  $N_{ldpc\_parity}$  개의 LDPC 패리티 비트들이 LDPC 패리티 비트들 이후에 부가되고, LDPC 패리티 비트들의 처음  $N_{repeat}-N_{ldpc\_parity}$  개의 비트들이 먼저 부가된  $N_{ldpc\_parity}$  개의 LDPC 패리티 비트들 이후에 추가적으로 부가될 수 있다.

[0155] 따라서,  $(i_0, i_1, \dots, \overset{i}{i}_{K_{ldpc}-1}, p_0, p_1, \dots, \overset{P}{p}_{N_{ldpc}-K_{ldpc}-1}, p_0, p_1, \dots, \overset{P}{p}_{N_{ldpc}-K_{ldpc}-1}, p_0, p_1, \dots, \overset{P}{p}_{N_{repeat}-N_{ldpc\_parity}-1})$ 와 같이  $N_{repeat}$  개의 비트들은 LDPC 패리티 비트들 이후에 위치하게 된다.

[0156] 또한, 상술한 예에서는 앞 부분의 LDPC 패리티 비트들이 리피티션되는 것으로 설명하였으나, 이는 일 예에 불과하며, 리피티션부(120)는 LDPC 패리티 비트들의 뒤 부분 또는 중간 부분 등 다양한 위치에 존재하는 LDPC 패리티 비트들이 리피티션될 수도 있다.

[0157] 또한, 상술한 예에서는 LDPC 패리티 비트들이 리피티션되는 것으로 설명하였으나, 이는 일 예에 불과하며, LDPC 정보어 비트들 또는 LDPC 정보어 비트들의 일부 및 LDPC 패리티 비트들의 나머지 일부가 리피티션될 수도 있다.

[0158] 또한, 상술한 예에서는 리피티션이 수행되는 것으로 설명하였으나, 이는 일 예에 불과하며, 경우에 따라 리피티

션은 생략될 수도 있다. 이 경우, LDPC 코드워드에 포함된 LDPC 패리티 비트들의 일부 비트들은 후술할 평처링부(130)에 의해 평처링될 수 있다. 한편, 리피티션 수행 여부는 시스템에 따라 기설정되어 있을 수 있다.

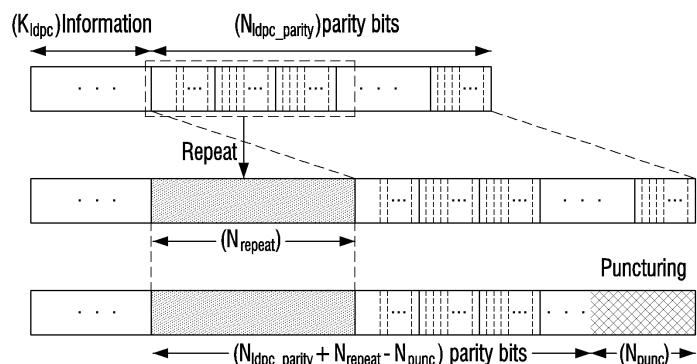

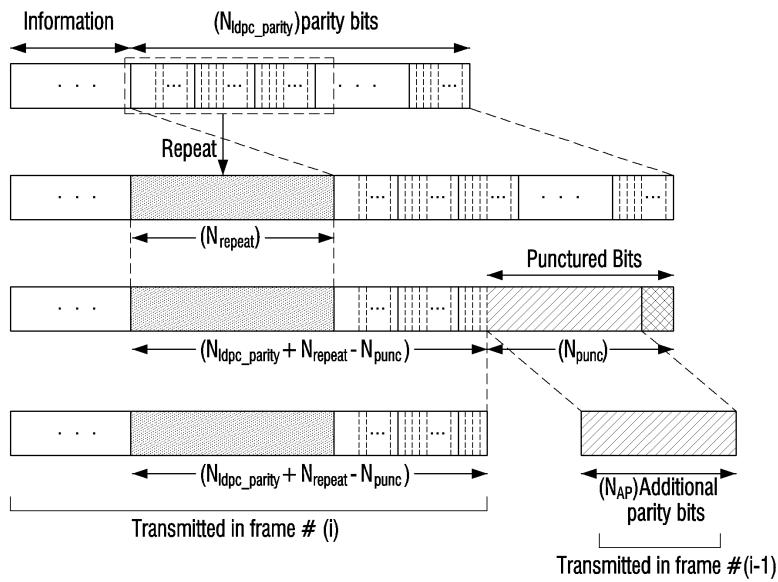

[0159] 평처링부(130)는 LDPC 패리티 비트들에서 일부 비트들을 평처링할 수 있다. 그리고, 평처링부(130)는 평처링된 LDPC 코드워드(즉, 평처링된 비트들을 제외한 나머지 LDPC 코드워드 비트들을 의미하며, 평처링 이후의 LDPC 코드워드라 할 수도 있다)를 출력한다. 또한, 평처링부(130)는 평처링된 LDPC 패리티 비트들에 대한 정보(가령, 평처링되는 비트들의 개수 및 위치 등)를 부가 패리티 생성부(140)로 제공할 수 있다.

[0160] 여기에서, 평처링(puncturing)은 LDPC 패리티 비트들의 일부 비트들을 수신 장치(200)로 전송하지 않는 것을 의미한다. 이 경우, 평처링부(130)는 평처링되는 LDPC 패리티 비트들을 제거하거나, LDPC 코드워드에서 평처링되는 LDPC 패리티 비트들을 제외하고 나머지 비트들만을 출력할 수 있다.

[0161] 구체적으로, 평처링부(130)는 LDPC 패리티 비트들에서 특정한 수의 비트들(가령,  $N_{punc}$  개의 비트들)을 평처링할 수 있다. 여기에서, 평처링되는 비트들의 수  $N_{punc}$ 는 0 또는 양의 정수로, 시스템에 따라 다양한 값을 가질 수 있다. 한편,  $N_{punc}=0$ 이라는 것은 평처링이 수행되지 않는 것을 의미한다.

[0162] 이 경우, 평처링부(130)는 LDPC 패리티 비트들의 뒷 부분에서 특정한 수의 비트들을 평처링할 수 있다. 예를 들어, 평처링부(130)는 마지막 LDPC 패리티 비트부터  $N_{punc}$  개의 LDPC 패리티 비트들을 평처링할 수 있다.

[0163] 하지만, 이는 일 예일 뿐이며, LDPC 패리티 비트들에서 비트들이 평처링되는 위치는 다양하게 변경될 수 있다. 예를 들어, 평처링부(130)는 LDPC 패리티 비트들의 앞 부분 또는 중간 부분에서  $N_{punc}$  개의 LDPC 패리티 비트들을 평처링하거나, LDPC 패리티 비트들에서 특정한 위치에 존재하는  $N_{punc}$  개의 LDPC 패리티 비트들을 평처링할 수도 있다.

[0164] 또한, 평처링부(130)는 리피티션이 수행된 경우, 리피티션 비트들이 아닌, 인코딩에 의해 생성된 LDPC 패리티 비트에서 특정한 수의 비트들을 평처링할 수 있다.

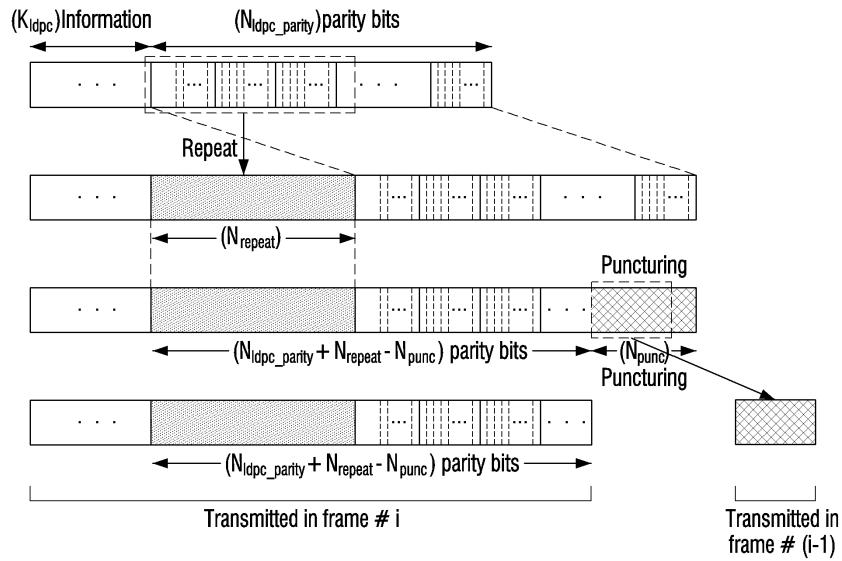

[0165] 예를 들어, 리피티션이 수행되어,  $N_{repeat}$  개의 LDPC 패리티 비트들이 LDPC 정보어 비트들 이후에 부가된 경우를 가정한다.

[0166] 이 경우, 리피티션 이후의 LDPC 코드워드는 리피티션 비트들 및 인코딩에 의해 생성된 LDPC 패리티 비트들을 포함한다. 이때, 리피티션 비트들은 LDPC 정보어 비트들과 인코딩에 의해 생성된 LDPC 패리티 비트들 사이에 위치하게 되므로, 평처링부(130)는 인코딩에 의해 생성된 LDPC 패리티 비트들 중 마지막 LDPC 패리티 비트부터  $N_{punc}$  개의 비트들을 평처링할 수 있다.

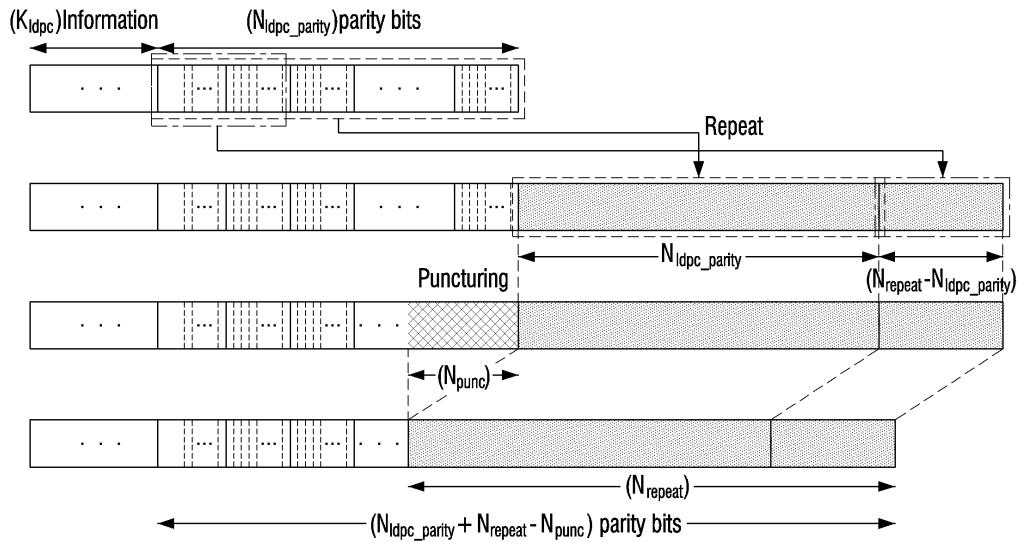

[0167] 이하에서는 첨부된 도 8 내지 도 11을 참조하여, 본 발명의 다양한 실시 예에 따라 평처링 방법을 설명하도록 한다. 도 8 내지 도 11에서는 도 4 내지 도 8과 같이 리피티션이 수행된 경우의 평처링 방법을 설명하기 위한 예들이다.

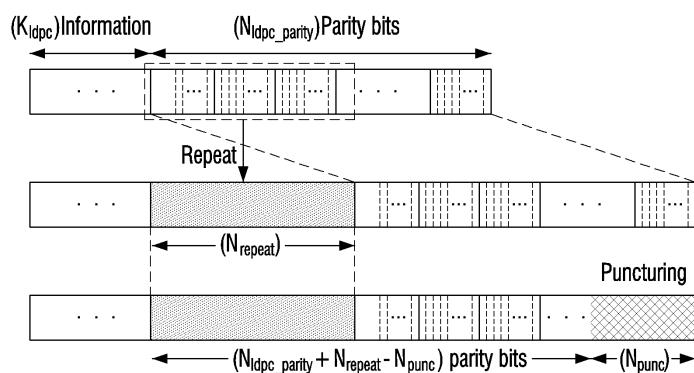

[0168] 먼저, 도 4와 같이, 리피티션에 의해  $N_{repeat}$  개의 LDPC 패리티 비트들이 LDPC 정보어 비트들 이후에 부가된 경우를 가정한다.

[0169] 이 경우, 도 8과 같이, 평처링부(130)는  $N_{ldpc\_parity}$  개의 LDPC 패리티 비트들의 마지막  $N_{punc}$  개의 비트들을 평처링할 수 있다.

[0170] 이에 따라, 리피티션 및 평처링 이후의 LDPC 코드워드(즉, 평처링된 비트들을 제외하고, 리피티션된 비트들을 포함하는 LDPC 코드워드 비트들)에서 LDPC 패리티 비트들은  $N_{ldpc\_parity} + N_{repeat} - N_{punc}$  개이고,

$(p_0, p_1, \dots, \mathbf{P}^{N_{repeat}-1}, p_0, p_1, \dots, \mathbf{P}^{N_{ldpc} - K_{ldpc} - N_{punc} - 1})$ 와 나타낼 수 있다.

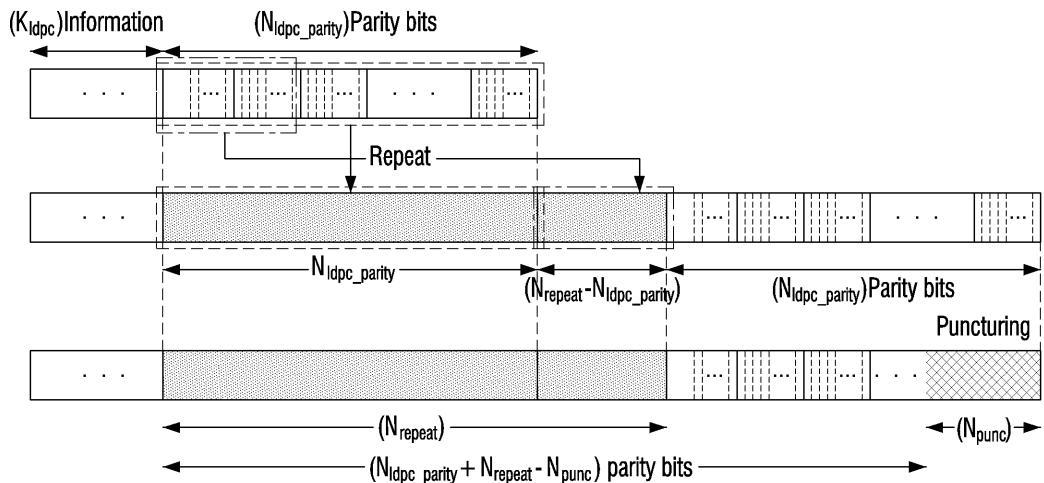

[0171] 다른 예로, 도 5와 같이, 리피티션에 의해  $N_{repeat}$  개의 LDPC 패리티 비트들이 LDPC 정보어 비트들 이후에 부가된 경우를 가정한다.

[0172] 이 경우, 도 9와 같이, 평처링부(130)는  $N_{ldpc\_parity}$  개의 LDPC 패리티 비트들의 마지막  $N_{punc}$  개의 비트들을 평처링할 수 있다.

- [0173] 이에 따라, 리피티션 및 평처링 이후의 LDPC 코드워드에서 LDPC 패리티 비트들은  $N_{ldpc\_parity} + N_{repeat} - N_{punc}$  개이고,  $(p_0, p_1, \dots, \mathbf{P}^{N_{ldpc} - K_{ldpc} - 1}, p_0, p_1, \dots, \mathbf{P}^{N_{repeat} - N_{ldpc\_parity} - 1}, p_0, p_1, \dots, \mathbf{P}^{N_{ldpc} - K_{ldpc} - N_{punc} - 1})$ 와 같이 나타낼 수 있다.

- [0174] 또 다른 예로, 도 6과 같이, 리피티션에 의해  $N_{repeat}$  개의 LDPC 패리티 비트들이 LDPC 패리티 비트들 이후에 부가된 경우를 가정한다.

- [0175] 이 경우, 도 10과 같이, 평처링부(130)는  $N_{ldpc\_parity}$  개의 LDPC 패리티 비트들의 마지막  $N_{punc}$  개의 비트들을 평처링할 수 있다.

- [0176] 이에 따라, 리피티션 및 평처링 이후의 LDPC 코드워드에서 LDPC 패리티 비트들은  $N_{ldpc\_parity} + N_{repeat} - N_{punc}$  개이고,  $(p_0, p_1, \dots, \mathbf{P}^{N_{ldpc} - K_{ldpc} - N_{punc} - 1}, p_0, p_1, \dots, \mathbf{P}^{N_{repeat} - 1})$ 와 같이 나타낼 수 있다.

- [0177] 또 다른 예로, 도 7과 같이, 리피티션에 의해  $N_{repeat}$  개의 LDPC 패리티 비트들이 LDPC 패리티 비트들 이후에 부가된 경우를 가정한다.

- [0178] 이 경우, 도 11과 같이, 평처링부(130)는  $N_{ldpc\_parity}$  개의 LDPC 패리티 비트들의 마지막  $N_{punc}$  개의 비트들을 평처링할 수 있다.

- [0179] 이에 따라, 리피티션 및 평처링 이후의 LDPC 코드워드에서 LDPC 패리티 비트들은  $N_{ldpc\_parity} + N_{repeat} - N_{punc}$  개이고,  $(p_0, p_1, \dots, \mathbf{P}^{N_{ldpc} - K_{ldpc} - N_{punc} - 1}, p_0, p_1, \dots, \mathbf{P}^{N_{ldpc} - K_{ldpc} - 1}, p_0, p_1, \dots, \mathbf{P}^{N_{repeat} - N_{ldpc\_parity} - 1})$ 와 같이 나타낼 수 있다.

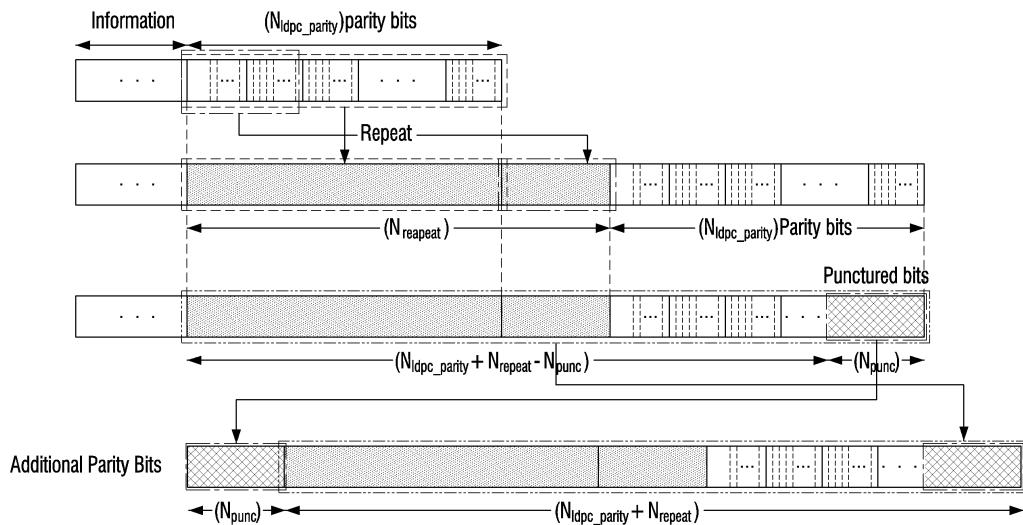

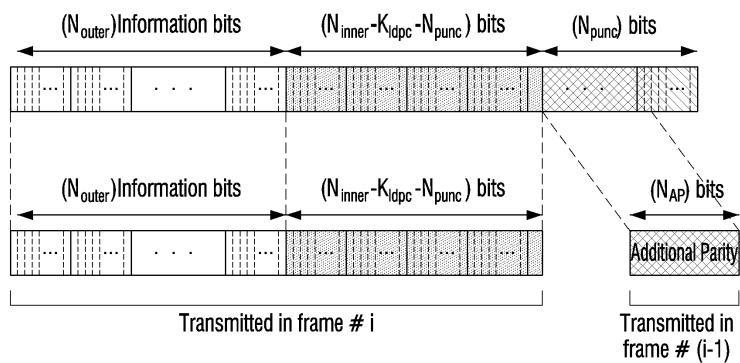

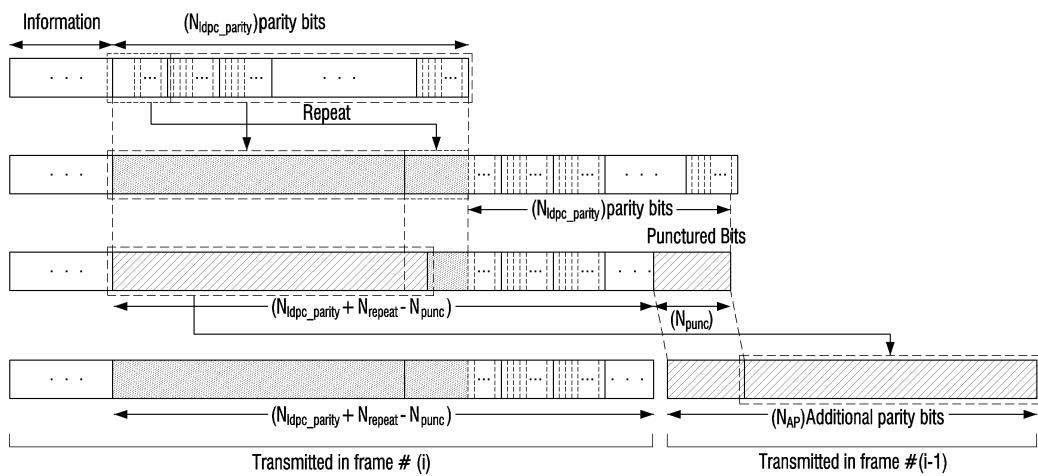

- [0180] 부가 패리티 생성부(140)는 패리티 비트들에서 적어도 일부의 비트들을 선택하여, 이전 프레임에서 전송되는 부가 패리티 비트들(additional parity bits)을 생성한다.

- [0181] 이 경우, 부가 패리티 비트들은 현재 프레임에서 전송되는 정보어 비트들에 기초하여 생성된 LDPC 패리티 비트들 중에서 선택되어 현재 프레임 이전의 프레임 즉, 이전 프레임을 통해 수신 장치(200)로 전송될 수 있다.

- [0182] 구체적으로, 정보어 비트들을 포함하는 입력 비트들은 LDPC 인코딩되고, LDPC 인코딩에 의해 생성된 LDPC 패리티 비트들이 입력 비트들에 부가되어 LDPC 코드워드를 구성한다.

- [0183] 그리고, LDPC 코드워드에 대해 리피티션, 평처링 및 쇼트닝이 수행되고, 리피티션, 평처링 및 쇼트닝된 LDPC 코드워드(repeated/punctured/shortened LDPC codeword)(즉, 평처링된 비트들 및 쇼트닝된 비트들을 제외하고, 리피티션된 비트들을 포함하는 LDPC 코드워드 비트들로, 리피티션, 평처링 및 쇼트닝 이후의 LDPC 코드워드라 할 수도 있다)은 프레임에 맵핑되어 수신 장치(200)로 전송될 수 있다. 다만, 리피티션이 수행되지 않는 경우, 평처링 및 쇼트닝 이후의 LDPC 코드워드가 프레임에 맵핑되어 수신 장치(200)로 전송될 수 있다.

- [0184] 이 경우, 각 프레임마다 그에 대응되는 정보어 비트들이 LDPC 패리티 비트들과 함께 각 프레임을 통해 수신 장치(200)로 전송될 수 있다. 예를 들어,  $i-1$  번째 프레임에 대응되는 정보어 비트들을 포함하는 리피티션, 평처링 및 쇼트닝 이후의 LDPC 코드워드는  $i-1$  번째 프레임에 맵핑되어 수신 장치(200)로 전송되고,  $i$  번째 프레임에 대응되는 정보어 비트들을 포함하는 리피티션, 평처링 및 쇼트닝 이후의 LDPC 코드워드는  $i$  번째 프레임에 맵핑되어 수신 장치(200)로 전송될 수 있다.

- [0185] 한편, 부가 패리티 생성부(140)는  $i$  번째 프레임에서 전송되는 정보어 비트들에 기초하여 생성된 LDPC 패리티 비트들에서 적어도 일부 비트들을 선택하여 부가 패리티 비트들을 생성할 수 있다.

- [0186] 구체적으로, 정보어 비트들이 LDPC 인코딩되어 생성된 LDPC 패리티 비트들에서 일부 비트들은 평처링되어 수신 장치(200)로 전송되지 않는다. 이 경우, 부가 패리티 생성부(140)는  $i$  번째 프레임에서 전송되는 정보어 비트들이 LDPC 인코딩되어 생성된 LDPC 패리티 비트들 중 평처링된 LDPC 패리티 비트들에서 일부 또는 전체 비트들을 선택하여 부가 패리티 비트들을 생성할 수 있다.

- [0187] 또한, 부가 패리티 생성부(140)는  $i$  번째 프레임을 통해 수신 장치(200)로 전송되는 LDPC 패리티 비트들에서 적

어도 일부 비트들을 선택하여 부가 패리티 비트들을 생성할 수 있다.

[0188] 구체적으로, i 번째 프레임에 맵핑되는 리피티션, 평처링 및 쇼트닝 이후의 LDPC 코드워드에 포함된 LDPC 패리티 비트들은 인코딩에 의해 생성된 LDPC 패리티 비트들 및 리피티션된 LDPC 패리티 비트들로 구성될 수 있다.

[0189] 이 경우, 부가 패리티 생성부(140)는 i 번째 프레임에 맵핑되는 리피티션, 평처링 및 쇼트닝 이후의 LDPC 코드워드에 포함된 LDPC 패리티 비트들에서 적어도 일부 비트들을 선택하여 부가 패리티 비트들을 생성할 수 있다. 다만, 리피티션이 생략되는 경우, 부가 패리티 생성부(140)는 i 번째 프레임에 맵핑되는 평처링 및 쇼트닝 이후의 LDPC 코드워드에 포함된 LDPC 패리티 비트들에서 적어도 일부 비트들을 선택하여 부가 패리티 비트들을 생성할 수 있다.

[0190] 한편, 부가 패리티 비트들은 i 번째 프레임 이전의 프레임 즉, i-1 번째 프레임을 통해 수신 장치(200)로 전송될 수 있다.

[0191] 즉, 송신 장치(100)는 i-1 번째 프레임에 대응되는 정보어 비트들을 포함하는 리피티션, 평처링 및 쇼트닝 이후의 LDPC 코드워드뿐만 아니라, i 번째 프레임에서 전송되는 정보어 비트들에 기초하여 생성된 LDPC 패리티 비트들에서 선택되어 생성된 부가 패리티 비트들을 i-1 번째 프레임을 통해 수신 장치(200)로 전송할 수 있다.

[0192] 한편, 상술한 예에서는 부가 패리티 비트들이 i-1 번째 프레임을 통해 수신 장치(200)로 전송되는 것으로 설명하였으나 이는 일 예일 뿐이며, 부가 패리티 비트들은 시간적으로 i 번째 프레임 이전에 전송되는 프레임을 통해 수신 장치(200)로 전송될 수도 있다.

[0193] 이하에서는 LDPC 패리티 비트들에서 비트들을 선택하여 부가 패리티 비트들을 생성하는 방법에 대해 구체적으로 설명하도록 한다.

[0194] 부가 패리티 생성부(140)는 LDPC 코드워드 비트들에서 부가 패리티 비트들의 수만큼을 선택하여 부가 패리티 비트들을 생성할 수 있다.

[0195] 구체적으로, 부가 패리티 생성부(140)는 평처링된 LDPC 패리티 비트들의 수가 부가 패리티 비트들의 수보다 크거나 같은 경우, 평처링된 LDPC 패리티 비트들 중 첫 비트부터 부가 패리티 비트들의 수만큼의 비트들을 선택하여 부가 패리티 비트들을 생성할 수 있다.

[0196] 한편, 부가 패리티 생성부(140)는 평처링된 LDPC 패리티 비트들의 수가 부가 패리티 비트들의 수보다 작은 경우, 평처링된 모든 비트들을 먼저 선택하고, LDPC 코드워드에 포함된 LDPC 패리티 비트들 중 첫 번째 비트부터 부가 패리티 비트들의 수에서 평처링된 LDPC 패리티 비트들의 수를 뺀 수만큼의 비트들을 추가적으로 선택하여 부가 패리티 비트들을 생성할 수 있다.

[0197] 구체적으로, 리피티션이 수행되지 않은 경우, LDPC 코드워드에 포함된 LDPC 패리티 비트들은 인코딩에 의해 생성된 LDPC 패리티 비트들이다.

[0198] 이 경우, 부가 패리티 생성부(140)는 평처링된 모든 LDPC 패리티 비트들을 먼저 선택하고, 인코딩에 의해 생성된 LDPC 패리티 비트들 중 첫 번째 비트부터 부가 패리티 비트들의 수에서 평처링된 LDPC 패리티 비트들의 수를 뺀 수만큼의 비트들을 추가적으로 선택하여 부가 패리티 비트들을 생성할 수 있다.

[0199] 여기에서, 인코딩에 의해 생성된 LDPC 패리티 비트들은 평처링되지 않는 LDPC 패리티 비트들과 평처링되는 LDPC 패리티 비트들로 구분된다. 따라서, 인코딩에 의해 생성된 LDPC 패리티 비트들 중 마지막 비트부터 평처링이 수행되는 경우, 부가 패리티 비트들을 위해, 인코딩에 의해 생성된 LDPC 패리티 비트들 중 첫 번째 비트부터 비트들을 선택할 때, 평처링되지 않는 LDPC 패리티 비트들 및 평처링되는 LDPC 패리티 비트들 순으로 비트들이 선택될 수 있다.

[0200] 한편, 리피티션이 수행된 경우, 부가 패리티 생성부(140)는 리피티션 이후의 LDPC 코드워드에서 적어도 일부 비트들을 선택하여, 부가 패리티 비트들을 생성할 수 있다.

[0201] 상술한 바와 같이, 리피티션 이후의 LDPC 코드워드의 LDPC 패리티 비트들은 리피티션된 비트들 및 인코딩에 의해 생성된 LDPC 패리티 비트들을 포함한다. 이 경우, 부가 패리티 생성부(140)는 평처링된 모든 LDPC 패리티 비트들을 먼저 선택하고, 리피티션된 비트들 및 인코딩에 의해 생성된 LDPC 패리티 비트들 중 리피티션된 비트들의 첫 번째 비트부터 부가 패리티 비트들의 수에서 평처링된 LDPC 패리티 비트들의 수를 뺀 수만큼의 비트들을 추가적으로 선택하여 부가 패리티 비트들을 생성할 수 있다.

- [0202] 이에 따라, 부가 패리티 비트들의 수에서 평처링된 LDPC 패리티 비트들의 수를 뺀 수만큼의 비트들을 추가적으로 선택할 때, 리피티션된 비트들이 먼저 선택되고, 부가 패리티 비트들의 수에서 평처링된 LDPC 패리티 비트들의 수를 뺀 수가 리피티션 비트들의 수를 초과하는 경우 인코딩에 의해 생성된 LDPC 패리티 비트들에서 비트들이 추가로 선택될 수 있다. 이 경우, 인코딩에 의해 생성된 LDPC 패리티 비트들에서 추가로 선택되는 경우, 인코딩에 의해 생성된 LDPC 패리티 비트들 중 첫 번째 비트부터 선택될 수 있다.

- [0203] 여기에서, 상술한 바와 같이 리피티션 비트들은 리피티션 이후의 LDPC 코드워드 내에서 다양한 위치에 위치할 수 있다.

- [0204] 이하에서는, 리피티션된 LDPC 패리티 비트들은 LDPC 정보어 비트들 및 LDPC 패리티 비트들 사이에 위치하는 경우를 일 예로, 리피티션이 수행된 경우의 부가 패리티 생성 방법에 대해 보다 구체적으로 설명하도록 한다.

- [0205] 이 경우, 리피티션부(120)는 LDPC 패리티 비트들의 적어도 일부 비트들을 선택하여, LDPC 정보어 비트들 이후에 부가하고, 평처링부(130)는 리피티션된 LDPC 패리티 비트들 및 인코딩에 의해 생성된 LDPC 패리티 비트들을 포함하는 LDPC 패리티 비트들 중 마지막 비트부터 평처링을 수행하는 경우를 가정한다.

- [0206] 이 경우, 부가 패리티 생성부(140)는 부가 패리티 비트들의 수 및 평처링된 LDPC 패리티 비트들의 수에 기초하여 입력 비트들 즉, LDPC 정보어 비트들 이후에 부가된 리피티션된 비트들에서 적어도 일부 비트들을 선택하여 부가 패리티 비트들을 생성할 수 있다.

- [0207] 구체적으로, 부가 패리티 생성부(140)는 부가 패리티 비트들의 수가 평처링된 LDPC 패리티 비트들의 수보다 큰 경우, 평처링된 LDPC 패리티 비트들 전체를 선택하고, 리피티션된 비트들 중 첫 번째 비트부터 부가 패리티 비트들의 수에서 평처링된 LDPC 패리티 비트들의 수를 뺀 수만큼의 비트들을 선택하여 부가 패리티 비트들을 생성할 수 있다.

- [0208] 여기에서, 부가 패리티 비트들을 위해, 리피티션된 LDPC 패리티 비트들 중 첫 번째 비트부터 비트들을 선택할 때, 리피티션 비트들 및 인코딩에 의해 생성된 LDPC 패리티 비트들 순으로 선택될 수 있다. 또한, 인코딩에 의해 생성된 LDPC 패리티 비트들 내에서는, 평처링되지 않는 LDPC 패리티 비트들 및 평처링되는 LDPC 패리티 비트들 순으로 비트들이 선택될 수 있다.

- [0209] 이와 같이, 특정한 수만큼의 부가 패리티 비트들을 생성할 때, 평처링된 비트들을 가장 우선적으로 선택한다. 그리고, 평처링된 비트들을 초과하는 개수만큼의 비트들을 선택하는 경우, 리피티션 수행 여부에 따라, LDPC 패리티 비트들 중에서 리피티션된 LDPC 패리티 비트들을 우선적으로 선택하게 된다.

- [0210] 이와 같이, 평처링 비트들을 우선적으로 선택하여, 현재 프레임에서 전송되지 않는 패리티 비트들을 부가 패리티 비트들로서 전송한다는 점에서, 부호 이득을 얻을 수 있다. 그리고, 평처링 비트들을 선택한 이후에는, 리피티션된 LDPC 패리티 비트들을 선택함으로써 LDPC 패리티 비트들 중에서 더 중요한 비트들을 선택하게 된다. 또한, LDPC 패리티 비트들은 평처링 순서에 따라 정렬되어 있기 때문에, 패리티 비트들의 우선 순위에 따라 정렬되어 있는 것으로 생각할 수 있다. 한편, 평처링 순서와 관련된 구체적인 내용은 후술하기로 한다.

- [0211] 한편, 평처링이 수행되지 않는 경우, 즉, 평처링되는 비트들의 수가 0인 경우, 부가 패리티 생성부(140)는 리피티션 수행 여부에 따라 LDPC 코드워드 또는 리피티션 이후의 LDPC 코드워드에서 적어도 일부 비트들을 선택하여 부가 패리티 비트들을 생성할 수 있다.

- [0212] 먼저, 리피티션이 수행되지 않는 경우, 부가 패리티 생성부(140)는 LDPC 패리티 비트들 중 첫 번째 비트부터 부가 패리티 비트들의 수만큼의 비트들을 선택하여 부가 패리티 비트들을 생성할 수 있다. 즉, 평처링된 비트들의 수가 0이고, 리피티션된 비트들의 수가 0인 경우, 부가 패리티 생성부(140)는 인코딩에 의해 생성된 LDPC 패리티 비트들 중 첫 번째 비트부터 부가 패리티 비트들의 수만큼의 비트들을 선택하여 부가 패리티 비트들을 생성할 수 있다.

- [0213] 한편, 리피티션이 수행된 경우, 부가 패리티 생성부(140)는 리피티션된 LDPC 패리티 비트들 중 첫 번째 비트부터 부가 패리티 비트들의 수만큼의 비트들을 선택하여 부가 패리티 비트들을 생성할 수 있다.

- [0214] 즉, 평처링된 비트들의 수가 0이고, 리피티션된 비트들의 수가 1 이상인 경우, 부가 패리티 생성부(140)는 리피티션된 비트들 및 인코딩에 의해 생성된 LDPC 패리티 비트들 중 리피티션된 비트들의 첫 번째 비트부터 부가 패리티 비트들의 수만큼의 비트들을 선택하여 부가 패리티 비트들을 생성할 수 있다.

- [0215] 이에 따라, 리피티션된 비트들이 먼저 선택되고, 부가 패리티 비트들의 수에서 리피티션된 비트들의 수를 뺀 수

가 리피티션 비트들의 수를 초과하는 경우 인코딩에 의해 생성된 LDPC 패리티 비트들에서 비트들이 추가로 선택될 수 있다. 이 경우, 인코딩에 의해 생성된 LDPC 패리티 비트들에서 추가로 선택되는 경우, 인코딩에 의해 생성된 LDPC 패리티 비트들 중 첫 번째 비트부터 선택될 수 있다.

[0216] 한편, 평처링된 비트들의 의미는 정보어 비트들이 전송되는 프레임에서 전송될 평처링된 LDPC 코드워드에 기반하여 비트들이 평처링되었다는 것을 말한다.

[0217] 한편, 상술한 예에서 첫 번째 리피티션 비트부터 ( $N_{AP} - N_{punc}$ ) 개의 비트들을 추가적으로 선택하는 것으로 설명하였으나 이는 일 예에 불과하다. 즉, 부가 패리티 생성부(140)는 첫 번째 정보어 비트 또는 첫 번째 아우터 인코딩된 비트부터 ( $N_{AP} - N_{punc}$ ) 개의 비트들을 추가적으로 선택할 수도 있다.

[0218] 또한, LDPC 패리티 비트들이 평처링되지 않는 경우, 부가 패리티 생성부(140)는 리피티션 비트들 중 첫 번째 비트부터  $N_{AP}$  개의 비트들을 선택하여 부가 패리티 비트들을 생성할 수도 있다.

[0219] 이하에서는 부가 패리티 비트들의 수를 산출하는 방법에 대해 설명하도록 한다.

[0220] 먼저, 부가 패리티 생성부(140)는 하기의 수학식 8에 기초하여 부가 패리티 비트들의 임시적인 수  $N_{AP\_temp}$ 를 산출한다.

## 수학식 8

$$N_{AP\_temp} = \min \left\{ \begin{array}{l} 0.5 \times K \times (N_{outer} + N_{ldpc\_parity} - N_{punc} + N_{repeat}), \\ (N_{ldpc\_parity} + N_{punc} + N_{repeat}) \end{array} \right\}, K=0,1,2$$

[0221]

$$\min(a,b) = \begin{cases} a, & \text{if } a \leq b \\ b, & \text{if } b < a \end{cases}$$

[0222] 여기에서,  $N_{AP\_temp}$ 은  $a$ 와  $b$  중 더 작은 값을 의미하는 것이다.

[0223] 그리고,  $N_{ldpc\_parity}$ 는 LDPC 패리티 비트들의 수,  $N_{punc}$ 는 평처링된 LDPC 패리티 비트들의 수이다. 그리고,  $N_{outer}$ 는 아우터 인코딩된 비트들의 수이다. 여기에서, 아우터 인코딩이 BCH 코드에 의해 수행되는 경우,  $N_{outer}$ 는 BCH 인코딩된 비트들의 수이다. 또한,  $N_{repeat}$ 는 리피티션 비트들의 수로, 리피티션이 수행되지 않는 경우  $N_{repeat}=0$ 이다.

[0224] 이에 따라,  $N_{ldpc\_parity} - N_{punc} + N_{repeat}$ 는 정보어 비트들을 전송하는 현재 프레임에서 전송되는 LDPC 패리티 비트들의 총 수(즉, 리피티션, 평처링 및 쇼트닝 이후의 LDPC 코드워드에 포함된 LDPC 패리티 비트들의 총 수)이고,  $N_{outer} + N_{ldpc\_parity} - N_{punc} + N_{repeat}$ 는 현재 프레임에서 전송되는 LDPC 코드워드 비트들의 총 수(즉, 리피티션, 평처링 및 쇼트닝 이후의 LDPC 코드워드 비트들의 총 수)이다.

[0225] 또한, K는 리피티션, 평처링 및 쇼트닝 이후의 LDPC 코드워드를 구성하는 비트들의 총 수의 절반에 대한 부가 패리티 비트들의 수의 비율(ratio)을 나타낸다. 여기에서, K=2인 경우, 부가 패리티 비트들의 수는 현재 프레임에서 전송되는 LDPC 코드워드 비트들의 총 수와 동일하게 된다.

[0226] 이와 같이, 부가 패리티 비트들의 수는 현재 프레임에서 전송되는 비트들의 총 수에 기초하여 결정될 수 있다.

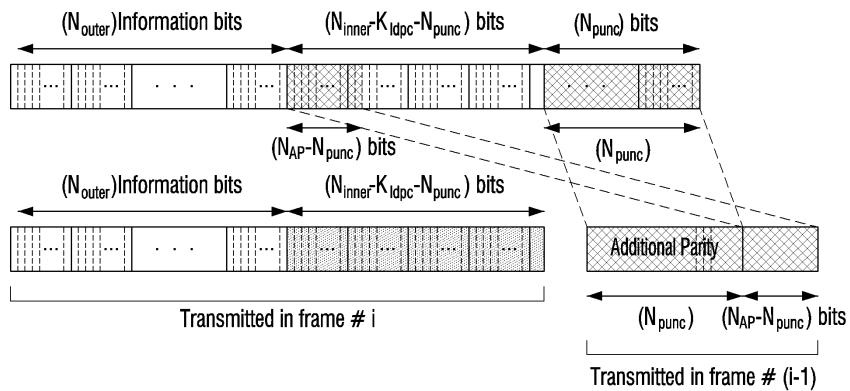

[0227] 한편, 수학식 12를 참조하면, 본 발명의 일 실시 예에서는 부가 패리티 비트들의 길이를 산출할 때, 성능과 복잡도를 모두 고려하여 평처링 비트들, 리피티션 비트들 및 LDPC 패리티 비트들을 모두 선택한 이후에는 추가로 더 선택하지 않도록 한다. 즉, 도 12와 같이, 부가 패리티 비트들의 길이가  $N_{AP\_max}$ (=  $N_{ldpc\_parity} + N_{punc} + N_{repeat}$ ) 보다 작거나 같아지도록 한다(즉, 부가 패리티 비트들의 길이가  $N_{AP\_max}$ (=  $N_{ldpc\_parity} + N_{punc} + N_{repeat}$ ) 보다 크지 않도록 한다).

[0228] 예를 들어, 평처링되는 LDPC 패리티 비트들의 수는 3200이고, K=2인 경우 부가 패리티 비트들의 수는

13000(=N<sub>outer</sub>+N<sub>ldpc\_parity</sub>-N<sub>punc</sub>=6480+9720-3200)인 경우를 가정한다.

[0229] 이 경우, 평처링되는 LDPC 패리티 비트들의 수는 3200이므로, 부가 패리티 비트들을 위해 평처링된 LDPC 패리티 비트들 전체를 선택하고 LDPC 패리티 비트들 전체를 선택하는 경우, 선택된 비트들의 수는 12920(=3200+9720)이 된다. 이에 따라, 별도의 제한이 없는 경우, 80 개의 비트들을 더 선택하여야 한다. 하지만, 수학식 12와 같이 부가 패리티 비트들의 최대 길이를 N<sub>ldpc\_parity</sub>+N<sub>punc</sub>+N<sub>repeat</sub>로 제한할 경우, 부가 패리티 비트들의 수는 12920로 제한되어 80 개의 비트들을 추가로 선택할 필요가 없게 된다.

[0230] 하지만, 이와 같이, 부가 패리티 비트들의 길이의 최대값을 제한하는 것은 일 예에 불과하며, 부가 패리티 비트들의 길이를 제한하지 않을 경우, 부가 패리티 비트들의 임시적인 N<sub>AP\_temp</sub>는 하기의 수학식 9에 기초하여 산출될 수 있다.

### 수학식 9

$$N_{AP\_temp} = 0.5 \times K \times (N_{outer} + N_{ldpc\_parity} - N_{punc} + N_{repeat}), K=0,1,2$$

[0231]

[0232] 이와 같이 부가 패리티 비트들의 길이를 제한하지 않을 경우, 부가 패리티 생성부(140)는 수학식 9에 기초하여 부가 패리티 비트들의 임시적인 N<sub>AP\_temp</sub>를 산출할 수 있다.

[0233] 한편, 부가 패리티 생성부(140)는 수학식 8 또는 수학식 9에 기초하여 산출된 부가 패리티 비트들의 임시적인 수 N<sub>AP\_temp</sub>에 기초하여 부가 패리티 비트들의 수 N<sub>AP</sub>를 산출할 수 있다.

[0234]

구체적으로, 부가 패리티 생성부(140)는 하기의 수학식 10에 기초하여 부가 패리티 비트들의 수 N<sub>AP</sub>를 산출할 수 있다.

[0235]

이와 같이, 부가 패리티 비트들의 수는 수학식 8 또는 수학식 9에 기초하여 산출된 부가 패리티 비트들의 임시적인 수 N<sub>AP\_temp</sub>에 기초하여 산출될 수 있으며, 구체적으로는, 하기의 수학식 10에 기초하여 산출될 수 있다.

### 수학식 10

$$N_{AP} = \left\lfloor \frac{N_{AP\_temp}}{n_{MOD}} \right\rfloor \times n_{MOD}$$

[0236]

[0237] 여기에서, n<sub>MOD</sub>는 변조 차수이다. 일 예로, QPSK(Quadrature Phase Shift Keying), 16-QAM(quadrature amplitude modulation), 64-QAM 및 256-QAM의 경우, n<sub>MOD</sub>는 2,4,6,8이 될 수 있다.

[0238]

이에 따라, 부가 패리티 비트들의 수는 변조 차수의 배수가 될 수 있다. 즉, 부가 패리티 비트들은 정보어 비트들과 별개로 변조되어 성상도 심볼들에 맵핑된다는 점에서, 수학식 10과 같이 부가 패리티 비트들의 수는 변조 차수의 배수가 되도록 결정될 수 있다.

[0239]

이 경우, 수학식 8은 하기의 수학식 11과 같이 나타내어지고, 수학식 9는 하기의 수학식 12와 같이 나타내어질 수도 있다.

## 수학식 11

$$N_{AP} = \left\lfloor \frac{\min \left\{ \frac{\alpha \times K \times (N_{outer} + N_{ldpc\_parity} - N_{punc} + N_{repeat}),}{(N_{ldpc\_parity} + N_{punc} + N_{repeat})} \right\}}{n_{MOD}} \right\rfloor \times n_{MOD}$$

[0240]

## 수학식 12

$$N_{AP} = \left\lfloor \frac{\alpha \times K \times (N_{outer} + N_{ldpc\_parity} - N_{punc} + N_{repeat})}{n_{MOD}} \right\rfloor \times n_{MOD}$$

[0241]

[0242] 이들 수학식에서  $\alpha=0.5$ 일 수 있다.

[0243] 이와 같이, 부가 패리티 비트들의 수는 현재 프레임에서 전송되는 아우터 인코딩된 비트들의 수 및 평처링 이후 남은 패리티 비트들의 수에 기초하여 결정될 수 있다.

[0244] 여기에서, 리피티션이 수행되는 경우, 부가 패리티 비트들의 수는 현재 프레임에서 전송되는 아우터 인코딩된 비트들의 수, 평처링 이후 남은 패리티 비트들의 수 및 현재 프레임에서 리피티션되는 비트들의 수에 기초하여 결정될 수 있다.

[0245] 이하에서는, 부가 패리티 비트들을 사용함에 따라 변경되는 부호율에 대해 설명하고자 한다.

[0246] 부가 패리티 비트들을 전송하지 않았을 경우의 부호율  $R$ 을  $R=(k/n)$ 이라고 하면, 부가 패리티 비트들을 전송할 경우의 부호율  $R_{ap}$ 은  $R_{ap}=(k/(n+N_{AP}))$ 이고,  $N_{AP}$ 는  $K$  값에 따라  $1/2 \times n$  또는  $n$  값을 갖게 된다. 따라서, 부가 패리티 비트들을 전송할 경우의 부호율  $R_{ap}$ 은  $R_{ap}=(k/(3/2 \times n))=2/3R$  또는  $R_{ap}=(k/(2 \times n))=1/2R$ 이므로, 부가 패리티 비트들을 전송하지 않았을 경우 대비 부호율은  $2/3$  또는  $1/2$ 로 낮아지게 되어, 부호어 이득을 얻을 수 있다. 또한, 부가 패리티 비트들을 제외한 부분들과 부가 패리티 비트들을 다른 프레임에서 전송함으로써 다이버시티 이득도 얻을 수 있게 된다. 이는 입력 길이 즉, 입력되는 정보어 비트들의 길이에 상관없이 상술한 바와 같이 부호율에 변경됨에 따라, 입력 길이에 따라 부호율을 변경하게 하는 특성을 유지할 수 있게 된다.

[0247] 이하에서는 LDPC 패리티 비트들에서 비트들을 선택하여 부가 패리티 비트들을 생성하는 방법을 도면을 참조하여 보다 구체적으로 설명하도록 한다.

[0248] 부가 패리티 생성부(140)는 LDPC 패리티 비트들에서 산출된 수만큼의 비트들을 선택하여 부가 패리티 비트들을 생성할 수 있다.

[0249] 구체적으로, 부가 패리티 생성부(140)는 부가 패리티 비트들의 수가 평처링된 LDPC 패리티 비트들의 수보다 작거나 같은 경우, 평처링된 LDPC 패리티 비트들 중 첫 번째 비트부터 산출된 수만큼의 비트들을 선택하여 부가 패리티 비트들을 생성할 수 있다.

[0250] 예를 들어, 리피티션에 의해 LDPC 패리티 비트들이 LDPC 정보어 비트들 이후에 부가되어, 리피티션 이후의 LDPC 코드워드가 LDPC 정보어 비트들, 리피티션된 LDPC 패리티 비트들 및 인코딩에 의해 생성된 LDPC 패리티 비트들 순으로 구성되는 경우를 가정한다.

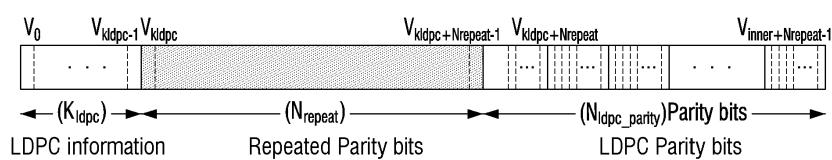

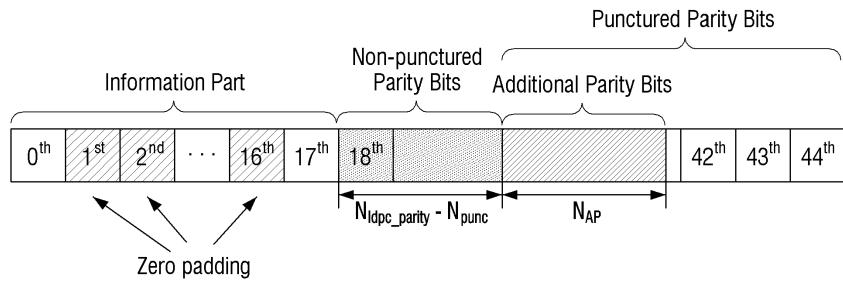

[0251] 이 경우, 리피티션 이후의 LDPC 코드워드  $V=(v_0, v_1, \dots, v_{N_{inner} + N_{repeat}-1})$ 는 도 13과 같이 나타낼 수 있다.

[0252] 구체적으로,  $N_{AP}$ 가  $N_{punc}$ 보다 작거나 같은 경우, 즉,  $N_{AP} \leq N_{punc}$ 인 경우, 부가 패리티 생성부(140)는 도 14 및 도 15와 같이, 평처링된 LDPC 패리티 비트들 중 첫 번째 비트부터  $N_{AP}$  개의 비트들을 선택하여 부가 패리티 비트들

을 생성할 수 있다.

- [0253] 이에 따라, 부가 패리티 비트들을 위해,  $(\mathbf{v}^{N_{repeat}+N_{inner}-N_{punc}}, \mathbf{v}^{N_{repeat}+N_{inner}-N_{punc}+1}, \dots, \mathbf{v}^{N_{repeat}+N_{inner}-N_{punc}+N_{AP}-1})$  가 선택될 수 있다.

- [0254] 한편, 부가 패리티 생성부(140)는 부가 패리티 비트들의 수가 평처링된 LDPC 패리티 비트들의 수보다 큰 경우, 평처링된 LDPC 패리티 비트들 전체를 선택하고, 리피티션 비트들 중 첫 번째 비트부터 부가 패리티 비트들의 수에서 평처링된 LDPC 패리티 비트들의 수를 뺀 수만큼의 비트들을 선택하여 부가 패리티 비트들을 생성할 수 있다.

- [0255] 예를 들어,  $N_{AP} > N_{punc}$ 인 경우, 즉,  $N_{AP} > N_{punc}$ 인 경우, 부가 패리티 생성부(140)는 도 16 및 도 17과 같이,

먼저, 평처링된 LDPC 패리티 비트들 전체를 선택할 수 있다. 이에 따라, 먼저  $(\mathbf{v}^{N_{repeat}+N_{inner}-N_{punc}}, \mathbf{v}^{N_{repeat}+N_{inner}-N_{punc}+1}, \dots, \mathbf{v}^{N_{repeat}+N_{inner}-1})$  이 선택될 수 있다.

- [0256] 그리고, 부가 패리티 생성부(140)는 리피티션된 LDPC 패리티 비트들과 인코딩에 의해 생성된 LDPC 패리티 비트들을 포함하는 LDPC 패리티 비트들 중 첫 번째 비트부터  $(N_{AP}-N_{punc})$  개의 비트들을 추가적으로 선택할 수 있다.

- [0257] 이 경우, 리피티션에 의해 LDPC 패리티 비트들이 LDPC 정보어 비트들 이후에 부가되어, 리피티션된 LDPC 패리티 비트들과 인코딩에 의해 생성된 LDPC 패리티 비트들이 순차적으로 배열되어 LDPC 패리티 비트들을 구성할 수 있다.

- [0258] 따라서, 부가 패리티 생성부(140)는 리피티션된 LDPC 패리티 비트들 중 첫 번째 비트부터 부가 패리티 비트들의 수에서 평처링된 LDPC 패리티 비트들의 수를 뺀 수만큼의 비트들 즉,  $(N_{AP}-N_{punc})$  개의 비트들을 추가적으로 선택하여 부가 패리티 비트들을 생성할 수 있다. 이 경우, 리피티션된 LDPC 패리티 비트들 중 첫 번째 비트부터 선택된다는 점에서,  $(N_{AP}-N_{punc})$  가 리피티션된 LDPC 패리티 비트들의 수  $N_{repeat}$ 보다 큰 경우, 인코딩에 의해 생성된 LDPC 패리티 비트들의 적어도 일부가 부가 패리티 비트들로 선택될 수도 있다.

- [0259] 이에 따라,  $(\mathbf{v}^{K_{ldpc}}, \mathbf{v}^{K_{ldpc}+1}, \dots, \mathbf{v}^{K_{ldpc}+N_{AP}-N_{punc}-1})$  이 추가적으로 선택될 수 있다.

- [0260] 결국, 부가 패리티 비트들을 위해  $(\mathbf{v}^{N_{repeat}+N_{inner}-N_{punc}}, \mathbf{v}^{N_{repeat}+N_{inner}-N_{punc}+1}, \dots, \mathbf{v}^{N_{repeat}+N_{inner}-1})$  및  $(\mathbf{v}^{K_{ldpc}}, \mathbf{v}^{K_{ldpc}+1}, \dots, \mathbf{v}^{K_{ldpc}+N_{AP}-N_{punc}-1})$  이 선택될 수 있다.

- [0261] 한편, 부가 패리티 생성부(140)는 상술한 방법 외에도 다양한 방법을 이용하여 부가 패리티 비트들을 생성할 수도 있다.

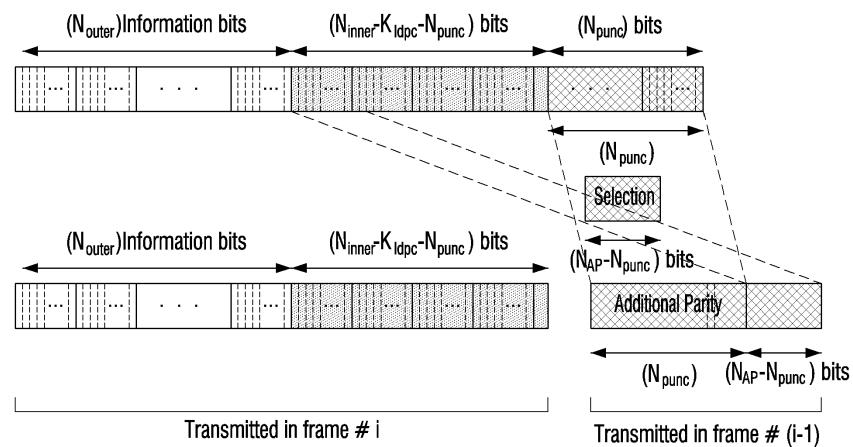

- [0262] 예를 들어, 부가 패리티 생성부(140)는 부가 패리티 비트들의 수가 평처링된 LDPC 패리티 비트들의 수보다 작거나 같은 경우, 평처링된 LDPC 패리티 비트들에서 부가 패리티 비트들의 수만큼의 비트들을 선택하여 부가 패리티 비트들을 생성할 수 있다.

- [0263] 즉,  $N_{AP} \leq N_{punc}$ 인 경우, 부가 패리티 생성부(140)는 도 18과 같이, 평처링된 LDPC 패리티 비트들 중 첫 번째 비트부터  $N_{AP}$  개의 비트들을 선택하여 부가 패리티 비트들을 생성할 수 있다. 이에 따라, 부가 패리티 비트들을 위해

$(\mathbf{v}^{N_{repeat}+N_{inner}-N_{punc}}, \mathbf{v}^{N_{repeat}+N_{inner}-N_{punc}+1}, \dots, \mathbf{v}^{N_{repeat}+N_{inner}-N_{punc}+N_{AP}-1})$  가 선택될 수 있다.

- [0264] 그리고, 부가 패리티 생성부(140)는 부가 패리티 비트들의 수가 평처링된 LDPC 패리티 비트들의 수보다 크지만 (인코딩에 의해 생성된 LDPC 패리티 비트들의 수 + 평처링된 LDPC 패리티 비트들의 수)보다 작거나 같은 경우, 평처링된 LDPC 패리티 비트들 전체를 선택하고, 인코딩에 의해 생성된 LDPC 패리티 비트들 중 첫 번째 비트부터

부가 패리티 비트들의 수에서 평처링된 LDPC 패리티 비트들의 수를 뺀 수만큼의 비트들을 선택하여 부가 패리티 비트들을 생성할 수 있다.

[0265] 즉,  $N_{\text{punc}} < N_{\text{AP}} \leq N_{\text{ldpc\_parity}} + N_{\text{punc}}$ 인 경우, 부가 패리티 생성부(140)는 도 19와 같이, 먼저 평처링된 LDPC 패리티 비

트들 전체를 선택할 수 있다. 이에 따라, 먼저  $(\mathbf{v}^{N_{\text{repeat}} + N_{\text{inner}} - N_{\text{punc}}},$

$\mathbf{v}^{N_{\text{repeat}} + N_{\text{inner}} - N_{\text{punc}} + 1}, \dots, \mathbf{v}^{N_{\text{repeat}} + N_{\text{inner}} - 1})$ 이 선택될 수 있다.

[0266] 그리고, 부가 패리티 생성부(140)는 인코딩에 의해 생성된  $N_{\text{ldpc\_parity}}$  개의 LDPC 패리티 비트들 중 첫 번째 비트

부터  $(N_{\text{AP}} - N_{\text{punc}})$  개의 비트들을 추가적으로 선택할 수 있다. 이에 따라,  $(\mathbf{v}^{N_{\text{repeat}} + K_{\text{ldpc}}},$

$\mathbf{v}^{N_{\text{repeat}} + K_{\text{ldpc}} + 1}, \dots, \mathbf{v}^{N_{\text{repeat}} + K_{\text{ldpc}} + N_{\text{AP}} - N_{\text{punc}} - 1})$ 이 추가적으로 선택될 수 있다.

[0267] 결국, 부가 패리티 비트들을 위해  $(\mathbf{v}^{N_{\text{repeat}} + N_{\text{inner}} - N_{\text{punc}}}, \mathbf{v}^{N_{\text{repeat}} + n_{\text{inner}} - N_{\text{punc}} + 1}, \dots, \mathbf{v}^{N_{\text{repeat}} + N_{\text{inner}} - 1})$  및

$(\mathbf{v}^{N_{\text{repeat}} + K_{\text{ldpc}}}, \mathbf{v}^{N_{\text{repeat}} + K_{\text{ldpc}} + 1}, \dots, \mathbf{v}^{N_{\text{repeat}} + K_{\text{ldpc}} + N_{\text{AP}} - N_{\text{punc}} - 1})$ 이 선택될 수 있다.

[0268] 또한, 부가 패리티 생성부(140)는 부가 패리티 비트들의 수가 (인코딩에 의해 생성된 LDPC 패리티 비트들의 수 + 평처링된 LDPC 패리티 비트들의 수)보다 큰 경우, 평처링된 LDPC 패리티 비트들 전체 및 인코딩에 의해 생성된 LDPC 패리티 비트들 전체를 선택하고, 리피티션된 LDPC 패리티 비트들 중 첫 번째 비트부터 부가 패리티 비트들의 수에서 인코딩에 의해 생성된 LDPC 패리티 비트들의 수와 평처링된 LDPC 패리티 비트들의 수를 뺀 수만큼의 비트들을 선택하여 부가 패리티 비트들을 생성할 수 있다.

[0269] 즉,  $N_{\text{ldpc\_parity}} + N_{\text{punc}} < N_{\text{AP}}$ 인 경우, 부가 패리티 생성부(140)는 도 20과 같이, 먼저 평처링된 LDPC 패리티 비트들 전체를 선택한다. 이에 따라, 먼저,  $(\mathbf{v}^{N_{\text{repeat}} + N_{\text{inner}} - N_{\text{punc}}}, \mathbf{v}^{N_{\text{repeat}} + N_{\text{inner}} - N_{\text{punc}} + 1}, \dots, \mathbf{v}^{N_{\text{repeat}} + N_{\text{inner}} - 1})$ 이 선택될 수 있다.

[0270] 그리고, 부가 패리티 생성부(140)는 인코딩에 의해 생성된  $N_{\text{ldpc\_parity}}$  개의 LDPC 패리티 비트들 전체를 추가적으로 선택한다. 이에 따라,  $(\mathbf{v}^{N_{\text{repeat}} + K_{\text{ldpc}}}, \mathbf{v}^{N_{\text{repeat}} + K_{\text{ldpc}} + 1}, \dots, \mathbf{v}^{N_{\text{repeat}} + N_{\text{inner}} - 1})$ 이 추가적으로 선택될 수 있다.

[0271] 그리고, 부가 패리티 생성부(140)는 리피티션된 LDPC 패리티 비트들 중 첫 번째 비트부터  $(N_{\text{AP}} - N_{\text{ldpc\_parity}} - N_{\text{punc}})$  개의 비트들을 추가적으로 선택할 수 있다. 이에 따라,  $(\mathbf{v}^{K_{\text{ldpc}}},$

$\mathbf{v}^{K_{\text{ldpc}} + 1}, \dots, \mathbf{v}^{K_{\text{ldpc}} + N_{\text{AP}} - N_{\text{punc}} - N_{\text{inner}} - 1})$ 가 추가적으로 선택될 수 있다.

[0272] 결국, 부가 패리티 비트들을 위해  $(\mathbf{v}^{N_{\text{repeat}} + N_{\text{inner}} - N_{\text{punc}}}, \mathbf{v}^{N_{\text{repeat}} + n_{\text{inner}} - N_{\text{punc}} + 1}, \dots, \mathbf{v}^{N_{\text{repeat}} + N_{\text{inner}} - 1})$ ,

$(\mathbf{v}^{N_{\text{repeat}} + K_{\text{ldpc}}}, \mathbf{v}^{N_{\text{repeat}} + K_{\text{ldpc}} + 1}, \dots, \mathbf{v}^{N_{\text{repeat}} + N_{\text{inner}} - 1})$  및  $(\mathbf{v}^{K_{\text{ldpc}}},$

$\mathbf{v}_{K_{ldpc}+1}, \dots, \mathbf{v}_{K_{ldpc}+N_{AP}-N_{punc}-N_{inner}-1}$ )가 선택될 수 있다.

[0273] 한편, 상술한 에서는 리피티션에 의해 리피티션 비트들이 LDPC 정보어 비트들 다음에 부가되는 경우를 가정하였다.

[0274] 이하에서는 다른 예로, 리피티션에 의해 리피티션 비트들이 LDPC 패리티 비트들 다음에 부가되는 경우, 부가 패리티 비트들을 생성하는 방법에 대해 설명하도록 한다. 이 경우, 인코딩에 의해 생성된 LDPC 패리티 비트들과 리피티션된 LDPC 패리티 비트들은 순차적으로 배열되어 LDPC 패리티 비트들을 구성할 수 있다.

[0275] 한편, 리피티션 이후의 LDPC 코드워드는  $\mathbf{v}=(v_0, v_1, \dots, \mathbf{v}_{N_{inner}+N_{repeat}-1})$ 와 같이 나타낼 수 있다.

[0276] 먼저, 부가 패리티 생성부(140)는 부가 패리티 비트들의 수가 (평처링된 LDPC 패리티 비트들의 수 + 리피티션된 LDPC 패리티 비트들의 수)보다 작거나 같은 경우, 평처링된 LDPC 패리티 비트들 중 첫 번째 비트부터 부가 패리티 비트들의 수만큼의 비트들을 선택하여 부가 패리티 비트들을 생성할 수 있다.

[0277] 이 경우, 인코딩에 의해 생성된 LDPC 패리티 비트들과 리피티션된 LDPC 패리티 비트들이 순차적으로 배열된다는 점에서, 평처링된 LDPC 패리티 비트들 중 첫 번째 비트부터 비트들을 선택하는 경우, 부가 패리티 비트들의 수에 따라 리피티션된 LDPC 패리티 비트들의 적어도 일부가 부가 패리티 비트들로 선택될 수도 있다.

[0278] 즉,  $N_{AP} \leq N_{punc} + N_{rep}$ 인 경우, 부가 패리티 생성부(140)는 도 21과 같이, 평처링된 LDPC 패리티 비트들 중 첫 번째 비트부터  $N_{AP}$  개의 비트들을 선택할 수 있다. 이에 따라, 부가 패리티 비트들 위해

$(\mathbf{v}_{N_{inner}-N_{punc}}, \mathbf{v}_{N_{inner}-N_{punc}+1}, \dots, \mathbf{v}_{N_{inner}-N_{punc}+N_{AP}-1})$ 가 선택될 수 있다.

[0279] 그리고, 부가 패리티 생성부(140)는 부가 패리티 비트들의 수가 (평처링된 LDPC 패리티 비트들의 수 + 리피티션된 LDPC 패리티 비트들의 수)보다 큰 경우, 평처링된 LDPC 패리티 비트들 전체 및 리피티션된 LDPC 패리티 비트들 전체를 선택하고, 인코딩에 의해 생성된 LDPC 패리티 비트들 중 첫 번째 비트부터 부가 패리티 비트들의 수에서 평처링된 LDPC 패리티 비트들의 수 및 리피티션된 LDPC 패리티 비트들의 수를 뺀 수만큼의 비트들을 선택하여 부가 패리티 비트들을 생성할 수 있다.

[0280] 즉,  $N_{AP} > N_{punc} + N_{rep}$ 인 경우, 부가 패리티 생성부(140)는 도 22와 같이, 먼저 평처링된 LDPC 패리티 비트들 전체 및 리피티션된 LDPC 패리티 비트들 전체를 선택할 수 있다. 이에 따라, 먼저

$(\mathbf{v}_{N_{inner}-N_{punc}}, \mathbf{v}_{N_{inner}-N_{punc}+1}, \dots, \mathbf{v}_{N_{inner}+N_{repeat}-1})$ 가 선택될 수 있다.

[0281] 그리고, 부가 패리티 생성부(140)는 인코딩에 의해 생성된  $N_{ldpc\_parity}$  개의 LDPC 패리티 비트들 중 첫 번째 비트부터  $(N_{AP}-N_{punc})$  개의 비트들을 추가적으로 선택할 수 있다. 이에 따라,

$(\mathbf{v}_{K_{ldpc}}, \mathbf{v}_{K_{ldpc}+1}, \dots, \mathbf{v}_{K_{ldpc}+N_{AP}-N_{punc}-1})$ 가 추가적으로 선택될 수 있다.

[0282] 결국, 부가 패리티 비트들을 위해  $(\mathbf{v}_{N_{inner}-N_{punc}}, \mathbf{v}_{N_{inner}-N_{punc}+1}, \dots, \mathbf{v}_{N_{inner}+N_{repeat}-1})$  및  $(\mathbf{v}_{K_{ldpc}}, \mathbf{v}_{K_{ldpc}+1}, \dots, \mathbf{v}_{K_{ldpc}+N_{AP}-N_{punc}-1})$ 가 선택될 수 있다.

[0283] 다른 예로, 부가 패리티 생성부(140)는 부가 패리티 비트들의 수가 평처링된 LDPC 패리티 비트들의 수보다 작거나 같은 경우, 평처링된 LDPC 패리티 비트들에서 부가 패리티 비트들의 수만큼의 비트들을 선택하여 부가 패리티 비트들을 생성할 수 있다.

[0284] 즉,  $N_{AP} \leq N_{punc}$ 인 경우, 부가 패리티 생성부(140)는 도 23과 같이, 평처링된 LDPC 패리티 비트들 중 첫 번째 비트

부터  $N_{AP}$  개의 비트들을 선택하여 부가 패리티 비트들을 생성할 수 있다. 이에 따라, 부가 패리티 비트들을 위해

$$(\mathbf{v}_{N_{inner} \cdot N_{punc}}, \mathbf{v}_{N_{inner} \cdot N_{punc} + 1}, \dots, \mathbf{v}_{N_{inner} \cdot N_{punc} + N_{AP} - 1}) \text{가 선택될 수 있다.}$$

[0285] 그리고, 부가 패리티 생성부(140)는 부가 패리티 비트들의 수가 평처링된 LDPC 패리티 비트들의 수보다 큰 경우, 평처링된 LDPC 패리티 비트들 전체를 선택하고, 인코딩에 의해 생성된 LDPC 패리티 비트들 중 첫 번째 비트부터 부가 패리티 비트들의 수에서 평처링된 LDPC 패리티 비트들의 수를 뺀 수만큼의 비트들을 선택하여 부가 패리티 비트들을 생성할 수 있다.

[0286] 즉,  $N_{AP} > N_{punc}$ 인 경우, 부가 패리티 생성부(130)는 도 24와 같이, 먼저 평처링된 LDPC 패리티 비트들 전체를 선

택할 수 있다. 이에 따라, 먼저  $(\mathbf{v}_{N_{inner} \cdot N_{punc}}, \mathbf{v}_{N_{inner} \cdot N_{punc} + 1}, \dots, \mathbf{v}_{N_{inner} \cdot N_{punc} + N_{AP} - 1})$ 가 선택될 수 있다.

[0287] 그리고, 부가 패리티 생성부(140)는 인코딩에 의해 생성된  $N_{ldpc\_parity}$  개의 LDPC 패리티 비트들 중 첫 번째 비트

부터  $(N_{AP} - N_{punc})$  개의 비트들을 추가적으로 선택할 수 있다. 이에 따라,  $(\mathbf{v}_{K_{ldpc}},$

$$(\mathbf{v}_{K_{ldpc} + 1}, \dots, \mathbf{v}_{K_{ldpc} + N_{AP} - N_{punc} - 1})$$

가 추가적으로 선택될 수 있다.

[0288] 결국, 부가 패리티 비트들을 위해  $(\mathbf{v}_{N_{inner} \cdot N_{punc}}, \mathbf{v}_{N_{inner} \cdot N_{punc} + 1}, \dots, \mathbf{v}_{N_{inner} \cdot N_{punc} + N_{AP} - 1})$  및

$$(\mathbf{v}_{K_{ldpc}}, \mathbf{v}_{K_{ldpc} + 1}, \dots, \mathbf{v}_{K_{ldpc} + N_{AP} - N_{punc} - 1})$$

가 선택될 수 있다.

[0289] 한편, 이하에서는 부가 패리티 비트들을 생성하는 다른 방법에 대해 설명하도록 한다.

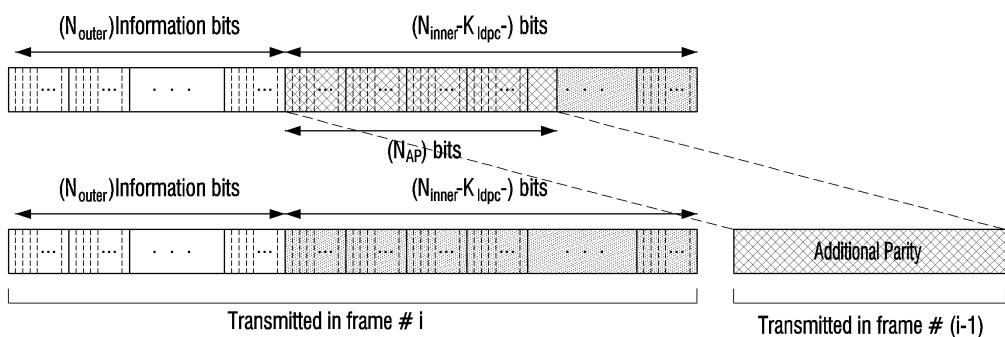

[0290] 일 예로,  $N_{punc} > 0$ 이고,  $N_{repeat} = 0$ 인 경우를 가정한다.

[0291] 구체적으로, 부가 패리티 생성부(140)는 평처링된 LDPC 패리티 비트들의 수가 부가 패리티 비트들의 수보다 크거나 같은 경우, 평처링된 LDPC 패리티 비트들에서 적어도 일부를 선택하여 부가 패리티 비트들을 생성하고, 다른 경우, 평처링된 LDPC 패리티 비트들 전체를 선택하고, 나머지 비트들을 LDPC 코드워드에서 순차적으로 선택하여 부가 패리티 비트들을 생성할 수 있다.

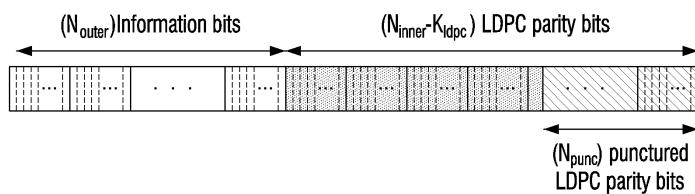

[0292] 예를 들어,  $N_{punc} > 0$ 이고,  $N_{repeat} = 0$ 인 경우, LDPC 코드워드는 도 25와 같이 나타낼 수 있다. 한편, 도 25에서 LDPC 정보어 비트들의 수는  $N_{outer}$ 이다. 즉, 제로 비트들이 패딩되지 않고 아우터 인코딩된 비트들만으로 LDPC 정보어 비트들이 구성되는 경우이다.

[0293] 먼저,  $N_{AP} \leq N_{punc}$ 인 경우, 부가 패리티 생성부(140)는 도 26과 같이 평처링된 LDPC 패리티 비트들에서  $N_{AP}$  개의 비트들을 선택하여 부가 패리티 비트들을 생성할 수 있다.

[0294] 그리고,  $N_{AP} > N_{punc}$ 인 경우, 부가 패리티 생성부(140)는 도 27과 같이 평처링된 LDPC 패리티 비트들 전체를 선택하고, LDPC 패리티 비트들 중 첫 번째 비트부터  $(N_{AP} - N_{punc})$  개의 비트들을 추가적으로 선택하여 부가 패리티 비트들을 생성할 수 있다.

[0295] 한편, 상술한 예에서는 첫 번째 비트부터  $(N_{AP} - N_{punc})$  개의 비트들을 추가적으로 선택하는 것으로 설명하였으나, 이는 일 예에 불과하다. 즉, 부가 패리티 생성부(140)는 정보어 비트들 중 첫 번째 비트부터  $(N_{AP} - N_{punc})$  개의 비트들을 추가적으로 선택할 수도 있다.

[0296] 다른 예로,  $N_{AP} > N_{punc}$ 인 경우, 부가 패리티 생성부(140)는 도 28과 같이 평처링된 LDPC 패리티 비트들 전체를 선

택하고, 기설정된 패턴에 기초하여 LDPC 패리티 비트들 중에서 ( $N_{AP} - N_{punc}$ ) 개의 비트들을 추가적으로 선택하여 부가 패리티 비트들을 생성할 수 있다.

[0297] 또 다른 예로,  $N_{punc} = 0$ 인 경우, 부가 패리티 생성부(140)는 도 29와 같이 첫 번째 LDPC 패리티 비트들부터  $N_{AP}$  개의 비트들을 선택하여 부가 패리티 비트들을 생성할 수 있다.

[0298] 한편, 상술한 예에서는, 리피티션 이후의 LDPC 코드워드 내에서 비트들을 선택하여 부가 패리티 비트들을 생성하는 것으로 설명하였다.

[0299] 하지만, 본 발명의 일 실시 예에 따르면, 리피티션이 수행되기 전의 LDPC 코드워드 내에서 비트들을 선택하여 부가 패리티 비트들을 생성할 수도 있다. 이를 위해, LDPC 인코더(110)는 LDPC 코드워드를 부가 패리티 생성부(140)로 출력할 수 있다.

[0300] 예를 들어,  $N_{repeat} > 0$ 인 경우를 가정한다. 이하에서는, LDPC 정보어 비트들의 수가  $K_{ldpc}$ 인 것으로 가정하도록 한다.

[0301] 부가 패리티 생성부(140)는 평처링된 LDPC 패리티 비트들을 우선적으로 선택하여 부가 패리티 비트들을 생성하고, 평처링된 LDPC 패리티 비트들의 수가 부가 패리티 비트들의 수보다 작은 경우에 한하여 LDPC 패리티 비트들 중 일부를 선택하여 부가 패리티 비트들을 생성할 수 있다.

[0302] 이 경우, LDPC 패리티 비트들은 인코딩에 의해 생성된 LDPC 패리티 비트만으로 구성될 수 있다.

[0303] 구체적으로, 부가 패리티 생성부(140)는 첫 번째 LDPC 패리티 비트부터 선택하여 부가 패리티 비트들을 생성할 수 있다.

[0304] 예를 들어,  $N_{repeat} < N_{ldpc\_parity} - N_{punc}$ 인 경우를 가정한다.

[0305] 이 때,  $N_{AP} \leq N_{punc}$ 인 경우, 부가 패리티 생성부(140)는 평처링된 LDPC 패리티 비트들에서 선택하여 부가 패리티 비트들을 생성할 수 있다.

[0306] 예를 들어, 부가 패리티 생성부(140)는 도 30과 같이 평처링된 LDPC 패리티 비트들 중 첫 번째 비트부터  $N_{AP}$  개의 비트들을 선택하여 부가 패리티 비트들을 생성할 수 있다. 이 경우, 리피티션부(120)는 도 30과 같이 LDPC 패리티 비트들 중 첫 번째 비트부터  $N_{repeat}$  개의 비트들을 선택하여, LDPC 패리티 비트들 이후에 부가할 수 있고, 평처링 이후, 리피티션 비트들은 평처링되지 않은 LDPC 패리티 비트들 이후에 위치하게 된다.

[0307] 한편,  $N_{AP} > N_{punc}$ 인 경우, 부가 패리티 생성부(140)는 도 31과 같이 평처링된 LDPC 패리티 비트들 전체를 선택하고, 첫 번째 LDPC 패리티 비트부터 ( $N_{AP} - N_{punc}$ ) 개의 비트들을 선택하여 부가 패리티 비트들을 생성할 수 있다.

[0308] 이 경우, 리피티션부(120)는 도 30과 같이 LDPC 패리티 비트들 중 첫 번째 비트부터  $N_{repeat}$  개의 비트들을 선택하여, LDPC 패리티 비트들 이후에 부가할 수 있고, 평처링 이후, 리피티션 비트들은 평처링되지 않은 LDPC 패리티 비트들 이후에 위치하게 된다.

[0309] 다른 예로,  $N_{ldpc\_parity} \geq N_{repeat} \geq N_{ldpc\_parity} - N_{punc}$ 인 경우를 가정한다.

[0310] 이 때,  $N_{AP} \leq N_{punc}$ 인 경우, 부가 패리티 생성부(140)는 도 32와 같이 평처링된 LDPC 패리티 비트들 중 첫 번째 비트부터  $N_{AP}$  개의 비트들을 선택하여 부가 패리티 비트들을 생성할 수 있다. 이 경우, 리피티션부(120)는 도 32와 같이 LDPC 패리티 비트들 중 첫 번째 비트부터  $N_{repeat}$  개의 비트들을 선택하여, LDPC 패리티 비트들 이후에 부가할 수 있고, 평처링 이후, 리피티션 비트들은 평처링되지 않은 LDPC 패리티 비트들 이후에 위치하게 된다.

[0311] 한편,  $N_{AP} > N_{punc}$ 인 경우, 부가 패리티 생성부(140)는 도 33과 같이 평처링된 LDPC 패리티 비트들 전체를 선택하고, 첫 번째 LDPC 패리티 비트부터 ( $N_{AP} - N_{punc}$ ) 개의 비트들을 선택하여 부가 패리티 비트들을 생성할 수 있다.

[0312] 이 경우, 리피티션부(120)는 도 33과 같이 LDPC 패리티 비트들 중 첫 번째 비트부터  $N_{repeat}$  개의 비트들을 선택하여, LDPC 패리티 비트들 이후에 부가할 수 있고, 평처링 이후, 리피티션 비트들은 평처링되지 않은 LDPC 패리티 비트들 이후에 위치하게 된다.

티 비트들 이후에 위치하게 된다. 이에 따라, LDPC 패리티 비트들에서 부가 패리티 비트들로 선택된 비트들 중 적어도 일부가 리피티션 비트들로 선택될 수 있다.

[0313] 다른 예로,  $N_{repeat} > N_{ldpc\_parity}$ 인 경우를 가정한다.

[0314] 이때,  $N_{AP} \leq N_{punc}$ 인 경우, 부가 패리티 생성부(140)는 도 34와 같이 평처링된 LDPC 패리티 비트들 중 첫 번째 비트부터  $N_{AP}$  개의 비트들을 선택하여 부가 패리티 비트들을 생성할 수 있다.

[0315] 한편,  $N_{AP} > N_{punc}$ 인 경우, 부가 패리티 생성부(140)는 도 33과 같이 평처링된 LDPC 패리티 비트들 전체를 선택하고, 첫 번째 LDPC 패리티 비트부터 ( $N_{AP} - N_{punc}$ ) 개의 비트들을 선택하여 부가 패리티 비트들을 생성할 수 있다.

[0316] 이들 경우, 리피티션부(120)는 도 33 및 도 34와 같이 LDPC 패리티 비트들 중 첫 번째 비트부터  $N_{repeat}$  개의 비트들을 선택하여, LDPC 패리티 비트들 이후에 부가할 수 있고, 평처링 이후, 리피티션 비트들은 평처링되지 않은 LDPC 패리티 비트들 이후에 위치하게 된다.

[0317] 또한,  $N_{repeat}$ 가  $N_{ldpc\_parity}$  보다 큰 경우, 도 34 및 도 35와 같이, LDPC 패리티 비트들 전체는 리피티션되고, LDPC 패리티 비트들 중 적어도 일부는 추가로 리피티션될 수 있다.

[0318] 한편, 부가 패리티 생성부(140)는 LDPC 패리티 비트들 중에서 리피티션되는 LDPC 패리티 비트들을 제외한 나머지 LDPC 패리티 비트들에서 특정한 수의 비트들을 선택할 수도 있다.

[0319] 예를 들어,  $N_{AP} \leq N_{punc}$ 인 경우, 부가 패리티 생성부(140)는 도 36과 같이 평처링된 LDPC 패리티 비트들 중 첫 번째 비트부터  $N_{AP}$  개의 비트들을 선택하여 부가 패리티 비트들을 생성할 수 있다.

[0320] 그리고,  $N_{AP} > N_{punc}$ 인 경우, 부가 패리티 생성부(140)는 도 37과 같이 평처링된 LDPC 패리티 비트들 전체를 선택하고, LDPC 패리티 비트들 중에서 리피티션되는 LDPC 패리티 비트들을 제외한 나머지 LDPC 패리티 비트들 중 첫 번째 비트부터 ( $N_{AP} - N_{punc}$ ) 개의 비트들을 선택하여 부가 패리티 비트들을 생성할 수 있다.

[0321] 이 경우, 부가 패리티 생성부(130)는 도 38과 같이 LDPC 패리티 비트들 중에서 리피티션되는 LDPC 패리티 비트들을 제외한 나머지 LDPC 패리티 비트들이 모두 선택되면, 나머지 비트들은 리피티션되는 LDPC 패리티 비트들에서 선택하여 부가 패리티 비트들을 생성할 수 있다.

[0322] 한편, 상술한 예에서는 LDPC 패리티 비트들을 선택하여 부가 패리티 비트들을 생성하는 것으로 설명하였으나 이는 일 예에 불과하고, 부가 패리티 생성부(140)는 LDPC 패리티 비트들의 수가 부가 패리티 비트들의 수보다 작은 경우 아우터 인코딩된 비트들 및 LDPC 패리티 비트들에서 비트들을 선택하여 부가 패리티 비트들을 생성할 수도 있다.

[0323] 이 경우, 부가 패리티 생성부(140)는 아우터 인코딩된 비트들 및 LDPC 패리티 비트들에서 비트들을 선택할 때, 이미 선택되었던 비트들을 제외하고 비트들을 선택할 수 있다. 이때, 중복하여 선택할 경우 선택된 횟수가 가장 작은 비트들부터 선택될 수 있다.

[0324] 또한, 상술한 예에서는 리피티션이 수행된 이후, 리피티션 비트들을 고려하여 부가 패리티 비트들을 생성하는 것으로 설명하였으나 이는 일 예에 불과하다. 즉, 경우에 따라, 리피티션은 생략될 수도 있다.

[0325] 이 경우, 부가 패리티 생성부(140)는 부가 패리티 비트들의 수가 평처링된 LDPC 패리티 비트들보다 작거나 같은 경우, 평처링된 LDPC 패리티 비트들 중 첫 번째 비트부터 부가 패리티 비트들의 수만큼의 비트들을 선택하여 부가 패리티 비트들을 생성할 수 있다.

[0326] 또한, 부가 패리티 생성부(140)는 부가 패리티 비트들의 수가 평처링된 LDPC 패리티 비트들보다 큰 경우, 평처링된 LDPC 패리티 비트들 전체를 선택하고, LDPC 패리티 비트들 즉, 인코딩에 의해 생성된 LDPC 패리티 비트들 중 첫 번째 비트부터 부가 패리티 비트들의 수에서 평처링된 LDPC 패리티 비트들의 수를 뺀 값만큼의 비트들을 선택하여 부가 패리티 비트들을 생성할 수도 있다.

[0327] 또한, 상술한 예에서는 비트 단위로 LDPC 패리티 비트들을 선택하여 부가 패리티 비트들을 생성하는 것으로 설명하였으나 이는 일 예에 불과하고, 부가 패리티 생성부(140)는 비트 그룹 단위로 LDPC 패리티 비트들을 선택하여 부가 패리티 비트들을 생성할 수도 있다.

[0328] 예를 들어, LDPC 코드워드  $(v_0, v_1, \dots, v_{N_{inner}-1})$  가  $N_{group}$  개의 비트 그룹으로 구분되어,  $V=(Y_0, Y_1, \dots, Y_{N_{group}-1})$  와 같이 나타내어지는 경우를 가정한다.

[0329] 이 경우, 부가 패리티 생성부(140)는 하기와 같은 수학식 13에 기초하여 부가 패리티 비트들의 임시적인 수  $N_{AP\_temp}$ 를 산출할 수 있다.

### 수학식 13

$$N_{AP\_temp} = \alpha \times K \times (N_{ldpc\_parity} - N_{punc}),$$

[0330]

[0331] 여기에서,  $N_{ldpc\_parity}$ 는 LDPC 패리티 비트들의 수,  $N_{punc}$ 는 평처링된 LDPC 패리티 비트들의 수이다. 그리고,  $\alpha = 0.5$ ,  $K=0,1,2$ 가 될 수 있다.

[0332] 그리고, 부가 패리티 생성부(140)는 하기의 수학식 14 또는 수학식 15에 기초하여 부가 패리티 비트들의 수  $N_{AP}$ 를 산출할 수 있다.

### 수학식 14

$$N_{AP} = \left\lceil \frac{N_{AP\_temp}}{n_{MOD}} \right\rceil \times n_{MOD}$$

[0333]

### 수학식 15

$$N_{AP} = \left\lfloor \frac{N_{AP\_temp}}{n_{MOD}} \right\rfloor \times n_{MOD}$$

[0335] 이들 수학식에서,  $\lceil x \rceil$  은  $x$ 보다 크거나 같은 최소 정수를 의미하고,  $\lfloor x \rfloor$  는  $x$ 보다 크지 않는 최대 정수를 의미한다. 그리고,  $n_{MOD}$ 는 변조 차수이다. 일 예로, QPSK, 16-QAM, 64-QAM 및 256-QAM의 경우,  $n_{MOD}$ 는 2, 4, 6, 8이 될 수 있다.

[0336] 이후, 부가 패리티 생성부(140)는 LDPC 패리티 비트들에서 산출된 수만큼의 비트들을 선택하여 부가 패리티 비트들을 생성할 수 있다.

[0337] 구체적으로, 부가 패리티 생성부(140)는 부가 패리티 비트들의 수가 평처링된 LDPC 패리티 비트들의 수보다 작거나 같은 경우, 평처링된 LDPC 패리티 비트들 중 첫 번째 비트부터 산출된 수만큼의 비트들을 선택하여 부가 패리티 비트들을 생성할 수 있다.

[0338] 즉,  $N_{AP} \leq N_{punc}$ 인 경우, 부가 패리티 생성부(140)는 도 39와 같이, 평처링된 LDPC 패리티 비트들 중 첫 번째 비트부터  $N_{AP}$  개의 비트들을 선택하여 부가 패리티 비트들을 생성할 수 있다. 이에 따라, 부가 패리티 비트들을 위해

$$(\mathbf{v}_{N_{inner} \cdot N_{punc}}, \mathbf{v}_{N_{inner} \cdot N_{punc} + 1}, \dots, \mathbf{v}_{N_{inner} \cdot N_{punc} + N_{AP} - 1})$$

가 선택될 수 있다.

[0339] 한편, 부가 패리티 생성부(140)는 부가 패리티 비트들의 수가 평처링된 LDPC 패리티 비트들의 수보다 큰 경우,

$$\text{즉, } N_{AP} > N_{punc} \text{인 경우, 먼저, 평처링된 LDPC 패리티 비트들 전체를 선택할 수 있다. 이에 따라, } (\mathbf{v}_{N_{inner} \cdot N_{punc}},$$

$$\mathbf{v}_{N_{inner} \cdot N_{punc} + 1}, \dots, \mathbf{v}_{N_{inner} \cdot N_{punc} + N_{AP} - 1})$$

가 부가 패리티 비트들로 선택될 수 있다

[0340] 그리고, 부가 패리티 생성부(140)는 부가 패리티 비트들의 수에서 평처링된 LDPC 패리티 비트들의 수를 뺀 수만큼의 비트들을 비트 그룹 단위로 선택할 수 있다.

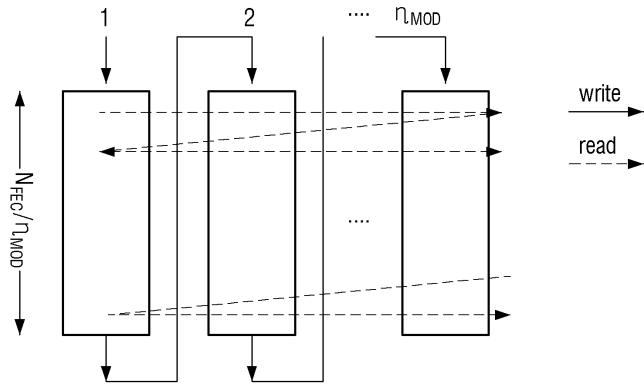

[0341] 이를 위해, 부가 패리티 생성부(140)는 하기의 수학식 16에 기초하여 비트 그룹 내의 모든 비트들이 부가 패리티 비트들을 위해 선택되는 비트 그룹의 개수를 산출할 수 있다.

### 수학식 16

$$N_{AP\_groups} = \left\lfloor \frac{N_{AP} - N_{punc}}{360} \right\rfloor$$

[0342]

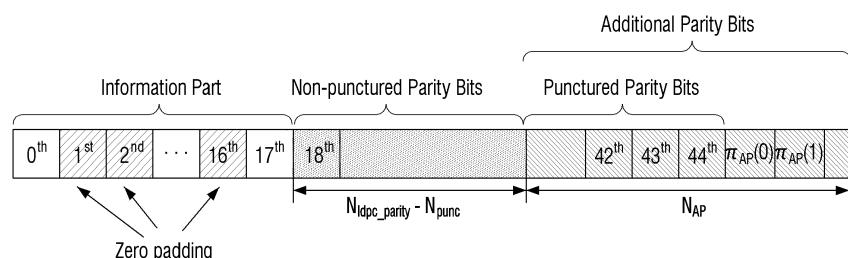

[0343] 그리고, 부가 패리티 생성부(140)는 부가 패리티 패턴에 기초하여, 복수의 비트 그룹 중 부가 패리티 비트들의 생성에 이용되는 비트 그룹을 판단하고, 판단된 비트 그룹 중 일부 비트 그룹 내의 모든 비트들 및 나머지 비트 그룹 내의 일부 비트들을 선택하여, 부가 패리티 비트들을 생성할 수 있다.

[0344] 이 경우, 부가 패리티 패턴은 LDPC 패리티 비트들을 구성하는 복수의 비트 그룹 중 부가 패리티 비트들로 선택되는 비트 그룹의 순서를 정의하는 패턴으로, 일 예로,  $\pi_{AP}(j) (0 \leq j < N_{group})$ 에 대해,  $\pi_{AP}(0) = x_0$ ,  $\pi_{AP}(1) = x_1, \dots, \pi_{AP}(N_{group} - 1) = x_{N_{group} - 1}$ 과 같이 정의되어 있을 수 있다.

[0345] 여기에서,  $x_0, x_1, \dots, x_{N_{group} - 1}$ 은 LDPC 패리티 비트들을 구성하는 복수의 비트 그룹의 인덱스이고,  $N_{group}$ 은 LDPC 패리티 비트들을 구성하는 복수의 비트 그룹의 수이며, 하나의 비트 그룹은 360 개의 비트들로 구성되어 있을 수 있다.

[0346] 구체적으로, 부가 패리티 생성부(140)는 부가 패리티 패턴에 기초하여 복수의 비트 그룹 중  $\pi_{AP}(0)$  번째 비트 그룹,  $\pi_{AP}(1)$  번째 비트 그룹,  $\dots$ ,  $\pi_{AP}(N_{AP\_groups} - 1)$  번째 비트 그룹의 모든 비트들을 부가 패리티 비트들을 위해

선택할 수 있다. 즉,  $x_0$  번째 비트 그룹,  $x_1$  번째 비트 그룹,  $\dots$ ,  $x_{N_{group} - 1}$  번째 비트 그룹의 모든 비트들을 부가 패리티 비트들로 선택할 수 있다.

[0347] 한편, 부가 패리티 생성부(140)는  $N_{AP} - N_{punc}$  개의 비트들을 선택하여야 하지만,  $N_{AP\_groups}$  개의 비트 그룹에서 선택된 비트들은  $(360 \times N_{AP\_groups})$ 이므로, 부가 패리티 생성부(140)는  $(N_{AP} - N_{punc} - 360 \times N_{AP\_groups})$  개의 비트들을 추가적으로 선택할 수 있다.

[0348] 이 경우, 부가 패리티 생성부(140)는 부가 패리티 패턴에 기초하여 추가적으로 선택되는 비트들을 포함하는 비트 그룹을 판단하고, 판단된 비트 그룹의 첫 번째 비트부터  $(N_{AP} - N_{punc} - 360 \times N_{AP\_groups})$  개의 비트들을 추가적으로

선택할 수 있다.

[0349] 구체적으로, 부가 패리티 생성부(140)는 부가 패리티 패턴에 기초하여  $\pi_{AP}(N_{AP\_groups})$  번째 비트 그룹을 판단하고,  $\pi_{AP}(N_{AP\_groups})$  번째 비트 그룹의 첫 번째 비트부터 ( $N_{AP}-N_{punc}-360 \times N_{AP\_groups}$ ) 개의 비트들을 부가 패리

티 비트들을 위해 선택할 수 있다. 즉,  $x^{N_{group}}$  번째 비트 그룹의 트부터 ( $N_{AP}-N_{punc}-360 \times N_{AP\_groups}$ ) 개의 비트들을 부가 패리티 비트들로 추가적으로 선택할 수 있다.

[0350] 결국,  $N_{AP} > N_{punc}$ 인 경우, 부가 패리티 생성부(140)는 도 40과 같이, 평처링된 LDPC 패리티 비트들 전체를 선택하고,  $\pi_{AP}(0)$  번째 비트 그룹,  $\pi_{AP}(1)$  번째 비트 그룹, ...,  $\pi_{AP}(N_{AP\_groups}-1)$  번째 비트 그룹의 모든 비트들 및  $\pi_{AP}(N_{AP\_groups})$  번째 비트 그룹의 첫 번째 비트부터 ( $N_{AP}-N_{punc}-360 \times N_{AP\_groups}$ ) 개의 비트들을 선택하여 부가 패리티 비트들을 생성할 수 있다.

[0351] 한편, 리피티션이 소정의 패턴을 기반으로 선택될 경우, 부가 패리티 비트들을 선택할 때 소정의 리피티션 패턴을 우선으로 고려하여 사용할 수 있다. 즉, 리피티션 패턴에 기반하여 리피티션된 비트들 이후의 비트들부터 선택하여 부가 패리티로 선택하도록 한다. 리피티션 패턴으로 정의된 리피티션 비트들의 최대 개수에서 리피티션 비트의 개수를 제외한 개수가 부가 패리티 비트의 개수보다 클 경우, 리피티션 패턴과 부가 패리티 패턴 모두를 기반으로 하여, 부가 패리티 비트를 생성할 수 있다. 리피티션 패턴이라고 함은 주어진 LDPC 코드워드 중에서 추가로 전송할 때 성능이 우수한 그룹의 순서를 의미하므로 리피티션 패턴을 기반으로 부가 패리티를 생성하고, 부가 패리티 비트가 더 필요할 경우 부가 패리티 비트의 패턴을 기반하도록 한다.

[0352] 한편, 송신 장치(100)는 평처링부(130)에서 출력되는 비트들 및 부가 패리티 생성부(140)에서 출력되는 비트들을 수신 장치(200)로 전송할 수 있다.

[0353] 이 경우, 송신 장치(100)는 평처링부(130)에서 출력되는 리피티션 및 평처링 이후의 LDPC 코드워드에서 패딩된 제로 비트들을 제외한 LDPC 코드워드 비트들 즉, 리피티션, 평처링 및 쇼트닝 이후의 LDPC 코드워드를 수신 장치(200)로 전송할 수 있다.

[0354] 구체적으로, 송신 장치(100)는 리피티션, 평처링 및 쇼트닝 이후의 LDPC 코드워드 비트들 및 부가 패리티 비트들을 각각 변조하여 성상도 심볼들에 맵핑하고, 이들을 프레임에 맵핑하여 수신 장치(200)로 전송할 수 있다.

[0355] 다만, 리피티션이 생략되는 경우, 송신 장치(100)는 평처링 이후의 LDPC 코드워드에서 패딩된 제로 비트들을 제외한 LDPC 코드워드 비트들 즉, 평처링 및 쇼트닝 이후의 LDPC 코드워드를 수신 장치(200)로 전송할 수 있다.

[0356] 이 경우, 송신 장치(100)는 QPSK, 16-QAM, 64-QAM 또는 256-QAM 등을 이용하여 변조할 수 있으며, 리피티션, 평처링 및 쇼트닝 이후의 LDPC 코드워드 비트들(또는, 평처링 및 쇼트닝 이후의 LDPC 코드워드) 및 부가 패리티 비트들을 동일한 변조 방식으로 이용하여 변조할 수 있다.

[0357] 한편, 송신 장치(100)는 현재 프레임에서 전송되는 정보어 비트들에 기초하여 생성된 부가 패리티 비트들을 해당 프레임 이전의 프레임에 맵핑할 수 있다.

[0358] 즉, 송신 장치(100)는  $i-1$  번째 프레임에 대응되는 정보어 비트들을 포함하는 평처링 및 쇼트닝 이후의 LDPC 코드워드는  $i-1$  번째 프레임에 맵핑하고,  $i$  번째 프레임에 대응되는 정보어 비트들에 기초하여 생성된 부가 패리티 비트들을  $i-1$  번째 프레임에 추가로 맵핑하여 수신 장치(200)로 전송할 수 있다.

[0359] 이에 따라,  $i-1$  번째 프레임에는  $i-1$  번째 프레임에 대응되는 정보어 비트들 및 그에 기초하여 생성된 패리티 비트들뿐만 아니라,  $i$  번째 프레임에 대응되는 정보어 비트들에 기초하여 생성된 부가 패리티 비트들이 맵핑될 수 있다.

[0360] 한편, 상술한 바와 같이, 정보어 비트들은 데이터에 대한 시그널링 정보를 포함하는 시그널링이라는 점에서, 송신 장치(100)는 데이터를 해당 데이터를 처리하기 위한 시그널링과 함께 프레임에 맵핑하여 수신 장치(200)로 전송할 수 있다.

[0361] 구체적으로, 송신 장치(100)는 데이터를 일정한 방식으로 처리하여 성상도 심볼들을 생성하고, 이들을 각 프레임의 데이터 심볼에 맵핑할 수 있다. 그리고, 송신 장치(100)는 각 프레임에 맵핑된 데이터에 대한 시그널링을 해당 프레임의 프리앰블에 맵핑할 수 있다. 예를 들어, 송신 장치(100)는  $i$  번째 프레임에 맵핑된 데이터에 대

한 시그널링 정보를 포함하는 시그널링을  $i$  번째 프레임에 맵핑할 수 있다.

[0362] 이에 따라, 수신 장치(200)는 프레임으로부터 획득한 시그널링을 이용하여 해당 프레임으로부터 데이터를 획득하여 처리할 수 있게 된다.

[0363] 한편, 본 발명의 일 실시 예에 따르면, 상술한 정보어 비트들은 L1 디테일 시그널링(L1-detail signaling)으로 구현될 수 있다. 이에 따라, 송신 장치(100)는 상술한 방법을 이용하여 L1 디테일 시그널링에 대한 부가 패리티 비트들을 생성하여 수신 장치(200)로 전송할 수 있다.

[0364] 여기에서, L1 디테일 시그널링은 ATSC(Advanced Television System Committee) 3.0 표준에서 정의된 시그널링 일 수 있다.

[0365] 구체적으로, L1 디테일 시그널링 처리하는 모드는 7 개로 구분되는데, 본 발명의 일 실시 예에 따른 송신 장치(100)는 7 개의 모드에 따라 L1 디테일 시그널링에 대한 부가 패리티 비트들을 생성할 수 있다.

[0366] 한편, ATSC 3.0 표준에서는 L1 디테일 시그널링 외에도 L1 베이직 시그널링(L1-basic signaling)을 정의하고 있는데, 송신 장치(100)는 L1 베이직 시그널링 및 L1 디테일 시그널링을 특정 방식으로 처리하여 수신 장치(200)로 전송할 수 있다.

[0367] 한편, L1 베이직 시그널링 및 L1 디테일 시그널링을 처리하는 구체적인 방법은 후술하기로 한다.

[0368] 송신 장치(100)는 L1 베이직 시그널링 및 L1 디테일 시그널링을 프레임의 프리앰블에 맵핑하고, 데이터를 프레임의 데이터 심볼에 맵핑하여 수신 장치(200)로 전송할 수 있다.

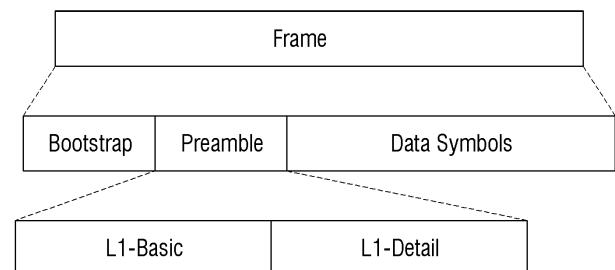

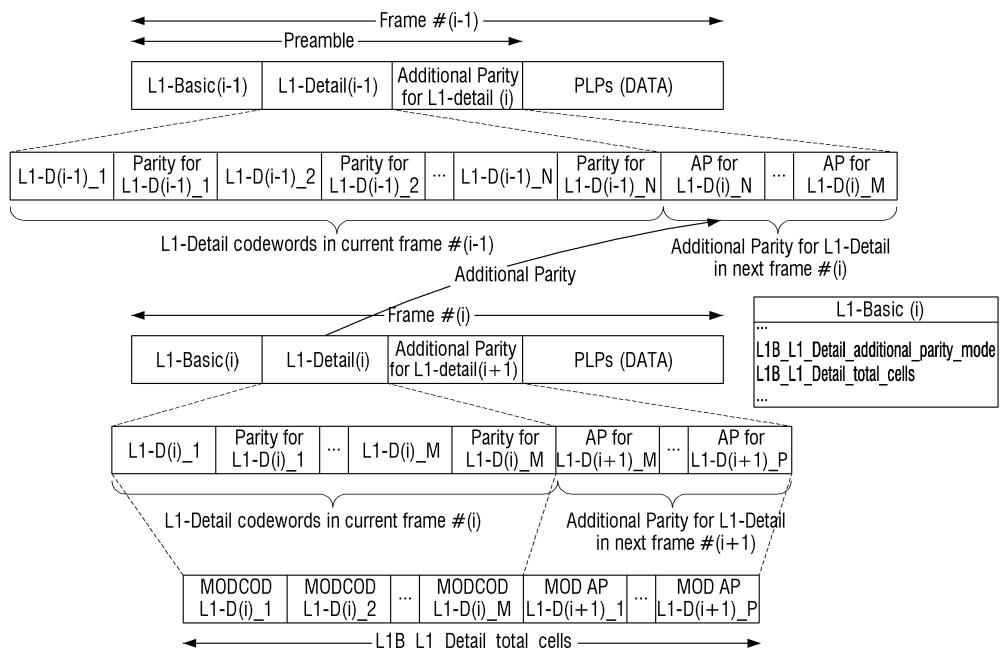

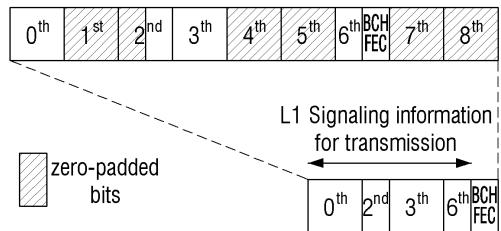

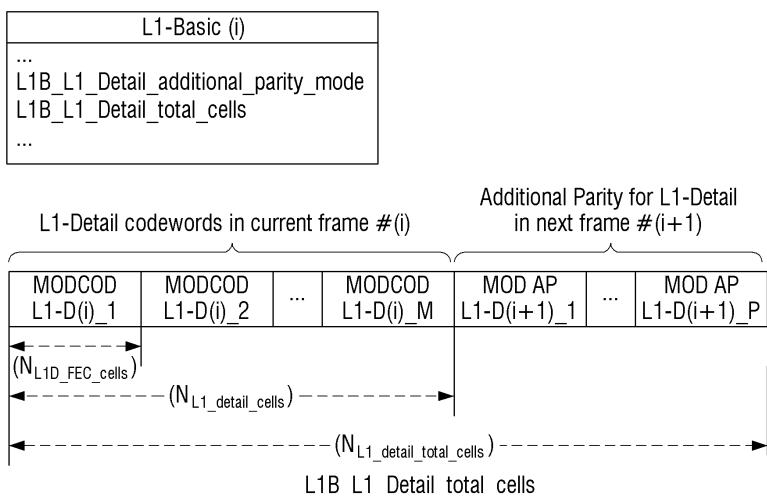

[0369] 도 41을 참조하면, 프레임은 3 가지 파트 즉, 부트스트랩(bootsrap) 파트, 프리앰블 파트 및 데이터 파트로 구성될 수 있다.

[0370] 부트스트랩 파트는 초기 동기화(synchronization)를 위해 이용되며, 수신 장치(200)가 L1 시그널링을 디코딩하기 위한 기본적인 파라미터를 제공한다. 또한, 부트스트랩 파트는 송신 장치(100)가 L1 베이직 시그널링을 처리한 모드에 대한 정보 즉, 송신 장치(100)가 어떠한 모드로 L1 베이직 시그널링을 처리하였는지에 대한 정보를 포함할 수 있다.

[0371] 프리앰블 파트는 L1 시그널링을 포함하며, 2 개의 파트 즉, L1 베이직 시그널링 및 L1 디테일 시그널링으로 구성될 수 있다.

[0372] 여기에서, L1 베이직 시그널링은 L1 디테일 시그널링에 대한 정보를 포함하고, L1 디테일 시그널링은 데이터(여기에서, 데이터는 방송 서비스를 제공하기 위한 방송 데이터로, 하나 이상의 물리 계층 파이프(Physical Layer Pipes, PLPs)를 통해 전송될 수 있다)에 대한 정보를 포함할 수 있다.

[0373] 구체적으로, L1 베이직 시그널링은 수신 장치(200)가 L1 디테일 시그널링을 처리하기 위해 필요한 정보(예를 들어, 송신 장치(100)가 L1 디테일 시그널링을 처리한 모드에 대한 정보(즉, 송신 장치(100)가 어떠한 모드로 L1 디테일 시그널링을 처리하였는지에 대한 정보), L1 디테일 시그널링의 길이에 대한 정보, 부가 패리티 모드에 대한 정보(즉, L1B\_L1\_Detail\_additional\_parity\_mode로, 송신 장치(100)에서 부가 패리티 비트들을 생성하기 위해 이용한 K 값에 대한 정보(여기에서, L1B\_L1\_Detail\_additional\_parity\_mode가 '00'으로 설정된 경우 K=0이며, 부가 패리티 비트들은 이용되지 않은 것이다) 및 total cells의 길이에 대한 정보)를 포함한다. 또한, L1 베이직 시그널링은 FFT(Fast Fourier Transform) 사이즈, 가드 인터벌 및 파일럿 패턴 등과 같은 시스템의 기본적인 시그널링 정보를 포함할 수도 있다.

[0374] 그리고, L1 디테일 시그널링은 수신 장치(200)가 PLPs를 디코딩하기 위해 필요한 정보(예를 들어, PLP 별로 데이터 심볼에 맵핑된 셀들의 시작 위치, PLP ID, PLP의 사이즈, 변조 방식 및 부호율 등)를 포함한다.

[0375] 이에 따라, 수신 장치(200)는 프레임의 동기를 획득하고 프리앰블로부터 L1 베이직 시그널링 및 L1 디테일 시그널링을 획득하고, L1 디테일 시그널링을 이용하여 데이터 심볼로부터 사용자가 필요로 하는 방송 데이터를 수신 할 수 있다.

[0376] 한편, 이하에서는 첨부된 도면을 참조하여, L1 베이직 시그널링 및 L1 디테일 시그널링을 처리하는 방법에 대해 보다 구체적으로 설명하도록 한다.

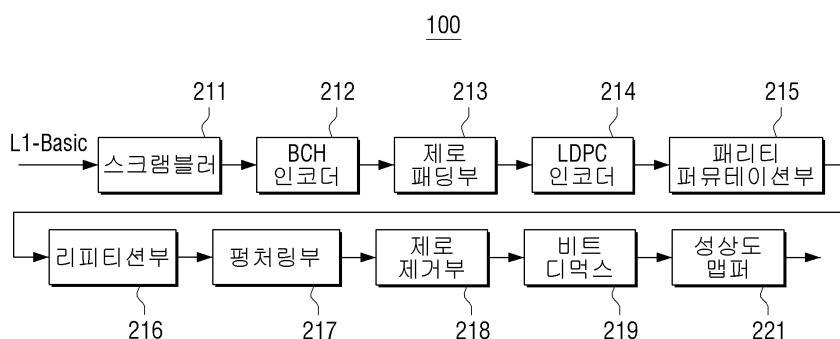

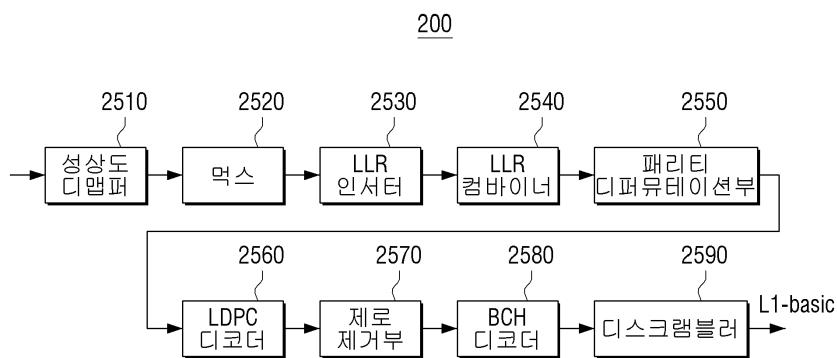

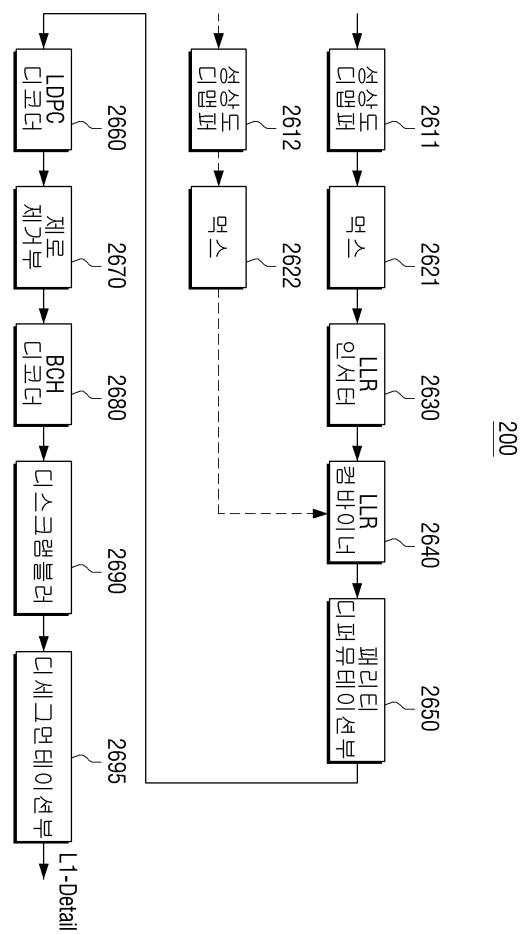

[0377] 도 42 및 도 43은 본 발명의 일 실시 예에 따른 송신 장치의 세부 구성을 설명하기 위한 블록도이다.

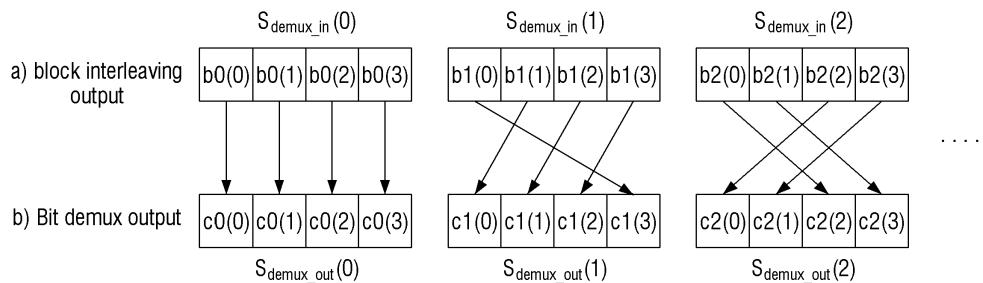

[0378] 구체적으로, 도 42와 같이, 송신 장치(100)는 L1 베이직 시그널링을 처리하기 위해, 스크램블러(211), BCH 인코

더(212), 제로 패딩부(213), LDPC 인코더(214), 패리티 퍼뮤테이션부(215), 리퍼티션부(216), 평처링부(217), 제로 제거부(218), 비트 디믹스(219) 및 성상도 맵퍼(221)를 포함할 수 있다.

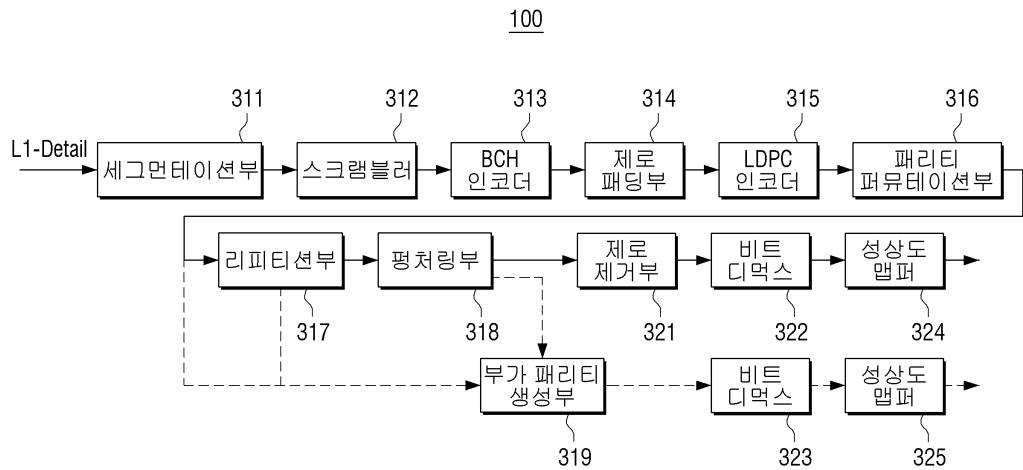

[0379] 또한, 도 43과 같이, 송신 장치(100)는 L1 디테일 시그널링을 처리하기 위해, 세그먼테이션부(311), 스크램블러(312), BCH 인코더(313), 제로 패딩부(314), LDPC 인코더(315), 패리티 퍼뮤테이션부(316), 리퍼티션부(317), 평처링부(318), 부가 패리티 생성부(319), 제로 제거부(321), 비트 디믹스(322, 323) 및 성상도 맵퍼(324, 325)를 포함할 수 있다.

[0380] 여기에서, 도 42 및 도 43에 도시된 구성요소는, L1 베이직 시그널링 및 L1 디테일 시그널링에 대한 인코딩 및 변조(encoding and modulation)를 수행하는 구성요소로서, 이는 일 예일 뿐이며, 경우에 따라 도 42 및 도 43에 도시된 구성요소 중 일부는 생략 또는 변경될 수 있고, 다른 구성요소가 더 추가될 수도 있다.