(19) 日本国特許庁(JP)

## (12) 特 許 公 報(B2)

(11) 特許番号

特許第6317876号

(P6317876)

(45) 発行日 平成30年4月25日(2018.4.25)

(24) 登録日 平成30年4月6日(2018.4.6)

(51) Int.Cl.

F 1

**G 11 C** 7/10 (2006.01)

**G 11 C** 11/419 (2006.01)

**G 06 F** 12/00 (2006.01)

|        |        |         |

|--------|--------|---------|

| G 11 C | 7/10   | 4 8 0   |

| G 11 C | 7/10   | 4 5 5   |

| G 11 C | 11/419 | 1 4 0   |

| G 06 F | 12/00  | 5 7 0 C |

請求項の数 19 (全 25 頁)

(21) 出願番号 特願2012-201000 (P2012-201000)

(22) 出願日 平成24年9月12日 (2012.9.12)

(65) 公開番号 特開2013-65391 (P2013-65391A)

(43) 公開日 平成25年4月11日 (2013.4.11)

審査請求日 平成27年7月1日 (2015.7.1)

(31) 優先権主張番号 13/234, 925

(32) 優先日 平成23年9月16日 (2011.9.16)

(33) 優先権主張国 米国(US)

前置審査

(73) 特許権者 597154922

アルテラ コーポレイション

Altera Corporation

アメリカ合衆国 95134 カリフォルニア州 サンホセ イノベーション ドライヴ 101

(74) 代理人 100078282

弁理士 山本 秀策

(74) 代理人 100113413

弁理士 森下 夏樹

(72) 発明者 フレイルエイシエン

アメリカ合衆国 カリフォルニア 95035, ミルピタス, ピナード ストリート 2240

最終頁に続く

(54) 【発明の名称】メモリ仲裁回路網

## (57) 【特許請求の範囲】

## 【請求項 1】

第1および第2のポートを有するデュアルポートメモリであって、該デュアルポートメモリは、

単一ポートメモリ要素のアレイと、

該アレイに連結されており、かつ該アレイからデータを読み取り、該アレイにデータを書き込む制御回路と、

該第1のポートから第1のメモリアクセス要求を受信する第1の要求生成器と、

該第2のポートから第2のメモリアクセス要求を受信する第2の要求生成器と、

該制御回路、並びに該第1および第2の要求生成器に連結されている仲裁回路とを含み、

該仲裁回路は、同期モードを有しており、該同期モードにおいて、該第1および第2の要求生成器は、第1および第2のクロック信号を用いて制御され、該第1および第2のクロック信号は、位相が整合しており、かつ、等しい周波数を有し、該仲裁回路は、読み取り優先および書き込み優先からなる群から選択される優先度に基づいて、該第1および第2のメモリアクセス要求のうちの所与の1つを満たすように、該制御回路に指示し、該仲裁回路は、該第1および第2のメモリアクセス要求のうちの該所与の1つを満たすように該制御回路に指示するために、出力信号をアサートし、該第1および第2のメモリアクセス要求のうちの該所与の1つの満足に応じて該出力信号をデアサートする、デュアルポートメモリ。

10

20

**【請求項 2】**

前記第1および第2の要求生成器のうちの少なくとも1つは、パルス生成器およびラッチング回路を含み、該パルス生成器は、メモリアクセス要求を受信することに応じて、パルスを生成し、該ラッチング回路は、該メモリアクセス要求が未だ実行されていない場合に、第1の論理値を格納し、該メモリアクセス要求が前記制御回路を用いて実行された場合に、該第1の論理値とは異なる第2の論理値を格納する、請求項1に記載のデュアルポートメモリ。

**【請求項 3】**

前記仲裁回路は、所定の論理表に基づいて、メモリアクセス遂行のために、前記第1および第2のメモリアクセス要求のうちの1つのみを選択する、請求項1に記載のデュアルポートメモリ。10

**【請求項 4】**

前記仲裁回路は、前記第1の要求生成器から第1の出力信号を受信する第1の入力と、前記第2の要求生成器から第2の出力信号を受信する第2の入力と、前記制御回路から制御信号を受信する第3の入力と、出力信号が提供される出力を有する論理ゲートを含み、該出力信号は、該制御回路が前記アレイにアクセスしている間にアサートされる、請求項1に記載のデュアルポートメモリ。

**【請求項 5】**

前記仲裁回路は、前記第2の要求生成器に連結されている第1の入力と、前記第1の要求生成器および該第2の要求生成器に連結されている第2の入力と、出力信号が提供される出力を有する論理ゲートを含み、該出力信号は、前記第1のメモリアクセス要求を満たす場合に、第1の論理値を有し、前記第2のメモリアクセス要求を満たす場合に、該第1の論理値とは異なる第2の論理値を有する、請求項1に記載のデュアルポートメモリ。20

**【請求項 6】**

前記仲裁回路は、非同期モードも有しており、該非同期モードにおいて、前記第1および第2の要求生成器は、異なる周波数を有する少なくとも2つのクロック信号を用いて制御され、該仲裁回路は、所与の時間に、前記同期モードおよび該非同期モードのうちの1つのみにおいて動作する、請求項1に記載のデュアルポートメモリ。

**【請求項 7】**

前記第1および第2の要求生成器のうちの少なくとも1つは、パルス生成器およびラッチング回路を含み、該パルス生成器は、メモリアクセス要求を受信することに応じて、パルスを生成し、該ラッチング回路は、該メモリアクセス要求が未だ実行されていない場合に、第1の論理値を格納し、該メモリアクセス要求が前記制御回路を用いて実行された場合に、該第1の論理値とは異なる第2の論理値を格納する、請求項6に記載のデュアルポートメモリ。30

**【請求項 8】**

前記仲裁回路は、前記同期モードで動作するとき、所定の論理表に基づいて、メモリアクセス遂行のために、前記第1および第2のメモリアクセス要求のうちの1つのみを選択する、請求項6に記載のデュアルポートメモリ。

**【請求項 9】**

前記第1および第2のメモリアクセス要求は、異なる時間に到達し、前記仲裁回路は、前記非同期モードで動作するとき、メモリアクセス遂行のために、該第1および第2のメモリアクセス要求のうちのより早く到達する1つを選択する、請求項6に記載のデュアルポートメモリ。40

**【請求項 10】**

第1および第2のポートを有するデュアルポートメモリであって、該デュアルポートメモリは、

单一ポートメモリ要素のアレイと、

該アレイに連結されており、かつ該アレイからデータを読み取り、該アレイにデータを書き込む制御回路と、50

該第1のポートから第1のメモリアクセス要求を受信する第1の要求生成器と、該第2のポートから第2のメモリアクセス要求を受信する第2の要求生成器と、該制御回路、並びに該第1および第2の要求生成器に連結されている仲裁回路とを含み、

該仲裁回路は、非同期モードを有しており、該非同期モードにおいて、該第1および第2の要求生成器は、異なるそれぞれの周波数を有する2つの異なるクロック信号を用いて制御され、該2つの異なるクロック信号のうちの1つの周波数は、該2つの異なるクロック信号のうちの別の1つの整数倍ではなく、該仲裁回路は、同期モードも有しており、該仲裁回路は、所与の時間に、該同期モードおよび該非同期モードのうちの1つのみにおいて動作し、該仲裁回路は、該第1および第2のメモリアクセス要求のうちの所与の1つを満たすように該制御回路に指示するために、出力信号をアサートし、該第1および第2のメモリアクセス要求のうちの該所与の1つの満足に応じて該出力信号をデアサートする、デュアルポートメモリ。10

#### 【請求項11】

前記第1および第2の要求生成器のうちの少なくとも1つは、パルス生成器およびラッチング回路を含み、該パルス生成器は、メモリアクセス要求を受信することに応じて、パルスを生成し、該ラッチング回路は、該メモリアクセス要求が未だ実行されていない場合に、第1の論理値を格納し、該メモリアクセス要求が前記制御回路を用いて実行された場合に、該第1の論理値とは異なる第2の論理値を格納する、請求項10に記載のデュアルポートメモリ。20

#### 【請求項12】

前記第1および第2の要求生成器を制御する前記2つの異なるクロック信号は、異なるそれぞれの位相を有する、請求項10に記載のデュアルポートメモリ。

#### 【請求項13】

前記第1および第2のメモリアクセス要求は、異なる時間に到達し、前記仲裁回路は、前記非同期モードで動作する間、メモリアクセス遂行のために、該第1および第2のメモリアクセス要求のうちのより早く到達する1つを選択する、請求項10に記載のデュアルポートメモリ。

#### 【請求項14】

前記仲裁回路は、第1および第2の交差連結された論理ゲートを有するラッチング回路を含み、該第1の論理ゲートは、前記第1の要求生成器から第1の出力信号を受信し、かつ第1の論理値を有する第1の制御信号を生成し、該第2の論理ゲートは、前記第2の要求生成器から第2の出力信号を受信し、かつ該第1の論理値とは異なる第2の論理値を有する第2の制御信号を生成する、請求項10に記載のデュアルポートメモリ。30

#### 【請求項15】

单一ポートメモリ要素のアレイと、第1および第2のポートとを含むデュアルポートメモリを使用するための方法であって、該方法は、

制御回路を用いて、該单一ポートメモリ要素のアレイにアクセスすることと、

第1の要求生成器を用いて、該第1のポートから第1のメモリアクセス要求を受信することと、40

第2の要求生成器を用いて、該第2のポートから第2のメモリアクセス要求を受信することと、

仲裁回路を用いて、出力信号をアサートすることによって、該第1および第2のメモリアクセス要求のうちの選択された1つを満たすように該制御回路に指示することと、

該制御回路を用いて、該選択されたメモリアクセス要求の満足に応じて、制御信号をアサートすることと、

該第1および第2の要求生成器を用いて該制御信号を受信することと、

該制御回路が該制御信号をアサートすることに応じて、該仲裁回路を用いて、該出力信号をデアサートすることと

を含む、方法。50

**【請求項 1 6】**

同期モードで前記デュアルポートメモリを動作させることをさらに含み、該同期モードにおいて、前記第1および第2の要求生成器は、等しい周波数を有する少なくとも2つのクロック信号を用いて制御される、請求項1\_5に記載の方法。

**【請求項 1 7】**

非同期モードで前記デュアルポートメモリを動作させることをさらに含み、該非同期モードにおいて、前記第1および第2の要求生成器は、異なる周波数を有する少なくとも2つのクロック信号を用いて制御される、請求項1\_5に記載の方法。

**【請求項 1 8】**

同期モードで前記デュアルポートメモリを動作させることと、非同期モードで該デュアルポートメモリを動作させることとをさらに含み、該同期モードにおいて、前記第1および第2の要求生成器は、等しい周波数を有する少なくとも2つのクロック信号を用いて制御され、該非同期モードにおいて、該第1および第2の要求生成器は、異なる周波数を有する少なくとも2つのクロック信号を用いて制御される、請求項1\_5に記載の方法。 10

**【請求項 1 9】**

前記第1および第2の要求生成器のうちの少なくとも1つは、パルス生成器およびラッチング回路を含み、前記方法は、

該パルス生成器を用いて、メモリアクセス要求が該第1および第2の要求生成器のうちの該少なくとも1つに到達したことを検出することに応じてパルスを生成することと、

該ラッチング回路を用いて、該メモリアクセス要求が未だ満たされていない場合に、第1の論理値を格納し、該メモリアクセス要求が前記制御回路を用いて満たされた場合に、該第1の論理値とは異なる第2の論理値を格納することと 20

をさらに含む、請求項1\_5に記載の方法。

**【発明の詳細な説明】****【技術分野】****【0 0 0 1】**

この出願は、2011年9月16日に出願した米国特許出願第13/234,925に対して優先権を主張する。上記文献は、全体として本明細書において参照することによって援用される。

**【背景技術】****【0 0 0 2】****(背景)**

集積回路（例えば、プログラマブル集積回路）は、静的ランダムアクセスメモリ（SRAM）セルの形態の揮発性メモリ要素を含み得る。揮発性メモリ要素（例えば、SRAMセル）は、典型的に、交差連結されたインバータ（すなわち、ラッチ）に基づく。メモリ要素は、しばしば、アレイで配列される。典型的アレイにおいて、データラインは、メモリ要素内にデータを書き込み、メモリ要素からデータを読み取るために使用される。アドレスラインは、どのメモリ要素がアクセスされるかを選択するために使用され得る。

**【0 0 0 3】**

あるアプリケーションは、メモリ要素がデュアルポート能力を有する（すなわち、メモリ要素が2つのポートを含み、2つのポートの各々は、読み取り／書き込み動作を実行するため使用される）ことを要求する。デュアルポート動作をサポートするために、メモリ要素は、典型的に、8トランジスタ構成において形成される。デュアルポートメモリ要素は、2つの交差連結されたインバータを含む。第1の対のアクセストランジスタは、第1の読み取り／書き込みポートとして機能するために、交差連結されたインバータに連結され、その一方で、第2の対のアクセストランジスタは、第2の読み取り／書き込みポートとして機能するために、交差連結されたインバータに連結される。しかしながら、このように配列された従来の8トランジスタ（8T）デュアルポートメモリセルは、従来の6トランジスタ（6T）単一ポートメモリセルの面積の2倍より多くの面積を占用する。 40

**【0 0 0 4】**

50

20

30

40

50

デュアルポートメモリ回路網の面積を低減するために、6 Tメモリ要素を用いて同期デュアルポート機能を提供する（すなわち、両方のポートが單一クロックを用いて制御される）ことを可能にする技術が開発された。例えば、ダブルクロッキング技術は、（第1のポートに関連付けられた要求を満たすために）高いクロック位相の間、および（第2のポートに関連付けられた要求を満たすために）低いクロック位相の間にメモリ要素にアクセスすることを含む。しかしながら、ダブルクロッキングメモリアクセスは、メモリの性能を制限し、非同期デュアルポート動作（すなわち、2つのポートを制御するために、異なるクロック周波数および／または位相を有する2つの別個のクロック信号を使用することを含む動作）をサポートするために使用されることができない。

【発明の概要】

10

【課題を解決するための手段】

【0005】

メモリ要素回路網を有する集積回路が提供される。メモリ要素は、アレイで配列された単一ポートメモリ要素を含み得る。メモリ要素は、多重ポートメモリ機能を提供する周辺メモリ制御回路網とインターフェースでつなぐように構成され得る。

【0006】

例えば、メモリ回路網は、制御回路を含み得、制御回路は、メモリアレイ内の特定位置において読み取りアクセスおよび書き込みアクセスを実行するように、列アドレッシング回路網および行ドライバー／感知回路網に指示する。メモリ回路網はまた、それぞれ、少なくとも第1および第2のポートを介して少なくとも第1および第2の処理回路からメモリアクセス要求を生成するように構成されるデータレジスタおよび論理回路を含み得る。メモリ回路網は、第1のポートに関連付けられたメモリ要求を受信するように動作可能な第1の要求生成器と、第2のポートに関連付けられたメモリ要求を受信するように動作可能な第2の要求生成器とを含み得る。第1および第2の要求生成器の各々は、未処理の要求が存在する場合に、高くラッチし、未処理の要求がない場合に、低くラッチするストレージ回路を含み得る。

20

【0007】

メモリ回路網はまた、第1および第2の要求生成器と制御回路との間に連結された仲裁回路を含み得る。仲裁回路は、第1および第2の要求生成器からメモリアクセス要求を受信し、かつ第1および第2のポートに関連付けられたメモリアクセス要求が実行される順番を扱うように構成され得る。

30

【0008】

本発明の1つの適切な実施形態において、仲裁回路は、同期モード（すなわち、第1および第2のポートからの要求が單一クロックを用いて制御されるモード）で動作可能であり得る。所与のクロックサイクルの間に、1つのメモリ要求のみが2つのポートのうちの第1のポートにおいて受信されている場合に、第1のポートに関連付けられた1つのメモリ要求が実行され得る。異なるタイプのメモリ要求が、それぞれ、第1および第2のポートにおいて同時に受信される（すなわち、1つのポートが読み取りを受信し、もう1つのポートが書き込みを受信する）場合に、仲裁回路は、読み取り優先（すなわち、仲裁回路が、先に読み取り動作を実行し得ること）または書き込み優先（すなわち、仲裁回路が、先に書き込み動作を実行し得ること）を提供するように構成され得る。同じタイプのメモリ要求が、第1および第2のポートにおいて同時に受信される（すなわち、両方のポートが読み取りを受信するかまたは両方のポートが書き込みを受信する）場合に、仲裁回路は、第1のポート優先（すなわち、仲裁回路が、先に第1のポートに関連付けられた動作を実行し得ること）または第2のポート優先（すなわち、仲裁回路が、先に第2のポートに関連付けられた動作を実行し得ること）を提供するように構成され得る。

40

【0009】

本発明の別の適切な実施形態において、仲裁回路は、非同期モード（すなわち、第1および第2のポートからの要求が、異なる周波数および／または位相を有する第1および第2のクロック信号を用いて制御されるモード）で動作可能であり得る。非同期モードにお

50

いて、仲裁回路は、メモリアクセス要求が受信されるとすぐに、メモリアクセス要求を実行する。例えば、仲裁回路が、第1のポートにおいて所与のメモリ要求を検出する場合に、仲裁回路は、所与のメモリ要求を実行するように制御回路に指示する。第2のメモリ要求が、所与のメモリが満たされる前に第2のポートにおいて受信される場合に、第2のメモリ要求は、所与のメモリ要求が完了されるまで保留され得る。仲裁回路が、所与のメモリ要求が満たされたことを検出した場合に、仲裁回路は、第2のメモリ要求を実行するように制御回路に指示する。

#### 【0010】

例えば、本発明は以下の項目を提供する。

##### (項目1)

第1および第2のポートを有するデュアルポートメモリであって、該デュアルポートメモリは、

単一ポートメモリ要素のアレイと、

該アレイに連結されており、かつ該アレイからデータを読み取り、該アレイにデータを書き込むように動作可能である制御回路と、

該第1のポートから第1のメモリアクセス要求を受信するように動作可能な第1の要求生成器と、

該第2のポートから第2のメモリアクセス要求を受信するように動作可能な第2の要求生成器と、

該制御回路、並びに該第1および第2の要求生成器に連結されている仲裁回路と

を含み、

該仲裁回路は、同期モードで動作可能であり、該同期モードにおいて、該第1および第2の要求生成器は、等しい周波数を有する少なくとも2つのクロック信号を用いて制御され、該少なくとも2つのクロック信号の各クロックサイクルの間に、該第1および第2のメモリアクセス要求のうちの1つのみを満たすために、該制御回路に指示するように動作可能である、デュアルポートメモリ。

##### (項目2)

上記第1および第2の要求生成器のうちの少なくとも1つは、パルス生成器およびラッチング回路を含み、該パルス生成器は、メモリアクセス要求を受信することに応じて、パルスを生成するように動作可能であり、該ラッチング回路は、該メモリアクセス要求が未だ実行されていない場合に、第1の論理値を格納するように動作可能であり、該メモリアクセス要求が上記制御回路を用いて実行された場合に、該第1の論理値とは異なる第2の論理値を格納するように動作可能である、上記項目に記載のデュアルポートメモリ。

##### (項目3)

上記仲裁回路は、所定の論理表に基づく満足に対して、上記第1および第2のメモリアクセス要求のうちの1つのみを選択するように動作可能である、上記項目のいずれかに記載のデュアルポートメモリ。

##### (項目4)

上記仲裁回路は、上記第1の要求生成器から第1の出力信号を受信するように動作可能である第1の入力と、上記第2の要求生成器から第2の出力信号を受信するように動作可能である第2の入力と、上記制御回路から制御信号を受信するように動作可能である第3の入力と、出力信号が提供される出力とを有する論理ゲートを含み、該出力信号は、該制御回路が上記アレイにアクセスしている間にアサートされる、上記項目のいずれかに記載のデュアルポートメモリ。

##### (項目5)

上記仲裁回路は、上記第2の要求生成器に連結されている第1の入力と、上記第1の要求生成器および該第2の要求生成器に連結されている第2の入力と、出力信号が提供される出力とを有する論理ゲートを含み、該出力信号は、上記第1のメモリアクセス要求を満たす場合に、第1の論理値を有し、上記第2のメモリアクセス要求を満たす場合に、該第1の論理値とは異なる第2の論理値を有する、上記項目のいずれかに記載のデュアルポートメモリ。

10

20

30

40

50

トメモリ。

(項目 6)

上記仲裁回路は、非同期モードにおいてさらに動作可能であり、該非同期モードにおいて、上記第1および第2の要求生成器は、異なる周波数を有する少なくとも2つのクロック信号を用いて制御されている、上記項目のいずれかに記載のデュアルポートメモリ。

(項目 7)

上記第1および第2の要求生成器のうちの少なくとも1つは、パルス生成器およびラッチング回路を含み、該パルス生成器は、メモリアクセス要求を受信することに応じて、パルスを生成するように動作可能であり、該ラッチング回路は、該メモリアクセス要求が未だ実行されていない場合に、第1の論理値を格納するように動作可能であり、該メモリアクセス要求が上記制御回路を用いて実行された場合に、該第1の論理値とは異なる第2の論理値を格納するように動作可能である、上記項目のいずれかに記載のデュアルポートメモリ。10

(項目 8)

上記仲裁回路は、上記同期モードで動作するとき、所定の論理表に基づく満足に対して、上記第1および第2のメモリアクセス要求のうちの1つのみを選択するように動作可能である、上記項目のいずれかに記載のデュアルポートメモリ。

(項目 9)

上記第1および第2のメモリアクセス要求は、異なる時間に到達し、上記仲裁回路は、上記非同期モードで動作するとき、満足に対して、該第1および第2のメモリアクセス要求のうちのより早く到達する1つを選択するように動作可能である、上記項目のいずれかに記載のデュアルポートメモリ。20

(項目 10)

上記仲裁回路は、上記第1および第2のメモリアクセス要求のうちの選択された1つを満たすように上記制御回路に指示するために、出力信号をアサートし、該選択されたメモリアクセス要求の満足に応じて該出力信号をデアサートするように動作可能である、上記項目のいずれかに記載のデュアルポートメモリ。

(項目 11)

第1および第2のポートを有するデュアルポートメモリであって、該デュアルポートメモリは、30

单一ポートメモリ要素のアレイと、

該アレイに連結されており、かつ該アレイからデータを読み取り、該アレイにデータを書き込むように動作可能である制御回路と、

該第1のポートから第1のメモリアクセス要求を受信するように動作可能な第1の要求生成器と、

該第2のポートから第2のメモリアクセス要求を受信するように動作可能な第2の要求生成器と、

該制御回路、並びに該第1および第2の要求生成器に連結されている仲裁回路とを含み、

該仲裁回路は、非同期モードで動作可能であり、該非同期モードにおいて、該第1および第2の要求生成器は、異なるそれぞれの周波数を有する2つの異なるクロック信号を用いて制御される、デュアルポートメモリ。40

(項目 12)

上記第1および第2の要求生成器のうちの少なくとも1つは、パルス生成器およびラッチング回路を含み、該パルス生成器は、メモリアクセス要求を受信することに応じて、パルスを生成するように動作可能であり、該ラッチング回路は、該メモリアクセス要求が未だ実行されていない場合に、第1の論理値を格納するように動作可能であり、該メモリアクセス要求が上記制御回路を用いて実行された場合に、該第1の論理値とは異なる第2の論理値を格納するように動作可能である、上記項目のいずれかに記載のデュアルポートメモリ。50

## (項目 1 3 )

上記第 1 および第 2 の要求生成器を制御する上記 2 つの異なるクロック信号は、異なるそれぞれの位相を有する、上記項目のいずれかに記載のデュアルポートメモリ。

## (項目 1 4 )

上記第 1 および第 2 のメモリアクセス要求は、異なる時間に到達し、上記仲裁回路は、上記非同期モードで動作する間、満足に対して、該第 1 および第 2 のメモリアクセス要求のうちのより早く到達する 1 つを選択するように動作可能である、上記項目のいずれかに記載のデュアルポートメモリ。

## (項目 1 5 )

上記仲裁回路は、第 1 および第 2 の交差連結された論理ゲートを有するラッチング回路を含み、該第 1 の論理ゲートは、上記第 1 の要求生成器から第 1 の出力信号を受信するように動作可能であり、かつ第 1 の論理値を有する第 1 の制御信号を生成するように動作可能であり、該第 2 の論理ゲートは、上記第 2 の要求生成器から第 2 の出力信号を受信するように動作可能であり、かつ該第 1 の論理値とは異なる第 2 の論理値を有する第 2 の制御信号を生成するように動作可能である、上記項目のいずれかに記載のデュアルポートメモリ。

10

## (項目 1 6 )

単一ポートメモリ要素のアレイと、第 1 および第 2 のポートとを含むデュアルポートメモリを使用するための方法であって、該方法は、

制御回路を用いて、該単一ポートメモリ要素のアレイにアクセスすることと、

20

第 1 の要求生成器を用いて、該第 1 のポートから第 1 のメモリアクセス要求を受信することと、

第 2 の要求生成器を用いて、該第 2 のポートから第 2 のメモリアクセス要求を受信することと、

仲裁回路を用いて、出力信号をアサートすることによって、該第 1 および第 2 のメモリアクセス要求のうちの選択された 1 つを満たすように該制御回路に指示することとを含む、方法。

## (項目 1 7 )

上記選択されたメモリアクセス要求の満足に応じて上記出力信号をデアサートすることをさらに含む、上記項目のいずれかに記載の方法。

30

## (項目 1 8 )

同期モードで上記デュアルポートメモリを動作させることをさらに含み、該同期モードにおいて、上記第 1 および第 2 の要求生成器は、等しい周波数を有する少なくとも 2 つのクロック信号を用いて制御される、上記項目のいずれかに記載の方法。

## (項目 1 9 )

非同期モードで上記デュアルポートメモリを動作させることをさらに含み、該非同期モードにおいて、上記第 1 および第 2 の要求生成器は、異なる周波数を有する少なくとも 2 つのクロック信号を用いて制御される、上記項目のいずれかに記載の方法。

## (項目 2 0 )

同期モードで上記デュアルポートメモリを動作させることと、非同期モードで該デュアルポートメモリを動作させることをさらに含み、該同期モードにおいて、上記第 1 および第 2 の要求生成器は、等しい周波数を有する少なくとも 2 つのクロック信号を用いて制御され、該非同期モードにおいて、該第 1 および第 2 の要求生成器は、異なる周波数を有する少なくとも 2 つのクロック信号を用いて制御される、上記項目のいずれかに記載の方法。

40

## (項目 2 1 )

上記制御回路を用いて、上記選択されたメモリアクセス要求の満足に応じて制御信号をアサートすることと、

上記第 1 および第 2 の要求生成器を用いて該制御信号を受信することとをさらに含む、上記項目のいずれかに記載の方法。

50

## (項目 22)

上記第1および第2の要求生成器のうちの少なくとも1つは、パルス生成器およびラッチング回路を含み、上記方法は、

該パルス生成器を用いて、メモリアクセス要求が該第1および第2の要求生成器のうちの該少なくとも1つに到達したことを検出することに応じてパルスを生成することと、

該ラッチング回路を用いて、該メモリアクセス要求が未だ満たされていない場合に、第1の論理値を格納し、該メモリアクセス要求が上記制御回路を用いて満たされた場合に、該第1の論理値とは異なる第2の論理値を格納することと

をさらに含む、上記項目のいずれかに記載の方法。

## 【0011】

10

## (摘要)

メモリ要素を有する集積回路が提供される。メモリ要素は、多重ポートメモリ機能を提供するために使用される单一ポートメモリセルであり得る。集積回路は、少なくとも第1および第2の生成器からメモリアクセス要求を受信するように動作可能な仲裁回路を含み得る。仲裁回路は、同期モードおよび非同期モードで動作するように構成され得る。同期モードで動作する仲裁回路は、所定の論理表に基づいてポート選択を実行し得る。非同期モードで動作する仲裁回路は、メモリ要求が仲裁回路によって受信されるとすぐにメモリ要求を実行し得る。現在のメモリアクセスが実行されている間に受信される要求は、現在のメモリアクセスが完了されるまで保留され得る。

## 【0012】

20

本発明のさらなる特徴、本発明の本質およびさまざまな利点は、添付の図面および以下の詳細な説明からより明白になる。

## 【図面の簡単な説明】

## 【0013】

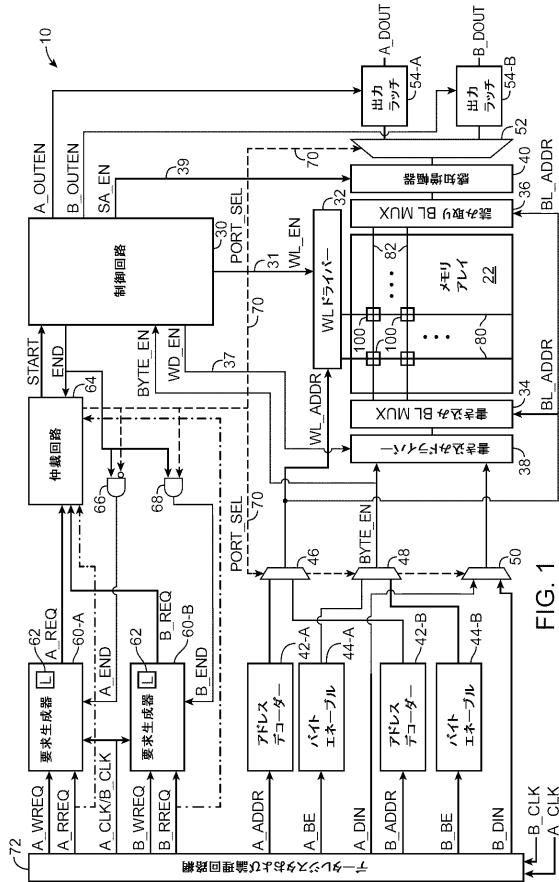

【図1】図1は、本発明の実施形態に従う、仲裁回路を有する多重ポートメモリ回路網のダイヤグラムである。

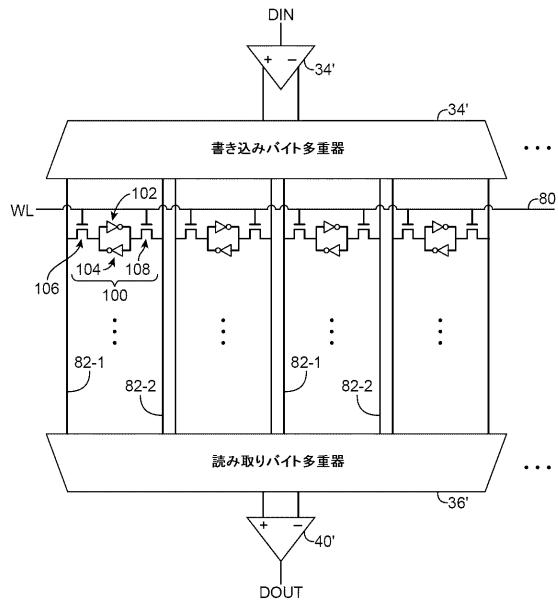

【図2】図2は、本発明の実施形態に従う、関連付けられた行多重化回路に連結されたメモリ要素回路網のダイヤグラムである。

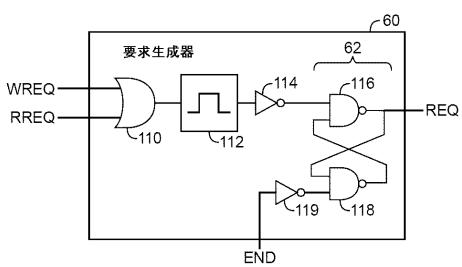

【図3】図3は、本発明の実施形態に従う例示的な要求生成器の回路ダイヤグラムである。

30

【図4】図4は、本発明の実施形態に従う、同期デュアルポートメモリ動作の間にどのポートが選択されるかを決定するための表である。

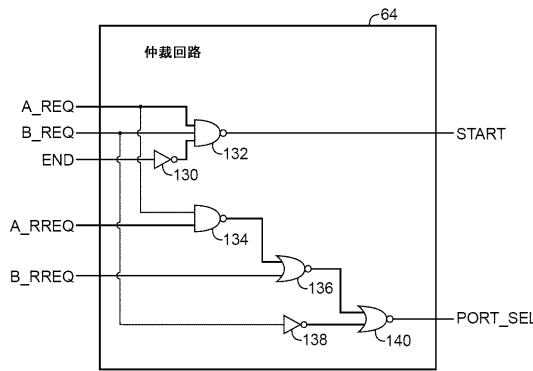

【図5】図5は、本発明の実施形態に従う、同期デュアルポートメモリ動作をサポートするように動作可能で例示的な仲裁回路の回路ダイヤグラムである。

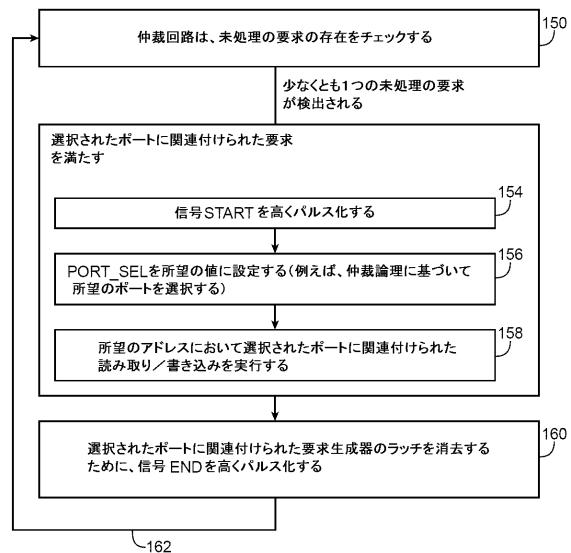

【図6】図6は、本発明の実施形態に従う、同期デュアルポートモードにおいて未処理メモリアクセス要求を処理するための代表的なステップのフローチャートである。

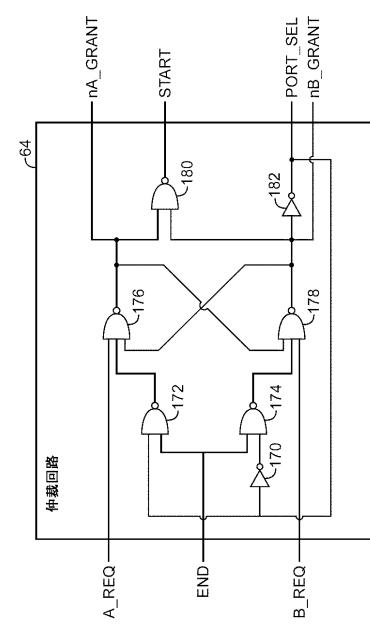

【図7】図7は、本発明の実施形態に従う、非同期デュアルポートメモリ動作をサポートするように動作可能で例示的な仲裁回路の回路ダイヤグラムである。

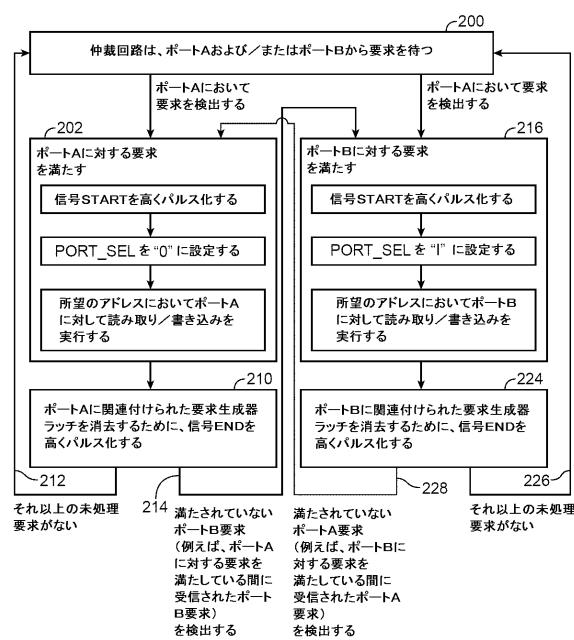

【図8】図8は、本発明の実施形態に従う、非同期デュアルポートモードにおいて未処理メモリアクセス要求を処理するための例示的なステップのフローチャートである。

40

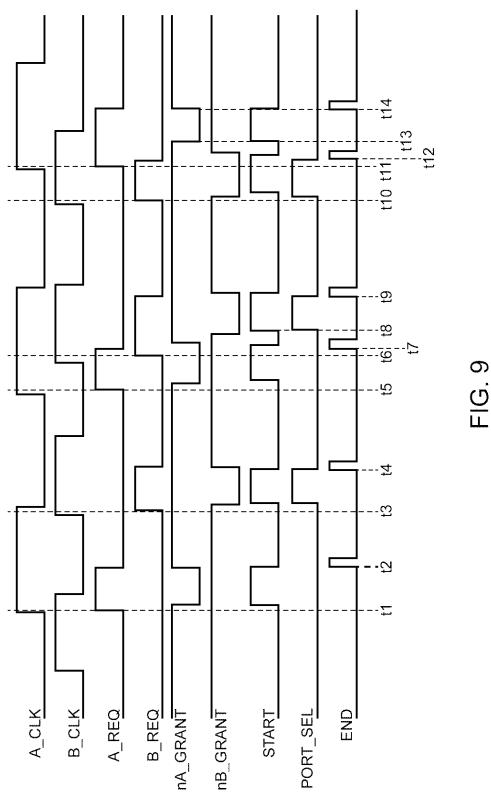

【図9】図9は、本発明の実施形態に従う、非同期デュアルポートモードの間に異なるメモリアクセスシーケンスを例示するタイミングダイヤグラムである。

## 【発明を実施するための形態】

## 【0014】

## (詳細な説明)

本発明の実施形態は、静的ランダムアクセスメモリ回路網に関連する。本発明のメモリ回路網は、任意の適切な集積回路内に使用され得る。例えば、メモリ回路網は、集積回路メモリデバイスまたは特定用途の集積回路(A S I C)内において使用され得る。

## 【0015】

図1は、同期および非同期の多重メモリ動作をサポートするように構成された仲裁回路

50

を有するメモリ回路網を含む集積回路 10 のダイヤグラムである。メモリ回路網は、少なくとも 1 つのメモリアレイ 22 を含み得る。図 1 に示されるように、メモリアレイ 22 は、列および行に配列されたメモリ要素（ときには、メモリセルと呼ばれる）100 を含み得る。メモリセル 100 は、単一ポートメモリセルを含み得る。例えば、メモリセル 100 は、6 つのトランジスタを有する単一ポート差動メモリセル（例えば、メモリセルに対して単一ポートとして機能する一対のアクセストランジスタを有するメモリセル）であり得る。デュアルポートメモリ機能を提供するために単一ポートメモリセルを使用することは、ダイ步留まりを増大させることを助け、低減された最小要求電源電圧（すなわち、低減された電力消費）を提供し、集積回路の実際の所有面積を保存し得る。

## 【0016】

10

メモリセル 100 の各列は、関連付けられたワードライン 80 を介してワードライン（WL）ドライバー回路網 32 に連結され得る。例えば、メモリセル 100 の第 1 の列は、第 1 のワードライン 80 を介して WL ドライバー回路網 32 に連結され得、メモリセル 100 の第 2 の列は、第 2 のワードライン 80 等を介して WL ドライバー回路網 32 に連結され得る。WL ドライバー回路網 32 は、メモリセル 100 の列を選択するようにワードライン 80 のうちの選択された 1 つにおいてワードライン信号をアサートするために使用され得る。ワードライン信号およびワードライン 80 は、ときには、それぞれ、アドレス信号およびアドレスラインと呼ばれる。

## 【0017】

20

メモリセル 100 の各行は、関連付けられたビットライン（BL）82 を介して、多重化（MUX）回路（例えば、書き込みビットライン多重化回路網 34 および読み取りビットライン多重化回路網 36）に連結され得る。ビットライン 82 は、ときには、データラインと呼ばれ得る。例えば、メモリセル 100 の第 1 の行は、第 1 対のビットラインを介して、回路網 34 および 36 に連結され得、メモリセル 100 の第 2 の行は、第 2 対のビットライン等を介して、回路網 34 および 36 に連結され得る。ビットライン 82 は、選択されたメモリセル 100 からデータを読み取り、またはそれにデータを書き込むために適切な電圧を供給され得る。本明細書において説明される用語、列および行は、単なる例示に過ぎず、相互交換可能に使用され得、またはメモリの任意のグループ / 集合を指すように使用され得る。

## 【0018】

30

書き込み BL 多重化回路網 34 は、書き込みドライバー回路網 38 によって駆動されるべきビットライン 82 のサブセットを選択するように構成され得る（例えば、回路網 34 は、データラインの選択された部分を書き込みドライバー回路網 38 に連結するように構成され得る）。例えば、メモリアレイ 22 が、128 行のメモリセル 100 を含み、書き込みドライバー回路網 38 が、32 個の差動書き込みドライバーのみを含むシナリオを考える。この例において、書き込み BL 多重化回路網 34 は、4 対のビットラインのグループ内の選択された一対のビットラインを回路網 38 内の対応する書き込みドライバーに連結するために使用される 4 : 1 多重化回路を含み得る（すなわち、多重化回路網 34 は、書き込み動作の間に、4 対のビットライン毎を対応する書き込みドライバーに連結するために使用され得る）。

40

## 【0019】

読み取り BL 多重化回路網 36 は、ビットライン 82 のサブセットを感知增幅器回路網 40 に連結するように構成され得る（例えば、回路網 36 は、データラインの選択された部分を感知增幅器回路網 38 に連結するように構成され得る）。例えば、メモリアレイ 22 が、128 行のメモリセル 100 を含み、感知增幅器回路網 40 が 32 個の差動感知增幅器のみを含むシナリオを考える。この例において、読み取り BL 多重化回路網 36 は、4 対のビットラインの各グループ内の選択された一対のビットラインを回路網 40 内の対応する感知增幅器に連結するために使用される 4 : 1 多重化回路を含み得る（すなわち、多重化回路網 36 は、読み取り動作の間に、4 対のビットライン毎を対応する感知增幅器に連結するために使用され得る）。概して、多重化回路網 34 および 36 の複雑さ（すな

50

わち、回路網 3 4 および 3 6 が、2 : 1 多重化、4 : 1 多重化、8 : 1 多重化等を提供するか否か)は、メモリアレイ 2 2 内に存在するメモリ行の数と、ビットライン対 8 2 上に信号を駆動するための書き込みドライバーおよびビットライン対 8 2 から信号を受信するための感知増幅器の数とに依存し得る。

#### 【 0 0 2 0 】

アレイ 2 2 の 6 T 単一ポートメモリセル 1 0 0 は、周辺メモリ回路網の使用を介してデュアルポート機能を提供し得る。例えば、ワードラインドライバー回路網 3 2 は、多重器 4 6 を介して第 1 のアドレスデコーダー 4 2 - A および第 2 のアドレスデコーダー 4 2 - B のうちの 1 つから列アドレス信号 W L \_ A D D R を受信し得る。多重器 4 6 は、アドレスデコーダー 4 2 - A に連結されている第 1 の入力と、アドレスデコーダー 4 2 - B に連結されている第 2 の入力と、ワードラインドライバー回路網 3 2 に連結されている出力と有し得る。ビットライン多重化回路網 3 4 および 3 6 はまた、多重器 4 6 を介して、アドレスデコーダー 4 2 - A および 4 2 - B のうちの 1 つから行アドレス信号 B L \_ A D D R を受信し得る。

#### 【 0 0 2 1 】

アドレスデコーダー 4 2 - A は、アドレス信号 A \_ A D D R (すなわち、第 1 のメモリポートに関連付けられた列および行アドレス信号) を受信し得、その一方で、アドレスデコーダー 4 2 - B は、アドレス信号 B \_ A D D R (すなわち、第 2 のメモリポート関連付けられた列および行アドレス信号) を受信し得る。多重器 4 6 は、信号 A \_ A D D R および B \_ A D D R のうちの 1 つをその出力に選択的にルーティングさせるために使用され得る(すなわち、それにより、ワードラインドライバー 3 2 は、2 つのメモリポートのうちの選択された 1 つから列信号 W L \_ A D D R を受信し、並びに多重化回路網 3 4 および 3 6 は、選択されたメモリポートから行信号 B L \_ A D D R を受信する)。

#### 【 0 0 2 2 】

書き込みドライバー回路網 3 8 は、多重器 4 8 の出力において生成されたバイトエネーブル信号 B Y T E \_ E N によって制御され得る。多重器 4 8 は、第 1 のバイトエネーブル回路 4 4 - A に連結されている第 1 の入力と、第 2 のバイトエネーブル回路 4 4 - B に連結されている第 2 の入力とを有し得る。バイトエネーブル回路 4 4 - A は、第 1 のメモリポートに関連付けられたエネーブル信号 A \_ B E を受信し得、その一方で、バイトエネーブル回路 4 4 - B は、第 2 のメモリポートに関連付けられたエネーブル信号 B \_ B E を受信し得る。多重器 4 8 は、エネーブル信号 A \_ B E および B \_ B E のうちの 1 つをその出力に選択的にルーティングさせるために使用され得る。

#### 【 0 0 2 3 】

信号 B Y T E \_ E N は、書き込みドライバー回路網 3 8 の選択された部分をオンにするために使用され得る。例えば、書き込みドライバー回路網 3 8 が 3 2 個の書き込みドライバーを含むシナリオを考える。単一 B Y T E \_ E N は、8 つの行が同時にロードされる(すなわち、1 バイトのデータのみが一回で書き込まれる)ように、3 2 個の書き込みドライバーのうちの 8 つのみをオンにし、残り 2 4 個の書き込みドライバーを停止させるために使用され得る。所望なら、単一 B Y T E \_ E N は、書き込みドライバー回路網 3 8 の任意の適切なサブセットを選択するために使用され得る。

#### 【 0 0 2 4 】

書き込みドライバー回路網 3 8 および W L ドライバー回路網 3 2 は、制御回路(例えば、制御回路網 3 0)によって制御され得る。例えば、制御回路 3 0 は、読み取り / 書き込み動作の間、回路網 3 2 をオンにするために、バス 3 1 をわたってワードラインエネーブル信号 W L \_ E N を W L ドライバー回路 3 2 に提供し得る。制御回路 3 0 はまた、書き込み動作の間、書き込みドライバー回路網 3 8 をオンにするために、バス 3 7 をわたって書き込みエネーブル信号 W D \_ E N を、および読み取り動作の間、感知増幅器回路網 4 0 をオンにするためにバス 3 9 をわたって読み取りエネーブル信号 S A \_ E N を提供し得る。

#### 【 0 0 2 5 】

感知増幅器回路網 4 0 は、多重器 5 2 を介して、第 1 のメモリポートに関連付けられた

10

20

30

40

50

第1の出力ラッチ54-Aと、第2のメモリポートに関連付けられた第2の出力ラッチ54-Bとに連結され得る。多重器52は、2つの出力ラッチ54-Aおよび54-Bのうちの選択された1つに読み取り信号をルーティングせしめるように構成され得る。出力ラッチ54-Aはまた、(例として)第1のポートに対する読み出しの間、ラッチ54-Aが感知増幅器回路網40からの32個の出力データ信号から8バイトを選択的に取り込むことを可能にするエネーブル信号A\_OUTENを受信し得る。同様に、出力ラッチ54-Bは、第2のポートに対する読み出しの間、ラッチ54-Bが感知増幅器回路網40から全部の出力データバイトのサブセットを選択的に取り込むことを可能にする信号B\_OUTENを受信し得る。信号A\_OUTENおよびB\_OUTENは、信号BTYEEによって可能にされた行に対応する同じバイトを可能にし得る。概して、出力ラッチ54-Aおよび54-Bは、感知増幅器回路網40から出力バイトの任意の所望の部分を取り込むように構成され得る。

10

#### 【0026】

書き込みドライバー回路網38は、多重器50の出力から書き込みデータを受信し得る。多重器50は、第1のメモリポートに関連付けられた書き込みデータADINを受信する第1の入力と、第2のメモリポートに関連付けられた書き込みデータBDINを受信する第2の入力を有し得る。多重器50は、信号ADINおよびBDINのうちの1つを書き込みドライバー回路の入力にルーティングせしめるように構成され得る。図1に示されるように、アドレス信号A\_ADDRおよびB\_ADDR、エネーブル信号A\_BEおよびB\_BE、入力データ信号ADINおよびBDIN、並びに他の制御信号は、データレジスタおよび論理回路網72を用いて提供され得る。回路網72は、第1のメモリポートに関連付けられた第1のクロック信号ACLKと、第2のメモリポートに関連付けられた第2のクロック信号BCLKとを受信し得る。メモリ回路網が、第1および第2のポートから読み取りおよび書き込み要求を渡すことが可能であるので、メモリ回路網は、データレジスタおよび論理回路網72の参照ポイントからのデュアルポートメモリとして見え、第1および第2のポートの各々が、異なる信号ACLKおよび/またはBCLKを用いて制御される。

20

#### 【0027】

回路網72は、第1のポートに関連付けられた第1の書き込み要求信号AWREQおよび第1の読み取り要求信号ARREQが生成される第1の対の出力と、第2のポートに関連付けられた第2の書き込み要求信号BWRQおよび第2の読み取り要求信号BRREQが生成される第2の対の出力を有し得る。信号AWREQおよびARREQは、第1の要求生成器60-Aを用いて受信され得、その一方で、信号BWRQおよびBRREQは、第2の要求生成器60-Bを用いて受信され得る。第1および第2の要求生成器は各々、未処理の満たされていない要求の存在を高くラッチし、メモリ要求のないことを低くラッチするラッシング回路62を含み得る。

30

#### 【0028】

要求生成器は、読み取りまたは書き込み要求を受信することに応じてその出力においてパルスを生成するように構成され得る。例えば、要求生成器60-Aが、書き込み要求を受信する場合に、信号ARREQは、所定の時間期間に対して高くパルス化される。別の例として、要求生成器60-Bが、読み取り要求を受信する場合に、信号BREQは、所定の時間期間に対して高くパルス化される。

40

#### 【0029】

信号ARREQおよびBREQは、仲裁回路(例えば、仲裁回路64)を用いて受信され得る。仲裁回路64はまた、(点線に示されるように)データレジスタおよび論理回路網72から直接に読み取り要求信号ARREQおよびBREQを受信し得る。仲裁回路64は、第1および第2のポートからの要求を処理する順番を決定するために機能し得る。仲裁回路64は、出力バス70をわたってポート選択信号PORT\_SELを出力し得る。信号PORT\_SELは、選択されたポートに関連付けられた回路網をメモリアレイ22に対してルーティングせしめるために、バス70をわたって、多重器46、48

50

、50および52の制御入力を与えられ得る。例えば、低いPORT\_SELは、第1のポートからの要求が、現在、処理のために選択されていることを示し得、その一方で、高いPORT\_SELは、第2のポートからの要求が、現在、処理のために選択されていることを示し得る。仲裁回路64が、要求を実行することを決定する場合に、回路64は、所望の読み取り／書き込み動作を始動させるために、出力信号STARTを制御回路30に指示するように一時的にアサートする。

#### 【0030】

現在のメモリ要求が満たされた場合（すなわち、所望のメモリ位置においてメモリアレイ22内に読み取り／書き込み動作を完了した際に）、仲裁回路64は、制御回路30からアサートされた信号ENDを受信し得る。信号ENDは、論理ANDゲート66を介して戻るように要求生成器60-Aに連結され得、論理ANDゲート68を介して戻るように要求生成器60-Bに連結され得る。特に、論理ANDゲート66は、信号ENDを受信する第1の入力と、信号PORT\_SELを受信する第2の反転入力と、信号A-ENDが提供される生成器60-Aに連結された出力とを有し得る。論理ANDゲート68は、信号ENDを受信する第1の入力と、信号PORT\_SELを受信する第2の反転入力と、信号B-ENDが提供される生成器60-Bに連結された出力とを有し得る。要求生成器60-Aのラッチ62は、高いA-ENDを受信することに応じて消去され得、その一方で、要求生成器60-Bのラッチ62は、高いB-ENDを受信することに応じて消去され得る。

#### 【0031】

図1に関連して説明されたメモリ構造は、単なる例示に過ぎず、本発明の範囲を限定するように意図されていない。所望なら、仲裁回路64は、3ポートメモリモード、4ポートメモリモード等をサポートするために、任意の所望の数のポートからのメモリ要求を扱うように構成され得る。

#### 【0032】

図2は、4：1行多重化（すなわち、4行に1行が、書き込みの間、共用の差動書き込みドライバー34'によって駆動され、その一方で、4行に1行が、読み取りの間、共用の差動感知増幅器40'に連結される）を例示するダイヤグラムである。図2に示されるように、各行は、1対のビットライン82-1および82-2に連結された複数のメモリポートを含み得る。例えば、メモリセル100は、1対の交差連結されたインバータ102および104から形成された双安定要素を含み得る。インバータ104は、セル100に対して、第1のデータストレージノードとして機能する出力を有し得、その一方で、インバータ102は、セル100に対して第2のデータストレージノードとして機能する出力を有し得る。第1のアクセストランジスタ106は、第1のデータストレージノードと第1のビットライン82-1との間に連結され得、その一方で、第2のアクセストランジスタ108は、第2のデータストレージノードと第1のビットライン82-2との間に連結され得る。アクセストランジスタ106および108（ときには、アドレストランジスタと呼ばれる）は、ワードライン80をわたって提供されたワードライン信号WLによって制御され得る。この例において、信号WLは、メモリセル100のうちの1列を選択するようにアサートされ得、隣接するセルの4つに1つからの外側の1つは、データローディング動作の間に関連付けられた書き込みドライバー34'、またはデータ感知する動作の間に関連付けられた感知増幅器に連結され得る。

#### 【0033】

図2のメモリセルは、単なる例示に過ぎず、本発明の範囲を限定するように意図されていない。所望なら、メモリセル10は、单一端部の単一ポートメモリセルであり得、2つより多い交差連結された反転回路を含み得、または任意の適切な単一ポートメモリ構成を用いて実装され得る。

#### 【0034】

図3は、要求生成器60（すなわち、要求生成器60-Aまたは60-B）の回路ダイヤグラムである。図3に示されるように、要求生成器60は、書き込み要求信号WREQ

10

20

30

40

50

が受信され得る第1の入力と、読み取り要求信号RREQが受信され得る第2の入力と、信号ENDが受信され得る第3の出力とを有し得る。要求生成器60は、生成器60に対して第1および第2の入力として機能する第1および第2の入力を有する（すなわち、生成器110の第1の入力がWREQを受信し得、その一方で、生成器110の第2の入力がRREQを受信し得る）論理ORゲート110を含み得る。論理ゲート110は、1ショットパルス生成器112に連結されている出力を有し得る。1ショットパルス生成器112は、信号WREQおよび/またはRREQの立ち上りエッジを検出することに応じて所与のパルス幅を有するパルスを生成するように構成され得る。

#### 【0035】

生成器112によって生成されたパルスは、インバータ114を介してラッピング回路62の第1の入力に与えられ得る。回路62は、（例として）交差連結された論理NANDゲート116および118を含む設定・再設定（SR）ラッチであり得る。所与のパルス幅は、ラッチ62の状態を設定または再設定するように十分の時間を提供するために、十分に広くあり得る。ラッピング回路62は、インバータ119を介して信号ENDを受信するように構成された第2の入力と、信号REQが提供される出力を有し得る。1ショットパルス生成器112がSRラッチ62の「設定」入力に連結されているので、信号REQは、信号WERQおよび/またはRREQの立ち上りエッジを検出することに応じて高く上げられる（すなわち、ラッチ62は、高い状態に置かれる）。信号ENDがSRラッチ62の「再設定」入力にルーティングされるので、ラッチ62は、アサートされた信号ENDを検出することに応じて低い状態に置かれ得る（すなわち、信号REQは、強制的に低くされる）。

#### 【0036】

仲裁回路64は、同期モードまたは非同期モードで動作可能であり得る。同期モードにおいて、複数のポートからの要求は、单一クロックソースを用いて制御され得る。結果として、複数のポートからのメモリアクセス要求は、单一クロック信号の立ち上りエッジにおいて同時に到達し得る。同期モードの仲裁回路64は、例えば、複数のポートのうちのどれが図4の表に基づいて選択されるべきであるかを決定し得る。

#### 【0037】

2つのポートのうちの1つのみに未処理の要求があるシナリオにおいて、未処理の要求に関連付けられたポートは、処理のために選択され得る（例えば、列120を参照）。1つのポートが書き込み要求を受信し、およびもう1つのポートが読み取り要求を受信するシナリオにおいて、読み取り要求を受信するポートは、処理のために選択され得る（すなわち、列122に示されるように、仲裁回路64は、読み取りポートの優先度を実装するように構成され得る）。所望なら、仲裁回路64はまた、書き込みポート優先度を実装するように構成され得る（すなわち、書き込み要求を受信するポートは、処理のために選択され得る）。両方のポートが書き込み要求を受信し、または両方のポートが読み取り要求を受信するシナリオにおいて、列124に例示されるように、第2のポートBは、所与の優先度を有し得る（すなわち、ポートBでの要求は、ポートAでの要求の前に処理される）。所望なら、仲裁回路64はまた、両方のポートが同じタイプのメモリ要求を受信したときに、ポートAが優先であることを実装するように構成され得る（すなわち、ポートAおよびBの両方が読み取り要求を受信する場合、またはポートAおよびBの両方が書き込み要求を受信する場合、ポートAでの要求は、ポートBでの要求の前に処理される）。

#### 【0038】

図5は、図4の表に関連して説明されるポート選択能力を提供するように構成された仲裁回路64の回路ダイヤグラムである。図5に示されるように、仲裁回路64は、論理NANDゲート132および134、並びに論理NORゲート136および140を含み得る。論理NANDゲート132は、要求生成器60-Aから信号A\_REQを受信する第1の入力と、要求生成器60-Bから信号B\_REQを受信する第2の入力と、インバータ130を介して制御回路30から信号ENDを受信する第3の入力とを有し得る。論理NANDゲート134は、信号A\_REQを受信する第1の入力と、データレジスタおよ

10

20

30

40

50

び論理回路網 7 2 から信号 A\_R R E Q を受信する第 2 の入力と、出力とを有し得る。論理 N O R ゲート 1 3 6 は、ゲート 1 3 4 の出力に連結されている第 1 の入力と、データレジスタおよび論理回路網 7 2 から信号 B\_R R E Q を受信する第 2 の入力と、出力とを有し得る。論理 N O R ゲート 1 4 0 は、ゲート 1 3 6 の出力に連結されている第 1 の入力と、インバータ 1 3 8 を介して要求生成器 6 0 - B から信号 B\_R E Q を受信する第 2 の入力と、信号 P O R T\_S E L が生成される出力とを有し得る。図 5 の例示的な回路ダイヤグラムは、単なる例示に過ぎず、本発明の範囲を限定するように機能しない。仲裁回路 6 4 は、所望のポート選択能力を提供するように構成された任意の適切な配列を用いて形成され得る。

## 【 0 0 3 9 】

10

図 6 は、同期モードにおいてメモリ回路網を動作させることにかかる代表的なステップのフローチャートである。ステップ 1 5 0 において、仲裁回路 6 4 は、未処理の要求の存在をチェックし得る。少なくとも 1 つの未処理の要求が検出される場合に、選択されたポートに関連付けられた要求が満たされる（すなわち、要求が、図 4 に関連して説明されたタイプの論理表に基づいて選択されたポートに関連付けられる）。

## 【 0 0 4 0 】

選択された要求を満たすことにおいて、仲裁回路 6 4 は、メモリアレイ 2 2 のアクセスを始動させるように制御回路 3 0 に指示するために、信号 S T A R T をアサートし得る（ステップ 1 5 4）。ステップ 1 5 6 において、信号 P O R T\_S E L は、仲裁回路 6 4 の論理に基づいて所望の値に設定され得る。ステップ 1 5 8 は、選択されたポートに関連付けられた読み取りまたは書き込み動作は、所望のメモリアドレスにおいて実行され得る。

20

## 【 0 0 4 1 】

メモリアクセスが完了した際に、制御回路 3 0 は、現在の要求の完了を信号で送るために、選択されたポートに関連付けられた要求生成器を消去するように信号 E N D を高くパルス化し得る（ステップ 1 6 0）。バス 1 6 2 に示されるように、処理は、連続的な要求を処理するために、ステップ 1 5 0 に戻るようにループし得る。このときに、選択されていないポートに関連付けられた以前に未処理の要求（すなわち、選択されたポートに関連付けられた要求と平行して受信された要求）は、（存在する場合）、選択されたポートからの別の要求を処理する前に処理され得る。未処理の要求が存在しない場合に、仲裁回路 6 4 は、新しく到着するメモリ要求を待ち、かつその入力を監視し得る（ステップ 1 5 0）。

30

## 【 0 0 4 2 】

本発明の別の実施形態において、仲裁回路 6 4 は、非同期モードで（例えば、複数のポートからの要求が異なる位相および／または周波数のクロックを用いて制御されるモードにおいて）動作するように構成され得る。非同期デュアルポート動作において、異なるメモリポートからの要求は、しばしば、異なる時間に到達し得る。結果として、仲裁回路 6 4 は、第 1 の到達するメモリ要求が回路 6 4 によって受信されるとすぐに処理されることと、第 1 の到達メモリ要求が満たされたときに第 2 の（後に）到達するメモリ要求が処理されることとを行うように構成され得る。

## 【 0 0 4 3 】

40

図 7 は、非同期モードで動作可能な仲裁回路 6 4 の 1 つの適切な配列の例示的な回路ダイヤグラムである。図 7 に示されるように、仲裁回路 6 4 は、それぞれ、複数の入力および 1 つの出力を有する論理 N A N D ゲート 1 7 2、1 7 4、1 7 6、1 7 8、および 1 8 0 を含み得る。論理 N A N D ゲート 1 7 6 は、要求生成器 6 0 - A から信号 A\_R E Q を受信する第 1 の入力と、ゲート 1 7 2 の出力に連結されている第 2 の入力と、ゲート 1 7 8 の出力に連結されている第 3 の入力とを有し得、その出力において信号 n A\_G R A N T を生成し得る。論理 N A N D ゲート 1 7 8 は、要求生成器 6 0 - B から信号 B\_R E Q を受信する第 1 の入力と、ゲート 1 7 4 の出力に連結されている第 2 の入力と、ゲート 1 7 6 の出力に連結されている第 3 の入力とを有し得、その出力において信号 n B\_G R A N T を生成し得る。信号 n A\_G R A N T は、生成器 6 0 - A からの要求が選択される場

50

合に強制的に低くされ得、その一方で、信号 n B\_G R A N T は、生成器 6 0 - B からの要求が選択される場合に強制的に低くされ得る。

#### 【 0 0 4 4 】

仲裁回路 6 4 はまた、ゲート 1 7 8 の出力に連結された入力と、信号 P O R T \_ S E L が提供される出力を有するインバータ 1 8 2 を含み得る。論理 N A N D ゲート 1 8 0 は、ゲート 1 7 6 の出力に連結された第 1 の入力と、ゲート 1 7 8 の出力に連結された第 2 の入力を有し得、その出力において信号 S T A R T を生成し得る。論理 N A N D ゲート 1 7 2 は、インバータ 1 8 2 の出力に連結された第 1 の入力と、制御回路 3 0 から信号 E N D を受信する第 2 の入力を有し得、その一方で、論理 N A N D ゲート 1 7 4 は、別のインバータ 1 7 0 を介してインバータ 1 8 2 の出力に連結されている第 1 の入力と、信号 E N D を受信する第 2 の入力を有し得る。10

#### 【 0 0 4 5 】

このように交差連結された N A N D ゲート 1 7 6 および 1 7 8 は、仲裁回路 6 4 に対してラッチングおよびゲーティング能力を提供するように機能し得る。例えば、ゲート 1 7 6 および 1 7 8 は、信号 n A\_G R A N T および n B\_G R A N T のうちの 1 つのみをアサートし、信号 E N D の立ち上りエッジが検出される場合にのみ P O R T \_ S E L をトグルする。図 7 の例示的な回路ダイヤグラムは、単なる例示に過ぎず、本発明の範囲を限定するように機能しない。

#### 【 0 0 4 6 】

図 8 は、非同期モードで図 1 のメモリ回路網を動作させるための例示的なステップのフローチャートである。ステップ 2 0 0 において、仲裁回路 6 4 は、要求生成器 6 0 - A (ポート A) および 6 0 - B (ポート B) から要求を待ち得る。ポート A での要求が、ポート B での要求を検出する前に検出される場合に、ポート A からの要求が満たされ得る (ステップ 2 0 2)。ポート B での要求が、ポート A での要求を検出する前に検出される場合に、ポート B からの要求が満たされ得る (ステップ 2 1 6)。20

#### 【 0 0 4 7 】

ステップ 2 0 2 において、信号 S T A R T が、高く上げられ得、信号 P O R T \_ S E L が、「0」に設定され得、所望の読み取り / 書き込み動作が、特定のアドレス位置において実行され得る。ステップ 2 1 0 において、信号 E N D は、要求生成器 6 0 - A を消去し、および現在のメモリアクセスの完了を表すために信号 S T A R T を低くするように高くパルス化され得る。未処理の要求がない場合には、バス 2 1 2 によって示されるように、処理は、ステップ 2 0 0 に戻るようにループされ得る。ポート B において未処理の要求 (すなわち、ステップ 2 0 2 が実行されている間に受信されている未処理の要求) が検出される場合には、バス 2 1 4 に示されるように、処理は、ステップ 2 1 6 に戻るようにループされ得る。30

#### 【 0 0 4 8 】

ステップ 2 1 6 において、ポート B からの要求が満たされ得る。例えば、信号 S T A R T が、高く上げられ得、信号 P O R T \_ S E L が、「1」に設定され得、所望の読み取り / 書き込み動作が、特定のアドレス位置において実行され得る。ステップ 2 2 4 において、信号 E N D は、要求生成器 6 0 - B を消去し、および現在のメモリアクセスの完了を表すために信号 S T A R T を低くするように高くパルス化され得る。未処理の要求がない場合には、バス 2 2 6 によって示されるように、処理は、ステップ 2 0 0 に戻るようにループされ得る。ポート A において未処理の要求 (すなわち、ステップ 2 1 6 が実行されている間に受信されている未処理の要求) が検出される場合には、バス 2 2 8 に示されるように、処理は、ステップ 2 0 2 に戻るようにループされ得る。40

#### 【 0 0 4 9 】

概して、ポート A および B からのメモリ要求が同時に到達するような場合に、2つの要求のうちのランダムの 1 つが、処理のために選択される。ポート A および B からの同時に到達するメモリ要求が満たされる順番に関わらず、仲裁回路 6 4 は、両方の要求されたメモリが確実に実行されるようにする。50

**【 0 0 5 0 】**

図9は、非同期モードにおける仲裁回路64の動作を示すタイミングダイヤグラムである。図9に示されるように、ポートAクロック信号A\_CLKおよびポートBクロック信号B\_CLKは、異なるクロック周波数および位相を有し得る。時間t1において、信号A\_REQが高く上げられ、その一方で、B\_REQは低いままである（すなわち、ポートAからの単一の要求が受信される）。A\_REQの立ち上りに応じて、信号STARTが強制的に高くされ得、信号nA\_GRANTが強制的に低くされ得る。時間t2において、信号ENDは、ポートAの要求の完了を表すために（生成器60-A内のラッチ62を消去するために）一時的に高くパルス化され得、A\_REQおよびSTARTが強制的に低くさせられ、nA\_GRANTが強制的に高くさせられる。

10

**【 0 0 5 1 】**

時間t3において、信号B\_REQが高く上げられ、その一方で、A\_REQは低いままである（すなわち、ポートBからの単一の要求が受信される）。B\_REQの立ち上りに応じて、信号PORT\_SELが強制的に高くされ得、信号STARTが強制的に高くされ得、信号nB\_GRANTが強制的に低くされ得る。時間t4において、信号ENDは、ポートBの要求の完了を表すために（生成器60-B内のラッチ62を消去するために）一時的に高くパルス化され得、B\_REQ、START、およびPORT\_SELが強制的に低くさせられ、nB\_GRANTが強制的に高くさせられる。それ故に、時間t1～t4は、仲裁回路64は、2つの異なるポートから第1および第2の要求を受信し、第1の要求が満たされた後に第2の要求が受信されるシナリオを示す。

20

**【 0 0 5 2 】**

時間t5からt9までに例示されるように、仲裁回路64は、ポートAからのメモリ要求を処理している間に、ポートBからメモリ要求を受信することも可能である。時間t5において、信号A\_REQが高く上げられ、その一方で、B\_REQは低いままである。A\_REQの立ち上りに応じて、信号STARTが強制的に高くされ得、信号nA\_GRANTが強制的に低くされ得る。時間t6において、信号B\_REQが高く上げられ、その一方で、A\_REQは依然高い（すなわち、ポートAに関連付けられたアクセスが完了する前に、要求がポートBにおいて受信された）。ポートAからの要求が未だ、完了されていないので、B\_REQにおけるこの変化は、制御信号（すなわち、信号nA\_GRANT、nB\_GRANT、START、PORT\_SEL、およびEND）に影響しない。

30

**【 0 0 5 3 】**

時間t6の直後（時間t7）において、信号ENDは、ポートAの要求の完了を表すために高くパルス化され得、信号A\_REQおよびSTARTが強制的に低くさせられ、nA\_GRANTが強制的に高くさせられる。B\_REQが依然高いので、仲裁回路64は、（時間t8において）信号PORT\_SELを高く、信号STARTを高く、信号nB\_GRANTを強制的に低くすることによってポートBからのこの未処理の要求を直ちに実行する。時間t9において、信号ENDは、ポートBの要求の完了を表すために一時的に高くパルス化され得、B\_REQ、START、およびPORT\_SELが強制的に低くさせられ、nB\_GRANTが強制的に高くさせられる。それ故に、時間t5～t9は、仲裁回路64は、2つの異なるポートから第1および第2の要求を受信し、第1の要求が満たされる前に第2の要求が受信されるシナリオを示す。

40

**【 0 0 5 4 】**

時間t10からt14までに例示されるように、仲裁回路64は、ポートBからのメモリ要求を処理している間に、ポートAからメモリ要求を受信することも可能である。時間t10において、信号B\_REQが高く上げられ、その一方で、A\_REQは低いままである。B\_REQの立ち上りに応じて、信号PORT\_SELが強制的に高くされ得、信号STARTが強制的に高くされ得、信号nB\_GRANTが強制的に低くされ得る。時間t11において、信号A\_REQが高く上げられ、その一方で、B\_REQは依然高い（すなわち、ポートBに関連付けられたアクセスが完了する前に、要求がポートAにおい

50

て受信された）。ポートBからの要求が未だ、完了されていないので、A\_REQにおけるこの変化は、制御信号n A\_GRANT、n B\_GRANT、START、PORT\_SEL、およびENDに影響しない。

#### 【0055】

時間t11の直後（時間t12）において、信号ENDは、ポートBの要求の完了を表すために高くパルス化され得、信号B\_REQ、START、およびPORT\_SELが強制的に低くさせられ、n B\_GRANTが強制的に高くさせられる。A\_REQが依然高いので、仲裁回路64は、（時間t13において）信号STARTを高く、信号n A\_GRANTを強制的に低くすることによってポートAからのこの未処理の要求を直ちに実行する。時間t14において、信号ENDは、ポートAの要求の完了を表すために一時的に高くパルス化され得、A\_REQおよびSTARTが強制的に低くさせられ、n A\_GRANTが強制的に高くさせられる。10

#### 【0056】

図1～9に関連して説明されたメモリ回路網のデュアル機能は、単なる例示に過ぎず、本発明の範囲を限定するように意図されていない。仲裁回路64は、ユーザーによって望まれるような同期モードまたは非同期モードで動作するように構成され得る（仲裁回路64は、現在のカスタム化可能な用途に依存して、同期モードと非同期モードとの間で切り替え得る）。所望なら、本明細書において説明された実施形態は、他のタイプのメモリセルに適用され得、同期および非同期モードで多重ポートメモリ動作をサポートするように構成され得る。20

#### 【0057】

##### （追加の実施形態）

###### （実施形態1）

第1および第2のポートを有するデュアルポートメモリであって、該デュアルポートメモリは、

单一ポートメモリ要素のアレイと、

該アレイに連結されており、かつ該アレイからデータを読み取り、該アレイにデータを書き込むように動作可能である制御回路と、

該第1のポートから第1のメモリアクセス要求を受信するように動作可能な第1の要求生成器と。30

該第2のポートから第2のメモリアクセス要求を受信するように動作可能な第2の要求生成器と、

該制御回路、並びに該第1および第2の要求生成器に連結されている仲裁回路とを含み、

該仲裁回路は、同期モードで動作可能であり、該同期モードにおいて、該第1および第2の要求生成器は、等しい周波数を有する少なくとも2つのクロック信号を用いて制御され、該少なくとも2つのクロック信号の各クロックサイクルの間に、該第1および第2のメモリアクセス要求のうちの1つのみを満たすために、該制御回路に指示するように動作可能である、デュアルポートメモリ。40

#### 【0058】

###### （実施形態2）

上記第1および第2の要求生成器のうちの少なくとも1つは、パルス生成器およびラッチング回路を含み、該パルス生成器は、メモリアクセス要求を受信することに応じて、パルスを生成するように動作可能であり、該ラッチング回路は、該メモリアクセス要求が未だ実行されていない場合に、第1の論理値を格納するように動作可能であり、該メモリアクセス要求が上記制御回路を用いて実行された場合に、該第1の論理値とは異なる第2の論理値を格納するように動作可能である、実施形態1に記載のデュアルポートメモリ。

#### 【0059】

###### （実施形態3）

上記仲裁回路は、所定の論理表に基づく満足に対して、上記第1および第2のメモリア50

クセス要求のうちの 1 つのみを選択するように動作可能である、実施形態 1 に記載のデュアルポートメモリ。

【 0 0 6 0 】

( 実施形態 4 )

上記仲裁回路は、上記第 1 の要求生成器から第 1 の出力信号を受信するように動作可能である第 1 の入力と、上記第 2 の要求生成器から第 2 の出力信号を受信するように動作可能である第 2 の入力と、上記制御回路から制御信号を受信するように動作可能である第 3 の入力と、出力信号が提供される出力とを有する論理ゲートを含み、該出力信号は、該制御回路が上記アレイにアクセスしている間にアサートされる、実施形態 1 に記載のデュアルポートメモリ。

10

【 0 0 6 1 】

( 実施形態 5 )

上記仲裁回路は、上記第 2 の要求生成器に連結されている第 1 の入力と、上記第 1 の要求生成器および該第 2 の要求生成器に連結されている第 2 の入力と、出力信号が提供される出力とを有する論理ゲートを含み、該出力信号は、上記第 1 のメモリアクセス要求を満たす場合に、第 1 の論理値を有し、上記第 2 のメモリアクセス要求を満たす場合に、該第 1 の論理値とは異なる第 2 の論理値を有する、実施形態 1 に記載のデュアルポートメモリ。

【 0 0 6 2 】

( 実施形態 6 )

20

上記仲裁回路は、非同期モードにおいてさらに動作可能であり、該非同期モードにおいて、上記第 1 および第 2 の要求生成器は、異なる周波数を有する少なくとも 2 つのクロック信号を用いて制御されている、実施形態 1 に記載のデュアルポートメモリ。

【 0 0 6 3 】

( 実施形態 7 )

上記第 1 および第 2 の要求生成器のうちの少なくとも 1 つは、パルス生成器およびラッチング回路を含み、該パルス生成器は、メモリアクセス要求を受信することに応じて、パルスを生成するように動作可能であり、該ラッチング回路は、該メモリアクセス要求が未だ実行されていない場合に、第 1 の論理値を格納するように動作可能であり、該メモリアクセス要求が上記制御回路を用いて実行された場合に、該第 1 の論理値とは異なる第 2 の論理値を格納するように動作可能である、実施形態 6 に記載のデュアルポートメモリ。

30

【 0 0 6 4 】

( 実施形態 8 )

上記仲裁回路は、上記同期モードで動作するとき、所定の論理表に基づく満足に対して、上記第 1 および第 2 のメモリアクセス要求のうちの 1 つのみを選択するように動作可能である、実施形態 6 に記載のデュアルポートメモリ。

【 0 0 6 5 】

( 実施形態 9 )

上記第 1 および第 2 のメモリアクセス要求は、異なる時間に到達し、上記仲裁回路は、上記非同期モードで動作するとき、満足に対して、該第 1 および第 2 のメモリアクセス要求のうちのより早く到達する 1 つを選択するように動作可能である、実施形態 6 に記載のデュアルポートメモリ。

40

【 0 0 6 6 】

( 実施形態 10 )

上記仲裁回路は、上記第 1 および第 2 のメモリアクセス要求のうちの選択された 1 つを満たすように上記制御回路に指示するために、出力信号をアサートし、該選択されたメモリアクセス要求の満足に応じて該出力信号をデアサートするように動作可能である、実施形態 6 に記載のデュアルポートメモリ。

【 0 0 6 7 】

( 実施形態 11 )

50

第1および第2のポートを有するデュアルポートメモリであって、該デュアルポートメモリは、

単一ポートメモリ要素のアレイと、

該アレイに連結されており、かつ該アレイからデータを読み取り、該アレイにデータを書き込むように動作可能である制御回路と、

該第1のポートから第1のメモリアクセス要求を受信するように動作可能な第1の要求生成器と、

該第2のポートから第2のメモリアクセス要求を受信するように動作可能な第2の要求生成器と、

該制御回路、並びに該第1および第2の要求生成器に連結されている仲裁回路と

を含み、

該仲裁回路は、非同期モードで動作可能であり、該非同期モードにおいて、該第1および第2の要求生成器は、異なるそれぞれの周波数を有する2つの異なるクロック信号を用いて制御される、デュアルポートメモリ。

#### 【0068】

(実施形態12)

上記第1および第2の要求生成器のうちの少なくとも1つは、パルス生成器およびラッチング回路を含み、該パルス生成器は、メモリアクセス要求を受信することに応じて、パルスを生成するように動作可能であり、該ラッチング回路は、該メモリアクセス要求が未だ実行されていない場合に、第1の論理値を格納するように動作可能であり、該メモリアクセス要求が上記制御回路を用いて実行された場合に、該第1の論理値とは異なる第2の論理値を格納するように動作可能である、実施形態11に記載のデュアルポートメモリ。

20

#### 【0069】

(実施形態13)

上記第1および第2の要求生成器を制御する上記2つの異なるクロック信号は、異なるそれぞれの位相を有する、実施形態11に記載のデュアルポートメモリ。

#### 【0070】

(実施形態14)

上記第1および第2のメモリアクセス要求は、異なる時間に到達し、上記仲裁回路は、上記非同期モードで動作する間、満足に対して、該第1および第2のメモリアクセス要求のうちのより早く到達する1つを選択するように動作可能である、実施形態11に記載のデュアルポートメモリ。

30

#### 【0071】

(実施形態15)

上記仲裁回路は、第1および第2の交差連結された論理ゲートを有するラッチング回路を含み、該第1の論理ゲートは、上記第1の要求生成器から第1の出力信号を受信するように動作可能であり、かつ第1の論理値を有する第1の制御信号を生成するように動作可能であり、該第2の論理ゲートは、上記第2の要求生成器から第2の出力信号を受信するように動作可能であり、かつ該第1の論理値とは異なる第2の論理値を有する第2の制御信号を生成するように動作可能である、実施形態11に記載のデュアルポートメモリ。

40

#### 【0072】

(実施形態16)

単一ポートメモリ要素のアレイと、第1および第2のポートとを含むデュアルポートメモリを使用するための方法であって、該方法は、

制御回路を用いて、該単一ポートメモリ要素のアレイにアクセスすることと、

第1の要求生成器を用いて、該第1のポートから第1のメモリアクセス要求を受信することと、

第2の要求生成器を用いて、該第2のポートから第2のメモリアクセス要求を受信することと、

仲裁回路を用いて、出力信号をアサートすることによって、該第1および第2のメモリ

50

アクセス要求のうちの選択された 1 つを満たすように該制御回路に指示することと

を含む、方法。

【 0 0 7 3 】

( 実施形態 17 )

上記選択されたメモリアクセス要求の満足に応じて上記出力信号をアサートすること

をさらに含む、実施形態 16 に記載の方法。

【 0 0 7 4 】

( 実施形態 18 )

同期モードで上記デュアルポートメモリを動作させることをさらに含み、該同期モード

において、上記第 1 および第 2 の要求生成器は、等しい周波数を有する少なくとも 2 つの

クロック信号を用いて制御される、実施形態 16 に記載の方法。 10

【 0 0 7 5 】

( 実施形態 19 )

非同期モードで上記デュアルポートメモリを動作させることをさらに含み、該非同期モ

ードにおいて、上記第 1 および第 2 の要求生成器は、異なる周波数を有する少なくとも 2

つのクロック信号を用いて制御される、実施形態 16 に記載の方法。

【 0 0 7 6 】

( 実施形態 20 )

同期モードで上記デュアルポートメモリを動作させることと、非同期モードで該デュ

アルポートメモリを動作させることをさらに含み、該同期モードにおいて、上記第 1 および

第 2 の要求生成器は、等しい周波数を有する少なくとも 2 つのクロック信号を用いて制御

され、該非同期モードにおいて、該第 1 および第 2 の要求生成器は、異なる周波数を有す

る少なくとも 2 つのクロック信号を用いて制御される、実施形態 16 に記載の方法。 20

【 0 0 7 7 】

( 実施形態 21 )

上記制御回路を用いて、上記選択されたメモリアクセス要求の満足に応じて制御信号を

アサートすることと、

上記第 1 および第 2 の要求生成器を用いて該制御信号を受信することと

をさらに含む、実施形態 16 に記載の方法。

【 0 0 7 8 】

30

( 実施形態 22 )

上記第 1 および第 2 の要求生成器のうちの少なくとも 1 つは、パルス生成器およびラッ

チング回路を含み、上記方法は、

該パルス生成器を用いて、メモリアクセス要求が該第 1 および第 2 の要求生成器のうち

の該少なくとも 1 つに到達したことを検出することに応じてパルスを生成することと、

該ラッチング回路を用いて、該メモリアクセス要求が未だ満たされていない場合に、第

1 の論理値を格納し、該メモリアクセス要求が上記制御回路を用いて満たされた場合に、

該第 1 の論理値とは異なる第 2 の論理値を格納することと

をさらに含む、実施形態 16 に記載の方法。

【 0 0 7 9 】

40

上記の内容は、単なる本発明の原理の例示に過ぎず、さまざまな改変が、本発明の範囲

および精神から逸脱することなしに、当業者によって加えられ得る。上記実施形態は、單

独も任意の組み合わせでも実装され得る。

【 四 1 】

【 図 2 】

FIG. 2

【図3】

FIG. 3

【 図 4 】

|     | ポート A | ポート B | ポート選択 |

|-----|-------|-------|-------|

| 120 | —     | R     | B     |

|     | —     | W     | B     |

|     | R     | —     | A     |

|     | W     | —     | A     |

| 122 | W     | R     | B     |

|     | R     | W     | A     |

|     | W     | W     | B     |

| 124 | R     | R     | B     |

FIG. 4

【図5】

FIG. 5

【図6】

FIG. 6

【図7】

FIG. 7

【 図 8 】

FIG. 8

【図9】

FIG. 9

---

フロントページの続き

(72)発明者 ユ ハイミン

アメリカ合衆国 カリフォルニア 94566, プレザントン, サン ルイス コート 57

24

(72)発明者 チョウ ハオ - ユアン ハワード

アメリカ合衆国 カリフォルニア 95132, サン ノゼ, ダルトリー ウェイ 1811

審査官 堀田 和義

(56)参考文献 特開2002-197864(JP,A)

特開平9-81449(JP,A)

特開2000-30460(JP,A)

特開平3-88196(JP,A)

特開2008-217297(JP,A)

米国特許第6078527(US,A)

特開2010-44821(JP,A)

(58)調査した分野(Int.Cl., DB名)

G11C 7/10

G11C 11/419

G06F 12/00