【公報種別】特許法第17条の2の規定による補正の掲載

【部門区分】第7部門第3区分

【発行日】平成23年10月6日(2011.10.6)

【公開番号】特開2011-142665(P2011-142665A)

【公開日】平成23年7月21日(2011.7.21)

【年通号数】公開・登録公報2011-029

【出願番号】特願2011-40461(P2011-40461)

【国際特許分類】

H 03 L 7/095 (2006.01)

H 03 L 7/081 (2006.01)

H 03 K 5/135 (2006.01)

【F I】

H 03 L 7/08 B

H 03 L 7/08 J

H 03 K 5/135

【手続補正書】

【提出日】平成23年8月23日(2011.8.23)

【手続補正1】

【補正対象書類名】明細書

【補正対象項目名】0006

【補正方法】変更

【補正の内容】

【0006】

図5を参照して説明すれば、従来技術に係るDLL回路1000は、外部クロックCLKをバッファリングして外部クロックCLKの立上りエッジ(又は、立下りエッジ)に同期したソースクロックiclkを生成するクロックバッファ100と、ソースクロックiclkを入力としてプログラム可能な多数の単位コース遅延(粗遅延)セルを含むコース遅延ライン110と、コース遅延ライン110から出力されたコース遅延クロックcd\_clkを入力としてプログラム可能な多数の単位ファイン遅延(微細遅延)セルを含むファイン遅延ライン120と、ファイン遅延ライン120から出力されたファイン遅延クロックfd\_clkを入力として実際のクロック信号経路の遅延分量をモデリングした遅延モデル130と、ソースクロックiclkと遅延モデル130から出力されたフィードバッククロックfb\_clkとの位相を比較するための第1位相比較器140と、第1位相比較器140から出力されたコース遅延制御用の位相比較信号pc\_out1によって、コース遅延ライン110の遅延量を制御するためのコース遅延制御部150と、コース遅延制御部150から出力されたコース遅延調整終了信号cd\_endに応答して、ソースクロックiclkとフィードバッククロックfb\_clkとの位相を比較するための第2位相比較器160と、第2位相比較器160から出力されたファイン遅延制御用の位相比較信号pc\_out2によって、ファイン遅延ライン120の遅延量を制御するためのファイン遅延制御部170と、ファイン遅延ライン120から出力されたファイン遅延クロックfd\_clkを入力としてDLLクロックdli\_clkを生成するDLLドライバ180とを備えて構成されている。

【手続補正2】

【補正対象書類名】明細書

【補正対象項目名】0013

【補正方法】変更

【補正の内容】

【0013】

上記目的を達成するため、この発明によれば、外部クロックと内部遅延クロックの位相

関係を表すコース遅延制御用の位相比較信号に応じてコース遅延調整を行うコース遅延ライン及びコース遅延調整の終了後に外部クロックと内部遅延クロックの位相関係を表すファイン遅延制御用の位相比較信号に応じてファイン遅延調整を行うファイン遅延ラインを備えた階層的遅延ライン構造のディレイロックループブロックと、前記ディレイロックループブロックから出力される前記コース遅延制御用の位相比較信号及びコース遅延調整終了信号に応答して、コース遅延調整終了時点での比較対象クロックの位相状態を記憶するための位相状態記憶手段と、前記ディレイロックループブロックから出力される前記コース遅延制御用の位相比較信号、前記ファイン遅延制御用の位相比較信号、前記コース遅延調整終了信号及び前記位相状態記憶手段から出力される位相状態信号に応答して、ファイン遅延調整によって前記ファイン遅延制御用の位相比較信号の遷移時点を検出し、その時点にアサートされるディレイロック信号を生成するためのディレイロック状態検出手段とを備えてなる半導体素子を提供する。

【手続補正3】

【補正対象書類名】明細書

【補正対象項目名】0014

【補正方法】変更

【補正の内容】

【0014】

この発明は、階層的遅延ラインを備えたDLLにおいて、コース遅延調節動作を終了する時点での内部クロックと外部クロックとの位相がどのような関係にあるかを予め記憶しておき、ファイン遅延調節動作を行って内部クロックと外部クロックとの位相が既に記憶された以前の位相状態とは異なり、位相が同じになる時点を検出し、この時点にDLLがディレイロック状態になったことを示す内部信号をアサートするようとする。

【手続補正4】

【補正対象書類名】明細書

【補正対象項目名】0019

【補正方法】変更

【補正の内容】

【0019】

図1を参照すれば、この実施形態に係る半導体素子2000は、コース遅延ライン及びファイン遅延ラインを含む階層的遅延ライン構造のDLLブロック1000と、階層的遅延ライン構造のDLLブロック1000から出力されたコース遅延制御用の位相比較信号pc\_out1及びコース遅延調整終了信号cd\_endに応答して、コース遅延調整終了時点でのソースクロックiclkに対するフィードバッククロックfb\_clkの位相状態を記憶するための位相状態記憶部200と、DLLブロック1000から出力されたコース遅延制御用の位相比較信号pc\_out1、コース遅延調整終了信号cd\_end、ファイン遅延制御用の位相比較信号pc\_out2及び位相状態記憶部200から出力された位相状態信号lock\_selに応答して、ファイン遅延調整による前記位相比較信号pc\_out2の遷移時点を検出して、その時点にアサートされるディレイロック信号lock\_inを生成するためのディレイロック状態検出部300とを備えて構成される。

【手続補正5】

【補正対象書類名】明細書

【補正対象項目名】0027

【補正方法】変更

【補正の内容】

【0027】

図3aを参照すれば、コース遅延調整終了信号cd\_endが論理レベルハイにアサートされた時点、すなわち、コース遅延調整が完了した時点において、フィードバッククロックfb\_clkの立上りエッジがソースクロックiclkの立上りエッジより先行する位相を有する場合には、コース遅延制御用の位相比較信号pc\_out1は論理レベルハイHを呈し、この時位相

状態信号lock\_selは論理レベルローLを呈する。

【手続補正6】

【補正対象書類名】明細書

【補正対象項目名】0028

【補正方法】変更

【補正の内容】

【0028】

他方、図3bを参照すれば、コース遅延調整が完了した時点でフィードバッククロックfb\_clkの立上りエッジがソースクロックiclkの立上りエッジより遅れた位相を有する場合には、コース遅延制御用の位相比較信号pc\_out1は論理レベルローLを呈し、この時位相状態信号lock\_selは論理レベルハイHを呈する。

【手続補正7】

【補正対象書類名】明細書

【補正対象項目名】0032

【補正方法】変更

【補正の内容】

【0032】

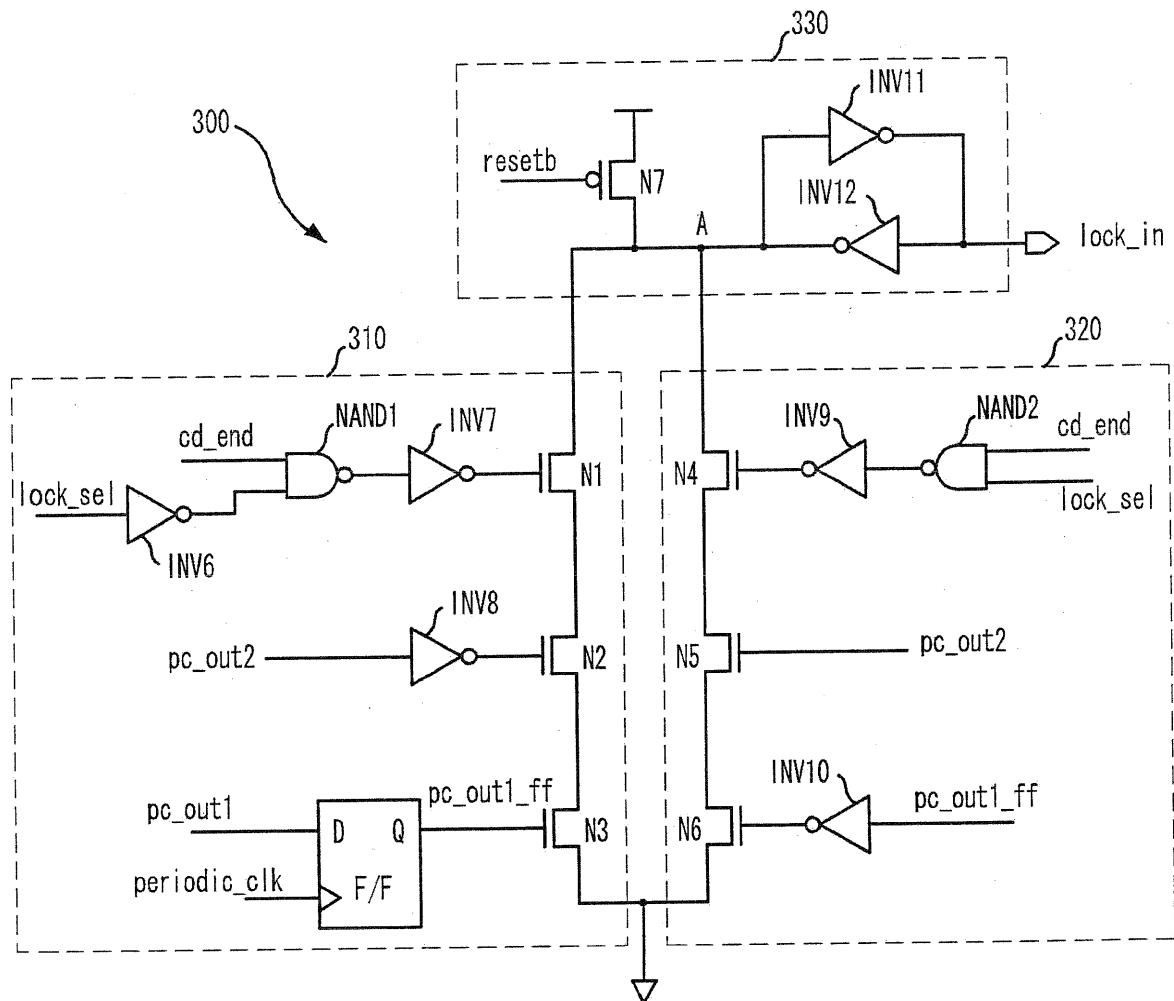

一方、第1遷移検出部310は、位相状態信号lock\_selを入力とするインバータINV6と、インバータINV6の出力信号及びコース遅延調整終了信号cd\_endを入力とするNANDゲートNAND1と、NANDゲートNAND1の出力信号を入力とするインバータINV7と、位相比較信号pc\_out2を入力とするインバータINV8と、周期クロックperiodic\_clkをクロック入力とし、位相比較信号pc\_out1をデータ入力とするフリップフロップFFと、共通出力ノードAと接地電圧端との間に直列に接続され、それぞれ、インバータINV7の出力信号、インバータINV8の出力信号、フリップフロップFFの出力信号pc\_out1\_ffをゲート入力とするNMOSトランジスタN1、N2、N3とを含んで構成されている。

【手続補正8】

【補正対象書類名】明細書

【補正対象項目名】0033

【補正方法】変更

【補正の内容】

【0033】

また、第2遷移検出部320は、位相状態信号lock\_sel及びコース遅延調整終了信号cd\_endを入力とするNANDゲートNAND2と、NANDゲートNAND2の出力信号を入力とするインバータINV9と、フリップフロップFFの出力信号pc\_out1\_ffを入力とするインバータINV10と、共通出力ノードAと接地電圧端との間に直列に接続され、それぞれ、インバータINV9の出力信号、位相比較信号pc\_out2、インバータINV10の出力信号をゲート入力とするNMOSトランジスタN4、N5、N6とを含んで構成されている。

【手続補正9】

【補正対象書類名】明細書

【補正対象項目名】0038

【補正方法】変更

【補正の内容】

【0038】

コース遅延調整終了信号cd\_endが論理レベルハイにアサートされた後には、階層的遅延ライン構造のDLLブロック1000で、ファイン遅延調整過程を行うことになる。コース遅延調整が完了した時点でフィードバッククロックfb\_clkの立上りエッジがソースクロックiclkの立上りエッジより先行した位相を有する場合は、図3aに示すように、コース遅延制御用の位相比較信号pc\_out1が論理レベルハイHを呈し、位相状態信号lock\_selは

論理レベルロー<sub>L</sub>を呈しており、そのとき同じくファイン遅延制御用の位相比較信号pc\_out2も論理レベルハイHを呈していて、位相状態信号lock\_selは論理レベルロー<sub>L</sub>を呈している訳であるから、ファイン遅延ラインに対する遅延調整によって、フィードバッククロックfb\_clkの位相を少しずつ後に押す過程を行うようになり、このような過程を繰り返して行っていけば、ある瞬間にはフィードバッククロックfb\_clkの立上りエッジがソースクロックiclkの立上りエッジより遅れる状態が生じるようになる。この時、ファイン遅延制御用の位相比較信号pc\_out2が論理レベルハイから論理レベルローに遷移され、ファイン遅延調整が完了する。一方、コース遅延調整が完了した時点でフィードバッククロックfb\_clkの立上りエッジがソースクロックiclkの立上りエッジより遅れた位相を有する場合は、図3bに示すように、コース遅延制御用の位相比較信号pc\_out1が論理レベルローを呈し、位相状態信号lock\_selは論理レベルハイHを呈しており、そのとき同じくファイン遅延制御用の位相比較信号pc\_out2も論理レベルロー<sub>L</sub>を呈していて、位相状態信号lock\_selは論理レベルハイHを呈している訳であるから、ファイン遅延ラインに対する遅延調整によって、フィードバッククロックfb\_clkの位相を少しずつ前に引く過程を行うようになり、このような過程を繰り返して行っていけば、ある瞬間にはフィードバッククロックfb\_clkの立上りエッジがソースクロックiclkの立上りエッジより先行する状態が生じるようになる。この時、ファイン遅延制御用の位相比較信号pc\_out2が論理レベルローからハイに遷移され、ファイン遅延調整が完了する。

【手続補正10】

【補正対象書類名】明細書

【補正対象項目名】0039

【補正方法】変更

【補正の内容】

【0039】

この発明では、このようにファイン遅延調整過程で用いられるファイン遅延制御用の位相比較信号pc\_out2の遷移時点を検出し、その時点をディレイロック状態として認識するようとする。

【手続補正11】

【補正対象書類名】明細書

【補正対象項目名】0040

【補正方法】変更

【補正の内容】

【0040】

前記図4に示されたディレイロック状態検出部300は、コース遅延調整過程が完了した時点に記憶された位相状態信号lock\_selを基準として、ファイン遅延調整過程でファイン遅延制御用の位相比較信号pc\_out2が遷移される時点を検出して、ディレイロック信号lock\_inを生成する回路である。

【手続補正12】

【補正対象書類名】明細書

【補正対象項目名】0045

【補正方法】変更

【補正の内容】

【0045】

ここで、コース遅延調整過程が完了した時点で、フィードバッククロックfb\_clkの立上りエッジがソースクロックiclkの立上りエッジより先行する位相を有する場合は、図3aに示すように、位相比較信号pc\_out1が論理レベルハイHであり、位相状態信号lock\_selが論理レベルロー<sub>L</sub>であるので、第1遷移検出部310のN MOSトランジスタN1がターンオンされる。また、周期クロックperiodic\_clk(例えば、8t<sub>CK</sub>ごとに論理レベルハイにアサートされるクロック)の立上りエッジが発生する時点ごとに、位相比較信号pc\_out1をラッチするフリップフロップF/Fの出力信号pc\_out1\_ffも論理レベルハイ状態に

なって、N M O SトランジスタN 3もまたターンオン状態となる。このような状態でファイン遅延調整過程を繰り返しながら、ファイン遅延制御用の位相比較信号pc\_out2が論理レベルローに遷移すれば、N M O SトランジスタN 2もターンオンされ、共通出力ノードAを放電させて、最終的な出力であるディレイロック信号lock\_inは、論理レベルハイにアサートされる。一方、このように第1遷移検出部3 1 0が動作する間、第2遷移検出部3 2 0のN M O SトランジスタN 4はターンオフ状態を維持するので、共通出力ノードAに影響を与えない。

【手続補正1 3】

【補正対象書類名】明細書

【補正対象項目名】0 0 4 6

【補正方法】変更

【補正の内容】

【0 0 4 6】

他方、コース遅延調整過程が完了した時点でフィードバッククロックfb\_clkの立上りエッジがソースクロックiclkの立上りエッジより遅い位相を有する場合は、図3 bに示すように、位相比較信号pc\_out1が論理レベルローであり、位相状態信号lock\_se1が論理レベルハイであるので、第2遷移検出部3 2 0のN M O SトランジスタN 4がターンオンされ、フリップフロップF / Fの出力信号pc\_out1\_ffも論理レベルロー状態になってN M O SトランジスタN 6もまたターンオン状態となる。このような状態でファイン遅延調整過程を繰り返しながら、ファイン遅延制御用の位相比較信号pc\_out2が論理レベルハイに遷移すれば、N M O SトランジスタN 5もターンオンされ、共通出力ノードAを放電させて、最終的な出力であるディレイロック信号lock\_inは、論理レベルハイにアサートされる。一方、このように第2遷移検出部3 2 0が動作する間、第1遷移検出部3 1 0のN M O SトランジスタN 1は、ターンオフ状態を維持するので、共通出力ノードAに影響を与えない。

【手続補正1 4】

【補正対象書類名】明細書

【補正対象項目名】0 0 4 7

【補正方法】変更

【補正の内容】

【0 0 4 7】

すなわち、第1遷移検出部3 1 0と第2遷移検出部3 2 0とは、コース遅延調整が完了した時点でのフィードバッククロックfb\_clkとソースクロックiclkとの位相関係に応じて、排他的に動作し、ファイン遅延調整過程で用いられるファイン遅延制御用の位相比較信号pc\_out2の遷移時点を検出する。

【手続補正1 5】

【補正対象書類名】特許請求の範囲

【補正対象項目名】全文

【補正方法】変更

【補正の内容】

【特許請求の範囲】

【請求項1】

外部クロックと内部遅延クロックの位相関係を表すコース遅延制御用の位相比較信号に応じてコース遅延調整を行うコース遅延ライン及びコース遅延調整の終了後に外部クロックと内部遅延クロックの位相関係を表すファイン遅延制御用の位相比較信号に応じてファイン遅延調整を行うファイン遅延ラインを有する階層的遅延ライン構造のディレイロックループロックと、

前記ディレイロックループロックから出力される前記コース遅延制御用の位相比較信号及びコース遅延調整終了信号に応答して、コース遅延調整終了時点での比較対象クロックの位相状態を記憶するための位相状態記憶手段と、

前記ディレイロックループブロックから出力される前記コース遅延制御用の位相比較信号、前記ファイン遅延制御用の位相比較信号、前記コース遅延調整終了信号及び前記位相状態の記憶手段から出力される位相状態信号に応答して、ファイン遅延調整によって前記ファイン遅延制御用の位相比較信号の遷移時点を検出し、その時点にアサートされるディレイロック信号を生成するためのディレイロック状態検出手段とを備えてなる半導体素子。

#### 【請求項 2】

請求項 1 に記載の半導体素子において、

前記位相状態記憶手段は、

前記コース遅延調整終了信号に応答して、前記コース遅延制御用の位相比較信号をスイッチングするためのスイッチング部と、

前記スイッチング部の出力信号をラッチするためのラッチ部とを含んでなることを特徴とする半導体素子。

#### 【請求項 3】

請求項 1 又は 2 に記載の半導体素子において、

前記ディレイロック状態検出手段は、

ファイン遅延調整過程で前記ファイン遅延制御用の位相比較信号が論理レベルハイからローに遷移される時点を検出するための第 1 遷移検出部と、

ファイン遅延調整過程で前記ファイン遅延制御用の位相比較信号が論理レベルローからハイに遷移される時点を検出するための第 2 遷移検出部と、

前記第 1 遷移検出部及び第 2 遷移検出部の共通出力ノードに接続されて、前記ディレイロック信号を出力する出力部とを含んでなることを特徴とする半導体素子。

#### 【請求項 4】

請求項 3 に記載の半導体素子において、

前記出力部は、

前記第 1 遷移検出部及び第 2 遷移検出部の共通出力ノードに係る信号をラッチするラッチ部と、

リセット信号に応答して、前記共通出力ノードを初期化するリセット部とを含んでなることを特徴とする半導体素子。

#### 【請求項 5】

請求項 4 に記載の半導体素子において、

前記第 1 遷移検出部及び第 2 遷移検出部は、それぞれ、

前記コース遅延調整終了信号及び前記位相状態信号により制御される第 1 スイッチング素子と、

現在の前記ファイン遅延制御用の位相比較信号により制御される第 2 スイッチング素子と、

ラッチされる以前の前記コース遅延制御用の位相比較信号により制御される第 3 スイッチング素子とを含んでなり、

前記第 1 スイッチング素子、第 2 スイッチング素子及び第 3 スイッチング素子は、前記第 1 遷移検出部及び第 2 遷移検出部の共通出力ノードと接地電圧端との間に直列に接続されている

ことを特徴とする半導体素子。

#### 【請求項 6】

請求項 4 に記載の半導体素子において、

前記第 1 遷移検出部は、

前記位相状態信号を入力とする第 1 インバータと、

前記インバータの出力信号及び前記コース遅延調整終了信号を入力とする第 1 N A N D ゲートと、

前記第 1 N A N D ゲートの出力信号を入力とする第 2 インバータと、

前記ファイン遅延制御用の位相比較信号を入力とする第3インバータと、

前記ディレイロックループブロックの比較動作周期ごとに前記コース遅延制御用の位相比較信号をラッチするためのフリップフロップと、

前記共通出力ノードと接地電圧端との間に直列に接続され、それぞれ、前記第2インバータの出力信号、前記第3インバータの出力信号、前記フリップフロップの出力信号をゲート入力とする第1N MOSトランジスタ、第2N MOSトランジスタ及び第3N MOSトランジスタとを含んでなる

ことを特徴とする半導体素子。

#### 【請求項7】

請求項6に記載の半導体素子において、

前記第2遷移検出部は、

前記位相状態信号及び前記コース遅延調整終了信号を入力とする第2NANDゲートと、

前記第2NANDゲートの出力信号を入力とする第4インバータと、

前記フリップフロップの出力信号を入力とする第5インバータと、

前記共通出力ノードと前記接地電圧端との間に直列に接続され、それぞれ、前記第4インバータの出力信号、前記ファイン遅延制御用の位相比較信号、前記第5インバータの出力信号をゲート入力とする第4N MOSトランジスタ、第5N MOSトランジスタ及び第6N MOSトランジスタとを含んでなる

ことを特徴とする半導体素子。

#### 【請求項8】

請求項2に記載の半導体素子において、

前記位相状態記憶手段の前記スイッチング部は、

前記コース遅延制御用の位相比較信号を入力とする第1インバータと、

前記コース遅延調整終了信号を入力とする第2インバータと、

前記コース遅延調整終了信号及び前記第2インバータの出力信号により制御されて、前記第1インバータの出力信号を選択的に前記ラッチ部に伝達するトランスマッピングゲートとを含んでなる

ことを特徴とする半導体素子。

#### 【請求項9】

請求項8に記載の半導体素子において、

前記位相状態記憶手段の前記ラッチ部は、

前記スイッチング部の出力信号を入力とするインバタラッチと、

前記インバタラッチの出力信号を入力として前記位相状態信号を出力する第3インバータとを含んでなる

ことを特徴とする半導体素子。

#### 【請求項10】

請求項4に記載の半導体素子において、

前記出力部の前記ラッチ部は、

前記第1遷移検出部及び第2遷移検出部の共通出力ノードに接続されたインバタラッチを含んでなる

ことを特徴とする半導体素子。

#### 【請求項11】

請求項4に記載の半導体素子において、

前記出力部の前記リセット部は、

前記リセット信号をゲート入力とし、電源電圧端と前記第1遷移検出部及び第2遷移検出部の共通出力ノードとの間に接続されたPMOSトランジスタを含んでなる

ことを特徴とする半導体素子。

#### 【手続補正16】

#### 【補正対象書類名】図面

【補正対象項目名】図 1

【補正方法】変更

【補正の内容】

【図 1】

【手続補正 1 7】

【補正対象書類名】図面

【補正対象項目名】図 4

【補正方法】変更

【補正の内容】

【図4】