(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7513743号**

**(P7513743)**

(45)発行日 令和6年7月9日(2024.7.9)

(24)登録日 令和6年7月1日(2024.7.1)

(51)国際特許分類

F I

|         |                  |         |        |

|---------|------------------|---------|--------|

| H 0 4 N | 19/593 (2014.01) | H 0 4 N | 19/593 |

| H 0 4 N | 19/426 (2014.01) | H 0 4 N | 19/426 |

| H 0 4 N | 19/96 (2014.01)  | H 0 4 N | 19/96  |

| H 0 4 N | 19/46 (2014.01)  | H 0 4 N | 19/46  |

請求項の数 7 (全46頁)

|                   |                             |

|-------------------|-----------------------------|

| (21)出願番号          | 特願2022-560453(P2022-560453) |

| (86)(22)出願日       | 令和4年1月18日(2022.1.18)        |

| (65)公表番号          | 特表2023-525213(P2023-525213) |

|                   | A)                          |

| (43)公表日           | 令和5年6月15日(2023.6.15)        |

| (86)国際出願番号        | PCT/US2022/012725           |

| (87)国際公開番号        | WO2022/220898               |

| (87)国際公開日         | 令和4年10月20日(2022.10.20)      |

| 審査請求日             | 令和4年10月4日(2022.10.4)        |

| (31)優先権主張番号       | 63/175,929                  |

| (32)優先日           | 令和3年4月16日(2021.4.16)        |

| (33)優先権主張国・地域又は機関 | 米国(US)                      |

| (31)優先権主張番号       | 17/569,681                  |

| (32)優先日           | 令和4年1月6日(2022.1.6)          |

最終頁に続く

|          |                         |

|----------|-------------------------|

| (73)特許権者 | 520353802               |

|          | テンセント・アメリカ・エルエルシー       |

|          | アメリカ合衆国 9 4 3 0 6 カリフォル |

|          | ニア州 パロアルト パーク・ブルヴァ      |

|          | ード 2 7 4 7              |

| (74)代理人  | 100107766               |

|          | 弁理士 伊東 忠重               |

| (74)代理人  | 100070150               |

|          | 弁理士 伊東 忠彦               |

| (74)代理人  | 100135079               |

|          | 弁理士 宮崎 修                |

| (72)発明者  | ジャオ , リアン               |

|          | アメリカ合衆国 9 4 0 8 5 カリフォル |

|          | ニア州 サニーベール , サンタ セシリア   |

|          | テラス 7 2 3               |

最終頁に続く

(54)【発明の名称】 多重参照ライン・イントラ予測のための方法、装置及びコンピュータ・プログラム

**(57)【特許請求の範囲】****【請求項 1】**

ビデオ復号化における多重参照ラインのイントラ予測のための方法であって：

命令を記憶するメモリと前記メモリと通信するプロセッサとを含むデバイスが、カレント・ブロックのコーディングされるビデオ・ビットストリームを受信するステップ；

前記デバイスが、前記コーディングされるビデオ・ビットストリームからパラメータを取り出すステップであって、前記パラメータは、前記カレント・ブロックにおけるイントラ予測のための1つの非隣接参照ラインを示す、ステップ；

前記デバイスが、前記カレント・ブロックをパーティション化して複数のサブ・ブロックを取得するステップ；及び

前記複数のサブ・ブロック内のサブ・ブロックが前記カレント・ブロックの境界に位置していることに応じて、前記デバイスが、前記サブ・ブロックに対する上の全ての非隣接参照ラインに対する値として、上の隣接参照ラインを使用するステップ；

を含み、本方法は、前記デバイスが、前記サブ・ブロックをパーティション化して複数の変換ブロックを取得するステップを更に含み；

前記複数の変換ブロック内の第1の変換ブロックが前記サブ・ブロックの上境界に位置している場合に、前記デバイスは、前記第1の変換ブロックに対する上の全ての非隣接参照ラインに対する値として、前記上の隣接参照ラインを使用し；及び

前記複数の変換ブロック内の第2の変換ブロックが前記サブ・ブロックの上境界に位置していない場合に、前記デバイスは、前記第2の変換ブロックに対して前記パラメータによ

り示される参照ラインを使用する、方法。

**【請求項 2】**

請求項1に記載の方法において、前記デバイスが、前記サブ・ブロックに対する左の隣接参照ラインを使用するステップを更に含む方法。

**【請求項 3】**

請求項1に記載の方法において、前記カレント・ブロックは、スーパー・ブロック、最大コーディング・ブロック、コーディング・ツリー・ブロック(CTB)、最大コーディング・ユニット(LCU)、所定のサイズの所定のブロックのうちの少なくとも1つを含んでいる、方法。

**【請求項 4】**

請求項1に記載の方法において、前記カレント・ブロックの前記境界は、前記カレント・ブロックの上境界、前記カレント・ブロックの左境界、前記カレント・ブロックの左及び上境界双方のうちの1つを含んでいる、方法。

**【請求項 5】**

請求項1に記載の方法において、前記サブ・ブロックに対する上の全ての非隣接参照ラインに対する値として、上の隣接参照ラインを使用するステップは：

前記上の隣接参照ラインからのサンプルを、上の他の全ての非隣接参照ラインにコピーするステップを含む、方法。

**【請求項 6】**

ビデオ復号化における多重参照ラインのイントラ予測のための装置であって：

命令を記憶するメモリ；及び

前記メモリと通信するプロセッサ；

を含み、前記命令は、請求項1-5のうちの何れか1項に記載の方法を前記プロセッサに実行させる、装置。

**【請求項 7】**

請求項1-5のうちの何れか1項に記載の方法をプロセッサに実行させるコンピュータ・プログラム。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

[0001] 関連出願

本件は、2021年4月16日付で出願された米国仮出願第63/175,929号、及び2022年1月6日付で出願された米国非仮出願第17/569,681号に基づいており且つそれらの優先権を主張するものであり、何れの出願もそれらの全体に対する参照により本件に援用される。

**【0002】**

[0002] 技術分野

本件は、ビデオ・コーディング及び/又はデコーディング技術に関連し、特に、改善された少メモリ設計及び多重参照ライン選択方式のシグナリングに関連する。

**【背景技術】**

**【0003】**

[0003] 開示の背景

本件で行われる背景の説明は、本開示の状況を一般的に提示するためのものである。以下の発明者名の下になされる仕事は、その仕事が、この背景のセクションだけでなく、別の方法で本件の出願時における先行技術としての適格性を付与されない可能性のある記述の態様で説明される範囲において、本開示に対する先行技術として、明示的にも暗示的にも認められていない。

**【0004】**

[0004] ビデオ・コーディング及びデコーディングは、動き補償を伴うインター・ピクチャ予測を用いて実行されることが可能である。圧縮されていないデジタル・ビデオは一連のピクチャを含むことが可能であり、各ピクチャは、例えば1920×1080のルミナンス

10

20

30

40

50

・サンプル及び関連する完全な又はサブサンプリングされたクロミナンス・サンプルの空間次元を有する。一連のピクチャは、例えば60ピクチャ/秒、即ち毎秒60フレームの固定された又は可変のピクチャ・レート（非公式に、フレーム・レートとして知られている）を有することが可能である。圧縮されていないビデオは、ストリーミング又はデータ処理に関する特定のビットレート要件を有する。例えば、カラー・チャネル当たりピクセル当たり8ビットにおいて、 $1920 \times 1080$ のピクセル・解像度、60フレーム/秒のフレーム・レート、及び4:2:0のクロマ・サブサンプリングを伴うビデオは、1.5Gbit/sに近い帯域幅を必要とする。このようなビデオの1時間は、600Gバイトを超える記憶スペースを必要とする。

#### 【0005】

[0005] ビデオのコーディング及びデコーディングの目的の1つは、圧縮により、非圧縮入力ビデオ信号における冗長性を低減することであることができる。圧縮は、場合によっては、2桁以上の大きさで、前述の帯域幅又は記憶スペース要件を低減するのに役立つ可能性がある。ロスレス圧縮及び非ロスレス圧縮の両方、並びにそれらの組み合わせを用いることができる。ロスレス圧縮とは、元の信号の正確なコピーが、圧縮された元の信号から、復号化プロセスを経て再構成することができる技術をいう。非ロスレス圧縮は、元のビデオ情報が、コーディングの際に完全には維持されておらず、デコーディングで完全には復元できないコーディング／デコーディング・プロセスを指す。非ロスレス圧縮を使用する場合、再構成された信号は、元の信号と同一ではないかもしれないが、元の信号と再構成された信号との間の歪は、再構成された信号が、幾らかの情報損失があるものの、意図される用途にとって有用である程度に十分に小さくされる。ビデオの場合、非ロスレス圧縮が多くの用途で広く用いられている。許容される歪の量は、用途に依存する。例えば、特定の消費者ストリーミング・アプリケーションのユーザーは、映画又はテレビ放送アプリケーションのユーザーよりも高い歪に耐え得るかもしれない。特定のコーディング・アルゴリズムにより達成可能な圧縮比は、様々な歪許容可能性を反映するよう選択又は調整されることが可能であり；一般に、より高い歪許容可能性は、より高い損失及びより高い圧縮比をもたらすコーディング・アルゴリズムを許容する。

#### 【0006】

[0006] ビデオ・エンコーダ及びデコーダは、例えば、動き補償、フーリエ変換、量子化、及びエントロピー・コーディングを含む幾つかの広範なカテゴリ及びステップからの技術を利用することができる。

#### 【0007】

[0007] ビデオ・コーデック技術は、イントラ・コーディングとして知られる技術を含むことが可能である。イントラ・コーディングでは、サンプル値は、以前に再構成された参照ピクチャからのサンプル又はその他のデータを参照することなく、表現される。幾つかのビデオ・コーデックでは、ピクチャはサンプルのブロックに空間的に分割される。サンプルの全てのブロックがイントラ・モードでコーディングされる場合、そのピクチャはイントラ・ピクチャと言及することが可能である。イントラ・ピクチャとその派生物、例えば独立デコーダ・リフレッシュ・ピクチャは、デコーダ状態をリセットするために使用されることが可能であり、従って、コーディングされるビデオ・ビットストリーム及びビデオ・セッションにおける最初のピクチャとして、又は静止画像として使用されることが可能である。イントラ予測後のブロックのサンプルは、次いで、周波数ドメインへの変換を施され、そのように生成された変換係数は、エントロピー・コーディングの前に量子化されることが可能である。イントラ予測は、変換前のドメインにおけるサンプル値を最小化する技術を意味する。場合によっては、変換後のDC値が小さく、AC係数が小さいほど、エントロピー・コーディングにブロックを表現するために所与の量子化ステップ・サイズで必要とされるビット数は少ない。

#### 【0008】

[0008] 例えばMPEG-2世代コーディング技術で知られているような伝統的なイントラ・コーディングは、イントラ予測を使用しない。しかしながら、幾つかの新しいビデオ圧

10

20

30

40

50

縮技術は、空間的に隣接するもののエンコード及び／又はデコードの際に取得される周辺サンプル・データ及び／又はメタデータであって、イントラ・コーディング又はデコーディングされるデータのブロックに、復号化順序で先行する周辺サンプル・データ及び／又はメタデータに基づいて、ブロックのコーディング／デコーディングを試みる技術を含む。このような技術は以後「イントラ予測」技術と呼ばれる。少なくとも幾つかのケースにおいて、イントラ予測は、他の参照ピクチャからではなく、再構築中のカレント・ピクチャのみから、参照データを使用していることに留意されたい。

#### 【0009】

[0009] 様々な多数の形式のイントラ予測が存在し得る。所与のビデオ・コーディング技術において、1つより多くのそのような技術が利用可能である場合、使用する技術は、イントラ予測モードとして言及することが可能である。1つ以上の予測モードは、特定のコーデックで提供される可能性がある。あるケースでは、モードは、サブモードを有する可能性があり、及び／又は様々なパラメータに関連付けられる可能性があり、ビデオのブロックに対するモード／サブモード情報及びイントラ・コーディング・パラメータは、モード・コードワードにおいて個別にコーディングされるか又はまとめて包含されることが可能である。所与のモード、サブモード、及び／又はパラメータの組み合わせに使用するコードワードは、イントラ予測を通じてコーディング効率ゲインに影響を及ぼす可能性があり、また、コードワードをビットストリームに変換するために使用されるエントロピー・コーディング技術についても同様である。

10

#### 【0010】

[0010] 特定のイントラ予測モードがH.264で導入され、H.265で改良され、共同探査モデル（JEM）、汎用ビデオ・コーディング（VVC）、及びベンチマーク・セット（BMS）のようなより新しいコーディング技術で更に改良されている。一般に、イントラ予測に關し、予測子ブロック（predictor block）は、利用可能になっている隣接するサンプル値を使用して形成されることが可能である。例えば、所定の方向及び／又はラインに沿う隣接するサンプルの特定のセットのうちの利用可能な値は、予測子ブロックにコピーされる可能性がある。使用中の方向に対する参照又はリファレンスは、ビットストリームでコーディングされることが可能であるし、又はそれ自身予測されてもよい。

20

#### 【0011】

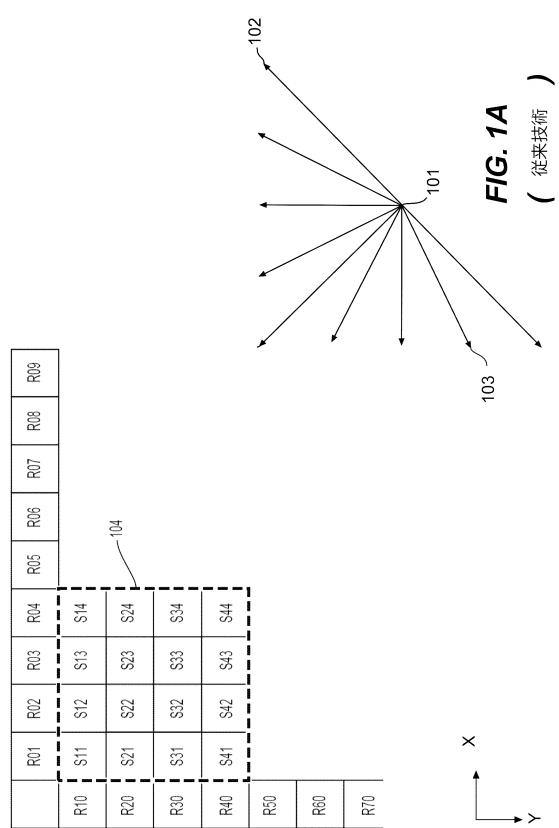

[0011] 図1Aを参照すると、右下に示されているものは、（H.265で規定されている35個のイントラ・モードのうちの33個の角度モードに対応する）H.265の33個の可能なイントラ予測方向で指定されている9個の予測方向のサブセットである。矢印が集まる点（101）は、予測されるサンプルを表現する。矢印は或る方向を示しており、その方向からの隣接するサンプルが、101におけるサンプルを予測するために使用される。例えば、矢印（102）は、サンプル（101）が、水平方向から45度の角度で、隣接する1つのサンプル又は複数のサンプルから右上に向かって予測されることを示す。同様に、矢印（103）は、サンプル（101）が、水平方向から22.5度の角度で、隣接する1つのサンプル又は複数のサンプルから、サンプル（101）の左下に向かって予測されることを示す。

30

#### 【0012】

[0012] 引き続き図1Aを参照すると、左上には、 $4 \times 4$ サンプルの正方形ブロック（104）が示されている（破線の太線で示されている）。正方形ブロック（104）は、16個のサンプルを含み、各々は、“S”と、Y次元におけるその位置（例えば、行インデックス）と、X次元におけるその位置（例えば、列インデックス）とでラベル付けされている。例えば、サンプルS21は、Y次元の第2サンプル（上から）及びX次元の第1サンプル（左から）である。同様に、サンプルS44は、Y及びX次元の両方においてブロック（104）の第4サンプルである。ブロックのサイズは $4 \times 4$ サンプルであるので、S44は右下にある。更に、同様な番号付け方式に従う参照サンプルが示されている。参照サンプルはRと、ブロック（104）に対するY位置（例えば、行インデックス）と、X位置（列インデックス）とでラベル付けされている。H.264とH.265の両方において、再構成中に、ブロックに隣接しているサンプルが使用される。

40

50

**【 0 0 1 3 】**

[0013] ブロック104のイントラ・ピクチャ予測は、シグナリングされた予測方向に従って隣接サンプルから参照サンプル値をコピーすることによって始めることができる。例えば、コーディングされるビデオ・ビットストリームは、このブロック104について、矢印(102)の予測方向を示すシグナリングを含むことを仮定し、即ち、サンプルは、水平方向から45度の角度で、1つ又は複数の予測サンプルから右上に向かって予測される。その場合、サンプルS41、S32、S23、及びS14は、同じ参照サンプルR05から予測される。そして、サンプルS44は参照サンプルR08から予測される。

**【 0 0 1 4 】**

[0014] あるケースでは、特に方向が45度で均一に分割可能でない場合には、ある参照サンプルを計算するために、複数の参照サンプルの値が、例えば補間によって組み合わせられることが可能である。

10

**【 0 0 1 5 】**

[0015] 可能な方向の数は、ビデオ・コーディング技術が発達し続けるにつれて増えている。例えば、H.264(2003年)では、9つの異なる方向がイントラ予測に利用可能である。これは、H.265(2013年)で33にまで増加し、本開示時の時点におけるJEM/VVC/BMSは、65個に及ぶ方向をサポートすることができる。最も適切なイントラ予測方向を同定すること支援する実験研修が行われてあり、方向に関するある程度のビット・ペナルティを受け入れつつ、少ないビット数で最も適切な方向をエンコードするために、エントロピー・コーディングにおいて特定の技術が使用される可能性がある。更に、しばしば方向それ自体が、デコードされている隣接するブロックのイントラ予測で使用される隣接方向から予測されることが可能である。

20

**【 0 0 1 6 】**

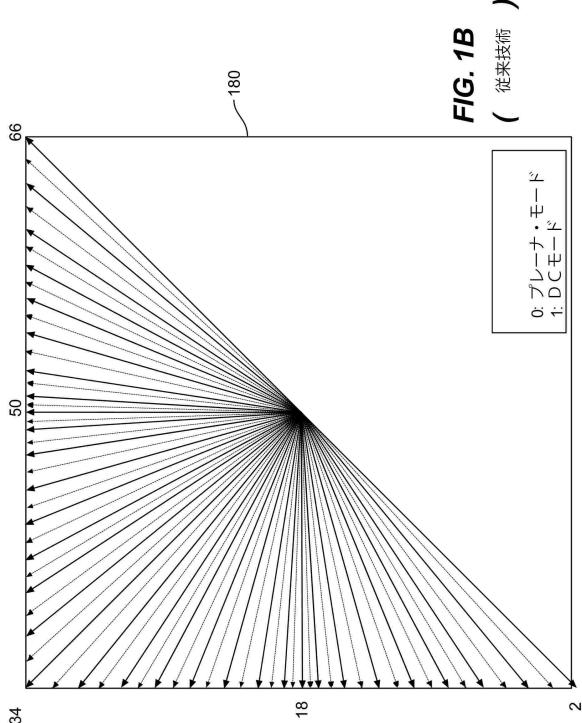

[0016] 図1Bは、JEMによる65個のイントラ予測方向を描いた概略(180)を示しており、時を経て発達する様々な符号化技術において増加する予測方向数を示す。

**【 0 0 1 7 】**

[0017] イントラ予測方向を表現するビットを、コーディングされるビデオ・ビットストリームにおける予測方向にマッピングする方法は、ビデオ・コーディング技術ごとに異なる可能性があり；例えば、予測方向のイントラ予測モードへの、コードワードへのシンプルな直接的なマッピングから、最も可能性の高いモードを含む複雑な適応方式や、類似の技術に及ぶ可能性がある。しかしながら、全てのケースにおいて、ビデオ・コンテンツにおいて、特定の他の方向よりも統計的に起こりにくい特定のイントラ予測方向が存在する可能性がある。ビデオ圧縮のゴールは冗長性の低減であるので、良好に設計されたビデオ・コーディング技術においては、より可能性の低い方向は、より可能性の高い方向よりも多くのビット数で表現される。

30

**【 0 0 1 8 】**

[0018] インター・ピクチャ予測又はインター予測は、動き補償に基づくことが可能である。動き補償において、動きベクトル(以下、MVと呼ぶ)で示される方向に空間的にシフトした後に、以前に再構成されたピクチャ又はその一部(参照ピクチャ)からのサンプル・データのブロックは、新たに再構成されるピクチャ又はピクチャの一部分の予測に使用される可能性がある。場合によっては、参照ピクチャは、現在再構成中のピクチャと同じである可能性がある。MVは、2つの次元X及びY、又は3次元を有する可能性があり、第3の次元は、使用中の参照ピクチャを指示するものである(後者は、時間次元である)。

40

**【 0 0 1 9 】**

[0019] 一部のビデオ圧縮技術では、サンプル・データの特定のエリアに適用可能な現在のMV(カレントMV)は、例えば、再構成中のエリアに空間的に隣接するサンプル・データの他のエリアに関連する他のMVであって復号化の順番でカレントMVに先行するものから、予測することが可能である。このようにすると、MVをコーディングするために必要なデータ総量を大幅に削減することができ、それによって圧縮効率を高めることができ

50

る。例えば、カメラ（ナチュラル・ビデオとして知られる）から導出される入力ビデオ信号をコーディングする場合、単一のMVが適用可能であるエリアよりも大きなエリアが、ビデオ・シーケンスの中で同様な方向に移動する統計的な尤度が存在し、従って場合によつては、隣接するエリアのMVから導出される同様な動きベクトルを用いて予測することが可能であるので、MV予測は効果的に機能する可能性がある。これは、与えられたエリアに対して、周囲のMVから予測されるMVに類似する又は同一である実際のMVをもたらす。それは、隣接するMVから予測するのではなく、エントロピー・コーディングの後に、MVが直接的にコーディングする場合に使用されるものよりも、より少ないビット数で表現されることが可能である。場合によつては、MV予測は、元の信号（即ち、サンプル・ストリーム）から導出される信号（即ち、MV）のロスレス圧縮の一例である可能性がある。他の場合に、MV予測それ自体は、例えば幾つかの周囲のMVから予測子を計算する場合に、丸め誤差に起因して非ロスレスとなる可能性がある。

10

#### 【0020】

[0020] 様々なMV予測メカニズムは、H.265/HEVC (ITU-T Rec.H.265, "High Efficiency Video Coding", December 2016) に記載されている。H.265が規定する多くのMV予測メカニズムのうち、本件で以下に説明されるものは、今後「空間マージ」と呼ばれる。

#### 【0021】

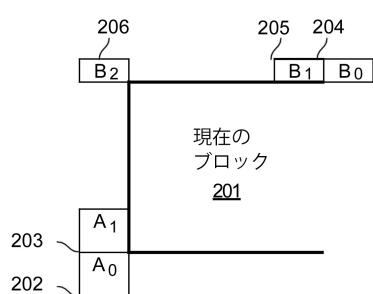

[0021] 図2を参照すると、カレント・ブロック（現在の処理対象のブロック）(201)は、空間的にシフトされた同じサイズの以前のブロックから予測可能であるように動き探索プロセス中にエンコーダによって発見されているサンプルを含む。そのMVを直接的にコーディングする代わりに、MVは、1つ以上の参照ピクチャに関連付けられたメタデータから、例えばA0、A1、B0、B1、B2と示される5つの周辺サンプル（それぞれ202ないし206で示される）の何れかに関連付けられたMVを使用して、例えば（復号化の順序で）最新の参照ピクチャから、導出されることが可能である。H.265では、MV予測は、隣接ブロックが使用しているものと同じ参照ピクチャからの予測子を使用することができる。

20

#### 【発明の概要】

#### 【0022】

[0022] 本件開示は、ビデオ符号化及び／又は復号化のための方法、装置、及びコンピュータ読み取り可能な記憶媒体の様々な実施形態を説明している。

30

#### 【0023】

[0023] 一態様によれば、本件開示の実施形態は、ビデオ復号化における多重参照ラインのイントラ予測のための方法を提供する。本方法は、デバイスが、カレント・ブロックのコーディングされるビデオ・ビットストリームを受信するステップを含む。デバイスは、命令を記憶するメモリと、メモリと通信するプロセッサとを含む。本方法は、デバイスが、コーディングされるビデオ・ビットストリームからパラメータを取り出すステップであつて、パラメータは、カレント・ブロックにおけるイントラ予測のための1つの非隣接参照ラインを示す、ステップ；デバイスが、カレント・ブロックをパーティション化して複数のサブ・ブロックを取得するステップ；及び複数のサブ・ブロック内のサブ・ブロックがカレント・ブロックの境界に位置していることに応じて、デバイスが、サブ・ブロックに対する上の全ての非隣接参照ラインに対する値として、上の隣接参照ラインを使用するステップを含む。

40

#### 【0024】

[0024] 別の態様によれば、本開示の実施形態は、ビデオ符号化及び／又は復号化のための装置を提供する。装置は、メモリ記憶命令；及びメモリと通信するプロセッサを含む。プロセッサが命令を実行すると、プロセッサは、ビデオ復号化及び／又は符号化のための上記方法を装置に実行させるように構成される。

#### 【0025】

[0025] 別の態様において、本開示の実施形態は、ビデオ復号化及び／又は符号化のためにコンピュータによって実行される場合に、ビデオ復号化及び／又は符号化に関する上

50

記方法をコンピュータに実行させる命令を記憶する非一時的なコンピュータ読み取り可能な記憶媒体を提供する。

**【0026】**

[0026] 上記及びその他の態様並びにそれらの実装は、図面、明細書、及び特許請求の範囲において詳細に記載されている。

**【図面の簡単な説明】**

**【0027】**

[0027] 開示される対象事項の更なる特徴、性質、及び種々の利点は、以下の詳細な説明及び添付の図面から更に明らかになるであろう。

**【図1A】[0028]** 図1Aは、イントラ予測方向モードの例示的なサブセットの概略図を示す。 10

**【図1B】[0029]** 図1Bは、例示的なイントラ予測方向の例を示す。

**【図2】[0030]** 図2は、一例におけるカレント・ブロック及びその周囲の空間マージ候補の概略図を示す。

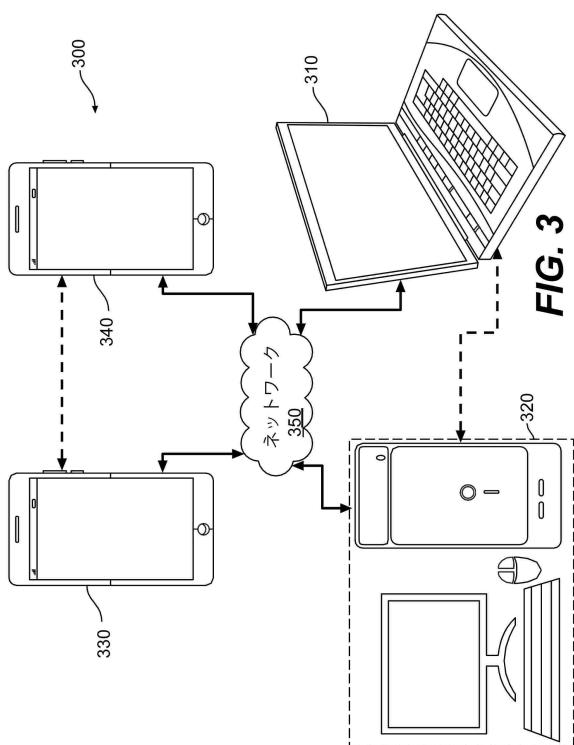

**【図3】[0031]** 図3は、例示的な実施形態による通信システム(300)の簡略化されたブロック図の概略図を示す。

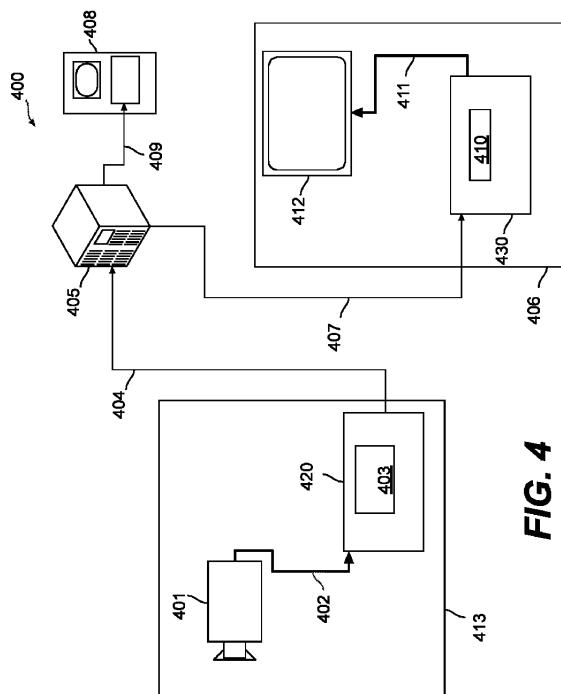

**【図4】[0032]** 図4は、例示的な実施形態による通信システム(400)の簡略化されたブロック図の概略図を示す。

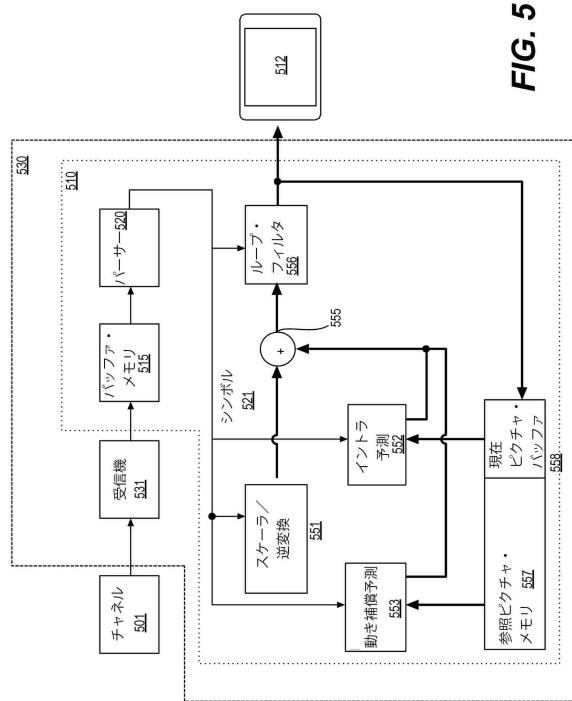

**【図5】[0033]** 図5は、例示的な実施形態によるビデオ・デコーダの簡略化されたブロック図の概略図を示す。

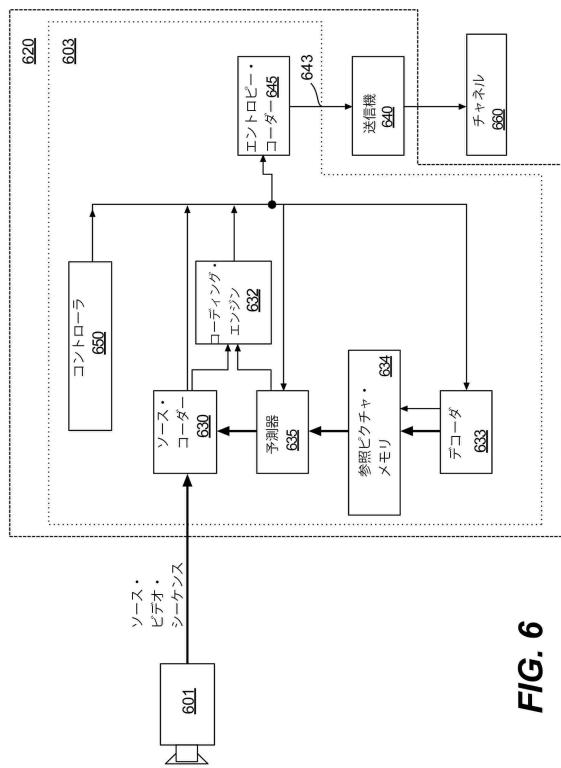

**【図6】[0034]** 図6は、例示的な実施形態によるビデオ・エンコーダの簡略化されたブロック図の概略図を示す。

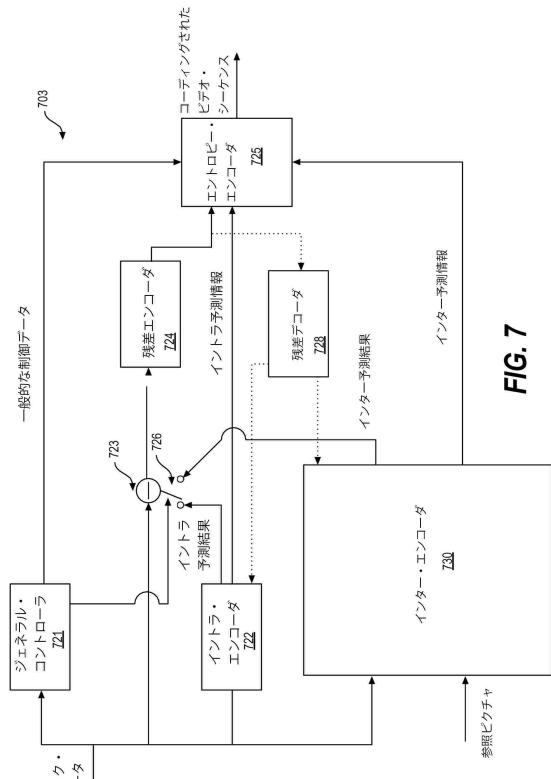

**【図7】[0035]** 図7は、他の例示的な実施形態によるビデオ・エンコーダのブロック図を示す。

**【図8】[0036]** 図8は、他の例示的な実施形態によるビデオ・デコーダのブロック図を示す。

**【図9】[0037]** 図9は、本開示の例示的な実施形態によるコーディング・ブロック・パーティショニングの方式を示す。

**【図10】[0038]** 図10は、本開示の例示的な実施形態によるコーディング・ブロック・パーティショニングの別的方式を示す。 30

**【図11】[0039]** 図11は、本開示の例示的な実施形態によるコーディング・ブロック・パーティショニングの別的方式を示す。

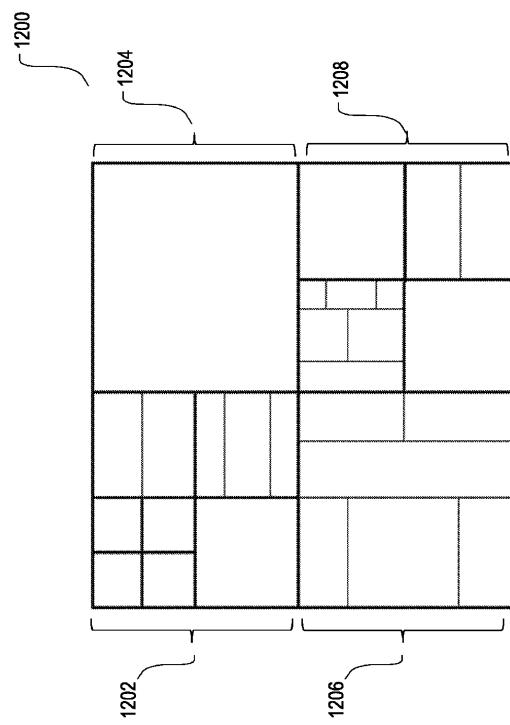

**【図12】[0040]** 図12は、本開示の例示的な実施形態によるコーディング・ブロック・パーティショニングの別的方式を示す。

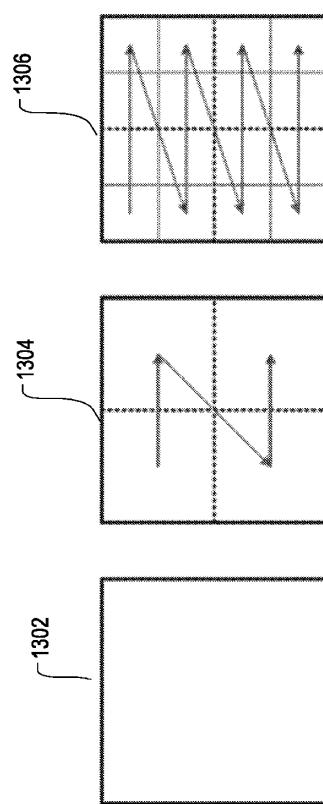

**【図13】[0041]** 図13は、本開示の例示的な実施形態による、コーディング・ブロックを複数の変換ブロックにパーティション化する方式と変換ブロックのコーディング順序とを示す。

**【図14】[0042]** 図14は、本開示の例示的な実施形態による、コーディング・ブロックを複数の変換ブロックにパーティション化する方式と変換ブロックのコーディング順序とを示す。

**【図15】[0043]** 図15は、本開示の例示的な実施形態による、コーディング・ブロックを複数の変換ブロックにパーティション化する別的方式を示す。

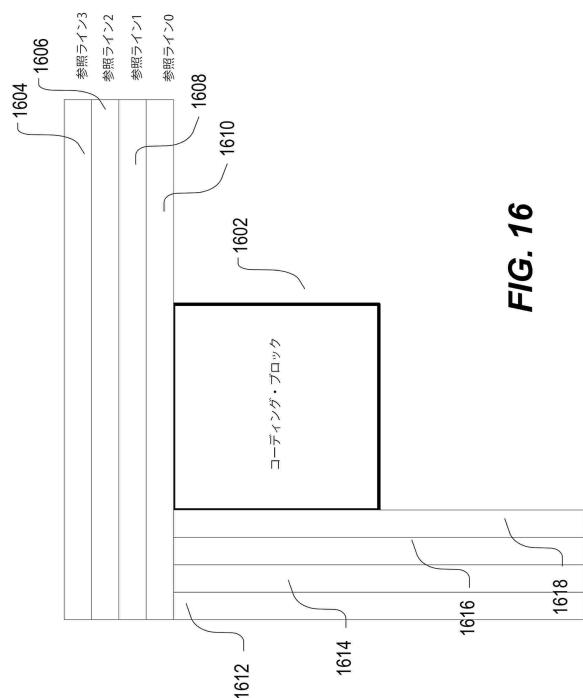

**【図16】[0044]** 図16は、本開示の例示的な実施形態による、種々の参照ラインに基づくイントラ予測方式を示す。

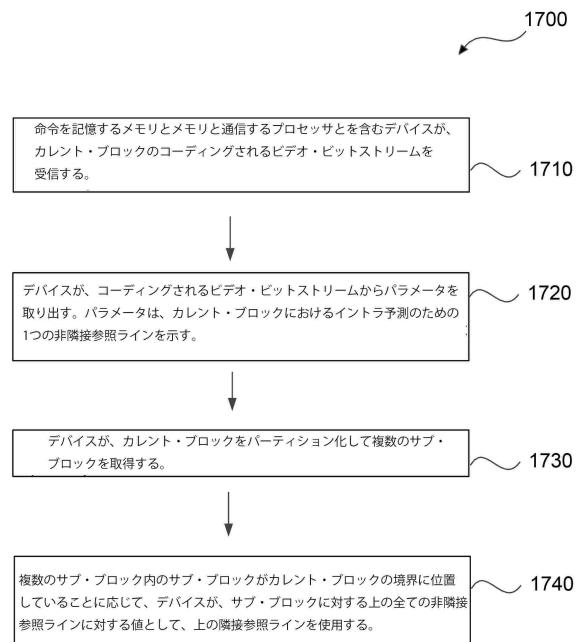

**【図17】[0045]** 図17は、本開示の例示的な実施形態による方法のフロー・チャートを示す。

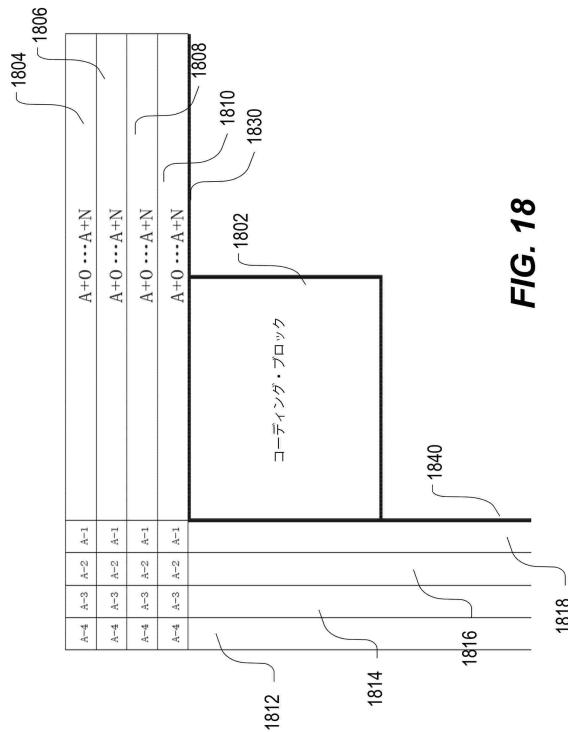

**【図18】[0046]** 図18は、本開示の例示的な実施形態による複数の参照ラインに基づくイントラ予測方式を示す。

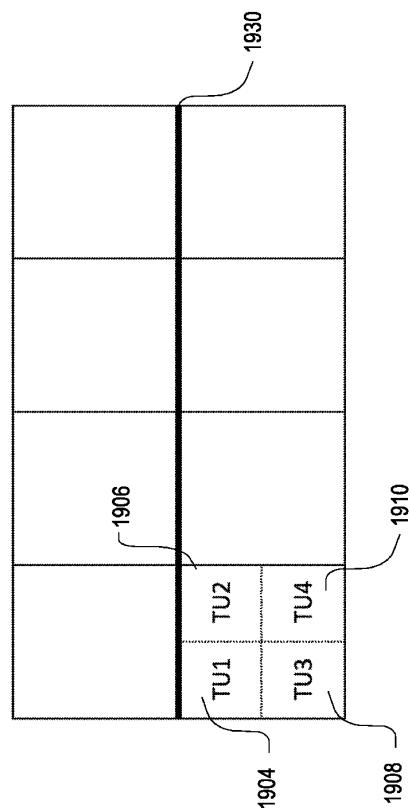

**【図19】[0047]** 図19は、本開示の例示的な実施形態による複数の参照ラインに基づくイントラ予測方式を示す。 50

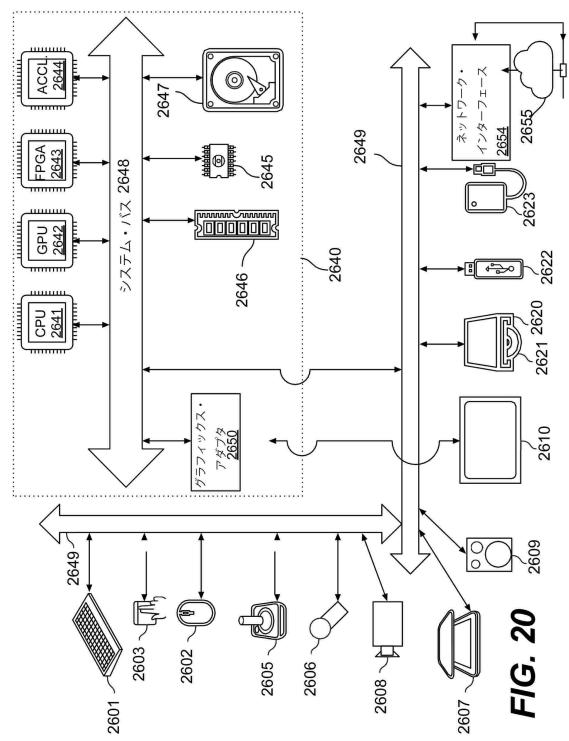

【図20】[0048] 図20は、本開示の例示的な実施形態によるコンピュータ・システムの概略図を示す。

【発明を実施するための形態】

【0028】

[0049] 本開示の詳細な説明

以下、本発明の一部を形成し且つ実施形態の特定の例を例示する添付図面を参照しながら、本発明を詳細に説明する。しかしながら、本発明は、様々な異なる形態で実施される可能性があり、従って、カバーされる又はクレームされる対象事項は、以下で説明される何らかの実施形態に限定されないように解釈されるべく意図されている留意されたい。また、本発明は、方法、デバイス、コンポーネント又はシステムとして実施される可能性があることに留意されたい。従って、本発明の実施形態は、例えば、ハードウェア、ソフトウェア、ファームウェア、又はそれらの任意の組み合わせの形態をとる可能性がある。

【0029】

[0050] 明細書及びクレームを通じて、用語は、明示的に記述された意味を上回って文脈で示唆又は暗示されるニュアンスを伴う意味を有する可能性がある。本件で使用されるフレーズ「一実施形態において」又は「幾つかの実施形態において」は、必ずしも同じ実施形態を指すとは限らず、本件で使用されるフレーズ「別の実施形態において」又は「他の実施形態において」は、必ずしも異なる実施形態を指すとは限らない。同様に、本件で使用されるフレーズ「ある実装において」又は「幾つかの実装において」は、必ずしも同じ実装を指すとは限らず、本件で使用されるフレーズ「別の実装において」又は「他の実装において」は、必ずしも異なる実装を指すとは限らない。例えば、クレームされた対象事項は、例示的な実施形態/実装の全体又は一部の組み合わせを含む、ということが意図されている。

【0030】

[0051] 一般に、用語は、少なくとも部分的には、文脈における用法から理解することが可能である。例えば、「及び」、「又は」又は「及び／又は」のような用語は、本件で使用される場合、そのような用語が使用される文脈に少なくとも部分的に依存する可能性がある様々な意味を包含する可能性がある。典型的には、「又は」は、A、B又はCのようなリストを関連付けるために使用される場合、本件で包括的な意味で使用されるA、B及びCに加えて、本件で排他的な意味で使用されるA、B又はCも意味するように意図されている。更に、本件で使用される用語「1つ以上」又は「少なくとも1つ」は、少なくとも部分的に文脈に依存して、単数の意味で任意の特長、構造、又は特徴を説明するために使用されてもよいし、あるいは複数の意味で特長、構造、又は特徴の組み合わせを説明するために使用されてもよい。同様に、「ある」、「或る」、又は「その」("a", "an", or "the")のような用語は、少なくとも部分的には文脈に依存して、単数の用法を伝えるか、又は複数の用法を伝えるように理解することが可能である。更に、「基づいて」又は「によって決定される」という用語は、必ずしも排的な一連の要因を伝えるように意図されることは限らず、むしろ、ここでも少なくとも部分的には文脈に依存して、必ずしも明示的には記述されていない追加の要因の存在を許容する可能性がある。

【0031】

[0052] 図3は、本開示の実施形態による通信システム(300)の簡略化されたブロック図を示す。通信システム(300)は、例えばネットワーク(350)を介して互いに通信することが可能な複数の端末デバイスを含む。例えば、通信システム(300)は、ネットワーク(350)を介して相互接続された第1ペアの端末デバイス(310)及び(320)を含む。図3の例では、第1ペアの端末デバイス(310)及び(320)は、データの一方向送信を実行してもよい。例えば、端末デバイス(310)は、ネットワーク(350)を介する他の端末デバイス(320)への伝送のために、ビデオ・データ(例えば、端末デバイス(310)によって捕捉されたビデオ・ピクチャのストリーム)をコーディングすることができる。符号化されたビデオ・データは、1つ以上のコーディングされるビデオ・ビットストリームの形態で送信することができる。端末デバイス(320)は、コーディングされる

10

20

30

40

50

ビデオ・データをネットワーク(250)から受信し、コーディングされるビデオ・データを復号化して、ビデオ・ピクチャを復元し、復元されたビデオ・データに従ってビデオ・ピクチャを表示することができる。一方向性データ伝送は、メディア・サービング・アプリケーション等において実現されてもよい。

#### 【0032】

[0053] 別の例では、通信システム(300)は、例えば、ビデオ・カンファレンス・アプリケーションの最中に発生する可能性があるコーディングされるビデオ・データの双方向伝送を行う第2ペアの端末デバイス(330)及び(340)を含む。データの双方向伝送に関し、例えば、端末デバイス(330)及び(340)の各端末デバイスは、ネットワーク(350)を介して端末デバイス(330)及び(340)のうちの他方の端末デバイスへ伝送するために、ビデオ・データ(例えば、端末デバイスによって捕捉されるビデオ・ピクチャのストリーム)をコーディングすることができる。端末デバイス(330)及び(340)の各端末デバイスもまた、端末デバイス(330)及び(340)の他方の端末デバイスによって送信されたコーディングされるビデオ・データを受信することが可能であり、コーディングされるビデオ・データを復号化してビデオ・ピクチャを復元することが可能であり、復元されたビデオ・データに従って、アクセス可能なディスプレイ・デバイスでビデオ・ピクチャを表示することが可能である。

#### 【0033】

[0054] 図3の例において、端末デバイス(310)、(320)、(330)、及び(340)は、サーバー、パーソナル・コンピュータ、スマートフォンとして実装されてもよいが、本開示の原理による用途はそのように限定されなくてよい。本開示の実施形態は、デスクトップ・コンピュータ、ラップトップ・コンピュータ、タブレット・コンピュータ、メディア・プレーヤ、ウェアラブル・コンピュータ、専用のビデオ・カンファレンス装置、及び／又は等々において実装されてもよい。ネットワーク(350)は、例えば有線(配線されたもの)及び／又は無線通信ネットワークを含む、コーディングされるビデオ・データを端末デバイス(310)、(320)、(330)、及び(340)の間で運ぶ任意数の又は任意タイプのネットワークを表現する。通信ネットワーク(350)は、回線交換型、パケット交換型、及び／又は他のタイプのチャネルでデータを交換することができる。代表的なネットワークは、テレコミュニケーション・ネットワーク、ローカル・エリア・ネットワーク、ワイド・エリア・ネットワーク、及び／又はインターネットを含む。本開示の目的に關し、ネットワーク(350)のアーキテクチャ及びトポロジーは、本件において明示的に説明されない限り、本開示の動作にとって重要ではない可能性がある。

#### 【0034】

[0055] 図4は、開示される対象事項の適用例として、ストリーミング環境におけるビデオ・エンコーダ及びビデオ・デコーダの配置を示す。開示される対象事項は、例えば、ビデオ・カンファレンス、デジタルTV放送、ゲーミング、仮想現実、圧縮されたビデオのデジタル・メディア(CD、DVD、メモリ・スティック等を含む)での記憶などを含む、他のビデオの用途にも等しく適用することが可能である。

#### 【0035】

[0056] ビデオ・ストリーミング・システムは、圧縮されていないビデオ・ピクチャ又は画像のストリームを生成する、例えばデジタル・カメラのようなビデオ・ソース(401)を含むことが可能なビデオ・キャプチャ・サブシステム(413)を含む可能性がある。一例では、ビデオ・ピクチャのストリーム(402)は、ビデオ・ソース(401)のデジタル・カメラによって記録されるサンプルを含む。符号化されたビデオ・データ(404)(又はコーディングされるビデオ・ビットストリーム)と比較した場合に、より多くのデータ量を強調するために太い線として描かれているビデオ・ピクチャのストリーム(402)は、ビデオ・ソース(401)に結合されたビデオ・エンコーダ(403)を含む電子デバイス(420)によって処理されることが可能である。ビデオ・エンコーダ(403)は、ハードウェア、ソフトウェア、又はそれらの組み合わせを含み、以下で詳細に説明されるような開示される対象事項の態様を動作可能にする又は実現することが可能である。非圧縮の

ビデオ・ピクチャのストリーム(402)と比較した場合に、より少ないデータ量を強調するために細い線として描かれている符号化されたビデオ・データ(404)(又は符号化されたビデオ・ビット・ストリーム(404))は、将来の使用のために又はビデオ・デバイス(図示せず)への直接的なダウンストリーミングのために、ストリーミング・サーバー(405)に記憶されることが可能である。図4のクライアント・サブシステム(406)及び(408)のような1つ以上のストリーミング・クライアント・サブシステムは、ストリーミング・サーバー(405)にアクセスして、符号化されたビデオ・データ(404)のコピー(407)及び(409)を取り出すことができる。クライアント・サブシステム(406)は、例えば電子デバイス(430)内にビデオ・デコーダ(410)を含むことができる。ビデオ・デコーダ(410)は、符号化されたビデオ・データの到来するコピー(407)を復号化し、ディスプレイ(412)(例えばディスプレイ・スクリーン)又はその他のレンダリング・デバイス(不図示)でレンダリングすることができる非圧縮のビデオ・ピクチャの出力ストリーム(411)を生成する。ビデオ・デコーダ(410)は、本開示で説明される種々の機能の一部又は全部を実行するように構成されてもよい。幾つかのストリーミング・システムでは、符号化されたビデオ・データ(404)、(407)、及び(409)(例えば、ビデオ・ビットストリーム)は、特定のビデオ・コーディング/圧縮規格に従つて符号化されることが可能である。これらの規格の例は、ITU-T勧告H.265を含む。一例において、開発中のビデオ・コーディング規格は、多用途ビデオ・コーディング(Versatile Video Coding, VVC)として非公式に知られている。開示される対象事項はVVCの状況、及びその他のビデオ・コーディング規格において使用されてもよい。

10

20

## 【0036】

[0057] 電子デバイス(420)及び(430)は、他のコンポーネント(図示せず)を含むことが可能であることに留意されたい。例えば、電子デバイス(420)は、ビデオ・デコーダ(不図示)を含むことが可能であり、電子デバイス(430)は、ビデオ・エンコーダ(不図示)を含むことも可能である。

## 【0037】

[0058] 図5は本開示の何らかの実施形態によるビデオ・デコーダ(510)のブロック図を以下に示している。ビデオ・デコーダ(510)は、電子デバイス(530)に含まれることが可能である。電子デバイス(530)は、受信機(531)(例えば、受信回路)を含むことが可能である。ビデオ・デコーダ(510)は、図4の例におけるビデオ・デコーダ(410)の代わりに使用することが可能である。

30

## 【0038】

[0059] 受信機(531)は、ビデオ・デコーダ(510)によって復号化されるべき1つ以上のコーディングされるビデオ・シーケンスを受信することが可能である。同じ又は別の実施形態において、一度に1つのコーディングされるビデオ・シーケンスが復号化されてもよく、ここで、各々のコーディングされるビデオ・シーケンスの復号化は、他のコーディングされるビデオ・シーケンスから独立している。各ビデオ・シーケンスは、複数のビデオ・フレーム又は画像に関連付けることが可能である。コーディングされるビデオ・シーケンスは、チャネル(501)から受信されることが可能であり、このチャネルは、符号化されたビデオ・データを記憶するストレージ・デバイス、又は符号化されたビデオ・データを送信するストリーミング・ソースへのハードウェア/ソフトウェア・リンクであつてもよい。受信機(531)は、符号化されたビデオ・データを、他のデータ、例えばコーディングされたオーディオ・データ及び/又は補助的なデータ・ストリームとともに受信することが可能であり、これらのデータは、それぞれの処理回路(不図示)に転送されることが可能である。受信機(531)は、コーディングされるビデオ・シーケンスを他のデータから分離することができる。ネットワーク・ジッタに対処するために、バッファ・メモリ(515)は、受信機(531)とエントロピー・デコーダ/パーサー(520)(以後「パーサー(520)」と言及する)との間に結合されてもよい。特定のアプリケーションでは、バッファ・メモリ(515)はビデオ・デコーダ(510)の一部である。他のアプリケーションにおいて、それはビデオ・デコーダ(510)の外側にありかつ分離している可

40

50

能性がある（不図示）。更に別のアプリケーションにおいて、例えばネットワーク・ジッタに対処するために、ビデオ・デコーダ（510）の外側にバッファ・メモリ（不図示）が存在する可能性があり、また、例えば再生タイミングを取り扱うためにビデオ・デコーダ（510）の内側に別の追加的なバッファ・メモリ（515）が、存在する可能性がある。受信機（531）が、十分な帯域幅及び制御可能性を有する記憶／転送デバイスから、又は同期ネットワークから、データを受信している場合、バッファ・メモリ（515）は必要とされない可能性があり、又は小さくすることが可能である。インターネットのようなベスト・エフォート・パケット・ネットワークでの使用のために、十分なサイズのバッファ・メモリ（515）が必要とされる可能性があり、そのサイズは比較的大きい可能性がある。そのようなバッファ・メモリは、適応的なサイズで実現されてもよく、また、ビデオ・デコーダ（510）の外側のオペレーティング・システム又は類似の要素（不図示）において少なくとも部分的に実現されてもよい。

#### 【0039】

[0060] ビデオ・デコーダ（510）は、コーディングされるビデオ・シーケンスからシンボル（521）を再構成するためにパーサー（520）を含むことが可能である。これらのシンボルのカテゴリは、ビデオ・デコーダ（510）の動作を管理するために使用される情報、及び潜在的には、図5に示されているように、電子デバイス（530）の一体的な部分であってもなくてもよいが電子デバイス（530）に結合されることが可能なレンダリング・デバイス（512）（例えば、ディスプレイ・スクリーン）のようなレンダリング・デバイスを制御するための情報を含む。レンダリング・デバイスの制御情報は、サブルメントナル・エンハンスメント情報（SEIメッセージ）又はビデオ・ユーザビリティ情報（VUI）パラメータ・セット・フラグメント（不図示）の形態におけるものであってもよい。パーサー（520）は、パーサー（520）により受信したコーディングされるビデオ・シーケンスを解析／エントロピー復号化することができる。コーディングされるビデオ・シーケンスのエントロピー・コーディングは、ビデオ・コーディング技術又は規格に従うことが可能であり、可変長コーディング、ハフマン・コーディング、コンテキストの影響を伴う又は伴わない算術コーディング等を含む種々の原理に従うことが可能である。パーサー（520）は、サブグループに対応する少なくとも1つのパラメータに基づいて、ビデオ・デコーダにおいてピクセルのサブグループの少なくとも1つに対するサブグループ・パラメータのセットを、コーディングされるビデオ・シーケンスから抽出することができる。サブグループは、グループ・オブ・ピクチャ（GOP）、ピクチャ、タイル、スライス、マクロブロック、コーディング・ユニット（CU）、ブロック、変換ユニット（TU）、予測ユニット（PU）等を含むことが可能である。パーサー（520）はまた、変換係数（例えば、フーリエ変換係数）、量子化パラメータ値、動きベクトル等のようなコーディングされるビデオ・シーケンス情報から抽出することも可能である。

#### 【0040】

[0061] パーサー（520）は、シンボル（521）を生成するために、バッファ・メモリ（515）から受信したビデオ・シーケンスに対してエントロピー復号化／解析処理を実行することが可能である。

#### 【0041】

[0062] シンボル（521）の再構築は、コーディングされるビデオ・ピクチャ又はその部分のタイプ（例えば：インター及びイントラ・ピクチャ、インター及びイントラ・ブロック）及びその他の要因に応じて、複数の異なる処理又は機能ユニットを含むことが可能である。どのユニットがどのように包含されるかは、コーディングされるビデオ・シーケンスからパーサー（520）によって解析されたサブグループ制御情報によって制御されることが可能である。パーサー（520）と以降の複数の処理又は機能ユニットとの間のこのようなサブグループ制御情報の流れは、明確性のために描かれていない。

#### 【0042】

##### [0063]

ビデオ・デコーダ（510）は、既に述べた機能ブロックを超えて更に、以下に説明する

10

20

30

40

50

のような複数の機能ユニットに概念的に細分されることが可能である。商業的制約の下で動作する実用的な実装では、これらのユニットの多くは互いに密接に相互作用し、少なくとも部分的に互いに統合されることが可能である。しかしながら、開示される対象事項の様々な機能を明確性とともに説明する目的に関し、機能ユニットへの概念的な細分が以下の開示で採用されている。

#### 【0043】

[0064] 第1ユニットは、スケーラ / 逆変換ユニット (551) を含む可能性がある。スケーラ / 逆変換ユニット (551) は、量子化された変換係数だけでなく制御情報（使用する逆変換のタイプ、ブロック・サイズ、量子化因子 / パラメータ、量子化スケーリング行列などを含む）も、パーサー (520) からシンボル (521) として受信する。スケーラ / 逆変換ユニット (551) は、アグリゲータ (555) に入力されることが可能なサンプル値を含むブロックを出力することが可能である。10

#### 【0044】

[0065] 場合によっては、スケーラ / 逆変換 (551) の出力サンプルは、イントラ・コーディングされるブロック、即ち、以前に再構成されたピクチャからの予測情報を使用しないが、現在のピクチャの以前に再構成された部分からの予測情報を使用する可能性があるブロック、に関連する可能性がある。このような予測情報は、イントラ・ピクチャ予測ユニット (552) によって提供することが可能である。場合によっては、イントラ・ピクチャ予測ユニット (552) は、カレント・ピクチャ・バッファ (558) に保存されている既に再構成されている周辺ブロック情報を使用して、再構成中のブロックの同じサイズ及び形状のブロックを生成することが可能である。現在のピクチャ・バッファ (558) は、例えば、部分的に再構成されたカレント・ピクチャ及び / 又は完全に再構成されたカレント・ピクチャをバッファリングする。アグリゲータ (555) は、幾つかの実装では、サンプル毎に、イントラ予測ユニット (522) が生成した予測情報を、スケーラ / 逆変換ユニット (551) によって提供されるような出力サンプル情報に加えることが可能である。20

#### 【0045】

[0066] それ以外の場合には、スケーラ / 逆変換ユニット (551) の出力サンプルは、インター・コーディングされ且つ動き補償される可能性のあるブロックに関連することが可能である。このような場合において、動き補償予測ユニット (553) は、インター・ピクチャ予測に使用されるサンプルを取得するために、参照ピクチャ・メモリ (557) にアクセスすることが可能である。ブロックに関連するシンボル (521) に従って、取得されたサンプルを動き補償した後に、これらのサンプルは、アグリゲータ (555) によって、スケーラ / 逆変換ユニット (551) の出力に加えられ（ユニット551の出力は、残差サンプル又は残差信号と言及されてもよい）、出力サンプル情報を生成する。30

動き補償予測ユニット (553) が予測サンプルを取り出す元である参照ピクチャ・メモリ (557) 内のアドレスは、例えばX、Y成分（シフト）及び参照ピクチャ成分（時間）を有することが可能なシンボル (521) の形態で、動き補償予測ユニット (553) にとって利用可能な動きベクトルによって制御されることが可能である。また、動き補償は、サブ・サンプルの正確な動きベクトルが使用される場合に、参照ピクチャ・メモリ (557) から取り出されるようなサンプル値の補間を含むことが可能であり、また動きベクトル予測メカニズム等に関連付けられることも可能である。40

#### 【0046】

[0067] アグリゲータ (555) の出力サンプルは、ループ・フィルタ・ユニット (556) 内の様々なループ・フィルタリング技術の影響を受けることが可能である。ビデオ圧縮技術は、ループ内フィルタ技術を含むことが可能であり、その技術は、コーディングされるビデオ・シーケンス（コーディングされるビデオ・ビットストリームとも呼ばれる）に含まれ、且つパーサー (520) からのシンボル (521) としてループ・フィルタ・ユニット (556) にとって利用可能にされるパラメータによって制御されるが、コーディングされるピクチャ又はコーディングされるビデオ・シーケンスの（復号化の順番で）以前の部分の復号化の間に取得されたメタ情報に応答することが可能であるとともに、以前に再構50

成されたループ・フィルタリングされたサンプル値にも応答することが可能である。以下に更に詳細に説明するように、幾つかのタイプのループ・フィルタは、様々な順序でループ・フィルタ・ユニット556の一部として含まれてもよい。

#### 【0047】

[0068] ループ・フィルタ・ユニット(556)の出力は、レンダリング・デバイス(512)に出力できるだけでなく、将来のインター・ピクチャ予測に使用するために参照ピクチャ・メモリ(557)に格納することも可能なサンプル・ストリームであるとすることが可能である。

#### 【0048】

[0069] 所定のコーディングされるピクチャは、いったん完全に再構成されると、将来のインター・ピクチャ予測のための参照ピクチャとして使用することが可能である。例えば、カレント・ピクチャに対応するコーディングされるピクチャが完全に再構成され、且つコーディングされるピクチャが（例えば、パーサー(520)によって）参照ピクチャとして識別されると、カレント・ピクチャ・バッファ(558)は参照ピクチャ・メモリ(557)の一部となることが可能であり、新しいカレント・ピクチャ・バッファは、以後のコーディングされるピクチャの再構成を開始する前に、再割り当てされることが可能である。

10

#### 【0049】

[0070] ビデオ・デコーダ(510)は、ITU-T Rec.H.265のような規格で採用されている所定のビデオ圧縮技術に従って復号化動作を実行することが可能である。コーディングされるビデオ・シーケンスは、コーディングされるビデオ・シーケンスが、ビデオ圧縮技術又は規格のシンタックス、及びビデオ圧縮技術又は規格で文書化されているようなプロファイルの両方に従うという意味で、使用されているビデオ圧縮技術又は規格によって指定されたシンタックスに準拠することが可能である。具体的には、プロファイルは、特定のツールを、そのプロファイルの下で使用できる唯一のツールとして、ビデオ圧縮技術又は規格で使用可能なすべてのツールから選択することが可能である。また、コンプライアンスのために必要なことは、コーディングされるビデオ・シーケンスの複雑さが、ビデオ圧縮技術又は規格のレベルによって定義される範囲内に収まることであってもよい。場合によっては、そのレベルは、最大ピクチャ・サイズ、最大フレーム・レート、最大再構成サンプル・レート（例えば、毎秒当たりのメガサンプルで測定される）、最大参照ピクチャ・サイズ等を制限する。レベルによって設定される限界は、場合によっては、コーディングされるビデオ・シーケンスでシグナリングされるHRDバッファ管理のための仮説リフレンス・デコーダ(Hypothetical

20

Reference Decoder, HRD)仕様及びメタデータによって更に制限される可能性がある。

30

#### 【0050】

[0071] 幾つかの例示的な実施形態において、受信機(531)は、符号化されたビデオとともに追加的（冗長的）なデータを受信する可能性がある。追加的なデータは、コーディングされたビデオ・シーケンスの一部として含まれる可能性がある。追加的なデータは、データを適切に復号化するため、及び／又は元のビデオ・データをより正確に再構成するために、ビデオ・デコーダ(510)によって使用されてもよい。追加的なデータは、例えば、時間、空間、又は信号雑音比(SNR)エンハンスマント・レイヤ、冗長スライス、冗長ピクチャ、前方誤り訂正コード等の形態におけるものとすることができる。

40

#### 【0051】

[0072] 図6は、本開示の例示的な実施形態によるビデオ・エンコーダ(603)のブロック図を示す。ビデオ・エンコーダ(603)は、電子デバイス(620)に含まれてもよい。電子デバイス(620)は、送信機(640)（例えば、送信回路）を含む可能性がある。ビデオ・エンコーダ(603)は、図4の例におけるビデオ・エンコーダ(403)の代わりに使用することが可能である。

#### 【0052】

[0073] ビデオ・エンコーダ(603)は、ビデオ・エンコーダ(603)によってコーディングされるべきビデオ画像を捕捉することが可能なビデオ・ソース(601)（図6の例

50

では電子デバイス(620)の一部ではない)から、ビデオ・サンプルを受信することが可能である。別の例では、ビデオ・ソース(601)は、電子デバイス(620)の一部として実現されてもよい。

#### 【0053】

[0074] ビデオ・ソース(601)は、任意の適切なビット深度(例えば、8ビット、10ビット、12ビット、...)、任意の色空間(例えば、BT.601 YCrCb、RGB、...)、及び任意の適切なサンプリング構造(例えば、YCrCb 4:2:0、YCrCb 4:4:4)であるとすることが可能なデジタル・ビデオ・サンプル・ストリームの形態で、ビデオ・エンコーダ(603)によってコーディングされるべきソース・ビデオ・シーケンスを提供することが可能である。メディア・サービング・システムにおいて、ビデオ・ソース(601)は、事前に準備されたビデオを記憶することが可能なストレージ・デバイスであってもよい。ビデオ・カンファレンス・システムでは、ビデオ・ソース(601)は、ローカルな画像情報をビデオ・シーケンスとして捕捉するカメラであってもよい。ビデオ・データは、シーケンスで見た場合に動きを伝える複数の個々のピクチャ又は画像として提供されてもよい。ピクチャ自体は、ピクセルの空間アレイとして組織されることが可能であり、ここで、各ピクセルは、使用中のサンプリング構造、色空間などに応じて、1つ以上のサンプルを含むことが可能である。当業者は、ピクセルとサンプルとの間の関係を容易に理解することが可能である。以下の説明は、サンプルに焦点を当てている。

10

#### 【0054】

[0075] 幾つかの実施形態によれば、ビデオ・エンコーダ(603)は、リアル・タイムに、又はアプリケーションによって要求される他の任意の時間制約の下で、ソース・ビデオ・シーケンスのピクチャを、コーディングされるビデオ・シーケンス(643)にコーディングして圧縮することが可能である。適切なコーディング速度を強制することは、コントローラ(650)の1つの機能を構成する。幾つかの実施形態において、コントローラ(650)は、以下で説明されるように他の機能ユニットを制御し、他の機能ユニットに機能的に結合されることが可能である。その結合は明確性のために描かれていない。コントローラ(650)によって設定されるパラメータは、レート制御関連パラメータ(ピクチャ・スキップ、量子化器、レート歪最適化技術のラムダ値、...)、ピクチャ・サイズ、グループ・オブ・ピクチャ(GOP)レイアウト、最大動きベクトル探索範囲などを含むことが可能である。コントローラ(650)は、特定のシステム設計のために最適化されたビデオ・エンコーダ(603)に関連する他の適切な機能を有するように構成することが可能である。

20

#### 【0055】

[0076] 幾つかの例示的な実施形態では、ビデオ・エンコーダ(603)は、コーディング・ループで動作するように構成されてもよい。極端に単純化された説明として、一例において、コーディング・ループは、ソース・コーダ(630)(例えば、コーディングされるべき入力ピクチャ及び参照ピクチャに基づいて、シンボル・ストリームのようなシンボルを生成する責任がある)と、ビデオ・エンコーダ(603)に組み込まれた(ローカル)デコーダ(633)とを含むことが可能である。たとえ組み込まれたデコーダ(633)が、エントロピー・コーディングせずに、ソース・コーダ(630)によるコーディングされるビデオ・ストリームを処理したとしても、デコーダ(633)は、(リモート)デコーダが生成するのと同様な方法で、サンプル・データを生成するためにシンボルを再構成する(エントロピー・コーディングにおいて、シンボルとコーディングされるビデオ・ビットストリームとの間の任意の圧縮は、開示される対象事項で考慮されるビデオ圧縮技術ではロスレスである可能性があるからである)。再構成されたサンプル・ストリーム(サンプル・データ)は、参照ピクチャ・メモリ(634)に入力される。シンボル・ストリームの復号化は、デコーダの位置(ローカル又はリモート)に依存しないビット・イグザクト(bit-exact)な結果をもたらすので、参照ピクチャ・メモリ(634)内の内容もまた、ローカル・エンコーダとリモート・エンコーダとの間でビット・イグザクトである。言い換えると、エンコーダの予測部は、デコーダが復号化中に予測を使用する場合に「見る(see)」ものと厳密に同じサンプル値を、参照ピクチャ・サンプルとして「見る」。参照ピクチ

30

40

50

ヤ同期のこの基本原理（及び、例えばチャネル・エラーに起因して同期性が維持できない場合には、結果としてドリフトが生じる）は、コーディング品質を改善するために使用される。

#### 【0056】

[0077] 「ローカル」デコーダ（633）の動作は、図5に関連して上記で詳細に既に説明されているビデオ・デコーダ（510）のような「リモート」デコーダのものと同じであるとすることが可能である。しかしながら、図5も簡単に参照すると、シンボルが利用可能であり、且つエントロピー・コーダ（645）及びパーサー（520）による、シンボルのコーディングされたビデオ・シーケンスへの符号化／復号化はロスレスであるとすることが可能であるので、バッファ・メモリ（515）及びパーサー（520）を含むビデオ・デコーダ（510）のエントロピー復号化部は、エンコーダにおけるローカル・デコーダ（633）では完全には実現されない可能性がある。10

#### 【0057】

[0078] この時点で行うことが可能な観察は、デコーダに存在するだけであるかもしれない解析／エントロピー復号化以外の任意のデコーダ技術は、必然的に、実質的に同一の機能形態で、対応するエンコーダにも存在する必要があるということである。この理由のために、開示される対象事項はデコーダの動作にしばしば焦点を当てている可能性があり、それはエンコーダの復号化部分と同様である。エンコーダ技術の説明は、包括的に説明されたデコーダ技術の逆であるので、省略することが可能である。特定の分野又は態様においてのみ、エンコーダのより詳細な説明が以下で行われている。20

#### 【0058】

[0079] 動作中に、ソース・コーダ（630）は、幾つかの例示的な実装において、「参照ピクチャ」として指定されたビデオ・シーケンスからの1つ以上の以前にコーディングされたピクチャを参照して、入力ピクチャを予測符号化する、動き補償された予測コーディングを実行することが可能である。このようにして、コーディング・エンジン（632）は、入力ピクチャのピクセル・ブロックと、入力ピクチャに対する予測参照として選択され得る参照ピクチャのピクセル・ブロックとの間の、カラー・チャネルにおける差分（又は残差）をコーディングする。

#### 【0059】

[0080] ローカル・ビデオ・デコーダ（633）は、ソース・コーダ（630）によって生成されたシンボルに基づいて、参照ピクチャとして指定されることが可能なピクチャのコーディングされたビデオ・データを復号化することが可能である。コーディング・エンジン（632）の動作は、有利なことに、非ロスレス・プロセスであってもよい。コーディングされたビデオ・データがビデオ・デコーダ（図6には示されていない）で復号化されることが可能である場合、再構成されたビデオ・シーケンスは、典型的には、幾らかのエラーを伴うソース・ビデオ・シーケンスのレプリカである可能性がある。ローカル・ビデオ・デコーダ（633）は、参照ピクチャにおいてビデオ・デコーダによって実行されることが可能な復号化プロセスを繰り返し、再構成された参照ピクチャが、参照ピクチャ・キャッシュ（634）に記憶されることを引き起こすことが可能である。このように、ビデオ・エンコーダ（603）は、遠方端の（リモート）ビデオ・デコーダによって得られる予定の再構成された参照ピクチャとして共通の内容を有する再構成された参照ピクチャのコピーを、局所的に記憶することが可能である（伝送エラーはないものとする）。3040

#### 【0060】

[0081] 予測器（635）は、コーディング・エンジン（632）のために予測探索を行うことが可能である。即ち、コーディングされるべき新しいピクチャについて、予測器（635）は、サンプル・データ（候補の参照ピクセル・ブロックとして）又は所定のメタデータ（参照ピクチャ動きベクトル、ブロック形状など）について、参照ピクチャ・メモリ（634）を探索することができ、これらは、新しいピクチャについての適切な予測参照として役立つ可能性がある。予測器（635）は、適切な予測参照を見出すために、サンプル・ブロック - ピクセル・ブロック・ベースで動作することが可能である。場合によっては、

予測器(635)によって得られた探索結果によって決定されるように、入力ピクチャは、参照ピクチャ・メモリ(634)に記憶された複数の参照ピクチャから引き出される予測参照を有する可能性がある。

#### 【0061】

[0082] コントローラ(650)は、例えば、ビデオ・データを符号化するために使用されるパラメータ及びサブグループ・パラメータの設定を含む、ソース・コーダ(630)のコーディング動作を管理することが可能である。

#### 【0062】

[0083] 前述の全ての機能ユニットの出力は、エントロピー・コーダ(645)においてエントロピー・コーディングを受けることが可能である。エントロピー・コーダ(645)は、ハフマン・コーディング、可変長コーディング、算術コーディング等の技術に従って、シンボルをロスレス圧縮することによって、種々の機能ユニットによって生成されたシンボルを、コーディングされるビデオ・シーケンスに変換する。10

#### 【0063】

[0084] 送信機(640)は、エントロピー・コーダ(645)によって作成されるようなコーディングされたビデオ・シーケンスをバッファリングして、通信チャネル(660)を介する送信の準備を行うことが可能であり、通信チャネル(660)は、符号化されたビデオ・データを記憶する記憶デバイスへのハードウェア/ソフトウェア・リンクであってもよい。送信機(640)は、ビデオ・コーダ(603)からのコーディングされるビデオ・データを、例えばコーディングされるオーディオ・データ及び/又は補助的なデータ・ストリーム(ソースは不図示)のような送信されるべき他のデータとマージすることが可能である。20

#### 【0064】

[0085] コントローラ(650)は、ビデオ・エンコーダ(603)の動作を管理することができる。コーディングの間に、コントローラ(650)は、コーディングされたピクチャの各々に、特定のコーディングされるピクチャ・タイプを割り当てることが可能であり、これは、各ピクチャに適用されることが可能なコーディング技術に影響を及ぼす可能性がある。例えば、ピクチャは、しばしば、次のピクチャ・タイプの1つとして割り当てられてもよい。

#### 【0065】

[0086] イントラ・ピクチャ(Iピクチャ)は、シーケンス内の如何なる他のピクチャも予測のソースとして使用せずに、コーディング及びデコーディングされることが可能なものである。幾つかのビデオ・コーデックは、例えば、独立デコーダ・リフレッシュ("IDR")ピクチャを含む異なるタイプのイントラ・ピクチャを許容する。当事者は、Iピクチャのこれらの変形例、並びにそれら各自の用途及び特徴を認識している。30

#### 【0066】

[0087] 予測ピクチャ(Pピクチャ)は、各ブロックのサンプル値を予測するために、高々1つの動きベクトル及び参照インデックスを用いるイントラ予測又はインター予測を用いてコーディング及びデコーディングされることが可能なものである。

#### 【0067】

[0088] 双-方向予測ピクチャ(Bピクチャ)は、各ブロックのサンプル値を予測するために、高々2つの動きベクトル及び参照インデックスを用いるイントラ予測又はインター予測を用いてコーディング及びデコーディングされることが可能なものである。同様に、複数の予測ピクチャは、1つのブロックの再構成のために、2つより多い参照ピクチャ及び関連するメタデータを使用することが可能である。40

#### 【0068】

[0089] ソース・ピクチャは、通常、複数のサンプル・コーディング・ブロック(例えば、 $4 \times 4$ 、 $8 \times 8$ 、 $4 \times 8$ 、又は $16 \times 16$ サンプルのブロック)に空間的に細分され、ブロック毎にコーディングされることが可能である。ブロックは、ブロックそれぞれのピクチャに適用されるコーディング割り当てによって決定されるように、他の(既にコーディン50

グされた) ブロックを参照して予測符号化されることが可能である。例えば、Iピクチャのブロックは、非予測的にコーディングされてもよいし、又は、それらは同じピクチャの既にコーディングされたブロックを参照して予測コーディングされてもよい(空間予測又はイントラ予測)。Pピクチャのピクセル・ブロックは、以前にコーディングされた1つの参照ピクチャを参照して、空間的な予測又は時間的な予測により予測コーディングされてもよい。Bピクチャのブロックは、1つ又は2つの以前にコーディングされた参照ピクチャを参照して、空間的な予測又は時間的な予測により予測コーディングされてもよい。ソース・ピクチャ又は中間処理されたピクチャは、他の目的のために、他のタイプのブロックに細分化されてもよい。コーディング・ブロックの分割及びブロックの他のタイプは、以下で更に詳細に説明されるように、同じ方法に従ってもよいし、従わなくてもよい。

10

#### 【0069】

[0090] ビデオ・エンコーダ(603)は、ITU-T Rec.H.265のような所定のビデオ・コーディング技術又は規格に従ってコーディング動作を行うことが可能である。この動作において、ビデオ・エンコーダ(603)は、入力ビデオ・シーケンスにおける時間的及び空間的な冗長性を活用する予測コーディング動作を含む種々の圧縮動作を実行することが可能である。コーディングされるビデオ・データは、従って、使用されているビデオ・コーディング技術又は規格によって指定されたシンタックスに準拠することが可能である。

#### 【0070】

[0091] 幾つかの例示的な実施形態では、送信機(640)は、符号化されたビデオとともに追加データを送信することが可能である。ソース・コーダ(630)は、そのようなデータを、コーディングされるビデオ・シーケンスの一部として含むことが可能である。追加データは、時間的/空間的/SNRエンハンスメント・レイヤ、他の形式の冗長データ(冗長ピクチャ及びスライス、SEIメッセージ、VUIパラメータ・セット・フラグメント等)を含む可能性がある。

20

#### 【0071】

[0092] ビデオは、時間シーケンスにおける複数のソース・ピクチャ(ビデオ・ピクチャ)として捕捉することが可能である。イントラ・ピクチャ予測(しばしば、イントラ予測と略される)は、所与のピクチャにおける空間相関を利用してあり、インター・ピクチャ予測は、ピクチャ間の(時間的又は他の)相関を利用する。一例では、カレント・ピクチャと言及される符号化/復号化の下にある特定のピクチャは、ブロックにパーティション化されることが可能である。ビデオの中で以前にコーディングされ且つ依然としてバッファリングされている参照ピクチャの中の参照ブロックに類似している場合、現在のピクチャ内のブロックは、ベクトルとして言及されるベクトルによってコーディングされることが可能である。動きベクトルは、参照ピクチャ内の参照ブロックを指し、複数の参照ピクチャが使用される場合には、参照ピクチャを識別する第3の次元を有することが可能である。

30

#### 【0072】

[0093] 幾つかの例示的な実施形態において、インター・ピクチャ予測に双-予測技術を用いることが可能である。そのような双-予測技術によれば、ビデオ内でカレント・ピクチャに対して復号化順序で両方とも先行している(ただし、表示順序ではそれぞれ過去又は将来におけるものである可能性がある)第1参照ピクチャ及び第2参照ピクチャのような2つの参照ピクチャが使用される。現在のピクチャ内のブロックは、第1参照ピクチャ内の第1参照ブロックを指す第1動きベクトルと、第2参照ピクチャ内の第2参照ブロックを指す第2動きベクトルとによってコーディングされることが可能である。ブロックは、第1参照ブロックと第2参照ブロックとの組み合わせによって合同で予測されることが可能である。

40

#### 【0073】

[0094] 更に、コーディング効率を改善するために、インター・ピクチャ予測にマージ・モード技術が使用されてもよい。本開示の幾つかの例示的な実施形態によれば、インター・ピクチャ予測及びイントラ・ピクチャ予測のような予測は、ブロックの単位で実行さ

50

れる。例えば、ビデオ・ピクチャのシーケンス中のピクチャは、圧縮のためにコーディング・ツリー・ユニット(CTU)にパーティション化され、ピクチャ内のCTUは、 $64 \times 64$ ピクセル、 $32 \times 32$ ピクセル、又は $16 \times 16$ ピクセルのような同じサイズを有する可能性がある。一般に、CTUは、1つのルマCTBと2つのクロマCTBである3つの並列的なコーディング・ツリー・ロック(CTB)を含む可能性がある。各CTUは、1つ以上のコーディング・ユニット(CU)に再帰的に4分木分割されることが可能である。例えば、 $64 \times 64$ ピクセルのCTUは、 $64 \times 64$ ピクセルの1個のCU、 $32 \times 32$ ピクセルの4個のCUに分割されることが可能である。1つ以上の $32 \times 32$ ブロックは、 $16 \times 16$ ピクセルの4つのCUに更に分割されることが可能である。幾つかの例示的な実施形態において、各CUは、符号化中に分析されて、インター予測タイプ又はイントラ予測タイプのような種々の予測タイプの中でも、CUの予測タイプを決定することができる。CUは、時間的及び/又は空間的な予測可能性に依存して、1つ以上の予測単位(PU)に分割されることが可能である。一般に、各PUはルマ予測ブロック(PB)と2つのクロマPBとを含む。実施形態において、コーディング(符号化/復号化)における予測動作は、予測ブロックの単位で実行される。CUのPU(又は異なるカラー・チャネルのPB)への分割は、様々な空間パターンで実行されてもよい。ルマ又はクロマPBは、例えば、 $8 \times 8$ ピクセル、 $16 \times 16$ ピクセル、 $8 \times 16$ ピクセル、 $16 \times 8$ サンプルなどのような、サンプルの値(例えば、ルマ値)のマトリクスを含んでもよい。

#### 【0074】

[0096] 図7は本開示の別の実施形態によるビデオ・エンコーダ(703)の図を示す。ビデオ・エンコーダ(703)は、ビデオ・ピクチャのシーケンス内の現在のビデオ・ピクチャ内のサンプル値の処理ブロック(例えば、予測ブロック)を受信し、処理ブロックを、コーディングされるビデオ・シーケンスの一部であるコーディングされるピクチャに符号化するように構成される。例示的なビデオ・エンコーダ(703)は、図4の例のビデオ・エンコーダ(403)の代わりに使用されてもよい。

#### 【0075】

[0097] 例えば、ビデオ・エンコーダ(703)は、 $8 \times 8$ サンプルの予測ブロック等のような処理ブロックのサンプル値のマトリクスを受信する。ビデオ・エンコーダ(703)は、イントラ・モード、インター・モード、又は双-予測モードを使用して、例えばレート歪最適化(rate-distortion optimization, RDO)を使用して、処理ブロックが最良にコーディングされるかどうかを判定する。処理ブロックがイントラ・モードでコーディングされるように決定された場合、ビデオ・エンコーダ(703)は、処理ブロックを、コーディングされるピクチャに符号化するために、イントラ予測技術を使用することが可能であり；処理ブロックがインター・モード又は双-予測モードでコーディングされるように決定された場合、ビデオ・エンコーダ(703)は、処理ブロックを、コーディングされるピクチャに符号化するために、それぞれインター予測技術又は双-予測技術を使用することが可能である。幾つかの例示的な実施形態において、マージ・モードはインター予測ピクチャのサブモードとして使用されてもよく、その場合、動きベクトルは、予測器外部のコーディングされた動きベクトル成分の恩恵なしに、1つ以上の動きベクトル予測子から導出される。幾つかの他の例示的な実施形態において、対象ブロックに適用可能な動きベクトル成分が存在する可能性がある。従って、ビデオ・エンコーダ(703)は、処理ブロックのモードを決定するために、モード決定モジュールのような、図7に明示的には示されていないコンポーネントを含む可能性がある。

#### 【0076】

[0098] 図7の例では、ビデオ・エンコーダ(703)は、インター・エンコーダ(730)、イントラ・エンコーダ(722)、残差計算器(723)、スイッチ(726)、残差エンコーダ(724)、汎用コントローラ(721)、及びエントロピー・エンコーダ(725)を、図7の例示的な配置で示されるように共に結合して含んでいる。

#### 【0077】

[0099] インター・エンコーダ(730)は、カレント・ブロック(例えば、処理しているブロック)のサンプルを受信し、そのブロックを、参照ピクチャ内の1つ以上の参照ブ

ロック（例えば、表示の順序で以前のピクチャと以後のピクチャにおけるロック）と比較し、インター予測情報（例えば、インター符号化技術による冗長情報の記述、動きベクトル、マージ・モード情報）を生成し、任意の適切な技術を用いてインター予測情報に基づいて、インター予測結果（例えば、予測ブロック）を計算するように構成される。幾つかの例では、参照ピクチャは、復号化された参照ピクチャであって、図6の例示的なエンコーダ（620）に組み込まれた復号化ユニット（633）（以下で更に詳細に説明されるような図7の残差デコーダ728として示されているもの）を用いて、符号化されたビデオ情報に基づいて復号化されたものである。

#### 【0078】

[0100] イントラ・エンコーダ（722）は、カレント・ロック（例えば、処理ブロック）のサンプルを受信し、そのブロックを、同じピクチャ内で既にコーディングされたブロックと比較し、変換後に量子化された係数を生成し、場合によってはイントラ予測情報（例えば、1つ以上のイントラ符号化技術に従ったイントラ予測方向情報）も生成するよう構成される。イントラ・エンコーダ（722）は、同じピクチャ内のイントラ予測情報及び参照ブロックに基づいて、イントラ予測結果（例えば、予測ブロック）を計算することが可能である。10

#### 【0079】

[0101] ゼネラル・コントローラ（721）は、一般的な制御データを決定し、一般的な制御データに基づいてビデオ・エンコーダ（703）の他のコンポーネントを制御するように構成されてもよい。一例では、ゼネラル・コントローラ（721）は、ブロックのモードを決定し、予測モードに基づいて制御信号をスイッチ（726）に提供する。例えば、予測モードがイントラ・モードである場合、ゼネラル・コントローラ（721）は、スイッチ（726）を制御して、残差計算器（723）による使用のためにイントラ・モード結果を選択し、且つエントロピー・エンコーダ（725）を制御して、イントラ予測情報を選択し、イントラ予測情報をピットストリームに含め；ブロックの予測モードがインター・モードである場合、ゼネラル・コントローラ（721）は、スイッチ（726）を制御して、残差計算器（723）による使用のためにインター予測結果を選択し、且つエントロピー・エンコーダ（725）を制御して、インター予測情報を選択し、インター予測情報をピットストリームに含める。20

#### 【0080】

[0102] 残差計算器（723）は、受信ブロックと、イントラ・エンコーダ（722）又はインター・エンコーダ（730）から選択されたブロックに対する予測結果との間の差分（残差データ）を計算するように構成されてもよい。残差エンコーダ（724）は、残差データを符号化して変換係数を生成するように構成されてもよい。例えば、残差エンコーダ（724）は、残差データを空間ドメインから周波数ドメインへ変換し、変換係数を生成するように構成されてもよい。次いで、変換係数は、量子化された変換係数を得るために量子化処理を施される。様々な実施形態において、ビデオ・エンコーダ（703）はまた、残差デコーダ（728）も含む。残差デコーダ（728）は、逆変換を実行し、復号化された残差データを生成するように構成される。復号化された残差データは、イントラ・エンコーダ（722）及びインター・エンコーダ（730）によって適切に使用することが可能である。30

例えば、インター・エンコーダ（730）は、復号化された残差データ及びインター予測情報に基づいて、復号化されたブロックを生成することが可能であり、イントラ・エンコーダ（722）は、復号化された残差データ及びイントラ予測情報に基づいて、復号化されたブロックを生成することが可能である。復号化されたブロックは、復号化されたピクチャを生成するために適切に処理され、復号化されたピクチャは、メモリ回路（不図示）内でバッファリングされ、参照ピクチャとして使用することが可能である。40

#### 【0081】

[0103] エントロピー・エンコーダ（725）は、符号化されたブロックを含むようにピットストリームをフォーマット化し、エントロピー・コーディングを実行するように構成されてもよい。エントロピー・エンコーダ（725）は、種々の情報をピットストリームに50

含めるように構成される。例えば、エントロピー・エンコーダ(725)は、一般的な制御データ、選択された予測情報（例えば、イントラ予測情報又はインター予測情報）、残差情報、及びその他の適切な情報をビットストリームに含めるように構成されてもよい。インター・モード又は双-予測モードの何れかのマージ・サブモードでブロックをコーディングする場合に、残差情報は存在しない可能性がある。

#### 【0082】

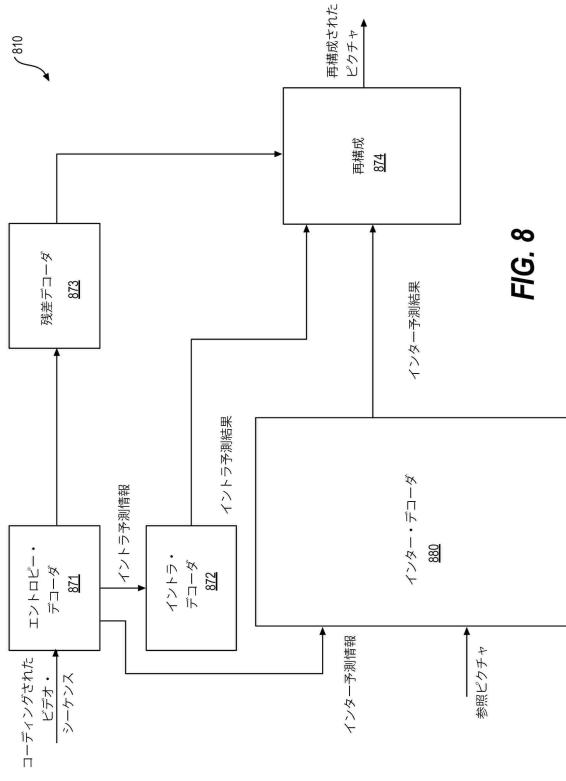

[0104] 図8は、本開示の別の実施形態によるビデオ・デコーダ(810)の図を示す。ビデオ・デコーダ(810)は、コーディングされたビデオ・シーケンスの一部であるコーディングされたピクチャを受信し、コーディングされたピクチャを復号化して、再構成されたピクチャを生成するように構成される。一例では、ビデオ・デコーダ(810)は、図4の例におけるビデオ・デコーダ(410)の代わりに使用されてもよい。10

#### 【0083】

[0105] 図8の例では、ビデオ・デコーダ(810)は、エントロピー・デコーダ(871)、インター・デコーダ(880)、残差デコーダ(873)、再構成モジュール(874)、及びイントラ・デコーダ(872)を、図8の例示的な配置で示されるように共に結合して含んでいる。

#### 【0084】

[0106] エントロピー・デコーダ(871)は、コーディングされるピクチャを作り上げるシンタックス要素を表す特定のシンボルを、コーディングされるピクチャから再構成するように構成されることが可能である。このようなシンボルは、例えば、ブロックがコーディングされるモード（例えば、イントラ・モード、インター・モード、双-予測モード、マージ・サブモード又は別のサブモード）、イントラ・デコーダ(872)又はインター・デコーダ(880)によって予測のために使用される特定のサンプル又はメタデータを識別することが可能な予測情報（例えば、イントラ予測情報又はインター予測情報）、残差情報（例えば、量子化された変換係数の形式におけるもの）等を含むことが可能である。一例において、予測モードがインター又は双-予測モードである場合には、インター予測情報がインター・デコーダ(880)に提供され；予測タイプがイントラ予測タイプである場合には、イントラ予測情報がイントラ・デコーダ(872)に提供される。残差情報は、逆量子化を施されることが可能であり、残差デコーダ(873)に提供される。20

#### 【0085】

[0107] インター・デコーダ(880)は、インター予測情報を受信し、インター予測情報に基づいてインター予測結果を生成するように構成されてもよい。30

#### 【0086】

[0108] イントラ・デコーダ(872)は、イントラ予測情報を受信し、イントラ予測情報に基づいて予測結果を生成するように構成されてもよい。

#### 【0087】

[0109] 残差デコーダ(873)は、逆量子化を実行して量子化解除された変換係数を取り出し、量子化解除された変換係数を処理して残差を周波数ドメインから空間ドメインへ変換するように構成されてもよい。残差デコーダ(873)はまた、特定の制御情報（量子化パラメータ（QP）を含む）を使用する可能性があり、その情報は、エントロピー・デコーダ(871)によって提供されてもよい（これは、僅かな量の制御情報でしかないかもしれませんので、データ経路は描かれていない）。40

#### 【0088】

[0110] 再構成モジュール(874)は、空間ドメインにおいて、残差デコーダ(873)による出力としての残差と、予測結果（場合によっては、インター又はイントラ予測モジュールによって出力されるもの）とを組み合わせて、再構成されたビデオの一部として再構成されたピクチャの一部を形成する再構成されたブロックを形成するように構成される可能性がある。デブロッキング処理などのような他の適切な処理が、視覚的な品質を改善するために実行される可能性があることに留意されたい。

#### 【0089】

10

20

30

40

50

[0111] ビデオ・エンコーダ(403)、(603)、及び(703)、並びにビデオ・デコーダ(410)、(510)、及び(810)は、任意の適切な技術を用いて実現されることが可能であることに留意されたい。幾つかの実施形態において、ビデオ・エンコーダ(403)、(603)、及び(703)、並びにビデオ・デコーダ(410)、(510)、及び(810)は、1つ以上の集積回路を使用して実現することが可能である。別の実施形態において、ビデオ・エンコーダ(403)、(603)、及び(703)、並びにビデオ・デコーダ(410)、(510)、及び(810)は、ソフトウェア命令を実行する1つ以上のプロセッサを使用して実現することが可能である。

#### 【0090】

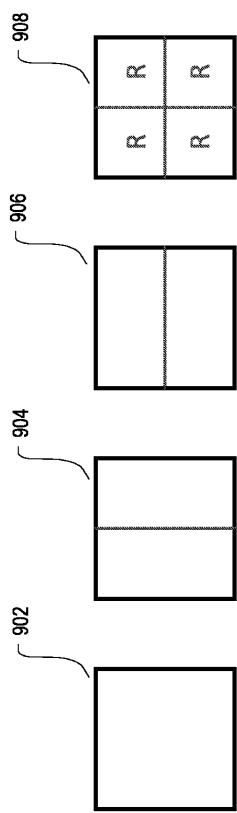

[0112] コーディング・ブロック・パーティショニングに関し、幾つかの例示的な実装では、所定のパターンが適用される可能性がある。図9に示されるように、第1の所定レベル(例えば、 $64 \times 64$ ブロック・レベル)から第2の所定レベル(例えば、 $4 \times 4$ レベル)へ下り始める例示的な4-wayパーティション・ツリーが使用される可能性がある。例えば、ベース・ブロックは、902、904、906、及び908によって示される4つのパーティション化オプションに従う可能性があり、Rとして示されるパーティションは、図9に示されるものと同じパーティション・ツリーが、最低レベル(例えば、 $4 \times 4$ レベル)まで、より下位のスケールで反復される可能性がある。幾つかの実装において、追加的な制約が、図9のパーティショニング方式に適用されてもよい。図9の実装において、矩形パーティション(例えば、1:2/2:1の矩形パーティション)が許容されているかもしれないが、それらは再帰的には許容されない可能性がある一方、正方形パーティション化は再帰的に許容される。再帰を伴う図9に続くパーティション化は、必要に応じて、コーディング・ブロックの最終セットを生成する。そのような方式は、1つ以上のカラー・チャネルに適用される可能性がある。

10

#### 【0091】

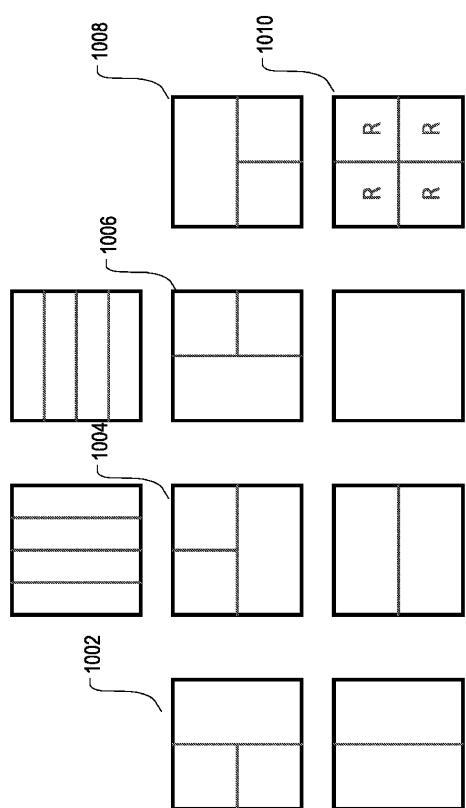

[0113] 図10は、再帰的パーティション化を許容してパーティション化ツリーを形成する別の例示的な所定のパーティション化パターンを示す。図10に示すように、例示的な10-wayパーティション化構造又はパターンが予め定められていてもよい。ルート・ブロックは、予め定められたレベル(例えば、 $128 \times 128$ レベル、又は $64 \times 64$ レベル)から始まってもよい。図10の例示的なパーティション化構造は、様々な2:1/1:2、及び4:1/1:4の矩形パーティションを含む。なお、図10の第2行に示されている3つのサブ・パーティションを伴うパーティション・タイプ1002、1004、及び1008は、「T型」パーティションと言及されてもよい。「T型」パーティション1002、1004、1006、1008は、「Left T-Type」、「Top T-Type」、「Right T-Type」、「Bottom T-Type」と言及されてもよい。幾つかの実装において、図10の矩形パーティションは何れも、更に細分化することは許容されない。コーディング・ツリー深度は、ルート・ノード又はルート・ブロックからの分割深度を示すために、更に定義されていてもよい。例えば、ルート・ノード又はルート・ブラックに対するコーディング・ツリー深度、例えば、 $128 \times 128$ ブロックに対するものは、0に設定されてもよく、ルート・ブロックが図10に続いて更に一度分割された後、コーディング・ツリー深度は、1つだけ増やされる。幾つかの実装において、1010の全てが正方形のパーティションのみが、図10のパターンに続くパーティション化ツリーの次のレベルへの再帰的パーティション化を、許可されてもよい。換言すれば、再帰的なパーティション化は、パターン1002、1004、1006、及び1008を伴う正方形パーティションについては、許可されない可能性がある。再帰を伴う図10に続くパーティション化は、必要に応じて、コーディング・ブロックの最終セットを生成する。そのような方式は、1つ以上のカラー・チャネルに適用される可能性がある。

20

30

#### 【0092】

[0114] ベース・ブロックを分割又はパーティション化し、再度、上記の何らかのパーティション化手順又はその他の手順を行った後に、パーティション又はコーディング・ブロックの最終セットが得られてもよい。これらのパーティションの各々は、様々なパーティション化レベルのうちの1つである可能性がある。各々のパーティションは、コーディ

40

50

ング・ブロック (CB) と言及されてもよい。上記の様々な例のパーティション化の実装に

関し、結果として得られる各CBは、許容される任意のサイズ及びパーティション化レベル

であってもよい。それらはコーディング・ブロックと言及され、なぜなら、それらは幾つ

かの基本的なコーディング / デコーディングの決定が行われる可能性のあるユニットを形

成する可能性があり、コーディング / デコーディング・パラメータは、符号化されたビデ

オ・ビットストリームにおいて最適化、決定、及びシグナリングされる可能性があるから

である。最後のパーティションにおける最高レベルは、コーディング・ブロック・パー

ティション化ツリーの深度を表現する。コーディング・ブロックは、ルマ・コーディング・

ブロック又はクロマ・コーディング・ブロックであってもよい。

## 【0093】

10

[0115] 幾つかの他の実装では、四分木構造が、ベース・ルマ及びクロマ・ブロックを

再帰的にコーディング・ユニットに分割するために使用されてもよい。このような分割構

造は、コーディング・ツリー・ユニット (CTU) と言及されることが可能であり、これは

、四分木構造を使用して、パーティション化をベースCTUの様々なローカル特性に適合さ

せることによって、コーディング・ユニット (CU) に分割される。そのような実装では、

暗黙の四分木分割がピクチャ境界で実行される可能性があり、その結果、ブロックは、そ

のサイズがピクチャ境界に適合するまで、四分木分割を維持する。用語CUは、ルマ及び

クロマ・コーディング・ブロック (CB) のユニットを総称するために使用される。

## 【0094】

20

[0116] 幾つかの実装では、CBは更にパーティション化されてもよい。例えば、CBは

、コーディング及びデコーディング・プロセスの間のイントラ又はインター・フレーム予

測の目的のために、複数の予測ブロック (PB) に更にパーティション化されてもよい。言

い換えれば、CBは、異なるサブ・パーティションに更に分割される可能性があり、その場

合に、個々の予測決定 / 構成が行われる可能性がある。これと並行して、CBは、ビデオ・

データの変換又は逆変換が実行されるレベルを描写する目的のために、複数の変換ブロッ

クに更にパーティション化されてもよい。CBのPBとTBへのパーティション化方式は、同

じであってもよいし、或いは同じでなくてもよい。例えば、各々のパーティション化方式

は、例えば、ビデオ・データの様々な特長に基づいて、それ自身の手順を用いて実行され

てもよい。PBとTBのパーティション化方式は、幾つかの例示的な実装では独立してい

てもよい。PBとTBのパーティション化方式及び境界は、幾つかの他の例示的な実装で相

関させることが可能である。幾つかの実装において、例えば、TBは、PBパーティションの

後にパーティション化されてもよく、特に、各PBは、コーディング・ブロックのパーティ

ション化の後に決定された後、1つ以上のTBに更にパーティション化されてもよい。例

えば、幾つかの実装において、PBは1つ、2つ、4つ、又はその他の個数のTBに分割され

てもよい。

30

## 【0095】

[0117] 幾つかの実装では、ベース・ブロックをコーディング・ブロックにパーティシ

ョン化し、更に予測ブロック及び/又は変換ブロックにパーティション化するために、ルマ

・チャネル及びクロマ・チャネルは別様に取り扱われてもよい。例えば、幾つかの実装で

は、コーディング・ブロックの予測ブロック及び/又は変換ブロックへのパーティション化

は、ルマ・チャネルに対しては許容されているかもしれないが、そのようなコーディング

・ブロックの予測ブロック及び/又は変換ブロックへのパーティション化は、クロマ・チャ

ネルに対しては許容されていないかもしれない。そのような実装では、ルマ・ブロックの

変換及び/又は予測は、コーディング・ブロック・レベルでのみ実行される可能性がある

。別の例では、ルマ・チャネルとクロマ・チャネルの最小変換ブロック・サイズは異なっ

ている可能性があり、例えば、ルマ・チャネルのコーディング・ブロックは、クロマ・チ

ャネルよりも小さな変換及び/又は予測ブロックにパーティション化される可能性がある。

更に別の例では、コーディング・ブロックの変換ブロック及び/又は予測ブロックへのパー

ティション化の最大深度は、ルマ・チャネルとクロマ・チャネルの間で相違する可能性が

あり、例えば、ルマ・チャネルに関するコーディング・ブロックは、クロマ・チャネルよ

40

50

りも深い変換及び/又は予測ブロックにパーティション化されるように許容されていてよい。特定の例では、ルマ・コーディング・ブロックは、最大2つのレベルまで下がる再帰的パーティションによって表現されることが可能な複数のサイズの変換ブロックにパーティション化されてもよく、正方形、2:1/1:2、4:1/1:4のような変換ブロック形状や、4×4ないし64×64への変換ブロック・サイズが許容されてもよい。しかしながら、クロマ・ブロックの場合、ルマ・ブロックに指定された可能な最大変換ブロックのみが許容される可能性がある。

#### 【 0 0 9 6 】

[0118] コーディング・ブロックをPBにパーティション化するための幾つかの例示的な実装では、PBパーティション化の深度、形状、及び/又はその他の特徴は、PBがイントラ又はインター・コーディングされるかどうかに依存する可能性がある。10

#### 【 0 0 9 7 】

[0119] コーディング・ブロック（又は予測ブロック）の変換ブロックへのパーティショニングは、様々な例示的な方式で実装される可能性があり、その例示的な方式は、再帰的又は非再帰的に、また、コーディング・ブロック又は予測ブロックの境界での変換ブロックに対する追加的な考慮とともに、四分木分割及び所定のパターン分割を含むが、これらに限定されない。一般に、結果的に得られる変換ブロックは、異なる分割レベルにおけるものであってもよく、同じサイズのものでなくてもよく、また、正方形の形状である必要もなくてよい（例えば、それらは、許容されるサイズ及びアスペクト比を有する矩形である可能性がある）。20

#### 【 0 0 9 8 】

[0120] 幾つかの実装では、コーディング・パーティション・ツリー方式又は構造が使用されてもよい。ルマ及びクロマ・チャネルに使用されるコーディング・パーティション・ツリー方式は、同じである必要はないかもしれない。言い換えると、ルマ及びクロマ・チャネルは別々のコーディング・ツリー構造を有する可能性がある。更に、ルマ及びクロマ・チャネルが、同一又は異なるコーディング・パーティション・ツリー構造を使用しているかどうか、及び使用される実際のコーディング・パーティション・ツリー構造は、コーディングされるスライスがP、B、又はIスライスであるかどうかに依存する可能性がある。例えば、Iスライスに関し、クロマ・チャネルとルマ・チャネルは、別々のコーディング・パーティション・ツリー構造又はコーディング・パーティション・ツリー構造モードを有する可能性がある一方、P又はBスライスに関し、ルマ及びクロマ・チャネルは、同じコーディング・パーティション・ツリー方式を共有する可能性がある。別々のコーディング・パーティション・ツリー構造又はモードが適用される場合、ルマ・チャネルは、1つのコーディング・パーティション・ツリー構造によってCBにパーティション化され、クロマ・チャネルは、別のコーディング・パーティション・ツリー構造によってクロマCBにパーティション化される可能性がある。30

#### 【 0 0 9 9 】

[0121] コーディング・ブロックと変換ブロックのパーティショニングの具体的な実装例を以下で説明する。このような例示的な実装では、ベース・コーディング・ブロックは、上述した再帰的な四分木分割を使用して、コーディング・ブロックに分割されることが可能である。各レベルにおいて、特定のパーティションの更なる四分木分割が続くべきか否かは、ローカル・ビデオ・データ特性によって決定されてもよい。その結果生じるCBは、様々なサイズの様々な四分木分割レベルである可能性がある。インター・ピクチャ（時間的）又はイントラ・ピクチャ（空間的）予測を使用してピクチャ領域をコーディングするかどうかの決定は、CBレベルで（又はCUレベル、全ての3色チャネルに対して）行われる可能性がある。各CBは、更に、PB分割タイプに応じて、1つ、2つ、4つ、又はその他の個数のPBに分割される可能性がある。1つのPBの内側では、同じ予測プロセスが適用され、関連情報がPBベースでデコーダに伝送される。PB分割型に基づいて予測プロセスを適用することによって、残差ブロックを取得した後、CBは、CBのコーディング・ツリーに類似する別の四分木構造に従って、TBにパーティション化されることが可能である。こ40

の特定の実装では、CB又はTBは、正方形である可能性があるが、正方形に限定されなければならないわけではないわけではない。更に、この特定の例では、PBは、インター予測に関して正方形又は長方形の形状であってもよく、イントラ予測に関してのみ正方形であってもよい。コーディング・ブロックは、例えば、4つの正方形形状のTBに更に分割されてもよい。各TBは、残差クワッド・ツリー (Residual Quad-Tree, RQT) と呼ばれる小さなTBに(四分木分割を用いて)再帰的に更に分割されてもよい。

#### 【0100】

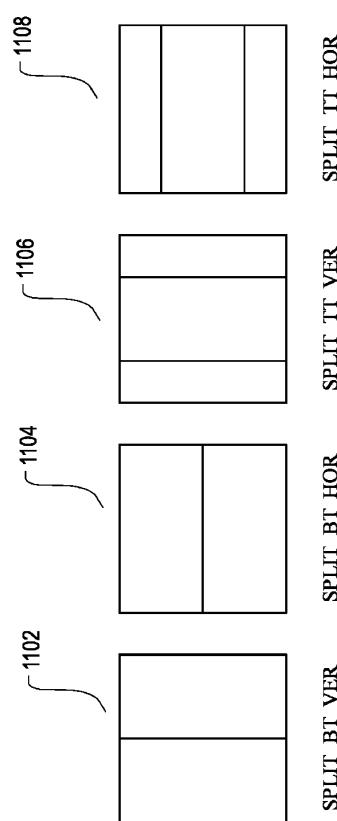

[0122] 以下、ベース・コーディング・ブロックをCB及び他のPB及び/又はTBにパーティション化するための別の具体例を説明。例えば、図10に示されているような複数のパーティション・ユニット・タイプを使用するのではなく、バイナリ及びターナリーフィルセグメンテーション構造 (binary and ternary splits segmentation structure) を用いて、入れ子状になったマルチ・タイプ・ツリーを伴う四分木が使用されてもよい。CB、PB及びTBの概念を分けること(即ち、CBをPB及び/又はTBにパーティション化すること、及びPBをTBにパーティション化すること)は、最大変換長に対して大きすぎるサイズを有するCBに必要とされる場合を除いて放棄されることが可能であり、そのようなCBは更なる分割を必要とする可能性がある。この例示的なパーティション化方式は、CBパーティション形状に対して更なる柔軟性をサポートするよう設計される可能性があり、その結果、予測及び変換の両方が、更なるパーティション化なしにCBレベルで実行されることが可能である。そのようなコーディング・ツリー構造において、CBは、正方形又は長方形の何れかの形状を有している可能性がある。具体的には、コーディング・ツリー・ブロック (CTB) は、先ず、四分木構造によってパーティション化されることが可能である。次いで、四分木リーフ・ノードは、マルチ・タイプ・ツリー構造によって更にパーティション化される可能性がある。マルチ・タイプ・ツリー構造の一例は図11に示されている。具体的には、図11の例示的なマルチ・タイプ・ツリー構造は、垂直二分割 (SPLIT\_BT\_VER) (1102)、水平二分割 (SPLIT\_BT\_HOR) (1104)、垂直三分割 (SPLIT\_TT\_VER) (1106)、及び水平三分割 (SPLIT\_TT\_HOR) (1108) と呼ばれる4つの分割タイプを含む。そして、CBはマルチ・タイプ・ツリーのリーフに対応する。この例の実装では、CBが最大変換長に対して大き過ぎない限り、このセグメンテーションは、更なるパーティション化を伴うことなく、予測及び変換処理の双方に使用される。これは、ほとんどの場合、CB、PB、及びTBは、入れ子状にされたマルチ・タイプ・ツリー・コーディング・ブロック構造を伴う四分木ツリーにおいて、同じブロック・サイズを有することを意味する。例外は、サポートされる最大変換長が、CBの色成分の幅又は高さよりも小さい場合に生じる。

#### 【0101】

[0123] 1つのCTBに対するブロック・パーティションの入れ子状にされたマルチ・タイプ・ツリー・コーディング・ブロック構造を伴う四分木の一例が、図12に示されている。より詳細には、図12は、CTB 1200が4つの正方形パーティション1202、1204、1206、及び1208に分割されていることを示す。分割のために図11のマルチ・タイプ・ツリー構造を更に使用する決定は、四分木分割パーティションの各々に対して行われる。図12の例では、パーティション1204は、それ以上分割されない。パーティション1202と1208はそれぞれ、別の四分木分割を採用している。パーティション1202では、第2のレベルの四分木分割、左上、右上、左下、及び右下パーティションが、四分木、図11の1104、非分割、図11の1108の第3のレベル分割をそれぞれ採用している。パーティション1208は、別の四分木分割を採用し、第2のレベルの四分木分割、左上、右上、左下、及び右下パーティションは、図11の1106、非分割、非分割、及び図11の1104の第3レベル分割をそれぞれ採用している。1208の第3のレベルの左上パーティションのうちの2つのサブ・パーティションは、1104と1108に従って更に分割されている。パーティション1206は、2つのパターンへの図11の1102に従う第2のレベルの分割パターンを採用し、その2つのパターンは、図11の1108と1102による第3のレベルで更に分割される。第4のレベルの分割は、図11の1104に従って、それらのうちの1つに更に適用される。

10

20

30

40

50

**【0102】**

[0124] 上記の特定の例では、最大ルマ変換サイズは $64 \times 64$ であってもよく、サポートされる最大クロマ変換サイズは、ルマと異なる可能性があり、例えば、 $32 \times 32$ である。ルマ・コーディング・ブロック又はクロマ・コーディング・ブロックの幅又は高さが、最大変換幅又は高さよりも大きい場合、ルマ・コーディング・ブロック又はクロマ・コーディング・ブロックは、水平方向及び/又は垂直方向で自動的に、その方向で変換サイズ制約に合うように分割されることが可能である。

**【0103】**

[0125] ベース・コーディング・ブロックを上記のCBにパーティション化する特定の例において、コーディング・ツリー方式は、ルマとクロマが別々のブロック・ツリー構造を有する機能をサポートする可能性がある。例えば、P及びBスライスの場合、1つのCTUのルマCTB及びクロマCTBは、同一のコーディング・ツリー構造を共有することができる。例えば、1スライスの場合、ルマとクロマは、別々のコーディング・ブロック・ツリー構造を有する可能性がある。個別のブロック・ツリーモードが適用される場合、ルマCTBは1つのコーディング・ツリー構造によってルマCBにパーティション化される可能性があり、クロマCTBは別のコーディング・ツリー構造によってクロマCBに分割される。これは、1スライスのCUが、ルマ成分のコーディング・ブロック、又は2つのクロマ成分のコーディング・ブロックで構成されること、そして、P又はBスライスのCUは、ビデオがモノクロでない限り、常に3つのカラー成分全てのコーディング・ブロックで構成されることを意味する。

10

**【0104】**

[0126] コーディング・ブロック又は予測ブロックを変換ブロックにパーティション化するための例示的な実装、及び変換ブロックのコーディング順序を、以下で更に詳細に説明する。幾つかの例示的な実装において、変換パーティション化は、複数の形状の変換ブロック、例えば、1:1(正方形)、1:2/2:1、及び1:4/4:1をサポートしてもよく、変換ブロック・サイズは、例えば、 $4 \times 4$ ないし $64 \times 64$ の範囲に及ぶ。幾つかの実装において、コーディング・ブロックが $64 \times 64$ 以下であるならば、変換ブロック・パーティショニングは、ルマ成分に対してのみ適用される可能性があり、その結果、クロマ・ブロックの場合、変換ブロック・サイズはコーディング・ブロック・サイズと同一である。それ以外の場合、コーディング・ブロックの幅又は高さが64より大きい場合、ルマ及びクロマ・コーディング・ブロック双方は、 $\min(W, 64) \times \min(H, 64)$ 、及び $\min(W, 32) \times \min(H, 32)$ の倍数の変換ブロックに、暗黙的にそれぞれ分割される可能性がある。

20

**【0105】**

[0127] 幾つかの例示的な実装において、イントラ及びインター・コーディングされるブロックの両方に關し、コーディング・ブロックは、所定の数のレベル(例えば、2レベル)までのパーティション化深度を伴う複数の変換ブロックに更にパーティション化される可能性がある。変換ブロック・パーティション化深度及びサイズは関連付けられていてもよい。現在の深度の変換サイズから次の深度の変換サイズへの例示的なマッピングは、以下のテーブルに示されている。

30

**【0106】**

40

テーブル1：変換パーティション・サイズ設定

**【0107】**

50

【表 1】

| 現在の深度の<br>変換サイズ | 次の深度の<br>変換サイズ |    |

|-----------------|----------------|----|

| TX_4X4          | TX_4X4         |    |

| TX_8X8          | TX_4X4         |    |

| TX_16X16        | TX_8X8         |    |

| TX_32X32        | TX_16X16       | 10 |

| TX_64X64        | TX_32X32       |    |

| TX_4X8          | TX_4X4         |    |

| TX_8X4          | TX_4X4         |    |

| TX_8X16         | TX_8X8         |    |

| TX_16X8         | TX_8X8         |    |

| TX_16X32        | TX_16X16       |    |

| TX_32X16        | TX_16X16       |    |

| TX_32X64        | TX_32X32       |    |

| TX_64X32        | TX_32X32       | 20 |

| TX_4X16         | TX_4X8         |    |

| TX_16X4         | TX_8X4         |    |

| TX_8X32         | TX_8X16        |    |

| TX_32X8         | TX_16X8        |    |

| TX_16X64        | TX_16X32       |    |

| TX_64X16        | TX_32X16       |    |

30

[0128] テーブル1の例示的なマッピングに基づいて、1:1正方形ブロックに対して、次のレベルの変換分割は、4つの1:1正方形サブ変換ブロックを生成する可能性がある。変換パーティションは、例えば、 $4 \times 4$ で停止してもよい。従って、 $4 \times 4$ の現在の深度に対する変換サイズは、次の深度に関し、 $4 \times 4$ の同じサイズに対応する。テーブル1の例では、1:2/2:1の非正方形ブロックについては、次のレベルの変換分割は、2つの1:1正方形サブ変換ブロックを作成するであろうが、1:4/4:1の非正方形ブロックについては、次のレベル変換分割は、2つの1:2/2:1サブ変換ブロックを作成するであろう。

#### 【0108】

[0129] 幾つかの例示的な実装において、イントラ・コーディングされるブロックのルマ成分に關し、追加的な制限が適用されてもよい。例えば、変換パーティション化の各レベルに対して、全てのサブ変換ブロックは、等しいサイズを有するように制限されてもよい。例えば、 $32 \times 16$ のコーディング・ブロックの場合、レベル1の変換分割は、2つの $16 \times 16$ サブ変換ブロックを生成し、レベル2の変換分割は、8つの $8 \times 8$ サブ変換ブロックを生成する。換言すれば、第2レベル分割は、変換ユニットを等しいサイズに維持するために、全ての第1レベル・サブ・ブロックに適用されなければならない。テーブル1に続くイントラ・コーディングされる正方形ブロックに対する変換ブロック・パーティション化の例は、図13に示されており、コーディング順序が矢印で一緒に示されている。具体的には、1302は、正方形コーディング・ブロックを示す。テーブルによる4つの等しいサイズの変換ブロックへの第1レベル分割は、矢印で示されるコーディング順序とともに1304で示されている。第1レベルの等しいサイズのブロック全てについての、テーブル1による16

40

50

個の等しいサイズの変換ブロックへの第2レベル分割は、矢印で示されたコーディング順序とともに1306に示されている。

#### 【0109】

[0130] 幾つかの実装において、インター・コーディングされるブロックのルマ成分に対して、イントラ・コーディングに対する上記の制限は適用されない可能性がある。例えば、第1レベルの変換分割の後、サブ変換ブロックのうちの何れか1つは、もう1つ多いレベルで独立に更に分割されてもよい。従って、結果的に生じた変換ブロックは、同じサイズであるかもしれないし、或いは同じサイズでないかもしれない。インター・コーディングされるブロックを変換ブロックに、それらのコーディング順序とともに分割する例が、図14に示されている。図14の例では、インター・コーディングされるブロック1402は、テーブル1に従って2つのレベルで変換ブロックに分割される。第1レベルでは、インター・コーディングされるブロックは、等しいサイズの4つの変換ブロックに分割される。そして、4つの変換ブロックのうちの唯1つ（それらのうちの全てではない）が、4つのサブ変換ブロックに更に分割され、1404で示されるように、2つの異なるサイズを有する合計7つの変換ブロックをもたらす。これら7つの変換ブロックの例示的なコーディング順序は、図14の1404内の矢印によって示されている。10

#### 【0110】

[0131] 幾つかの例示的な実装では、クロマ成分に対して、変換ブロックに対する幾つかの追加的な制限が適用されてもよい。例えば、クロマ成分の場合、変換ブロック・サイズは、コーディング・ブロック・サイズと同じ大きさとすることが可能であるが、所定のサイズ、例えば $8 \times 8$ より小さくはない。20

#### 【0111】

[0132] 幾つかの他の例示的な実装において、コーディング・ブロックの幅（W）又は高さ（H）の何れかが64より大きい場合、ルマ及びクロマ・コーディング・ブロック双方は、 $\min(W, 64) \times \min(H, 64)$ 、及び $\min(W, 32) \times \min(H, 32)$ の倍数の変換ブロックに、暗黙的にそれぞれ分割される可能性がある。30

#### 【0112】

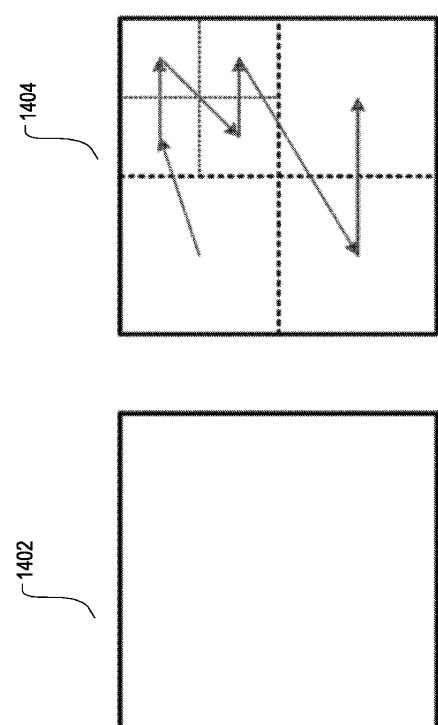

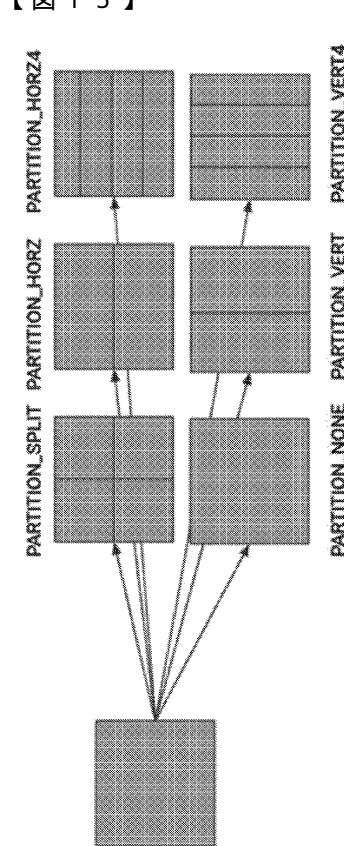

[0133] 図15は、コーディング・ブロック又は予測ブロックを変換ブロックにパーティション化するための別の代替例の方式を更に示している。図15に示されるように、再帰的な変換パーティション化を使用する代わりに、パーティション化タイプの所定のセットが、コーディング・ブロックの変換タイプに従ってコーディング・ブロックに適用されてもよい。図15に示される特定の例では、6つの例のパーティション化タイプのうちの1つが、コーディング・ブロックを、様々な数の変換ブロックに分割するために適用される可能性がある。このような方式は、コーディング・ブロック又は予測ブロックの何れかに適用されてもよい。40

#### 【0113】

[0134] より詳細には、図15のパーティション化方式は、図15に示されているように、任意の所与の変換タイプに対して最大6個のパーティション・タイプを提供する。この方式では、全てのコーディング・ブロック又は予測ブロックは、例えば、レート歪コストに基づいて変換タイプを割り当てられることが可能である。一例では、コーディング・ブロック又は予測ブロックに割り当てられるパーティション・タイプは、コーディング・ブロック又は予測ブロックの変換パーティション・タイプに基づいて決定されてもよい。特定のパーティション・タイプは、図15に示される4つのパーティション・タイプによって示されるように、変換ブロック分割サイズ及びパターン（又はパーティション・タイプ）に対応する可能性がある。種々の変換タイプと種々のパーティション・タイプとの間の対応関係は、事前に定義されてもよい。例示的な対応関係が以下に示されており、大文字のラベルは、レート歪コストに基づいて、コーディング・ブロック又は予測ブロックに割り当てられることが可能な変換タイプを示す。

#### 【0114】

[0135] · PARTITION\_NONE：ブロック・サイズに等しい変換サイズを割り当てる。50

**【0115】**

[0136] ・PARTITION\_SPLIT：ブロック・サイズの幅の1/2、ブロック・サイズの高さの1/2を有する変換サイズを割り当てる。

**【0116】**

[0137] ・PARTITION\_HORZ：ブロック・サイズと同じ幅、ブロック・サイズの1/2の高さを有する変換サイズを割り当てる。

**【0117】**

[0138] ・PARTITION\_VERT：ブロック・サイズの幅の1/2、ブロック・サイズと同じ高さを有する変換サイズを割り当てる。

**【0118】**

[0139] ・PARTITION\_HORZ4：ブロック・サイズと同じ幅、ブロック・サイズの1/4の高さを有する変換サイズを割り当てる。

10

**【0119】**

[0140] ・PARTITION\_VERT4：ブロック・サイズの幅の1/4、ブロック・サイズと同じ高さを有する変換サイズを割り当てます

[0141] 上記の例では、図15に示されるようなパーティション・タイプは全て、パーティション化された変換ブロックに対して均一な変換サイズを含む。これは、単なる例であり、限界ではない。幾つかの他の実装では、混合された変換ブロック・サイズが、特定のパーティション・タイプ（又はパターン）でパーティション化された変換ブロックに使用されてもよい。

20

**【0120】**

[0142] イントラ予測に戻ると、幾つかの例示的な実装において、コーディング・ブロック又は予測ブロックにおけるサンプルの予測は、参照ラインのセットのうちの1つに基づく可能性がある。換言すれば、最も近い隣接ライン（例えば、上記の図1に示されているように、予測ブロックの真上の隣接ライン又は直ぐ左の隣接ライン）を常に使用するのではなく、複数の参照ラインが、イントラ予測に関する選択オプションとして提供されている可能性がある。このようなイントラ予測実装は、多重参照ライン選択（Multiple Reference Line Selection, MRLS）と言及されてもよい。これらの実装では、エンコーダは、複数の参照ラインのうちのどの参照ラインがイントラ予測子を生成するために使用されるかを決定してシグナリングする。デコーダ側では、参照ライン・インデックスを解析した後、現在のイントラ予測ブロックのイントラ予測は、イントラ予測モード（方向性、非方向性、及びその他のイントラ予測モード）に従って、指定された参照ラインを検索することにより再構成された参照サンプルを識別することによって、生成することが可能である。幾つかの実装では、参照ライン・インデックスは、コーディング・ブロック・レベルでシグナリングされてもよく、複数の参照ラインのうちの1つのみが、1つのコーディング・ブロックのイントラ予測のために選択されて使用されてもよい。幾つかの例において、1つより多い参照ラインが、イントラ予測のために一緒に選択される可能性がある。例えば、1つより多い参照ラインが、組み合わせられたり、平均化されたり、補間されたり、あるいは他の何らかの方法で、ウェイトを伴うか又は伴わずに、予測を生成することが可能である。一部の例示的な実装において、MRLSはルマ成分にのみ適用されてもよく、クロマ成分には適用されなくてもよい。

30

**【0121】**

[0143] 図16では、4つの参照ラインMRLSの例が描かれている。図16の例に示されているように、イントラ・コーディング・ブロック1602は、4つの水平参照ライン1604、1606、1608、及び1610、並びに4つの垂直参照ライン1612、1614、1616、及び1618のうちの1つに基づいて予測されてもよい。これらの参照ラインのうち、1610と1618は、直近の隣接するの参照ラインである。参照ラインは、コーディング・ブロックからのそれらの距離に従ってインデックス化されることが可能である。例えば、参照ライン1610と1618はゼロ参照ライン（zero reference line）と言及されることが可能である一方、他の参照ラインは非ゼロ（non-z

40

50

ero) 参照ラインと言及されてもよい。具体的には、参照ライン1608と1616は第1参照ラインとして言及されることが可能であり；参照ライン1606と1614は第2参照ラインとして参照されることが可能であり；参照ライン1604と1612は第3参照ラインとして参照されることが可能である。

#### 【0122】

[0144] 多重参照ライン選択 (MRLS) 方式の実装に関連して幾つかの課題 / 問題が存在する可能性がある。複数の参照ラインを選択しない実装では、最も近い (又は隣接する) トップの (又は上方の) 及び / 又は左側の参照ラインのみが関連し、最も近い (又は隣接する) トップの (即ち上方の) 及び / 又は左側の参照ラインからのサンプルのみが、カレント・ブロックのイントラ予測のためにバッファリング / 保存されることを必要とする。MRLSがイントラ・コーディングされるブロックに適用される場合、4つのトップの (又は上位の) の参照ラインと4つの左側の4つの参照ラインとがイントラ予測に使用される可能性がある。その結果、隣接する参照サンプルを記憶するためのバッファは、3倍増やす必要がある。更に、スーパー・ブロックの場合、バッファの長さは、スーパー・ブロック境界における参照ラインの長さと同じ長さであってもよく、それは、場合によっては、ハードウェア・デコーダにおけるピクチャ幅に等しくてもよく、そのため、3倍のバッファ・サイズ増加は、ハードウェア・デコーダにとって大きな負担である。

10

#### 【0123】

[0145] 本開示は、ビデオ・コーディング及び / 又はデコーディングにおけるイントラ予測のための、少メモリ設計及び / 又は多重参照ライン選択方式のシグナリングを改善し、上述の課題 / 問題のうちの少なくとも1つに対処するための種々の実施形態を記述する。

20

#### 【0124】

[0146] 図17に関し、様々な実施形態において、ビデオ復号化における多重参照ラインのイントラ予測のための方法が説明される。方法1700は、以下のステップのうちの全部又は一部を含む可能性がある：命令を記憶するメモリとメモリと通信するプロセッサとを含むデバイスが、カレント・ブロックのコーディングされるビデオ・ビットストリームを受信するステップ1710；デバイスが、コーディングされるビデオ・ビットストリームからパラメータを取り出すステップであって、パラメータは、カレント・ブロックにおけるイントラ予測のための1つの非隣接参照ラインを示す、ステップ1720；デバイスが、カレント・ブロックをパーティション化して複数のサブ・ブロックを取得するステップ1730；及び / 又は複数のサブ・ブロック内のサブ・ブロックがカレント・ブロックの境界に位置していることに応じて、デバイスが、サブ・ブロックに対する上の全ての非隣接参照ラインに対する値として、上の隣接参照ラインを使用するステップ1740。

30

#### 【0125】

[0147] 幾つかの実施形態において、現在のブロックはブロックと言及されてもよく、現在のブロックをパーティション化することにより得られる複数のサブ・ブロックは、複数のコーディングされるブロックと言及されてもよい。幾つかの他の実装において、ステップ1720は、デバイスが、コーディングされるビデオ・ビットストリームからパラメータを取り出すステップを含んでもよく、パラメータは、カレント・ブロックにおけるイントラ予測のための参照ラインを示す。

40

#### 【0126】

[0148] 本開示における種々の実施形態において、ブロックのサイズ（例えば、限定ではないが、コーディング・ブロック、予測ブロック、又は変換ブロック）は、ブロックの幅又は高さを指す可能性がある。ブロックの幅又は高さは、ピクセル単位の整数であってもよい。

#### 【0127】

[0149] 本開示における様々な実施形態において、ブロックのサイズ（例えば、限定ではないが、コーディング・ブロック、予測ブロック、又は変換ブロック）は、ブロックのエリア・サイズを指す可能性がある。ブロックのエリア・サイズは、ブロックの幅にブロックの高さをピクセル単位で乗算することによって計算された整数であってもよい。

50

## 【0128】

[0150] 本開示における幾つかの様々な実施形態において、ブロックのサイズ（例えば、限定ではないが、コーディング・ブロック、予測ブロック、又は変換ブロック）は、ブロックの幅又は高さの最大値、ブロックの幅又は高さの最小値、又はブロックのアスペクト比を指す可能性がある。ブロックのアスペクト比は、幅をブロックの幅を高さで幅を除算したものとして計算されてもよいし、又はブロックの高さを幅で除算したものとして計算されてもよい。

## 【0129】

[0151] 本開示において、参照ライン・インデックスは、複数の参照ラインの中の参照ラインを示す。様々な実施形態において、ブロックに関する0である参照ライン・インデックスは、ブロックに対する隣接する参照ラインであって、ブロックに最も近い参照ラインであるものを指定することが可能である。例えば、図16のブロック(1602)を参照すると、上参照ライン(1610)は、ブロック(1602)の上に隣接する参照ラインであって、ブロックに最も近い上の参照ラインでもあり；左参照ライン(1618)は、ブロック(1602)の左に隣接する参照ラインであって、ブロックに最も近い左の参照ラインでもある。ブロックに対する0より大きな参照ライン・インデックスは、ブロックの非隣接参照ラインであって、ブロックに対して最近接ではない参照ラインでもある。例えば、図16のブロック(1602)を参照すると、1である参照ライン・インデックスは、上の参照ライン(1608)及び/又は左の参照ライン(1616)を示すことが可能であり；2である参照ライン・インデックスは、上の参照ライン(1606)及び/又は左の参照ライン(1614)を示すことが可能であり；及び/又は3である参照ライン・インデックスは、上の参照ライン(1604)及び/又は左の参照ライン(1612)を示すことが可能である。

10

## 【0130】

[0152] ステップ1710に関し、デバイスは、図5の電子デバイス(530)又は図8のビデオ・デコーダ(810)であってもよい。幾つかの実装において、デバイスは図6のエンコーダ(620)内のデコーダ(633)であってもよい。他の実装において、デバイスは、図5の電子デバイス(530)の一部、図8のビデオ・デコーダ(810)の一部、又は図6のエンコーダ(620)内のデコーダ(633)の一部であってもよい。コーディングされるビデオ・ビットストリームは、図8のコーディングされるビデオ・シーケンス、或いは図6又は図7の中間的なコーディングされるデータであってもよい。

20

## 【0131】

[0153] 一部の実装において、ブロックはスーパー・ブロックを指す可能性がある。スーパー・ブロックは、最大コーディング・ブロック、例えばコーディング・ツリー・ブロック(CTB)、及び/又は最大コーディング・ユニット(LCU)を指す可能性があるが、これらに限定されない。幾つかの他の実装において、スーパー・ブロックは、所定のブロック・サイズ、例えば $32 \times 32$ 、 $64 \times 64$ 、 $128 \times 128$ 、及び/又は $256 \times 256$ を指す可能性があるが、これらに限定されない。

30

## 【0132】

[0154] ステップ1720に関し、デバイスは、コーディングされるビデオ・ビットストリームからパラメータを取り出すことが可能であり、そのパラメータは、MRLSに使用され、ブロック内のイントラ予測のための参照ラインを示すことが可能である。幾つかの実装において、パラメータによって示される参照ラインは、N個のうちの1つの参照ラインであってもよく、ここで、Nは1より大きな整数である。幾つかの他の実装において、パラメータによって示される参照ラインは、N個のうちの1つの非隣接参照ラインであってもよい。

40

## 【0133】

[0155] 幾つかの実装において、方法1700は、デバイスが、ブロックに対して左の隣接参照ラインを使用することを更に含んでもよい。幾つかの他の実装において、左の隣接参照ラインは、ブロックに対して左のN個の参照ラインのうちの1つであってもよい。

## 【0134】

50

[0156] ステップ1730に関し、デバイスは、ロックをパーティション化して、複数のコーディングされるロックを取得することができる。幾つかの実装において、デバイスは、ロックをパーティション化して、コーディング・ロック・パーティション化ツリーを取得することができる。コーディング・ロック・パーティション化ツリーは、複数のコーディングされるロックを含む可能性がある。

#### 【0135】

[0157] ステップ1740を参照すると、複数のコーディングされるロックからのコーディングされるロックに関し、そのコーディングされるロックがロックの境界に位置する場合、デバイスは、コーディングされるロックに対して上の全ての非隣接参照ラインのための値として、上の隣接参照ラインを使用してもよい。幾つかの実装において、ロック（例えば、スーパー・ロック）の境界（又は複数の境界）は、ロックの上境界のみ、ロックの左境界のみ、又はロックの左及び上境界双方を指す可能性がある。

10

#### 【0136】

[0158] 様々な実施形態において、複数の参照ラインからのサンプルを記憶するためのメモリ・サイズを低減するために、現在のイントラ・コーディングされるロックがスーパー・ロックの境界に位置する場合、N個の左参照ライン（カラム）内のサンプルはイントラ予測に使用されことが可能であり、最も近い（又は隣接する）上の（又はトップの）参照ラインは、イントラ予測に使用されることが可能である。

#### 【0137】

[0159] Nは、2、3、4のような1より大きな正の整数である。例えば、N=3の場合、スーパー・ロックの境界におけるコーディング・ロックに対して、3つの左の参照ラインと隣接する上の参照ラインとが、イントラ予測に使用されてもよい。幾つかの実装において、3つの左の参照ラインは、ロックの最も近い左の3つの参照ライン、例えば、図16における参照ライン（1618、1616、及び1614）であってもよい。

20

#### 【0138】

[0160] 幾つかの実装において、現在のイントラ・コーディングされるロックがスーパー・ロック境界に位置するかどうかによらず、参照ライン・インデックスはシグナリングされ、ビットストリームにコーディングされることが可能である。

#### 【0139】

[0161] 再びステップ1740に関し、コーディング・ロックに対して上の全ての非隣接参照ラインの値として、上の隣接参照ラインを使用するステップは、上の隣接参照ラインからのサンプルを、上の他の全ての非隣接参照ラインにコピーするステップを含むことが可能であり、その結果、上の他の全ての非隣接参照ラインからのサンプルを格納するためのメモリ・サイズを大幅に削減する。

30

#### 【0140】

[0162] 幾つかの実装において、現在のイントラ・コーディングされるロックがロック（例えば、スーパー・ロック）の境界に位置し、非ゼロ（又は非隣接）参照ラインが現在のコーディングされるロックのイントラ予測に使用される場合、トップの（又は上の）非ゼロ参照ライン内のサンプルが、現在のコーディングされるロックのイントラ予測に使用される場合、トップの（又は上の）非ゼロ参照ライン内のサンプルは、最も近いトップの（又は上の）参照ラインからコピーすることによって導出される。

40

#### 【0141】

[0163] 図18における一例として、コーディング・ロック（コーディングされるロック又はコード化されたとも呼ばれる）（1802）は、ロック（例えば、スーパー・ロック）の上境界（1830）及び左境界（1840）として配置されている。スーパー・ロックの上境界（1830）及び左境界（1840）は、図18に示すような太線によって示すことが可能である。コーディング・ロック（1802）の最も近い上の参照ライン（1810）内の左上のサンプル（A-4, A-3, A-2, 及び / 又は A-1）と上のサンプル（A+0, ..., A+N）との両方が、上の非ゼロ参照ライン（1808, 1806, 及び / 又は 1804）にコピーされる。幾つかの実装において、複数の左の参照ライン（1818, 1816, 1814, 及び / 又は

50

1812)は、それらのサンプルを別々に保存するように許容されてもよい。

#### 【0142】

[0164] 上述の種々の実装において、トップの隣接参照ラインは一例として使用されており、同様の方式が左の隣接参照ラインに適用可能である可能性があり、少メモリ設計を改善するために、左の非ゼロ参照ライン内のサンプルは、例えば隣接する左の参照ラインをコピーすることによって、最も近い(又は隣接する)左の参照ラインから導出されてもよい。

#### 【0143】

[0165] 様々な実施形態において、方法1700は、デバイスが、コーディングされるブロックをパーティション化して複数の変換ブロックを取得するステップを、オプションとして更に含んでもよい。幾つかの実装において、デバイスは、コーディングされるブロックをパーティション化して、複数の変換ブロックを含む変換ブロック・パーティション化ツリーを取得してもよい。幾つかの実装において、方法1700は、オプションとして次のステップを含んでもよい：複数の変換ブロック内の第1の変換ブロックがコーディングされるブロックの上境界に位置していることに応じて、デバイスが、第1の変換ブロックに対する上の全ての非隣接参照ラインに対する値として、上の隣接参照ラインを使用するステップ；及び／又は複数の変換ブロック内の第2の変換ブロックがコーディングされるブロックの上境界に位置していないことに応じて、デバイスが、第2の変換ブロックに対してパラメータにより示される参照ラインを使用するステップ。幾つかの実装において、パラメータによって示される参照ラインは、第2の変換ブロックに対するトップのN個のうちの1つの参照ラインのであってもよい。

10

20

30

#### 【0144】

[0166] 幾つかの実装において、現在のコーディングされるブロックは、1つより多い変換ブロック(TB)及び／又は1つより多い変換ユニット(TU)に分割されてもよい。現在のコーディングされるブロックがスーパー・ブロック境界に位置し、参照ライン・インデックスが、非ゼロ参照ラインが現在のコーディングされるブロックに使用されることを示す場合には、上の最も近い参照ライン内のサンプルのみが、スーパー・ブロック境界に位置するTUのイントラ予測に使用されてもよい；現在のコーディングされるブロックがスーパー・ブロック境界に位置し、参照ライン・インデックスが、非ゼロ参照ラインが現在のコーディングされるブロックに使用されることを示す場合には、上の非ゼロ参照ライン内のサンプルが、スーパー・ブロック境界に位置しないTUに更に使用されてもよい。

#### 【0145】

[0167] 図19を参照する一例として、太い実線(1930)は、スーパー・ブロックの上境界を示す。複数の変換ユニット(TU1, TU2, TU3, 及び／又はTU4)(1904, 1906, 1908, 及び1910)は、1つのコーディングされるブロック内にある。TU1(1904)とTU2(1906)は、太い水平実線(1930)で示されるスーパー・ブロック境界に位置しており、TU3(1908)とTU4(1910)は、スーパー・ブロックの上境界に位置していない。従って、上の最も近い参照ライン内のサンプルのみがTU1とTU2に使用される可能性がある一方、非ゼロ参照ライン内のサンプルがTU3とTU4に更に使用される可能性がある。同様に、幾つかの他の実装において、コーディング・ブロック内の変換ブロックがスーパー・ブロックの左境界に位置している場合、左の最も近い参照ライン内のサンプルのみが、変換ブロックに対して使用されてもよい。

40

#### 【0146】

[0168] 本開示の実施形態は、別々に又は任意の順序で組み合わせて使用されてもよい。更に、各々の方法(又は実施形態)、エンコーダ、及びデコーダは、処理回路(例えば、1つ以上のプロセッサ、又は1つ以上の集積回路)によって実現されてもよい。一例では、1つ以上のプロセッサは、非一時的なコンピュータ読み取り可能な媒体に保存されたプログラムを実行する。本開示の実施形態は、ルマ・ブロック又はクロマ・ブロックに適用されることが可能であり；クロマ・ブロックでは、実施形態は、1つより多い色成分に別々に適用されることが可能であり、又は1つより多い色成分に一緒に適用されることが可能

50

である。

#### 【0147】

[0169] 上述した技術は、コンピュータ読み取り可能な命令を用いてコンピュータ・ソフトウェアとして実装することが可能であり、1つ以上のコンピュータ読み取り可能な媒体に物理的に記憶することが可能である。例えば、図20は、開示される対象事項の特定の実施形態を実現するのに適したコンピュータ・システム(2600)を示す。

#### 【0148】

[0170] コンピュータ・ソフトウェアは、アセンブリ、コンパイル、リンク、又は類似のメカニズムの対象となり得る任意の適切なマシン・コード又はコンピュータ言語を使用してコーディングされて、1つ以上のコンピュータ中央処理ユニット(CPU)、グラフィック処理ユニット(GPU)等によって、直接的に実行されることが可能な命令、又は解釈やマイクロコード実行などを経由する命令、を含むコードを作成することが可能である。10

#### 【0149】

[0171] 命令は、例えば、パーソナル・コンピュータ、タブレット・コンピュータ、サーバー、スマートフォン、ゲーム・デバイス、モノのインターネット・デバイス等を含む、種々のタイプのコンピュータ又はそのコンポーネント上で実行されることが可能である。

#### 【0150】

[0172] コンピュータ・システム(2600)について図20に示されているコンポーネントは、本質的に例示的なものであり、本開示の実施形態を実現するコンピュータ・ソフトウェアの使用範囲又は機能性に関する如何なる制限も示唆するようには意図されていない。また、コンポーネントの構成は、コンピュータ・システム(2600)の例示的な実施形態に示されたコンポーネントの任意の1つ又は組み合わせに関する何らかの従属性や要件を有するものとして解釈されなければならない。20

#### 【0151】

[0173] コンピュータ・システム(2600)は、特定のヒューマン・インターフェース入力デバイスを含むことが可能である。このようなヒューマン・インターフェース入力デバイスは、例えば、触覚入力(例えば、キーストローク、スワイプ、データ・グローブの動き)、聴覚的な入力(例えば、声、拍手)、視覚的な入力(例えば、ジェスチャ)、嗅覚的な入力(図示されていない)を介して、1人以上の人間ユーザーによる入力に応答することが可能である。また、ヒューマン・インターフェース・デバイスは、オーディオ(例えば、会話、音楽、周囲音)、画像(例えば、スキャンされた画像、静止画像カメラから得られる写真画像)、ビデオ(例えば、2次元ビデオ、立体ビデオを含む3次元ビデオ)のような、人間による意識的な入力に必ずしも直接的に関係しない特定のメディアを捕捉するために使用することが可能である。30

#### 【0152】

[0174] 入力ヒューマン・インターフェース・デバイスは、キーボード(2601)、マウス(2602)、トラックパッド(2603)、タッチ・スクリーン(2610)、データ・グローブ(不図示)、ジョイスティック(2605)、マイクロホン(2606)、スキャナ(2607)、カメラ(2608)のうちの(描かれているものはそれぞれ唯1つであるが)1つ以上を含む可能性がある。

#### 【0153】

[0175] コンピュータ・システム(2600)は、特定のヒューマン・インターフェース出力デバイスを含むことも可能である。このようなヒューマン・インターフェース出力デバイスは、例えば、触覚出力、音、光、及び嗅覚/味覚を通じて、1人以上の人間ユーザーの感覚を刺激することが可能である。このようなヒューマン・インターフェース出力デバイスは、触覚出力デバイス(例えば、タッチ・スクリーン(2610)、データ・グローブ(不図示)、ジョイスティック(2605))による触覚フィードバックであるが、入力デバイスとして役立たない触覚フィードバック・デバイスが存在する可能性もある)、聴覚的な出力デバイス(例えば、スピーカー(2609)、ヘッドフォン(不図示せず))、視覚的な出力デバイス(例えば、CRTスクリーン、LCDスクリーン、プラズマ・スクリーン4050)

、OLEDスクリーンを含むスクリーン(2610)であり、各々はタッチ・スクリーン入力機能を備えるか又は備えておらず、各々は触覚フィードバック機能を備えるか又は備えておらず、それらのうちの幾つかは、二次元的な視覚的な出力、立体出力のような手段による三次元以上の出力を出力することが可能であってもよい；仮想現実メガネ(図示せず)、ホログラフィック・ディスプレイ、及びスマート・タンク(図示せず)、及びプリンタ(図示せず)を含むことが可能である。

#### 【0154】

[0176] コンピュータ・システム(2600)はまた、CD/DVD等の媒体(2621)を伴うCD/DVD ROM/RW(2620)を含む光媒体、サム・ドライブ(2622)、リムーバブル・ハード・ドライブ又はソリッド・ステート・ドライブ(2623)、テープ及びフロッピー・ディスク(図示せず)等のレガシー磁気媒体(不図示)、セキュリティ・ドングル(不図示)等の特殊化されたROM/ASIC/PLDベースのデバイスのような、人間がアクセス可能な記憶デバイス及びそれらに関連する媒体を含むことも可能である。10

#### 【0155】

[0177] 当業者はまた、ここで開示される対象事項に関連して使用される用語「コンピュータ読み取り可能な媒体」は、伝送媒体、搬送波、又はその他の過渡的な信号を包含しないことも理解するはずである。

#### 【0156】

[0178] コンピュータ・システム(2600)はまた、1つ以上の通信ネットワーク(2655)へのインターフェース(2654)を含むことも可能である。ネットワークは、例えば、無線、有線、光であるとすることが可能である。ネットワークは、更に、ローカル、ワイド・エリア、メトロポリタン、車両産業、リアル・タイム、遅延耐性などに関するものであるとすることが可能である。ネットワークの例は、イーサーネット、無線LAN、セルラー・ネットワーク(GSM、3G、4G、5G、LTE等を含む)、TVの有線又は無線ワイド・エリア・デジタル・ネットワーク(ケーブルTV、衛星TV、及び地上放送TVを含む)、CANBusを含む車両産業などを含む。特定のネットワークは、一般に、特定の汎用データ・ポート又は周辺バス(2649)に取り付けられる外部ネットワーク・インターフェース・アダプタを必要とする(例えば、コンピュータ・システム(2600)のUSBポート)；その他は、一般に、以下に説明するようなシステム・バスに取り付けることによって、コンピュータ・システム(2600)のコアに統合される(例えば、イーサーネット・インターフェースはPCコンピュータ・システム内に、セルラー・ネットワーク・インターフェースはスマートフォン・コンピュータ・システム内に統合される)。これらのうちの任意のネットワークを使用して、コンピュータ・システム(2600)は、他のエンティティと通信することが可能である。このような通信は、片-方向受信専用(例えば、放送テレビ)、片-方向送信専用(例えば、特定のCANbusデバイスに対するCANbus)、又は双-方向、例えばローカル又はワイド・エリア・デジタル・ネットワークを使用する他のコンピュータ・システムに対するものであるとすることが可能である。特定のプロトコル及びプロトコル・スタックは、上述のように、それらのネットワーク及びネットワーク・インターフェースの各々で使用されることが可能である。2030

#### 【0157】

[0179] 前述のヒューマン・インターフェース・デバイス、ヒューマン・アクセシブル・ストレージ・デバイス、及びネットワーク・インターフェースは、コンピュータ・システム(2600)のコア(2640)に取り付けられることが可能である。40

#### 【0158】

[0180] コア(2640)は、1つ以上の中央処理ユニット(CPU)(2641)、グラフィックス処理ユニット(GPU)(2642)、フィールド・プログラマブル・ゲート・エリア(FPGA)(2643)の形式における特殊プログラマブル処理デバイス、特定タスク用のハードウェア・アクセラレータ(2644)、グラフィックス・アダプタ(2650)等を含むことが可能である。これらのデバイスは、リード・オンリ・メモリ(ROM)(2645)、ランダム・アクセス・メモリ(2646)、内部大容量ストレージ・デバイス(例えば、内的

10

20

30

40

50

な非ユーザー・アクセシブル・ハード・ドライブ、SSD等) (2647)と共に、システム・バス (2648)を介して接続されることが可能である。幾つかのコンピュータ・システムでは、システム・バス (2648)は、追加のCPU、GPU等による拡張を可能にするために、1つ以上の物理的プラグの形態でアクセス可能である可能性がある。周辺デバイスは、コアのシステム・バス (2648)に直接取り付けられるか、又は周辺バス (2649)を介して取り付けられることが可能である。一例ではスクリーン (2610)をグラフィックス・アダプタ (2650)に接続することができる。周辺バスのアーキテクチャは、PCI、USB等を含む。

#### 【0159】

[0181]

CPU (2641)、GPU (2642)、FPGA (2643)、及びアクセラレータ (2644)は、組み合わされて、前述のコンピュータ・コードを構成することが可能な特定の命令を実行することが可能である。コンピュータ・コードは、ROM (2645)又はRAM (2646)に記憶されることが可能である。一時的なデータはRAM (2646)に格納されることが可能である一方、永続的なデータは例えば内部の大容量ストレージ (2647)に格納されることが可能である。任意のメモリ・デバイスに対する高速な記憶及び検索は、キャッシュ・メモリを利用することで可能になる可能性があり、キャッシュ・メモリは、1つ以上のCPU (2641)、GPU (2642)、大容量ストレージ (2647)、ROM (2645)、RAM (2646)等と密接に関連付けることが可能である。

#### 【0160】

[0182] コンピュータ読み取り可能な媒体は、様々なコンピュータ実装済み動作を実行するためのコンピュータ・コードをその上に有することが可能である。媒体及びコンピュータ・コードは、本開示の目的のために特別に設計及び構築されたものであるとすることが可能であり、又はそれらは、コンピュータ・ソフトウェアの分野における当業者にとって周知であり且つ入手可能な種類のものであるとすることが可能である。

#### 【0161】

[0183] 非限定的な例示として、アーキテクチャ (2600)、具体的にはコア (2640)を有するコンピュータ・システムは、プロセッサ (CPU、GPU、FPGA、アクセラレータ等を含む)の結果として、1つ以上の有形のコンピュータ読み取り可能な媒体に具現化されたソフトウェアを実行する機能を提供することが可能である。そのようなコンピュータ読み取り可能な媒体は、コア内部の大容量ストレージ (2647)又はROM (2645)のような非一時的な性質のコア (2640)の特定のストレージと同様に、上述したようなユーザー・アクセシブル大容量ストレージに関連するメディアであるとすることが可能である。本開示の様々な実施形態を実現するソフトウェアは、そのようなデバイスに記憶され、コア (2640)によって実行されることが可能である。コンピュータ読み取り可能な媒体は、特定のニーズに応じて、1つ以上のメモリ・デバイス又はチップを含むことが可能である。ソフトウェアは、RAM (2646)に記憶されたデータ構造を定めること、及びソフトウェアによって定められたプロセスに従ってそのようなデータ構造を修正することを含む、本願で説明された特定のプロセス又は特定のプロセスの特定の部分を、コア (2640)及び特にその中のプロセッサ (CPU、GPU、FPGA等を含む)に実行させることが可能である。更に又は代替として、コンピュータ・システムは、回路(例えば、アクセラレータ (2644))内に配線された又は他の方法で組み込まれたロジックの結果として機能を提供することが可能であり、その回路は、本願で説明された特定のプロセス又は特定のプロセスの特定の部分を実行することを、ソフトウェアの代わりに又はそれと共に実行することが可能である。ソフトウェアに対する言及はロジックを含み、必要に応じて、その逆も可能である。コンピュータ読み取り可能な媒体に対する言及は、実行のためのソフトウェアを記憶する(集積回路 (IC)のような)回路、実行のためのロジックを具体化する回路、又は適切な場合にはその両方を包含することが可能である。本開示はハードウェア及びソフトウェアの適切な任意の組み合わせを包含する。

#### 【0162】

10

20

30

40

50

[0184] 特定の発明が例示的な実施形態を参照しながら説明されてきたが、本説明は限定であるようには意図されていない。本発明の例示的な実施形態及び追加の実施形態についての様々な修正は、本説明から当業者には明らかであろう。当業者は、本発明の精神及び範囲から逸脱することなく、本件で例示され説明された例示的な実施形態に対して、これら及び種々の他の修正が行われ得ることを容易に理解するであろう。従って、添付のクレームは、そのような如何なる修正や代替的な実施形態もカバーするであろう、ということが想定されている。図中の特定の比率は誇張されている一方、他の比率は最小化されている可能性がある。従って、本開示及び図面は、限定的ではなく例示的であると解釈されるべきである。

## 【0163】

10

## [0185] 付記

## (付記1)

ビデオ復号化における多重参照ラインのイントラ予測のための方法であって：

命令を記憶するメモリと前記メモリと通信するプロセッサとを含むデバイスが、カレント・ブロックのコーディングされるビデオ・ビットストリームを受信するステップ；

前記デバイスが、前記コーディングされるビデオ・ビットストリームからパラメータを取り出すステップであって、前記パラメータは、前記カレント・ブロックにおけるイントラ予測のための1つの非隣接参照ラインを示す、ステップ；

前記デバイスが、前記カレント・ブロックをパーティション化して複数のサブ・ブロックを取得するステップ；及び

前記複数のサブ・ブロック内のサブ・ブロックが前記カレント・ブロックの境界に位置していることに応じて、前記デバイスが、前記サブ・ブロックに対する上の全ての非隣接参照ラインに対する値として、上の隣接参照ラインを使用するステップ；

を含む方法。

## 【0164】

20

## (付記2)

付記1に記載の方法において、前記デバイスが、前記サブ・ブロックに対する左の隣接参照ラインを使用するステップを更に含む方法。

## 【0165】

30

## (付記3)

付記1に記載の方法において、前記カレント・ブロックは、スーパー・ブロック、最大コーディング・ブロック、コーディング・ツリー・ブロック(CTB)、最大コーディング・ユニット(LCU)、所定のサイズの所定のブロックのうちの少なくとも1つを含んでいる、方法。

## 【0166】

## (付記4)

付記1に記載の方法において、前記カレント・ブロックの前記境界は、前記カレント・ブロックの上境界、前記カレント・ブロックの左境界、前記カレント・ブロックの左及び上境界双方のうちの1つを含んでいる、方法。

## 【0167】

40

## (付記5)

付記1に記載の方法において、前記サブ・ブロックに対する上の全ての非隣接参照ラインに対する値として、上の隣接参照ラインを使用するステップは：

前記上の隣接参照ラインからのサンプルを、上の他の全ての非隣接参照ラインにコピーするステップを含む、方法。

## 【0168】

## (付記6)

付記1に記載の方法において、前記デバイスが、前記サブ・ブロックをパーティション化して複数の変換ブロックを取得するステップを更に含む方法。

## 【0169】

50

## (付記 7 )

付記1-6のうちの何れか1項に記載の方法において：

前記複数の変換ブロック内の第1の変換ブロックが前記サブ・ブロックの上境界に位置していることに応じて、前記デバイスが、前記第1の変換ブロックに対する上の全ての非隣接参照ラインに対する値として、前記上の隣接参照ラインを使用するステップ；及び

前記複数の変換ブロック内の第2の変換ブロックが前記サブ・ブロックの上境界に位置していないことに応じて、前記デバイスが、前記第2の変換ブロックに対して前記パラメータにより示される参照ラインを使用するステップ；

を更に含む方法。

## (付記 8 )

ビデオ復号化における多重参照ラインのイントラ予測のための装置であって：

命令を記憶するメモリ；及び

前記メモリと通信するプロセッサ；

を含み、前記プロセッサが前記命令を実行すると、前記プロセッサは、前記装置に：

カレント・ブロックのコーディングされるビデオ・ビットストリームを受信するステップ；

前記コーディングされるビデオ・ビットストリームからパラメータを取り出すステップであって、前記パラメータは、前記カレント・ブロックにおけるイントラ予測のための1つの非隣接参照ラインを示す、ステップ；

前記カレント・ブロックをパーティション化して複数のサブ・ブロックを取得するステップ；及び

前記複数のサブ・ブロック内のサブ・ブロックが前記カレント・ブロックの境界に位置していることに応じて、前記サブ・ブロックに対する上の全ての非隣接参照ラインに対する値として、上の隣接参照ラインを使用するステップ；

を行わせるように構成されている、装置。

## 【0170】

## (付記 9 )

付記8に記載の装置において、前記プロセッサが前記命令を実行すると、前記プロセッサは、前記装置に：

前記サブ・ブロックに対する左の隣接参照ラインを使用するステップ

を行わせるように更に構成されている、装置。

## 【0171】

## (付記 10 )

付記8に記載の装置において、前記カレント・ブロックは、スーパー・ブロック、最大コーディング・ブロック、コーディング・ツリー・ブロック(CTB)、最大コーディング・ユニット(LCU)、所定のサイズの所定のブロックのうちの少なくとも1つを含んでいる、装置。

## 【0172】

## (付記 11 )

付記8に記載の装置において、前記カレント・ブロックの前記境界は、前記カレント・ブロックの上境界、前記カレント・ブロックの左境界、前記カレント・ブロックの左及び上境界双方のうちの1つを含んでいる、装置。

## 【0173】

## (付記 12 )

付記8に記載の装置において、前記プロセッサが、前記サブ・ブロックに対する上の全ての非隣接参照ラインに対する値として、上の隣接参照ラインを使用するステップを前記装置に行わせるように構成されている場合に、前記プロセッサは、前記装置に：

前記上の隣接参照ラインからのサンプルを、上の他の全ての非隣接参照ラインにコピーするステップ

を行わせるように構成されている、装置。

10

20

30

40

50

**【 0 1 7 4 】**

(付記 1 3 )

付記8に記載の装置において、前記プロセッサが前記命令を実行すると、前記プロセッサは、前記装置に：

前記サブ・ブロックをパーティション化して複数の変換ブロックを取得するステップを行わせるように更に構成されている、装置。

**【 0 1 7 5 】**

(付記 1 4 )

付記8-13のうちの何れか1項に記載の装置において、前記プロセッサが前記命令を実行すると、前記プロセッサは、前記装置に：

前記複数の変換ブロック内の第1の変換ブロックが前記サブ・ブロックの上境界に位置していることに応じて、前記第1の変換ブロックに対する上の全ての非隣接参照ラインに対する値として、前記上の隣接参照ラインを使用するステップ；及び

前記複数の変換ブロック内の第2の変換ブロックが前記サブ・ブロックの上境界に位置していないことに応じて、前記第2の変換ブロックに対して前記パラメータにより示される参照ラインを使用するステップ；

を行わせるように更に構成されている、装置。

**【 0 1 7 6 】**

(付記 1 5 )

命令を記憶する非一時的なコンピュータ読み取り可能な記憶媒体であって、前記命令がプロセッサにより実行されると、前記命令は、前記プロセッサに：

カレント・ブロックのコーディングされるビデオ・ビットストリームを受信するステップ；

前記コーディングされるビデオ・ビットストリームからパラメータを取り出すステップであって、前記パラメータは、前記カレント・ブロックにおけるイントラ予測のための1つの非隣接参照ラインを示す、ステップ；

前記カレント・ブロックをパーティション化して複数のサブ・ブロックを取得するステップ；及び

前記複数のサブ・ブロック内のサブ・ブロックが前記カレント・ブロックの境界に位置していることに応じて、前記サブ・ブロックに対する上の全ての非隣接参照ラインに対する値として、上の隣接参照ラインを使用するステップ；

を行わせるように構成されている、非一時的なコンピュータ読み取り可能な記憶媒体。

**【 0 1 7 7 】**

(付記 1 6 )

付記15に記載の非一時的なコンピュータ読み取り可能な記憶媒体において、前記命令が前記プロセッサにより実行されると、前記命令は、前記プロセッサに：

前記サブ・ブロックに対する左の隣接参照ラインを使用するステップ

を行わせるように更に構成されている、記憶媒体。

**【 0 1 7 8 】**

(付記 1 7 )

付記15に記載の非一時的なコンピュータ読み取り可能な記憶媒体において、前記カレント・ブロックは、スーパー・ブロック、最大コーディング・ブロック、コーディング・ツリー・ブロック(CTB)、最大コーディング・ユニット(LCU)、所定のサイズの所定のブロックのうちの少なくとも1つを含んでいる、記憶媒体。

(付記 1 8 )

付記15に記載の非一時的なコンピュータ読み取り可能な記憶媒体において、前記カレント・ブロックの前記境界は、前記カレント・ブロックの上境界、前記カレント・ブロックの左境界、前記カレント・ブロックの左及び上境界双方のうちの1つを含んでいる、記憶媒体。

**【 0 1 7 9 】**

10

20

30

40

50

(付記 19)

付記15に記載の非一時的なコンピュータ読み取り可能な記憶媒体において、前記命令が、前記サブ・ブロックに対する上の全ての非隣接参照ラインに対する値として、上の隣接参照ラインを使用するステップを前記プロセッサに行わせるように構成されている場合に、前記命令は、前記プロセッサに：

前記上の隣接参照ラインからのサンプルを、上の他の全ての非隣接参照ラインにコピーするステップ

を行わせるように構成されている、記憶媒体。

【0180】

(付記 20)

10

付記15に記載の非一時的なコンピュータ読み取り可能な記憶媒体において、前記命令が前記プロセッサにより実行されると、前記命令は、前記プロセッサに：

前記サブ・ブロックをパーティション化して複数の変換ブロックを取得するステップを行わせるように更に構成されている、記憶媒体。

20

30

40

50

## 【図面】

## 【図 1 A】

## 【図 1 B】

10

20

30

40

## 【図 2】

## FIG. 2

(従来技術)

## 【図 3】

0: ブレーナ・モード

1: DCモード

FIG. 1B

(従来技術)

50

【 図 4 】

FIG. 4

【 四 5 】

FIG. 5

【 四 6 】

FIG. 6

【四七】

FIG. 7

【図 8】

FIG. 8

10

【図 9】

FIG. 9

20

【図 10】

FIG. 10

30

【図 11】

FIG. 11

40

SPLIT\_BT\_VER      SPLIT\_BT\_HOR      SPLIT\_BT\_VER      SPLIT\_BT\_HOR

50

【図 1 2】

【図 1 3】

FIG. 13

10

20

【図 1 4】

FIG. 14

30

40

FIG. 15

50

【図 1 6】

【図 1 7】

10

20

30

40

50

【図 1 8】

【図 1 9】

【図 20】

FIG. 20

10

20

30

40

50

---

フロントページの続き

(33) 優先権主張国・地域又は機関

米国(US)

(72) 発明者 ジャオ , シン

アメリカ合衆国 95129 カリフォルニア州 サン ノゼ , フェアホーツ ウェイ 1172

(72) 発明者 リウ , シヤン

アメリカ合衆国 95125 カリフォルニア州 サン ノゼ , ネバダ アベニュー 1155

審査官 松元 伸次

(56) 参考文献 国際公開第2020/226359 (WO , A1 )

Po-Han Lin, et al. , CE3-related: Non-zero reference lines padding method on the top-line of

CTU , Joint Video Experts Team (JVET) of ITU-T SG 16 WP 3 and ISO/IEC JTC 1/SC 29/WG

11 12th Meeting: Macao, CN, 3-12 Oct. 2018 , JVET-L0515-v3 , 廉内DB (送付可) , 201

8年10月07日 , pp.1-2

(58) 調査した分野 (Int.Cl. , DB名)

H 04 N 19 / 00 - 19 / 98