(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6289618号

(P6289618)

(45) 発行日 平成30年3月7日(2018.3.7)

(24) 登録日 平成30年2月16日(2018.2.16)

(51) Int.CI.

H02M 3/28 (2006.01)

F 1

H02M 3/28

P

請求項の数 9 (全 18 頁)

(21) 出願番号 特願2016-519137 (P2016-519137)

(86) (22) 出願日 平成27年3月6日 (2015.3.6)

(86) 国際出願番号 PCT/JP2015/056612

(87) 国際公開番号 WO2015/174123

(87) 国際公開日 平成27年11月19日 (2015.11.19)

審査請求日 平成28年4月27日 (2016.4.27)

(31) 優先権主張番号 特願2014-101080 (P2014-101080)

(32) 優先日 平成26年5月15日 (2014.5.15)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000006013

三菱電機株式会社

東京都千代田区丸の内二丁目7番3号

(74) 代理人 100094916

弁理士 村上 啓吾

(74) 代理人 100073759

弁理士 大岩 増雄

(74) 代理人 100127672

弁理士 吉澤 憲治

(74) 代理人 100088199

弁理士 竹中 岳生

(72) 発明者 近藤 亮太

東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内

最終頁に続く

(54) 【発明の名称】電力変換装置

## (57) 【特許請求の範囲】

## 【請求項 1】

複数のダイオードがフルブリッジ構成され、交流電源からの入力を整流する整流回路と、上記整流回路の直流端子に接続されるリクトルと、第1スイッチング素子および第2スイッチング素子が直列接続され、その接続点を第1交流端とする第1レグと、第3スイッチング素子および第4スイッチング素子が直列接続され、その接続点を第2交流端とする第2レグと、直流コンデンサとが直流母線間に並列接続されて構成され、上記第1交流端が上記整流回路の正極側直流端子に接続され、負極側直流母線が上記整流回路の負極側直流端子に接続されるインバータ回路と、

一次巻線、二次巻線を有し、該一次巻線の両端に上記インバータ回路の上記第1交流端、上記第2交流端が接続される絶縁トランスと、

上記インバータ回路を出力制御する制御回路とを備え、

上記制御回路は、上記第1レグのPWM制御により、上記交流電源から上記整流回路を介して流れる回路電流の高力率制御を行い、上記第1レグのduty比以下のduty比を用いた上記第2レグのPWM制御により、上記直流コンデンサの電圧を制御して上記絶縁トランスの二次側に出力する電力を制御する

電力変換装置。

## 【請求項 2】

上記絶縁トランスの上記二次巻線に接続される第2整流回路と、該第2整流回路の直流端子に接続される第2リクトルとを備え、

10

20

上記制御回路は、上記第2レグをPWM制御することにより上記第2整流回路に接続される直流回路への出力電力を制御する

請求項1に記載の電力変換装置。

【請求項3】

上記制御回路は、

上記第1レグおよび上記第2レグを、同期する等しい駆動周期でPWM制御し、

上記回路電流が目標正弦波電流になるように上記第1レグを制御し、

上記直流コンデンサの電圧が、上記交流電源のピーク電圧よりも高い目標電圧になるよう

に上記第2レグを制御する

請求項1または請求項2に記載の電力変換装置。

10

【請求項4】

上記制御回路は、上記第3スイッチング素子および上記第4スイッチング素子のduty

比を等しくし、該duty比を、上記第1、第2スイッチング素子の2つのduty比内の

小さい方を上限として制限する

請求項3に記載の電力変換装置。

【請求項5】

上記制御回路は、

上記第1スイッチング素子とオンオフが反転するように上記第2スイッチング素子を制御

し、

上記第1スイッチング素子と対角の関係にある上記第4スイッチング素子を、上記第1ス

イッチング素子のオン期間内のみにオン期間を有するように制御し、

上記第2スイッチング素子と対角の関係にある上記第3スイッチング素子を、上記第2ス

イッチング素子のオン期間内のみにオン期間を有するように制御する

請求項3または請求項4に記載の電力変換装置。

20

【請求項6】

上記制御回路は、

上記第1レグ、上記第2レグのPWM制御のキャリア波に鋸波を用い、

上記第1スイッチング素子へのゲート信号パルスの立ち上がりと、上記第4スイッチング

素子へのゲート信号パルスの立ち上がりとを同期させ、

上記第2スイッチング素子へのゲート信号パルスの立ち上がりと、上記第3スイッチング

素子へのゲート信号パルスの立ち上がりとを同期させる

請求項5に記載の電力変換装置。

30

【請求項7】

上記制御回路は、

上記第1レグ、上記第2レグのPWM制御のキャリア波に三角波を用い、

上記第1スイッチング素子へのゲート信号パルスの中心と、上記第4スイッチング素子へ

のゲート信号パルスの中心とを同期させ、

上記第2スイッチング素子へのゲート信号パルスの中心と、上記第3スイッチング素子へ

のゲート信号パルスの中心とを同期させる

請求項5に記載の電力変換装置。

40

【請求項8】

上記制御回路は、

上記第3、第4スイッチング素子の一方の素子へのduty比の指令値を生成し、該duty

比の指令値と上記三角波との比較により上記一方の素子への上記ゲート信号パルスを

生成し、

上記duty比の指令値を1から差し引いた値と上記三角波との比較により、上記第3、

第4スイッチング素子の他方の素子への上記ゲート信号パルスを生成する

請求項7に記載の電力変換装置。

【請求項9】

複数のダイオードがフルブリッジ構成され、交流電源からの入力を整流する整流回路と、

50

上記整流回路の直流端子に接続されるリアクトルと、

第1スイッチング素子および第2スイッチング素子が直列接続され、その接続点を第1交流端とする第1レグと、第3スイッチング素子および第4スイッチング素子が直列接続され、その接続点を第2交流端とする第2レグと、直流コンデンサとが直流母線間に並列接続されて構成され、上記第1交流端が上記整流回路の正極側直流端子に接続され、負極側直流母線が上記整流回路の負極側直流端子に接続されるインバータ回路と、

一次巻線、二次巻線を有し、該一次巻線の両端に上記インバータ回路の上記第1交流端、上記第2交流端が接続される絶縁トランスと、

上記インバータ回路を出力制御する制御回路とを備え、

上記制御回路は、上記第1レグにより入力電流の高力率制御を行い、上記第2レグにより出力電力制御を行う

電力変換装置。

【発明の詳細な説明】

【技術分野】

【0001】

交流電源からの入力を電力変換して絶縁トランスの二次側に所望の電力を供給する電力変換装置に関するものである。

【背景技術】

【0002】

近年、1つの電力変換装置で入力の交流電流の力率制御と、出力電力制御を同時に実現するワンステージ変換方式が提案されている。従来のワンステージ変換方式の電力変換装置として、充電器用のコンバータ回路を以下に示す。

充電器用のコンバータ回路は、2つのダイオードより成るハーフブリッジ整流回路と、前記ハーフブリッジ整流回路の両端に並列接続したコンデンサと、夫々2つのスイッチ素子(1)と(2)より成る第1のハーフブリッジ回路および2つのスイッチ素子(3)と(4)より成る第2のハーフブリッジ回路の両端を前記コンデンサの両端に並列接続して構成した4つのスイッチ素子より成るフルブリッジ回路と、上記第1のハーフブリッジ回路におけるスイッチ素子同士の接続点に一端を接続した交流電源の他端とハーフブリッジ整流回路におけるダイオード同士の接続点との間に設けたリアクタと、前記第1と第2のハーフブリッジ回路におけるスイッチ素子同士の接続点との間を接続した高周波トランスの1次コイルと、前記4つのスイッチ素子に接続した4つの駆動回路と制御回路とによってコンバータの1次回路を構成する。制御回路は、4つのスイッチ素子より成るフルブリッジ回路におけるスイッチ素子(1)と(4)より成るグループ、およびスイッチ素子(2)と(3)より成るグループを交互にオン・オフ制御する。

そして、前記高周波トランスの2次コイルに並列接続したフルブリッジ整流回路と、前記フルブリッジ整流回路の両端に並列接続したコンデンサとによってコンバータの2次回路を構成し、前記1次回路において生成された高周波電力を整流してバッテリーを充電させる(例えば、特許文献1参照)。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開平11-243646号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

このような従来の電力変換装置では、フルブリッジ回路の2つのハーフブリッジ回路を同じduty比で同期して制御している。このため、入力電流の高力率制御を行うと、フルブリッジ回路の直流コンデンサ電圧が動作範囲から外れることがあり、電力変換装置に過電圧が印加されたり、出力電流のリップル成分がより拡大するという問題点があった。

【0005】

10

20

30

40

50

この発明は、上記のような問題点を解決するためになされたものであり、入力電流の高力率制御と、出力電力制御とを高い信頼性で同時に実現できる電力変換装置を提供することを目的とする。

【課題を解決するための手段】

【0006】

この発明に係る第1の電力変換装置は、複数のダイオードがフルブリッジ構成され、交流電源からの入力を整流する整流回路と、上記整流回路の直流端子に接続されるリクトルと、インバータ回路と、絶縁トランスと、上記インバータ回路を出力制御する制御回路とを備える。上記インバータ回路は、第1スイッチング素子および第2スイッチング素子が直列接続され、その接続点を第1交流端とする第1レグと、第3スイッチング素子および第4スイッチング素子が直列接続され、その接続点を第2交流端とする第2レグと、直流コンデンサとが直流母線間に並列接続されて構成され、上記第1交流端が上記整流回路の正極側直流端子に接続され、負極側直流母線が上記整流回路の負極側直流端子に接続される。上記絶縁トランスは、一次巻線、二次巻線を有し、該一次巻線の両端に上記インバータ回路の上記第1交流端、上記第2交流端が接続される。

そして上記制御回路は、上記第1レグのPWM制御により、上記交流電源から上記整流回路を介して流れる回路電流の高力率制御を行い、上記第1レグのduty比以下のduty比を用いた上記第2レグのPWM制御により、上記直流コンデンサの電圧を制御して上記絶縁トランスの二次側に出力する電力を制御する。

【0007】

また、この発明に係る第2の電力変換装置は、複数のダイオードがフルブリッジ構成され、交流電源からの入力を整流する整流回路と、上記整流回路の直流端子に接続されるリクトルと、第1スイッチング素子および第2スイッチング素子が直列接続され、その接続点を第1交流端とする第1レグと、第3スイッチング素子および第4スイッチング素子が直列接続され、その接続点を第2交流端とする第2レグと、直流コンデンサとが直流母線間に並列接続されて構成され、上記第1交流端が上記整流回路の正極側直流端子に接続され、負極側直流母線が上記整流回路の負極側直流端子に接続されるインバータ回路と、一次巻線、二次巻線を有し、該一次巻線の両端に上記インバータ回路の上記第1交流端、上記第2交流端が接続される絶縁トランスと、上記インバータ回路を出力制御する制御回路とを備え、上記制御回路は、上記第1レグにより入力電流の高力率制御を行い、上記第2レグにより出力電力制御を行う。

【発明の効果】

【0008】

この発明の第1の電力変換装置によれば、入力電流の高力率制御と、出力電力制御とを高い信頼性で同時に実現できる。

【0009】

またこの発明の第2の電力変換装置によれば、入力電流の高力率制御と、出力電力制御とを高い信頼性で同時に実現できる。

【図面の簡単な説明】

【0010】

【図1】この発明の実施の形態1による電力変換装置の構成を示す図である。

【図2】この発明の実施の形態1による電力変換装置の動作を説明するゲート信号および各部の波形図である。

【図3】この発明の実施の形態1による電力変換装置の第1モードにおける動作を説明する電流経路図である。

【図4】この発明の実施の形態1による電力変換装置の第2モードにおける動作を説明する電流経路図である。

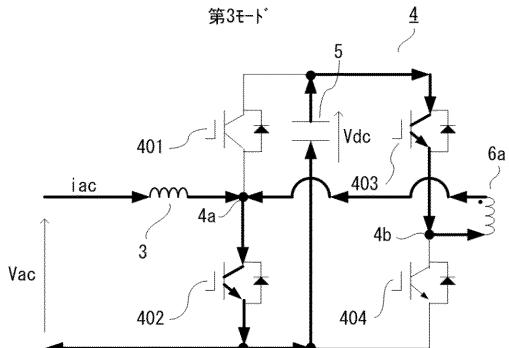

【図5】この発明の実施の形態1による電力変換装置の第3モードにおける動作を説明する電流経路図である。

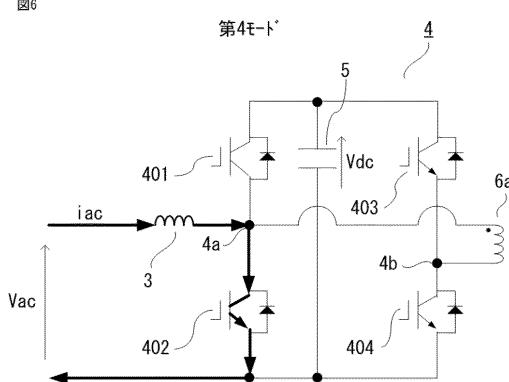

【図6】この発明の実施の形態1による電力変換装置の第4モードにおける動作を説明す

10

20

30

40

50

る電流経路図である。

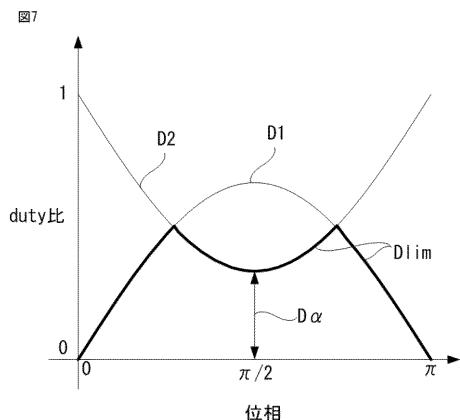

【図7】この発明の実施の形態1による第1レグのduty比を示す図である。

【図8】この発明の実施の形態1による第2レグのduty比を示す図である。

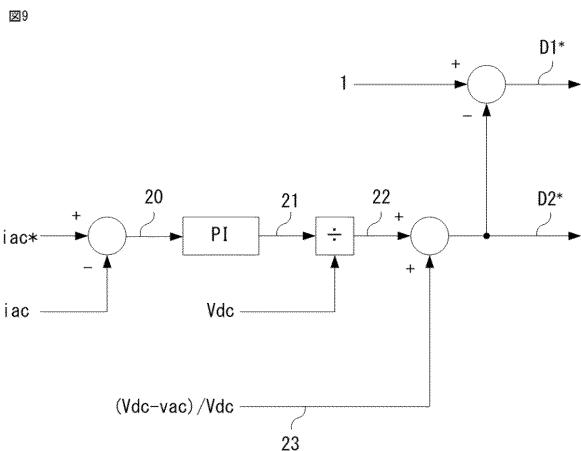

【図9】この発明の実施の形態1による第1レグのduty指令の生成を示す制御プロック図である。

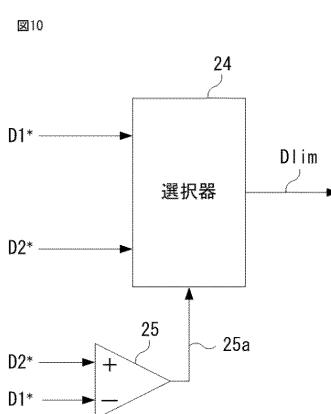

【図10】この発明の実施の形態1による第2レグのduty指令上限の生成を示す制御プロック図である。

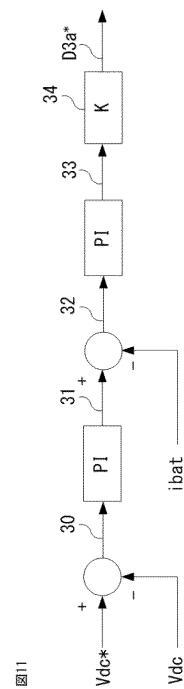

【図11】この発明の実施の形態1による第2レグの基本duty指令の生成を示す制御プロック図である。

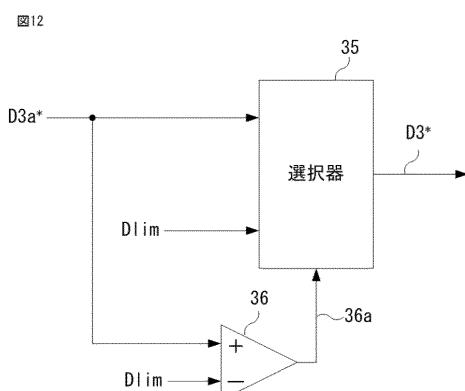

【図12】この発明の実施の形態1による第2レグのduty指令の生成を示す制御プロック図である。 10

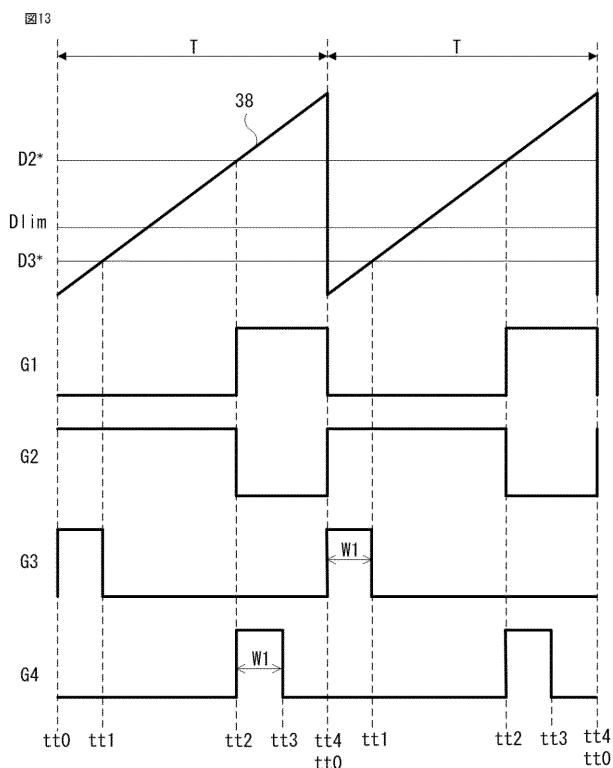

【図13】この発明の実施の形態1による電力変換装置における鋸波を用いたゲート信号の生成を説明する波形図である。

【図14】この発明の実施の形態1による第1レグのゲート信号の生成を示す制御プロック図である。

【図15】この発明の実施の形態1による第2レグのゲート信号の生成を示す制御プロック図である。

【図16】この発明の実施の形態2による電力変換装置における三角波を用いたゲート信号の生成を説明する波形図である。

【図17】この発明の実施の形態2による第1レグのゲート信号の生成を示す制御プロック図である。 20

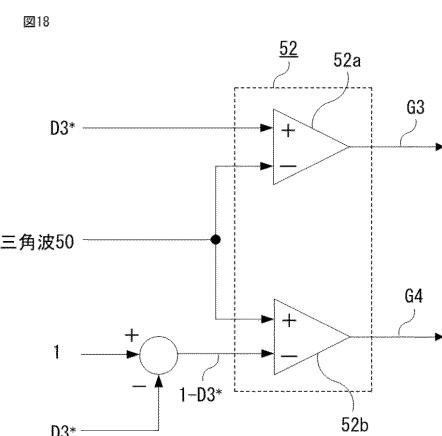

【図18】この発明の実施の形態2による第2レグのゲート信号の生成を示す制御プロック図である。

【発明を実施するための形態】

【0011】

実施の形態1.

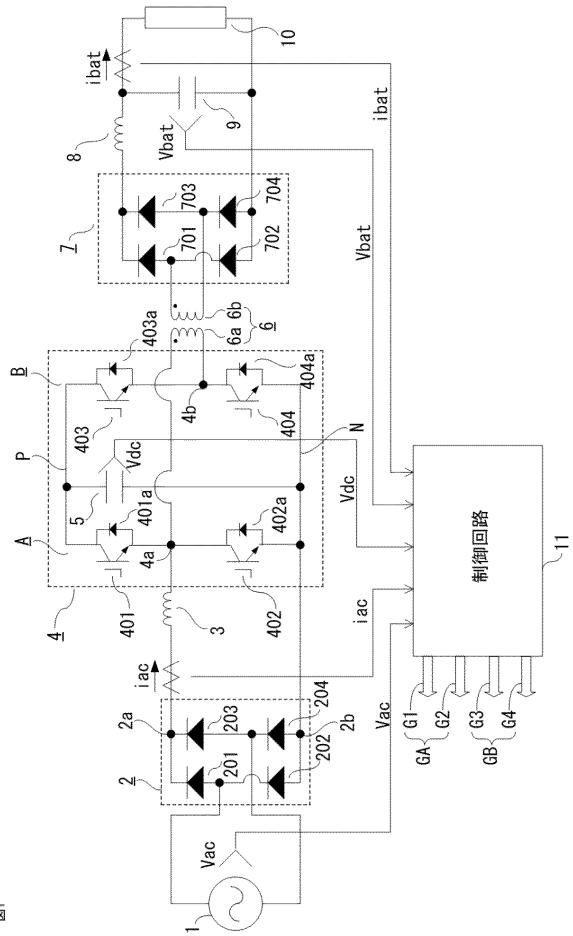

以下、この発明の実施の形態1による電力変換装置について説明する。図1はこの発明の実施の形態1による電力変換装置の概略構成図である。

図1に示すように、電力変換装置は、交流電源1の交流電力を直流電力に変換して直流回路であるバッテリ10に出力するための主回路と制御回路11とを備える。 30

主回路は、交流電源1からの入力を整流する整流回路2と、限流回路としてのリアクトル3と、インバータ回路4と、絶縁トランス6と、第2整流回路7と、第2リアクトルとしての平滑リアクトル8と、平滑コンデンサ9とを備える。

【0012】

整流回路2は4つのダイオード201～204をフルブリッジ構成したダイオード整流回路である。インバータ回路4は、第1スイッチング素子401および第2スイッチング素子402が直列接続され、その接続点を第1交流端4aとする第1レグAと、第3スイッチング素子403および第4スイッチング素子404が直列接続され、その接続点を第2交流端4bとする第2レグBと、直流コンデンサ5とが直流母線間(PN母線間)に並列接続されたフルブリッジインバータ回路である。 40

第2整流回路7は、この場合、4つのダイオード701～704をフルブリッジ構成したダイオード整流回路であるが、その他のダイオードを用いた整流方式や能動素子を用いた整流方式でも良い。

【0013】

絶縁トランス6は、一次巻線6aおよび二次巻線6bを有し、一次巻線6aの両端にインバータ回路4の第1交流端4a、第2交流端4bが接続され、二次巻線6bの両端に第2整流回路7の交流端子が接続される。

また絶縁トランス6の一次側では、交流電源1の出力は整流回路2の交流端子に接続され、整流回路2の正極側直流端子2aはリアクトル3を介してインバータ回路4の第1交流端4aに接続される。整流回路2の負極側直流端子2bは、インバータ回路4の負極側 50

直流母線（以下、N母線）に接続される。

絶縁トランス6の二次側では、平滑コンデンサ9がバッテリ10に並列接続され、第2整流回路7の第1直流出力端子が平滑リアクトル8を介して平滑コンデンサ9の第1端子に接続され、第2整流回路7の第2直流出力端子が平滑コンデンサ9の第2端子に接続される。

【0014】

第1～第4スイッチング素子401～404は、それぞれダイオード401a～404aを逆並列に接続したIGBT（Insulated Gate Bipolar Transistor）で構成される。

なお、第1～第4スイッチング素子401～404は、IGBT以外でも、ソース・ドレイン間にダイオードが内蔵されたMOSFET（Metal Oxide Semiconductor Field Effect Transistor）等の半導体スイッチング素子でもよい。またMOSFETを用いる場合は、内蔵ダイオードをダイオード401a～404aに用いても良い。

【0015】

また、リアクトル3は、整流回路2の正極側直流端子2aに接続しているが、負極側直流端子2bに接続するものでも良く、また、整流回路2の正極側直流端子2a、負極側直流端子2bの双方に分散して接続しても良い。

さらに、直流回路は、バッテリ10の他、交流電源1からの入力と絶縁を必要とする直流負荷であれば良く、例えば電気2重層キャパシタなどで構成してもよい。

【0016】

また、交流電源1の電圧V<sub>a c</sub>、直流コンデンサ5の電圧V<sub>d c</sub>、平滑コンデンサ9の電圧V<sub>b a t</sub>をそれぞれ検出する電圧センサと、交流電源1から整流回路2を介して流れる回路電流としての電流i<sub>a c</sub>、バッテリ10への充電電流（直流電流）i<sub>b a t</sub>をそれぞれ検出する電流センサとが備えられる。この場合、電流i<sub>a c</sub>としてリアクトル3を流れる電流を検出する。

【0017】

制御回路11には、検出された直流コンデンサ電圧V<sub>d c</sub>、平滑コンデンサ電圧V<sub>b a t</sub>、交流電源電圧（交流電圧）V<sub>a c</sub>、電流i<sub>a c</sub>および充電電流i<sub>b a t</sub>が入力され、制御回路11は、これらの値に基づいて高周波PWM制御により、第1～第4スイッチング素子401～404へのゲート信号G1～G4を生成して、インバータ回路4を出力制御する。その際、制御回路11は、交流電源1からの入力力率が概1になるように、即ち、電流i<sub>a c</sub>を高力率制御するように第1レグAへのゲート信号G A（G1、G2）を生成し、かつ直流コンデンサ5の電圧V<sub>d c</sub>が目標電圧V<sub>d c</sub>\*になるように第2レグBへのゲート信号G B（G3、G4）を生成して、第1～第4スイッチング素子401～404をオンオフさせてインバータ回路4を出力制御する。

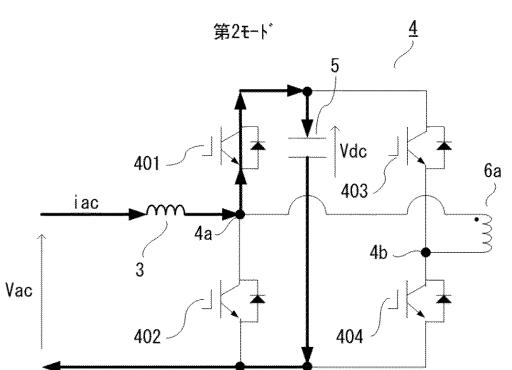

【0018】

このように構成される電力変換装置の動作、即ちバッテリ10に直流電力を出力する動作について、以下に説明する。

図2は、第1～第4スイッチング素子401～404へのゲート信号G1～G4と、電流i<sub>a c</sub>と、直流コンデンサ5の電圧V<sub>d c</sub>とを示す図である。なお、直流コンデンサ5の電圧V<sub>d c</sub>は、目標電圧V<sub>d c</sub>\*を、交流電源1の電圧V<sub>a c</sub>のピーク電圧V<sub>p</sub>より高く設定し、ピーク電圧V<sub>p</sub>より高く制御されている。

交流電源1からの電圧V<sub>a c</sub>は整流回路2で全波整流されるため、交流周期の2倍周期で動作する。ゲート信号G1、G2により動作する第1レグAの第1、第2スイッチング素子401、402は、交流電源1からの入力電流量を一定に、かつ入力力率が概1になるようにPWM制御により電流i<sub>a c</sub>を制御する。またゲート信号G3、G4により動作する第2レグBの第3、第4スイッチング素子403、404は、バッテリ10に供給する電力量と直流コンデンサ5の充放電量を調整して直流コンデンサ5の電圧V<sub>d c</sub>が一定の目標電圧V<sub>d c</sub>\*になるように制御する。以下、交流電源1からの入力力率が概1になるように電流i<sub>a c</sub>を制御することを、単に電流制御と称す。

10

20

30

40

50

## 【0019】

図2に示すように、第1～第4スイッチング素子401～404の駆動周期をTとすると、駆動周期Tは、 $t_0 \sim t_1$ 、 $t_1 \sim t_2$ 、 $t_2 \sim t_3$ 、 $t_3 \sim t_4$  ( $t_0$ )の4期間に分割でき、各期間の動作モードを第1～第4モードとする。

$t_0$  (=  $t_4$ )の時、ゲート信号G1で動作する第1スイッチング素子401がオンしてゲート信号G2で動作する第2スイッチング素子402がオフする。この時、ゲート信号G4で動作する第4スイッチング素子404も同時にオンする。

$t_1$ の時、第4スイッチング素子404がオフする。

$t_2$ の時、第1スイッチング素子401がオフして第2スイッチング素子402がオンする。この時、ゲート信号G3で動作する第3スイッチング素子403も同時にオンする 10

。

$t_3$ の時、第3スイッチング素子403がオフする。

## 【0020】

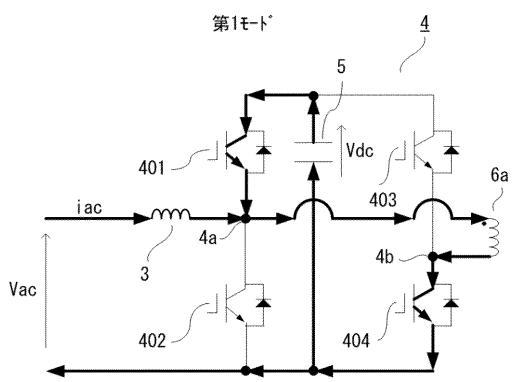

各期間の動作モード毎の動作を説明するための電流経路図を図3～図6に示す。なお、電流経路図はインバータ回路4での電流経路を示す。この場合、リアクトル3に流れる電流*i<sub>ac</sub>*は、交流電源1から整流回路2を介してリアクトル3に流れてインバータ回路4の第1交流端4aに入力される。

$t_0 \sim t_1$ における第1モードでは、第1、第4スイッチング素子401、404が共にオン状態で、図3に示す電流経路で電流が流れる。即ち、リアクトル3に流れる電流*i<sub>ac</sub>*は、絶縁トランジスタ6の一次巻線6aに流れ、第4スイッチング素子404を介して入力側へ戻る。また直流コンデンサ5から第1スイッチング素子401を介して一次巻線6aへ電流が流れ、第4スイッチング素子404を介して直流コンデンサ5へと電流が戻る。 20

この第1モードでは、第1スイッチング素子401がオン状態であるため、リアクトル3のインバータ回路4側の電位は電圧V<sub>dc</sub>に固定される。直流コンデンサ5の電圧V<sub>dc</sub>は、交流電源1の電圧V<sub>ac</sub>のピーク電圧V<sub>p</sub>より高く制御され、リアクトル3に流れる電流*i<sub>ac</sub>*は減少する。また直流コンデンサ5では電流を放電しているため電圧V<sub>dc</sub>は減少する。

## 【0021】

$t_1 \sim t_2$ における第2モードでは、第1スイッチング素子401のみがオン状態で、図4に示す電流経路で電流が流れる。即ち、リアクトル3に流れる電流*i<sub>ac</sub>*は、第1スイッチング素子401を介して直流コンデンサ5へと流入する。第2～第4スイッチング素子402～404はオフ状態であるため、上記以外の電流経路は存在しない。 30

この第2モードでは、第1スイッチング素子401がオン状態であるため、リアクトル3のインバータ回路4側の電位は電圧V<sub>dc</sub>に固定される。直流コンデンサ5の電圧V<sub>dc</sub>は、交流電源1の電圧V<sub>ac</sub>のピーク電圧V<sub>p</sub>より高く制御され、リアクトル3に流れる電流*i<sub>ac</sub>*は減少する。また直流コンデンサ5では電流を充電しているため電圧V<sub>dc</sub>は増加する。

## 【0022】

$t_2 \sim t_3$ における第3モードでは、第2、第3スイッチング素子402、403が共にオン状態で、図5に示す電流経路で電流が流れる。即ち、リアクトル3に流れる電流*i<sub>ac</sub>*は、第2スイッチング素子402を介して入力側へと還流する。また直流コンデンサ5から第3スイッチング素子403を介して一次巻線6aへ電流が流れ、第2スイッチング素子402を介して直流コンデンサ5へと電流が戻る。 40

この第3モードでは、第2スイッチング素子402がオン状態であるため、リアクトル3のインバータ回路4側の電位はN母線の電位0に固定され、リアクトル3に流れる電流*i<sub>ac</sub>*は増加する。また直流コンデンサ5では電流を放電しているため電圧V<sub>dc</sub>は減少する。

## 【0023】

$t_3 \sim t_4$  (=  $t_0$ )における第4モードでは、第2スイッチング素子402のみがオ 50

ン状態で、図 6 に示す電流経路で電流が流れる。即ち、リクトル 3 に流れる電流  $i_{ac}$  は、第 2 スイッチング素子 402 を介して入力側へと還流する。第 1、第 3、第 4 スイッチング素子 401、403、404 はオフ状態であるため、上記以外の電流経路は存在しない。

この第 4 モードでは、第 2 スイッチング素子 402 がオン状態であるため、リクトル 3 のインバータ回路 4 側の電位は N 母線の電位 0 に固定され、リクトル 3 に流れる電流  $i_{ac}$  は増加する。また直流コンデンサ 5 では電流の充放電がなく電圧  $V_{dc}$  は変化しない。

#### 【0024】

第 1 モードおよび第 3 モードでは、絶縁トランス 6 に電流が流れ、第 1 モードと第 3 モードとで一次巻線 6a に流れる電流極性は反転している。即ち、絶縁トランス 6 に交流電流が入力され、二次巻線 6b に接続される第 2 整流回路にて交流電力を直流電力に変換し、平滑リクトル 8 および平滑コンデンサ 9 にて直流電力を平滑してバッテリ 10 に電力供給する。このように、第 1 モードおよび第 3 モードにてバッテリ 10 に直流電力を供給する。

なお、第 1 モードと第 3 モードとで絶縁トランス 6 に逆極性に電流が流れるため、絶縁トランス 6 の偏磁を抑制するために、第 1 モードと第 3 モードとの期間は等しく設定する。即ち、第 4 スイッチング素子 404 のオン期間と第 3 スイッチング素子 403 のオン期間とは等しく、duty 比は等しく制御される。

#### 【0025】

図 2 に示すように、第 1 スイッチング素子 401 と第 2 スイッチング素子 402 とはオンオフが反転する制御であり、第 1 スイッチング素子 401 のオン期間に電流  $i_{ac}$  が減少し、第 2 スイッチング素子 402 のオン期間に電流  $i_{ac}$  が増加する。図 2 における  $t_2$  を調整する、即ち、第 1、第 2 スイッチング素子 401、402 の duty 比を調整することで、電流  $i_{ac}$  の増減を調整して電流制御を実現できる。

#### 【0026】

また、第 4 スイッチング素子 404 は、第 1 スイッチング素子 401 のオン期間内のみにオン期間を有し、第 3 スイッチング素子 403 は、第 2 スイッチング素子 402 のオン期間内のみにオン期間を有する。そして、第 3、第 4 スイッチング素子 403、404 のオン期間に電圧  $V_{dc}$  が減少し、第 1 スイッチング素子 401 のみがオンする期間で電圧  $V_{dc}$  が増加する。図 2 における  $t_3$ 、 $t_1$  を調整する、即ち、第 3、第 4 スイッチング素子 403、404 の duty 比を調整することで、直流コンデンサ 5 の電圧  $V_{dc}$  の増減を調整して目標電圧  $V_{dc}^*$  に維持する。

#### 【0027】

このように、第 1 レグ A の第 1、第 2 スイッチング素子 401、402 を用いた電流  $i_{ac}$  の電流制御と、第 2 レグ B の第 3、第 4 スイッチング素子 403、404 を用いた電圧  $V_{dc}$  の電圧制御とを、それぞれ個別の duty 比を用いて行うことで、電流制御と電圧制御とを同時に実現しながらバッテリ 10 に直流電力を供給する。この電流制御と電圧制御の詳細について、以下に詳述する。

#### 【0028】

まず、 $t_2$  は電流制御によって定まるタイミングであり、第 1 スイッチング素子 401 における駆動周期  $T$  あたりのオン期間 ( $t_0 - t_2$ ) である duty 比  $D_1$  は、(式 1) で表される。また、第 2 スイッチング素子 402 における駆動周期  $T$  あたりのオン期間 ( $t_2 - t_4$ ) である duty 比  $D_2$  は(式 2) で表される。但し、 $v_{ac}$  は交流電源 1 の電圧波形、 $V_{dc}$  は直流コンデンサ 5 の電圧である。

#### 【0029】

$$D_1 = v_{ac} / V_{dc} \quad \dots \text{ (式 1)}$$

$$D_2 = (V_{dc} - v_{ac}) / V_{dc} \quad \dots \text{ (式 2)}$$

#### 【0030】

第 1、第 2 スイッチング素子 401、402 は、上記(式 1)、(式 2)に基づく  $d$  u

10

20

30

40

50

$t_y$  比で駆動される。

【0031】

また、第4スイッチング素子404は第1スイッチング素子401と同時にオンし、第3スイッチング素子403は第2スイッチング素子402と同時にオンし、第4スイッチング素子404のオン期間( $t_0 - t_1$ )と第3スイッチング素子403のオン期間( $t_2 - t_3$ )とは等しい。第3、第4スイッチング素子403、404における駆動周期Tあたりのオン期間であるduty比 $D_3$ 、 $D_4$ は、(式3)で表される。但し、 $V_{bat}$ は平滑コンデンサ9の電圧、 $N_1$ は絶縁トランス6の一次巻線6aの巻き数、 $N_2$ は絶縁トランス6の二次巻線6bの巻き数である。

【0032】

$$D_3 = D_4 = (1/2) \cdot (V_{bat} / V_{dc}) \cdot (N_2 / N_1) \quad \dots \quad (\text{式3})$$

【0033】

また、第4スイッチング素子404は、第1スイッチング素子401のオン期間内のみにオン期間を有し、第3スイッチング素子403は、第2スイッチング素子402のオン期間内のみにオン期間を有する。このため、duty比 $D_3$ 、 $D_4$ は、常にduty比 $D_1$ 、 $D_2$ より小さく、 $t_0 \sim t_4$ の関係は、

$$t_0 \quad t_1 \quad t_2, \quad t_2 \quad t_3 \quad t_4$$

となる。

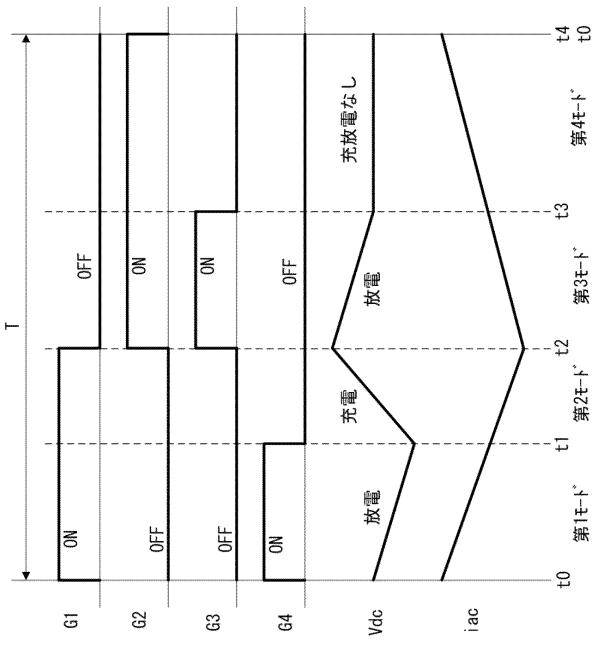

【0034】

第1レグAのduty比 $D_1$ 、 $D_2$ の概略duty軌跡図と、第2レグBのduty比 $D_3$ ( $D_4$ )の上限となる $D_{lim}$ とを図7に示す。 $D_{lim}$ の各点は、その位相における、 $\min(D_1, D_2)$ であり、即ち、 $D_{lim}$ は、 $D_1$ 、 $D_2$ の小さい方のduty比である。

図7に示すように、 $D_1$ は交流電圧のゼロクロス位相0、 $\pi/2$ となり、位相 $\pi/2$ ではピーク値となる。このため、位相0、 $\pi/2$ 付近では $D_{lim} = D_1$ となる。この場合、位相 $\pi/2$ 付近では、 $D_2 < D_1$ であり、 $D_{lim} = D_2$ となる。

また、位相 $\pi/2$ の時の $D_{lim}$ の値 $D$ は、(式4)で表される。但し、 $V_p$ は交流電圧 $V_{ac}$ のピーク電圧である。

【0035】

$$D = \min(V_p / V_{dc}, (V_{dc} - V_p) / V_{dc}) \quad \dots \quad (\text{式4})$$

【0036】

duty比 $D_3$ ( $D_4$ )を $D_{lim}$ より小さくすることで、絶縁トランス6への電流通流期間である第1モードおよび第3モードの期間を調整して電圧 $V_{dc}$ の制御を実現できる。ここでは、電圧 $V_{dc}$ の制御が可能となる条件、即ち可制御条件を以下の式で示す。

$$D_3(D_4) < D$$

即ち、

$$(1/2) \cdot (V_{bat} / V_{dc}) \cdot (N_2 / N_1) < \min(V_p / V_{dc}, (V_{dc} - V_p) / V_{dc}) \quad \dots \quad (\text{式5})$$

【0037】

図8は、第2レグBのduty比 $D_3$ ( $D_4$ )を示す図である。上記(式5)で示す可制御条件を満たすとき、(式3)で演算される $D_3$ ( $D_4$ )の値を基本duty比 $D_{3a}$ とし、

$$D_{3a} < D_{lim}$$

$$D_{3a} = D_{lim}$$

とする。

交流電圧のゼロクロス位相0、 $\pi/2$ 付近では $D_{lim}$ が原理上限りなく0に近い。このため、 $D_3$ ( $D_4$ )の演算値が $D_{lim}$ 以上となる位相範囲で $D_3$ ( $D_4$ )を $D_{lim}$ の値に設定する。それ以外の位相範囲では、上記可制御条件から、 $D_3$ ( $D_4$ )は $D_{lim}$ より小さい。これにより、全位相においてduty比 $D_3$ ( $D_4$ )を $D_{lim}$ より小さくでき、電圧 $V_{dc}$ を制御できる。

## 【0038】

このように、第2レグBの第3、第4スイッチング素子403、404のduty比D3(D4)を、位相に拘わらず、第1レグAの第1、第2スイッチング素子401、402のduty比D1、D2より小さくすることができ、電圧Vdcを一定の目標電圧Vdc<sup>\*</sup>に制御できる。この電圧制御は、出力電力量を制御して電圧Vdcを制御する出力電力制御である。

これにより、第1レグAのduty制御により電流制御を行い、第2レグBのduty制御により出力電力制御を行い、即ち、電流制御と出力電力制御とをフルブリッジ構成の1つのインバータ回路4で実現することができる。

## 【0039】

10

一般に単相系統に接続される単相インバータでは直流部に交流周波数の2倍の周波数の電圧脈動が発生する。この実施の形態では、直流コンデンサ5の充電と放電とをインバータ回路4の駆動周期T内で行うため、発生する電圧脈動は駆動周期Tに基づき、特に、第2モードにおける充電期間で規定される。このためインバータ回路4では、交流周波数の2倍の周波数の電圧脈動は発生せず、直流コンデンサ5の容量を大幅に低減することができ、直流コンデンサ5を小型化することができる。

## 【0040】

交流電源1にて、力率1の電圧vacと電流iacは、(式6)、(式7)で定義される。交流電源1の電力Pacは(式8)となる。この実施の形態では、(式8)で示す電力Pacがすべてバッテリ10へと伝送される。バッテリ10が一定の電圧Vbatであると、バッテリ10に供給される電流ibatは(式9)となり、交流周波数の2倍の周波数の脈動成分を有するものとなる。但し、vac、Iacは交流電源1の電圧実効値、電流実効値である。

20

## 【0041】

$$vac = (2) Vac \cdot \sin(t) \quad \dots \text{ (式6)}$$

$$iac = (2) Iac \cdot \sin(t) \quad \dots \text{ (式7)}$$

$$Pac = Vac \cdot Iac (1 - \cos(2t)) \quad \dots \text{ (式8)}$$

$$ibat = (Vac / Vbat) \cdot Iac (1 - \cos(2t)) \quad \dots \text{ (式9)}$$

## 【0042】

次に、電流制御と電圧制御とを行うためのduty比D1～D4の指令値の生成について説明する。以下、duty比の指令値をduty指令と称す。

30

図9は、制御回路11による第1レグAのduty指令の生成を示す制御ブロック図である。D1<sup>\*</sup>、D2<sup>\*</sup>は、第1、第2スイッチング素子401、402をPWM制御する為のduty指令である。このduty指令D1<sup>\*</sup>、D2<sup>\*</sup>により、交流電源1からの電流量を制御し、交流電源1からの入力力率が概1になるように電流iacを制御する。

## 【0043】

図9に示すように、交流電源1の電圧vacに同期した正弦波の電流指令(目標正弦波電流)iac<sup>\*</sup>と検出された電流iacとの差20をフィードバック量として、PI制御した出力21を電圧Vdcで割ることで、第2スイッチング素子402の基準duty指令22を求める。そして基準duty指令22にフィードフォワード項23を加算して第2スイッチング素子402のduty指令D2<sup>\*</sup>とする。フィードフォワード項23は、上記(式2)で示す(Vdc - vac) / Vdcであり、交流電源1の位相に従ってインバータ回路4の駆動周期毎に決定する。また、1からduty指令D2<sup>\*</sup>を減算した値を、第1スイッチング素子401のduty指令D1<sup>\*</sup>とする。

40

## 【0044】

図10は、第2レグBのduty指令上限となるD1imの生成を示す制御ブロック図である。図10に示すように、D1<sup>\*</sup>、D2<sup>\*</sup>は、選択器24に入力されると共に、比較器25にも入力される。選択器24は、比較器25からの比較信号25aに基づいてD1<sup>\*</sup>、D2<sup>\*</sup>のいずれか一方をD1imとして出力する。

D2<sup>\*</sup>がD1<sup>\*</sup>の値以上である時、比較器25からの比較信号25aはHとなり、選択

50

器 2 4 は  $D 1^*$  を  $D 1 i m$  として出力する。  $D 2^*$  が  $D 1^*$  の値未満である時、比較器 2 5 からの比較信号 2 5 a は L となり、選択器 2 4 は  $D 2^*$  を  $D 1 i m$  として出力する。

#### 【 0 0 4 5 】

図 1 1 は、第 2 レグ B の基本  $d u t y$  指令の生成を示す制御ブロック図である。  $D 3 a^*$  は、図 8 で示す基本  $d u t y$  比  $D 3 a$  の指令値、即ち、基本  $d u t y$  指令である。この基本  $d u t y$  指令  $D 3 a^*$  は、出力電力量を制御して電圧  $V d c$  を目標電圧  $V d c^*$  に維持するように演算される。

図 1 1 に示すように、直流コンデンサ 5 の目標電圧  $V d c^*$  と検出された電圧  $V d c$  との差 3 0 をフィードバック量として、P I 制御した出力をバッテリ 1 0 への出力電流指令値 3 1 とする。この出力電流指令値 3 1 と検出された電流  $i b a t$  との差分 3 2 をフィードバック量として P I 制御した出力 3 3 を、ゲイン調整器 3 4 にて調整して、基本  $d u t y$  指令  $D 3 a^*$  を生成する。

#### 【 0 0 4 6 】

図 1 2 は、第 2 レグ B の  $d u t y$  指令の生成を示す制御ブロック図である。  $D 3^*$  (=  $D 4^*$ ) は、第 3、第 4 スイッチング素子 4 0 3、4 0 4 を PWM 制御する為の  $d u t y$  指令である。

図 1 2 に示すように、基本  $d u t y$  指令  $D 3 a^*$  と  $D 1 i m$  とは、選択器 3 5 に入力されると共に、比較器 3 6 にも入力される。選択器 3 5 は、比較器 3 6 からの比較信号 3 6 a に基づいて  $D 3 a^*$ 、 $D 1 i m$  のいずれか一方を  $D 3^*$  として出力する。

$D 3 a^*$  が  $D 1 i m$  の値以上である時、比較器 3 6 からの比較信号 3 6 a は H となり、選択器 3 5 は  $D 1 i m$  を  $D 3^*$  として出力する。  $D 3 a^*$  が  $D 1 i m$  の値未満である時、比較器 3 6 からの比較信号 3 6 a は L となり、選択器 3 5 は  $D 3 a^*$  を  $D 3^*$  として出力する。

#### 【 0 0 4 7 】

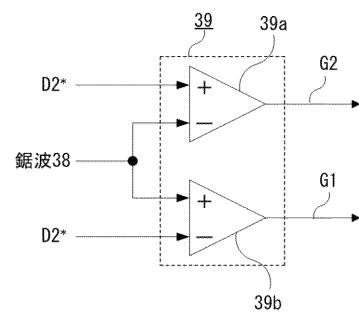

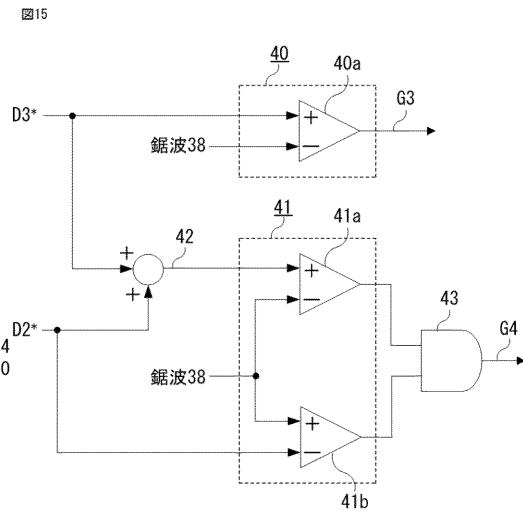

次に、インバータ回路 4 の第 1 ~ 第 4 スイッチング素子 4 0 1 ~ 4 0 4 を制御するゲート信号  $G 1$  ~  $G 4$  の生成について、図 1 3 ~ 図 1 5 に基づいて以下に説明する。図 1 3 は、ゲート信号  $G 1$  ~  $G 4$  の生成を説明する波形図であり、図 1 4 は、第 1 レグ A のゲート信号  $G 1$ 、 $G 2$  の生成を示す制御ブロック図、図 1 5 は、第 2 レグ B のゲート信号  $G 3$ 、 $G 4$  の生成を示す制御ブロック図である。

図 1 3 に示すように、ゲート信号  $G 1$  ~  $G 4$  は、第 1 レグ A、第 2 レグ B の  $d u t y$  指令とキャリア波とを用いた PWM 制御により生成され、この場合、キャリア波に鋸波 3 8 を用いる。第 1 レグ A の  $d u t y$  指令として  $D 2^*$  を用い、第 2 レグ B の  $d u t y$  指令は  $D 3^*$  (=  $D 4^*$ ) を用いる。なお、各ゲート信号  $G 1$  ~  $G 4$  の生成に用いる鋸波 3 8 は、同位相、同じ値の波形である。

#### 【 0 0 4 8 】

図 1 4 に示すように、第 1 レグ A のゲート信号生成器 3 9 は、2 つの比較器 3 9 a、3 9 b を備え、それぞれ  $D 2^*$  と鋸波 3 8 とを比較してゲート信号  $G 2$ 、 $G 1$  を生成する。

$D 2^*$  が鋸波 3 8 の値以上の期間 ( $t t 0$  ~  $t t 2$ ) で、ゲート信号  $G 2$  は H となり、第 2 スイッチング素子 4 0 2 をオン状態にする。また、鋸波 3 8 の値が  $D 2^*$  以上の期間 ( $t t 2$  ~  $t t 4$  (=  $t t 0$ )) で、ゲート信号  $G 1$  は H となり、第 1 スイッチング素子 4 0 1 をオン状態にする。

#### 【 0 0 4 9 】

図 1 5 に示すように、第 2 レグ B のゲート信号  $G 3$  を生成するゲート信号生成器 4 0 は 1 つの比較器 4 0 a を備える。また、ゲート信号  $G 4$  は、2 つの比較器 4 1 a、4 1 b を備えるゲート信号生成器 4 1 と AND 回路 4 3 とを用いて生成する。

ゲート信号  $G 3$  を生成するゲート信号生成器 4 0 では、比較器 4 0 a が  $D 3^*$  と鋸波 3 8 とを比較してゲート信号  $G 3$  を生成する。  $D 3^*$  が鋸波 3 8 の値以上の期間 ( $t t 0$  ~  $t t 1$ ) で、ゲート信号  $G 3$  は H となり、第 3 スイッチング素子 4 0 3 をオン状態にする。また、ゲート信号  $G 2$ 、 $G 3$  は共に  $t t 0$  で立ち上がり、即ち、ゲート信号パルスの立ち上がりが同期する。

## 【0050】

ゲート信号生成器41では、比較器41aは、D2\*とD3\*とを加算した和42と、鋸波38とを比較し、比較器41bは、鋸波38とD2\*とを比較する。2つの比較器41a、41bからの比較信号はAND回路43に入力され、AND回路43は論理積を生成してゲート信号G4を出力する。ゲート信号G4は、鋸波38がD2\*の値以上となるタイミング(tt2)から、D3\*に基づくゲート信号G3のパルス幅W1だけHとなり、期間(tt2~tt3)で第4スイッチング素子404をオン状態にする。また、ゲート信号G1、G4は共にtt2で立ち上がり、即ち、ゲート信号パルスの立ち上がりが同期する。

## 【0051】

なお、図13におけるtt0、tt1、tt2、tt3は、図2におけるt2、t3、t4(t0)、t1に対応するものである。即ち、tt0~tt1、tt1~tt2、tt2~tt3、tt3~tt4(t0)の各期間の動作モードは、順に第3モード、第4モード、第1モード、第2モードとなる。

## 【0052】

以上のように、この実施の形態では、第1レグAをduty比D1、D2を調整してPWM制御することにより、交流電源1から整流回路2を介して流れる電流iacの高力率制御を行い、第2レグBをduty比D3(D4)をduty比D1、D2以下の値で調整してPWM制御することにより、直流コンデンサ5の電圧Vdcを制御して絶縁トランス6の二次側に出力する電力を制御する。これにより、電流制御と出力電力制御とをフルブリッジ構成の1つのインバータ回路4で実現することができ、電力変換装置の簡略化、小型化を実現することができる。

## 【0053】

また、制御回路11は、第1レグAおよび第2レグBを、同期する等しい駆動周期TでPWM制御し、電流iacが目標正弦波電流である電流指令iac\*になるように第1レグAを制御するduty指令D1\*、D2\*を生成し、直流コンデンサ5の電圧Vdcが、交流電源1のピーク電圧Vpよりも高い目標電圧Vdc\*になるように第2レグBを制御するduty指令D3\*(D4\*)を生成する。これにより、電流iacの高力率制御と電圧Vdcを目標電圧Vdc\*に維持する出力電力制御とを、信頼性良く実現できる。

## 【0054】

また、第2レグBの第3、第4スイッチング素子403、404を制御するduty比D3、D4が等しくなるよう制御するため、絶縁トランス6の偏磁を抑制する。さらに、duty比D3、D4を、第1、第2スイッチング素子401、402のduty比D1、D2内の小さい方を上限D1imとして制限するようにした。このため、第4スイッチング素子404を、第1スイッチング素子401のオン期間内のみにオン期間を有するように、また第3スイッチング素子403を、第2スイッチング素子402のオン期間内のみにオン期間を有するように制御することができる。このため、直流コンデンサ5の充電と放電との期間を確実に制御でき、電圧Vdcを目標電圧Vdc\*に信頼性良く制御できる。

## 【0055】

また、第1レグA、第2レグBのPWM制御のキャリア波に鋸波38を用い、第1スイッチング素子401へのゲート信号パルスの立ち上がりと、第4スイッチング素子404へのゲート信号パルスの立ち上がりとを同期させ、第2スイッチング素子402へのゲート信号パルスの立ち上がりと、第3スイッチング素子403へのゲート信号パルスの立ち上がりとを同期させるようにゲート信号G1~G4を生成する。このため、高力率制御による制約条件内で、第2レグBのduty比D3(D4)を自由に調整することが可能となり、高力率制御と出力電力制御とを信頼性良く独立して実現でき、伝送電力の品質をより高め、より信頼性の高い電力変換装置の出力制御を実現することができる。

## 【0056】

また、この実施の形態では、直流コンデンサ5の充電と放電とをインバータ回路4の駆

10

20

30

40

50

動周期 T 内で行うため、発生する電圧脈動は駆動周期 T に基づく。このため、交流電源 1 にて生じる交流電源周期の 2 倍の周波数で脈動する電力脈動はすべて絶縁トランス 6 の二次側のバッテリ 10 に伝達され、交流電源周期の 2 倍の周波数の電力脈動を直流コンデンサ 5 で担保する必要がない。直流コンデンサ 5 は、インバータ回路 4 の駆動周期 T に起因した充放電だけを担保すればよく、大幅な容量低減により小型化が図れる。

#### 【0057】

なお、上記実施の形態では、第 1、第 4 スイッチング素子 401、404 へのゲート信号パルスの立ち上がりを同期させ、第 2、第 3 スイッチング素子 402、403 へのゲート信号パルスの立ち上がりを同期させたものを示したが、双方ともゲート信号パルスの立ち下がりを同期させる様にしても良い。

10

#### 【0058】

また、第 1 レグ A の第 1、第 2 スイッチング素子 401、402 のスイッチングに短絡防止用のデッドタイムを設けても良い。同様に、第 2 レグ B の第 3、第 4 スイッチング素子 403、404 のスイッチングに短絡防止用のデッドタイムを設けても良い。

#### 【0059】

また、リアクトル 3 を、負極側直流端子 2b に接続する場合、あるいは整流回路 2 の正極側直流端子 2a、負極側直流端子 2b の双方に分散して接続する場合も、上記実施の形態と同様に、第 1 レグ A を PWM 制御することにより電流制御を行い、第 2 レグ B を PWM 制御することにより、直流コンデンサ 5 の電圧 Vdc を制御することにより、上記実施の形態と同様の効果が得られる。

20

#### 【0060】

なお上記実施の形態では、電力変換装置は、絶縁トランス 6 の二次側構成、即ち、第 2 整流回路 7、平滑リアクトル 8 および平滑コンデンサ 9 を有して構成するものとしたが、それら二次側回路はこれに限るものではなく、また電力変換装置内では省略し、他装置で構成されたものと接続して用いても良い。

#### 【0061】

#### 実施の形態 2 .

以下、この発明の実施の形態 2 による電力変換装置について説明する。上記実施の形態 1 では、インバータ回路 4 の PWM 制御のキャリア波に鋸波 38 を用いたが、この実施の形態 2 では、キャリア波に三角波を用いる。この実施の形態 2 による電力変換装置は、主回路構成および各 duty 指令 D1\* ~ D4\* の生成については、上記実施の形態 1 と同様である。

30

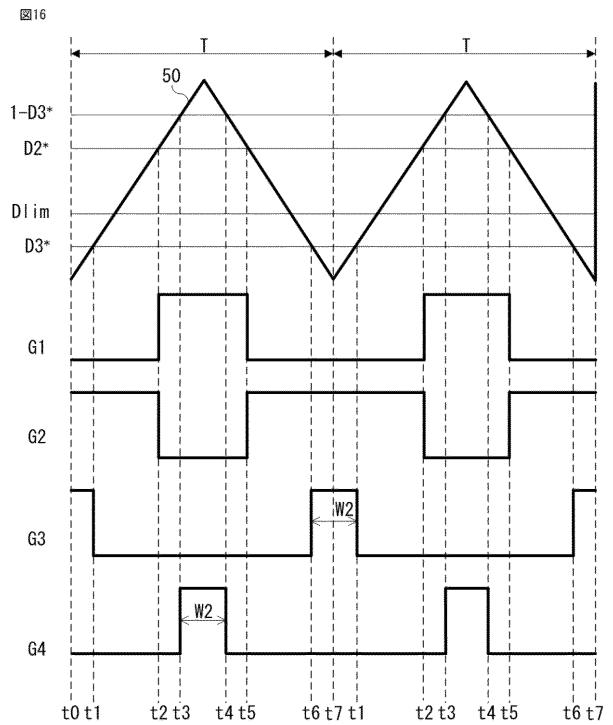

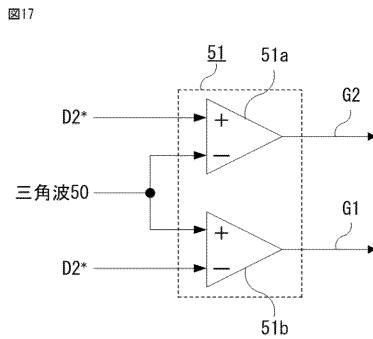

この実施の形態 2 におけるインバータ回路 4 の第 1 ~ 第 4 スイッチング素子 401 ~ 404 を制御するゲート信号 G1 ~ G4 の生成について、図 16 ~ 図 18 に基づいて以下に説明する。図 16 は、ゲート信号 G1 ~ G4 の生成を説明する波形図であり、図 17 は、第 1 レグ A のゲート信号 G1、G2 の生成を示す制御プロック図、図 18 は、第 2 レグ B のゲート信号 G3、G4 の生成を示す制御プロック図である。

#### 【0062】

図 16 に示すように、ゲート信号 G1 ~ G4 は、第 1 レグ A、第 2 レグ B の duty 指令とキャリア波とを用いた PWM 制御により生成され、この場合、キャリア波に三角波 50 を用いる。第 1 レグ A の duty 指令として D2\* を用い、第 2 レグ B の duty 指令は D3\* (= D4\*) を用いる。なお、各ゲート信号 G1 ~ G4 の生成に用いる三角波 50 は同一である。

40

#### 【0063】

図 17 に示すように、第 1 レグ A のゲート信号生成器 51 は、2 つの比較器 51a、51b を備え、それぞれ D2\* と三角波 50 とを比較してゲート信号 G2、G1 を生成する。

D2\* が三角波 50 の値以上の期間 (t0 ~ t2、t5 ~ t7 (t0)) で、ゲート信号 G2 は H となり、第 2 スイッチング素子 402 をオン状態にする。また、三角波 50 の値が D2\* 以上の期間 (t2 ~ t5) で、ゲート信号 G1 は H となり、第 1 スイッチング

50

素子401をオン状態にする。

【0064】

図18に示すように、第2レグBのゲート信号生成器52は、2つの比較器52a、52bを備える。比較器52aは、D3\*と三角波50とを比較してゲート信号G3を生成する。D3\*が三角波50の値以上の期間(t6～t0(t7)～t1)で、ゲート信号G3はHとなり、第3スイッチング素子403をオン状態にする。また、ゲート信号G2、G3によるゲート信号パルスの中心は、三角波50の下のピーク位相で同期する。

比較器52bは、三角波50と、1からD3\*を減算した値であるduty指令(1-D3\*)とを比較してゲート信号G4を生成する。三角波50が(1-D3\*)以上の期間(t3～t4)で、ゲート信号G4はHとなり、第4スイッチング素子404をオン状態にする。ゲート信号G3、G4によるゲート信号パルスのパルス幅W2は等しく、第3、第4スイッチング素子403、404のオン期間の長さは同じである。また、ゲート信号G1、G4によるゲート信号パルスの中心は、三角波50の上のピーク位相で同期する。

【0065】

この実施の形態による電力変換装置においても、上記実施の形態1で示した4種の動作モードにより動作する。t0～t1は第3モード、t1～t2は第4モード、t2～t3は第2モード、t3～t4は第1モード、t4～t5は第2モード、t5～t6は第4モード、t6～t7(t0)は第3モードにて動作する。

【0066】

以上のように、この実施の形態2においても、第1レグAをduty比D1、D2を調整してPWM制御することにより、交流電源1から整流回路2を介して流れる電流iacの高力率制御を行い、第2レグBをduty比D3(D4)をduty比D1、D2以下の値で調整してPWM制御することにより、直流コンデンサ5の電圧Vdcを制御して絶縁トランス6の二次側に出力する電力を制御する。これにより、上記実施の形態1と同様に電流制御と出力電力制御とをフルブリッジ構成の1つのインバータ回路4で実現することができ、電力変換装置の簡略化、小型化を実現することができる。

【0067】

また、第1レグA、第2レグBのPWM制御のキャリア波に三角波50を用い、第1スイッチング素子401へのゲート信号パルスの中心と、第4スイッチング素子404へのゲート信号パルスの中心とを三角波50の上のピーク位相で同期させ、第2スイッチング素子402へのゲート信号パルスの中心と、第3スイッチング素子403へのゲート信号パルスの中心とを三角波50の下のピーク位相で同期させるようにゲート信号G1～G4を生成する。このため、高力率制御による制約条件内で、第2レグBのduty比D3(D4)を自由に調整することが可能となり、高力率制御と出力電力制御とを信頼性良く独立して実現でき、伝送電力の品質をより高め、より信頼性の高い電力変換装置の出力制御を実現することができる。

【0068】

また、キャリア波に三角波50を用いることで、第2モードと第4モードとの合計期間、即ち絶縁トランス6に電力を伝送しない期間が、駆動周期Tの中で三角波50のピーク位相を中心に対称となる。このため、第1モードにて絶縁トランス6に電流を通流した後に第2モードにてトランス電流が減少する際、第4スイッチング素子404を流れる電流量と、第3モードにて絶縁トランス6に電流を通流した後に第4モードにてトランス電流が減少する際、第3スイッチング素子403を流れる電流量とが等しくなる。これにより第3、第4スイッチング素子403、404の損失が均一となり、放熱構成が簡略化でき、電力変換装置の小型化が促進できる。

【0069】

なお、この発明は、発明の範囲内において、各実施の形態を自由に組み合わせたり、各実施の形態を適宜、変形、省略することが可能である。

10

20

30

40

【図1】

【図3】

図3

【図4】

図4

【図2】

【図5】

図5

【図6】

図6

【図7】

【図8】

【図11】

【図9】

【図10】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

---

フロントページの続き

(72)発明者 高原 貴昭

東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内

(72)発明者 村上 哲

東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内

(72)発明者 山田 正樹

東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内

(72)発明者 上原 直久

東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内

(72)発明者 木下 英彦

東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内

審査官 戸次 一夫

(56)参考文献 特開2012-249454 (JP, A)

特開2007-068396 (JP, A)

特開平11-055950 (JP, A)

特開2012-050264 (JP, A)

特開2012-249375 (JP, A)

米国特許出願公開第2011/0149609 (US, A1)

特開平11-243646 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H02M3/00 - 3/44

7/00 - 7/40