(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3580452号

(P3580452)

(45) 発行日 平成16年10月20日(2004.10.20)

(24) 登録日 平成16年7月30日(2004.7.30)

(51) Int.CI.<sup>7</sup>

F 1

H 01 L 21/60

H 01 L 21/92 604 C

H 01 L 21/301

H 01 L 21/78 Q

請求項の数 1 (全 9 頁)

(21) 出願番号

特願平7-260728

(22) 出願日

平成7年9月12日(1995.9.12)

(65) 公開番号

特開平9-82717

(43) 公開日

平成9年3月28日(1997.3.28)

審査請求日

平成14年9月12日(2002.9.12)

前置審査

(73) 特許権者 000002185

ソニー株式会社

東京都品川区北品川6丁目7番35号

(74) 代理人 100082740

弁理士 田辺 恵基

(72) 発明者 石川 夏也

東京都品川区北品川6丁目7番35号ソニ

一株式会社内

(72) 発明者 尾崎 裕司

東京都品川区北品川6丁目7番35号ソニ

一株式会社内

(72) 発明者 長谷川 深

東京都品川区北品川6丁目7番35号ソニ

一株式会社内

最終頁に続く

(54) 【発明の名称】半導体装置の製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

半導体ウエハに所定の処理を施すことによりその一面に複数の半導体集積回路を形成する第1の工程と、

上記半導体ウエハの上記一面全面上にフォトレジストを塗布することによりレジスト層を積層形成すると共に、当該レジスト層をパターニングすることにより上記レジスト層に各上記半導体集積回路の各電極及びその周辺部のみがそれぞれ露出するよう複数の開口を形成する第2の工程と、

上記レジスト層の各上記開口をそれぞれ介して上記半導体ウエハの上記一面にパンプ用の金属材を厚みが上記レジスト層の1.3倍以下となるように蒸着することにより、各上記半導体集積回路の各上記電極上にそれぞれ第1のパンプ層を積層形成すると共に、上記レジスト層上に上記金属材からなる第2のパンプ層を積層形成する第3の工程と、

上記第1のパンプ層上には貼り付けず、上記第2のパンプ層上にのみ粘着テープを貼り付けた後、当該粘着テープを引き剥がすことにより上記レジスト層上から上記第2のパンプ層を除去する第4の工程と、

上記レジスト層を上記半導体ウエハの上記一面から除去する第5の工程と、

各上記半導体集積回路の各上記電極上にそれぞれ積層形成された上記第1のパンプ層を加熱溶融して整形する第6の工程と

を具えることを特徴とする半導体装置の製造方法。

## 【発明の詳細な説明】

## 【0001】

## 【目次】

以下の順序で本発明を説明する。

## 発明の属する技術分野

従来の技術(図3(A)～図4(H))

発明が解決しようとする課題(図3(A)～図4(H))

課題を解決するための手段(図1(A)～図2(E))

発明の実施の形態(図1(A)～図2(E))

## 発明の効果

## 【0002】

10

## 【発明の属する技術分野】

本発明は、半導体装置の製造方法に関し、例えば大口径の半導体ウエハ(以下、半導体ウエハを単にウエハと呼ぶ)から狭電極ピッチのICチップを形成する場合に適応して好適なものである。

## 【0003】

## 【従来の技術】

従来、例えばフリップチップ等のベアチップ実装用のICチップにおいては、ウエハと呼ばれる半導体の単結晶板の一面に、所定パターンでエッティング、酸化及び又は不純物注入等の所定処理を施すことにより複数の半導体集積回路(半導体IC)を形成し、これら各半導体ICの各電極上にバンプと呼ばれる突起電極をそれぞれ形成した後、各半導体ICをそれぞれ個別に切り離すことにより形成されている。 20

## 【0004】

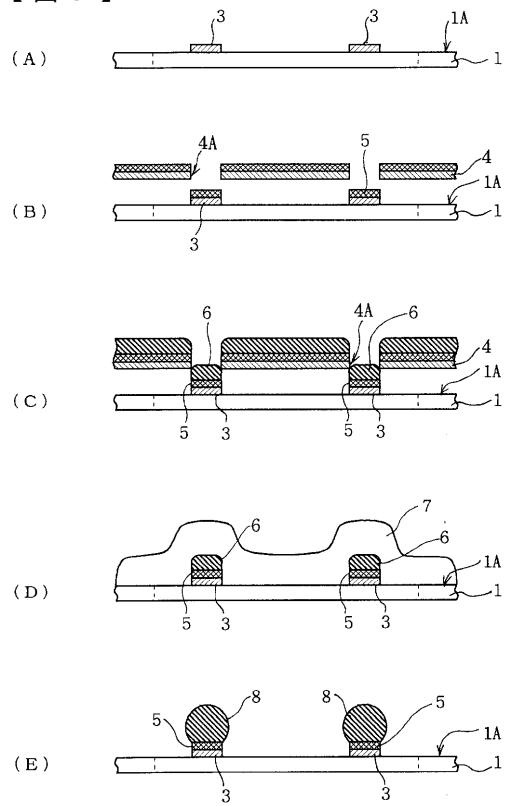

この場合これら切り離す前の各半導体ICの各電極上にはんだバンプを形成するはんだバンプ形成法としては、従来からメタルマスク法と電界めつき法がある。

メタルマスク法は、図3(A)に示すように、ウエハ1に形成された各半導体ICの各電極3にそれぞれ対応させて、図3(B)のように開口4Aが設けられたメタルマスク4を用いて行われる。

## 【0005】

すなわちメタルマスク法では、まずこのメタルマスク4を各開口4Aから半導体ICの対応する電極3及びその周辺部がそれぞれ露出するようにウエハ1の一面1A上に治具(図示せず)を用いて密着させる。 30

次いでこのメタルマスク4の各開口4Aを介してウエハ1の一面1A上に、例えばスパッタ装置を用いてTi、Cu及びAuなどの金属材をそれぞれ所定の厚みに堆積させることにより各半導体ICの対応する各電極3及びその周辺部上にそれぞれメタルバリア層5を積層形成する。

## 【0006】

続いて図3(C)に示すように、このバリアメタル層5上に例えば蒸着装置を用いてSn及びPb等のはんだ材を蒸着することによりはんだ層6を形成し、この後ウエハ1の一面1A上からメタルマスク4を除去する。

続いて図3(D)に示すように、各半導体ICの各電極3の周辺部上にそれぞれフラックス7を塗布し、この後各半導体ICの各電極3上に積層形成された各はんだ層6を加熱溶融した後、ウエハ1の一面1A上に残存するフラックス7を溶剤を用いて除去する。 40

## 【0007】

これによりウエハ1の各半導体ICの各電極3上にそれぞれ図3(E)のような球状のはんだバンプ8を形成することができる。

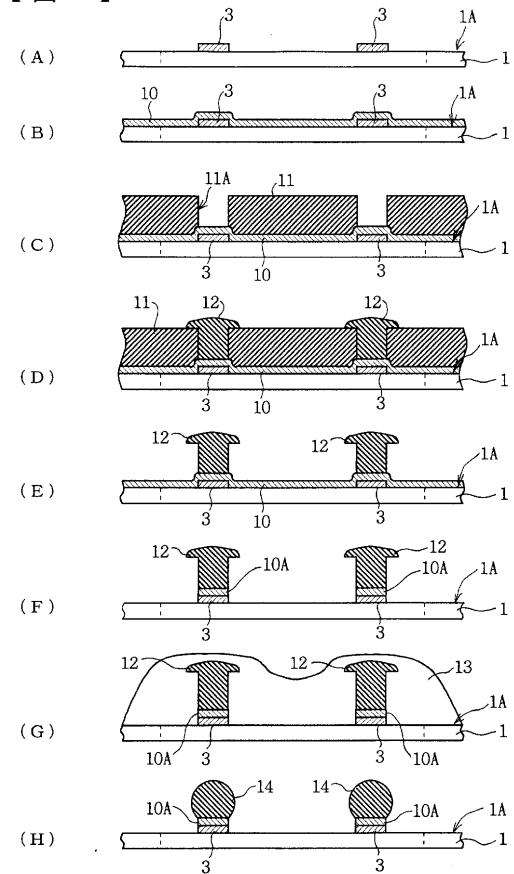

一方電界めつき法においては、例えば図4(A)～(H)に示すような手順により行われ、まず図4(A)に示すように、ウエハ1の一面1A上に、例えばスパッタリング法などによりTi、Cu又はAuなどの金属材を堆積させることにより図4(B)のようにバリアメタル層10を形成する。

## 【0008】

50

次いでこのバリアメタル層 10 上にフォトレジストを塗布することによりレジスト層 11 (図 4 (C)) を形成し、この後このレジスト層 11 を所定パターンで露光し、現像することにより、図 4 (C) のように各半導体 IC の各電極 3 及びその周辺部と、めつき用取出し電極 (図示せず) 及びその周辺部とのみがそれぞれ露出するようにレジスト層 11 をパターニングする。

続いてめつき用取出し電極をアノード側としてめつき浴中ではんだを電解めつきにより堆積させることにより、図 4 (D) のように所定厚のはんだ層 12 を形成し、この後図 4 (E) のように、このウエハ 1 の一面 1A 上からレジスト層 11 を剥離液によつて溶解させることにより除去する。

#### 【0009】

続いて図 4 (F) に示すように、ウエハ 1 の一面 1A 上に形成されたバリアメタル層 10 のうち、各はんだ層 12 の直下以外の部分をエッティング液を用いて除去する。

この後ウエハ 1 の一面 1A 上に、図 4 (G) に示すように、各はんだ層 12 を取り囲むようにフラックス 13 をコーティングした後、これら各はんだ層 12 を加熱溶融する。これによりウエハ 1 に形成された各半導体 IC の各電極 3 上にそれぞれ図 4 (H) に示すような球状のはんだバンプ 14 を形成することができる。

#### 【0010】

##### 【発明が解決しようとする課題】

ところで、近年、IC の製造技術が飛躍的に進歩し、ウエハ 1 枚からの IC チップの収量を増加させるために、大口径のウエハを用いることや、IC チップ内部の配線幅等を縮小させることによる IC チップ自身の小型化、及びそれに伴う IC チップ上の電極の狭ピッチ化が進んでいる。

この場合このような IC チップの製造工程で用いられるウエハは、一般的に 8" 以上のものであり、また各 IC チップの電極間隔も 150 [μm] を切つている。

#### 【0011】

ところが上述したような従来のメタルマスク法では、Mo、Cr 又はステンレスなどからなるメタルマスク 4 と、ウエハ 1 との間ににおける熱膨張係数の違いから、例えばスパッタリングにより各半導体 IC の各電極 3 上にバリアメタル層 5 を形成する際や、このバリアメタル層 5 上に蒸着法によりはんだ層 6 を形成する際に、発生する熱によつてメタルマスク 4 の各開口 4A と半導体 IC の対応する電極 3 との間に位置ずれが生じることがあり、このため各半導体 IC の各電極 3 上に精度良くバリアメタル層 5 やはんだ層 6 (はんだバンプ 8) を形成し難い問題があつた。この傾向はウエハ 1 が大口径化し、半導体 IC の電極ピッチが狭くなる程難しくなる問題があつた。

#### 【0012】

一方上述したような従来のめつき法では、めつき浴中の組成 (例えば Pb 及び Sn) の管理が難しく、このため各半導体 IC の各電極 3 上にそれぞれ形成される各はんだバンプ 14 間に組成のずれが生じたりする問題がある。また従来のめつき法では、めつきによる各はんだ層 12 の形成時にウエハ 1 の一面 1A 全面を均一な電界強度に保つことが難しく、このため各半導体 IC の各電極 3 上にそれぞれ形成されるはんだ層 12 (及び最終的にこれら各半導体 IC の各電極 3 上にそれぞれ形成されるはんだバンプ 14) の高さにばらつきが生じ易い問題がある。このような各はんだバンプ 14 の組成や高さは、ウエハ 1 が大口径化する程、制御し難い問題があつた。

#### 【0013】

特にめつき法では、形成される各はんだバンプ 14 間での高さのばらつきが大きく、このため各電極 3 上にめつき法を用いてはんだバンプ 14 が形成された IC チップを配線基板上にマウントする場合に、1 チップ内におけるはんだバンプ 14 の高さばらつきのために全てのはんだバンプ 14 を配線基板上の対応する電極に接合させ難く、実装した半導体 IC と配線基板との間で接続不良が生じ易い問題があつた。

#### 【0014】

本発明は以上の点を考慮してなされたもので、大口径のウエハから形成される、狭電極ピ

10

20

30

40

50

ツチな各半導体チップの各電極上に位置精度良く、かつ均一な組成で高さのそろつたバンプを形成することのできる半導体装置の製造方法を提案しようとするものである。

#### 【0015】

##### 【課題を解決するための手段】

かかる課題を解決するため本発明においては、一面に複数の半導体集積回路が形成された半導体ウエハの一面全面上に、フォトレジストからなるレジスト層を形成すると共に当該レジスト層をパターニングすることによりレジスト層に各半導体集積回路の各電極及びその周辺部のみがそれぞれ露出するように複数の開口を形成し、当該レジスト層の各開口をそれぞれ介して半導体ウエハの一面にバンプ用の金属材を厚みがレジスト層の1.3倍以下となるように蒸着することにより、各半導体集積回路の各電極上にそれぞれ第1のバンプ層を積層形成するとともに、レジスト層上にバンプ用の金属材からなる第2のバンプ層を積層形成し、第1のバンプ層上には貼り付けず、第2のバンプ層上にのみ粘着テープを貼り付けた後、当該粘着テープを引き剥がすことによりレジスト層上から第2のバンプ層を除去し、この後レジスト層を半導体ウエハの一面から除去した後、第1のバンプ層を加熱溶融して整形するようにして半導体装置を製造するようにした。10

#### 【0016】

このように半導体ウエハの一面に積層形成されたレジスト層を各半導体集積回路の各電極が露出するようにパターニングする場合、半導体集積回路の電極ピッチが狭い場合にも各電極にそれぞれ対応させてレジスト層に位置精度良く狭ピッチで開口を形成できる。この開口精度はウエハ径が大きくなつても変化しない。またこのレジスト層の各開口をそれぞれ介して各半導体集積回路の各電極上にバンプ用の金属材を蒸着する場合、当該半導体集積回路の各電極上に均一な組成でかつ高さのばらつきが少なく第1のバンプ層を形成することができる。20

#### 【0017】

##### 【発明の実施の形態】

以下図面について、本発明の一実施例を詳述する。

#### 【0018】

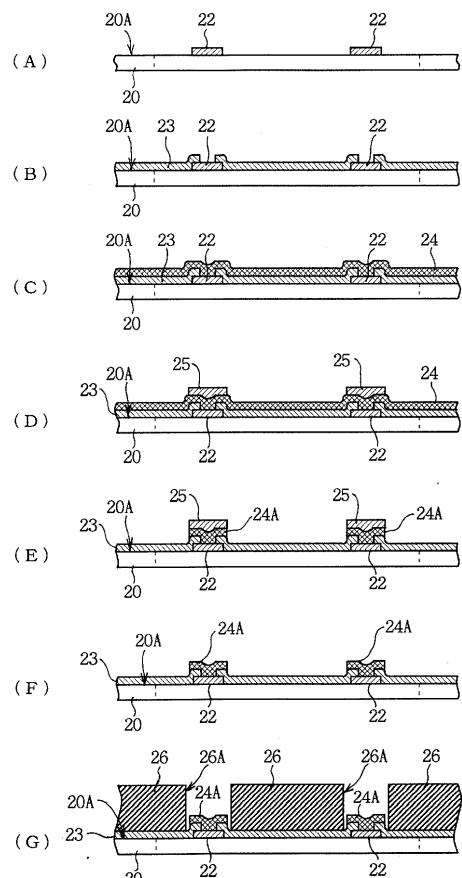

図1(A)～図2(E)は実施例による半導体装置の製造方法を示すものであり、まずウエハに所定の処理を施すことにより、その一面に複数の半導体ICを形成し(図1(A))、この後ウエハ20的一面20A上に、図1(B)のように各半導体ICの各A1電極22のパッド径を制限しながらポリイミド等からなるパッジベーション膜23を形成する。30

#### 【0019】

次いで図1(C)に示すように、このウエハ20的一面20A上に全面に亘つてTi、Cu及びAu等の金属材をスパッタリングすることによりバリアメタル層24を形成する。この後このバリアメタル層24上にフォトレジストを塗布することによりレジスト層を形成した後、このレジスト層を、露光し、現像することにより、図1(D)のように各半導体ICの各A1電極22及びその周辺部のみが残るようにパターニングする。

#### 【0020】

続いて図1(E)に示すように、ウエハ20的一面20A上に形成されたバリアメタル層24のうち、各半導体ICの各A1電極22及びその周辺部上以外のバリアメタル層24をエッチャントを用いてエッティングすることにより除去し、この後図1(F)に示すように、残存するバリアメタル層24A上の各レジスト層25をそれぞれ剥離液を用いて除去する。40

#### 【0021】

さらにこの後図1(G)に示すように、再びパッジベーション膜23上に高粘度のフォトレジストを塗布することによりレジスト層26を形成すると共に、この後このレジスト層26を露光し、現像するようにしてパターニングすることにより、レジスト層26に各半導体ICの各A1電極22及びその周辺部のみがそれぞれ露出するように複数の開口26Aを形成する。50

**【0022】**

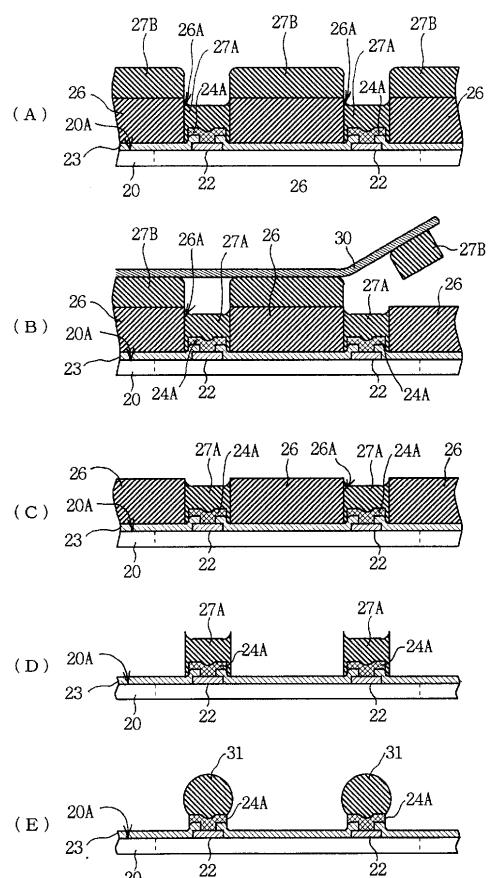

続いてこのレジスト層26の各開口26Aをそれぞれ介してSn及びPb等のはんだ材をウエハ20の一面20A上に蒸着することにより、図2(A)に示すように、各半導体ICの各電極22及びその周辺部上にはんだ層27Aを形成し、この後図2(B)に示すように、上述のはんだ材の蒸着工程(図2(B))時においてレジスト層26上に形成されたはんだ層27B上に粘着テープ30を貼り付けた後、これを引き剥がす。

**【0023】**

この際粘着テープ30としては、レジスト層26及びはんだ層27B間の密着力よりも粘着力が強いものを用いるようにし、これによりレジスト層26上に形成されたはんだ層27Bを粘着テープ30と一緒に剥ぎ取るようにする。従つてこの工程の終了後、ウエハ20の一面20A上には、図2(C)に示すように、レジスト層26の開口26A内にのみ(すなわち各半導体ICの各電極22上にのみ)はんだ層27Aが残存する。

さらにこの後図2(D)に示すように、ウエハ20の一面20A上からレジスト層26を剥離液を用いて除去する。因に、このような方法により各半導体ICの各A1電極22上に形成されたはんだ層27Aの組成は、蒸着時におけるPb及びSnの蒸気圧の違いにより、上層にSn成分が多くなつている。

**【0024】**

この後このはんだ層27Aの表面にフラツクスをコーティングし、当該はんだ層27Aを加熱溶融し、球状に整形した後、フラツクスを洗浄液を使用し除去する。これにより図2(E)に示すように、各半導体ICの各A1電極22上にそれぞれ球形状のはんだバンプ31を形成することができる。

さらにこの後このウエハ20を、各半導体ICをそれぞれ個別に切り離すように分割する。これにより各A1電極22上にそれぞれ球形状のはんだバンプ31が形成されてなるICチップを得ることができる。

**【0025】**

ここでこの実施例の場合、はんだ材の蒸着工程(図2(A))では、はんだ層27A、28Bの厚みがレジスト層26の厚みの1.3倍以下になるようにはんだ層27A、28Bを形成するようとする。

これは実験的に、はんだ層27A、27Bの厚みがレジスト層26の厚みの1.3倍以上になると、レジスト層26の開口26A内に形成されたはんだ層27Aの一部も粘着テープ30に粘着し、これらが当該粘着テープ30と一緒にウエハ20の一面20A上から剥がれることによりA1電極22上にはんだバンプ31が形成されないおそれがあるためである。

**【0026】**

従つてはんだ材の蒸着工程(図2(A))において、上述のようにはんだ層27A、27Bの厚みがレジスト層26の厚みの1.3倍以下となるように制御することにより、このようなはんだバンプ31の欠落を未然に防止することができる。

**【0027】**

以上の構成において、この実施例では、各半導体ICの各電極22上に形成された各バリアメタル層24A上にはんだ層27Aを形成する工程(図1(G)～図2(D))を、パッシベーション膜23上にフォトレジストを塗布することによりレジスト層26を形成すると共に、当該レジスト層26を、各半導体ICの各電極22及びその周辺部がそれぞれ露出する開口26Aを有するようにパターニングした後、このレジスト層26をマスクとして各半導体ICの各A1電極22上に形成された各バリアメタル層24A上にはんだを蒸着することにより行う。

**【0028】**

従つてこの方法では、はんだ材の蒸着工程(図2(A))においてマスクとなるレジスト層26を通常のフォトプロセスを用いてパターニングしている分、各開口26Aを狭いピッチで位置精度良く形成できる。またこの精度はウエハ20の径が大きくなつても変化しないため、ウエハ20が大口径でかつ各半導体ICが狭電極ピッチである場合にもこれら

各半導体ICの各電極22にそれぞれ対応させて精度良くはんだ層26の開口26Aを形成することができる。

#### 【0029】

さらにこの方法では、このようにして形成されたレジスト層26の各開口26Aをそれぞれ介して各半導体ICの各電極22上にはんだ層27Aを形成する際に蒸着法を用いるため、これら各電極22上に均一な組成でかつ高さのばらつきが少なくはんだ層27A（及びはんだバンプ31）を形成することができる。

#### 【0030】

従つてこの実施例のような半導体装置の製造方法を用いることによつて、1枚のウエハ20あたりのICチップの収量を増加させ得ると共に、その分コストも低減させることができ、かつ各半導体ICの各電極22上に高さのばらつきが少なくはんだ層27A（及びはんだバンプ31）を形成し得る分、このICチップを配線基板に実装する際の当該ICチップと配線基板との間の接続不良を低減できる。

#### 【0031】

以上の構成によれば、ウエハ20の一面20A上に成膜されたパツシベーション膜23上にフォトレジストを塗布することによりレジスト層26を形成し、当該レジスト層26を露光し、現像することによつて当該レジスト層26に各半導体ICの各電極22にそれぞれ対応させて開口26Aを形成すると共に、このレジスト層26の各開口26Aをそれぞれ介して露出する各半導体ICの各電極22上に蒸着法によりはんだ材を蒸着するようにしてはんだ層27Aを形成するようにしたことにより、ウエハ20の口径に関わりなくレジスト層26の各開口26Aを精度良く形成し得ると共に各半導体ICの各電極22上に均一な組成で高さのばらつきが少なくはんだ層27Aを形成することができ、かくして大口径なウエハから形成される、狭電極ピッチの各半導体ICの各電極上に位置精度良く、かつ均一な組成で高さのそろつたはんだバンプを形成することができる半導体装置の製造方法を実現できる。

#### 【0032】

なお上述の実施例においては、本発明をウエハ20に形成された各半導体ICの各電極22上にはんだバンプ31を形成する際に適用するようにした場合について述べたが、本発明はこれに限らず、各半導体ICの各電極22上にはんだ材以外のバンプ用の金属材からなるバンプを形成する場合にも適用して好適なものである。

#### 【0033】

また上述の実施例においては、レジスト層26上に形成された各はんだ層27Bを除去する際、粘着テープ30を利用するようにした場合について述べたが、本発明はこれに限らず、この他種々の方法を適用できる。この場合はんだ材の蒸着工程（図2（A））では、必要に応じてはんだ層27A、27Bの厚みがレジスト層26の厚みの1.3倍以上となるように制御しても良い。

#### 【0034】

##### 【発明の効果】

上述のように本発明によれば、一面に複数の半導体集積回路が形成された半導体ウエハの一面全面上に、フォトレジストからなるレジスト層を形成すると共に当該レジスト層をパターニングすることによりレジスト層に各半導体集積回路の各電極及びその周辺部のみがそれぞれ露出するように複数の開口を形成し、当該レジスト層の各開口をそれぞれ介して半導体ウエハの一面にバンプ用の金属材を厚みがレジスト層の1.3倍以下となるように蒸着することにより、各半導体集積回路の各電極上にそれぞれ第1のバンプ層を積層形成するとともに、レジスト層上にバンプ用の金属材からなる第2のバンプ層を積層形成し、第1のバンプ層上には貼り付けず、第2のバンプ層上にのみ粘着テープを貼り付けた後、当該粘着テープを引き剥がすことによりレジスト層上から第2のバンプ層を除去し、この後レジスト層を半導体ウエハの一面から除去した後、第1のバンプ層を加熱溶融して整形するようにして半導体装置を製造するようにしたことにより、半導体ウエハの口径に関わりなくかつ半導体集積回路の電極ピッチが狭い場合にも各電極にそれぞれ対応させて位

10

20

30

40

50

置精度良くレジスト層に開口を形成できると共に、このレジスト層の各開口をそれぞれ介して各半導体集積回路の各電極上にバンプ用の金属材を均一な組成でかつ高さのばらつきが少なく供給することができ、かくして大口径なウエハから形成される狭電極ピッチの半導体チップの各電極上に位置精度良く、かつ均一な組成で高さのそろつたバンプを形成することができる半導体装置の製造方法を実現できる。

**【図面の簡単な説明】**

**【図1】** 実施例による半導体製造方法に適用するはんだバンプ形成方法の説明に供する断面図である。

**【図2】** 実施例による半導体製造方法に適用するはんだバンプ形成方法の説明に供する断面図である。

10

**【図3】** 従来のメタルマスク法によるはんだバンプの形成工程を示す断面図である。

**【図4】** 従来のめつき法によるはんだバンプの形成工程を示す断面図である。

**【符号の説明】**

20 ……ウエハ、 20A ……一面、 21 ……半導体IC、 22 ……電極、 23 ……パツシベーション膜、 24、 24A ……バリアメタル層、 25、 26 ……レジスト層、 27A、 27B ……はんだ層、 30 ……粘着テープ、 31 ……はんだバンプ。

**【図1】**

図1 実施例による半導体装置の製造方法（1）

**【図2】**

図2 実施例による半導体装置の製造方法（2）

【図3】

図3 従来のメタルマスク法によるはんだバンプの形成工程

【図4】

図4 従来のメッキ法によるはんだバンプの形成工程

---

フロントページの続き

審査官 田中 永一

(56)参考文献 特開平2 - 82625 (JP, A)

特開昭56 - 169325 (JP, A)

特開平2 - 90624 (JP, A)

特開平9 - 82711 (JP, A)

(58)調査した分野(Int.Cl.<sup>7</sup>, DB名)

H01L 21/60

H01L 21/301