(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-274726

(P2004-274726A)

(43) 公開日 平成16年9月30日(2004.9.30)

(51) Int.CI.<sup>7</sup>

H03F 3/217

F 1

H03F 3/217

テーマコード(参考)

5J5OO

審査請求 未請求 請求項の数 5 O L (全 12 頁)

|              |                            |

|--------------|----------------------------|

| (21) 出願番号    | 特願2004-14541 (P2004-14541) |

| (22) 出願日     | 平成16年1月22日(2004.1.22)      |

| (31) 優先権主張番号 | 特願2003-38735 (P2003-38735) |

| (32) 優先日     | 平成15年2月17日(2003.2.17)      |

| (33) 優先権主張国  | 日本国 (JP)                   |

|           |                                                                                                                    |

|-----------|--------------------------------------------------------------------------------------------------------------------|

| (71) 出願人  | 301066006<br>株式会社デノン<br>東京都文京区湯島三丁目16番11号                                                                          |

| (74) 代理人  | 100078134<br>弁理士 武 顯次郎                                                                                             |

| (74) 代理人  | 100093492<br>弁理士 鈴木 市郎                                                                                             |

| (74) 代理人  | 100111914<br>弁理士 藤原 英夫                                                                                             |

| (72) 発明者  | 福島 貢<br>神奈川県相模原市相模大野7丁目35番1号 株式会社デノン相模原オフィス内                                                                       |

| F ターム(参考) | 5J500 AA02 AA27 AA41 AC04 AC23<br>AF15 AH10 AH19 AH29 AH35<br>AK04 AK17 AK33 AK42 AM22<br>AS05 AT01 AT06 DP02 WU02 |

(54) 【発明の名称】パルス幅変調增幅装置

## (57) 【要約】

## 【課題】

電源電圧変動に伴う出力歪みを抑制することのできる

パルス幅変調增幅装置を提供する。

## 【解決手段】

直流電源に第1のスイッチング素子1, 11及び第2のスイッチング素子2, 12を直列接続してなる直列回路を複数組備え、各組の直列回路における第1のスイッチング素子1, 11と第2のスイッチング素子2, 12の各接続点に共通に一つの負荷の一端を接続し、前記各組のスイッチング素子をスイッチングして前記一つの負荷にパルス幅変調された増幅出力を供給するパルス幅変調增幅装置であって、前記各組の直列回路のそれぞれ同一位置にあるスイッチング素子をそれぞれ重複して導通しないように駆動する駆動回路を備えた。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

直流電源に第1のスイッチング素子及び第2のスイッチング素子を直列接続してなる直列回路を複数組備え、

各組の直列回路における第1のスイッチング素子と第2のスイッチング素子の各接続点に共通に一つの負荷の一端を接続し、前記各組のスイッチング素子をスイッチングして前記一つの負荷にパルス幅変調された増幅出力を供給するパルス幅変調増幅装置であって、

前記各組の直列回路のそれぞれ同一位置にあるスイッチング素子同士をそれぞれ重複して導通しないように駆動する駆動回路を備えたことを特徴とするパルス幅変調増幅装置。

**【請求項 2】**

直流電源に第1のスイッチング素子と第2のスイッチング素子からなる直列回路及び第3のスイッチング素子と第4のスイッチング素子からなる直列回路を接続してなるブリッジ回路を複数組備え、

各組のブリッジ回路における第1のスイッチング素子と第2のスイッチング素子の各接続点及び第3のスイッチング素子と第4のスイッチング素子の各接続点間に共通に一つの負荷を接続し、前記各組のスイッチング素子をスイッチングして前記一つの負荷にパルス幅変調された増幅出力を供給するパルス幅変調増幅装置であって、

前記各組のブリッジ回路のそれぞれ同一位置にあるスイッチング素子同士をそれぞれ重複して導通しないように駆動する駆動回路を備えたことを特徴とするパルス幅変調増幅装置。

**【請求項 3】**

請求項1または2記載のパルス幅変調増幅装置において、

複数組のブリッジ回路における各直列回路に電力を供給する直流電源はそれぞれ独立であることを特徴とするパルス幅変調増幅装置。

**【請求項 4】**

請求項3記載のパルス幅変調増幅装置において、

駆動回路は、各電源が連続して電力を供給しない順序でスイッチング素子を駆動することを特徴とするパルス幅変調増幅装置。

**【請求項 5】**

直流電源に第1のスイッチング素子と第2のスイッチング素子からなる直列回路及び第3のスイッチング素子と第4のスイッチング素子からなる直列回路を接続してなるブリッジ回路を3組以上備え、

各組のブリッジ回路における第1のスイッチング素子と第2のスイッチング素子の各接続点及び第3のスイッチング素子と第4のスイッチング素子の各接続点間に共通に一つの負荷を接続し、前記各組のスイッチング素子をスイッチングして前記一つの負荷にパルス幅変調された増幅出力を供給するパルス幅変調増幅装置であって、

前記各組のブリッジ回路における同一直流電源に接続した第1のスイッチング素子と第3のスイッチング素子は、それぞれを駆動する駆動信号の間に他の直流電源に接続したスイッチング素子を駆動する信号を挿入し、第1のスイッチング素子と第3のスイッチング素子がそれぞれ連続して導通しないように駆動する駆動回路を備えたことを特徴とするパルス幅変調増幅装置。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明はパルス幅変調増幅装置にかかり、特に出力歪みを抑制することのできるパルス幅変調増幅装置に関する。

**【背景技術】****【0002】**

パルス幅変調増幅装置(PWM(Pulse Width Modulation)増幅装置)等のD級増幅装置は、A級増幅装置あるいはB級増幅装置と比べて出力段における損失が少ないため、近年

10

20

30

40

50

は省電力化の観点から注目されている。ところで、パルス幅変調増幅装置の出力は、その出力段を構成するスイッチング素子のオン・オフにより定まる出力パルス幅及び電源電圧により定まるパルス振幅で表すことができる。

### 【0003】

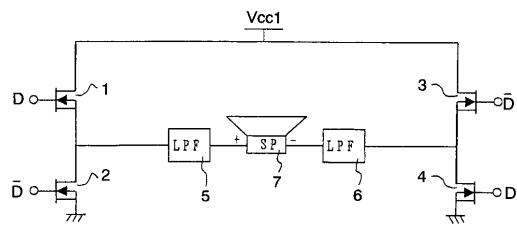

図5は、従来のパルス幅変調増幅装置を説明する図である。図において、Vcc1は電源である。1, 2, 3, 4はそれぞれ第1のスイッチング素子、第2のスイッチング素子、第3のスイッチング素子、第4のスイッチング素子であり、これらのスイッチング素子1, 2, 3, 4によりブリッジ回路を構成する。5, 6はノイズ除去用のローパスフィルタ、7はブリッジ回路の負荷としてのスピーカである。

### 【0004】

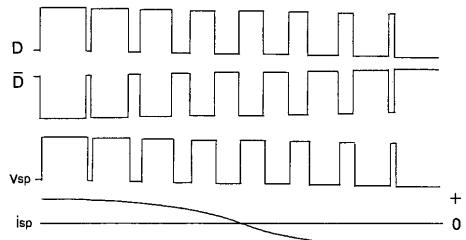

図6は、従来のパルス幅変調増幅装置の各部の動作波形を説明する図である。図において、Dはスイッチング素子1及び4に供給する駆動信号、-D(Dの反転信号)はスイッチング素子2及び3に供給する駆動信号、vspはスピーカに印加される電圧、ispはスピーカ電流である。

### 【0005】

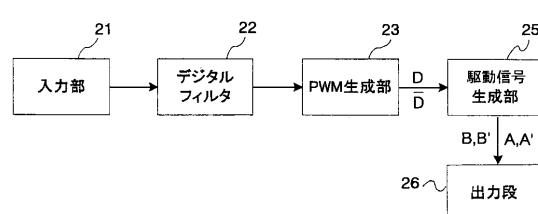

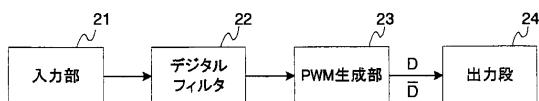

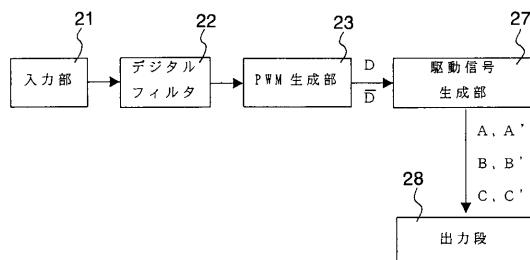

図7は、従来のパルス幅変調増幅装置の構成を説明するブロック図である。図において、21は入力部であり、例えばCD(Compact Disc)プレーヤ等のオーディオデータの再生装置からオーディオデータを入力する。22はデジタルフィルタであり、前記オーディオデータに対してトーンコントロール、低域濾波等の演算処理を施す。23はスイッチング素子1, 2, 3, 4を駆動する駆動信号(D, -D)を生成するPWM生成部である。PWM生成部23は、例えば前記オーディオデータと三角波を比較し、その比較結果をもとに駆動信号(D, -D)を生成する。24は出力段であり、例えば図5に示すようにスイッチング素子をブリッジ接続して構成する。

### 【0006】

PWM生成部23は、スイッチング素子1及び4に駆動信号Dを供給して、スイッチング素子1及び4をオンに駆動する。このときスピーカ7には正方向電圧が印加される。同様にスイッチング素子2及び3に駆動信号-Dを供給して、スイッチング素子2及び3をオンに駆動するとスピーカ7に負方向電圧が印加される。従って、図6に示すvspの波形の左方に示すようにスピーカ7に正方向電圧が印加される期間がスピーカ7に負方向電圧が印加される期間よりも長い場合はスピーカは正方向駆動され、図6に示すvspの波形の右方に示すようにスピーカ7に正方向電圧が印加される期間がスピーカ7に負方向電圧が印加される期間よりも短い場合はスピーカは負方向駆動されることになる。

### 【0007】

以上の動作から分かるように歪みのない増幅器出力を得るためには、パルス幅変調増幅装置の出力段には、正確なパルス幅の駆動信号(D, -D)と電圧変動の少ない電源電圧を供給することが必要となる。

### 【0008】

電源電圧変動による歪みを抑制する技術としては、例えば、特許文献1に、前記スイッチング素子をトランジスタで構成し、このトランジスタに定電圧機能を付与することにより電源電圧変動に伴う歪みを除去することが示されている。また、特許文献2、3には、電源電圧変動を検出し、検出した値に応じて駆動信号のパルス幅を補正することにより電源電圧変動に伴う歪みを除去することが示されている。

### 【特許文献1】特開昭52-96854号公報

### 【特許文献2】特開昭61-39708号公報

### 【特許文献3】特開平3-159409号公報

### 【発明の開示】

### 【発明が解決しようとする課題】

### 【0009】

しかしながら、特許文献1に開示されているように前記スイッチング素子をトランジスタで構成し、このトランジスタに定電圧機能を付与することにより電源電圧変動に伴う歪

10

20

30

40

50

みを除去する方法は、大出力に対応しようとすると出力段のトランジスタによる損失が増大し効率が著しく低下する。また、特許文献2,3に開示されているように電源電圧変動を検出し、検出した値に応じて駆動信号のパルス幅を補正する方法は、電源電圧変動を検出してからパルス幅補正を行うまでに遅延が発生し、この遅延により出力に歪みが生じる。

#### 【0010】

本発明は、これらの問題点に鑑みてなされたもので、電源電圧変動に伴う出力歪みを抑制することのできるパルス幅変調增幅装置を提供する。

#### 【課題を解決するための手段】

#### 【0011】

本発明は上記課題を解決するため、次のような手段を採用した。

#### 【0012】

直流電源に第1のスイッチング素子及び第2のスイッチング素子を直列接続してなる直列回路を複数組備え、各組の直列回路における第1のスイッチング素子と第2のスイッチング素子の各接続点に共通に一つの負荷の一端を接続し、前記各組のスイッチング素子をスイッチングして前記一つの負荷にパルス幅変調された增幅出力を供給するパルス幅変調增幅装置であって、前記各組の直列回路のそれぞれ同一位置にあるスイッチング素子同士をそれぞれ重複して導通しないように駆動回路を備えた。

#### 【発明の効果】

#### 【0013】

本発明は、以上の構成を備えるため、電源電圧変動に伴う出力歪みを抑制することのできるパルス幅変調增幅装置を提供することができる。

#### 【発明を実施するための最良の形態】

#### 【0014】

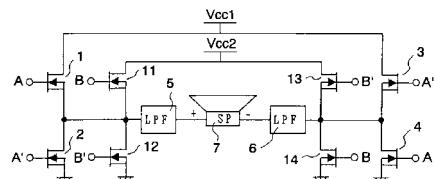

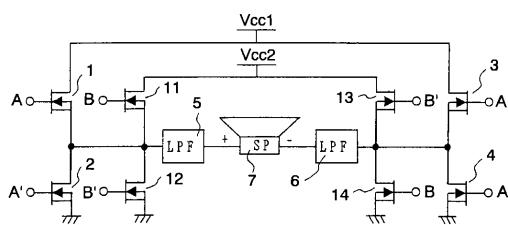

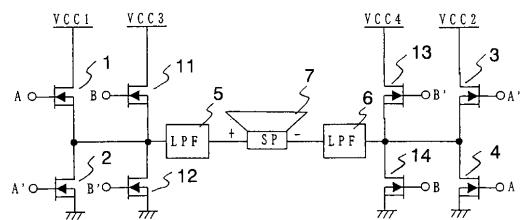

以下、最良の実施形態を添付図面を参照しながら説明する。図1は、本発明の第1の実施形態にかかるパルス幅変調增幅装置を説明する図である。図において、Vcc1は第1の電源である。1, 2, 3, 4はそれぞれ、第1のブリッジ回路における、例えばFET(Field Effect Transistor)で構成した第1のスイッチング素子、第2のスイッチング素子、第3のスイッチング素子、第4のスイッチング素子であり、これらのスイッチング素子1, 2, 3, 4により第1のブリッジ回路を構成する。5, 6はノイズ除去用のローパスフィルタ、7はブリッジ回路の負荷としてのスピーカである。

#### 【0015】

また、Vcc2は第2の電源である。11, 12, 13, 14はそれぞれ、第2のブリッジ回路における、例えばFETで構成した第1のスイッチング素子、第2のスイッチング素子、第3のスイッチング素子、第4のスイッチング素子であり、これらのスイッチング素子11, 12, 13, 14により第2のブリッジ回路を構成する。すなわち、スイッチング素子1, 2, 3, 4とスイッチング素子11, 12, 13, 14はそれぞれ相互にブリッジ回路における同一位置にあることになる。従って、各組のブリッジ回路における第1のスイッチング素子と第2のスイッチング素子の各接続点及び第3のスイッチング素子と第4のスイッチング素子の各接続点間には、共通に前記一つの負荷回路(スピーカ7)及びノイズ除去用のローパスフィルタ5, 6を接続することができる。

#### 【0016】

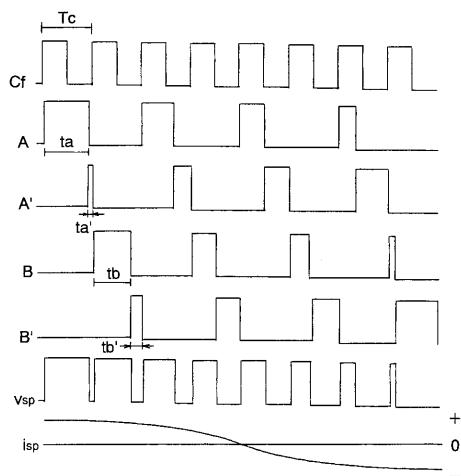

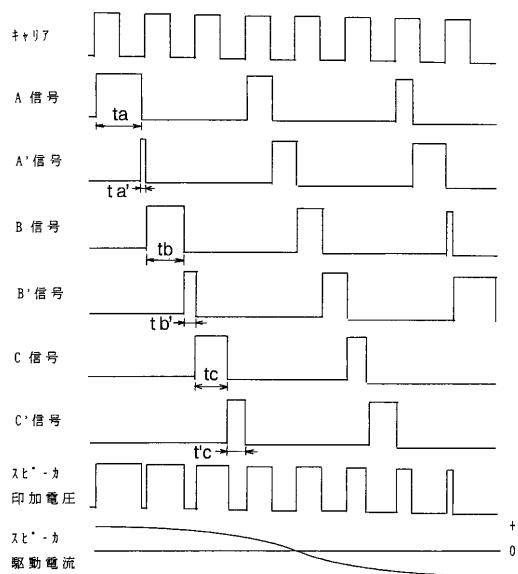

図2は、パルス幅変調增幅装置の各部の動作波形を説明する図である。図において、cfは制御の基準となるキャリア信号、Aは第1のブリッジ回路における第1のスイッチング素子1及び第4のスイッチング素子4に供給する駆動信号、A'は第1のブリッジ回路における第2のスイッチング素子2及び第3のスイッチング素子3に供給する駆動信号である。なお、駆動信号Aの駆動期間ta及び駆動信号A'の駆動期間ta'の和はキャリア信号cfの周期Tcに略等しく設定しておく。

#### 【0017】

また、Bは第2のブリッジ回路における第1のスイッチング素子11及び第4のスイッ

10

20

30

40

50

チング素子 1 4 に供給する駆動信号、  $B'$  は第 2 のブリッジ回路における第 2 のスイッチング素子 1 2 及び第 3 のスイッチング素子 1 3 に供給する駆動信号である。なお、駆動信号  $B$  の駆動期間  $t_b$  及び駆動信号  $B'$  の駆動期間  $t_{b'}$  の和はキャリア信号  $c_f$  の周期  $T_c$  に略等しく設定しておく。また、  $v_{sp}$  はスピーカに印加される電圧、  $i_{sp}$  はスピーカ電流である。

#### 【 0 0 1 8 】

図 3 は、パルス幅変調増幅装置の構成を説明するブロック図である。図において、 25 は後述する駆動信号生成部であり、前記駆動信号 ( $D$ 、  $-D$ ) をもとに、第 1 のブリッジ回路における第 1 のスイッチング素子 1 及び第 4 のスイッチング素子 4 に供給する駆動信号  $A$ 、第 1 のブリッジ回路における第 2 のスイッチング素子 2 及び第 3 のスイッチング素子 3 に供給する駆動信号  $A'$ 、第 2 のブリッジ回路における第 1 のスイッチング素子 1 1 及び第 4 のスイッチング素子 1 4 に供給する駆動信号  $B$ 、及び第 2 のブリッジ回路における第 2 のスイッチング素子 1 2 及び第 3 のスイッチング素子 1 3 に供給する駆動信号  $B'$  を生成する。 26 は出力段であり、図 1 に示すように、第 1 の電源  $V_{cc1}$  に接続した第 1 のブリッジ回路及び第 2 の電源  $V_{cc2}$  に接続した第 2 のブリッジ回路の並列回路から構成される。なお、図 3 において図 7 に示される部分と同一部分については同一符号を付してその説明を省略する。

#### 【 0 0 1 9 】

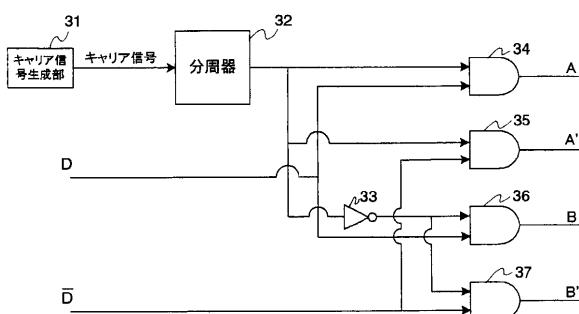

図 4 は、駆動信号生成部の詳細を説明する図である。図において、 31 は前記キャリア信号  $c_f$  を生成するキャリア信号生成部、 32 はキャリア信号  $c_f$  を例えれば 1 / 2 分周する分周器、 33 はノット回路、 34, 35, 36, 37 はアンド回路である。

#### 【 0 0 2 0 】

図 3 及び図 4 に示すように、入力部 21 に入力したオーディオデータに対し、デジタルフィルタ 22 においてトーンコントロール、低域濾波等の演算処理を施した後、 PWM 生成部 23 において前記オーディオデータと三角波を比較しその比較結果をもとに駆動信号 ( $D$ 、  $-D$ ) を生成する。

#### 【 0 0 2 1 】

駆動信号生成部 25 では、図 4 に示すように前記駆動信号 ( $D$ 、  $-D$ ) と分周器出力の論理積をとることにより、前記駆動信号  $A$ 、  $A'$ 、  $B$ 、  $B'$  を得ることができる。このようにして得た駆動信号は、第 1 のブリッジ回路における第 1 のスイッチング素子 1 及び第 4 のスイッチング素子 4、第 1 のブリッジ回路における第 2 のスイッチング素子 2 及び第 3 のスイッチング素子 3、第 2 のブリッジ回路における第 1 のスイッチング素子 1 1 及び第 4 のスイッチング素子 1 4、及び第 2 のブリッジ回路における第 2 のスイッチング素子 1 2 及び第 3 のスイッチング素子 1 3 にそれぞれ供給する。

#### 【 0 0 2 2 】

スイッチング素子 1, 4 及び 2, 3 には、それぞれ図 2 に示す駆動信号  $A$  及び  $A'$  が入力され、これらの駆動信号が供給されたとき (駆動信号  $A$  あるいは  $A'$  がアクティブになったとき)、それぞれ第 1 の電源  $V_{cc1}$  がスピーカ 7 に対して正方向あるいは負方向に接続される。同様に、スイッチング素子 1 1, 1 4 及び 1 2, 1 3 には、それぞれ図 2 に示す駆動信号  $B$  及び  $B'$  が入力され、これらの駆動信号が供給されたとき (駆動信号  $B$  あるいは  $B'$  がアクティブになったとき)、それぞれ第 2 の電源  $V_{cc2}$  がスピーカ 7 に対して正方向あるいは負方向に接続される。

#### 【 0 0 2 3 】

駆動信号  $A$ 、  $A'$  及び駆動信号  $B$ 、  $B'$  は、キャリア信号  $c_f$  に対して順番にアクティブになる。このため図 1 に示す例のように、出力段として 2 組の電源 ( $V_{cc1}$ ,  $V_{cc2}$ ) と、2 組のブリッジ回路を用いた場合は、各電源から電力を取り出す期間は 1 / 2 になる。

#### 【 0 0 2 4 】

なお、2 組のブリッジ回路により作り出される出力電圧は、スピーカ 7 の両端で合成されるので、スピーカ 7 の印加電圧は従来のパルス幅変調増幅装置と同様であり、図 2 に示

す  $v_{sp}$  の波形の左側に示すようにスピーカ 7 に正方向電圧が印加される期間がスピーカ 7 に負方向電圧が印加される期間よりも長い場合はスピーカ 7 は正方向駆動され、図 2 に示す  $v_{sp}$  の波形の右側に示すようにスピーカ 7 に正方向電圧が印加される期間がスピーカ 7 に負方向電圧が印加される期間よりも短い場合はスピーカ 7 は負方向駆動されることになる。

#### 【0025】

すなわち、2組のブリッジ回路のそれぞれ同一位置にある各スイッチング素子は重複することなく交互に動作（すなわち一方の組のブリッジ回路が動作中は他方の組のブリッジ回路は動作しない）する。従って第1の電源  $V_{cc1}$  及び第2の電源  $V_{cc2}$  は交互に電源電流を供給することになる。このため、電源電流の供給に伴って一方の電源の出力電圧が低下した場合においても、この電源は他方の電源が電源電流を供給している間に出力電圧を回復することができる。従って、電源に大電流の負荷電流が流れた後においても電圧降下を回復させるための時間を確保することができるため、電源電圧の変動を抑制することができる。またこれにより出力の歪を抑制することができる。

10

#### 【0026】

なお、以上の説明では、2組の電源と2組のブリッジ回路を用いてパルス幅変調增幅装置を構成する例を示したが、3組以上の電源とブリッジ回路を用いて構成することができる。またブリッジ回路としてフルブリッジ回路を用い構成する例を示したが、第1のスイッチング素子と第2のスイッチング素子の直列回路を備えるハーフブリッジ回路を用いて構成することができる。

20

#### 【0027】

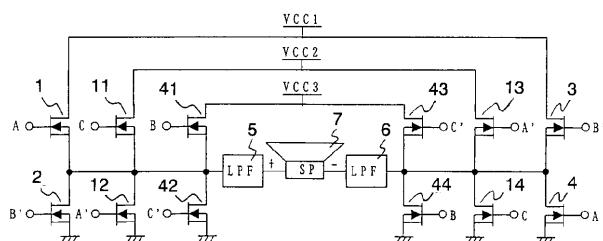

次に、図8を参照して、本発明の第2の実施形態を説明する。

#### 【0028】

図において、 $V_{cc1}$ 、 $V_{cc2}$  はそれぞれ第1の電源、第2の電源である。1、2、3、4 はそれぞれ、第1のブリッジ回路における、第1のスイッチング素子、第2のスイッチング素子、第3のスイッチング素子、第4のスイッチング素子であり、これらのスイッチング素子 1, 2, 3, 4 により第1のブリッジ回路を構成する。5, 6 はノイズ除去用のローパスフィルタ、7 はブリッジ回路の負荷としてのスピーカである。ここで、第1の電源  $V_{cc1}$  は第1のスイッチング素子 1 及び第2のスイッチング素子 2 からなる直列回路に電源を供給する電源であり、第2の電源  $V_{cc2}$  は第3のスイッチング素子 3 及び第4のスイッチング素子 4 からなる直列回路に電源を供給する電源である。

30

#### 【0029】

$V_{cc3}$ 、 $V_{cc4}$  はそれぞれ第3の電源、第4の電源である。また、11、12、13、14 はそれぞれ、第2のブリッジ回路における、第1のスイッチング素子、第2のスイッチング素子、第3のスイッチング素子、第4のスイッチング素子であり、これらのスイッチング素子 11, 12, 13, 14 により第2のブリッジ回路を構成する。ここで、第3の電源  $V_{cc3}$  は第1のスイッチング素子 11 及び第2のスイッチング素子 12 からなる直列回路に電源を供給する電源であり、第2の電源  $V_{cc2}$  は第3のスイッチング素子 13 及び第4のスイッチング素子 14 からなる直列回路に電源を供給する電源である。また、第1の電源  $V_{cc1}$ 、第2の電源  $V_{cc2}$ 、第3の電源  $V_{cc3}$ 、第4の電源  $V_{cc4}$  はそれぞれ独立した電源として構成する。

40

#### 【0030】

なお、第1のブリッジ回路における第1のスイッチング素子 1 及び第4のスイッチング素子 4 に供給する駆動信号 A、第1のブリッジ回路における第2のスイッチング素子 2 及び第3のスイッチング素子 3 に供給する駆動信号 A'、第2のブリッジ回路における第1のスイッチング素子 11 及び第4のスイッチング素子 14 に供給する駆動信号 B、並びに第2のブリッジ回路における第2のスイッチング素子 12 及び第3のスイッチング素子 13 に供給する駆動信号 B' は、前記第1の実施形態と同じ方法で生成し供給することができる。

#### 【0031】

50

すなわち、スイッチング素子 1, 4 及び 2, 3 には、それぞれ図 2 に示す駆動信号 A 及び A' が入力される。駆動信号 A がアクティブになったとき、第 1 の電源 Vcc1 がスピーカ 7 に対して正方向に接続され、駆動信号 A' がアクティブになったとき、第 2 の電源 Vcc2 がスピーカ 7 に対して負方向に接続される。

#### 【0032】

同様に、スイッチング素子 11, 14 及び 12, 13 には、それぞれ図 2 に示す駆動信号 B 及び B' が入力される。駆動信号 B がアクティブになったとき、第 3 の電源 Vcc3 がスピーカ 7 に対して正方向に接続され、駆動信号 B' がアクティブになったとき、第 4 の電源 Vcc4 がスピーカ 7 に対して負方向に接続される。

#### 【0033】

また、各電源は連続して電力を供給しないように駆動される（例えば、駆動信号 A がアクティブになったとき、第 1 の電源 Vcc1 がスピーカ 7 に対して正方向に接続され、続いて駆動信号 A' がアクティブになったとき、第 2 の電源 Vcc2 がスピーカ 7 に対して負方向に接続される。更に駆動信号 B がアクティブになったとき、第 3 の電源 Vcc3 がスピーカ 7 に対して正方向に接続され、続いて駆動信号 B' がアクティブになったとき、第 4 の電源 Vcc4 がスピーカ 7 に対して負方向に接続される）。このため、電源電流の供給に伴って一方の電源の出力電圧が低下した場合においても、この電源は他の電源が電源電流を供給している間に出力電圧を回復することができる。従って、電源に大電流の負荷電流が流れた後においても電圧降下を回復させるための時間を確保することができるため、電源電圧の変動を抑制することができる。またこれにより出力の歪を抑制することができる。

#### 【0034】

なお、駆動信号 A, A' 及び駆動信号 B, B' は、キャリア信号 cf に対して順番にアクティブになる。このため図 8 に示す例のように、出力段として 4 組の電源 (Vcc1, Vcc2, Vcc3, Vcc4) と、4 組のハーフブリッジ回路を用いた場合は、各電源から電力を取り出す期間（信号 A, A' あるいは B, B' がアクティブとなる期間）は全アクティブ期間 (2Tc) の 1/2 未満になる。なお、以上の説明では、4 組の電源と 4 組のハーフブリッジ回路を用いてパルス幅変調增幅装置を構成する例を示したが、5 組以上の電源とブリッジ回路を用いて構成することができる。

#### 【0035】

図 9、10, 11, 12 は、本発明の第 3 の実施形態を説明する図である。なお、これらの図において、図 1 ないし図 4 に示される部分と同一部分については同一符号を付してその説明を省略する。

#### 【0036】

図 9 は本実施形態にかかるにかかるパルス幅変調增幅装置を説明する図である。図において、Vcc3 は第 3 の電源である。41, 42, 43, 44 はそれぞれ、ブリッジ回路を構成する第 1 のスイッチング素子、第 2 のスイッチング素子、第 3 のスイッチング素子、第 4 のスイッチング素子であり、これらのスイッチング素子 41, 42, 43, 44 により第 3 のブリッジ回路を構成する。5, 6 はノイズ除去用のローパスフィルタ、7 はブリッジ回路の負荷としてのスピーカである。

#### 【0037】

図 10 は、パルス幅変調增幅装置の各部の動作波形を説明する図である。図において、C は第 2 のブリッジ回路における第 1 のスイッチング素子 11 及び第 4 のスイッチング素子 14 に供給する駆動信号、C' は第 3 のブリッジ回路における第 2 のスイッチング素子 42 及び第 3 のスイッチング素子 43 に供給する駆動信号である。なお、駆動信号 C の駆動期間 tc 及び駆動信号 C' の駆動期間 tc' の和はキャリア信号 cf の周期 Tc に略等しく設定しておく。

#### 【0038】

図 11 は、パルス幅変調增幅装置の構成を説明するブロック図である。図において、27 は後述する駆動信号生成部であり、前記駆動信号 (D, -D) をもとに、第 1 のブリッ

10

20

30

40

50

ジ回路における第1のスイッチング素子1及び第4のスイッチング素子4に供給する駆動信号A、第2のブリッジ回路における第2のスイッチング素子12及び第3のスイッチング素子13に供給する駆動信号A'、第3のブリッジ回路における第1のスイッチング素子41及び第4のスイッチング素子44に供給する駆動信号B、及び第1のブリッジ回路における第2のスイッチング素子2及び第3のスイッチング素子3に供給する駆動信号B'、第2のブリッジ回路における第1のスイッチング素子11及び第4のスイッチング素子14に供給する駆動信号C、及び第3のブリッジ回路における第2のスイッチング素子42及び第3のスイッチング素子43に供給する駆動信号C'を生成する。

## 【0039】

28は出力段であり、図9に示すように、第1の電源Vcc1に接続した第1のブリッジ回路、第2の電源Vcc2に接続した第2のブリッジ回路及び第3の電源Vcc3に接続した第3のブリッジ回路の並列回路から構成される。 10

## 【0040】

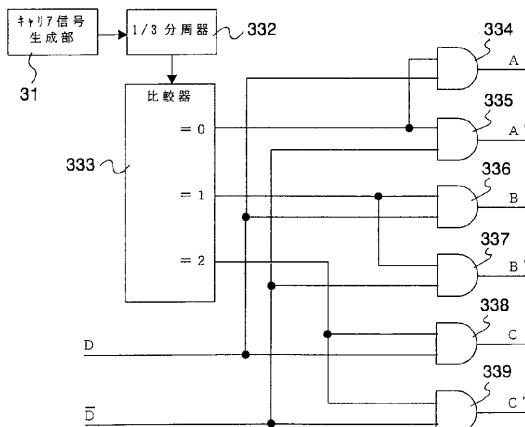

図12は、駆動信号生成部の詳細を説明する図である。図において、31は前記キャリア信号cfを生成するキャリア信号生成部、332はキャリア信号cfを1/3分周する分周器、333は比較器、334, 335, 336, 337, 338, 339はアンド回路である。

## 【0041】

図11及び図12に示すように、入力部21に入力したオーディオデータに対し、デジタルフィルタ22においてトーンコントロール、低域濾波等の演算処理を施した後、PWM生成部23において前記オーディオデータと三角波を比較しその比較結果をもとに駆動信号(D, -D)を生成する。 20

## 【0042】

駆動信号生成部27では、図12に示すように前記駆動信号(D, -D)と比較器333の出力との論理積をとることにより、駆動信号A, A', B, B', C, C'を得ることができる。このようにして得た駆動信号は、第1のブリッジ回路における第1のスイッチング素子1及び第4のスイッチング素子4、第2のブリッジ回路における第2のスイッチング素子12及び第3のスイッチング素子13、第3のブリッジ回路における第1のスイッチング素子41及び第4のスイッチング素子44、第1のブリッジ回路における第2のスイッチング素子2及び第3のスイッチング素子3、並びに第2のブリッジ回路における第1のスイッチング素子11及び第4のスイッチング素子14、第3のブリッジ回路における第2のスイッチング素子42及び第3のスイッチング素子43にそれぞれ供給する。 30

## 【0043】

スイッチング素子1, 4及び12, 13には、それぞれ図10に示す駆動信号A及びA'が入力され、駆動信号Aがアクティブになったとき、第1の電源Vcc1がスピーカ7に対して正方向に接続され、続いて駆動信号A'がアクティブになったとき、第2の電源Vcc2がスピーカ7に対して負方向に接続される。更に駆動信号Bがアクティブになったとき、第3の電源Vcc3がスピーカ7に対して正方向に接続され、続いて駆動信号B'がアクティブになったとき、第1の電源Vcc1がスピーカ7に対して負方向に接続される。更に駆動信号Cがアクティブになったとき、第2の電源Vcc2がスピーカ7に対して正方向に接続され、続いて駆動信号C'がアクティブになったとき、第3の電源Vcc3がスピーカ7に対して負方向に接続される。 40

## 【0044】

このように、各組のブリッジ回路における同一直流電源(Vcc1)に接続した第1のスイッチング素子1と第3のスイッチング素子3は、それぞれを駆動する駆動信号の間に他の直流電源(Vcc2, Vcc3)に接続したスイッチング素子を駆動する信号を挿入し、第1のスイッチング素子と第3のスイッチング素子がそれぞれ連続して導通しないように駆動する。

## 【0045】

10

20

30

40

50

このため、電源電流の供給に伴って一の電源の出力電圧が低下した場合においても、この電源は他の電源が電源電流を供給している間に出力電圧を回復することができる。従って、電源に大電流の負荷電流が流れた後においても電圧降下を回復させるための時間を確保することができるため、電源電圧の変動を抑制することができる。またこれにより出力の歪を抑制することができる。以上、3組の電源と3組のブリッジ回路を備える例について説明したが、これらは3組以上備えることができる。

#### 【0046】

3以上の奇数組とする場合には、各電源が出力回路に電源電圧を供給する順序を一定( $V_{cc1}, V_{cc2}, V_{cc3}, V_{cc1}, V_{cc2}, V_{cc3} \dots$ )にすることにより、次に電源電流を供給するまでの待機期間を等しくすることができる。このため、前記待機期間中に各電源電圧に生じた出力電圧の低下を回復させることにより各電源の電源電圧誤差によって生じるオフセットを低減することができる。一方、偶数組(例えば4組)とする場合には、各電源が出力回路に電源電流を供給する順序が( $V_{cc1}, V_{cc2}, V_{cc3}, V_{cc4}, V_{cc2}, V_{cc1}, V_{cc4}, V_{cc3} \dots$ )となる。この場合にも、各電源が連続して電源電流を供給しない構成とすることができる。しかし、次に電源電流を供給するまでの待機期間を等しくすることはできない。従って電源とブリッジ回路の組数は3以上の奇数組とすることが望ましい。

#### 【0047】

なお、駆動信号A, A'、B, B'、C, C'は、キャリア信号 $c_f$ に対して順番にアクティブになる。このため図9に示す例のように、出力段として3組の電源( $V_{cc1}, V_{cc2}, V_{cc3}$ )と、3組のブリッジ回路を用いた場合は、各電源から電力を取り出す期間(例えば信号A, A'がアクティブとなる期間)は全アクティブ期間( $3T_c$ )の $1/3$ 未満である。なお、本実施形態では各電源電圧が同一である場合を説明したが、電源電圧が異なる場合でも本発明の効果がある。

#### 【0048】

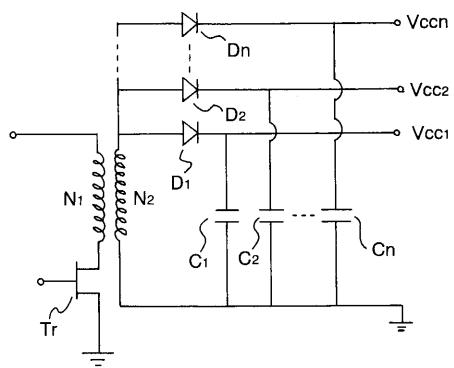

図13は、複数の出力を有する電源( $V_{cc1}, V_{cc2} \dots V_{ccn}$ )の構成を説明する図である。図において、 $T_r$ はスイッチングトランジスタ、 $N_1$ は一次側巻線、 $N_2$ は二次側巻線、 $D_1$ ないし $D_n$ はダイオード、 $C_1$ ないし $C_n$ はそれぞれダイオード $D_1$ ないし $D_n$ に接続した平滑用のコンデンサであり、これらのコンデンサ $C_1$ ないし $C_n$ の両端から同一の電源電圧( $V_{cc1}, V_{cc2} \dots V_{ccn}$ )を得ることができる。なお、戦記スイッチングトランジスタのスイッチング周波数は前記キャリア信号 $c_f$ の周波数に比して十分高く設定することが望ましい。

#### 【0049】

以上説明したように、本発明の各実施形態によれば、電源に大電流が流れた後に、電源の電圧降下を復帰させるための時間を与えることができる。このため、電源電圧変動を抑制し、電源電圧変動に伴う出力歪みを抑制することができる。

#### 【図面の簡単な説明】

#### 【0050】

【図1】本発明の実施形態にかかるパルス幅変調增幅装置を説明する図である。

【図2】パルス幅変調增幅装置の各部の動作波形を説明する図である。

【図3】パルス幅変調增幅装置の構成を説明するブロック図である。

【図4】駆動信号生成部の詳細を説明する図である。

【図5】従来のパルス幅変調增幅装置を説明する図である。

【図6】従来のパルス幅変調增幅装置の各部の動作波形を説明する図である。

【図7】従来のパルス幅変調增幅装置の構成を説明するブロック図である。

【図8】第2の実施形態を説明する図である。

【図9】第3の実施形態にかかるパルス幅変調增幅装置を説明する図である。

【図10】パルス幅変調增幅装置の各部の動作波形を説明する図である。

【図11】パルス幅変調增幅装置の構成を説明するブロック図である。

【図12】駆動信号生成部の詳細を説明する図である。

10

20

30

40

50

【図13】複数の出力を有する電源の構成を説明する図である。

【符号の説明】

【0051】

1, 2, 3, 4, 11, 12, 13, 14, 41, 42, 43, 44 スイッチング素子

5, 6 ローパスフィルタ

7 スピーカ

21 入力部

22 デジタルフィルタ

23 PWM生成部

24, 26, 28 出力段

25 駆動信号生成部

31 キャリア信号生成部

32 分周器

33 ノット回路

34~37, 334~339 アンド回路

333 比較器

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図10】

【図8】

【図9】

【図11】

【図12】

【図13】