# (19) United States

## (12) Patent Application Publication (10) Pub. No.: US 2005/0229078 A1 Kikuchi et al.

## (43) Pub. Date:

# Oct. 13, 2005

#### (54) CODING SYSTEM AND DECODING SYSTEM

(75) Inventors: Yoshihiro Kikuchi, Yokohama-Shi (JP); Toshiaki Watanabe, Yokohama-Shi (JP); Kenshi Dachiku, Kawasaki-Shi (JP); Takeshi Chujoh, Tokyo-To (JP); Takeshi Nagai, Tokyo-To (JP)

> Correspondence Address: FINNEGAN, HENDERSON, FARABOW, **GARRETT & DUNNER** LLP 901 NEW YORK AVENUE, NW **WASHINGTON, DC 20001-4413 (US)**

(73) Assignee: Kabushiki Kaisha Toshiba, Kawasaki-

shi (JP)

(21) Appl. No.: 11/127,203

(22) Filed: May 12, 2005

## Related U.S. Application Data

Continuation of application No. 10/023,851, filed on Dec. 21, 2001, now Pat. No. 6,918,080, which is a continuation of application No. 09/142,871, filed on Sep. 16, 1998, now Pat. No. 6,571,361, filed as 371 of international application No. PCT/JP97/00864, filed on Mar. 18, 1997, which is a continuation-in-part of application No. 08/720,067, filed on Sep. 27, 1996, now Pat. No. 5,862,153.

#### (30)Foreign Application Priority Data

| G 20 1005     | (TD) | 25,002,4005 |

|---------------|------|-------------|

| Sep. 29, 1995 | (JP) | 276993/1995 |

| Mar. 18, 1996 | (JP) | 61450/1996  |

| Jun. 24, 1996 | (JP) | 163082/1996 |

| Sep. 2, 1996  | (JP) |             |

| Sep. 13, 1996 | (JP) |             |

#### **Publication Classification**

| (51) | Int. Cl. <sup>7</sup> | Н03М | 13/00  |

|------|-----------------------|------|--------|

| (52) | U.S. Cl.              |      | 14/758 |

#### **ABSTRACT** (57)

In a coding system wherein an error correction/detect-ion coding is combined with a synchronization recovering technique using a synchronization code, the problems of a pseudo synchronization and a step out due to error detect-ion are solved. There is provided a coding part 212 for coding an input multiplexed code string 201 to an error correcting-/ detecting code comprising an information bit and a check bit, and code string assembling part 213 for inserting a synchronization code into any one of a plurality of periodically predetermined synchronization code inserting positions in the code string 201, for arranging the information bit at an optional position in the code string, and for arranging the check bit at a position other than the synchronization code inserting positions in the code string 201 to assemble an output code string 205.

FIG. 2

FIG. (3)

FIG. 4

FIG.5

FIG.6

SYNCHRONIZATION CODE DETECTION

WINDOW OF "sync-0-len+2"BIT

BIT IS ADDED

**FIG.12**

FIG. 13

FIG. 14

FIG. 15

FIG. 16

FIG. 21

FIG. 24

FIG.30

FIG.31

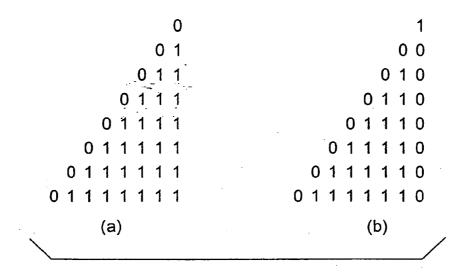

00000000 00000000 00000001 00010101 SEC 00000000 00000000 00000001 00101010 **PSC** 00000000 00000000 00000001 00000000 **GSC** 00000000 00000000 1

(a)

FIG.34

### CODING SYSTEM AND DECODING SYSTEM

#### TECHNICAL FIELD

[0001] The present invention relates generally to a system for transmitting and/or storing information via a medium of a high error rate, such as a radio transmission line. More specifically, the invention relates to a coding and/or decoding system suited to carry out the error correction/detection coding of a compressed code string obtained by the high efficiency compression coding to transmit and/or store the compressed code string.

#### BACKGROUND ART

[0002] For example, in a system for carrying out the high-efficient compression coding of a picture and/or voice information so as to have a small information content to transmit the compression-coded picture and/or voice information via a radio transmission line, such as a radio visual telephone, a portable information terminal and a digital television broadcast system, it is important how to transmit the obtained code string with a high quality since the transmission line has a high error rate.

[0003] In a case where a code string is transmitted and/or stored via such a medium of a high error rate, an error correcting code, such as a Bose-Chaudhuri-Hocquenghem (BCH) code, a Recommended Standard (RS) code and a convolutional code, is often used as means for reducing the error rate. In addition, an error correcting code, such as a check sum and a cyclic redundancy check (CRC), is used as means for enabling the error correction on the receiving side. The aforementioned error correction and/or error detection adds excessive bits (redundancy) to the transmitted and/or stored information in accordance with a predetermined rule to examine whether the transmitted and/or stored code string obeys the rule during decoding, to carry out the error correction/detection on the basis of the results.

[0004] However, in such a method for coding a code string obtained by a high-efficiency compression coding into error correcting/detecting codes to transmit and/or store the codes, there is a disadvantage in that it is difficult to be combined with a synchronous recovering technique for recovering a step out caused by a code word error in the transmission line/medium. As a synchronous recovering technique, a method for inserting a uniformly decodable code called a synchronization code to resume the decoding immediately after the synchronization code is detected when a step out occurs is often used.

[0005] In order to make a uniformly decodable code word of the synchronization code, the code word must be combined with another code word so as not to form the same bit pattern as the synchronization code. However, in an error correction-/detection coding, it is generally difficult to form a code word so as to prevent a certain bit pattern from occurring. When the same bit pattern as the synchronization code occurs, a pseudo synchronization may be caused by the error detection of the synchronization code.

[0006] In order to avoid this problem, there is used a method for preventing the pseudo synchronization by determining whether the same bit pattern as the synchronization code exists in the code string after performing the error correction/detection coding, inserting a dummy bit into the

bit pattern in accordance with a certain rule when the same bit pattern exists, and deleting the dummy bit in the same rule in a decoding system. However, in a case where the code string is transmitted and/or stored via a medium in which errors are easy to occur, errors may occur in the inserted bit, so that there is a problem in that a new step out or a new pseudo synchronization may occur.

[0007] In addition, in a case where the error correction/ detection coding of a code string is carried out to insert a synchronization code, there is also a problem in that the coding efficiency is lowered since it is required to add many inserted bits to the code string in order to compensate an excess of information bits, for which the error detection and/or detection coding is to be carried out, at the end portion of a synchronization interval between the adjacent synchronization codes.

[0008] On the other hand, in order to enhance the error correcting/detecting capability, the redundancy of the transmitted and/or stored information may be enhanced. However, if the redundancy is enhanced, the number of bits required to transmit the same information is increased. Therefore, if the error correcting/detecting capability is enhanced, it is required to provide a transmission line of a higher transmission rate, or the number of bits of information to be stored is increased. In addition, if the transmission rate and the stored capacity are the same, the amount of information, which can be transmitted and/or stored, is decreased as the redundancy is enhanced. In a case where a picture and/or voice information is high-efficiently compression-coded to be transmitted and/or stored, in order to add the redundancy to improve the error resistance, the compression coding into a smaller amount of information must be carried out if the transmission and/or storage rate is the same, so that the picture quality and sound quality are lowered.

[0009] Therefore, as a method for providing a smaller redundancy and a high error resistance, there is a method called hierarchical coding. This is a method for enhancing the error resistance using the same means redundancy in comparison with when the same error correcting/detecting code is used, by classifying the high-efficiency compression-coded information in accordance with the magnitude of errors influencing the picture quality and the sound quality, using an error correcting/detecting code of a higher error correction/detection capacity while having a high redundancy, for information under a great influence of the error, and using an error correcting/detecting code of a less redundancy while having not so high error correction/detection capacity, for information which is not so greatly influenced by the error.

[0010] For example, in a coding system, which is formed by combining the motion-compensated prediction with the orthogonal transform and which is often used for the high-efficiency compression coding of a dynamic image, i.e., in a system for motion compensation predicting an input dynamic image signal to orthogonal transform its prediction residue by a DCT (discrete cosine transform) or the like, the error correcting/detecting codes of a high error correcting/detecting capability are used for motion vector information, which greatly deteriorate the picture quality if an error occurs, and for lower coefficients of the orthogonal transformation coefficients of the prediction residual signal, and

the error correcting/detecting codes of a low error correcting-/detecting capability are used for higher coefficients of the orthogonal transformation coefficients of the prediction residual signal, which are under a small influence of the error.

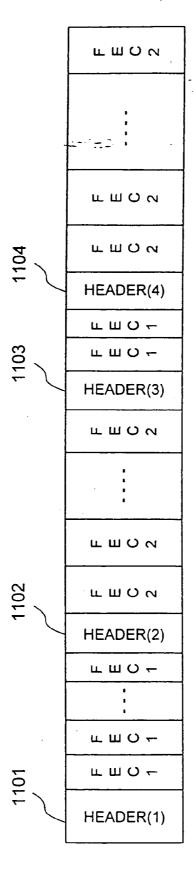

[0011] In order to achieve such a hierarchical coding, it is required to switch the error correcting/detecting codes of different error correcting/detecting capabilities in the middle of the output code string. As a method for switching the error correcting/detecting codes of different error correcting/detecting capabilities, there is a method for adding a header information representative of the kind of the error correcting/detecting codes to a code string. FIG. 11 shows an example of a code string, to which the header information is added to switch the error correcting/detecting codes. In this example, two kinds of error correcting/detecting codes FEC1 and FEC2 are switched. The headers 1101 to 1104 have a header information representative of the kind of the error correcting/detecting codes and the number of the code words. In a coding system, code words, which are error correction/detection coded, are arranged after the header information. In a decoding system, the header information is decoded, and the error correcting/detecting codes are decoded in accordance with the decoding of the header information.

[0012] However, in the method for switching the error correcting/detecting codes by adding such a header information, there is a problem in that the number of bits of the code string to be transmitted and/or stored by adding the header information is increased. In a case where the picture and/or voice information is high-efficiency compression coded to be transmitted and/or stored, if the number of bits is occupied by the header information, the number of bits used for the high-efficiency compression coding of the picture and/or voice information is decreased, so that the picture quality and sound quality are deteriorated.

[0013] As mentioned above, if the error correction/detection coding of the code string, in which the high-efficiency compression coding of dynamic image signals and so forth is performed, is carried out, an optional bit pattern is produced. Therefore, in a case where the error correction-/detection coding is combined with the synchronous recovering technique using a uniformly decodable synchronization code, there is a problem in that a pseudo synchronization is caused by the error detection of the synchronization code. Also in a case where the dummy bit is inserted to prevent the pseudo synchronization, there is a problem in that a new step out or a new pseudo synchronization is caused by the error of the inserted bit.

[0014] In addition, in a case where the error correction-/detection coding of the code string is performed and the synchronization code is inserted, it is conventionally required to use many inserted bits to compensate an excess of information bits, for which the error detection and/or detection coding is to be carried out, at the end portion of a synchronization interval between the adjacent synchronization codes, so that there is a problem in that the coding efficiency is lowered.

[0015] Moreover, in a coding/decoding system for switching error correcting/detecting codes of different error correcting/detecting capabilities by adding a header information, the number of bits to be transmitted and/or stored by

adding the header information is increased. Therefore, in a case where a picture and/or voice information is high-efficiency compression coded to be transmitted and/or stored, there is a problem in that the information content assigned to the picture and/or voice information is decreased to lower the picture quality and the sound quality.

#### DISCLOSURE OF INVENTION

[0016] It is therefore a principal object of the present invention to eliminate the aforementioned problems and to provide coding and decoding systems, which can prevent a pseudo synchronization and a step out due to the error detection of a synchronization code.

[0017] It is another object of the present invention to provide coding and decoding systems, which prevent a pseudo synchronization and a step out due to the error detection when an error correction/detection coding is combined with a synchronization recovering technique using a synchronization code.

[0018] It is further object of the present invention to provide coding and decoding systems, which can decrease the number of inserted bits used at the end portion in a synchronization interval to enhance the coding efficiency, when an error correction/detection coding is combined with a synchronization recovering technique using a synchronization code.

[0019] It is still further object of the present invention to provide coding and decoding systems which can decrease the number of bits of a code string, to which a header information representative of the kind of error correction/detection coding must be added and which is transmitted and/or stored, to improve the quality of information.

[0020] (1) A first coding system, according to the present invention, comprises: coding means for coding an input code string to an error correcting/detecting code comprising an information bit and a check bit; and code string assembling means for inserting a synchronization code into any one of a plurality of predetermined synchronization code inserting positions in an output code string, for arranging the information bit at an optional position in the output code string, and for arranging the check bit at a position other than the synchronization code inserting positions in the output code string to assemble the output code string.

[0021] A first decoding system, according to the present invention, comprises: synchronization code detecting means for detecting a synchronization code at a plurality of predetermined synchronization code inserting positions on the basis of a code string, which is coded to an error correcting/detecting code comprising an information bit and a check bit; code string resolving means for resolving the code string to extract the information bit of the error correcting/detecting code and the check bit of the error correcting/detecting code arranged at a position other than the synchronization code inserting positions; and decoding means for receiving the information bit and the check bit extracted by the code string resolving means to decode the error correcting/detecting code.

[0022] Thus, in the first coding/decoding system, the synchronization code exists only at the predetermined synchronization code inserting position in the output code string, and the check bit of the error correcting/detecting code

exists at a position other than the synchronization code inserting position. Therefore, even if the same bit pattern as the synchronization code is contained in the check bit, there is no probability that it is erroneously detected that the same bit pattern as the synchronization code is a synchronization code. Accordingly, since it is not required to use a special error correcting/detecting code for preventing a particular bit pattern and to insert a bit for preventing a synchronization code after the error correction/detection coding, the degree of freedom for the used error correcting/detecting code can be increased. In addition, since there is no probability that a new synchronization detection error may occur due to the insertion of an error into an inserted bit, it is possible to improve the resistance to errors.

[0023] (2) In a second coding system according to the present invention, code string transforming means is added to the first coding system. The code string transforming means transforms an input code string other than synchronization codes arranged at a plurality of predetermined synchronization code inserting positions in an output code string so that a humming distance from the synchronization code is equal to or greater than a predetermined value. The code string transformed by the code string transforming means is inputted to coding means to be coded to an error correcting/detecting code comprising an information bit and a check bit.

[0024] In a second decoding system according to the present invention, code string transforming means is added to the first decoding system. The code string transforming means transforms a code string other than the synchronization code, which exists at a synchronization code inserting position and which is transformed so that a humming distance from the synchronization code in the code string decoded by the decoding means is equal to or greater than a predetermined value, into the original code string.

[0025] Thus, in the second coding/decoding system, the coding system carries out the transforming process so that the humming distance from the synchronization code with respect to a bit string arranged at the synchronization code inserting position is equal to or greater than a predetermined value, and the decoding system carries out the reverse transformation. Therefore, since the same bit pattern as the synchronization code is not contained in the bit string, it is possible to prevent the error detection of a synchronization code. In addition, if the transform is carried out so that the humming distances between the synchronization code and the other code strings are great, the synchronization code can be distinguished from the other code strings even if an error is mixed into the code strings, so that the probability of the error detection of the synchronization code due to errors can be decreased.

[0026] Since this transforming/inverse transforming process is carried out only at the synchronization code inserting position, the overhead is less than those in conventional methods for carrying out transforming/inverse transforming process over the whole code string. In addition, in the code string inputted to the coding system, it is not required to carry out the transforming process so as not to produce the same bit pattern as the synchronization code, and it is not required to use a special code string. In particular, in a case where a variable length coding system for switching and using different code word tables is used as an input of this

coding system, if the code word table is prepared so as not to produce the same pattern as the synchronization code in the variable length coding system, there is a problem in that the coding efficiency is lowered. However, the second coding/decoding system can eliminate such a problem.

[0027] (3) A third coding system, according to the present invention, comprises: coding means for coding an input code string to an error correcting/detecting code; synchronization code inserting means for inserting a synchronization code into the code string; and determining means for determining the number of bits an information to be coded to an error correcting/detecting code immediately before the synchronization code in the code string, wherein the coding means causes the error correcting/detecting code immediately before the synchronization code, to be a degenerate code, which adaptively degenerated on the basis of the number of bits determined by the determining means.

[0028] A third decoding system, according to the present invention, comprises: decoding means for decoding a code string, which is coded to an error correcting/detecting code and into which a synchronization code is inserted; synchronization code detecting means for detecting the synchronization code in the code string; and determining means for determining the number of bits of an information, which is coded to an error correcting/detecting code immediately before the synchronization code in the code string detected by the synchronization code detecting means, wherein the decoding means decodes by identifying whether the error correcting/detecting code immediately before the synchronization code is a degenerate code on the basis of the determined result of the determining means.

[0029] Thus, in the third coding/decoding system, since a degenerate code degenerated to the number of bits required to code the information bit remaining at the end portion of a synchronization interval is used as the error correcting-/detecting code immediately before the synchronization code, it is not required to use many inserted bits in order to compensate the remainder of the information bit at the end portion of the synchronization interval, so that the coding efficiency can be improved.

[0030] (4) A fourth coding system, according to the present invention, comprises: coding means for coding a code string containing kinds of input information to an error correct-ing/detecting code; and switching means for switching the kind of the error correcting/detecting code in accordance with the kinds of the input information in the code string.

[0031] A fourth decoding system, according to the present invention, comprises: decoding means for decoding a code string, which is coded to a different kind of error correcting/detecting code in accordance of the kind of information, to generate the original information; and means for determining the kind of the error correcting-/detecting code on the basis of the kind of information generated by the decoding means, to inform the decoding means.

[0032] Thus, in the fourth coding/decoding system, in a case where the coding/decoding is carried out by switching the error correcting/detecting code in accordance with the kind of information, the coding system switches the error correcting/detecting code in accordance with the kind of information of the input code string, and the decoding

system determines the kind of the error correcting-/detecting code on the basis of the decoded information to carry out the same switching as that of the coding system. Therefore, it is not required to use a header information representative of the kind of the error correcting/detecting code unlike conventional systems, so that it is possible to remove the overhead due to the header information.

[0033] (5) A fifth coding system, according to the present invention, comprises: code string transforming means for transforming an input code string other than synchronization codes, which are arranged at a plurality of predetermined synchronization code inserting positions in an output code string and in intervals of a predetermined number of bits before and after the predetermined synchronization code inserting positions in an output code string, so that a humming distance from the synchronization code is equal to or greater than a predetermined value; coding means for coding a code string transformed by the code string transforming means, to an error correcting-/detecting code comprising an information bit and a check bit; and code string assembling means for inserting a synchronization code into any one of a plurality of predetermined synchronization code inserting positions in the output code string, for arranging the information bit at an optional position in the output code string, and for arranging the check bit at a position other than the synchronization code inserting positions in the output code string to assemble the output code string.

[0034] A fifth decoding system, according to the present invention, comprises: synchronization code detecting means for detecting a synchronization code at a predetermined synchronization code inserting position and in an interval of a predetermined number of bits before and after the predetermined synchronization code inserting position, on the basis of a code string, which is coded to an error correcting/ detecting code comprising an information bit and a check bit and into which the synchronization code; code string resolving means for resolving the code string to extract the information bit of the error correcting-/detecting code and the check bit of the error correcting/detecting code arranged at a position other than the synchronization code inserting position; decoding means for receiving the information bit and the check bit extracted by the code string resolving means to decode the error correcting/detecting code; and code string transforming means for transforming a code string other than the synchronization code, which is transformed so that a humming distance from the synchronization code in the code string decoded by the decoding means is equal to or greater than a predetermined value and which exists at the synchronization code inserting position and in an interval of a predetermined number of bits before and after the synchronization code inserting position, into the original code string.

[0035] Thus, in the fifth coding/decoding system, the input code string is transformed in the synchronization code inserting interval as well as in the interval of the predetermined number of bits before and after the synchronization code inserting interval so that the humming distance is equal to or greater than the predetermined value, and the decoding system carries out the reverse transformation of the input code string, so that the same bit pattern as the synchronization code is not contained in this interval. Therefore, even if the transmission/storage of a bit string coded through a transmission line or a storage medium for causing a bit loss,

in which a part of bits is lost, and a bit addition, in which an excess bit is added, is carried out, the synchronization code can be distinguished from the other code strings if the number of lost/added bits is equal to or less than a predetermined number of bits, so that the decoding system can correctly carry out the synchronization detection.

[0036] (6) A sixth coding system, according to the present invention, comprises: multiplexing means for multiplexing kinds of compressed codes, which are obtained by compression coding an input signal, to produce a multiplexed code string; and code string assembling means for inputting the multiplexed code string to assemble an output code string, wherein the code string assembling means inserts a synchronization code into any one of a plurality of periodically predetermined synchronization code inserting positions in the output code string.

[0037] In this case, in order to insert the synchronization code into any one of the plurality of periodically predetermined synchronization code inserting positions in the output code string, the code string assembling means inserts a stuffing bit into the output code string, or periodically determines the plurality of synchronization code inserting positions in the output code string and inserts an information (a pointer information) representative of the boundary of the multiplexed code string, to insert the synchronization code into any one of the plurality of synchronization code inserted only into any one of the plurality of periodically predetermined synchronization code inserting positions.

[0038] The stuffing bit is preferably a code, which can be uniformly decoded in a backward direction of the output code string. Thus, if the decoding system compares the decoding end position of the code string immediately before the stuffing bit with the starting position of the stuffing bit, it is possible to easily detect an error in the input code string.

[0039] Moreover, the humming distances of the stuffing bit from the synchronization code and the part thereof are preferably equal to or greater than a predetermined value. Thus, there is an advantage in that the probability of the occurrence of a pseudo synchronization.

[0040] A sixth decoding system, according to the present invention, comprises: synchronization code detecting means for detecting a synchronization code in an output code string; demultiplexing means for demultiplexing on the basis of the position of the synchronization code detected by the synchronization code detecting means from the input code string, to produce a compressed code string; and decoding means for decoding the compressed code to output a reconstructed signal, wherein the synchronization code detecting means detects the synchronization code at a plurality of periodically predetermined synchronization code inserting positions in the input code string.

[0041] Thus, in the case of the sixth coding/decoding system, since the coding system inserts the synchronization code into the multiplexed code string, which is obtained by multiplexing kinds of compressed codes, only at the periodically predetermined synchronization code inserting positions, the decoding system may carry out the synchronization detection only at the synchronization code inserting positions, so that the number of synchronization code detecting processes can be decreased in comparison with conven-

tional systems for inserting a synchronization code into a code string at an optional position. In addition, in accordance with the decrease of the number of the synchronization code detecting processes, it is possible to decrease the probability that a pseudo synchronization occurs because of the bit string inputted to the decoding system changed to the same bit pattern as the synchronization code due to bit error. Therefore, according to the present invention, it is possible to decrease the number of the occurrences of the pseudo synchronization, so that the processing quantity in the synchronization code detection can be decreased.

[0042] (7) In a seventh coding system according to the present invention, code string transforming means is added to the sixth coding system. The code string transforming means transforms a code string other than said synchronization code, which is arranged at said synchronization code inserting position in said output code string, so that a humming distance from said synchronization code is equal to or greater than a predetermined value.

[0043] A seventh decoding system, according to the present invention, further comprises: code string transforming means for transforming a code string other than the synchronization code, which is transformed so that a humming distance from the synchronization code is equal to or greater than a predetermined value at the synchronization code inserting position of the input code string, into the original code string.

[0044] Thus, in the seventh coding/decoding system, in addition to the construction of the sixth coding/decoding system, the bit insertion in view of the error of the synchronization code, i.e., the transformation of the humming distance of the bit string arranged at the synchronization code inserting position from the synchronization code, is carried out, so that the same bit pattern as the synchronization code is contained in the bit code string. Therefore, it is possible to ensure that the error detection of the synchronization code does not occur with respect to an error of a supposed number of bits or less, so that it is possible to decrease the probability of the error detection of the synchronization code.

[0045] Furthermore, in the present invention, the synchronization code is a code string, which is inserted into a code string for synchronization recovery and which can be uniformly decoded. For example, if a code string for inserting a synchronization code is a multiplexed code string, which is obtained by multiplexing a plurality of kinds of compressed codes obtained by compression coding an image signal inputted for each frame, the synchronization code is a code representative of a partition of a coding frame, partitions of the plurality of kinds of compressed codes, and other partitions.

[0046] As described above, according to the present invention, the following advantages can be obtained.

[0047] (1) According to the first coding/decoding system, the synchronization codes are inserted only into the synchronization code inserting positions arranged at regular intervals, and the check bits of the error correcting-/detecting code are shifted so as to exist at positions other than the synchronization code inserting positions. Therefore, even if the same bit pattern as the synchronization code occurs in the check bit, the same pattern as the synchronization code

does not occur at the synchroni-zation code inserting position, and, in theory, there is no probability that synchronization is detected.

[0048] In addition, if the bit insertion into a code string at the synchronization code inserting position is carried out so as not to produce a pseudo synchronization code, it is possible to eliminate the difficulty in forming a code word so as not to produce the same bit pattern as the synchroni-zation bit.

[0049] (2) According to the second coding/decoding system, in addition to the construction of the first coding system, the bit insertion is carried out in view of the synchronization code, i.e., the transforming process is carried out so that the humming distance from the synchronization code is equal to or greater than the predetermined value with respect to the bit string arranged at the synchronization code inserting position, and the decoding system carries out the backward transformation, so that the bit code does not contain the same bit pattern as the synchronization code. Therefore, it is possible to ensure to prevent the error detection of the synchronization code from occurring due to the errors of the supposed number of bits or less, so that the probability of the error detection of the synchronization code is decreased. In addition, if such transformation is carried out, it is possible to distinguish the synchronization code from the other code strings even if an error is mixed into the code string, so that the probability of the error detection of the synchronization code due to errors can be decreased.

[0050] Moreover, since the error correction/detection coding is carried out after the code word is transformed by the bit insertion, the error protection is carried out for the inserted bit. Therefore, in comparison with conventional systems for carrying out the bit insertion after the error correction/detection coding, the probability that an error occurs in the inserted bit is decreased. In addition, since the bit insertion is carried out only into the synchronization code inserting position, the increase of the quantity of cods due to the bit insertion is smaller than that in conventional systems for carrying out the bit insertion over the whole code string, so that the coding efficiency is improved.

[0051] (3) According to the third coding/decoding system, since the error correcting/detecting code immediately before the synchronization code is a degenerate code, it is possible to decrease the number of inserted bits for compensating the remainder of the information bit at the portion immediately before the synchronization code, to improve the coding efficiency, in comparison with conventional coding systems.

[0052] (4) According to the fourth coding/decoding system, the coding system utilizes the multiplexing rule in the high-efficiency compression coding system, such as image and voice, and switches the error correcting/detecting code in accordance with the kind of the information of an input code\_string, and the decoding system determines the kind of the error correcting/detecting-code on the basis of the decoded information to carry out the same switching as that of the coding system. Therefore, it is not required to add the header information representative of the kind of the error correcting/detecting code, and it is possible to assign the number of bits to high efficiency compression coding, such as image and voice, so that it is possible to improve the information quality, such as picture quality and sound quality.

[0053] (5) According to fifth coding/decoding system, the coding system transforms an input code string so that a humming distance in a synchronization code inserting interval as well as a humming distance in an interval of a predetermined number of bits before and after the synchronization code inserting interval are equal to or greater than a predetermined value, and the decoding system carries out the inverse transformation of the input code string, so that it is possible to prevent the same bit pattern as the synchronization code from being contained in this interval. Therefore, even if a bit string coded through a transmission line and/or a storage medium, which may cause a bit loss for losing a part of bit is lost and a bit addition for adding an excess bit, is transmitted/stored, if the number of lost/added bits is equal to or less than a predetermined number of bits, it is possible to distinguish a synchronization code from other code strings, so that the decoding system can correctly carry out the synchronization detection.

[0054] (6) According to the sixth coding/decoding system, since the coding system inserts synchronization codes only into synchronization code inserting positions periodically predetermined in a multiplexed code string, which is obtained by multiplexing kinds of compressed codes, the decoding system may carry out the synchronization detection only at the synchronization code inserting positions, so that the number of the synchronization code detecting processes can be decreased in comparison with conventional systems for inserting synchronization codes into a code string at optional positions.

[0055] In addition, since the probability that a pseudo synchronization occurs by the variation of the bit string inputted to the decoding system into the same bit pattern as the synchronization code, is decreased in accordance with the decrease of the number of the synchronization code detecting processes, it is possible to prevent the pseudo synchronization according to the present invention, so that the processing quantity for the synchronization code detection decreases.

[0056] (7) According to the seventh coding/decoding system, in addition to the construction of the sixth coding/decoding system, the bit insertion in view of the error of the synchronization code, i.e., the transformation of the humming distance of the bit string at the synchronization code inserting position from the synchronization code is carried out, so that the same bit pattern as the synchronization code is not contained in the bit string. Therefore, it is ensured that the error detection of the synchronization code does not occur with respect to errors of the supposed number of bits, so that the probability of error detection of synchronization codes can be decreased.

# BRIEF DESCRIPTION OF THE DRAWINGS

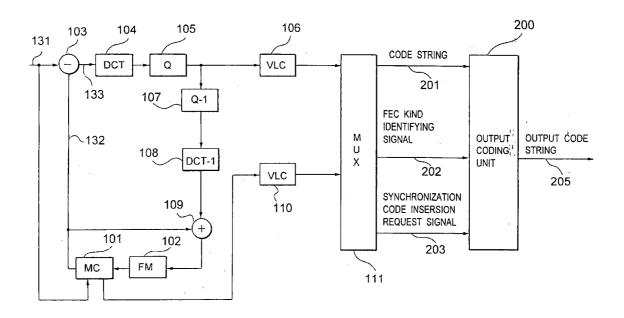

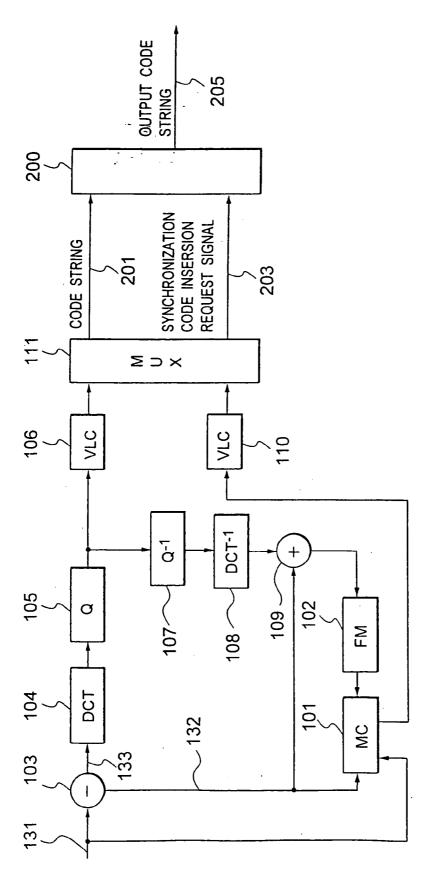

[0057] FIG. 1 is a block diagram of the first and second preferred embodiments of a dynamic image coding system according to the present invention.

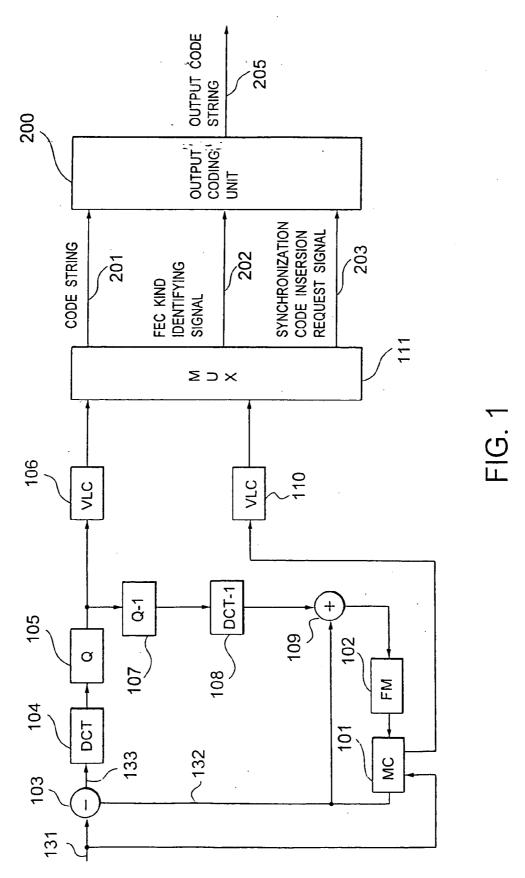

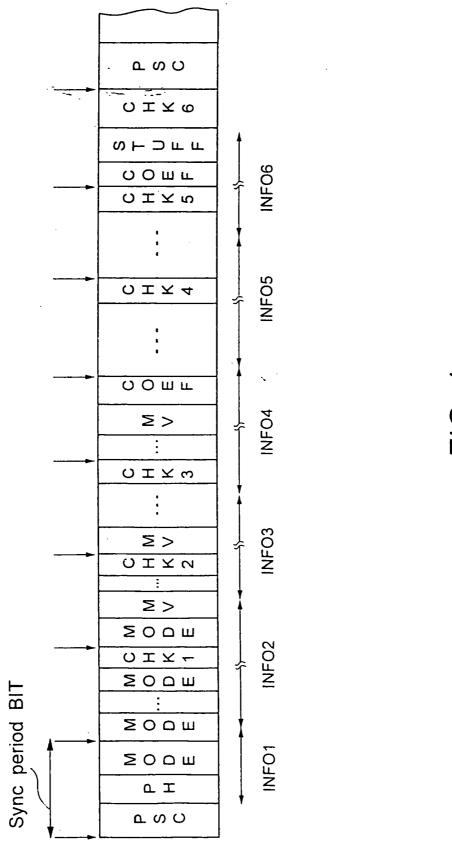

[0058] FIG. 2 is a diagram illustrating a multiplexing rule in a multiplexer of the dynamic image coding system of FIG. 1.

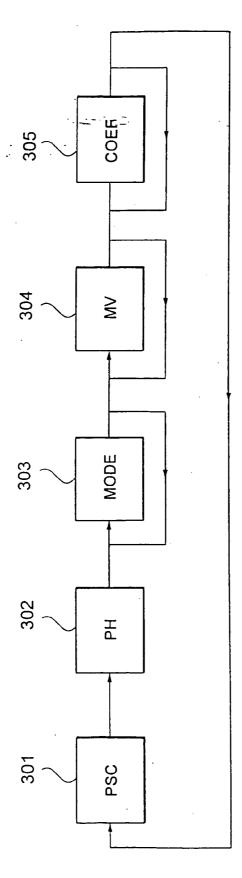

[0059] FIG. 3 is a block diagram of an output coding unit of the dynamic image coding system of FIG. 1.

[0060] FIG. 4 is a diagram illustrating an example of an output code string of the dynamic image coding system of FIG. 1.

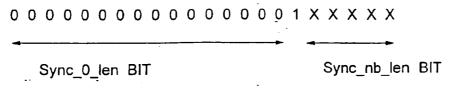

[0061] FIG. 5 is a diagram illustrating an example of a synchronization code.

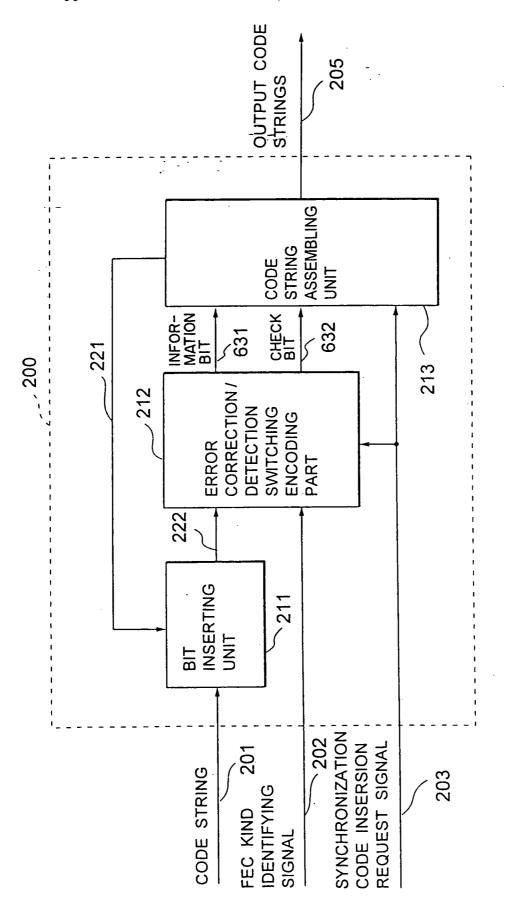

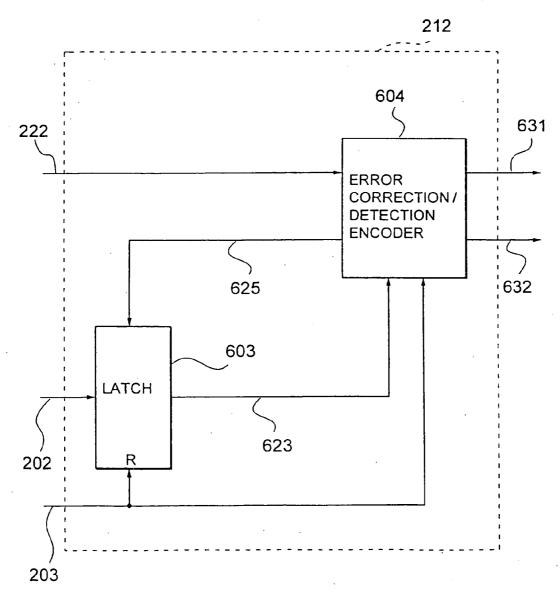

[0062] FIG. 6 is a block diagram of an error correction-/detection switching coding part in the output coding unit of FIG. 3.

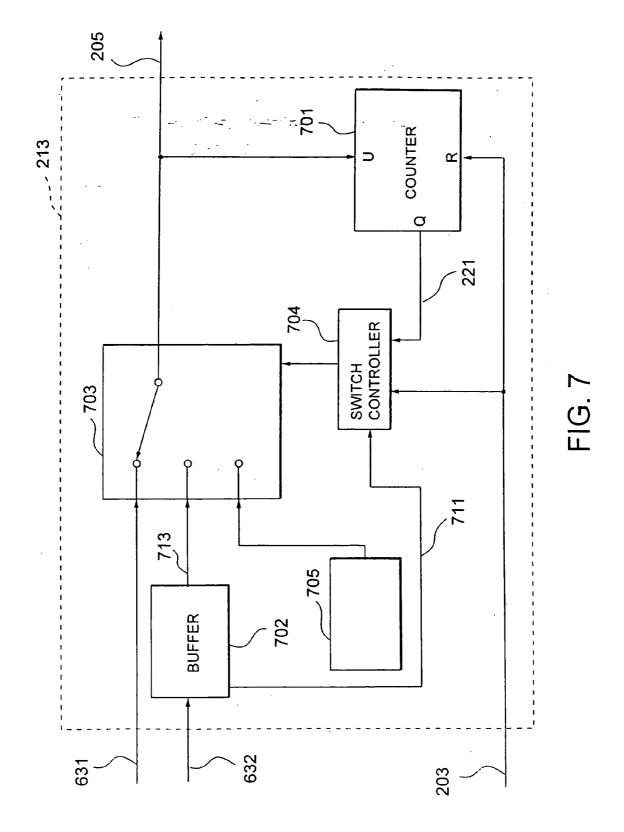

[0063] FIG. 7 is a block diagram of a code string assembling unit of the output coding unit of FIG. 3.

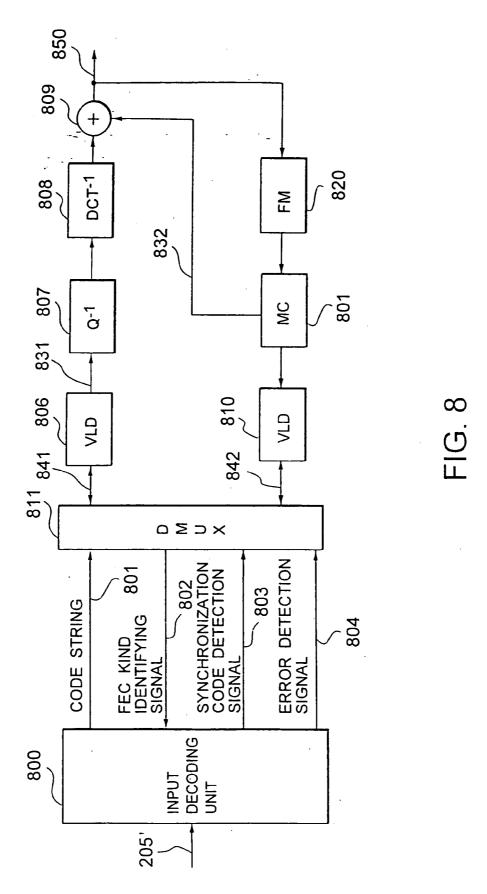

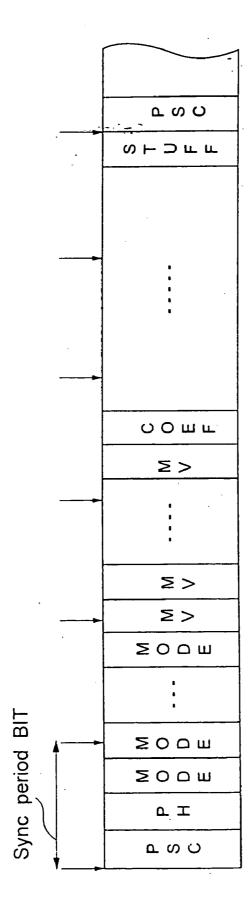

[0064] FIG. 8 is a block diagram of the first and second preferred embodiments of a dynamic image decoding system according to the present invention.

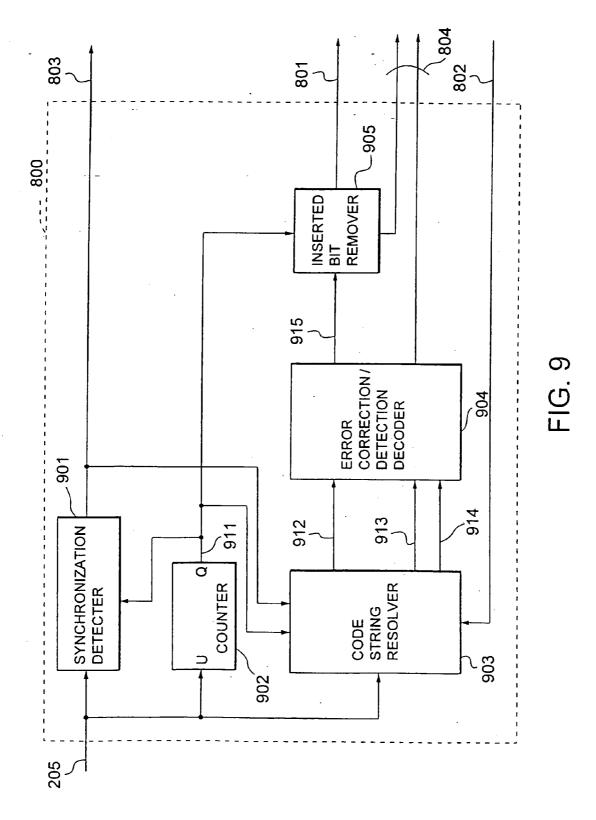

[0065] FIG. 9 is a block diagram of an input decoding unit of the dynamic image decoding system of FIG. 8.

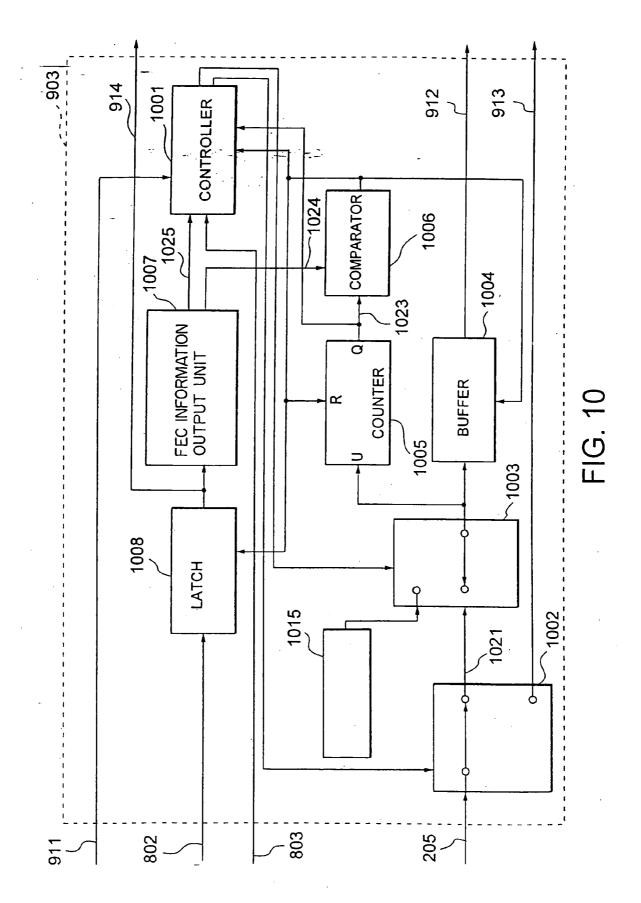

[0066] FIG. 10 is a block diagram of a code string resolver of the input decoding unit of FIG. 9.

[0067] FIG. 11 is a diagram illustrating an example of a code string obtained by a conventional error correction-/detection switching coding system.

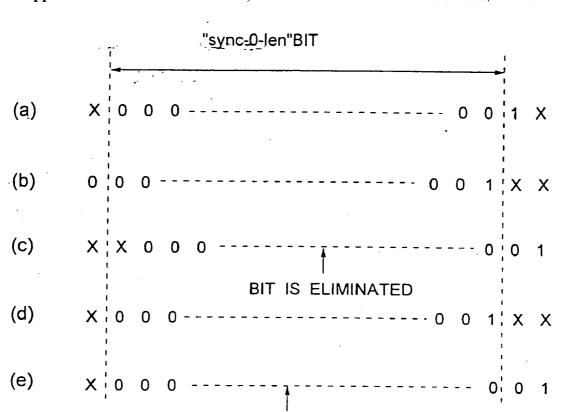

[0068] FIG. 12 is a diagram illustrating an example of a synchronization code, in which an error is caused by the addition/loss of a bit(s) in a transmission line, for explaining the second preferred embodiment of the present invention.

[0069] FIG. 13 is a diagram explaining the operation of a bit inserting unit of FIG. 3 in the second preferred embodiment.

[0070] FIG. 14 is a diagram explaining the operations of a synchronization detector and an inserted bit removing unit of FIG. 9 in the second preferred embodiment.

[0071] FIG. 15 is a diagram illustrating an example of a code string, in which a synchronization protection is carried out using a frame length information in the first and second preferred embodiments.

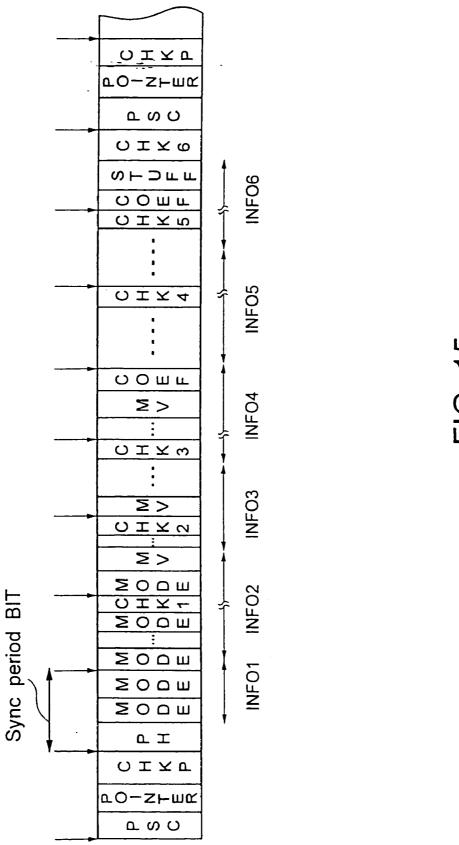

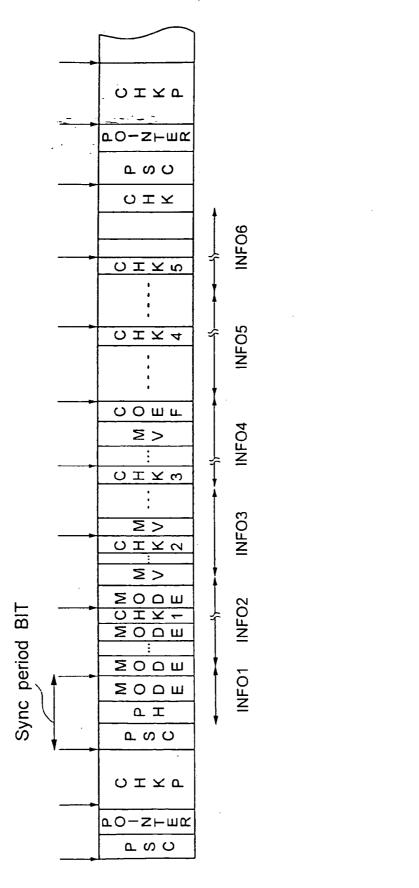

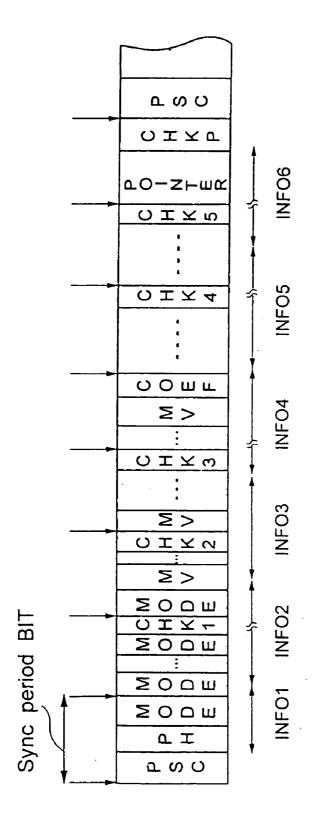

**[0072] FIG. 16** is diagram illustrating another example of a code string, in which a synchronization protection is carried out using a frame length information in the first and second preferred embodiments.

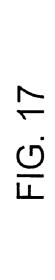

[0073] FIG. 17 is diagram illustrating further example of a code string, in which a synchronization protection is carried out using a frame length information in the first and second preferred embodiments.

[0074] FIG. 18 is a block diagram of the third and fourth preferred embodiments of a dynamic image coding system according to the present invention.

[0075] FIG. 19 is a block diagram of an output coding unit of the third preferred embodiment of a dynamic image coding system according to the present invention.

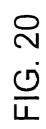

[0076] FIG. 20 is a diagram illustrating an example of an output code string of the third preferred embodiment of a dynamic image coding system according to the present invention.

[0077] FIG. 21 is a block diagram of the third and fourth preferred embodiments of a dynamic image decoding system according to the present invention.

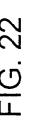

[0078] FIG. 22 is a block diagram of an input decoding unit of the third preferred embodiment of a dynamic image decoding system according to the present invention.

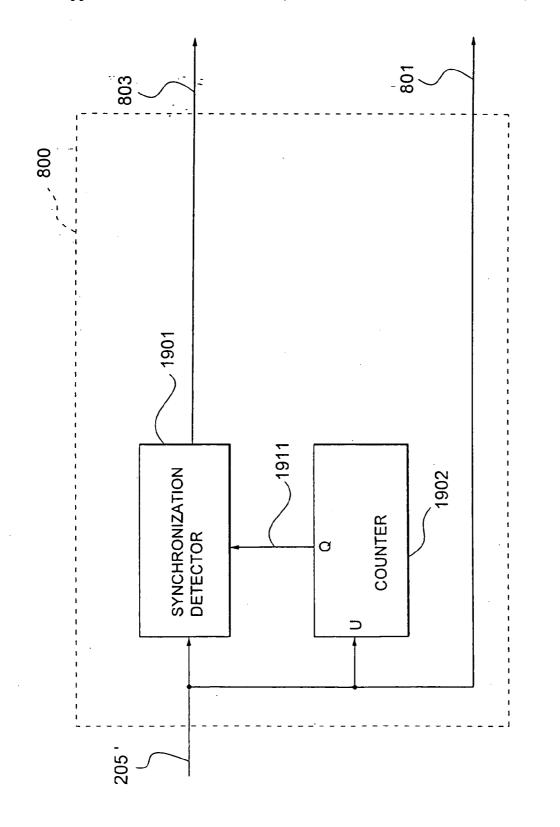

[0079] FIG. 23 is a block diagram of an output coding unit of the fourth preferred embodiment of a dynamic image coding system according to the present invention.

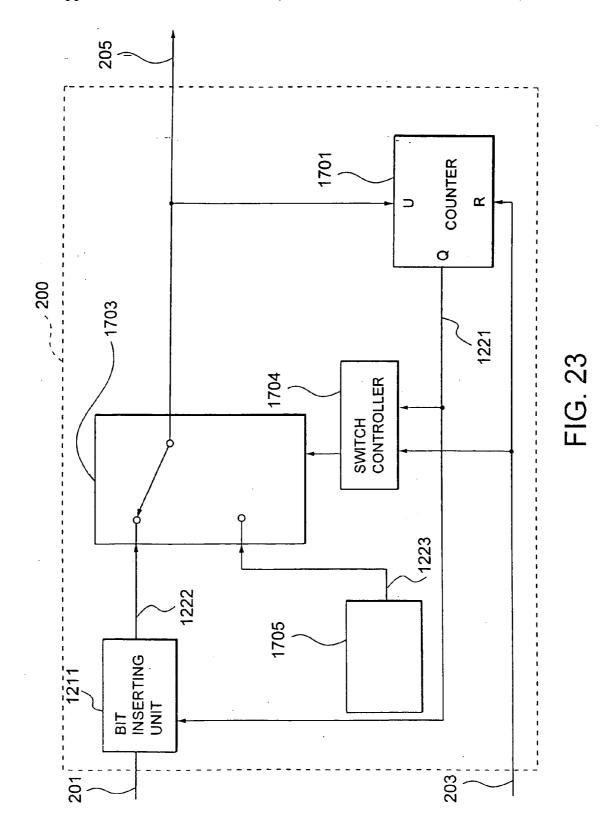

[0080] FIG. 24 is a block diagram of an input decoding unit of the fourth preferred embodiment of a dynamic image decoding system according to the present invention.

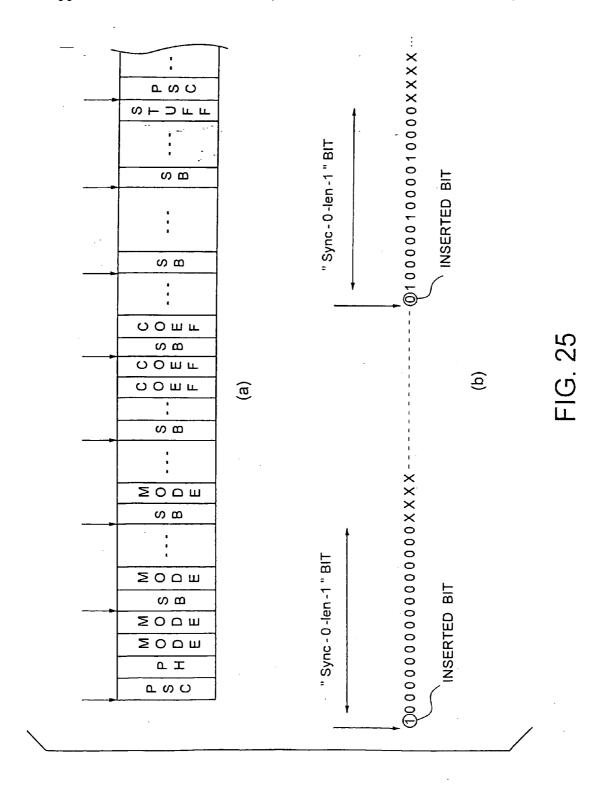

[0081] FIG. 25 is a block diagram of an example of an output code string of the fourth preferred embodiment of a dynamic image coding system according to the present invention.

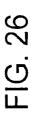

[0082] FIG. 26 is a diagram illustrating a multiplexing rule in a multiplexer of a dynamic image coding system.

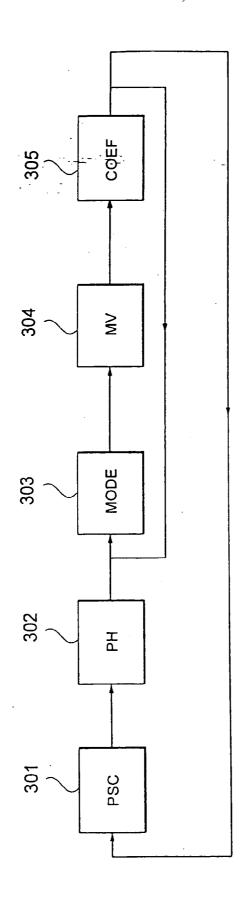

[0083] FIG. 27 is a block diagram of examples of output code strings of the fifth preferred embodiment of a dynamic image coding system according to the present invention.

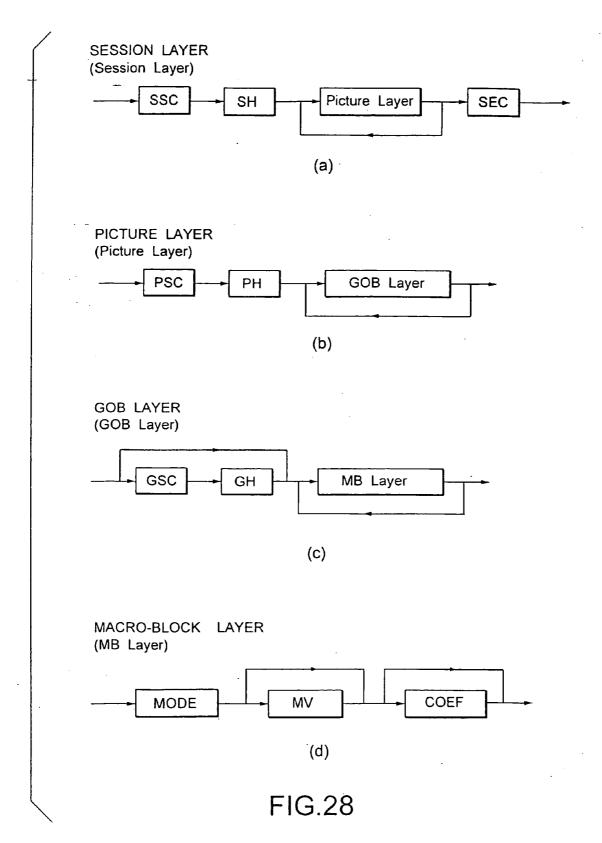

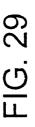

[0084] FIG. 28 is a diagram illustrating other examples of multiplexing rules in a multiplexer of a dynamic image coding system.

[0085] FIG. 29 is a diagram of an output code string, in which synchronization codes are processed when the multiplexing shown in FIG. 28 is carried out.

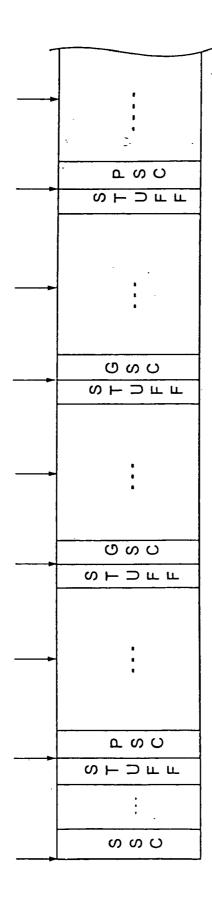

[0086] FIG. 30 is a code table for explaining examples of stuffing bits used for the present invention.

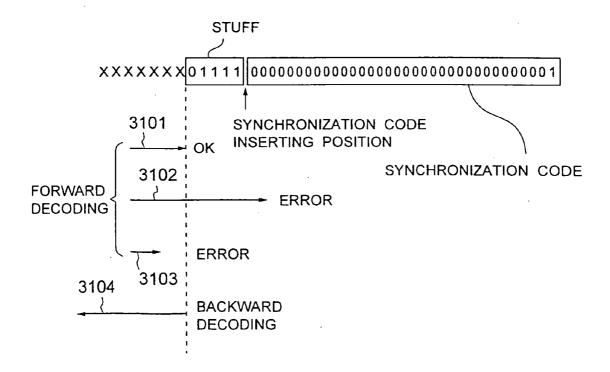

[0087] FIG. 31 is a diagram explaining a process in a decoding system when the stuffing bits of FIG. 30 are used.

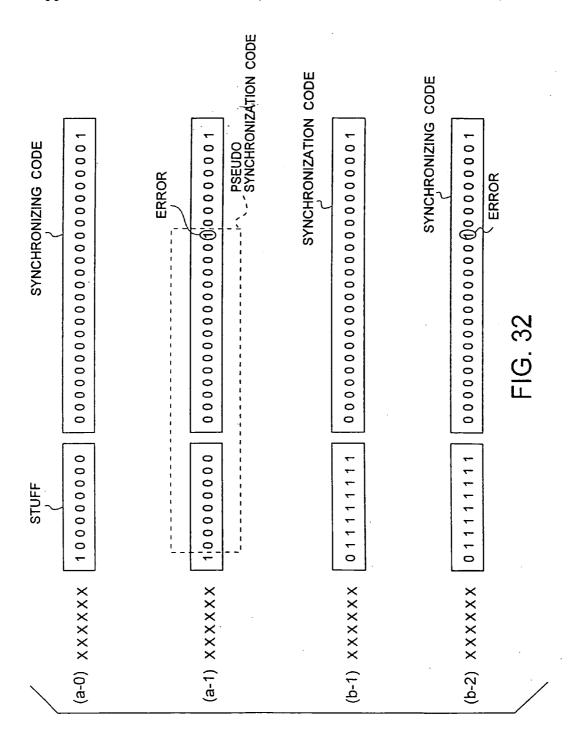

[0088] FIG. 32 is a diagram explaining the characteristics of the stuffing bits of FIG. 30.

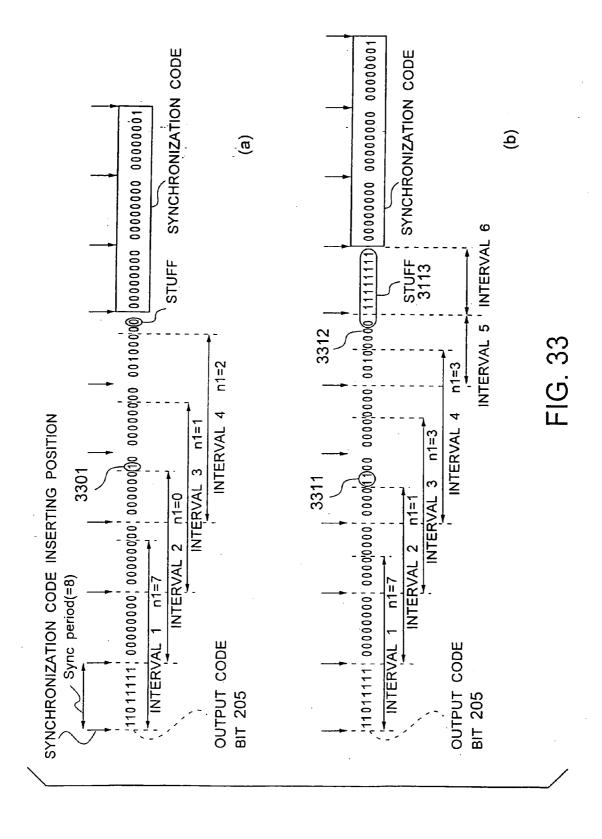

[0089] FIG. 33 is a diagram of examples of output code strings when a synchronization code inserting interval is shorter than a synchronization code.

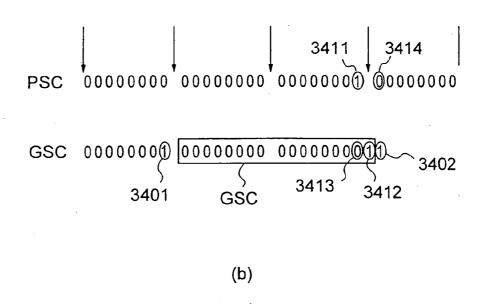

[0090] FIG. 34 is a diagram of examples of the use of synchronization codes of different lengths.

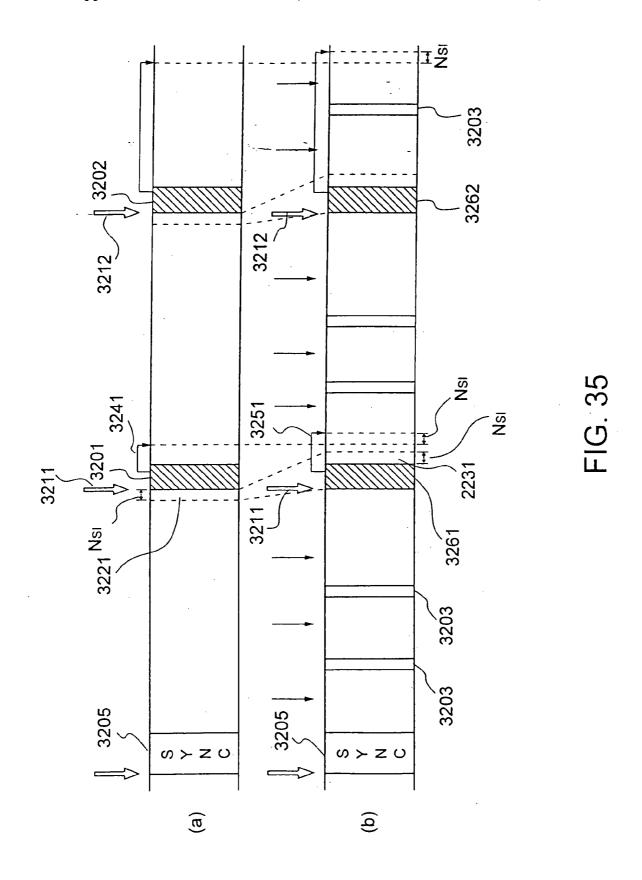

[0091] FIG. 35 is a diagram of examples of output code strings of the sixth preferred embodiment of a dynamic image coding system according to the present invention.

# BEST MODE FOR CARRYING OUT THE INVENTION

[0092] Referring now to the accompanying drawings, the preferred embodiments of the present invention will be described below.

# First Preferred Embodiment

[0093] FIG. 1 is a block diagram of the first preferred embodiment of a dynamic image coding system, according to the present invention, wherein a coding system having an error correcting/detecting code switching function of the present invention is combined with a high-efficiency compression coding system which uses a motion-compensated adaptive prediction and a discrete cosine transform coding serving as a kind of an orthogonal transform coding. A coding system comprising the combination of a motion-compensated adaptive prediction and a discrete cosine coding is detailed in, e.g., Literature 1 "International Standard of Multimedia Coding" by Hiroshi Yasuda, Maruzen (June 1991). Therefore, only the operation of the coding system will be schematically described. In addition, it is assumed

that information bits are separated from detection bits in an error correcting/detecting code similar to a BCH code.

[0094] In FIG. 1, with respect to an input dynamic image signal 131 serving as an object to be coded, which is inputted for each frame, a motion-compensated adaptive prediction is first carried out for each small region, such as a macro block. That is, in a motion-compensated adaptive predictor 101, a motion vector between an input dynamic image signal 131 and an image signal, which is stored in a frame memory 102 and which has been encoded and/or locally decoded, is detected, and a prediction signal 132 is produced by the motion-compensated prediction on the basis of the motion vector. In this motion-compensated predictor 101, a prediction mode suitable for coding is selected from the motioncompensated prediction coding and the intraframe coding (prediction signal=0), which directly encodes the input dynamic image signal 131, to produce the corresponding prediction signal 132.

[0095] The prediction signal 132 is inputted to a subtracter 103, wherein the prediction signal 132 is subtracted from the input dynamic image signal 131 to output a prediction residual signal 133. The prediction residual signal 133 is discrete-cosine-transformed (DCT) in a discrete cosine transformer 104 for each block having a predetermined size to produce a DCT coefficient. The DCT coefficient is quantized by means of a quantizer 105. The DCT coefficient data quantized by the quantizer 105 are divided into two parts, one of which is variable-length-encoded by means of a first variable length encoder 106, and the other of which is inverse-quantized by means of an inverse quantizer 107 to be inverse-discrete-cosine-transformed (inverse DCT) by means of an inverse discrete cosine transformer 108. The output of the inverse discrete cosine transformer 108 is added to the prediction signal 132 in an adder 109 to produce a locally decoded signal. This locally decoded signal is stored in the frame memory 102.

[0096] On the other hand, the information on the prediction mode and the motion vector, which have been determined by the motion-compensated adaptive predictor 101, is variable-length-encoded by means of a second variable length encoder 110. The variable length codes (compressed codes) outputted from the first and second variable length encoders 106 and 110 are multiplexed by means of a multiplexer 111 to be outputted as a multiplexed code string

[0097] The multiplexer 11 outputs the multiplexed code string 201, a FEC kind identifying signal 202 representative of the kind of an error correcting/detecting code corresponding thereto, and a synchronization code insertion request signal for requesting to insert a synchronization code. The code string 202, the FEC kind identifying signal 202 and the synchronization code insertion request signal 203 are inputted to an output coding unit 200 for switching and encoding the code string 202 to kinds of error correcting/detecting codes of different error correcting-/detecting capabilities, to produce a final output code string 205. In this preferred embodiment, the output coding unit 200 corresponds to a coding system according to the present invention.

[0098] FIG. 2 is a diagram illustrating a multiplexing flow in the multiplexer 111. The multiplexing is carried out for each coding frame. First, a synchronization code 301 is multiplexed. When the synchronization code 301 is multiplexed.

plexed, the synchronization code insertion request signal 203 is outputted from the multiplexer 111, and the coding system 200 has notice that the multiplexed code word is a synchronization code. Then, picture headers 203 representative of various coding modes of the coding frame are multiplexed to be the multiplexed code string 201. Then, a prediction mode information 303 representative of a prediction mode in a motion-compensated adaptive predictor MC in each region is multiplexed, and a motion vector information 304 and a DCT coefficient 305 of a predictive residual signal (hereinafter referred to as a "residual DCT coefficient") are multiplexed. When the picture header 302, the prediction mode information 303, the motion vector information 304 and the residual DCT coefficient 305 are multiplexed, the FEC kind identifying signals 202 representative of the kind of error correcting-/detecting codes corresponding thereto are outputted.

[0099] The error correcting/detecting codes of high correct-ing/detecting capabilities are used for the picture header 302, the prediction mode information 303 and the motion vector information 304, which greatly deteriorate the picture quality if an error is mixed. On the other hand, if an error is mixed into the residual DCT coefficient 305, it is possible to prevent the picture quality from greatly deteriorating by detecting the error and setting the residue to be zero. Therefore, the error correcting capacity is not required to be high, and only the error detection may be carried out.

[0100] FIG. 3 is a block diagram of an output coding unit of FIG. 1. The output coding unit 200 comprises a bit inserting unit 211, an error correction/detection switching encoder 212 and a code string assembling unit 213. FIG. 4 shows an example of an output code string 205 produced by the output coding unit 200. In FIG. 4, PSC denotes a synchronization signal, PH denotes a picture header, MODE denotes a prediction mode information, MV denotes a motion vector, CHK denotes a check bit of an error correcting-/detecting code, DOEF is a residual DCT coefficient, and STUFF denotes a stuffing bit (an inserted bit). This output code string 205 has the following characteristics.

[0101] (1) The synchronization codes PSC are inserted into only synchronization code inserting positions indicated by arrows, which are arranged at regular intervals (every sync\_period bits). The length of the sync\_period is set to be greater than the length of the synchronization code PSC and the maximum length of the check bit CHK. The check bit CHK is shifted so as to be arranged immediately before the synchronization code inserting position.

[0102] (2) The error correcting/detecting code at the end part of a frame, i.e., a synchronization period between a synchronization code PSC and the next PSC, is a degenerate code for encoding only the finally remaining information bit, and the stuffing bits STUFF having the number of bits required to displace the check bit CHK (CHK6 in the example of FIG. 4) are inserted.

[0103] (3) The FEC kind identifying signal representative of the kind and number of the error correcting/detecting codes does not exist in the output code string 205 of FIG. 4

[0104] In this output code string 205, since the check bit CHK is displaced as described in (1), no check bit CHK enters the synchronization code inserting positions indicated

by the arrows, so that there is no probability that a pseudo synchronization is produced by the check bit CHK. In addition, in a case where the error correction/detection coding of the end of the frame is carried out as described in (2), it has been required to insert many inserted bits (dummy bits) in the prior art. However, in this preferred embodiment, since the end of the frame has the degenerate code, the number of inserted bits may be small. Moreover, as described in (3), since the header information representative of the kind and number of the error correcting/detecting codes are contained in the output code string 205, the amount of codes is not increased therefor.

[0105] Comparing the multiplexed code string 201 of FIG. 2 outputted from the multiplexer 111 with the output code string 205 of FIG. 4, the construction and operation of the output coding unit 200 of FIG. 3 for producing such an output code string 205 will be described in detail below.

[0106] When the synchronization code 301 is multiplexed in the multiplexer 111, the synchronization code insertion request signal 203 is outputted as described above. For example, as shown in FIG. 5, the synchronization code 301 comprises "0"s of sync\_0\_len bits, a "1" of one bit, and a "xxxxx" of sync\_nb\_len bits representative of the kind of the synchronization code 301. The output coding unit 200 outputs a synchronization code (PSC) serving as an output code string 205 from the code string assembling unit 213 when receiving the synchronization code 301 and the synchronization code insertion request signal 203 from the multiplexer 111.

[0107] As shown in FIG. 4, since the synchronization code 301 can be inserted only at the synchronization code inserting positions arranged at intervals of sync\_period bits, when the end of the output code string 205 produced is not arranged at the synchronization code inserting position, a stuffing bit STUFF is inserted so that the synchronization code 301 is arranged at the synchronization code inserting position as described later.

[0108] After the synchronization code 301 is outputted to the output code string 205, the picture header 302, the prediction mode information 303, the motion vector information 304 and the residual DCT coefficient 305 are encoded as follows. The bit insertion into the multiplexed code string 201 outputted from the multiplexer 111 is carried out to prevent a pseudo synchronization from occurring in the bit inserting unit 211. That is, if the same bit pattern as the code word of the synchronization code 301 exists in the output code string 201, the bit insertion is carried out, if necessary, in order to prevent the synchronization code 301 from being not able to be uniformly decoded. For example, in a case where the synchronization code 301 is a code word having continuous "0"s of sync\_0 len bits as shown in FIG. 5, if a "1" is inserted so that "0"s of the sync\_0 len bits or more do not continue in code strings other than the synchronization code 301, it is possible to prevent a pseudo synchronization from being produced.

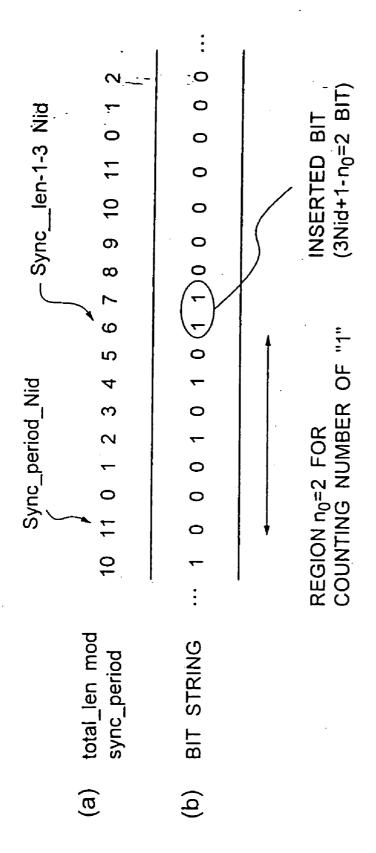

[0109] As described above, since the synchronization codes 301 are inserted only at the synchronization code inserting positions, the bit inserting operations for preventing the pseudo synchronization from occurring may be carried out only at the synchronization code inserting positions. Therefore, a counted value 221 representative of the total number of bits of the output code strings 205 produced

is outputted from the code string assembling unit 213, and it is determined by the bit inserting unit 211 on the basis of the counted value 221 whether the bit insertion is required. Assuming that the counted value 221, i.e., the total number of bits of the output code strings 205 produced, is total\_len, the number of "1"s in the multiplexed code string 201 is counted in an interval wherein 0<total\_len mod sync\_period≤sync\_0\_len. If no "1" exists in this interval, a "1" of one bit is inserted. A mod B denotes a remainder when A is divided by B.

[0110] In addition, in order to decrease the probability of the error detection of the synchronization code 301, the bit insertion may be carried out as follows.

[0111] In order to detect the synchronization code 301 even if an error of n bits is mixed into the synchronization code 301, it is required to determine that a code word having a hamming distance of n or less from a true synchronization code in an input decoding unit of a dynamic image decoding system as described later is a synchronization code. However, if such a determination is carried out while the code strings other than the synchronization code 301 are as they are, bit patterns having a hamming distance of n or less from the synchronization code may exist even in the code strings other than the synchronization code 301. Therefore, if this is arranged at the synchronization code inserting position, it may be erroneously determined to be the synchronization code 301.

[0112] Therefore, the bit insertion into the multiplexed code string 201 is carried out by means of the bit inserting unit 211, so that the code strings other than the synchronization codes arranged at the synchronization code inserting positions in the multiplexed code string 201 are transformed so as to have a humming distance of 2\*n+1 or more from the synchronization code 301. Specifically, the number of "1"s (assumed to be n0) is counted in an interval wherein 0<total\_len mod sync\_period ≤sync\_0\_len-(2\*N+1). If n0 is equal to or less than 2\*n+1, "1"s of 2\*n+1-n0 bits are inserted into the multiplexed code string 201.

[0113] Thus, a code string 222, in which the bit insertion is carried out by means of the bit inserting unit 211, together with the FEC kind identifying signal 202 representative of the kind of an error correcting/detecting code, is inputted to the error correcting/detecting code switching encoding part 212

[0114] FIG. 6 is a block diagram of an error correcting-/detecting code switching encoding part 212. A latch circuit 603 is a circuit for latching a FEC kind identifying signal 202. When the output of a synchronization code from the multiplexer 111 to the multiplexed code string 201 is completed to stop the output of the synchronization code insertion request signal 203, the latch circuit 603 latches the FEC kind identifying signal 202 to supply a latched signal 623 to an error correction/detection encoder 604.

[0115] An error correction/detection encoder 604 carries out the error correction/detection coding of a code string 222, which is outputted from a bit inserting unit 211, on the basis of the latched signal 623 to output an information bit 631 and a check bit 632. In addition, when the error correction/detection coding of one block is completed, the error correction/detection encoder 604 outputs a latch indicating signal 625, which indicates the latch of the next FEC

kind identifying signal 202, to the latch circuit 603. The latch circuit 603 latches in accordance with the latch indicating signal 625 to supply the latched signal 623 to the error correction/detection encoding 604.

[0116] The aforementioned operation is repeated in the output coding unit 200, so that the error correction/detection coding of the bit-inserted code string 222 outputted from the bit inserting unit 211 is carried out while switching the error correcting/detecting code in the error correct-ion/detection switching encoder 212 on the basis of the FEC kind identifying signal 202 outputted from the multiplexer 111. Since the FEC kind identifying signal 202 is latched by the latch circuit 603 only at the time that the coding of the error correcting/detecting code of one block is completed, the same error correcting/detecting codes are applied before this switching point. For example, in a case where the picture header 302 uses an error correcting/detecting code FEC1 and the prediction mode information 303 uses an error correcting/detecting code FEC2, if the number of bits of the picture header 302 is smaller than the number of information bits of one block of the FEC1, the FEC1 is used as the error correcting/detect-ing code of the subsequent prediction mode information 303 until the number of bits of the picture header 302 reaches the number of information bits of the

[0117] FIG. 7 is a block diagram of a code string assembling unit 213 of FIG. 3. The code string assembling unit 213 comprises a counter 701 for counting the number of bits of the output code string 205, a buffer 702 for temporarily storing the check bit 632 and the number of bits thereof, a switch 703 for switching the output code string 205, and a switch controller 704 for controlling the switch 703.

[0118] The counter 701 is reset to be a value of a synchronization code length sync len when the synchronization code insertion request signal 203 is inputted, and counts up sequentially from the next bit of the synchronization code until the next synchronization code is inputted. The switch 703 is operated so that the information bit 631 is outputted before the initial check bit 632 is inputted after the synchronization code is inputted. When the check bit 632 is inputted, it is stored in the buffer 702 and the number of bits thereof (the number of check bits) 711 is outputted from the buffer 702 to the switch-controller 704.

[0119] The switch controller 704 controls the switch 703 on the basis of the number 711 of check bits and the counted value 221 of the counter 701 so that the check bit is displaced in order to prevent the check bit 632 from being outputted to the synchronization code inserting position as described above. For example, assuming the counted value 221 is bit\_count and the number 711 of check bits is check\_len, the information bit 631 is outputted when bit\_count mod sync\_period<sync\_period-check\_len, and a check bit 713 stored in the buffer 702 is outputted when sync\_period<-check\_len ≦total\_bits mod sync\_period<-sync\_period-check\_then sync\_period sync\_period. Thereafter, the aforementioned process is repeated while the information bit 631 and the check bit 632 are inputted.

[0120] As described above, since the output coding unit 200 uses a degenerate code as an error correcting/detecting code at the end portion of one frame and performs the bit insertion to displace the check bit, it performs operation different from usual operations of portions other than the end

portion. That is, when the output of the multiplexed code string 201 of one frame is completed, the multiplexer 111 outputs a synchronization code insertion request signal 203 for the next frame. In response thereto, the error correcting/detecting code 604 in the error correction-/detection switching encoding part 212 of FIG. 6 performs the error correction/detection coding using a degenerate code, assuming that a shortage of the information bits 631 of the error correcting/detecting code is a predetermined bit pattern outputted from an inserted bit generator 705. This bit pattern may be a bit pattern wherein all bits are "1"s or "0"s, or may be a specific repeated pattern such as "0101 . . . ". This compensated inserted bits are not outputted to the information bit 631.

[0121] In the code string assembling unit 213 of FIG. 7, after the information bit 613 is outputted to the end, the switch 713 is switched from the bit generator 705 to the input, and the inserted bits are inserted so that the check bit 713 stored in the buffer 702 is arranged immediately before the next synchronization code. Assuming that the counted value 221 of the counter 701 is total\_len when the last information bit 631 of one frame is outputted and that the number of the finally outputted check bits 632 is last check len, the number of inserted bits stuffing len is stuffing\_len=sync\_period-last\_check\_len-(total\_len mod sync period). Furthermore, in a case where no degenerate code is used, it is required to insert (into len-last into len) bits, which is a shortage of the last information bit last into len from the usual information bit into len, and to insert a shortage of bits for displacing the check bit. Therefore, it is required to insert more inserted bits than those in the use of the degenerate code, by into len-last into len+(intolen-last into len) mod sync period.

[0122] Thus, after the code string assembling unit 213 outputs the information bits 631 and the inserted bits to the output code string 205 via the switch 703, and it finally outputs the check bit 713 to the output code string 205.

[0123] The first preferred embodiment of a dynamic image decoding system, according to the present invention, will be described below.

[0124] FIG. 8 is a block diagram of a dynamic image decoding system corresponding to the dynamic image coding system of FIG. 1. The output code string 205 outputted from the dynamic image decoding system of FIG. 1 passes through a transmission/storage system to be inputted to an input decoding unit 800 as an input code string 205. In this preferred embodiment, the input decoding unit 800 corresponds to a decoding system of the present invention.

[0125] The input decoding unit 800 switches error correcting/detecting codes on the basis of a FEC kind identifying signal 802 representative of the kind of an error correcting/detecting code outputted from a downstream demultiplexer 811, to output a code string 801, which has been error correction/detection encoded, a synchronization code detection signal 803 and an error detection signal 804. The demultiplexer 811 receives the code string 801, the synchronization code detection signal 803 and the error detection signal 804 to separately output a prediction residual signal 841 and a motion-compensated adaptive prediction information code 842.

[0126] The prediction residual signal 841 and the motion-compensated adaptive prediction information code 842 are

inputted to first and second variable length decoders 806 and 810, respectively. For a residual DCT coefficient 831 decoded by the first variable length decoder 806, a series of processes are carried out, i.e., the inverse quantization is carried out by means of an inverse quantizer 807 and the inverse discrete cosine transform is carried out by means of an inverse DCT unit 808. Then, the processed residual DCT coefficient is added to a motion-compensated adaptive prediction signal 832, which is an output of the motioncompensated adaptive predictor 801, in an adder 809 to be outputted as a reconstructed image signal 850. The reconstructed image signal 850 is outputted to the outside of the system and recorded in a frame memory 820. The motioncompensated adaptive prediction information decoded by the second variable length decoder 810 is inputted to the motion-compensated adaptive predictor 801 to produce the motion-compensated adaptive prediction signal 832.

[0127] The aforementioned processes are processes for producing a dynamic image so as to correspond to the dynamic image coding system of FIG. 1. The processes of the inverse quantizer 807, the inverse DCT unit 808, the adder 809 and the frame memory 820 are basically the same as those the inverse quantizer 107, the inverse DCT unit 108, the adder 109 and the frame memory 102 although the realizing means may be different. In addition, the processes in the first and second variable length decoders 806 and 810, the demultiplexer 811 and the input decoding unit 800 are inverse processes to those in the variable length encoders 106 and 110, the multiplexer 111 and the output coding unit 200, except for the case that an error is mixed into the code string.

[0128] FIG. 9 is a block diagram of the input decoding unit 800. The input decoding unit 800 comprises a synchroni-zation detector 901 for detecting a synchronization code in the input code string 205, a counter 902 for counting the number of bits of the input code string 205, a code string resolver 903 for resolving a code string into information bits 912 and check bits 913, an error correction/detection decoder 904, and an inserted bit remover 905.

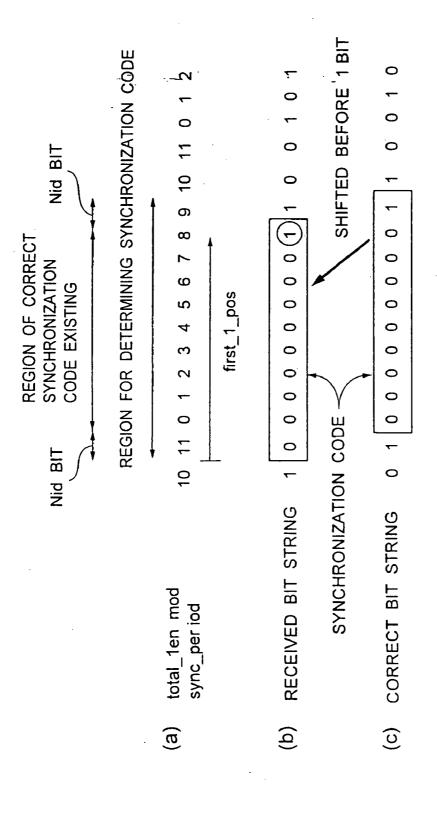

[0129] The synchronization detector 901 detects synchronization codes only at the synchronization code inserting positions on the basis of the counted value 911 of the counter 902. For example, assuming that the interval between the adjacent synchronization code inserting positions is sync\_period, the counted value 911 is bit\_count, and the length of the synchronization code is sync\_len, the synchronization detection is carried out only when 0<br/>bit\_count % sync\_period≤sync\_len.

[0130] Furthermore, the synchronization code may be detected in view of errors in the synchronization code.

[0131] In the bit inserting unit 211 of the output coding unit of FIG. 3, if the code string is transformed by inserting bits so as to have a humming distance of 2\*n+1 or more from the synchronization code in view of errors of n bits or less, even if it is determined that the code string having a humming distance of n or less from a true synchronization signal is a synchronization code, error synchronization detection does not occur when the error of n bits or less is mixed.

[0132] FIG. 10 is a block diagram of the code string resolver 903. The input code string 205 is switched into

information bits 1021 and check bits 913 by means of a first switch 1002 controlled by a controller 1001 which will be described later. When the information bits 1021 are outputted from the first switch 1002, an information bit length of the information bits 1021 are transmitted to a buffer 1004 via a second switch 1003 to be stored therein. A counter 1005 counts the number of output bits from the second switch 1003. A comparator 1006 compares a counted value 1023 of the counter 1005 with an information bit length 1024 outputted from an error correct-ing/detecting code information output unit 1007. When both are the same, the counter 1005 is reset, the FEC kind identifying signal 802 representative of the kind of an error detecting/correcting code is latched by means of a latch circuit 1008, and the buffer 1004 outputs the information bit 904. The output 914 of the latch circuit 1008 is inputted to the error correcting/detecting code information output circuit 1007, and outputted to the error correction/detection decoder 904 shown in FIG. 9.

[0133] As described above, the check bits of the error correcting/detecting code are displaced to be arranged between the information bits of the error correcting/detecting code after the code string 205. The controller 1001 controls so that the displaced check bits are separated from the information bits. When the input of the information bits of the error correcting/detecting code of one block is completed, the counted value 1023 corresponds to the information bit length 1024 in the comparator 1006. In response thereto, the controller 1001 receives a check bit length 1025 from the error correction/detection information output unit 1007, and calculates the positions of the check bits arranged between the next information bits. When it is determined by the comparator 1006 that both correspond to each other, assuming that the counted value 911 of the number of input bits of the code string 205' is bit\_count and the check bit length is check len, the check bit starting position checkstart is check start=(bit count/sync period+1)\*sync per iod-check\_len, and the check bit end position check\_end is check\_end=(bit\_count/sync\_period\_+1)\*sync\_period. The controller 1001 controls the switch 1002 so that the check bits 913 are outputted from the check start to the check end of the counted value 911.

[0134] Since the end of one frame is a degenerate code and the error correction/detection encoding thereof is carried out, it is specially processed. When reaching the end of one frame, a signal 803 representative of the detection of the next frame is outputted. In response to this signal 803, the controller 1001 calculates the positions of the check bits of the last error correcting/detecting code of the frame and the number of insufficient bits of the information bits. It is assumed that the counted value 911 of the number of bits of the code string 205' inputted when starting to input the last error correcting/detecting code of one frame is pre\_lastcount, the counted value 911 when the input of the code string 205' of one frame is completed is total count, the counted value 911 during the process is bit count, the check bit length of the last error correcting/detecting code of one frame is last\_check\_len, and the check bit length of the error correcting/detecting code immediately before of the last error correcting/detecting code is pre last check len. First, the excess and deficiency of information bits due to the error correcting code being a degenerate code and due to the insertion of bits is calculated. Among the information bits of the last error correcting/detecting code of one frame, the number of bits contained in the output code string 205, last\_info\_len, is last\_info\_len=total\_co unt-last\_check\_len-pre\_last\_count-pre\_last\_check\_len. When last\_info\_len is shorter than the information length of the error correcting code info\_len, it is determined that the error correcting code is a degenerate code. In addition, when the counted value 1023 is in the range of from last\_into\_len to info\_len, the switch 1021 is switched to a bit pattern outputted from an inserted bit generator 1015, to make up for the deficiency of information bits due to degeneracy. The output bit pattern from the inserted bit generator 1015 generates the same bit pattern as that of the inserted bit generator 705 of FIG. 7 of the encoder.

[0135] On the other hand, when last\_info\_len is longer than info\_len, it is determined that the error correcting code is the inserted bit part, so that the information bits 912 are not outputted for the portion wherein the counted value 1023 is equal to or greater than info\_len. With respect to the check bits, the switch 1002 is controlled so as to output, as check bits, the output code string 205 when total\_count\_check\_len<br/>

string\_count\_string\_count.

[0136] The error correction/detection decoder 904 receives the information bits 912 and the check bits 913, which are outputted from the code string resolver 903, and decode the error correcting/detecting code on the basis of the FEC kind identifying signal 914 representative of the kind of the error correcting/detecting code latched by the latch circuit 1008 of FIG. 10, to output an error corrected code string 915 and an error detection signal 804.

[0137] The error corrected code string 915 is inputted to the inputted bit remover 905. The inserted bit remover 905 removes the inserted bits for preventing the pseudo synchronization signal inserted by the bit inserting unit 211 of the output coding unit 200. As described above, since the bit insertion is carried out only at the synchronization inserting position, the synchronization inserting position is determined on the basis of the counted value 911 of the counter 902.

[0138] For example, when the synchronization code word is that shown in FIG. 5 and when the bit inserting unit 211 inserts bits into the portion "0000..." of the first sync\_len bits of the synchronization code so that the humming distance from the synchronization code is greater than 2\*n+1, the number of "1"s (=n0) of "sync\_0\_len-(2\*n+1)" bits from the synchronization code inserting position is counted. When the n0 is equal to or less than 2\*n+1, 2\*n+1-n0 bits are removed. However, since it is determined that the inserted bit is "1", when the bit determined as the inserted bit by the inserted bit removing unit 905 is "0", it is considered that an error is mixed in the synchronization code inserting interval. In this case, the error detection signal 804 is outputted.

[0139] Thus, the code string 801 decoded by the input decoding unit 800 is inverse multiplexed by means of the demulti-plexer 811. This is operation for separating and output-ting the multiplexed code word as shown in FIG. 2. This inverse multiplexer 811 works with the first and second variable length decoders 806 and 810.

[0140] First, when the synchronization code detection signal 803 is inputted from the output decoding system 800, the demultiplexer 811 returns to the initial state of the frame process. Then, the kind of the error correcting/detecting

code to the picture header is outputted as the FEC kind identifying signal 802 representative of the kind of the error correcting/detecting code, and the code string 801 is inputted to decode the picture header 302, so that it is determined whether there is no error in the picture header. When there is no error, the kind of the error correcting-/detecting code to the prediction mode information 303 is outputted as the FEC kind identifying signal 802, and the code string 801 is inputted to demultiplex the prediction mode information to output it to the second variable length decoder 810.