(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6543053号

(P6543053)

(45) 発行日 令和1年7月10日(2019.7.10)

(24) 登録日 令和1年6月21日(2019.6.21)

(51) Int.Cl.

F 1

|              |           |            |       |      |

|--------------|-----------|------------|-------|------|

| HO1L 21/336  | (2006.01) | HO1L 29/78 | 29/78 | 627B |

| HO1L 29/786  | (2006.01) | HO1L 29/78 | 29/78 | 627F |

| HO1L 21/8242 | (2006.01) | HO1L 29/78 | 29/78 | 626C |

| HO1L 27/108  | (2006.01) | HO1L 29/78 | 29/78 | 619A |

|              |           | HO1L       | 29/78 | 618A |

請求項の数 11 (全 64 頁) 最終頁に続く

|              |                               |

|--------------|-------------------------------|

| (21) 出願番号    | 特願2015-50523 (P2015-50523)    |

| (22) 出願日     | 平成27年3月13日 (2015.3.13)        |

| (65) 公開番号    | 特開2015-188084 (P2015-188084A) |

| (43) 公開日     | 平成27年10月29日 (2015.10.29)      |

| 審査請求日        | 平成30年3月8日 (2018.3.8)          |

| (31) 優先権主張番号 | 特願2014-51720 (P2014-51720)    |

| (32) 優先日     | 平成26年3月14日 (2014.3.14)        |

| (33) 優先権主張国  | 日本国 (JP)                      |

|           |                                                |

|-----------|------------------------------------------------|

| (73) 特許権者 | 000153878<br>株式会社半導体エネルギー研究所<br>神奈川県厚木市長谷398番地 |

| (72) 発明者  | 山崎 舜平<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (72) 発明者  | 坂倉 真之<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (72) 発明者  | 浜田 崇<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内    |

| 審査官       | 脇水 佳弘                                          |

最終頁に続く

(54) 【発明の名称】半導体装置の作製方法

## (57) 【特許請求の範囲】

## 【請求項 1】

絶縁表面上に第1の導電体を形成する第1のステップと、

前記第1の導電体上に、CVD法により第1の絶縁体を成膜する第2のステップと、

前記第1の絶縁体上に、CVD法により第1の半導体を成膜する第3のステップと、

前記第1の半導体上に、CVD法により第2の半導体を成膜する第4のステップと、

前記第2の半導体を加工して、第3の半導体を形成する第5のステップと、

前記第5のステップの後、前記第1の半導体を加工して、第4の半導体を形成する第6のステップと、

前記第6のステップの後、前記第3の半導体上に、CVD法により第2の導電体を成膜する第7のステップと、

前記第2の導電体を加工して、第3の導電体および第4の導電体を形成するとともに、

前記第3の半導体を露出させる第8のステップと、

前記第3の半導体上、前記第3の導電体上および前記第4の導電体上に、CVD法により第5の半導体を成膜する第9のステップと、

前記第5の半導体上に、CVD法により第2の絶縁体を成膜する第10のステップと、

前記第2の絶縁体上に、CVD法により第5の導電体を成膜する第11のステップと、

前記第5の導電体を加工して、第6の導電体を形成する第12のステップと、

前記第12のステップの後、前記第2の絶縁体を加工して、第3の絶縁体を形成する第13のステップと、

10

20

前記第13のステップの後、前記第5の半導体を加工して、第6の半導体を形成する第14のステップと、を有し、

前記第2のステップと、前記第3のステップと、の間で大気に暴露せず、

前記第9のステップと、前記第10のステップと、の間で大気に暴露せず、

前記第3の半導体、前記第4の半導体、及び前記第6の半導体は、In、Ga、及びZnを含み、

前記第3の半導体は、前記第4の半導体よりも膜厚が大きい領域を有し、

前記第3の半導体は、前記第6の半導体よりも膜厚が大きい領域を有することを特徴とする半導体装置の作製方法。

【請求項2】

10

請求項1において、

前記第3のステップと、前記第4のステップと、の間で大気に暴露しないことを特徴とする半導体装置の作製方法。

【請求項3】

請求項1または請求項2において、

前記第4のステップの後に、加熱処理を行うことを特徴とする半導体装置の作製方法。

【請求項4】

請求項1乃至請求項3のいずれか一において、

前記第14のステップの後に、水素をブロックする機能を有する第4の絶縁体をCVD法により成膜するステップを有することを特徴とする半導体装置の作製方法。

20

【請求項5】

請求項1乃至請求項4のいずれか一において、

前記第3のステップの後に、前記第1の半導体に酸素を添加するステップを有することを特徴とする半導体装置の作製方法。

【請求項6】

絶縁表面上に第1の導電体を形成する第1のステップと、

前記第1の導電体上に、CVD法により第1の絶縁体を成膜する第2のステップと、

前記第1の絶縁体上に、CVD法により第1の半導体を成膜する第3のステップと、

前記第1の半導体上に、CVD法により第2の半導体を成膜する第4のステップと、

前記第2の半導体上に、CVD法により第2の導電体を成膜する第5のステップと、

30

前記第2の導電体を加工して、第3の導電体を形成する第6のステップと、

前記第6のステップの後、前記第2の半導体を加工して、第3の半導体を形成する第7のステップと、

前記第7のステップの後、前記第1の半導体を加工して、第4の半導体を形成する第8のステップと、

前記第8のステップの後、前記第3の導電体を加工して、第4の導電体および第5の導電体を形成するとともに、前記第3の半導体を露出させる第9のステップと、

前記第3の半導体上、前記第4の導電体上および前記第5の導電体上に、CVD法により第5の半導体を成膜する第10のステップと、

前記第5の半導体上に、CVD法により第2の絶縁体を成膜する第11のステップと、

40

前記第2の絶縁体上に、CVD法により第6の導電体を成膜する第12のステップと、

前記第6の導電体を加工して、第7の導電体を形成する第13のステップと、

前記第13のステップの後、前記第2の絶縁体を加工して、第3の絶縁体を形成する第14のステップと、

前記第14のステップの後、前記第5の半導体を加工して、第6の半導体を形成する第15のステップと、を有し、

前記第2のステップと、前記第3のステップと、の間で大気に暴露せず、

前記第10のステップと、前記第11のステップと、の間で大気に暴露せず、

前記第3の半導体、前記第4の半導体、及び前記第6の半導体は、In、Ga、及びZnを含み、

50

前記第3の半導体は、前記第4の半導体よりも膜厚が大きい領域を有し、

前記第3の半導体は、前記第6の半導体よりも膜厚が大きい領域を有することを特徴とする半導体装置の作製方法。

【請求項7】

請求項6において、

前記第3のステップと、前記第4のステップと、の間で大気に暴露しないことを特徴とする半導体装置の作製方法。

【請求項8】

請求項6または請求項7において、

前記第4のステップと、前記第5のステップと、の間で大気に暴露しないことを特徴とする半導体装置の作製方法。 10

【請求項9】

請求項6乃至請求項8のいずれか一において、

前記第4のステップの後に、加熱処理を行うことを特徴とする半導体装置の作製方法。

【請求項10】

請求項6乃至請求項9のいずれか一において、

前記第15のステップの後に、水素をブロックする機能を有する第4の絶縁体をCVD法により成膜するステップを有することを特徴とする半導体装置の作製方法。

【請求項11】

請求項7乃至請求項10のいずれか一において、

前記第3のステップの後に、前記第1の半導体に酸素を添加するステップを有することを特徴とする半導体装置の作製方法。 20

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、物、方法、または、製造方法に関する。または、本発明は、プロセス、マシン、マニュファクチャ、または組成物（コンポジション・オブ・マター）に関する。特に、本発明は、例えば、半導体、半導体装置、表示装置、発光装置、照明装置、蓄電装置、記憶装置、プロセッサに関する。または、半導体、半導体装置、表示装置、液晶表示装置、発光装置、記憶装置の製造方法に関する。または、半導体装置、表示装置、液晶表示装置、発光装置、記憶装置の駆動方法に関する。 30

【0002】

なお、本明細書等において半導体装置とは、半導体特性を利用して機能しうる装置全般を指す。表示装置、発光装置、照明装置、電気光学装置、半導体回路および電子機器は、半導体装置を有する場合がある。

【背景技術】

【0003】

絶縁表面を有する基板上の半導体を用いて、トランジスタを構成する技術が注目されている。当該トランジスタは集積回路や表示装置のような半導体装置に広く応用されている。トランジスタに適用可能な半導体としてシリコンが知られている。 40

【0004】

トランジスタの半導体に用いられるシリコンは、用途によって非晶質シリコンと多結晶シリコンとが使い分けられている。例えば、大型の表示装置を構成するトランジスタに適用する場合、大面積基板への成膜技術が確立されている非晶質シリコンを用いると好適である。一方、駆動回路と画素回路とを同一基板上に形成するような高機能の表示装置を構成するトランジスタに適用する場合、高い電界効果移動度を有するトランジスタを作製可能な多結晶シリコンを用いると好適である。多結晶シリコンは、非晶質シリコンに対し高温での熱処理、またはレーザ光処理を行うことで形成する方法が知られる。

【0005】

近年は、酸化物半導体が注目されている。例えば、非晶質In-Ga-Zn酸化物を用い 50

たトランジスタが開示されている（特許文献1参照。）。酸化物半導体は、スパッタリング法などを用いて成膜できるため、大型の表示装置を構成するトランジスタの半導体に用いることができる。また、酸化物半導体を用いたトランジスタは、高い電界効果移動度を有するため、駆動回路と画素回路とを同一基板上に形成するような高機能の表示装置を実現できる。また、非晶質シリコンを用いたトランジスタの生産設備の一部を改良して利用することが可能であるため、設備投資を抑えられるメリットもある。

#### 【0006】

また、酸化物半導体を用いたトランジスタは、非導通状態において極めてリーク電流が小さいことが知られている。例えば、酸化物半導体を用いたトランジスタのリーク電流が低いという特性を応用した低消費電力のC P Uなどが開示されている（特許文献2参照。）。また、酸化物半導体からなる活性層で井戸型ポテンシャルを構成することにより、高い電界効果移動度を有するトランジスタが得られることが開示されている（特許文献3参照。）。

10

#### 【先行技術文献】

##### 【特許文献】

##### 【0007】

【特許文献1】特開2006-165528号公報

【特許文献2】特開2012-257187号公報

【特許文献3】特開2012-59860号公報

#### 【発明の概要】

20

#### 【発明が解決しようとする課題】

##### 【0008】

電気特性の良好なトランジスタを提供することを課題の一とする。または、電気特性の安定したトランジスタを提供することを課題の一とする。または、オフ時の電流の小さいトランジスタを提供することを課題の一とする。または、該トランジスタを有する半導体装置を提供することを課題の一とする。または、該半導体装置を有するモジュールを提供することを課題の一とする。または、該半導体装置、または該モジュールを有する電子機器を提供することを課題の一とする。または、新規な半導体装置を提供することを課題の一とする。または、新規なモジュールを提供することを課題の一とする。または、新規な電子機器を提供することを課題の一とする。

30

##### 【0009】

なお、これらの課題の記載は、他の課題の存在を妨げるものではない。なお、本発明の一態様は、これらの課題の全てを解決する必要はないものとする。なお、これら以外の課題は、明細書、図面、請求項などの記載から、自ずと明らかとなるものであり、明細書、図面、請求項などの記載から、これら以外の課題を抽出することが可能である。

#### 【課題を解決するための手段】

##### 【0010】

(1) 本発明の一態様は、基板上に、C V D法により第1の導電体を成膜する第1のステップと、第1のステップの後の、第1の導電体を加工して、第2の導電体を形成する第2のステップと、第2のステップの後の、第2の導電体上に、C V D法により第1の絶縁体を成膜する第3のステップと、第3のステップの後の、第1の絶縁体上に、C V D法により第1の半導体を成膜する第4のステップと、第4のステップの後の、第1の半導体上に、C V D法により第2の半導体を成膜する第5のステップと、第5のステップの後の、第2の半導体を加工して、第3の半導体を形成する第6のステップと、第6のステップの後の、第1の半導体を加工して、第4の半導体を形成する第7のステップと、第7のステップの後の、第3の半導体上に、C V D法により第3の導電体を成膜する第8のステップと、第8のステップの後の、第3の導電体を加工して、第4の導電体および第5の導電体を形成するとともに、第3の半導体を露出させる第9のステップと、第9のステップの後の、第3の半導体上、第4の導電体上および第5の導電体上に、C V D法により第5の半導体を成膜する第10のステップと、第10のステップの後の、第5の半導体上に、C V D

40

50

法により第2の絶縁体を成膜する第11のステップと、第11のステップの後の、第2の絶縁体上に、CVD法により第6の導電体を成膜する第12のステップと、第12のステップの後の、第6の導電体を加工して、第7の導電体を形成する第13のステップと、第13のステップの後の、第2の絶縁体を加工して、第3の絶縁体を形成する第14のステップと、第14のステップの後の、第5の半導体を加工して、第6の半導体を形成する第15のステップと、を有し、第3のステップと、第4のステップと、の間で大気に暴露せず、第10のステップと、第11のステップと、の間で大気に暴露しない半導体装置の作製方法である。

【0011】

(2) または、本発明の一態様は、(1)において、第4のステップと、第5のステップと、の間で大気に暴露しない半導体装置の作製方法である。 10

【0012】

(3) または、本発明の一態様は、(1)または(2)において、第5のステップの後に、加熱処理を行う半導体装置の作製方法である。

【0013】

(4) または、本発明の一態様は、(1)乃至(3)のいずれか一において、第1のステップの前に、CVD法により水素をブロックする機能を有する第4の絶縁体を成膜するステップを有する半導体装置の作製方法である。 20

【0014】

(5) または、本発明の一態様は、(1)乃至(4)のいずれか一において、第15のステップの後に、CVD法により水素をブロックする機能を有する第5の絶縁体を成膜するステップを有する半導体装置の作製方法である。 20

【0015】

(6) または、本発明の一態様は、(1)乃至(5)のいずれか一において、第4のステップの後に、第1の半導体に酸素を添加するステップを有する半導体装置の作製方法である。

【0016】

(7) または、本発明の一態様は、基板上に、CVD法により第1の導電体を成膜する第1のステップと、第1のステップの後の、第1の導電体を加工して、第2の導電体を形成する第2のステップと、第2のステップの後の、第2の導電体上に、CVD法により第1の絶縁体を成膜する第3のステップと、第3のステップの後の、第1の絶縁体上に、CVD法により第1の半導体を成膜する第4のステップと、第4のステップの後の、第1の半導体上に、CVD法により第2の半導体を成膜する第5のステップと、第5のステップの後の、第2の半導体上に、CVD法により第3の導電体を成膜する第6のステップと、第6のステップの後の、第3の導電体を加工して、第4の導電体を形成する第7のステップと、第7のステップの後の、第2の半導体を加工して、第3の半導体を形成する第8のステップと、第8のステップの後の、第1の半導体を加工して、第4の半導体を形成する第9のステップと、第9のステップの後の、第4の導電体を加工して、第5の導電体および第6の導電体を形成するとともに、第3の半導体を露出させる第10のステップと、第10のステップの後の、第3の半導体上、第5の導電体上および第6の導電体上に、CVD法により第5の半導体を成膜する第11のステップと、第11のステップの後の、第5の半導体上に、CVD法により第2の絶縁体を成膜する第12のステップと、第12のステップの後の、第2の絶縁体上に、CVD法により第7の導電体を成膜する第13のステップと、第13のステップの後の、第7の導電体を加工して、第8の導電体を形成する第14のステップと、第14のステップの後の、第2の絶縁体を加工して、第3の絶縁体を形成する第15のステップと、第15のステップの後の、第5の半導体を加工して、第6の半導体を形成する第16のステップと、を有し、第3のステップと、第4のステップと、の間で大気に暴露せず、第11のステップと、第12のステップと、の間で大気に暴露しない半導体装置の作製方法である。 40

【0017】

(8) または、本発明の一態様は、(7)において、第4のステップと、第5のステップと、の間で大気に暴露しない半導体装置の作製方法である。

【0018】

(9) または、本発明の一態様は、(7)または(8)において、第5のステップと、第6のステップと、の間で大気に暴露しない半導体装置の作製方法である。

【0019】

(10) または、本発明の一態様は、(7)乃至(9)のいずれか一において、第5のステップの後に、加熱処理を行う半導体装置の作製方法である。

【0020】

(11) または、本発明の一態様は、(7)乃至(10)のいずれか一において、第1のステップの前に、CVD法により水素をブロックする機能を有する第4の絶縁体を成膜するステップを有する半導体装置の作製方法である。 10

【0021】

(12) または、本発明の一態様は、(7)乃至(11)のいずれか一において、第16のステップの後に、CVD法により水素をブロックする機能を有する第5の絶縁体を成膜するステップを有する半導体装置の作製方法である。

【0022】

(13) または、本発明の一態様は、(7)乃至(12)のいずれか一において、第4のステップの後に、第1の半導体に酸素を添加するステップを有する半導体装置の作製方法である。 20

【発明の効果】

【0023】

電気特性の良好なトランジスタを提供することができる。または、電気特性の安定したトランジスタを提供することができる。または、オフ時の電流の小さいトランジスタを提供することができる。または、該トランジスタを有する半導体装置を提供することができる。または、該半導体装置を有するモジュールを提供することができる。または、該半導体装置、または該モジュールを有する電子機器を提供することができる。または、新規な半導体装置を提供することができる。または、新規なモジュールを提供することができる。または、新規な電子機器を提供することができる。

【0024】

なお、これらの効果の記載は、他の効果の存在を妨げるものではない。なお、本発明の一態様は、これらの効果の全てを有する必要はない。なお、これら以外の効果は、明細書、図面、請求項などの記載から、自ずと明らかとなるものであり、明細書、図面、請求項などの記載から、これら以外の効果を抽出することが可能である。 30

【図面の簡単な説明】

【0025】

【図1】本発明の一態様に係るトランジスタを示す上面図および断面図。

【図2】本発明の一態様に係るトランジスタの作製方法を示す断面図。

【図3】本発明の一態様に係るトランジスタの作製方法を示す断面図。

【図4】本発明の一態様に係るトランジスタの作製方法を示す断面図。 40

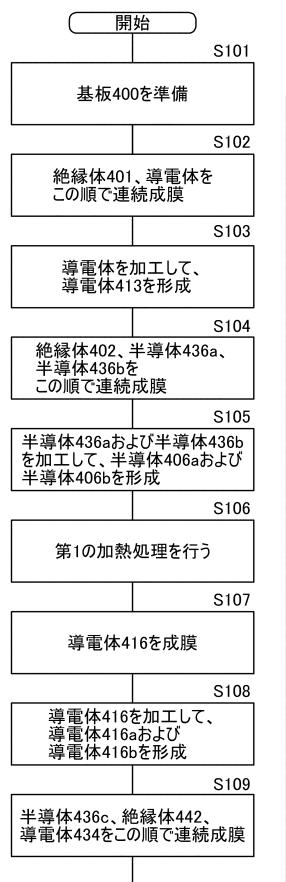

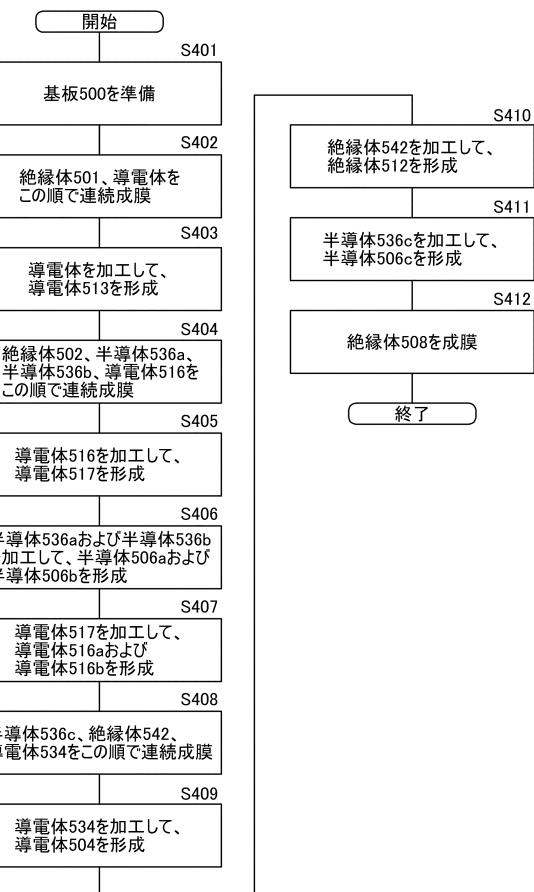

【図5】本発明の一態様に係るトランジスタの作製方法を示すフローチャート。

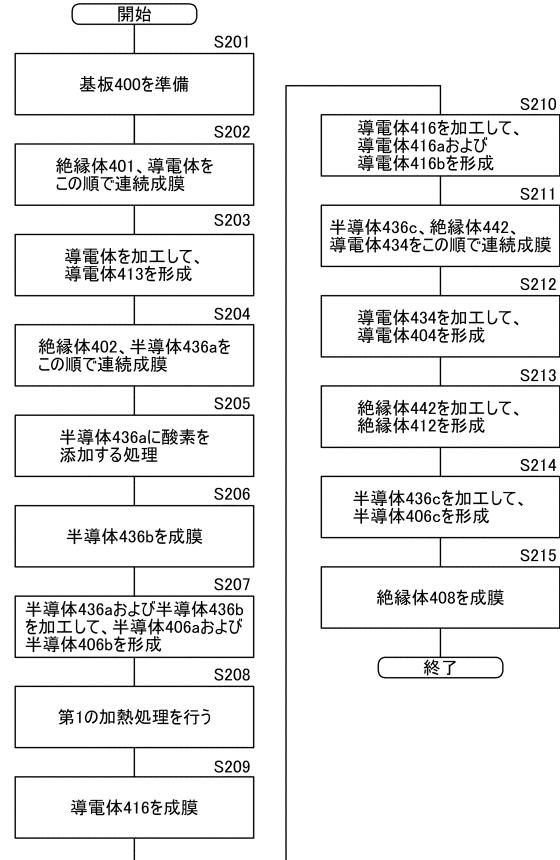

【図6】本発明の一態様に係るトランジスタの作製方法を示すフローチャート。

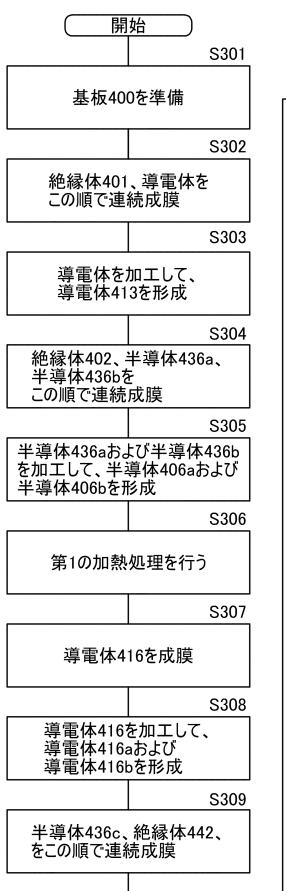

【図7】本発明の一態様に係るトランジスタの作製方法を示すフローチャート。

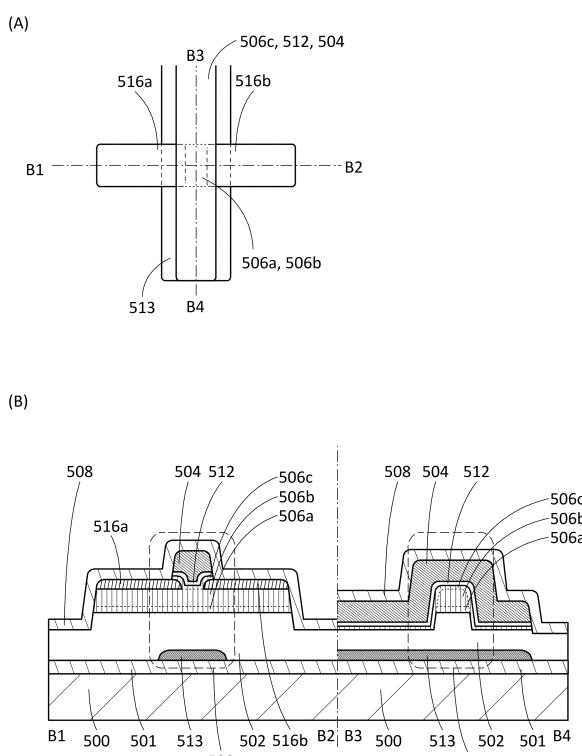

【図8】本発明の一態様に係るトランジスタを示す上面図および断面図。

【図9】本発明の一態様に係るトランジスタの作製方法を示す断面図。

【図10】本発明の一態様に係るトランジスタの作製方法を示す断面図。

【図11】本発明の一態様に係るトランジスタの作製方法を示す断面図。

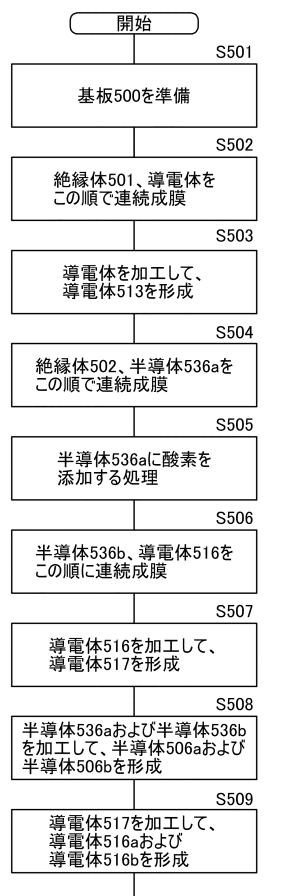

【図12】本発明の一態様に係るトランジスタの作製方法を示すフローチャート。

【図13】本発明の一態様に係るトランジスタの作製方法を示すフローチャート。

【図14】本発明の一態様に係るトランジスタの作製方法を示すフローチャート。 50

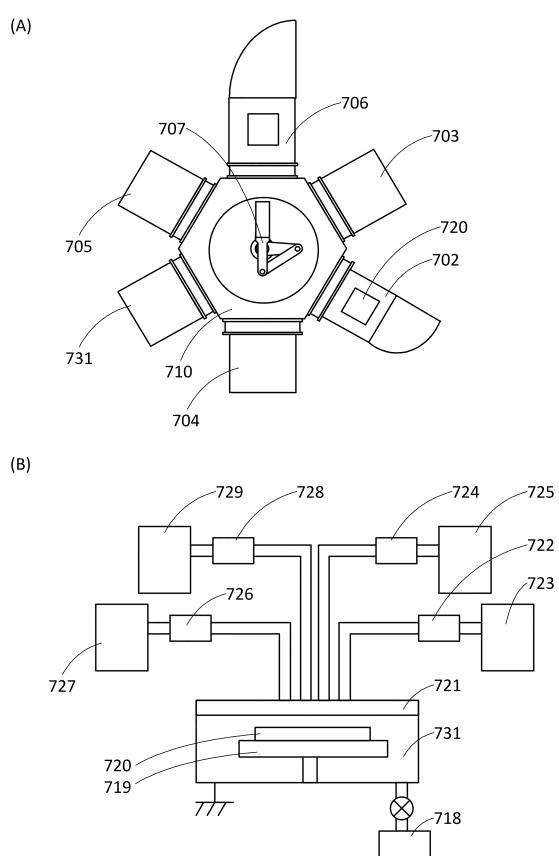

- 【図15】本発明の一態様に係る製造装置を示す図。

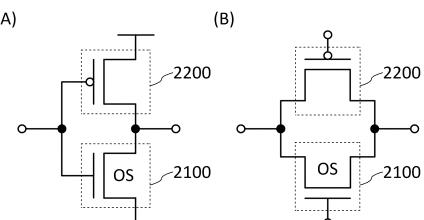

- 【図16】本発明の一態様に係る半導体装置の回路図。

- 【図17】本発明の一態様に係る記憶装置の回路図。

- 【図18】本発明の一態様に係るR F タグのブロック図。

- 【図19】本発明の一態様に係るR F タグの使用例を示す図。

- 【図20】本発明の一態様に係るC P Uを示すブロック図。

- 【図21】本発明の一態様に係る記憶素子の回路図。

- 【図22】本発明の一態様に係る表示装置の上面図および回路図。

- 【図23】本発明の一態様に係る表示モジュールを説明する図。

- 【図24】本発明の一態様に係る電子機器を示す図。

- 【図25】本発明の一態様に係る電子機器を示す図。

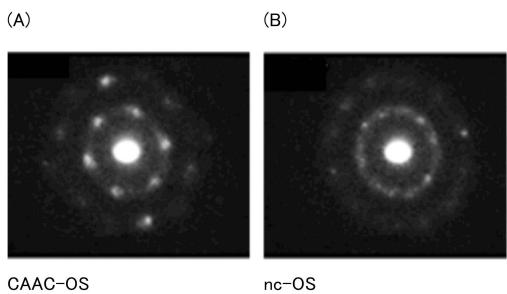

- 【図26】酸化物半導体のナノビーム電子回折パターンを示す図。

- 【図27】電子の累積照射量と結晶部の大きさの関係を示す図。

- 【図28】本発明の一態様に係る半導体装置のバンド構造を説明する図。

【発明を実施するための形態】

【0026】

本発明の実施の形態について、図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、その形態および詳細を様々に変更し得ることは、当業者であれば容易に理解される。また、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、図面を用いて発明の構成を説明するにあたり、同じものを指す符号は異なる図面間でも共通して用いる。なお、同様のものを指す際にはハッチパターンを同じくし、特に符号を付さない場合がある。

【0027】

なお、図において、大きさ、膜（層）の厚さ、または領域は、明瞭化のために誇張されている場合がある。

【0028】

なお、本明細書において、例えば、物体の形状を「径」、「粒径」、「大きさ」、「サイズ」、「幅」などで規定する場合、物体が収まる最小の立方体における一辺の長さ、または物体の一断面における円相当径と読み替えてよい。物体の一断面における円相当径とは、物体の一断面と等しい面積となる正円の直径をいう。

【0029】

なお、電圧は、ある電位と、基準の電位（例えば接地電位（G N D）またはソース電位）との電位差のことを示す場合が多い。よって、電圧を電位と言い換えることが可能である。

【0030】

なお、第1、第2として付される序数詞は便宜的に用いるものであり、工程順または積層順を示すものではない。そのため、例えば、「第1の」を「第2の」または「第3の」などと適宜置き換えて説明することができる。また、本明細書等に記載されている序数詞と、本発明の一態様を特定するために用いられる序数詞は一致しない場合がある。

【0031】

なお、「半導体」と表記した場合でも、例えば、導電性が十分低い場合は「絶縁体」としての特性を有する場合がある。また、「半導体」と「絶縁体」は境界が曖昧であり、厳密に区別できない場合がある。したがって、本明細書に記載の「半導体」は、「絶縁体」と言い換えることができる場合がある。同様に、本明細書に記載の「絶縁体」は、「半導体」と言い換えることができる場合がある。

【0032】

また、「半導体」と表記した場合でも、例えば、導電性が十分高い場合は「導電体」としての特性を有する場合がある。また、「半導体」と「導電体」は境界が曖昧であり、厳密に区別できない場合がある。したがって、本明細書に記載の「半導体」は、「導電体」と言い換えることができる場合がある。同様に、本明細書に記載の「導電体」は、「半導体」

10

20

30

40

50

」と言い換えることができる場合がある。

【0033】

なお、半導体の不純物とは、例えば、半導体を構成する主成分以外をいう。例えば、濃度が0.1原子%未満の元素は不純物である。不純物が含まれることにより、例えば、半導体のDOS (Density of State) が形成されることや、キャリア移動度が低下することや、結晶性が低下することなどが起こる場合がある。半導体が酸化物半導体である場合、半導体の特性を変化させる不純物としては、例えば、第1族元素、第2族元素、第14族元素、第15族元素、主成分以外の遷移金属などがあり、特に、例えば、水素（水にも含まれる）、リチウム、ナトリウム、シリコン、ホウ素、リン、炭素、窒素などがある。酸化物半導体の場合、例えば水素などの不純物の混入によって酸素欠損を形成する場合がある。また、半導体がシリコンである場合、半導体の特性を変化させる不純物としては、例えば、酸素、水素を除く第1族元素、第2族元素、第13族元素、第15族元素などがある。

【0034】

なお、本明細書において、Aが濃度Bの領域を有する、と記載する場合、例えば、Aのある領域における深さ方向全体の濃度がBである場合、Aのある領域における深さ方向の濃度の平均値がBである場合、Aのある領域における深さ方向の濃度の中央値がBである場合、Aのある領域における深さ方向の濃度の最大値がBである場合、Aのある領域における深さ方向の濃度の最小値がBである場合、Aのある領域における深さ方向の濃度の収束値がBである場合、測定上Aそのものの確からしい値の得られる領域における濃度がBである場合などを含む。

【0035】

また、本明細書において、Aが大きさB、長さB、厚さB、幅Bまたは距離Bの領域を有する、と記載する場合、例えば、Aのある領域における全体の大きさ、長さ、厚さ、幅、または距離がBである場合、Aのある領域における大きさ、長さ、厚さ、幅、または距離の平均値がBである場合、Aのある領域における大きさ、長さ、厚さ、幅、または距離の中央値がBである場合、Aのある領域における大きさ、長さ、厚さ、幅、または距離の最大値がBである場合、Aのある領域における大きさ、長さ、厚さ、幅、または距離の最小値がBである場合、Aのある領域における大きさ、長さ、厚さ、幅、または距離の収束値がBである場合、測定上Aそのものの確からしい値の得られる領域での大きさ、長さ、厚さ、幅、または距離がBである場合などを含む。

【0036】

なお、チャネル長とは、例えば、トランジスタの上面図において、半導体（またはトランジスタがオン状態のときに半導体の中で電流の流れる部分）とゲート電極とが互いに重なる領域、またはチャネルが形成される領域における、ソース（ソース領域またはソース電極）とドレイン（ドレイン領域またはドレイン電極）との間の距離をいう。なお、一つのトランジスタにおいて、チャネル長が全ての領域で同じ値をとるとは限らない。即ち、一つのトランジスタのチャネル長は、一つの値に定まらない場合がある。そのため、本明細書では、チャネル長は、チャネルの形成される領域における、いずれか一の値、最大値、最小値または平均値とする。

【0037】

チャネル幅とは、例えば、半導体（またはトランジスタがオン状態のときに半導体の中で電流の流れる部分）とゲート電極とが互いに重なる領域、またはチャネルが形成される領域における、ソースとドレインとが向かい合っている部分の長さをいう。なお、一つのトランジスタにおいて、チャネル幅がすべての領域で同じ値をとるとは限らない。即ち、一つのトランジスタのチャネル幅は、一つの値に定まらない場合がある。そのため、本明細書では、チャネル幅は、チャネルの形成される領域における、いずれか一の値、最大値、最小値または平均値とする。

【0038】

なお、トランジスタの構造によっては、実際にチャネルの形成される領域におけるチャネ

10

20

30

40

50

ル幅（以下、実効的なチャネル幅と呼ぶ。）と、トランジスタの上面図において示されるチャネル幅（以下、見かけ上のチャネル幅と呼ぶ。）と、が異なる場合がある。例えば、立体的な構造を有するトランジスタでは、実効的なチャネル幅が、トランジスタの上面図において示される見かけ上のチャネル幅よりも大きくなり、その影響が無視できなくなる場合がある。例えば、微細かつ立体的な構造を有するトランジスタでは、半導体の上面に形成されるチャネル領域の割合に対して、半導体の側面に形成されるチャネル領域の割合が大きくなる場合がある。その場合は、上面図において示される見かけ上のチャネル幅よりも、実際にチャネルの形成される実効的なチャネル幅の方が大きくなる。

#### 【0039】

ところで、立体的な構造を有するトランジスタにおいては、実効的なチャネル幅の、実測による見積もりが困難となる場合がある。例えば、設計値から実効的なチャネル幅を見積もるために、半導体の形状が既知という仮定が必要である。したがって、半導体の形状が正確にわからない場合には、実効的なチャネル幅を正確に測定することは困難である。

10

#### 【0040】

そこで、本明細書では、トランジスタの上面図において、半導体とゲート電極とが互いに重なる領域における、ソースとドレインとが向かい合っている部分の長さである見かけ上のチャネル幅を、「囲い込みチャネル幅（SCW：Surrounded Channel Width）」と呼ぶ場合がある。また、本明細書では、単にチャネル幅と記載した場合には、囲い込みチャネル幅または見かけ上のチャネル幅を指す場合がある。または、本明細書では、単にチャネル幅と記載した場合には、実効的なチャネル幅を指す場合がある。なお、チャネル長、チャネル幅、実効的なチャネル幅、見かけ上のチャネル幅、囲い込みチャネル幅などは、断面TEM像などを取得して、その画像を解析することなどによって、値を決定することができる。

20

#### 【0041】

なお、トランジスタの電界効果移動度や、チャネル幅当たりの電流値などを計算して求める場合、囲い込みチャネル幅を用いて計算する場合がある。その場合には、実効的なチャネル幅を用いて計算する場合とは異なる値をとる場合がある。

#### 【0042】

なお、本明細書において、AがBより迫り出した形状を有すると記載する場合、上面図または断面図において、Aの少なくとも一端が、Bの少なくとも一端よりも外側にある形状を有することを示す場合がある。したがって、AがBより迫り出した形状を有すると記載されている場合、例えば上面図において、Aの一端が、Bの一端よりも外側にある形状を有すると読み替えることができる。

30

#### 【0043】

なお、本明細書において、「平行」とは、二つの直線が-10°以上10°以下の角度で配置されている状態をいう。したがって、-5°以上5°以下の場合も含まれる。また、「垂直」とは、二つの直線が80°以上100°以下の角度で配置されている状態をいう。したがって、85°以上95°以下の場合も含まれる。

#### 【0044】

なお、本明細書において、結晶が三方晶または菱面体晶である場合、六方晶系として表す。

40

#### 【0045】

##### <トランジスタの構造>

以下では、本発明の一態様に係るトランジスタの構造について説明する。

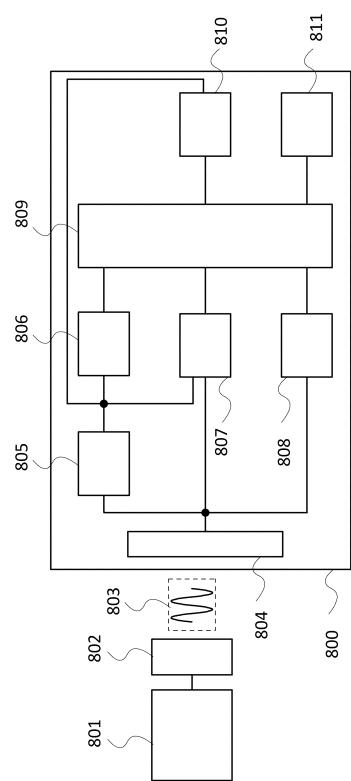

#### 【0046】

##### <トランジスタ構造1>

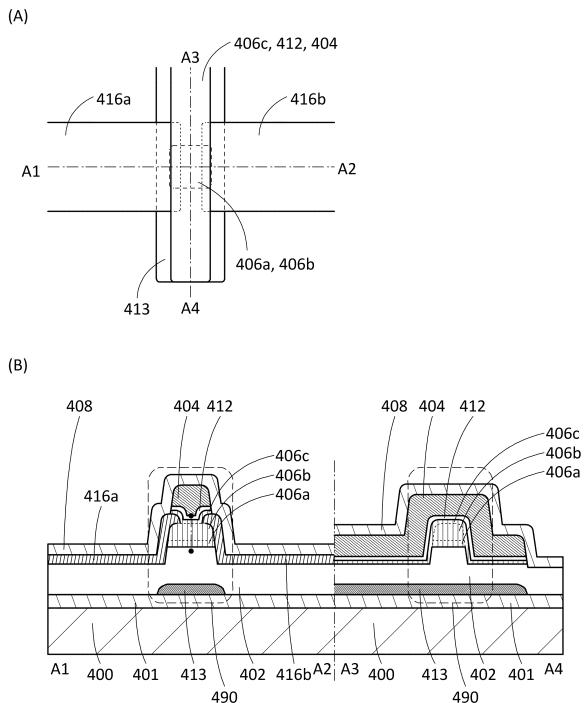

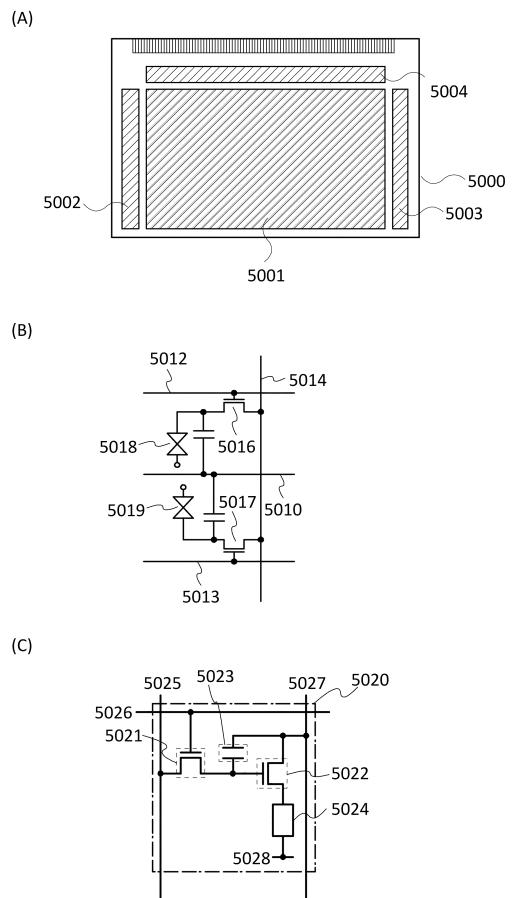

図1(A)および図1(B)は、本発明の一態様に係るトランジスタ490の上面図および断面図である。図1(A)は上面図であり、図1(B)は、図1(A)に示す一点鎖線A1-A2、および一点鎖線A3-A4に対応する断面図である。なお、図1(A)の上面図では、図の明瞭化のために一部の要素を省いて図示している。

50

## 【0047】

図1(A)および図1(B)に示すトランジスタ490は、基板400上の導電体413と、基板400上および導電体413上の凸部を有する絶縁体402と、絶縁体402の凸部上の半導体406aと、半導体406a上の半導体406bと、半導体406bの上面および側面と接し、間隔を開けて配置された導電体416aおよび導電体416bと、半導体406b上、導電体416a上および導電体416b上の半導体406cと、半導体406c上の絶縁体412と、絶縁体412上の導電体404と、導電体416a上、導電体416b上および導電体404上の絶縁体408と、を有する。

## 【0048】

なお、半導体406cは、A3-A4断面において、少なくとも半導体406bの上面および側面と接する。また、導電体404は、A3-A4断面において、半導体406cおよび絶縁体412を介して半導体406bの上面および側面と面する。また、導電体413は、絶縁体402を介して半導体406bの下面と面する。また、絶縁体402が凸部を有さなくても構わない。また、絶縁体401を有さなくても構わない。また、導電体413を有さなくても構わない。また、半導体406cを有さなくても構わない。また、絶縁体408を有さなくても構わない。

## 【0049】

なお、半導体406bは、トランジスタ490のチャネル形成領域としての機能を有する。また、導電体404は、トランジスタ490の第1のゲート電極(フロントゲート電極ともいう。)としての機能を有する。また、導電体413は、トランジスタ490の第2のゲート電極(バックゲート電極ともいう。)としての機能を有する。また、導電体416aおよび導電体416bは、トランジスタ490のソース電極およびドレイン電極としての機能を有する。また、絶縁体408は、バリア層としての機能を有する。絶縁体408は、例えば、酸素または/および水素をブロックする機能を有する。または、絶縁体408は、例えば、半導体406aまたは/および半導体406cよりも、酸素または/および水素をブロックする能力が高い。

## 【0050】

なお、絶縁体402は過剰酸素を含む絶縁体であると好ましい。

## 【0051】

例えば、過剰酸素を含む絶縁体は、加熱処理によって酸素を放出する機能を有する絶縁体である。例えば、過剰酸素を含む酸化シリコン層は、加熱処理などによって酸素を放出することができる酸化シリコン層である。したがって、絶縁体402は膜中を酸素が移動可能な絶縁体である。即ち、絶縁体402は酸素透過性を有する絶縁体とすればよい。例えば、絶縁体402は、半導体406aよりも酸素透過性の高い絶縁体とすればよい。

## 【0052】

過剰酸素を含む絶縁体は、半導体406b中の酸素欠損を低減させる機能を有する場合がある。半導体406b中で酸素欠損は、DOSを形成し、正孔トラップなどとなる。また、酸素欠損のサイトに水素が入ることによって、キャリアである電子を生成することができる。したがって、半導体406b中の酸素欠損を低減することで、トランジスタ490に安定した電気特性を付与することができる。

## 【0053】

ここで、加熱処理によって酸素を放出する絶縁体は、昇温脱離ガス分光法(TDS: Thermal Desorption Spectroscopy)分析にて、100以上700以下または100以上500以下の表面温度の範囲で $1 \times 10^{-8}$ atoms/cm<sup>3</sup>以上、 $1 \times 10^{-9}$ atoms/cm<sup>3</sup>以上または $1 \times 10^{-20}$ atoms/cm<sup>3</sup>以上の酸素(酸素原子数換算)を放出することもある。

## 【0054】

ここで、TDS分析を用いた酸素の放出量の測定方法について、以下に説明する。

## 【0055】

測定試料をTDS分析したときの気体の全放出量は、放出ガスのイオン強度の積分値に比

10

20

30

40

50

例する。そして標準試料との比較により、気体の全放出量を計算することができる。

【0056】

例えば、標準試料である所定の密度の水素を含むシリコン基板のTDS分析結果、および測定試料のTDS分析結果から、測定試料の酸素分子の放出量( $N_{O_2}$ )は、下に示す式で求めることができる。ここで、TDS分析で得られる質量電荷比32で検出されるガスの全てが酸素分子由来と仮定する。 $CH_3OH$ は質量電荷比32であるが、存在する可能性が低いものとしてここでは考慮しない。また、酸素原子の同位体である質量数17の酸素原子および質量数18の酸素原子を含む酸素分子についても、自然界における存在比率が極微量であるため考慮しない。

【0057】

10

$$N_{O_2} = N_{H_2} / S_{H_2} \times S_{O_2} \times$$

【0058】

$N_{H_2}$ は、標準試料から脱離した水素分子を密度で換算した値である。 $S_{H_2}$ は、標準試料をTDS分析したときのイオン強度の積分値である。ここで、標準試料の基準値を、 $N_{H_2} / S_{H_2}$ とする。 $S_{O_2}$ は、測定試料をTDS分析したときのイオン強度の積分値である。は、TDS分析におけるイオン強度に影響する係数である。上に示す式の詳細に関しては、特開平6-275697公報を参照する。なお、上記酸素の放出量は、電子科学株式会社製の昇温脱離分析装置EMD-WA1000S/Wを用い、標準試料として、例えば $1 \times 10^{16} \text{ atoms/cm}^2$ の水素原子を含むシリコン基板を用いて測定する。

20

【0059】

また、TDS分析において、酸素の一部は酸素原子として検出される。酸素分子と酸素原子の比率は、酸素分子のイオン化率から算出することができる。なお、上述のは酸素分子のイオン化率を含むため、酸素分子の放出量を評価することで、酸素原子の放出量についても見積もることができる。

【0060】

なお、 $N_{O_2}$ は酸素分子の放出量である。酸素原子に換算したときの放出量は、酸素分子の放出量の2倍となる。

【0061】

30

または、加熱処理によって酸素を放出する絶縁体は、過酸化ラジカルを含むこともある。具体的には、過酸化ラジカルに起因するスピニ密度が、 $5 \times 10^{17} \text{ spins/cm}^3$ 以上であることをいう。なお、過酸化ラジカルを含む絶縁体は、ESRにて、g値が2.01近傍に非対称の信号を有することもある。

【0062】

または、過剰酸素を含む絶縁体は、酸素が過剰な酸化シリコン( $SiO_x (X > 2)$ )であってもよい。酸素が過剰な酸化シリコン( $SiO_x (X > 2)$ )は、シリコン原子数の2倍より多い酸素原子を単位体積当たりに含むものである。単位体積当たりのシリコン原子数および酸素原子数は、ラザフォード後方散乱法(RBS: Rutherford Backscattering Spectrometry)により測定した値である。

【0063】

40

なお、上述した過剰酸素を含む絶縁体についての説明を、過剰酸素を含む半導体に対しても適用することができる場合がある。

【0064】

図1(B)に示すように、半導体406bの側面は、導電体416aおよび導電体416bと接する。また、導電体404の電界によって、半導体406bを電気的に取り囲むことができる(導電体から生じる電界によって、半導体を電気的に取り囲むトランジスタの構造を、surrounded channel(s-channel)構造とよぶ。)。そのため、半導体406bの全体(バルク)にチャネルが形成される場合がある。s-channel構造では、トランジスタのソース-ドレイン間に大電流を流すことができ、導通時の電流(オン電流)を高くすることができる。

50

## 【0065】

高いオン電流が得られるため、s-channel構造は、微細化されたトランジスタに適した構造といえる。トランジスタを微細化できるため、該トランジスタを有する半導体装置は、集積度の高い、高密度化された半導体装置とすることが可能となる。例えば、トランジスタ490は、チャネル長が好ましくは40nm以下、さらに好ましくは30nm以下、より好ましくは20nm以下の領域を有し、かつ、トランジスタ490は、チャネル幅が好ましくは40nm以下、さらに好ましくは30nm以下、より好ましくは20nm以下の領域を有する。

## 【0066】

また、導電体413に、ソース電極よりも低い電圧または高い電圧を印加し、トランジスタ490のしきい値電圧をプラス方向またはマイナス方向へ変動させてもよい。例えば、トランジスタ490のしきい値電圧をプラス方向に変動させることで、ゲート電圧が0Vであってもトランジスタ490が非導通状態（オフ状態）となる、ノーマリーオフが実現できる場合がある。なお、導電体413に印加する電圧は、可変であってもよいし、固定であってもよい。導電体413に印加する電圧を可変にする場合、電圧を制御する回路を導電体413と電気的に接続してもよい。

## 【0067】

以下では、半導体406a、半導体406b、半導体406cなどに適用可能な酸化物半導体の構造について説明する。

## 【0068】

以下では、酸化物半導体の構造について説明する。

20

## 【0069】

酸化物半導体は、非単結晶酸化物半導体と単結晶酸化物半導体とに大別される。非単結晶酸化物半導体とは、CAAC-OS (C Axis Aligned Crystaline Oxide Semiconductor)、多結晶酸化物半導体、微結晶酸化物半導体、非晶質酸化物半導体などをいう。

## 【0070】

まずは、CAAC-OSについて説明する。

## 【0071】

CAAC-OSは、c軸配向した複数の結晶部を有する酸化物半導体の一つである。

30

## 【0072】

透過型電子顕微鏡（TEM: Transmission Electron Microscope）によって、CAAC-OSの明視野像および回折パターンの複合解析像（高分解能TEM像ともいう。）を観察することで複数の結晶部を確認することができる。一方、高分解能TEM像によっても明確な結晶部同士の境界、即ち結晶粒界（グレインバウンダリーともいう。）を確認することができない。そのため、CAAC-OSは、結晶粒界に起因する電子移動度の低下が起こりにくいといえる。

## 【0073】

試料面と概略平行な方向から、CAAC-OSの断面の高分解能TEM像を観察すると、結晶部において、金属原子が層状に配列していることを確認できる。金属原子の各層は、CAAC-OSの膜を形成する面（被形成面ともいう。）または上面の凹凸を反映した形状であり、CAAC-OSの被形成面または上面と平行に配列する。

40

## 【0074】

一方、試料面と概略垂直な方向から、CAAC-OSの平面の高分解能TEM像を観察すると、結晶部において、金属原子が三角形状または六角形状に配列していることを確認できる。しかしながら、異なる結晶部間で、金属原子の配列に規則性は見られない。

## 【0075】

なお、CAAC-OSに対し、電子回折を行うと、配向性を示すスポット（輝点）が観測される。例えば、CAAC-OSの上面に対し、例えば1nm以上30nm以下の電子線を用いる電子回折（ナノビーム電子回折ともいう。）を行うと、スポットが観測される（

50

図26(A)参照。)。

【0076】

断面の高分解能TEM像および平面の高分解能TEM像より、CAAC-OSの結晶部は配向性を有していることがわかる。

【0077】

なお、CAAC-OSに含まれるほとんどの結晶部は、一辺が100nm未満の立方体内に収まる大きさである。したがって、CAAC-OSに含まれる結晶部は、一辺が10nm未満、5nm未満または3nm未満の立方体内に収まる大きさの場合も含まれる。ただし、CAAC-OSに含まれる複数の結晶部が連結することで、一つの大きな結晶領域を形成する場合がある。例えば、平面の高分解能TEM像において、2500nm<sup>2</sup>以上、5μm<sup>2</sup>以上または1000μm<sup>2</sup>以上となる結晶領域が観察される場合がある。

10

【0078】

CAAC-OSに対し、X線回折(XRD: X-Ray Diffraction)装置を用いて構造解析を行うと、例えばInGaZnO<sub>4</sub>の結晶を有するCAAC-OSのout-of-plane法による解析では、回折角(2θ)が31°近傍にピークが現れる場合がある。このピークは、InGaZnO<sub>4</sub>の結晶の(009)面に帰属されることから、CAAC-OSの結晶がc軸配向性を有し、c軸が被形成面または上面に概略垂直な方向を向いていることが確認できる。

【0079】

一方、CAAC-OSに対し、c軸に概略垂直な方向からX線を入射させるin-plane法による解析では、2θが56°近傍にピークが現れる場合がある。このピークは、InGaZnO<sub>4</sub>の結晶の(110)面に帰属される。InGaZnO<sub>4</sub>の単結晶酸化物半導体であれば、2θを56°近傍に固定し、試料面の法線ベクトルを軸(c軸)として試料を回転させながら分析(スキャン)を行うと、(110)面と等価な結晶面に帰属されるピークが6本観察される。これに対し、CAAC-OSの場合は、2θを56°近傍に固定してスキャンした場合でも、明瞭なピークが現れない。

20

【0080】

以上のことから、CAAC-OSでは、異なる結晶部間ではa軸およびb軸の配向は不規則であるが、c軸配向性を有し、かつc軸が被形成面または上面の法線ベクトルに平行な方向を向いていることがわかる。したがって、前述の断面の高分解能TEM観察で確認された層状に配列した金属原子の各層は、結晶のab面に平行な面である。

30

【0081】

なお、結晶部は、CAAC-OSを成膜した際、または加熱処理などの結晶化処理を行った際に形成される。上述したように、結晶のc軸は、CAAC-OSの被形成面または上面の法線ベクトルに平行な方向に配向する。したがって、例えば、CAAC-OSの形状をエッチングなどによって変化させた場合、結晶のc軸がCAAC-OSの被形成面または上面の法線ベクトルと平行にならないこともある。

【0082】

また、CAAC-OS中において、c軸配向した結晶部の分布が均一でなくてもよい。例えば、CAAC-OSの結晶部が、CAAC-OSの上面近傍からの結晶成長によって形成される場合、上面近傍の領域は、被形成面近傍の領域よりもc軸配向した結晶部の割合が高くなることがある。また、不純物の添加されたCAAC-OSは、不純物が添加された領域が変質し、部分的にc軸配向した結晶部の割合の異なる領域が形成されることもある。

40

【0083】

なお、InGaZnO<sub>4</sub>の結晶を有するCAAC-OSのout-of-plane法による解析では、2θが31°近傍のピークの他に、2θが36°近傍にもピークが現れる場合がある。2θが36°近傍のピークは、CAAC-OS中の一部に、c軸配向性を有さない結晶が含まれることを示している。CAAC-OSは、2θが31°近傍にピークを示し、2θが36°近傍にピークを示さないことが好ましい。

50

## 【0084】

C A A C - O S は、不純物濃度の低い酸化物半導体である。不純物は、水素、炭素、シリコン、遷移金属元素などの酸化物半導体の主成分以外の元素である。特に、シリコンなどの、酸化物半導体を構成する金属元素よりも酸素との結合力の強い元素は、酸化物半導体から酸素を奪うことで酸化物半導体の原子配列を乱し、結晶性を低下させる要因となる。また、鉄やニッケルなどの重金属、アルゴン、二酸化炭素などは、原子半径（または分子半径）が大きいため、酸化物半導体内部に含まれると、酸化物半導体の原子配列を乱し、結晶性を低下させる要因となる。なお、酸化物半導体に含まれる不純物は、キャリアトラップやキャリア発生源となる場合がある。

## 【0085】

また、C A A C - O S は、欠陥準位密度の低い酸化物半導体である。例えば、酸化物半導体中の酸素欠損は、キャリアトラップとなることや、水素を捕獲することによってキャリア発生源となることがある。

## 【0086】

不純物濃度が低く、欠陥準位密度が低い（酸素欠損の少ない）ことを、高純度真性または実質的に高純度真性と呼ぶ。高純度真性または実質的に高純度真性である酸化物半導体は、キャリア発生源が少ないため、キャリア密度を低くすることができる。したがって、当該酸化物半導体を用いたトランジスタは、しきい値電圧がマイナスとなる電気特性（ノーマリーオンともいう。）になることが少ない。また、高純度真性または実質的に高純度真性である酸化物半導体は、キャリアトラップが少ない。そのため、当該酸化物半導体を用いたトランジスタは、電気特性の変動が小さく、信頼性の高いトランジスタとなる。なお、酸化物半導体のキャリアトラップに捕獲された電荷は、放出するまでに要する時間が長く、あたかも固定電荷のように振る舞うことがある。そのため、不純物濃度が高く、欠陥準位密度が高い酸化物半導体を用いたトランジスタは、電気特性が不安定となる場合がある。

## 【0087】

また、C A A C - O S を用いたトランジスタは、可視光や紫外光の照射による電気特性の変動が小さい。

## 【0088】

次に、多結晶酸化物半導体について説明する。

## 【0089】

多結晶酸化物半導体は、高分解能 T E M 像において結晶粒を確認することができる。多結晶酸化物半導体に含まれる結晶粒は、例えば、高分解能 T E M 像で、2 nm 以上 300 nm 以下、3 nm 以上 100 nm 以下または 5 nm 以上 50 nm 以下の粒径が多い。また、多結晶酸化物半導体は、高分解能 T E M 像で、結晶粒界を確認できる場合がある。

## 【0090】

多結晶酸化物半導体は、複数の結晶粒を有し、当該複数の結晶粒間において結晶の方位が異なっている場合がある。また、多結晶酸化物半導体に対し、X R D 装置を用いて構造解析を行うと、例えば I n G a Z n O<sub>4</sub> の結晶を有する多結晶酸化物半導体の o u t - o f - p l a n e 法による解析では、2<sup>θ</sup> が 31° 近傍のピーク、2<sup>θ</sup> が 36° 近傍のピーク、またはそのほかのピークが現れる場合がある。

## 【0091】

多結晶酸化物半導体は、高い結晶性を有するため、高い電子移動度を有する場合がある。したがって、多結晶酸化物半導体を用いたトランジスタは、高い電界効果移動度を有する。ただし、多結晶酸化物半導体は、結晶粒界に不純物が偏析する場合がある。また、多結晶酸化物半導体の結晶粒界は欠陥準位となる。多結晶酸化物半導体は、結晶粒界がキャリアトラップやキャリア発生源となる場合があるため、多結晶酸化物半導体を用いたトランジスタは、C A A C - O S を用いたトランジスタと比べて、電気特性の変動が大きく、信頼性の低いトランジスタとなる場合がある。

10

20

30

40

50

## 【0092】

次に、微結晶酸化物半導体について説明する。

## 【0093】

微結晶酸化物半導体は、高分解能TEM像において、結晶部を確認することができる領域と、明確な結晶部を確認することのできない領域と、を有する。微結晶酸化物半導体に含まれる結晶部は、1nm以上100nm以下、または1nm以上10nm以下の大きさであることが多い。特に、1nm以上10nm以下、または1nm以上3nm以下の微結晶であるナノ結晶(nc:nanocrystalline)を有する酸化物半導体を、nc-OS(nanocrystalline Oxide Semiconductor)と呼ぶ。また、nc-OSは、例えば、高分解能TEM像では、結晶粒界を明確に確認できない場合がある。10

## 【0094】

nc-OSは、微小な領域(例えば、1nm以上10nm以下の領域、特に1nm以上3nm以下の領域)において原子配列に周期性を有する。また、nc-OSは、異なる結晶部間で結晶方位に規則性が見られない。そのため、膜全体で配向性が見られない。したがって、nc-OSは、分析方法によっては、非晶質酸化物半導体と区別が付かない場合がある。例えば、nc-OSに対し、結晶部よりも大きい径のX線を用いるXRD装置を用いて構造解析を行うと、out-of-plane法による解析では、結晶面を示すピークが検出されない。また、nc-OSに対し、結晶部よりも大きいプローブ径(例えば50nm以上)の電子線を用いる電子回折(制限視野電子回折ともいう。)を行うと、ハローパターンのような回折パターンが観測される。一方、nc-OSに対し、結晶部の大きさと近いか結晶部より小さいプローブ径の電子線を用いるナノビーム電子回折を行うと、スポットが観測される。また、nc-OSに対しナノビーム電子回折を行うと、円を描くように(リング状に)輝度の高い領域が観測される場合がある。また、nc-OSに対しナノビーム電子回折を行うと、リング状の領域内に複数のスポットが観測される場合がある(図26(B)参照。)。20

## 【0095】

nc-OSは、非晶質酸化物半導体よりも規則性の高い酸化物半導体である。そのため、nc-OSは、非晶質酸化物半導体よりも欠陥準位密度が低くなる。ただし、nc-OSは、異なる結晶部間で結晶方位に規則性が見られない。そのため、nc-OSは、CAAC-OSと比べて欠陥準位密度が高くなる。30

## 【0096】

したがって、nc-OSは、CAAC-OSと比べて、キャリア密度が高くなる場合がある。キャリア密度が高い酸化物半導体は、電子移動度が高くなる場合がある。したがって、nc-OSを用いたトランジスタは、高い電界効果移動度を有する場合がある。また、nc-OSは、CAAC-OSと比べて、欠陥準位密度が高いため、キャリアトラップが多くなる場合がある。したがって、nc-OSを用いたトランジスタは、CAAC-OSを用いたトランジスタと比べて、電気特性の変動が大きく、信頼性の低いトランジスタとなる。ただし、nc-OSは、比較的不純物が多く含まれていても形成することができるため、CAAC-OSよりも形成が容易となり、用途によっては好適に用いることができる場合がある。そのため、nc-OSを用いたトランジスタを有する半導体装置は、生産性高く作製することができる場合がある。40

## 【0097】

次に、非晶質酸化物半導体について説明する。

## 【0098】

非晶質酸化物半導体は、膜中における原子配列が不規則であり、結晶部を有さない酸化物半導体である。石英のような無定形状態を有する酸化物半導体が一例である。

## 【0099】

非晶質酸化物半導体は、高分解能TEM像において結晶部を確認することができない。

## 【0100】

非晶質酸化物半導体に対し、XRD装置を用いた構造解析を行うと、out-of-plane法による解析では、結晶面を示すピークが検出されない。また、非晶質酸化物半導体に対し、電子回折を行うと、ハローパターンが観測される。また、非晶質酸化物半導体に対し、ナノビーム電子回折を行うと、スポットが観測されず、ハローパターンが観測される。

【0101】

非晶質酸化物半導体は、水素などの不純物を高い濃度で含む酸化物半導体である。また、非晶質酸化物半導体は、欠陥準位密度の高い酸化物半導体である。

【0102】

不純物濃度が高く、欠陥準位密度が高い酸化物半導体は、キャリアトラップやキャリア発生源が多い酸化物半導体である。 10

【0103】

したがって、非晶質酸化物半導体は、n<sub>c</sub>-OSと比べて、さらにキャリア密度が高くなる場合がある。そのため、非晶質酸化物半導体を用いたトランジスタは、ノーマリーオンの電気特性になりやすい。したがって、ノーマリーオンの電気特性が求められるトランジスタに好適に用いることができる場合がある。非晶質酸化物半導体は、欠陥準位密度が高いため、キャリアトラップが多くなる場合がある。したがって、非晶質酸化物半導体を用いたトランジスタは、CAAC-OSやn<sub>c</sub>-OSを用いたトランジスタと比べて、電気特性の変動が大きく、信頼性の低いトランジスタとなる。

【0104】

次に、単結晶酸化物半導体について説明する。 20

【0105】

単結晶酸化物半導体は、不純物濃度が低く、欠陥準位密度が低い（酸素欠損が少ない）酸化物半導体である。そのため、キャリア密度を低くすることができる。したがって、単結晶酸化物半導体を用いたトランジスタは、ノーマリーオンの電気特性になることが少ない。また、単結晶酸化物半導体は、不純物濃度が低く、欠陥準位密度が低いため、キャリアトラップが少なくなる場合がある。したがって、単結晶酸化物半導体を用いたトランジスタは、電気特性の変動が小さく、信頼性の高いトランジスタとなる。

【0106】

なお、酸化物半導体は、欠陥が少ないと密度が高くなる。また、酸化物半導体は、結晶性が高いと密度が高くなる。また、酸化物半導体は、水素などの不純物濃度が低いと密度が高くなる。単結晶酸化物半導体は、CAAC-OSよりも密度が高い。また、CAAC-OSは、微結晶酸化物半導体よりも密度が高い。また、多結晶酸化物半導体は、微結晶酸化物半導体よりも密度が高い。また、微結晶酸化物半導体は、非晶質酸化物半導体よりも密度が高い。 30

【0107】

なお、酸化物半導体は、n<sub>c</sub>-OSと非晶質酸化物半導体との間の物性を示す構造を有する場合がある。そのような構造を有する酸化物半導体を、特に非晶質ライク酸化物半導体(a-like OS: amorphous-like Oxide Semiconductor)と呼ぶ。 40

【0108】

a-like OSは、高分解能TEM像において鬆（ボイドともいう。）が観察される場合がある。また、高分解能TEM像において、明確に結晶部を確認することができる領域と、結晶部を確認することのできない領域と、を有する。a-like OSは、TEMによる観察程度の微量な電子照射によって、結晶化が起こり、結晶部の成長が見られる場合がある。一方、良質なn<sub>c</sub>-OSであれば、TEMによる観察程度の微量な電子照射による結晶化はほとんど見られない。

【0109】

なお、a-like OSおよびn<sub>c</sub>-OSの結晶部の大きさの計測は、高分解能TEM像を用いて行うことができる。例えば、InGaZnO<sub>4</sub>の結晶は層状構造を有し、In 50

- O層の間に、Ga-Zn-O層を2層有する。InGaZnO<sub>4</sub>の結晶の単位格子は、In-O層を3層有し、またGa-Zn-O層を6層有する、計9層がc軸方向に層状に重なった構造を有する。よって、これらの近接する層同士の間隔は、(009)面の格子面間隔(d値ともいう。)と同程度であり、結晶構造解析からその値は0.29nmと求められている。そのため、高分解能TEM像における格子縞に着目し、格子縞の間隔が0.28nm以上0.30nm以下である箇所においては、それぞれの格子縞がInGaZnO<sub>4</sub>の結晶のa-b面に対応すると見なした。その格子縞の観察される領域の最大長を、a-like OSおよびnc-OSの結晶部の大きさとする。なお、結晶部の大きさは、0.8nm以上のものを選択的に評価する。

## 【0110】

10

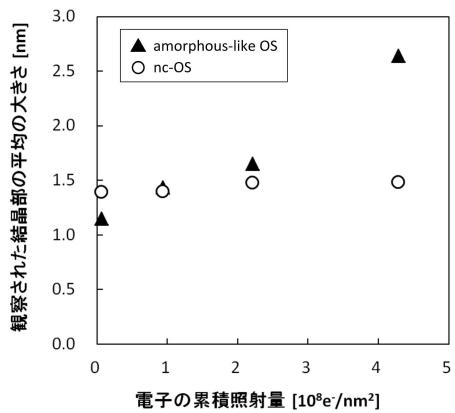

高分解能TEM像により、a-like OSおよびnc-OSの結晶部(20箇所から40箇所)の平均の大きさの変化を調査する。図27は、電子の累積照射量と結晶部の大きさの関係を示す図である。図27より、a-like OSは、電子の累積照射量に応じて結晶部が大きくなっていくことがわかる。具体的には、TEMによる観察初期においては1.2nm程度の大きさだった結晶部が、累積照射量が $4.2 \times 10^8 e^-/nm^2$ においては2.6nm程度の大きさまで成長していることがわかる。一方、良質なnc-OSは、電子照射開始時から電子の累積照射量が $4.2 \times 10^8 e^-/nm^2$ になるまでの範囲で、電子の累積照射量によらず結晶部の大きさに変化が見られないことがわかる。

## 【0111】

20

また、図27に示す、a-like OSおよびnc-OSの結晶部の大きさの変化を線形近似して、電子の累積照射量 $0 e^-/nm^2$ まで外挿すると、結晶部の平均の大きさが正の値をとることがわかる。そのため、a-like OSおよびnc-OSの結晶部が、TEMによる観察前から存在していることがわかる。

## 【0112】

なお、酸化物半導体は、例えば、非晶質酸化物半導体、微結晶酸化物半導体、CAC-OSのうち、二種以上を有する積層膜であってもよい。

## 【0113】

以上が、半導体406a、半導体406b、半導体406cなどに適用可能な酸化物半導体の構造である。

## 【0114】

30

次に、半導体406a、半導体406b、半導体406cなどに適用可能な半導体の、その他の要素について説明する。

## 【0115】

半導体406bは、例えば、インジウムを含む酸化物半導体である。半導体406bは、例えば、インジウムを含むと、キャリア移動度(電子移動度)が高くなる。また、半導体406bは、元素Mを含むと好ましい。元素Mは、好ましくは、アルミニウム、ガリウム、イットリウムまたはスズなどとする。そのほかの元素Mに適用可能な元素としては、ホウ素、シリコン、チタン、鉄、ニッケル、ゲルマニウム、イットリウム、ジルコニウム、モリブデン、ランタン、セリウム、ネオジム、ハフニウム、タンタル、タングステンなどがある。ただし、元素Mとして、前述の元素を複数組み合わせても構わない場合がある。元素Mは、例えば、酸素との結合エネルギーが高い元素である。例えば、酸素との結合エネルギーがインジウムよりも高い元素である。または、元素Mは、例えば、酸化物半導体のエネルギーギャップを大きくする機能を有する元素である。また、半導体406bは、亜鉛を含むと好ましい。酸化物半導体は、亜鉛を含むと結晶化しやすくなる場合がある。

40

## 【0116】

ただし、半導体406bは、インジウムを含む酸化物半導体に限定されない。半導体406bは、例えば、亜鉛スズ酸化物、ガリウムスズ酸化物、酸化ガリウムなどの、インジウムを含まず、亜鉛を含む酸化物半導体、ガリウムを含む酸化物半導体、スズを含む酸化物半導体などであっても構わない。

## 【0117】

50

半導体 406b は、例えば、エネルギーギャップが大きい酸化物を用いる。半導体 406b のエネルギーギャップは、例えば、2.5 eV 以上 4.2 eV 以下、好ましくは 2.8 eV 以上 3.8 eV 以下、さらに好ましくは 3 eV 以上 3.5 eV 以下とする。

【0118】

例えば、半導体 406a および半導体 406c は、半導体 406b を構成する酸素以外の元素一種以上、または二種以上から構成される酸化物半導体である。半導体 406b を構成する酸素以外の元素一種以上、または二種以上から半導体 406a および半導体 406c が構成されるため、半導体 406a と半導体 406b との界面、および半導体 406b と半導体 406c との界面において、界面準位が形成されにくい。

【0119】

半導体 406a、半導体 406b および半導体 406c が、インジウムを含む場合について説明する。なお、半導体 406a が In - M - Zn 酸化物のとき、In および M の和を 100 atomic % としたとき、好ましくは In が 50 atomic % 未満、M が 50 atomic % 以上、さらに好ましくは In が 25 atomic % 未満、M が 75 atomic % 以上とする。また、半導体 406b が In - M - Zn 酸化物のとき、In および M の和を 100 atomic % としたとき、好ましくは In が 25 atomic % 以上、M が 75 atomic % 未満、さらに好ましくは In が 34 atomic % 以上、M が 66 atomic % 未満とする。また、半導体 406c が In - M - Zn 酸化物のとき、In および M の和を 100 atomic % としたとき、好ましくは In が 50 atomic % 未満、M が 50 atomic % 以上、さらに好ましくは In が 25 atomic % 未満、M が 75 atomic % 以上とする。なお、半導体 406c は、半導体 406a と同種の酸化物を用いても構わない。

10

【0120】

半導体 406b は、半導体 406a および半導体 406c よりも電子親和力の大きい酸化物を用いる。例えば、半導体 406b として、半導体 406a および半導体 406c よりも電子親和力の 0.07 eV 以上 1.3 eV 以下、好ましくは 0.1 eV 以上 0.7 eV 以下、さらに好ましくは 0.15 eV 以上 0.4 eV 以下大きい酸化物を用いる。なお、電子親和力は、真空準位と伝導帯下端のエネルギーとの差である。

【0121】

なお、インジウムガリウム酸化物は、小さい電子親和力と、高い酸素ブロック性を有する。そのため、半導体 406c がインジウムガリウム酸化物を含むと好ましい。ガリウム原子割合 [Ga / (In + Ga)] は、例えば、70% 以上、好ましくは 80% 以上、さらに好ましくは 90% 以上とする。

30

【0122】

ただし、半導体 406a または / および半導体 406c が、酸化ガリウムであっても構わない。例えば、半導体 406a として、酸化ガリウムを用いると導電体 416a または導電体 416b と導電体 413 との間に生じるリーク電流を低減することができる。また、例えば、半導体 406c として、酸化ガリウムを用いると導電体 416a または導電体 416b と導電体 404 との間に生じるリーク電流を低減することができる。即ち、トランジスタ 490 のオフ電流を小さくすることができる。

40

【0123】

このとき、ゲート電圧を印加すると、半導体 406a、半導体 406b、半導体 406c のうち、電子親和力の大きい半導体 406b にチャネルが形成される。

【0124】

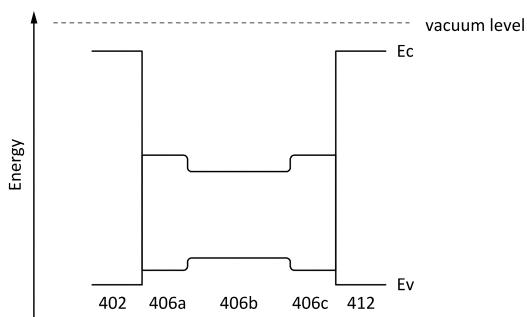

図 1 (B) に示す一点鎖線に対応するバンド構造を図 28 に示す。図 28 には、真空準位 (vacuum level と表記。)、各層の伝導帯下端のエネルギー (Ec と表記。) および価電子帯上端のエネルギー (Ev と表記。) を示す。

【0125】

ここで、半導体 406a と半導体 406b との間には、半導体 406a と半導体 406b との混合領域を有する場合がある。また、半導体 406b と半導体 406c との間には、

50

半導体406bと半導体406cとの混合領域を有する場合がある。混合領域は、界面準位密度が低くなる。そのため、半導体406a、半導体406bおよび半導体406cの積層体は、それぞれの界面近傍において、エネルギーが連続的に変化する（連続接合ともいう。）バンド構造となる。

【0126】

このとき、電子は、半導体406a中および半導体406c中ではなく、半導体406b中を主として移動する。したがって、半導体406aおよび半導体406bの界面における界面準位密度、半導体406bと半導体406cとの界面における界面準位密度を低くすることによって、半導体406b中で電子の移動が阻害されることが少なく、トランジスタ490のオン電流を高くすることができます。

10

【0127】

なお、トランジスタ490がs-channel構造を有する場合、半導体406bの全体にチャネルが形成される。したがって、半導体406bが厚いほどチャネル領域は大きくなる。即ち、半導体406bが厚いほど、トランジスタ490のオン電流を高くすることができます。例えば、20nm以上、好ましくは40nm以上、さらに好ましくは60nm以上、より好ましくは100nm以上の厚さの領域を有する半導体406bとすればよい。ただし、半導体装置の生産性が低下する場合があるため、例えば、300nm以下、好ましくは200nm以下、さらに好ましくは150nm以下の厚さの領域を有する半導体406bとすればよい。

【0128】

20

また、トランジスタ490のオン電流を高くするためには、半導体406cの厚さは小さいほど好ましい。例えば、10nm未満、好ましくは5nm以下、さらに好ましくは3nm以下の領域を有する半導体406cとすればよい。一方、半導体406cは、チャネルの形成される半導体406bへ、隣接する絶縁体を構成する酸素以外の元素（水素、シリコンなど）が入り込まないようブロックする機能を有する。そのため、半導体406cは、ある程度の厚さを有することが好ましい。例えば、0.3nm以上、好ましくは1nm以上、さらに好ましくは2nm以上の厚さの領域を有する半導体406cとすればよい。また、半導体406cは、絶縁体402などから放出される酸素の外方拡散を抑制するために、酸素をブロックする性質を有すると好ましい。

【0129】

30

また、信頼性を高くするためには、半導体406aは厚く、半導体406cは薄いことが好ましい。例えば、10nm以上、好ましくは20nm以上、さらに好ましくは40nm以上、より好ましくは60nm以上の厚さの領域を有する半導体406aとすればよい。半導体406aの厚さを、厚くすることで、隣接する絶縁体と半導体406aとの界面からチャネルの形成される半導体406bまでの距離を離すことができる。ただし、半導体装置の生産性が低下する場合があるため、例えば、200nm以下、好ましくは120nm以下、さらに好ましくは80nm以下の厚さの領域を有する半導体406aとすればよい。

【0130】

40

例えば、酸化物半導体中のシリコンは、キャリアトラップやキャリア発生源となる場合がある。したがって、半導体406bのシリコン濃度は低いほど好ましい。例えば、半導体406bと半導体406aとの間に、例えば、二次イオン質量分析法（SIMS：Secondary Ion Mass Spectrometry）において、 $1 \times 10^{19}$  atoms/cm<sup>3</sup>未満、好ましくは $5 \times 10^{18}$  atoms/cm<sup>3</sup>未満、さらに好ましくは $2 \times 10^{18}$  atoms/cm<sup>3</sup>未満のシリコン濃度となる領域を有する。また、半導体406bと半導体406cとの間に、SIMSにおいて、 $1 \times 10^{19}$  atoms/cm<sup>3</sup>未満、好ましくは $5 \times 10^{18}$  atoms/cm<sup>3</sup>未満、さらに好ましくは $2 \times 10^{18}$  atoms/cm<sup>3</sup>未満のシリコン濃度となる領域を有する。

【0131】

また、半導体406bは、SIMSにおいて、 $2 \times 10^{20}$  atoms/cm<sup>3</sup>以下、好

50

ましくは  $5 \times 10^{19}$  atoms / cm<sup>3</sup> 以下、より好ましくは  $1 \times 10^{19}$  atoms / cm<sup>3</sup> 以下、さらに好ましくは  $5 \times 10^{18}$  atoms / cm<sup>3</sup> 以下の水素濃度となる領域を有する。また、半導体 406b の水素濃度を低減するために、半導体 406a および半導体 406c の水素濃度を低減すると好ましい。半導体 406a および半導体 406c は、SIMSにおいて、 $2 \times 10^{20}$  atoms / cm<sup>3</sup> 以下、好ましくは  $5 \times 10^{19}$  atoms / cm<sup>3</sup> 以下、さらに好ましくは  $5 \times 10^{18}$  atoms / cm<sup>3</sup> 以下の水素濃度となる領域を有する。また、半導体 406b は、SIMSにおいて、 $5 \times 10^{19}$  atoms / cm<sup>3</sup> 未満、好ましくは  $5 \times 10^{18}$  atoms / cm<sup>3</sup> 以下、より好ましくは  $1 \times 10^{18}$  atoms / cm<sup>3</sup> 以下、さらに好ましくは  $5 \times 10^{17}$  atoms / cm<sup>3</sup> 以下の窒素濃度となる領域を有する。また、半導体 406b の窒素濃度を低減するために、半導体 406a および半導体 406c の窒素濃度を低減すると好ましい。半導体 406a および半導体 406c は、SIMSにおいて、 $5 \times 10^{19}$  atoms / cm<sup>3</sup> 未満、好ましくは  $5 \times 10^{18}$  atoms / cm<sup>3</sup> 以下、より好ましくは  $1 \times 10^{18}$  atoms / cm<sup>3</sup> 以下、さらに好ましくは  $5 \times 10^{17}$  atoms / cm<sup>3</sup> 以下の窒素濃度となる領域を有する。

#### 【0132】

なお、酸化物半導体に銅が混入すると、電子トラップを生成する場合がある。電子トラップは、トランジスタのしきい値電圧をプラス方向へ変動させる場合がある。したがって、半導体 406b の表面または内部における銅濃度は低いほど好ましい。例えば、半導体 406b は、銅濃度が  $1 \times 10^{19}$  atoms / cm<sup>3</sup> 以下、 $5 \times 10^{18}$  atoms / cm<sup>3</sup> 以下、または  $1 \times 10^{18}$  atoms / cm<sup>3</sup> 以下となる領域を有すると好ましい。

#### 【0133】

上述の 3 層構造は一例である。例えば、半導体 406a または半導体 406c のない 2 層構造としても構わない。または、半導体 406a の上もしくは下、または半導体 406c 上もしくは下に、半導体 406a、半導体 406b および半導体 406c として例示した半導体のいずれか一を有する 4 層構造としても構わない。または、半導体 406a の上、半導体 406a の下、半導体 406c の上、半導体 406c の下のいずれか二箇所以上に、半導体 406a、半導体 406b および半導体 406c として例示した半導体のいずれか一を有する n 層構造 (n は 5 以上の整数) としても構わない。

#### 【0134】

または、導電体 416a (または / および導電体 416b) の、少なくとも一部 (または全部) は、半導体 406b などの半導体の、表面、側面、上面、または / および、下面の少なくとも一部 (または全部) と、接している。または、導電体 416a (または / および導電体 416b) の、少なくとも一部 (または全部) は、半導体 406b などの半導体の少なくとも一部 (または全部) と、接している。

#### 【0135】

基板 400 としては、例えば、絶縁体基板、半導体基板または導電体基板を用いればよい。絶縁体基板としては、例えば、ガラス基板、石英基板、サファイア基板、安定化ジルコニア基板 (イットリア安定化ジルコニア基板など)、樹脂基板などがある。また、半導体基板としては、例えば、シリコン、ゲルマニウムなどの単体半導体基板、または炭化シリコン、シリコンゲルマニウム、ヒ化ガリウム、リン化インジウム、酸化亜鉛、酸化ガリウムなどの化合物半導体基板などがある。さらには、前述の半導体基板内部に絶縁体領域を有する半導体基板、例えば SOI (Silicon On Insulator) 基板などがある。導電体基板としては、黒鉛基板、金属基板、合金基板、導電性樹脂基板などがある。または、金属の窒化物を有する基板、金属の酸化物を有する基板などがある。さらには、絶縁体基板に導電体または半導体が設けられた基板、半導体基板に導電体または絶縁体が設けられた基板、導電体基板に半導体または絶縁体が設けられた基板などがある。または、これらの基板に素子が設けられたものを用いてよい。基板に設けられる素子としては、容量素子、抵抗素子、スイッチ素子、発光素子、記憶素子などがある。

#### 【0136】

10

20

30

40

50

また、基板400として、可とう性基板を用いてもよい。なお、可とう性基板上にトランジスタを設ける方法としては、非可とう性の基板上にトランジスタを作製した後、トランジスタを剥離し、可とう性基板である基板400に転置する方法もある。その場合には、非可とう性基板とトランジスタとの間に剥離層を設けるとよい。なお、基板400として、繊維を編みこんだシート、フィルムまたは箔などを用いてもよい。また、基板400が伸縮性を有してもよい。また、基板400は、折り曲げや引っ張りをやめた際に、元の形状に戻る性質を有してもよい。または、元の形状に戻らない性質を有してもよい。基板400は、例えば、5μm以上700μm以下、好ましくは10μm以上500μm以下、さらに好ましくは15μm以上300μm以下の厚さとなる領域を有する。基板400を薄くすると、半導体装置を軽量化することができる。また、基板400を薄くすることで、ガラスなどを用いた場合にも伸縮性を有する場合や、折り曲げや引っ張りをやめた際に、元の形状に戻る性質を有する場合がある。そのため、落下などによって基板400上の半導体装置に加わる衝撃などを緩和することができる。即ち、丈夫な半導体装置を提供することができる。

#### 【0137】

可とう性基板である基板400としては、例えば、金属、合金、樹脂もしくはガラス、またはそれらの繊維などを用いることができる。可とう性基板である基板400は、線膨張率が低いほど環境による変形が抑制されて好ましい。可とう性基板である基板400としては、例えば、線膨張率が $1 \times 10^{-3} / K$ 以下、 $5 \times 10^{-5} / K$ 以下、または $1 \times 10^{-5} / K$ 以下である材質を用いればよい。樹脂としては、例えば、ポリエステル、ポリオレフィン、ポリアミド（ナイロン、アラミドなど）、ポリイミド、ポリカーボネート、アクリルなどがある。特に、アラミドは、線膨張率が低いため、可とう性基板である基板400として好適である。

#### 【0138】

絶縁体401としては、例えば、ホウ素、炭素、窒素、酸素、フッ素、マグネシウム、アルミニウム、シリコン、リン、塩素、アルゴン、ガリウム、ゲルマニウム、イットリウム、ジルコニウム、ランタン、ネオジム、ハフニウムまたはタンタルを含む絶縁体を、単層で、または積層で用いればよい。例えば、絶縁体401としては、酸化アルミニウム、酸化マグネシウム、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニウム、酸化ランタン、酸化ネオジム、酸化ハフニウムまたは酸化タンタルを用いればよい。なお、絶縁体401は、酸化アルミニウムを有することが好ましい。例えば、絶縁体401が酸化アルミニウムを有することで、半導体406bに水素などの不純物が混入することを抑制することができる。

#### 【0139】

導電体413としては、例えば、ホウ素、窒素、酸素、フッ素、シリコン、リン、アルミニウム、チタン、クロム、マンガン、コバルト、ニッケル、銅、亜鉛、ガリウム、イットリウム、ジルコニウム、モリブデン、ルテニウム、銀、インジウム、スズ、タンタルおよびタンゲステンを一種以上含む導電体を、単層で、または積層で用いればよい。または、前述の元素を含む合金や化合物であってもよく、アルミニウムを含む導電体、銅およびチタンを含む導電体、銅およびマンガンを含む導電体、インジウム、スズおよび酸素を含む導電体、チタンおよび窒素を含む導電体などを用いてもよい。

#### 【0140】

絶縁体402としては、例えば、ホウ素、炭素、窒素、酸素、フッ素、マグネシウム、アルミニウム、シリコン、リン、塩素、アルゴン、ガリウム、ゲルマニウム、イットリウム、ジルコニウム、ランタン、ネオジム、ハフニウムまたはタンタルを含む絶縁体を、単層で、または積層で用いればよい。例えば、絶縁体402としては、酸化アルミニウム、酸化マグネシウム、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニウム、酸化ランタン、酸化ネオジム、酸化ハフニウムまたは酸化タンタルを用いればよい。

10

20

30

40

50

## 【0141】

なお、絶縁体402は、比誘電率の高い絶縁体を有することが好ましい。例えば、絶縁体402は、酸化ガリウム、酸化ハフニウム、アルミニウムおよびハフニウムを有する酸化物、アルミニウムおよびハフニウムを有する酸化窒化物、シリコンおよびハフニウムを有する酸化物、シリコンおよびハフニウムを有する酸化窒化物などを有することが好ましい。または、絶縁体402は、酸化シリコンまたは酸化窒化シリコンと、比誘電率の高い絶縁体と、の積層構造を有することが好ましい。酸化シリコンおよび酸化窒化シリコンは、熱的に安定であるため、比誘電率の高い絶縁体と組み合わせることで、熱的に安定かつ比誘電率の高い積層構造とすることができます。例えば、酸化アルミニウム、酸化ガリウムまたは酸化ハフニウムを半導体406a側に有することで、酸化シリコンまたは酸化窒化シリコンに含まれるシリコンが、半導体406aまたは/および半導体406bに混入することを抑制することができる。また、例えば、酸化シリコンまたは酸化窒化シリコンを半導体406a側に有することで、酸化アルミニウム、酸化ガリウムまたは酸化ハフニウムと、酸化シリコンまたは酸化窒化シリコンと、の界面にトラップセンターが形成される場合がある。該トラップセンターは、電子を捕獲することでトランジスタのしきい値電圧をプラス方向に変動させることができる場合がある。なお、比誘電率の高い絶縁体は、比誘電率が6以上、好ましくは8以上、さらに好ましくは12以上、より好ましくは20以上とする。

## 【0142】

絶縁体402は、基板400からの不純物の拡散を防止する役割を有してもよい。また、半導体406bが酸化物半導体である場合、絶縁体402は、半導体406bに酸素を供給する役割を担うことができる。

## 【0143】

導電体416aおよび導電体416bとしては、例えば、ホウ素、窒素、酸素、フッ素、シリコン、リン、アルミニウム、チタン、クロム、マンガン、コバルト、ニッケル、銅、亜鉛、ガリウム、イットリウム、ジルコニウム、モリブデン、ルテニウム、銀、インジウム、スズ、タンタルおよびタンクステンを一種以上含む導電体を、単層で、または積層で用いればよい。または、前述の元素を含む合金や化合物であってもよく、アルミニウムを含む導電体、銅およびチタンを含む導電体、銅およびマンガンを含む導電体、インジウム、スズおよび酸素を含む導電体、チタンおよび窒素を含む導電体などを用いてもよい。

## 【0144】

絶縁体412としては、例えば、ホウ素、炭素、窒素、酸素、フッ素、マグネシウム、アルミニウム、シリコン、リン、塩素、アルゴン、ガリウム、ゲルマニウム、イットリウム、ジルコニウム、ランタン、ネオジム、ハフニウムまたはタンタルを含む絶縁体を、単層で、または積層で用いればよい。例えば、絶縁体412としては、酸化アルミニウム、酸化マグネシウム、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニウム、酸化ランタン、酸化ネオジム、酸化ハフニウムまたは酸化タンタルを用いればよい。

## 【0145】

なお、絶縁体412は、比誘電率の高い絶縁体を有することが好ましい。例えば、絶縁体412は、酸化ガリウム、酸化ハフニウム、アルミニウムおよびハフニウムを有する酸化物、アルミニウムおよびハフニウムを有する酸化窒化物、シリコンおよびハフニウムを有する酸化物、シリコンおよびハフニウムを有する酸化窒化物などを有することが好ましい。または、絶縁体412は、酸化シリコンまたは酸化窒化シリコンと、比誘電率の高い絶縁体と、の積層構造を有することが好ましい。酸化シリコンおよび酸化窒化シリコンは、熱的に安定であるため、比誘電率の高い絶縁体と組み合わせることで、熱的に安定かつ比誘電率の高い積層構造とすることができます。例えば、酸化アルミニウム、酸化ガリウムまたは酸化ハフニウムを半導体406c側に有することで、酸化シリコンまたは酸化窒化シリコンに含まれるシリコンが、半導体406cまたは/および半導体406bに混入することを抑制することができる。また、例えば、酸化シリコンまたは酸化窒化シリコンを半

10

20

30

40

50

導体 406c 側に有することで、酸化アルミニウム、酸化ガリウムまたは酸化ハフニウムと、酸化シリコンまたは酸化窒化シリコンと、の界面にトラップセンターが形成される場合がある。該トラップセンターは、電子を捕獲することでトランジスタのしきい値電圧をプラス方向に変動させることができる場合がある。

【0146】

導電体 404 としては、例えば、ホウ素、窒素、酸素、フッ素、シリコン、リン、アルミニウム、チタン、クロム、マンガン、コバルト、ニッケル、銅、亜鉛、ガリウム、イットリウム、ジルコニウム、モリブデン、ルテニウム、銀、インジウム、スズ、タンタルおよびタンゲステンを一種以上含む導電体を、単層で、または積層で用いればよい。または、前述の元素を含む合金や化合物であってもよく、アルミニウムを含む導電体、銅およびチタンを含む導電体、銅およびマンガンを含む導電体、インジウム、スズおよび酸素を含む導電体、チタンおよび窒素を含む導電体などを用いてもよい。

10

【0147】

絶縁体 408 としては、例えば、ホウ素、炭素、窒素、酸素、フッ素、マグネシウム、アルミニウム、シリコン、リン、塩素、アルゴン、ガリウム、ゲルマニウム、イットリウム、ジルコニウム、ランタン、ネオジム、ハフニウムまたはタンタルを含む絶縁体を、単層で、または積層で用いればよい。例えば、絶縁体 408 としては、酸化アルミニウム、酸化マグネシウム、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニウム、酸化ランタン、酸化ネオジム、酸化ハフニウムまたは酸化タンタルを用いればよい。なお、絶縁体 408 は、酸化アルミニウムを有することが好ましい。例えば、絶縁体 408 が酸化アルミニウムを有することで、半導体 406b に水素などの不純物が混入することを抑制することができる。

20

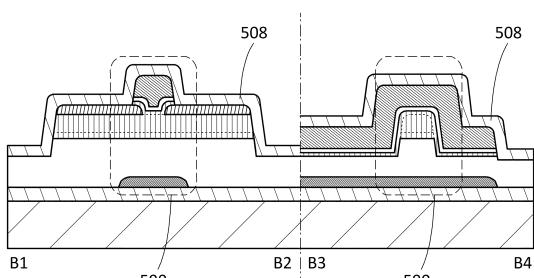

【0148】

<トランジスタ構造 1 の作製方法>

以下では、上述したトランジスタ 490 の作製方法について、図 2、図 3、図 4 および図 5 を用いて説明する。

【0149】

まず、基板 400 を準備する（図 5 ステップ S101 参照。）。

【0150】

30

次に、基板 400 上に絶縁体 401 を成膜する（図 5 ステップ S102 参照。）。なお、絶縁体 401 の成膜には、化学気相成長（CVD：Chemical Vapor Deposition）法または原子層堆積（ALD：Atomic Layer Deposition）法を用いると好ましい。特に、MOCVD 法を用いると好ましい。

【0151】

なお、CVD 法は、プラズマを利用するプラズマ CVD（PECVD：Plasma Enhanced CVD）法、熱を利用する熱 CVD（TCVD：Thermal CVD）法、光を利用する光 CVD（Photo CVD）法などに分類できる。さらに用いる原料ガスによって金属 CVD（MCVD：Metal CVD）法、有機金属 CVD（MOCVD：Metal Organic CVD）法に分けることができる。

40

【0152】

プラズマ CVD 法は、比較的低温で高品質の膜が得られる。また、熱 CVD 法は、プラズマを用いないため、被処理物へのプラズマダメージを小さくすることが可能な成膜方法である。例えば、半導体装置に含まれる配線、電極、素子（トランジスタ、容量素子など）などは、プラズマから電荷を受け取ることでチャージアップする場合がある。このとき、蓄積した電荷によって、半導体装置に含まれる配線、電極、素子などが破壊される場合がある。一方、プラズマを用いない熱 CVD 法の場合、こういったプラズマダメージが生じないため、半導体装置の歩留まりを高くすることができる。また、熱 CVD 法では、成膜中のプラズマダメージが生じないため、欠陥の少ない膜が得られる。

【0153】

50

また、ALD法も、被処理物へのプラズマダメージを小さくすることが可能な成膜方法である。また、ALD法も、成膜中のプラズマダメージが生じないため、欠陥の少ない膜が得られる。

【0154】

CVD法およびALD法は、ターゲットなどから放出される粒子が堆積する成膜方法とは異なり、被処理物の表面における反応により膜が形成される成膜方法である。したがって、被処理物の形状の影響を受けにくく、良好な段差被覆性を有する成膜方法である。特に、ALD法は、優れた段差被覆性と、優れた厚さの均一性を有するため、アスペクト比の高い開口部の表面を被覆する場合などに好適である。ただし、ALD法は、比較的成膜速度が遅いため、成膜速度の速いCVD法などの他の成膜方法と組み合わせて用いることが好ましい場合もある。

10

【0155】

CVD法およびALD法は、原料ガスの流量比によって、得られる膜の組成を制御することができる。例えば、CVD法およびALD法では、原料ガスの流量比によって、任意の組成の膜を成膜することができる。また、例えば、CVD法およびALD法では、成膜しながら原料ガスの流量比を変化させることによって、組成が連続的に変化した膜を成膜することができる。原料ガスの流量比を変化させながら成膜する場合、複数の成膜室を用いて成膜する場合と比べて、搬送や圧力調整に掛かる時間の分、成膜に掛かる時間を短くすることができる。したがって、トランジスタの生産性を高めることができる場合がある。MOCVD法を用いることが可能な成膜装置、およびALD法を用いることが可能な成膜装置の具体例については後述する。

20

【0156】

または、例えば、スパッタリング法、MBE法、PLD法、ALD法を用いてもよい場合もある。

【0157】

次に、絶縁体401上に導電体を成膜する（図5ステップS102参照。）。該導電体の成膜には、CVD法またはALD法を用いると好ましい。特に、MOCVD法を用いると好ましい。

【0158】

ここで、絶縁体401と導電体とを大気に暴露せずに、続けて成膜することが好ましい。こうすることで、界面に不純物が混入することを抑制することができる。

30

【0159】

半導体装置を作製するクリーンルームなどには、クリーンフィルターに起因した不純物（ホウ素など）が大気中に存在する場合がある。ホウ素に代表される大気中の不純物は、半導体の性質を変化させる要因となる。そのため、半導体装置内の意図せぬ箇所に不純物が混入することを抑制することは、半導体装置の電気特性を良好、かつ安定にするために好ましいことがわかる。

【0160】

なお、このように異なる膜を大気に暴露せずに続けて成膜することを、本明細書では連続成膜と呼ぶ。連続成膜する場合、同じ成膜方法または/および同じ成膜室を用いて成膜できる場合がある。異なる膜を、同じ成膜室で成膜することで、半導体装置の生産性を高くすることができる場合がある。ただし、連続成膜は、同じ成膜室で行う場合に限定されない。また、連続成膜は、同じ成膜方法を用いる場合に限定されない。即ち、上述した成膜方法のいずれかを組み合わせて連続成膜することも可能である。

40

【0161】

なお、ここでは絶縁体401と導電体とを連続成膜した例を示したが、これに限定されない。例えば、絶縁体401と導電体とを連続成膜しなくても構わない場合ある。

【0162】

次に、導電体を加工して導電体413を形成する（図2（A）および図5ステップS103参照。）。

50

## 【0163】

なお、本明細書において「加工する」とは、例えば、フォトリソグラフィ法によって形成したレジストマスクを用い、エッチング処理を行って、所望の形状を得ることをいう。

## 【0164】

ここで、レジストマスクの形成方法の一例を説明する。まず、レジストマスクとなる感光性を有する有機物または無機物の層を、スピンドルコート法などを用いて形成する。次に、フォトマスクを用いて、レジストマスクとなる層に光を照射する。当該光としては、KrFエキシマレーザ光、ArFエキシマレーザ光、EUV (Extreme Ultraviolet) 光などを用いればよい。また、基板と投影レンズとの間に液体（例えば水）を満たして露光する、液浸技術を用いてもよい。また、レジストマスクとなる層に照射する光に代えて、電子ビームやイオンビームを用いてもよい。なお、電子ビームやイオンビームを用いる場合には、フォトマスクは不要となる。次に、現像液を用いて、レジストマスクとなる層の露光された領域を、除去または残存させてレジストマスクを形成する。以上のようにして、レジストマスクを形成することができる。

10

## 【0165】

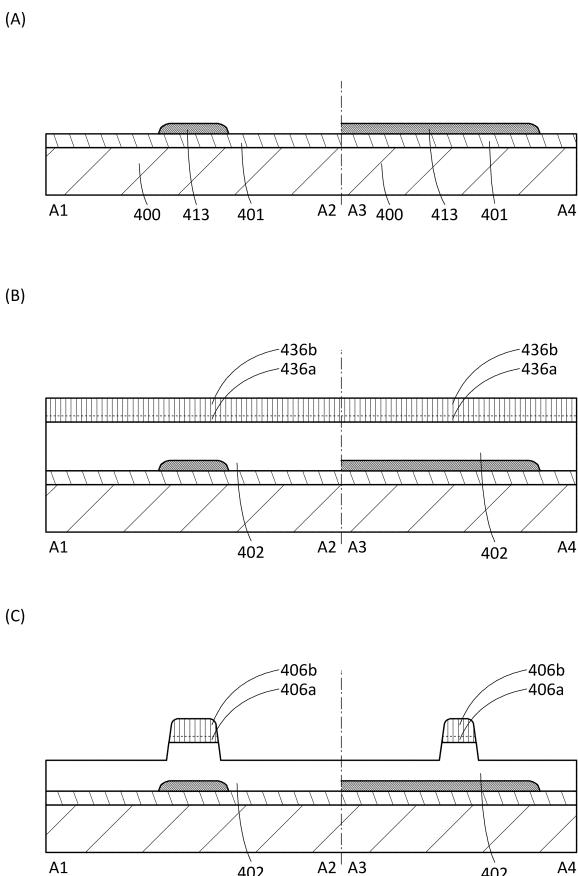

次に、絶縁体401上および導電体413上に、絶縁体402を成膜する（図5ステップS104参照。）。絶縁体402の成膜には、CVD法またはALD法を用いると好ましい。特に、PECVD法またはMOCVD法を用いると好ましい。

## 【0166】

次に、絶縁体402上に、半導体436aを成膜する（図5ステップS104参照。）。半導体436aの成膜には、CVD法またはALD法を用いると好ましい。特に、MOCVD法を用いると好ましい。このとき、反応ガスとして酸素、オゾンなどの酸化性ガスを用いることで、絶縁体402に過剰酸素を添加することができる場合がある。なお、半導体436aは、後に図1に示した半導体406aとなる半導体である。

20

## 【0167】

次に、半導体436a上に、半導体436bを成膜する（図2（B）および図5ステップS104参照。）。半導体436bの成膜には、CVD法またはALD法を用いると好ましい。特に、MOCVD法を用いると好ましい。このとき、反応ガスとして酸素、オゾンなどの酸化性ガスを用いることで、絶縁体402または/および半導体436aに過剰酸素を添加することができる場合がある。なお、半導体436bは、後に図1に示した半導体406bとなる半導体である。

30

## 【0168】

例えば、絶縁体402と半導体436aと半導体436bとを連続成膜することで、各界面に不純物が混入することを抑制することができる。即ち、絶縁体402と半導体436aと半導体436bとを連続成膜することで、各界面における界面準位密度を低くすることができる。また、これらの成膜に、ダメージの小さい成膜方法を用いることでも、各界面における界面準位密度を低くすることができる。したがって、各界面における界面準位密度を低くすることにより、トランジスタ490の電気特性を良好、かつ安定にすることができる。また、絶縁体402は、導電体413をゲート電極として用いた場合にゲート絶縁体として機能する。また、半導体436aもゲート絶縁体として機能する場合がある。

40

## 【0169】

次に、半導体436bを加工して半導体406bを形成する（図5ステップS105参照。）。

## 【0170】

次に、半導体436aを加工して半導体406aを形成する（図2（C）および図5ステップS105参照。）。

## 【0171】

なお、半導体436bと半導体436aとの加工は、同じ工程で行っても構わない。半導体436bと半導体436aとの加工を同じ工程で行うことで、半導体装置の生産性を高

50

くすることができる場合がある。

【0172】

なお、半導体436aの加工の際に、絶縁体402の一部をエッティングしても構わない。即ち、絶縁体402が、半導体406aおよび半導体406bと接する領域に凸部を有しても構わない(図2(C)参照。)。絶縁体402の一部が凸部を有することで、s-channel構造を実現しやすくなる場合がある。

【0173】

次に、第1の加熱処理を行うと好ましい(図5ステップS106参照。)。第1の加熱処理は、250以上650以下、好ましくは450以上600以下、さらに好ましくは520以上570以下で行えばよい。第1の加熱処理は、不活性ガス雰囲気、または酸化性ガスを10ppm以上、1%以上もしくは10%以上含む雰囲気で行う。第1の加熱処理は減圧状態で行ってもよい。または、第1の加熱処理は、不活性ガス雰囲気で加熱処理した後に、脱離した酸素を補うために酸化性ガスを10ppm以上、1%以上または10%以上含む雰囲気で加熱処理を行ってもよい。第1の加熱処理によって、半導体406aまたは/および半導体406bの結晶性を高めることや、水素や水などの不純物を除去することなどができる。なお、第1の加熱処理を、半導体436bを成膜した後、かつ半導体436bを加工する前に行っても構わない。なお、第1の加熱処理は、同等の加熱処理を各層の成膜時の加熱によって兼ねることができる場合、行わなくてもよい場合がある。

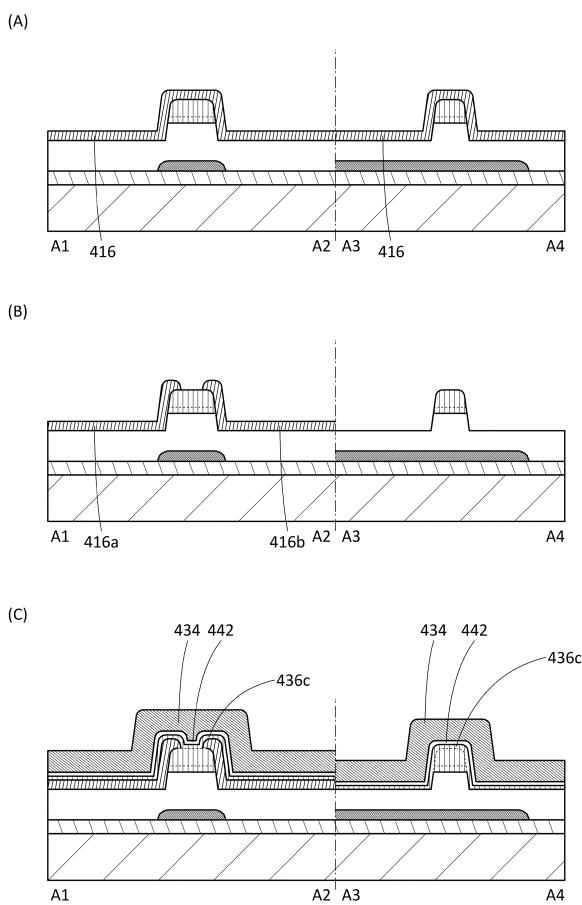

【0174】

次に、絶縁体402上および半導体406b上に、導電体416を成膜する(図3(A)および図5ステップS107参照。)。なお、導電体416は、後に図1に示した導電体416aおよび導電体416bとなる導電体である。

【0175】

導電体416の成膜には、CVD法またはALD法を用いると好ましい。特に、MCVD法を用いると好ましい。導電体416をCVD法またはALD法を用いて成膜することで、半導体406bへのダメージを小さくすることができる。そのため、ダメージによって半導体406bに低抵抗領域が形成されることを抑制することができる。また、導電体416と半導体406bとの混合層の形成を抑制することができる。

【0176】

次に、導電体416を加工して、導電体416aおよび導電体416bを形成する(図3(B)および図5ステップS108参照。)。

【0177】

次に、絶縁体402上、半導体406b上、導電体416a上および導電体416b上に、半導体436cを成膜する(図5ステップS109参照。)。半導体436cの成膜には、CVD法またはALD法を用いると好ましい。特に、MOCVD法を用いると好ましい。このとき、反応ガスとして酸素、オゾンなどの酸化性ガスを用いることで、絶縁体402、半導体406a、半導体406bのいずれか一以上に過剰酸素を添加することができる場合がある。なお、半導体436cは、後に図1に示した半導体406cとなる半導体である。

【0178】

次に、半導体436c上に、絶縁体442を成膜する(図5ステップS109参照。)。絶縁体442の成膜には、CVD法またはALD法を用いると好ましい。特に、MOCVD法を用いると好ましい。このとき、反応ガスとして酸素、オゾンなどの酸化性ガスを用いることで、絶縁体402、半導体406a、半導体406b、半導体436cのいずれか一以上に過剰酸素を添加することができる場合がある。なお、絶縁体442は、後に図1に示した絶縁体412となる絶縁体である。

【0179】

次に、絶縁体442上に、導電体434を成膜する(図3(C)および図5ステップS109参照。)。導電体434の成膜には、CVD法またはALD法を用いると好ましい。

10

20

30

40

50

特に、M C V D 法を用いると好ましい。なお、導電体 4 3 4 は、後に図 1 に示した導電体 4 0 4 となる導電体である。

【 0 1 8 0 】

ここで、半導体 4 3 6 c と絶縁体 4 4 2 と導電体 4 3 4 とを連続成膜することが好ましい。こうすることで、各界面に不純物が混入することを抑制することができる。即ち、半導体 4 3 6 c と絶縁体 4 4 2 と導電体 4 3 4 とを連続成膜することで、各界面における界面準位密度を低くすることができる。また、これらの成膜に、ダメージの小さい成膜方法を用いることでも、各界面における界面準位密度を低くすることができる。したがって、トランジスタ 4 9 0 の電気特性を良好、かつ安定にすることができる。また、後に絶縁体 4 1 2 となる絶縁体 4 4 2 は、後に導電体 4 0 4 となる導電体 4 3 4 をゲート電極として用いた場合にゲート絶縁体として機能する。また、半導体 4 3 6 c もゲート絶縁体として機能する場合がある。

【 0 1 8 1 】

次に、導電体 4 3 4 を加工して導電体 4 0 4 を形成する（図 5 ステップ S 1 1 0 参照。）。

。

【 0 1 8 2 】

次に、絶縁体 4 4 2 を加工して絶縁体 4 1 2 を形成する（図 5 ステップ S 1 1 1 参照。）。

。

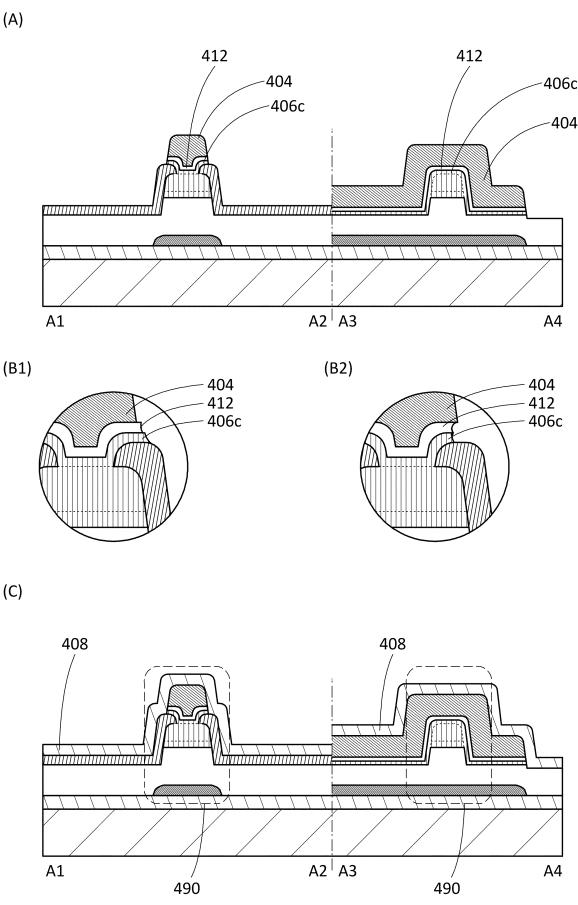

【 0 1 8 3 】

次に、半導体 4 3 6 c を加工して半導体 4 0 6 c を形成する（図 4 ( A ) および図 5 ステップ S 1 1 2 参照。）。

20

【 0 1 8 4 】

なお、導電体 4 3 4 と絶縁体 4 4 2 と半導体 4 3 6 c との加工は、同じ工程で行っても構わない。導電体 4 3 4 と絶縁体 4 4 2 と半導体 4 3 6 c との加工と同じ工程で行うことでの、半導体装置の生産性を高くすることができる場合がある。

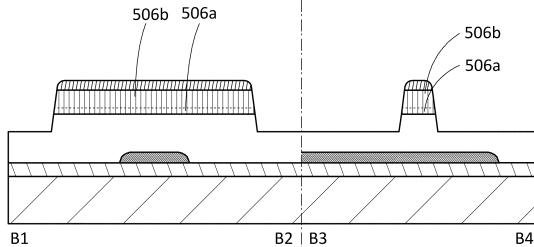

【 0 1 8 5 】

なお、絶縁体 4 1 2 、半導体 4 0 6 c 、導電体 4 0 4 の全部または一部を異なるフォトリソグラフィ工程で形成してもよい。その場合、図 4 ( B 1 ) に示す拡大断面のように、導電体 4 0 4 よりも絶縁体 4 1 2 または / および半導体 4 0 6 c が突出した（迫り出した）形状となる場合や、図 4 ( B 2 ) に示す拡大断面のように、導電体 4 0 4 が絶縁体 4 1 2 または / および半導体 4 0 6 c よりも突出した（迫り出した）形状となる場合がある。これらに示すような形状とすることによって、形状不良が低減され、ゲートリーコ電流を低減できる場合がある。

30

【 0 1 8 6 】

また、ここでは導電体 4 0 4 と絶縁体 4 1 2 と半導体 4 0 6 c とが、上面図において同様の形状となる例を示すが、これに限定されない。例えば、絶縁体 4 4 2 または / および半導体 4 3 6 c を加工せずに用いても構わない場合がある。

【 0 1 8 7 】

次に、絶縁体 4 0 2 上、導電体 4 1 6 a 上、導電体 4 1 6 b 上および導電体 4 0 4 上に、絶縁体 4 0 8 を成膜する（図 4 ( C ) および図 5 ステップ S 1 1 3 参照。）。絶縁体 4 0 8 の成膜には、C V D 法または A L D 法を用いると好ましい。特に、M O C V D 法を用いると好ましい。

40

【 0 1 8 8 】

以上のようにして、トランジスタ 4 9 0 を作製することができる。トランジスタ 4 9 0 は、各層の界面への不純物の混入が起こりにくく、かつ成膜に起因した各層へのダメージが小さいことにより、電気特性が良好で、かつ電気特性が安定なトランジスタとなる。

【 0 1 8 9 】

または、トランジスタ 4 9 0 は、図 6 に示すフローチャートによても作製することができる。

【 0 1 9 0 】

50

図6に示すフローチャートは、図5に示したフローチャートと比べて、半導体436aの成膜後に、半導体436aに酸素を添加する処理を行っている点が異なる（図6ステップS205参照。）。図6に示すステップS201乃至ステップS215の各ステップは、図5に示したステップS101乃至ステップS113の記載を適宜参照することができる。

#### 【0191】

半導体436aに酸素を添加する処理としては、例えば、イオン注入法、プラズマ処理法などがある。なお、半導体436aに添加された酸素は、過剰酸素となる。

#### 【0192】

イオン注入法では、原料ガスに酸素原子を含むガスを用い、被処理物に向けて加速電圧を印加することで行えればよい。なお、酸素原子を含むガスとしては、例えば、酸素ガス、オゾンガス、一酸化炭素ガス、二酸化炭素ガス、亜酸化窒素ガス、一酸化窒素ガス、二酸化窒素ガスなどを用いることができる。特に好ましくは酸素ガスを用いる。

#### 【0193】

イオン注入法は、質量分離したイオンを用いてもよいし、質量分離していないイオンを用いてもよい。質量分離したイオンを用いた場合、注入深さのばらつき、面内ばらつきなどを小さく注入することができる。例えば、質量分離して $O_2^+$ イオンを用いた場合、 $O^+$ イオンを用いた場合よりも、同じ加速電圧において浅い領域に注入することができる。したがって、半導体436aが薄い場合などは、質量分離して $O_2^+$ イオンを用いることが好ましい場合がある。また、不純物の混入も少なくすることができる。一方、質量分離していないイオンを用いた場合、高いドーズ量を短い時間で注入することができる。したがって、ドーズ量を多くしたい場合は、質量分離していないイオンを用いることが好ましい場合がある。

#### 【0194】

プラズマ処理法は、例えば、被処理物に高周波電力を印加することでプラズマを生成し、該プラズマ中の酸素含むイオンを自己バイアス電圧によって加速することで酸素を添加することができる。なお、誘導結合プラズマなどを用いても構わない。

#### 【0195】

なお、酸素を添加する処理は半導体436aのみでなく、絶縁体402に対して行っても構わない。例えば、半導体436aを介して絶縁体402に酸素を添加しても構わない。

#### 【0196】

半導体436aに酸素を添加する処理を行った後、半導体436a上に半導体436bを成膜する（図2（B）および図6ステップS206参照。）。

#### 【0197】

なお、半導体436aの成膜と、酸素を添加する処理と、半導体436bの成膜と、を大気に暴露せずに続けて行うと好ましい。こうすることで、界面に不純物が混入することを抑制することができる。

#### 【0198】

次に、半導体436bを加工して半導体406bを形成する（図6ステップS207参照。）。

#### 【0199】

次に、半導体436aを加工して半導体406aを形成する（図2（C）および図6ステップS207参照。）。

#### 【0200】

次に、第1の加熱処理を行うと好ましい（図6ステップS208参照。）。第1の加熱処理は、250以上650以下、好ましくは450以上600以下、さらに好ましくは520以上570以下で行えればよい。第1の加熱処理は、不活性ガス雰囲気、または酸化性ガスを10ppm以上、1%以上もしくは10%以上含む雰囲気で行う。第1の加熱処理は減圧状態で行ってもよい。または、第1の加熱処理は、不活性ガス雰囲気で加熱処理した後に、脱離した酸素を補うために酸化性ガスを10ppm以上、1%以上ま

10

20

30

40

50

たは 10 % 以上含む雰囲気で加熱処理を行ってもよい。第 1 の加熱処理によって、半導体 406a または / および半導体 406b の結晶性を高めることや、水素や水などの不純物を除去することなどができる。なお、第 1 の加熱処理を、半導体 436b を成膜した後、かつ半導体 436b を加工する前に行なって構わない。なお、第 1 の加熱処理は、同等の加熱処理を各層の成膜時の加熱によって兼ねることができる場合、行わなくてもよい場合がある。

【 0201 】

このとき、半導体 406a 中に酸素（過剰酸素）が含まれることにより、半導体 406b の酸素欠損を低減することができる場合がある。また、絶縁体 402 と比べて半導体 406a は半導体 406b に近い。そのため、半導体 406a が過剰酸素を含む場合のほうが、絶縁体 402 が過剰酸素を含む場合よりも、効果的に半導体 406b の酸素欠損を低減することができる。

【 0202 】

また、例えば、絶縁体 402 が酸化シリコンまたは酸化窒化シリコンである場合、加熱処理によって過剰酸素は広範囲に拡散する。一方、半導体 406a の場合、酸化シリコン、酸化窒化シリコンなどと比較して加熱処理によって過剰酸素が拡散する距離が短いため、第 1 の加熱処理の温度を高くすることができる。第 1 の加熱処理の温度を高くすることができるため、半導体 406a または / および半導体 406b に含まれる不純物を低減できる。また、さらに半導体 406a または / および半導体 406b の結晶性を高くすることができる場合がある。

【 0203 】

なお、本明細書において、酸化窒化物とは、窒素を 0.1 atomic % 以上 25 atomic % 未満含む酸化物をいう。なお、窒化酸化物とは、酸素を 0.1 atomic % 以上 25 atomic % 未満含む窒化物をいう。例えば、酸化窒化シリコンは酸化窒化物であり、窒化酸化シリコンは窒化酸化物である。

【 0204 】

または、トランジスタ 490 は、図 7 に示すフローチャートによっても作製することができる。

【 0205 】

図 7 に示すフローチャートは、図 5 に示したフローチャートと比べて、絶縁体 442 の成膜後に、第 2 の加熱処理を行っている点が異なる（図 7 ステップ S310 参照。）。図 7 に示すステップ S301 乃至ステップ S315 の各ステップは、図 5 に示したステップ S101 乃至ステップ S113 の記載を適宜参照することができる。

【 0206 】

絶縁体 442 の成膜後に第 2 の加熱処理を行うことで、絶縁体 402 または / および半導体 436a に含まれる過剰酸素が半導体 406b まで移動する。半導体 406b は半導体 436c で覆われているため、過剰酸素の外方拡散が起こりにくい。そのため、このタイミングで第 2 の加熱処理を行うことで、効率的に半導体 406b の欠陥（酸素欠損）を低減することができる。なお、第 2 の加熱処理は、絶縁体 402 または / および半導体 436a 中の過剰酸素（酸素）が半導体 406b まで拡散する温度で行なえばよい。例えば、第 1 の加熱処理についての記載を参考しても構わない。または、第 2 の加熱処理は、第 1 の加熱処理よりも低い温度が好ましい。第 1 の加熱処理と第 2 の加熱処理との温度差は、20 以上 150 以下、好ましくは 40 以上 100 以下とする。これにより、絶縁体 402 または / および半導体 436a から余分に過剰酸素（酸素）が放出することを抑えることができる。なお、第 2 の加熱処理は、同等の加熱処理を各層の成膜時の加熱によって兼ねることができる場合、行わなくてもよい場合がある。

【 0207 】

第 2 の加熱処理を行った後、絶縁体 442 上に導電体 434 を成膜する（図 3 (C) および図 7 ステップ S311 参照。）。

【 0208 】

10

20

30

40

50

なお、絶縁体 442 の成膜と、第 2 の加熱処理と、導電体 434 の成膜と、を大気に暴露せずに続けて行うと好ましい。こうすることで、界面に不純物が混入することを抑制することができる。

**【0209】**

次に、導電体 434 を加工して導電体 404 を形成する（図 7 ステップ S312 参照。）。

**【0210】**

次に、絶縁体 442 を加工して絶縁体 412 を形成する（図 7 ステップ S313 参照。）。

**【0211】**

次に、半導体 436c を加工して半導体 406c を形成する（図 4 (A) および図 7 ステップ S314 参照。）。

10

**【0212】**

なお、図 5、図 6 および図 7 に示したトランジスタ 490 の作製方法は、組み合わせても構わない。例えば、図 6 に示した酸素を添加する処理を、図 7 に示した作製方法に組み合わせても構わない。

**【0213】**

<トランジスタ構造 2>

以下に、図 1 などに示したトランジスタ 490 と異なるトランジスタの例を示す。

**【0214】**

図 1 などではソース電極およびドレイン電極として機能する導電体 416a および導電体 416b が、半導体 406b の上面および側面、絶縁体 402 の上面などと接する例を示したが、本発明の一態様に係るトランジスタの構造はこれに限定されない。

20

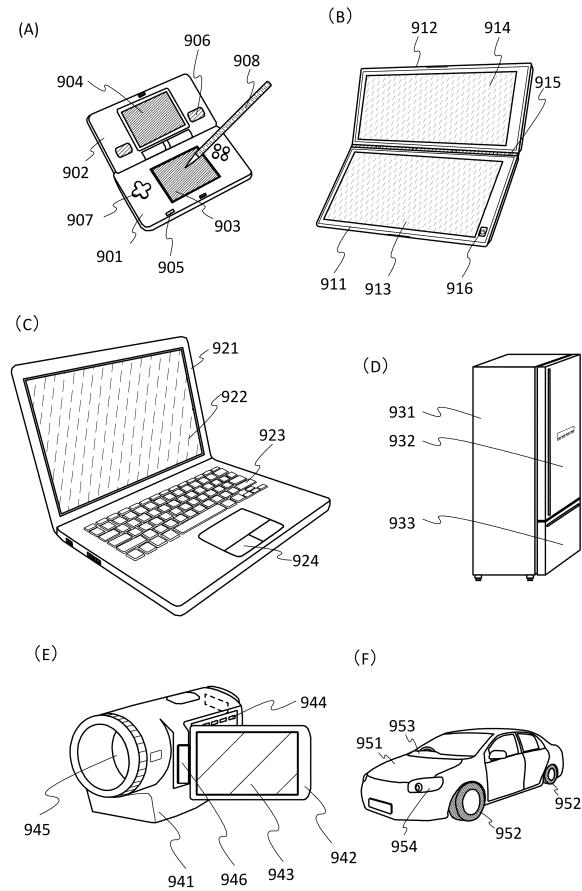

**【0215】**

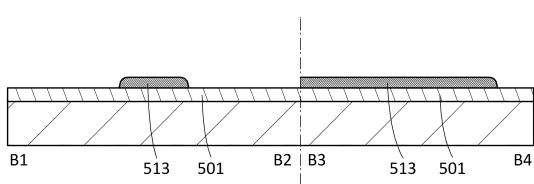

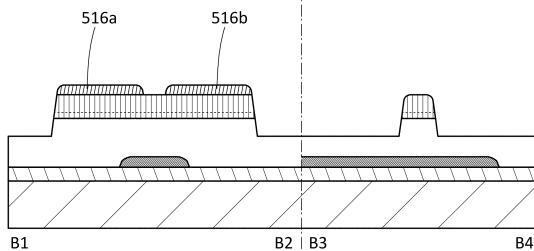

図 8 (A) は、トランジスタ 590 の上面図の一例である。図 8 (A) の一点鎖線 B1 - B2 および一点鎖線 B3 - B4 に対応する断面図の一例を図 8 (B) に示す。なお、図 8 (A) では、理解を容易にするため、絶縁体などの一部を省略して示す。

**【0216】**

なお、基板 500 は基板 400 についての記載を参照する。また、絶縁体 501 は絶縁体 401 についての記載を参照する。また、導電体 513 は導電体 413 についての記載を参照する。また、絶縁体 502 は絶縁体 402 についての記載を参照する。また、半導体 506a は、半導体 406a についての記載を参照する。また、半導体 506b は、半導体 406b についての記載を参照する。また、導電体 516a および導電体 516b は導電体 416a および導電体 416b についての記載を参照する。また、半導体 506c は、半導体 406c についての記載を参照する。また、絶縁体 512 は絶縁体 412 についての記載を参照する。また、導電体 504 は導電体 404 についての記載を参照する。また、絶縁体 508 は絶縁体 408 についての記載を参照する。

30

**【0217】**

図 8 に示すトランジスタは、導電体 516a および導電体 516b は、半導体 506b の側面と接しない。したがって、第 1 のゲート電極として機能する導電体 504 から半導体 506b の側面に向けて印加される電界が、導電体 516a および導電体 516b によって遮蔽されにくい構造である。また、導電体 516a および導電体 516b は、絶縁体 502 の上面と接しない。そのため、絶縁体 502 から放出される過剰酸素（酸素）が導電体 516a および導電体 516b を酸化させるために消費されない。したがって、絶縁体 502 から放出される過剰酸素（酸素）を、半導体 506b の酸素欠損を低減するために効率的に利用することのできる構造である。即ち、図 8 に示す構造のトランジスタは、高いオン電流、高い電界効果移動度、低いサブスレッショルドスイング値、高い信頼性などを有する優れた電気特性のトランジスタである。

40

**【0218】**

<トランジスタ構造 2 の作製方法>

50

以下では、上述したトランジスタ 590 の作製方法について、図 9、図 10、図 11 および図 12 を用いて説明する。

【0219】

まず、基板 500 を準備する（図 12 ステップ S401 参照。）。

【0220】

次に、基板 500 上に絶縁体 501 を成膜する（図 12 ステップ S402 参照。）。なお、絶縁体 501 の成膜には、CVD 法または ALD 法を用いると好ましい。特に、MOCVD 法を用いると好ましい。

【0221】

次に、絶縁体 501 上に導電体を成膜する（図 12 ステップ S402 参照。）。該導電体の成膜には、CVD 法または ALD 法を用いると好ましい。特に、MCVD 法を用いると好ましい。10

【0222】

ここで、絶縁体 501 と導電体とを大気に暴露せずに、続けて成膜することが好ましい。こうすることで、界面に不純物が混入することを抑制することができる。

【0223】

なお、ここでは絶縁体 501 と導電体とを連続成膜した例を示したが、これに限定されない。例えば、絶縁体 501 と導電体とを連続成膜しなくても構わない場合ある。

【0224】

次に、導電体を加工して導電体 513 を形成する（図 9 (A) および図 12 ステップ S403 参照。）。

【0225】

次に、絶縁体 501 上および導電体 513 上に、絶縁体 502 を成膜する（図 12 ステップ S404 参照。）。絶縁体 502 の成膜には、CVD 法または ALD 法を用いると好ましい。特に、PECVD 法または MOCVD 法を用いると好ましい。

【0226】

次に、絶縁体 502 上に、半導体 536a を成膜する（図 12 ステップ S404 参照。）。半導体 536a の成膜には、CVD 法または ALD 法を用いると好ましい。特に、MOCVD 法を用いると好ましい。このとき、反応ガスとして酸素、オゾンなどの酸化性ガスを用いることで、絶縁体 502 に過剰酸素を添加することができる場合がある。なお、半導体 536a は、後に図 8 に示した半導体 506a となる半導体である。30

【0227】

次に、半導体 536a 上に、半導体 536b を成膜する（図 12 ステップ S404 参照。）。半導体 536b の成膜には、CVD 法または ALD 法を用いると好ましい。特に、MOCVD 法を用いると好ましい。このとき、反応ガスとして酸素、オゾンなどの酸化性ガスを用いることで、絶縁体 502 または / および半導体 536a に過剰酸素を添加することができる場合がある。なお、半導体 536b は、後に図 8 に示した半導体 506b となる半導体である。

【0228】

次に、半導体 536b 上に、導電体 516 を成膜する（図 9 (B) および図 12 ステップ S404 参照。）。なお、導電体 516 は、後に図 8 に示した導電体 516a および導電体 516b となる導電体である。40

【0229】

導電体 516 の成膜には、CVD 法または ALD 法を用いると好ましい。特に、MCVD 法を用いると好ましい。導電体 516 を CVD 法または ALD 法を用いて成膜することで、半導体 536b へのダメージを小さくすることができる。そのため、ダメージによって半導体 536b に低抵抗領域が形成されることを抑制することができる。また、導電体 516 と半導体 536b との混合層の形成を抑制することができる。

【0230】

例えば、絶縁体 502 と半導体 536a と半導体 536b と導電体 516 とを連続成膜す50

ることで、各界面に不純物が混入することを抑制することができる。即ち、絶縁体 502 と半導体 536a と半導体 536b と導電体 516 を連続成膜することで、各界面における界面準位密度を低くすることができる。また、これらの成膜に、ダメージの小さい成膜方法を用いることでも、各界面における界面準位密度を低くすることができる。したがって、トランジスタ 590 の電気特性を良好、かつ安定にすることができる。また、絶縁体 502 は、導電体 513 をゲート電極として用いた場合にゲート絶縁体として機能する。また、半導体 536a もゲート絶縁体として機能する場合がある。

#### 【0231】

次に、導電体 516 を加工して導電体 517 を形成する（図 9（C）および図 12 ステップ S405 参照。）。導電体 517 は、ハードマスクとしての機能を有する。

10

#### 【0232】

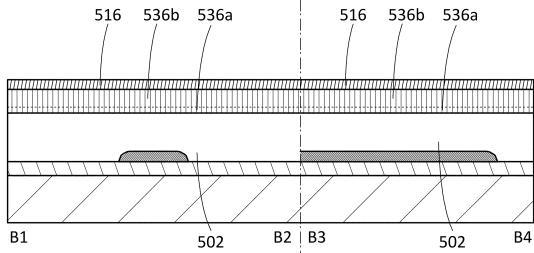

次に、半導体 536b を加工して半導体 506b を形成する（図 12 ステップ S406 参照。）。

#### 【0233】

次に、半導体 536a を加工して半導体 506a を形成する（図 10（A）および図 12 ステップ S406 参照。）。

#### 【0234】

なお、導電体 516 と半導体 536b と半導体 536a との加工の少なくとも一部は、同じ工程で行っても構わない。導電体 516 と半導体 536b と半導体 536a との加工の少なくとも一部を同じ工程で行うことで、半導体装置の生産性を高くすることができる場合がある。

20

#### 【0235】

なお、半導体 536a の加工の際に、絶縁体 502 の一部をエッティングしても構わない。即ち、絶縁体 502 が、半導体 506a および半導体 506b と接する領域に凸部を有しても構わない（図 10（C）参照。）。絶縁体 502 の一部が凸部を有することで、s-channel 構造を実現しやすくなる場合がある。

#### 【0236】

次に、導電体 517 を加工して、導電体 516a および導電体 516b を形成する（図 10（B）および図 12 ステップ S407 参照。）。

#### 【0237】

30

次に、絶縁体 502 上、半導体 506b 上、導電体 516a 上および導電体 516b 上に、半導体 536c を成膜する（図 12 ステップ S408 参照。）。半導体 536c の成膜には、CVD 法または ALD 法を用いると好ましい。特に、MOCVD 法を用いると好ましい。このとき、反応ガスとして酸素、オゾンなどの酸化性ガスを用いることで、絶縁体 502、半導体 506a、半導体 506b のいずれか一以上に過剰酸素を添加することができる場合がある。なお、半導体 536c は、後に図 8 に示した半導体 506c となる半導体である。

#### 【0238】

次に、半導体 536c 上に、絶縁体 542 を成膜する（図 12 ステップ S408 参照。）。絶縁体 542 の成膜には、CVD 法または ALD 法を用いると好ましい。特に、MOCVD 法を用いると好ましい。このとき、反応ガスとして酸素、オゾンなどの酸化性ガスを用いることで、絶縁体 502、半導体 506a、半導体 506b、半導体 536c のいずれか一以上に過剰酸素を添加することができる場合がある。なお、絶縁体 542 は、後に図 8 に示した絶縁体 512 となる絶縁体である。

40

#### 【0239】

次に、絶縁体 542 上に、導電体 534 を成膜する（図 10（C）および図 12 ステップ S408 参照。）。導電体 534 の成膜には、CVD 法または ALD 法を用いると好ましい。特に、MCVD 法を用いると好ましい。なお、導電体 534 は、後に図 8 に示した導電体 504 となる導電体である。

#### 【0240】

50

ここで、半導体 536c と絶縁体 542 と導電体 534 とを連続成膜することが好ましい。こうすることで、各界面に不純物が混入することを抑制することができる。即ち、半導体 536c と絶縁体 542 と導電体 534 とを連続成膜することで、各界面における界面準位密度を低くすることができる。また、これらの成膜に、ダメージの小さい成膜方法を用いることでも、各界面における界面準位密度を低くすることができる。したがって、トランジスタ 590 の電気特性を良好、かつ安定にすることができる。また、後に絶縁体 512 となる絶縁体 542 は、後に導電体 504 となる導電体 534 をゲート電極として用いた場合にゲート絶縁体として機能する。また、半導体 536c もゲート絶縁体として機能する場合がある。

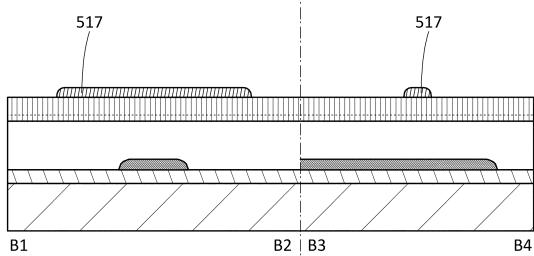

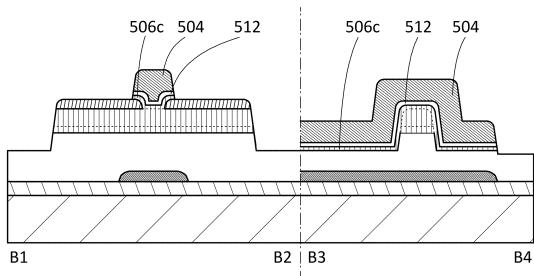

## 【0241】

10

次に、導電体 534 を加工して導電体 504 を形成する（図 12 ステップ S409 参照。）。

## 【0242】

次に、絶縁体 542 を加工して絶縁体 512 を形成する（図 12 ステップ S410 参照。）。

## 【0243】

次に、半導体 536c を加工して半導体 506c を形成する（図 11 (A) および図 12 ステップ S411 参照。）。

## 【0244】

20

なお、導電体 534 と絶縁体 542 と半導体 536c との加工は、同じ工程で行っても構わない。導電体 534 と絶縁体 542 と半導体 536c との加工と同じ工程で行うことでの半導体装置の生産性を高くすることができる場合がある。

## 【0245】

なお、絶縁体 512、半導体 506c、導電体 504 の全部または一部を異なるフォトリソグラフィ工程で形成してもよい。その場合、導電体 504 よりも絶縁体 512 または／および半導体 506c が突出した（迫り出した）形状となる場合や、導電体 504 が絶縁体 512 または／および半導体 506c よりも突出した（迫り出した）形状となる場合がある。これらに示すような形状とすることによって、形状不良が低減され、ゲートリーク電流を低減できる場合がある。

## 【0246】

30

また、ここでは導電体 504 と絶縁体 512 と半導体 506c とが、上面図において同様の形状となる例を示すが、これに限定されない。例えば、絶縁体 542 または／および半導体 536c を加工せずに用いても構わない場合がある。

## 【0247】

次に、絶縁体 502 上、導電体 516a 上、導電体 516b 上および導電体 504 上に、絶縁体 508 を成膜する（図 11 (B) および図 12 ステップ S412 参照。）。絶縁体 508 の成膜には、CVD 法または ALD 法を用いると好ましい。特に、MOCVD 法を用いると好ましい。

## 【0248】

40

以上のようにして、トランジスタ 590 を作製することができる。トランジスタ 590 は、各層の界面への不純物の混入が起こりにくく、かつ成膜に起因した各層へのダメージが小さいことにより、電気特性が良好で、かつ電気特性が安定なトランジスタとなる。

## 【0249】

または、トランジスタ 590 は、図 13 に示すフローチャートによっても作製することができる。

## 【0250】

図 13 に示すフローチャートは、図 12 に示したフローチャートと比べて、半導体 536a の成膜後に、半導体 536a に酸素を添加する処理を行っている点が異なる（図 13 ステップ S505 参照。）。図 13 に示すステップ S501 乃至ステップ S515 の各ステップは、図 12 に示したステップ S401 乃至ステップ S413 の記載を適宜参照するこ

50

とができる。

【0251】

半導体536aに酸素を添加する処理としては、例えば、イオン注入法、プラズマ処理法などがある。なお、半導体536aに添加された酸素は、過剰酸素となる。半導体536aに酸素を添加する処理は、半導体436aに酸素を添加する処理についての記載を参照する。

【0252】

なお、酸素を添加する処理は半導体536aのみでなく、絶縁体502に対して行っても構わない。例えば、半導体536aを介して絶縁体502に酸素を添加しても構わない。

【0253】

半導体536aに酸素を添加する処理を行った後、半導体536a上に半導体536bを成膜する(図13ステップS506参照。)。

【0254】

なお、半導体536aの成膜と、酸素を添加する処理と、半導体536bの成膜と、を大気に暴露せずに続けて行うと好ましい。こうすることで、界面に不純物が混入することを抑制することができる。

【0255】

次に、半導体536b上に、導電体516を成膜する(図13ステップS506参照。)

。

【0256】

半導体536bと導電体516とを連続成膜することで、界面に不純物が混入することを抑制することができる。即ち、半導体536bと導電体516とを連続成膜することで、界面における界面準位密度を低くすることができる。また、これらの成膜に、ダメージの小さい成膜方法を用いることでも、各界面における界面準位密度を低くすることができる。

。

【0257】

または、トランジスタ590は、図14に示すフローチャートによっても作製することができる。

【0258】

図14に示すフローチャートは、図12に示したフローチャートと比べて、半導体536bの成膜後に第1の加熱処理を行っている点、および絶縁体542の成膜後に第2の加熱処理を行っている点が異なる(図14ステップS605および図14ステップS611参照。)。図14に示すステップS601乃至ステップS615の各ステップは、図12に示したステップS401乃至ステップS413の記載を適宜参照することができる。

【0259】

第1の加熱処理は、250以上650以下、好ましくは450以上600以下、さらに好ましくは520以上570以下で行えばよい。第1の加熱処理は、不活性ガス雰囲気、または酸化性ガスを10ppm以上、1%以上もしくは10%以上含む雰囲気で行う。第1の加熱処理は減圧状態で行ってもよい。または、第1の加熱処理は、不活性ガス雰囲気で加熱処理した後に、脱離した酸素を補うために酸化性ガスを10ppm以上、1%以上または10%以上含む雰囲気で加熱処理を行ってもよい。第1の加熱処理によって、半導体536aまたは/および半導体536bの結晶性を高めることや、水素や水などの不純物を除去することなどができる。なお、第1の加熱処理は、同等の加熱処理を各層の成膜時の加熱によって兼ねることができる場合、行わなくてもよい場合がある。

【0260】

第1の加熱処理を行った後、半導体536上に導電体516を成膜する(図9(B)および図14ステップS606)

【0261】

絶縁体542の成膜後に第2の加熱処理を行うことで、絶縁体502または/および半導体536aに含まれる過剰酸素が半導体506bまで移動する。半導体506bは半導体

10

20

30

40

50

536cで覆われているため、過剰酸素の外方拡散が起こりにくい。そのため、このタイミングで第2の加熱処理を行うことで、効率的に半導体506bの欠陥(酸素欠損)を低減することができる。なお、第2の加熱処理は、絶縁体502または/および半導体536a中の過剰酸素(酸素)が半導体506bまで拡散する温度で行えばよい。例えば、第1の加熱処理についての記載を参照しても構わない。または、第2の加熱処理は、第1の加熱処理よりも低い温度が好ましい。第1の加熱処理と第2の加熱処理との温度差は、20以上150以下、好ましくは40以上100以下とする。これにより、絶縁体502から余分に過剰酸素(酸素)が放出することを抑えることができる。なお、第2の加熱処理は、同等の加熱処理を各層の成膜時の加熱によって兼ねることができる場合、行わなくてよい場合がある。

10

**【0262】**

第2の加熱処理を行った後、絶縁体542上に導電体534を成膜する(図10(C)および図14ステップS612参照。)。

**【0263】**

なお、絶縁体542の成膜と、第2の加熱処理と、導電体534の成膜と、を大気に暴露せずに続けて行うと好ましい。こうすることで、界面に不純物が混入することを抑制することができる。

**【0264】**

次に、導電体534を加工して導電体504を形成する(図14ステップS613参照。)。

20

**【0265】**

次に、絶縁体542を加工して絶縁体512を形成する(図14ステップS614参照。)。

**【0266】**

次に、半導体536cを加工して半導体506cを形成する(図11(A)および図14ステップS615参照。)。

**【0267】**

なお、図12、図13および図14に示したトランジスタ590の作製方法は、組み合わせても構わない。例えば、図13に示した酸素を添加する処理を、図14に示した作製方法に組み合わせても構わない。

30

**【0268】**

**<成膜装置>**

以下では、本発明の一態様に係る半導体装置を製造する際に用いることが可能な、成膜装置の一例について説明する。

**【0269】**

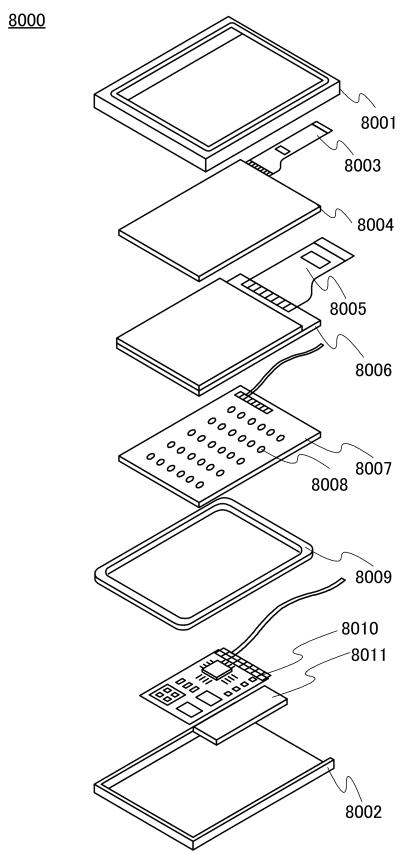

図15(A)に示す成膜装置を含む製造装置は、ロード室702、搬送室710、処理室703、処理室705、処理室731、アンロード室706を少なくとも有する。また、図15(A)に示す製造装置は、大気に触れることなく、連続的に成膜を行うことができる。そのため、積層膜を成膜する場合、膜中および膜の界面へ不純物の混入を防止することができる。なお、製造装置のチャンバー(ロード室、処理室、搬送室、成膜室、アンロード室などを含む)は、チャンバー内壁への水分の付着などを防ぐため、露点が-60未満、好ましくは-80未満、さらに好ましくは-100未満の不活性ガス(窒素ガス、希ガスなど)を充填させておくことが好ましい。または、圧力を1Pa未満、好ましくは0.1Pa未満、さらに好ましくは $1 \times 10^{-4}$ Pa未満の減圧状態とする。

40

**【0270】**

また、処理室704、処理室705、処理室731の少なくともいずれかを、CVD法を利用する成膜室、またはALD法を利用する成膜室としてもよい。または、処理室704、処理室705、処理室731の少なくともいずれかを、イオン注入法を利用する処理室、プラズマ処理法を利用する処理室としてもよい。または、処理室704、処理室705、処理室731の少なくともいずれかを、加熱処理室としてもよい。

50

## 【0271】

例えば、処理室731にて半導体を成膜し、処理室704にて絶縁体を成膜し、処理室705にて導電体を成膜してもよい。その場合、それらの積層膜を大気に触れることなく、連続的に成膜することができる。

## 【0272】

まず、基板720をロード室702に搬入する。次に、搬送室710の搬送ユニット707によって基板を処理室703に搬送する。処理室703では、基板表面を洗浄する処理や加熱処理を行う。次に、基板を処理室731に搬送して半導体を成膜する。処理室703で処理されることによって、基板表面を清浄化することができる。また、基板表面の処理から半導体の成膜までの間に大気に触れないため、不純物などが基板表面に付着することを抑制できる。10

## 【0273】

次に、搬送ユニット707によって基板を処理室704に搬送して酸化ハフニウムなどの絶縁体を成膜する。次に、搬送ユニット707によって基板を処理室705に搬送してタンゲステンなどの導電体を成膜する。次に、搬送ユニット707によって基板をアンロード室706に搬送する。以上の手順により、半導体、絶縁体および導電体を順に積層することができる。

## 【0274】

または、例えば、処理室731にて半導体を成膜し、処理室704にて酸素を添加する処理を行い、処理室705にて半導体を成膜してもよい。または、例えば、処理室731にて半導体を成膜し、処理室704にて加熱処理を行い、処理室705にて導電体を成膜してもよい。20

## 【0275】

図15(B)に熱CVD装置の一例を示す。熱CVD装置は、基板の搬入されたチャンバーに原料ガス(一種または複数種)、酸化剤( $O_2$ 、 $O_3$ など)などを同時に供給し、基板近傍または基板表面で反応させ、生成物を堆積させることで成膜を行う。

## 【0276】

熱CVD装置の処理室731は、基板ホルダ719と、複数の原料ガスの導入口の接続された部材721と、排気装置718とを少なくとも有する。原料ガスの導入口には、それぞれ供給管、圧力調整器、バルブ、マスフローコントローラ(マスフローコントローラ722、マスフローコントローラ724、マスフローコントローラ726、マスフローコントローラ728)を介して原料供給部(原料供給部723、原料供給部725、原料供給部727、原料供給部729)と接続されており、排出口は、排出管やバルブや圧力調整器を介して排気装置718と接続されている。30

## 【0277】

成膜時の処理室731内は大気圧としてもよいし、減圧としてもよい。

## 【0278】

また、原料ガスを供給する際には、シャワーヘッドのような複数の開口部から原料ガスを供給してもよい。

## 【0279】

また、基板面内における膜の厚さを均一にするため、基板ホルダ719を回転させ、基板ホルダ719に固定されている基板720を回転させてもよい。40

## 【0280】

なお、熱CVD法は、プラズマを用いないため、プラズマに起因して膜に欠陥が生成されることがない。

## 【0281】

熱CVD法によって、金属、半導体、絶縁体など様々な膜を形成することができる。例えば、In-Ga-Zn酸化物を成膜する場合には、原料ガスとして、トリメチルインジウム( $(CH_3)_3In$ )、トリメチルガリウム( $(CH_3)_3Ga$ )、およびジメチル亜鉛( $(CH_3)_2Zn$ )などを用いる。ただし、In-Ga-Zn酸化物の原料ガスは、50

これらの組み合わせに限定されない。例えば、トリメチルガリウムに代えてトリエチルガリウム( $(C_2H_5)_3Ga$ )を用いることもでき、ジメチル亜鉛に代えてジエチル亜鉛( $(C_2H_5)_2Zn$ )を用いることもできる。また、例えば、酸化ガリウムを成膜する場合には、原料ガスとして、トリメチルガリウムまたはトリエチルガリウムを用いればよい。

【0282】

また、図15(A)では搬送室710の上面形状が六角形であるマルチチャンバーの製造装置の例を示しているが、それより角の多い多角形(七角形、八角形など)としてより多くのチャンバーと連結させてもよい。または、搬送室710の上面形状が五角形または四角形であるマルチチャンバーの製造装置であってもよい。また、チャンバーを複数連結することで搬送室を省略した、インライン製造装置としてもよい。インライン製造装置は、搬送室が少ないとにより、搬送の時間が短くできるため、生産性の高い製造装置である。なお、図15(A)では枚葉式の製造装置の例を示したが、複数枚の基板を一度に成膜するバッチ式の成膜装置としてもよい。また、各処理室にクリーニング(例えばプラズマクリーニングなど)を行うための機構を有してもよい。

【0283】

また、図15(B)においては、処理室704、処理室705および処理室731に熱CVD装置を用いる例を示したが、いずれか一を、スパッタリング法を利用した成膜室やALD法を利用した成膜室など、そのほかの成膜法を利用した成膜室としてもよい。

【0284】

<半導体装置>

以下では、本発明の一態様に係る半導体装置を例示する。

【0285】

<回路>

以下では、本発明の一態様に係るトランジスタを利用した回路の一例について説明する。

【0286】

[CMOSインバータ]

図16(A)に示す回路図は、pチャネル型のトランジスタ2200とnチャネル型のトランジスタ2100を直列に接続し、かつそれぞれのゲートを接続した、いわゆるCMOSインバータの構成を示している。

【0287】

[CMOSアナログスイッチ]

また図16(B)に示す回路図は、トランジスタ2100とトランジスタ2200のそれぞれのソースとドレインを接続した構成を示している。このような構成とすることで、いわゆるCMOSアナログスイッチとして機能させることができる。

【0288】

[記憶装置の例]

本発明の一態様に係るトランジスタを用いた、電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い半導体装置(記憶装置)の一例を図17に示す。

【0289】

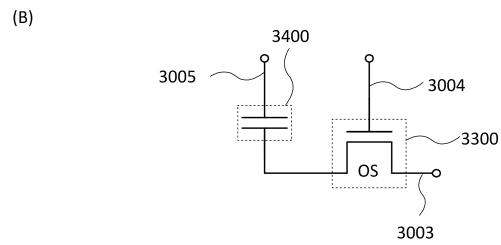

図17(A)に示す半導体装置は、第1の半導体を用いたトランジスタ3200と第2の半導体を用いたトランジスタ3300、および容量素子3400を有している。なお、トランジスタ3300としては、上述したトランジスタを用いることができる。

【0290】

トランジスタ3300は、酸化物半導体を用いたトランジスタである。トランジスタ3300のオフ電流が小さいことにより、半導体装置の特定のノードに長期にわたり記憶内容を保持することができる。つまり、リフレッシュ動作を必要としない、またはリフレッシュ動作の頻度が極めて少なくすることが可能となるため、消費電力の低い半導体装置となる。

10

20

30

40

50

## 【0291】

図17(A)において、第1の配線3001はトランジスタ3200のソースと電気的に接続され、第2の配線3002はトランジスタ3200のドレインと電気的に接続される。また、第3の配線3003はトランジスタ3300のソース、ドレインの一方と電気的に接続され、第4の配線3004はトランジスタ3300のゲートと電気的に接続されている。そして、トランジスタ3200のゲート、およびトランジスタ3300のソース、ドレインの他方は、容量素子3400の電極の一方と電気的に接続され、第5の配線3005は容量素子3400の電極の他方と電気的に接続されている。

## 【0292】

図17(A)に示す半導体装置は、トランジスタ3200のゲートの電位が保持可能という特性を有することで、以下に示すように、情報の書き込み、保持、読み出しが可能である。

10

## 【0293】

情報の書き込みおよび保持について説明する。まず、第4の配線3004の電位を、トランジスタ3300が導通状態となる電位にして、トランジスタ3300を導通状態とする。これにより、第3の配線3003の電位が、トランジスタ3200のゲート、および容量素子3400の電極の一方と電気的に接続するノードFGに与えられる。即ち、トランジスタ3200のゲートには、所定の電荷が与えられる(書き込み)。ここでは、異なる二つの電位レベルを与える電荷(以下Lowレベル電荷、Highレベル電荷という。)のどちらかが与えられるものとする。その後、第4の配線3004の電位を、トランジスタ3300が非導通状態となる電位にして、トランジスタ3300を非導通状態とすることにより、ノードFGに電荷が保持される(保持)。

20

## 【0294】

トランジスタ3300のオフ電流は極めて小さいため、ノードFGの電荷は長期間にわたって保持される。

## 【0295】

次に情報の読み出しについて説明する。第1の配線3001に所定の電位(定電位)を与えた状態で、第5の配線3005に適切な電位(読み出し電位)を与えると、第2の配線3002は、ノードFGに保持された電荷量に応じた電位をとる。これは、トランジスタ3200をnチャネル型とすると、トランジスタ3200のゲートにHighレベル電荷が与えられている場合の見かけ上のしきい値電圧 $V_{th\_H}$ は、トランジスタ3200のゲートにLowレベル電荷が与えられている場合の見かけ上のしきい値電圧 $V_{th\_L}$ より低くなるためである。ここで、見かけ上のしきい値電圧とは、トランジスタ3200を「導通状態」とするために必要な第5の配線3005の電位をいうものとする。したがって、第5の配線3005の電位を $V_{th\_H}$ と $V_{th\_L}$ の間の電位 $V_0$ とすることにより、ノードFGに与えられた電荷を判別できる。例えば、書き込みにおいて、ノードFGにHighレベル電荷が与えられていた場合には、第5の配線3005の電位が $V_0$ ( $> V_{th\_H}$ )となれば、トランジスタ3200は「導通状態」となる。一方、ノードFGにLowレベル電荷が与えられていた場合には、第5の配線3005の電位が $V_0$ ( $< V_{th\_L}$ )となっても、トランジスタ3200は「非導通状態」のままである。このため、第2の配線3002の電位を判別することで、ノードFGに保持されている情報を読み出すことができる。

30

## 【0296】

なお、メモリセルをアレイ状に配置する場合、読み出し時には、所望のメモリセルの情報を読み出さなくてはならない。ほかのメモリセルの情報を読み出さないためには、ノードFGに与えられた電荷によらずトランジスタ3200が「非導通状態」となるような電位、つまり、 $V_{th\_H}$ より低い電位を第5の配線3005に与えればよい。または、ノードFGに与えられた電荷によらずトランジスタ3200が「導通状態」となるような電位、つまり、 $V_{th\_L}$ より高い電位を第5の配線3005に与えればよい。

40

## 【0297】

50

図17(B)に示す半導体装置は、トランジスタ3200を有さない点で図17(A)に示した半導体装置と異なる。この場合も図17(A)に示した半導体装置と同様の動作により情報の書き込みおよび保持動作が可能である。

【0298】

図17(B)に示す半導体装置における、情報の読み出しについて説明する。トランジスタ3300が導通状態になると、浮遊状態である第3の配線3003と容量素子3400とが導通し、第3の配線3003と容量素子3400の間で電荷が再分配される。その結果、第3の配線3003の電位が変化する。第3の配線3003の電位の変化量は、容量素子3400の電極の一方の電位(または容量素子3400に蓄積された電荷)によって、異なる値をとる。

10

【0299】

例えば、容量素子3400の電極の一方の電位をV、容量素子3400の容量をC、第3の配線3003が有する容量成分をCB、電荷が再分配される前の第3の配線3003の電位をVB0とすると、電荷が再分配された後の第3の配線3003の電位は、 $(CB \times VB0 + CV) / (CB + C)$ となる。したがって、メモリセルの状態として、容量素子3400の電極の一方の電位がV1とV0( $V1 > V0$ )の2つの状態をとるとすると、電位V1を保持している場合の第3の配線3003の電位( $= (CB \times VB0 + CV1) / (CB + C)$ )は、電位V0を保持している場合の第3の配線3003の電位( $= (CB \times VB0 + CV0) / (CB + C)$ )よりも高くなることがわかる。

20

【0300】

そして、第3の配線3003の電位を所定の電位と比較することで、情報を読み出すことができる。

【0301】

この場合、メモリセルを駆動させるための駆動回路に上記第1の半導体が適用されたトランジスタを用い、トランジスタ3300として第2の半導体が適用されたトランジスタを駆動回路上に積層して配置する構成とすればよい。

30

【0302】

以上に示した半導体装置は、酸化物半導体を用いたオフ電流の極めて小さいトランジスタを適用することで、長期にわたって記憶内容を保持することが可能となる。つまり、リフレッシュ動作が不要となるか、またはリフレッシュ動作の頻度を極めて低くすることが可能となるため、消費電力の低い半導体装置を実現することができる。また、電力の供給がない場合(ただし、電位は固定されていることが好ましい)であっても、長期にわたって記憶内容を保持することが可能である。

【0303】

また、該半導体装置は、情報の書き込みに高い電圧が不要であるため、素子の劣化が起こりにくい。例えば、従来の不揮発性メモリのように、フローティングゲートへの電子の注入や、フローティングゲートからの電子の引き抜きを行わないため、絶縁体の劣化といった問題が全く生じない。即ち、本発明の一態様に係る半導体装置は、従来の不揮発性メモリで問題となっている書き換え可能回数に制限はなく、信頼性が飛躍的に向上した半導体装置である。さらに、トランジスタの導通状態、非導通状態によって、情報の書き込みが行われるため、高速な動作が可能となる。

40

【0304】

<RFタグ>

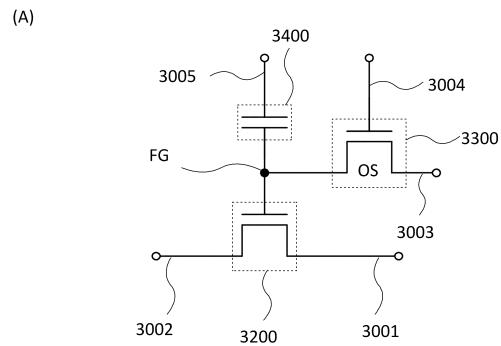

以下では、上述したトランジスタ、または記憶装置を含むRFタグについて、図18を用いて説明する。

【0305】

本発明の一態様に係るRFタグは、内部に記憶回路を有し、記憶回路に情報を記憶し、非接触手段、例えば無線通信を用いて外部と情報の授受を行うものである。このような特徴から、RFタグは、物品などの個体情報を読み取ることにより物品の識別を行う個体認証システムなどに用いることが可能である。なお、これらの用途に用いるためには高い信頼

50

性が要求される。

【0306】

R F タグの構成について図18を用いて説明する。図18は、R F タグの構成例を示すブロック図である。

【0307】

図18に示すようにR F タグ800は、通信器801（質問器、リーダ/ライタなどともいう）に接続されたアンテナ802から送信される無線信号803を受信するアンテナ804を有する。またR F タグ800は、整流回路805、定電圧回路806、復調回路807、変調回路808、論理回路809、記憶回路810、R O M 811を有している。なお、復調回路807に含まれる整流作用を示すトランジスタの半導体には、逆方向電流を十分に抑制することが可能な、例えば、酸化物半導体を用いてもよい。これにより、逆方向電流に起因する整流作用の低下を抑制し、復調回路の出力が飽和することを防止できる。つまり、復調回路の入力に対する復調回路の出力を線形に近づけることができる。なお、データの伝送形式は、一対のコイルを対向配置して相互誘導によって交信を行う電磁結合方式、誘導電磁界によって交信する電磁誘導方式、電波を利用して交信する電波方式の3つに大別される。R F タグ800は、そのいずれの方式に用いることも可能である。

【0308】

次に各回路の構成について説明する。アンテナ804は、通信器801に接続されたアンテナ802との間で無線信号803の送受信を行うためのものである。また、整流回路805は、アンテナ804で無線信号を受信することにより生成される入力交流信号を整流、例えば、半波2倍圧整流し、後段の容量素子により、整流された信号を平滑化することで入力電位を生成するための回路である。なお、整流回路805の入力側または出力側には、リミッタ回路を有してもよい。リミッタ回路とは、入力交流信号の振幅が大きく、内部生成電圧が大きい場合に、ある電力以上の電力を後段の回路に入力しないように制御するための回路である。

【0309】

定電圧回路806は、入力電位から安定した電源電圧を生成し、各回路に供給するための回路である。なお、定電圧回路806は、内部にリセット信号生成回路を有していてもよい。リセット信号生成回路は、安定した電源電圧の立ち上がりを利用して、論理回路809のリセット信号を生成するための回路である。

【0310】

復調回路807は、入力交流信号を包絡線検出することにより復調し、復調信号を生成するための回路である。また、変調回路808は、アンテナ804より出力するデータに応じて変調をおこなうための回路である。

【0311】

論理回路809は復調信号を解析し、処理を行うための回路である。記憶回路810は、入力された情報を保持する回路であり、ロウデコーダ、カラムデコーダ、記憶領域などを有する。また、R O M 811は、固有番号（I D）などを格納し、処理に応じて出力をを行うための回路である。

【0312】

なお、上述の各回路は、適宜、取捨することができる。

【0313】

ここで、上述した記憶装置を、記憶回路810に用いることができる。本発明の一態様に係る記憶装置は、電源が遮断された状態であっても情報を保持できるため、R F タグに好適である。さらに本発明の一態様に係る記憶装置は、データの書き込みに必要な電力（電圧）が従来の不揮発性メモリに比べて低いため、データの読み出し時と書き込み時の最大通信距離の差を生じさせないことも可能である。さらに、データの書き込み時に電力が不足し、誤動作または誤書き込みが生じることを抑制することができる。

【0314】

また、本発明の一態様に係る記憶装置は、不揮発性メモリとして用いることが可能である

10

20

30

40

50

ため、ROM811に適用することもできる。その場合には、生産者がROM811にデータを書き込むためのコマンドを別途用意し、ユーザが自由に書き換えできないようにしておくことが好ましい。生産者が出荷前に固有番号を書込んだのちに製品を出荷することで、作製したRFタグすべてについて固有番号を付与するのではなく、出荷する良品にのみ固有番号を割り当てることが可能となり、出荷後の製品の固有番号が不連続になることがなく出荷後の製品に対応した顧客管理が容易となる。

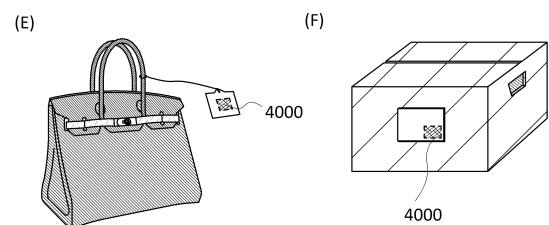

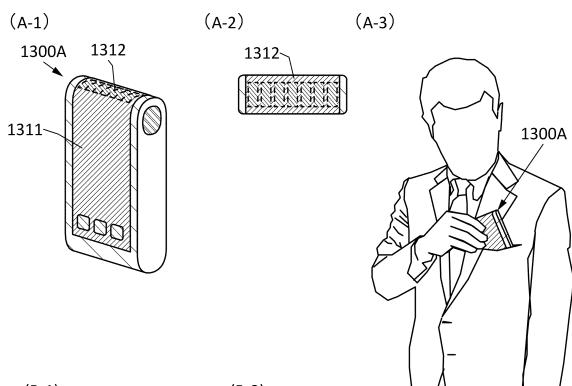

【0315】

<RFタグの使用例>

以下では、本発明の一態様に係るRFタグの使用例について図19を用いて説明する。RFタグの用途は広範にわたるが、例えば、紙幣、硬貨、有価証券類、無記名債券類、証書類（運転免許証や住民票等、図19（A）参照。）、包装用容器類（包装紙やボトル等、図19（C）参照。）、記録媒体（DVDやビデオテープ等、図19（B）参照。）、乗り物類（自転車等、図19（D）参照。）、身の回り品（鞄や眼鏡等）、食品類、植物類、動物類、人体、衣類、生活用品類、薬品や薬剤を含む医療品、または電子機器（液晶表示装置、EL表示装置、テレビジョン装置、または携帯電話）等の物品、もしくは各物品に取り付ける荷札（図19（E）および図19（F）参照。）等に設けて使用することができる。

10

【0316】

本発明の一態様に係るRFタグ4000は、表面に貼る、または埋め込むことにより、物品に固定される。例えば、本であれば紙に埋め込み、有機樹脂からなるパッケージであれば当該有機樹脂の内部に埋め込み、各物品に固定される。本発明の一態様に係るRFタグ4000は、小型、薄型、軽量を実現するため、物品に固定した後もその物品自体のデザイン性を損なうことがない。また、紙幣、硬貨、有価証券類、無記名債券類、または証書類等に本発明の一態様に係るRFタグ4000により、認証機能を付与することができ、この認証機能を活用すれば、偽造を防止することができる。また、包装用容器類、記録媒体、身の回り品、食品類、衣類、生活用品類、または電子機器等に本発明の一態様に係るRFタグ4000を取り付けることにより、検品システム等のシステムの効率化を図ることができる。また、乗り物類であっても、本発明の一態様に係るRFタグ4000を取り付けることにより、盗難などに対するセキュリティ性を高めることができる。

20

【0317】

以上のように、本発明の一態様に係るRFタグは、上述したような各用途に用いることができる。

30

【0318】

<CPU>

以下では、上述したトランジスタや上述した記憶装置などの半導体装置を含むCPUについて説明する。

【0319】

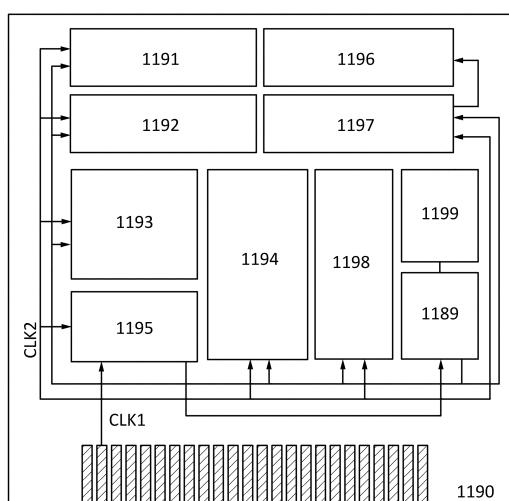

図20は、上述したトランジスタを一部に用いたCPUの一例の構成を示すブロック図である。

40

【0320】

図20に示すCPUは、基板1190上に、ALU1191（ALU：Arithmetic logic unit、演算回路）、ALUコントローラ1192、インストラクションデコーダ1193、インタラプトコントローラ1194、タイミングコントローラ1195、レジスタ1196、レジスタコントローラ1197、バスインターフェース1198、書き換え可能なROM1199、およびROMインターフェース1189を有している。基板1190は、半導体基板、SOI基板、ガラス基板などを用いる。ROM1199およびROMインターフェース1189は、別チップに設けてよい。もちろん、図20に示すCPUは、その構成を簡略化して示した一例にすぎず、実際のCPUはその用途によって多種多様な構成を有している。例えば、図20に示すCPUまたは演算回路を含む構成を一つのコアとし、当該コアを複数含み、それぞれのコアが並列で動作するよ

50

うな構成としてもよい。また、CPUが内部演算回路やデータバスで扱えるビット数は、例えば8ビット、16ビット、32ビット、64ビットなどとすることができます。

【0321】

バスインターフェース1198を介してCPUに入力された命令は、インストラクションデコーダ1193に入力され、デコードされた後、ALUコントローラ1192、インタラプトコントローラ1194、レジスタコントローラ1197、タイミングコントローラ1195に入力される。

【0322】

ALUコントローラ1192、インタラプトコントローラ1194、レジスタコントローラ1197、タイミングコントローラ1195は、デコードされた命令に基づき、各種制御を行なう。具体的にALUコントローラ1192は、ALU1191の動作を制御するための信号を生成する。また、インタラプトコントローラ1194は、CPUのプログラム実行中に、外部の入出力装置や、周辺回路からの割り込み要求を、その優先度やマスク状態から判断し、処理する。レジスタコントローラ1197は、レジスタ1196のアドレスを生成し、CPUの状態に応じてレジスタ1196の読み出しや書き込みを行なう。

10

【0323】

また、タイミングコントローラ1195は、ALU1191、ALUコントローラ1192、インストラクションデコーダ1193、インタラプトコントローラ1194、およびレジスタコントローラ1197の動作のタイミングを制御する信号を生成する。例えばタイミングコントローラ1195は、基準クロック信号CLK1を元に、内部クロック信号CLK2を生成する内部クロック生成部を備えており、内部クロック信号CLK2を上記各種回路に供給する。

20

【0324】

図20に示すCPUでは、レジスタ1196に、メモリセルが設けられている。レジスタ1196のメモリセルとして、上述したトランジスタや記憶装置などを用いることができる。

【0325】

図20に示すCPUにおいて、レジスタコントローラ1197は、ALU1191からの指示に従い、レジスタ1196における保持動作の選択を行う。即ち、レジスタ1196が有するメモリセルにおいて、フリップフロップによるデータの保持を行うか、容量素子によるデータの保持を行うかを、選択する。フリップフロップによるデータの保持が選択されている場合、レジスタ1196内のメモリセルへの、電源電圧の供給が行われる。容量素子におけるデータの保持が選択されている場合、容量素子へのデータの書き換えが行われ、レジスタ1196内のメモリセルへの電源電圧の供給を停止することができる。

30

【0326】

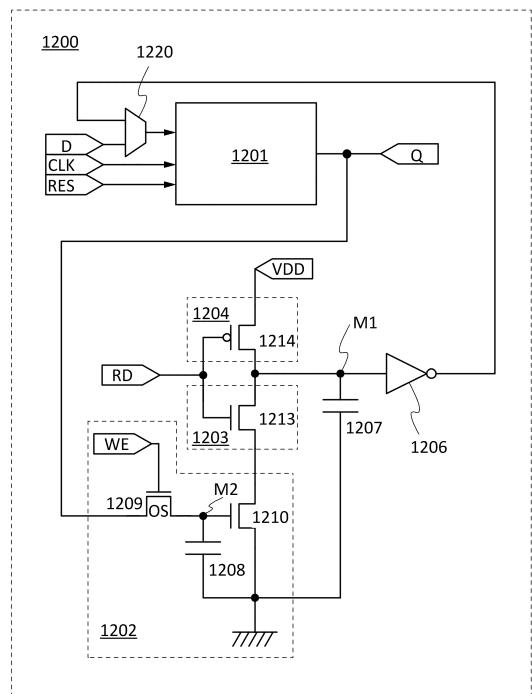

図21は、レジスタ1196として用いることのできる記憶素子1200の回路図の一例である。記憶素子1200は、電源遮断で記憶データが揮発する回路1201と、電源遮断で記憶データが揮発しない回路1202と、スイッチ1203と、スイッチ1204と、論理素子1206と、容量素子1207と、選択機能を有する回路1220と、を有する。回路1202は、容量素子1208と、トランジスタ1209と、トランジスタ1210と、を有する。なお、記憶素子1200は、必要に応じて、ダイオード、抵抗素子、インダクタなどのその他の素子をさらに有していてもよい。

40

【0327】

ここで、回路1202には、上述した記憶装置を用いることができる。記憶素子1200への電源電圧の供給が停止した際、回路1202のトランジスタ1209のゲートにはGND(0V)、またはトランジスタ1209がオフする電位が入力され続ける構成とする。例えば、トランジスタ1209のゲートが抵抗等の負荷を介して接地される構成とする。

【0328】

スイッチ1203は、一導電型(例えば、nチャネル型)のトランジスタ1213を用い

50

て構成され、スイッチ 1204 は、一導電型とは逆の導電型（例えば、p チャネル型）のトランジスタ 1214 を用いて構成した例を示す。ここで、スイッチ 1203 の第 1 の端子はトランジスタ 1213 のソースとドレインの一方に対応し、スイッチ 1203 の第 2 の端子はトランジスタ 1213 のソースとドレインの他方に対応し、スイッチ 1203 はトランジスタ 1213 のゲートに入力される制御信号 RD によって、第 1 の端子と第 2 の端子の間の導通または非導通（つまり、トランジスタ 1213 の導通状態または非導通状態）が選択される。スイッチ 1204 の第 1 の端子はトランジスタ 1214 のソースとドレインの一方に対応し、スイッチ 1204 の第 2 の端子はトランジスタ 1214 のソースとドレインの他方に対応し、スイッチ 1204 はトランジスタ 1214 のゲートに入力される制御信号 RD によって、第 1 の端子と第 2 の端子の間の導通または非導通（つまり、トランジスタ 1214 の導通状態または非導通状態）が選択される。10

#### 【0329】

トランジスタ 1209 のソースとドレインの一方は、容量素子 1208 の一対の電極のうちの一方、およびトランジスタ 1210 のゲートと電気的に接続される。ここで、接続部分をノード M2 とする。トランジスタ 1210 のソースとドレインの一方は、低電源電位を供給することのできる配線（例えば GND 線）に電気的に接続され、他方は、スイッチ 1203 の第 1 の端子（トランジスタ 1213 のソースとドレインの一方）と電気的に接続される。スイッチ 1203 の第 2 の端子（トランジスタ 1213 のソースとドレインの他方）はスイッチ 1204 の第 1 の端子（トランジスタ 1214 のソースとドレインの一方）と電気的に接続される。スイッチ 1204 の第 2 の端子（トランジスタ 1214 のソースとドレインの他方）は電源電位 VDD を供給することのできる配線と電気的に接続される。スイッチ 1203 の第 2 の端子（トランジスタ 1213 のソースとドレインの他方）と、スイッチ 1204 の第 1 の端子（トランジスタ 1214 のソースとドレインの一方）と、論理素子 1206 の入力端子と、容量素子 1207 の一対の電極のうちの一方と、は電気的に接続される。ここで、接続部分をノード M1 とする。容量素子 1207 の一対の電極のうちの他方は、一定の電位が入力される構成とすることができます。例えば、低電源電位（GND 等）または高電源電位（VDD 等）が入力される構成とすることができます。容量素子 1207 の一対の電極のうちの他方は、低電源電位を供給することのできる配線（例えば GND 線）と電気的に接続される。容量素子 1208 の一対の電極のうちの他方は、一定の電位が入力される構成とすることができます。例えば、低電源電位（GND 等）または高電源電位（VDD 等）が入力される構成とすることができます。容量素子 1208 の一対の電極のうちの他方は、低電源電位を供給することのできる配線（例えば GND 線）と電気的に接続される。20

#### 【0330】

なお、容量素子 1207 および容量素子 1208 は、トランジスタや配線の寄生容量等を積極的に利用することによって省略することも可能である。

#### 【0331】

トランジスタ 1209 のゲートには、制御信号 WE が入力される。スイッチ 1203 およびスイッチ 1204 は、制御信号 WE とは異なる制御信号 RD によって第 1 の端子と第 2 の端子の間の導通状態または非導通状態を選択され、一方のスイッチの第 1 の端子と第 2 の端子の間が導通状態のとき他方のスイッチの第 1 の端子と第 2 の端子の間は非導通状態となる。40

#### 【0332】

トランジスタ 1209 のソースとドレインの他方には、回路 1201 に保持されたデータに対応する信号が入力される。図 21 では、回路 1201 から出力された信号が、トランジスタ 1209 のソースとドレインの他方に入力される例を示した。スイッチ 1203 の第 2 の端子（トランジスタ 1213 のソースとドレインの他方）から出力される信号は、論理素子 1206 によってその論理値が反転された反転信号となり、回路 1220 を介して回路 1201 に入力される。

#### 【0333】

50

30

40

50

なお、図21では、スイッチ1203の第2の端子（トランジスタ1213のソースとドレインの他方）から出力される信号は、論理素子1206および回路1220を介して回路1201に入力する例を示したがこれに限定されない。スイッチ1203の第2の端子（トランジスタ1213のソースとドレインの他方）から出力される信号が、論理値を反転させられることなく、回路1201に入力されてもよい。例えば、回路1201内に、入力端子から入力された信号の論理値が反転した信号が保持されるノードが存在する場合に、スイッチ1203の第2の端子（トランジスタ1213のソースとドレインの他方）から出力される信号を当該ノードに入力することができる。

【0334】

また、図21において、記憶素子1200に用いられるトランジスタのうち、トランジスタ1209以外のトランジスタは、酸化物半導体以外の半導体でなる膜または基板1190にチャネルが形成されるトランジスタとすることができる。例えば、シリコン膜またはシリコン基板にチャネルが形成されるトランジスタとすることができる。また、記憶素子1200に用いられるトランジスタ全てを、チャネルが酸化物半導体で形成されるトランジスタとすることもできる。または、記憶素子1200は、トランジスタ1209以外にも、チャネルが酸化物半導体で形成されるトランジスタを含んでいてもよく、残りのトランジスタは酸化物半導体以外の半導体でなる層または基板1190にチャネルが形成されるトランジスタとすることもできる。

【0335】

図21における回路1201には、例えばフリップフロップ回路を用いることができる。また、論理素子1206としては、例えばインバータやクロックドインバータ等を用いることができる。

【0336】

本発明の一態様に係る半導体装置では、記憶素子1200に電源電圧が供給されない間は、回路1201に記憶されていたデータを、回路1202に設けられた容量素子1208によって保持することができる。

【0337】

また、酸化物半導体にチャネルが形成されるトランジスタはオフ電流が極めて小さい。例えば、酸化物半導体にチャネルが形成されるトランジスタのオフ電流は、結晶性を有するシリコンにチャネルが形成されるトランジスタのオフ電流に比べて著しく低い。そのため、当該トランジスタをトランジスタ1209として用いることによって、記憶素子1200に電源電圧が供給されない間も容量素子1208に保持された信号は長期間にわたり保たれる。こうして、記憶素子1200は電源電圧の供給が停止した間も記憶内容（データ）を保持することが可能である。

【0338】

また、スイッチ1203およびスイッチ1204を設けることによって、プリチャージ動作を行うことを特徴とする記憶素子であるため、電源電圧供給再開後に、回路1201が元のデータを保持しなおすまでの時間を短くすることができる。

【0339】

また、回路1202において、容量素子1208によって保持された信号はトランジスタ1210のゲートに入力される。そのため、記憶素子1200への電源電圧の供給が再開された後、容量素子1208によって保持された信号を、トランジスタ1210の状態（導通状態、または非導通状態）に変換して、回路1202から読み出すことができる。それ故、容量素子1208に保持された信号に対応する電位が多少変動していても、元の信号を正確に読み出すことが可能である。

【0340】

このような記憶素子1200を、プロセッサが有するレジスタやキャッシュメモリなどの記憶装置に用いることで、電源電圧の供給停止による記憶装置内のデータの消失を防ぐことができる。また、電源電圧の供給を再開した後、短時間で電源供給停止前の状態に復帰することができる。よって、プロセッサ全体、もしくはプロセッサを構成する一つ、また

10

20

30

40

50

は複数の論理回路において、短い時間でも電源停止を行うことができるため、消費電力を抑えることができる。

【0341】

記憶素子1200をCPUに用いる例として説明したが、記憶素子1200は、DSP (Digital Signal Processor)、カスタムLSI、PLD (Programmable Logic Device)等のLSI、RF-ID (Radio Frequency Identification)にも応用可能である。

【0342】

<表示装置>

以下では、本発明の一態様に係る表示装置の構成例について説明する。

10

【0343】

[構成例]

図22(A)には、本発明の一態様に係る表示装置の上面図を示す。また、図22(B)には、本発明の一態様に係る表示装置の画素に液晶素子を用いた場合における画素回路を示す。また、図22(C)には、本発明の一態様に係る表示装置の画素に有機EL素子を用いた場合における画素回路を示す。

【0344】

画素に用いるトランジスタは、上述したトランジスタを用いることができる。ここでは、nチャネル型のトランジスタを用いる例を示す。なお、画素に用いたトランジスタと、同一工程を経て作製したトランジスタを駆動回路として用いても構わない。このように、画素や駆動回路に上述したトランジスタを用いることにより、表示品位が高い、または/および信頼性の高い表示装置となる。

20

【0345】