(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7042224号**

**(P7042224)**

(45)発行日 令和4年3月25日(2022.3.25)

(24)登録日 令和4年3月16日(2022.3.16)

## (51)国際特許分類

|         |                 |     |         |       |       |

|---------|-----------------|-----|---------|-------|-------|

| B 4 1 J | 2/14 (2006.01)  | F I | B 4 1 J | 2/14  | 6 1 1 |

| B 4 1 J | 2/01 (2006.01)  |     | B 4 1 J | 2/01  | 2 0 7 |

| G 0 1 R | 31/50 (2020.01) |     | G 0 1 R | 31/50 |       |

| G 0 1 R | 31/52 (2020.01) |     | G 0 1 R | 31/52 |       |

| G 0 1 R | 31/54 (2020.01) |     | G 0 1 R | 31/54 |       |

請求項の数 19 (全34頁) 最終頁に続く

|                   |                             |

|-------------------|-----------------------------|

| (21)出願番号          | 特願2018-567584(P2018-567584) |

| (86)(22)出願日       | 平成29年6月29日(2017.6.29)       |

| (65)公表番号          | 特表2019-521018(P2019-521018) |

|                   | A)                          |

| (43)公表日           | 令和1年7月25日(2019.7.25)        |

| (86)国際出願番号        | PCT/GB2017/051911           |

| (87)国際公開番号        | WO2018/002634               |

| (87)国際公開日         | 平成30年1月4日(2018.1.4)         |

| 審査請求日             | 令和2年6月25日(2020.6.25)        |

| (31)優先権主張番号       | 1611464.7                   |

| (32)優先日           | 平成28年6月30日(2016.6.30)       |

| (33)優先権主張国・地域又は機関 | 英國(GB)                      |

|          |                                                                                                          |

|----------|----------------------------------------------------------------------------------------------------------|

| (73)特許権者 | 516154934<br>ザール テクノロジー リミテッド<br>X A A R T E C H N O L O G Y L I M<br>I T E D                            |

|          | イギリス国 ピーイー29 6エックスエ<br>ックス ケンブリッジシャー ハンティン<br>ドン アーミン ビジネス パーク ハリケ<br>ーン クローズ 1 インテレクチュアル<br>プロパティ チーム 内 |

| (74)代理人  | 100116850<br>弁理士 廣瀬 隆行                                                                                   |

| (74)代理人  | 100165847<br>弁理士 関 大祐                                                                                    |

| (72)発明者  | バード ニール クリストファー<br>イギリス国 シービー4 0エックスア一<br>最終頁に続く                                                         |

(54)【発明の名称】 液滴堆積装置およびその試験回路

**(57)【特許請求の範囲】****【請求項1】**

アクチュエータ素子アレイ中のアクチュエータ素子の静電容量を決定する試験回路であつて、前記試験回路は、

コントローラと、

試験入力を生成する電源と、

前記試験回路と前記アクチュエータ素子との間の試験経路での1つ以上の試験値を測定するように構成された測定回路と、を備え、

前記コントローラは、試験期間中、

前記アクチュエータ素子に関連する第1のスイッチを制御して前記アクチュエータ素子を前記試験経路に接続し、

前記電源を制御して第1の試験入力を生成し、

前記第1の試験入力に応じて生成される第1の試験値から全静電容量を決定し、前記全静電容量は、アクチュエータ素子の容量とアクチュエータ素子に関連する寄生容量を含み、前記全静電容量から前記アクチュエータ素子の前記静電容量を決定する、ように構成される、試験回路。

**【請求項2】**

前記コントローラは、前記試験期間中、

さらなるアクチュエータ素子に関連する第2のスイッチを制御して、前記試験経路と前記さらなるアクチュエータ素子との間の短絡が存在するとき、前記さらなるアクチュエータ

素子を前記試験経路に接続するようにさらに構成される、請求項 1 に記載の試験回路。

**【請求項 3】**

前記コントローラは、

前記試験値と決定された前記静電容量とのうちの 1 つ以上に応じて前記アクチュエータ素子に関連する不具合を検出するようにさらに構成され、

前記不具合は、

断線と、前記アクチュエータ素子の両端間の短絡と、前記試験経路と前記さらなるアクチュエータ素子との間の短絡と、の 1 つ以上を含む、請求項 1 または 2 に記載の試験回路。

**【請求項 4】**

前記コントローラは、第 1 の較正期間中、

前記アクチュエータ素子に関連する前記第 1 のスイッチを制御して前記アクチュエータ素子を前記試験経路から絶縁し、

前記試験経路での第 2 の試験入力を制御して前記アクチュエータ素子に関連する寄生容量を充電し、

前記第 2 の試験入力に応じて生成される第 2 の試験値から前記関連する寄生容量を決定する、ようにさらに構成され、

前記関連する寄生容量は前記全静電容量から前記アクチュエータ素子の前記静電容量を決定するのに用いられる、請求項 1 ~ 3 のいずれかに記載の試験回路。

**【請求項 5】**

前記第 1 の試験値は前記第 1 の試験入力と寄生電流とに応じてさらに生成され、

前記コントローラは、第 1 の較正期間中、

前記電源を制御して前記寄生電流にバイアスをかけて前記アクチュエータ素子から離し、前記アクチュエータ素子に関連する前記第 1 のスイッチを制御して前記アクチュエータ素子を前記試験経路から電気的に絶縁し、

前記電源を制御して前記アクチュエータ素子に関連する寄生容量を前記寄生電流で充電し、前記関連する寄生容量を前記寄生電流で充電するのに応じて第 2 の試験値を生成する、ようにさらに構成される、請求項 1 ~ 3 に記載の試験回路。

**【請求項 6】**

前記コントローラは、第 2 の較正期間中、

前記電源を制御して前記寄生電流にバイアスをかけて前記アクチュエータ素子から離し、前記アクチュエータ素子に関連する前記第 1 のスイッチを制御して前記アクチュエータ素子を前記試験経路から電気的に絶縁し、

前記関連する寄生容量を前記寄生電流と第 2 の試験入力とで充電するように前記電源を制御し、

前記関連する寄生容量を前記寄生電流と前記第 2 の試験入力とで充電するのに応じて第 3 の試験値を生成するようにさらに構成され、

前記第 2 の試験値と前記第 3 の試験値とが前記全静電容量から前記アクチュエータ素子の前記静電容量を決定するのに用いられる、請求項 5 に記載の試験回路。

**【請求項 7】**

前記測定回路は、各々が前記試験経路での 1 つ以上の前記試験値と設定されたレベルの入力を受けるように配置される 1 つ以上のコンパレータと、

前記 1 つ以上のコンパレータから出力を受けるように配置されるタイマを備える、請求項 1 ~ 6 のいずれかに記載の試験回路。

**【請求項 8】**

前記試験回路は、前記試験経路から前記試験回路を電気的に絶縁するよう配置される試験スイッチをさらに備える、請求項 1 ~ 7 のいずれかに記載の試験回路。

**【請求項 9】**

前記試験回路は前記試験経路を放電する放電スイッチをさらに備える、請求項 1 ~ 8 のいずれかに記載の試験回路。

**【請求項 10】**

10

20

30

40

50

前記電源は定電流源を備え、前記第1の試験入力は定電流を備える、請求項1～9のいずれかに記載の試験回路。

**【請求項11】**

1つ以上のアクチュエータ素子を備えるアクチュエータ素子アセンブリと、

前記1つ以上のアクチュエータ素子のうちのアクチュエータ素子を試験経路または駆動経路に選択的に接続する複数のスイッチを備えるスイッチ回路と、

前記試験経路に接続されるときに全静電容量から前記アクチュエータ素子の静電容量を決定するように構成された試験回路と、を備え、

前記全静電容量は、前記アクチュエータ素子の前記静電容量と前記アクチュエータ素子に関連する寄生容量を含む、液滴堆積ヘッド回路。

10

**【請求項12】**

前記試験回路は、

コントローラと、

前記試験経路についての試験入力を生成する電源と、

前記試験入力に応じて生成される前記試験経路での1つ以上の試験値を測定する測定回路と、を備える、請求項11に記載の液滴堆積ヘッド回路。

**【請求項13】**

前記試験経路は、前記試験回路と前記1つ以上のアクチュエータ素子との間にある第1の試験バスを備え、

前記駆動経路は、駆動回路と前記1つ以上のアクチュエータ素子との間にある前記第1の試験バスを備える、請求項11または12に記載の液滴堆積ヘッド回路。

20

**【請求項14】**

前記駆動経路は、駆動回路と前記1つ以上のアクチュエータ素子との間にある第2の試験バスを備える、請求項13に記載の液滴堆積ヘッド回路。

**【請求項15】**

前記試験経路は、前記駆動経路から前記試験回路を電気的に絶縁する試験スイッチを備える、請求項11～13に記載の液滴堆積ヘッド回路。

**【請求項16】**

前記複数のスイッチのうちのあるスイッチは、直列に配置されている第1のスイッチ素子および第2のスイッチ素子を備え、前記第1の試験バスは前記第1のスイッチ素子および第2のスイッチ素子間に接続され、前記第1のスイッチ素子は、前記駆動経路から前記試験回路を電気的に絶縁するように構成される、請求項13又は14に記載の液滴堆積ヘッド回路。

30

**【請求項17】**

プリントヘッド回路中のアクチュエータ素子の静電容量を決定する方法であって、

前記アクチュエータ素子を試験経路に接続することと、

前記試験経路についての第1の試験入力を試験回路で生成することと、

前記第1の試験入力に応じて生成される前記試験経路での第1の試験値を前記試験回路で測定すること、

全静電容量を前記第1の試験値に応じて決定することであって、前記全静電容量は前記アクチュエータ素子の前記静電容量と前記アクチュエータ素子に関連する寄生容量とを含むこと、

前記全静電容量から前記アクチュエータ素子の前記静電容量を決定することと、を含む、方法。

40

**【請求項18】**

請求項1～10のいずれかに記載の試験回路を有する液滴堆積装置。

**【請求項19】**

請求項1～10のいずれかに記載の試験回路を備える試験モジュール。

**【発明の詳細な説明】**

**【技術分野】**

50

**【 0 0 0 1 】**

本発明は試験回路に関する。これは、特に、液滴堆積装置のアクチュエータ、センサまたはエナジハーベスタなどの圧電素子を利用する装置に有効に応用することができる。

**【背景技術】****【 0 0 0 2 】**

液滴堆積ヘッドからの液滴の吐出の制御を実現し、このような液滴の配置を制御して受容媒体(*receiving medium*)または印刷媒体にドットを生成することを実現するインクジェットプリンタなどの液滴堆積装置が公知である。

**【 0 0 0 3 】**

インクジェットプリントヘッドなどの液滴堆積ヘッドは一般的にはアクチュエータ素子によって実現される吐出機構を備える。

10

**【 0 0 0 4 】**

アクチュエータ素子および関連駆動回路に対して診断試験を実行することは、例えば、プリントヘッドに組み込む前またはプリントヘッドに組み込んだ後のアクチュエータ素子の不具合を特定して、意図しない印刷不良を生じ得るあらゆる不具合を特定するのにも重要である。

**【 0 0 0 5 】**

試験される不具合は、例えば、熱損傷、ハンドリング時の損傷やヒートショック、製造欠陥や組み立て欠陥によって生じる場合があるアクチュエータ素子の両端間の断線や短絡を含む。

20

**【 0 0 0 6 】**

試験アクチュエータ素子について様々な診断試験技術が存在する。

**【 0 0 0 7 】**

例えば、アクチュエータ素子の両端間の短絡について試験する場合、電流を、プローブを介してアクチュエータ素子によって引き込み、対応する電圧を測定したり、印加された電圧と生じた電流とを測定したりする。しかし、プリントヘッドまたはプリンタに組み込まれた場合にはプローブでアクチュエータ素子にアクセスすることは困難である。プリントヘッドの特徴寸法が減少すると、これはますます困難になるか、実現できなくなる。したがって、この方法を用いた断線試験は困難である。

30

**【 0 0 0 8 】**

この代わりに、アクチュエータ素子の両端間の断線の試験に光学的技術を用いられる場合がある。これを用いて、アクチュエータ素子を所定の波形で駆動して、アクチュエータ素子の充電および放電に起因する熱を赤外線( I R )カメラで撮影する。ヒートスポットにより断線の有無が確かめられる。

**【 0 0 0 9 】**

しかし、ヒートスポットを撮影するのに必要な装置は、複雑かつ高価であり、一般的にプリントヘッド内のハードウェアにより I R カメラの視線が遮られるので、アクチュエータ素子がプリントヘッドに組み込まれた後は特に適さない。

40

**【 0 0 1 0 】**

さらに、短絡によって駆動時にアクチュエータ素子から熱が発生するので、光学的技術は単独で行なわれる場合には不正確である場合があり、短絡の存在を除外するために光学的技術とともにさらなる試験を行なうことが必要であり、したがって、このような試験は遅滞する場合がある。

**【 0 0 1 1 】**

したがって、アクチュエータ素子を試験する既存の試験技術は遅滞するものであり、複雑であり、高価でありかつ / または不正確である。

**【発明の概要】****【 0 0 1 2 】**

一態様に係れば、アクチュエータ素子アレイ中のアクチュエータ素子の静電容量( C A C T )を決定する試験回路であって、試験回路は、コントローラと、試験入力を生成する電

50

源と、試験回路とアクチュエータ素子との間の試験経路での1つ以上の試験値を測定する測定回路とを備えており、コントローラは、試験期間中、アクチュエータ素子を試験経路に接続するように、アクチュエータ素子に関連する第1のスイッチを制御し、第1の試験入力を生成するように電源を制御し、第1の試験入力に応じて生成される第1の試験値からアクチュエータ素子の全静電容量( $C_{PAR} + C_{ACT}$ )を決定し、全静電容量( $C_{PAR} + C_{ACT}$ )からアクチュエータ素子の静電容量( $C_{ACT}$ )を決定するように構成されている、試験回路が提供される。

#### 【0013】

好ましくは、コントローラは、第1の期間中、試験経路とさらなるアクチュエータ素子との間の短絡が存在するとき、さらなるアクチュエータ素子を試験経路に接続するように、さらなるアクチュエータ素子に関連する第2のスイッチを制御するようにさらに構成されている。

10

#### 【0014】

好ましくは、コントローラは、試験値と決定された静電容量との1つ以上に応じてアクチュエータ素子に関連する不具合を検出するようにさらに構成されており、不具合は、断線と、アクチュエータの両端間の短絡と、試験経路とさらなるアクチュエータ素子との間の短絡との1つ以上を備える。

#### 【0015】

好ましくは、不具合は、決定された静電容量が静電容量閾値未満であることを備える。

20

#### 【0016】

好ましくは、コントローラは、第1の較正期間中、アクチュエータ素子を試験経路から絶縁するように、アクチュエータ素子に関連する第1のスイッチを制御し、アクチュエータ素子に関連する寄生容量( $C_{PAR}$ )を充電するように試験経路での第2の試験入力を制御し、第2の試験入力に応じて生成される第2の試験値から関連する寄生容量( $C_{PAR}$ )を決定するようにさらに構成されており、アクチュエータ素子についての関連する寄生容量( $C_{PAR}$ )は全静電容量( $C_{PAR} + C_{ACT}$ )からアクチュエータ素子の静電容量( $C_{ACT}$ )を決定するのに用いられる。

#### 【0017】

好ましくはさらに、第1の試験値は第1の試験入力と寄生電流とに応じてさらに生成され、コントローラは、第1の較正期間中、寄生電流にバイアスをかけてアクチュエータ素子から離すように電源を制御し、アクチュエータ素子を試験経路から電気的に絶縁するように、アクチュエータ素子に関連する第1のスイッチを制御し、アクチュエータ素子に関連する寄生容量を寄生電流で充電するように電源を制御し、関連する寄生容量を寄生電流で充電するのに応じて第2の試験値を生成するようにさらに構成されている。

30

#### 【0018】

好ましくは、コントローラは、第2の較正期間中、寄生電流にバイアスをかけてアクチュエータ素子から離すように電源を制御し、アクチュエータ素子を試験経路から電気的に絶縁するように、アクチュエータ素子に関連する第1のスイッチを制御し、関連する寄生容量を寄生電流と第2の試験入力とで充電するように電源を制御し、関連する寄生容量を寄生電流と第2の試験入力とで充電するのに応じて第3の試験値を生成するようにさらに構成されている。

40

#### 【0019】

好ましくは、第2の試験値と第3の試験値とが全静電容量( $C_{PAR} + C_{ACT}$ )からアクチュエータ素子の静電容量( $C_{ACT}$ )を決定するのに用いられる。

#### 【0020】

好ましくは、測定回路は、各々が試験経路での1つ以上の試験値を受けるように配置されている1つ以上のコンパレータを備えており、コンパレータの各々は設定されたレベルの入力を受けるように配置されており、および／または設定されたレベルの入力は電圧レベルと電流レベルとのうちの1つを備える。

#### 【0021】

50

好ましくは、測定回路は、1つ以上のコンパレータから出力を受けるように配置されているタイマを備えており、タイマは、第1の設定レベルから第2の設定レベルへの第1の試験値の遷移時間と、第3の設定レベルから第4の設定レベルへの第2の試験値の遷移時間と、第5の設定レベルから第6の設定レベルへの第3の試験値の遷移時間とのうちの1つ以上を測定するように構成されている。

#### 【0022】

好ましくは、第1、第3および第5の設定レベルのうちの1つ以上は実質的に等しく、および/または第2、第4および第6の設定レベルのうちの1つ以上は実質的に等しい。

#### 【0023】

好ましくは、試験回路は、試験経路から試験回路を電気的に絶縁するよう配置されている試験スイッチをさらに備える。

10

#### 【0024】

好ましくは、試験回路は、1つ以上の試験入力をさらなる測定回路に選択的に提供する精度回路をさらに備える。

#### 【0025】

好ましくは、試験回路は試験経路を放電する放電スイッチをさらに備える。

#### 【0026】

好ましくは、電源は定電流源を備えており、第1の試験入力は定電流を備える。

#### 【0027】

さらなる態様に係れば、アクチュエータ素子アレイでの不具合を検出する試験回路であって、試験回路は、コントローラと、試験入力を生成する電源と、試験経路での1つ以上の試験値を測定する測定回路とを備えており、コントローラは、第1の期間中、第1のアクチュエータ素子を試験経路に接続するように、アレイの第1のアクチュエータ素子に関連する第1のスイッチを制御し、第1の試験入力を生成するように電源を制御し、第1の試験入力に応じて生成される第1の試験値から不具合を検出するように構成されている、試験回路が提供される。

20

#### 【0028】

好ましくは、コントローラは、アレイ中の第2のアクチュエータ素子に関連する第2のスイッチを、第2のアクチュエータ素子を放電するように制御するようにさらに構成されている。

30

#### 【0029】

好ましくは、不具合は、第1のアクチュエータ素子の両端間の短絡を備えており、および/または不具合は試験経路と第2のアクチュエータ素子との間の短絡を備える。

#### 【0030】

さらなる態様に係れば、1つ以上のアクチュエータ素子を備えるアクチュエータ素子アセンブリと、1つ以上のアクチュエータ素子のうちのアクチュエータ素子を試験経路または駆動経路に選択的に接続する複数のスイッチを備えるスイッチ回路と、試験経路に接続されるときにアクチュエータ素子の静電容量を決定する、および/またはアクチュエータ素子アセンブリの不具合を検出するように構成されている試験回路と、を備える液滴堆積ヘッド回路が提供される。

40

#### 【0031】

好ましくは、試験回路は、コントローラと、試験経路についての試験入力を生成する電源と、試験入力に応じて生成される試験経路での1つ以上の試験値を測定する測定回路とを備える。

#### 【0032】

好ましくは、試験経路は、試験経路での静電容量を放電するように構成されている放電スイッチを備える。

#### 【0033】

好ましくは、試験経路は、試験回路と1つ以上のアクチュエータ素子との間に第1の試験バスを備えており、駆動経路は、駆動回路と1つ以上のアクチュエータ素子との間に

50

ある第 1 の試験バスを備える。

**【 0 0 3 4 】**

好ましくは、駆動経路は、駆動回路と 1 つ以上のアクチュエータ素子との間にある第 2 の試験バスを備える。

**【 0 0 3 5 】**

好ましくは、試験経路は、駆動経路から試験回路を電気的に絶縁する試験スイッチを備える。

**【 0 0 3 6 】**

好ましくは、複数のスイッチのうちのスイッチは、直列に配置されている第 1 および第 2 のスイッチ素子を備える。

10

**【 0 0 3 7 】**

好ましくは、スイッチは、第 1 および第 2 のスイッチ素子と並列に配置されている第 3 のスイッチ素子をさらに備えており、第 1 および第 2 のスイッチ素子の ON 抵抗は第 3 のスイッチ素子の ON 抵抗よりも低い。

**【 0 0 3 8 】**

好ましくは、第 1 の試験バスは第 1 および第 2 のスイッチ素子間に接続され、第 1 のスイッチ素子は、駆動経路から試験回路を電気的に絶縁するように構成されている。

**【 0 0 3 9 】**

好ましくは、スイッチは、第 1 のスイッチ素子と並列に配置されている第 3 のスイッチ素子をさらに備えており、第 1 の試験バスは第 2 および第 3 のスイッチ素子間に接続され、試験スイッチは試験バスに設けられている。

20

**【 0 0 4 0 】**

好ましくは、液滴堆積ヘッド回路は、不具合が検出されるときに不具合対応を開始するようさら構成されている。

**【 0 0 4 1 】**

好ましくは、不具合は、断線と、短絡と、静電容量が閾値に達することとのうちの 1 つを備える。

**【 0 0 4 2 】**

さらなる態様に係れば、プリントヘッド回路中のアクチュエータ素子の静電容量 (C A C T) を決定する方法であって、アクチュエータ素子を試験経路に接続する工程と、試験経路についての第 1 の入力を試験回路で生成する工程と、試験入力に応じて生成される試験経路での第 1 の試験値を試験回路で測定する工程と、第 1 の試験値からアクチュエータ素子の全静電容量 (C P A R + C A C T) を第 1 の試験値に応じて決定する工程と、全静電容量 (C P A R + C A C T) からアクチュエータ素子の静電容量 (C A C T) を決定する工程とを備える方法が提供される。

30

**【 0 0 4 3 】**

好ましくは、方法は、第 1 の試験値に応じて不具合を検出する工程と、不具合が検出されるときにプリントヘッド回路に対して不具合対応を開始する工程とをさらに備える。

**【図面の簡単な説明】**

**【 0 0 4 4 】**

40

以降、以下に示す添付の図面を参照して実施形態を説明する。

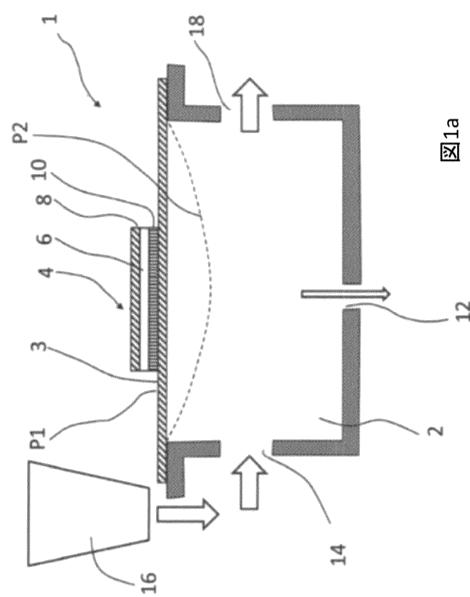

**【図 1 a】** 図 1 a は、公知の液滴堆積ヘッドの一部の断面を概略的に示す。

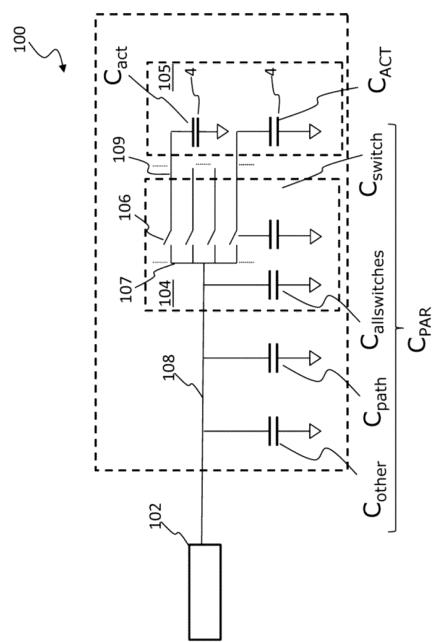

**【図 1 b】** 図 1 b は、実施形態に係る図 1 の複数のアクチュエータ素子を駆動する公知の回路の例を概略的に示す。

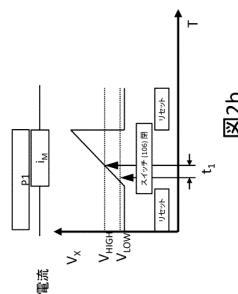

**【図 2 a】** 図 2 a は、実施形態に係るアクチュエータ素子の試験回路を概略的に示す。

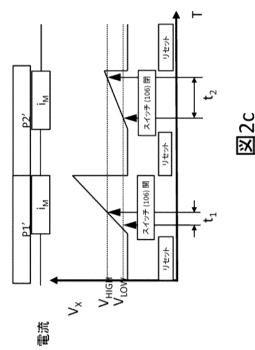

**【図 2 b】** 図 2 b は、図 2 a の試験回路を用いて得られる測定値をグラフで示す。

**【図 2 c】** 図 2 c は、図 2 a の試験回路を用いて得られるさらなる測定値をグラフで示す。

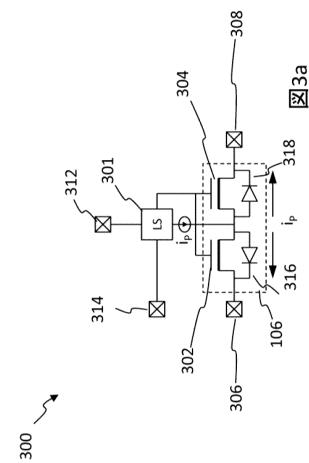

**【図 3 a】** 図 3 a は、実施形態に係るスイッチ例を概略的に示す。

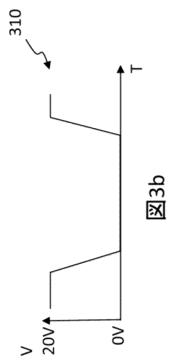

**【図 3 b】** 図 3 b は、実施形態に係る駆動波形例を概略的に示す。

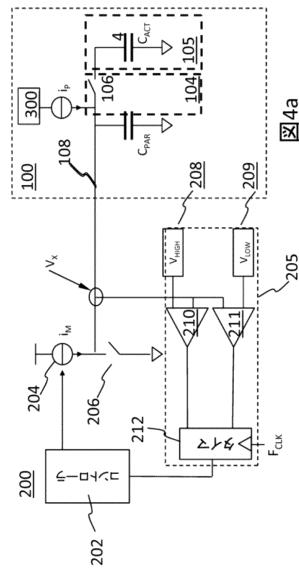

**【図 4 a】** 図 4 a は、アクチュエータ素子が実施形態に係る図 3 a のスイッチによって駆

50

動される場合の図 2 a の試験回路の例を概略的に示す。

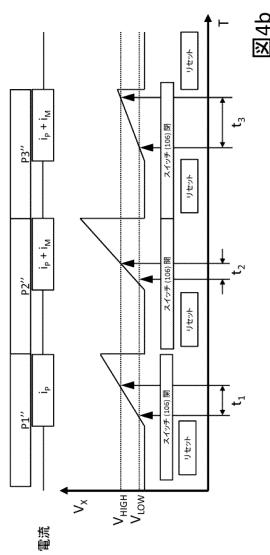

【図 4 b】図 4 b は、図 4 a の試験回路を用いて得られる測定値をグラフで示す。

【図 5 a】図 5 a は、実施形態に係る試験回路を有する回路を概略的に示す。

【図 5 b】図 5 b は、図 5 a の回路中のアクチュエータ素子の両端間の短絡を概略的に示す。

【図 5 c】図 5 c は、図 5 a の回路中のアクチュエータ素子間の短絡を概略的に示す。

【図 6】図 6 は、実施形態に係る試験回路を有する回路を概略的に示す。

【図 7 a】図 7 a は、さらなる実施形態に係る試験回路を有する回路を概略的に示す。

【図 7 b】図 7 b は、実施形態に係る駆動波形例を概略的に示す。

【図 7 c】図 7 c は、さらなる実施形態に係る試験回路を有する回路を概略的に示す。 10

【図 7 d】図 7 d は、さらなる駆動波形例を概略的に示す。

【図 8】図 8 は、専用の回路として実施される試験回路を概略的に示す。

【発明を実施するための形態】

【0045】

図 1 a は、公知の液滴堆積ヘッド（以下「プリントヘッド」）の一部の断面を概略的に示す。プリントヘッドは公知の液滴堆積装置（以下「プリンタ」）の一部であってもよい。

【0046】

本例では、プリントヘッド 1 は少なくとも 1 つの圧力室 2 を備え、圧力室 2 は、アクチュエータ素子 4 が付された膜 3 を有し、アクチュエータ素子 4 は膜 3 上に設けられ、ニュートラル位置としてここで示されている第 1 の位置（P 1 と示されている）との間で、圧力室内に向かって内部に第 2 の位置（P 2 と示されている）まで膜 3 の動きを実現する。P 1 から、P 2 の方向とは反対の方向に膜を撓ませる（すなわち圧力室の外部）ようにアクチュエータ素子 4 を配置することもできることが分かる。 20

【0047】

圧力室 2 は、圧力室 2 と流体連通する状態で配置されるリザーバ 1 6 から液を受ける液流入ポート 1 4 を備える。

【0048】

リザーバ 1 6 は図示のために圧力室 2 に隣接した状態でしか描かれていない。ただし、さらに上流に設けたり、出入りする液の流れを調整する一連のポンプ／バルブを適宜用いてプリントヘッドから離したりしてもよい。 30

【0049】

本例では、アクチュエータ素子 4 は、アクチュエータ素子 4 の両端間に電界を印加することでアクチュエータ素子 4 が充電され、これにより、アクチュエータ素子 4 に歪みが生じて変形するように、圧電材料 6 を第 1 の電極 8 と第 2 の電極 10 との間に設ける圧電アクチュエータ素子 4 として示されている。アクチュエータ素子を圧電アクチュエータ素子とすることには限定されず、電気容量応答を示す任意の適當なアクチュエータ素子 4 を適宜用いてもよいことが分かる。

【0050】

図 1 の概略例では、圧力室 2 は、一般的に「ルーフ様式（r o o f m o d e）」構成と呼ばれるもので構成され、これにより、膜 3 が撓むと、容積が変化し、したがって、圧力室 2 内で圧力が変化する。膜 3 に適當な撓み手順を適用することによって、十分な正圧が圧力室 2 内で発生して 1 つ以上の液滴が圧力室 2 から吐出される。 40

【0051】

下部電極 1 0 を接地電位などの基準電位に維持しつつ、電圧波形で形成される 1 つ以上の駆動パルスを関連アクチュエータ素子 4 に（例えば第 1 の電極 8 に）印加することによってノズル 1 2 からのこのようない液滴吐出を実現してもよい。駆動波形をきめ細かく設計することによって、ノズル 1 2 からの予測可能で均一な液滴吐出を実現することができる。

【0052】

実施形態では、プリントヘッド 1 は、プリントヘッド 1 に 1 つ以上の配列で配置される複数のアクチュエータ素子および関連する複数のノズルを備えてよい。

10

20

30

40

50

**【 0 0 5 3 】**

実施形態では、1つ以上の駆動パルスの列を備える共通駆動波形を駆動回路によって生成して、複数のアクチュエータ素子に関連するノズルから液滴を吐出するための駆動波形として複数のアクチュエータ素子に選択的に印加してもよい。

**【 0 0 5 4 】**

この代わりに、1つ以上の駆動パルスの列を備える駆動波形をアクチュエータ素子毎に生成してもよい。このような駆動波形は、例えば、プリントヘッド上の駆動回路によって生成したり、プリントヘッドと通信する駆動回路によって生成したりしてもよい。

**【 0 0 5 5 】**

ピクセルとして定義される受容媒体の所定のエリア内に（必要な場合には、受容媒体の動きを調整しつつ）正確に着弾するように液滴の吐出のタイミング合わせを行なってもよいことは、当業者であれば理解するであろう。

10

**【 0 0 5 6 】**

これらのピクセルは、印刷データから得られる印刷予定の画像のラスタ化に基づいており、受容媒体上の得られるドットの所望の位置を決定するのに用いられる。

**【 0 0 5 7 】**

単純な二値表現の場合は、各ピクセルに1つの液滴が入れられるか、液滴が入れられないかである。

**【 0 0 5 8 】**

より複雑な表現では、各ピクセルに2つ以上の液滴を印刷して得られるピクセルの知覚色濃度を変えることによってグレースケールレベルを付加することができる。

20

**【 0 0 5 9 】**

1つの圧力室2しか図1aに示されていないが、複数の圧力室をプリントヘッド1に適当な構成で配置してもよいと解される。

**【 0 0 6 0 】**

プリントヘッド1と、その関連特徴（例えば、1つ以上のノズル、1つ以上のアクチュエータ素子、1つ以上の膜、1つ以上の液ポートなど）とを、微小電気機械システム（*micro-electrical-mechanical systems*）（MEMS）プロセスやバルク製造プロセス（*bulk manufacturing process*）などの任意の適当な作製プロセスまたは技術を用いて作製してもよい。

30

**【 0 0 6 1 】**

ここに記載されている技術はループ様式構成で動作するプリントヘッドに限定されず、共有壁構成などの他の構成を持つプリントヘッドに同様に適用されると解される。

**【 0 0 6 2 】**

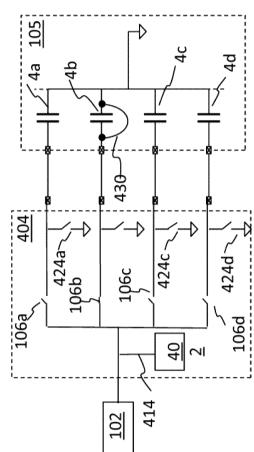

図1bは、上述の通り複数のアクチュエータ素子4を有するアクチュエータ素子アレイ105を備えるプリントヘッド回路100の例を概略的に示す。

**【 0 0 6 3 】**

プリントヘッド回路100は駆動回路102と電気接続する状態で設けられ、この状態で、駆動回路102は例えばアンプ（図示せず）を用いて駆動波形を生成する。

**【 0 0 6 4 】**

駆動回路102はスイッチ回路104と電気接続する状態で配置され、この状態で、スイッチ回路104は、アクチュエータ素子アレイ105の複数のアクチュエータ素子4に駆動波形を選択的に印加する複数のスイッチ106を備える。

40

**【 0 0 6 5 】**

本例では、スイッチ106は、電線108と、すべてのスイッチ106に共通のバス107とを介して駆動回路102に接続されている。代替例では、スイッチ106を各々、個々の電線を介して駆動回路102に接続してもよい。各スイッチ106は、関連するアクチュエータ素子4に、両者の間の個々のアクチュエータ線109を介して接続されている。

**【 0 0 6 6 】**

スイッチ回路104は集積回路であってもよく、例えば、特定用途向け集積回路（ASIC）

50

C)を備えてもよい。例えば、オンにして(例えば、閉じて)、対応するアクチュエータ素子が駆動回路と電気接続することを実現するように特定のスイッチを制御することで、駆動波形をアクチュエータ素子4に印加することができたり、例えば、オフにして(例えば、開いて)、駆動回路102からアクチュエータ素子を電気的に絶縁するように特定のスイッチを制御することができたりする点で、スイッチ回路104はマルチブレクサに機能的に類似する。単純にするために、駆動回路とアクチュエータ素子4との間の電気径路を「駆動経路」と呼ぶ。

#### 【0067】

本例では、アクチュエータ素子4は圧電アクチュエータ素子であり、このため、各アクチュエータ素子4の電気的挙動はコンデンサと同様であり、したがって、各アクチュエータ素子4は関連する静電容量C<sub>ACT</sub>を持つ。C<sub>ACT</sub>は、アクチュエータ素子4に関連する回路(例えばコンポネント/ロジック/機能)の静電容量、例えば、そのアクチュエータ線109の静電容量や、アクチュエータ素子をアクチュエータ線109に接続する物理的接続部の静電容量も含んでもよいと解される。

10

#### 【0068】

プリントヘッド回路100の別の回路/構成要素も関連する静電容量を持つことになる。本出願では、アクチュエータ素子に関連する静電容量C<sub>ACT</sub>以外の静電容量を「寄生容量」と考える。

#### 【0069】

図1b中、プリントヘッド回路100のすべての寄生容量をC<sub>PAR</sub>と示し、これは、電線108の寄生容量(C<sub>path</sub>)と、すべてのスイッチ106の複合寄生容量(C<sub>all 1 switches</sub>) (個々のスイッチ106の寄生容量(C<sub>switch</sub>))と、他の寄生容量(C<sub>other</sub>) (駆動回路102と、プリントヘッド回路100の構成要素間の接続部とに関連する寄生容量など)とを含む。このような構成要素は、駆動回路102と電線108との間またはスイッチ回路104と電線108との間の物理的結合部を含んでもよい。このような結合部は異方性導電フィルム結合部を含んでもよい。

20

#### 【0070】

上記で詳述されているように、1つ以上の診断試験を行なう、例えば、製造後およびプリントヘッドに組み込む前後でアクチュエータ素子の静電容量の定量、および/またはアクチュエータ素子アレイ105中の断線または短絡の検出を行なうことは有用である。いくつかの例では、定量静電容量で断線や短絡を表わす場合がある。例えば、所定の閾値静電容量未満の定量静電容量で断線を表わす場合がある。

30

#### 【0071】

しかし、このような試験は、例えば、プリントヘッドのアクチュエータ素子アレイの配置が原因で行なうのが困難であったり、このような試験は、例えば、試験結果に影響する寄生容量が原因で不正確であったりする場合がある。

#### 【0072】

図2aは、実施形態に係るプリントヘッド回路100のアクチュエータ素子4に診断試験を行なう試験回路200の例を概略的に示す。同様の特徴を記述するのに同様の符号付けを全体にわたって用いる。

40

#### 【0073】

試験回路200は、電線108と、スイッチロジック104の対応するスイッチ106とを介して1つ以上のアクチュエータ素子4と電気接続する状態で配置される(1つのアクチュエータ素子4のみを図2aに示す)。

#### 【0074】

単純にするために、試験回路200とアクチュエータアレイ105との間の電気径路を「試験経路」と考え、このように考えると、適宜、1つ以上のアクチュエータ素子を試験経路に電気的に接続したり、絶縁させたりするようにスイッチ106を制御することができる。

#### 【0075】

50

図 2 a 中、試験回路 200 は、例えば、プリンタまたはプリントヘッドのインターフェースを介してプリントヘッド回路 100 と電気接続するように示されている。他の例では、プリントヘッド回路 100 の一部として試験回路 200 を組み込んでもよい。

#### 【0076】

試験回路 200 は、コントローラ 202、電源 204 および測定回路 205 を備える。

#### 【0077】

コントローラ 202 は、例えば、フィールドプログラマブルゲートアレイ (FPGA)、マイクロコントローラまたは他の適当な回路（例えば、コンポネント、ロジック、機能）を備えてもよい。

#### 【0078】

コントローラ 202 は、プリントヘッド回路 100、駆動回路（図 2 a には示されていない）および / またはプリンタ上の他の回路（図示せず）などの、試験回路 200 中の様々な回路および構成要素と接続される。例えば、コントローラ 202 がスイッチ 106 を制御することで、診断試験を行なう試験回路 200 に 1 つ以上のアクチュエータ素子 4 を適時に接続することができる。

10

#### 【0079】

以下の例では、電源 204 は定電流 ( $i_M$ ) を生成する電流源であり、そのレベルはコントローラ 202 によって定められる。明確になるように、アクチュエータ素子を線形的に充電して静電容量測定の正確度を改善するために、電流源 204 は好ましくは高い出力インピーダンスを持つ。

20

#### 【0080】

測定回路 205 は、診断試験中、試験経路上で感知すなわち測定を行なって 1 つ以上の値を処理するように構成されている。

#### 【0081】

本例では、測定回路 205 は、電源 208、209、コンパレータ 210、211 およびタイマ 212 を備える。

#### 【0082】

リセットスイッチ 206 は試験経路を放電するように設けられ、試験経路を基準電圧（例えばグランド）に接続する任意の適当なスイッチ素子（例えば NMOS ドラッグ）であってもよい。リセットスイッチ 206 はコントローラ 202 によって制御可能である。

30

#### 【0083】

電源 208、209 は、以下の例では、デジタル・アナログコンバータ (DAC) として示されており、各々は所定の電圧レベル (DAC 208 による VHIGH、および DAC 209 による VLOW として示されている) を生成する。DAC 208、209 が生成する電圧レベルをコントローラ 202 からの信号（図示せず）に応じて定めてよい。

#### 【0084】

コンパレータ 210、211 は各々、DAC 208、209 によって定められる第 1 の入力としての電圧レベルと、試験経路からの第 2 の入力としての電圧  $V_X$  とのうちの 1 つを用いる。図 2 a 中、コンパレータ 210 への第 1 の入力が DAC 208 からの VHIGH である一方で、コンパレータ 211 への第 1 の入力は DAC 209 からの VLOW である。

40

#### 【0085】

タイマ 212 はコンパレータ 210、211 の出力を受けて、VLOW から VHIGH への  $V_X$  の遷移の時間を測定する。タイマ 212 はクロック周波数 FCLK で動作し、クロック周波数 FCLK は任意の適当な周波数（例えば ~10MHz）で動作する任意の適当な周波数源によって生成される。クロック周波数を高くすることによってそれによる測定の正確度を改善することができる事が分かる。タイマ 212 を FPGA またはマイクロコントローラで実施してもよいし、専用集積回路 (IC) として実施してもよい。代替例では、タイマ 212 をコントローラ 202 に組み込んでもよい。

#### 【0086】

試験回路 200 を用いてアクチュエータ素子 4 の静電容量 CACT を決定することができ

50

、図2 bは、その場合の実施形態に係るC A C Tの決定の際に試験回路200を用いて得られる測定値をグラフで示す。

#### 【0087】

一例として、第1の試験期間P1に、コントローラ202は、リセットスイッチ206を閉じて寄生容量C<sub>PAR</sub>（いくつかの例では、静電容量C<sub>ACT</sub>）を放電することにより試験経路中の静電容量をリセットした状態で、スイッチ106を閉じ、リセットスイッチ206を開くことで、電流i<sub>M</sub>を備える試験入力により複合静電容量C<sub>PAR</sub>+C<sub>ACT</sub>が充電され、これにより、図2 bに示されているように、電圧V<sub>X</sub>は式（1）によって与えられる比率で時間（T）とともに上昇する。

#### 【0088】

#### 【数1】

$$(1) \quad \left| \frac{dV}{dt} \right|_I = \frac{(i_M)}{(C_{PAR} + C_{ACT})}$$

#### 【0089】

V<sub>X</sub>はコンパレータ210、211への入力であり、V<sub>X</sub>が上昇すると、タイマ212はV<sub>LOW</sub>コンパレータ211の切り替わり（すなわち、V<sub>X</sub>がV<sub>LOW</sub>を通過する）とV<sub>HIGH</sub>コンパレータ210の切り替わり（すなわち、V<sub>X</sub>がV<sub>HIGH</sub>を通過する）との間の遷移時間（t<sub>1</sub>）を測定する。

#### 【0090】

測定された遷移時間（t<sub>1</sub>）は式（2）および式（3）から得られる。

#### 【数2】

$$(2) \quad \left| \frac{dV}{dt} \right|_I = \frac{(V_{HIGH} - V_{LOW})}{t_1}$$

#### 【数3】

$$(3) \quad t_1 = \frac{(C_{(PAR)} + C_{(ACT)}) (V_{HIGH} - V_{LOW})}{i_M}$$

#### 【0091】

したがって、全静電容量は（4）から決定される。

#### 【数4】

$$(4) \quad (C_{(PAR)} + C_{(ACT)}) = \frac{i_M t_1}{(V_{HIGH} - V_{LOW})}$$

#### 【0092】

したがって、C A C Tは（5）から計算することができる。

#### 【数5】

$$(5) \quad C_{ACT} = \frac{i_M t_1}{(V_{HIGH} - V_{LOW})} - C_{PAR}$$

#### 【0093】

しかし、C<sub>PAR</sub>は未知であるので、（C<sub>(PAR)</sub>+C<sub>(ACT)</sub>）を用いてもC A C

10

20

30

40

50

Tの正確な決定が実現されず、したがって、C A C Tを用いても断線の有無が最終的に示されない場合がある。

【0094】

寄生容量C P A R ,について推定値を考えることができるが、すべての回路についてのバッチ処理とバッチ処理との間の変動が寄生容量とアクチュエータ静電容量との両方に影響する場合があるため、この変動により寄生容量を正確に推定する困難が増す場合がある。

【0095】

したがって、より正確にC A C Tを決定するために、試験回路により2つの期間P<sub>1</sub>'およびP<sub>2</sub>'にわたって2回の測定を行ない、図2cは、その場合のさらなる実施形態に係るC A C Tの決定の際に試験回路200を用いて得られる測定値をグラフで示す。

10

【0096】

較正期間であると考えることができる第1の期間P<sub>1</sub>'に、コントローラ202は、試験経路中の静電容量をリセットした状態で、スイッチ106を開き、リセットスイッチ206を開くことで、試験入力電流i<sub>M</sub>によりP<sub>1</sub>',中に寄生容量C P A Rが充電され、これにより、図2cに示されているように、電圧V<sub>X</sub>は(6)によって与えられる比率で時間とともに上昇する。

【0097】

【数6】

$$(6) \quad \left| \frac{dV}{dt} \right|_I = \frac{(i_M)}{(C_{PAR})}$$

20

【0098】

V<sub>X</sub>が上昇すると、タイマ212はV<sub>LOW</sub>コンパレータ211の切り替わりとV<sub>HIGH</sub>コンパレータ210の切り替わりとの間の遷移時間(t<sub>1</sub>)を測定する。

【0099】

測定された遷移時間(t<sub>1</sub>)は(7)から得られる。

【数7】

$$(7) \quad t_1 = \frac{(C_{PAR})(V_{HIGH} - V_{LOW})}{i_M}$$

30

【0100】

したがって、寄生容量は(8)から決定される。

【数8】

$$(8) \quad C_{PAR} = \frac{i_M t_1}{(V_{HIGH} - V_{LOW})}$$

40

【0101】

試験期間であると考えることができる第2の期間P<sub>2</sub>'に、コントローラ202はリセットスイッチ206を閉じて試験経路中の静電容量をリセットした後、スイッチ106を閉じ、リセットスイッチ206を開くことで、試験入力電流i<sub>M</sub>により複合静電容量C P A R + C A C Tが充電され、これにより、図2cに示されているように、電圧V<sub>X</sub>は(9)によって与えられる比率で時間とともに上昇する。

【0102】

【数9】

50

$$(9) \quad \left| \frac{dV}{dt} \right|_2 = \frac{(i_M)}{(C_{PAR} + C_{ACT})}$$

## 【0103】

$V_X$  が上昇すると、タイマ 212 は  $V_{LOW}$  コンパレータ 211 の切り替わりと  $V_{HIGH}$  ハコンパレータ 210 の切り替わりとの間の遷移時間  $t_2$  を測定し、これは (10a) によって与えられる。

## 【数10】

$$(10a) \quad t_2 = \frac{(C_{PAR} + C_{ACT}) (V_{HIGH} - V_{LOW})}{i_M}$$

10

## 【0104】

したがって、全静電容量を 10b により決定することができる。

## 【数11】

$$(10b) \quad (C_{PAR} + C_{ACT}) = \frac{i_M t_2}{(V_{HIGH} - V_{LOW})}$$

20

(8) の C\_PAR に代入して C\_ACT を決定することができる。

## 【数12】

$$(11) \quad C_{(ACT)} = \frac{i_M}{(V_{HIGH} - V_{LOW})} (t_2 - t_1)$$

## 【0105】

したがって、較正期間を用いて最初に C\_PAR を決定する場合、C\_PAR を推定することと比較してより正確に C\_ACT を決定することができる。したがって、C\_ACT に基づいて、またはそれに応じて断線の有無をより正確に検出することもまた可能である。

30

## 【0106】

図 3a は、スイッチ 106 の例と、実施形態に係るスイッチ制御回路 300 とを概略的に示し、図 3b は 1 つ以上のアクチュエータ素子を駆動するのに用いる駆動波形 310 の例を示す。

## 【0107】

本例では、スイッチ 106 は 2 つのスイッチ素子を備え、例えばパスゲート構成で直列に配置されているトランジスタ 302、304 として示されている。このような配置により印刷中に高電圧・大電流動作が実現される。スイッチ 106 のスイッチ素子はトランジスタとして示されているが、スイッチ素子をトランジスタにすることに限定されず、また、スイッチ素子の数を 2 にすることに限定されない。

40

## 【0108】

スイッチ 106 の ON 抵抗を最小にすることで、プリントヘッド回路での電力散逸を（例えば、コンダクタ ( $I^2 R$ ) 損失を低減することによって）最小にし、駆動波形 310 の形状（例えば、エッジおよびスルーレート）を最適化することで、所望の液滴速度および液滴容積を得ることが有効である。

## 【0109】

本例では、トランジスタ 302、304 は共通のソースを共有する。トランジスタ 302 のドレインは端子 306 を介して駆動回路 / 試験回路（図示せず）と電気接続する状態で配置され、トランジスタ 304 のドレインは端子 308 を介してアクチュエータ素子（図示せず）と電気接続する状態で配置されている。また、各トランジスタ 302、304 は

50

、電流がソースからドレインに（矢印で示されているように）流れるように、各トランジスタ 302、304 のソースとドレインとの間に配置されているそれぞれのダイオード 316、318 を有する。ダイオード 316、318 各々は、トランジスタ 302、304 に内蔵されたダイオードであってもよい。

#### 【0110】

スイッチ 106 をオンにするために（すなわち、スイッチを閉じるために）、約 5 V の電位差を各トランジスタ 302、304 のソースとゲートとの間に印加する。

#### 【0111】

0 V ~ 20 V で遷移する図 3 b に示されている駆動波形 310 のような駆動波形が異なる電圧の間で遷移する際、要求時にトランジスタ 302、304 がオンに維持されるために、共通のソースの電圧がこれらの異なる電圧に応答することが必要である。10

#### 【0112】

このような制御は、駆動波形 310 が異なる電圧の間で遷移する際に共通のソース電圧の上にある可変電圧を生成して必要な電位差を提供するように構成されているレベルシフタ 301 を備えるスイッチ制御回路 300 によって実現される。

#### 【0113】

レベルシフタ 301 が端子 312 を介して電力供給される一方で、端子 314 を介して例えば駆動回路から受けるレベル信号に応じて可変電圧を生成してもよい。

#### 【0114】

レベルシフタ 301 によって寄生電流  $i_p$  が生成され、この状態で、 $i_p$  はスイッチ 106 が閉じられるときに共通のソースを流れ、スイッチ 106 が開かれるときにも共通のソースを流れる。20

#### 【0115】

他の実施形態では寄生電流  $i_p$  をレベルシフタ以外の構成要素 / 回路で生成してもよいことは当業者であれば理解するであろう。

#### 【0116】

スイッチ 106 が開かれると、 $i_p$  はダイオード 316 を介して端子 306 に流れることができ、このとき、 $i_p$  は（例えば駆動回路中のアンプによって）シンクされる。これに加えて、または、これの代わりに、電流  $i_p$  はダイオード 318 を介して端子 308 に流れることができ、これにより、電流  $i_p$  により端子 308 と電気接続されるアクチュエータ素子が充電される。したがって、スイッチ 106 が開かれると、 $i_p$  は寄生電流であるように見える。30

#### 【0117】

スイッチ 106 がオフであるときに  $i_p$  が流れる方向を制御するために、スイッチ 106 の両側（例えば端子 306、308）の電圧を試験回路 200 によって、例えばさらなる D A C（図 3 に示されていない）を用いて設定して、端子 306、308（または、これと接続されているアクチュエータ素子などの回路）にバイアスをかけてよい。したがって、試験回路 200 は端子 306、308 にバイアスをかけて、スイッチ 106 が開かれると確実に  $i_p$  がダイオード 318 を流れないようにすることができる。

#### 【0118】

図 4 a は実施形態に係るプリントヘッド回路 100 のアクチュエータ素子 4 に診断試験を行なう試験回路 200 の例を概略的に示し、本図によれば、アクチュエータ素子 4 は関連するスイッチ制御遠回り 300 を有するスイッチ 106 に接続されており、これにより、上述のように寄生電流  $i_p$  によってアクチュエータ素子 4 が充電される。

#### 【0119】

図 4 b はさらなる実施形態に係る C A C T の決定の際に図 4 a の試験回路 200 を用いて得られる測定値をグラフで示す。

#### 【0120】

上記のように、アクチュエータ素子 4 の静電容量 C A C T を決定することは有用である場合がある。しかし、図 4 a に示されている回路には複数の未知の値がある。例えば、アク40

チュエータ静電容量 (C A C T)、寄生容量 (C P A R) および寄生電流 ( $i_p$ ) が未知である。

【0121】

したがって、より正確に C A C T を決定するために、試験回路 202 は、3つの期間  $P_1'$ 、 $P_2'$  および  $P_3'$  にわたって 3 回の測定を行なう。

【0122】

第 1 の較正期間であると考えることができる第 1 の期間  $P_1'$  に、コントローラはリセットスイッチ 206 を開き、スイッチ 106 を閉じ、 $i_M$  を生成してスイッチ 106 および / またはアクチュエータ素子 4 の端子にバイアスをかけるように電流源 204 を制御して  $i_p$  の方向を制御することで、 $i_p$  を備える試験入力により寄生容量 C P A R が充電されることになる。 10

【0123】

アクチュエータ素子 4 にバイアスがかけられると、コントローラ 202 はスイッチ 106 を開いて試験経路からアクチュエータ素子 4 を電気的に絶縁し、リセットスイッチ 206 を閉じ、電流源 204 を制御して  $i_M$  が流れないようにすることで、試験経路中の C P A R が放電する。

【0124】

コントローラ 202 はリセットスイッチ 206 を開き、スイッチ 106 を開き、 $i_M$  が流れないように電流源 204 を制御する。

【0125】

図 4 b に示されているように、電圧  $V_X$  は以下によって与えられるスルーレート  $S R_1$  で  $i_p$  に応じて  $P_1'$  中に時間とともに上昇する。 20

【数 13】

$$(12) \quad SR_1 = \left| \frac{dV}{dt} \right|_1 = \frac{(i_p)}{(C_{PAR})}$$

【0126】

第 2 の較正期間を表わすと考えることができる第 2 の期間  $P_2'$  に、コントローラ 202 はスイッチ 106 を閉じ、リセットスイッチ 206 を開き、 $i_M$  を生成してスイッチ 106 および / またはアクチュエータ素子 4 の端子にバイアスをかけるように電流源 204 を制御して  $i_p$  の方向を制御することで、 $i_p$  を備える試験入力により寄生容量 C P A R が充電されることになる。 30

【0127】

その後、コントローラ 202 はスイッチ 106 を開いて試験経路からアクチュエータ素子 4 を電気的に絶縁し、リセットスイッチ 206 を閉じ、 $i_M$  が流れないように電流源 204 を制御することで、試験経路中の C P A R が放電する。

【0128】

コントローラ 202 はリセットスイッチ 206 を開き、スイッチ 106 を開き、 $i_M$  を生成するように電流源 204 を制御することで、( $i_p + i_M$ ) を備える試験入力により第 2 の較正期間  $P_2'$  中に寄生容量 C P A R が充電される。 40

【0129】

図 4 b に示されているように、以下によって与えられるスルーレート  $S R_2$  で  $P_2'$  中に電圧  $V_X$  は上昇する。

【数 14】

$$(13) \quad SR_2 = \left| \frac{dV}{dt} \right|_2 = \frac{(i_p + i_M)}{(C_{PAR})}$$

10

20

40

50

## 【0130】

したがって、(12)および(13)から

## 【数15】

$$(14) \quad \frac{(SR_2)}{(SR_1)} = \frac{(i_p + i_M)}{(i_p)}$$

## 【0131】

試験期間を表わすと考えることができる第3の期間P<sub>3</sub>’’に、コントローラ202は、アクチュエータ素子4を試験経路に電気的に接続するようにスイッチ106を閉じ、リセットスイッチ206を開じ、i<sub>M</sub>が流れないようにするように電流源204を制御することで、試験経路中のPARが放電する。

10

## 【0132】

コントローラ202はリセットスイッチ206を開き、スイッチ106を開じ、i<sub>M</sub>を生成するように電流源204を制御することで、(i<sub>p</sub> + i<sub>M</sub>)を備える試験入力により、P<sub>3</sub>’’中に複合した寄生コンデンサとアクチュエータコンデンサとが全静電容量(PAR + CAPT)まで充電される。

20

## 【0133】

図4bに示されているように、以下によって与えられるスルーレートSR<sub>3</sub>でP<sub>3</sub>’’中に電圧V<sub>X</sub>は上昇する。

## 【数16】

$$(15) \quad SR_3 = \left| \frac{dV}{dt} \right|_3 = \frac{(i_p + i_M)}{(C_{PAR} + C_{ACT})}$$

## 【0134】

所定の遷移期間z中のスルーレートは以下によって与えられる。

## 【数17】

$$(16) \quad SR_z = \frac{(V_{HIGH} - V_{LOW})}{t_z} \text{ または } t_z = \frac{(V_{HIGH} - V_{LOW})}{SR_z}$$

30

## 【0135】

したがって、(14)を書き換えることで以下が得られる。

## 【数18】

$$(17) \quad \frac{(i_p + i_M)}{(i_p)} = \frac{\left( \frac{(V_{HIGH} - V_{LOW})}{t_2} \right)}{\frac{(V_{HIGH} - V_{LOW})}{t_1}} = \frac{(t_1)}{(t_2)}$$

40

## 【0136】

したがって

## 【数19】

$$(18) \quad \frac{(i_M)}{(i_p)} = \frac{(t_1)}{(t_2)} - 1$$

さらに、(15)を書き換えてSR<sub>3</sub>に代入することで以下が得られる。

50

## 【数20】

$$(19) \quad C_{ACT} = \frac{(i_M + i_p)t_3}{(V_{HIGH} - V_{LOW})} - C_{PAR}$$

(12) および (16) から

【数21】

$$(20) \quad i_p = C_{PAR} \frac{(V_{HIGH} - V_{LOW})}{t_1}, \quad \text{および} \quad C_{PAR} = \frac{i_p t_1}{(V_{HIGH} - V_{LOW})}$$

10

【0137】

$i_p$  および (20) の  $C_{PAR}$  を (19) に代入することで以下が得られる。

【数22】

$$(21) \quad C_{ACT} = \frac{(i_M + i_p)t_3}{(V_{HIGH} - V_{LOW})} - \frac{i_p t_1}{(V_{HIGH} - V_{LOW})} = \frac{i_M t_3 + i_p(t_3 - t_1)}{(V_{HIGH} - V_{LOW})} = \frac{i_M}{(V_{HIGH} - V_{LOW})} \left[ t_3 + \frac{i_p}{i_M} (t_3 - t_1) \right]$$

20

【0138】

書き換えることで以下が得られる。

【数23】

$$(22) \quad C_{ACT} = \frac{i_M}{(V_{HIGH} - V_{LOW})} \left[ t_3 + \frac{(t_3 - t_1)}{\left(\frac{i_M}{i_p}\right)} \right]$$

30

【0139】

(18) を (22) に代入することで以下が得られる。

【数24】

$$(23) \quad C_{ACT} = \frac{i_M}{(V_{HIGH} - V_{LOW})} \left[ t_3 + \frac{\left( \frac{t_3 - t_1}{\left( \frac{t_1}{t_2} - 1 \right)} \right)}{\left( \frac{t_1}{t_2} - 1 \right)} \right]$$

40

【0140】

書き換えることで以下が得られる。

【数25】

$$(24) \quad C_{ACT} = \frac{i_M}{(V_{HIGH} - V_{LOW})} \left[ t_3 + \frac{t_2(t_3 - t_1)}{(t_1 - t_2)} \right]$$

【0141】

(24) から、制御した電流  $i_M$ 、および設定した  $V_{HIGH}$  と  $V_{LOW}$  との差とともに、3つの測定した遷移時間  $t_1$ 、 $t_2$  および  $t_3$  から  $C_{ACT}$  を決定することができる。

【0142】

上述の実施形態では、個々の期間（例えば較正 / 試験期間）の  $V_{HIGH}$  および  $V_{LOW}$

50

の値は実質的に等しい。しかし、代替実施形態では、VHIGHおよびVLOWのそれぞれの値を所定の期間中に修正してCACTを決定する正確度を高くしてもよい。

#### 【0143】

スイッチ106が開かれている間に $i_p$ が流れないようにするように図3aのレベルシフタを制御することができるが、レベルシフタの制御に無関係にスイッチ106が閉じられると $i_p$ は流れる。しかし、スイッチが開かれている間に $i_p$ を測定しない限り、 $i_p$ を決定することができず、したがって、決定されたCACTの正確度は $i_p$ により下がる。

#### 【0144】

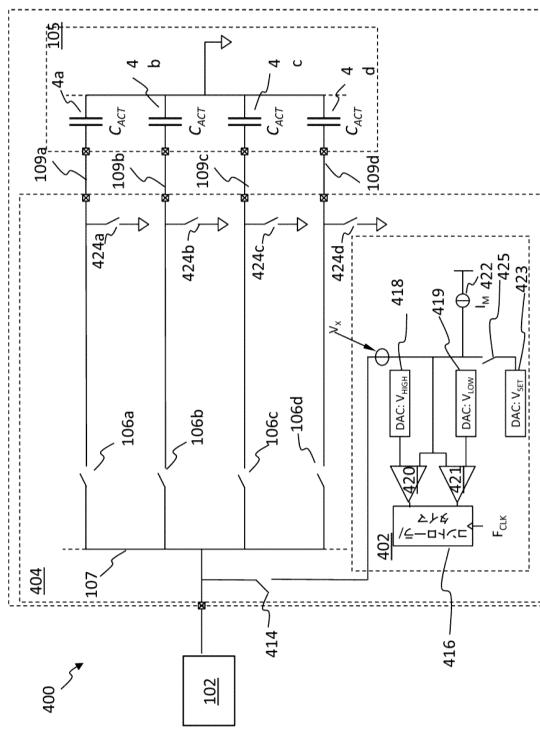

図5aはさらなる実施形態に係るプリントヘッド回路400を概略的に示し、本図によれば、試験回路402はプリントヘッド回路400のスイッチ回路404に組み込まれ、この状態で、プリントヘッド回路400は上述のようにアクチュエータ素子アレイ105も含む。

10

#### 【0145】

上記のように、アクチュエータ素子アレイ105は、バス107を介して駆動回路102と電気接続する状態で配置されている複数のアクチュエータ素子4a～4dを備え、したがって、スイッチ106は必要に応じて関連するアクチュエータ素子を駆動経路に選択的に接続する。

#### 【0146】

試験回路402は複数のアクチュエータ素子4a～4dと電気接続する状態で配置され、したがって、試験スイッチ414は試験回路402をバス107に選択的に接続する。試験スイッチ414は、任意の適当な形態をとってもよく、例えば、1つ以上のトランジスタを備えてもよい。

20

#### 【0147】

また、試験されるアクチュエータ素子4はバス107および試験回路(スイッチ414が閉じられる場合)に、関連するスイッチ106a～dをオンにすることによって接続される。

#### 【0148】

通常、試験回路402が約5Vの電圧で動作する一方で、駆動回路102は>5Vの波形を生成する。したがって、例えば、駆動回路102がアクチュエータ素子の1つ以上を駆動しているときに、駆動電流/電圧によって試験回路402が損傷するのを避けるよう、試験スイッチ414により試験回路402を駆動経路から電気的に絶縁してもよい。

30

#### 【0149】

コントローラ416を用いて(例えば、駆動回路または他の回路からの信号に応じて)試験スイッチ414を制御してもよい。

#### 【0150】

試験回路402は図2aおよび図4aで説明されている試験回路と同様であり、したがって、本例では、試験回路402は、VHIGHおよびVLOWを生成するDAC418、419と、コンパレータ420、421と、定電流 $i_M$ を生成する電流源422とを備える。タイマは、コントローラ402に組み込まれるものとして示されている。

40

#### 【0151】

試験回路402はVSETを生成するDAC423をさらに備え、バイアススイッチ425が閉じられると、DAC423は、例えば、寄生電流 $i_p$ の流れの方向を制御するよう、試験経路上の回路にバイアスをかけることができる。

#### 【0152】

試験回路402を用いてアクチュエータ素子4の1つ以上の静電容量を決定することにより、上述のようにアクチュエータ素子の1つ以上の両端間の断線を検出してもよい。アクチュエータ素子4の両端間の断線は、アクチュエータ素子に関連する電線109などの電線の両端間の断線を含むものとも考えられる。

#### 【0153】

試験回路402は、アクチュエータ素子の両端間の短絡などの他の不具合を検出するのに

50

も用いてよい。

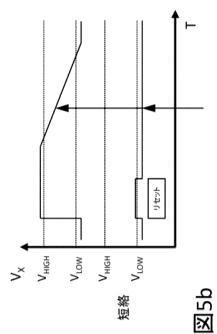

**【 0 1 5 4 】**

図 5 b は、アクチュエータ素子 4 b の両端間の短絡 4 3 0 の検出を概略的に示す。スイッチ 1 0 6 b および 4 1 4 が閉じられることで、アクチュエータ素子 4 b が試験経路を介して試験回路 4 0 2 と電気接続される。

**【 0 1 5 5 】**

電流源 4 2 2 (図 5 a に示されている) がオンにされ、アクチュエータ素子の両端間に短絡 4 3 0 があると、アクチュエータ素子 4 b は充電されない。その両端間に短絡がない場合、アクチュエータ素子 4 b が充電され、その後のアクチュエータ素子の放電が試験経路から  $V_X$  としてコンパレータに入力される。この構成によれば、本例では、 $V_X \quad V_{LOW}$   $V_X \quad V_{HIGH}$  10 がアクチュエータ素子 4 b の両端間の短絡を示す一方で、 $V_{LOW} \quad V_X \quad V_{HIGH}$  は短絡がないことを示す。

**【 0 1 5 6 】**

しかし、試験回路 4 0 2 は、特定のアクチュエータ素子からの放電を測定してその両端間の短絡を検出する (または短絡がないことを検出する) ものに限定されず、代替例では、このような短絡を示すのに異なる測定を考えてもよい。例として、指定期間内に閾値レベルに達しない  $V_X$  によりアクチュエータ素子の両端間の短絡を示してもよい。

**【 0 1 5 7 】**

本実施形態では、各アクチュエータ素子 4 は関連する放電スイッチ 4 2 4 にも接続され、放電スイッチ 4 2 4 を用いて、例えば、閉じられてグランドに接続されるときにその関連するアクチュエータ素子 4 を (例えばグランドに) 放電することができる。

**【 0 1 5 8 】**

放電スイッチ 4 2 4 はトランジスタを備えてもよく、コントローラ 4 1 6 によって制御されるスイッチロジック 4 0 4 中に設けてよい。放電スイッチを適切に制御することによって、アクチュエータ素子アレイ 1 0 5 中のアクチュエータ素子間 (例えば隣接するアクチュエータ素子間) の短絡 (アクチュエータ素子の電線 1 0 9 間の短絡も含んでもよい) を検出するのにも試験回路 4 0 2 を用いることができる。

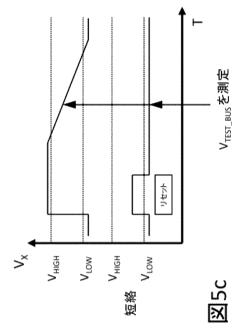

**【 0 1 5 9 】**

図 5 c はアクチュエータ素子 4 b および 4 c 間の短絡 (短絡 4 3 2 と示されている) の検出を概略的に示し、本図によれば、スイッチ 1 0 6 b および 4 1 4 が閉じられることで、アクチュエータ素子 4 b が試験経路を介して試験回路 4 0 2 と電気接続する。放電スイッチ 4 2 4 c も閉じられて、アクチュエータ素子 4 c を放電する経路が設けられる。

**【 0 1 6 0 】**

電流源 4 2 2 (図 5 a に示されている) がオンにされ、隣接するアクチュエータ素子 4 b および 4 c 間に短絡 4 3 2 が存在すると、放電スイッチ 4 2 4 c により放電経路が設けられることになり、アクチュエータ素子 4 b は充電されないことになる。短絡がない場合、アクチュエータ素子 4 b が充電され、その後の放電が試験経路から  $V_X$  としてコンパレータに入力される。この構成によれば、本例については、 $V_X \quad V_{LOW}$  がアクチュエータ素子 4 b および 4 c の両端間の短絡を示す一方で、 $V_{LOW} \quad V_X \quad V_{HIGH}$  は短絡がないことを示す。このような試験は隣接するアクチュエータ素子に限定されず、アクチュエータ素子アレイ 1 0 5 中の任意の数のアクチュエータ素子間の試験を含んでもよいと解される。

**【 0 1 6 1 】**

しかし、試験回路 4 0 2 は、特定のアクチュエータ素子からの放電を測定してアクチュエータ素子間の短絡を検出する (または短絡がないことを検出する) ものに限定されず、代替例では、このような短絡を検出するのに異なる測定を考えてもよい。例えば、指定期間内に閾値レベルに達しない  $V_X$  によりアクチュエータ素子間の短絡を示してもよい。

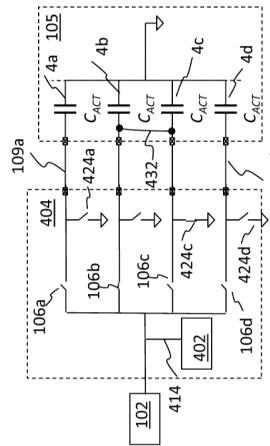

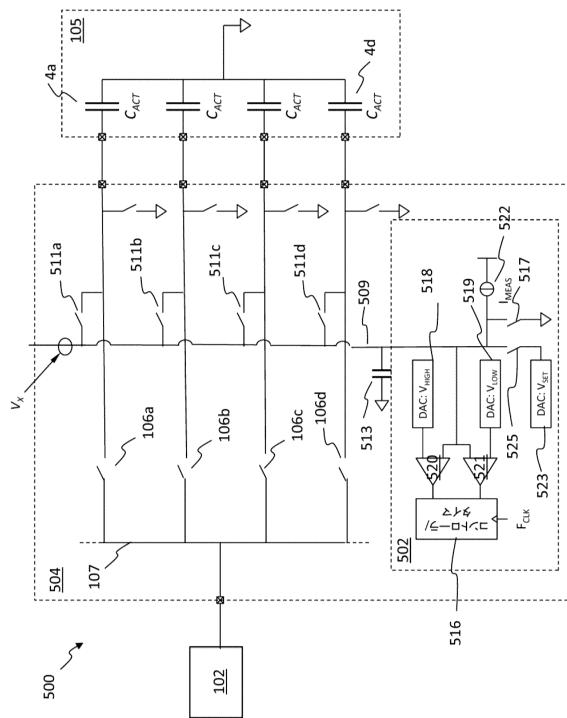

**【 0 1 6 2 】**

図 6 はさらなる実施形態に係るプリントヘッド回路 5 0 0 を概略的に示し、本図によれば、試験回路 5 0 2 はプリントヘッド回路 5 0 0 のスイッチ回路 5 0 4 に組み込まれ、この

10

20

30

40

50

状態で、プリントヘッド回路 500 は上述のようにアクチュエータ素子アレイ 105 も含む。

#### 【0163】

上記のように、アクチュエータ素子アレイ 105 は、バス 107 を介して駆動回路 102 と電気接続する状態で配置されている複数のアクチュエータ素子 4a ~ 4d を備え、したがって、スイッチ 106 は関連するアクチュエータ素子をバス 107 に選択的に接続する。

#### 【0164】

試験回路 502 は図 5a で説明されている試験回路と同様であり、したがって、本例では、試験回路 502 は、VHIGH および VLOW を生成する DAC 518、519 と、コンパレータ 520、521 と、定電流  $i_M$  を生成する電流源 522 と、VSET を生成する DAC 523 と、バイアススイッチ 525 を備える。

10

#### 【0165】

したがって、試験回路 502 は、アクチュエータ素子 4 のうちの 1 つ以上の静電容量を決定し、アクチュエータ素子の両端間の断線を検出し、および / またはアクチュエータ素子の両端間 / アクチュエータ素子間の閉路を検出するのに用いることができるが分かる。

#### 【0166】

本実施形態では、アクチュエータ素子 4a ~ 4d は専用の試験バス 509 を介して試験回路 502 と電気接続する状態で配置され、したがって、試験スイッチ 511 は、必要に応じて、関連するアクチュエータ素子を試験バス 509 に選択的に接続する。試験スイッチ 511 は任意の適当な形態をとってもよく、例えば、1 つ以上のトランジスタを備えてよい。試験スイッチ 511 はコントローラ 516 によって制御可能であり、および / または他の回路によって制御してもよい。

20

#### 【0167】

理解されるであろうが、試験バス 509 は関連する静電容量 513 を持つことになり、これは、アクチュエータ素子の静電容量を測定して断線を検出するための寄生容量であると考えられる。

#### 【0168】

本実施形態では、試験回路 502 は、試験バス 509 と電気接続されて、必要に応じて寄生容量 513 を放電する放電スイッチ 517 を含む。

#### 【0169】

試験バス 509 構成により、試験バス 509 と駆動回路 102 との間の強い電気絶縁が実現される。これは、試験回路 502 がアクチュエータ素子に診断試験を行なうときに、駆動回路 102 が試験回路 502 から電気的に絶縁されることを確実とするようにスイッチ 106 を（例えば、試験回路中のコントローラ、駆動回路中のコントローラまたは他の適当な制御回路によって）制御することができるからである。

30

#### 【0170】

さらに、上述のように、スイッチ 106 の ON 抵抗を最小にすることが有効である場合がある。しかし、スイッチの ON 抵抗を最小にすると、その寄生容量が増大する。

#### 【0171】

試験スイッチ 511 を用いてアクチュエータ素子 4 を試験バス 509 に接続し、駆動回路 102 がアクチュエータ素子 4 を駆動する間に開くように試験スイッチ 511 を制御すると、試験スイッチ 511 は駆動波形にほぼ影響しない。したがって、試験スイッチ 511 の ON 抵抗をスイッチ 106 と比較して高くすることができ、試験スイッチ 511 の寄生容量をスイッチ 106 と比較して低減することができる。

40

#### 【0172】

したがって、図 5a で説明されているバス 107 を介する試験経路の寄生容量と比較して、試験バス 509 を介する試験経路の寄生容量を低減することができる。この結果、専用の試験バス 509 を介する試験経路についての診断試験の感度と、特に特定のアクチュエータ素子の CACT の決定の正確度とが改善される場合がある。

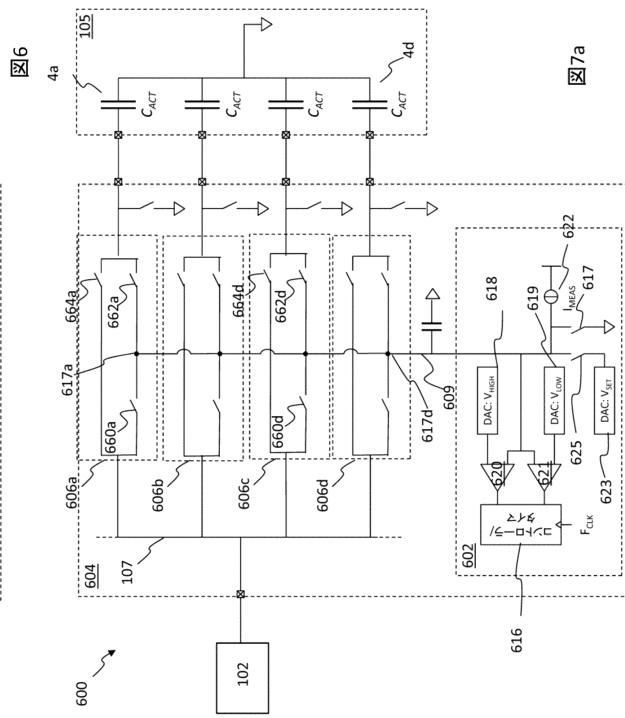

#### 【0173】

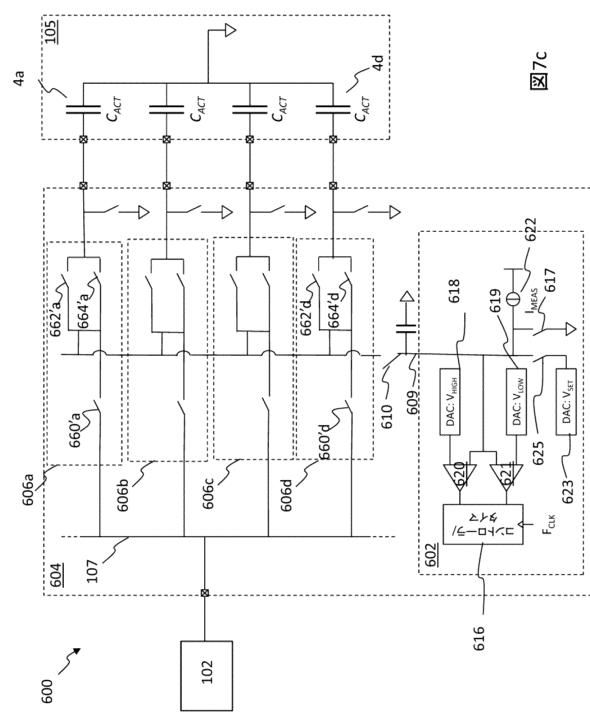

図 7 a はさらなる実施形態に係るプリントヘッド回路 600 に概略的に示し、本図によれば、試験回路 602 はプリントヘッド回路 600 のスイッチ回路 604 に組み込まれ、この状態で、プリントヘッド回路 600 は上述のようにアクチュエータ素子アレイ 105 も含む。

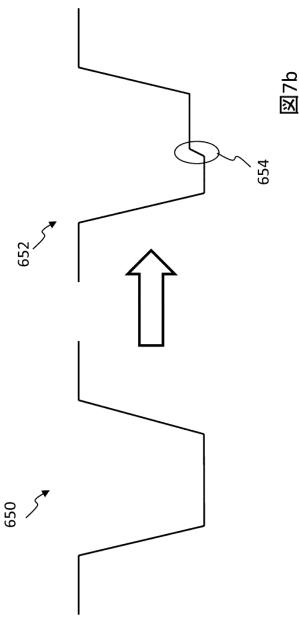

#### 【0174】

図 7 b は、共通駆動波形 650 と、スイッチ 606 を用いて得られる切り欠かれた波形 652 との例を概略的に示す。

#### 【0175】

試験回路 602 は図 6 で説明されている試験回路と同様であり、したがって、本例では、試験回路 602 は、VHIGH および VLOW を生成する DAC 618、619 と、コンパレータ 620、621 と、定電流  $i_M$  を生成する電流源 622 と、VSET<sub>;</sub> を生成する DAC 623 と、バイアススイッチ 625 とを備える。10

#### 【0176】

したがって、試験回路 602 は、アクチュエータ素子 4 のうちの 1 つ以上の静電容量を決定し、アクチュエータ素子の両端間の断線を検出し、および / またはアクチュエータ素子の両端間 / アクチュエータ素子間の閉路を検出するのに用いることができる。この状態で、駆動回路 102 は、すべてのアクチュエータ素子に印加される共通駆動波形を修正してもよい。しかし、いくつかの印加については、駆動波形をアクチュエータ素子毎に修正することが必要である。20

#### 【0177】

いくつかの実施形態では、駆動波形の形状を修正して、すなわち、「切り欠いて (trim)」、例えば、液滴速度および / または液滴の容積を調節する必要がある場合がある。

#### 【0178】

このような切り欠きを実現するために、駆動回路 102 は、すべてのアクチュエータ素子に印加される共通駆動波形を修正してもよい。しかし、いくつかの印加については、駆動波形をアクチュエータ素子毎に修正することが必要である。20

#### 【0179】

図 7 a の例では、スイッチ素子 660 および 662 はバスゲート構成でスイッチ素子 664 と並列に配置され、この状態で、スイッチ素子 660 および 662 はスイッチ素子 664 と比較して高い ON 抵抗を持つ。

#### 【0180】

スイッチ素子 660、662 および 664 を試験回路 602 中のコントローラ 616、駆動回路中のコントローラ ( 図示せず ) または他の適当な制御回路によって制御してもよい。30

#### 【0181】

スイッチ素子 660、662 および 664 は、駆動回路 102 から対応するアクチュエータ素子 4 まで共通駆動波形 650 を選択的に通過させるように構成されている。スイッチ素子 664 の ON 抵抗を最小にすることで、所望の波形形状 ( 例えば、所定の前端 / 後端およびスルーレートを持つ波形形状 ) を得てもよい。

#### 【0182】

プリントヘッド動作中、低 ON 抵抗スイッチ素子 664 が閉じられ、高 ON 抵抗スイッチ素子 660、662 が開かれることで、共通駆動波形がスイッチ素子 664 を通過して、関連するアクチュエータ素子 4 に印加される。

#### 【0183】

共通駆動波形を切り欠くために、共通駆動波形がスイッチ素子を通過する間に、低 ON 抵抗スイッチ素子 664 が開かれ、高 ON 抵抗スイッチ素子 660、662 が閉じられる。40

#### 【0184】

共通駆動波形 650 が高 ON 抵抗スイッチ素子 660、662 を通過すると、高 ON 抵抗スイッチ素子 660、662 は共通駆動波形 650 を修正する ( 図 7 b のステップ 654 を形成するように示されている )。所望の切り欠きが完了すると、スイッチ素子 664 が閉じられ、スイッチ素子 660、662 が開かれ、これにより、共通駆動波形 650 の残りが低 ON 抵抗スイッチ素子 664 を通過して、スイッチ素子 664 を介してアクチュエータ素子に印加される。

#### 【0185】

本例では、専用の試験バス 609 が、各スイッチ 606 の高 ON 抵抗スイッチ素子 660 および 662 間の共通の接続部 617 に接続されている。

#### 【0186】

特定のアクチュエータ素子 4 を試験経路に接続するために、対応するスイッチ 606 の高 ON 抵抗スイッチング素子 662 が閉じられるように制御される一方で、対応するスイッチの他のスイッチング素子 660 および 664 は開かれるように制御される。

#### 【0187】

したがって、高 ON 抵抗スイッチング素子 662 は専用の試験スイッチ素子または専用の駆動スイッチ素子ではないが、アクチュエータ素子を駆動経路および試験経路に接続するのに用いられることが分かる。

10

#### 【0188】

試験回路 602 は駆動回路 102 から電気的に絶縁されるので、低 ON 抵抗スイッチ素子 664 が駆動波形を通過させる間に、駆動電圧 / 電流による損害を受けない。

#### 【0189】

本例では、関連するアクチュエータ素子 4 についての駆動波形を切り欠くとき、高 ON 抵抗スイッチング素子 660 および 662 の両方が閉じられ、したがって、駆動回路 102 と、関連するアクチュエータ素子 4 との間の抵抗は、同時に切り欠かれているアクチュエータ素子の数に無関係である。

#### 【0190】

高 ON 抵抗スイッチング素子 660a ~ 660d の 1 つ以上をともに統合して单一のスイッチ素子を設けてもよいが、このような構成では、このような単一のスイッチング素子の有効抵抗は、適時に（すなわち、1 つ以上のアクチュエータ素子の駆動波形が切り欠かれているとき）閉じられる高 ON 抵抗スイッチングスイッチ素子 662 の数に、統合されたスイッチ素子 660 の数を加えたものの関数であることが分かる。

20

#### 【0191】

図 7c はさらなる実施形態に係るプリントヘッド回路 600 を概略的に示し、本図によれば、試験回路 602 はプリントヘッド回路 600 のスイッチ回路 604 に組み込まれ、この状態で、プリントヘッド回路 600 は上述のようにアクチュエータ素子アレイ 105 も含む。

#### 【0192】

30

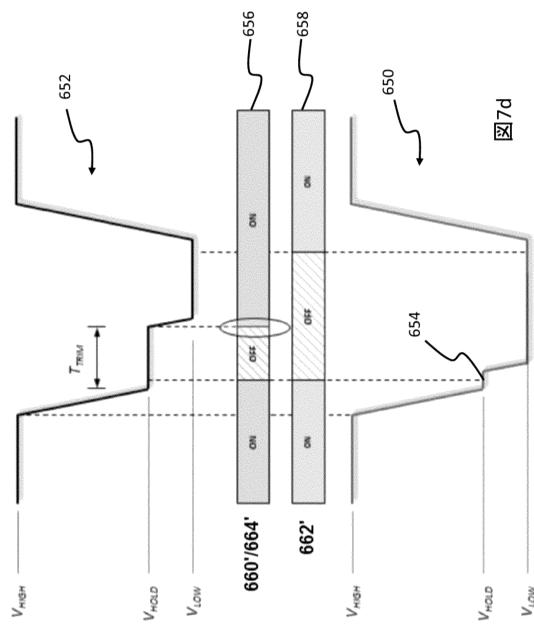

図 7d は、共通駆動波形 (common drive waveform) 650 と、スイッチ 606 を用いて得られる切り欠かれた波形 652 との例を概略的に示す。

#### 【0193】

図 7c の例では、各スイッチ 606 は、複合バスゲート構成で配置されるスイッチ素子 660'、スイッチ素子 662' およびスイッチ素子 664' を備え、この状態で、スイッチ素子 662' はスイッチ素子 664' と並列に配置されている。

#### 【0194】

本例では、スイッチ素子 660' および 662' はスイッチ素子 664' と比較して低い ON 抵抗を持つ。上記のように、スイッチ素子 660'、662' および 664' を試験回路 602 中のコントローラ 616、駆動回路中のコントローラ（図示せず）または他の適当な制御回路によって制御してもよい。

40

#### 【0195】

C DW 650 のスルー制御ステップ型切り欠きスキーム (slew controlled step-based trimming scheme) の基本的な実施のためのタイミング図を示す図 7d に関して、駆動波形 652 でアクチュエータ素子を駆動するためのスイッチ 606 の動作を説明する。

#### 【0196】

C DW 650 は、任意の形状を持ち得るパルスを備える。結果駆動波形 652 もパルスを有する。

#### 【0197】

50

本例では、ステップ 654 は C DW650 のパルスの前端にあり、ステップの電圧は電圧 V H O L D である。

#### 【 0198 】

駆動波形 652 を取得するためのスイッチ素子 660'、662'、664' のタイミングは 2 つの横棒線 656、658 に示されており、上の棒線 656 はスイッチ素子 660' および 664' の状態を示し、下の棒線 658 はスイッチ素子 662' の状態を示す。

#### 【 0199 】

C DW650 中のパルスの前端のためにスイッチ素子 660'、662'、664' が閉じられることが、横棒線 656 および 658 の両方によって示されている。これは、パサゲートの ON 抵抗がスイッチ素子 660' およびスイッチ素子 662' によって決定されることを意味する。10

#### 【 0200 】

ステップ 654 の平坦部分の始点の後（井桁（h a s h i n g）で示されている）、アクチュエータ素子 4 が駆動経路から切り離されている間、スイッチ素子が開かれるので、駆動波形 652 のパルス中のステップは制御が行なわれている期間 T T R I M だけ延び、C DW650 中のステップ 654 の終点を踏襲しない。

#### 【 0201 】

制御が行なわれている期間 T T R I M の後にアクチュエータ素子 4 を駆動経路に再接続することで、駆動波形 652 中のステップ 650 の終点が生じ、駆動波形 652 の電圧が V H O L D から降下して C DW650 中のパルスの底の電圧 V L O W を辿る。20 パサゲートの半分だけ、すなわち、スイッチ素子 660' およびスイッチ素子 664' をオンにすることによって V H O L D から V L O W への遷移を可能にする。

#### 【 0202 】

スイッチ素子 664' はスイッチ素子 660' と比較して高い ON 抵抗を持つので、この遷移のためのパサゲートの ON 抵抗は大きくなる。これにより、V H I G H から V H O L D への遷移を悪化させることなく V H O L D から V L O W への遷移を遅くすることができる。ステップ期間 T T R I M のタイミングはスイッチ素子 660' および 664' がオンになるタイミング（図 7d の丸によって強調されている遷移）によって決まり、したがって、切り欠きの量もこれによって決まる。

#### 【 0203 】

専用の試験バス 609 は各スイッチ 606 のスイッチ素子 662' および 664' に接続されている。30

#### 【 0204 】

特定のアクチュエータ素子 4 を試験経路に接続させるために、対応するスイッチ 606 のスイッチ素子 660' が開かれるように制御される一方で、スイッチ素子 662' および 664' は必要な立ち上がり / 測定時間に応じてアクチュエータ素子 4 を試験経路に接続させるように制御される。さらに、本例では、試験スイッチ 610 が試験回路 602 を試験バス 609 に選択的に接続するように配置されている。試験スイッチ 414 は、任意の適当な形態をとってもよく、例えば、1 つ以上のトランジスタを備えててもよい。

#### 【 0205 】

例えば、スイッチ素子 662' および 664' のそれぞれの ON 抵抗により、スイッチ素子 662' を開いてスイッチ素子 664' を閉じると、最長の立ち上がり / 測定時間が得られ、その一方で、スイッチ素子 662' を閉じてスイッチ素子 664' を開くと、短い立ち上がり / 測定時間が得られ、その一方で、スイッチ素子 662' および 664' の両方を閉じると、最短の立ち上がり / 測定時間が得られる。40

#### 【 0206 】

したがって、スイッチ素子 662' および 664' は専用の試験スイッチ素子でも専用の駆動スイッチ素子でもなく、アクチュエータ素子 4 を駆動経路と試験経路との両方に接続するのに用いられる一方で、スイッチ素子 662' および 664' を制御すると、立ち上がり / 測定時間の変化が得られることが分かる。50

**【0207】**

図7aおよび図7cの概略例については、スイッチ素子660'、662'および664'は図示のために限って単純なスイッチロジックとして示されており、実際には、これらはMOSデバイスまたは任意の適当なデバイスとして実施してもよい点に留意する。

**【0208】**

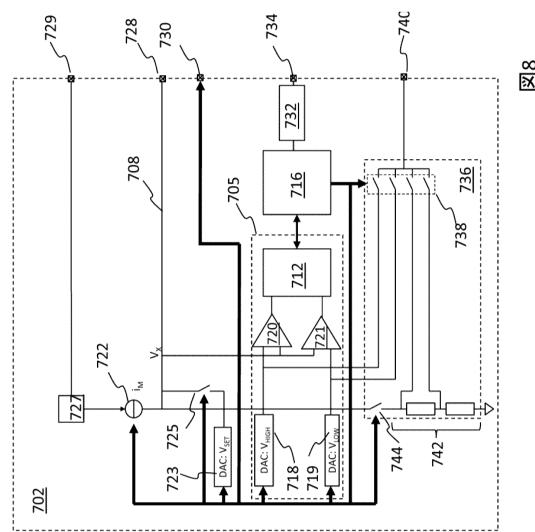

図8は、プリント回路基板(PCB)上などにある専用の回路として実施される試験回路702を概略的に示す。PCBをプリンタ(プリントヘッド)に挿入してもよいし、例えば、プリンタ/プリントヘッドに接続される別体の試験モジュールの一部として用いてもよい。

**【0209】**

試験回路702は、構成および機能の点で、図7aで説明されている試験回路と同様であり、これを踏まえて、本例では、試験回路702は、端子728を介してプリントヘッド回路(図示せず)上のアクチュエータ素子と電気接続する状態で設けることができる電線708を備える。

**【0210】**

試験回路702は、上記のように試験回路702の回路を制御するコントローラ716を備える。コントローラ702は、コントローラ702の1つ以上の外部回路または構成要素を制御するのに用いられる信号も生成する。例えば、プリントヘッド回路上のスイッチ回路中の個々のスイッチを、端子730を介して制御するのに用いられる信号も生成する。

**【0211】**

試験回路702は、VHIGHおよびVLOW(コントローラ716によって決定される)を生成するDAC718、719を含む測定回路705と、測定値VXをそれぞれのDAC出力と比較するコンパレータ720、721と、VLOWからVHIGHへのVXの遷移の時間を測定して、結果をコントローラ716に提供するタイマ712とを備える。上記のように、タイマ712はFPGAで実施してもよいし、専用のICであってもよい。

**【0212】**

試験回路702は、例えばコントローラ716によって決定される定電流IMを生成するプログラム可能な電流源722をさらに備える。上記のように、実施形態では、アクチュエータ素子を線形的に充電して静電容量測定の正確度を改善するために、電流源722は高い出力インピーダンスを持つ。

**【0213】**

試験回路702は、上述されているようなVSETを生成するDAC723とバイアススイッチ725とをさらに備える。

**【0214】**

電源727は電流源722に適当な電圧を供給する。電源727は端子729を介してプリントヘッド回路などの外部遠回りにも電圧を供給してもよい。電源727によって供給されるこのような電圧は、与えられた印加に依存してもよく、例えば、1.8V~40Vであってもよい。

**【0215】**

コントローラ716は、通信回路732および端子734を介してさらなる外部回路(例えばコンピュータ端末)と通信してもよい。回路は、シリアルリンクを備える通信インターフェース(例えばユニバーサルシリアルバス(USB)からシリアルリンクへ)を備えてよい。理解されるであろうが、必要に応じて、例えば、特定の通信プロトコルに必要な際に、信号の送信/受信/生成を行なうここでは説明されていないさらなる遠回り/端子が必要である場合がある。例として、I2Cプロトコルでは、試験回路702によってクロック信号が生成されることが必要である場合がある。

**【0216】**

試験回路702を用いて診断試験を行なって、アクチュエータ素子の静電容量CACTを決定し、および/または、アクチュエータ素子の両端間の断線、もしくはアクチュエータ素子の両端間/アクチュエータ素子間の閉路などの不具合を検出してもよいことが分かる

10

20

30

40

50

。添付の例中のアクチュエータ素子の数は 4 に限定されず、任意の数の作動要素に同様にして適用してもよい。

#### 【 0 2 1 7 】

試験回路 7 0 2 中に精度回路 7 3 6 を設けてもよく、この場合、試験回路 7 0 2 中で生成される電流および電圧を測定することができる外部測定回路またはデバイスと電気接続する状態で精度回路を配置してもよく、このようにせずに試験回路自体の固有の正確度で達成されるよりも、正確に測定することができる。

#### 【 0 2 1 8 】

本例では、精度回路 7 3 6 は電流源 7 2 2 および各 D A C 7 1 8 、 7 1 9 の出力部を端子 7 4 0 に選択的に接続するのに用いる精度スイッチアレイ 7 3 8 を備えることで、デジタル電圧計 ( d i g i t a l v o l t m e t e r ) ( D V M ) ( 例えば、プリントヘッド回路中のものまたはプリンタから離れた場所にあるもの ) などの外部測定回路 / デバイスを端子 7 4 0 に接続して、接続しない場合に電流源 7 2 2 および D A C 7 2 0 、 7 2 1 の固有の正確度で達成されるよりも正確に  $i_M$  ,  $V_HIGH$  および  $V_LOW$  を測定してもよい。その際、 D V M がコントローラ 7 1 6 と通信して、測定値に応じて電流源 7 2 2 、 D A C 7 2 0 および / または D A C 7 2 1 からの出力を調節してもよい。

10

#### 【 0 2 1 9 】

本例では、精度スイッチ 7 4 4 が例えばコントローラ 7 1 6 によって閉じられるときの精度レジスタ構成 7 4 2 での電圧低下から  $i_M$  は測定される。このような精度回路は図 2 a ~ 図 7 a で上述されている他の試験回路に含まれてもよいことも分かる。

20

#### 【 0 2 2 0 】

上記の実施形態では、時間測定に基づいて、すなわち時間測定に応じて静電容量を決定したり、不具合を検出したりすることが開示されているが、本発明は時間測定に限定されない。

#### 【 0 2 2 1 】

例えば、試験回路中のコンパレータをアナログ・デジタルコンバーター ( A D C ) と置換してもよい。図 2 a の試験回路を例として考えると、コンパレータを A D C と置換すれば、電圧  $V_X$  は A D C に対するアナログ入力である。この場合、コントローラが所定の時間だけ定電源を制御することで、静電容量 ( C P A R および / または C A C T ) がそれに応じて充電される。時間遷移を測定する代わりに、コントローラは測定電圧の変化に応じた A D C からのデジタル信号を測定する。しかし、理解されるであろうが、このような測定の正確度は A D C のビット数に依存することになる。

30

#### 【 0 2 2 2 】

上記において実施形態で説明されている試験回路により、診断試験を行なってアクチュエータ素子の静電容量 C A C T を決定し、および / または、アクチュエータ素子の両端間 ( 関連する電線の両端間を含む ) の断線、もしくはアクチュエータ素子の両端間 / アクチュエータ素子間の閉路などの不具合を検出してもよい。

#### 【 0 2 2 3 】

実施形態では、上述のこのような試験回路をプリンタから離れた場所に配置して、プリントヘッド回路中のアクチュエータ素子を試験するように構成してもよく、これにより、プリントヘッド回路をプリンタに組み込む前でも後でも静電容量が決定され、 / 任意の不具合が検出される。

40

#### 【 0 2 2 4 】

他の実施形態では、試験回路をプリンタに組み込んでもよく ( 例えば図 5 a 、図 6 および図 7 a に示されているプリントヘッド回路の一部として組み込む ) 、これにより、印刷する前でも後でも診断試験を行なうことができる ( 例えば、初期化、スタンバイ、シャットダウンルーチンの一部として診断試験を行なう、および / または印刷実行と印刷実行との間に診断試験を行なう ) 。

#### 【 0 2 2 5 】

実施形態では、アクチュエータ素子での不具合を検出すると、試験回路 ( またはプリンタ

50

上の他の回路)は不具合対応を行なってもよい。

**【0226】**

このような不具合対応はユーザに対する警報の生成を含んでもよい。このような警報は、ユーザ画面に不具合特定の通知を行なうことであってもよい。他の実施形態では、不具合対応は、ユーザが例えばプリントヘッド回路を交換することによって不具合に対処するまでプリンタが限られた機能で動作することを含んでもよい。

**【0227】**

他の実施形態では、不具合対応は、特定のアクチュエータ素子が駆動回路によって駆動されるのを試験回路(またはプリンタ上の他の回路)が避ける(例えば、関連するスイッチを適切に制御することによって避ける)ことを備えてよい。

10

**【0228】**

不具合対応は、駆動回路が任意の適當な技術を用いて、任意の検出された不具合を、例えば、隣接する1つ以上のノズルから吐出される液滴容積を増やすことによって適宜補償することも含んでもよい。

**【0229】**

さらに、アクチュエータ素子が経年劣化することにより、達成可能な落下速度は、アクチュエータ素子が作動しなくなるまで、設定された駆動電圧に応じて低下する。実際には、駆動電圧を増加させて、低下した落下速度を補償することができる。しかし、駆動電圧を増加させると、アクチュエータ素子の寿命が短くなる。

**【0230】**

アクチュエータ素子の静電容量も時間とともに低下し(例えば、経年劣化および消耗のため)、一般的には落下速度に追従する。したがって、静電容量を経時記録することによって、アクチュエータ素子が作動しなくなるまでにどの程度迫っているかを決定および/または予測することが可能である。

20

**【0231】**

作動しなくなることを予測する1つの方法としては、定期的にアクチュエータ素子の静電容量を決定すること、決定された静電容量値を(例えば、試験回路またはプリントヘッド回路上の)記憶回路に静電容量履歴データ(例えば、時間の関数としてのデータ)として記憶すること、および静電容量閾値を設定することである。閾値に達する際に、不具合とみなし、これに応じて適切な不具合対応を開始してもよい。

30

**【0232】**

したがって、実施形態では、アクチュエータ素子の決定された静電容量履歴データを用いて、アクチュエータ素子の動作を経時的に追跡し、アクチュエータ素子が将来に作動しなくなるのを予測することができる。

**【0233】**

記憶された静電容量履歴データの解析に基づいてアクチュエータ素子の機能を修正してもよく、したがって、静電容量履歴に応じて駆動波形に調節/切り欠きを行なってもよいことが分かる。このような解析は、プリントヘッド回路、試験回路または他の任意の適當な回路によって行なってもよい。

**【0234】**

上記のように、例えば、初期化、スタンバイまたはシャットダウンルーチンの一部として、静電容量を定期的に決定して静電容量履歴データを記憶してもよい。これの代わりに、アクチュエータ素子が駆動回路に接続されていない状態で、静電容量を印刷実行と印刷実行との間に決定してもよい。

40

**【0235】**

用語「備える( c o m p r i s i n g )」が本説明および請求項において用いられている場合、他の要素または工程を除外せず、以降に挙げられる手段に限定されると解釈るべきではない。

**【0236】**

単数名詞に言及するときに不定冠詞または定冠詞が用いられる場合(例えば「a」または

50

「 a n 」、 「 t h e 」 ) 、別段の記載が特ない限り、これはその名詞の複数形を含む。

【 0 2 3 7 】

別の代替例では、本技術の好ましい実施形態を、それ自体に機能データを有するデータキャリアの形態で実現してもよい。前記機能データは、コンピュータシステムまたはネットワークにロードされて、これによる作用を受けるときに、前記コンピュータシステムが方法のすべての工程を実行するのを可能にする機能的コンピュータデータ構造を備える。

【 0 2 3 8 】

本技術の範囲を逸脱しない限りにおいて多くの改善及び修正を前述の例示的な実施形態に行なうことができることは当業者には明らかである。

10

20

30

40

50

【図面】

【図 1 a】

図1a

【図 1 b】

図1b(先行技術)

10

20

【図 2 a】

【図 2 b】

30

40

50

【図 2 c】

図2c

【図 3 a】

図3a

10

【図 3 b】

図3b

【図 4 a】

図4a

20

30

40

50

【図 4 b】

図4b

【図 5 a】

図5a

10

20

30

40

50

【図 5 b】

図5b

【図 5 c】

図5c

【図 6】

【図 7 a】

【図 7 b】

【図 7 c】

10

20

30

40

50

【図 7 d】

【図 8】

10

20

30

40

50

---

フロントページの続き

(51)国際特許分類

G 0 1 R 31/58 (2020.01)

F I

G 0 1 R 31/58

ル ケンブリッジ サイエンスパーク 316 ザール テクノロジー リミテッド内

(72)発明者 イスラム ムジャヒドゥル

イギリス国 シービー4 0 エックスアール ケンブリッジ サイエンスパーク 316 ザール テク

ノロジー リミテッド内

審査官 牧島 元

(56)参考文献 特開2001-063033 (JP, A)

特開2010-076329 (JP, A)

特開平06-242159 (JP, A)

特開2007-326237 (JP, A)

米国特許出願公開第2008/0136859 (US, A1)

(58)調査した分野 (Int.Cl., DB名)

B 4 1 J 2 / 0 1 - 2 / 2 1 5

G 0 1 R 31 / 5 0 - 31 / 5 8