(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6043862号

(P6043862)

(45) 発行日 平成28年12月14日(2016.12.14)

(24) 登録日 平成28年11月18日(2016.11.18)

(51) Int.Cl.

G 11 C 19/28 (2006.01)

F 1

G 11 C 19/28 230

請求項の数 10 (全 25 頁)

(21) 出願番号 特願2015-502059 (P2015-502059)

(86) (22) 出願日 平成24年11月19日 (2012.11.19)

(65) 公表番号 特表2015-518624 (P2015-518624A)

(43) 公表日 平成27年7月2日 (2015.7.2)

(86) 國際出願番号 PCT/CN2012/084836

(87) 國際公開番号 WO2013/143303

(87) 國際公開日 平成25年10月3日 (2013.10.3)

審査請求日 平成27年11月18日 (2015.11.18)

(31) 優先権主張番号 201210089651.3

(32) 優先日 平成24年3月29日 (2012.3.29)

(33) 優先権主張国 中国(CN)

(73) 特許権者 510280589

京東方科技集團股▲ふん▼有限公司

BOE TECHNOLOGY GROUP CO., LTD.

中華人民共和国 100015 北京市朝陽區

酒仙橋路 10 號

No. 10 Jiuxiaqiao Rd., Chaoyang District, Beijing 100015, CHINA

(74) 代理人 100108453

弁理士 村山 靖彦

(74) 代理人 100089037

弁理士 渡邊 隆

最終頁に続く

(54) 【発明の名称】シフトレジスタ、駆動回路及び表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

シフトレジスタであって、

電圧シフトモジュールと、電圧逆方向モジュールと、補充電圧モジュールと、電圧シフト制御モジュールと、第1の出力ポートと、第2の出力ポートとを有し、

電圧シフトモジュールは、第1の起動電圧信号の制御のもとで起動電圧と同じ方向の電圧を受け付け、第2の起動電圧信号の制御のもとで、受け付けた起動電圧と同じ方向の電圧を前記第2の出力ポートから出力し、同時に電圧逆方向モジュールに出力し、

電圧逆方向モジュールは、電圧シフトモジュールに接続され、受け付けた前記電圧シフトモジュールが出力した電圧と逆方向電圧源が提供する電圧の制御のもとで、起動電圧と逆方向の電圧を、前記第1の出力ポートから出力し、同時に補充電圧モジュールに出力し、第1の起動電圧信号と起動電圧源の提供する電圧、あるいは第3の起動電圧信号と起動電圧源が提供する電圧の制御のもとで、起動電圧と同じ方向の電圧を前記第1の出力ポートから出力し、同時に補充電圧モジュールに出力し、

補充電圧モジュールは、電圧逆方向モジュールと電圧シフトモジュールとに接続され、受け付けた前記電圧逆方向モジュールが出力した電圧と逆方向電圧源が提供する電圧の制御のもとで、電圧逆方向モジュールが起動電圧と同じ方向の電圧を出力した場合、前記第2の出力ポートから前記起動電圧と逆方向の電圧を出力し、同時に電圧逆方向モジュールに出力し、

電圧シフト制御モジュールは電圧シフトモジュールに接続され、第3の起動電圧信号と

10

20

逆方向電圧源が提供する電圧の制御のもとで、電圧シフトモジュールのオフを制御する、シフトレジスタ。

**【請求項 2】**

前記第1の起動電圧信号は第1のクロック信号（CLK1）であり、前記第2の起動電圧信号は第2のクロック信号（CLK2）であり、前記第3の起動電圧信号は第3のクロック信号（CLK3）である請求項1に記載のシフトレジスタ。

**【請求項 3】**

前記電圧シフトモジュールは、

第1の起動電圧信号（CLK1）の制御のもとでスイッチ操作を行い、受け付けた前記起動電圧と同じ方向の電圧を、充電電圧として第1のコンデンサに出力し、制御電圧として第2のスイッチ素子に出力するように制御する第1のスイッチ素子と、

第1のスイッチ素子がオンになって起動電圧と同じ方向の電圧を受け付けたとき、第2のスイッチ素子に一つの駆動制御電圧を提供するように充電を行う第1のコンデンサと、

第1のスイッチ素子が出力する起動電圧、第1のコンデンサが提供する駆動制御電圧あるいは第1の制御素子が出力する逆方向電圧の制御のもとでスイッチ操作を行い、起動電圧が第2の出力ポートから出力するように制御する第2のスイッチ素子と、を有し、

前記電圧逆方向モジュールは、

第3のスイッチ素子が出力する起動電圧の制御のもとでスイッチ操作を行い、逆方向電圧源が第4のスイッチ素子を通じて第1の出力ポートから出力するように制御する第4のスイッチ素子と、

第1の起動電圧信号（CLK1）の制御のもとでスイッチ操作を行い、起動電圧源が充電電圧として第2のコンデンサに出力し、制御電圧として第6のスイッチ素子に出力するように制御する第5のスイッチ素子と、

第4のスイッチ素子がオンになって逆方向電圧源を受け付けたとき、第6のスイッチ素子をオフにする第2のコンデンサと、

第5のスイッチ素子、第7のスイッチ素子が出力する制御電圧あるいは第2のコンデンサの制御のもとでスイッチ操作を行い、起動電圧源が第1の出力ポートから出力するように制御する第6のスイッチ素子と、

第3の起動電圧信号（CLK3）の制御のもとでスイッチ操作を行い、起動電圧源が制御電圧として第6のスイッチ素子に出力するように制御する第7のスイッチ素子と、を有し、

前記補充電圧モジュールは、

第1の出力ポートが出力する電圧の制御のもとでスイッチ操作を行い、逆方向電圧源がオフ電圧として第4のスイッチ素子に出力し、且つ逆方向電圧源を第2の出力ポートから出力するように制御する第3の制御素子と、を有し、

前記電圧シフト制御モジュールは、

第3の起動電圧信号（CLK3）の制御のもとでスイッチ操作を行い、第1のコンデンサが逆方向電圧源と接続した後に放電するように制御し、逆方向電圧源が制御電圧として第2のスイッチ素子に出力するように制御する第1の制御素子と、を有し、

逆方向電圧源は起動電圧シフトモジュールの電圧と逆方向の電圧を出力するために用いられ、

起動電圧源は起動電圧シフトモジュールの電圧と同じ方向の電圧を出力するために用いられる請求項1または請求項2に記載のシフトレジスタ。

**【請求項 4】**

当該シフトレジスタは、更に、

電圧シフトモジュールと電圧逆方向モジュールに接続され、起動電圧源が提供する電圧の制御のもとで、受け付けた電圧シフトモジュールが出力した電圧を電圧安定させた後に第2の出力ポートから出力し、且つ電圧逆方向モジュールに出力するために用いられる電圧安定モジュールと、

電圧逆方向モジュールと電圧安定モジュールに接続され、受け付けた前記電圧逆方向モ

10

20

30

40

50

ジュールが第1の出力ポートから出力した電圧と逆方向電圧源が提供する電圧の制御のもとで、電圧逆方向モジュールが起動電圧と同じ方向の電圧を出力したときに、電圧安定モジュールをオフにするために用いられる電圧安定制御モジュールと、を有する請求項1ないし請求項3のいずれかに記載のシフトレジスタ。

**【請求項5】**

前記電圧安定モジュールは、

第2のスイッチ素子が出力する制御電圧あるいは第2の制御素子が出力する制御電圧の制御のもとでスイッチ操作を行い、起動電圧源が制御電圧として第4のスイッチ素子に出力するように制御し、起動電圧源が第2の出力ポートから出力するように制御する第3のスイッチ素子と、を有し、

10

前記電圧安定制御モジュールは、

第1の出力ポートが出力する電圧の制御のもとでスイッチ操作を行い、逆方向電圧源がオフ電圧として第3のスイッチ素子に出力するように制御する第2の制御素子と、を有する請求項4に記載のシフトレジスタ。

**【請求項6】**

前記第1ないし第7のスイッチ素子、第1の制御素子ないし第3の制御素子がN型電界効果トランジスタである場合、前記逆方向電圧源は低電圧源( $V_{g1}$ )であり、前記起動電圧源は高電圧源( $V_{gh}$ )であり、且つ、

第1のスイッチ素子は、第1の薄膜トランジスタ(M1)を有し、当該第1の薄膜トランジスタは第1の起動電圧信号(CLK1)を受け付ける一つのゲート極と、起動電圧と同じ方向の電圧を受け付ける一つのドレイン極と、第2の薄膜トランジスタ(M2)のゲート極と第1のコンデンサの一端に接続される一つのソース極とを有し、

20

第2のスイッチ素子は、第2の薄膜トランジスタ(M2)を有し、当該第2の薄膜トランジスタ(M2)は、第1の薄膜トランジスタ(M1)のソース極に接続される一つのゲート極と、第2の起動電圧信号(CLK2)を受け付ける一つのドレイン極と、第3の薄膜トランジスタ(M3)のゲート極に接続される一つのソース極とを有し、

第1のコンデンサの一端は第2の薄膜トランジスタ(M2)のゲート極に接続され、他端は第2の薄膜トランジスタ(M2)のソース極に接続され、

第3のスイッチ素子は、第3の薄膜トランジスタ(M3)を有し、当該第3の薄膜トランジスタ(M3)は、第2の薄膜トランジスタ(M2)のソース極に接続される一つのゲート極と、高電圧源( $V_{gh}$ )を受け付ける一つのドレイン極と、第4の薄膜トランジスタ(M4)のゲート極と第2の出力ポートに接続される一つのソース極とを有し、

30

第4のスイッチ素子は、前記第4の薄膜トランジスタ(M4)を有し、当該第4の薄膜トランジスタ(M4)は、第3の薄膜トランジスタ(M3)のソース極に接続される一つのゲート極と、第1の出力ポートに接続される一つのドレイン極と、低電圧源( $V_{g1}$ )を受け付ける一つのソース極とを有し、

第5のスイッチ素子は、第5の薄膜トランジスタ(M5)を有し、当該第5の薄膜トランジスタ(M5)は、第1の起動電圧信号(CLK1)を受け付ける一つのゲート極と、高電圧源( $V_{gh}$ )を受け付ける一つのドレイン極と、第6の薄膜トランジスタ(M6)のゲート極に接続される一つのソース極とを有し、

40

第2のコンデンサの一端は前記第6の薄膜トランジスタ(M6)のゲート極に接続され、他端は前記第6の薄膜トランジスタ(M6)のソース極に接続され、

第6のスイッチ素子は、前記第6の薄膜トランジスタ(M6)を有し、当該第6の薄膜トランジスタは、前記第5の薄膜トランジスタ(M5)と第7の薄膜トランジスタ(M7)のソース極に接続される一つのゲート極と、高電圧源( $V_{gh}$ )を受け付ける一つのドレイン極と、第4の薄膜トランジスタ(M4)のドレイン極に接続され、第1の出力ポートに接続される一つのソース極とを有し、

第7のスイッチ素子は、前記第7の薄膜トランジスタ(M7)を有し、当該第7の薄膜トランジスタ(M7)は、第3の起動電圧信号(CLK3)を受け付ける一つのゲート極と、高電圧源( $V_{gh}$ )を受け付ける一つのドレイン極と、第6の薄膜トランジスタ(M6)のゲート極に接続される一つのソース極とを有し、

50

6 ) のゲート極に接続される一つのソース極とを有し、

第1の制御素子は、第8の薄膜トランジスタ(M8)を有し、当該第8の薄膜トランジスタ(M8)は、第3の起動電圧信号(CLK3)を受け付ける一つのゲート極と、第2の薄膜トランジスタ(M2)のゲート極に接続される一つのドレイン極と、低電圧源(Vg1)を受け付ける一つのソース極とを有し、

第2の制御素子は、第9の薄膜トランジスタ(M9)を有し、当該第9の薄膜トランジスタ(M9)は、第4の薄膜トランジスタ(M4)のドレイン極に接続される一つのゲート極と、第3の薄膜トランジスタ(M3)のゲート極に接続される一つのドレイン極と、低電圧源(Vg1)を受け付ける一つのソース極とを有し、

第3の制御素子は、第10の薄膜トランジスタ(M10)を有し、当該第10の薄膜トランジスタは、第4の薄膜トランジスタ(M4)のドレイン極に接続される一つのゲート極と、第3の薄膜トランジスタ(M3)のソース極に接続される一つのドレイン極と、低電圧源(Vg1)を受け付ける一つのソース極と、を有する請求項5に記載のシフトレジスタ。

#### 【請求項7】

前記第1ないし第7のスイッチ素子、第1の制御素子ないし第3の制御素子がP型電界効果トランジスタである場合、前記逆方向電圧源は高電圧源(Vgh)であり、前記起動電圧源は低電圧源(Vgl)であり、且つ、

第1のスイッチ素子は、第1の薄膜トランジスタ(M1)を有し、当該第1の薄膜トランジスタ(M1)は第1の起動電圧信号(CLK1)を受け付ける一つのゲート極と、起動電圧と同じ方向の電圧を受け付ける一つのドレイン極と、第2の薄膜トランジスタ(M2)のゲート極に接続される一つのソース極とを有し、

第2のスイッチ素子は、前記第2の薄膜トランジスタ(M2)を有し、当該第2の薄膜トランジスタ(M2)は、前記第1の薄膜トランジスタ(M1)のソース極に接続される一つのゲート極と、第2の起動電圧信号(CLK2)を受け付ける一つのドレイン極と、第3の薄膜トランジスタ(M3)のゲート極に接続される一つのソース極とを有し、

第1のコンデンサの一端は第2の薄膜トランジスタ(M2)のゲート極に接続され、他端は第2の薄膜トランジスタ(M2)のソース極に接続され、

第3のスイッチ素子は、前記第3の薄膜トランジスタ(M3)を有し、当該第3の薄膜トランジスタ(M3)は、前記第2の薄膜トランジスタ(M2)のソース極に接続される一つのゲート極と、低電圧源(Vgl)を受け付ける一つのドレイン極と、第4の薄膜トランジスタ(M4)のゲート極と第2の出力ポートに接続される一つのソース極とを有し、

第4のスイッチ素子は、前記第4の薄膜トランジスタ(M4)を有し、当該第4の薄膜トランジスタ(M4)は、前記第3の薄膜トランジスタ(M3)のソース極に接続される一つのゲート極と、第1の出力ポートに接続される一つのドレイン極と、高電圧源(Vgh)を受け付ける一つのソース極とを有し、

第5のスイッチ素子は、第5の薄膜トランジスタ(M5)を有し、当該第5の薄膜トランジスタ(M5)は、第1の起動電圧信号(CLK1)を受け付ける一つのゲート極と、低電圧源(Vgl)を受け付ける一つのドレイン極と、第6の薄膜トランジスタ(M6)のゲート極に接続される一つのソース極とを有し、

第2のコンデンサの一端は第6の薄膜トランジスタ(M6)のゲート極に接続され、他端は第6の薄膜トランジスタ(M6)のソース極に接続され、

第6のスイッチ素子は、前記第6の薄膜トランジスタ(M6)を有し、当該第6の薄膜トランジスタは、前記第5の薄膜トランジスタ(M5)のソース極に接続される一つのゲート極と、低電圧源(Vgl)を受け付ける一つのドレイン極と、第1の出力ポートに接続される一つのソース極とを有し、

第7のスイッチ素子は、第7の薄膜トランジスタ(M7)を有し、当該第7の薄膜トランジスタ(M7)は、第3の起動電圧信号(CLK3)を受け付ける一つのゲート極と、低電圧源(Vgl)を受け付ける一つのドレイン極と、前記第6の薄膜トランジスタ(M6)のゲート極に接続される一つのソース極とを有し、

10

20

30

40

50

6 ) のゲート極に接続される一つのソース極とを有し、

第1の制御素子は、第8の薄膜トランジスタ(M8)を有し、当該第8の薄膜トランジスタ(M8)は、第3の起動電圧信号(CLK3)を受け付ける一つのゲート極と、前記第2の薄膜トランジスタ(M2)のゲート極に接続される一つのドレイン極と、高電圧源(Vgh)を受け付ける一つのソース極とを有し、

第2の制御素子は、第9の薄膜トランジスタ(M9)を有し、当該第9の薄膜トランジスタ(M9)は、前記第4の薄膜トランジスタ(M4)のドレイン極に接続される一つのゲート極と、第3の薄膜トランジスタ(M3)のゲート極に接続される一つのドレイン極と、高電圧源(Vgh)を受け付ける一つのソース極とを有し、

第3の制御素子は、第10の薄膜トランジスタ(M10)を有し、当該第10の薄膜トランジスタは、前記第4の薄膜トランジスタ(M4)のドレイン極に接続される一つのゲート極と、前記第3の薄膜トランジスタ(M3)のソース極に接続される一つのドレイン極と、高電圧源(Vgh)を受け付ける一つのソース極と、を有する請求項5に記載のシフトレジスタ。10

#### 【請求項8】

シフトレジスタがシフトを実現する方法であって、前記シフトレジスタは、電圧シフトモジュールと、電圧逆方向モジュールと、補充電圧モジュールと、電圧シフト制御モジュールと、第1の出力ポートと、第2の出力ポートとを有し、当該方法は、

電圧シフトモジュールは、第1の起動電圧の制御のもとで起動電圧と同じ方向の電圧を受け付け、第2の起動電圧信号の制御のもとで第2の出力ポートから起動電圧と同じ方向の電圧を出力し。20

電圧逆方向モジュールは、受け付けた電圧シフトモジュールが出力した電圧の制御のもとで、起動電圧と逆方向の電圧を、前記第1の出力ポートから出力し、第1の起動電圧と第3の起動電圧の制御のもとで、起動電圧と同じ方向の電圧を前記第1の出力ポートから出力し、

補充電圧モジュールは、受け付けた前記電圧逆方向モジュールが出力した電圧の制御のもとで、電圧逆方向モジュールが起動電圧を出力した場合に、前記第2の出力ポートから前記起動電圧と逆方向の電圧を出力し、

電圧シフト制御モジュールは、受け付けた第3の起動電圧の制御のもとで、電圧逆方向モジュールが起動電圧を出力した場合に、電圧シフトモジュールのオフを制御する方法。30

#### 【請求項9】

駆動回路であって、第1段のシフトレジスタと、最後の段のシフトレジスタと、少なくとも一つの中間の段のシフトレジスタを有し、それぞれのシフトレジスタは請求項1～7のいずれかに記載のシフトレジスタであり、前記シフトレジスタ間はカスケード接続方式で接続され、一段上のシフトレジスタにおける第2の出力ポートは一段下のシフトレジスタの電圧シフトモジュールに接続され、

第1段のシフトレジスタは、外部電圧を受け付け、第2の出力ポートから一段下のシフトレジスタに電圧を出力し、且つ第1の出力ポートから第2の出力ポートが出力する電圧と逆方向の電圧を出力するために用いられ、

それぞれの中間の段のシフトレジスタは、一段上のシフトレジスタの第2の出力ポートが出力する電圧を受け付け、各自の第2の出力ポートから一段下のシフトレジスタに電圧を出力し、且つ各自の第1の出力ポートから各自の第2の出力ポートが出力する電圧と逆方向の電圧を出力するために用いられ。40

最後の段のシフトレジスタは、一段上のシフトレジスタの第2の出力ポートが出力する電圧を受け付け、且つ第1の出力ポートからその第2の出力ポートが出力する電圧と逆方向の電圧を出力するために用いられ、

一段上のシフトレジスタの第1の起動電圧信号のオフを制御した後、一段下のシフトレジスタの第1の起動電圧信号のオンを制御する、駆動回路。

#### 【請求項10】

表示装置であって、請求項9に記載の駆動回路を有する表示装置。50

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、表示技術分野に関し、特にシフトレジスタ、駆動回路、表示装置に関する。

**【背景技術】****【0002】**

伝統的なシフトレジスタの出力特性はシフトレジスタを構成する TFT 極性と関係する。即ち、N型 TFT シフトレジスタの作業区間は高電圧 Vgh を出力し、P型 TFT シフトレジスタの作業区間は低電圧 Vgl を出力する。従来のシフトレジスタは同時に低電圧と高電圧を出力することはできない。

10

**【0003】**

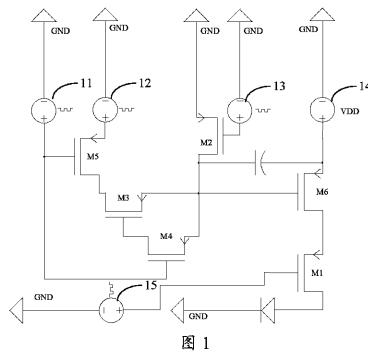

また、補償機能を有する AMOLED (Active Matrix Organic Light Emitting Diode : アクティブマトリックス有機 LED パネル) の画素構造の回路において、電圧自体を起動電圧として起動しなければならないだけでなく、起動電圧と逆方向の電圧も起動電圧としなければならない。図 1 に示す P 型 TFT 補償型画素構造は 5 つの駆動信号を必要とし、DATA (データ) 信号 11 と VDD (電源) 信号 14 は Source IC (駆動回路基板) によって直接提供され、他の 3 つの信号はシフトレジスタによって画素構造に入力され、このうち、GATE (ゲート) 信号 12 と RESET (リセット) 信号 13 の起動電圧は低電圧であるが、EMISSION (発光) 信号 15 の起動電圧は高電圧である。したがって、従来のシフトレジスタは低電圧である GATE (ゲート) と RESET (リセット) 信号及び高電圧である EMISSION 信号を同時に提供する目的を果たせない。

20

**【発明の概要】****【課題を解決するための手段】****【0004】**

本発明の実施例は、シフトレジスタであって、受け付けた起動電圧を遅延して出力でき、遅延して出力する起動電圧と逆方向の逆方向電圧も同時に出力できるシフトレジスタを提供する。

**【0005】**

本発明の実施例は、シフトレジスタであって、電圧シフトモジュールと、電圧逆方向モジュールと、補充電圧モジュールと、電圧シフト制御モジュールと、第 1 の出力ポートと、第 2 の出力ポートとを有し、電圧シフトモジュールは、第 1 の起動電圧信号の制御のもとで起動電圧と同じ方向の電圧を受け付け、第 2 の起動電圧信号の制御のもとで、受け付けた起動電圧と同じ方向の電圧を、前記第 2 の出力ポートから出力し、同時に電圧逆方向モジュールに出力し、電圧逆方向モジュールは、電圧シフトモジュールに接続され、受け付けた前記電圧シフトモジュールが出力した電圧と逆方向電圧源が提供する電圧の制御のもとで、起動電圧と逆方向の電圧を、前記第 1 の出力ポートから出力し、同時に補充電圧モジュールに出力し、第 1 の起動電圧信号と起動電圧源の提供する電圧、あるいは第 3 の起動電圧信号と起動電圧源が提供する電圧の制御のもとで、起動電圧と同じ方向の電圧を前記第 1 の出力ポートから出力し、同時に補充電圧モジュールに出力し、補充電圧モジュールは、電圧逆方向モジュールと電圧シフトモジュールとに接続され、受け付けた前記電圧逆方向モジュールが出力した電圧と逆方向電圧源が提供する電圧の制御のもとで、電圧逆方向モジュールが起動電圧と同じ方向の電圧を出力した場合、前記第 2 の出力ポートから前記起動電圧と逆方向の電圧を出力し、同時に電圧逆方向モジュールに出力し、電圧シフト制御モジュールは電圧シフトモジュールに接続され、第 3 の起動電圧信号と逆方向電圧源が提供する電圧の制御のもとで、電圧シフトモジュールのオフを制御する、シフトレジスタを提供する。

30

**【0006】**

本発明の実施例は、更に、シフトレジスタが実現するシフト方法であって、前記シフトレジスタは、電圧シフトモジュールと、電圧逆方向モジュールと、補充電圧モジュールと

40

50

、電圧シフト制御モジュールと、第1の出力ポートと、第2の出力ポートとを有し、当該方法は、電圧シフトモジュールは、第1の起動電圧の制御のもとで起動電圧と同じ方向の電圧を受け付け、第2の起動電圧の制御のもとで第2の出力ポートから起動電圧と同じ方向の電圧を出力し、電圧逆方向モジュールは、受け付けた電圧シフトモジュールが出力した電圧の制御のもとで、起動電圧と逆方向の電圧を、前記第1の出力ポートから出力し、第1の起動電圧と第3の起動電圧の制御のもとで、起動電圧と同じ方向の電圧を前記第1の出力ポートから出力し、補充電圧モジュールは、受け付けた前記電圧逆方向モジュールが出力した電圧の制御のもとで、電圧逆方向モジュールが起動電圧を出力した場合に、前記第2の出力ポートから前記起動電圧と逆方向の電圧を出力し、電圧シフト制御モジュールは、受け付けた第3の起動電圧の制御のもとで、電圧逆方向モジュールが起動電圧を出力した場合に、電圧シフトモジュールのオフを制御する、シフト方法を提供する。10

#### 【0007】

本発明の実施例は、更に、駆動回路であって、第1段のシフトレジスタと、最後の段のシフトレジスタと、少なくとも一つの中間の段のシフトレジスタを有し、それぞれのシフトレジスタは上記のシフトレジスタであり、前記シフトレジスタ間はカスケード接続方式で接続され、一段上のシフトレジスタにおける第2の出力ポートは一段下のシフトレジスタの電圧シフトモジュールに接続され、第1段のシフトレジスタの電圧シフトモジュールは起動電圧と同じ方向の電圧を受け付け、第2の出力ポートから一段下のシフトレジスタの電圧シフトモジュールに電圧を出力し、第1の出力ポートから第2の出力ポートが出力する電圧と逆方向の電圧を出力し、それぞれの中間の段のシフトレジスタの電圧シフトモジュールは一段上のシフトレジスタの第2の出力ポートが出力する電圧を受け付け、第2の出力ポートから一段下のシフトレジスタの電圧シフトモジュールに電圧を出力し、且つ第1の出力ポートから第2の出力ポートが出力する電圧と逆方向の電圧を出力し、最後の段のシフトレジスタの電圧シフトモジュールは一段上のシフトレジスタの第2の出力ポートが出力する電圧を受け付け、且つ第1の出力ポートから第2の出力ポートが出力する電圧と逆方向の電圧を出力し、一段上のシフトレジスタの第1の起動電圧信号のオフを制御した後、一段下のシフトレジスタの第1の起動電圧信号のオンを制御する、駆動回路を提供する。20

#### 【0008】

本発明の実施例は更に上記駆動回路を備える表示装置を提供する。30

#### 【0009】

本発明の実施例のシフトレジスタは、一段下のシフトレジスタに起動電圧を提供すると同時に、起動電圧と逆方向の電圧を提供することによって、シフトレジスタに、一段下のシフトレジスタの遅延された同じ方向の起動電圧のみならず、遅延された起動電圧と逆方向の逆方向電圧を提供させるようとする。

#### 【図面の簡単な説明】

#### 【0010】

【図1】P型 TFT補償型画素構造である。

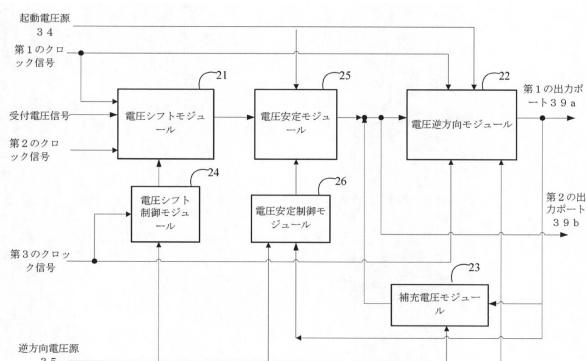

【図2】本発明の実施例一における構造の模式図である。

【図3】本発明の具体的な実施例二における回路の構造の模式図である。40

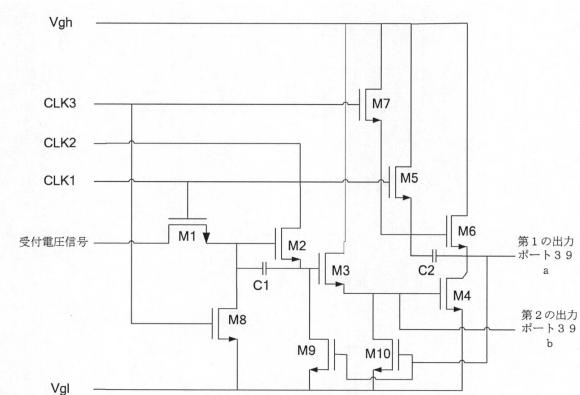

【図4】本発明の具体的な実施例三において、Nチャネル型TFTを採用する回路の構造の模式図である。

【図5】本発明の具体的な実施例三において、Nチャネル型TFTを採用する回路のシーケンス図である。

【図6】本発明の具体的な実施例四において、Pチャネル型TFTを採用する回路の構造の模式図である。

【図7】本発明の具体的な実施例四において、Pチャネル型TFTを採用する回路のシーケンス図である。

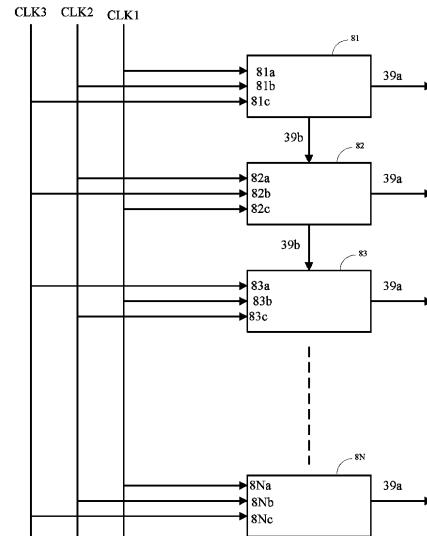

【図8】本発明の実施例における複数のシフトレジスタからなる駆動回路の構造の模式図である。50

【図9】本発明の実施例における方法のフロー図である。

【発明を実施するための形態】

【0011】

シフトレジスタに、受け付けた電圧信号が遅延した後の電圧信号を出力させるのみならず、同時に遅延した後の電圧信号と逆方向の電圧信号を出力させるために、本発明は逆方向出力を有するシフトレジスタを提供する。

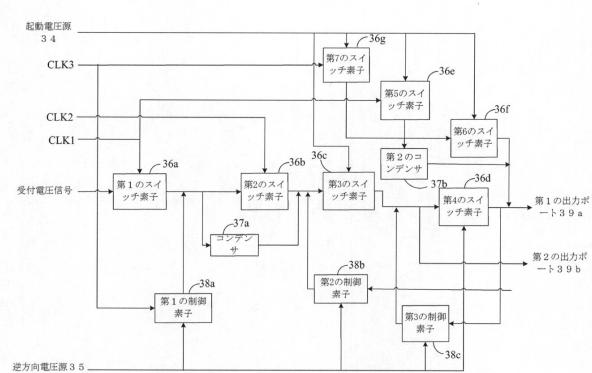

【0012】

以下に図面を用いて本発明の実施例における実施を説明する。本発明の実施例一は、図2に示すように、逆方向出力を有するシフトレジスタであって、電圧シフトモジュール21と、電圧逆方向モジュール22と、補充電圧モジュール23と、電圧シフト制御モジュール24と、電圧安定モジュール25と、電圧安定制御モジュール26と、第1の出力ポート39aと、第2の出力ポート39bとを有する。

10

【0013】

本実施例における第1の起動電圧信号、第2の起動電圧信号、第3の起動電圧信号はそれぞれ第1のクロック信号、第2のクロック信号、第3のクロック信号である。

【0014】

本実施例における電圧シフトモジュール21は、第1のクロック信号の制御のもとで、起動電圧と同じ方向の電圧信号を受け付け、第2のクロック信号の制御のもとで、受け付けた起動電圧と同じ方向の電圧信号を前記第2の出力ポートから出力し、同時に電圧安定モジュール25に出力する。

20

【0015】

電圧シフトモジュール21が受け付ける電圧信号は外部のトリガ電圧信号であってもよく、カスケード方式を用いて接続される複数のシフトレジスタの組み合わせからなる駆動回路の場合の一段上のシフトレジスタが出力する電圧信号でもよい。第1のクロック信号が制御するときに限って電圧シフトモジュール21は電圧信号を受け付けることができ、第2のクロック信号が制御するときに電圧シフトモジュール21は第2の出力ポート39bから受け付けた電圧信号を出力する。

【0016】

電圧安定モジュール25は、起動電圧源が提供する電圧の制御のもとで、前記電圧シフトモジュール21が出力する電圧と同じ方向であり且つ安定した電圧を前記第2の出力ポート39bから出力するために用いられる。電圧安定モジュール25の入力端は、電圧シフトモジュール21の出力ポートに接続され、電圧安定モジュール25の出力ポートは電圧逆方向モジュール22の入力端に接続される。電圧安定モジュール25は出力する電圧が安定であり、且つ起動電圧と同じ方向の電圧であることを保証する。実際には、個別に電圧シフトモジュール21が出力する電圧と同じ方向の電圧源を使って安定した同じ方向の電圧を提供してもよい。

30

【0017】

電圧逆方向モジュール22は、電圧安定モジュール25に接続され、受け付けた電圧安定モジュール25が出力する電圧信号と起動電圧源34が提供する電圧制御のもとで、起動電圧と逆方向の電圧信号を前記第1の出力ポート39aから出力し、同時に補充電圧モジュール23と電圧安定制御モジュール26に出力し、第1のクロック信号と起動電圧源34が提供する電圧、あるいは第3のクロック信号と起動電圧源34が提供する電圧の制御のもとで、起動電圧と同じ方向の電圧を前記第1の出力ポート39aから出力し、同時に補充電圧モジュール23と電圧安定制御モジュール26に出力するために用いられる。

40

【0018】

電圧逆方向モジュール22は、電圧安定モジュール25に接続される。電圧シフトモジュール21が出力する起動電圧を電圧安定モジュール25に入力し、電圧安定モジュール25が出力する電圧を電圧逆方向モジュール22に入力する。電圧逆方向モジュール22は電圧安定モジュール25が出力する起動電圧と同じ方向の電圧、及び起動電圧源34が提供する電圧を受け付けると同時に、起動電圧と逆方向の電圧を出力し、第1のクロック

50

信号と起動電圧源 3 4 が提供する電圧、あるいは第 3 のクロック信号と起動電圧源 3 4 が提供する電圧の制御のもとで、起動電圧と同じ方向の電圧を前記第 1 の出力ポート 3 9 a から出力し、同時に補充電圧モジュール 2 3 と電圧安定制御モジュール 2 6 に出力する。

#### 【 0 0 1 9 】

実際には、電圧シフトモジュール 2 1 と電圧逆方向モジュール 2 2 は直接接続されてもよい。それは、電圧安定モジュール 2 5 は、電圧シフトモジュール 2 1 が出力する電圧を更に安定させるために、電圧シフトモジュール 2 1 と電圧逆方向モジュールの間に電圧安定モジュール 2 5 を付け加えるからである。しかし、電圧安定モジュール 2 5 がなくても、電圧シフトモジュール 2 1 と電圧逆方向モジュール 2 2 の機能は影響されない。電圧シフトモジュール 2 1 は依然として受け付けた電圧をシフトして出力でき、電圧逆方向モジュールは電圧シフトモジュール 2 1 が出力した電圧を受け付け、逆方向の電圧を出力できる。10

#### 【 0 0 2 0 】

補充電圧モジュール 2 3 は、電圧逆方向モジュール 2 2 に接続され、受け付けた前記電圧逆方向モジュール 2 2 が出力した電圧と逆方向電圧源 3 5 が提供する電圧の制御のもとで、電圧逆方向モジュールが起動電圧と同じ方向の電圧を出力したときに、前記第 2 の出力ポートから前記起動電圧と逆方向の電圧を出力し、同時に電圧逆方向モジュール 2 2 に出力するために用いられる。

#### 【 0 0 2 1 】

補充電圧モジュール 2 3 は、電圧逆方向モジュール 2 2 が出力する電圧の制御を受け、電圧シフトモジュールが出力しないときに起動電圧と逆方向の電圧を第 2 の出力ポート 3 9 b から出力する。20

#### 【 0 0 2 2 】

電圧シフト制御モジュール 2 4 は、電圧シフトモジュール 2 1 に接続され、第 3 のクロック信号と逆方向電圧源 3 5 が提供する電圧の制御のもとで、電圧シフトモジュール 2 1 のオフを制御するために用いられる。

#### 【 0 0 2 3 】

電圧シフト制御モジュール 2 4 は、第 3 のクロック信号の制御を受け、続いて制御電圧を電圧シフトモジュール 2 1 に出力し、電圧シフト制御モジュール 2 4 は電圧逆方向モジュール 2 2 が起動電圧と同じ方向の電圧を出力するときに、電圧シフトモジュール 2 1 をオフにする。30

#### 【 0 0 2 4 】

電圧安定制御モジュール 2 6 は、受け付けた前記電圧逆方向モジュールが第 1 の出力ポートから出力した電圧と逆方向電圧源が提供する電圧の制御のもとで、電圧逆方向モジュールが起動電圧と同じ方向の電圧を出力するときに、電圧安定モジュールをオフにするために用いられる。

#### 【 0 0 2 5 】

電圧安定モジュール 2 5 がなければ、電圧安定制御モジュール 2 6 も必要ない。

#### 【 0 0 2 6 】

本実施例において、前記第 1 のクロック信号がオフになった後、第 2 のクロック信号はオンになり、第 2 のクロック信号がオフになった後、第 3 のクロック信号はオンになり、第 3 のクロック信号がオフになった後、第 1 のクロック信号はオンになる、といった具合に類推する。40

#### 【 0 0 2 7 】

電圧シフトモジュール 2 1 は、第 1 のクロック信号の制御のもとで起動電圧と同じ方向の電圧を受け付け、第 2 のクロック信号の制御のもとで起動電圧と同じ方向の電圧を第 2 の出力ポート 3 9 b に出力し、第 1 のクロック信号と第 3 のクロック信号の制御のもとでは電圧信号を出力しない。電圧逆方向モジュール 2 2 は第 1 のクロック信号と第 3 のクロック信号の制御のもとで起動電圧と同じ方向の電圧を出力し、且つ第 1 の出力ポート 3 9 a から出力し、第 2 のクロック信号の制御のもとで電圧逆方向モジュール 2 2 は起動電圧50

と逆方向の電圧を第1の出力ポート39aに出力する。第1の出力ポート39aが起動電圧と逆方向の電圧を出力したとき、第1の出力ポート39aが出力する電圧は、補充電圧モジュール23が第1の出力ポート39aの出力する電圧と逆方向の電圧を出力し、且つ第2の出力ポート39bから出力するように制御する。以上により、第2の出力ポート39bから出力される起動電圧は電圧シフトモジュール21が受け付ける起動電圧と比べ、一つのクロック信号分遅延し、第1の出力ポート39aから出力される電圧と第2の出力ポート39bから出力される電圧は完全に逆方向となる。このシフトレジスタは、受け付けた電圧信号を遅延して出力し、同時に、遅延して出力した電圧信号と逆方向の電圧信号を出力する目的を果たす。

## 【0028】

10

本実施例におけるシフトレジスタは、受け付けた電圧信号を遅延して出力することができ、且つ同時に、遅延して出力した電圧信号と逆方向の電圧を提供する。

## 【0029】

## 実施例二

図3は本発明の具体的な回路構造の模式図を示している。

## 【0030】

本実施例において、CLK1、CLK2、CLK3によって起動電圧信号を提供し、起動電圧源34と逆方向電圧源35はそれぞれ起動電圧と同じ方向の電圧と起動電圧と逆方向の電圧を提供する。このうち、CLK1は1/3周期ごとに一つの長さ1/3周期の電圧シフトモジュール起動電圧が出現し、CLK2は1/3周期ごとに一つの長さ1/3周期の電圧シフトモジュール起動電圧が出現し、且つ起動電圧の出現は第1のクロック信号の起動電圧より1/3周期遅れて出現し、CLK3は1/3周期ごとに一つの長さ1/3周期の電圧シフトモジュール起動電圧が出現し、且つ起動電圧は第2のクロック信号CLK2の起動電圧より1/3周期遅れる。

20

## 【0031】

本実施例における電圧シフトモジュールは、第1のスイッチ素子36aと、第1のコンデンサ37aと、第2のスイッチ素子36bとを有する。

## 【0032】

第1のスイッチ素子36aは、CLK1の制御のもとでスイッチ操作を行い、受け付けた起動電圧と同じ方向の電圧を、充電電圧として第1のコンデンサ37aに出力し、制御電圧として第2のスイッチ素子36bに出力するように制御する。

30

## 【0033】

第1のスイッチ素子36aの制御端はCLK1を受け付け、入力端は電圧信号を受け付け、出力端は第2のスイッチ素子36bの制御端に接続される。入力端が受け付ける電圧信号は外部のトリガ電圧信号であってもよく、カスケード方式を用いて接続される複数のシフトレジスタの組み合わせからなる駆動回路の場合の一段上のシフトレジスタが出力する電圧信号でもよい。

## 【0034】

第1のコンデンサ37aは、前記第1のスイッチ素子36aがオンし、起動電圧と同じ方向の電圧を受け付けるとき、一つの駆動制御電圧を第2のスイッチ素子36bに提供するように充電を行う

40

## 【0035】

第1のコンデンサ37aの一端は第2のスイッチ素子36bの制御端に接続され、他端は第2のスイッチ素子36bの出力端に接続される。第1のスイッチ素子36aがオンになったときに、第1のコンデンサ37aは充電を開始し、第1のスイッチ素子36aがオフになったときは、第1のコンデンサ37aは第2のスイッチ素子36bに電圧を提供する。

## 【0036】

第2のスイッチ素子36bは、第1のスイッチ素子36aが出力する制御電圧、第1のコンデンサ37aが提供する駆動制御電圧、あるいは第1の制御素子38aが出力する制

50

御電圧の制御のもとで、スイッチ操作を行うことによって、CLK2を制御電圧として第3のスイッチ素子36cに出力するように制御する。

【0037】

第2のスイッチ素子36bの制御端は第1のスイッチ素子36aの出力端に接続され、入力端はCLK2を受け付け、出力端は第3のスイッチ素子36cの制御端に接続される。

【0038】

前記電圧逆方向モジュールは第4のスイッチ素子36dと、第5のスイッチ素子36eと、第2のコンデンサ37bと、第6のスイッチ素子36fと、第7のスイッチ素子36gとを有する。

10

【0039】

第4のスイッチ素子36dは、第3のスイッチ素子36cが出力する制御電圧の制御のもとでスイッチ操作を行い、逆方向電圧源35が提供する電圧を第1の出力ポート39aから出力するように制御し、前記逆方向電圧源は該シフトレジスタの起動電圧と逆方向の電圧であり、前記第1の出力ポート39aは本段のシフトレジスタの出力に用いられることができる。

【0040】

第4のスイッチ素子36dの制御端は第3のスイッチ素子36cの出力端に接続され、入力端は逆方向電圧源35が提供する電圧を受け付け、出力端は第1の出力ポート39aに接続される。

20

【0041】

第1のスイッチ素子ないし第4のスイッチ素子が順次オンになり、起動電圧と同じ方向の起動電圧を起動電圧として一段後のシフトレジスタに出力するだけでなく、本段にも起動電圧と逆方向の電圧を提供する。

【0042】

第5のスイッチ素子36eは、CLK1の制御のもとでスイッチ操作を行い、起動電圧源34が提供する電圧を充電電圧として第2のコンデンサ37bに出力し、制御電圧として第6のスイッチ素子36fに出力するように制御する。

【0043】

第5のスイッチ素子36eの制御端はCLK1を受け付け、入力端は起動電圧源34が提供する電圧を受け付け、入力端は第6のスイッチ素子36fの制御端に接続される。

30

【0044】

第2のコンデンサ37bは、第5のスイッチ素子36eがオンのときに起動電圧源34が提供する電圧を受け付け、第4のスイッチ素子36dがオンのときに第6のスイッチ素子36fをオフにする。

【0045】

第2のコンデンサ37bの一端は第6のスイッチ素子36fの制御端に接続され、他端は第6のスイッチ素子36fの出力端に接続される。

【0046】

第6のスイッチ素子36fは、第5のスイッチ素子36e、第7のスイッチ素子36gが出力する制御電圧の制御のもとでスイッチ操作を行い、起動電圧源34が第1の出力ポート39aから出力するように制御する。

40

【0047】

第6のスイッチ素子36fの制御端は第5のスイッチ素子36eの出力端に接続され、入力端は起動電圧源34が提供する電圧を受け付け、出力端は第1の出力ポート39aに接続される。

【0048】

第7のスイッチ素子36gは、CLK3の制御のもとでスイッチ操作を行い、起動電圧源34が提供する電圧を制御電圧として第6のスイッチ素子36fに出力するように制御し、起動電圧源34が提供する電圧を第2のコンデンサ37bに出力して充電させる。

50

**【 0 0 4 9 】**

第7のスイッチ素子36gの制御端はC L K 3を受け付け、入力端は起動電圧源34に接続され、出力端は第6のスイッチ素子36fの制御端に接続される。

**【 0 0 5 0 】**

前記補充電圧モジュールは第3の制御素子38cとを有する。

**【 0 0 5 1 】**

第3の制御素子38cは、第1の出力ポート39aが出力する電圧の制御のもとでスイッチ操作を行い、逆方向電圧源35がオフ電圧として第4のスイッチ素子36dに電圧信号を出力するように制御し、且つ逆方向電圧源35が出力した電圧信号を第2の出力ポート39bから出力する。

10

**【 0 0 5 2 】**

第3の制御素子38cの制御端は第1の出力端39aに接続され、入力端は逆方向電圧源35が出力する電圧信号を受け付け、出力端は第4のスイッチ素子36dの制御端に接続される。

**【 0 0 5 3 】**

第5のスイッチ素子ないし第7のスイッチ素子は、第2の制御素子と第3の制御素子がオンになった後に第3のスイッチ素子、第4のスイッチ素子及び第2の出力ポートの出力を制御するように、第1の出力ポートに起動電圧を提供する。

**【 0 0 5 4 】**

前記電圧シフト制御モジュールは第1の制御素子38aとを有する。

20

**【 0 0 5 5 】**

第1の制御素子38aは、C L K 3の制御のもとでスイッチ操作を行い、第1のコンデンサ37aが逆方向電圧源35と接続された後に放電するように制御する。

**【 0 0 5 6 】**

第1の制御素子38aの制御端はC L K 3を受け付け、入力端は逆方向電圧源35に接続され、出力端は第2のスイッチ素子36の制御端に接続される。

**【 0 0 5 7 】**

前記電圧安定モジュールは第3のスイッチ素子36cとを有する。

**【 0 0 5 8 】**

第3のスイッチ素子36cは、第2のスイッチ素子36bが出力する制御電圧或は第2の制御素子38bが出力する制御電圧の制御のもとでスイッチ操作を行い、起動電圧源34が制御電圧として第4のスイッチ素子36dに出力するように制御し、起動電圧源が第2の出力ポート39bから出力するように制御し、前記第2の出力ポート36bは一段下のシフトレジスタに起動電圧を提供するために用いられ、前記起動電圧源は当該シフトレジスタの起動電圧と同じ電圧である。

30

**【 0 0 5 9 】**

第3のスイッチ素子36cの制御端は第2のスイッチ素子36bの出力端に接続され、入力端は起動電圧源34を受け付け、出力端は第4のスイッチ素子36dの制御端に接続される。

**【 0 0 6 0 】**

前記電圧安定制御モジュールは第2の制御素子38bとを有する。

40

**【 0 0 6 1 】**

第2の制御素子38bの出力端は第3のスイッチ素子36cの制御端に接続される。

**【 0 0 6 2 】**

第2の制御素子38bがオンになった後、第3のスイッチ素子36cをオフにする。

**【 0 0 6 3 】**

第2の出力ポート39bが出力するのは受け付けた電圧信号より遅延した後の電圧信号であり、当該信号は複数のシフトレジスタからなる駆動回路において、一段下のシフトレジスタに入力する信号としてもよい。また、第1の出力ポート39aが出力するのは第2の出力ポート39bが出力する電圧信号と逆方向の電圧信号であり、同時に逆方向電圧信

50

号による駆動が必要な回路に提供するために用いられる。

【 0 0 6 4 】

本実施例の作業シーケンスフローは以下の通りである。CLK1が起動電圧と同じ方向の電圧を出力した場合、第1のスイッチ素子36aはオンになり、第1のスイッチ素子36aが受け付けた起動電圧と同じ方向の電圧は第2のスイッチ素子36bに出力され、且つ第1のコンデンサ37aに出力され充電する。

【 0 0 6 5 】

第5のスイッチ素子36eはCLK1が出力した起動電圧と同じ方向の電圧の制御のもとでオンになり、起動電圧源34は第5のスイッチ素子36eを通じて第6のスイッチ素子36fに出力し、且つ第2のコンデンサ37bを充電し、第6のスイッチ素子36fは起動電圧源の制御のもとでオンになり、起動電圧源34は第6のスイッチ素子36fを通じて第1の出力ポート39aから起動電圧を出力する。

10

【 0 0 6 6 】

第2の制御素子38bと第3の制御素子38cは第1の出力ポート39aが出力する起動電圧の制御のもとでオンになり、逆方向電圧源35は第2の制御素子38bと第3の制御素子38cを通じて第3のスイッチ素子36cと第4のスイッチ素子36dにそれぞれ電圧信号を出力し、第3のスイッチ素子36cと第4のスイッチ素子36dをオフにし、このとき第2の出力ポート39bは逆方向電圧源35が提供する電圧信号を出力する。

【 0 0 6 7 】

C L K 1 が出力する電圧を起動電圧と逆方向の電圧に転換し、第 1 のコンデンサ 3 7 a は格納した電圧を第 2 のスイッチ素子 3 6 b に出力して、オンにする。

20

[ 0 0 6 8 ]

このとき、C L K 2 が出力した起動電圧と同じ方向の電圧はオンになった第2のスイッチ素子3 6 bを通じて第3のスイッチ素子3 6 cに出力され、第3のスイッチ素子3 6 cはC L K 2 が出力する起動電圧の制御のもとでオンになり、起動電圧源3 4 は第3のスイッチ素子3 6 cを介して第2の出力ポート3 9 bから起動電圧を出力するし、起動電圧源3 4 は第3のスイッチ素子3 6 cを通じて電圧信号を第4のスイッチ素子3 6 dに出力する。

[ 0 0 6 9 ]

第 4 のスイッチ素子 3 6 d がオンになった後、逆方向電圧源 3 5 は第 4 のスイッチ素子 3 6 d を介して第 1 の出力ポート 3 9 a から電圧信号を出力する。

30

【 0 0 7 0 】

第 2 のコンデンサ 37b は第 6 のスイッチ素子 36f にブートストラップファンクションを提供し、第 6 のスイッチ素子 36f をオフにさせる。

【 0 0 7 1 】

C L K 1 が起動電圧と同じ方向の電圧であるとき、第 5 のスイッチ素子 3 6 e がオンになり、さらに第 6 のスイッチ素子 3 6 f に起動電圧源 3 4 を提供し、C L K 2 が起動電圧と同じ方向の電圧であるとき、第 5 のスイッチ素子 3 6 e がオフになり、第 6 のスイッチ素子を C L K 2 が起動電圧であるときにオフにさせるために、コンデンサの両端を第 6 のスイッチ素子の制御端と出力端に接続する必要がある。それは、C L K 1 が起動電圧と同じ方向の電圧であるとき、起動電圧と同じ方向の電圧はオンである第 5 のスイッチ素子を通じて第 6 のスイッチ素子の制御端に出力されるからである。そして C L K 2 が起動電圧と同じ方向の電圧であるとき、第 5 のスイッチ素子がオフになり、第 6 のスイッチ素子の制御端はフローティングし、このとき、C L K 2 が起動電圧と同じ方向の電圧であるとき、第 1 の出力ポートの出力端は起動電圧と逆方向の電圧となるので、第 6 のスイッチ素子の制御端と出力端の電位差は第 6 スイッチ素子をオンにさせ、第 1 の出力ポートにも起動電圧と同じ方向の電圧を出力させて電圧の混乱を招いてしまう。したがって、第 6 のスイッチ素子の制御端の電圧を制御し、第 6 のスイッチ素子をオフの状態にするコンデンサが必要となる。したがって、第 2 のコンデンサ 3 7 b を付け加えることによって、第 2 のコンデンサ 3 7 b のポートストラップファンクションにより第 6 のスイッチ素子 3 6 f の制

40

50

御端電圧を起動電圧源の電圧から逆方向電圧源の電圧に転換し、次のクロック信号の起動電圧信号を受け付けるまで第6のスイッチ素子36fをオフの状態にさせる。

#### 【0072】

第1の出力ポート39aが出力する起動電圧と逆方向の電圧は第2の制御素子38bと第3の制御素子38cをもオフにする。

#### 【0073】

C L K 2 が output する 電圧信号が起動電圧と逆方向の電圧であるとき、C L K 3 は起動電圧と同じ方向の電圧を出力し、第7スイッチ素子36gと第1の制御素子38aをオンにする。第7のスイッチ素子36gがオンになった後、起動電圧源34は第6のスイッチ素子36fに電圧信号を出力し、第6のスイッチ素子36fをオンにする。第6のスイッチ素子36fがオンになった後、起動電圧源34は第1の出力ポート39aから電圧信号を出力し、起動電圧源34は第2の制御素子38bと第3の制御素子38cに電圧信号を出力する。第2の制御素子38bと第3の制御素子38cがオンになった後、逆方向電圧源35は第3のスイッチ素子36c、第2の出力ポート39b、第4のスイッチ素子36dに出力する。第3のスイッチ素子36cと第4のスイッチ素子36dはオフになり、第2の出力ポート39bは逆方向電圧を出力する。

10

#### 【0074】

本発明が提供するシフトレジスタは、第2の出力ポートからシフトされた電圧信号を出力し、且つ第1の出力ポートから第2の出力ポートが出力する電圧信号と逆方向の信号を出力することができ、逆方向の電圧信号を同時に必要とする需要に応えることができる。

20 したがって、本発明の提供するシフトレジスタによれば、一段下のシフトレジスタに受け付けた起動電圧を遅延させた後の電圧信号を出力するだけでなく、本段に、一段下のシフトレジスタに出力する信号と逆方向の電圧信号を出力することもできる。

#### 【0075】

本実施におけるC L K 1、C L K 2、C L K 3の起動電圧の継続時間は一周期の1/3に限らず、起動電圧の継続時間は必要に応じて調整することができ、C L K 1、C L K 2及びC L K 3の起動電圧の出現が時間上つながって循環するものであればよい。即ち、C L K 1の起動電圧がオフになったときにC L K 2の起動電圧がオンになり、C L K 2の起動電圧がオフになったときにC L K 3の起動電圧がオンになり、C L K 3の起動電圧がオフになったときにC L K 1の起動電圧がオンになればよい。

30

#### 【0076】

##### 実施例三

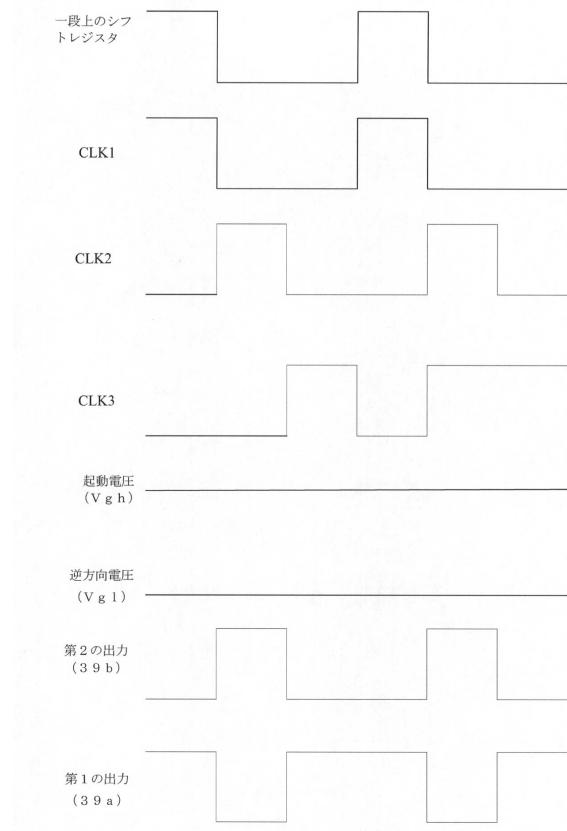

本発明のスイッチ素子と制御素子は電界効果トランジスタ、トライオード、薄膜トランジスタのいずれか又はいくつかの組み合わせであってもよい。本実施例において、Nチャネル型薄膜トランジスタをスイッチ素子と制御素子の手段として採用し、回路構造は図3と図4に示すとおりである。

#### 【0077】

本実施例は三つのクロック信号、高電圧電源と低電圧電源によってシフトレジスタにおける素子のオンとオフを制御する。本実施例が採用するのはNチャネル型薄膜トランジスタであるため、本実施例の起動電圧源は高電圧であり、逆方向電圧源は低電圧である。本実施例において、三つのクロック信号は以下のものが含まれる。C L K 1は1/3周期ごとに一つの長さ1/3周期の電圧シフトモジュール起動電圧が出現し、C L K 2は1/3周期ごとに一つの長さ1/3周期の電圧シフトモジュール起動電圧が出現し、且つ起動電圧の出現はC L K 1の起動電圧より1/3周期遅れて出現し、C L K 3は1/3周期ごとに一つの長さ1/3周期の電圧シフトモジュール起動電圧が出現し、且つ起動電圧はC L K 2の起動電圧より1/3周期遅れて出現し、また、高電圧源Vghと低電圧源Vglは、それぞれ起動電圧と同じ方向の電圧と起動電圧と逆方向の電圧を提供する。

40

#### 【0078】

本実施例において、第1のスイッチ素子36aは、一つの薄膜トランジスタM1を有する。当該薄膜トランジスタはC L K 1を受け付ける一つのゲート極と、起動電圧と同じ方

50

向の電圧を受け付ける一つのドレイン極と、薄膜トランジスタM 2 のゲート極に接続される一つのソース極とを有する。M 1 は C L K 1 の制御のもとでスイッチ操作を行い、受け付けた電圧信号を充電電圧として第1のコンデンサC 1 ( 3 7 a )に出力するように制御し、M 2 のオンを制御する。

#### 【 0 0 7 9 】

第2のスイッチ素子3 6 b は一つの薄膜トランジスタM 2 を有する。当該薄膜トランジスタは、薄膜トランジスタM 1 のソース極に接続される一つのゲート極と、C L K 2 を受け付ける一つのドレイン極と、薄膜トランジスタM 3 のゲート極に接続される一つのソース極とを有する。M 2 はM 1 が出力する制御電圧、第1のコンデンサC 1 が提供する駆動制御電圧あるいは薄膜トランジスタM 8 が出力する制御電圧の制御のもとでオンまたはオフになり、C L K 2 を制御電圧として薄膜トランジスタM 3 に出力するように制御する。

10

#### 【 0 0 8 0 】

第1のコンデンサC 1 ( 3 7 a )はM 1 がオンになって起動電圧信号を付けつけたとき、M 2 に一つの駆動制御電圧を提供するように充電を行う。

#### 【 0 0 8 1 】

第1のコンデンサC 1 の一端はM 2 のゲート極に接続され、他端はM 2 のソース極に接続される。

#### 【 0 0 8 2 】

第3のスイッチ素子3 6 c は一つの薄膜トランジスタM 3 を有する。当該薄膜トランジスタは、薄膜トランジスタM 2 のソース極に接続される一つのゲート極と、V g h を受け付ける一つのドレイン極と、薄膜トランジスタM 4 のゲート極に接続され、且つ第2の出力ポート3 9 b に接続される一つのソース極とを有する。M 3 はM 2 が出力する制御電圧あるいは薄膜トランジスタM 9 が出力する制御電圧の制御のもとでスイッチ操作を行い、V h g を制御電圧として薄膜トランジスタM 4 に出力し、同時に第2出力ポート3 9 b に出力するように制御する。

20

#### 【 0 0 8 3 】

第4のスイッチ素子3 6 d は一つの薄膜トランジスタM 4 を有する。当該薄膜トランジスタは、薄膜トランジスタM 3 のソース極に接続される一つのゲート極と、第1の出力ポート3 9 b に接続される一つのドレイン極と、V g 1 を受け付ける一つのソース極とを有する。M 4 はM 3 のソース極が出力する制御電圧の制御のもとでスイッチ操作を行い、V g 1 を第1の出力ポート3 9 a から出力するように制御し、前記第1の出力ポートは本段のシフトレジスタの出力として用いてもよい。薄膜トランジスタM 1 0 のドレイン極はM 4 のゲート極に接続される。

30

#### 【 0 0 8 4 】

M 1 - M 4 が順次オンになることで、受け付けた高電圧を遅延して一段下のシフトレジスタに出力することができる。

#### 【 0 0 8 5 】

第5のスイッチ素子3 6 e は一つの薄膜トランジスタM 5 を有する。当該薄膜トランジスタは、C L K 1 に接続される一つのゲート極と、V g h を受け付ける一つのドレイン極と、薄膜トランジスタM 6 のゲート極に接続される一つのソース極とを有する。M 5 はC L K 1 の制御のもとでスイッチ操作を行い、V g h を充電電圧として第2のコンデンサC 2 に出力し、制御電圧として薄膜トランジスタM 6 に出力するように制御する。

40

#### 【 0 0 8 6 】

第2のコンデンサC 2 ( 3 7 b )はM 4 がオンになってV g 1 を受け付けたときにM 6 をオフにする。

#### 【 0 0 8 7 】

第2のコンデンサC 2 の一端はM 6 のゲート極に接続され、他端はM 6 のソース極に接続される。

#### 【 0 0 8 8 】

第6のスイッチ素子3 6 f は一つの薄膜トランジスタM 6 を有する。当該薄膜トランジ

50

スタは、薄膜トランジスタM 5 のソース極に接続される一つのゲート極と、V<sub>g h</sub>を受け付ける一つのドレイン極と、第1の出力ポート39aに接続される一つのソース極とを有する。M 6 は、M 5 、薄膜トランジスタM 7 が出力する制御電圧または制御のもとでスイッチ操作を行い、V<sub>g h</sub>を第1の出力ポート39aから出力するように制御する。

#### 【0089】

第7のスイッチ素子36gは一つの薄膜トランジスタM 7 を有し、当該薄膜トランジスタは、CLK3を受け付ける一つのゲート極と、V<sub>g h</sub>を受け付ける一つのドレイン極と、薄膜トランジスタM 6 のゲート極に接続される一つのソース極とを有する。M 7 はCLK3の制御のもとでスイッチ操作を行い、V<sub>g h</sub>を制御電圧としてM 6 に出力するように制御する。

10

#### 【0090】

第1の制御素子38aは一つの薄膜トランジスタM 8 を有し、当該薄膜トランジスタは、CLK3を受け付ける一つのゲート極と、薄膜トランジスタM 2 のゲート極に接続される一つのドレイン極と、V<sub>g l</sub>を受け付ける一つのソース極とを有する。M 8 はCLK3の制御のもとでスイッチ操作を行い、第1のコンデンサC 1 がV<sub>g l</sub>に接続された後に放電するように制御する。

#### 【0091】

第2の制御素子38bは一つの薄膜トランジスタM 9 を有し、当該薄膜トランジスタは、第1の出力ポート39aに接続される一つのゲート極と、薄膜トランジスタM 3 のゲート極に接続される一つのドレイン極と、V<sub>g l</sub>を受け付ける一つのソース極とを有する。第1の出力ポート39aが出力する電圧の制御のもとでスイッチ操作を行い、V<sub>g l</sub>をオフ電圧としてM 3 に出力するように制御する。

20

#### 【0092】

第3の制御素子38cは一つの薄膜トランジスタM 10 を有し、当該薄膜トランジスタは、第1の出力ポート39aに接続される一つのゲート極と、M 3 のソース極に接続される一つのドレイン極と、V<sub>g l</sub>を受け付ける一つのソース極とを有する。第1の出力ポート39aが出力する電圧の制御のもとでスイッチ操作を行い、V<sub>g l</sub>をオフ電圧としてM 4 に出力し、且つV<sub>g l</sub>を第2の出力ポート39bから出力するように制御する。

#### 【0093】

M 5 ないしM 7 は、M 9 とM 10 がオンになった後にM 3 、M 4 と第2の出力ポート39bの出力を制御するよう、第1の出力ポート39aに高電圧を提供する。

30

#### 【0094】

M 8 はオンになった後に第1のコンデンサC 1 を放電し、M 2 をオフにする。

#### 【0095】

第2の出力ポート39bが出力するのは受け付けた電圧信号を遅延させた後の電圧信号であり、当該信号は複数のシフトレジスタが組み合わさった駆動回路において一段下のシフトレジスタに入力する信号とすることができ、第1の出力ポート39aが出力するのは第2の出力ポート39bが出力する電圧信号と逆方向の電圧信号であり、同時に逆方向電圧信号による駆動が必要な回路に提供するために用いられる。

#### 【0096】

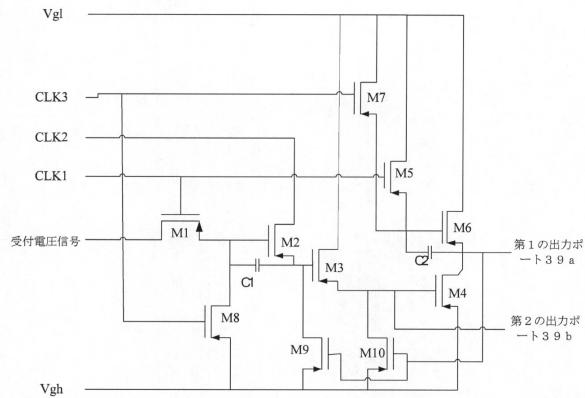

40

本実施例の作業フローは以下のとおりであり、シーケンス図は図5に示すとおりである。CLK1、CLK2、CLK3、起動電圧V<sub>g h</sub>、逆方向電圧V<sub>g l</sub>は入力信号であり、第1の出力39aと第2の出力39bはシフトレジスタの二つの出力ポートが出力する電圧信号である。

#### 【0097】

M 1 はCLK1の高電圧信号の制御のもとでオンになり、受け付けた高電圧をM 2 に出力し第1のコンデンサC 1 を充電する。M 5 はCLK1の高電圧信号の制御のもとでオンになり、高電圧をM 6 に出力し第2のコンデンサC 2 を充電する。M 6 はCLK1の高電圧信号の制御のもとでオンになり、高電圧を第1の出力ポート39aから出力する。M 9 、M 10 は第1の出力ポートが出力する高電圧のもとでオンになり、低電圧をM 3 、M 4

50

に出力し、M 3、M 4 をオフにする。低電圧はオンになったM 1 0 を通じて第2の出力ポート3 9 b から出力される。

#### 【0098】

C L K 2 は高電圧を出力し、同時にC L K 1 は低電圧に下がる。M 2 は第1のコンデンサC 1 の充電の作用のもとでオンになり、C L K 2 の高電圧はM 2 を通じてM 3 に出力される。M 3 がオンになった後、高電圧を第2の出力ポート3 9 b とM 4 に出力する。M 4 は高電圧の制御のもとでオンになり、低電圧はM 4 を通じて第1の出力ポート3 9 a から出力される。C L K 2 が起動電圧であるとき、M 6 の出力端の電圧はV g 1 であり、M 6 の制御端と出力端の電位差によってM 6 はオンになり、M 6 がオンになった後に高電圧も第1の出力ポート3 9 a から出力され、このとき、第1の出力ポート3 9 a は混乱状態になる。したがって、第2のコンデンサC 2 を付け加えることによって、C L K 2 が起動電圧に転換されたとき、第2のコンデンサC 2 のブートストラップファンクションによりM 6 の制御端の電圧を高電圧から低電圧に転換し、次の高電圧信号を受け付けるまでM 6 をオフの状態にする。M 9 、M 1 0 は第1の出力ポートが出力した低電圧の制御のもとでオフになる。10

#### 【0099】

C L K 3 は高電圧を出力し、C L K 2 は低電圧に下がる。M 7 はC L K 3 の制御もとでオンになり、高電圧をM 6 に出力し、M 6 はオンになった後に高電圧を第1の出力ポート3 9 a から出力する。M 9 、M 1 0 は第1の出力ポートが出力する高電圧の制御のもとでオンになり、低電圧をM 3 、第2の出力ポート3 9 b とM 4 に出力し、M 3 、M 4 がオフになる。M 8 は第3のクロック信号の制御のもとでオンになり、低電圧を第1のコンデンサC 1 に出力し、放電させる。20

#### 【0100】

本実施例におけるC L K 1 、C L K 2 とC L K 3 の起動電圧の継続時間は一周期の1 / 3 に限らず、起動電圧の継続時間は必要に応じて調整することができ、C L K 1 、C L K 2 及びC L K 3 の起動電圧の出現が時間上つながって循環するものであればよい。即ち、C L K 1 の起動電圧がオフになったときにC L K 2 の起動電圧がオンになり、C L K 2 の起動電圧がオフになったときにC L K 3 の起動電圧がオンになり、C L K 3 の起動電圧がオフになったときにC L K 1 の起動電圧がオンになればよい。

#### 【0101】

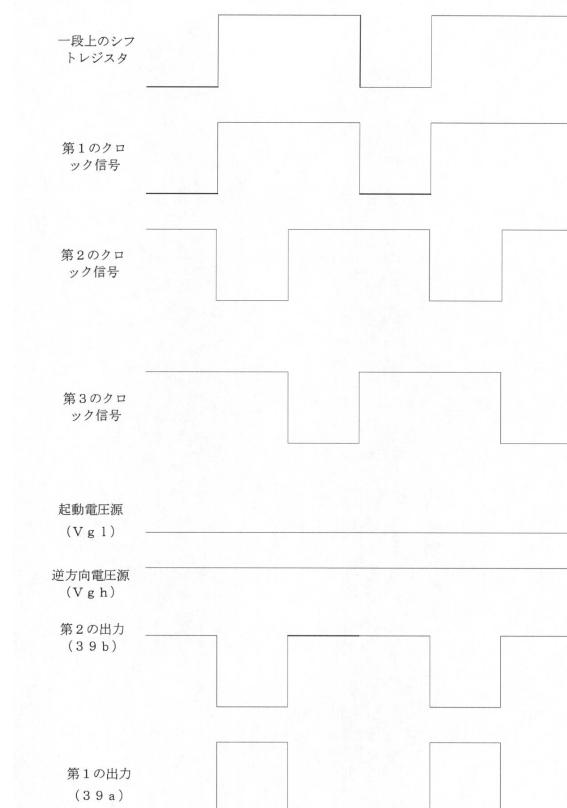

##### 実施例四

本発明におけるスイッチ素子と制御素子は電界効果トランジスタ、トライオード、薄膜トランジスタのいずれか又はいくつかの組み合わせであってもよい。本実施例において、Pチャネル型薄膜トランジスタをスイッチ素子と制御素子の手段として採用し、回路構造は図3と図6に示すとおりである。

#### 【0102】

本実施例は三つのクロック信号、高電圧電源と低電圧電源によってシフトレジスタにおける素子のオンとオフを制御する。本実施例が採用するのはPチャネル型薄膜トランジスタであるため、本実施例の起動電圧源は低電圧であり、逆方向電圧源は高電圧である。本実施例において、三つのクロック信号には以下のものが含まれる。C L K 1 は1 / 3 周期ごとに一つの長さ1 / 3 周期の電圧シフトモジュール起動電圧が出現し、C L K 2 は1 / 3 周期ごとに一つの長さ1 / 3 周期の電圧シフトモジュール起動電圧が出現し、且つ起動電圧の出現は第1のクロック信号の起動電圧より1 / 3 周期遅れて出現し、C L K 3 は1 / 3 周期ごとに一つの長さ1 / 3 周期の電圧シフトモジュール起動電圧が出現し、且つ起動電圧はC L K 2 の起動電圧より1 / 3 周期遅れて出現し、また、高電圧源V g h と低電圧源V g l は、それぞれ起動電圧と同じ方向の電圧と起動電圧と逆方向の電圧を提供する。40

#### 【0103】

当該シフトレジスタは以下のものを有する。

#### 【0104】

10

20

30

40

50

第1の出力素子36aは、一つの薄膜トランジスタM1を有する。当該薄膜トランジスタはCLK1を受け付ける一つのゲート極と、起動電圧と同じ方向の電圧即ち本実施例におけるVg1を受け付ける一つのドレイン極と、薄膜トランジスタM2のゲート極に接続される一つのソース極とを有する。M1はCLK1の制御のもとでスイッチ操作を行い、受け付けた電圧を充電電圧として第1のコンデンサC1に出力するように制御し、M2のオンを制御する。

#### 【0105】

第2のスイッチ素子36bは一つの薄膜トランジスタM2を有する。当該薄膜トランジスタは、薄膜トランジスタM1のソース極に接続される一つのゲート極と、CLK2を受け付ける一つのドレイン極と、薄膜トランジスタM3のゲート極に接続される一つのソース極とを有する。M2はM1が出力する制御電圧、第1のコンデンサC1が提供する駆動制御電圧あるいは薄膜トランジスタM8が出力する制御電圧の制御のもとでオンまたはオフになり、CLK2を制御電圧として薄膜トランジスタM3に出力するように制御する。

#### 【0106】

第1のコンデンサC1(37a)はM1がオンになって起動信号を付けつけたとき、M2に一つの駆動制御電圧を提供するように充電を行う。

#### 【0107】

第1のコンデンサC1の一端はM2のゲート極に接続され、他端はM2のソース極に接続される。

#### 【0108】

第3のスイッチ素子36cは一つの薄膜トランジスタM3を有する。当該薄膜トランジスタは、薄膜トランジスタM2のソース極に接続される一つのゲート極と、Vg1を受け付ける一つのドレイン極と、薄膜トランジスタM4のゲート極に接続され、且つ第2の出力ポート39bに接続される一つのソース極とを有する。M3はM2が出力する制御電圧あるいは薄膜トランジスタM9が出力する制御電圧の制御のもとでスイッチ操作を行い、Vg1をM4に出力してM4を制御し、且つ第2出力ポート39bにVg1を出力する。

#### 【0109】

薄膜トランジスタM9のドレイン極はM3のゲート極に接続される。

#### 【0110】

第4のスイッチ素子36dは一つの薄膜トランジスタM4を有する。当該薄膜トランジスタは、薄膜トランジスタM3のソース極に接続される一つのゲート極と、第1の出力ポート39bに接続される一つのドレイン極と、Vghを受け付ける一つのソース極とを有する。M4はM3のソース極が出力する制御電圧の制御のもとでスイッチ操作を行い、Vghを第1の出力ポート39aから出力するように制御する。薄膜トランジスタM10のドレイン極はM4のゲート極に接続される。

#### 【0111】

M1-M4が順次オンになることで、受け付けた起動電圧である低電圧を遅延して一段下のシフトレジスタに出力する。

#### 【0112】

第5のスイッチ素子36eは一つの薄膜トランジスタM5を有する。当該薄膜トランジスタは、CLK1を受け付ける一つのゲート極と、Vg1を受け付ける一つのドレイン極と、薄膜トランジスタM6のゲート極に接続される一つのソース極とを有する。M5はCLK1の制御のもとでスイッチ操作を行い、Vg1を充電電圧として第2のコンデンサC2に出力し、制御電圧として薄膜トランジスタM6に出力するように制御する。

#### 【0113】

第2のコンデンサC2(37b)は第4のスイッチ素子36dがオンになってVghを受け付けたときにM6をオフにする。

#### 【0114】

第2のコンデンサの一端はM6のゲート極に接続され、他端はM6のソース極に接続される。

10

20

30

40

50

**【 0 1 1 5 】**

第6のスイッチ素子36fは一つの薄膜トランジスタM6を有する。当該薄膜トランジスタは、薄膜トランジスタM5のソース極に接続される一つのゲート極と、Vg1を受け付ける一つのドレイン極と、第1の出力ポート39aに接続される一つのソース極とを有する。M6は、M5、薄膜トランジスタM7が出力する制御電圧または制御のもとでスイッチ操作を行い、Vg1を第1の出力ポート39aから出力するように制御する。

**【 0 1 1 6 】**

第7のスイッチ素子36gは一つの薄膜トランジスタM7を有する。当該薄膜トランジスタは、CLK3を受け付ける一つのゲート極と、Vg1を受け付ける一つのドレイン極と、薄膜トランジスタM6のゲート極に接続される一つのソース極とを有する。M7はCLK3の制御のもとでスイッチ操作を行い、Vg1を制御電圧としてM6に出力するよう10に制御する。

**【 0 1 1 7 】**

第1の制御素子38aは一つの薄膜トランジスタM8を有する。当該薄膜トランジスタは、CLK3を受け付ける一つのゲート極と、薄膜トランジスタM2のゲート極に接続される一つのドレイン極と、Vghを受け付ける一つのソース極とを有する。M8はCLK3の制御のもとでスイッチ操作を行い、第1のコンデンサC1がVghに接続された後に放電ように制御する。

**【 0 1 1 8 】**

第2の制御素子38bは一つの薄膜トランジスタM9を有する。当該薄膜トランジスタは、第1の出力ポート39aに接続される一つのゲート極と、薄膜トランジスタM3のゲート極に接続される一つのドレイン極と、Vghを受け付ける一つのソース極とを有する。第1の出力ポート39aが出力する電圧の制御のもとでスイッチ操作を行い、Vghをオフ電圧としてM3に出力するよう20に制御する。

**【 0 1 1 9 】**

第3の制御素子38cは一つの薄膜トランジスタM10を有する。当該薄膜トランジスタは、第1の出力ポート39aに接続される一つのゲート極と、M3のソース極に接続される一つのドレイン極と、Vghを受け付ける一つのソース極とを有する。第1の出力ポート39aが出力する電圧の制御のもとでスイッチ操作を行い、Vghをオフ電圧としてM4に出力し、且つVghを第2の出力ポート39bに出力するよう30に制御する。

**【 0 1 2 0 】**

M5ないしM7は、M9とM10がオンになった後にM3、M4を制御してM3、M4をオフにし、且つVghを第2の出力ポート39bから出力するように、第1の出力ポート39aに低電圧を提供する。

**【 0 1 2 1 】**

M8はオンになった後に第1のコンデンサC1を放電し、M2をオフにする。

**【 0 1 2 2 】**

第2の出力ポート39bが出力するのは受け付けた電圧信号を遅延させた後の電圧信号であり、当該信号は複数のシフトレジスタが組み合わさった駆動回路において一段下のシフトレジスタに入力する信号とすることができます、第1の出力ポート39aが出力するのは第2の出力ポート39bが出力する電圧信号と逆方向の電圧信号であり、同時に逆方向電圧信号による駆動が必要な回路に提供するために用いられる。

**【 0 1 2 3 】**

本実施例の作業フローは以下のとおりであり、シーケンス図は図7に示すとおりである。CLK1、CLK2、CLK3、逆方向電圧Vgh、起動電圧Vg1は入力信号であり、第1の出力39aと第2の出力39bはシフトレジスタの二つの出力ポートが出力する電圧信号である。

**【 0 1 2 4 】**

M1はCLK1の低電圧信号の制御のもとでオンになり、受け付けた起動電圧と同じ方向の電圧をM2に出力し第1のコンデンサC1を充電する。M5はCLK1の低電圧信号50

の制御のもとでオンになり、低電圧をM 6に出力し第2のコンデンサC 2を充電する。M 6はCLK 1の低電圧信号の制御のもとでオンになり、低電圧を第1の出力ポート3 9 aから出力する。M 9、M 10は第1の出力ポートが出力する低電圧のもとでオンになり、高電圧をM 3、M 4に出力し、M 3、M 4をオフにする。高電圧はオンになったM 10を通じて第2の出力ポート3 9 bから出力される。

#### 【0125】

CLK 2は低電圧を出力し、同時にCLK 1は高電圧に上がる。CLK 1が低電圧を出力するときに第1のコンデンサC 1に蓄積した電圧は、CLK 2が低電圧を出力するときにM 2に提供され、M 2は第1のコンデンサC 1の充電電圧の作用のもとでオンになり、CLK 2の低電圧はM 2を通じてM 3に出力される。M 3がオンになった後、低電圧を第2の出力ポート3 9 bとM 4に出力する。M 4は低電圧の制御のもとでオンになり、高電圧はM 4を通じて第1の出力ポート3 9 aから出力される。CLK 2が低電圧であるとき、M 6の出力端の電圧はVg hであり、M 6の制御端はフローリングするため、M 6の出力端と制御端の電位差によってM 6はオンになり、低電圧も第1の出力ポート3 9 aから出力され、このとき、第1の出力ポート3 9 aは混乱状態になる。したがって、第2のコンデンサC 2を付け加えることによって、第2のコンデンサC 2のポートストラップファンクションによりM 6の制御端の電圧を低電圧から高電圧に転換し、次の高電圧信号を受け付けるまでM 6をオフの状態にする。M 9、M 10は第1の出力ポートが出力した高電圧の制御のもとでオフになる。

#### 【0126】

CLK 3は低電圧を出力し、CLK 2は高電圧に上がる。M 7は第3のクロック信号の制御もとでオンになり、低電圧をM 6に出力し、M 6はオンになった後に低電圧を第1の出力ポート3 9 aから出力する。M 9、M 10は第1の出力ポートが出力する低電圧の制御のもとでオンになり、高電圧をM 3、第2の出力ポート3 9 bとM 4に出力し、M 3、M 4がオフになる。M 8はCLK 3の制御のもとでオンになり、高電圧を第1のコンデンサC 1に出力し、放電させる。

#### 【0127】

本実施例におけるCLK 1、CLK 2とCLK 3の起動電圧の継続時間は一周期の1/3に限らず、起動電圧の継続時間は必要に応じて調整することができ、CLK 1、CLK 2及びCLK 3の起動電圧の出現が時間上つながって循環するものであればよい。即ち、CLK 1の起動電圧がオフになったときにCLK 2の起動電圧がオンになり、CLK 2の起動電圧がオフになったときにCLK 3の起動電圧がオンになり、CLK 3の起動電圧がオフになったときにCLK 1の起動電圧がオンになればよい。

#### 【0128】

本発明は複数のシフトレジスタが組み合わさって構成される駆動回路を更に提供する。以下、図面を用いて本発明の駆動回路について説明する。

#### 【0129】

図8に示すように、駆動回路は第1段のシフトレジスタ8 1と、最後の段のシフトレジスタ8 Nと、少なくとも一つの中間の段のシフトレジスタ8 2～8 N-1から構成される。それぞれのシフトレジスタは上記の各実施例における前記シフトレジスタを採用し、各シフトレジスタの間はカスケード接続方式を用いて接続される。それぞれのシフトレジスタは二つの出力ポートを有し、第1の出力ポートが出力する電圧信号は受け付けた電圧信号がシフトされた後に出力する電圧信号であり、第2の出力ポートが出力する電圧信号は第1の出力ポートが出力する電圧信号と逆方向の電圧信号である。それぞれの段のシフトレジスタの電圧シフトモジュールは起動電圧と同じ方向の電圧を受け付ける。

#### 【0130】

第1段のシフトレジスタ8 1は、起動電圧と同じ方向の電圧を受け付け、当該起動電圧と同じ方向の電圧は外部からのトリガであり、第2の出力ポート3 9 bから一段下のシフトレジスタの電圧シフトモジュールに電圧を出力し、且つ第1の出力ポート3 9 aから第2の出力ポート3 9 bが出力する電圧と逆方向の電圧を出力するために用いられる。

10

20

30

40

50

**【 0 1 3 1 】**

それぞれの中間の段のシフトレジスタ 8 2 ~ 8 N - 1 は一段上のシフトレジスタの第 2 の出力ポート 3 9 b が出力する電圧を受け付け、第 2 の出力ポート 3 9 b から一段下のシフトレジスタの電圧シフトモジュールに電圧を出力し、且つ第 1 の出力ポート 3 9 a から第 2 の出力ポート 3 9 b が出力する電圧と逆方向の電圧を出力するために用いられる。

**【 0 1 3 2 】**

最後の段のシフトレジスタ 8 N は一段上のシフトレジスタの第 2 の出力ポート 3 9 b が出力する電圧を受け付け、且つ第 1 の出力ポート 3 9 a から第 2 の出力ポート 3 9 b が出力する電圧と逆方向の電圧を出力するために用いられる。

**【 0 1 3 3 】**

一段上のシフトレジスタの第 2 の出力ポートが出力する電圧を一段下のシフトレジスタの電圧シフトモジュールに入力する。また、一段上のシフトレジスタの第 1 の起動電圧信号をオフにするように制御した後、一段下のシフトレジスタの第 1 の起動電圧信号をオンにするように制御する。

**【 0 1 3 4 】**

図 8 における実施例では、シフトレジスタ 8 1 は駆動回路における第 1 段のシフトレジスタである。シフトレジスタ 8 2 はシフトレジスタ 8 1 の一段下のシフトレジスタであり、シフトレジスタ 8 3 はシフトレジスタ 8 2 の一段下のシフトレジスタであり、といった具合に、8 N の最後の段のシフトレジスタまで類推する。それぞれのシフトレジスタはいずれも C L K 1、C L K 2 と C L K 3 によって制御される。そして、C L K 1 が先に一つの起動電圧を出現させ、C L K 1 の起動電圧がオフになった後に C L K 2 に一つの起動電圧が一つの起動電圧を出現させ、C L K 2 の起動電圧がオフになった後に C L K 3 に一つの起動電圧が出現され、C L K 3 の起動電圧がオフになった後に C L K 1 に一つの起動電圧が出現される。

**【 0 1 3 5 】**

シフトレジスタ 8 1 の第 1 の起動電圧信号 8 1 a は C L K 1 から入力され、第 2 の起動電圧信号 8 1 b は C L K 2 から入力され、第 3 の起動電圧信号 8 1 c は C L K 3 から入力される。また、シフトレジスタ 8 1 の一段下のシフトレジスタであるシフトレジスタ 8 2 の第 1 の起動電圧信号 8 2 a は C L K 2 から入力され、第 2 の起動電圧信号 8 2 b は C L K 3 から入力され、第 3 の起動電圧信号 8 2 c は C L K 1 から入力される、といった具合に類推していく。このように、一段上のシフトレジスタの第 1 の起動電圧信号がオフになった後に一段下のシフトレジスタの第 1 の起動電圧信号がオンになるように制御する。即ち、一段下のシフトレジスタの第 1 のクロック信号のクロックはいずれも一段上のシフトレジスタの第 1 のクロック信号のクロックより 1 / 3 周期遅れる。本実施例において、三つのクロック信号の起動電圧期間は同一であるが、実際の応用ではこのような制限はなく、一つ前の起動信号がオフになった後に一つ後の起動信号がオンになり、三つのクロック信号が順次に循環してオンになればよい。

**【 0 1 3 6 】**

本実施例の駆動回路において、初めのシフトレジスタが受け付ける信号は外部からのトリガであり、中間の段のシフトレジスタと最後の段のシフトレジスタが受け付ける信号はいずれも自身と接続されている一段上のシフトレジスタの第 2 の出力ポートが出力した電圧である。同時に、それぞれの段のシフトレジスタはいずれも第 1 の出力ポートから第 2 の出力ポートが出力する電圧と逆方向の電圧を本段の出力として出力する。

**【 0 1 3 7 】**

本実施例における駆動回路は、複数の本発明におけるシフトレジスタから構成される。それぞれのシフトレジスタはいずれも自身が受け付けた起動電圧を遅延させて出力し、且つ遅延させた電圧と逆方向の電圧も出力する。このように、画素回路において同じ方向と逆方向の二種類の電圧が同時に必要となる場合、本発明の提供する電圧はこのような要求を満たすことができる。

**【 0 1 3 8 】**

10

20

30

40

50

本発明が提供する表示装置の実施例は、それぞれの表示装置において、上記駆動回路を取り付けるものである。駆動回路は少なくとも二つのシフトレジスタを有し、すべてのシフトレジスタはカスケード接続方式で接続される。

【0139】

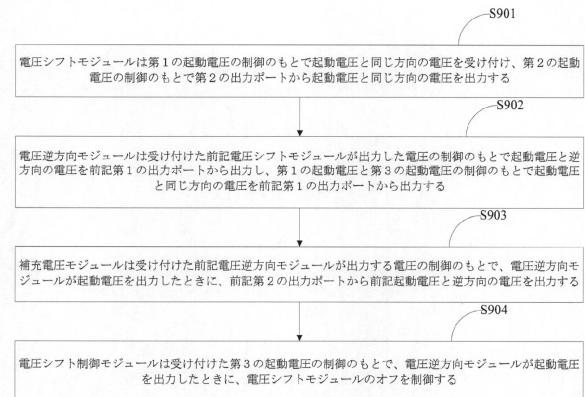

本発明は更に逆方向の出力を有するシフトレジスタにおけるシフト方法を提供し、以下に図9を用いて本発明の方法の実施例を説明する。

【0140】

ステップS901において、電圧シフトモジュールは第1の起動電圧の制御のもとで起動電圧と同じ方向の電圧を受け付け、第2の起動電圧の制御のもとで第2の出力ポートから起動電圧と同じ方向の電圧を出力する。

10

【0141】

ステップS902において、電圧逆方向モジュールは受け付けた前記電圧シフトモジュールが出力した電圧の制御のもとで、起動電圧と逆方向の電圧を前記第1の出力ポートから出力し、第1の起動電圧と第3の起動電圧の制御のもとで起動電圧と同じ方向の電圧を前記第1の出力ポートから出力する。

【0142】

ステップS903において、補充電圧モジュールは受け付けた前記電圧逆方向モジュールが出力する電圧の制御のもとで、電圧逆方向モジュールが起動電圧を出力したときに、前記第2の出力ポートから前記起動電圧と逆方向の電圧を出力する。

20

【0143】

ステップS904において、電圧シフト制御モジュールは受け付けた第3の起動電圧の制御のもとで、電圧逆方向モジュールが起動電圧を出力したときに、電圧シフトモジュールのオフを制御する。

【0144】

ただし、前記第1の起動電圧信号、前記第2の起動電圧信号、前記第3の起動電圧信号は順次に循環して出現する。

【0145】

当業者は、本発明の趣旨と範囲を逸脱することなく本発明に対して各種変更及び変形を行うことができることは明らかである。このように、これらの変更及び変形が本発明の特許請求の範囲及びその同視できる技術的範囲内であれば、本発明はこれらの変更及び変形を含む意味を有する。

30

【符号の説明】

【0146】

- |       |                    |

|-------|--------------------|

| 1 1   | D A T A 信号         |

| 1 2   | G A T E 信号         |

| 1 3   | R E S E T 信号       |

| 1 4   | V D D 信号           |

| 1 5   | E M I S S I O N 信号 |

| 2 1   | 電圧シフトモジュール         |

| 2 2   | 電圧逆方向モジュール         |

| 2 3   | 補充電圧モジュール          |

| 2 4   | 電圧シフト制御モジュール       |

| 2 5   | 電圧安定モジュール          |

| 2 6   | 電圧安定制御モジュール        |

| 3 9 a | 第1の出力ポート           |

| 3 9 b | 第2の出力ポート           |

40

【図1】

图1

【図8】

图8

【図2】

【図4】

【図3】

【図5】

【図6】

【図7】

【図9】

---

フロントページの続き

(74)代理人 100110364

弁理士 実広 信哉

(72)発明者 馬 占 潔

中華人民共和国 100176 北京市 経 濟 技 術 開 発 区 地 澤 路 9 号

審査官 塚田 肇

(56)参考文献 米国特許出願公開第 2011 / 0193892 (U.S., A1)

米国特許出願公開第 2009 / 0262051 (U.S., A1)

特開 2001 - 060398 (JP, A)

特開 2013 - 211088 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G 11 C 19 / 28