(12) 发明专利申请

(10) 申请公布号 CN 112166313 A

(43) 申请公布日 2021.01.01

(21) 申请号 201980035695.8

(74) 专利代理机构 北京柏杉松知识产权代理事

(22) 申请日 2019.04.10

务所(普通合伙) 11413

(30) 优先权数据

代理人 谢攀 刘继富

18174623.1 2018.05.28 EP

(51) Int.CI.

(85) PCT国际申请进入国家阶段日

G01L 9/00 (2006.01)

2020.11.26

H03M 3/00 (2006.01)

(86) PCT国际申请的申请数据

G01L 9/12 (2006.01)

PCT/EP2019/059149 2019.04.10

G01L 27/00 (2006.01)

(87) PCT国际申请的公布数据

G01L 1/14 (2006.01)

W02019/228700 EN 2019.12.05

H03M 1/10 (2006.01)

(71) 申请人 希奥检测有限公司

权利要求书2页 说明书22页 附图15页

地址 荷兰埃因霍温

(72) 发明人 阿尔贝托·马乔尼

权利要求书2页 说明书22页 附图15页

威廉·弗雷德里克·阿德里亚努

斯·贝斯林

(54) 发明名称

传感器装置和操作传感器装置的方法

(57) 摘要

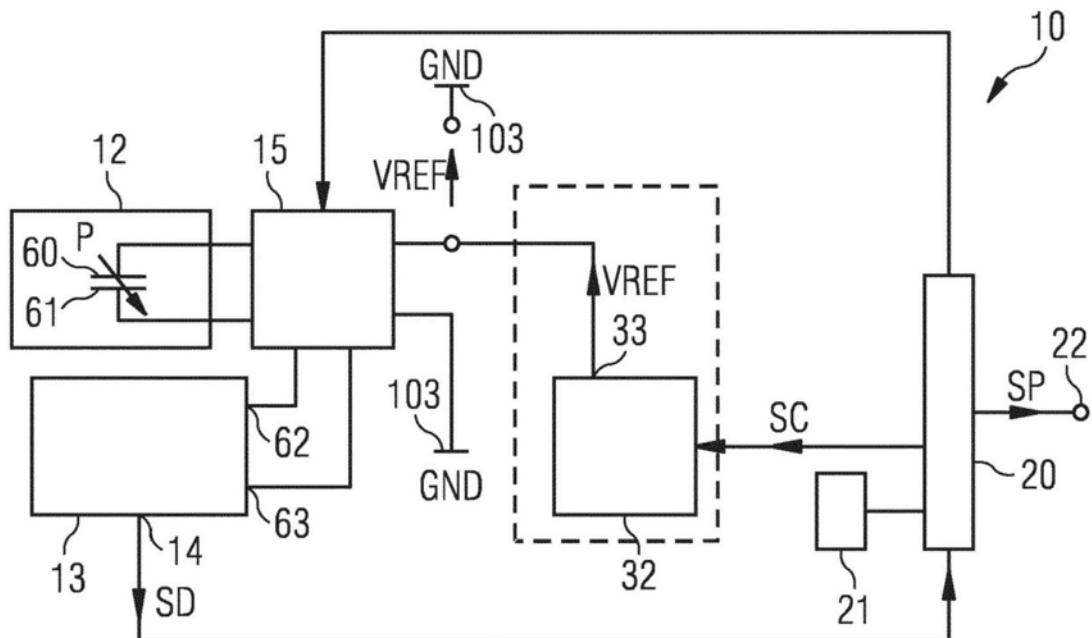

一种传感器装置(10)，包括：压力传感器(12)，其实现为电容式压力传感器；电容至数字转换器(13)，其耦接至压力传感器(12)并实现为delta-sigma模拟至数字转换器；以及参考电压发生器(32)，其具有用于接收控制信号(SC)的控制输入端和用于提供参考电压(VREF)的输出端(33)。参考电压发生器(32)的输出端(33)连接至电容至数字转换器(13)的输入端。参考电压发生器(32)被配置成根据控制信号(SC)来设置参考电压(VREF)的值。参考电压(VREF)的至少两个不同的值具有相同的符号和不同的量。

1. 一种传感器装置,包括

-压力传感器(12),其被实现为电容式压力传感器,

-电容至数字转换器(13),其耦接至所述压力传感器(12)并且被实现为delta-sigma模拟至数字转换器,以及

-参考电压发生器(32),其具有用于接收控制信号(SC)的控制输入端和用于提供参考电压(VREF)的输出端(33),

其中,所述参考电压发生器(32)的输出端(33)连接至所述电容至数字转换器(13)的输入端,

其中,所述参考电压发生器(32)被配置成根据所述控制信号(SC)来设置所述参考电压(VREF)的值,以及

其中,所述参考电压(VREF)的至少两个不同的值具有相同的符号和不同的量。

2. 根据权利要求1所述的传感器装置,

其中,所述传感器装置(10)被实现为半导体本体(11),并且

其中,所述半导体本体(11)包括所述压力传感器(12)和所述电容至数字转换器(13)。

3. 根据权利要求1或2所述的传感器装置,

包括被实现为电容式压力传感器的另一压力传感器(30),其中,所述电容至数字转换器(13)耦接至所述另一压力传感器(30)。

4. 根据权利要求3所述的传感器装置,

其中,所述半导体本体(11)包括所述另一压力传感器(30)。

5. 根据权利要求1至4中的一项所述的传感器装置,包括

-数字电路(20),其耦接至所述电容至数字转换器(13)和所述参考电压发生器(32),以及

-存储器(21),其连接至所述数字电路(20),

其中,所述数字电路(20)被配置成生成所述控制信号(SC)。

6. 根据权利要求5所述的传感器装置,

其中,在操作的测试阶段中,

所述数字电路(20)被配置成通过所述控制信号(SC)来控制所述参考电压发生器(32),使得所述参考电压发生器(32)连续地生成所述参考电压(VREF)的至少两个不同的值,

所述电容至数字转换器(13)被配置成根据包括所述压力传感器(12)和所述另一压力传感器(30)的组中的至少一个传感器的电容值来生成数字信号(SD)的至少两个值,以及

所述数字电路(20)被配置成根据所述数字信号(SD)的至少两个值来生成参数A0和/或校正数据。

7. 根据权利要求6所述的传感器装置,

其中,所述数字电路(20)被配置成将所述参数A0或校正数据存储在所述存储器(21)中。

8. 根据权利要求5至7中的一项所述的传感器装置,

其中,在操作的测量阶段中,所述数字电路(20)被配置成根据由所述电容至数字转换器(13)提供的数字信号(SD)并且根据存储在所述存储器(21)中的参数A0和/或校正数据来生成数字化压力信号(SP)。

9. 根据权利要求3至8中的一项所述的传感器装置，

其中，所述传感器装置(10)被配置成确定所述压力传感器(12)与所述另一压力传感器(30)之间的不匹配，例如参数A0的不匹配。

10. 一种设备，

包括根据权利要求1至9中的一项所述的传感器装置(10)，其中，所述设备被实现为移动设备、可穿戴设备、医疗设备、车辆和空调之一。

11. 一种操作传感器装置的方法，包括

在参考电压发生器(32)的控制输入端处接收控制信号(SC)，

在所述参考电压发生器(32)的输出端(33)处提供参考电压(VREF)，以及

由电容至数字转换器(13)根据由所述电容至数字转换器(13)提供给压力传感器(12)的所述参考电压(VREF)来测量所述压力传感器(12)的电容，

其中，所述压力传感器(12)被实现为电容式压力传感器，

其中，所述电容至数字转换器(13)被实现为delta-sigma模拟至数字转换器，

其中，所述参考电压发生器(32)的输出端(33)连接至所述电容至数字转换器(13)的输入端，

其中，所述参考电压发生器(32)根据所述控制信号(SC)来设置所述参考电压(VREF)的值，以及

其中，所述参考电压(VREF)的至少两个不同的值具有相同的符号和不同的量。

12. 根据权利要求11所述的方法，

其中，所述参考电压(VREF)是DC电压。

13. 根据权利要求11或12所述的方法，

其中，所述参考电压(VREF)施加在所述压力传感器(12)的第一电极(60)与所述压力传感器(12)的第二电极(61)之间。

14. 根据权利要求11至13中的一项所述的方法，

其中，在操作的测试阶段中，

由所述电容至数字转换器(13)向所述压力传感器(12)提供所述参考电压(VREF)的至少两个不同的值，

所述电容至数字转换器(13)根据所述压力传感器(12)的电容值生成数字信号(SD)的至少两个值，以及

数字电路(20)根据所述数字信号(SD)的至少两个值生成参数A0和/或校正数据。

## 传感器装置和操作传感器装置的方法

[0001] 本公开内容涉及传感器装置和操作传感器装置的方法。

[0002] 传感器装置包括传感器,例如压力传感器。压力传感器通常具有膜。压力传感器还可以包括两个或多于两个的膜。所述膜可以被制造为微机电系统膜,缩写为MEMS膜。在膜的两侧之间存在压差的情况下,膜被偏转。压力传感器通常被实现为电容式压力传感器。因此,膜的偏转导致压力传感器的电容值的变化。压力传感器通常连接至电容至数字转换器以产生取决于膜的两侧之间的压力差的数字值。文献US 2015/0295587A1示出了电容至数字转换器的示例。压力测量的稳定性和灵敏度高度取决于膜的物理特性。这些物理特性在压力传感器的不同示例中可以不同,并且在压力传感器的寿命期间可以变化。

[0003] 目的是提供一种传感器装置和一种操作传感器装置的方法,所述传感器装置提高了传感器测量结果的精度。

[0004] 通过独立权利要求的主题来实现这些目的。在从属权利要求中描述进一步的发展和实施例。

[0005] 在实施例中,传感器装置包括被实现为电容式压力传感器的压力传感器、耦接至所述压力传感器并被实现为delta-sigma模拟至数字转换器的电容至数字转换器、以及具有用于接收控制信号的控制输入端和用于提供参考电压的输出端的参考电压发生器。参考电压发生器的输出端连接至电容至数字转换器的输入端。参考电压发生器被配置成根据控制信号来设置参考电压的值。参考电压的至少两个不同的值具有相同的符号和不同的量。

[0006] 有利地,能够将参考电压的至少两个不同的值施加至压力传感器。因此,传感器的第一电极到压力传感器的第二电极的距离能够通过参考电压的至少两个不同值来改变。第一电极可以是压力传感器的膜或膜的一部分。因此,能够使用不同的参考电压的值来测试压力传感器。

[0007] 在实施例中,传感器装置被实现为半导体本体。半导体本体包括压力传感器,简称为传感器,以及电容至数字转换器,简称为转换器或变换器。有利地,传感器与转换器的连接能够保持短接。

[0008] 在实施例中,传感器装置包括被实现为电容式压力传感器的另一压力传感器。电容至数字转换器被耦接至另一压力传感器,其简称为另一传感器。通过使用两个传感器能够提高精度。

[0009] 在实施例中,半导体本体包括另一传感器。有利地,传感器和另一传感器利用相同的制造步骤生产。

[0010] 在实施例中,传感器装置包括耦接至电容至数字转换器和参考电压发生器的数字电路。传感器装置包括连接至数字电路的存储器。数字电路被配置成产生控制信号。

[0011] 在实施例中,在操作的测试阶段中,数字电路被配置成通过控制信号来控制参考电压发生器,使得参考电压发生器连续地生成参考电压的至少两个不同的值。电容至数字转换器被配置成根据包括压力传感器和另一压力传感器的组中的至少一个传感器的电容值来生成数字信号的至少两个值。数字电路被配置成根据数字信号的至少两个值来生成参数A0和/或校正数据。有利地,传感器装置被配置成仅使用作为传感器装置的一部分的电路

部分来执行校准。

[0012] 在实施例中,在操作的测试阶段,参考电压的值和数字信号的值用于使用例如以下等式之一确定参数A0和/或参数B0和/或参数C0:

[0013]  $C = C_0 + B_0 \cdot V_{REF} + A_0 \cdot V_{REF}^2$ , 或

[0014]  $C = C_0 + A_0 \cdot V_{REF}^2$ ,

[0015] 其中,C是包括压力传感器和另一压力传感器的组中的至少一个传感器的电容值CA、CB,VREF是参考电压或施加在至少一个传感器的第一电极与第二电极之间的电压的值,并且C0、B0和A0是参数。有时,C0被写为A2,并且B0被写为A1。

[0016] 在实施例中,数字电路被配置成将参数A0或校正数据存储在存储器中。

[0017] 在实施例中,在操作的测量阶段,数字电路被配置成根据由电容至数字转换器提供的数字信号并根据存储在存储器中的参数A0和/或校正数据来生成数字化压力信号。操作的测量阶段在操作的测试阶段之后。

[0018] 在实施例中,传感器装置被配置成确定压力传感器与另一压力传感器之间的不匹配,例如参数A0的不匹配。有利地,仅正确操作的传感器的数据用于生成数字化压力信号。

[0019] 在实施例中,一种设备包括传感器装置。所述设备被实现为移动设备、可穿戴设备、医疗设备、车辆和空调之一。

[0020] 在实施例中,一种操作传感器装置的方法包括:在参考电压发生器的控制输入端处接收控制信号;在参考电压发生器的输出端处提供参考电压;以及由电容至数字转换器根据由电容至数字转换器提供给传感器的参考电压来测量压力传感器的电容。压力传感器被实现为电容式压力传感器。电容至数字转换器被实现为delta-sigma模拟至数字转换器。参考电压发生器的输出端连接至电容至数字转换器的输入端。参考电压发生器根据控制信号来设置参考电压的值。参考电压的至少两个不同的值具有相同的符号和不同的量。

[0021] 在实施例中,参考电压是DC电压。

[0022] 在实施例中,参考电压施加在压力传感器的第一电极与压力传感器的第二电极之间。

[0023] 在实施例中,在操作的测试阶段,由电容至数字转换器向传感器提供参考电压的至少两个不同的值。电容至数字转换器根据传感器的电容值生成数字信号的至少两个值。数字电路根据数字信号的至少两个值生成参数A0和/或校正数据。

[0024] 在实施例中,在操作的测试阶段,如果参数B0被设置为0,则在参考电压的正好两个值处的测量给出相关信息,例如参数A0和C0。因此,可以使用等式: $C = C_0 + A_0 \cdot V_{REF}^2$

[0025] 在实施例中,在操作的测试阶段,由电容至数字转换器向传感器提供参考电压的至少三个不同的值。电容至数字转换器根据传感器的电容值产生数字信号的至少三个值。数字电路根据数字信号的至少三个值来产生参数A0和/或校正数据。因此,可以使用以下等式之一:

[0026]  $C = C_0 + A_0 \cdot V_{REF}^2$  or  $C = C_0 + B_0 \cdot V_{REF} + A_0 \cdot V_{REF}^2$

[0027] 在一个实施例中,因为由于内建电荷,C-V曲线的底部不一定在 $V_{REF} = 0V$ 处,因此仅当在参考电压的至少三个值处测量传感器的电容值的情况下,才能正确地得到参数A0。

[0028] 在一个实施例中,如果不使用参考电压,则不能正确地测量传感器的电容值。

[0029] 可以例如通过根据以上定义的实施例之一的传感器装置来实现操作传感器装置

的方法。

[0030] 本公开内容涉及一种具有采用可变电压参考的四个端子的差分电容至数字转换器设计。

[0031] 压力传感器是应变敏感设备。在最终测试期间,机械应力被施加在封装上,并因此它们能够被转移至压力敏感膜。较大的膜应力通常导致较小的膜挠曲,并因此观察到的压力读数向较低压力移动。校准期间的机械负载导致在校准算法中得到补偿的应力条件。存储在设备的存储器中的校准常数属于最终测试期间的应力状态。然而,在去除机械应力条件之后,所述设备将不再给出正确的读数。在焊接安装压敏设备之后,由于压力传感器封装和PCB材料 (PCB是印刷电路板的简称) 的热膨胀系数不匹配,因此压力传感器将暴露于热应力。这些不同的应力条件也没有得到补偿,并且导致与实际环境压力的进一步偏离。由于老化,例如由于胶硬化,传感器也会随着时间经历不同的应力条件。而且,不同的湿度水平可能使胶或PCB材料膨胀,这将对压力输出读数产生影响。

[0032] 本公开内容涉及在校准期间测量换能器特性,并且在将换能器焊接安装到客户PCB材料上之后将换能器与换能器特性相关联。因此,本公开内容能够用于补偿在测试、组装期间和在寿命期间的不同应力条件。

[0033] 本公开内容基于用作对电容式压力传感器的读出的电容至数字变换器或转换器(简写为C2D)设计。使用这种C2D变换器,能够通过测量电压来测量换能器电容。利用这种方法,能够提取膜柔度和压力灵敏度。在施加偏压时,压力敏感膜被静电力朝向对电极吸引。能够通过电容的增加来感测增加的膜偏转。对于某一膜分离的电容变化越大,设备的压力灵敏度越大。C2D变换器被配置成差动式并且具有四个端子。两个匹配的压力敏感膜可以连接至C2D变换器。

[0034] 两个压力敏感膜可以直接构造在CMOS读出电路的顶部上,以便减小寄生电容并减小噪声。

[0035] 压力敏感膜的特征可以是例如在没有读出ASIC的情况下通过在晶圆上探测它并且用网络或阻抗分析器测量电容至电压响应。

[0036] 每个生产晶圆中的特定区域可以专用于测试在最终产品中未使用的膜。尽管这些过程控制监视器 (PCM) 结构给出对膜柔度、堆叠高度、膜厚度等的一般反馈,但是它们不能够用于校准位于PCM周围或者甚至与PCM相邻的个体设备。集成的解决方案,即具有可偏置参考电压的电容至数字变换器得到针对每个个体的设备的特征设备属性,例如电容至电压响应 (A0参数)。

[0037] 传感器装置可以被配置成例如以下中的至少之一:

[0038] -由于差分读出的低噪声电容转换。

[0039] -测量C-V曲线 (C-V是电容对电压或电容电压的缩写) 的可能性。

[0040] -测量两个电容的不匹配。

[0041] -在校准之后和在组装之后使用片上读出电路提取压力灵敏度/膜柔度。

[0042] -使用片上C-V测量方法基于灵敏度分析来重新调整校准参数。

[0043] 在实施例中,传感器装置基于用于具有两个压力敏感膜和例如四个端子的电容式压力传感器的差分电容至数字变换器设计。能够改变电容至数字变换器的电压参考,以便产生柔性压力敏感膜朝向固定底部电极的可变静电吸引。然后根据施加的电压测量电容。

在正常操作中(例如在测量阶段),参考电压是固定的。在测试模式中(例如在测试阶段中),针对不同的参考电压记录电容变化。

[0044] 以下对实施例的附图的描述还可以示出和说明了传感器装置和操作传感器装置的方法的各方面。具有相同结构和相同效果的设备和电路部分分别用相同的附图标记表示。在设备或电路部件在不同附图中在其功能方面彼此对应的情况下,对于以下附图中的每一个不再重复其描述。

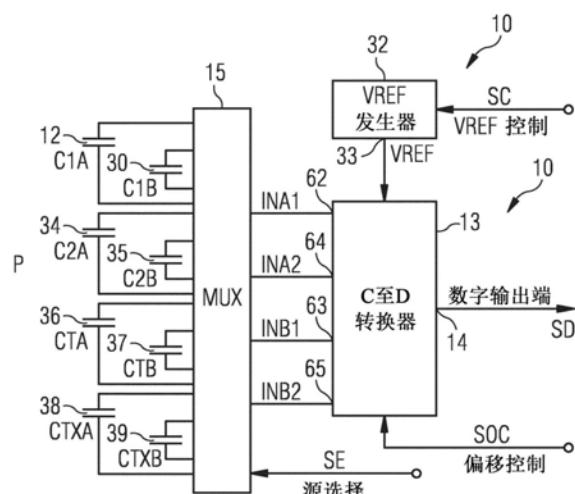

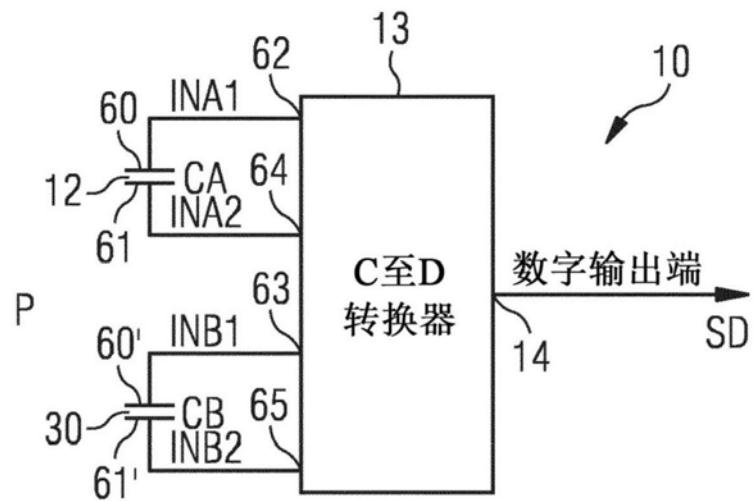

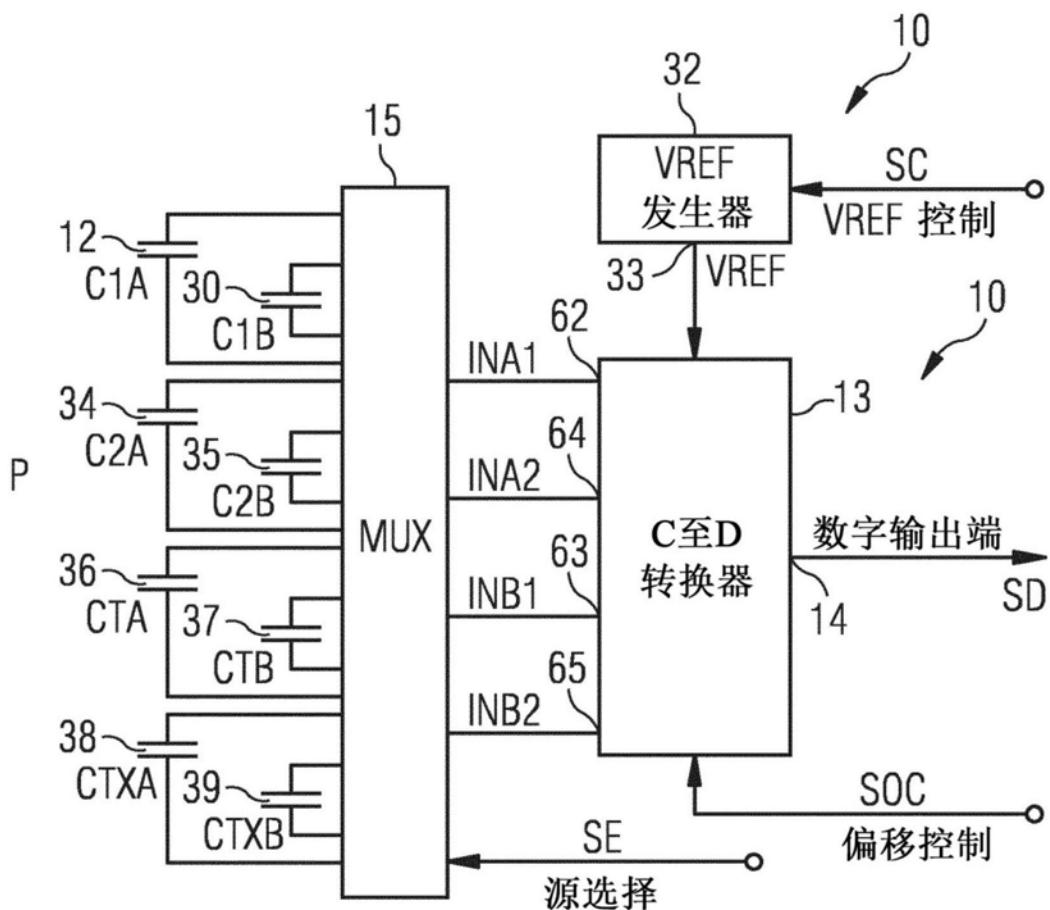

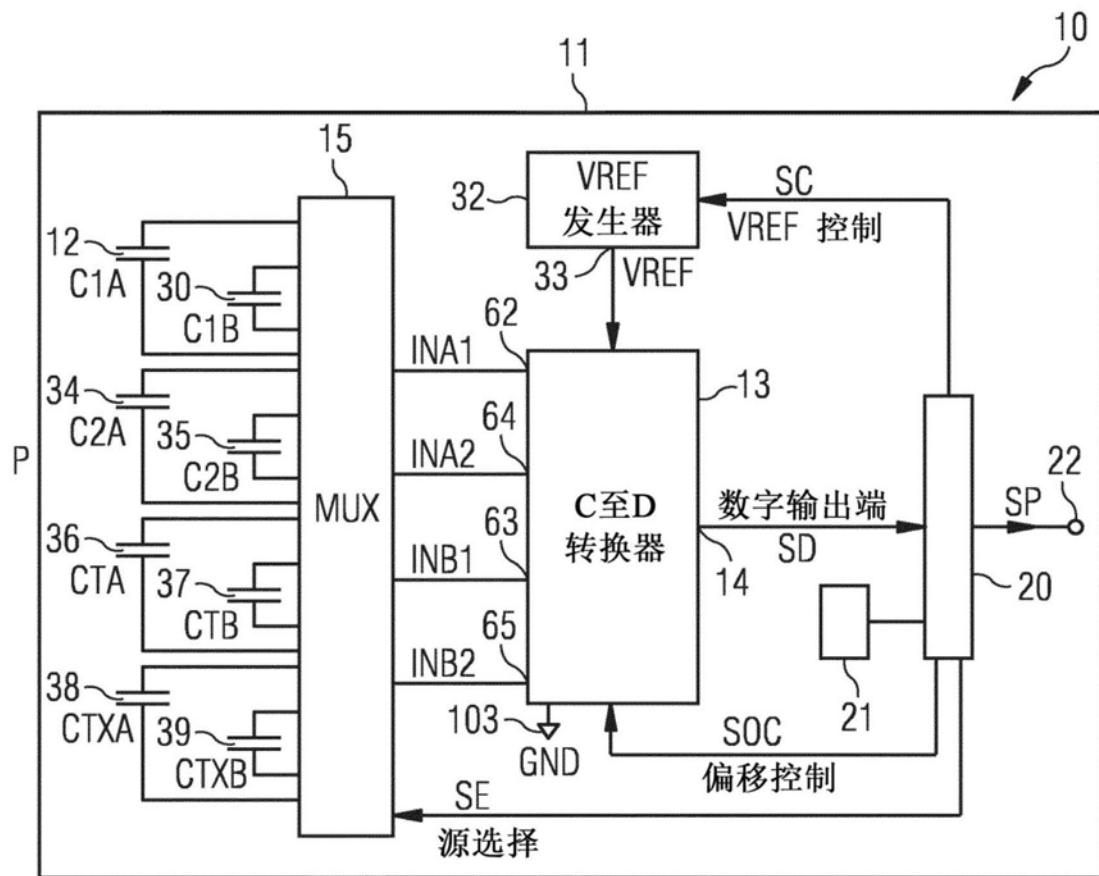

[0045] 图1A至图1D示出了传感器装置的示例;

[0046] 图2示出了压力传感器的示例;

[0047] 图3A至图3H示出了传感器装置的另一示例;

[0048] 图4A至图4F示出了传感器装置的特性的示例;以及

[0049] 图5A和图5B示出了传感器装置的其他示例。

[0050] 图1A示出了传感器装置10(简称为装置)的实施例的示例。装置10包括压力传感器12,其被实现为电容式压力传感器并且简称为传感器。压力传感器12具有电容CA(其可以被称为C1)。因此,传感器装置10被实现为压力传感器装置。装置10包括电容至数字转换器13,简称为转换器。转换器13耦接至传感器12。传感器12包括第一电极60和第二电极61。装置10包括另一压力传感器30,其被实现为另一电容式压力传感器并简称为另一传感器。另一传感器30具有另一电容CB(其可以被称为C2)。另一传感器30包括第一电极60'和第二电极61'。

[0051] 转换器13包括第一输入端62和第二输入端63。传感器12的第一电极60耦接至转换器13的第一输入端62,并且另一传感器30的第一电极60'耦接至转换器13的第二输入端63。传感器12的第二电极61可以耦接至转换器13的第三输入端64,并且另一传感器30的第二电极61'可以耦接至转换器13的第四输入端65。转换器13包括输出端14。输入端62至65可以实现为端子、输出端或组合的输入端/输出端。

[0052] 电容CA和另一电容CB取决于施加至装置10的压力P。在转换器13的输出端14处提供数字信号SD。数字信号SD也能够称为数字输出或数字输出信号。转换器13将电容CA和另一电容CB转换成数字信号SD。因此,数字信号SD是压力P的函数。在图1A中,示出了传感器装置10的电路的示意性框图。传感器装置10由具有四个输入端子62至65的电容至数字变换器13实现。

[0053] 图1B示出了作为图1A所示的示例的进一步发展的传感器装置10的另一示例。在图1B中,示出了传感器装置10的电路的扩展框图。装置10包括开关电路15。开关电路15可以实现为多路复用器,简写为MUX。开关电路15将转换器13耦接至传感器12和另一传感器30。转换器13的第一输入端62和第二输入端63经由开关电路15耦接至传感器12的第一电极60和另一传感器30的第一电极60'。类似地,转换器13的第三输入端64和第四输入端65可以经由开关电路15耦接至传感器12的第二电极61和另一传感器30的第二电极61'。

[0054] 此外,传感器装置10包括参考电压发生器32,简称为发生器。发生器32的输出端33连接至转换器13的输入端。装置10可以包括第一电容器34至第六电容器39。转换器13经由开关电路15耦接至第一电容器34至第六电容器39。第一电容器34至第六电容器39可以实现为附加的压力传感器和/或固定电容器。固定电容器是压敏的。图1A所示的电容CA对应于图1B所示的电容C1A。图1A所示的电容CB对应于图1B所示的电容C1B。

[0055] 在一个示例中,开关电路15可以将具有电容C2A、CTA、CTXA的第一、第三和第五电容器34、36、38中的至少之一替代传感器12或者与传感器12并联地耦接至转换器13。开关电路15可以将具有电容C2B、CTB、CTXB的第二、第四和第六电容器35、37、39中的至少之一替代另一传感器30或者与另一传感器30并联地耦接至转换器13(例如,如图3E所示)。因此,在有缺陷的情况下,压力传感器12、30可以由另一传感器代替,或者可以增加要由转换器13测量的电容值。

[0056] 控制信号SC被提供给发生器32。控制信号SC可以被称为VREF控制。发生器32产生参考电压VREF。参考电压VREF取决于控制信号SC。参考电压VREF被提供给转换器13。偏移控制信号SOC被提供给转换器13。源选择信号SE被施加至开关电路15。

[0057] 图1C示出了作为图1A和图1B所示实施例的进一步发展的传感器装置10的另一示例。装置10在半导体本体11上实现。传感器12、另一传感器30和转换器13在半导体本体11的第一表面上实现。开关电路15和发生器32也在半导体本体11的第一表面上实现。固定电容器34至39可以实现为例如半导体本体11的第一表面上的金属-绝缘体-金属电容器。

[0058] 此外,传感器装置10包括数字电路20,所述数字电路耦接至转换器13、发生器32以及开关电路15。数字电路20接收数字信号SD。数字电路20产生控制信号SC、偏移控制信号SOC以及源选择信号SE。此外,传感器装置10包括耦接至数字电路20的存储器21。转换器13连接至参考电位端子103。在参考电位端子103处,能够分接参考电位GND。数字电路20包括输出端22。在数字电路20的输出端22处提供数字化压力信号SP。在转换的一个或多个特定相位中,转换器13可以例如经由输入端62至65之一向开关电路15提供参考电压VREF。在转换的一个或多个相位中,转换器13也可以例如经由输入端62至65之一向开关电路15提供参考电位GND。

[0059] 两个电容式压力传感器膜12、30直接集成在CMOS、CMOS电路、CMOS管芯或CMOS半导体本体11的顶部上。因此,双电容器12、30与转换器13在同一管芯中(没有到CDC转换器的连接线,尤其没有倒装芯片连接的接合线)。两个传感器12、30完全相同,并且具有相同的寄生电容器,然而,寄生电容器非常小,因此在此未示出。它们对待测量的量的响应是相同的。在本公开中,电容器是成双的,连接至CDC转换器13的两个互补输入端62、63。传感器装置10实现为使用四个输入端子62至65(即不允许端子共享)的电容式压力传感器的电容至数字变换器设计的差分配置。双膜12、30通过四个端子62至65连接至电容至数字变换器13(短接CDC)。

[0060] 对于可替代的电容式压力传感器,可以采用单端电容至数字变换器拓扑结构用于电容读出。压力传感器可以使用可以经由引线接合连接至读出ASIC的独立的MEMS电容式压力传感器元件。可以使用单个压力敏感膜配置。

[0061] 在未示出的可替代实施例中,装置10包括比图1B和图1C中示出的电容器少的电容器34至39。例如,装置10可以包括电容器34至39中的正好一个、正好两个或正好四个电容器。装置10还可以例如没有另一电容器。

[0062] 图1D示出了作为图1A至图1C所示的实施例的进一步发展的装置10的另一示例。装置10可以没有另一压力传感器30。发生器32可以产生两个不同的参考电压值VREF。两个值中的每个值可以是正的。发生器32产生用于传感器12的测试的两个参考电压值VREF。发生器32可以被称为测试电路。

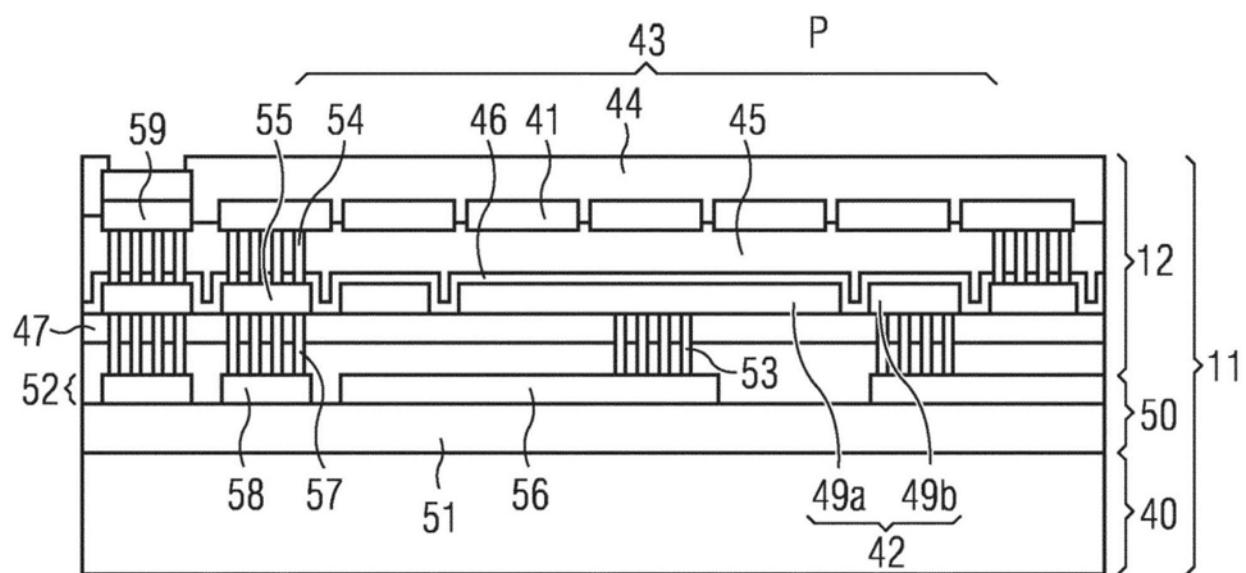

[0063] 图2示出了在图1A至图1D所示的实施例中实现的传感器12的示例。传感器12能够被称作电容式压力换能器。半导体本体11包括半导体衬底40。传感器12在半导体衬底40的顶部实现。实现了CMOS顶部的一个或多个压力敏感膜的集成。半导体本体11可以是CMOS半导体本体。传感器12包括顶部电极41和底部电极42。顶部电极41可以实现为顶部金属电极。底部电极42可以实现为底部金属电极。传感器12包括膜43。膜43包括顶部电极41。此外，膜43包括介电层44。介电层44可以布置在顶部电极41的顶部。介电层44可以被制造为钝化密封层。

[0064] 传感器12包括腔45。腔45在顶部电极41与底部电极42之间。顶部电极41在腔45与介电层44之间。传感器12可以包括另一介电层46。所述另一介电层46可以实现为蚀刻停止层。另一介电层46布置在底部电极42与腔45之间。通过蚀刻牺牲层(图2中未示出)来制造腔45。

[0065] 半导体本体11包括金属化叠层50。金属化叠层50包括第一介电层51和第一金属化层52。金属化叠层50可以包括图2中未示出的另外的金属化层和另外的介电层。第一金属化层52的一部分56通过过孔53连接至底部电极42。顶部电极41也通过第一过孔54连接至金属层55。金属层55通过第二过孔57连接至金属化层52的另一部分58。

[0066] 半导体本体11包括传感器12和集成电路。装置10可以实现为设备。集成电路由半导体衬底40和金属化叠层50实现。金属化层52的部分56、58连接至集成电路。集成电路包括图1A至图1D和图3A至图3H中所示的电路，例如转换器13、开关电路15、发生器32、数字电路20和存储器21。集成电路实现为互补金属氧化物半导体电路，简称为CMOS电路。半导体本体11包括例如用于提供数字化压力信号SP的接合焊盘59。集成电路可以被设计为ASIC。半导体本体11被实现为管芯。装置10集成在一个管芯上。装置10集成在CMOS管芯的顶部上。

[0067] 通过顶部电极41中的孔蚀刻未示出的牺牲层。在去除牺牲层之后，孔被介电层44封闭。腔45的边界在顶部由顶部电极41和填充顶部电极41的孔的介电层44限定、在底部由另一介电层46限定以及在侧面由过孔54限定。膜43的厚度等于顶部电极41的厚度和在顶部电极41的顶部上的介电层44的厚度的和。膜43的区域由过孔54限定。过孔54围绕腔45。另一传感器30可以如传感器12一样地实现。

[0068] 传感器装置10实现电容相对于DC电压偏置的方法。如果在底部电极41与顶部电极42之间施加DC电压偏置或DC偏置电压，则静电力导致膜43向下偏转。电容C随着DC偏置电压(VDC)增加为：

$$C = C_0 + A_0 \cdot V_{DC}^2,$$

[0070] 其中，C是传感器12的电容CA，C0和A0是参数，而VDC是传感器12的顶部电极41与底部电极42之间的电压值。如果C-V曲线的底部以零伏为中心，则所述公式可以是有效的。顶部电极41可以是传感器12的第一电极60，并且底部电极42可以是传感器12的第二电极61，反之亦然。取决于开关电路15的状态，电压VDC可以等于参考电压VREF。

[0071] 参数A0取决于膜硬度。膜硬度的相对变化等于参数A0的相对变化。参数A0也取决于大气压力P。因此，在晶圆级和/或最终测试期间确定参数A0。当在晶圆级电子分选(e-sort)期间执行时，不合规的设备能够与将组装在最终封装中的设备分离。在压力校准期间的最终测试中，在各种压力和温度点下确定参数A0，以便提取压力-A0和/或温度-A0的相依关系。稍后，当在终端应用中，即在用户PCB上组装所述设备时，压力-A0和/或温度-A0行为

的变化能够用于校正机械或热引起的应力变化。在寿命期间,例如由于除气、材料如胶的老化以及或者应力变化引起的潜在传感器输出偏移将导致参数A0对大气压力P的相依关系的附加偏移。

[0072] 通过物理模型或者通过加速寿命测试来找出参数A0的变化与传感器输出之间的相关性。通过知道此相关性,ASIC能够通过测量参数A0的变化来补偿传感器输出偏移。

[0073] 传感器装置10可以被实现为例如用于以下中的至少之一:

[0074] -使用两个相同的电容传感器12、30来直接生成差分信号。

[0075] -在各种参考电压VREF处测量电容CA的可能性。

[0076] -混合选择电容传感器以检测不匹配。

[0077] 传感器装置10的示例可以实现单端电容到数字变换器设计(参见图3A)。压力换能器包括单个电容式压力传感器膜元件。

[0078] 装置10的优点可以是例如以下中的至少之一:

[0079] -由于使用两个膜而使得的2倍灵敏度提高。

[0080] -电容范围的线性度显著提高:

[0081] 与转换器的单端设计的非线性度相比,转换器13的差分设计的非线性度可以例如低十倍到三十倍。

[0082] -由于差分设计引起的共模抑制:

[0083] 提高了对抗EMC干扰(EMC代表电磁兼容性)的鲁棒性。

[0084] -CMOS上的膜集成:没有由于没有引线接合而产生的寄生效应。

[0085] -较小的膜电容/范围降低了总电容噪声,从而提高了压力分辨率。

[0086] -嵌入的电容到电压特性使得能够补偿应力变化和腔压力变化。

[0087] 传感器装置10被配置成将表面微机械的电容式压力传感器12集成在CMOS读出电路的顶部上。CMOS读出电路包括电容至数字变换器。与常规的压阻读出传感器相比,具有电容读出的压力传感器12的主要优点是超低功耗和高很多的灵敏度。此外,当在集成读出电路的顶部上直接构造压力敏感膜43时(单个管芯解决方案),能够实现形状因素的显著改进。此方法使得能够减小寄生电容,并且因此将受益于比独立电容式压力传感器管芯好的信噪比。此外,从形状因素和封装的观点来看,在CMOS的顶部上构造压力敏感膜而不是使用需要电连接即引线接合至读出电路的单个压力换能器元件是有利的。

[0088] 电容式压力传感器12直接构造在CMOS电路例如CMOS读出电路的最终钝化层51的顶部上。压力传感器技术将利用公共的线路后端(BEOL)层来布线和屏蔽板或屏蔽电极48(在图5B中示出)。设备12包括被腔45和隔离/蚀刻停止层46彼此分开的底部电极板42和顶部电极板41。可移动膜43在从外部施加的压力P下偏转。压力P的变化与金属电极板41、42之间的电容C的变化直接相关。金属电极板41、42之一,即顶部电极41,集成在压力敏感膜43中,并且可以有利地由Ti/TiN/W构成。底部电极板42是固定的。

[0089] 为了生成覆盖腔45的自由悬挂膜43,在底部电极42和蚀刻停止层46上沉积牺牲层。将通过使用干式蚀刻方法在膜43中蚀刻的小孔除去牺牲层以避免粘附。在牺牲蚀刻之后,形成悬置的、穿孔的膜43,所述膜随后用SiN介电薄膜44密封。图2中示出了电容式压力传感器的示意性横截面。

[0090] 在实施例中,如图2所示,底部电极42是分段的。底部电极42包括中心部分49a和围

绕中心部分49a的外环49b。底部电极42能够连接至转换器13(例如,经由开关电路15),以测量底部电极42的中心部分49a与顶部电极41之间的电容,或者底部电极42的外环49b与顶部电极41之间的电容。与顶部电极41被底部电极42的外环49b静电激励的情况相比,由于底部电极42的中心部分49a与顶部电极41之间的较小间隔,静电吸引将显著增加。

[0091] 在可替代的实施例中,传感器12和另一传感器30可以不同。例如,传感器12的膜43的区域可以不同于另一传感器30的膜的区域。形成传感器12的膜43的层41、44可以等于形成另一传感器30的膜43'的层41'、44'。

[0092] 在未示出的可替代实施例中,半导体本体11包括传感器12和集成电路。集成电路包括图1A至图1D和图3A至图3H中所示的电路的子集,例如转换器13以及可选地还包括开关电路15。另外的半导体本体包括例如发生器32、数字电路20和存储器21。

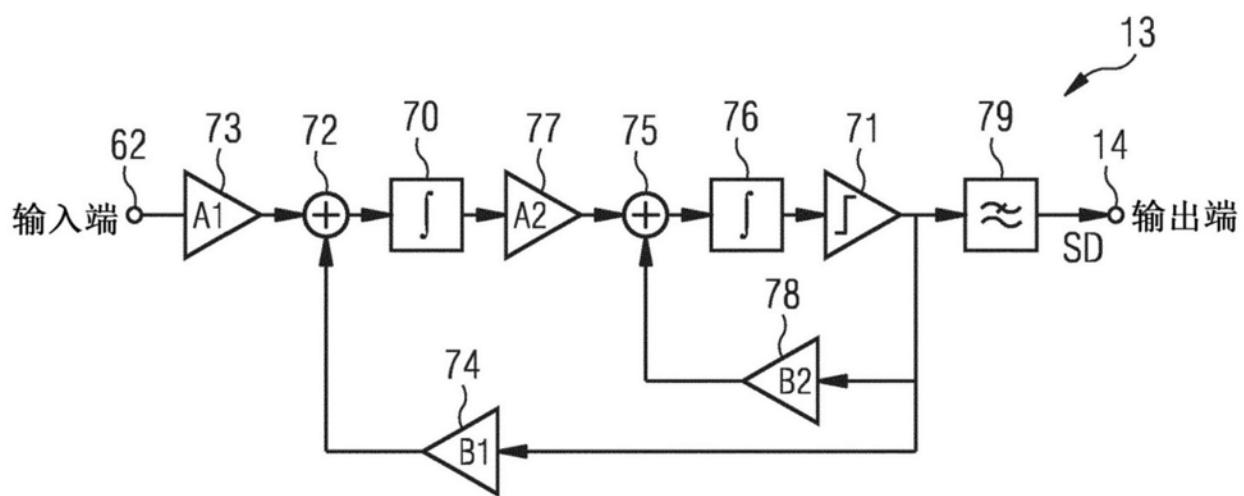

[0093] 图3A示出了作为上述实施例的进一步发展的装置10的电容至数字转换器13的示例。转换器13被实现为delta-sigma模拟至数字转换器。转换器13也可以称为sigma-delta转换器或delta-sigma转换器。在图3A中,示出了电路结构的概况,即,装置10的二阶sigma-delta调制器加上滤波器79的高级模型。转换器13包括第一积分器70、量化器71和第一加法器72。转换器13的第一输入端62耦接至第一加法器72的输入端。第一加法器72的输出端耦接至第一积分器70的输入端。第一积分器70的输出端耦接至量化器71的输入端。量化器71的输出端耦接至转换器13的输出端14。此外,量化器71的输出端耦接至第一加法器72的另一输入端。

[0094] 转换器13的第一缓冲器73可以将转换器13的第一输入端62耦接至第一加法器72的输入端。第一缓冲器73具有放大因子A1。第二缓冲器74将量化器71的输出端耦接至第一加法器72的另一输入端。第二缓冲器74具有放大因子B1。此外,转换器13包括第二加法器75,所述第二加法器具有耦接至第一积分器70的输出端的输入端。量化器71的输出端耦接至第二加法器75的另一输入端。转换器13包括第二积分器76,所述第二积分器将第二加法器75的输出端耦接至量化器71的输入端。第三缓冲器77将第一积分器70的输出端耦接至第二加法器75的输入端。第三缓冲器77具有放大因子A2。第四缓冲器78将量化器71的输出端耦接至第二加法器75的另一输入端。第四缓冲器78具有放大因子B2。量化器71可以实现为比较器(其是1比特量化器)。

[0095] 另外,转换器13包括滤波器79。滤波器79的输出端连接至转换器13的输出端14。量化器71的输出端连接至滤波器79的输入端。滤波器79实现为低通滤波器。滤波器79是数字滤波器。因此,转换器13被实现为两级转换器。

[0096] 在可替代的实施例中,转换器13被实现为一级转换器或者包括多于两级。

[0097] 在图3A所示的示例中,转换器13仅包括一个输入端,即第一输入端62。然而,转换器13可以被实现为附加地包括第二输入端63的差分转换器。因此,转换器13执行诸如在以下附图中所示的差分信号处理。

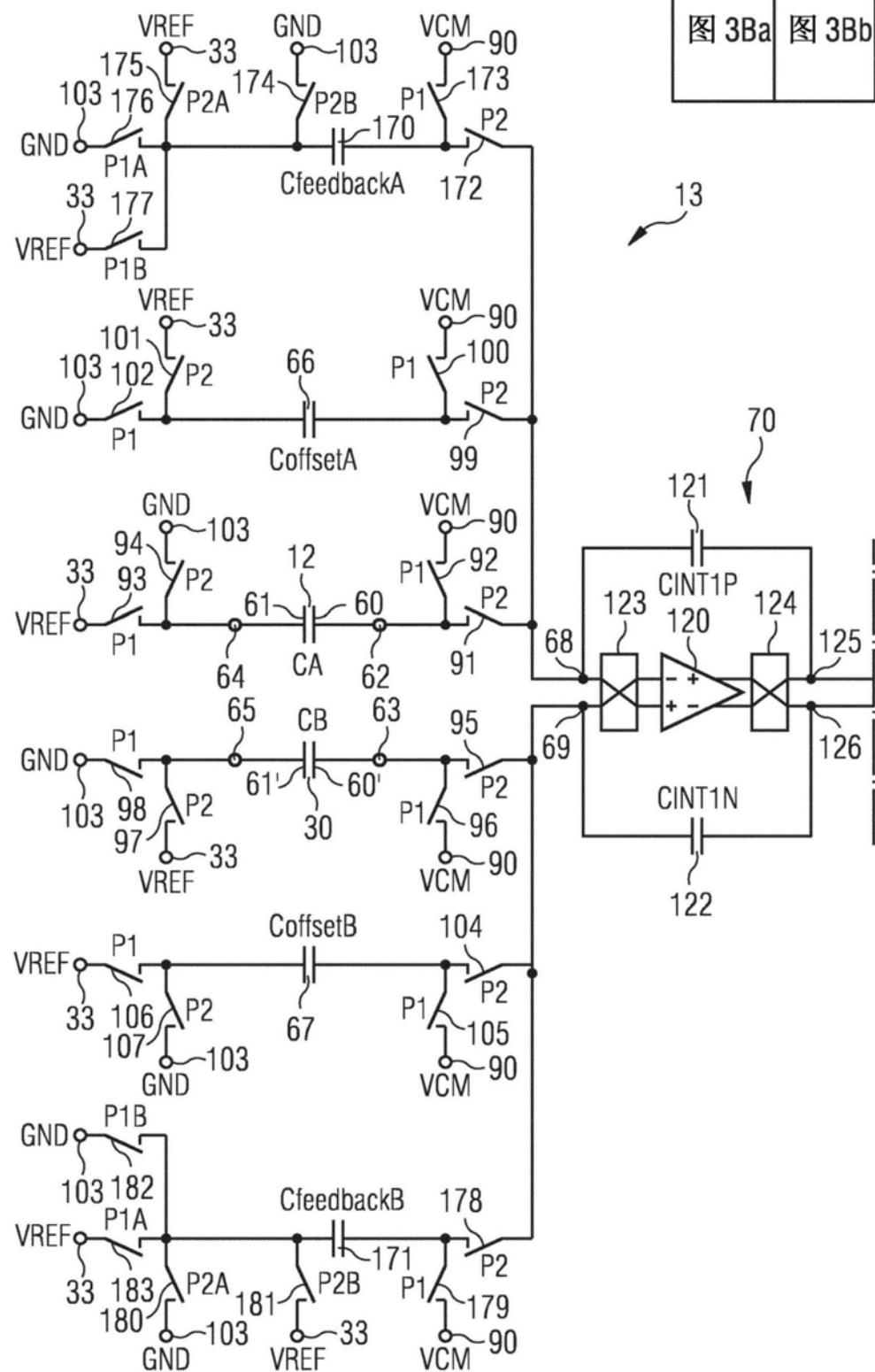

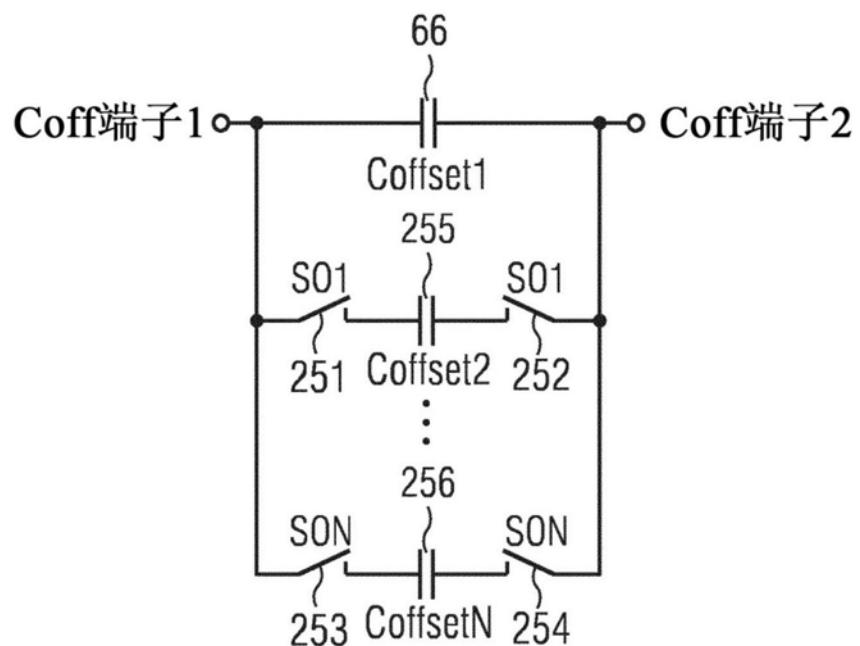

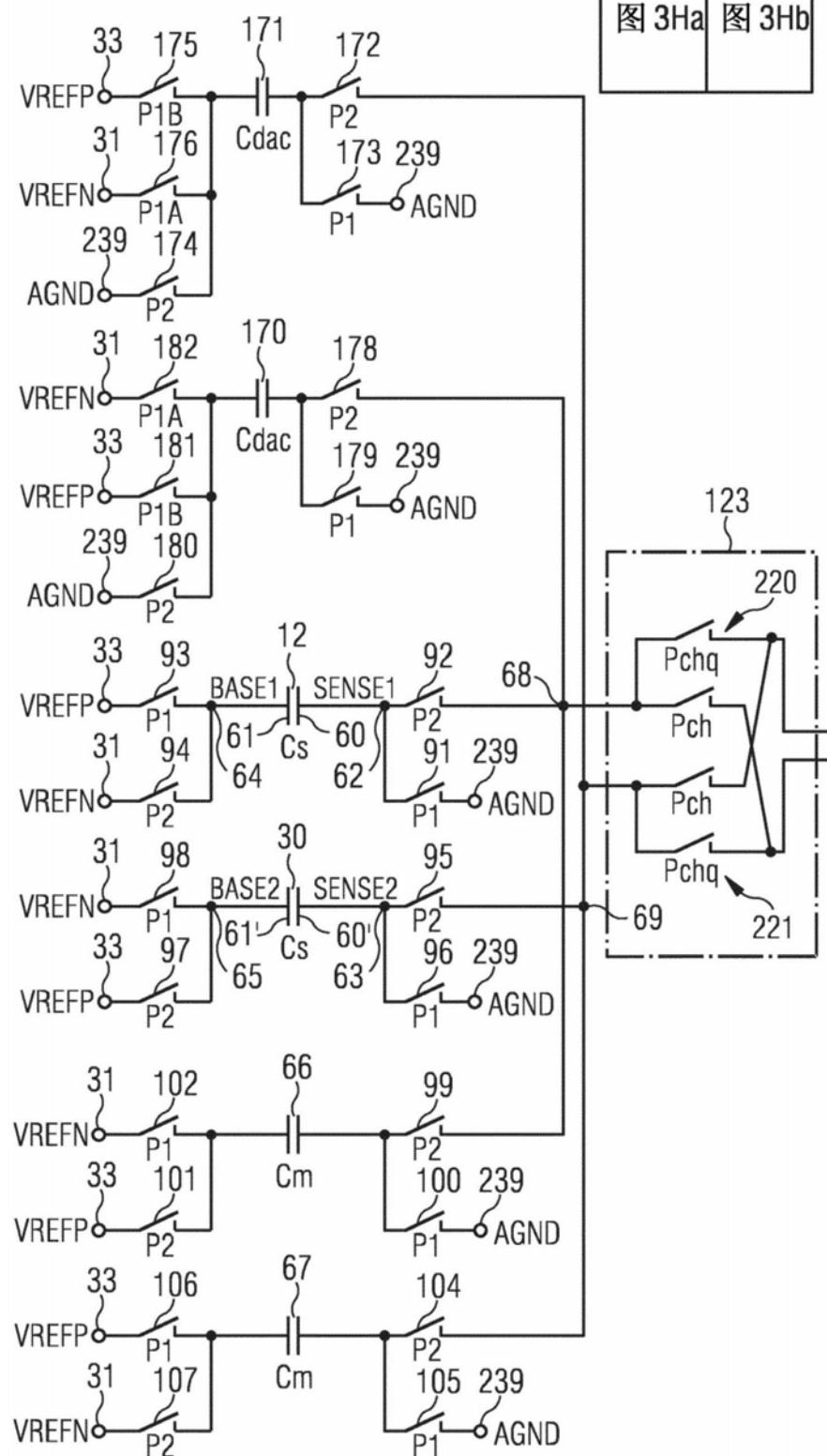

[0098] 图3B示出了具有转换器13的装置10的另一示例,其是图1A至图1D和图3A中所示的实施例的进一步发展。装置10包括具有电容值CA的传感器12和具有电容值CB的另一传感器30。此外,转换器13包括第一偏移电容器66和第二偏移电容器67。第一偏移电容器66具有电容值CoffsetA,并且第二偏移电容器67具有电容值CoffsetB。装置10可以没有开关电路15。装置10在转换器13与传感器12之间可以没有任何开关,并且在转换器13与另一传感器30之

间没有任何开关。因此,传感器12的第一电极60和第二电极61直接并永久地连接至转换器13的第一输入端62和第三输入端64。另一传感器30的第一电极60'和第二电极61'直接并永久地连接至转换器13的第二输入端63和第四输入端65。

[0099] 转换器13包括第一开关91至第四开关94。转换器13的第一输入端62经由第一开关91耦接至第一积分器70的第一输入端68。第二开关92将转换器13的第一输入端62耦接至共模端子90。第三开关93将转换器13的第三输入端64耦接至发生器32的输出端33。第四开关94将转换器13的第三输入端64耦接至参考电位端子103。

[0100] 另外,转换器13包括第五开关95至第八开关98。转换器13的第二输入端63经由第五开关95耦接至第一积分器70的第二输入端69。第六开关96将转换器13的第二输入端63耦接至共模端子90。第七开关97将转换器13的第四输入端65耦接至发生器32的输出端33。第八开关98将转换器13的第四输入端65耦接至参考电位端子103。

[0101] 此外,转换器13包括第九开关至第十六开关99至102、104至107。第一偏移电容器66的第一电极经由第九开关99耦接至第一积分器70的第一输入端68,并且经由第十开关100耦接至共模端子90。第一偏移电容器66的第二电极经由第十一开关101耦接至发生器32的输出端33,并且经由第十二开关102耦接至参考电位端子103。

[0102] 第二偏移电容器67的第一电极经由第十三开关104耦接至第一积分器70的第二输入端69,并且经由第十四开关105耦接至共模端子90。第二偏移电容器67的第二电极经由第十五开关106耦接至发生器32的输出端33,并且经由第十六开关107耦接至参考电位端子103。

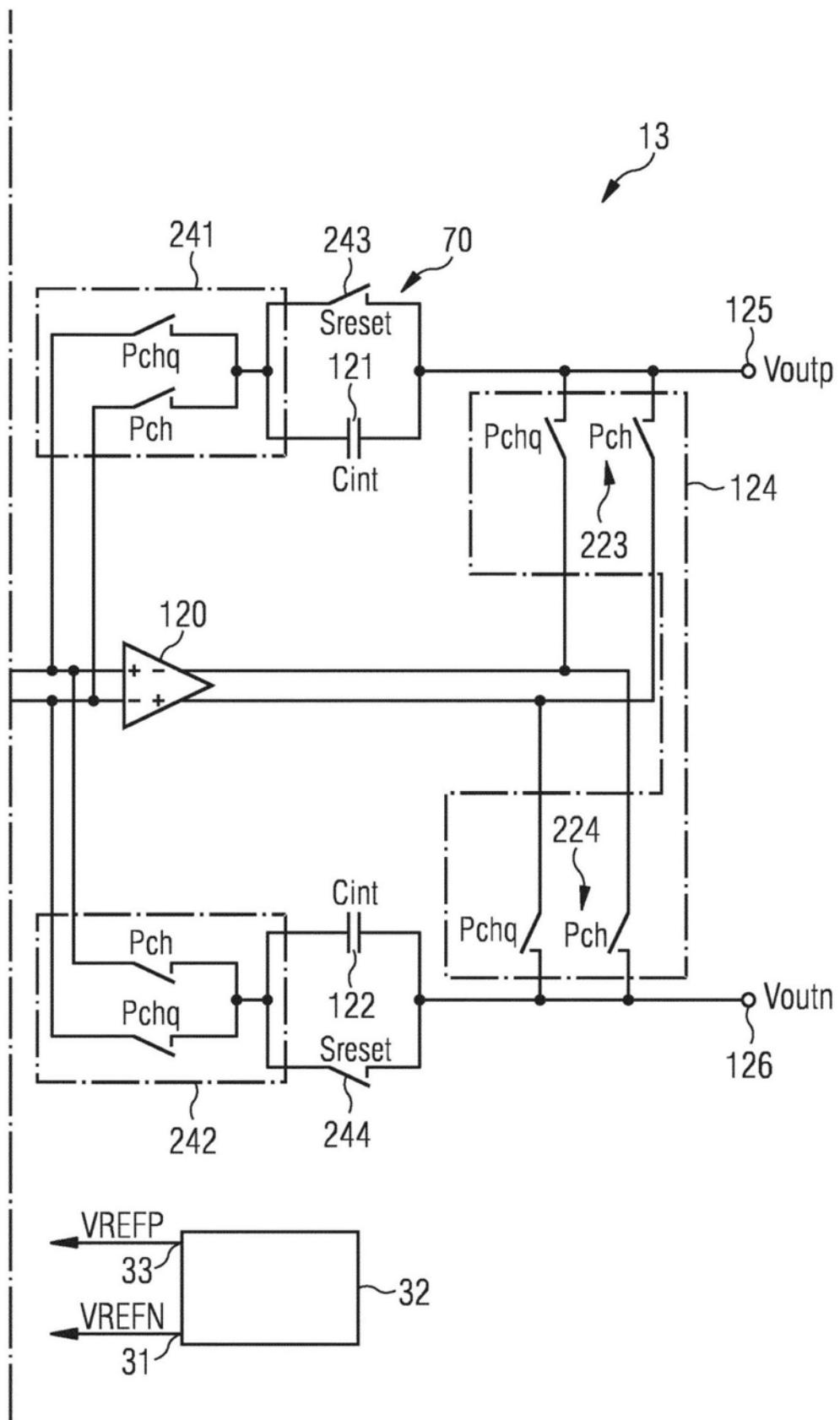

[0103] 第一积分器70实现为差分积分器。第一积分器70包括放大器120以及第一积分电容器121和第二积分电容器122。第一积分电容器121和第二积分电容器122将放大器120的输入侧耦接至放大器120的输出侧。此外,第一积分器70包括第一斩波电路123和第二斩波电路124。第一积分器70的第一输入端68经由第一斩波电路123耦接至放大器120的第一输入端和第二输入端。相应地,第一积分器70的第二输入端69经由第一斩波电路123耦接至放大器120的第一输入端和第二输入端。第一输入端可以是放大器120的反相输入端,第二输入端可以是放大器的非反相输入端。

[0104] 放大器120的第一输出端和第二输出端经由第二斩波电路124耦接至第一积分器70的第一输出端125。另外,放大器120的第一输出端和第二输出端经由第二斩波电路124耦接至第一积分器70的第二输出端126。放大器120的第一输出端可以是放大器120的非反相输出端,并且放大器120的第二输出端可以是放大器120的反相输出端。

[0105] 第一积分电容器121耦接在第一积分器70的第一输入端68与第一积分器70的第一输出端125之间。相应地,第二积分电容器122耦接在第一积分器70的第二输入端69与第一积分器70的第二输出端126之间。第一积分电容器121和第二积分电容器122具有电容值CINT1P、CINT1N。

[0106] 第二积分器76被实现为差分积分器。第二积分器76在其输入侧耦接至第一积分器70的第一输出端125和第二输出端126。转换器13包括将第一积分器70的输出侧耦接至第二积分器76的输入侧的采样级129。采样级120可以实现第三缓冲器77(如图3A所示)。量化器71在其输入侧耦接至第二积分器76的输出侧。量化器71的阈值可以在量化器71内部产生。

[0107] 此外,转换器13包括触发器130,所述触发器具有连接至量化器71的输出端的输入

端。触发器130的输入端实现为D输入端。触发器130的输出端耦接至转换器13的输出端14。触发器130的输出端实现为Q输出端。触发器130包括时钟输入端。滤波器79(图3A中所示)可以将触发器130的输出端耦接至转换器13的输出端14。

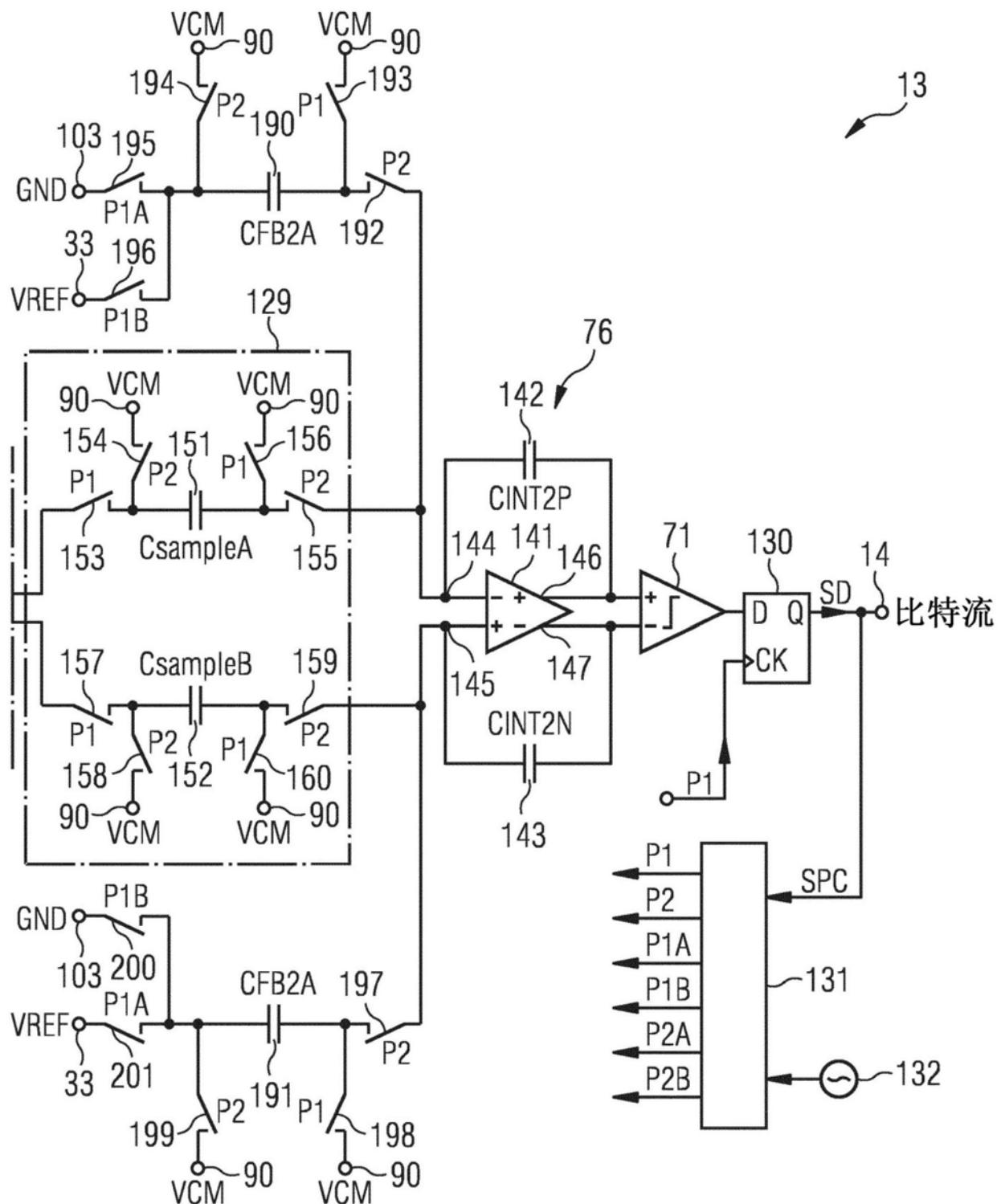

[0108] 第二积分器76包括另一放大器141以及第三积分电容器142和第四积分电容器143。第三积分电容器142和第四积分电容器143具有电容值CINT2P、CINT2N。第一积分电容器142将另一放大器141的第一输入端144耦接至另一放大器141的第一输出端146。第四积分电容器143将放大器141的第二输入端145耦接至另一放大器141的第二输出端147。第一输入端144可以被实现为放大器141的反相输入端,而第二输入端145可以被实现为放大器的非反相输入端。可以将另一放大器141的第一输出端146实现为非反相输出端,并且可以将另一放大器141的第二输出端147实现为反相输出端。另一放大器141的第一输出端146和第二输出端147形成第二积分器76的第一输出端和第二输出端,并且耦接至量化器71的第一输入端和第二输入端。

[0109] 采样级129包括第一采样电容器151和第二采样电容器152(其可以具有例如电容CsampleA、CsampleB)。此外,采样级129包括第一采样开关153至第八采样开关160。第一采样电容器151的第一电极经由第一采样开关153耦接至第一积分器70的第一输出端125,并且经由第二采样开关154耦接至共模端子90。第一采样电容器151的第二电极经由第三采样开关155和采样级129的第一输出端耦接至另一放大器141的第一输入端144。第一采样电容器151的第二电极经由第四采样开关156耦接至共模端子90。

[0110] 第二采样电容器152的第一电极经由第五采样开关157耦接至第一积分器70的第二输出端126,并且经由第六采样开关158耦接至共模端子90。第二采样电容器152的第二电极经由第七采样开关159和采样级129的第二输出端耦接至另一放大器141的第二输入端145。第二采样电容器152的第二电极经由第八采样开关160耦接至共模端子90。

[0111] 此外,转换器包括第一反馈电容器170和第二反馈电容器171(其可以具有例如电容CfeedbackA、CfeedbackB)以及第一反馈开关172至第十二反馈开关183。第一反馈电容器170的第一电极经由第一反馈开关172耦接至第一积分器70的第一输入端68,并且经由第二反馈开关173耦接至共模端子90。第一反馈电容器170的第二电极经由第三反馈开关174耦接至参考电位端子103、经由第四反馈开关175耦接至发生器32的输出端33、经由第五反馈开关176耦接至参考电位端子103并且经由第六反馈开关177耦接至发生器32的输出端33。

[0112] 另外,第二反馈电容器171的第一电极经由第七反馈开关178耦接至第一积分器70的第二输入端69,并且经由第八反馈开关179耦接至共模端子90。第二反馈电容器171的第二电极经由第九反馈开关180耦接至参考电位端子103、经由第十反馈开关181耦接至发生器32的输出端33、经由第十一反馈开关182耦接至参考电位端子103并且经由第十二反馈开关183耦接至发生器32的输出端33。

[0113] 此外,转换器13包括第三反馈电容器190和第四反馈电容器191(二者均可以具有电容CFB2A)和另外的反馈开关192至201。第三反馈电容器190的第一电极经由第一反馈开关192耦接至第二积分器76的第一输入端144,并且经由第二反馈开关193耦接至共模端子90。第三反馈电容器190的第二电极经由第三反馈开关194耦接至共模端子90,经由第四反馈开关195耦接至参考电位端子103,并且经由第五反馈开关196耦接至发生器32的输出端33。

[0114] 第四反馈电容器191的第一电极经由另一第六反馈开关197耦接至第二积分器76的第二输入端145，并且经由另一第七反馈开关198耦接至共模端子90。第四反馈电容器191的第二电极经由另一第八反馈开关199耦接至共模端子90、经由另一第九反馈开关200耦接至参考电位端子103并且经由另一第十反馈开关201耦接至发生器32的输出端33。

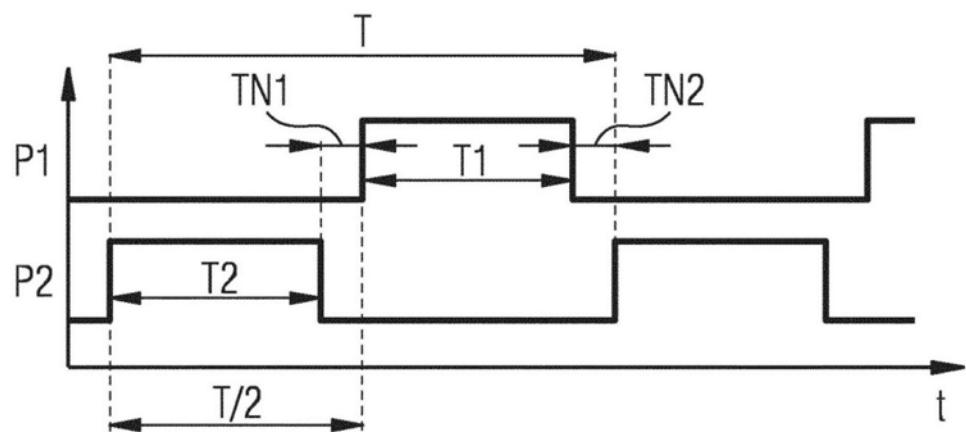

[0115] 在共模端子90处，提供共模电压VCM。如图3B所示，转换器13的开关由第一相位信号P1、第二相位信号P2、另一第一相位信号P1A、附加第一相位信号P1B、另一第二相位信号P2A和附加第二相位信号P2B控制。第一相位信号P1也施加至触发器130的时钟输入端。相位发生器131产生相位信号P1、P2、P1A、P1B、P2A、P2B。在图3B和其他图中，在开关的控制输入端处指示控制信号。相位发生器131的输入端接收相位控制信号SPC，并且可以连接至量化器71的输出端、触发器130的输出端和/或数字电路20。时钟电路132可以连接至相位发生器131。

[0116] 传感器装置10可以包括这些电路块中的至少之一：

[0117] -两个压力敏感膜12、30。

[0118] -附加的成对的压力敏感膜或压力不敏感膜。

[0119] -一定数量对的固定电容器66、67、142、143、151、152、170、171、121、122、142、143、190、191。

[0120] -sigma-delta调制器13。

[0121] -数字低通滤波器79。

[0122] -可编程电压发生器32。

[0123] -相位发生器131。

[0124] 此电路的目的是将电容值CA转换成数字数SP。sigma-delta调制器13以全差分方式工作；正支路上的电压变化对应于负支路上的相反符号的变化；操作相对于共模电压VCM是对称的。相位发生器131以相同频率产生两个非交叠相位P1、P2。Σ Δ 调制器输入端由对压力P敏感的两个相同的电容器12、30驱动，这两个电容器在没有公共电压信号的情况下直接产生差分电压。如果两个传感器12、30之间存在不匹配，则能够产生共模信号；在这种情况下，差分结构拒绝任何共模信号。

[0125] 图3B中的作为二阶sigma-delta模拟至数字转换器13（模拟到数字转换器缩写为ADC）的电路实现了图3A的高级等效物中所指示的功能。由于输入电容总是正的并且ADC的输入范围是双极性的，因此可能需要将电容移位固定量，以便使ADC范围适应传感器范围。这是通过使用第一偏移电容器66和第二偏移电容器67的偏移支路来完成的，所述偏移支路注入具有相对于主输入电容器12、30的符号相反符号的电荷；因此，要转换的表观电容是CA-Coffset或CA-CoffsetA。如例如图3F所示，通过添加并联的附加电容器，Coffset本身是可控制的；这使得能够进一步使CDC 13的输入范围适应感测电容器值。优点在于，由于减去了偏移电容，因此能够减小噪声系数，因为此电容不再对噪声有贡献。

[0126] 以主时钟频率对比较器输出进行采样，并且其采样值通过对相位信号P1A/P2A或相位信号P1B/P2B使能来确定由使用反馈电容器170、171、190、191的反馈分支注入的电荷的符号。以使整个环路稳定的方式选择符号。

[0127] 在操作时，输入电容器12、30在一个相位期间被充电至参考电压VREF，并且在下一个相位期间被放电，使得跨它们的端子产生大于零的平均电压。然后，可编程发生器32能够

用于测量电容相对于电压的变化 (C相对于V), 这给出了关于压力敏感膜43的各种参数的信息。

[0128] 在图3B中未示出但在图1B、图1C和图3E中示出的可替代实施例中, 装置10包括开关电路15。在CDC块13前面添加mux 15给出了测量附加的传感器对或固定电容器对例如电容器36至39的可能性。固定的电容器(简称为固定电容器)能够用于测试CDC 13。mux 15中的交叉连接开关使得所测量的电容器的不同组合, 例如传感器1+固定电容器以及传感器2+固定电容器(例如传感器12和第三电容器36, 然后是另一传感器30和第三电容器36)。由于固定电容器完全相同, 因此以上两个测量结果之间的比较结果能够给出关于传感器1与传感器2(即传感器12与另一传感器30)之间的不匹配的信息。

[0129] sigma-delta调制器的其他拓扑结构也是可能的, 例如更高阶的, 具有在第二级或级联之后的附加的级, 具有附接至初级回路的附加的回路。

[0130] 电容至数字转换器13基于三阶delta-sigma差分ADC, 可选地通过模拟开关矩阵15连接至压力膜12、30。对于特定的膜大小, C2D 13的偏移和电容范围需要与压力范围上的电容变化相匹配。偏移电容器coff或CoffsetA或CoffsetB被调谐至预期范围的中间(例如, 对于此处使用的示例为1.6pF)。参考电容器被选择成使得压力传感器12的所需电容范围能够被完全覆盖以包括处理范围。可以说参考电容器的大小是期望动态范围的一半。一系列参考电容器例如从0.5pF到2.4pF, 能够与1.0pF+0.1/…/2.2pF的偏移电容器组合, 以覆盖膜的所有可能的电容范围。

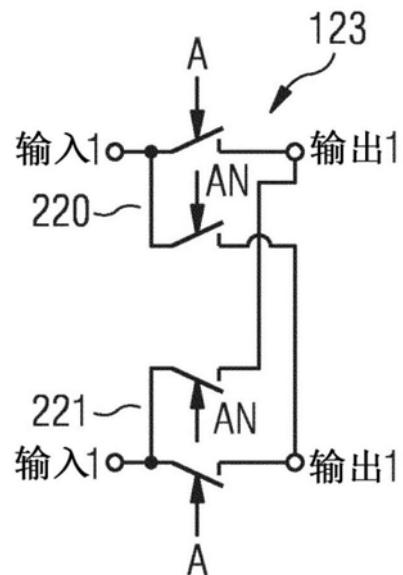

[0131] 图3C示出了图3B或图3H中所示的转换器13的细节, 即opam斩波开关。在图3C中, 示出第一斩波电路123和第二斩波电路124的示例。第一斩波电路123包括第一切换开关220和第二切换开关221。第一切换开关220将第一斩波电路123的第一输入端耦接至第一斩波电路123的第一输出端和第二输出端。相应地, 第二切换开关222将第一斩波电路123的第二输出端耦接至斩波电路123的第一输出端和第二输出端。第一切换开关220和第二切换开关221由第一斩波器信号A和第二斩波器信号AN控制。第二斩波器信号AN可以是相对于第一斩波器信号A的反相信号。

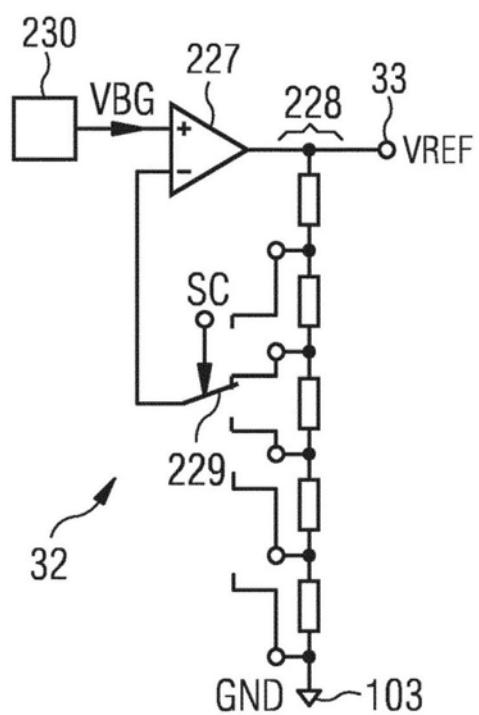

[0132] 图3D示出了作为参考电压发生器的上述示例的进一步发展的参考电压发生器32的示例。发生器32包括放大器227, 所述放大器具有连接至发生器32的输出端33的输出端。此外, 发生器32包括将发生器32的输出端33耦接至参考电位端子103的电阻分压器228。电阻分压器228可以包括至少两个电阻器。在图3D所示的示例中, 电阻器的数量为五。此外, 发生器33包括切换开关229, 所述切换开关具有连接至电阻分压器228的电阻器之间的节点的输入端。放大器227包括第一输入端和第二输入端。放大器227的第一输入端可以是非反相输入端, 并且放大器227的第二输入端可以是反相输入端。切换开关229的输出端连接至放大器227的第二输入端。带隙电压V<sub>BG</sub>被提供给放大器227的第一输入端。

[0133] 装置10可以包括具有连接至放大器227的第一输入端的输出端的带隙电压参考发生器230。带隙电压参考发生器230产生带隙电压V<sub>BG</sub>。控制信号SC控制切换开关229。有利地, 发生器32根据控制信号SC在输出端33处提供参考电压V<sub>REF</sub>的不同值。参考电压V<sub>REF</sub>的不同值具有不同的量并且相对于参考电位GND具有相同的符号。

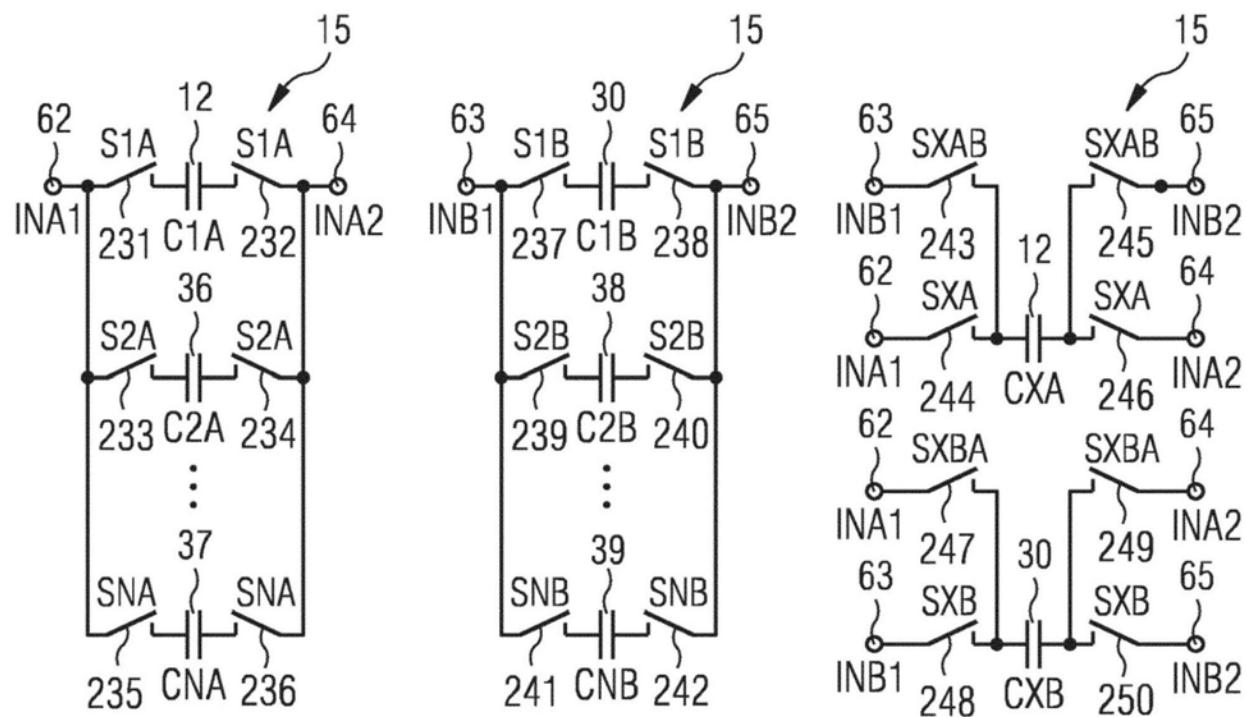

[0134] 图3E示出了作为上述实施例的进一步发展的装置10的进一步细节, 即CDC输入mux。装置10包括能够并联耦接至传感器12(具有电容值C1A)的第一电容器34和第三电容器

36(具有电容值C2A、CNA)。由开关电路15提供传感器12与第一电容器34和第三电容器36的耦接,所述开关电路包括由信号S1A、S2A、SNA控制的开关231至236。如点所示,可以存在与传感器12并联连接的另外的电容器。相应地,装置10可以包括并联耦接至另一传感器30(具有电容值C1B)的第二电容器35和第四电容器37(具有电容值C2B、CNB)。通过开关电路15来实现所述耦接,所述开关电路包括由信号S1B、S2B、SNB控制的开关237至242。如点所示,可以存在与另一传感器30并联连接的另一电容器。

[0135] 在如图3E的右部所示的一个示例中,可以用开关243至250来互换传感器12(具有电容值CXA)和另一传感器30(具有电容值CXB)的位置。因此,通过开关电路15,传感器12可以在第一操作阶段中连接至转换器13的第一输入端62,并且在第二操作阶段中连接至转换器13的第二输入端63。相应地,通过开关电路15,另一传感器30在第一操作阶段中连接至转换器13的第二输入端63,并且在第二操作阶段中连接至转换器13的第一输入端62。为了获得传感器12、30、偏移电容器66、67、参考电容器和其他电容器的不同值,使用并联操作,但是相同的装置作为开关工作:它可以单独地连接不同的传感器电容器12、30(在不同的测量期间)。

[0136] 图3F示出了转换器13的细节的另一示例,即可变偏移电容的实现。一个或两个电容器255、256使用开关251至254以并联电路耦接至第一偏移电容器66(具有电容值Coffset1)。因此,另一电容器255(具有电容值Coffset2)可以通过两个开关251、252并联耦接至第一偏移电容器66。附加电容器256(具有电容值CoffsetN)可以通过另外的开关253、254并联耦接至第一偏移电容器66。因此,根据开关251至254的状态,由第一偏移电容器66、另一电容器255和附加电容器256的并联电路形成第一偏移电容。开关251、252由信号S01控制,并且另外的开关253、254由信号S0N控制。类似于图3F所示,第二偏移电容器67可以耦接至另外的电容器。转换器13包括开关251至254。

[0137] 图3G示出了上述装置10的第一相位信号P1和第二相位信号P2的示例。第一相位信号P1和第二相位信号P2具有脉冲形式。第一相位信号P1和第二相位信号P2被循环重复。第一相位信号P1的脉冲在第二相位信号P2的两个脉冲之间(且反之亦然,除了第一脉冲之外)。第一相位信号P1的脉冲具有第一持续时间T1,并且第二相位信号P2的脉冲具有第二持续时间T2。具有持续时间TN1的第一非交叠时间在第二相位信号P2的脉冲与随后的第一相位信号P1的脉冲之间。具有持续时间TN2的第二非交叠时间在第一相位信号P1的脉冲与随后的第二相位信号P2的脉冲之间。非交叠相位提高了电容到数字转换的性能。因此,能够根据以下等式计算循环时间T:

$$T = T2 + TN1 + T1 + TN2$$

[0139] 在第一相位信号P1的脉冲期间,参考电压VREF被施加至传感器12的第二电极61,而共模电压VCM被施加至传感器12的第一电极60。因此,在传感器12的第一电极60与第二电极61之间施加电压VREF-VCM。在第二相位信号P2的脉冲期间,参考电压VREF被施加至另一传感器30的第二电极61',另一传感器30的第一电极60'连接至第一积分器70的第二输入端69。

[0140] 根据相位发生器131的输入端处的相位控制信号SPC,另一第一相位信号P1A的脉冲能够与第一相位信号P1的脉冲同时或者被跳过。根据相位控制信号SPC,附加第一相位信号P1B的脉冲能够与第一相位信号P1的脉冲同时或者被跳过。在同一时间,另一第一相位信

号P1A和附加第一相位信号P1B中只有一个具有脉冲。类似地,相位信号P2A、P2B的脉冲与第二相位信号P2的脉冲同时或被跳过。

[0141] 图3H示出了作为上述实施例的进一步发展的装置10的另一示例。在图3H中,示出了具有C2D变换器设计的传感器装置10的示例,所述转换器设计具有四个端子62至65 (SENSE1、BASE1、SENSE2和BASE2)。第一斩波器电路123包括第一切换开关220和第二切换开关221,所述第一切换开关和第二切换开关将第一积分器70的第一输入端68和第二输入端69耦接至放大器120的输入侧。此外,第二斩波器电路124的第三切换开关223将放大器120的第一输出端和第二输出端耦接至第一积分器70的第一输出端125。第二斩波器电路124的第四切换开关224将放大器120的第一输出端和第二输出端耦接至第一积分器70的第二输出端126。第一斩波器电路123和第二斩波器电路124由第一斩波器信号Pch和第二斩波器信号Pchq (其可以等于信号A、AN) 控制。

[0142] 与图3B所示的示例相反,第一积分电容器121和第二积分电容器122耦接在放大器120的输入侧与第一积分器70的输出侧之间。第一积分器70的第一切换开关241将第一积分电容器121的第一电极耦接至放大器120的第一输入端和第二输入端。第一积分器70的第二切换开关242将第二积分电容器122的第一电极耦接至放大器120的第一输入端和第二输入端。第一输入端可以是放大器120的非反相输入端,并且第二输入端可以是所述放大器的反相输入端。第一积分电容器121的第二电极连接至第一积分器70的第一输出端125。第二积分电容器122的第二电极连接至第一积分器70的第二输出端126。

[0143] 第一积分器70的第一重置开关243将第一积分电容器121的第一电极耦接至第二电极。相应地,第一积分器70的第二重置开关244将第二积分电容器122的第一电极耦接至第二电极。第一重置开关243和第二重置开关244由重置信号Sreset控制。

[0144] 装置10包括布置在第三输入端64 (命名为BASE1) 与第一输入端62 (命名为SENSE1) 之间的传感器12,以及布置在第四输入端65 (命名为BASE2) 与第二输入端63 (命名为SENSE2) 之间的另一传感器30。由于传感器12和另一传感器30具有大致相同的电容值,因此在传感器12、30二者处都指示为电容Cs。

[0145] 在附加参考端子239处,分接附加参考电位AGND。附加参考电位AGND可以具有图3B所示的共模电压VCM的值或者参考电位GND的值。传感器12的第二电极61经由第三开关93和第四开关94耦接至正参考电压VREFP及负参考电压VREFN。在参考电压发生器32的另一输出端31处提供负参考电压VREFN。正参考电压VREFP可以具有参考电压VREF的值。如图3B所示,负参考电压VREFN可以具有参考电位GND的值,或者可以具有与诸如参考电压VREF相同的量,但是具有关于参考电位GND的符号相反的符号。另外,另一传感器30的第二电极61'经由第七开关97和第八开关98耦接至正参考电压VREFP和负参考电压VREFN。

[0146] 第一偏移电容器66和第二偏移电容器67可以具有相等的电容值Cm。第一偏移电容器66和第二偏移电容器67的第二电极经由开关101、102、106、107耦接至正参考电压VREFP和负参考电压VREFN。第一反馈电容器170和第二反馈电容器171可以具有相等的电容值Cdac。第一反馈电容器170和第二反馈电容器171的第二电极经由开关174至176、180至182耦接至正参考电压VREFP、负参考电压VREFN和附加参考电位AGND。

[0147] 第一积分器70的第一输出端125和第二输出端126可以直接并永久地连接至量化器71的两个输入端。可替代地,第一积分器70的第一输出端125和第二输出端126可以经由

采样级129和第二积分器76耦接至量化器71的两个输入端。图3H中所示的装置10的操作可以对应于图3A至图3G中所示的装置10的操作。

[0148] 通过引用来并入专利申请US 2015/0295587 A1 (例如,用于说明上述转换器13的示例的细节)。

[0149] 芯片设计可以基于差分四端子电容至数字变换器设计。两个匹配的压力敏感膜43连接至电容至数字变换器(参见图3H)。能够对参考电压或电压VREF、VREFN、VREF进行调谐以便将膜43静电吸引至底部电极42,从而增加电容Cs。C-V行为使得能够确定膜压力灵敏度。

[0150] 下面列出任选的或可能的差异和改进:

[0151] • 差动传感器。

[0152] • 两个膜对比一个膜:使信号动态范围加倍。

[0153] • 提高了CDC 13的线性度(全差分而不是伪差分;与传感器12一起校准非线性)。

[0154] • 共模抑制:提高了对抗EMC干扰的鲁棒性。

[0155] • 较小的传感器电容和C范围:低2倍的噪声。

[0156] • 较高的参考电压VREF(例如,1.2V至1.65V):例如33%的噪声降低。

[0157] • 较高的时钟频率(例如66kHz至132kHz):导致在给定速度下较低的电流和噪声电荷。

[0158] • 没有对传感器防护的寄生。

[0159] • 不需要屏蔽驱动器,使得节省功率。

[0160] • 相关双采样减少了参考和电源噪声的影响。

[0161] • 电容器Cref和Coff(例如,电容器34至39、66、67)是金属-绝缘体-金属电容器,简称MIM电容器。

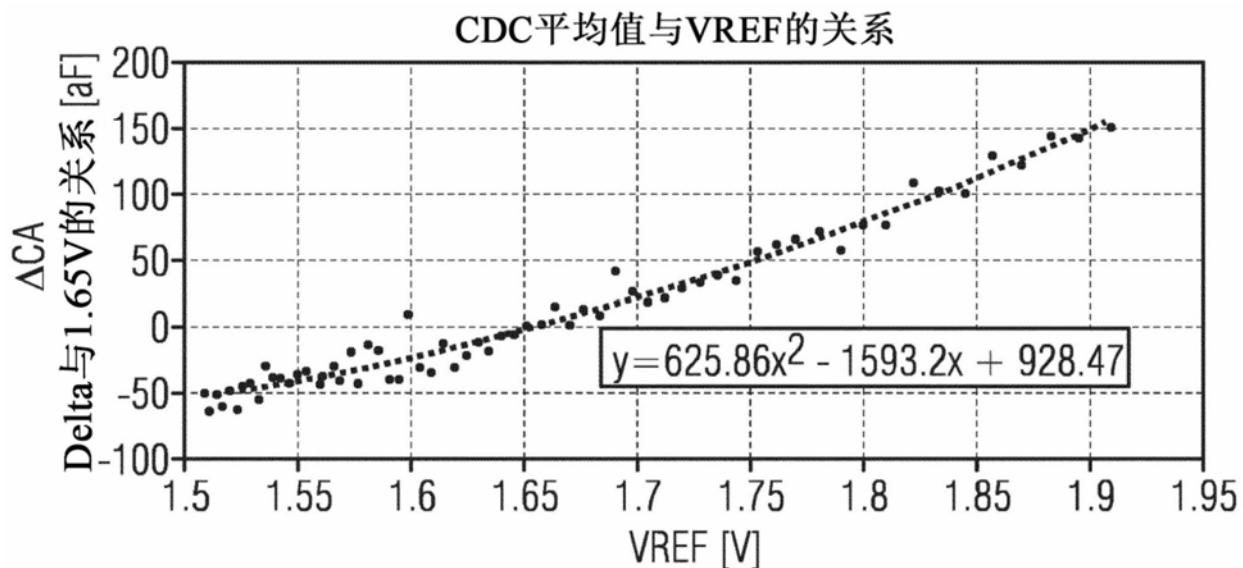

[0162] 图4A至图4F示出了上述实施例之一的装置10的特性的示例。在图4A中,根据参考电压VREF示出传感器12的电容CA。电容CA随着参考电压VREF的值上升而上升。通过上升的参考电压VREF,传感器12的第一电极60与第二电极61之间的吸引力增加,导致电容CA增加。示出了相对于在VREF=1.65V处测量的电容随着参考电压VREF的电容变化。能够清楚地感知特性抛物线电容对电压的行为的影响。C-V数据点的拟合产生作为膜柔性的量度的参数A0。如图4A所示,电容CA取决于参考电压VREF,如下:

[0163]  $CA = C0 + B0 \cdot VREF + A0 \cdot VREF^2$ 。

[0164] C0、B0、A0是参数。如果要确定参数B0,则需要第三点来拟合曲线。可替代地,也能够使用以下等式来执行C-V数据点的拟合:

[0165]  $CA = C0 + A0 \cdot VREF^2$ 。

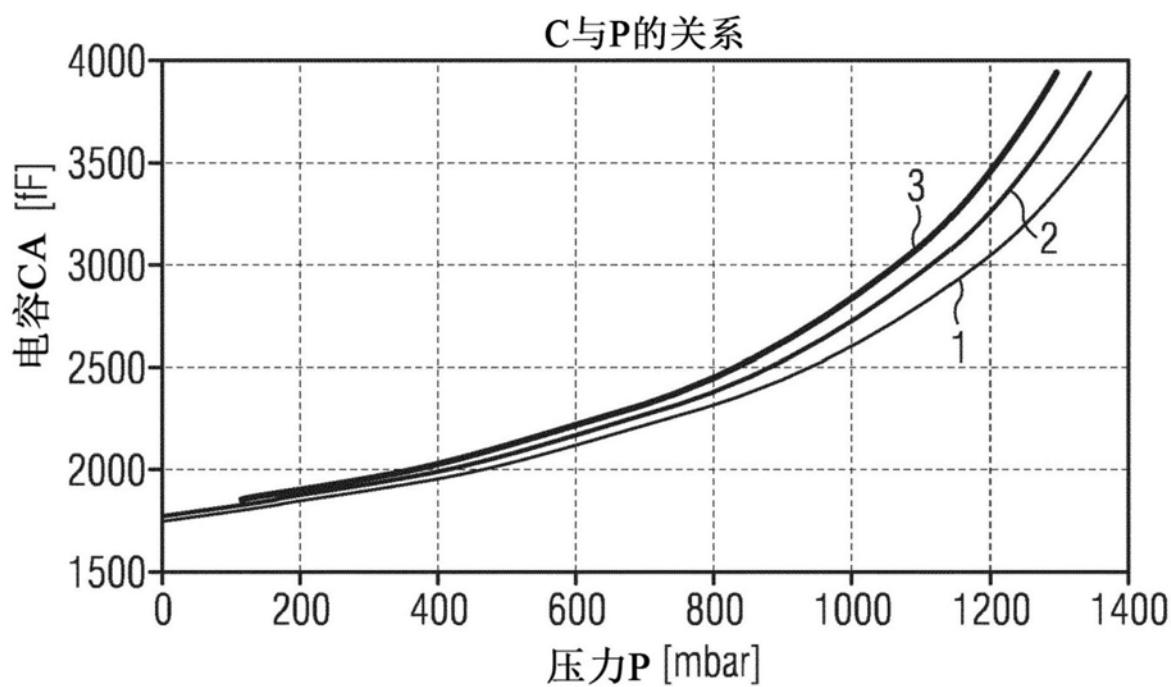

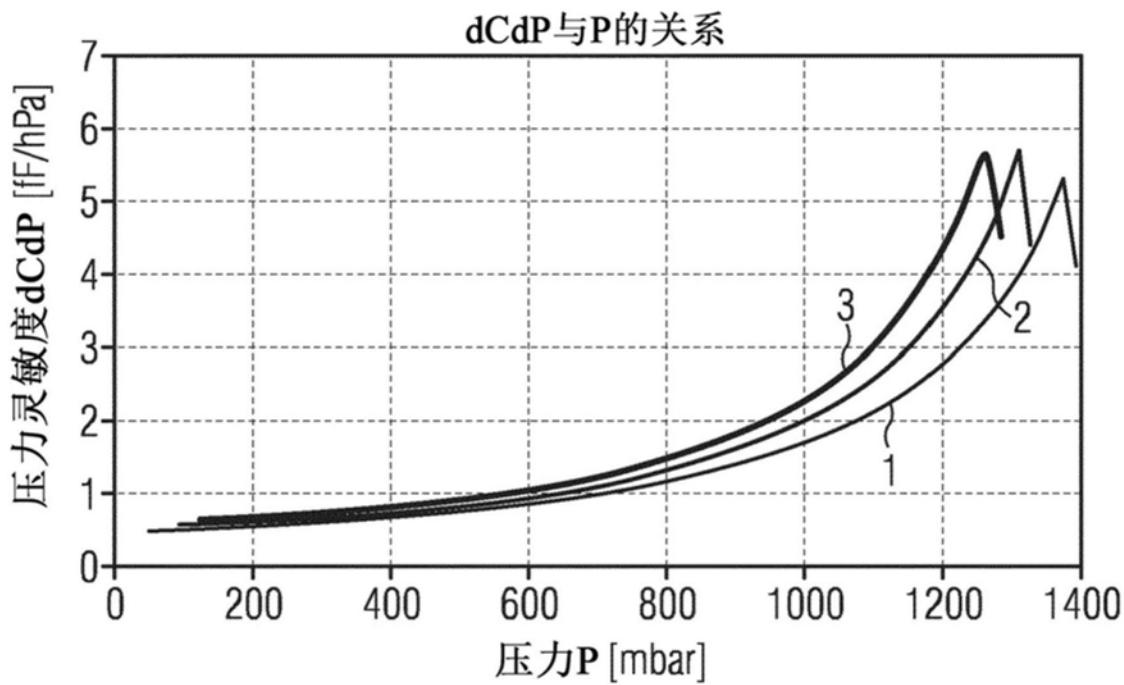

[0166] 在图4B和图4C中,示出了压力传感器12的电容CA和压力灵敏度dCdP随所施加的压力P的变化。

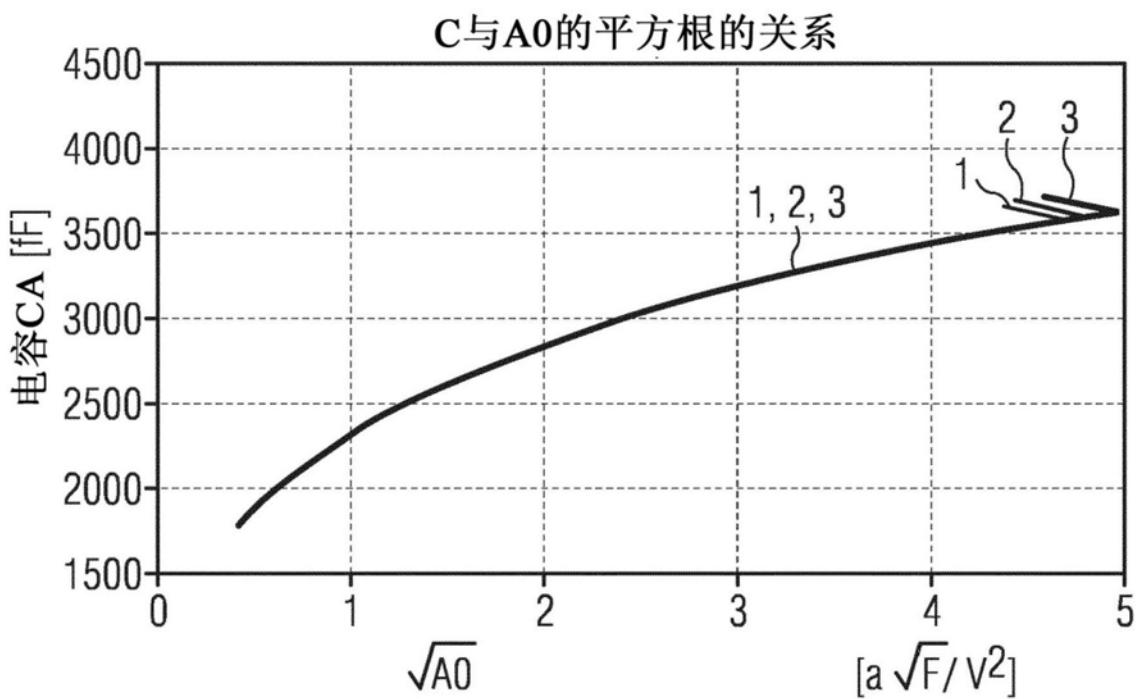

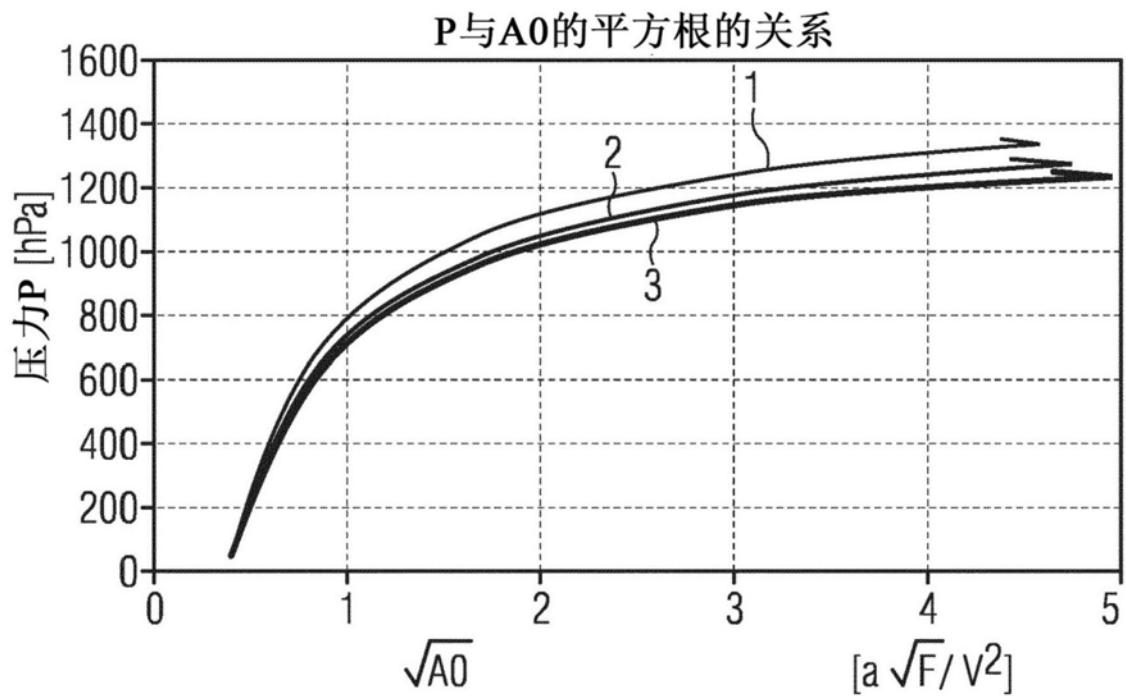

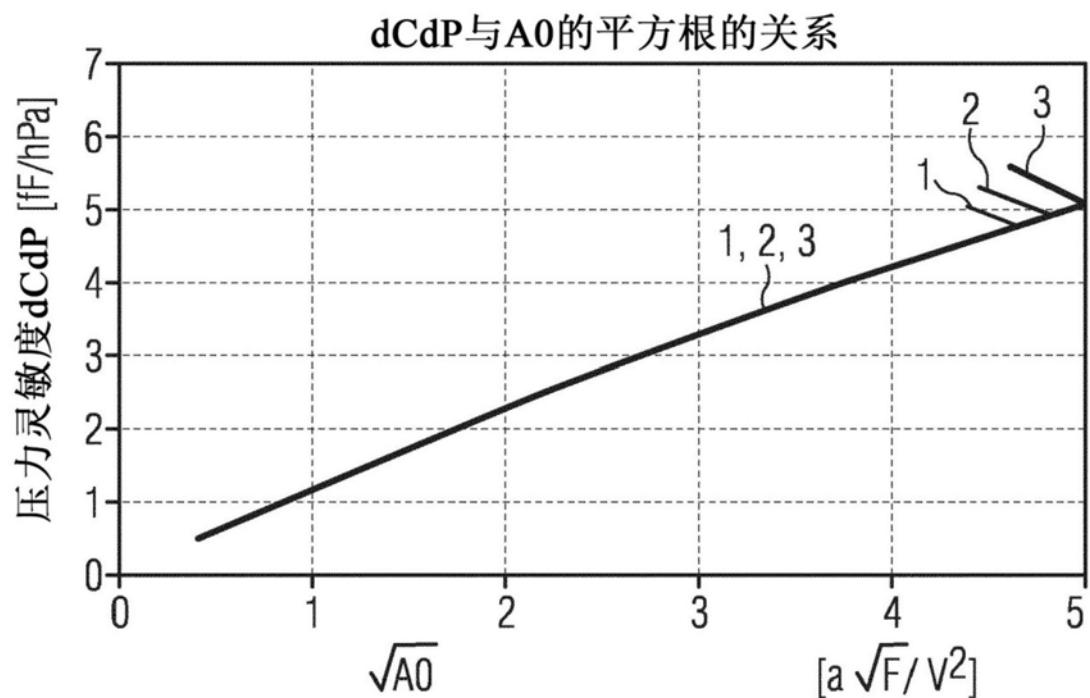

[0167] 图4D示出了在不同退火条件之后传感器12的电容CA与参数A0的平方根的关系。图4E示出了在不同退火条件之后压力P与参数A0的平方根的关系。

[0168] 图4F示出了在不同退火条件之后压力灵敏度与参数A0的平方根的关系特性。如图4F所示,在压力灵敏度(dCdP)与A0的平方根之间发现几乎线性的行为。如果这种关系是已知的,则能够利用压力灵敏度的变化将换能器电容CA正确地转换为正确的压力输出。

[0169] 在图4B至图4F中,传感器12的第一示例的测量特性用1标记,传感器12的第二示例的特性用2标记,并且传感器12的第三示例的特性用3标记。

[0170] 具有压力传感器12的传感器装置10可以实现:在电子分选期间传感器可能良好的管芯选择(即,正确的灵敏度);检查在电子分选期间膜43是否被适当地释放;现场的传感器校准/重新校准;传感器自测试;确定传感器特性在组装期间和寿命期间是否改变以及改变了多少;以及返回商品授权支持,缩写为RMA支持。

[0171] 传感器装置10的优点可以是:降低了组装成本;降低测试成本(更少的校准点);提高使用寿命期间的精度;实现可能的良好管芯选择(例如,对于压力传感器麦克风组合);组装前的产量跟踪和产量改进研究;以及评估封装对传感器移位的影响;对应力解耦效果给出直接反馈。

[0172] 传感器装置10可以包括以下特征:

[0173] 1) 电容式压力传感器12集成在具有嵌入式差分电容至数字转换器13的CMOS的顶部,所述嵌入式差分电容至数字转换器具有四个端子62至65和两个压力敏感膜;

[0174] 2) 采用可变电压参考VREF以允许电容-电压测量和在两个匹配的压敏元件上提取参数A0;

[0175] 3) 将根据压力P和芯片上的温度的参数A0存储在例如存储器21中;

[0176] 4) 基于A0-压力和A0-温度变化来校正P输出随寿命的变化;

[0177] 5) 开关矩阵15连接不同的膜/电容器配置以确定不匹配。

[0178] 参考电压VREF可以被实现为由偏置电路提供的偏置电压或源电压VCM。参考电压发生器32可以被实现为可编程VREF发生器或偏置电路。

[0179] 转换器13可以命名为变换器,反之亦然。

[0180] 转换器13可以实现为电容至数字转换器(简称CDC、C2D或CDC转换器)。模拟至数字转换器(简称ADC)可以实现为CDC,反之亦然。

[0181] 压力传感器12可命名为传感器1,并且另一压力传感器30可以命名为传感器2。

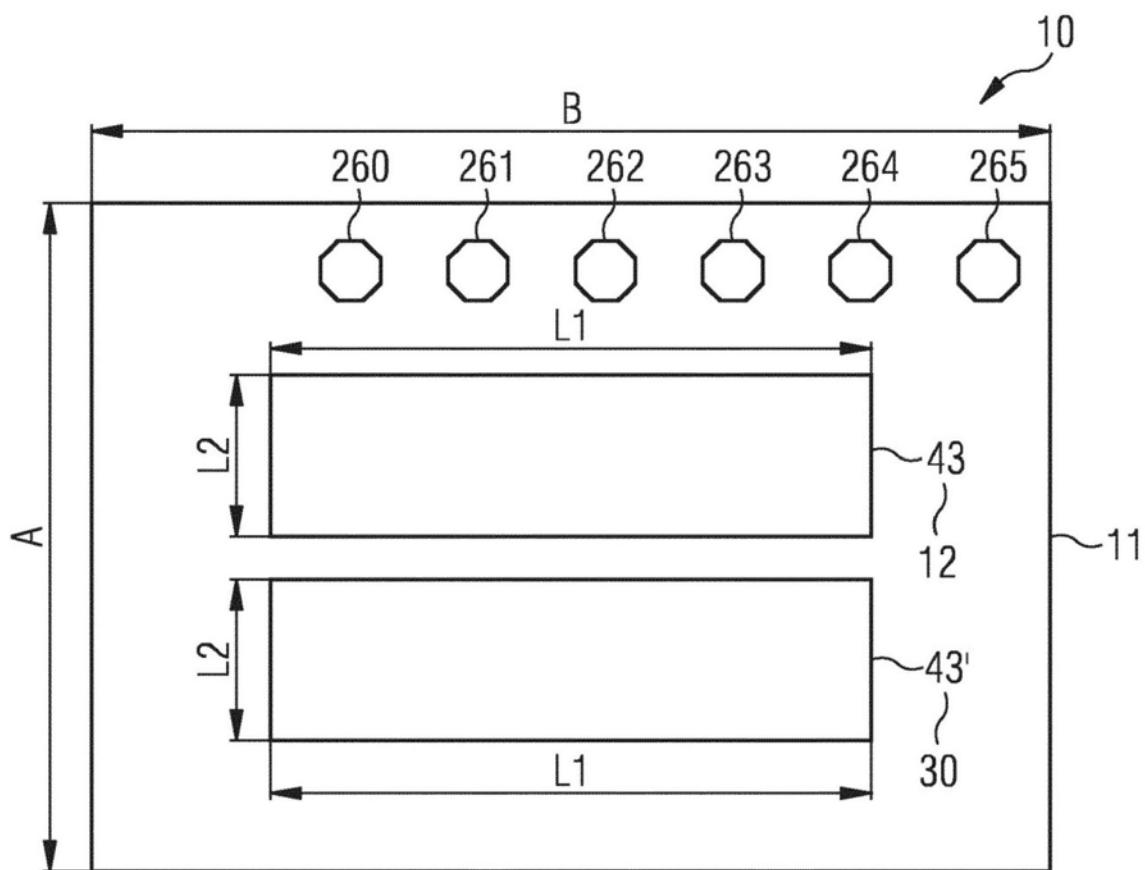

[0182] 图5A示出了作为上述示例的进一步发展的装置10的另一示例。图5A是装置10的半导体本体11的第一表面上的顶部视图。半导体本体11是具有第一长度A和第二长度B的矩形。第一长度A例如不同于第二长度B。传感器12和另一传感器30二者都具有矩形膜43、43'。两个膜43、43'都具有相同的第一侧长度L1和相同的第二侧长度L2。第二侧长度L2大于第一侧长度L1。第二侧长度L2可以大于第一侧长度L1两倍。可替代地,第二侧长度L2可大于第一侧长度L1三倍。传感器12的膜43的长侧平行于另一传感器30的膜43'的长侧。

[0183] 此外,装置10包括几个接合焊盘260至265,所述几个接合焊盘可以仅被布置在半导体本体11的第一表面的一个边界处。半导体本体11的第一表面上不用于实现传感器12和另一传感器30的膜43、43'的区域包括电路部分,例如转换器13、发生器32、开关电路15和数字电路20。

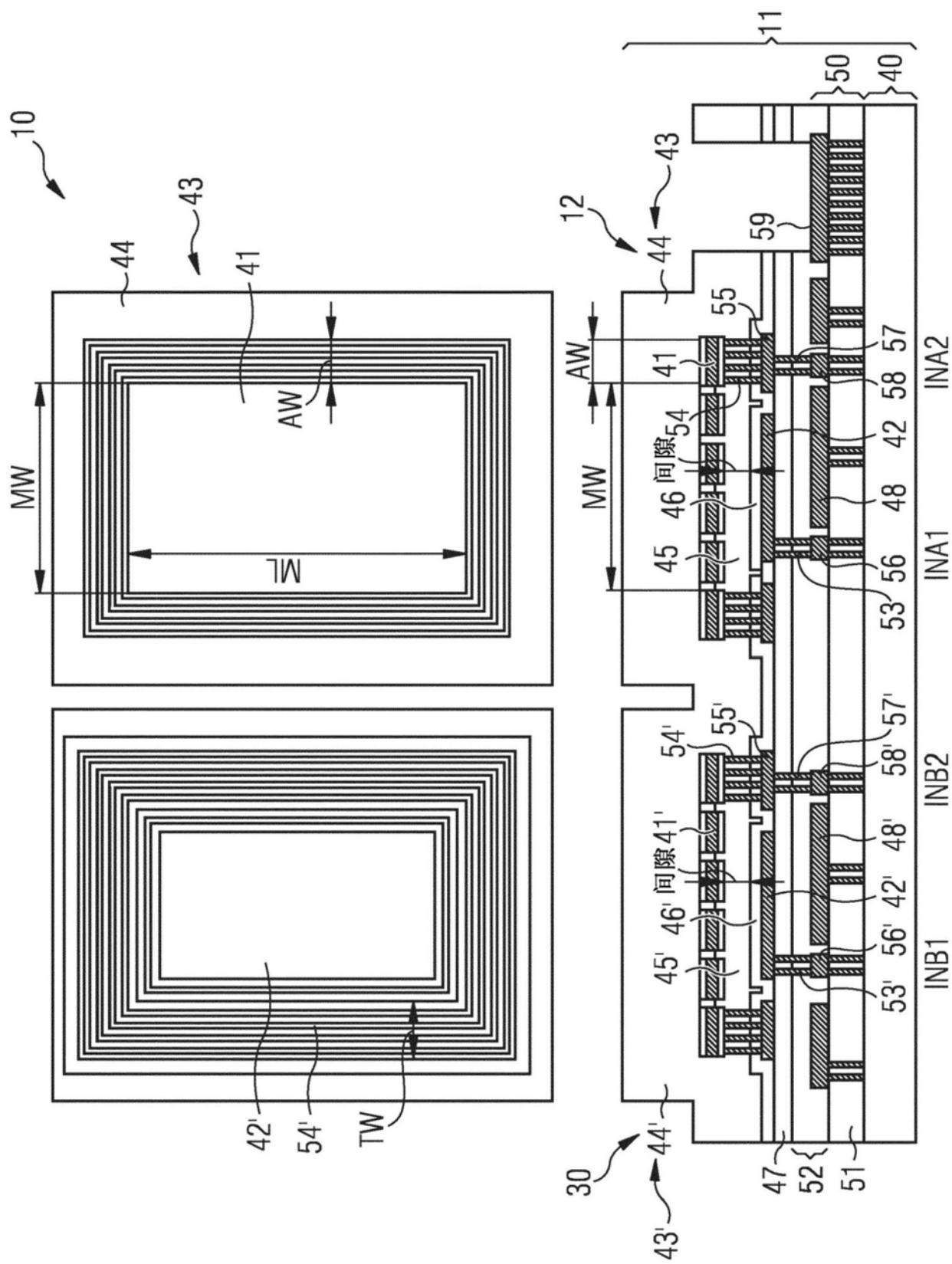

[0184] 图5B示出了装置10的截面和顶部视图。示出了传感器12和另一传感器30的细节。传感器12和另一传感器30在半导体本体11的同一表面上实现。两个传感器12、30并排布置。图5B所示的截面是图2所示的传感器12的截面的进一步发展。传感器12和另一传感器30通过相同的制造工艺实现,并使用相同的层序列。膜43、43'的大小与传感器12和另一传感器30的其他结构可以是相同的。传感器12和另一传感器30的顶部电极41、41'与底部电极42、

42'之间的间隙的值是相等的。接合焊盘59和在底部电极42下方的屏蔽电极48可以由第一金属化层52实现。钝化层47位于屏蔽电极48与底部电极42之间。介电层44执行膜43的密封。

[0185] 在左侧的顶部视图中,示出了另一传感器30的底部电极42'。顶部电极41'不仅覆盖底部电极42'的区域,而且覆盖底部电极42'周围的具有宽度TW的框架。因此,顶部电极41'的区域大于底部电极42'的区域。

[0186] 在右侧的顶部视图中,示出了传感器12的膜43。膜43下面具有腔45。腔45被过孔54围绕。过孔54被实现为锚(anchor)。锚由条带(或线)形成。锚可以是W锚。条带之间的材料例如是牺牲氧化物。

[0187] 在下文中,指定了本公开内容的另外的方面。列举各个方面以便于参考其他方面的特征。

[0188] 1、一种传感器装置,包括

[0189] -压力传感器12,其被实现为电容式压力传感器,以及

[0190] -电容至数字转换器13,其耦接至压力传感器。

[0191] 2、根据方面1的传感器装置,

[0192] 其中,传感器装置10被实现为半导体本体11,以及

[0193] 其中,半导体本体11包括压力传感器12和电容至数字转换器13。

[0194] 3、根据方面1或2的传感器装置,

[0195] 包括被实现为电容式压力传感器的另一压力传感器30,其中,电容至数字转换器13耦接至另一压力传感器30。

[0196] 4、根据方面3的传感器装置,

[0197] 其中,半导体本体11包括另一压力传感器30。

[0198] 5、根据方面1至4中的一个方面的传感器装置,

[0199] 其中,电容至数字转换器13被实现为delta-sigma模拟至数字转换器。

[0200] 6、根据方面1至5中的一个方面的传感器装置,

[0201] 其中,电容至数字转换器13被实现为delta-sigma差分模拟至数字转换器。

[0202] 7、根据方面1至6中的一个方面的传感器装置,

[0203] 其中,电容至数字转换器13的第一端子和第二端子耦接至压力传感器12的第一电极60和第二电极61,以及/或者

[0204] 电容至数字转换器13的第三端子和第四端子耦接至另一压力传感器12的第三电极和第四电极。

[0205] 8、根据方面1至7中的一个方面的传感器装置,

[0206] 其中,电容至数字转换器13被配置成根据提供给传感器的参考电压、偏置电压或源电压VCM,测量由压力传感器12和另一压力传感器30组成的组中的至少一个传感器的电容。

[0207] 9、根据方面8的传感器装置,

[0208] 其中,参考电压、偏置电压或源电压VCM是DC电压。

[0209] 10、根据方面8或9的传感器装置,

[0210] 其中,在时间点或在阶段中,参考电压、偏置电压或源电压VCM被施加在压力传感器的第一电极与压力传感器的第二电极之间。

- [0211] 11、根据方面8至9中的一个方面的传感器装置，

[0212] 其中，在时间点或在阶段中，参考电压、偏置电压或源电压VCM被施加在另一压力传感器的第三电极与另一压力传感器的第四电极之间。

[0213] 12、根据方面1至11中的一个方面的传感器装置，

[0214] 包括：参考电压发生器，其具有用于接收控制信号的控制输入端和用于提供参考电压的输出端；并且

[0215] 其中，参考电压发生器被配置成根据控制信号来设置参考电压的值。

[0216] 13、根据方面12的传感器装置，

[0217] 其中，参考电压的至少两个不同值具有相同的符号和不同的量。

[0218] 14、根据方面12或13的传感器装置，

[0219] 其中，参考电压发生器的输出端连接至电容至数字转换器13的输入端。

[0220] 15、根据方面12至14中的一方面的传感器装置，包括

[0221] -数字电路20，其耦接至电容至数字转换器13和参考电压发生器，以及

[0222] -存储器21，其连接至数字电路20，

[0223] 其中，数字电路20被配置成产生控制信号。

[0224] 16、根据方面15的传感器装置，

[0225] 其中，在操作的测试阶段中，

[0226] 数字电路20被配置成通过控制信号控制参考电压发生器以使得参考电压发生器连续地生成参考电压的至少两个不同值，

[0227] 电容至数字转换器13被配置成根据包括压力传感器和另一压力传感器的组中的至少一个传感器的电容值来生成数字信号的至少两个值，以及

[0228] 数字电路20被配置成根据数字信号的至少两个值来生成参数A0和/或校正数据。

[0229] 17、根据方面16所述的传感器装置，

[0230] 其中，数字电路20被配置成将参数A0或校正数据存储在存储器21中。

[0231] 18、根据方面15或16的传感器装置，

[0232] 其中，数字电路20被配置成根据传感器装置的温度和压力中的至少之一来生成参数A0和/或校正数据。

[0233] 19、根据方面15至18中的一个方面的传感器装置，

[0234] 其中，在操作的测量阶段，数字电路20被配置成根据由电容至数字转换器13提供的数字信号SD并且根据存储在存储器21中的参数A0和/或校正数据来生成数字化压力信号SP。

[0235] 20、根据方面15至19中的一个方面的传感器装置，

[0236] 其中，在操作的测量阶段中，数字电路20被配置成通过控制信号控制参考电压发生器，使得参考电压发生器精确地生成参考电压的一个值。

[0237] 21、根据方面1至20中的一个方面的传感器装置，

[0238] 其中，传感器装置10被配置成确定压力传感器12与另一压力传感器30之间的不匹配，例如参数A0的不匹配。

[0239] 22、根据方面1至21中的一个方面的传感器装置，

[0240] 其中，传感器装置10没有将电容至数字转换器13耦接至压力传感器12和另一压力

传感器30的开关电路15。

[0241] 23、根据方面1至21中的一个方面的传感器装置，

[0242] 包括开关电路15或开关矩阵，其将电容至数字转换器13耦接至包括压力传感器12、另一压力传感器30、参考电容器和另一参考电容器的组中的至少一个电容器，或者耦接至所述组中的至少两个电容器。

[0243] 24、根据方面3至23中的一个方面的传感器装置，

[0244] 其中，压力传感器12包括压力敏感膜，并且另一压力传感器30包括另一压力敏感膜，以及

[0245] 其中，所述膜和另一膜具有相同的大小和相同的厚度。

[0246] 25、根据方面3至24中的一个方面的传感器装置，

[0247] 其中，电容至数字转换器13电连接至压力传感器12和另一压力传感器30，并且被配置成根据压力传感器12的电容值和另一压力传感器30的电容值产生数字信号。

[0248] 26、一种操作传感器装置的方法，包括

[0249] 由电容至数字转换器13根据压力传感器12的电容值和另一压力传感器30的电容值产生数字信号，

[0250] 其中，压力传感器12和另一压力传感器30二者均被实现为电容式压力传感器，并且

[0251] 其中，电容至数字转换器13电连接至压力传感器12和另一压力传感器30。

[0252] 27、根据方面26所述的方法，

[0253] 其中，传感器装置10包括压力传感器12、另一压力传感器30和电容至数字转换器13，并且传感器装置集成在单个半导体本体11上。

[0254] 28、一种操作传感器装置的方法，包括

[0255] 由电容至数字转换器13根据由电容至数字转换器13提供给传感器的参考电压、偏置电压或源电压VCM测量包括压力传感器12和另一压力传感器30的组中的至少一个传感器的电容。

[0256] 29、根据方面28所述的方法，

[0257] 其中，参考电压、偏置电压或源电压VCM是DC电压。

[0258] 30、根据方面28或29所述的方法，

[0259] 其中，参考电压、偏置电压或源电压VCM被施加在压力传感器的第一电极与压力传感器的第二电极之间。

[0260] 31、根据方面28至30中的一个方面的方法，

[0261] 其中，参考电压、偏置电压或源电压VCM被施加在另一压力传感器的第三电极与另一压力传感器的第四电极之间。

[0262] 32、根据方面28至31中的一个方面的方法，

[0263] 其中，在操作的测试阶段中，

[0264] 电容至数字转换器13向传感器提供参考电压的至少两个不同的值，并且

[0265] 电容至数字转换器13根据传感器的电容值产生数字信号的至少两个值，以及

[0266] 数字电路20根据数字信号的至少两个值，产生参数A0和/或校正数据。

[0267] 如所述的图1A至图5B中所示的实施例代表改进的传感器装置的示例实施例，因此

它们不构成根据改进的传感器装置的所有实施例的完整列表。实际的传感器装置配置可以例如在电路部件、形状、大小和材料方面不同于所示的实施例。

[0268] 附图标记

|        |            |          |

|--------|------------|----------|

| [0269] | 10         | 传感器装置    |

| [0270] | 11         | 半导体本体    |

| [0271] | 12         | 压力传感器    |

| [0272] | 13         | 电容至数字转换器 |

| [0273] | 14         | 输出端      |

| [0274] | 15         | 开关电路     |

| [0275] | 20         | 数字电路     |

| [0276] | 21         | 存储器      |

| [0277] | 22         | 输出端      |

| [0278] | 30         | 另一压力传感器  |

| [0279] | 31         | 另一输出端    |

| [0280] | 32         | 参考电压发生器  |

| [0281] | 33         | 输出端      |

| [0282] | 34至39      | 电容器      |

| [0283] | 40         | 半导体衬底    |

| [0284] | 41、41'     | 顶部电极     |

| [0285] | 42、42'     | 底部电极     |

| [0286] | 43、43'     | 膜        |

| [0287] | 44、44'、46  | 介电层      |

| [0288] | 46'、47、51  | 介电层      |

| [0289] | 45、45'     | 腔        |

| [0290] | 48、48'     | 屏蔽电极     |

| [0291] | 49a        | 中心部分     |

| [0292] | 49b        | 外环       |

| [0293] | 50         | 金属化叠层    |

| [0294] | 52         | 金属化层     |

| [0295] | 53、53'、54  | 过孔       |

| [0296] | 54'、57、57' | 过孔       |

| [0297] | 55、55'     | 金属层      |

| [0298] | 56、56'     | 部分       |

| [0299] | 58、58'     | 部分       |

| [0300] | 59         | 接合焊盘     |

| [0301] | 60、60'     | 第一电极     |

| [0302] | 61、61'     | 第二电极     |

| [0303] | 62至65      | 输入端      |

| [0304] | 66、67      | 偏移电容器    |

|        |             |           |

|--------|-------------|-----------|

| [0305] | 68、69       | 输入端       |

| [0306] | 70          | 第一积分器     |

| [0307] | 71          | 量化器       |

| [0308] | 72          | 第一加法器     |

| [0309] | 73、74、77、78 | 缓冲器       |

| [0310] | 75          | 第二加法器     |

| [0311] | 76          | 第二积分器     |

| [0312] | 79          | 滤波器       |

| [0313] | 90          | 共模端子      |

| [0314] | 91至102      | 开关        |

| [0315] | 103         | 参考电位端子    |

| [0316] | 104至107     | 开关        |

| [0317] | 120         | 放大器       |

| [0318] | 121、122     | 积分电容器     |

| [0319] | 123、124     | 斩波器电路     |

| [0320] | 125、126     | 输出端       |

| [0321] | 129         | 采样级       |

| [0322] | 130         | 触发器       |

| [0323] | 131         | 相位发生器     |

| [0324] | 132         | 时钟电路      |

| [0325] | 141         | 另一放大器     |

| [0326] | 142、143     | 集成电容器     |

| [0327] | 144、145     | 输入端       |

| [0328] | 146、147     | 输出端       |

| [0329] | 151、152     | 采样电容器     |

| [0330] | 153至160     | 采样开关      |

| [0331] | 170、171     | 反馈电容器     |

| [0332] | 172至183     | 反馈开关      |

| [0333] | 190、191     | 反馈电容器     |

| [0334] | 192至201     | 反馈开关      |

| [0335] | 220、221     | 切换开关      |

| [0336] | 227         | 放大器       |

| [0337] | 228         | 电阻分压器     |

| [0338] | 229         | 切换开关      |

| [0339] | 230         | 带隙电压参考发生器 |

| [0340] | 231至254     | 开关        |

| [0341] | 255、256     | 电容器       |

| [0342] | 239         | 附加参考端子    |

| [0343] | 241、242     | 切换开关      |

---

|        |             |         |

|--------|-------------|---------|

| [0344] | 243、244     | 重置开关    |

| [0345] | 260至265     | 接合焊盘    |

| [0346] | A、AN        | 斩波器信号   |

| [0347] | AGND        | 附加参考电位  |

| [0348] | GND         | 参考电位    |

| [0349] | P           | 压力      |

| [0350] | Pch、Pchq    | 斩波器信号   |

| [0351] | P1、P1A、P1B  | 相位信号    |

| [0352] | P2、P2A、P2B  | 相位信号    |

| [0353] | SC          | 控制信号    |

| [0354] | SD          | 控制信号    |

| [0355] | SE          | 源选择信号   |

| [0356] | SP          | 数字化压力信号 |

| [0357] | SPC         | 相位控制信号  |

| [0358] | SOC         | 偏移控制信号  |

| [0359] | Sreset      | 重置信号    |

| [0360] | VBG         | 带隙电压    |

| [0361] | VCM         | 共模电压    |

| [0362] | VREF        | 参考电压    |

| [0363] | VREFP、VREFN | 参考电压。   |

图1A

图1B

图1C

图1D

图2

图3A

图 3B

|       |       |

|-------|-------|

| 图 3Ba | 图 3Bb |

|-------|-------|

图3Ba

图3Bb

图3C

图3D

图3E

图3F

图3G

图 3H

图 3Ha 图 3Hb

图 3Ha

图3Hb

图4A

图4B

图4D

图 4E

图 4F

图5A

图5B