(19) RÉPUBLIQUE FRANÇAISE

INSTITUT NATIONAL

DE LA PROPRIÉTÉ INDUSTRIELLE

PARIS

N° de publication :

2 648 292

(21) N° d'enregistrement national :

90 06745

(51) Int CI<sup>a</sup>: H 03 L 7/089; H 04 L 7/10; H 03 K 5/26.

## DEMANDE DE BREVET D'INVENTION

**A1**

(22) Date de dépôt : 30 mai 1990.

(12)

- (30) Priorité: KR, 13 juin 1989, nº 1989-8113.

- (71) Demandeur(s): ELECTRONICS AND TELECOMMUNICA-TIONS RESEARCH INSTITUTE et KOREA TELECOMMU-NICATION AUTHORITY. — KR.

- 72) Inventeur(s): Dong Kwan Shin.

- Références à d'autres documents nationaux apparentés :

(43) Date de la mise à disposition du public de la demande : BOPI « Brevets » n° 50 du 14 décembre 1990.

- (73) Titulaire(s):

- 74 Mandataire(s): Cabinet Harle et Phelip.

- (54) Circuit de resynchronisation numérique à phase autocommandée.

- (57) Ce circuit comprend une porte de sommation logique OR1 produisant des signaux de données, une porte de sommation logique OR2 produisant des impulsions inversées, deux bascules bistables de type D FF1, FF2 produisant des signaux de données resynchronisés en fonction des impulsions d'horloge, et des portes de sommation logique OU-Exclusif EXOR1, EXOR2 produisant quatre signaux de sortie inversés deux-àdeux, qui sont interconnectés de manière à produire des signaux d'états de phase et un processeur de boucle traitant des signaux.

Application notamment à la suppression des erreurs de resynchronisation dans les circuits de communication et de traitement numérique.

La présente invention concerne un circuit de resynchronisation numérique à phase autocommandée servant à empêcher une erreur de resynchronisation lorsqu'une impulsion d'horloge de resynchronisation réalise la resynchronisation automatique des données d'entrée dans la position centrale du diagramme en oeil des données d'entrée.

Pour traiter des données introduites à partir de l'extérieur dans tous les systèmes de communication et/ou de traitement numérique, le processus de resynchronisation avec une impulsion d'horloge de référence sans aucune erreur de resynchronisation doit être mis en oeuvre avant tout.

10

15

20

25

30

35

A cet instant, l'impulsion d'horloge de référence peut être extraite des données d'entrée extérieures ou introduite dans le système lui-même et les relations de phase entre une impulsion d'horloge de resynchronisation et des données d'entrée n'est pas invariable en raison de différents facteurs comme par exemple la forme de réalisation du circuit, des variations dues à la température et au vieil-lissement, etc.

Etant donné qu'on peut utiliser le circuit de resynchronisation numérique à phase autocommandée dans tous les systèmes de communication et/ou de traitement numérique, n'importe quel domaine réel de la technologie classique, que l'on peut considérer, est très étendu, mais on peut en discuter sur la base des deux aspects suivants.

Tout d'abord, il s'agit du cas de la resynchronisation de données d'entrée avec une impulsion d'horloge extraite de données d'entrée dans un répéteur numérique de transmission de données.

Les données reçues sont habituellement affectées par une atténuation du signal dans des canaux de transmission, par le bruit produit dans les canaux de transmission et dans les récepteurs et par une interférence entre symboles, due à une largeur de bande de transmission

insuffisante, etc, ce qui a pour effet qu'il faut récupérer des formes d'ondes nettes au moyen d'une resynchronisation de ces données avec l'impulsion d'horloge extraite.

Pour la récupération d'une impulsion d'horloge à partir de données d'entrée, on utilise habituellement ce qu'on appelle un circuit de synthonisation, un filtre SAW et un circuit PLL de récupération de l'impulsion d'horloge, que l'on classe parmi les circuits d'extraction d'impulsions d'horloge auto-synchronisés.

10

15

20

35

Dans le circuit de synthonisation ou dans le filtre SAW, la différence de phase mutuelle entre l'impulsion d'horloge extraite et les données d'entrée varie fortement en raison de la forme de réalisation pratique du circuit, de la variation due à la température et au veillissement du filtre, etc, et par conséquent la phase de l'impulsion d'horloge de resynchronisation doit être réglée sur le centre du diagramme en oeil des données d'entrée moyennant qui retarde l'utilisation d'un dispositif de retard d'une durée fixe le signal d'entrée. Cependant, ceci est complexe étant donné qu'il faut mesurer et régler la différence de phase mutuelle dans chaque circuit de resynchronisation individuel. En outre, le temps de retard des signaux est fixe de sorte que la phase de l'impulsion d'horloge de resynsans rapport avec une variachronisation peut être tion due à la température, à une variation due au vieillis-25 sement et une variation du niveau d'énergie appliqué.

On utilise un circuit, qui réalise une resynchronisation au moyen de la détection de la différence de phase entre l'impulsion d'horloge récupérée et les données d'en-30 trée (ici la phase des données d'entrée désigne le moment de transition des données en liaison avec la phase de l'impulsion d'horloge, et la phase de l'impulsion d'horloge désigne l'instant important), et qui décale automatiquement la phase de l'impulsion d'horloge en direction du centre du diagramme en oeil des données d'entrée.

Ces exemples sont les suivants: "Alignement de synchronisation automatique pour un répéteur régénératif", publié dans Electronics Letters, Vol. 21, N°24, "Un régénérateur sous-marin à fibre, optique, utilisant un module de substrat intégré et un montage de filtre SAW flix-chip , publié dans IEEE Jr.SAC, Vol. 2, N°6, "Nouveau régénérateur possédant un circuit simple d'extraction de l'impulsion d'horloge et de resynchronisation à commande automatique de phase" publié dans Electronics Letters, Vol. 25, N°1.

Cependant, le fait d'utiliser actuellement une cellule de Gilbert ou une diode varactor, etc, qui sont des constituants d'un déphaseur analogique, présente un inconvénient qui est l'aberration du niveau de l'énergie appliquée.

10

15

De même, il n'est pas facile de traiter les signaux de commande de déphasage. En outre, ils sont volumineux pour un fonctionnement à basse fréquence.

Un circuit de récupération de la synchronisation, 20 qui utilise un circuit PLL de récupération de l'impulsion d'horloge peut être agencé de manière que l'instant important de l'impulsion d'horloge soit resynchronisé de façon automatique au centre du diagramme en oeil des données d'entrée. Un exemple est le "Circuit de récupération de l'impulsion d'horloge, à correction automatique, possédant une performance améliorée vis-à-vis des petites instabilités des signaux", publié dans Electronics Letters, Vol. 23, N°2. Mais, en raison de l'utilisation d'un filtre de boucle analogique et d'un oscillateur commandé par la tension, ce 30 circuit présente des inconvénients consistant en ce qu'il possède des dimensions plus importantes et plus complexes que dans le cas de l'utilisation d'un filtre SAW, etc.

En second lieu, des systèmes SONET (réseaux optiques synchrones) et des systèmes de commutation et des 35 systèmes d'abonnés sont constitués par un grand nombre d'unités de traitement des signaux et nécessitent une transmission des données entre les différentes unités.

Dès à présent, étant donné que l'impulsion d'horloge de référence est délivrée par le poste central déli-5 vrant l'impulsion d'horloge, il n'est pas nécessaire d'extraire des impulsions d'horloge à partir des données d'entrée dans chacune des unités de traitement des signaux, mais de réaliser une resynchronisation avec des impulsions d'horloge délivrées, situés au centre du diagramme en oeil des données d'entrée.

Etant donné que les impulsions d'horloge et les données d'entrée sont transmises à chaque unité selon des trajets indépendants, il est difficile de connaître exactement leur relation de phase mutuelle entre l'impulsion d'horloge et les données dans chaque unité de traitement.

10

15

20

25

30

35

Dans le cas de la resynchronisation par décalage de la phase de l'impulsion d'horloge au moyen de l'utilisation de dispositifs présentant un retard fixe pour les signaux, il existe des circuits qui non seulement règlent et mesurent la différence de phase entre les données et les impulsions d'horloge par rapport à chacune des unités de traitement des impulsions, mais qui peuvent également réaliser une resynchronisation dans une position inappropriée variations du nipar rapport à la température, aux veau d'énergie envoyé et à une variation due au vieillissement.

Comme autre exemple, les problèmes indiqués précédemment se posent également dans le cas de l'application de données et d'une impulsion d'horloge dans des équipements de mesure du taux BER (taux d'erreurs sur les bits), qui sont toujours utilisés pour tester la performance de systèmes de communication.

Un circuit de resynchronisation numérique classique publié dans "Commutation d'un signal à 140 M.bits/s dans un système de communication à large bande" dans Electrical Communication, Vol. 58, N°4, présente un inconvénient consistant en ce qu'il ne peut pas réaliser une resynchronisation au centre du diagramme en oeil des données d'entrée, et de même un circuit de resynchronisation numérique, qui est constitué par une boucle DPLL (boucle PLL numérique), a une vitesse de fonctionnement limitée étant donné qu'il est nécessaire d'utiliser un oscillateur fonctionnant à une fréquence supérieure.

C'est pourquoi, un but de l'invention est de 10 fournir un circuit de resynchronisation numérique à phase autocommandée, qui positionne automatiquement la phase de l'impulsion d'horloge de resynchronisation au centre du diagramme en oeil des données d'entrée, auquel cas l'effet de l'interférence entre les symboles est minimal et la to-15 lérance du bruit est maximale, grâce à la détection de la différence de phase entre l'impulsion d'horloge de resynchronisation et les données, et au moyen du suivi adaptatif de la variation de phase mutuelle dans le cas où la différence de phase mutuelle entre les données et l'impulsion 20 d'horloge de resynchronisation est incertaine et varie dans le temps dans des systèmes de transmission numérique et/ou de traitement de signaux numériques.

Plus précisément, l'invention concerne un circuit de resynchronisation numérique à phase auto-commandée, caractérisé en ce qu'il comprend:

25

35

une première porte de sommation logique servant à recevoir des signaux de données d'entrée dont la phase est commandée et à produire des premier et second signaux de données;

une seconde porte de sommation logique servant à recevoir 30 une impulsion d'horloge d'entrée et à produire une première impulsion d'horloge et une seconde impulsion d'horloge inversée;

une première bascule bistable de type D servant à produire une impulsion de données resynchronisée conformément à ladite seconde impulsion d'horloge inversée et possédant une borne d'entrée de données servant à recevoir ledit premier signal de données provenant de ladite première porte de sommation logique et une borne de délivrance des impulsions d'horloge servant à recevoir ladite seconde impulsion d'horloge inversée à partir de ladite seconde porte de sommation logique;

une seconde bascule bistable de type D servant à produire un signal de données resynchronisé conformément à ladite première impulsion d'horloge et possédant une borne d'entrée de données servant à recevoir un second signal de données à partir de ladite première porte de sommation logique et une borne de réception d'une impulsion d'horloge servant à recevoir ladite première impulsion d'horloge à partir de ladite seconde porte de sommation logique;

10

35

- une première porte de sommation logique exclusive servant à produire un premier signal de sortie et un second signal de sortie inversé au moyen de la combinaison OU-Exclusif dudit signal de donnée resynchronisé de ladite première bascule bistable de type D et dudit premier signal de données de

- ladite première porte de sommation logique;

une seconde porte de sommation logique exclusive servant à

produire un troisième signal de sortie et un quatrième signal de sortie inversé au moyen de la combinaison OU-Exclusif dudit signal de données resynchronisé de ladite seconde

bascule bistable de type D et dudit second signal de don-

- nées de ladite première porte de sommation logique; des premiers moyens de sommation logique servant à produire un premier signal d'état de phase au moyen du raccordement électrique de ladite seconde sortie de ladite première porte de sommation logique exclusive et de ladite troisième sortie de ladite seconde porte de sommation logique exclusive;

des seconds moyens de sommation logique servant à produire un second signal d'état de phase au moyen du raccordement électrique de ladite première sortie de ladite première porte de sommation logique exclusive et de ladite quatrième sortie de ladite seconde porte de sommation logique exclusive;

un processeur de boucle produisant, puis envoyant un signal de bus de commande de sorte que la différence de phase entre ladite donnée d'entrée, dont la phase est commandée, et une impulsion d'horloge d'entrée possèdent une relation de phase correcte moyennant l'utilisation des signaux de sortie desdits premiers et seconds moyens de sommation logique; et

un déphaseur commandant la phase desdites données d'entrée conformément audit signal de commande délivré par ledit processeur de boucle, puis envoyant les données d'entrée, dont la phase est commandée, à ladite première porte de sommation logique.

10

15

ladite impulsion d'horloge d'entrée étant une impulsion d'horloge de resynchronisation et le signal de sortie de ladite seconde bascule bistable de type D étant un signal de données resynchronisé.

- L'invention sera aisément comprise à la lecture de la description plus détaillée qui va suivre, à l'appui des dessins annexés et sur lesquels :

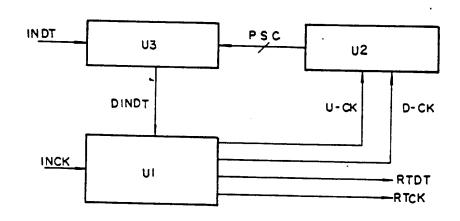

- la figure 1 représente un schéma de réalisation

montrant un circuit de resynchronisation numérique à phase autocommandée;

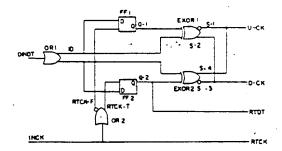

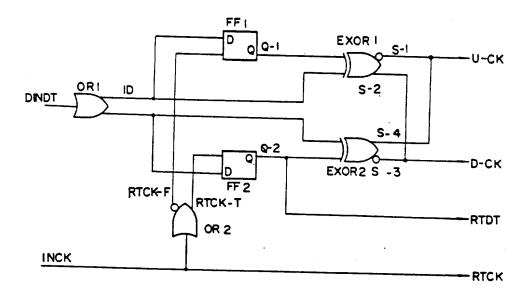

- la figure 2 représente un schéma-type d'un détecteur de phase/resynchroniseur;

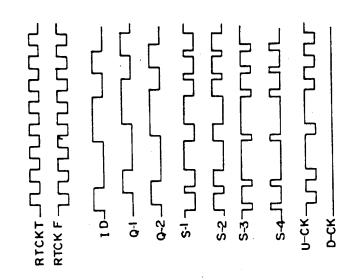

- la figure 3 représente un diagramme montrant 30 des formes d'ondes de cadencement pour chaque partie de la figure 2, lorsque la phase des données d'entrée est située entre le bord de transition montant d'une impulsion d'horloge de resynchronisation et celui d'une impulsion d'horloge de resynchronisation inversée;

- 35 la figure 4 représente un schéma montrant les

formes d'ondes de synchronisatin pour chaque partie de la figure 2, lorsque la phase des données d'entrée est située entre le bord de transition montant d'une impulsion d'horloge de resynchronisation inversée et celui d'une impulsion d'horloge de resynchronisation;

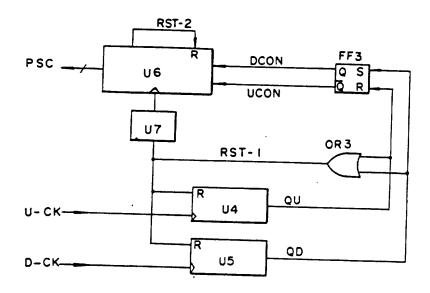

- la figure 5 représente un schéma-type représentant un processeur de boucle;

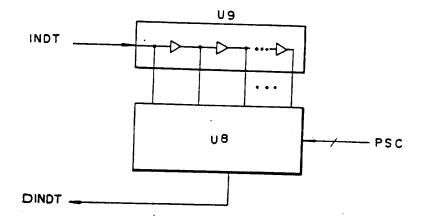

- la figure 6 représente un schéma-type montrant un déphaseur; et

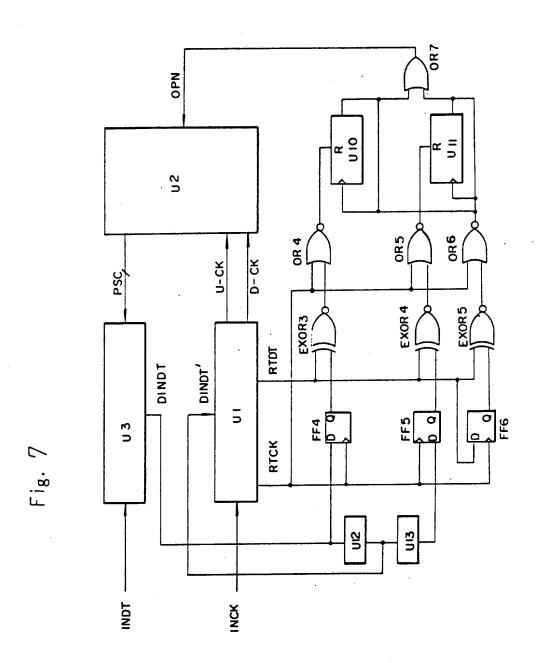

- la figure 7 représente un schéma de réalisation montrant un circuit de resynchronisation numérique stabilisé à phase autocommandée.

Un circuit de resynchronisation numérique à phase autocommandée conforme à l'invention est un circuit numérique à contreréaction, qui est constitué par un détecteur de phase/resynchroniseur (U1), un processeur de boucle (U2) et un déphaseur (U3), comme représenté sur la figure 1.

15

25

30

35

Un détecteur de phase/resynchroniseur (U1) détecte la différence de phase entre l'impulsion d'horloge d'entrée (INCK) et les données d'entrée retardées (DINDT), et l'envoie dans un processeur de boucle (U2), les signaux d'état représentant la phase d'avance ou de retard des données par rapport à l'instant important de l'impulsion d'horloge (c'est-à-dire le bord montant du signal de resynchronisation).

A cet instant, les signaux d'état réglés sur l'impulsion d'horloge sont appliqués à un processeur de boucle (U2), et les largeurs des impulsions de ces signaux d'état ne sont pas inférieures à celles des impulsions d'horloge de resynchronisation, de sorte que le circuit peut fonctionner à la vitesse maximale utilisable.

De même, un détecteur de phase/resynchroniseur (U1) ne resynchronise pas les données d'entrée retardées (DINDT), dont la phase est commandée de façon adaptative par un déphaseur (U3).

Un processeur de boucle (U2) produit et introduit dans un déphaseur (U3) le signal de bus de commande (PSC), en utilisant les signaux d'état de phase (U-CK, D-CK) appliqués par un détecteur de phase/resynchroniseur (U1).

Conformément à ce signal de bus de commande, un déphaseur (U3) commande la phase des données d'entrée (INDT) et introduit des données d'entrée retardées (DINDT) dans un détecteur de phase/resynchroniseur (U1).

5

20

25

La figure 2 représente un schéma permettant d'ex10 pliquer un détecteur de phase/resynchroniseur (U1) comportant une borne d'entrée de données (DINDT) et une borne

d'entrée d'impulsions d'horloge (INCK), et des sorties de

signaux d'état (U-CK, D-CK), une sortie des données resynchronisées (RTDT) et une sortie de l'impulsion d'hor15 loge de resynchronisation (RTCK).

Comme représenté sur la figure 2, une borne d'entrée de données (DINDT) est raccordée à l'entrée d'une porte de sommation logique (OR1), et des sorties (1D) de ladite porte de sommation logique (OR1) sont raccordées à des bornes d'entrée de données de bascules bistables D (FF1,FF2), et individuellement à une borne d'entrée de portes de sommation logique exclusives (EXOR1) et (EXOR2).

Une sortie de données (Q-1) de ladite bascule bistable de type D (FF1) est raccordée à une autre entrée de ladite porte de sommation logique (EXOR1), et une sortie de données (Q-2) de ladite bascule bistable de type D (FF2) est raccordée à une autre entrée de ladite porte de sommation logique exclusive (EXOR2). De même, ce signal devient la donnée de sortie resynchronisée (RTDT).

Un signal d'entrée d'horloge (INCK) est appliqué à une porte de sommation logique (OR2) et devient simultanément un signal de sortie d'horloge de resynchronisation (RTCK).

Une sortie inverseuse (RTCK-F) de ladite porte de 35 sommation logique (OR2) est raccordée à une borne d'entrée

de l'impulsion d'horloge de ladite bascule bistable de type D (FF1), et également une autre sortie non inverseuse (RTCK-T) de ladite porte de sommation logique (OR2) est raccordée à une borne d'entrée des impulsions d'horloge de ladite bascule bistable de type D (FF2).

Une sortie positive (S-2) de ladite porte de sommation logique exclusive (EXOR1) est raccordée selon une combinaison OU à une sortie négative (S-3) de ladite porte de sommation logique exclusive (EXOR2) et fournit un signal de sortie au niveau bas (D-CK). Si on ne peut pas disposer du câblage OU, on peut utiliser une porte de sommation logique à la place de la combinaison câblée OU.

10

15

20

25

30

35

De même, une sortie négative (S-1) de ladite porte de sommation logique exclusive (EXOR1) est raccordée selon la combinaison OU à une sortie positive (S-4) de ladite porte de sommation logique exclusive (EXOR2) et fournit un signal de sortie au niveau haut (U-CK). Si on ne dispose pas d'un système de câblage OU, on peut utiliser une porte de sommation logique à la place du système de câblage OU.

Lesdits signaux de sortie au niveau bas et au niveau haut (D-CK), (U-CK) constituent les signaux d'entrée d'un processeur de boucle (U2).

Dans le cas d'un système agencé conformément aux dispositifs indiqués plus haut, tout d'abord dans le cas où la phase des données d'entrée est située entre le bord montant d'une impulsion de resynchronisation (RTCK-T) et le bord montant d'une impulsion d'horloge de resynchronisation inversée (RTCK-F), on va expliquer comme indiqué ci-après le fonctionnement en liaison avec les formes id'ondes représentées sur la figure 3.

Chaque fois que des transitions de données apparaissent dans des données d'entrée (ID), un signal (S-2), obtenu au moyen de la combinaison OU-Exclusif d'un signal de sortie (Q-1) de la bascule bistable de type D (FF1), traité par

une impulsion d'horloge de resynchronisation inversé (RTCK-F), et d'une donnée d'entrée (ID), prend la valeur 1 pendant l'intervalle de temps s'étendant entre le bord de transition de la donnée d'entrée et le bord montant d'une impulsion d'horloge de resynchronisation inversé (RTCK-F), mais prend la valeur 0 pendant le reste du temps, comme représenté sur la figure 3.

Un signal (S-1) possède une valeur opposée à ce signal.

De même, chaque fois que des transitions de données apparaissent dans les données d'entrée (ID), un signal (S-4), qui est obtenu au moyen de la combinaison OU-Exclusif d'un signal de sortie (Q-2) de la bascule bistable de type D (FF2), traité par une impulsion d'horloge de resynchronisation (RTCK-T), et d'une donnée d'entrée (ID), prend la valeur 1 pendant l'intervalle de temps s'étendant entre le bord de transition de la donnée d'entrée et le bord montant d'une impulsion d'horloge de resynchronisation (RTCK-T), mais est égal à 0 pendant le reste du temps.

Un signal (S-3) possède la valeur opposée à ce signal.

Par conséquent, le signal (U-CK), qui est obtenu à partir de la combinaison OU des signaux (S-1) et (S-4) prend toujours la valeur 1, mais le signal (D-CK), obtenu au moyen de la combinaison OU des signaux (S-2) et (S-3), prend la valeur 0 pendant la moitié du cycle, chaque fois que des transitions de données (ID) se produisent, auquel cas il est alors possible de connaître l'état de la phase des données d'entrée par rapport à l'instant important des impulsions d'horloge de resynchronisation (RTCK-T).

25

30

35

Un cas, où la phase des données d'entrée est située entre le bord montant d'une impulsion d'horloge de resynchronisation inversée (RTCK-F) et celui d'une impulsion d'horloge de resynchronisation (RTCK-T), également traité selon le même principe, et dans ce cas, seul le signal

d'état au niveau haut (U-CK) est activé.

10

20

25

Les diagrammes de formes d'ondes, obtenus à cet instant, sont ceux représentés sur la figure 4.

A l'état permanent , l'instant important d'une impulsion d'horloge de resynchronisation (RTCK-T) est situé au centre du diagramme en oeil des données d'entrée, et fournit des données resynchronisées correctes.

Un processeur de boucle (U2) agit de manière à éliminer le risque d'une opération erronée due aux signaux indésirables comme par exemple le bruit et l'interférence entre symboles, associés aux données d'entrée, etc, et son exemple est décrit en référence à la figure 5.

Les signaux d'entrée comme par exemple le signal d'état au niveau haut et le signal d'état au niveau bas (U-CK, D-CK) sont appliqués individuellement à des entrées de signaux d'horloge de compteurs de division par N (U4 et U5).

Une sortie (QU) dudit compteur de division (U4) est raccordée à une entrée d'une porte de sommation logique (OR3) et à l'entrée de remise à l'état initial d'une bascule bistable de type SR (FF3).

De même, un signal de sortie (QD) dudit compteur de division (U5) est raccordé à une autre entrée d'une porte de sommation logique (QR3) et à l'entrée positionnée de ladite bascule bistable de type SR (FF3).

Une sortie (RST-1) de ladite porte de sommation logique (OR3) est raccordée aux entrées de remise à l'état initial desdits compteurs de division par N, (U4,U5) et à un groupe de portes de retard (U7).

Un signal de sortie est délivré par ledit groupe de portes de retard (U7) et est envoyé à la borne d'entrée des impulsions d'horloge d'un compteur progressif/régressif (U6).

De même, les sorties (DCON), (UCON) de ladite 35 bascule bistable de type SR (FF3) sont raccordées à des

bornes d'entrée de commande de direction d'un compteur progressif/régressif (U6).

Un signal de bus de sortie (PSC) dudit compteur progressif/régressif (U6) fournit les signaux de sorties de commande envoyés à un déphaseur (U3).

Avec l'agencement indiqué précédemment, on va tout d'abord donner l'explication du cas où seul le signal d'état au niveau haut (U-CK) est activé.

Dans l'état initial, un compteur de

division par N (U5) maintient en permanence l'état initial,

c'est-à-dire la valeur 0, un compteur de division par N (U4) compte le nombre d'impulsions d'horloge du

signal d'état à niveau haut (U-CK), et lorsque le signal de

sortie (QU) devient égal à 1 à l'instant où la valeur du

nombre d'impulsions d'horloge dépasse N, il ramène à 0 les

compteurs individuels de division par N (U4,U5).

Lorsque le signal de sortie (QU) revient à 0 après le temps de retard de propagation produit dans le compteur de division par N et dans la porte de sommation logique (OR3), il produit des impulsions d'horloge servant à activer un compteur progressif/régressif (U6).

20

25

30

35

Lorsqu'un groupe de portes de retard (U7) intervient pour appliquer l'impulsion d'horloge après un intervalle de temps suffisant, les signaux de sortie (DCON), (UCON) de la bascule bistable de type SR activent le compteur progressif/régressif avant l'arrivée des impulsions d'horloge.

Dans le cas opposé, il est également possible de donner l'explication sur la base des mêmes principes.

Un signal de remise à zéro (RST-2) d'un compteur progressif/régressif (U6), qui peut effectuer un comptage depuis 0 jusqu'à 2M, empêche une perte de données due à une brusque variation de la valeur de comptage de 0 à 2M, ou, inversement, faire démarrer le compteur progressif/régressif (U6) à partir de M lorsqu'il contrôle les valeurs de

comptage 0 ou 2M.

10

15

20

25

30

Un déphaseur U3 peut être réalisé de différentes manières, un exemple en est représenté sur la figure 6.

Il se compose d'un groupe de portes de retard U9 fournissant un retard 2M, chaque porte fournissant un retard de phase unité, par un multiplexeur 2M:1 (U8).

La valeur du retard de phase unité, D, et la demi-adresse du compteur progressif/régressif, M, satisfont à la relation  $D*M \ge T$ . Ici T est la durée de la période (c'est-à-dire l'inverse de la fréquence de fonctionnement).

Un circuit de resynchronisation numérique à phase autocommandée conforme à l'invention présente des caractéristiques consistant en ce que l'instant important de l'impulsion d'horloge de resynchronisation est située au centre du diagramme en oeil des données d'entrée.

Lors du démarrage du fonctionnement dans le cas où l'instant important de l'impulsion d'horloge de resynchronisation est situé au niveau de la transition des données, il arrive que cet instant ne se situe plus dans cette transition et passe à l'état permanent.

Ainsi, l'instant important de l'impulsion d'horloge de resynchronisation inversée se situe au niveau du bord de transition des données.

De façon plus précise, l'instant important de l'impulsion d'horloge de resynchronisation inversée par rapport au bord de transition des données est situé à l'intérieur de l'intervalle de temps positionné et du temps de maintien de la bascule bistable de type D, utilisé comme dispositif de resynchronisation.

Dans le cas de la réalisation d'un circuit de resynchronisation pour un traitement de données à une cadence de 155 M.bits/s moyennant l'utilisation d'un circuit logique ECL, la somme de l'instant de positionnement et de l'instant de maintien est égal à environ 0,5 ns. En supposant qu'on utilise une porte, dont le temps de retard de 35

propagation unité est égal à 1 ns, en tant que composant d'un groupe de portes de retard (U9), l'instant important de l'impulsion d'horloge de resynchronisation varie en fonction de l'écart d'environ 0,5 ns, en amont et en aval du centre du diagramme en oeil des données.

Par conséquent, l'instant important de l'impulsion d'horloge de resynchronisation est situé au centre du diagramme en oeil des données, avec un écart de 0,5 ns.

On va décrire en référence à la figure 7 l'agen-10 cement permettant d'éliminer cette variation et de ramener le signal dans la position centrée fixe à l'état permanent.

Le signal de sortie d'un déphaseur (U3) est appliqué à un détecteur de phase/resynchroniseur (U1) après avoir traversé un groupe de porte de retard (U12), et la 15 donnée de sortie est resynchronisée et délivrée par le détecteur de phase/resynchroniseur (U1) et comparée à deux signaux de sortie de deux bascules bistables de type D (FF4), (FF5), dont l'une réalise la resynchronisation di-20 recte du signal de sortie du déphaseur (U3), et dont l'autre réalise la resynchronisation du signal de sortie d'un groupe de portes de retard (Ul3) appliquant aux signaux le même retard que le groupe de portes de retard (U12). Les données resynchronisées (RTDT) et le signal 25 de sortie de la bascule bistable de type D (FF6) sont combinées selon la combinaison OU-Exclusif de sorte que ces données s'annulent uniquement lorsque les transitions de données apparaissent. .

Si les mêmes valeurs apparaissent plus de K fois au niveau de chacume des différentes sorties des portes de sommation logiques exclusif (EXOR3), (EXOR4), le signal de sortie de compteurs de division par K (U10) et (U11) prend la valeur 1, et ces signaux sont appliqués à l'entrée d'une porte de sommation logique (OR3) dans un processeur de boucle (U2), ce qui supprime la fluctuation du signal (PST)

5

10

15

20

25

35

de bus de commande du déphasage. De même, ces signaux de sortie de compteurs de division par K (U10), (U11) empêchent la poursuite du comptage des compteurs, jusqu'à ce que l'entrée de remise à zéro soit appliquée.

Une autre réalisation à titre d'exemple de l'invention est représentée sur la figure 7, sur laquelle un circuit stabilisé est constitué par des circuits de retard (U12), (U13), des bascules bistables de type D (FF4), (FF5), (FF6), des portes de sommation logique exclusive (EXOR3), (EXOR4), (EXOR5), des portes de sommation logique (OR4), (OR5), (OR6), des compteurs de division par K (U10), (U11) et une porte de sommation logique (OR7), en dehors d'un détecteur de phase/resynchroniseur (U1), d'un déphaseur (U3) et d'un processeur en boucle (U2), décrits précédemment.

La présente invention agencée comme indiqué précédemment fournit les effets suivants.

- 1. Les problèmes consistant en ce que la valeur statique de la différence de phase entre les impulsions d'horloge et les données est incertaine lors de la conception d'un circuit de resynchronisation, sont complètement éliminés.

- 2. Etant donné que la resynchronisation s'effectue toujours au centre du diagramme en oeil des données d'entrée par rapport à une fluctuation dynamique de la phase des données d'entrée, résultant de variations dues à la température et au vieillissement ou à des facteurs externes, il n'existe aucune erreur de resynchronisation.

- 3. Etant donné que la vitesse de fonctionnement du circuit dépend uniquement de la durée de positionnement et de la durée de maintien de la bascule bistable de type D, du dispositif de resynchronisation, il est possible d'utiliser un tel circuit en tant que circuit de resynchronisation fonctionnant à grande vitesse.

- 4. Etant donné que l'agencement du circuit consiste

uniquement en des dispositifs numériques, il est possible de le fabriquer avec de petits semiconducteurs adaptés en fonction de l'utilisation particulière.

- 5. La reproduction et la fiabilité associés à la fabrication en grandes séries, sont excellentes.

- 6. Etant donné que la présente invention présente une tolérance très élevée vis-à-vis de petites variations instables dans le cas où elle est utilisée en série avec un circuit de récupération de cadence (c'est-à-dire lors-qu'elle est utilisée dans un répéteur), permet de maximiser la section de maintenance

- 7. Lorsqu'elle est combinée avec un circuit d'extraction classique de cadence, la fonction de transfert des petites variations parasites et la fonction de tolérance des petites variations parasites d'entrée peuvent être commandées de façon indépendante.

10

## REVENDICATIONS

1. Circuit de resynchronisation numérique à phase auto-commandée, caractérisé en ce qu'il comprend:

une première porte de sommation logique (OR1) servant à recevoir des signaux de données d'entrée (DINDT) dont la phase est commandée et à produire des premier et second signaux de données;

une seconde porte de sommation logique (OR2) servant à recevoir une impulsion d'horloge d'entrée et à produire une première impulsion d'horloge et une seconde impulsion d'horloge inversée;

10

15

une première bascule bistable de type D (FF1) servant à produire un signal de données resynchronisé conformément à ladite seconde impulsion d'horloge inversée et possédant une borne d'entrée de données servant à recevoir ledit première signal de données provenant de ladite première porte de sommation logique (OR1) et une borne de délivrance des impulsions d'horloge servant à recevoir ladite seconde impulsion d'horloge inversée à partir de ladite seconde porte

de sommation logique (OR2);

une seconde bascule bistable de type D (FF2) servant à produire un signal de données resynchronisé conformément à ladite première impulsion d'horloge et possédant une borne

d'entrée de données servant à recevoir un second signal de

données à partir de ladite première porte de sommation logique (OR1) et une borne de réception d'une impulsion

d'horloge servant à recevoir ladite première impulsion d'horloge à partir de ladite seconde porte de sommation logique

(OR2);

une première porte de sommation logique exclusive (EXOR1) servant à produire un premier signal de sortie (S-2) et un second signal de sortie inversé (S-1) au moyen de la combinaison OU-Exclusif dudit signal de donnée resynchronisé de ladite première bascule bistable de type D (FF1) et dudit premier signal de données de ladite première porte de som-

mation logique (OR1);

une seconde porte de sommation logique exclusive (EXOR2) servant à produire un troisième signal de sortie (S-4) et un quatrième signal de sortie inversé (S-3) au moyen de la combinaison OU-Exclusif dudit signal de données resynchronisé de ladite seconde bascule bistable de type D (FF2) et dudit second signal de données de ladite première porte de sommation logique (OR1);

- des premiers moyens de sommation logique servant à produire un premier signal d'état de phase (U-CK) au moyen du raccordement électrique de ladite seconde sortie de ladite première porte de 'sommation logique exclusive (EXOR1) et de ladite troisième sortie de ladite seconde porte de sommation logique exclusive (EXOR2);

- des seconds moyens de sommation logique servant à produire un second signal d'état de phase (D-CK) au moyen du raccordement électrique de ladite première sortie de ladite première porte de sommation logique exclusive (EXOR1) et de ladite quatrième sortie de ladite seconde porte de sommation logique exclusive (EXOR2);

- un processeur de boucle (U2) produisant, puis envoyant un signal de bus de commande (PSC) de sorte que la différence de phase entre ladite donnée d'entrée (DINDT), dont la phase est commandée, et une impulsion d'horloge d'entrée

- 25 (INCK) possèdent une relation de phase correcte moyennant l'utilisation des signaux de sortie (U-CK, D-CK) desdits premiers et seconds moyens de sommation logique; et

- un déphaseur (U3) commandant la phase desdites données d'entrée conformément audit signal de commande délivré par ledit processeur de boucle (U2), puis envoyant les données d'entrée (DINDT), dont la phase est commandée, à ladite première porte de sommation logique (OR1),

- ladite impulsion d'horloge d'entrée (INCK) étant une impulsion d'horloge de resynchronisation (RTCK) et le signal de

- 35 sortie de ladite seconde bascule bistable de type D (FF2)

étant un signal de données resynchronisé (RTDT).

10

20

25

30

35

et

2. Circuit de resynchronisation numérique à phase auto-commandée selon la revendication 1, dans lequel ledit processeur de boucle (U2) est caractérisé en ce qu'il est constitué par

des premier et second compteurs de division par N (U4,U5), dont chacun possède une borne d'entrée pour l'impulsion d'horloge,

une bascule bistable de type SR (FF), un compteur progressif/régressif (U6), un circuit de retard de transfert (U7), et une troisième porte de sommation logique (OR3),

des signaux d'un premier et d'un second états (U-CK, D-CK) sont appliqués respectivement à chacune desdites bornes d'entrée d'impulsion d'horloge desdits premier et second compteurs de division par N (U4,U5), et

un signal de sortie (QU) dudit compteur de division par N (U4) est appliqué à une première borne d'entrée de ladite porte de sommation logique (OR3) et à une entrée de remise à l'état initial d'une bascule bistable de type SR (FF3), et

à un signal de sortie (RD) dudit compteur de division par N (U5) est appliqué à une seconde borne d'entrée de ladite porte de sommation logique (OR3) et à une entrée de positionnement d'une bascule bistable de type SR (FF3), et

un signal de sortie (RST-1) de ladite troisième porte de sommation logique (OR3) est appliqué à des entrées de remise à l'état initial desdits compteurs de division par N (U4, U5) et dudit circuit de porte de retard (U7), et

un signal de sortie dudit circuit de porte de retard (U7) est appliqué à une borne, qui reçoit l'impulsion d'horloge, dudit compteur progressif/regressif (U6), et

des signaux de sortie (DCON,CON) de ladite bascule bistable de type SR (FF3) sont envoyés à des bornes d'entrée de commande de direction dudit compteur progressif/régressif (U6), et

20

25

30

Ledit compteur progressif/régressif (U6) envoit un signal de bus de commande (PSC) audit déphaseur (U3) et ledit compteur progressif/régressif (U6) comprend une borne de remise à l'état initial servant à ramener à M l'état de comptage dudit compteur progressif/régressif (U6), lorsque l'état de comptage de ce compteur est égal à 0 ou 2M.

- 3. Circuit de resynchronisation numérique à phase autocommandée, selon la revendication 1, caractérisé en ce qu'il comporte en outre un premier circuit de porte de retard (U12) branché entre ladite borne de sortie dudit déphaseur (U3) et ladite borne d'entrée de ladite première porte de sommation logique (OR1).

- 4. Circuit de resynchronisation numérique à phase autocommandée selon la revendication 3, caractérisé en ce qu'il comporte en outre un circuit de stabilisation qui est constitué par :

un second circuit de porte de retard (U13) raccordé audit premier circuit de porte de retard (U12);

des troisième, quatrième et cinquième bascules bistables de type D (FF4,FF5,FF6), dont chacune possède une borne de type D permettant de recevoir respectivement un signal de sortie (DINDT) dudit déphaseur (U3), un signal de sortie dudit circuit de porte de retard (U13) et un signal de données de resynchronisation (RTDT);

lesdites troisième, quatrième et cinquième bascules bistables de type D (FF4,FF5,FF6) comportant chacune une borne de réception d'une impulsion d'horloge, qui sert à recevoir une impulsion d'horloge de resynchronisation (RTCK);

des troisième, quatrième et cinquième portes de sommation logique exclusives (EXOR3, EXOR4, EXOR5) comportant chacune une porte de sommation logique exclusive possédant des premières et secondes bornes d'entrée, chacune desdites premières bornes d'entrée servant à recevoir respectivement le signal de sortie desdites bascules bistables de type D (FF4,FF5,FF6), et chacune desdites secondes bornes d'entrée servant à recevoir un signal de données de resynchronisation (RTDT);

des quatrième, cinquième et sixième portes de sommation logique (OR4,OR5,OR6), dont chacune possède des première et seconde bornes d'entrée, ladite première borne d'entrée servant à recevoir respectivement ladite impulsion d'horloge de resynchronisation (RTCK), et ladite seconde borne d'entrée servant à recevoir respectivement des signaux de sortie inverses desdites portes de sommation logique exclusives (EXOR3, EXOR4, EXOR5);

10

25

des premier et second compteurs de di

15 -vision par K (U10,U11), dont chacun possède une borne de remise à zéro (R) servant à recevoir respectivement des signaux de sortie inverse de portes de sommation logique (OR4,OR5), et chacun desdits compteurs possédant une borne d'entrée d'une impulsion d'horloge servant à recevoir un signal de sortie inverse de ladite porte de sommation logique (OR6) et chacun desdits compteurs possédant une borne de sortie, chaque borne de sortie étant raccordée auxdites bornes respectives d'entrée d'impulsions d'horloge desdits premier et second compteurs de division par K; et

une porte de sommation logique (OR7) raccordée à ladite borne de sortie de chacun desdits premier et second compteurs de division par K (U10,U11),

un signal de sortie de ladite porte de sommation logique (OR7) est appliqué à une borne d'entrée de ladite porte de sommation logique (OR3) du processeur de boucle (U2).

Fig. 1

Fig. 2

RTCK-f

RT

Fig. 3

Fig. 5

Fig. 6