(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4409765号

(P4409765)

(45) 発行日 平成22年2月3日(2010.2.3)

(24) 登録日 平成21年11月20日(2009.11.20)

(51) Int.Cl.

G O 1 R 33/04 (2006.01)

F 1

G O 1 R 33/04

請求項の数 5 (全 12 頁)

(21) 出願番号 特願2000-533768 (P2000-533768)

(86) (22) 出願日 平成11年1月25日 (1999.1.25)

(65) 公表番号 特表2002-527718 (P2002-527718A)

(43) 公表日 平成14年8月27日 (2002.8.27)

(86) 國際出願番号 PCT/US1999/001441

(87) 國際公開番号 WO1999/044072

(87) 國際公開日 平成11年9月2日 (1999.9.2)

審査請求日 平成18年1月10日 (2006.1.10)

(31) 優先権主張番号 09/028,858

(32) 優先日 平成10年2月24日 (1998.2.24)

(33) 優先権主張国 米国(US)

(73) 特許権者 595103854

メソード エレクトロニクス インコーポ

レイテッド

アメリカ合衆国 イリノイ州 60706

ハーウッドハイツ ウエスト ウィルソ

ンアベニュー 7444

(74) 代理人 100079119

弁理士 藤村 元彦

(74) 代理人 100079304

弁理士 小島 隆司

(72) 発明者 クライプ デーヴィッド ダブリュ.

アメリカ合衆国 イリノイ州 623

20 キャンプポイント ボックス2

63 ローラルルートナンバー2

最終頁に続く

(54) 【発明の名称】微小電力型磁力計

## (57) 【特許請求の範囲】

## 【請求項 1】

外部磁界の強度及び方向を測定するためのフラックスゲート磁力計であって、

インダクタ鉄心を磁気的に飽和させるため、外部磁界及び交番入力信号に対する応答性

をもつ可飽和鉄心インダクタ；

鉄心に対する入力信号の印加時点と前記インダクタ鉄心が飽和状態となる時点の間の時

間を表わす飽和信号を提供するための飽和検出回路；

前記飽和信号を前記交番入力信号と比較し、前記交番入力信号パルスの立上り及び立下

りエッジの各々について、前記入力信号の交番パルスと前記インダクタのコイルのその後

の飽和の間の伝搬遅延を測定するための比較回路；及び、

前記磁界の強度及び方向を表示するため前記伝搬遅延に応答してアナログ出力信号を提

供するための出力回路を含み、

前記飽和検出回路が、前記インダクタの出力端と大地基準との間に接続されたコンデン

サと、前記コンデンサを横断する電圧降下を監視するように構成され、前記コンデンサを

横断する電圧降下が前記交番入力信号の振幅の約半分に等しい閾値電圧を越えた時点で、

真と偽との間で遷移する論理出力信号を生成する比較器と、を含み、

前記比較回路が、前記インダクタを通しての第1の信号伝搬遅延と等しいパルス幅を有

する第1のPWM信号を提供する第1のパルス幅変調器と、前記インダクタを通しての第

2の信号伝搬遅延と等しいパルス幅を有する第2のPWM信号を提供する第2のパルス幅

変調器と、を含み

10

20

前記第1の信号伝搬遅延は、前記入力信号の第1の遷移と前記比較器の論理出力信号のその後に続く反対の遷移との間の遅延に等しく、前記第2の信号伝搬遅延は、前記入力信号の第2の反対の遷移と前記比較器の論理出力信号のその後の遷移との間の遅延に等しいことを特徴とする磁力計。

【請求項2】

前記出力回路には、パルス幅復調器が含まれ、前記アナログ出力信号は、前記第1のPWM信号のパルス幅に比例していることを特徴とする請求項1記載の磁力計。

【請求項3】

前記出力回路が、RCフィルタに結合された3状態スイッチを含むことを特徴とする請求項1記載の磁力計。

【請求項4】

前記3状態スイッチが、

第1の出力電圧基準を基準とし、前記第1のPWM信号が論理真状態にあるとき前記RCフィルタの入力端に対し前記第1の出力電圧基準を接続する、第1のアナログスイッチ；及び

第2の出力電圧基準を基準とし、前記第2のPWM信号が論理真状態にあるとき前記RCフィルタの入力端に対し前記第2の出力電圧基準を接続する、第2のアナログスイッチ；

を含むことを特徴とする請求項3記載の磁力計。

【請求項5】

フックスゲートインダクタ；

交番する立上りエッジ及び立下りエッジを有する交番入力電圧信号を用いて前記フックスゲートインダクタを駆動するための発振器；

前記フックスゲートインダクタからの出力電圧信号を蓄積するための電圧蓄積手段；

前記電圧蓄積手段内に蓄積された前記出力電圧信号を前記入力電圧信号と比較することを目的とし、前記フックスゲートを通しての信号伝搬遅延を検出し、前記フックスゲートインダクタを通しての前記入力電圧信号の各パルスの立上り及び立下りエッジの各々について、前記伝搬遅延により変調されたパルス幅被変調信号を生成する比較手段；及び、

前記比較手段によって生成された前記パルス幅被変調信号に応答してアナログ電圧信号を生成し、前記磁界の強度及び方向を表示するためのパルス幅復調器手段；を含み、

前記電圧蓄積手段が、前記フックスゲートインダクタの出力端と大地基準電位との間に接続されたコンデンサを含み、

前記比較手段が、前記入力電圧信号の前記立上りエッジと前記コンデンサ内に蓄積された電圧が予め定められた電圧レベルに達する時点との間の時間的遅延に対応する第1の伝搬遅延によって第1のパルス幅被変調信号を変調する第1のパルス幅変調器と、前記入力電圧信号の立下りエッジと前記コンデンサを横断する電圧降下が予め定められた電圧レベルより低く降下した時点との間の時間的遅延に対応する第2の伝搬遅延によって第2の被変調信号のパルス幅を変調させる、前記第2のパルス幅被変調信号を生成する第2のパルス幅変調器とを含むことを特徴とする磁力計。

【発明の詳細な説明】

【0001】

【背景】

本発明は、磁界の存在を測定するための低電力フックスゲート磁力計に関する。フックスゲート磁力計は、当該技術分野において周知のものである。このような装置は、往々にしてフックスゲートと呼ばれる、可飽和鉄心インダクタのインダクタンスの変化を測定することによって、外部磁界の強度を測定する。このような装置では、フックスゲートインダクタは、例えば正弦波形又は矩形波形をもつ交流信号によって駆動される。交流入力電流は、フックスゲート鉄心内で交番磁界を誘導する。入力信号は、充分な振幅を有していることから、誘導された電流は入力波形の各サイクルでフックスゲート

10

20

30

40

50

鉄心を飽和状態へと駆動するのに充分大きいものとなる。外部磁界が検出され、外部磁界に付随する漂遊磁束の結果もたらされるフックスゲートコイルのインダクタンスに対する変化を測定することによって測定される。

#### 【0002】

フックスゲート鉄心が磁気的に飽和状態となった時点で、鉄心の透磁率は1に向かって降下し、フックスゲートコイルのインダクタンスはその当初の値の僅か数分の1にまで降下する。インダクタンスの急激な減少は、フックスゲートインダクタを横断して測定される通りの電圧の対応した降下をひき起こす。こうして、フックスゲートインダクタを横断する電圧信号を監視することにより、フックスゲート鉄心内の磁束密度が飽和状態に達する時点を、入力波形の交番サイクルとの関係において決定することができる。

10

#### 【0003】

フックスゲート鉄心内の磁束密度は、フックスゲートインダクタの中を流れる誘導通流及び外部磁界の存在に付随する何らかの漂遊磁束の両方の関数である。外部磁界成分は可変的であることから、フックスゲート鉄心を飽和状態へと駆動するのに必要な飽和電流  $I_{SAT}$  は、外部磁界の強度及び方向に応じて変動することになる。同様に、フックスゲートインダクタを横断する電圧波形は、フックスゲート鉄心が飽和状態に達した時点で崩壊することから、フックスゲート鉄心を飽和状態へと駆動する実際の飽和電流  $I_{SAT}$  は、入力電流波形に対し出力電圧波形を比較し入力電流波形の立上りと出力電圧波形の崩壊の間の遅延を測定することによって決定することができる。これらの測定された飽和電流変化に基づいて、外部磁界の絶対値及び方向を誘導することができる。

20

#### 【0004】

先行技術のフックスゲート磁力計は、定振幅の交流装置である。換言すると、入力電圧波形の各サイクル全体を通してフックスゲートインダクタの中を電流が流れている。指摘したとおり、飽和電流の絶対値は、フックスゲート鉄心が飽和状態に達するにつれてフックスゲートインダクタを横断する電圧波形の崩壊のタイミングを監視することによって誘導される。過去においては、これは、フックスゲート入力端と直列に抵抗器を設置し、フックスゲート出力端を接地することによって、標準的に達成してきた。直列抵抗は、回路が電圧波形による供給を受けるとき回路を通る電流が主としてフックスゲートコイルのインダクタンスではなく抵抗器によって決定されるように、フックスゲートインダクタのリアクタンスよりも何倍も大きくなるように選択される。フックスゲートコイルに対する入力端は同様に、フックスゲートインダクタを横断する電圧を監視する電圧比較器の1入力端にも接続される。この配置において、交流は、抵抗器とフックスゲートの組合せの中を連続的に流れ、従って、電力は抵抗器を横断して連続的に散逸される。

30

#### 【0005】

フックスゲートインダクタを横断する電圧は一般にインダクタ電流信号に追従するが、90°だけ先行する。一般に、磁力計回路は、各半サイクル中にフックスゲートコイルを飽和状態へと駆動するのに充分な振幅をもつ正弦波形によって駆動される。すでに指摘したように、フックスゲートを通る電流が飽和状態に達した時点で、コイルのインダクタンスは急激に降下し、こうしてフックスゲートを横断する電圧は、フックスゲート鉄心が飽和状態にとどまっている一方でほぼ0Vにまで降下する。フックスゲートを横断する電圧は、フックスゲート鉄心が飽和状態にとどまるかぎり、ほぼゼロに等しい状態にとどまることになる。しかしながら、フックスゲートは完璧なインダクタではないことから、コイル内の寄生抵抗及びインダクタンスは、フックスゲート鉄心が飽和状態にある間フックスゲート電圧にわずかな勾配をもたせることになり、明確なゼロ越えを確かめることができる。このゼロ越えは、フックスゲートの入力端に接続された比較器によって検出される。入力信号との関係におけるゼロ越えのタイミングから、飽和状態電流の絶対値を確認することができる。付加的な回路が、比較器の出力を入力電圧波形と比較し、ゼロ越えと入力電圧信号の間の関係を決定する。外部磁界の変動は飽和電流を変えることから、電圧波形の崩壊ひいては比較器により検出されるゼロ越えは、外部磁界の

40

50

絶対値及び方向に応じて、入力波形との関係において異なる時点で発生することになる。比較器出力信号と入力信号を比較することによって、外部磁界の絶対値及び方向を誘導することができる。

#### 【0006】

記述したとおり、先行技術のフックスゲート磁力計は、磁界の極端に線形で正確かつ雑音を排除した測定を提供する。フックスゲート磁力計の動作特性は、特にホール効果及び磁気抵抗装置に比べた場合、非常に有利である。しかしながら、このような装置がもつ重大な欠点は、その電力消費量が比較的大きいということにある。磁力計は定電流装置であることから、電力はこの装置によって継続的に散逸させられる。さらに装置に供給される電流は、フックスゲート鉄心を飽和させるのに充分でなくてはならず、標準的にこれは約数十ミリアンペアである。このことは、電力消費量の低いことが有意な設計基準である一部の利用分野にとっては重大な欠点でありうる。例えば、磁力計にバッテリから電力を供給しなければならない利用分野では、装置の電流消費量は、バッテリの寿命を保つため最低限に保たれなくてはならない。従って、無視できるほどの僅かな電流しか取り出すことなく、線形性、正確さ及び雑音排除性を含む従来のフックスゲート磁力計のプラスの特性を有する磁力計を提供することが望まれる。

10

#### 【0007】

##### 【発明の概要】

以上の背景に照らし合わせると、本発明の主たる目的は、外部磁界を検出し測定するための効率の良い、正確で低雑音の磁力計を提供することにある。

20

本発明によれば、可飽和鉄心フックスゲートインダクタのインダクタンスの変化を監視することにより外部磁界の強度及び方向を測定できる、可飽和鉄心フックスゲートインダクタをもつ磁力計が得られる。

#### 【0008】

本発明によれば、フックスゲートインダクタが比較的低周波数の交流電圧信号によって駆動される、フックスゲート磁力計が得られる。

本発明によれば、従来のフックスゲート磁力計によって消費される電力の数分の1の電力しか消費しない磁力計が得られる。

#### 【0009】

さらに本発明によれば、装置が取り出す電流が、5 Vの信号によって駆動されている場合に10  $\mu$  A未満でありうるフックスゲート磁力計が得られる。

30

これらの目的ならびに好ましい実施形態の詳細な説明を読んだ時点で明らかとなるその他の目的は、本書で開示する微小電力型フックスゲート磁力計によって満たされる。

#### 【0010】

本発明のフックスゲート磁力計は、外部磁界に付随する磁束の存在によってひき起こされるフックスゲートコイルのインダクタンスの変化を測定することによって外部磁界を測定する。フックスゲートは、公称100 Hzの方形波電圧信号によって駆動される可飽和鉄心インダクタを含んで成る。入力方形波は、入力信号の各サイクルでフックスゲートコアを磁気的に飽和させるのに充分な振幅をもつフックスゲートコイルを通して正弦波電流信号を生成する。フックスゲート出力端と大地の間にはコンデンサが接続されている。フックスゲートを通って流れる電流は入力波形の各サイクルでコンデンサを正弦的に充電及び放電し、電圧比較器は、コンデンサを横断する電圧に基づいて出力信号を生成する。好ましい実施形態においては、比較器はコンデンサを横断する電圧が入力電圧信号の振幅の1/2に達した時点で状態を変化する論理ゲートとして構成される。

40

#### 【0011】

比較器からの出力信号は入力信号に関係づけされるが、出力電圧信号の立上り及び立下りエッジのタイミングは、フックスゲートコイルのインダクタンスに起因して変えられる。外部磁界が全く存在しない場合、フックスゲートコイルを通しての伝搬遅延は、入力信号の立上りエッジ及び立下りエッジの両方について同じとなる。しかしながら、外部磁界が存在する場合、伝搬遅延は、立下りエッジと比較して信号の立上りエッジについて

50

異なるものとなる。

【0012】

比較器出力信号を入力電圧信号と比較し比較器出力信号の立上りエッジ及び立下りエッジの両方についての伝搬遅延を測定するために論理回路が提供される。論理回路は、2つのパルス幅被変調（PWM）信号を生成する。第1のPWM信号パルスのパルス幅は、立上りエッジ伝搬遅延に対応し、第2のPWM信号パルスのパルス幅は立下りエッジ伝搬遅延に対応する。

【0013】

立上りエッジと立下りエッジ信号の間のパルス幅の差を測定するために、パルス幅復調回路が提供される。復調器回路は、2つの信号のパルス幅の差に対応するアナログ電圧信号を生成する。2つの信号の間の相対的パルス幅は、外部磁界の強度及び方向に正比例することから、復調回路により生成されたアナログ信号は、外部磁界に正比例することなる。

【0014】

本発明の磁力計は、従来のフラックスゲート磁力計に比べはるかに少ない電流しか取り出さない。電流消費量は、フラックスゲートインダクタ及びコンデンサの配置に起因して減少している。入力電圧信号の立上りエッジでは、フラックスゲートを通る電流は、入力信号の最大電圧  $V_{DD}$  に向かってコンデンサを充電し始める。フラックスゲート鉄心が飽和状態に達した時点で、フラックスゲートのインダクタンスは、その当初の値の数分の1まで降下し、インダクタンスの降下は、フラックスゲートを通しての電流スパイクを結果としてもたらす。この電流スパイクは、コンデンサを  $V_{DD}$  まで急速に充電する。入力電圧サイクルのこの時点で、コンデンサ電圧の上昇は、フラックスゲート出力端と  $V_{DD}$  の間に接続されたショットキーダイオードによってクランプされることから、電流が  $V_{DD}$  から流れることはもはやない。このダイオードは、コイルの出力側の電圧が入力側の電圧に一致することから、ダイオードからフラックスゲートに至るまで、フラックスゲート電流がゼロまで減衰するまで、フラックスゲート電流を  $V_{DD}$  まで戻す。LC時間定数は、100Hzの入力電圧信号の半サイクルよりもはるかに短かい。このようにして、フラックスゲートは、入力波形の正の半サイクルの大部分を通じていかなる電流も消費しない。負の半サイクル中、コンデンサはフラックスゲートインダクタを通して放電し、そのため、付加的な電流が入力回路から取り出されることは全くない。こうして、磁力計により消費される電力は激烈に減少する。こうして、本発明は、バッテリ又は光起電力電源を必要とする利用分野に充分適している。本発明は同様に、従来ホール効果センサーが使用されてきた磁気ひずみトルク検知向け利用分野にも充分適している。このような利用分野では、本発明はトルク検知を必要とするポータブル式消費者製品及び磁界の存在を検知する必要があるその他のポータブル式装置にとって理想的である。

【0015】

【好ましい実施形態の詳細な説明】

本発明は、フラックスゲート磁力計、より特定的には、無視できるほどの量の電力しか消費しないフラックスゲート磁力計に関する。

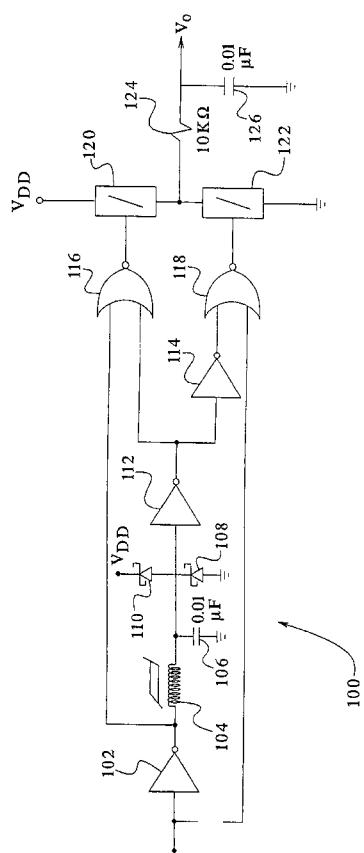

ここで図1を参照すると、微小電力型フラックスゲート磁力計回路が100として示されている。磁力計回路100の重要な要素としては、反転入力バッファ102；可飽和鉄心インダクタつまりフラックスゲート104；第1の0.01  $\mu$ Fのコンデンサ106；第1及び第2のショットキーダイオード108、110；反転出力バッファ112；第2の出力反転器114、第1及び第2のNORゲート116、118；第1及び第2のアナログスイッチ120、122；10kの抵抗器124；及び第2の0.01  $\mu$ Fのコンデンサ126が含まれる。

【0016】

物理的には、フラックスゲートインダクタ104は、外部磁界を測定すべき点の近くに位置づけされる。フラックスゲートコイル104は、外部磁界に付随する磁束がフラックスゲートインダクタの可飽和鉄心と相互作用することになるような形で方向づけされてい

10

20

30

40

50

る。磁力計回路 100 に対する入力端は、反転入力バッファ 102 と第 2 の NOR ゲート 118 の 1 つの入力端の両方を駆動する公称 100Hz の方形波電圧信号によって励起される。入力バッファ 102 は、入力電圧信号を反転させ、フラックスゲート回路を絶縁する。バッファ 102 の出力は、フラックスゲートインダクタ 104 及び第 1 の NOR ゲート 116 の 1 つの入力端を励起し、フラックスゲートインダクタ 104 の出力は、反転出力バッファ 112 を駆動する。第 1 の 0.01  $\mu$ F のコンデンサ 106 が、フラックスゲートインダクタ 104 の出力端と大地の間に接続されている。同様にして、第 1 のショットキーダイオード 108 と同じく、フラックスゲートインダクタ 104 出力端と大地の間に接続され、一方、直流供給電圧  $V_{DD}$  とフラックスゲートインダクタ 104 の出力端の間に第 2 のショットキーダイオード 110 が接続されている。反転出力バッファ 112 の出力は、第 2 の出力反転器 114 ならびに第 1 の NOR ゲート 116 に対する第 2 の入力端を駆動する。第 2 の出力反転器 114 の出力は、第 2 の NOR ゲート 118 の第 2 の入力端を駆動する。最後に、第 1 の NOR ゲート 116 の出力は、第 1 のアナログスイッチ 120 を駆動し、第 2 の NOR ゲート 118 の出力は第 2 のアナログスイッチ 122 を駆動する。

10

#### 【0017】

2 つのアナログスイッチ 120、122 は、3 状態スイッチとして動作するように構成されている。第 1 のアナログスイッチ 120 は、供給電圧  $V_{DD}$  を基準とし、第 2 のアナログスイッチ 122 は、大地を基準とする。2 つのアナログスイッチ 120、122 の出力端は互いに接続され、10k $\Omega$  の抵抗器 124 及び第 2 の 0.01  $\mu$ F コンデンサ 126 を含む低域フィルタに入力される。フィルタ網の出力は、フラックスゲートインダクタ 104 が中に浸漬されている外部磁界の強度に比例するアナログ電圧信号  $V_0$  を提供する。

20

#### 【0018】

動作中、反転入力バッファ 102 から出力された反転電圧信号はフラックスゲートインダクタ 104 を駆動する。この対称的方形波電圧信号は 0V と供給電圧  $V_{DD}$  の間で交番する。フラックスゲートインダクタ 104 は、磁気的に可飽和の鉄心を伴って構築されている。フラックスゲートに入力された方形波電圧信号は、鉄心を飽和させるのに充分なフラックスゲートインダクタ 104 を通る正弦波電流を誘導する。フラックスゲート鉄心を飽和させるしきい飽和電流  $I_{SAT}$  は、フラックスゲートインダクタの物理的構築によって決定され、フラックスゲート鉄心の近くに外部磁界に付随する付加的な磁束が存在することによって影響される。

30

#### 【0019】

入力電圧信号が 0V から  $V_{DD}$  まで遷移するにつれて、フラックスゲートインダクタ及びコンデンサを通る電流は、LC 回路に標準的な正弦的要領で増大する。フラックスゲートインダクタ 104 を通る電流が増加するにつれて、鉄心内の磁束密度も同様に増大する。鉄心内の磁束密度が飽和磁束密度を上回るにつれて、鉄心の相対的透磁率は 1 に向かって降下し、フラックスゲートコイルのインダクタンスの対応する降下をひき起こす。鉄心が飽和される一方で、フラックスゲートコイルのインダクタンスは、その不飽和値のわずか数分の 1 にとどまる。このインダクタンスの降下と共に、フラックスゲートを通る電流の変化速度は、急激に増大し、フラックスゲート 104 を通る電流スパイクをひき起こす。

40

#### 【0020】

フラックスゲート 104 に入力された電圧信号が 0V から  $V_{DD}$  まで遷移するとき、フラックスゲートを通る電流は、充電用コンデンサ 106 に向かって進む。フラックスゲート鉄心内の磁気 FD が飽和状態に達したとき、フラックスゲート 104 の出力電流内の対応するスパイクは急速にコンデンサ 106 を  $V_{DD}$  まで充電する。フラックスゲート 104 及びコンデンサ 106 の出力端に接続された反転出力バッファ 112 は、コンデンサ 106 を横断する電圧を監視する比較器として動作する。反転出力バッファ 112 の出力端は、コンデンサ 105 を横断する電圧が  $1/2 V_{DD}$  より低いとき論理 1 ( $V_{DD}$ ) にセットされることになる。換言すると、反転出力バッファ 112 の出力端は、コンデンサ 106 上の電圧が  $1/2 V_{DD}$  より大きいとき論理 0 (0.0V) にセットされることになる。フラック

50

スゲートインダクタ 104 とコンデンサ 106 の L C 組合せの共振エクスカーションから反転出力バッファ 112 の入力端を保護するためフラックスゲート 104 の出力端にショットキーダイオード 108、110 が付加される。

【0021】

以上で記述したことから、フラックスゲートインダクタ 104 へ入力される電圧信号が 0 V から  $V_{DD}$  まで遷移するにつれて、コンデンサ 106 は 0.0 V から  $V_{DD}$  に向かって共振的に充電し始める事になるということは明白である。コンデンサ 106 が充電を開始する速度は、フラックスゲートコイル 104 のインダクタンスによって左右されることになる。コンデンサ 106 を横断する電圧が  $1/2 V_{DD}$  未満である一方で、反転出力バッファ 112 の出力端は論理 1 つまり  $V_{DD}$  にセットされる。フラックスゲートインダクタ 104 の鉄心が飽和に達するにつれて、対応する出力電流スパイクは急速にコンデンサ 106 を  $V_{DD}$  まで充電し、反転出力バッファ 112 の  $1/2 V_{DD}$  しきい値を超える。こうして、鉄心が飽和に達した時点で、バッファ 112 の出力端は、ほぼ瞬時に論理 0 まで降下する。しかしながらこの遷移は、入力信号の正の遷移より、測定可能な時間的遅延だけ遅れる。この遅延の長さは、フラックスゲートコイル 104 のインダクタンス及びフラックスゲート鉄心と相互作用している可能性のあるあらゆる外部磁界の磁束密度の一関数である。

【0022】

類似の現象は、フラックスゲート 104 に入力された電圧信号が  $V_{DD}$  から 0.0 V まで遷移するにつれて発生する。正の半サイクル上で、コンデンサ 106 は、入力信号の電圧と整合する  $V_{DD}$  まで充電する。コンデンサ 106 上の電圧がひとたび  $V_{DD}$  に達した時点で、正パルスの残りの部分についていかなる電流もフラックスゲートインダクタ 104 の中を流れない。しかしながら入力信号が  $V_{DD}$  から 0.0 V まで遷移した時点で、フラックスゲート 104 の出力側の電圧は、入力側に印加された 0.0 V よりも大きくなる。コンデンサ 106 を充電する順方向電流の場合と同様に、フラックスゲートインダクタ 104 を通って流れる逆方向放電電流は、反対方向で飽和状態に達する。ここでもまた、コイルのインダクタンスは急激に降下し、フラックスゲート 104 を通る逆方向電流スパイクを引き起こす。この逆方向電流スパイクは、急速にコンデンサ 106 を放電させ、コンデンサ 106 を横断する電圧をほぼ即座に 0.0 V まで引き降ろす。コンデンサ 106 上の電圧が  $1/2 V_{DD}$  のしきい値を通過して降下するにつれて、反転出力バッファ 112 の出力端は、論理 0 から論理 1 つまり  $V_{DD}$  まで遷移する。コンデンサ 106 は、放電サイクル中、コンデンサ 106 を横断する電圧がほぼ  $1/2 V_{DD}$  に等しいときに飽和電流  $I_{SAT}$  が発生するような形でサイズ決定される。正の半サイクルの立上りエッジの場合と同様に、 $V_{DD}$  から 0.0 V までの入力信号の遷移と論理 0 から論理 1 までのバッファ 112 の出力の遷移の間の遅延は、フラックスゲートコイル 104 のインダクタンスによって左右され、外部磁界の存在によって影響される。

【0023】

指摘した通り、反転出力バッファ 112 の出力端は、NOR ゲート 116 の 1 つの入力端に直接接続され、反転入力波形駆動のフラックスゲート 104 はもう 1 つの入力端に接続されている。この組合せの結果、入力波形の各パルスの立上りエッジに対応する一連の論理パルスがもたらされる。NOR ゲート 116 から出力された各パルスの幅は、各入力パルスの立上りエッジと出力バッファ 112 の 0.0 V から  $V_{DD}$  までの正の遷移の間の時間的遅延に対応する。

【0024】

NOR ゲート 116 の 1 つの入力端に加えて、出力バッファ 112 は同様に第 2 の出力反転器 114 も駆動する。反転器 114 は、バッファ 112 の反転された出力を第 2 の NOR ゲート 118 の 1 つの入力端に適用する。磁力計回路 100 に入力された反転されていない方形波信号は、NOR ゲート 118 のもう 1 つの入力端に適用される。NOR ゲート 118 は、入力方形波パルスの立下りエッジに対応パルス列を出力する。NOR ゲート 118 から出力された各パルスの幅は、入力波形の各パルスの立下りエッジと出力バッファ 112 の出力波形の立下りエッジの間の時間的遅延に対応する。こうして、NOR ゲー

10

20

30

40

50

ト 116、118 から出力されたパルスの幅は、フラックスゲートインダクタ 104 を通る入力方形波信号の立上りエッジと立下りエッジの両方の伝搬遅延に対応する。

【0025】

周囲条件下で、いかなる外部磁界も存在しないとき、フラックスゲート 104 の鉄心を磁気的に飽和するのに必要とされる飽和電流  $I_{SAT}$  は、前方向及び逆方向の両方向において等しいものとなる。こうして、フラックスゲート 104 を通るインダクタンスひいては伝搬遅延は、入力電圧信号の立上りエッジ及び立下りエッジの両方について同じとなる。このことは、NOR ゲート 116、118 から出力されたパルス列において明白である。フラックスゲート鉄心 104 と相互作用する外部磁界が全く存在しない場合、NOR ゲート 116 から出力された各パルスのパルス幅は、NOR ゲート 118 から出力されたパルスのパルス幅と等しい。しかしながら、この対称性は、ひとたび外部磁界が導入されると、あてはまらない。

【0026】

入力電圧方形波の各々の半サイクルで、フラックスゲートインダクタ 104 を横断する電圧極性は逆転される。こうして、フラックスゲートを通る電流は、フラックスゲート鉄心内の磁束と同様、入力電圧信号の各半サイクルで逆転する。外部磁界が導入された時点で、この外部磁界に付随する磁束は、入力波形の半サイクル中、誘導された磁束に加わり、反対の半サイクル中、誘導された磁束から差引かれる。誘導された磁束とのこの相互作用は、フラックスゲートコイルを飽和状態に駆動するのに必要な飽和電流  $I_{SAT}$  を変化させる。しかしながら、外部磁界がもつ指向性に起因して、 $I_{SAT}$  の変化は、フラックスゲートインダクタ 104 を横断した順方向及び逆方向で異なっている。例えば、外部磁界が、入力波形の正の半サイクル中、フラックスゲート鉄心内に誘導された磁束の方向に平行である場合、フラックスゲート鉄心は、いかなる外部磁界も存在しない場合に比べ早く飽和状態に達することになる。このことは、順方向での飽和電流の減少を導く。換言すると、逆方向では、外部磁界の相対する磁束を克服するのにさらに大きな逆方向電流が必要である。こうして逆方向での飽和電流の増大が導かれる。

【0027】

順方向及び逆方向の飽和電流の変化は、フラックスゲートを通しての伝搬遅延に影響を及ぼす。磁力計回路 100 に入力された方形波信号は、フラックスゲートに入力される前に反転させられることから、入力波形の負の半サイクル中、フラックスゲートインダクタ内には順方向電流が誘導される。こうして、コンデンサ 106 は、入力信号が  $V_{DD}$  から 0 V まで遷移するとき、充電を開始する。以上で記述した例では、外部磁界は、順方向飽和電流が低下するような形で方向づけされる。このことはすなわち、フラックスゲート鉄心が、そうでなければ周囲条件下で見られるよりも入力電圧サイクル内のさらに早い時期に飽和状態に達することになり、こうしてコンデンサ 106 を横断する電圧が  $1/2 V_{DD}$  のしきい値を同じく比較的早く越えるようにしているということを意味している。究極的には、入力信号の負の遷移は、そうでなければ周囲条件下で見られるよりも早い時期に出力バッファ 112 の出力端において記録される。単純に推定すると、順方向の伝搬遅延は減少させられる。

【0028】

換言すると、入力波形の正の半サイクル中、フラックスゲート 104 内に逆方向電流が誘導される。コンデンサ 106 は、入力信号が 0 V から  $V_{DD}$  まで遷移するときに、放電を開始する。外部磁界は、逆方向飽和電流を上昇させるという影響をもつことから、フラックスゲート鉄心は、他の場合に比べ入力波形の正の半サイクル内のさらに遅い時点まで飽和状態とはならないことになる。こうして、コンデンサ 106 を横断する電圧は、周囲条件下で見られるよりもさらにサイクル内の遅い時点で  $1/2 V_{DD}$  しきい値より低く降下する。従って、入力信号の正の遷移は、同様に比較的遅い時点で出力バッファ 112 の出力端において記録される。換言すると、逆方向伝搬遅延は増大させられる。

【0029】

外部磁界の方向が逆転させられたならば、磁界の結果をもたらされる順方向及び逆方向

10

20

30

40

50

の伝搬遅延に対する変更も同様に逆転させられる。換言すると、順方向遅延は増大し、逆方向遅延は減少することになる。

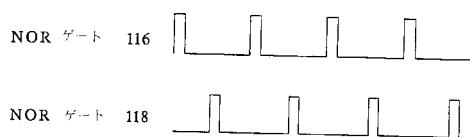

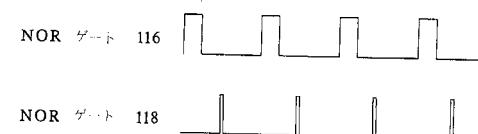

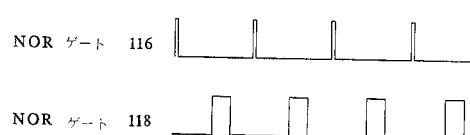

前述のとおり、順方向及び逆方向伝搬遅延におけるこれらの変化は、NORゲート116、118から出力された2つのパルス列のパルス幅を変える。図2では、さまざまな条件について、NORゲート116、118のための2つの出力パルス列が示されている。図2aは、ブラックスゲート104と相互作用する外部磁界が全く存在しない周囲条件下での出力パルス列を示す。図2bは、外部磁界が存在するときの同じ出力パルス列を示す。図2bでは、外部磁界は、インダクタ電流が正の方向に流れているとき外部磁束密度が誘導された磁束密度に対し付加的なものである1つの方向に、方向づけされている。最後に、図2cは、インダクタ電流が逆方向に流れているとき、外部磁束密度が誘導された磁束密度に対し付加的なものとなるような形で外部磁界が方向づけされている場合の出力パルス列を示す。

#### 【0030】

ここでわかるように、図2aの周囲条件下では、NORゲート116及び118から出力されたパルスは同じ幅を有する。しかしながら図2bでは、順方向伝搬遅延は減少し、逆方向伝搬遅延は増大している。従って、NORゲート118から出力されたパルス列のパルス幅は、NORゲート116から出力されたパルス列のパルス幅よりもはるかに狭い。同様にして、図2cは、外部磁界が図2bの場合と反対の方向に方向づけされている反対の条件を示している。図2cでは、順方向伝搬遅延は増大し、逆方向伝搬遅延は減少する。この場合、NORゲート116からの出力パルスのパルス幅は、NORゲート118からのより広い出力パルスよりもはるかに狭い。NORゲート116、118の出力は、実際には、2つの信号のパルス幅が外部磁界の強度及び方向によって決定されるパルス幅被変調信号である。

#### 【0031】

本発明の磁力計は、NORゲート116、118から出力された信号を復調し、2つの信号のパルス幅の差に比例するアナログ電圧信号を生成することによって、外部磁界を測定する。これらの信号を復調するための好ましい方法としては、アナログスイッチ120、122及び、10kの抵抗器124及び0.01μFのコンデンサ126を含む低域フィルタが含まれる。NORゲート116の出力は、アナログスイッチ120へと入力され、NORゲート122の出力はアナログスイッチ122に入力される。スイッチ120は供給電圧V<sub>DD</sub>を基準とし、スイッチ122は大地を基準としている。2つのスイッチの出力端は、合わせて低域フィルタに接続されこれに入力される。この構成においては、2つのアナログスイッチ120、122は3状態スイッチとして作用する。スイッチ120に対する入力が高いとき、スイッチ120が導通状態となり、V<sub>DD</sub>は低域フィルタに入力される。スイッチ122への入力が高い場合、スイッチ122が導通状態となり、大地電位がフィルタに印加される。そうでなければ、アナログスイッチ120、122は非導通状態である。NORゲート116から出力されたパルスは入力方形波パルスの立上りエッジに対応し、NORゲート118から出力されたパルスは、入力方形波パルスの立下りエッジに対応することから、スイッチ120、122に対する入力は、入力波形の各サイクルと共に交番することになる。こうして、低域フィルタに対する入力端は、入力波形の各パルスに伴って、まずはV<sub>DD</sub>に、次に大地に交番して接続されることになる。スイッチ120が導通状態にある間隔中、コンデンサ126が、V<sub>DD</sub>に向かって充電を開始することになる。同様にして、スイッチ122が導通状態にある間隔中、コンデンサ126は大地に向かって放電し始めることになる。コンデンサ126及び抵抗器124は、フィルタのRC時定数がNORゲート116、118から出力されたパルスの持続時間よりもはるかに大きくなるようにサイズ決定される。従って、いずれかのスイッチが導通状態にある間に発生するコンデンサ126の充電及び放電量は非常に少ない。

#### 【0032】

周囲条件下で、両方のスイッチ120、122に対する入力パルスの幅は、同じ持続時間を持つことになる。こうして、各サイクルで、スイッチ120は、スイッチ122と

10

20

30

40

50

同じ長さの時間だけ導通状態となり、従って、コンデンサ 126 は、大地に向かってそれが放電しているのと同じ長さの時間だけ  $V_{DD}$  に向かって充電することになる。その結果、コンデンサ 126 を横断する平均電圧は  $1/2 V_{DD}$  に等しくなる。

#### 【0033】

磁界が存在する場合、NOR ゲート 120、122 から出力されたパルスはもはや対称ではない。外部磁界が第 1 の方向に方向づけされている状態で、NOR ゲート 116 から出力されたパルスは、NOR ゲート 118 から出力されたものよりも長い持続時間を持つ。入力波形の各サイクル中、アナログスイッチ 120 は、スイッチ 122 よりも長い持続時間にわたり導通状態となる。このことはすなわち、コンデンサ 126 が、入力波形の各サイクル中放電よりも充電の方にわずかに多くの時間を費やすということを意味している。この結果、コンデンサ 126 を横断する平均電圧降下は、 $1/2 V_{DD}$  よりも大きくなる。外部磁界が第 1 の方向とは  $180^\circ$  反対側の第 2 の方向に方向づけされているならば、NOR ゲート 118 からの出力パルスは、NOR ゲート 116 から出力されたものよりも長い持続時間をもつことになる。従って、アナログスイッチ 122 は、アナログスイッチ 120 よりも長い持続時間にわたり導通状態にある。このことはすなわち、コンデンサ 126 が入力波形の各サイクル中充電よりも放電の方にわずかに多くの時間を費やすことを意味している。この結果、コンデンサ 126 を横断する平均電圧降下は  $1/2 V_{DD}$  未満となる。

#### 【0034】

外部磁界がいずれかの方向により強いものとなるにつれて、アナログスイッチ 120、122 のうちのいずれか一方が、もう一方のアナログスイッチに比べ増え長い時間だけ導通状態となる。こうして、コンデンサ 126 を横断して発生した出力電圧信号は、 $V_{DD}$  に向かって高い方に、又は大地に向かって低い方に駆動されることになる。その結果、外部磁界の強度及び方向に比例するアナログ信号がもたらされる。このアナログ信号は、外部磁界の測定値を提供するべく、従来の電圧計又はその他の何らかの装置を駆動するために使用することができる。

#### 【0035】

図 1 に示されている回路は、先行技術のフラックスゲート磁力計によって消費される電力のわずか数分の 1 しか消費しない。例えばフラックスゲートコイル 104 とコンデンサ 106 を含む回路の検知部分は、低い電力消費のために特定的に設計することができる。周波数  $f$  及び  $V_{DD}$  に等しい振幅をもつ交番信号によって駆動される場合、回路が  $1/2 V_{DD}^2 * 0.01 \mu F * f$  に等しい電力量を消費することを示すことができる。こうして、消費される電力の量は、入力波形のクロック速度を低減させ、 $V_{DD}$  の値を低減させかつコンデンサ 106 のキャパシタンスを低減させることによって最小限にすることができる。しかしながら、共振 L C サイクル中、コンデンサ 106 を横断する電圧がおよそ  $1/2 V_{DD}$  に等しいとき、フラックスゲートコイル 104 を通る電流が飽和電流  $I_{SAT}$  に達するような形でコンデンサ 106 をサイズ決定することも同様に必要である。これは、コンデンサ 106 のキャパシタンスをほぼ  $I_{SAT} L / V_{DD}^2$  に等しくセットすることによって達成できる。従って、コンデンサ 106 のサイズがこのように制約された状態で、回路の電力消費を低減させるためのオプションは、入力波形の周波数を変えることに縮約される。好みの実施形態においては、コンデンサ 106 =  $0.01 \mu F$ 、 $V_{DD} = 5 V$ 、そして入力周波数 =  $100 Hz$  である。こうした回路が構築されテストされ、 $7 \mu A$  の電流ひき取り出しという結果をもたらした。クロック周波数がさらに  $50 Hz$  まで低減され入力信号の振幅が  $3 V$  まで低減された状態で、電流降下は、 $5 \mu A$  までさらに一層減少した。このような低い電流取り出しが、回路を、バッテリ又は光起電力電源に基づいて動作する利用分野といったような、低電力磁力計を必要とする利用分野のために特に適したものにする。

#### 【0036】

当業者にとっては、本明細書に記述した現在好まれている実施形態に対するさまざまな変更及び修正が明白であるということを理解すべきである。このような変更及び修正は、本発明の精神及び範囲から逸脱することなく、かつその付随する利点を低減させることな

10

20

30

40

50

く加えることができる。従って、このような変更及び修正も添付の請求の範囲によって網羅することが意図される。

【図面の簡単な説明】

【図1】 本発明の好ましい実施形態に従った微小電力型磁力計回路の概略図である。

【図2】 図1に描かれているNORゲート116、118からのパルス幅被変調出力信号を示す。

【図2a】 外部磁界が全く存在しない場合の2つの信号を示す。

【図2b】 外部磁界が存在し、第1の方向に方向づけされている場合の2つの信号を示す。

【図2c】 外部磁界が存在し、図2b中の磁界の向きと180°反対の第2の方向に方向づけされている場合の2つの信号を示す。 10

【符号の説明】

100 磁力計回路

102 反転入力バッファ

104 可飽和鉄心インダクタ

106、126 コンデンサ

108、110 ショットキーダイオード

112 反転出力バッファ

114 第2の出力反転器

116、118 NORゲート

120、122 アナログスイッチ

124 抵抗器

20

【図1】

【図2a】

【図2b】

【図2c】

---

フロントページの続き

審査官 藤原 伸二

(56)参考文献 特開平05-034426 (JP, A)

特開平04-024574 (JP, A)

特開平09-166437 (JP, A)

特開平09-061506 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G01R 33/00-33/26