(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5224633号

(P5224633)

(45) 発行日 平成25年7月3日(2013.7.3)

(24) 登録日 平成25年3月22日(2013.3.22)

|                        |                 |

|------------------------|-----------------|

| (51) Int.Cl.           | F 1             |

| HO4N 5/357 (2011.01)   | HO4N 5/335 570  |

| HO1L 21/8234 (2006.01) | HO1L 27/08 102B |

| HO1L 27/088 (2006.01)  | HO1L 27/14 A    |

| HO1L 27/146 (2006.01)  | HO1L 31/10 A    |

| HO1L 31/10 (2006.01)   |                 |

請求項の数 5 (全 17 頁)

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2004-99346 (P2004-99346)    |

| (22) 出願日  | 平成16年3月30日 (2004.3.30)        |

| (65) 公開番号 | 特開2005-286168 (P2005-286168A) |

| (43) 公開日  | 平成17年10月13日 (2005.10.13)      |

| 審査請求日     | 平成19年3月29日 (2007.3.29)        |

| 審判番号      | 不服2012-7481 (P2012-7481/J1)   |

| 審判請求日     | 平成24年4月23日 (2012.4.23)        |

|           |                                            |

|-----------|--------------------------------------------|

| (73) 特許権者 | 000001007<br>キヤノン株式会社<br>東京都大田区下丸子3丁目30番2号 |

| (74) 代理人  | 100076428<br>弁理士 大塚 康徳                     |

| (74) 代理人  | 100112508<br>弁理士 高柳 司郎                     |

| (74) 代理人  | 100115071<br>弁理士 大塚 康弘                     |

| (74) 代理人  | 100116894<br>弁理士 木村 秀二                     |

| (74) 代理人  | 100130409<br>弁理士 下山 治                      |

| (74) 代理人  | 100134175<br>弁理士 永川 行光                     |

最終頁に続く

(54) 【発明の名称】半導体装置の製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

埋め込みチャネル型の第一導電型MOSトランジスタと表面チャネル型の第一導電型MOSトランジスタと共に備えた半導体装置の製造方法であって、前記埋め込みチャネル型のMOSトランジスタ及び表面チャネル型のMOSトランジスタのチャネル部に第一導電型の不純物領域を同一工程で形成する工程と、前記第一導電型の不純物領域を形成した後に、前記表面チャネル型のMOSトランジスタのチャネル部に、第二導電型の不純物領域を前記第一導電型の不純物領域を形成した位置より表面に近い領域に形成する工程とを含むことを特徴とする半導体装置の製造方法。

## 【請求項 2】

前記第一導電型の不純物領域を形成する際のドーズ量は、前記第二導電型の不純物領域を形成する際のドーズ量よりも少ないことを特徴とする請求項1に記載の半導体装置の製造方法。

## 【請求項 3】

前記第一導電型がn型であることを特徴とする請求項1又は2に記載の半導体装置の製造方法。

## 【請求項 4】

前記第一導電型の不純物領域の形成に、砒素を用いることを特徴とする請求項3に記載の半導体装置の製造方法。

## 【請求項 5】

更に、光電変換部を形成する工程を含むことを特徴とする請求項1から4のいずれか1項に記載の半導体装置の製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置とそれを用いた固体撮像装置その中でも特にC M O Sイメージセンサーとそれらの製造方法に関する。 10

【背景技術】

【0002】

固体撮像装置の代表的なものには、ホトダイオードおよびC C DシフトレジスタからなるC C Dセンサと、ホトダイオードおよびM O SトランジスタからなるA P S(Active Pixel Sensor)等のC M O Sセンサと呼ばれるものがある。 10

【0003】

A P Sは、1画素毎にホトダイオード、M O Sスイッチ、ホトダイオードからの信号を増幅するための増幅回路などを含み、「X Yアドレッシング」や「センサと信号処理回路の1チップ化」などが可能といった多くのメリットを有している。しかし、その一方で1画素内の素子数が多いことから、画素開口率の小さいことや、光学系の大きさを決定するチップサイズの縮小化が困難であり、市場の大部分をC C Dが占めている。 10

【0004】

近年は、M O Sトランジスタの微細化技術の向上と「センサと信号処理回路の1チップ化」や「低消費電力化」などの要求の高まりから、注目を集めている。 20

【0005】

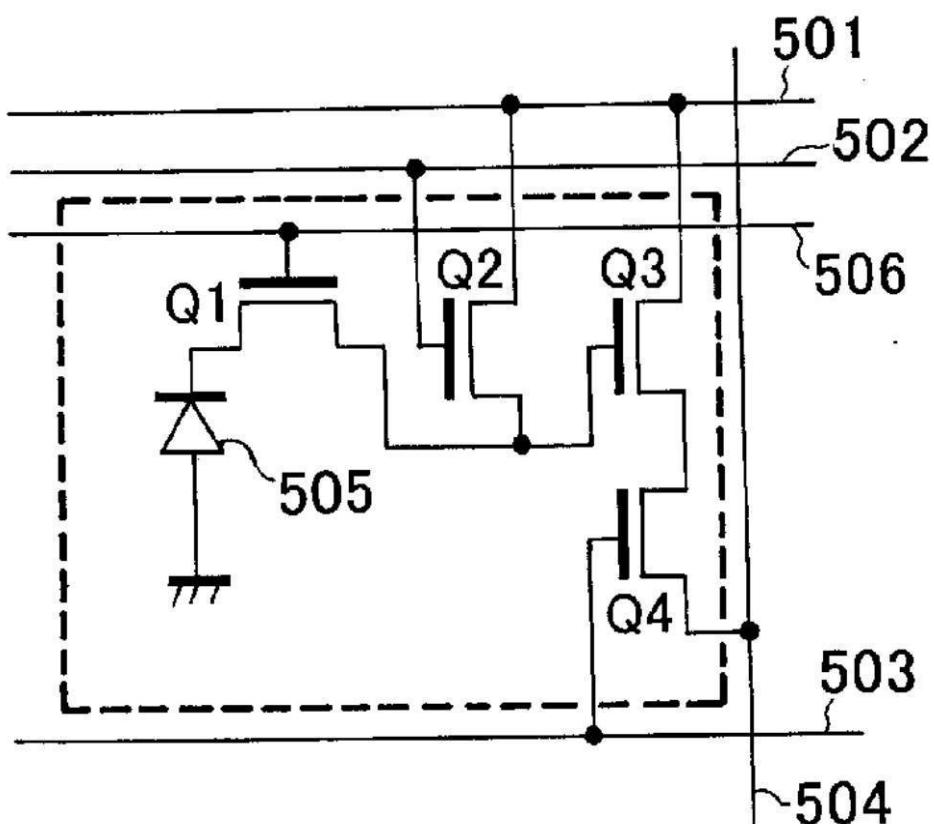

図5に従来のA P Sの等価回路図を示す(例えば、特許文献1参照)。従来技術の構成を以下簡単に説明する。

【0006】

501が電源線、502がリセットトランジスタを選択するリセットスイッチ線、503が選択トランジスタを選択する選択スイッチ線、504が信号出力線、505が光電変換部としてのホトダイオード、506が転送トランジスタを選択するための転送スイッチ線、Q1が転送トランジスタ、Q2がリセットトランジスタ、Q3が選択トランジスタ、Q4が増幅用のトランジスタである。光電変換部は、C M O SやC C D等で用いられている埋め込み型のホトダイオードである。埋め込み型のホトダイオードは、表面に濃い不純物濃度領域(例えばp層)を設けることで、S i O<sub>2</sub>面で発生する暗電流を抑制し、また、蓄積部(例えばn層)と表面のp層との間にも接合容量を設けることができ、ホトダイオードの飽和電荷量を増やすことができる。 30

【0007】

光電変換部505で蓄積した光信号電荷Q<sub>sig</sub>をM O Sトランジスタからなる転送部Q1を介し、浮遊拡散領域(Floating Diffusion Area)に読み出す。Q2は浮遊拡散領域の電位をリセットするためのトランジスタである。

【0008】

この浮遊拡散領域の容量C F Dにより、信号電荷Q<sub>sig</sub>/C F Dに電圧変換し、ソースフォロワ回路Q3を通して信号を読み出す。Q4は行選択のための選択スイッチである。 40

【0009】

また、リセットトランジスタ、転送トランジスタとして埋め込みチャネル型のM O Sトランジスタを用いた固体撮像装置がある(例えば、特許文献2参照)。

【特許文献1】特開平11-274454号公報

【特許文献2】特開2001-309243号公報

【発明の開示】

【発明が解決しようとする課題】

【0010】

しかしながら従来技術においては、ソースフォロア部のトランジスタ部で生じる1/f 50

ノイズのために出力電圧にノイズ成分がのってくるという問題点があった。そのためにソースフォロア部を埋め込み型のpMOSトランジスタで形成する方法等があるがプロセス的に複雑になりコスト増大の要因になる。また固体撮像装置に限らず、チップ内に表面チャネル型MOSトランジスタと、埋め込みチャネル型トランジスタとを併存させて用いる場合には、その製造プロセスが複雑となるという問題があった。

【0011】

そこで本発明は、制御性の高いトランジスタを簡易プロセスで形成することにより、ノイズの少ない半導体装置とその製造方法を提供することを目的とする。

【課題を解決するための手段】

【0012】

上述の課題を解決するため、本発明の固体撮像装置は、光電変換部と、前記光電変換部の電荷に基づく信号を増幅する増幅MOSトランジスタとを含む画素を有する固体撮像装置であって、前記増幅MOSトランジスタが埋め込みチャネル型であることの特徴とする。

【0013】

さらには、第一導電型がn型であることを特徴とし、第一導電型のチャネルドープ層は砒素であることが好ましい。こうすることで、制御性が高い半導体装置を形成できる。

【0014】

さらに、埋め込みチャネル型の第一導電型MOSトランジスタと表面チャネル型の第一導電型MOSトランジスタを共に有し、表面近傍に第一導電型のチャネルドープ層を前記埋め込みチャネル及び表面チャネル型のMOSトランジスタの両方にイオン注入法によって1つの工程で作成することを特徴とし、制御性の高いトランジスタを簡易プロセスで形成できるためコストの安い且つノイズの少ない半導体装置を提供できる。

【発明の効果】

【0016】

また埋め込みチャネル型の第一導電型MOSトランジスタと表面チャネル型の第一導電型MOSトランジスタを共に有し、表面近傍に第一導電型のチャネルドープ層を埋め込みチャネル及び表面チャネル型のMOSトランジスタの両方にイオン注入法によって作成することで、制御性の高いトランジスタを1つの工程で形成できるため、コストの安い且つノイズの少ない半導体装置を提供できる。

【発明を実施するための最良の形態】

【0017】

次に、本発明の最良の形態について図面を参照して、固体撮像装置を例にあげて説明する。

【0018】

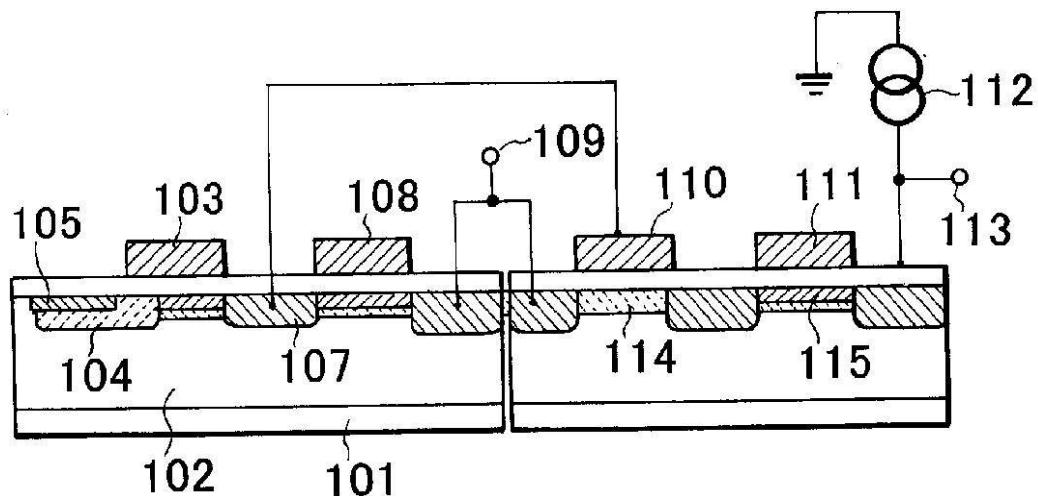

図1は、本発明の特徴を最も良く表した断面構造図である。図1において、光電変換素子は、n型基板101上に、p型ウエル102を形成し、その上に薄いn型層を形成しさらにホトダイオードのn層104を形成し、その上に埋め込み領域となるp層105を形成し、転送MOSトランジスタのゲート領域103を絶縁層を介してホトダイオード側面に形成する。

【0019】

また、転送MOSトランジスタのゲート領域103の側面下部に拡散浮遊領域FD107が形成されており、該拡散浮遊領域FD107は出力回路の増幅用MOSトランジスタのゲートに接続され、増幅用MOSトランジスタのソースには、行選択スイッチ用MOSトランジスタ111のドレインが接続され、行選択スイッチ用MOSトランジスタ111のソースには増幅用MOSトランジスタの負荷となる電流源112が接続されてソースフォロワ增幅回路を構成している。このソースフォロアのトランジスタ110に埋め込み型MOSトランジスタを使用し1/fノイズを減少させる。ここで埋め込み型MOSトランジスタとは、ソース・ドレイン領域と同じ導電型の不純物領域がゲート直下のチャネル領域にも形成されたMOSトランジスタである。

10

20

30

40

50

## 【0020】

また、該拡散浮遊領域F D 1 0 7には、該拡散浮遊領域F D 1 0 7のリセット用のリセットM O Sトランジスタ1 0 8のソースが接続され、そのドレインはリセット電源1 0 9が接続されている。ソースフォロアトランジスタ以外のM O Sトランジスタはここでは例えば閾値電圧0 . 4 Vの表面チャネル型M O Sトランジスタである。

## 【0021】

次に、読み出し動作を説明しながら、本発明の特徴を詳しく説明する。光が入射し、光電変換により生成された電子がホトダイオードのn層に蓄積する。この時、転送M O SトランジスタはO F F状態にある。所定の蓄積時間が経過したのち、転送M O Sトランジスタの制御電極（ゲート領域）1 0 3に正の電圧を印加し、転送M O SトランジスタをO N状態にし、ホトダイオードのn層の蓄積電荷を拡散浮遊領域に転送する。転送M O SトランジスタをO N状態にする前に、予め、拡散浮遊領域を所定の電圧にリセットしておく。蓄積電荷が拡散浮遊領域に転送されると、拡散浮遊領域の電圧は、転送電荷Q sigと拡散浮遊容量C F Dを用いると、転送電荷が電子であるため、Q sig / C F D分の電圧がリセット電圧から低下する。ホトダイオードの蓄積層がp型であるならば、転送電荷は正孔であるため、逆に電圧は上昇する。

10

## 【0022】

この様なA P Sにおいては、拡散浮遊領域1 0 7のリセット直後の出力信号V r1を一旦保持し、リセット信号にQ sig / C F D分だけ重畠された出力信号V sig1との差分（V sig1 - V r1）をとることやソースフォロアM O Sトランジスタを埋め込み型M O Sトランジスタにすることで、拡散浮遊領域1 0 7のリセットノイズ等のノイズ成分の大部分を除去することができる。特に、ホトダイオードと転送M O Sトランジスタ1 0 3が以下に述べる条件を満たすことが、より高いノイズの除去率を達成する。即ち、ホトダイオードのn層に蓄積された信号電荷をより高い割合で読み出すことが重要である。

20

## 【0023】

詳しく説明すると、信号を読み出し後のリセット電圧から、Q sig / C F Dの電圧だけ低下した拡散浮遊領域の電圧をV F D sig1とし、転送M O Sトランジスタが充分なO N状態であるならば、ホトダイオードのn層には、p型のウエルと表面の濃いp層のG N D電位に対しV F D sig1の逆バイアスが印加される。この時n層には、p型のウエルと表面の濃いp層から空乏層が延び、ホトダイオードのn層全体を空乏化することで、ホトダイオードに信号電荷を殆ど残さずに拡散浮遊領域に信号電荷を読み出すことができる。この場合、拡散浮遊領域に信号電荷を読み出すのと同時に、ホトダイオードのリセットも行っている。読み出し後、即ちホトダイオードのn層にV F D sig1の逆バイアスが印加された状態で、n層に残る電子数が0個ならば、リセット直後の出力信号V r1とリセット信号にQ sig / C F D分だけ重畠された出力信号V sig1との差分をとることでリセットノイズを完全に除去することができ、V sig1 - V r1 = Q sig / C F D × A（Aは画素毎にある出力回路のゲイン）という出力信号を得ることができる。

30

## 【0024】

この出力信号に1 / fノイズ等の画素毎にある出力回路のノイズV n1が重畠され、最終的なエリアセンサとして形成された集積回路I Cからの出力には、画素毎の出力回路以後の読み出し系のノイズV n2が重畠される。

40

## 【0025】

以上の様な読み出しを実現するためには、ホトダイオードのn層に逆バイアスを印加し、n層全体が空乏化しはじめる電圧をV depとすれば、V dep < V sig1とする必要がある。ここでホトダイオードの空乏化電圧とは、広くは、蓄積部の蓄積電荷数 < ネット不純物数となる逆バイアス電圧を意味する。理想的には、読み出し後にホトダイオードのn層に残る電子数は0個であるが、どの程度完全に読み出すかは設計事項となる。V n1は1 / fノイズ等が支配的であり、この場合はゲート酸化膜を薄くしたり、表面を清浄化する等の方法もあるが埋め込みチャネルM O Sトランジスタにすると非常に大きな効果がある。実質的には、先に述べた、読み出し系のノイズV n2に比べホトダイオード部でのノイズ

50

と  $V_{n1}$  が充分に小さければノイズ成分は  $V_{n2}$  で支配される。

【0026】

ソースフォロア部のトランジスタである埋め込みMOSトランジスタを形成する場合、ソース・ドレイン領域と同じ導電型の不純物114をチャネル部にドープし、表面より若干深い領域に最もポテンシャルの低い領域を作成する。コストを低く保つためにはパターニングをせずにこの埋め込み型トランジスタのチャネルドープ工程を行うことが必要で、他のトランジスタに与える影響を最低限にしようとするとドープ量を少なくすることが必要である。ドープ量を少なくするにはウエルとしてソース・ドレイン領域と同じ導電型のウエルを用いると良い。この時ゲート電圧0Vでもオフしない構成になりやすいが、ソースフォロアの使い方としては問題はない。線形性が保たれる範囲で使用するのが好ましい。ソースフォロア部以外のトランジスタはオフ特性や低基板バイアス効果が要求される。オフ特性においては異なる導電型の不純物115をチャネル部にドープして閾値電圧を制御する。埋め込み型MOSトランジスタに用いる同じ導電型のチャネルドープ量に比べて通常の表面チャネル型のトランジスタには異なる導電型の不純物115を多く注入して形成し、閾値電圧をエンハンス型になるまで持ち上げることが重要である。深さ的には埋め込みチャネル用のドープは表面からやや深めに、表面チャネル型用のドープはより表面に近い所に形成するように構成する。こうすることで埋め込みチャネル用の同じ導電型タイプのチャネルドープをパターニングせずに1工程で行うことが可能となる。したがってプロセス的に簡易になり低コストが実現できる上に、表面チャネル型MOSトランジスタにおいてもチャネル部下の基板濃度が薄くなり、基板バイアス効果の低減という効果が得られる。10

【0027】

ここでは第1の導電型について特に限定しない。好ましくはn型であり、埋め込みチャネルへのドーパントは浅い部分への急峻なプロファイルが得られることから制御性の面から砒素が好ましい。またウエルの型も特に限定されず、異なる導電型のウエルであっても構わないのはいうまでもない。実施例内で詳細に説明する。20

【実施例1】

【0028】

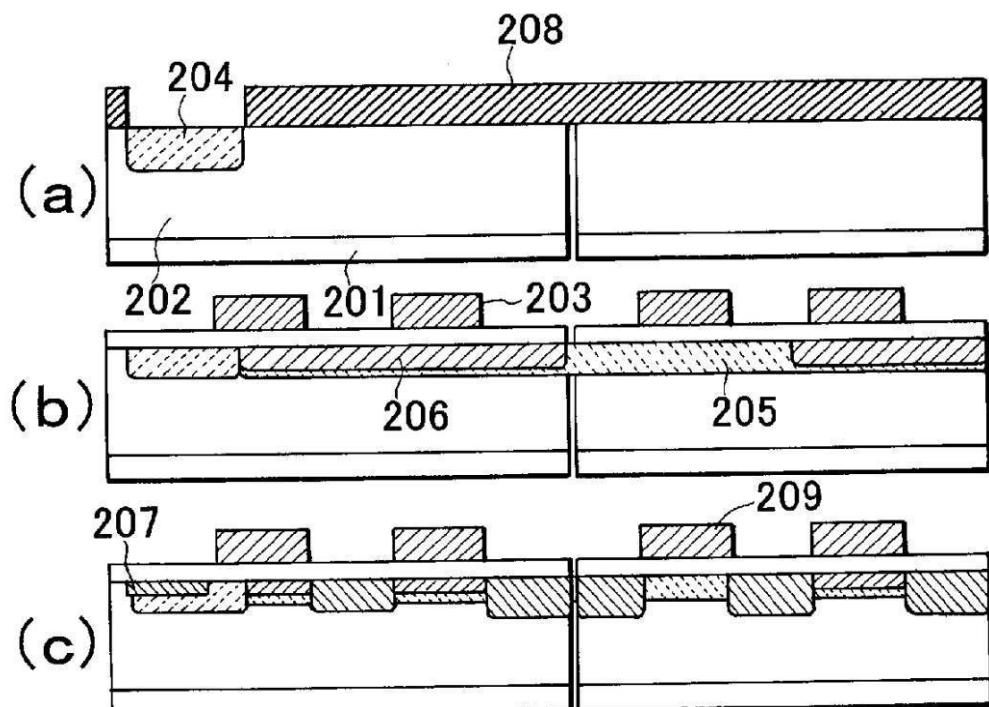

図2を用いて実施例1について説明する。本実施例のホトダイオードとその周辺は以下の手順で形成される。30

【0029】

p型基板201に対し、イオンインプラを用いボロンを導入し、熱処理を行い、表面濃度が約 $2 \times 10^{16} \text{ cm}^{-3}$ のn型ウエル202を形成した。ホトレジスト208を形成して、ホトダイオードのp層204を形成した<図2(a)>。

【0030】

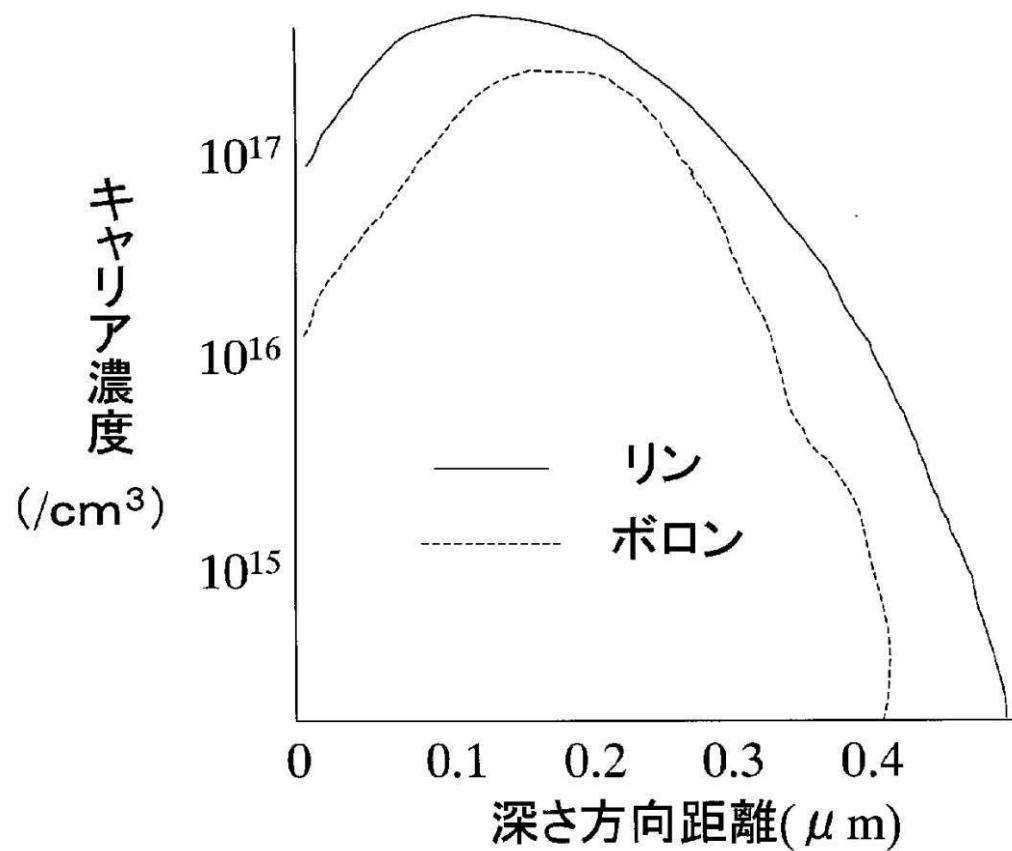

ゲート酸化膜を基板表面全般に形成後、イオン注入法によりボロンをドーズ量 $2 \times 10^{12} \text{ cm}^{-2}$ 、 $35 \text{ keV}$ で注入して、P型の第1のチャネルドープ領域205を形成した。ついでホトレジストを埋め込みチャネル部に形成してリンを $6 \times 10^{12} \text{ cm}^{-2}$ 、 $50 \text{ keV}$ で注入して、n型の第2のチャネルドープ領域206を形成した。埋め込みチャネル部及び表面チャネル部の不純物プロファイルを図3に示す。埋め込みチャネル型ではポテンシャルはゲート電圧とボロンの濃度プロファイルによって決定され、表面から離れた位置にポテンシャルの谷間が存在し埋め込みチャネルを実現する。一方表面チャネル型では不純物としてリンが支配的でポテンシャルを決定するが、チャネル下部ではボロンによりキャリアが相殺されキャリア濃度が小さくなり基板バイアス効果が小さくなる。40

【0031】

次に、ホトレジストを剥離した後に、リンがドープされたポリシリコン制御電極を形成しパターニングを行いソースフォロアMOSトランジスタや転送MOSトランジスタ等の制御電極203を形成した<図2(b)>。つぎに、基板表面のホトダイオード上と制御電極の一部の他の領域にホトレジストを形成し、制御電極203をマスクに表面の濃いn層207を形成した。50

## 【0032】

ついでpMOSトランジスタに対してボロンをイオン注入しソース・ドレイン領域を形成後埋め込みチャネル部のMOSトランジスタをホトレジストで覆った後にさらにボロンをイオン注入し、ポリシリコン制御電極をp型化(209)し、表面チャネルMOSトランジスタを形成する。

## 【0033】

この工程で、図示しない周辺回路部も含めて通常のpMOSトランジスタのソース・ドレイン領域を形成した。nMOSトランジスタに関しては通常の半導体プロセスで形成した<図2(c)>。

## 【0034】

この後、通常の半導体製造工程に従い、第1の層間絶縁膜、コンタクト、第1金属配線、第2の層間絶縁膜、第1金属配線と第2金属配線を接続するビア、第2金属配線、パッセーション膜を順次形成した。

## 【0035】

この結果、ポリシリコン制御電極がn型拡散電極からなる、埋め込み型のpMOSトランジスタ及びポリシリコン制御電極がp型拡散電極からなる表面型MOSトランジスタの閾値電圧を独立に形成することができた。全て表面チャネル型のMOSトランジスタで形成した場合のソースフォロア部のノイズに比べて本実施例のように埋め込みチャネル型MOSトランジスタをソースフォロア部に用いた場合はおよそ1/3にノイズが低減され良好な特性を得た。さらに、表面チャネルMOSトランジスタにおいてもチャネル部下の不純物濃度が低いために、基板バイアス効果が小さく良好な出力特性を得ることができた。

## 【実施例2】

## 【0036】

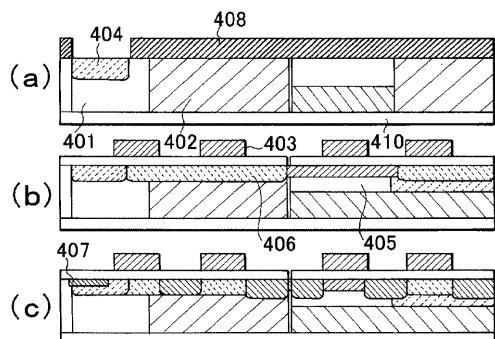

図4を用いて実施例2について説明する。本実施例のホトダイオードとその周辺は以下の手順で形成される。

## 【0037】

n型基板410に対し、イオンインプラを用いボロンを導入し、深いPウエル401を形成する。レジストパターニング後にホトダイオード部を除きボロンをイオン注入しn型に対するポテンシャル障壁およびN型の表面チャネル型MOSトランジスタのウエル402を作成する。ついでホトレジスト408を形成して、ホトダイオードのn層404を形成する<図4(a)>。

## 【0038】

ついでイオン注入法によりパターニングせずに基板全面に砒素をドーズ量6E11cm<sup>-2</sup>、60KeVで注入して、第1のチャネルドープ領域405を形成した。さらにホトレジストを埋め込みチャネル部に形成してN型の表面チャネル用のトランジスタのチャネル部にボロンを2E12cm<sup>-2</sup>、20KeVでイオン注入して、第2のチャネルドープ領域406を形成した。N型の埋め込みチャネル型ではポテンシャルは砒素の濃度プロファイル及びゲート電圧、深いPウエルの電圧で決定され、酸化膜表面から離れた位置にポテンシャルの谷間が存在しキャリアのパスとして埋め込みチャネルを実現する。一方表面チャネル型では不純物としてボロンが支配的でポテンシャルを決定する。これは砒素の濃度に比べてボロンの濃度を大きくしたためである。

## 【0039】

ゲート酸化膜を基板表面全面に形成後、高濃度にリンがドープされたポリシリコン制御電極403を形成しパターニングを行う<図4(b)>。つぎに、基板表面のホトダイオード上と制御電極の一部の領域にホトレジストの抜きパターンを形成し、制御電極403をマスクに表面の濃いp層407を形成した。

## 【0040】

その後通常の半導体プロセスで、図示しない周辺回路部も含めて、nMOSトランジスタ及びpMOSトランジスタを形成した<図4(c)>。

## 【0041】

10

20

30

40

50

さらに、通常の半導体製造工程に従い、第1の層間絶縁膜、コンタクト、第1金属配線、第2の層間絶縁膜、第1金属配線と第2金属配線を接続するビア、第2金属配線、パッセーション膜を順次形成した。

【0042】

この結果ソースフォロア部に形成した埋め込み型のN M O Sトランジスタ及びその他の表面型M O Sトランジスタの閾値電圧を独立に制御形成することができた。全て表面チャネル型のM O Sトランジスタで形成した場合のソースフォロア部のノイズに比べて本実施例のように埋め込みチャネル型のN M O Sトランジスタをソースフォロア部に用いた場合はおよそ1/3にノイズが低減され良好な特性を得た。実施例1と異なり、画素部にn M O Sを用いているために動作速度は速く、ホトダイオードも光により発生するキャリアは電子となる。ポテンシャル的に大きな器を形成しているため感度も大きく向上した。 10

【実施例3】

【0043】

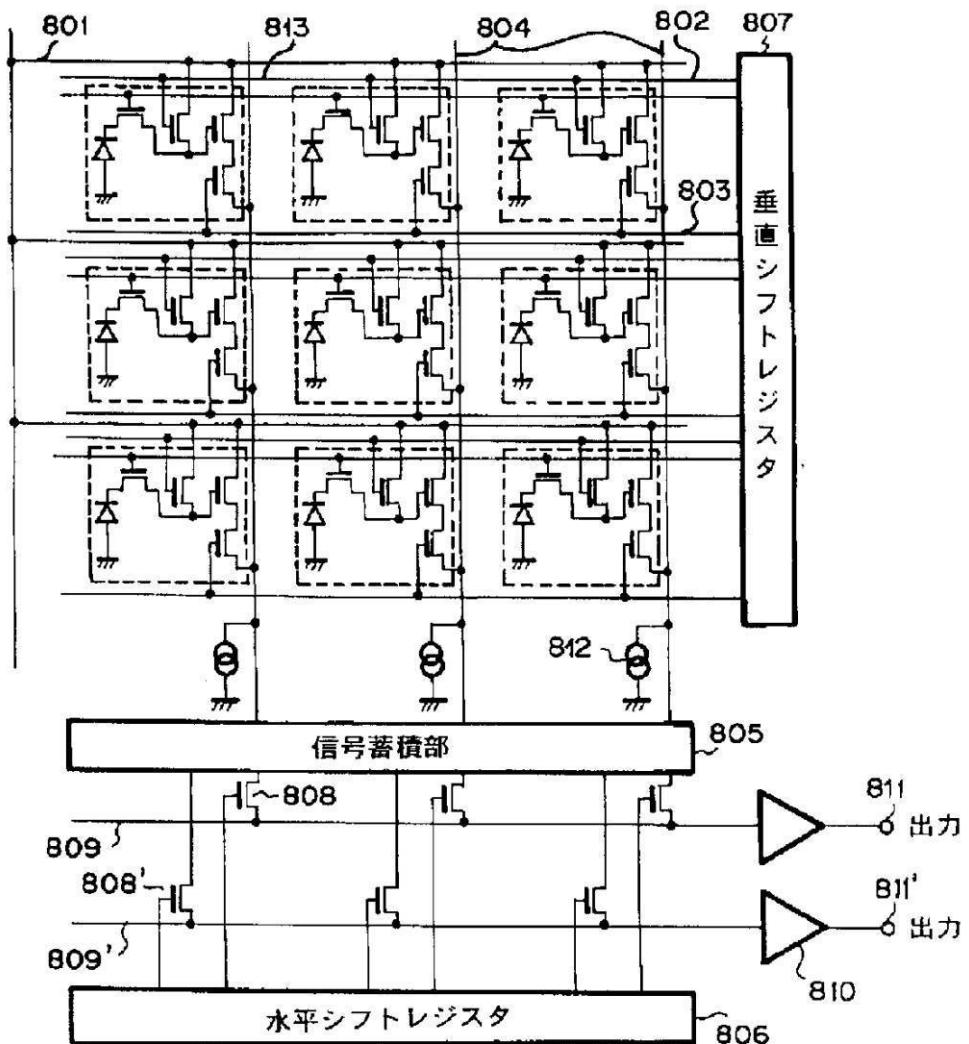

実施例1、2のホトダイオード505および転送M O SトランジスタQ 1を用い、図5に示す画素構成からなり、図6に示す読み出し回路からなるエリアセンサを作製した。

【0044】

図5においては、ホトダイオード505および転送M O Sトランジスタの転送スイッチQ 1を備え、Q 2は拡散浮遊領域をリセットするためのリセットM O Sトランジスタのリセットスイッチ、Q 3は拡散浮遊領域をゲートに接続され、ソース側の負荷として接続される定電流源812からなる埋め込みチャネルトランジスタで形成されたソースフォロワ增幅回路の入力M O Sトランジスタ、Q 4は読み出し画素を選択するための選択スイッチである。 20

【0045】

これらから構成された光電変換素子の画素セルを3行3列に用いた固体撮像装置を図6に示している。

【0046】

図5及び図6の基本的な動作を以下に説明する。リセットスイッチQ 2によりソースフォロワの入力ゲートにリセット電圧を入力するリセット動作と、選択スイッチQ 4による、行選択を行う。 30

【0047】

ソースフォロワの入力ノードの浮遊拡散領域のゲートをフローティングにし、リセットノイズおよびソースフォロワM O Sの閾値電圧のバラツキなどの固定パターンノイズからなるノイズ成分の読み出しを行い、その情報を信号蓄積部805に一旦保持する。

【0048】

その後、転送スイッチQ 1を開閉し、光信号により生成されたホトダイオードの蓄積電荷をソースフォロワの入力ノードに転送し、前述のノイズ成分と光信号成分の和を読み出し、信号蓄積部805に保持する。

【0049】

共通信号線への転送スイッチ808, 808を介して、共通信号線809, 809に、ノイズ成分の信号と、ノイズ成分と光信号成分の和の信号とをそれぞれ共通信号線1(808), 共通信号線2(808)の転送スイッチを導通して、読み出し、それぞれ各出力アンプ810を介して出力811, 811として出力する。 40

【0050】

その後、出力811と811の差をとることでリセットノイズおよび固定パターンノイズを除去して、光信号成分を取り出し、S/Nの高い画像信号を得ることができる。

【0051】

上記方法で読み出しを行い、信号とノイズ評価を行った。その結果、各ビット毎のダイナミックレンジ(S/N) = 75 ~ 85 dBという高いS/Nを得た。

【実施例4】

【0052】

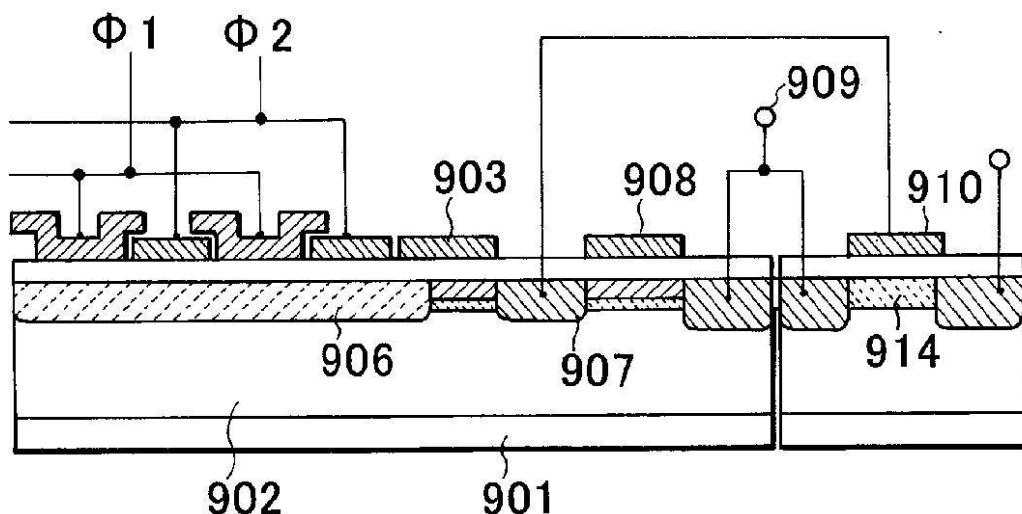

第7図を用いて本発明の第4実施例を説明する。図7は、本発明を用いたCCDイメージセンサーの断面構造図であり、ホトダイオードからのキャリアはポテンシャル井戸を通り、1、2のクロックで転送される。

【0053】

最終段は転送MOSトランジスタのゲート領域903の側面下部に拡散浮遊領域FD907が形成されており、該拡散浮遊領域FD907は出力回路の增幅用MOSトランジスタのゲートに接続され、ソースフォロワ增幅回路として出力する。このソースフォロアのトランジスタ910に埋め込み型MOSトランジスタを使用し1/fノイズを減少させる。

【0054】

また、該拡散浮遊領域FD907には、該拡散浮遊領域FD907のリセット用のリセットMOSトランジスタ908のソースが接続され、そのドレインはリセット電源909が接続されている。ソースフォロアトランジスタ以外のMOSトランジスタはここでは表面チャネル型MOSトランジスタである。埋め込みチャネル型MOSトランジスタと同型の表面チャネル型MOSトランジスタの作成方法その他は上記実施例と同様でありCCD構造においても本発明は適用されノイズ低減という大きな効果が有ることがわかった。

【実施例5】

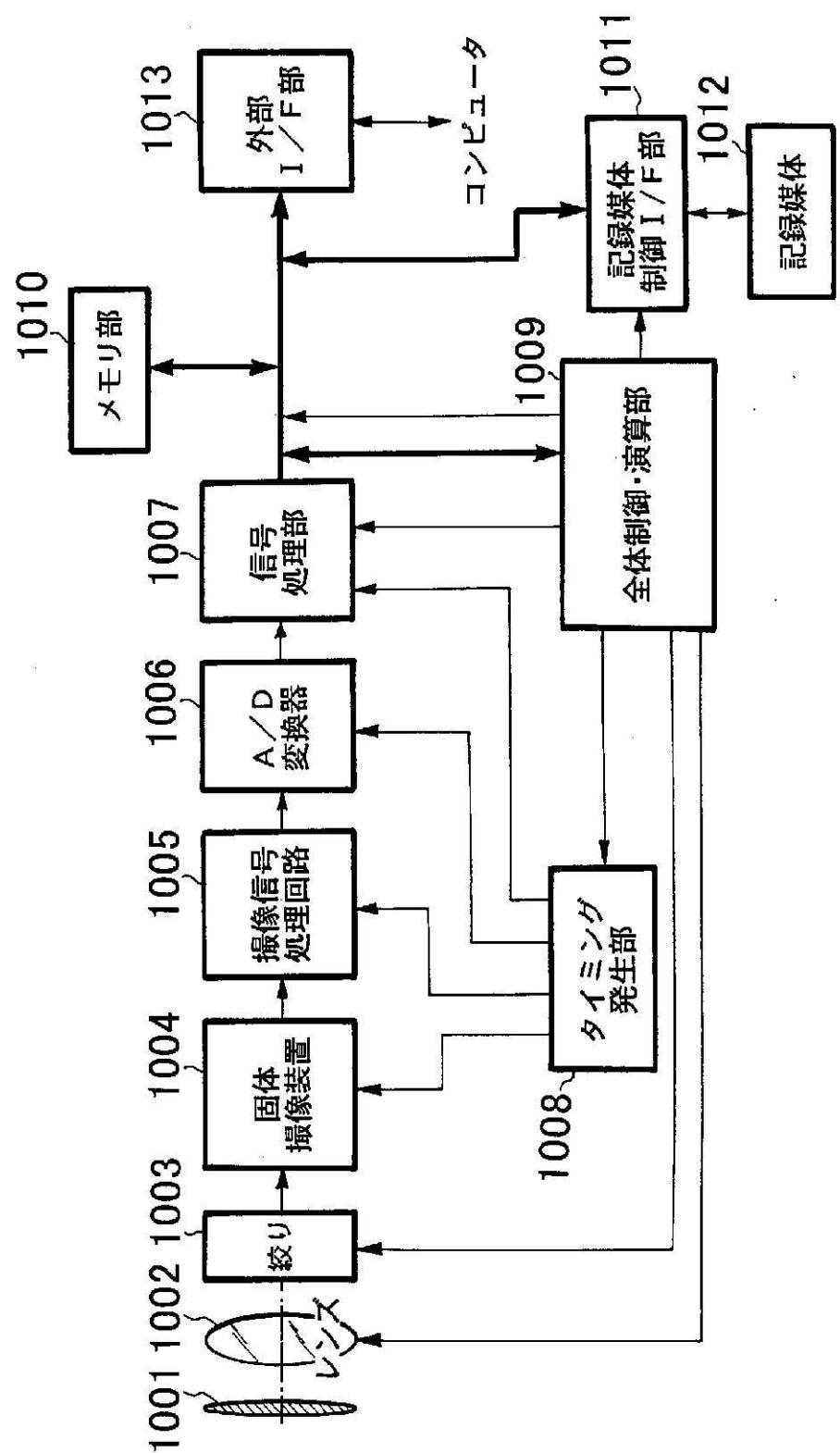

【0055】

図8は、本発明による固体撮像装置をカメラに応用する場合の回路ブロックの例を示したものである。撮影レンズ1002の手前にはシャッター1001があり、露出を制御する。絞り1003により必要に応じ光量を制御し、固体撮像装置1004に結像させる。固体撮像装置1004から出力された信号は信号処理回路1005で処理され、A/D変換器1006によりアナログ信号からデジタル信号に変換される。出力されるデジタル信号はさらに信号処理部1007で演算処理される。処理されたデジタル信号はメモリ1010に蓄えられたり、外部I/F1013を通して外部の機器に送られる。固体撮像装置1004、撮像信号処理回路1005、A/D変換器1006、信号処理部1007はタイミング発生部1008により制御される他、システム全体は全体制御部・演算部1009で制御される。記録媒体1012に画像を記録するために、出力デジタル信号は全体制御部・演算部で制御される記録媒体制御I/F部1011を通して、記録される。

【図面の簡単な説明】

【0056】

【図1】本発明の実施形態を表す図である。

【図2】本発明の第1実施例を表す断面図である。

【図3】本発明の第1実施例の不純物プロファイル図である。

【図4】本発明の第2実施例を表す断面図である。

【図5】固体撮像装置の画素の等価回路図である。

【図6】本発明を用いたエリアセンサの読み出し回路を含めた等価回路図である。

【図7】本発明の第4実施例を表す断面図である。

【図8】本発明による固体撮像装置をもちいたカメラシステムの構成ブロック図である。

【符号の説明】

【0057】

101, 201, 401, 901 基板

102, 202, 402, 902 ウエル

103, 203, 209, 403, 903 制御電極

104, 204, 404 ホトダイオード部

107, 907 拡散浮遊領域

108, 908 リセット用MOSトランジスタ

109, 501, 801, 909 電源

110, 910 ソースフォロアトランジスタ

10

20

30

40

50

|                               |                |    |

|-------------------------------|----------------|----|

| 1 1 1                         | 行選択スイッチ用トランジスタ |    |

| 1 1 2 , 8 1 2                 | 電流源            |    |

| 1 1 3                         | 出力端子           |    |

| 1 1 4 , 2 0 5 , 4 0 5 , 9 1 4 | 第1のチャネルドープ     |    |

| 1 1 5 , 2 0 6 , 4 0 6         | 第2のチャネルドープ     |    |

| 2 0 7 , 4 0 7                 | 表面層            |    |

| 2 0 8 , 4 0 8                 | ホトレジスト         |    |

| 4 1 0                         | 深いウエル          |    |

| 5 0 2 , 8 0 2                 | リセットスイッチ線      |    |

| 5 0 3 , 8 0 3                 | 選択スイッチ線        | 10 |

| 5 0 4 , 8 0 4                 | 信号出力線          |    |

| 5 0 5                         | ホトダイオード        |    |

| 5 0 6 , 8 1 3                 | 転送スイッチ線        |    |

| 8 0 5                         | 信号蓄積部          |    |

| 8 0 8                         | 共通信号線1への転送スイッチ |    |

| 8 0 8                         | 共通信号線2への転送スイッチ |    |

| 8 0 9                         | 共通信号線1         |    |

| 8 0 9                         | 共通信号線2         |    |

| 8 1 0                         | 出力アンプ          |    |

| 8 1 1                         | 出力1            | 20 |

| 8 1 1                         | 出力2            |    |

| 9 0 6                         | 電荷転送部ウエル       |    |

【図4】

- 401:深いウエル

402:ウエル

403:制御電極

404:ホトダイオード部

405:第1のチャネルドープ

406:第2のチャネルドープ

407:表面層

408:ホトレジスト

410:基板

【図1】

- 101: 基板

102: ウエル

103: 制御電極

104: ホトダイオード部

107: 拡散浮遊領域

108: リセット用MOSトランジスタ

109: 電源

110: ソースフォロアトランジスタ

111: 行選択スイッチ用トランジスタ

112: 電流源

113: 出力端子

114: 第1のチャネルドープ

115: 第2のチャネルドープ

【図2】

- 201:基板

202:ウェル

203:制御電極

204:ホトダイオード部

205:第1のチャネルドープ

206:第2のチャネルドープ

207:表面層

208:ホトレジスト

209:制御電極

【図3】

【図5】

501:電源

502:リセットスイッチ線

503:選択スイッチ線

504:信号出力線

505:ホトダイオード

506:転送スイッチ線

【図6】

801 : 電源

809 : 共通信号線 1

802 : リセットスイッチ線

809' : 共通信号線 2

803 : 選択スイッチ線

810 : 出力アンプ

804 : 信号出力線

812 : 定電流源

808 : 共通信号線 1 への転送スイッチ

813 : 転送スイッチ線

808' : 共通信号線 2 への転送スイッチ

【図7】

- 901: 基板

- 902: ウエル

- 903: 制御電極

- 906: 電荷転送部ウエル

- 907: 拡散浮遊領域

- 908: リセット用MOSトランジスタ

- 909: 電源

- 910: ソースフォロアトランジスタ

- 914: 第1のチャネルドープ

【図 8】

---

フロントページの続き

(72)発明者 市川 武史

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

合議体

審判長 鈴木 匡明

審判官 西脇 博志

審判官 早川 朋一

(56)参考文献 特開2002-33398 (JP, A)

特開平8-186250 (JP, A)

特開平7-99298 (JP, A)

特開2000-353756 (JP, A)

特開2002-329793 (JP, A)

特開2000-77613 (JP, A)

特開2004-158508 (JP, A)

特開2003-333431 (JP, A)

特開平7-321220 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L27/146

H01L27/088

H01L21/339

H01L21/8234

H01L29/762