(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2010-3161

(P2010-3161A)

(43) 公開日 平成22年1月7日(2010.1.7)

(51) Int.Cl.

G06F 12/00 (2006.01)

G06F 13/16 (2006.01)

F 1

G06F 12/00 564D

G06F 12/00 597U

G06F 13/16 51OC

テーマコード(参考)

5B060

審査請求 未請求 請求項の数 5 O L (全 16 頁)

(21) 出願番号

特願2008-162281 (P2008-162281)

(22) 出願日

平成20年6月20日 (2008.6.20)

(71) 出願人 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(74) 代理人 100089118

弁理士 酒井 宏明

(72) 発明者 長富 靖

東京都港区芝浦一丁目1番1号 株式会社

東芝内

F ターム(参考) 5B060 MB02

(54) 【発明の名称】メモリシステム

## (57) 【要約】

【課題】不揮発性記憶部の信号線の負荷容量が増大した場合においても、信号遅延を防止することが可能なメモリシステムを提供することを目的とする。

【解決手段】複数の Chip が搭載される NAND メモリと、NAND メモリを制御する NAND コントローラ 112 を備えたメモリシステムにおいて、NAND コントローラ 112 と NAND メモリに搭載される複数の Chip 間の信号線の接続を切り替えるバススイッチを設け、NAND メモリ 10 に対するアクセス時の信号線の負荷容量を低減して、信号遅延を防止する。

【選択図】

図 1 1

**【特許請求の範囲】****【請求項 1】**

複数の不揮発性メモリチップが搭載される不揮発性記憶部と、前記不揮発性記憶部を制御するコントロール回路と、前記コントロール回路を制御するMPUと、ホストとの通信を行うインターフェース回路とが基板上に搭載されるメモリシステムにおいて、

前記コントロール回路と前記複数の不揮発性メモリチップ間の信号線の接続を切り替えるバススイッチを備えたことを特徴とするメモリシステム。

**【請求項 2】**

前記バススイッチは、前記基板上または前記不揮発性記憶部に搭載されることを特徴とする請求項1に記載のメモリシステム。 10

**【請求項 3】**

前記コントロール回路は、リード／ライトアドレスに応じて、前記バススイッチの切り替えを指示するバススイッチ切替信号を前記バススイッチに出力するバススイッチ制御部を含み、

前記バススイッチは、前記バススイッチ切替信号に基づいて、前記信号線の接続の切り替えを行うことを特徴とする請求項1または請求項2に記載のメモリシステム。

**【請求項 4】**

前記バススイッチは、リード／ライトアドレスに応じて、前記信号線の接続の切り替えを行うことを特徴とする請求項1または請求項2に記載のメモリシステム。 20

**【請求項 5】**

前記バススイッチは、1または複数の不揮発性メモリチップ単位で前記信号線の接続の切り替えを行うことを特徴とする請求項1～請求項4のいずれか1つに記載のメモリシステム。 30

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、不揮発性半導体記憶装置を用いて構成されるメモリシステムに関する。

**【背景技術】****【0002】**

コンピュータシステムに用いられる外部記憶装置として、フラッシュメモリ（フラッシュE E P R O M）を搭載したメモリシステムとしてSSD（Solid State Drive）が注目されている。フラッシュメモリは、磁気ディスク装置に比べ、高速、軽量などの利点を有している。 30

**【0003】**

SSD内には、複数のフラッシュメモリチップ、ホスト装置からの要求に応じて各フラッシュメモリチップのリード／ライト制御を行うコントローラ、各フラッシュメモリチップとホスト装置との間でデータ転送を行うためのバッファメモリ、電源回路、ホスト装置に対する接続インターフェースなどを備えている（例えば、特許文献1）。

**【0004】**

しかしながら、SSDを設計する場合、コントローラチップのPin数や実装面積が限られた中で、データ容量を増やすために、メモリChipを複数枚Stack（積層）したStack品を使用する必要がある。かかるStack品では、内部でI/O信号線および制御信号線をメモリChip数分纏めた形となり、各信号線の負荷容量もStackしたメモリChip数につれて大きくなる。 40

**【0005】**

各信号線の負荷容量が大きくなると、I/O信号および制御信号のCR遅延による遅れが生じ、同期設計したコントローラを使用した場合、低負荷（Stack数：少）ではメモリからの読み取りデータをラッチして出力できるが、高負荷（Stack数：多）ではCR遅延によってメモリから読み出したデータの遅延のため、ラッチして出力できないおそれがある。同様に、各信号線の負荷容量が大きくなると、信号遅延のためにメモリに対す 50

る書き込みエラーが発生するおそれがある。

【0006】

【特許文献1】特許第3688835号公報

【発明の開示】

【発明が解決しようとする課題】

【0007】

本発明は、上記課題に鑑みてなされたものであり、不揮発性記憶部の信号線の負荷容量が増大した場合においても、信号遅延を防止することが可能なメモリシステムを提供することを目的とする。

【課題を解決するための手段】

【0008】

上述した課題を解決し、目的を達成するために、本発明は、複数の不揮発性メモリチップが搭載される不揮発性記憶部と、前記不揮発性記憶部を制御するコントロール回路と、前記コントロール回路を制御するMPUと、ホストとの通信を行うインターフェース回路とが基板上に搭載されるメモリシステムにおいて、前記コントロール回路と前記複数の不揮発性メモリチップ間の信号線の接続を切り替えるバススイッチを備えたことを特徴とする。

【発明の効果】

【0009】

本発明によれば、コントローラ回路と不揮発性記憶部に搭載される複数の不揮発性メモリチップ間の信号線の接続を切り替えるバススイッチを設けているので、不揮発性記憶部にアクセスする場合に、バススイッチにより、アクセスする不揮発性メモリチップを接続する一方、アクセスしない不揮発性メモリチップとの接続を遮断することができ、不揮発性記憶部に対するアクセス時の信号線の負荷容量を低減でき、不揮発性記憶部の信号線の負荷容量が増大した場合においても、信号遅延を防止することが可能なメモリシステムを提供することが可能となるという効果を奏する。

【発明を実施するための最良の形態】

【0010】

以下に、この発明につき図面を参照しつつ詳細に説明する。なお、この実施例によりこの発明が限定されるものではない。また、下記実施例における構成要素には、当業者が容易に想定できるものまたは実質的に同一のものが含まれる。

【0011】

本実施例のメモリシステムは、不揮発性半導体記憶装置を含み、たとえば、パーソナルコンピュータなどのホスト装置の2次記憶装置(SSD:Solid State Drive)として使用され、ホスト装置から書き要求が出されたデータを記憶し、またホスト装置から読み出しがあったデータを読み出してホスト装置に出力する機能を有する。

【0012】

【SSDの構成例】

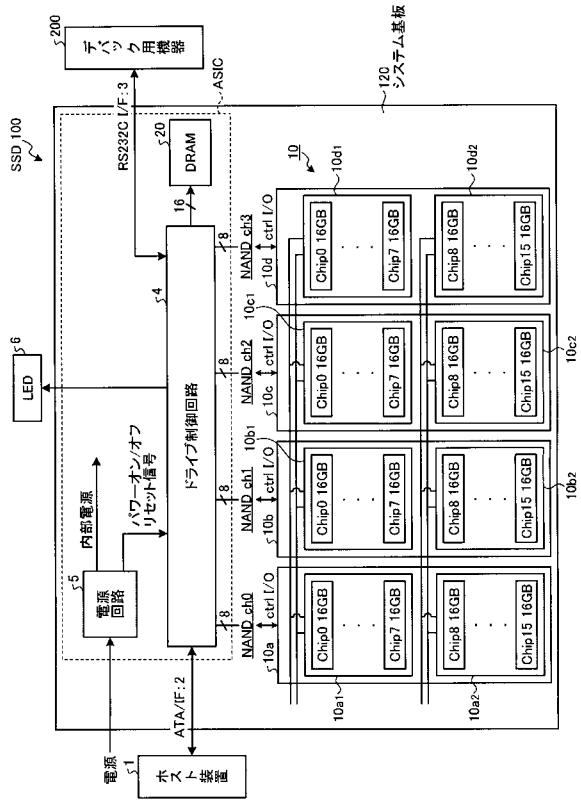

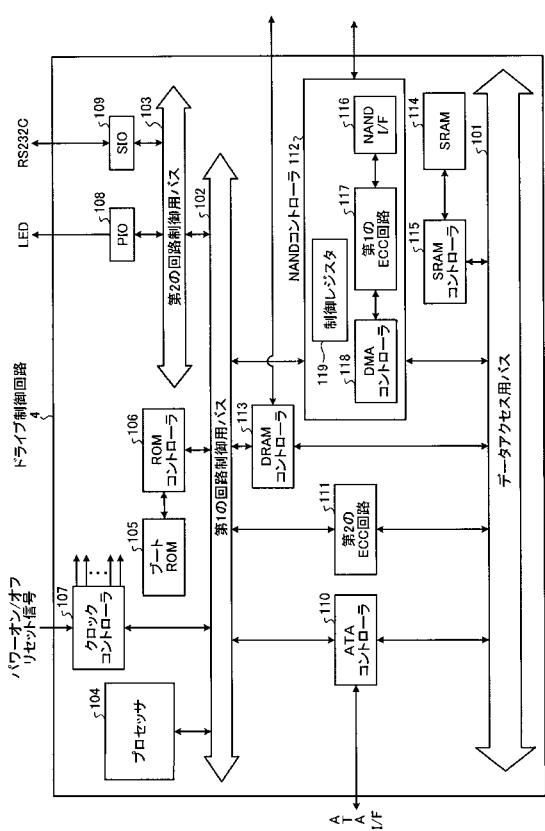

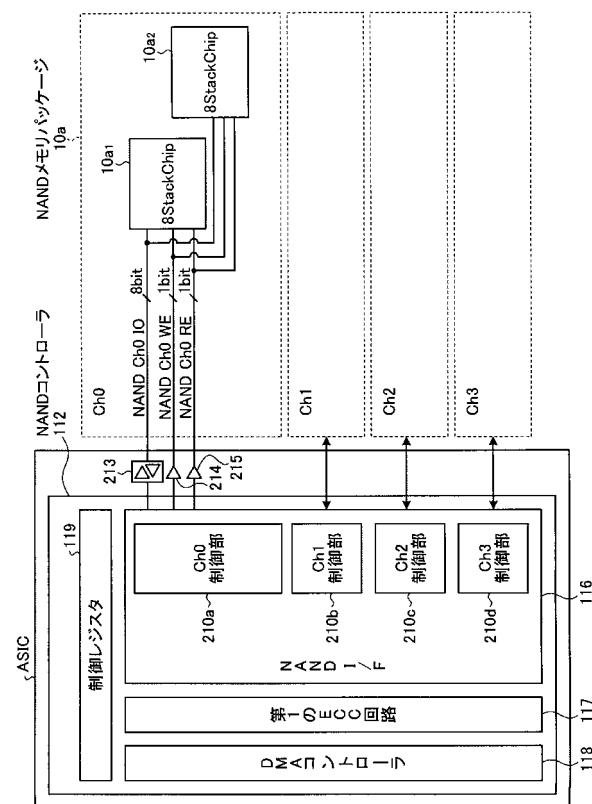

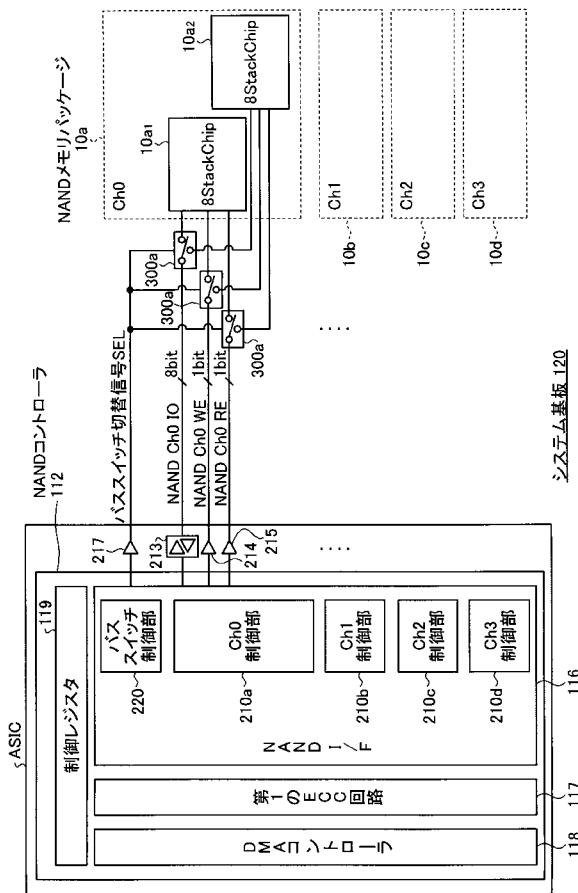

図1は、SSD100の構成例を示すブロック図である。SSD100は、システム基板(基板)120に搭載されたASICおよびNANDメモリ10で構成されている。また、ASICには、ドライブ制御回路4、電源回路5、DRAM20が搭載されている。

【0013】

SSD100は、ATAインターフェース(ATAI/F)2などのメモリ接続インターフェースを介してパソコンあるいはCPUコアなどのホスト装置(ホスト)1と接続され、ホスト装置1の外部メモリとして機能する。また、SSD100は、RS232Cインターフェース(RS232C/I/F)3などの通信インターフェースを介して、デバッグ用機器200との間でデータを送受信することができる。SSD100は、不揮発性メモリとしてのNANDフラッシュメモリ(以下、NANDメモリと略す)10と、コントローラとしてのドライブ制御回路4と、揮発性メモリとしてのDRAM20と、電源回路5と、状態表示用のLED6などを備えている。

10

20

30

40

50

## 【0014】

電源回路5は、ホスト装置1側の電源回路から供給される外部直流電源から複数の異なる内部直流電源電圧を生成し、これら内部直流電源電圧をSSD100内の各回路に供給する。また、電源回路5は、外部電源の立ち上がりまたは立ち下がりを検知し、パワーオンリセット信号またはパワーオフリセット信号を生成して、ドライブ制御回路4に供給する。

## 【0015】

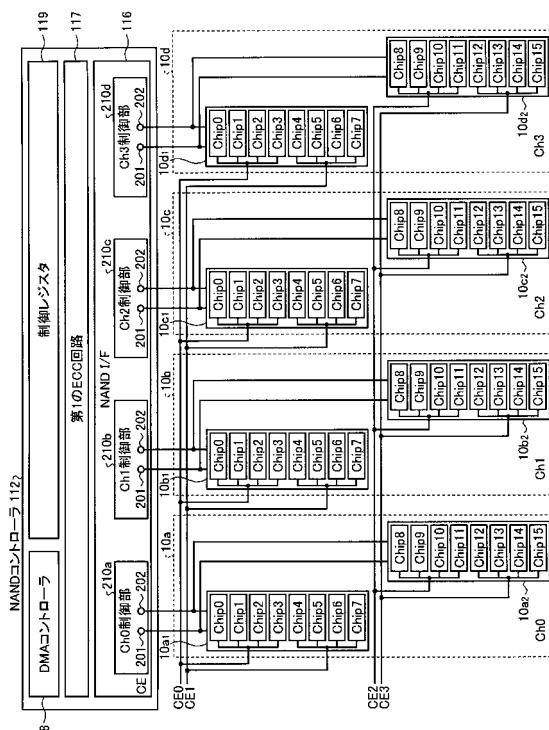

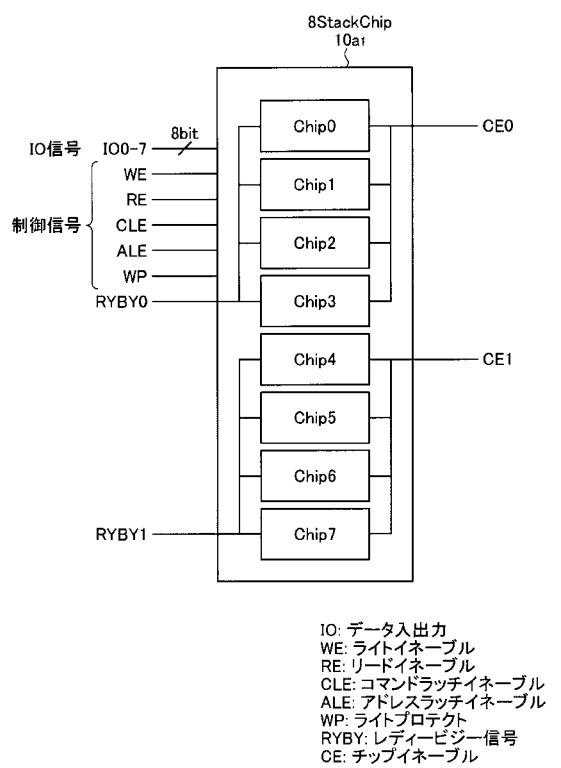

NANDメモリ(不揮発性記憶部)10は、4ChのNANDメモリパッケージ10a～10dを有する。1つのNANDメモリパッケージは、積層された複数のNANDメモリチップ(以下、「Chip」と称する)によって構成されている。図1に示す例では、例えば、NANDメモリパッケージ10aは、8枚のChip0～7(例えば、1Chip=16GB)がStackされた8StackChip10a1と、8枚のChip8～15がStackされた8StackChip10a2とを備え、他のNANDメモリパッケージ10b～dも同様に、2組の8StackChipを備えており、NANDメモリ10は128GBの容量を有する。4ChのNANDメモリパッケージ10a～10dは、4並列動作が可能となっている。

10

## 【0016】

DRAM20は、ホスト装置1とNANDメモリ10間でのデータ転送用キャッシュおよび作業領域用メモリとして機能する。ドライブ制御回路4は、ホスト装置1とNANDメモリ10との間でDRAM20を介してデータ転送制御を行うとともに、SSD100内の各構成要素を制御する。また、ドライブ制御回路4は、状態表示用LED6にステータス表示用信号を供給するとともに、電源回路5からのパワーオン/オフリセット信号を受けて、リセット信号およびクロック信号を自回路内およびSSD100内の各部に供給する機能も有している。

20

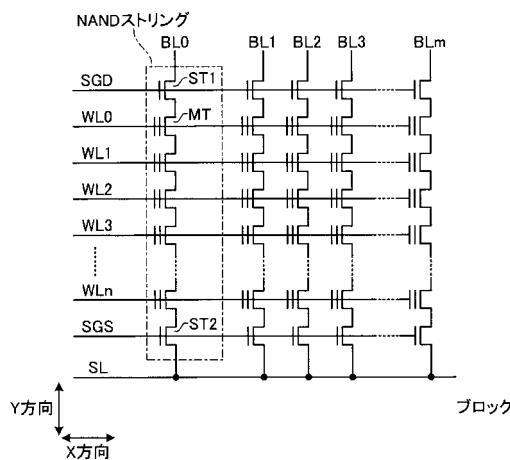

## 【0017】

各NANDメモリチップは、データ消去の単位であるブロックを複数配列して構成されている。図2は、NANDメモリチップに含まれる1個のブロックの構成例を示す回路図である。各ブロックは、X方向に沿って順に配列された(m+1)個のNANDストリングを備えている(mは、0以上の整数)。(m+1)個のNANDストリングにそれぞれ含まれる選択トランジスタST1は、ドレインがビット線BL0～BLmに接続され、ゲートが選択ゲート線SGDに共通接続されている。また、選択トランジスタST2は、ソースがソース線SLに共通接続され、ゲートが選択ゲート線SGSに共通接続されている。

30

## 【0018】

各メモリセルトランジスタMTは、半導体基板上に形成された積層ゲート構造を備えたMOSFET(metal oxide semiconductor field effect transistor)から構成される。積層ゲート構造は、半導体基板上にゲート絶縁膜を介在して形成された電荷蓄積層(浮遊ゲート電極)、及び電荷蓄積層上にゲート間絶縁膜を介在して形成された制御ゲート電極を含んでいる。メモリセルトランジスタMTは、浮遊ゲート電極に蓄えられる電子の数に応じて閾値電圧が変化し、この閾値電圧の違いに応じてデータを記憶する。メモリセルトランジスタMTは、1ビットを記憶するように構成されていてもよいし、多値(2ビット以上のデータ)を記憶するように構成されていてもよい。

40

## 【0019】

各NANDストリングにおいて、(n+1)個のメモリセルトランジスタMTは、選択トランジスタST1のソースと選択トランジスタST2のドレインとの間に、それぞれの電流経路が直列接続されるように配置されている。すなわち、複数のメモリセルトランジスタMTは、隣接するもの同士で拡散領域(ソース領域若しくはドレイン領域)を共有するような形でY方向に直列接続される。

## 【0020】

そして、最もドレイン側に位置するメモリセルトランジスタMTから順に、制御ゲート

50

電極がワード線 W L 0 ~ W L n にそれぞれ接続されている。従って、ワード線 W L 0 に接続されたメモリセルトランジスタ M T のドレインは選択トランジスタ S T 1 のソースに接続され、ワード線 W L n に接続されたメモリセルトランジスタ M T のソースは選択トランジスタ S T 2 のドレインに接続されている。

#### 【 0 0 2 1 】

ワード線 W L 0 ~ W L n は、ブロック内の N A N D ストリング間で、メモリセルトランジスタ M T の制御ゲート電極を共通に接続している。つまり、ブロック内において同一行にあるメモリセルトランジスタ M T の制御ゲート電極は、同一のワード線 W L に接続される。この同一のワード線 W L に接続される ( m + 1 ) 個のメモリセルトランジスタ M T は 1 ページとして取り扱われ、このページごとにデータの書き込み及びデータの読み出しが行われる。10

#### 【 0 0 2 2 】

また、ビット線 B L 0 ~ B L m は、ブロック間で、選択トランジスタ S T 1 のドレインを共通に接続している。つまり、複数のブロック内において同一列にある N A N D ストリングは、同一のビット線 B L に接続される。

#### 【 0 0 2 3 】

図 1 に示したように、N A N D メモリ 1 0 においては、4 つの並列動作要素である N A N D メモリパッケージ 1 0 a ~ 1 0 d が各 8 ビットの 4 チャネル ( 4 C h ) を介してドライブ制御回路 4 に並列接続されている。4 つの N A N D メモリパッケージ 1 0 a ~ 1 0 d を単独動作させるか、並列動作させるか、N A N D メモリ 1 0 の倍速モードを使用するか否か、という組み合わせにより、下記 3 種類のアクセスモードが提供される。20

##### ( 1 ) 8 ビットノーマルモード

1 C h だけ動作させ、8 ビット単位で読み書きをするモードである。転送サイズの 1 単位はページサイズ ( 4 k B ) である。

##### ( 2 ) 3 2 ビットノーマルモード

4 C h 並列で動作させ、3 2 ビット単位で読み書きをするモードである。転送サイズの 1 単位はページサイズ × 4 ( 1 6 k B ) である。

##### ( 3 ) 3 2 ビット倍速モード

4 C h 並列で動作させ、更に、N A N D メモリ 1 0 の倍速モードを利用して読み書きをするモードである。転送サイズの 1 単位はページサイズ × 4 × 2 ( 3 2 k B ) である。30

#### 【 0 0 2 4 】

4 C h 並列動作する 3 2 ビットノーマルモードまたは 3 2 ビット倍速モードでは、並列動作する 4 または 8 ブロックが、N A N D メモリ 1 0 としての消去単位となり、並列動作する 4 または 8 ページが、N A N D メモリ 1 0 としての書き込み単位及び読み出し単位となる。

#### 【 0 0 2 5 】

図 3 は、ドライブ制御回路 4 のハードウェア的な内部構成例を示すブロック図である。ドライブ制御回路 4 は、データアクセス用バス 1 0 1 、第 1 の回路制御用バス 1 0 2 、及び第 2 の回路制御用バス 1 0 3 を備えている。第 1 の回路制御用バス 1 0 2 には、ドライブ制御回路 4 全体を制御するプロセッサ 1 0 4 が接続されている。第 1 の回路制御用バス 1 0 2 には、N A N D メモリ 1 0 に記憶された各管理プログラム ( F W : ファームウェア ) をブートするブート用プログラムが格納されたブート R O M 1 0 5 が R O M コントローラ 1 0 6 を介して接続されている。また、第 1 の回路制御用バス 1 0 2 には、図 1 に示した電源回路 5 からのパワーオン / オフリセット信号を受けて、リセット信号及びクロック信号を各部に供給するクロックコントローラ 1 0 7 が接続されている。40

#### 【 0 0 2 6 】

第 2 の回路制御用バス 1 0 3 は、第 1 の回路制御用バス 1 0 2 に接続されている。第 2 の回路制御用バス 1 0 3 には、図 1 に示した状態表示用 L E D 6 にステータス表示用信号を供給するパラレル I O ( P I O ) 回路 1 0 8 、 R S 2 3 2 C I / F 3 を制御するシリアル I O ( S I O ) 回路 1 0 9 が接続されている。50

## 【0027】

ATAインターフェースコントローラ(ATAコントローラ)110、第2のECC(Error Check and Correct)回路111、NANDコントローラ112、及びDRAMコントローラ113は、データアクセス用バス101と第1の回路制御用バス102との両方に接続されている。ATAコントローラ110は、ATAインターフェース2を介してホスト装置1との間でデータを送受信する。データアクセス用バス101には、データ作業領域として使用されるSRAM114がSRAMコントローラ115を介して接続されている。SRAM114には、NANDメモリ10に記憶されているファームウェアが起動時、ブートROM105に記憶されたブート用プログラムによって転送される。

## 【0028】

NANDコントローラ112は、NANDメモリ10の各NANDメモリパッケージ10a～10dとのインターフェース処理を行うNAND I/F116、第1のECC回路117、NANDメモリ10-DRAM20間のアクセス制御を行うDMA転送制御用DMAコントローラ118、およびプロセッサ104により制御データが書き込まれる制御レジスタ119を備えている。

## 【0029】

NANDメモリ10にデータを書き込む場合は、第1のECC回路117は、書き込み対象のデータに対して、所定単位データD(例えば、512B)毎に、誤り検出符号(例えば、CRC32)および1bitの訂正能力がある第1の誤り訂正符号(例えば、ハミング符号)を生成して付加する。また、第1のECC回路117は、8個の単位データD毎に、複数bit(例えば、48bit)の訂正能力がある第2の誤り訂正符号(例えば、 BCH符号)を生成して付加する。誤り検出符号および第1の誤り訂正符号が付加されたデータがNAND I/F116によりNANDメモリ10に書き込まれる。

## 【0030】

また、NANDメモリ10からデータを読み出す場合は、第1のECC回路117は、NAND I/F116によりNANDメモリ10から読み出されたデータに対して、まず、第1の誤り訂正を行った後、誤り検出符号で誤りがあるか否かを検出し、第1の誤り訂正後のデータ、第1の誤り訂正による訂正bit数、および誤り検出結果を、DMAコントローラ118を介して、DRAM20に格納する。第2のECC回路111は、誤り検出結果で誤りがある場合に、すなわち、第1の誤り訂正で誤りを訂正できなかった場合に、第2の誤り訂正を行って、第2の誤り訂正後のデータおよび第2の誤り訂正による訂正bit数をDRAM20に格納する。

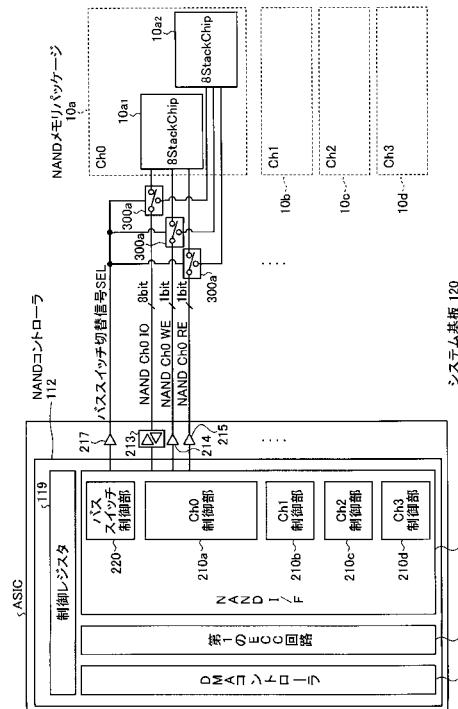

## 【0031】

## [NANDコントローラおよびNANDメモリ]

図4は、NAND I/F116とNANDメモリ10との接続を説明するための図である。NAND I/F116は、4Chのインターフェース回路であるCh0～Ch3制御部210a～210dを備えており、Ch0～Ch3制御部210a～210dの制御信号ピン201およびIO信号ピン202は、Ch0～Ch3のNANDパッケージ10a～10d(NAND Ch0～Ch3)とそれぞれ独立に接続されている。制御信号ピン201からは制御信号が出力され、IOピン202からは8ビットのデータIO0～7が入出力される。CE(チップイネーブル)0～3信号は、NANDパッケージ10a～10d(NAND Ch0～Ch3)を選択する。

## 【0032】

以下の説明では、各Chの構成は同一であるので、Ch0を代表させて説明する。図5および図6は、NANDメモリ10の負荷容量およびCR遅延を説明するための図である。図6において、213は入出力IO, 214および215は出力IOを示している。

## 【0033】

図5に示すように、8StackChip10a1は、IO信号(IOデータIO0～7(アドレスデータを含む))、制御信号{WE(ライトイネーブル)信号、RE(リードイネーブル)信号、CLE(コマンドラッティネーブル)信号、ALE(アドレスラッ

10

20

30

40

50

チイネーブル) 信号、W P (ライトプロテクト) 信号等} が 1 本 / 8 C h i p であるので、負荷容量が 8 倍に増加する。また、N A N D パッケージ 1 0 a は、信号 p i n を減らすために、I O 信号 I O 0 ~ 7 および制御信号 / 2 個の 8 S t a c k C h i p 1 0 a 1 , 1 0 a 2 としているため、負荷容量がさらに 2 倍に増加する。このため、C R 遅延が増加する。また、一般に負荷容量は I O 信号 > 制御信号であるため、I O 信号と制御信号で遅延差が生じる。

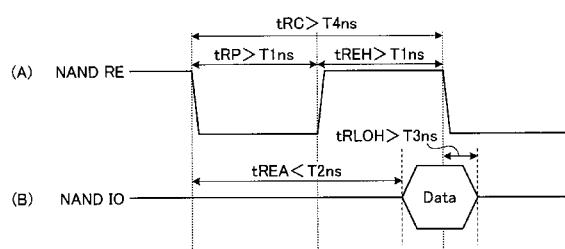

#### 【 0 0 3 4 】

図 7 は、N A N D メモリ 1 0 からのデータの読み出しを説明するためのタイミングチャートである。同図において、( A ) は R E 信号、( B ) は I O データを示している。ここで、システムは、R E 信号の立ち下がりから t R E A 経過した後に、読み出しデータの出力が保証され、R E の立ち上がりから t R L O H 経過した後は、読み出しデータの出力が保証されないスペックであるとする。この場合、負荷容量が大きく C R 遅延が大きい場合は、t R E A が遅れ負荷容量が小さい場合のラッチタイミングではデータを取得できなくなってしまい、そのタイミング調整が必要となる。

10

#### 【 0 0 3 5 】

図 8 ~ 図 1 0 を参照して、N A N D I / F 1 1 6 の C h 制御部に完全同期設計回路を搭載した場合の信号遅延について説明する。図 8 は、完全同期設計回路を説明するための図、図 9 は、負荷容量が小さい場合のタイミングチャート、図 1 0 は、負荷容量が大きい場合のタイミングチャートを示している。なお、以下、フリップフロップを F F と表記する。

20

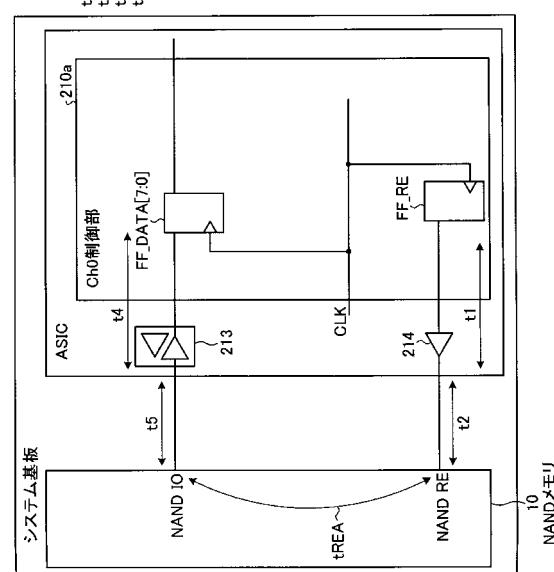

#### 【 0 0 3 6 】

図 8 において、C h 0 制御部 2 1 0 a は、クロックコントローラ 1 0 7 (図 3 参照) で生成された内部クロック C L K に同期して R E を出力する F F \_ R E と、内部クロック C L K に同期して I O [ 7 : 0 ] をラッピングして出力する F F \_ D A T A [ 7 : 0 ] とを備えている。同図において、t 1 は、I O と C R 遅延、t 2 , t 5 は、伝搬 (配線) 遅延、t 4 は I O 遅延、t R E A は N A N D データ出力と I O と C R 遅延を示している。

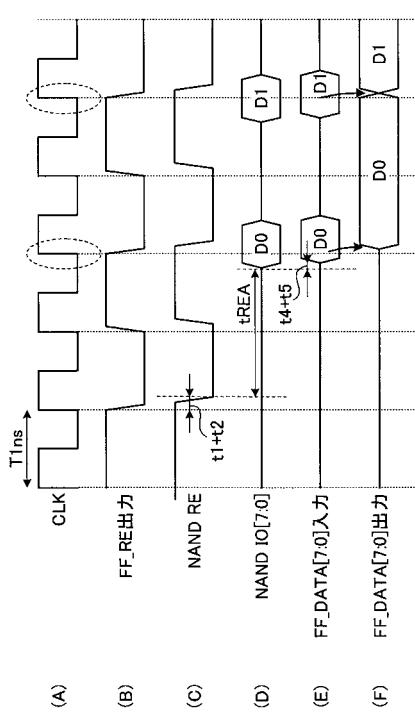

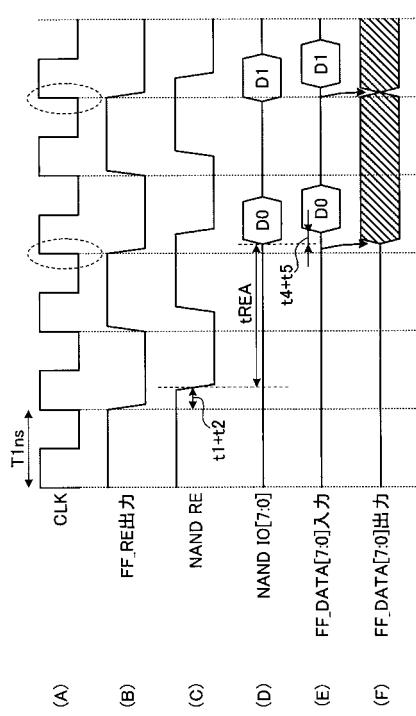

#### 【 0 0 3 7 】

図 9 および図 1 0 において、( A ) は内部 C L K 、( B ) は F F \_ R E 出力、( C ) は N A N D R E 、( D ) は N A N D I O [ 7 : 0 ] 、( E ) は F F \_ D A T A [ 7 : 0 ] 入力、( F ) は F F \_ D A T A [ 7 : 0 ] 出力を示している。

30

#### 【 0 0 3 8 】

図 9 に示すように、負荷容量が小さい場合には、t 1 および t R E A の C R 遅延が小さいため、内部クロック C L K のタイミングでデータを取得することができる。他方、図 1 0 に示すように、負荷容量が大きい場合には、t 1 および t R E A の C R 遅延が大きくなるため、内部クロック C L K のタイミングでデータを取得することができなくなってしまう。なお、ここでは、データリードの場合を説明したが、信号遅延によりライトエラーが発生する場合もある。このため、信号遅延を防止するために、N A N D メモリ 1 0 のアクセス (リード / ライト) 時に信号線 (バスライン) の負荷容量を低減する必要がある。

#### 【 0 0 3 9 】

##### [ N A N D メモリ 1 0 のリード / ライト時の負荷容量の低減 ]

図 1 1 ~ 図 1 5 を参照して、N A N D メモリ 1 0 のアクセス時に、信号線の負荷容量を低減して信号遅延を防止する方法について説明する。本実施の形態では、N A N D コントローラ 1 1 2 と C h i p 間の信号線の接続を切り替えるバススイッチを設け、N A N D メモリ 1 0 のリード / ライト時にアクセスしない C h i p との接続を遮断することにより、リード / ライト時の信号線の負荷容量を低減して信号遅延を防止する。

40

#### 【 0 0 4 0 】

##### ( 実施例 1 )

図 1 1 は、実施例 1 に係る N A N D コントローラ 1 1 2 および N A N D メモリ 1 0 を説明するための図である。図 1 1 において、上記図 6 と同様の機能を有する部位には同一符号を付しており、共通する部分の説明を省略する。実施例 1 は、図 1 1 に示すように、シ

50

システム基板上 120 にバススイッチ 300a を設けた構成である。なお、同図では、Ch 0 のみを図示しているが、他の Ch 1 ~ 3 についても同様にバススイッチが設けられている。また、同図において、217 は出力 IO を示している。

#### 【0041】

実施例 1 では、システム基板上 120 上に、IO 信号 IO0 ~ 7 および制御信号 (WE, RE, ...) の信号線の接続を、8StackChip10a1 と 8StackChip10a2 とで切り替えるためのバススイッチ 300a を配置した。IO 用のバススイッチ 300a は、8 ビット幅のスイッチが用いられており、制御信号用のバススイッチ 300a は、1 ビット幅のスイッチが用いられている。同図では、バススイッチ 300a を模式的に示しており、バススイッチ 300a は公知のバススイッチを使用することができる、その詳細な説明を省略する。NANDコントローラ 112 の NAND I/F 116 は、バススイッチ 300a の切り替えを制御するバススイッチ制御部 220 を備えている。

10

#### 【0042】

バススイッチ制御部 220 は、バススイッチ切替信号によりバススイッチ 300a の切替制御を実行し、リード / ライト時のアドレスに応じてバススイッチ 300a の上位 (8StackChip10a1 側) / 下位 (8StackChip10a2 側) の切り替えを行う。バススイッチ制御部 220 は、プロセッサ 104 から 8StackChip10a0 側のアクセス命令がきた場合には、バススイッチ切替信号 SEL = Low を、8StackChip10a1 側のアクセス命令がきた場合には、バススイッチ切替信号 SEL = High を、各バススイッチ 300a に出力する。バススイッチ制御部 220 は、ch 1 ~ ch 3 に設けられたバススイッチ (不図示) についても同様にその切り替えを制御する。

20

#### 【0043】

バススイッチ 300a は、バススイッチ切替信号 SEL = Low の場合は、8StackChip10a1 側を接続し、バススイッチ切替信号 (SEL) = High の場合は、8StackChip10a2 側を接続する。

30

#### 【0044】

これにより、8StackChip10a1 に対するリード / ライトの場合は、8StackChip10a2 が切断された状態であり、また、8StackChip10a2 に対するリード / ライトの場合は、8StackChip10a1 が切断された状態であるので、リード / ライト時の信号線の負荷容量を 1 / 2 にすることができる。

#### 【0045】

なお、実施例 1 では、負荷の分割数を 2 つとしているが、本発明はこれに限られるものではなく、NANDコントローラ 112 の pin 数や NAND メモリ 10 の負荷に応じて適宜分割することができる。

#### 【0046】

##### (実施例 2)

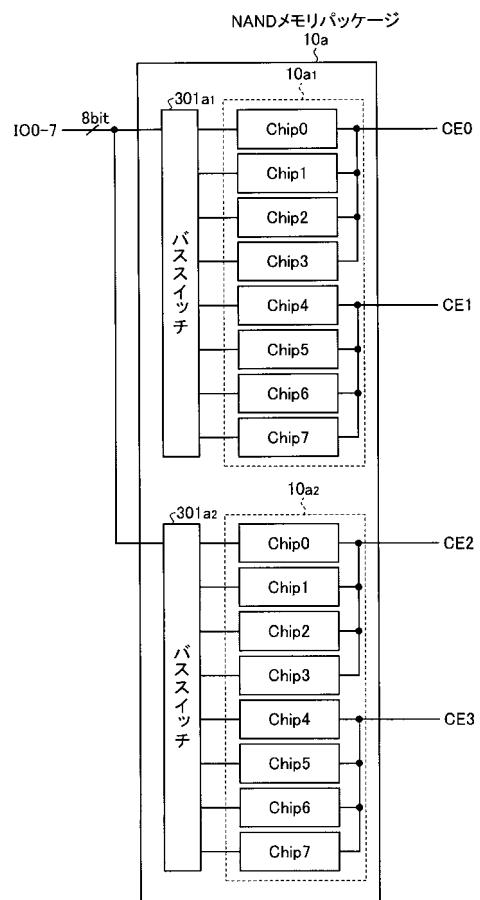

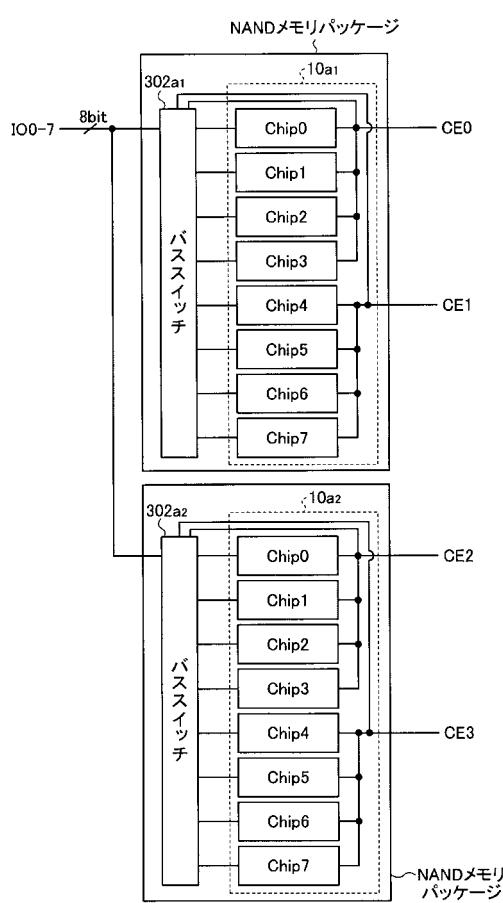

上記実施例 1 は、システム基板上 120 にバススイッチ 300a を設けた構成である。これに対して、実施例 2 は、各 NAND メモリ パッケージ 10a ~ 10d の内部にバススイッチを設けた構成である。図 12 は、実施例 2 に係る NAND メモリ 10 を説明するための図である。同図では、NAND メモリ パッケージ 10a のみを示しているが、NAND メモリ パッケージ 10b ~ 10d も同様な構成である。

40

#### 【0047】

同図に示すように、NAND メモリ パッケージ 10a の内部には、8StackChip10a1 の Chip 0 ~ 7 のいずれか 1 つを選択して接続するバススイッチ 301a1 と、8StackChip10a2 の Chip 0 ~ 7 のいずれか 1 つを選択して接続するバススイッチ 301a2 とが設けられている。バススイッチ 301a1、301a2 は、アクセスアドレスに基づいてアクセスする Chip を選択 (デコード) し、選択した Chip を接続する。実施例 2 では、バススイッチ 301a1、301a2 はアクセスアドレ

50

スに基づいてアクセスする Chip を選択する構成であるので、実施例 1 のように、バススイッチ制御部 220 (図 11 参照) を設ける必要がなくなる。

#### 【0048】

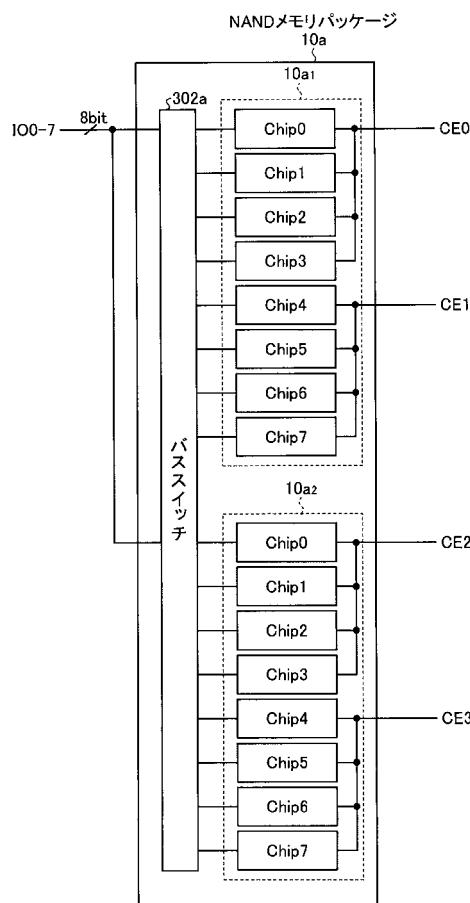

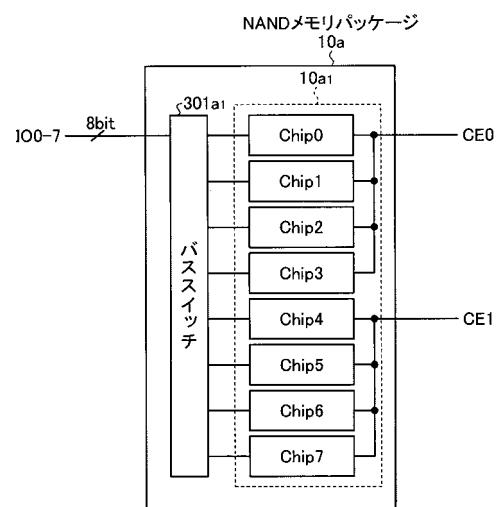

実施例 2 では、I/O 信号用のバススイッチ 301a、301b のみを示しているが、その他、WE / RE 等の制御信号全てに対して、バススイッチを設けることにしてよい。また、実施例 2 では、8StackChip10a1, 10a2 毎にバススイッチを設ける構成としたが、図 13-1 に示すように、8StackChip10a1, 10a2 の Chip の接続の切り替えを 1 つのバススイッチ 302a で行う構成としてもよい。また、図 13-2 に示すように、NAND メモリパッケージを 1 つの 8StackChip で構成し、8StackChip に 1 つのバススイッチを設ける構成としてもよい。また、図 13-3 に示すように、8StackChip 每に NAND メモリパッケージを構成し、各 8StackChip に 1 つのバススイッチを設けると共に、各 8StackChip で Chip が同時に選択されるのを防止するために、バススイッチ 301a1, 301a2 に、CE (チップイネーブル) 0 ~ 3 信号を入力する構成としてもよい。バススイッチ 301a1, 301a2 は CE (チップイネーブル) 0 ~ 3 信号に基づいて Chip 群を選択し、さらに、アクセスアドレスに基づいてアクセスする Chip を選択 (デコード) し、選択した Chip を接続する。これにより、本実施例 2 によれば、実施例 1 の効果に加えて、コントローラ側がバススイッチを制御する必要があり、またバススイッチがメモリに内蔵されるため部品数を減るため小型化を図ることができる。10

#### 【0049】

##### (実施例 3)

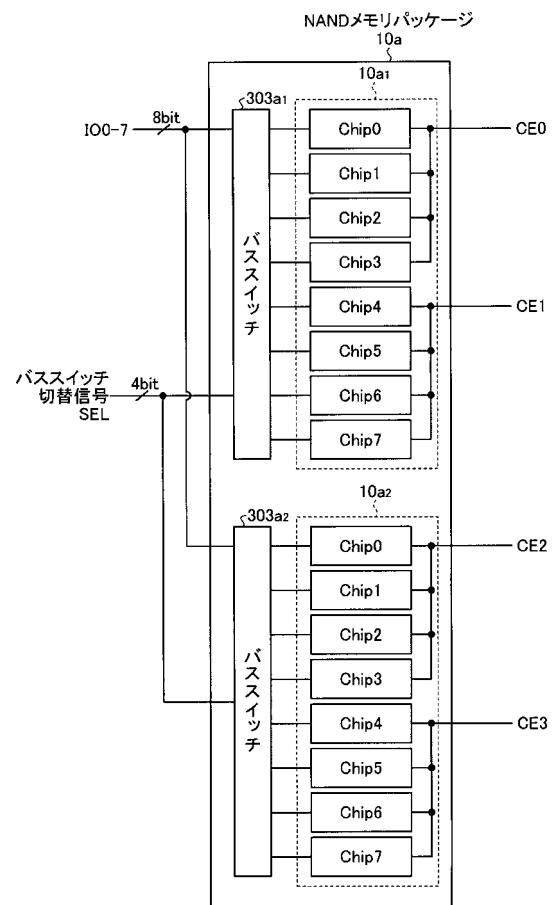

上記実施例 2 では、バススイッチ 301a1, 301a2 がアクセスアドレスに基づいてアクセスする Chip を選択する構成である。これに対して、実施例 3 は、バススイッチが NAND コントローラ 112 から入力されるバススイッチ切替信号 SEL に基づいて、Chip の接続の切り替えを行う構成である。図 14 は、実施例 3 に係る NAND メモリ 10 を説明するための図である。同図では、NAND メモリパッケージ 10a のみを示しているが、NAND メモリパッケージ 10b ~ 10d も同様な構成である。20

#### 【0050】

同図において、バススイッチ 303a1, 303a2 は、NAND コントローラ 112 から入力されるバススイッチ切替信号 SEL に基づいて、8StackChip10a1 の Chip 0 ~ 7 および 8StackChip10a2 の Chip 0 ~ 7 のいずれか 1 つを接続する。これにより、信号線の負荷容量を低減して信号遅延を防止することができる。なお、実施例 3 においても、実施例 2 の変形例 (図 13-1 ~ 図 13-3) のように構成することにしてよい。30

#### 【0051】

##### (実施例 4)

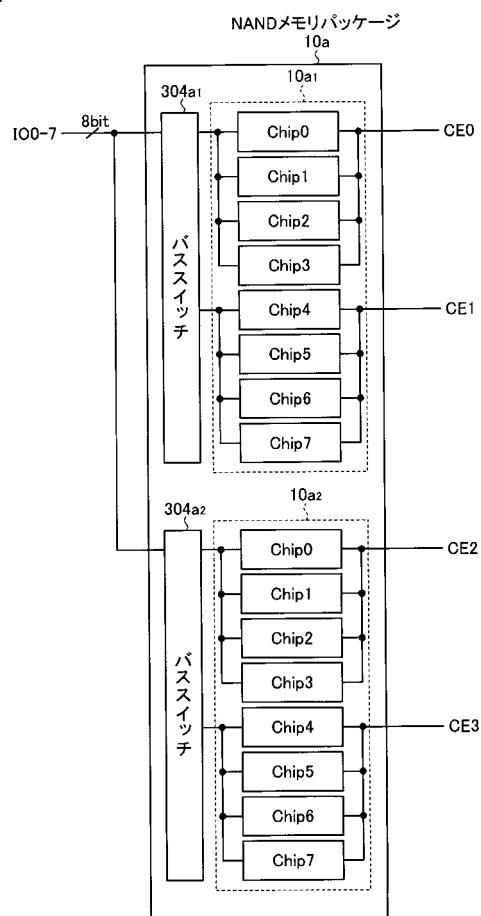

上記実施例 2 は、バススイッチにより NAND メモリ 10 の 1 つの Chip 単位で接続を切り替える構成である。これに対して、実施例 4 は、バススイッチにより NAND メモリ 10 の複数チップ単位で接続を切り替える構成である。図 15 は、実施例 4 に係る NAND メモリ 10 を説明するための図である。同図では、NAND メモリパッケージ 10a のみを示しているが、NAND メモリパッケージ 10b ~ 10d も同様な構成である。40

#### 【0052】

同図に示すように、8StackChip10a1 は、Chip 0 ~ 3 (チップ群) と Chip 4 ~ 7 (チップ群) の信号線がそれぞれ纏められており、すなわち、CE 信号の単位毎 (4 Chip 毎) に纏められている。同様に、8StackChip10a2 の信号線も CE 信号の単位毎 (4 Chip 毎) に纏められている。バススイッチ 304a1, 304a2 は、アクセスアドレスに基づいて、アクセスする Chip 群を選択し、選択した Chip 群に接続を切り替える。これにより、信号線の負荷容量を低減して信号遅延を防止することができる。なお、実施例 4 においても、実施例 2 の変形例 (図 13-1 ~ 図 13-3) のように構成することにしてよい。50

## 【0053】

なお、実施例1～実施例4は適宜組み合わせて実施可能であり、例えば、実施例1のように、システム基板120上にバススイッチを配置する場合においても、実施例2のように、バススイッチがアクセスアドレスに応じて信号線の接続を切り替える構成としてもよく、また、実施例2、4のように、バススイッチは、1または複数のChip単位で接続を切り替える構成としてもよい。

## 【0054】

以上説明したように、本実施の形態によれば、NANDコントローラ112とNANDメモリ10に搭載される複数のChip間の信号線の接続を切り替えるバススイッチを設けているので、NANDメモリ10にアクセスする場合に、バススイッチにより、アクセスするChipを接続する一方、アクセスしないChipとの接続を遮断することができ、NANDメモリ10に対するアクセス時の信号線の負荷容量を低減でき、NANDメモリ10の信号線の負荷容量が増大した場合においても、信号遅延を防止することが可能となる。

10

## 【0055】

また、バススイッチをシステム基板120上またはNANDメモリ10に搭載することとしたので、SSD100のレイアウトを考慮して、バススイッチを配置する位置を決定することが可能となる。

## 【0056】

また、NANDコントローラ112のNAND I/F116にリード/ライトアドレスに応じて、バススイッチの切り替えを指示するバススイッチ切替信号をバススイッチに出力するバススイッチ制御部110を設け、バススイッチは、バススイッチ切替信号に基づいて信号線の接続の切り替えを行うこととしたので、バススイッチの構成を簡素化することが可能となる。

20

## 【0057】

また、バススイッチは、リード/ライトアドレスに応じて、信号線の接続の切り替えを行うこととしたので、NANDコントローラ112の構成を簡素化することが可能となる。

30

## 【0058】

また、バススイッチは、1または複数のChip単位で信号線の接続の切り替えを行うこととしたので、NANDコントローラ112のpin数やNANDメモリ10の信号線の負荷容量に応じて、接続を切り替えるChip単位数を適宜選択することが可能となる。

## 【0059】

なお、上記実施の形態では、本発明を、NANDメモリを有するSSDに適用するようにしたが、NOR型などの他のフラッシュEEPROMを有するSSDに本発明を適用するようにしてもよい。

## 【図面の簡単な説明】

## 【0060】

【図1】SSD (Solid State Drive) の構成例を示すブロック図である。

40

【図2】NANDメモリチップに含まれる1個のブロックの構成例を示す回路図である。

【図3】ドライブ制御回路のハードウェア的な内部構成例を示すブロック図である。

【図4】NAND I/FとNANDメモリとの接続を説明するための図である。

【図5】NANDメモリの負荷容量およびCR遅延を説明するための図である。

【図6】NANDメモリの負荷容量およびCR遅延を説明するための図である。

【図7】NANDメモリからのデータの読み出しを説明するためのタイミングチャートである。

【図8】完全同期設計回路を説明するための図である。

【図9】負荷容量が小さい場合のタイミングチャートである。

【図10】負荷容量が大きい場合のタイミングチャートを示している。

50

【図11】実施例1に係るNANDコントローラおよびNANDメモリを説明するための図である。

【図12】実施例2に係るNANDコントローラおよびNANDメモリを説明するための図である。

【図13-1】実施例2の変形例1を説明するための図である。

【図13-2】実施例2の変形例2を説明するための図である。

【図13-3】実施例2の変形例3を説明するための図である。

【図14】実施例3に係るNANDコントローラおよびNANDメモリを説明するための図である。

【図15】実施例4に係るNANDコントローラおよびNANDメモリを説明するための図である。 10

#### 【符号の説明】

##### 【0061】

100 SSD

1 ホスト装置

2 ATAインターフェース(ATA I/F)

3 R S 2 3 2 C I / F

4 ドライブ制御回路

5 電源回路

6 LED

20

10 NANDメモリ

10a~d NANDメモリパッケージ

10a1, 10a2~10d1, 10d2 8 Stack Chip

20 DRAM

101 データアクセス用バス

102 第1の回路制御用バス

103 第2の回路制御用バス

104 プロセッサ

105 ブートROM

30

106 ROMコントローラ

107 クロックコントローラ

108 パラレルIO(PIO)回路

109 シリアルIO(SIO)回路

110 ATAインターフェースコントローラ(ATACコントローラ)

111 第2のECC(Error Check and Correct)回路

112 NANDコントローラ

113 DRAMコントローラ

114 SRAM

115 SRAMコントローラ

40

116 NAND I/F

117 第1のECC回路

118 DMAコントローラ

119 制御レジスタ

120 システム基板

220 バススイッチ制御部

300a, 301a, 302a, 303a, 304a バススイッチ

【図1】

【図2】

【図3】

【図4】

【図5】

【 図 6 】

【 図 7 】

【 四 8 】

【図 9】

【図 10】

【図 11】

【図 12】

【図 13-1】

【図 13-2】

【図 13-3】

【図 14】

【図15】