(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4474479号

(P4474479)

(45) 発行日 平成22年6月2日(2010.6.2)

(24) 登録日 平成22年3月12日(2010.3.12)

(51) Int.Cl.

F 1

|              |           |            |      |

|--------------|-----------|------------|------|

| HO1L 29/78   | (2006.01) | HO1L 29/78 | 301Q |

| HO1L 21/8238 | (2006.01) | HO1L 29/78 | 301S |

| HO1L 27/092  | (2006.01) | HO1L 29/78 | 301H |

| HO1L 29/786  | (2006.01) | HO1L 27/08 | 321C |

| HO1L 21/20   | (2006.01) | HO1L 27/08 | 321E |

請求項の数 4 (全 18 頁) 最終頁に続く

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2008-508953 (P2008-508953)  |

| (86) (22) 出願日 | 平成18年4月21日 (2006.4.21)        |

| (65) 公表番号     | 特表2008-539593 (P2008-539593A) |

| (43) 公表日      | 平成20年11月13日 (2008.11.13)      |

| (86) 國際出願番号   | PCT/US2006/015107             |

| (87) 國際公開番号   | W02006/116098                 |

| (87) 國際公開日    | 平成18年11月2日 (2006.11.2)        |

| 審査請求日         | 平成21年1月23日 (2009.1.23)        |

| (31) 優先権主張番号  | 11/116,053                    |

| (32) 優先日      | 平成17年4月27日 (2005.4.27)        |

| (33) 優先権主張国   | 米国(US)                        |

早期審査対象出願

|           |                                                                                                                                        |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 390009531<br>インターナショナル・ビジネス・マシーンズ・コーポレーション<br>INTERNATIONAL BUSINESS MACHINES CORPORATION<br>アメリカ合衆国10504 ニューヨーク州 アーモンク ニュー オーチャード ロード |

| (74) 代理人  | 100108501<br>弁理士 上野 剛史                                                                                                                 |

| (74) 代理人  | 100112690<br>弁理士 太佐 種一                                                                                                                 |

| (74) 代理人  | 100091568<br>弁理士 市位 嘉宏                                                                                                                 |

最終頁に続く

(54) 【発明の名称】電界効果トランジスタおよびCMOS回路

## (57) 【特許請求の範囲】

## 【請求項 1】

間にチャネルが配置され、間隔を空けてドープされたソース及びドレイン領域、及び、前記ソース及びドレイン領域と前記チャネルとの間に形成されたソース／ドレイン延長部を含む複合半導体領域と、

前記チャネル上に配置されたゲート誘電体と、

前記ゲート誘電体上に配置された導電性ゲートとを有する電界効果トランジスタ(FET)であって、

前記ゲートの下の前記複合半導体領域は、第1の表面配向を有する上部単結晶半導体と前記第1の表面配向とは異なる第2の表面配向を有する下部単結晶半導体とを含み、前記上部単結晶半導体及び前記下部単結晶半導体は接合界面で直接接しており、前記チャネルは前記第1の表面配向をもつ前記上部単結晶半導体内部にのみ位置付けられ、前記ソース及びドレイン領域の両方は、前記ソース及びドレイン領域の全体が、前記下部単結晶半導体の前記第2の表面配向を有する単結晶半導体内に配置され、かつ、前記ソース／ドレイン延長部は、深さ方向において前記上部単結晶半導体と前記下部単結晶半導体との両領域に跨るように形成された電界効果トランジスタ(FET)。

## 【請求項 2】

間にチャネルが配置され、間隔を空けてドープされたソース及びドレイン領域、及び、前記ソース及びドレイン領域と前記チャネルとの間に形成されたソース／ドレイン延長部を含む複合半導体領域と、

10

20

前記チャネル上に配置されたゲート誘電体と、

前記ゲート誘電体上に配置された導電性ゲートとを有する電界効果トランジスタ(FET)を含むCMOS回路であって、

前記ゲートの下の前記複合半導体領域は、第1の表面配向を有する上部単結晶半導体と前記第1の表面配向とは異なる第2の表面配向を有する下部単結晶半導体とを含み、前記上部単結晶半導体及び前記下部単結晶半導体は接合界面で直接接しており、前記チャネルは前記第1の表面配向をもつ前記上部単結晶半導体内部にのみ位置付けられ、前記ソース及びドレイン領域の両方は、前記ソース及びドレイン領域の全体が、前記下部単結晶半導体の前記第2の表面配向を有する単結晶半導体内に配置され、かつ、前記ソース／ドレイン延長部は、深さ方向において前記上部単結晶半導体と前記下部単結晶半導体との両領域に跨るように形成された電界効果トランジスタ(FET)を含む、CMOS回路。

10

#### 【請求項3】

前記チャネルは、Siを含み、横方向に隣接する前記ソース及びドレイン領域は、SiGe半導体である、請求項2に記載のCMOS回路。

#### 【請求項4】

ソース及びドレイン領域及びチャネルが単結晶半導体の单一の表面配向内に完全に含まれる別のFETをさらに含む、請求項2に記載のCMOS回路。

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

20

本発明は、n型電界効果トランジスタ(nFET)が電子移動度にとって最適な配向をもつ半導体内に配置され、p型電界効果トランジスタ(pFET)が正孔移動度にとって最適な異なる配向をもつ半導体内に配置される、相補型金属酸化膜半導体(CMOS)回路に関する。より具体的には、本発明は、最適に配向された半導体内に全体が形成されたFETの性能上の利点が、デバイスのチャネルのみを最適に配向された半導体内に配置することを必要とする構造体によって実現されるFET構造体に関する。また、本発明は、こうしたFETをハイブリッド配向基板上のCMOS回路内に組み込むことができる方法に関する。

#### 【背景技術】

#### 【0002】

30

本発明の半導体技術の相補型金属酸化膜半導体(CMOS)回路は、その動作のために電子キャリアを使用するn型電界効果トランジスタ(nFET)と、その動作のために正孔キャリアを使用するp型電界効果トランジスタ(pFET)とを含む。CMOS回路は、典型的には、通常の単結晶配向(100)を有するSiウェハ上に製造される。しかしながら、電子は((110)配向と比較して)(100)表面配向をもつSi内で高い移動度を有し、正孔は((100)配向と比較して)(110)表面配向をもつSi内で高い移動度を有するため、nFETを(100)配向Siに形成することができ、pFETを(110)配向Siに形成することができるよう、ハイブリッド配向基板上にCMOS回路を製造することに大いに関心がもたれている。

#### 【0003】

40

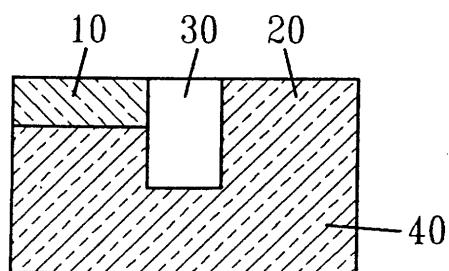

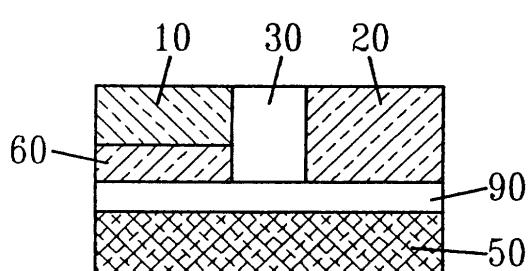

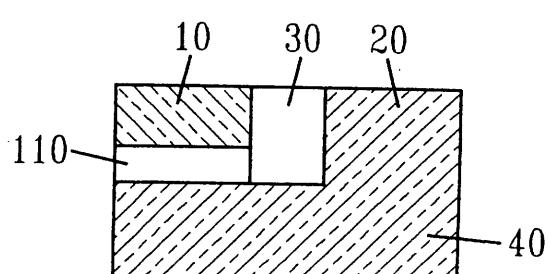

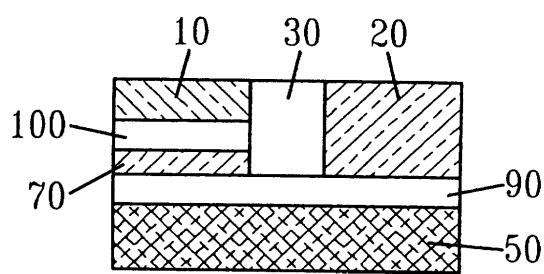

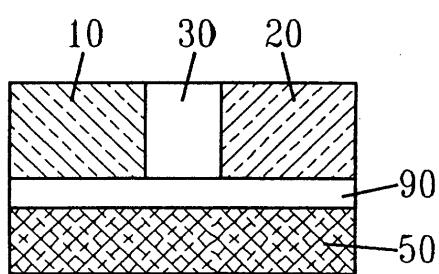

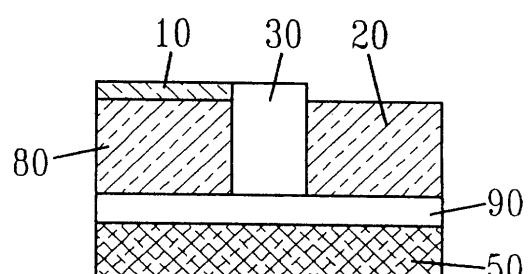

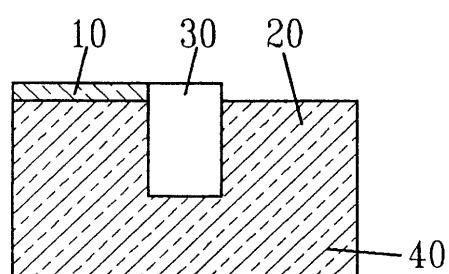

幾つかの従来技術のハイブリッド配向基板の例が図1乃至図7に示される。図示される従来技術の基板の全ては、10及び20と示され、絶縁体充填分離トレンチ30により分けられた、異なる配向をもつ単結晶半導体の同一平面上の表面領域、又は実質的に同一平面上の表面領域を含む。(ここで及び後続の図において、異なる方向の平行線模様が、異なる半導体の配向を示すために用いられる。)ベース基板40は、半導体領域20と同じ配向を有する単結晶半導体である。ベース基板50は、典型的には、特定されない配向の半導体又は絶縁体である。単結晶半導体領域60、70、及び80は、半導体領域20と同じ配向を有する。半導体領域10及び20は、図1及び図6の構造体に関してはバルク基板の一部を含み、図3、図4、図5、及び図7の構造体に関しては、埋め込み絶縁体層90及び/又は局部的な埋め込み絶縁体層100をもつ半導体オン・インシュレータ(S

50

O I ) 基板の一部を含み、図 2 の構造体に関しては、局部的な埋め込み絶縁層 110 をもつバルク / S O I 混合基板の一部を含む。図 4 の構造体は、半導体領域 10 と下方の半導体領域 70 との間に絶縁体の層を有するが、図 3 及び図 7 の構造体は、半導体領域 10 と下方の半導体領域 60 及び 80 との間に、直接半導体間接合 ( D S B ) 界面を有する。

#### 【 0 0 0 4 】

図 1 乃至図 7 に示される基板の製造方法は様々であるが、全ては、典型的には、( j , k ' 1 ' ) 配向の半導体ハンドル・ウェハ又はハンドル・ウェハ層に接合された ( j k 1 ) 配向半導体層から始まる。製造方法によって、接合は、( 例えば、半導体間の界面が得られるような ) 直接的なものであってもよいし、又は、( 例えば、酸化物又は他の絶縁層が少なくともある区域で接合界面に残る接合のような ) 間接的なものであってもよい。

10 図 1 乃至図 5 の基板構造体を製造するためには、( j k 1 ) 配向半導体層の選択領域は、( 必要に応じて、任意の露出された埋め込み絶縁体領域と共に ) 基板の ( j ' k ' 1 ' ) 配向を有する半導体と置き換えられる。こうしたことは、例えば、( j k 1 ) 配向半導体が最初に選択領域内でエッティングによって除去されて、下方の ( j ' k ' 1 ' ) 配向半導体を露出させる開口部を形成し、次いで、基板の配向を有するエピタキシャル成長半導体により置き換えられる ( 例えば、特許文献 1 に記載される ) トレンチ / エピタキシャル成長プロセスにより行うことができる。代替的には、( j k 1 ) 配向半導体の選択領域が最初に D S B 界面の下の深さまでアモルファス化され、次いで、下方の ( j ' k ' 1 ' ) 配向半導体をテンプレートとして用いてエピタキシャル再結晶化される、( 例えば、特許文献 2 に記載される ) アモルファス化 / テンプレート再結晶化 ( A T R ) プロセスを用いることができる。例えば、特許文献 2 及び特許文献 3 に記載されるように、付加的なプロセスのステップを実行して、埋め込み絶縁体層 90 、 100 、及び 110 を導入するか又は強化することができる。図 6 乃至図 7 の構造体は、典型的には、( 例えば、特許文献 4 に記載される ) 現場接合技術により、或いは、( j ' k ' 1 ' ) 配向基板層に直接的に接合された ( j k 1 ) 配向半導体層の領域を単にエッティングによって除去することにより製造される。

20

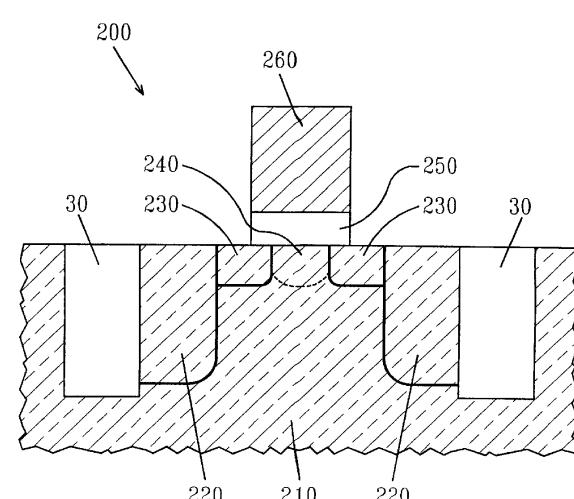

#### 【 0 0 0 5 】

今まで、こうしたハイブリッド配向基板内に製造された C M O S 回路内の全ての n F E T 及び p F E T は、共通して 1 つの特徴を有するが、それは、各々の F E T のチャネル及びソース / ドレイン領域は、その F E T キャリアの移動度を最適化するように選択された单一の配向を有する半導体内に形成されることである。こうした従来の F E T の例は図 8 に示されるが、そこでは、単一配向半導体 210 に形成された F E T 200 は、絶縁体充填分離トレンチ 30 により境界付けられたソース及びドレイン領域 220 と、ソース / ドレイン延長部 230 と、( 領域 240 内部の ) 半導体チャネル領域と、ゲート誘電体 250 と、導電性ゲート 260 とを含む。( 境界内の半導体材料が実際のソース / ドレイン及びソース / ドレイン延長部を構成するのであっても、明確にするために、後続の図におけるソース / ドレイン領域及びソース / ドレイン延長部は、これらの境界に関連する表示で識別することができる。 ) ウェル注入領域、ハロ注入部、ゲート上の側壁スペーサ、隆起ソース / ドレイン、ゲート・コンタクト、ソース / ドレイン・コンタクト、チャネル応力を生成するオーバーレイヤ及び / 又は置き換えソース / ドレイン領域等のような、共通の及び / 又は有利な他の F E T 構成要素は、存在してもよいが図 8 には示されない。

30

40

#### 【 0 0 0 6 】

図 8 の形状をもつ F E T は、単結晶半導体 10 及び 20 が、( 半導体 20 の場合は ) 同じ配向のバルク半導体によって、又は ( 半導体 10 の場合は ) 下の絶縁体層によって下方で境界付けられる図 2 、図 4 、又は図 5 の構造体を有するハイブリッド配向基板に関しては何の問題ももたらさない。しかしながら、こうした F E T 形状は、( j k 1 ) 配向領域 10 が ( j ' k ' 1 ' ) 配向領域 60 、 70 、又は 80 により下方で境界付けられる図 1 、図 3 、図 6 及び図 7 の構造体を有するハイブリッド配向基板とは適合性が低く、これは、F E T が「薄く」なければならない ( 即ち、ソース / ドレイン領域は接合された ( j k 1 ) 配向半導体層よりも浅くなければならない ) ため、言い換えると、ソース / ドレイン

50

領域の深さよりも厚い( j k l )配向 D S B 層に配置されなくてはならないためである。バルク半導体内の多くの C M O S 回路は深いソース / ドレインをもつ F E T を使用し、ハイブリッド配向基板は、典型的には、D S B 層が薄いときには形成するのが容易であるので、こうした制約はかなり限定的である可能性がある。再結晶化された半導体材料の欠陥性は、( D S B 層の厚さよりも大きくすることを余儀なくされる)アモルファス化の深さに伴って増加する傾向にあるため、薄い D S B 層は、A T R 技術により製造されたハイブリッド基板にとって特に望ましい。例えば、N . B u r b u r e 及び K . S . J o n e s ( 非特許文献 1 ) は、A T R の後で酸化物充填トレンチによりパターン形成された S i 基板上に残されたコーナ欠陥の横方向寸法は、アモルファス化注入の深さに正比例することを示している。

10

## 【 0 0 0 7 】

【特許文献 1】米国特許出願番号第 1 0 / 2 5 0 , 2 4 1 号

【特許文献 2】米国特許出願番号第 1 0 / 7 2 5 , 8 5 0 号

【特許文献 3】米国特許出願番号第 1 0 / 9 0 2 , 5 5 7 号

【特許文献 4】米国特許出願番号第 1 0 / 9 7 8 , 5 5 1 号

【非特許文献 1】材料研究学会、シンポジウム会報、8 1 0 C 4 . 1 9 . 2 0 0 4 年 1 月

## 【発明の開示】

## 【発明が解決しようとする課題】

## 【 0 0 0 8 】

従って、F E T 全体( 即ちそのソース / ドレイン及びチャネル ) を最適な配向をもつ半導体内に製造する必要なく、半導体の最適な配向において製造された F E T の利点及び性能を有する F E T 構造体を有することが望ましい。

20

## 【 0 0 0 9 】

従って、本発明の目的は、F E T 全体( 即ち、チャネル及びソース / ドレイン ) を最適配向の半導体内に製造する必要なく、最適配向の半導体内に全体が製造された従来の F E T の利点及び性能を有する F E T 構造体を提供することである。

## 【 0 0 1 0 】

本発明の関連する目的は、F E T の移動度にとって最適な配向を有する半導体の層が可能な限り薄いハイブリッド配向基板内に配置された、最適配向の半導体内に全体が製造された従来の F E T の利点及び性能を有する F E T 構造体を提供することである。

30

## 【 0 0 1 1 】

本発明のさらに別の目的は、バルク基板及び / 又は S O I ハイブリッド配向基板内に C M O S 回路を設けることであり、前述の C M O S 回路は、上述の目的のうちの少なくとも 1 つを満たす本発明の F E T のうちの少なくとも 1 つと、少なくとも 1 つの他の従来の F E T とを含む。

## 【課題を解決するための手段】

## 【 0 0 1 2 】

上記に列挙した目的及び他の目的によれば、F E T チャネルが第 1 の単結晶配向をもつ上部単結晶半導体層内に含まれ、F E T のソース / ドレイン領域の少なくともある部分が、異なる配向を有する下方の直接半導体接合単結晶半導体内に含まれる F E T 構造体が提供される。より一般的には、ソース / ドレイン領域を含む半導体の少なくともある部分が、チャネルを含む半導体の少なくともある部分の配向とは異なる配向を有する F E T 構造体が提供される。下方の単結晶半導体は、バルク半導体又は半導体オン・インシュレータ層とすることができます。S i 、G e 及び S i G e 合金半導体の場合は、結晶学的配向は、典型的には、( 1 1 0 )、( 1 1 1 )、及び( 1 0 0 )を含む群から選択される。

40

## 【 0 0 1 3 】

本発明の基本的な F E T 構造体の幾つかの実施形態が提供される。例えば、直接接合表面半導体層及び下方の異配向半導体は、例えば S i 及び S i G e のように、同じ又は異なる半導体材料を含むことができる。所与の配向の半導体領域は、層状半導体のような 2 つ以上の半導体材料をさらに含むことができる。ソース、ドレイン、及びチャネル領域を含

50

む半導体は、歪み半導体、非歪み半導体、又は、歪み領域と非歪み領域の複合半導体であつてもよい。また、ソース／ドレイン領域は、例えば、Siソース／ドレイン領域がSiGeと置き換えられた場合のように、元のソース／ドレイン領域の一部が異なる半導体材料と置き換えられた場合と同様に、横方向に隣接する半導体領域とは異なる材料を含むことができる。従来のFETと関連して上述された他の共通の及び／又は有利な特徴は、本発明のFET構造体に同様に組み込むことができる。

#### 【0014】

また、本発明は、バルク基板及び／又はSOIハイブリッド配向基板内にCMOS回路を提供するものであり、前述のCMOS回路は、（上述の本発明のFET構造体によるような）ソース／ドレイン及びチャネルが単結晶半導体の単一配向内に完全には含まれない少なくとも1つのFETと、（従来のFET構造体によるような）ソース／ドレイン及びチャネル領域が単結晶半導体の単一配向内に完全に含まれる少なくとも1つの他のFETとを含む。10

#### 【発明を実施するための最良の形態】

#### 【0015】

これら及び他の特徴、様様、及び利点は、本発明の以下の詳細な説明からより容易に明らかになり、より良く理解されるであろう。

#### 【0016】

ソース／ドレイン領域を含む半導体の少なくともある部分が、チャネルを含む半導体の少なくともある部分の配向とは異なる配向を有するFET構造体を提供する本発明をここでさらに詳細に説明する。本発明のFET構造体の下方の単結晶半導体は、バルク半導体又は半導体オン・インシュレータ層とすることができる。図9乃至図20の実施形態は、下方の単結晶半導体がバルク半導体である場合について示される。20

#### 【0017】

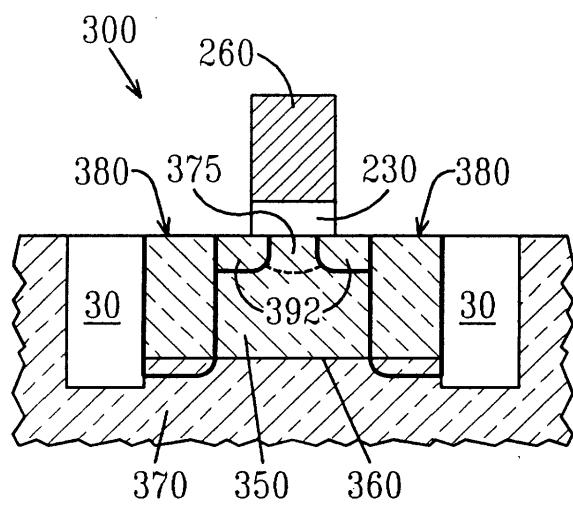

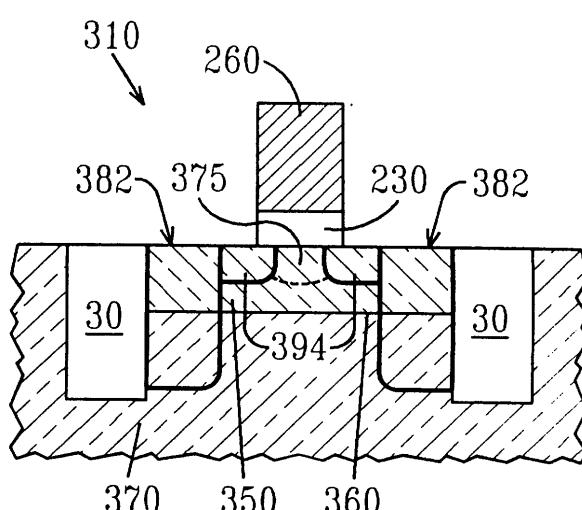

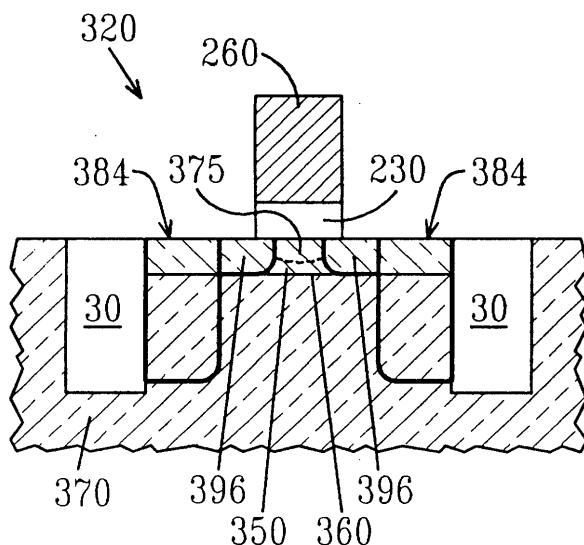

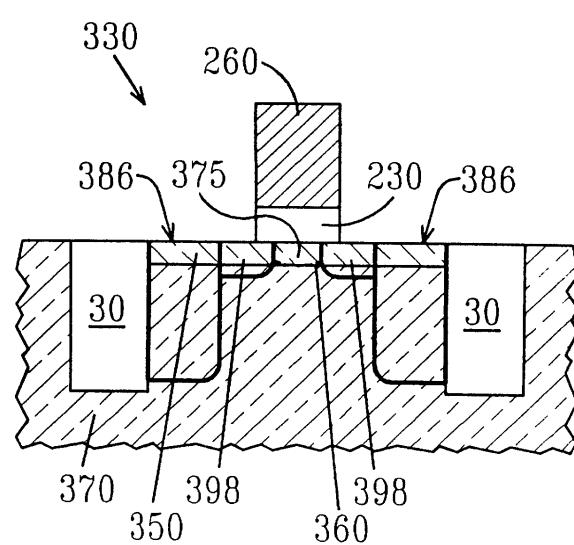

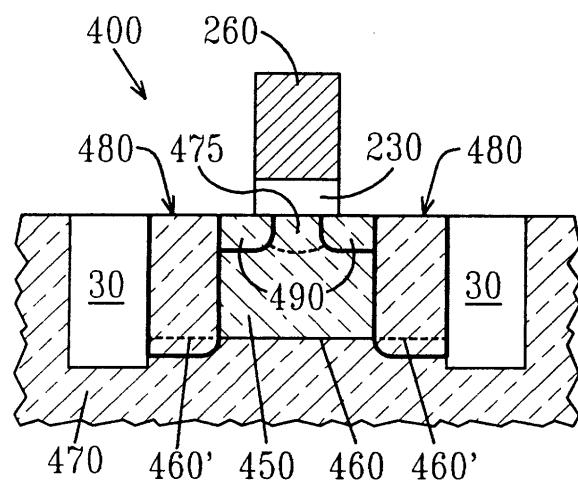

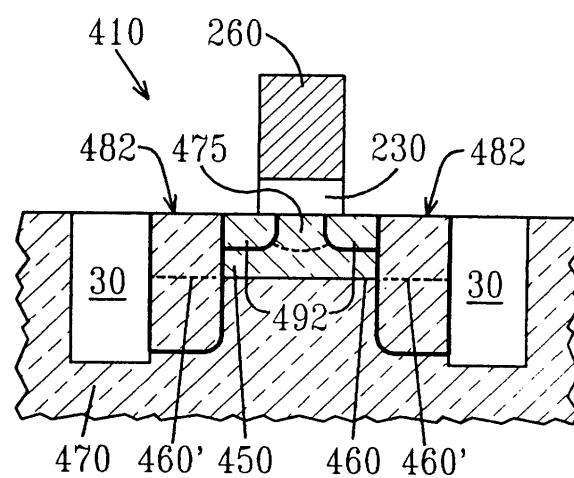

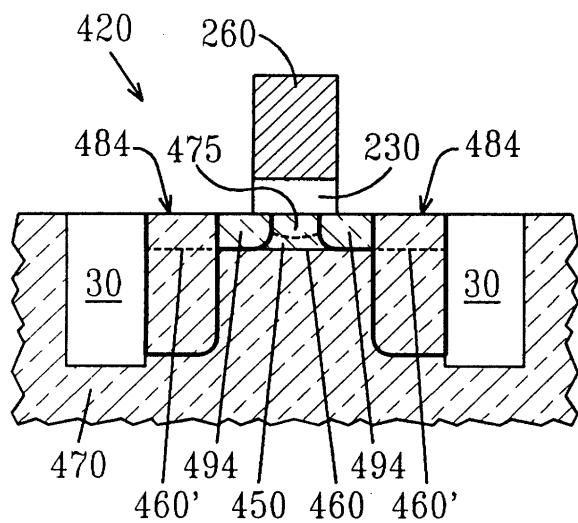

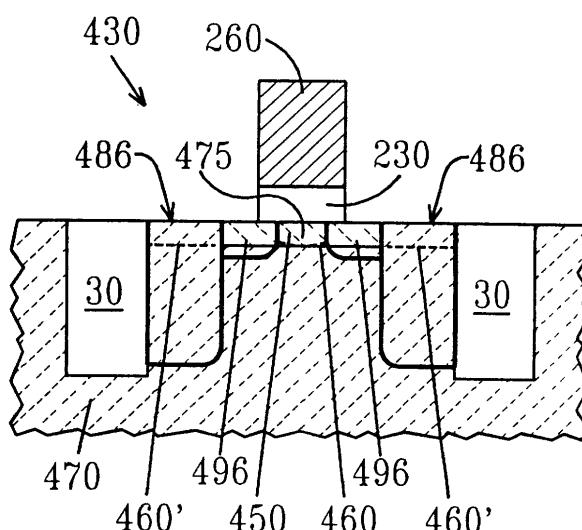

図9乃至図12は、ソース／ドレイン領域の上部分はチャネルと同じ配向を有し、ソース／ドレイン領域の下部分はチャネルの配向とは異なる配向を有する場合の本発明のFETを示す。図9乃至図12のFET300、310、320、及び330は、第1の配向を有し、第1の配向とは異なる第2の配向を有する下部単結晶半導体370に接合界面360で結合された上部単結晶半導体層350を含む。図8のFET200の要素と同様である、図9乃至図12のFETの各々における要素は、ゲート導体260、ゲート誘電体230、及び絶縁体充填分離トレンチ30を含む。さらに図9乃至図12のFETの各々に含まれるのは、上部単結晶半導体350内の（領域375内部の）半導体チャネル領域、ソース／ドレイン領域380、382、384、又は386、及び任意のソース／ドレイン延長部領域392、394、396、又は398である。30

#### 【0018】

図9乃至図12においては、接合界面360の上のソース／ドレイン領域は上部単結晶半導体350の配向を有し、接合界面360の下のソース／ドレイン領域は下部単結晶半導体370の配向を有して、ソース／ドレインの各々の部分は、横方向に隣接する半導体材料と同じ結晶配向を有するようになっている。FET300、310、320、及び330は、ソース／ドレイン領域の底部に対する接合界面360の位置についてのみ異なっている。FET300、310、及び320においては、任意のソース／ドレイン延長部392、394及び396は、完全に上部単結晶半導体層350内に配置される。FET300においては、接合界面360はソース／ドレイン領域380の底部の方向に位置し、ソース／ドレイン380はほとんどが上部単結晶半導体層350内に残る。FET310においては、接合界面360はソース／ドレインの厚さの約半分に相当する深さに位置し、ソース／ドレイン382は上部単結晶半導体層350と下部単結晶半導体層370との間でほぼ均等に分けられた状態である。FET320においては、接合界面360は、（存在する場合は）任意のソース／ドレイン延長部396の底部とほぼ等しい深さで、ソース／ドレイン領域384の上面の方向に位置し、ソース／ドレイン384はほとんどが下部単結晶半導体層370内に残る。FET330においては、接合界面360は、（F40

E T 3 2 0 におけるその位置と比較して) より一層表面の近くにある。F E T 3 3 0 内のソース / ドレイン領域 3 8 6 は、ほぼ完全に下部単結晶半導体層 3 7 0 内に配置され、(存在する場合は) 任意のソース / ドレイン延長部 3 9 8 は、上部単結晶半導体層 3 5 0 と下部単結晶半導体層 3 7 0 との間でほぼ均等に分けられる。

#### 【 0 0 1 9 】

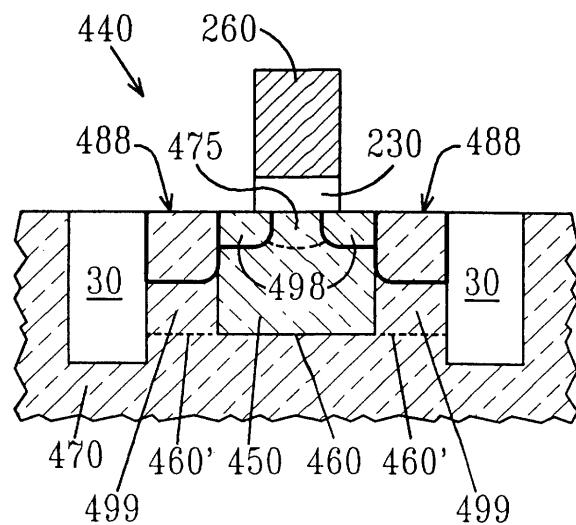

図 1 3 乃至図 1 7 は、ソース / ドレイン領域の全体が、チャネルの配向とは異なる配向を有する場合の本発明の F E T を示す。図 1 3 乃至図 1 7 の F E T 4 0 0 、 4 1 0 、 4 2 0 、 4 3 0 、 及び 4 4 0 は、第 1 の配向を有し、第 1 の配向とは異なる第 2 の配向を有する下部単結晶半導体 4 7 0 に接合界面 4 6 0 で結合された上部単結晶半導体層 4 5 0 を含む。図 8 の F E T 2 0 0 の要素と同様の図 1 3 乃至図 1 7 の要素は、ゲート導体 2 6 0 、ゲート誘電体 2 3 0 、及び絶縁体充填分離トレンチ 3 0 を含む。さらに図 1 3 乃至図 1 7 の F E T の各々に含まれるのは、上部単結晶半導体 4 5 0 内の(領域 4 7 5 内部の) 半導体のチャネル領域、ソース / ドレイン領域 4 8 0 、 4 8 2 、 4 8 4 、 4 8 6 、又は 4 8 8 及び任意のソース / ドレイン延長部領域 4 9 0 、 4 9 2 、 4 9 4 、 4 9 6 、又は 4 9 8 である。点線 4 6 0 ' は、接合界面 4 6 0 が、図 1 3 乃至図 1 6 におけるソース / ドレイン領域 4 8 0 、 4 8 2 、 4 8 4 、又は 4 8 6 の中まで、或いは図 1 7 におけるソース / ドレイン領域 4 8 8 の下の半導体領域 4 9 9 の中まで横方向に延ばされる位置を示す。接合界面 4 6 0 がソース / ドレイン領域からなくされるプロセスのステップは、図 2 5 乃至図 2 7 と関連して後述される。

#### 【 0 0 2 0 】

図 1 3 乃至図 1 7 においては、チャネル領域 4 7 5 及び任意のソース / ドレイン延長部 4 9 0 、 4 9 2 、 4 9 4 、 4 9 6 、及び 4 9 8 は、上部単結晶半導体 4 5 0 の配向を有し、ソース / ドレイン領域全体は下部単結晶半導体 4 7 0 の配向を有する。図 9 乃至図 1 2 の F E T とは対照的に、点線 4 6 0 ' より上のソース / ドレイン領域は、横方向に隣接する半導体とは異なる結晶配向を有する。図 1 3 乃至図 1 6 の F E T 4 0 0 、 4 1 0 、 4 2 0 、 及び 4 3 0 は、ソース / ドレイン領域の底部に対する接合界面 4 6 0 の位置についてのみ異なっている。F E T 4 0 0 、 4 1 0 、 4 2 0 、 及び 4 4 0 においては、任意のソース / ドレイン延長部 4 9 0 、 4 9 2 、 4 9 4 、及び 4 9 8 は、完全に上部単結晶半導体層 4 5 0 内に配置される。F E T 4 0 0 においては、接合界面 4 6 0 はソース / ドレイン領域 4 8 0 の底部の方向に位置し、ソース / ドレイン 4 8 0 はほとんど上部単結晶半導体 4 5 0 に隣接する下部単結晶半導体層 4 7 0 の上部領域内に残る。F E T 4 1 0 においては、接合界面 4 6 0 はソース / ドレインの厚さの約半分に相当する深さに位置し、ソース / ドレイン 4 8 2 は上部単結晶半導体層 4 5 0 と下部単結晶半導体層 4 7 0 との間でほぼ均等に分けられた状態である。F E T 4 2 0 においては、接合界面 4 6 0 は、(存在する場合は) 任意のソース / ドレイン延長部 4 9 4 の底部とほぼ等しい深さで、ソース / ドレイン領域 4 8 4 の上面の方向に位置し、ソース / ドレイン 4 8 4 はほとんど下部単結晶半導体層 4 7 0 内にある。F E T 4 3 0 においては、接合界面 4 6 0 は、(F E T 4 2 0 におけるその位置と比較して) より一層表面の近くにある。F E T 4 3 0 内のソース / ドレイン領域 4 8 6 は、ほぼ完全に下部単結晶半導体 4 7 0 内に配置され、(存在する場合は) 任意のソース / ドレイン延長部 4 9 6 は、上部単結晶半導体層 4 5 0 と下部単結晶半導体層 4 7 0 との間でほぼ均等に分けられる。

#### 【 0 0 2 1 】

また、図 1 7 の F E T は、ソース / ドレイン領域 4 8 8 の下であり、かつ点線 4 6 0 ' より上に配置された半導体領域 4 9 9 を含む。領域 4 9 8 及び 4 9 9 を形成するためのプロセスのステップは、図 2 5 乃至図 2 7 と関連して後述される。

#### 【 0 0 2 2 】

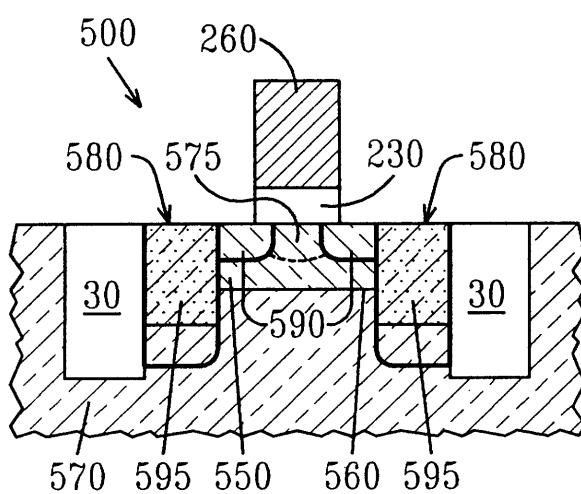

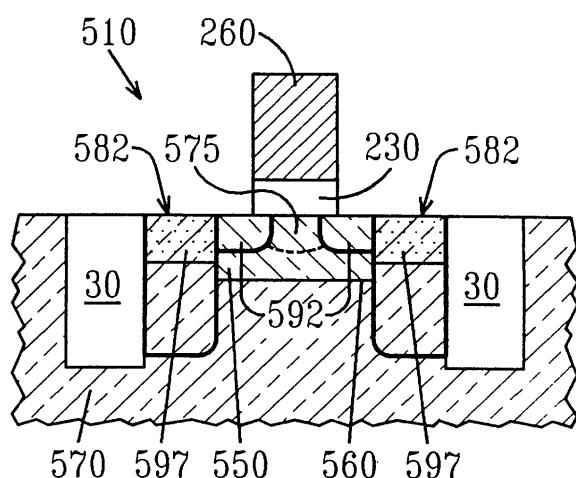

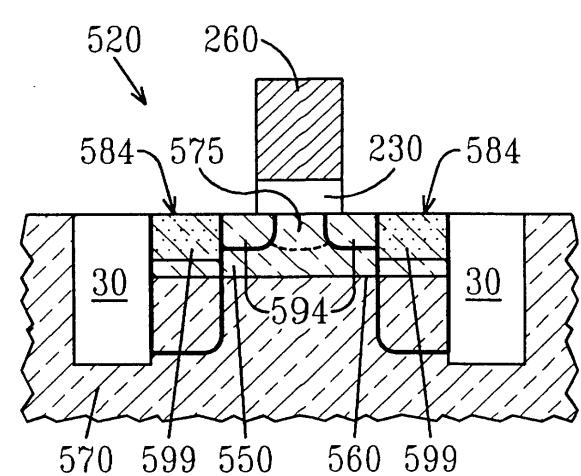

図 1 8 乃至図 2 0 は、ソース / ドレイン領域(及び / 又はソース / ドレイン延長部領域) の少なくともある部分が、元のソース / ドレイン領域の一部が除去されて、次に 1 つ又は複数の異なる半導体材料と置き換えられる場合のように、横方向に隣接する半導体領域とは異なる半導体材料を含む場合の本発明の F E T を示す。図 1 8 乃至図 2 0 の F E T 5

10

20

30

40

50

00、510、及び520は、第1の配向を有し、第1の配向とは異なる第2の配向を有する下部単結晶半導体570に接合界面560で結合された上部単結晶半導体層550を含む。図8のFET200の要素と同様の図18乃至図20のFETの各々の要素は、ゲート導体260、ゲート誘電体230、及び絶縁体充填分離トレンチ30を含む。さらに図18乃至図20のFETの各々に含まれるのは、上部単結晶半導体550内の（領域575内部の）半導体のチャネル領域、ソース／ドレイン領域580、582、又は584、及び任意のソース／ドレイン延長部領域590、592、又は594である。図18においては、FET500のソース／ドレイン領域580内の半導体595の材料は、下部単結晶半導体570の配向を有し、かつ上部単結晶半導体層の材料とは異なっている。図19のFET510は、ソース／ドレイン領域582内の半導体597の材料は、下部単結晶半導体570の配向を有し、上部単結晶半導体層550の材料とは異なっている点で図18のFET500と同様である。FET510は、FET500の半導体595は界面560より下に延びるが、FET510内の半導体597は延びないという点でFET500とは異なっている。図20においては、FET520のソース／ドレイン領域584内の半導体599の材料は、上部単結晶半導体層550の配向を有し、かつ上部単結晶半導体層の材料とは異なっている。領域595、597、及び599を形成するためのプロセスのステップは、図28乃至図31に関連して後述される。

## 【0023】

図18乃至図20のFETの形状は、例えば、Siソース／ドレイン材料を除去し、それをSiGeと置き換えることにより歪みチャネルを生成するのに用いることができる。（100）配向SiGeは（110）配向SiGeよりも容易に成長すると期待されるため、この手法は、上部単結晶半導体が（110）配向Siであり、ソース／ドレイン領域が、（100）配向をもつ下方のSi半導体から型造られる（100）配向SiGeにより置き換えられる場合に特に有利である。

## 【0024】

図9乃至図20のソース／ドレイン延長部は、チャネルと同じ配向を有するものとして示される。こうした配向は、（延長部とチャネルとの間の粒界欠陥を避けるために）延長部にとっては好ましい配向であるが、延長部が、ソース／ドレイン領域内の横方向に隣接する半導体と同じ配向を（こうした配向がチャネルの配向とは異なるときに）有することが望ましい幾つかの場合があり得る。従って、こうした特徴をもつ実施形態もまた本発明の範囲内である。

## 【0025】

同様に、図9乃至図20のチャネルは、完全に上部単結晶半導体内部に入るように示されるが、幾らかのチャネルが上部単結晶半導体内部に存在し、幾らかは下の異なる配向の半導体内に存在することが望ましい場合があり得る。従って、こうした特徴をもつ実施形態もまた本発明の範囲内である。

## 【0026】

直接的接合表面半導体層、下方の異配向半導体、及びソース／ドレイン領域内の任意の付加的な半導体は、同じ又は異なる半導体材料を含むことができ、Si、SiC、SiGe、SiGeC、Ge合金、Ge、C、GaAs、InAs、InP並びに他のII - V族又はII - VI族の複合半導体を含む群から選択することができる。また、1つ又は複数のドーパントをもつ又はもたない（例えばSiGe上のSi層のような）前述の半導体材料の層状の組み合わせ又は合金もここで検討される。ソース、ドレイン、チャネル、及び他の半導体領域を含む半導体は、所望の通りに、As、B、C、P、Sb及び／又は他の種でドープすることができる。ソース、ドレイン、及びチャネル領域を含む半導体は、歪み半導体、非歪み半導体、又は、歪み領域と非歪み領域の複合半導体とすることができます。Si、Ge、及びSiGe合金半導体の場合は、結晶学的配向は、典型的には、（110）、（111）、及び（100）を含む群から選択される。

## 【0027】

（ウェル注入領域、ハロ注入部、ゲート上の側壁スペーサ、隆起ソース／ドレイン、ゲ

10

20

30

40

50

ート・コンタクト、ソース／ドレイン・コンタクト、チャネル応力を誘起するように設計されたオーバーレイヤ及び／又は置き換えソース／ドレイン領域等の）従来のFETに関連して上述された他の共通の及び／又は有利な特徴、並びに、ソース／ドレイン及びソース／ドレイン延長部注入のより最適化された位置決めは、同様に本発明のFET構造体に組み込むことができる。

#### 【0028】

全ての場合において、本発明のFET構造体は、間にチャネルが配置された、間隔を空けてドープされたソース及びドレイン領域を含む複合半導体領域と、前述のチャネル上に配置されたゲート誘電体と、前述のゲート誘電体上に配置された導電性ゲートとを含み、前述のゲートの下の前述の複合半導体領域は、第1の配向を有する上部単結晶半導体と、第2の配向を有する下部単結晶半導体とを含み、前述の上部単結晶半導体及び下部単結晶半導体は接合界面で直接接しており、前述のチャネルの少なくともある部分は前述の第1の配向をもつ前述の上部単結晶半導体内に配置され、前述のソース及びドレイン領域の少なくともある部分は前述の下部単結晶半導体の配向を有する半導体内に配置される。

10

#### 【0029】

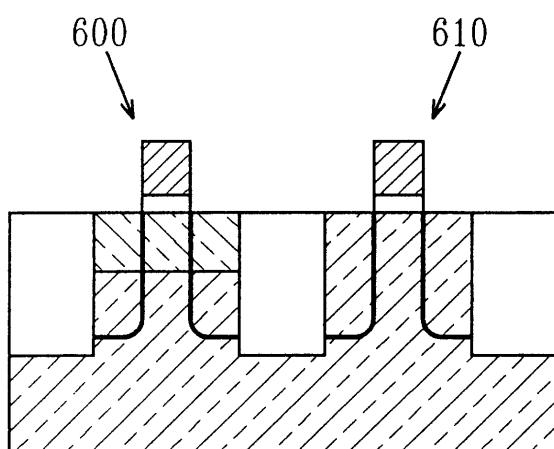

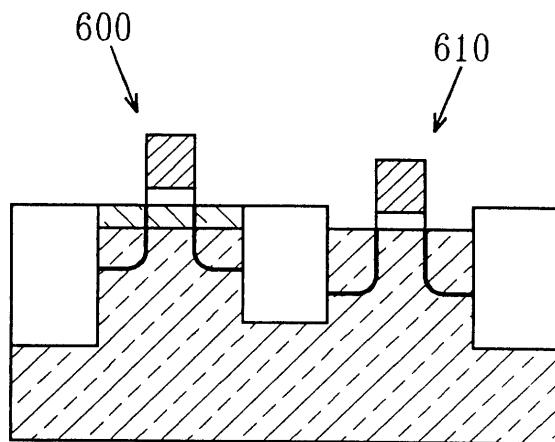

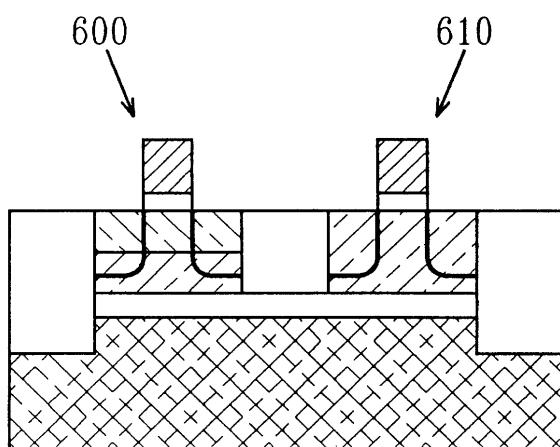

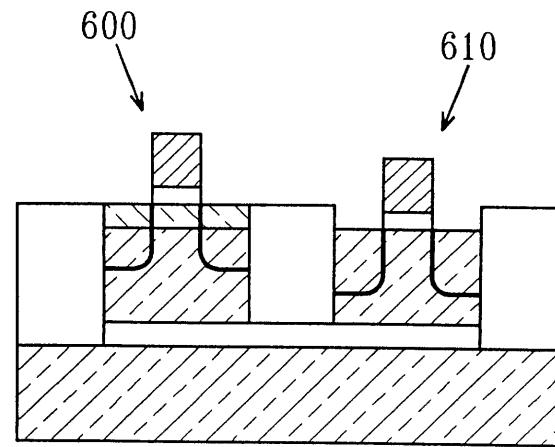

本発明の別の態様においては、ハイブリッド配向基板内にCMOS回路が提供され、前述のCMOS回路は、ソース／ドレイン及びチャネルが単結晶半導体の单一配向内に完全には含まれない少なくとも1つのFET（即ち本発明のFET）を含む。こうした回路は、典型的には、ソース／ドレイン及びチャネル領域が単結晶半導体の单一配向内に完全に含まれる少なくとも1つの他のFET（即ち従来のFET）を有する。図21乃至図24に示されるように、こうしたCMOS回路は、（例えば、図21及び図22に示される、図1及び図6の基板のような）バルク状の特性、又は、（例えば、図23及び図24に示される、図3及び図7の基板のような）半導体オン・インシュレータの特性を提供するハイブリッド配向基板上に配置することができる。図21乃至図24のFET600及び610は、本発明のFET及び従来のFETにそれぞれ相当し、FET600及び610のうちの一方はnFETであり、他方はpFETである。

20

#### 【0030】

ハイブリッド配向基板、本発明のFET構造体、及びそれらが組み込まれるCMOS回路を製造するためのプロセスのステップは、一般的に従来技術ではよく知られている。本発明のFET及びCMOS回路を作成するために必要とされる唯一の付加的なステップは、DSB層の底部の下に延びる注入領域を生成するソース／ドレイン注入条件の選択である。しかしながら、最終的にFETのソース／ドレイン領域の上部分がチャネルとは異なる配向及び／又は材料になり得る方法を詳述する価値はある。

30

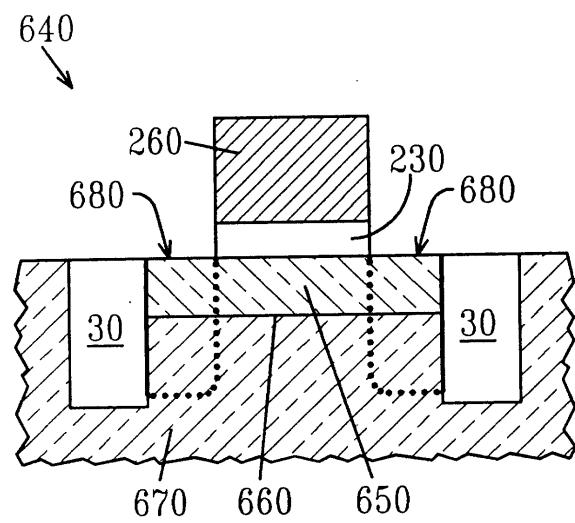

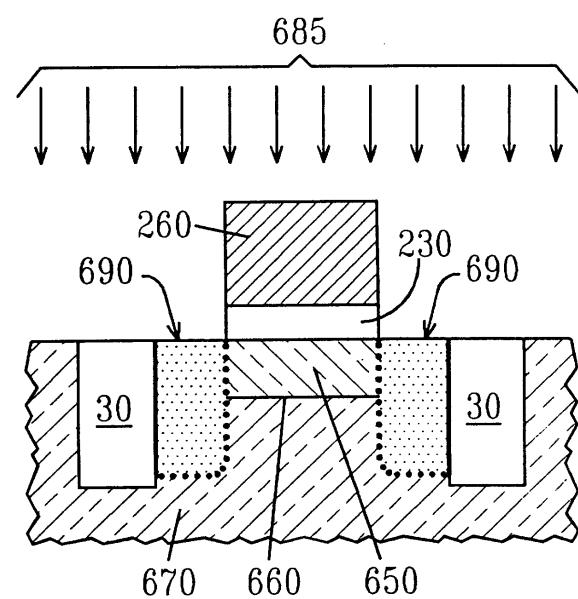

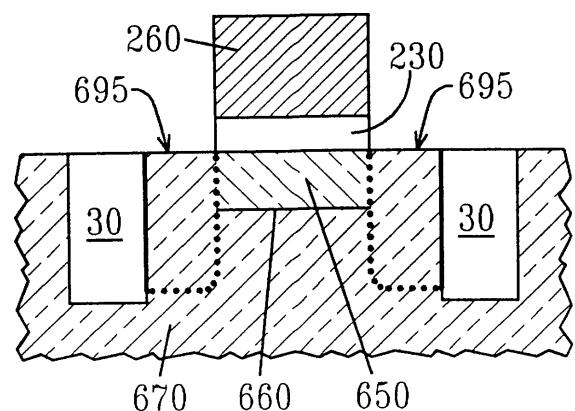

#### 【0031】

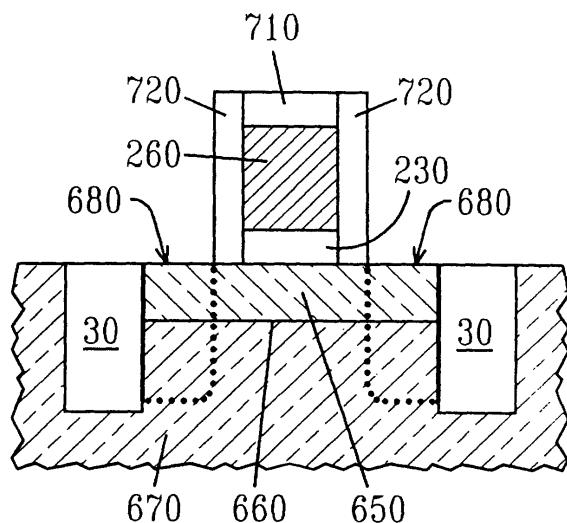

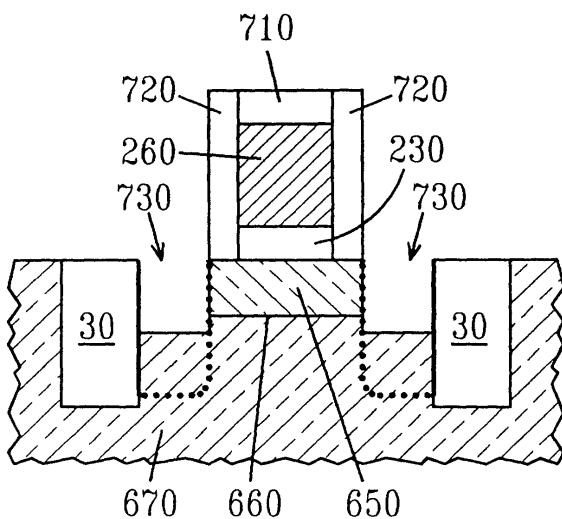

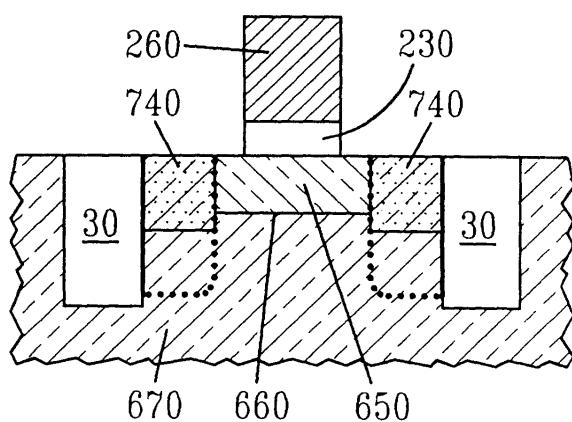

図25乃至図27は、2つの異配向の単結晶半導体領域を含むFETのソース／ドレイン領域を、ただ1つの単結晶半導体領域を含むソース／ドレイン領域に変換することができるアモルファス化／テンプレート化再結晶法を示す。図25は、第1の配向を有し、第1の配向とは異なる第2の配向を有する下部単結晶半導体670に接合界面660で結合された上部単結晶半導体層650を含む、部分的に完成されたFET構造体640を示す。図8のFET200の要素と同様の構造体640の要素は、ゲート導体260、ゲート誘電体230、及び絶縁体充填分離トレンチ30を含む。（点線で外形が示される）領域680は、ソース及びドレイン領域の予想位置を示す。図26は、図25の構造体がイオン注入685に曝され、ゲート導体260をマスクとして用いて、アモルファス化領域690を生成する状態を示す。注入は、（例えば、SiへのSi+又はGe+注入のような）アモルファス化のみを行うものとするか、又は、（例えば、B+、P+、若しくはAsを単独でSiに、又は、Si+若しくはGe+を組み合わせてSiに）アモルファス化及びドーピングを行うものとすることができる。アモルファス化領域690は、次に、固相エピタキシにより下部単結晶半導体670の配向に再結晶化されて、半導体領域695を形成する。図13のFET400のような構造体は、アモルファス化注入がドーパント注入と同じ深さを有するときに形成することができるが、図17のFET440のような構

40

50

造体は、アモルファス化注入より浅いドーパント注入で形成することができる。

**【0032】**

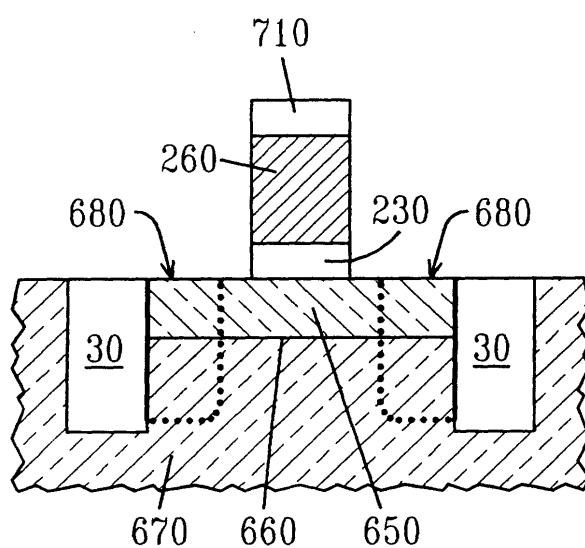

図28乃至図31は、2つの異配向の単結晶半導体領域を含むFETのソース／ドレイン領域が、ただ1つの単結晶半導体領域を含むソース／ドレイン領域により置き換えられることができるトレンチ／エピタキシャル成長方法を示す。図28は、ゲート導体260の上面の上に付加的なゲート不動態化層710をもつ図25の構造体を示す。図29は、誘電性側壁スペーサ720がゲート導体260の側面に形成された後の図28の構造体を示す。図30は、予想ソース／ドレイン領域680の近傍の半導体材料が、キャビティ730を形成するために、接合界面660より下の深さまでエッティングによって除去された後の図29の構造体を示す。次に、キャビティ730は、下層半導体670の配向を有するエピタキシャル成長の半導体740で充填され、その後、ゲート不動態化層710及びスペーサ720は除去されて、図31の構造体が形成される。図25乃至図27及び図28乃至図31のプロセスのステップは、図20のFET520のような構造体を製造するために組み合わせることができる。

10

**【0033】**

本発明は、その好ましい実施形態について具体的に示され説明されてきたが、当業者は、上記及び他の形態及び詳細の変更は、本発明の精神及び範囲から逸脱することなく行うことができるることを理解するであろう。従って、本発明は、説明され示された厳密な形態及び詳細に限定されることではなく、添付の特許請求の範囲内に含まれることが意図される。

20

**【図面の簡単な説明】**

**【0034】**

【図1】従来技術の平面ハイブリッド配向半導体基板構造体の例の断面図を示す。

【図2】従来技術の平面ハイブリッド配向半導体基板構造体の例の断面図を示す。

【図3】従来技術の平面ハイブリッド配向半導体基板構造体の例の断面図を示す。

【図4】従来技術の平面ハイブリッド配向半導体基板構造体の例の断面図を示す。

【図5】従来技術の平面ハイブリッド配向半導体基板構造体の例の断面図を示す。

【図6】従来技術の平面ハイブリッド配向半導体基板構造体の例の断面図を示す。

【図7】従来技術の平面ハイブリッド配向半導体基板構造体の例の断面図を示す。

【図8】FETのチャネル及びソース／ドレイン領域が、そのFETキャリアの移動度を最適化するように好適に選択された単一配向を有する半導体内に形成された従来形状のFETの断面図を示す。

30

【図9】ソース／ドレイン領域の上部分はチャネルと同じ配向を有し、ソース／ドレイン領域の下部分はチャネルの配向とは異なる配向を有する本発明のFETの断面図を示す。

【図10】ソース／ドレイン領域の上部分はチャネルと同じ配向を有し、ソース／ドレイン領域の下部分はチャネルの配向とは異なる配向を有する本発明のFETの断面図を示す。

。

【図11】ソース／ドレイン領域の上部分はチャネルと同じ配向を有し、ソース／ドレイン領域の下部分はチャネルの配向とは異なる配向を有する本発明のFETの断面図を示す。

。

【図12】ソース／ドレイン領域の上部分はチャネルと同じ配向を有し、ソース／ドレイン領域の下部分はチャネルの配向とは異なる配向を有する本発明のFETの断面図を示す。

。

【図13】ソース／ドレイン領域の全体がチャネルの配向とは異なる配向を有する本発明のFETの断面図を示す。

40

【図14】ソース／ドレイン領域の全体がチャネルの配向とは異なる配向を有する本発明のFETの断面図を示す。

【図15】ソース／ドレイン領域の全体がチャネルの配向とは異なる配向を有する本発明のFETの断面図を示す。

【図16】ソース／ドレイン領域の全体がチャネルの配向とは異なる配向を有する本発明

50

の F E T の断面図を示す。

【図 17】ソース / ドレイン領域の全体がチャネルの配向とは異なる配向を有する本発明の F E T の断面図を示す。

【図 18】ソース / ドレイン領域が、横方向に隣接する半導体領域とは異なる材料をさらに含むこともできる本発明の F E T の断面図を示す。

【図 19】ソース / ドレイン領域が、横方向に隣接する半導体領域とは異なる材料をさらに含むこともできる本発明の F E T の断面図を示す。

【図 20】ソース / ドレイン領域が、横方向に隣接する半導体領域とは異なる材料をさらに含むこともできる本発明の F E T の断面図を示す。

【図 21】F E T のうちの一方が本発明の F E T であり、他方が従来の F E T である、異なるハイブリッド配向基板上の C M O S 回路の 1 つの n F E T 及び 1 つの p F E T を断面図に示す。

10

【図 22】F E T のうちの一方が本発明の F E T であり、他方が従来の F E T である、異なるハイブリッド配向基板上の C M O S 回路の 1 つの n F E T 及び 1 つの p F E T を断面図に示す。

【図 23】F E T のうちの一方が本発明の F E T であり、他方が従来の F E T である、異なるハイブリッド配向基板上の C M O S 回路の 1 つの n F E T 及び 1 つの p F E T を断面図に示す。

【図 24】F E T のうちの一方が本発明の F E T であり、他方が従来の F E T である、異なるハイブリッド配向基板上の C M O S 回路の 1 つの n F E T 及び 1 つの p F E T を断面図に示す。

20

【図 25】2 つの異配向の単結晶半導体領域を含む F E T のソース / ドレイン領域を、ただ 1 つの単結晶半導体領域を含むソース / ドレイン領域に変換することができるアモルファス化 / テンプレート化再結晶法を断面図に示す。

【図 26】2 つの異配向の単結晶半導体領域を含む F E T のソース / ドレイン領域を、ただ 1 つの単結晶半導体領域を含むソース / ドレイン領域に変換することができるアモルファス化 / テンプレート化再結晶法を断面図に示す。

【図 27】2 つの異配向の単結晶半導体領域を含む F E T のソース / ドレイン領域を、ただ 1 つの単結晶半導体領域を含むソース / ドレイン領域に変換することができるアモルファス化 / テンプレート化再結晶法を断面図に示す。

30

【図 28】2 つの異配向の単結晶半導体領域を含む F E T のソース / ドレイン領域を、ただ 1 つの単結晶半導体領域を含むソース / ドレイン領域により置き換えることができるトレンチ / エピタキシャル成長法を断面図に示す。

【図 29】2 つの異配向の単結晶半導体領域を含む F E T のソース / ドレイン領域を、ただ 1 つの単結晶半導体領域を含むソース / ドレイン領域により置き換えることができるトレンチ / エピタキシャル成長法を断面図に示す。

【図 30】2 つの異配向の単結晶半導体領域を含む F E T のソース / ドレイン領域を、ただ 1 つの単結晶半導体領域を含むソース / ドレイン領域により置き換えることができるトレンチ / エピタキシャル成長法を断面図に示す。

【図 31】2 つの異配向の単結晶半導体領域を含む F E T のソース / ドレイン領域を、ただ 1 つの単結晶半導体領域を含むソース / ドレイン領域により置き換えることができるトレンチ / エピタキシャル成長法を断面図に示す。

40

【図 1】

【図 3】

【図 2】

【図 4】

【図 5】

【図 7】

【図 6】

【図 8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

---

フロントページの続き

(51)Int.CI.

F I

|         |       |         |

|---------|-------|---------|

| H 0 1 L | 29/78 | 6 2 0   |

| H 0 1 L | 29/78 | 6 1 3 A |

| H 0 1 L | 29/78 | 6 1 6 V |

| H 0 1 L | 29/78 | 6 1 8 E |

| H 0 1 L | 21/20 |         |

(74)代理人 100086243

弁理士 坂口 博

(72)発明者 デソーザ、ジョエル、ピー

アメリカ合衆国 10579 ニューヨーク州 パットナム・バレー ウエスト・ショア・ドライブ 10

(72)発明者 サダナ、デヴェンドラ・ケー

アメリカ合衆国 10570 ニューヨーク州 プレザントビル スカイ・トップ・ドライブ 90

(72)発明者 ゼンガー、キャサリン、エル

アメリカ合衆国 10562 ニューヨーク州 オッシニング アンダーヒル・ロード 115

(72)発明者 ソン、クンユン

アメリカ合衆国 12603 ニューヨーク州 ポキブシー ボリノ・ドライブ 11

(72)発明者 ヤン、ミン

アメリカ合衆国 10598 ニューヨーク州 ヨークタウン・ハイツ ゴーマー・ストリート 2970

(72)発明者 イン、ハイチョウ

アメリカ合衆国 12508 ニューヨーク州 ピーコン サウス・ロッキー・ウッズ・ロード 8エー

審査官 松嶋 秀忠

(56)参考文献 特開平02-170577(JP, A)

国際公開第2004/114400(WO, A1)

特開2003-092399(JP, A)

特開2002-100762(JP, A)

(58)調査した分野(Int.CI., DB名)

H01L 29/78

H01L 21/336

H01L 21/20

H01L 21/8238

H01L 27/092

H01L 29/786