(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2013-232622

(P2013-232622A)

(43) 公開日 平成25年11月14日(2013.11.14)

(51) Int.Cl.

H01L 25/00 (2006.01)

F 1

H01L 25/00

テーマコード (参考)

B

審査請求 有 請求項の数 5 O L (全 43 頁)

(21) 出願番号 特願2013-8640 (P2013-8640)

(22) 出願日 平成25年1月21日 (2013.1.21)

(62) 分割の表示 特願2012-104176 (P2012-104176)

の分割

原出願日 平成24年4月27日 (2012.4.27)

(71) 出願人 308033711

ラピスセミコンダクタ株式会社

神奈川県横浜市港北区新横浜二丁目4番地

8

(74) 代理人 100079049

弁理士 中島 淳

(74) 代理人 100084995

弁理士 加藤 和詳

(74) 代理人 100099025

弁理士 福田 浩志

(72) 発明者 武政 肇吾

宮崎県宮崎郡清武町大字木原727番地

ラピスセミコンダクタ宮崎株式会社内

最終頁に続く

(54) 【発明の名称】半導体装置及び計測機器

## (57) 【要約】

【課題】小型化すると共に、配線抵抗を低減した半導体装置及び計測機器を提供する。

【解決手段】発振素子を含み、一方の面に複数の端子を有する電子部品と、前記電子部品と電気的に接続されると共に、一方の面に複数の端子を有する半導体チップと、前記電子部品の端子と前記半導体チップの端子とが同一の方向を向くように夫々が搭載される搭載基材と、前記半導体チップの前記端子に接続された第1のボンディングワイヤと、前記電子部品の前記端子と前記半導体チップの前記端子とを接続すると共に前記第1のボンディングワイヤよりも頂点の低い第2のボンディングワイヤと、前記電子部品、前記半導体チップ、前記搭載基材、前記第1のボンディングワイヤ、及び前記第2のボンディングワイヤと、を封止する封止部材と、を備えている。

【選択図】図3

**【特許請求の範囲】****【請求項 1】**

発振素子を含み、一方の面に複数の端子を有する電子部品と、

前記電子部品と電気的に接続されると共に、一方の面に複数の端子を有する半導体チップと、

前記電子部品の端子と前記半導体チップの端子とが同一の方向を向くように夫々が搭載

される搭載基材と、

前記半導体チップの前記端子に接続された第1のボンディングワイヤと、

前記電子部品の前記端子と前記半導体チップの前記端子とを接続すると共に前記第1の

ボンディングワイヤよりも頂点の低い第2のボンディングワイヤと、

前記電子部品、前記半導体チップ、前記搭載基材、前記第1のボンディングワイヤ、及び前記第2のボンディングワイヤと、を封止する封止部材と、

を備えた半導体装置。

**【請求項 2】**

請求項1に記載の半導体装置と、

前記半導体装置から出力された信号に応じて積算量を計測する計測手段と、

を有する計測機器。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、半導体装置及び計測機器に関する。

**【背景技術】****【0002】**

近年、積算電力量を計測する電力メータなどの計測機器において、時間帯別に積算電力量を計測する需要が高まっている。これに伴い、計測機器の内部に、発振子（電子部品）と半導体チップを備えた半導体装置を組み込んで、電力と時間を計測できるようにした計測機器がある。また、リードフレームの表面に半導体チップを搭載し、リードフレームの裏面に発振子（電子部品）を搭載した圧電発振器がある（例えば、特許文献1）。

**【0003】**

特許文献1の発明では、半導体チップと発振子（電子部品）とを電気的に接続するため配線をリードフレームの裏側へ引き回す必要があり、配線抵抗が高くなる虞がある。

**【先行技術文献】****【特許文献】****【0004】**

【特許文献1】特開2007-234994号公報

**【発明の概要】****【発明が解決しようとする課題】****【0005】**

本発明は、上記の事実を考慮し、小型化すると共に、配線抵抗を低減した半導体装置及び計測機器を提供することを目的とする。

**【課題を解決するための手段】****【0006】**

請求項1に記載の半導体装置は、発振素子を含み、一方の面に複数の端子を有する電子部品と、前記電子部品と電気的に接続されると共に、一方の面に複数の端子を有する半導体チップと、前記電子部品の端子と前記半導体チップの端子とが同一の方向を向くように夫々が搭載される搭載基材と、前記半導体チップの前記端子に接続された第1のボンディングワイヤと、前記電子部品の前記端子と前記半導体チップの前記端子とを接続すると共に前記第1のボンディングワイヤよりも頂点の低い第2のボンディングワイヤと、前記電子部品、前記半導体チップ、前記搭載基材、前記第1のボンディングワイヤ、及び前記第2のボンディングワイヤと、を封止する封止部材と、を備えている。

10

20

30

40

50

## 【発明の効果】

## 【0007】

本発明は、上記の構成としたので、小型化すると共に、配線抵抗を低減した半導体装置及び計測機器を提供できる。

## 【図面の簡単な説明】

## 【0008】

【図1】第1実施形態に係る半導体装置を備えた積算電力量計の斜視図である。

【図2】第1実施形態に係る半導体装置を裏面から見た一部破断図である。

【図3】図2の3-3線断面図である。

【図4】第1実施形態に係る発振子を示す分解斜視図である。

10

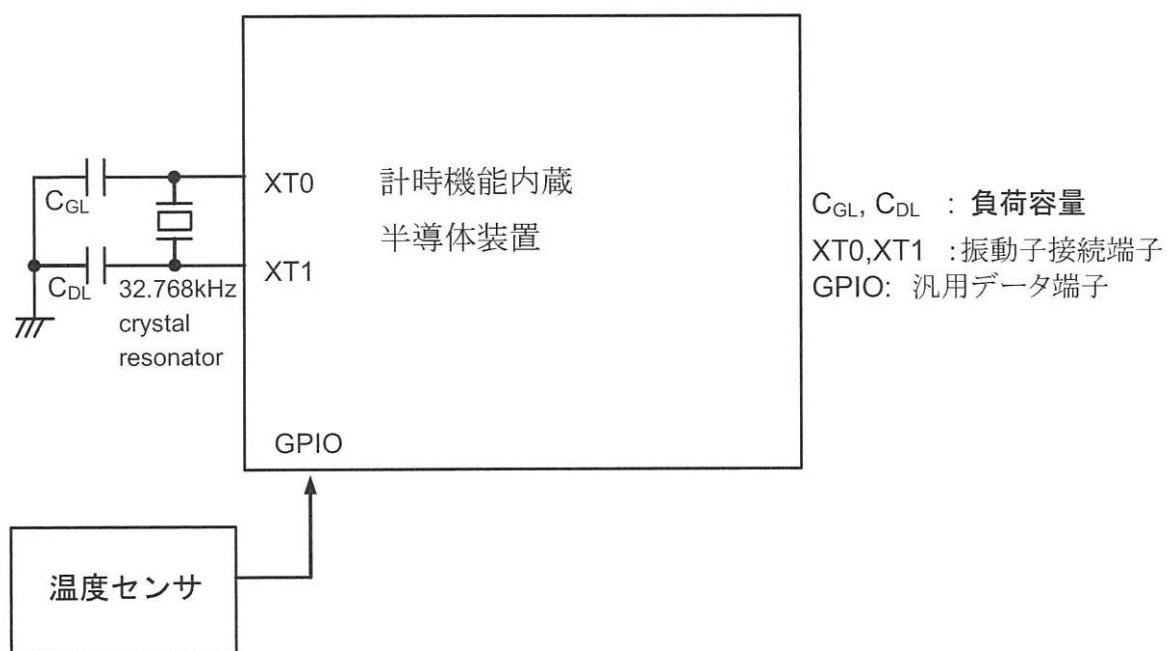

【図5】第1実施形態に係る半導体装置のLSIを説明するためのブロック図である。

【図6】(a)～(e)は、第1実施形態に係る半導体装置を製造する製造方法において発振子とLSIとをリードフレーム上に配置してワイヤボンディングする手順を示す説明図である。

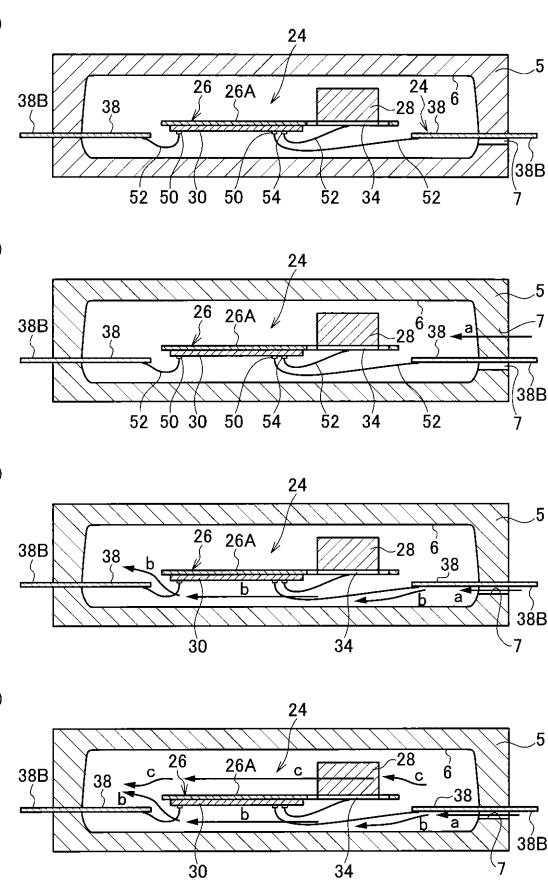

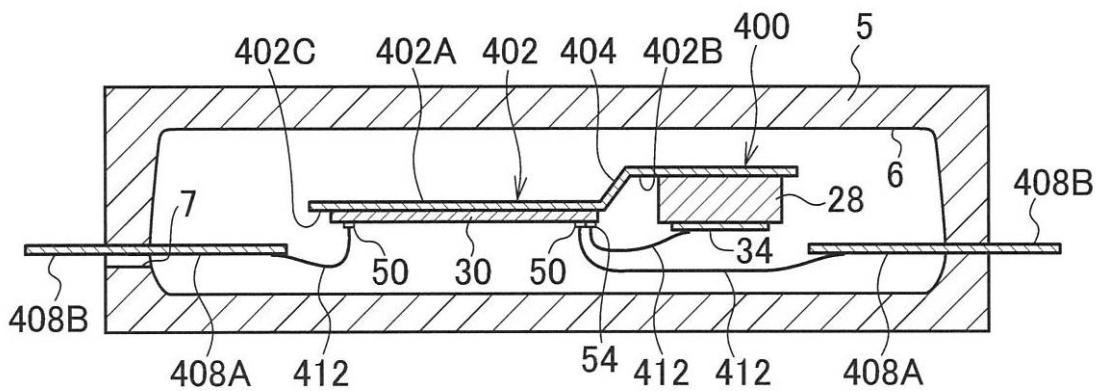

【図7】(a)～(d)は、第1実施形態に係る半導体装置を製造する製造方法においてリードフレームと発振子とLSIとを樹脂で封止する手順を示す説明図である。

【図8】第1実施形態に係る半導体装置の変形例を示す一部破断図である。

【図9】第1実施形態に係る第1周波数補正処理の流れを示すフローチャートである。

【図10】第1実施形態に係る第2周波数補正処理の流れを示すフローチャートである。

20

【図11】第1実施形態に係る半導体装置における温度と周波数偏差との関係を示す図である。

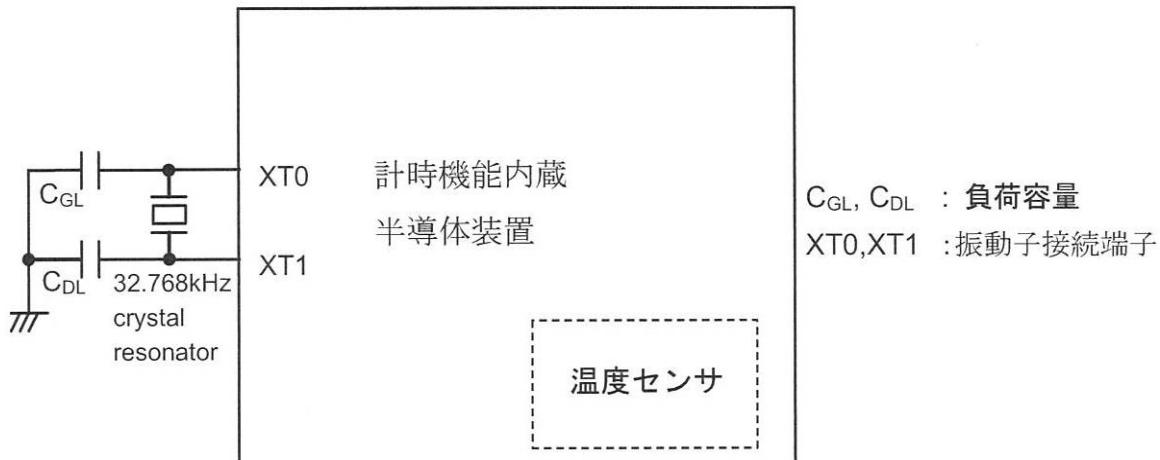

【図12】第2実施形態に係る半導体装置のLSIを説明するためのブロック図である。

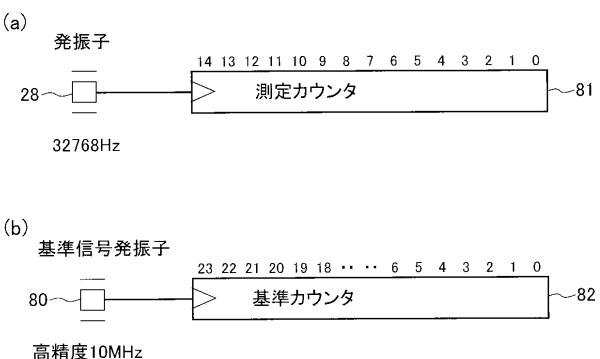

【図13】(a)は、第2実施形態に係る半導体装置の発振子のクロック値の一例を示す図であり、(b)は、第2実施形態に係る半導体装置の基準信号発振子のクロック値の一例を示す図である。

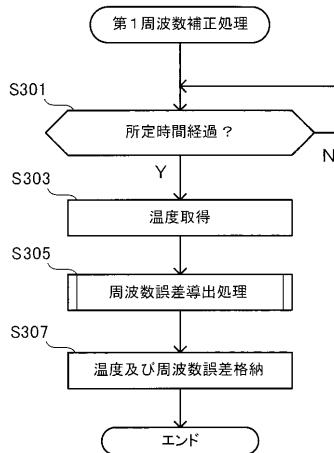

【図14】第2実施形態に係る第1周波数補正処理の流れを示すフローチャートである。

【図15】第2実施形態に係る周波数誤差導出処理の流れを示すフローチャートである。

【図16】第2実施形態に係る周波数誤差導出処理におけるタイミングチャートであり、(a)は、カウント開始時を示す図であり、(b)は、カウント停止時を示す図である。

30

【図17】第2実施形態に係る第2周波数補正処理の流れを示すフローチャートである。

【図18】第2実施形態に係る半導体装置のLSIの別例を説明するためのブロック図である。

【図19】第2実施形態に係る半導体装置のLSIの別例を説明するためのブロック図である。

【図20】第3実施形態に係る半導体装置を裏面から見た一部破断図である。

【図21】図20の21-21線断面図である。

【図22】第4実施形態に係る半導体装置を裏面から見た一部破断図である。

【図23】第4実施形態に係る半導体装置のリードフレームを説明するための説明図である。

【図24】第5実施形態に係る半導体装置を裏面から見た一部破断図である。

40

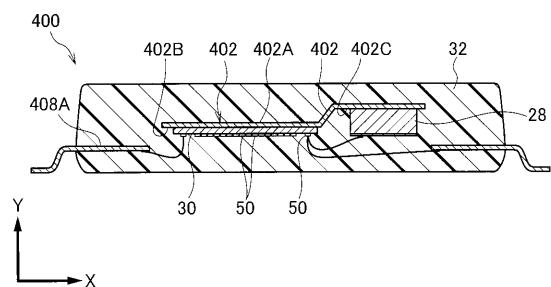

【図25】図24の14-14線断面図である。

【図26】(a)～(e)は、第5実施形態の半導体装置を製造する製造方法において発振子とLSIとをリードフレーム上に配置してワイヤボンディングする手順を示す説明図である。

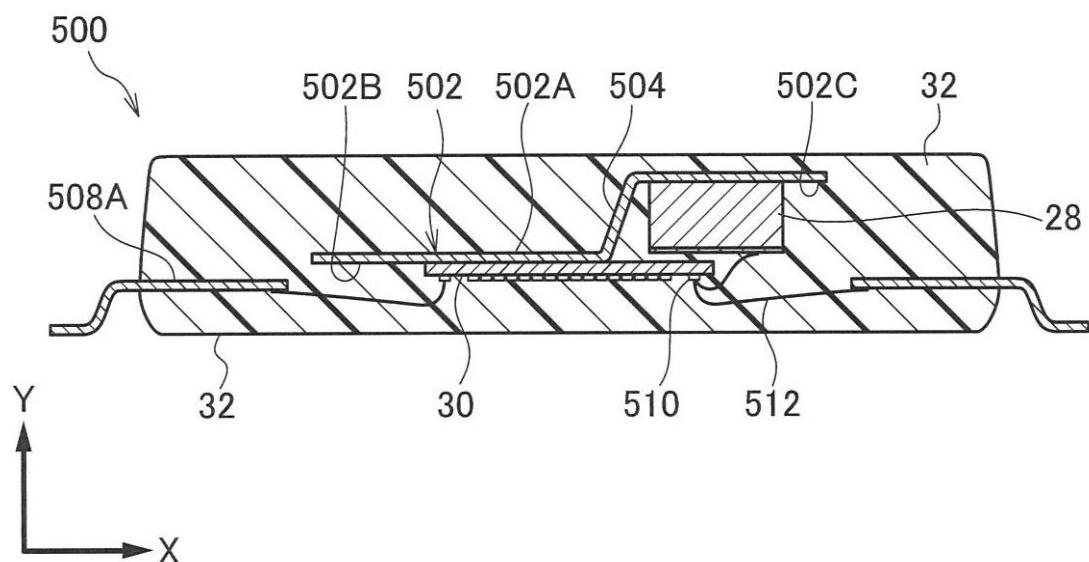

【図27】(a)～(d)は、第5実施形態に係る半導体装置を製造する製造方法においてリードフレームと発振子とLSIとを樹脂で封止する手順を示す説明図である。

【図28】第6実施形態に係る半導体装置を裏面から見た一部破断図である。

【図29】図28の18-18線断面図である。

【図30】従来の計時機能が内蔵された半導体装置と発振子とが接続された状態の一例を示すブロック図である。

50

【図31】従来の計時機能が内蔵された半導体装置と発振子とが接続された状態の一例を示すブロック図である。

【図32】従来のパッケージ化された一般的な半導体装置を示す概略断面図である。

【発明を実施するための形態】

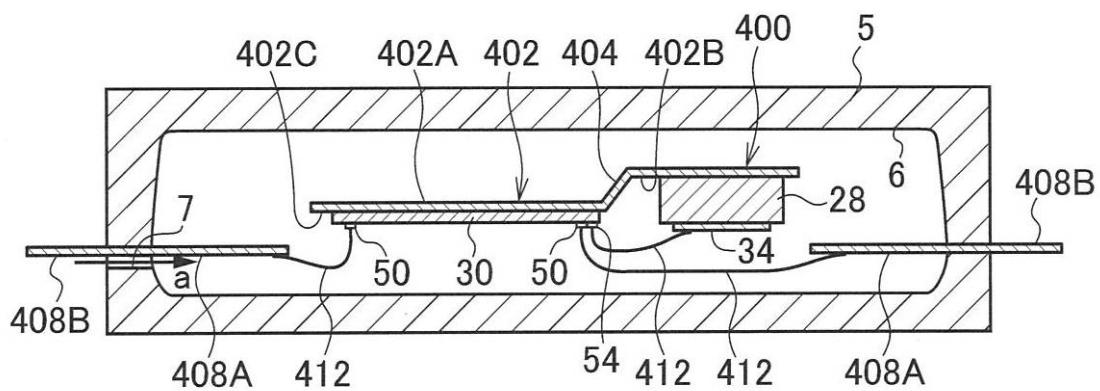

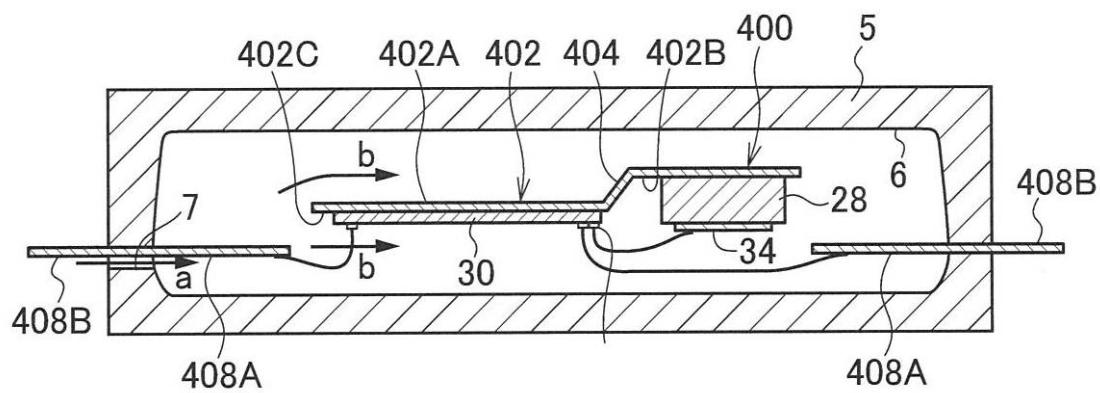

【0009】

(第1実施形態)

以下、本発明に係る半導体装置について添付図面を用いて詳細に説明する。

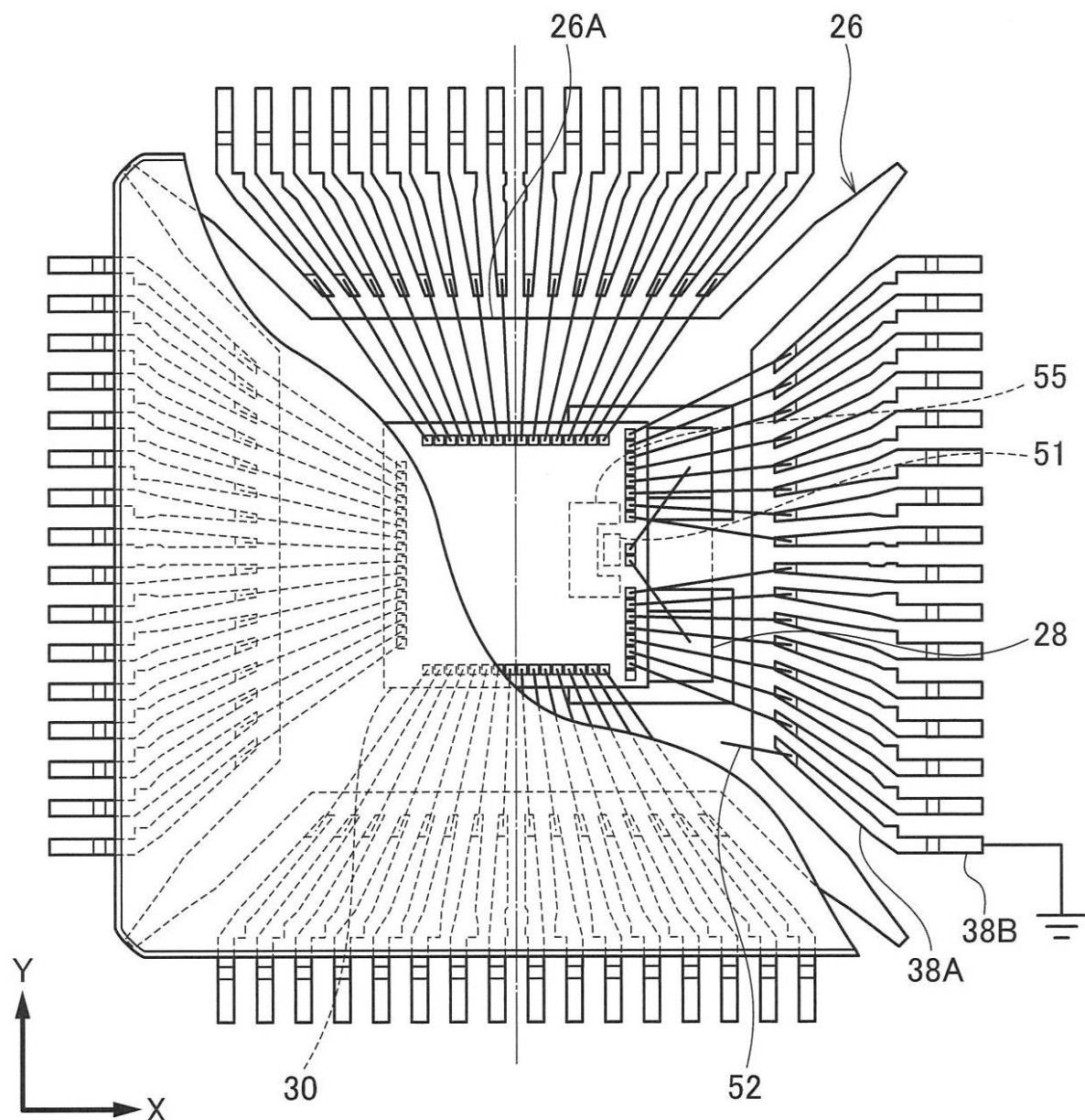

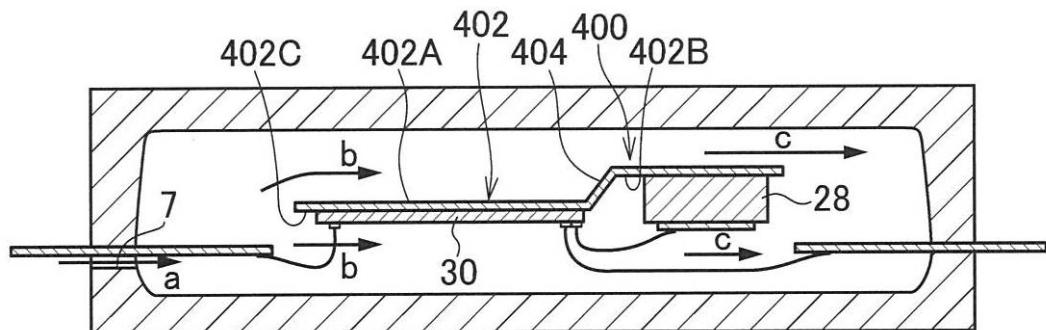

【0010】

<構成>

【0011】

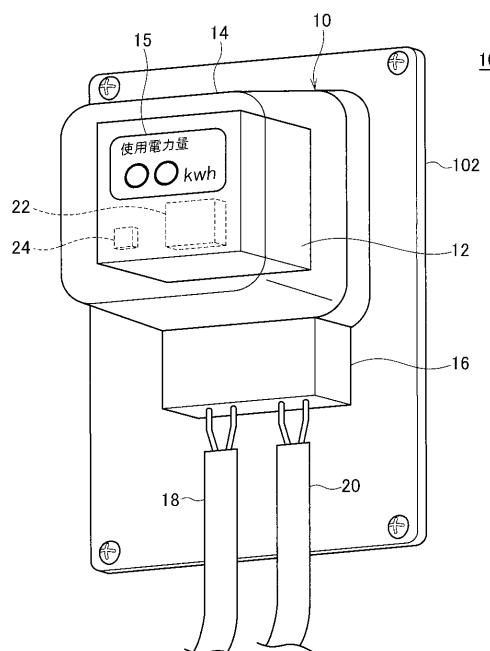

図1に示すように、実施形態1の半導体装置を備える積算電力量計10は、住宅などの外壁100に固定された固定板102の上面に取付けられており、主として、本体部12と、本体部12を覆う透明のカバー14と、本体部12の下部に設けられた接続部16とで構成されている。

【0012】

接続部16の下方からは、電源側配線18と負荷側配線20とが接続されており、積算電力量計10へ電流を供給している。本体部12は、平面視にて矩形状の箱体であり、本体部12の内部には、後述する半導体装置24、及び半導体装置24から出力された信号に応じて積算電力量を計測する計測手段としての電力量計測回路22が基板(不図示)上に実装されている。なお、図1において、説明の便宜上、電力量計測回路22、及び半導体装置24の大きさを誇張して描いている。

【0013】

本体部12の正面には、横長の液晶ディスプレイ15が設けられている。液晶ディスプレイ15には、電力量計測回路22が計測した単位時間当たりの使用電力量や、時間帯別に使用した積算電力量などが表示されている。なお、本実施形態に係る積算電力量計10は、計測手段として電力量計測回路22を用いた電子式の電力量計であるが、これに限らず、例えば、円盤を回転させて電力量を計測する誘導型の電力量計でもよい。

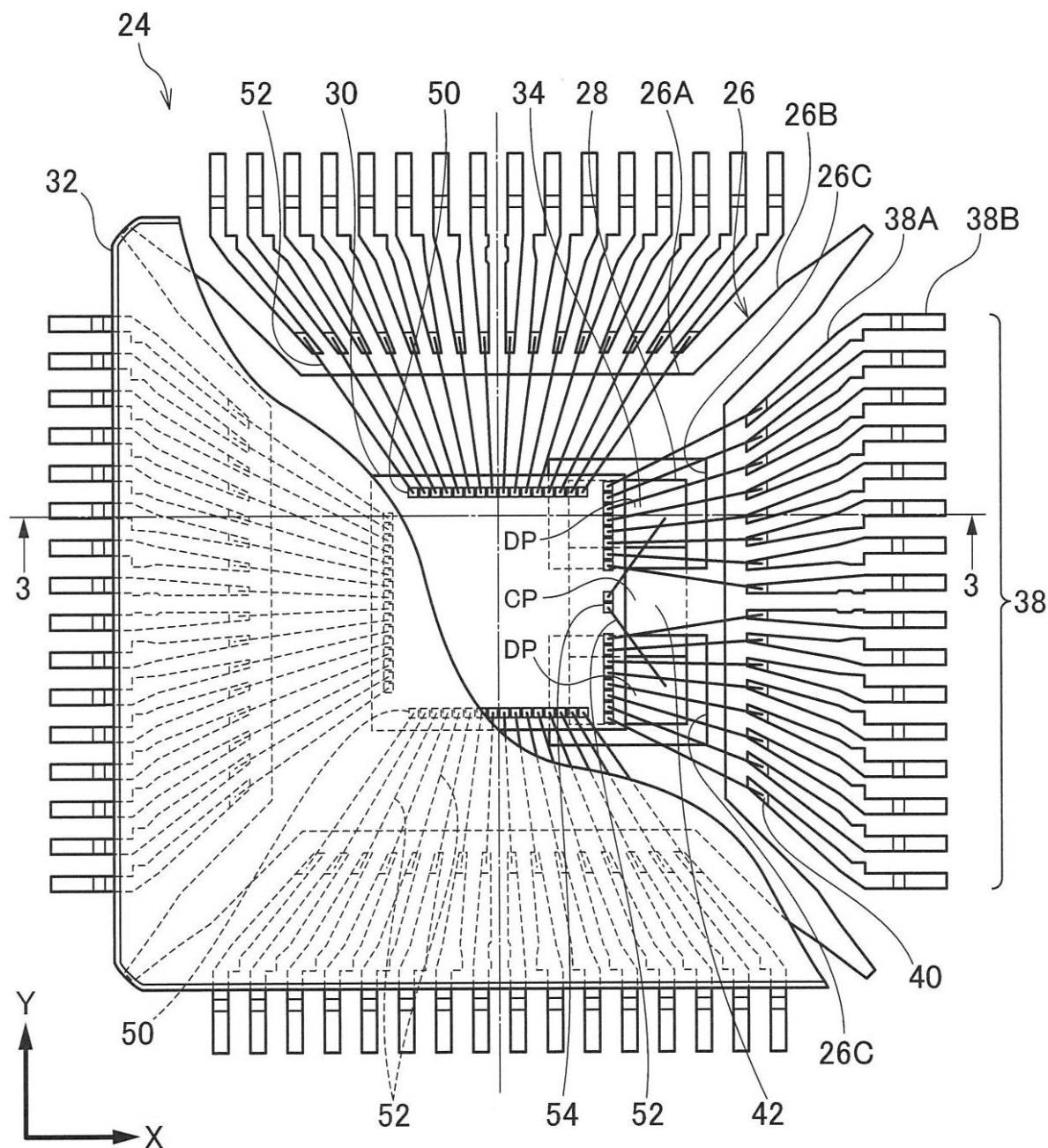

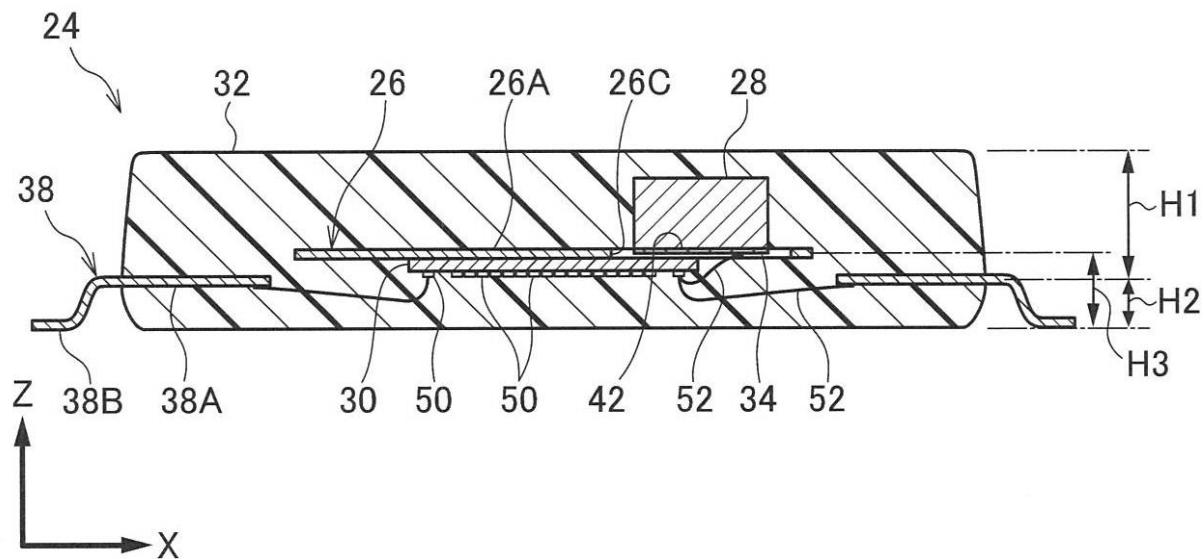

【0014】

次に、本実施形態に係る半導体装置24の詳細な構成を説明する。なお、以下の説明において、図2に示す半導体装置24の平面視における左右方向を矢印X方向とし、上下方向を矢印Y方向とし、図3に示す半導体装置24の断面図における高さ方向をZ方向として説明する。図2、及び図3に示すように、半導体装置24の外形形状は、平面視にて矩形状であり、骨格となる搭載基材としてのリードフレーム26と、リードフレーム26の表面(第1の面)に搭載された電子部品としての発振子28と、リードフレーム26の裏面(第2の面)に搭載された半導体チップとしてのLSI30と、封止部材となるモールド樹脂32と、を含んで構成されている。

【0015】

リードフレーム26は、銅(Cu)や鉄(Fe)とニッケル(Ni)の合金などの金属からなる平板をプレス機で打ち抜いて形成された板材であり、中央部に設けられた搭載部としてのダイパッド26Aと、ダイパッド26Aから対角線上に外側へ延びる吊りリード26Bと、隣り合う吊りリード26Bの間に設けられた複数のリード(端子)38とを含んで構成されている。

【0016】

リード38は、ダイパッド26Aの中央部へ向かって延びる細長い部材であり、ダイパッド26Aの周囲に所定の間隔で複数形成されている。本実施形態では、隣り合う吊りリード26Bの間に16本のリード38が形成されている。また、リード38は、ダイパッド26A側に位置するインナーリード38Aと、半導体装置24の外周端部側に位置するアウターリード38Bと、で構成されており、インナーリード38Aは、ダイパッド26Aより下方となるように、プレス機で押し下げられ、ダイパッド26Aと平行に延びている(図3参照)。また、ダイパッド26Aに最も近いインナーリード38Aの先端部は、

めっき膜 4 0 で被覆されている。本実施形態では一例として、めっき膜 4 0 を銀 (A g) で形成しているが、これに限らず、例えば、金 (A u) などの金属でめっき膜を形成してもよい。

#### 【0 0 1 7】

アウターリード 3 8 B は、モールド樹脂 3 2 から露出して下方へ屈曲され、先端部がインナーリード 3 8 A と平行になっている。すなわち、ガルウィングリードとなっている。また、アウターリード 3 8 B は、半田めっき膜により被覆されている。半田めっき膜の材質としては、錫 (S n)、錫 (S n) と鉛 (P b) の合金、又は錫 (S n) と銅 (C u) の合金などが用いられる。

#### 【0 0 1 8】

リードフレーム 2 6 の中央部のダイパッド 2 6 A は、平面視にて矩形状に形成された平板状の部材であり、ダイパッド 2 6 A の中央部より右側には、ダイパッド 2 6 A の厚み方向に貫通した 2 つの開口部 2 6 C が形成されている。開口部 2 6 C は、横長の矩形状に形成されており、後述する発振子 2 8 の外部電極 3 4 と対面するように設けられている (図 4 参照)。

#### 【0 0 1 9】

2 つの開口部 2 6 C の間の領域は、左右方向に延びる発振子搭載領域としての発振子搭載用梁 4 2 となっており、リードフレーム 2 6 の表面の発振子搭載用梁 4 2 には、接着剤 (不図示) を介して発振子 2 8 が搭載されている (図 4 参照)。換言すると、発振子搭載用梁 4 2 の両脇に開口部 2 6 C がそれぞれ設けられている。発振子 2 8 は、上下方向を長手方向とした矩形状の電子部品であり、本実施形態では、一般的な電子機器に搭載される周波数が 3 2 . 7 6 8 K H z の汎用の半導体装置 2 4 に対して外付け可能な発振子 2 8 を用いている。

#### 【0 0 2 0】

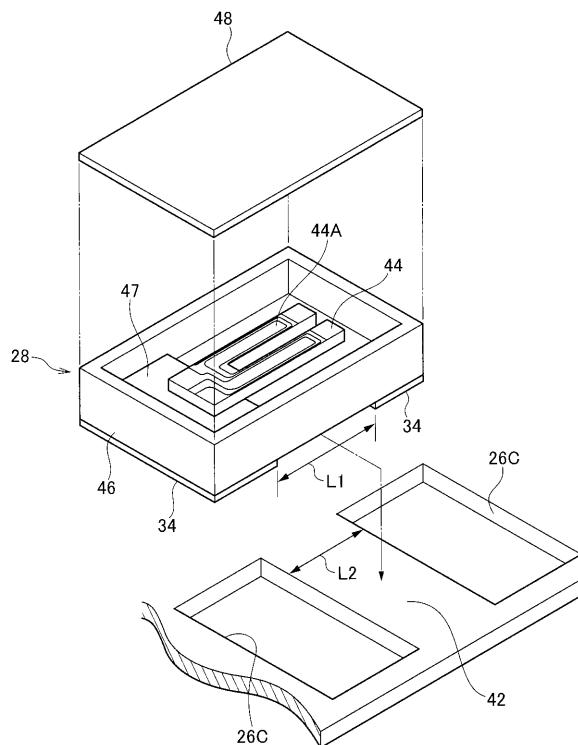

図 4 に示すように、発振子 2 8 は、振動片 4 4 と、振動片 4 4 を収容するパッケージ本体 4 6 と、蓋体 4 8 と、を含んで構成されており、平面視において矩形状をしている。振動片 4 4 は、人工水晶で形成された音叉型の水晶片の表面に励起電極 4 4 A を成膜した水晶振動片であり、励起電極 4 4 A に電流を流すと、圧電効果により振動片 4 4 が発振する。ここで、振動片 4 4 としては、音叉型に限らず、A T カットの水晶片を用いてもよい。また、水晶の他に、タンタル酸リチウム (L i T a O<sub>3</sub>) やニオブ酸リチウム (L i N b O<sub>3</sub>) で形成した振動片を用いてもよい。さらに、シリコンで形成されたM E M S 振動片を用いてもよい。

#### 【0 0 2 1】

パッケージ本体 4 6 は、上部が開口した箱体であり、長手方向一端側の底部には、振動片 4 4 が固定される台座 4 7 が形成されている。この台座 4 7 に振動片 4 4 の基部を固定して、振動可能とし、真空状態でパッケージ本体 4 6 と蓋体 4 8 とを接合することで、振動片 4 4 が気密封止される。また、パッケージ本体 4 6 の下面の両端には、振動片 4 4 の励起電極 4 4 A と電気的に接続された端子としての外部電極 3 4 が所定の距離 L 1 を離してそれぞれ形成されている。また、発振子搭載用梁 4 2 の幅 L 2 は、外部電極 3 4 間の距離より狭幅に形成されている。

#### 【0 0 2 2】

外部電極 3 4 は、パッケージ本体 4 6 の幅と同じ幅に形成されており、図 2 に示すように、外部電極 3 4 の大きさは、後述するL S I 3 0 に形成された電極パッド 5 0 、及び発振子用電極パッド 5 4 より大きくなっている。また、外部電極 3 4 よりダイパッド 2 6 A の開口部 2 6 C の方が大きく形成されている。

#### 【0 0 2 3】

図 2 及び図 3 に示すように、リードフレーム 2 6 の裏面には、ダイパッド 2 6 A の中央部に、接着材 (不図示) を介して半導体チップとしてのL S I 3 0 が搭載されている。L S I 3 0 は、矩形状で薄肉の電子部品であり、L S I 3 0 の右側の端部は、開口部 2 6 C を半分ほど覆っている。このため、平面視にて投影したとき、発振子 2 8 とL S I 3 0 と

10

20

30

40

50

が重なるように配置されている。また、LSI30側からリードフレーム26を見ると、開口部26Cから発振子28の外部電極34が露出している。

#### 【0024】

矩形形状をなすLSI30の各辺に沿った下面の外周端部には、LSI30の内部の配線と電気的に接続された複数の電極パッド50が設けられている。電極パッド50は、アルミ(A1)や銅(Cu)などの金属で形成されており、LSI30の各辺に16個ずつ設けられている。なお、電極パッド50の数は、各辺で同じでもよいし、後述する発振子用電極パッド54が設けられる辺は少なくするまたは多くするなど、異なるようにしてもよい。また、電極パッド50はそれぞれ、ボンディングワイヤ52(第1のボンディングワイヤ)によりリードフレーム26のインナーリード38Aと接続されている。なお、本実施形態では、電極パッド50の数は、リード38の数と一致するようにLSI30の各辺に16個ずつ設けられていたが、これに限らず、リード38の数より多く設けて他の用途に使用してもよい。

10

#### 【0025】

LSI30の発振子28側の外周端部には、電極パッド50とは別に発振子用電極パッド54が設けられている。発振子用電極パッド54は、LSI30の上下方向の中央部に2個設けられており、電極パッド50の間に位置している。すなわち、中央部に発振子用電極パッド54配置領域(第1の領域)が形成され、この中央部から発振子用電極パッド54が設けられた辺の終端までの領域にそれぞれと、残りの三辺に電極パッド50配置領域(第2の領域)が形成されている。また、発振子電極パッド54は、開口部26Cを通じて、発振子28の外部電極34とボンディングワイヤ52(第2のボンディングワイヤ)で接続されている。なお、ボンディングワイヤは、金(Au)、銅(Cu)等の金属からなる線状の導電部材である。

20

#### 【0026】

LSI30の上下方向の中央部に設けられた2つの発振子用電極パッド54は、同じ辺に設けられた電極パッド50から離して設けられている。換言すると、発振子用電極パッド54と、発振子用電極パッド54と隣接する電極パッド50との間の距離は、電極パッド50間の距離よりも長くなっている。

#### 【0027】

なお、発振子用電極パッド54と隣接する電極パッド50の間の距離を電極パッド50間の距離と等しくしておき、発振子用電極パッド54と隣接する電極パッド50をワイヤボンディングしないことで、ワイヤボンディングされた電極パッド50と発振子用電極パッド54との間の距離を、ワイヤボンディングされた電極パッド50間の距離よりも長くするようにしてもよい。換言すると、LSI30の電極パッド50上においては、電極パッド50とインナーリード38Aとを接続するボンディングワイヤ52間の距離よりも、発振子電極パッド54と外部電極34とを接続するボンディングワイヤ52と電極パッド50とインナーリード38Aとを接続するボンディングワイヤ52との距離のほうが長くなっている。

30

#### 【0028】

ここで、発振子用電極パッド54と外部電極34とを接続しているボンディングワイヤ52と、電極パッド50とインナーリード38Aとを接続しているボンディングワイヤ52は、立体交差しており、図3に示すように、電極パッド50とインナーリード38Aとを接続しているボンディングワイヤ52(第1のボンディングワイヤ)は、発振子用電極パッド54と外部電極34とを接続しているボンディングワイヤ52(第2のボンディングワイヤ)を跨ぐようにして形成されている。すなわち、ボンディングワイヤ52の短絡を防止するために、発振子用電極パッド54と外部電極34とを接続しているボンディングワイヤ52(第2のボンディングワイヤ)の頂点は、電極パッド50とインナーリード38Aとを接続しているボンディングワイヤ52(第1のボンディングワイヤ)の頂点より低くなるように形成されている。

40

#### 【0029】

50

なお、全ての電極パッド 50 とインナーリード 38A とを接続するボンディングワイヤ 52 の頂点の高さよりも、発振子用電極パッド 54 と外部電極 34 とを接続するボンディングワイヤ 52 の頂点の高さのほうが低くなるようしても良いし、発振子用電極パッド 54 と外部電極 34 との間にある電極パッド 50 とインナーリード 38A とを接続するボンディングワイヤ 52 の頂点の高さよりも低くするようにしてもよい。

#### 【0030】

また、LSI 30 の中心と直方体形状の発振子 28 の中心 CP とが X 軸上で略一致するように平行に配置されている。すなわち、発振子 28 の中心 CP の X 軸からの Y 軸方向へのずれ幅は、中央部の Y 軸方向の幅よりもせまい。そのような配置状態において、LSI 30 の任意の一辺の中央付近に設けられた発振子用電極パッド 54 と、発振子 28 の長手方向の両端に離して配置した外部電極 34 とをボンディングワイヤ 52 で接続している。それと共に、発振子用電極パッド 54 を挟むように並べて配置された電極パッド 50 と、電極パッド 50 と Y 軸方向に平行に並んでいるインナーリード 38A とをボンディングワイヤ 52 で接続している。

10

#### 【0031】

さらに、発振子用電極パッド 54 が電極パッド 50 から離して設けられているため、電極パッド 50 とインナーリード 38A とを接続するボンディングワイヤ 52 ( 第 1 のボンディングワイヤ ) は、発振子用電極パッド 54 と外部電極 34 とを接続するボンディングワイヤ 52 ( 第 2 のボンディングワイヤ ) の発振子 28 より低くなった部分を通過することとなる。すなわち、発振子用電極パッド 54 と外部電極 34 とを接続するボンディングワイヤ 52 ( 第 2 のボンディングワイヤ ) の頂点付近を通過して交差することを回避でき効率的に立体交差させることができる。さらに、電極パッド 50 とインナーリード 38A とを接続するボンディングワイヤ 52 ( 第 1 のボンディングワイヤ ) の頂点の高さを低く抑えることができるため、パッケージの高さを低くすることも可能である。

20

#### 【0032】

また、発振子 28 の外部電極 34 におけるボンディングワイヤ 52 の接続位置は、X 軸方向においては、発振子 28 の中心位置よりインナーリード 38A 側にずれている。このように接続することで、ボンディングワイヤ 52 が LSI 30 の端部に接触することを低減することができる。一方 X 軸方向においては、外部電極 34 の中心より発振子 28 の中心方向にずれている。このように接続することで、電極パッド 50 とインナーリード 38A とを接続するボンディングワイヤ 52 との交差回数を減らすことが可能である。

30

#### 【0033】

発振子 28 、 LSI 30 、及びリードフレーム 26 は、封止部材としてのモールド樹脂 32 により封止されており、半導体装置 24 の外形が形成されている。モールド樹脂 32 は、内部に空隙を設けないように充填されており、モールド樹脂 32 の高さは、インナーリード 38 の高さの 2 倍以上の高さとなっている。換言すると、モールド樹脂 32 の発振子 28 搭載側の表面からインナーリード 38 の中心までの距離 H1 は、モールド樹脂 32 の LSI 30 搭載側の表面からインナーリード 38 の中心までの距離 H2 よりも長い。また、モールド樹脂 32 の LSI 30 搭載側の表面からダイパッド 26 の中心までの距離 H3 は、モールド樹脂 32 の LSI 30 搭載側の表面からインナーリード 38 までの距離 H2 よりも長い。なお、本実施形態では、モールド樹脂 32 として、シリカ系の充填材を含有した熱硬化性のエポキシ樹脂を用いているが、これに限らず、例えば、熱可塑性の樹脂を用いてもよい。

40

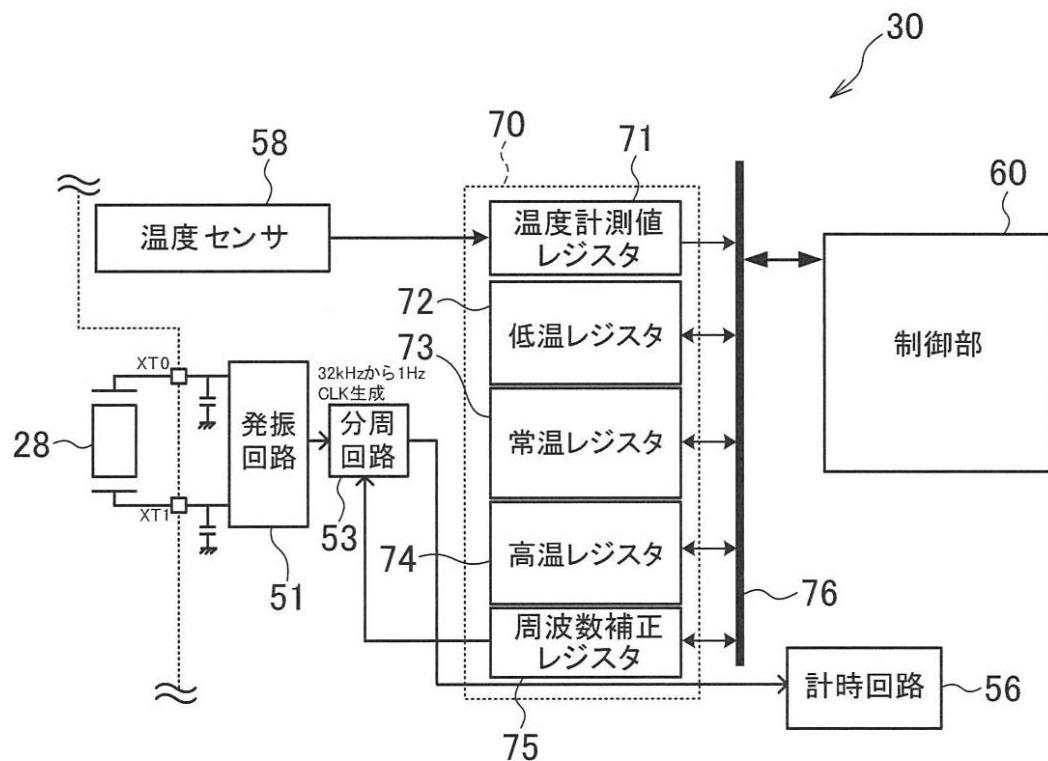

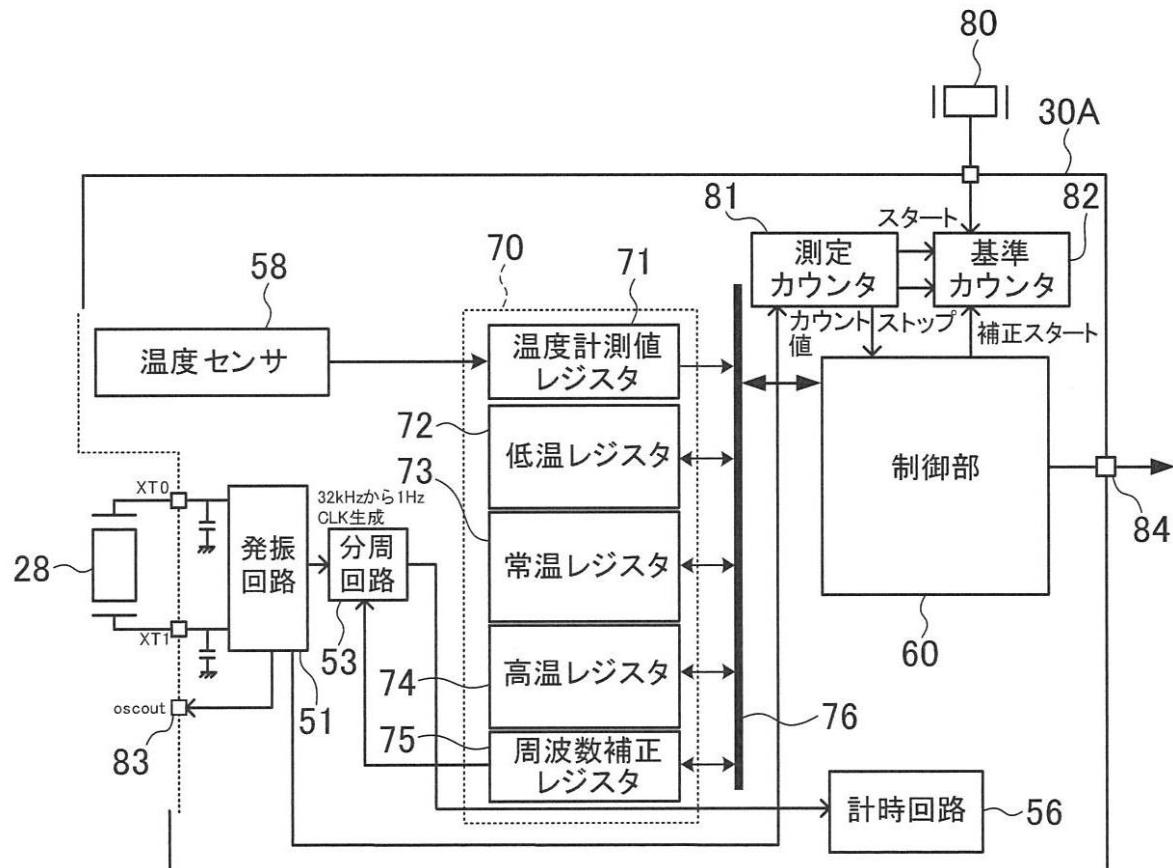

#### 【0034】

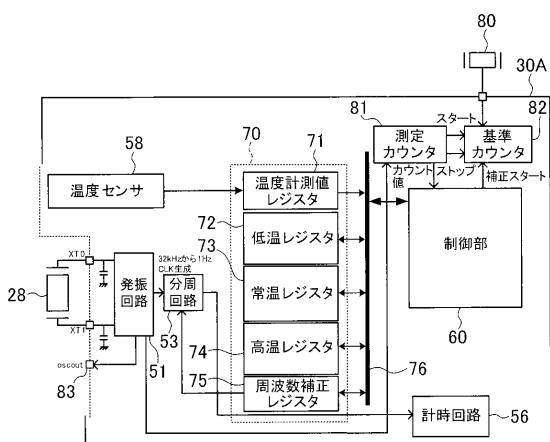

次に、LSI 30 の内部の構成について説明する。図 5 に示すように、LSI 30 には、発振回路 51 、分周回路 53 、計時回路 56 、温度センサ 58 、制御部 60 、及びレジスタ部 70 が内蔵されている。発振回路 51 は、発振子 28 と接続されており、発振子 28 を発振させる。分周回路 53 は、発振子 28 から出力された信号 ( 本実施形態では、32.768 kHz の周波数 ) を分周して、所定のクロック ( 例えば 1 Hz ) にする。計時回路 56 は、分周回路 53 により分周された信号に基づいて時間を計測し、制御部 60 へ

50

時間を伝達する。温度センサ58は、LSI30の温度を測定し、制御部60へ伝達する。なお、LSI30の近傍に同一リードフレームに配置させて、電気的にもLSI30と接続されている発振子28の温度はLSI30の温度と同一視することが可能である。すなわち、温度センサ58は、LSI30の周辺に配置された発振子28の温度を精度良く測定することが可能である。制御部60は、計時回路56が計測した時間に基づいて、電力量計測回路22が計測した単位時間当たりの積算電力量などを液晶ディスプレイ15へ表示させる(図1参照)。また、制御部60は、後述するように、発振子28の発振周波数を補正する手段としても機能する。レジスタ部70は、発振子28の発振周波数を補正する際に使用される各種データを格納するための複数のレジスタから構成される。なお、当該複数のレジスタについては後述する発振周波数の補正の説明において詳細に説明する。また、LSI30には、この他にも演算を行う演算回路や、内部電源が内蔵されている。

10

## 【0035】

## &lt;製造手順&gt;

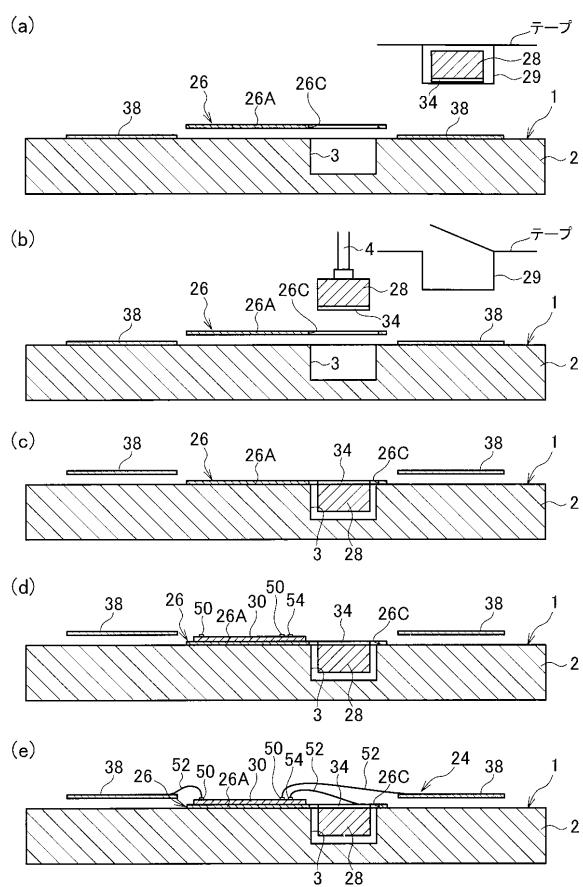

以下、半導体装置24の製造手順について説明する。

先ず、図6(a)に示すように、リードフレーム26を、リード38が下方に位置するように、ボンディング装置1の載置台2に載置する。なお、載置台2には、発振子28が第1の面に固定された状態でリードフレーム26を上下反転したときに発振子28を収容するための凹陥部3が形成されている。又、発振子28は、外部電極34を下方に向かた状態でテープ上のパッケージ29に封入されて搬送されてくる。なお、リードフレーム26には、予めプレス加工等によって開口部26Cを形成しておく。

20

## 【0036】

次に、図6(b)に示すように、パッケージ29を開封し、ピッカー4で発振子28を取り出し、ダイパッド26Aの第1の面、即ち図6(b)における上方の面に、発振子28の外部端子34が開口部26Cに重なるように発振子28を配置し、接着剤でダイパッド26Aに固定する。なお、発振子28が、外部電極34を上方に向かた状態でパッケージ29に封入されているときは、ピッカー4として回転機構付きのものを用い、ピッcker4で発振子28を取り出した後、回転機構で発振子28を上下反転させ、外部端子34を下方に向かってからダイパッド26Aの第1の面に載置するのが好ましい。

30

## 【0037】

発振子28をダイパッド26Aの第1の面に固定したら、図6(c)に示すように、リードフレーム26を上下反転させて載置台2に載置する。これにより、リードフレームは、第1の面が下方を向いた状態で載置台2に載置される。このとき、発振子28は、載置台2の凹陥部3に収容される。

## 【0038】

リードフレーム26を上下反転させて載置台2に載置したら、図6(d)に示すように、ダイパッド26Aの第1の面とは反対側の第2の面における開口部26Cに隣接する部分にLSI30を固定する。なお、図6(d)において第2の面は、ダイパッド26Aの上方の面である。

40

## 【0039】

最後に、図6(e)に示すように、LSI30の電極パッド50とリード38とをボンディングワイヤ52(第1のボンディングワイヤ)で接続すると共に、LSI30の発振子用電極パッド54と発振子28の外部電極34とをボンディングワイヤ52(第2のボンディングワイヤ)で接続して半導体装置24とする。その際に、LSI30の発振子用電極パッド54と発振子28の外部電極34とを接続するボンディングワイヤ52(第2のボンディングワイヤ)の頂点の高さが、LSI30の電極パッド50とリード38とを接続するボンディングワイヤ52(第1のボンディングワイヤ)の頂点の高さよりも低くなるように接続する。また、先にLSI30の発振子用電極パッド54と発振子28の外部電極34とをボンディングワイヤで接続した後に、そのボンディングワイヤ52の上を飛び越えるように、LSI30の電極パッド50とリード38とをボンディングワイヤ5

50

2で接続する。また、LSI30の発振子用電極パッド54と発振子28の外部電極34とを接続するボンディングワイヤ52と、電極パッド50とリード38とを接続するボンディングワイヤ52とが立体交差するように接続を行う。その際に、LSI30の発振子用電極パッド54と発振子28の外部電極34とを接続するボンディングワイヤ52の頂点からずれた位置で、LSI30の電極パッド50とリード38とを接続するボンディングワイヤ52が交差するように接続を行う。

#### 【0040】

図6(a)～図6(e)に示す手順で発振子28とLSI30とをリードフレーム26(ダイパッド26A)に固定し、LSI30と発振子28との接続を行うことにより、LSI30をダイパッド26Aにおいて発振子28が固定される第1の面とは反対側の第2の面に固定しているにもかかわらず、LSI30と発振子28との接続も、LSI30とリードフレームのリード38との接続と同様にダイパッド26Aの第2の面から行うことができ、能率的である。また、発振子28とLSI30とは、リードフレーム26を介さずにボンディングワイヤ32で直接に接続されるので、発振子28とLSI30とをリードフレーム26を介して接続する場合や、ボンディングワイヤをリードフレーム26の裏側に引き回して接続する場合と比較して配線抵抗を低減できる。

10

#### 【0041】

次に、半導体装置24をモールド樹脂32で封止する手順について説明する。

先ず、図7(a)に示すように、半導体装置24を、リードフレーム26(ダイパッド26A)の第1の面、即ち発振子28が固定された側の面が上面となり、リードフレーム26(ダイパッド26A)の第2の面、即ちLSI30が固定された側の面が下面となるように金型5のキャビティ6内部に固定する。ここで、発振子28はLSI30よりも厚みが厚いため、半導体装置24は、リードフレーム26(ダイパッド26A)が金型5におけるキャビティ6の高さ方向の中心よりも下方に位置するようにキャビティ6内部に配置される。又、半導体装置24がキャビティ6内部に固定された状態でアウターリード38Bが金型5の外側に突出するようにする。

20

#### 【0042】

半導体装置24がキャビティ6内部に固定されたら、図7(b)において矢印aで示すように、リードフレーム26の下面に沿って設けられた注入口7からモールド樹脂32を注入する。ここで、前述のように、リードフレーム26(ダイパッド26A)は、金型5におけるキャビティ6の高さ方向の中心よりも下方に位置するように固定されているから、はじめ、モールド樹脂32は、リードフレーム26(ダイパッド26A)に沿って注入される。ここで、注入されたモールド樹脂32は、より広い空間があるほうに流れ込もうとする特性があるので、例えばリードフレーム26の後端とダイパッド26Aとの隙間などからリードフレーム26の上方に流れ込もうとするが、発振子28によって進路を遮られるから、図7(c)において矢印bで示すように、リードフレーム26の下方に回り込むように流れる。

30

#### 【0043】

その後、図7(d)において矢印cで示すように、モールド樹脂32は、リードフレーム26の上面側にも流れ込む。そして、リードフレーム26の下面側がモールド樹脂32で満たされると、リードフレーム26の上面側もモールド樹脂32で満たされる。

40

#### 【0044】

リードフレーム26の両側がモールド樹脂32で満たされたら、金型5を加熱してモールド樹脂32を硬化させる。

#### 【0045】

半導体装置24においては、リードフレーム26(ダイパッド26A)の上面に発振子28が、下面にLSI30が固定されているから、半導体装置24をモールド樹脂32で封止する場合には、リードフレーム26が金型5のキャビティ6の高さ方向中心よりも下方に配置する必要がある。このようにリードフレーム26の上側に広い空間がある場合には、モールド樹脂32はリードフレーム26の上側に流れ込もうとする。

50

**【0046】**

したがって、注入口7からキャビティ6に注入されたモールド樹脂32による圧力は、リードフレーム26の両面に均等には加わらず、リードフレーム26の上面により強く加わると考えられる。

**【0047】**

しかしながら、発振子28を用いてモールド樹脂32の流路を調整し、モールド樹脂32を先にリードフレーム26の下方に流入させることにより、キャビティ6に注入されたモールド樹脂32によるリードフレーム26の下支えが期待できる。したがって、モールド樹脂32を注入中にキャビティ6内部においてリードフレーム26が上下方向に沿ってずれることが防止される。

10

**【0048】**

<作用>

**【0049】**

次に、本実施形態に係る半導体装置24、及び積算電力量計10の作用について説明する。本実施形態に係る半導体装置24では、発振子28とLSI30とがモールド樹脂32で封止されて一体となっており、LSI30は、発振回路51、分周回路53、及び計時回路56が内蔵されているので、図1に示す積算電力量計10の内部の基板に半導体装置24を実装するだけで、時間を計測できる。すなわち、発振子28や分周回路53などを別々に基板へ実装する必要がない。そのため、発振子28と半導体装置24との接続調整などの手間も不要となる。

20

**【0050】**

また、LSI30には、温度センサ58が内蔵されているので、発振子28の周囲の温度を正確に測定できる。これにより、発振子28から出力される信号（周波数）が温度変化によって変動しても、高精度で周波数の補正を行うことができる。そのため高価な高精度発振子を用いることなく、安価な発振子であっても周波数を高精度とすることができる。

**【0051】**

さらに、図2に示すように、発振子28の外部電極34とLSI30の発振子用電極パッド54とは、ボンディングワイヤ52によって開口部26Cを通じて直接接続されている。このため、リードフレーム26を介さずに最短距離で配線が可能となり、配線抵抗を低減できる。また、外部電極34と発振子用電極パッド54とを接続する2本のボンディングワイヤ52の長さが均一となっているので、ボンディングワイヤ52にかかる張力を等しくでき、ボンディングワイヤ52の破断やたわみによる接触を防止できる。また、リードフレーム26を介さずに配線できるので、ノイズの影響も受けにくいため、発振子28からLSI30へスムーズに信号を伝達できる。また、平行に形成されたボンディングワイヤ52の間には、ノイズが発生し易いが、発振子用電極パッド54と外部電極34とを接続しているボンディングワイヤ52（第2のボンディングワイヤ）は、他のボンディングワイヤ52に対して、立体交差しているので、発振子用電極パッド54と外部電極34とを接続するボンディングワイヤ52と他のボンディングワイヤ52間の干渉を低減することができ、特に他のボンディングワイヤ52から発振子28へのノイズの影響を低減できる。さらに、外部電極34は、発振子用電極パッド54より大きいので、ワイヤボンディングを容易に行うことができる。

30

**【0052】**

また、発振子28とLSI30とは、リードフレーム26の表面と裏面に搭載されており、平面視にて投影したときに重なるように配置されているので、発振子28とLSI30とをリードフレーム26の片面に並べて搭載する場合と比べて、半導体装置24の縦横のサイズを小さくできる。

40

**【0053】**

また、LSI30は、ダイパッド26Aの中央部に位置しているので、電極パッド50とインナーリード38とを接続するボンディングワイヤ52の長さを一定にできる。これ

50

により、ワイヤボンディングの作業が容易となり、歩留まりを向上できる。

【0054】

なお、本実施形態では、全てのインナーリード38AがLSI30の電極パッド50へ接続されていたが、これに限らず、図6に示す変形例のように、任意のインナーリード38Aをボンディングワイヤ52でダイパッド26Aへ接続させて、アウターリード38Bをアースに接続することで、ダイパッド26Aを接地してもよい。この場合、ダイパッド26Aが帯電するのを抑制できる。また、リードフレームを挟むようにリードフレームの両面に分けてLSI30と発振子28とを配置しているので、LSI30から発振子28へのノイズをダイパッド26Aによって遮蔽することができる。

【0055】

また、本変形例では、発振子用電極パッド54の近傍に発振回路51が配置されており、この発振回路51を囲むように、デジタル回路部55が配置されている。デジタル回路部55は、デジタル信号を処理する回路部であり、他の素子と比べてノイズが発生しにくい。このため、LSI30に内蔵された他の素子（特にアナログ回路部）から発振回路51が受けるノイズの影響を低減できる。なお、デジタル回路部55の一例としては、CPUなどがある。

【0056】

<発振周波数の補正>

【0057】

次に、本実施形態に係る半導体装置24における、発振子28の発振周波数の温度に依存する誤差を補正する周波数補正処理について説明する。

【0058】

半導体装置24は、例えば出荷時において、半導体装置24内部のLSI30の温度を常温（ここでは、25℃）とした場合、常温より温度が低い基準温度（以下、「低温」ともいう。）とした場合、及び常温より温度が高い基準温度（以下、「高温」ともいう。）とした場合の各々の状態で温度センサ58により温度を測定する。そして、半導体装置24は、例えば出荷後に、この測定で得られた温度をトリミングデータとして、温度センサ58の製造ばらつきにより発生する測定誤差を考慮して、発振子28の周波数誤差を補正する。

【0059】

上述したレジスタ部70（図5参照）は、温度センサ58により測定された温度を示すデータを格納する温度計測値レジスタ71、周辺温度を低温とした場合に温度センサ58により測定された温度を示すデータを格納する低温レジスタ72、周辺温度を常温とした場合に温度センサ58により測定された温度を示すデータを格納する常温レジスタ73、周辺温度を高温とした場合に温度センサ58により測定された温度を示すデータを格納する高温レジスタ74、及び、これらの温度を示すデータから導出される発振子28の発振周波数の補正值を格納するための周波数補正レジスタ75を有している。なお、各レジスタは制御部60にデータバス76を介して接続されており、制御部60はデータバス76を介して各レジスタに対して読み書きを行う。

【0060】

半導体装置24は、発振子28の周波数誤差を補正するために、半導体装置24の温度を低温とした場合、常温とした場合、及び高温とした場合の各々の状態で温度センサ58により温度を測定し、測定で得られた温度をトリミングデータとしてそれぞれ低温レジスタ72、常温レジスタ73、及び高温レジスタ74に格納する第1周波数補正処理を行う。

【0061】

試験者は、例えば出荷テスト時に、まず、槽内の温度が常温に設定された恒温槽の内部に半導体装置24を配置する。そして、ユーザは、半導体装置24に例えば温度センサ58による温度の計測を開始させるための計測動作信号を入力させることにより、半導体装置24に第1周波数補正処理を実行させる。この際、ユーザは、例えば半導体装置24の

10

20

30

40

50

リード 38 に当該計測動作信号を出力する機器を接続することにより、半導体装置 24 に当該計測動作信号を入力させる。また、当該計測動作信号は、恒温槽に設定された温度が常温、高温、または低温の何れであるかを示す情報を含んでいる。

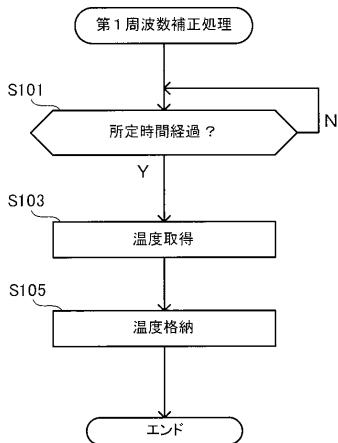

#### 【0062】

図 9 は、本実施形態に係る半導体装置 24 における第 1 周波数補正処理の流れを示すフローチャートである。当該第 1 周波数補正処理を実行するプログラムは、上記計測動作信号が入力されたタイミングで実行されるプログラムであり、制御部 60 が有する記憶手段に予め記憶されている。なお、実行されるタイミングはこれに限定されない。

#### 【0063】

ステップ S101において、制御部 60 は、計測動作信号が入力されてから所定時間（例えば、数時間）が経過したか否かを判定する。なお、当該所定時間は、半導体装置 24 の内部温度（LSI30 の温度）が、恒温槽の温度と一致するために必要な時間とするといい。

10

#### 【0064】

ステップ S101において所定時間が経過したと判定された場合、ステップ S103において、制御部 60 は、温度センサ 58 による計測値を取得する。なお、温度センサ 58 による計測値は、温度計測値格納レジスタ 71 に格納される。また、温度センサ 58 によって計測値を取得する際には、所定時間（例えば、1 分）経過毎に計測を行い、複数回の計測により得られた複数の計測値を平均した値を計測値として取得しても良い。

20

#### 【0065】

ステップ S105において、制御部 60 は、取得した計測値を、恒温槽に設定された温度が常温（ここでは、25℃）である場合には、常温レジスタ 73 に格納し、恒温槽に設定された温度が高温である場合には、高温レジスタ 74 に格納し、恒温槽に設定された温度が低温である場合には、低温レジスタ 72 に格納し、第 1 周波数補正処理を終了する。なお、上記第 1 周波数補正処理は、ウェハ状態のときに予め行っても良い。

20

#### 【0066】

試験者は、槽内の温度が常温に設定された恒温槽の内部に半導体装置 24 を配置した状態に加えて、槽内の温度が高温に設定された恒温槽の内部に半導体装置 24 を配置した状態、及び槽内の温度が低温に設定された恒温槽の内部に半導体装置 24 を配置した状態の各々において、半導体装置 24 にそれぞれ上記ステップ S101 乃至 S105 の処理を行わせる。これにより、常温レジスタ 73、高温レジスタ 74、低温レジスタ 72 にそれぞれ温度センサ 58 による計測値が格納される。

30

#### 【0067】

本実施形態に係る半導体装置 24 は、上述した処理が行われた後に出荷され、出荷後の予め定められたタイミングで、後述する第 2 周波数補正処理が行われる。

#### 【0068】

ユーザは、例えば出荷後に、半導体装置 24 に例えば周波数補正值の導出を開始させるための導出動作信号を入力させることにより、半導体装置 24 に第 2 周波数補正処理を実行させる。この際、ユーザは、例えば半導体装置 24 のリード 38 に当該導出動作信号を出力する機器を接続することにより、当該導出動作信号を入力させる。または、半導体装置 24 が一定の間隔で第 2 周波数補正処理を実行するようにしてても良い。

40

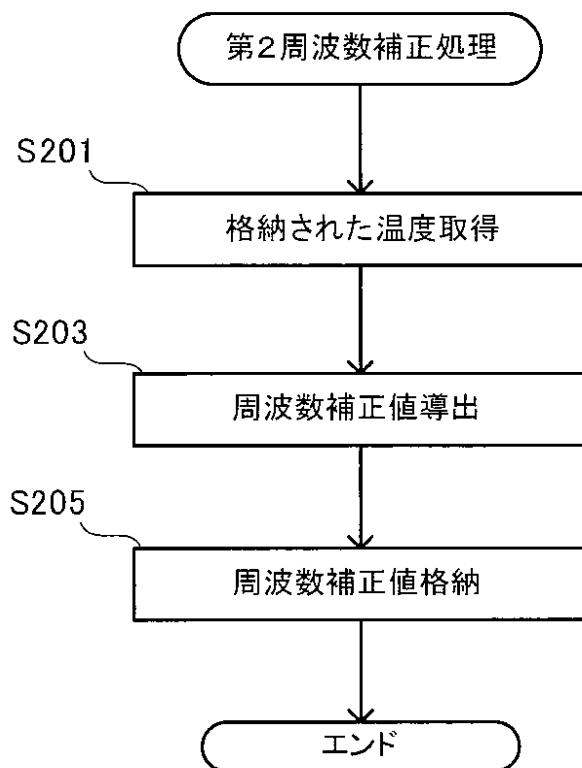

#### 【0069】

図 10 は、本実施形態に係る半導体装置 24 における第 2 周波数補正処理の流れを示すフローチャートである。当該第 2 周波数補正処理を実行するプログラムは、半導体装置 24 の出荷後に、上記導出動作信号が入力されたタイミングで実行されるプログラムであり、制御部 60 が有する記憶手段に予め記憶されている。

#### 【0070】

ステップ S201において、制御部 60 は、常温レジスタ 73、高温レジスタ 74、及び低温レジスタ 72 にそれぞれ格納されている計測値を取得する。

#### 【0071】

50

ステップ S 203において、制御部 60 は、ステップ S 201において取得した計測値を用いて、発振子 28 の発振周波数の補正值（以下、「周波数補正值」ともいう。）を導出する。

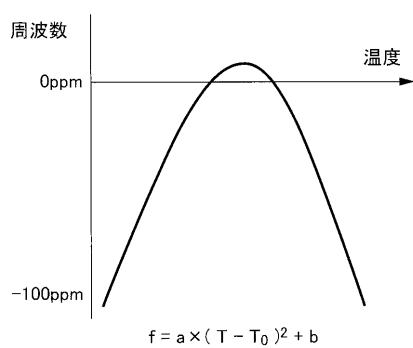

#### 【0072】

図 11 は、本実施形態に係る半導体装置における温度と周波数偏差との関係を示す図である。なお、図 11 は、実際の温度環境で得られた周波数誤差ではなく、二次関数による計算によって得られる理論値を示している。上記二次関数は、下記（1）式で表される。なお、下記（1）式において、 $f$  は周波数偏差、 $a$  は二次温度係数、 $T$  は測定された温度、 $T_0$  は頂点温度、 $b$  は頂点誤差である。上記二次温度係数  $a$  は、発振子 28 の個体差に応じて予め定められた定数であり、制御部 60 が有する記憶手段に予め記憶されている。10

#### 【0073】

##### 【数 1】

$$f = a \times (T - T_0)^2 + b \quad \dots (1)$$

#### 【0074】

第 1 実施形態では、周波数偏差  $f$  が未知であるが、既知である二次温度係数  $a$ 、常温レジスタ 73 に格納されている常温での計測値、高温レジスタ 74 に格納されている高温での計測値、及び低温レジスタ 72 に格納されている低温での計測値から、頂点誤差  $b$  を導出することができる。そして、制御部 60 は、常温での温度  $T_0$  において最も周波数偏差が小さくなるようにするために、頂点誤差  $b$  の値を周波数補正值とする。20

#### 【0075】

なお、上記周波数補正值の導出において、例えば -10 での測定環境下において、温度センサ 58 による計測値が -8 であった場合には、+2 に対応する補正が必要ということになる。出荷段階における製品は、常温、各レジスタに記憶されている高温及び低温の 3 ポイントの計測値をデータバス 76 を介して読み出し、読み出したデータをトリミングデータとして、実際の環境下の温度を導出する。温度センサ 58 による計測値が、各レジスタに記憶されていない値であった場合には、近接する二つのレジスタの値を用いて、実際の環境下の温度を導出すればよい。

#### 【0076】

ステップ S 205において、制御部 60 は、ステップ S 203において導出した周波数補正值を示すデータを、周波数補正レジスタ 75 に格納する。そして、半導体装置 24 では、分周回路 53 が、周波数補正レジスタ 75 に格納されている周波数補正值を用いて、発振回路から入力した信号からクロック信号を生成することで、発振子 28 の発振周波数の補正が行われる。30

#### 【0077】

このように、第 1 実施形態に係る半導体装置 24 によると、出荷時に、半導体装置 24 の 3 ポイントの環境温度下での温度センサ 58 による計測値をトリミングデータとして準備しておき、当該トリミングデータを元に周波数補正值を導出することにより、半導体装置 24 の個体毎の温度センサ 58 の製造上のばらつきに依存せずに、高精度な温度情報に基づいた周波数補正值を得ることができる。40

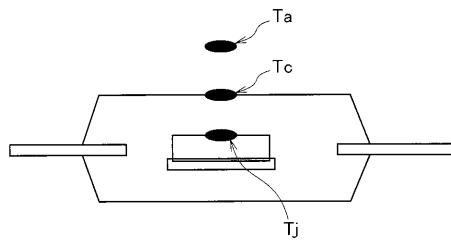

#### 【0078】

従来のパッケージ化された半導体装置において、図 32 に示すように、当該半導体装置を駆動させる場合、半導体装置の周辺温度  $T_a$ （）、パッケージ表面温度  $T_c$ （）及びチップ表面温度  $T_j$ （）は各々異なってくる。例えば、チップ表面温度  $T_j$  は、パッケージ熱抵抗（ジャンクション及び雰囲気間）を  $j_a$ 、チップの消費電力（最大または平均）を  $P$  とすると、下記の（2）式で表される。

#### 【0079】

##### 【数 2】

$$T_j = P \times \theta_{ja} + T_a$$

$$\dots (2)$$

10

20

30

40

50

## 【0080】

しかしながら、本実施形態に係る半導体装置24では、温度センサ58と発振子28とが一体に封止されていることにより、温度センサ58の周辺温度と発振子28の周辺温度とが同一となるため高精度に発振子28の温度をLSI30が有する温度センサ58で測定することができ、そのため発振子28及び温度センサ58間の温度差によって周波数補正の精度が低下することが防止される。

## 【0081】

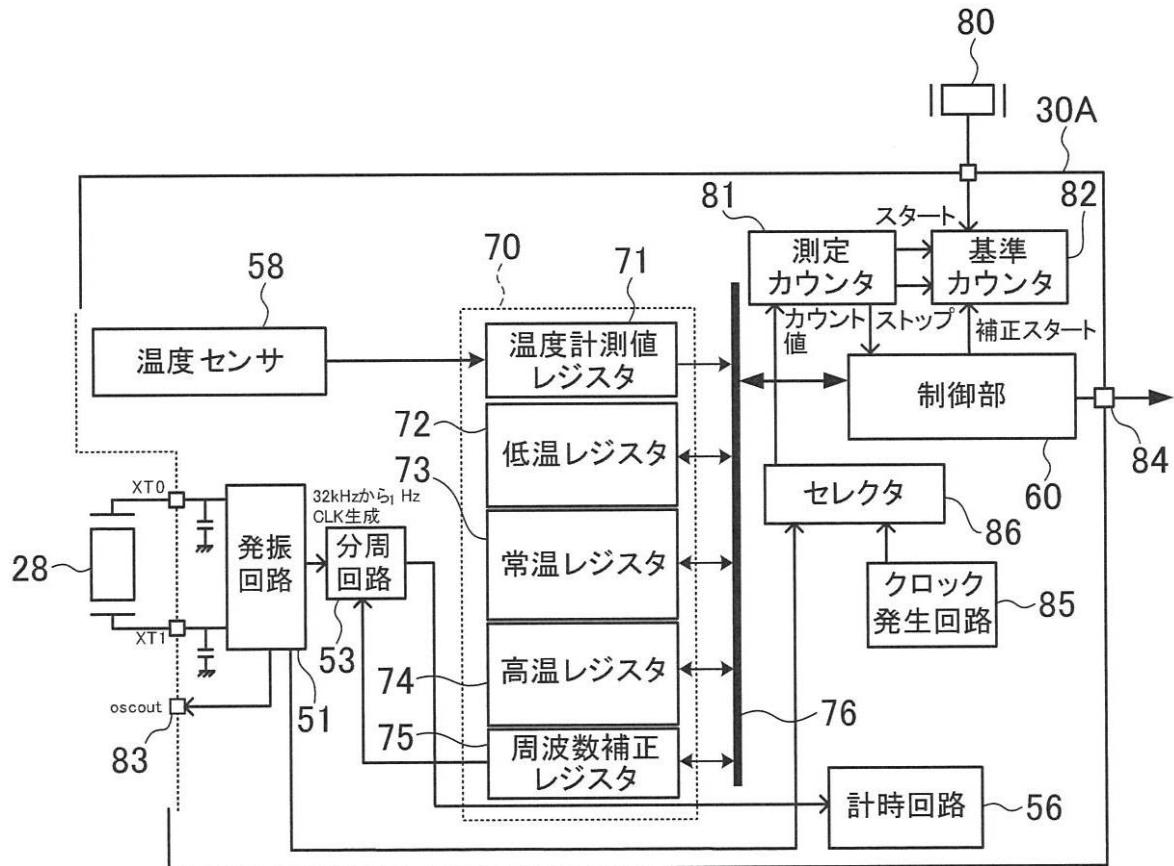

(第2実施形態)

## 【0082】

次に、本発明の第2実施形態に係る半導体装置24について説明する。なお、第1実施形態と同一の構成については、同一の符号を付し、説明を省略する。10

## 【0083】

図12に示すように、第2実施形態に係る半導体装置24には、LSI30Aに対して、発振子28の発振周波数の補正の際に基準とするクロック信号（以下、「基準クロック信号」ともいう。）を入力する、基準信号発振子80を備えたクロック発生装置が接続されている。また、第2実施形態に係る半導体装置24のLSI30Aは、第1実施形態に係る半導体装置24のLSI30の構成に加えて、測定カウンタ81、基準カウンタ82、及びクロック信号を発振回路57から外部へ出力する出力端子83を更に備えている。

## 【0084】

図13(a)及び(b)に示すように、基準信号発振子80は、発振子28よりも発振周波数が高い水晶振動子などの発振子である。なお、第2実施形態では、発振子28の発振周波数が32.768KHzであり、基準信号発振子80の発振周波数が10MHzである。20

## 【0085】

測定カウンタ81は、発振回路51に接続されていて、制御部60の制御に基づいて、発振子28によるクロック信号（以下、「測定クロック信号」ともいう。）を発振回路51から受信して当該クロック信号のクロック数をカウントするカウンタである。基準カウンタ82は、基準信号発振子80を備えたクロック発生装置に接続されていて、制御部60の制御に基づいて、基準信号発振子80によるクロック信号を受信して当該クロック信号のクロック数をカウントする。なお、図13(a)及び(b)に示すように、基準カウンタ82と測定カウンタ81とは、相互に同期しながら略同時に同一時間内にクロック数のカウントを行う。なお、測定カウンタ81と基準カウンタ82は、動作信号に基づいて相互に同期しながら動作させてもよいし、同期カウンタを用いても良い。30

## 【0086】

また、第2実施形態では、レジスタ部70において、温度計測値レジスタ71に、温度センサ58により測定された温度を示すデータが格納され、低温レジスタ72に、周辺温度を常温(25)より低温の基準温度とした場合に温度センサ58により測定された温度及びその温度における周波数誤差を示すデータが格納され、常温レジスタ73に、周辺温度を常温(25)とした場合に温度センサ58により測定された温度及びその温度における周波数誤差を示すデータが格納され、高温レジスタ74に、周辺温度を常温(25)40

)より高温の基準温度とした場合に温度センサ58により測定された温度及びその温度における周波数誤差を示すデータが格納され、周波数補正レジスタ75に、上述した周波数誤差を示すデータから導出される周波数補正值を示すデータが格納される。

## 【0087】

<発振周波数の補正>

## 【0088】

ユーザは、例えば出荷テスト時に、まず、槽内の温度が常温(ここでは、25)に設定された恒温槽の内部に半導体装置24を配置する。そして、ユーザは、半導体装置24に例えば温度センサ58による温度の計測を開始させるための計測動作信号を入力することにより、半導体装置24に第1周波数補正処理を実行させる。この際、ユーザは、例50

えば半導体装置 24 のリード 38 に当該計測動作信号を出力する機器を接続することにより、半導体装置 24 に当該計測動作信号を入力させる。また、当該計測動作信号には、恒温槽に設定された温度が常温、高温、または低温の何れであるかを示す情報を含んでいる。

#### 【0089】

図 14 は、本実施形態に係る半導体装置 24 における第 1 周波数補正処理の流れを示すフローチャートである。当該第 1 周波数補正処理を実行するプログラムは、半導体装置 24 の出荷時に、上記計測動作信号が入力されたタイミングで実行されるプログラムであり、制御部 60 が有する記憶手段に予め記憶されている。

#### 【0090】

ステップ S301において、制御部 60 は、計測動作信号が入力してから所定時間（例えば、数時間）が経過したか否かを判定する。当該所定時間は、半導体装置 24 の内部温度（LSI 30 の温度）が、恒温槽の温度と一致するために必要な時間とするといい。

#### 【0091】

ステップ S301において所定時間が経過したと判定された場合、ステップ S303において、制御部 60 は、温度センサ 58 による計測値を取得する。なお、温度センサ 58 による計測値は、温度計測値格納レジスタ 71 に格納される。また、温度センサ 58 は、試験により測定精度が予め定められた基準値以上であることが確認済みであり、温度センサ 58 により高精度に温度測定を行えることが保障されている。または温度センサ 58 による計測値を用いて補正を行うようにしても良い。

20

#### 【0092】

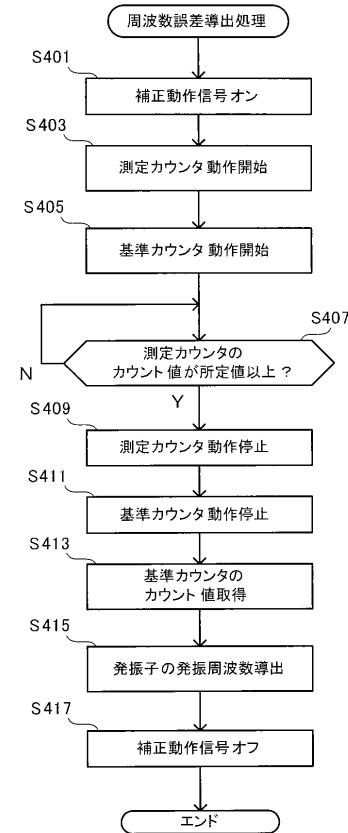

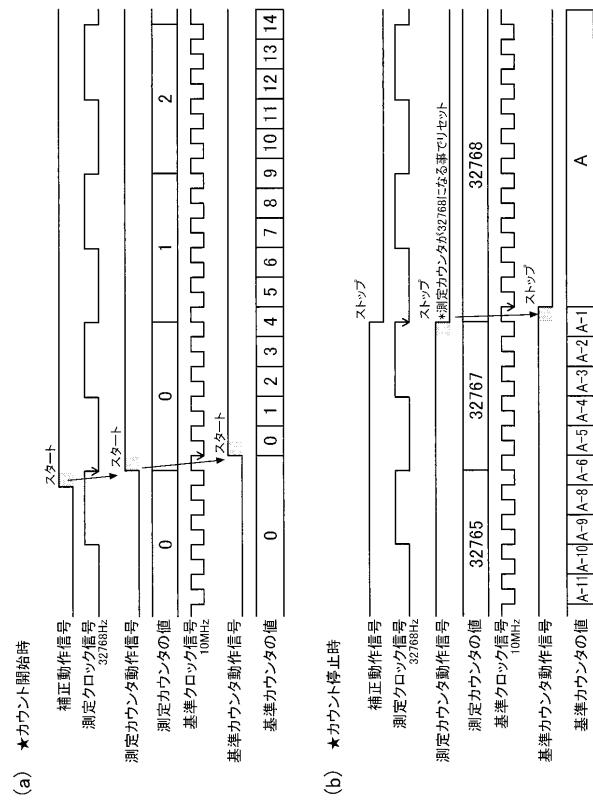

ステップ S305において、制御部 60 は、発振子 28 の発振周波数の誤差を導出する周波数誤差導出処理を行う。図 15 は、本実施形態に係る周波数誤差導出処理の流れを示すフローチャートである。また、図 16 は、本実施形態に係る周波数誤差導出処理におけるタイミングチャートであり、(a) は、カウント開始時を示す図であり、(b) は、カウント停止時を示す図である。

#### 【0093】

ステップ S401において、制御部 60 は、測定カウンタ 81 に対して補正動作信号を出力する。補正動作信号を入力した測定カウンタ 81 は、ステップ S403において、動作を開始し、発振子 28 によるクロック信号のクロック値のカウントを開始すると共に、基準カウンタ 82 に対して開始信号を出力する。

30

#### 【0094】

開始信号を受信した基準カウンタ 83 は、ステップ S405において、基準信号発振子 80 によるクロック信号のクロック値のカウントを開始する。すなわち、図 16 (a) に示すように、補正動作信号がオンになると、測定カウンタ 81 がカウントを開始すると共に、基準カウンタ 82 も測定カウンタ 81 に同期してカウントを開始する。

#### 【0095】

ステップ S407において、測定カウンタ 81 は、測定カウンタのカウント値が予め定められた所定値（本実施形態では、1 秒に相当する 32.768）以上であるか否かを判定する。ステップ S407において所定値以上でない場合は、測定カウンタ 81 はそのままカウントを継続する。

40

#### 【0096】

ステップ S407において所定値以上であると判定された場合は、ステップ S409において、測定カウンタ 81 は、カウントを停止すると共に、基準カウンタ 82 に対して停止信号を出力する。

#### 【0097】

停止信号を受信した基準カウンタ 82 は、ステップ S411において、カウントを停止する。すなわち、図 16 (b) に示すように、補正動作信号がオフになると、測定カウンタ 81 がカウントを停止すると共に、基準カウンタ 82 も測定カウンタ 81 に同期してカウントを停止する。

50

## 【0098】

ステップS413において、制御部60は、基準カウンタ82のカウント値を取得する。

## 【0099】

ステップS415において、制御部60は、ステップS413において取得した基準カウンタ82のカウント値から、発振子28の発振周波数の誤差を導出する。すなわち、制御部60は、発振子28による測定クロック信号において同一時間内に得られたカウント値（すなわち、32,768）を、発振子28よりも高精度に計時を行うことができる基準信号発振子80による基準クロック信号のカウント値と比較することにより、発振子28の発振周波数の誤差を導出する。

10

## 【0100】

例えば、基準信号発振子80の発振周波数が10MHzであるため、基準カウンタ82のカウント値が”100000000（十進数）”であれば、発振子28により正確に1秒を計時できていると推測でき、発振周波数の誤差は0で補正する必要がなく、発振周波数の誤差（周波数補正值）を0とする。一方、例えば、基準カウンタ82のカウント値が”10000002（十進数）”であれば、発振子28の発振周波数が0.2ppmだけ遅くなっていると推測でき、発振子28の発振周波数をその誤差の分、すなわち0.2ppm早くなるように補正する必要があり、発振周波数の誤差（周波数補正值）を+0.2ppmとする。また、例えば、基準カウンタ82の値が”9999990（十進数）”であれば、発振子28の発振周波数が1.0ppmだけ早くなっているので、発振子28の発振周波数をその誤差の分、すなわち1.0ppm遅くする必要があり、発振周波数の誤差（周波数補正值）を-1.0ppmとする。

20

## 【0101】

ステップS417において、制御部60は、測定カウンタ81に対する補正動作信号の出力を停止し、周波数誤差導出処理プログラムを終了する。また、測定カウンタ81及び基準カウンタ82は、補正動作信号の入力が停止すると、動作を停止する。

30

## 【0102】

ステップS307において、制御部60は、ステップS303において取得した温度の計測値と、ステップS415において導出された周波数誤差とを、恒温槽に設定された温度が常温である場合には、常温レジスタ73に、恒温槽に設定された温度が高温である場合には、高温レジスタ74に、恒温槽に設定された温度が低温である場合には、低温レジスタ72に格納して、第1周波数補正処理プログラムを終了する。

40

## 【0103】

ユーザは、槽内の温度が常温に設定された恒温槽の内部に半導体装置24を配置した状態に加えて、槽内の温度が高温の基準温度に設定された恒温槽の内部に半導体装置24を配置した状態、及び槽内の温度が低温の基準温度に設定された恒温槽の内部に半導体装置24を配置した状態において、半導体装置24にそれぞれ上記ステップS301乃至S309の処理を行わせる。これにより、常温レジスタ73、高温レジスタ74、低温レジスタ72にそれぞれ温度センサ58による温度の計測値及び発振子28の発振周波数の誤差が格納される。

40

## 【0104】

本実施形態に係る半導体装置24は、上述した処理を行った後に出荷され、出荷後の予め定められたタイミングで、発振子28の発振周波数が周波数補正レジスタ75に格納された周波数補正值を示すデータを用いて上述した(1)式に基づいて補正される。なお、第2実施形態における二次温度係数a及び頂点誤差bは、各温度において導出された周波数誤差によって決定される。なお、周波数誤差を決定したい温度よりも高い温度のレジスタと低い温度のレジスタに格納された発振周波数の誤差の値の差分から直線近似によって求めるようにしても良い。そして、システムリセット時や定期的に、あるいは、リード38を介する所定の信号の入力に応じて、または上記(1)式を用いて発振子28の発振周波数を補正をする際に後述する第2周波数補正処理が行われる。

50

**【0105】**

ユーザは、半導体装置24に例えば周波数補正值の導出を開始させるための導出動作信号を入力することにより、半導体装置24に第2周波数補正処理を実行させる。この際、ユーザは、例えば半導体装置24のリード38に当該計測動作信号を出力する機器を接続することにより、当該導出動作信号を入力させる。

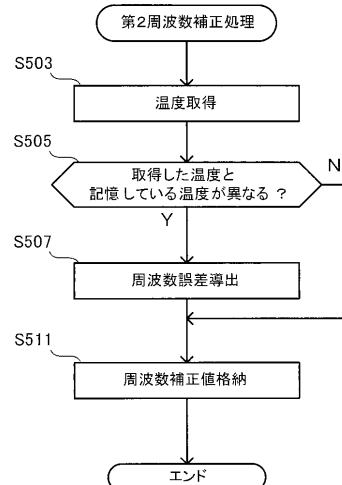

**【0106】**

図17は、本実施形態に係る半導体装置24における第2周波数補正処理の流れを示すフローチャートである。当該第2周波数補正処理を実行するプログラムは、上記計測動作信号が入力されたタイミングで実行されるプログラムであり、制御部60が有する記憶手段に予め記憶されている。

10

**【0107】**

ステップS503において、制御部60は、温度センサ58により現在の環境温度を計測し、その計測値を取得する。なお、温度センサ58による計測値は、温度計測値格納レジスタ71に格納される。

**【0108】**

ステップS505において、制御部60は、ステップS503において取得した温度が、恒温槽で計測された温度（例えばステップS303において取得された温度）と異なっているか否かを判定する。なお、この判定が不要な場合には、ステップS503の処理を行った後に、当該ステップS505の処理を行わずに、ステップS505に移行してもよい。

20

**【0109】**

ステップS505において温度が異なっていないと判定された場合は、制御部60は、周波数補正值を変更する必要がないと判断し、第2周波数補正処理を終了する。

**【0110】**

ステップS505において温度が異なっていると判定された場合は、制御部60は、ステップS507において、上述したステップS305と同様の処理を行うことで、周波数誤差を導出する。また、ステップS507において、制御部60は、レジスタ部70の各レジスタに記憶されているデータを、上述した（1）式に代入することにより、二次温度係数a及び頂点誤差bを導出する。

30

**【0111】**

ステップS511において、制御部60は、周波数補正值を周波数補正レジスタ75に格納する。この際、ステップS505において温度が異なっていないと判定された場合は、低温レジスタ72、常温レジスタ73、及び高温レジスタ74に格納されている温度及び周波数誤差を用いて周波数補正值を導出して格納する。一方、ステップS505において温度が異なっていると判定された場合は、ステップS507において導出した周波数誤差を用いて周波数補正值を導出して格納する。

**【0112】**

そして、半導体装置24では、分周回路53が、発振回路から入力した信号をこの周波数補正レジスタ75に格納されている周波数補正值に基づいて補正することで、発振子28の発振周波数の補正を行う。

40

**【0113】**

以上のように、第2実施形態に係る半導体装置24によると、実温度での周波数誤差を測定することで、発振子28の製造ばらつきにより温度によって周波数偏差が異なっていても、常に安定した計時を刻むことが可能となる。

**【0114】**

また、第2実施形態に係る半導体装置24によると、半導体装置24のLSI30Aの内部に時間補正回路を内蔵させる事で、外部から供給されるクロック信号の周波数精度が低くても高精度に時間測定を行うことができる。

**【0115】**

また、第2実施形態に係る半導体装置24によると、発振子28を内蔵したことによる

50

空き端子を別機能（例えばシリアル通信やI<sub>2</sub>Cの追加など）に置き換えることで、端子数が限られても高機能化を実現することができる。

【0116】

なお、本実施形態では、基準信号発振子80、測定カウンタ81及び基準カウンタ82を用いて発振子28の発振周波数の誤差を導出するが、誤差の導出方法はこれに限定されず、発振回路51から出力されるoscout端子から出力されるクロック信号における所定時間（本実施形態では、1秒（32,768CLK））の計時が、他の方法で正確に計時された当該所定時間と比較することにより、発振子28により当該所定時間の計時が実際にどれくらいかかっているかを測定しても良い。

【0117】

また、第2実施形態に係る半導体装置24における発振子28の発振周波数の誤差の補正を行った上で、必要に応じて、第1実施形態に係る半導体装置24における温度センサ58の測定誤差を考慮した補正を行っても良い。

【0118】

図18及び図19は、本実施形態に係る半導体装置24のLSI30Aの電気的構成の別例を示すブロック図である。

【0119】

図18に示すように、半導体装置24は、出力端子84を備えていて、制御部60により導出された発振子28の発振周波数の誤差（周波数補正值）が半導体装置24の外部に出力端子84を介して出力されるようにしても良い。これにより、基準クロック発生装置の特性劣化などを見つける為の定期校正を実施する事ができる。

【0120】

また、図19に示すように、半導体装置24のLSI30Aは、測定カウンタ81に校正の基準になる高精度のクロック発生装置85を接続しても良い。この場合には、上述したステップS413において、制御部60は、測定カウンタ81のカウント値及び基準カウンタ82のカウント値を取得し、測定カウンタ81のカウント値と基準カウンタ82のカウント値とを比較する。例えば、測定カウンタ81のクロック信号の周波数を10MHz、基準カウンタ82に接続されたクロック発生装置85の周波数を10MHzとする、基準信号発振子80を有するクロック発生装置と基準カウンタ82に接続されたクロック発生装置84とが同一の周波数のクロック信号を発生していれば、測定カウンタ81のカウント値と基準カウンタ82のカウント値とが同一の値になるが、基準信号発振子80の特性が変化している場合には、測定カウンタ81のカウント値と基準カウンタ82のカウント値とに差が生じる。測定カウンタ81のカウント値と基準カウンタ82のカウント値とに差が生じた場合には、その差を制御部60で、予め定められた許容誤差範囲内か否かを判断して、判断結果を8の出力端子84に出力する。これにより、基準信号発振子80を備えたクロック発生装置の特性劣化などを見つける為の定期校正を実施することができる。

【0121】

また、図19に示すように、半導体装置24のLSI30Aにクロック発生装置85が内蔵されている場合であっても、LSI30Aの内部に、発振回路51から出力されたクロック信号及びクロック発生装置85から出力されたクロック信号の何れか一方を選択に入力し、測定カウンタ81に出力するセレクタ86を接続しても良い。図19に示す半導体装置24では、セレクタ86を接続することにより、図18に示す半導体装置24と同様に機能させることができる。

【0122】

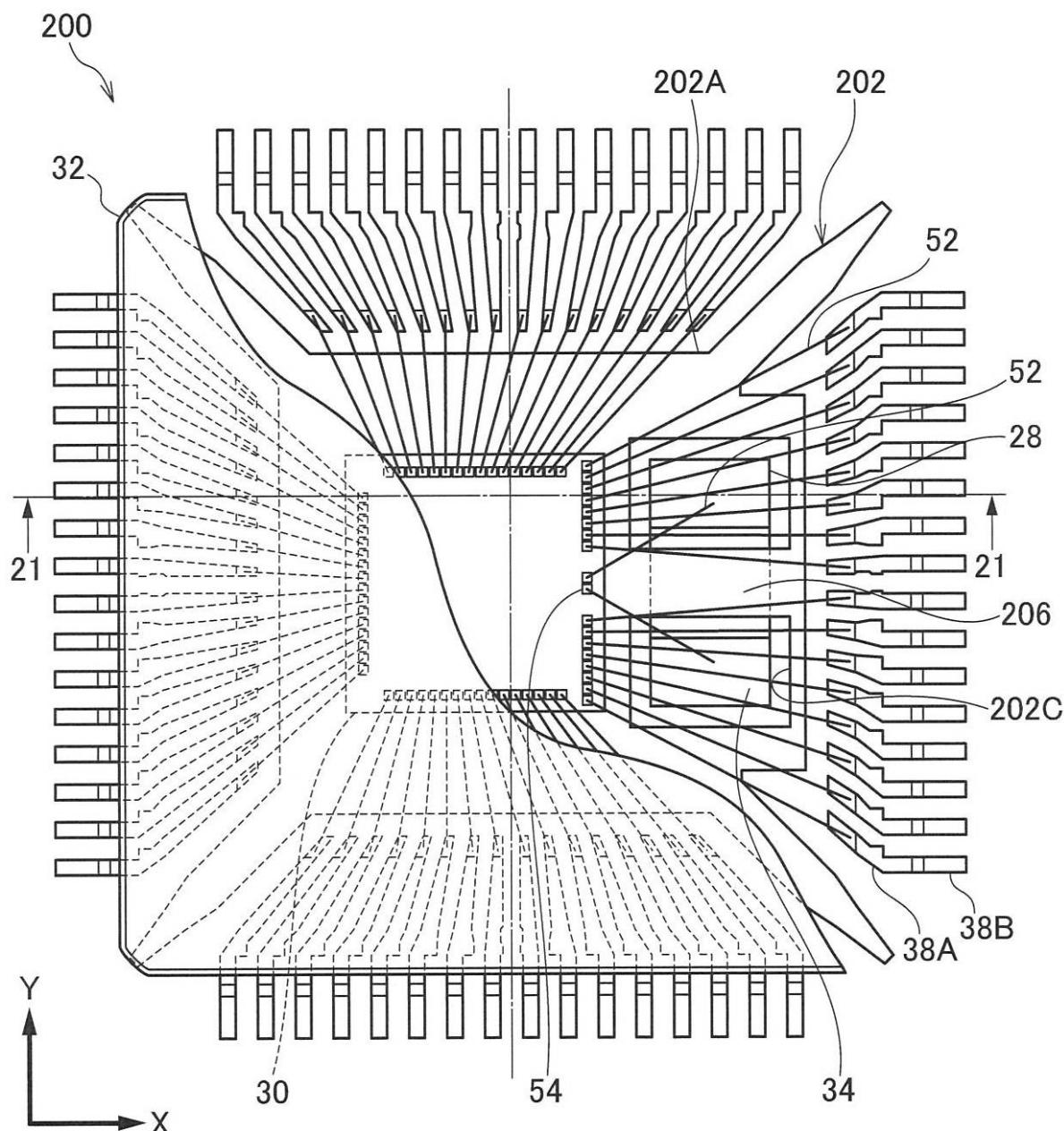

（第3実施形態）

【0123】

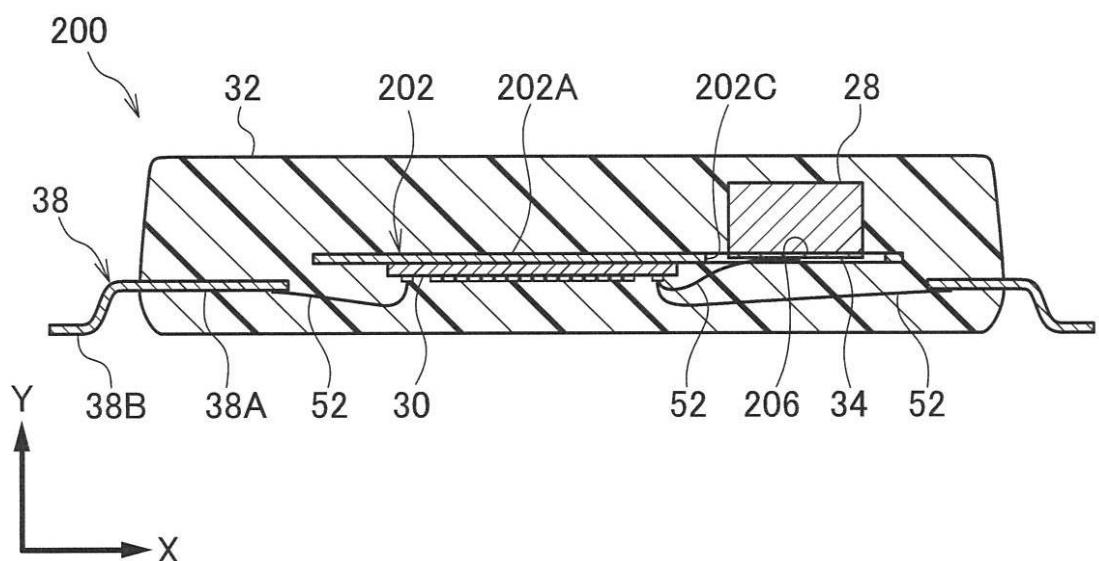

次に、本発明の第3実施形態に係る半導体装置200について説明する。なお、第1実施形態と同一の構成については、同一の符号を付し、説明を省略する。図9及び図10に示すように、本実施形態に係る半導体装置200を構成するリードフレーム202の表面

の発振子搭載用梁 206 には、接着剤を介して発振子 28 が搭載されており、リードフレーム 202 の裏面のダイパッド 202A には、接着剤を介して LSI30 が搭載されている。

#### 【0124】

ここで、LSI30 は、ダイパッド 202A の中央部より左側にずらして搭載されており、ダイパッド 202A に形成された開口部 202C と重ならないようになっている。このため、LSI30 の全面がダイパッド 202A と接着している。

#### 【0125】

ダイパッド 202A の第 1 の面に発振子 28 を、第 1 の面とは反対側の第 2 の面に LSI30 を固定し、LIS30 の LSI30 の発振子用電極パッド 54 と発振子 28 の外部電極 34、および LSI30 の電極パッド 50 とインナーリード 38A とをボンディングワイヤ 52 で接続して半導体装置 200 とする手順は、実施形態 1 の半導体装置 24 と同様に図 6 (a) ~ (e) に示すとおりである。半導体装置 200 をモールド樹脂 32 で封止する手順も、同様に図 7 (a) ~ (d) に示すとおりである。

10

#### 【0126】

本実施形態に係る半導体装置 200 では、第 1 実施形態に係る半導体装置 24 と比べて、LSI30 の接着強度を向上できる。また、発振子 28 の外部電極 34 の全面が露出しているので、発振子用電極パッド 54 と外部電極 34 とをボンディングワイヤ 52 で容易に接続できる。

20

#### 【0127】

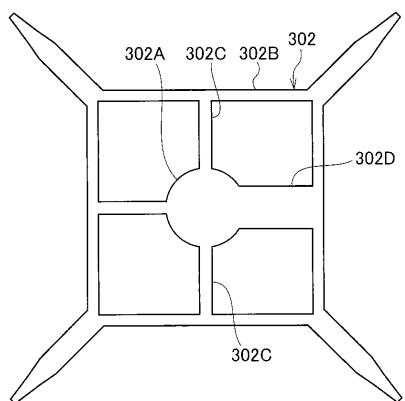

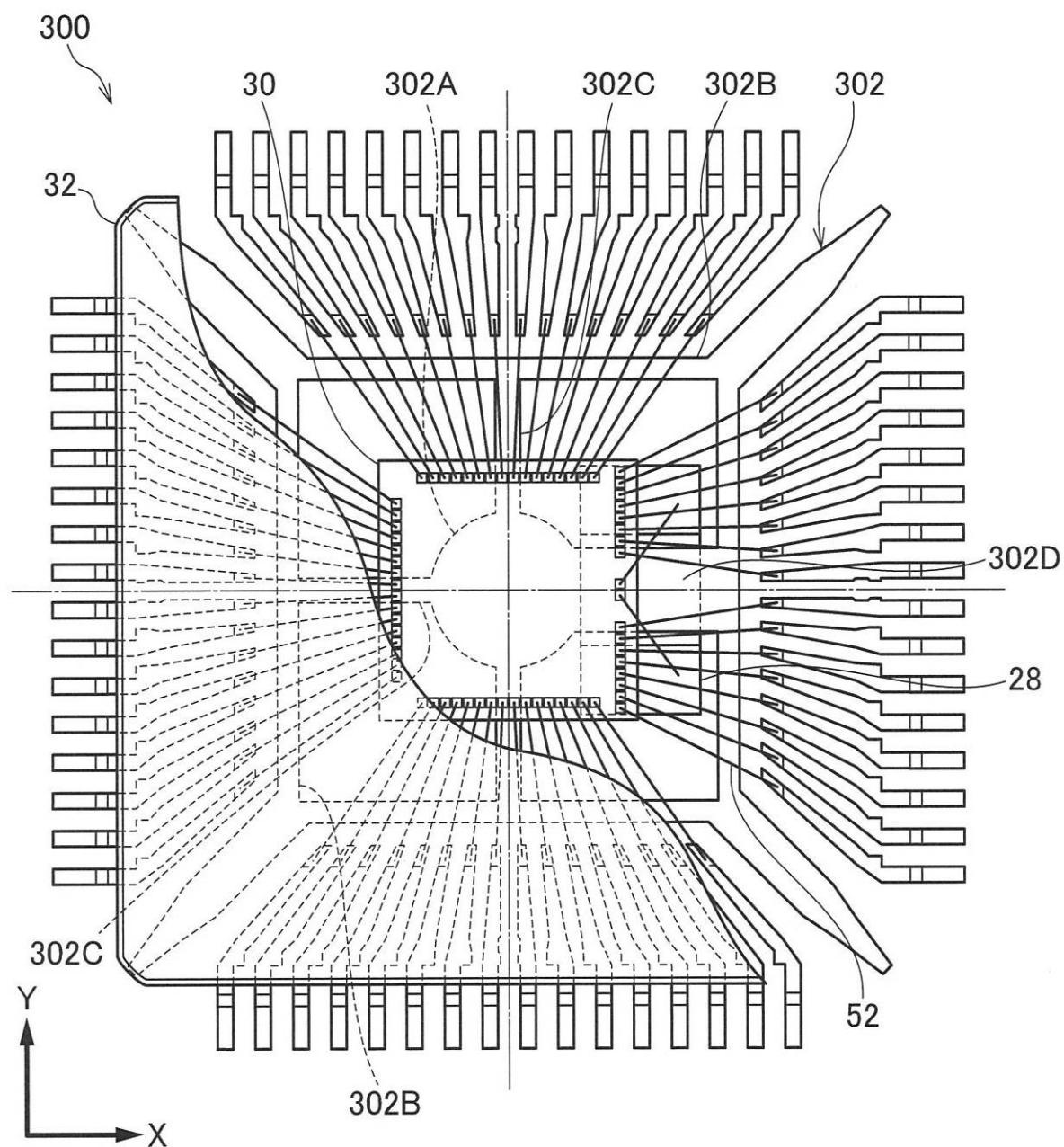

(第 4 実施形態)

#### 【0128】

次に、本発明の第 4 実施形態に係る半導体装置 300 について説明する。なお、第 1 実施形態と同一の構成については、同一の符号を付し、説明を省略する。図 22、及び図 23 に示すように、本実施形態に係る半導体装置 300 を構成するリードフレーム 302 は、円形のダイパッド 302A と、ダイパッド 302A の外周側に設けられた外枠部 302B とを支持梁 302C、及び発振子搭載梁 302D で架け渡した形状となっている。

30

#### 【0129】

ダイパッド 302A は、リードフレーム 302 の中央部に位置しており、ダイパッド 302A の裏面に搭載された LSI30 より小さくなっている。支持梁 302C は、ダイパッド 302A の上下、及び左側へ延びており、発振子搭載梁 302D は、ダイパッド 302A の右側へ延びている。また、発振子搭載梁 302D は、支持梁 302C より広幅に形成されると共に、発振子搭載梁 302D の幅は、発振子 28 の外部電極 34 間の距離よりも狭くなるように形成されており、接着剤を介して発振子 28 が搭載されている。

#### 【0130】

ダイパッド 302A の第 1 の面に発振子 28 を、第 1 の面とは反対側の第 2 の面に LSI30 を固定し、LIS30 の LSI30 の発振子用電極パッド 54 と発振子 28 の外部電極 34、および LSI30 の電極パッド 50 とリード 38 とをボンディングワイヤ 52 で接続して半導体装置 300 とする手順は、実施形態 1 の半導体装置 24 と同様に図 6 (a) ~ (e) に示すとおりである。半導体装置 300 をモールド樹脂 32 で封止する手順も、同様に図 7 (a) ~ (d) に示すとおりである。

40

#### 【0131】

本実施形態に係る半導体装置 300 では、ダイパッド 302A をできるだけ小さく形成し、ダイパッド 302A の外側を打ち抜いているので、第 1 実施形態に係る半導体装置 24 と比べて、リードフレーム 302 にかかる材料費を削減することができる。

#### 【0132】

また、ダイパッド 302A を小さくしたことで、第 1 実施形態と比べて、モールド樹脂 32 と LSI30 との接触面積が大きくなる。ここで、LSI30 とモールド樹脂 32 の接着力は、LSI30 とダイパッド 302A との接着力より大きいため、モールド樹脂 32 と LSI30 との接触面積が大きくなった分だけ、LSI30 が剥離しにくくなる。特

50

に、リフロー等で半導体装置 300 を基板に実装する際には、半導体装置 300 が加熱されるため、ダイパッド 302A とモールド樹脂 32 との密着力が低下する虞があるが、ダイパッド 302A を小さくし、モールド樹脂 32 と LSI 30 との接触面積を大きくすることで、加熱時にも密着力を確保できる。

#### 【0133】

さらに、外枠部 302B の内側に、支持梁 302C 及び発振子搭載梁 302D を十字形状（格子状）に配置し、発振子 28 を発振子搭載梁 302D に対して垂直に交差させて搭載しているので、支持梁 302C と発振子 28 の外部電極 34 とが接触して短絡するのを抑制できる。なお、ダイパッド 302A を支持する支持梁 302C を除去し、片持ちとして、発振子搭載梁 302D のみで外枠部 302B とダイパッド 302A とを連結してもよい。

10

#### 【0134】

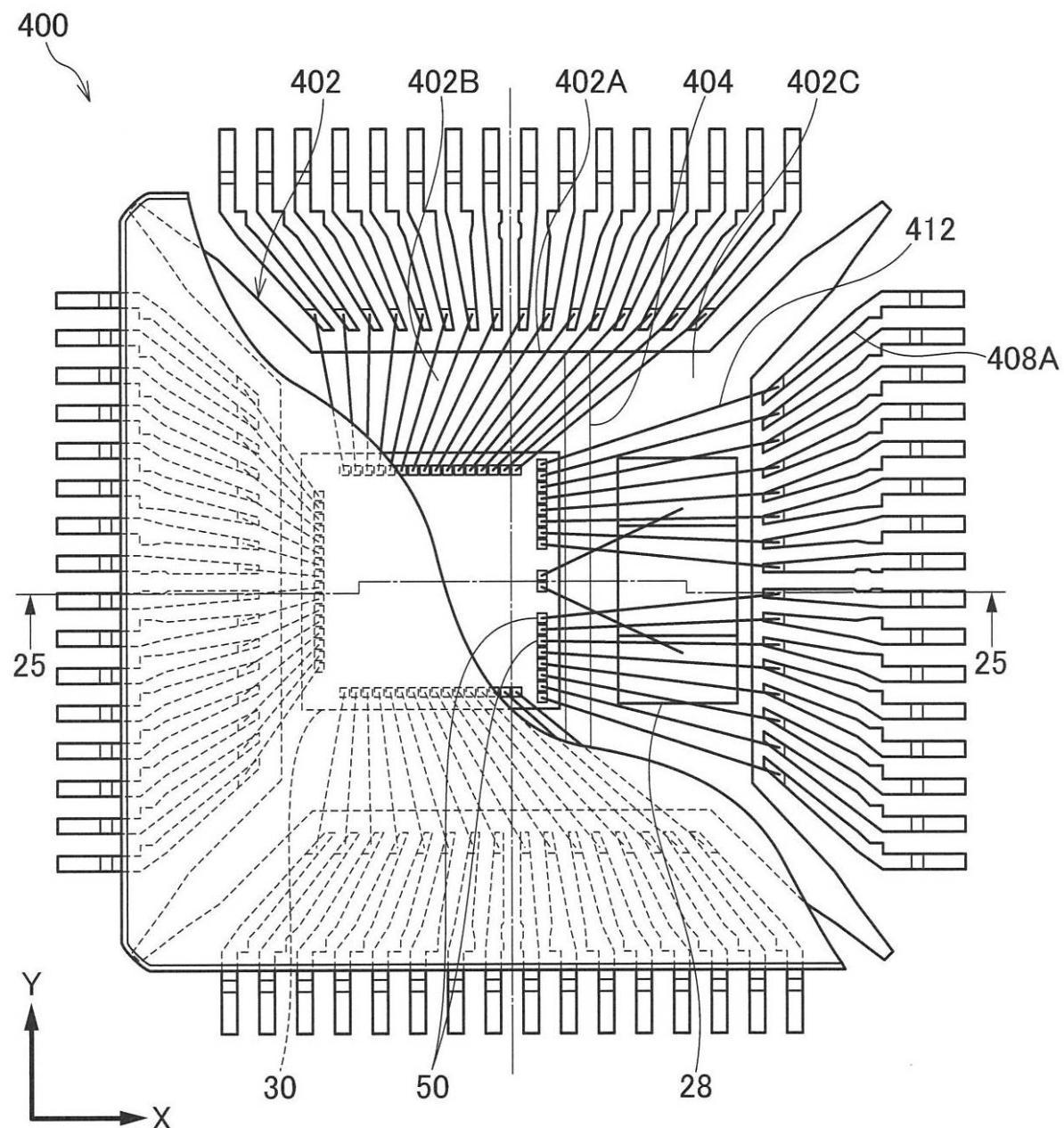

（第5実施形態）

#### 【0135】

次に、本発明の第5実施形態に係る半導体装置 400 について説明する。なお、第1実施形態と同一の構成については、同一の符号を付し、説明を省略する。図24、及び図25に示すように、本実施形態に係るリードフレーム 402 の中央部に位置するダイパッド 402A には、段差部 404 が設けられている。段差部 404 は、ダイパッド 402A の上下方向に延びてあり、図14に示すように、左から右へ向かって上方に傾斜している。このため、ダイパッド 402A は、段差部 404 を境にして、下方に位置する第1搭載面 402B と、上方に位置する第2搭載面 402C とに分けられている。

20

#### 【0136】

第1搭載面 402B、及び第2搭載面 402C は、リードフレーム 402 の裏面に連続して設けられており、インナーリード 408A と平行に形成されている。また、第1搭載面 402B には、接着剤を介して LSI 30 が搭載されており、LSI 30 の下面に設けられた電極パッド 50 とインナーリード 408A とがボンディングワイヤ 412 により電気的に接続されている。

20

#### 【0137】

第2搭載面 402C には、接着剤を介して発振子 28 が搭載されている。ここで、第2搭載面 402C は、半導体チップ 30 と発振子 28 との厚みの差分だけ第1搭載面 402B より上方に位置しており、LSI 30 の下面と発振子 28 の下面とが同じ高さとなっている。

30

#### 【0138】

図25に示すように、電極パッド 50 とインナーリード 408A とを接続しているボンディングワイヤ 412（第1のボンディングワイヤ）は、発振子用電極パッド 54 と外部電極 34 とを接続しているボンディングワイヤ 412（第2のボンディングワイヤ）を跨ぐようにして形成されている。すなわち、ボンディングワイヤ 412 の短絡を防止するために、発振子用電極パッド 54 と外部電極 34 とを接続しているボンディングワイヤ 412（第2のボンディングワイヤ）の頂点は、電極パッド 50 とインナーリード 408A とを接続しているボンディングワイヤ 412（第1のボンディングワイヤ）の頂点より低くなるように形成されている。

40

#### 【0139】

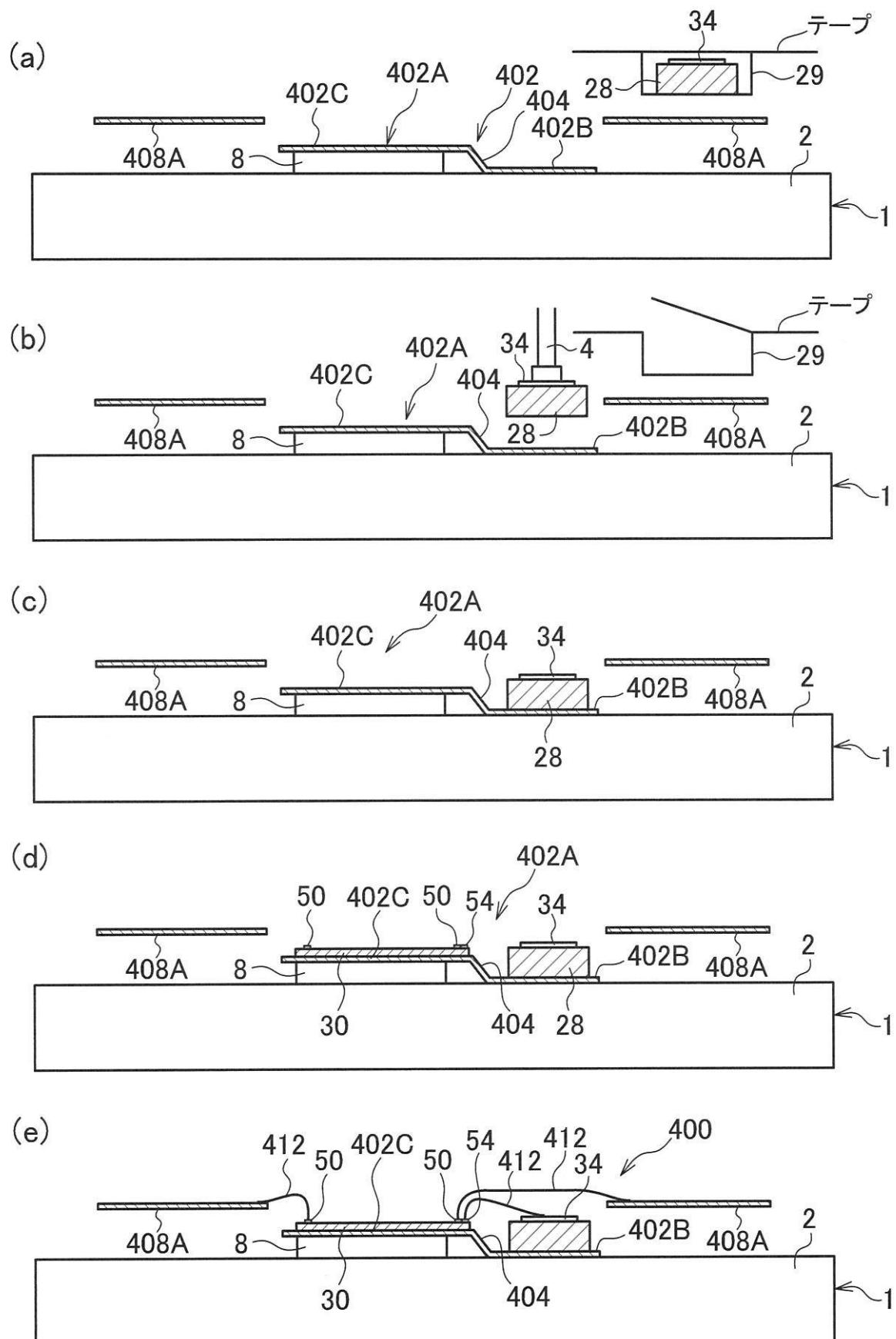

< 製造手順 >

#### 【0140】

以下、半導体装置 400 の製造手順について説明する。

#### 【0141】

先ず、図26（a）に示すように、リードフレーム 402 を、インナーリード 408A が上方に、ダイパッド 402A が下方に位置するように、ボンディング装置 1 の載置台 2 に載置する。なお、載置台 2 には、ダイパッド 402A における第2搭載面 402C が形成された部分を保持するための段差 8 が形成されている。この状態において、第1搭載面

50

402Bおよび第2搭載面402Cは何れも上方を向いている。また、発振子28は、外部電極34を上方に向けた状態でテープ上のパッケージ29に封入されて搬送されてくる。なお、リードフレーム402には、予めプレス加工等によって段差部404を形成しておく。

#### 【0142】

次に、図26(b)に示すように、パッケージ29を開封し、ピッカー4で発振子28を取り出し、図26(c)に示すように発振子28の外部電極34が上方を向くようにダイパッド402Aの第1搭載面402Bに発振子28を配置し、接着剤で第1搭載面402Bに固定する。なお、発振子28が、外部電極34を下方に向けた状態でパッケージ29に封入されているときは、ピッカー4として回転機構付きのものを用い、ピッcker4で発振子28を取り出した後、回転機構で発振子28を上下反転させ、外部電極34を上方に向けてからダイパッド26Aの第1の面に載置するのが好ましい。10

#### 【0143】

発振子28を第1搭載面402Bに固定したら、図26(d)に示すように、ダイパッド402Aの第2搭載面402Cに、LSI30を、電極パッド50と発振子用電極パッド54とが上方を向くように接着剤で固定する。なお、第2搭載面402Cは第1搭載面402Bと平面視で重ならないように形成されているから、LSI30も平面視で発振子28に重ならないように固定される。また、LSI30と発振子28とはダイパッド402Aにおける同じ側の面に固定される。20

#### 【0144】

LSI30を第2搭載面402Cに固定したら、図26(e)に示すように、LSI30の電極パッド50とリードフレーム402のインナーリード408Aとをボンディングワイヤ412で接続すると共に、LSI30の発振子用電極パッド54と発振子28の外部電極34とをボンディングワイヤ412で接続する。30

#### 【0145】

次に、半導体装置400をモールド樹脂32で封止する手順について説明する。

#### 【0146】

図27(a)に示すように、半導体装置400を図27(e)に示す状態から上下反転させた状態で金型5のキャビティ6内部に固定する。このとき、半導体装置400におけるLSI30が搭載された側が、発振子28が搭載された側よりも、金型5においてモールド樹脂32を注入する注入口7の近くに位置すると共に、ダイパッド402AにおけるLSI30が搭載された側の部分が、キャビティ6における高さ方向中心付近に位置するように、半導体装置400を配置することが好ましい。又、半導体装置400は、アウターリード408Bが金型5の外側に突出するように配置される。30

#### 【0147】

半導体装置400をキャビティ6内部に固定したら、図27(b)において矢印aで示すように、注入口7からキャビティ6内部にモールド樹脂32を注入する。

#### 【0148】

図27(c)に示すように、注入口7から注入されたモールド樹脂32は、リードフレーム402(ダイパッド402A)におけるLSI30が固定されている部分においては、リードフレーム402の上方と下方とに均等に流れ込む。40

#### 【0149】

しかしながら、リードフレーム402(ダイパッド402A)には、板厚方向に段差404が形成され、ダイパッド402Aにおける発振子28が固定されている部分は、段差404を境としてLSI30が固定されている部分に対して図27(a)～(d)における上方に屈曲している。

#### 【0150】

したがって、図27(d)において矢印cに示すように、ダイパッド402Aの発振子28が固定されている部分においては、ダイパッド402A下方の流速がダイパッド402A上方の流速よりも低くなる。これによってダイパッド402Aの前記部分においては50

、モールド樹脂は下方に優先的に充填されるから、リードフレーム402（ダイパッド402A）は注入されたモールド樹脂32によって下方から支持される。

【0151】

リードフレーム402の両側がモールド樹脂32で満たされたら、金型5を加熱してモールド樹脂32を硬化させる。

【0152】

本実施形態に係る半導体装置400では、発振子28とLSI30とがリードフレーム402の裏面に搭載されているので、発振子28とLSI30とを搭載する際に、リードフレーム402を反転させる必要がない。これにより、第1実施形態と比べて、半導体装置400の生産効率を向上できる。

10

【0153】

また、ボンディングワイヤ412が形成された面を上面とすると、第2搭載面402Cは、第1搭載面402Bより下方に位置しているので、発振子28を跨いでLSI30の電極パッド50とインナーリード408Aとをボンディングワイヤ412で接続する際に、発振子28がボンディングワイヤ412の妨げにならない。

20

【0154】

なお、本実施形態では、第1搭載面402Bと第2搭載面402Cとは、リードフレーム402の裏面に設けられていたが、これに限らず、リードフレーム402の表面に設けてもよい。この場合においても、ボンディングワイヤ412が形成された面を上面として、第2搭載面402Cを第1搭載面402Bより下方に形成することで、発振子28がボンディングワイヤ412の妨げとならないようにできる。

20

【0155】

また、本実施形態では、第2搭載面402Cは、第1搭載面402Bに対して、LSI30と発振子28との厚みの差分だけ上方に設けられていたが、これに限らず、ボンディングワイヤ412の妨げにならない程度に段差がついていればよく、発振子28の下面がLSI30の下面より下方へ突出していてもよい。

【0156】

（第6実施形態）

【0157】

次に、本発明の第6実施形態に係る半導体装置500について説明する。なお、第1実施形態と同一の構成については、同一の符号を付し、説明を省略する。図28、及び図29に示すように、本実施形態に係るリードフレーム502の中央部に位置するダイパッド502Aには、第5実施形態と同様に、段差部504が形成されている。図29に示すように、段差部504は、左から右へ向かって上方に傾斜しており、ダイパッド502Aは、段差部504を境にして、下方に位置する第1搭載面502Bと、上方に位置する第2搭載面502Cとに分けられている。

30

【0158】

第1搭載面502B、及び第2搭載面502Cは、共にリードフレーム502の裏面に連続して設けられており、インナーリード508Aと平行になっている。また、第1搭載面502Bには、接着剤を介してLSI30が搭載されており、第2搭載面502Cには、接着剤を介して発振子28が搭載されている。ここで、図28に示すように、LSI30は、リードフレーム502の中央部に位置しており、LSI30の右端部は、発振子28の一部を覆っている。すなわち、平面視にて投影したとき、発振子28とLSI30とが重なるように配置されている。

40

【0159】

ダイパッド502Aの第1搭載面502Bに発振子28を、第2搭載面502CにLSI30を固定し、LSI30のLSI30の発振子用電極パッド54と発振子28の外部電極34、およびLSI30の電極パッド50とリード38とをボンディングワイヤ512で接続して半導体装置500とする手順は、実施形態4の半導体装置400と同様に図26(a)～(e)に示すとおりである。また、半導体装置500をモールド樹脂32で

50

封止する手順も、同様に図 27 (a) ~ (d) に示すとおりである。

**【0160】**

本実施形態に係る半導体装置 500 では、LSI30 がリードフレーム 502 の中央部に搭載されているので、LSI30 の電極パッド 50 とインナーリード 508A との距離を LSI30 の各辺で一定にできる。これにより、ワイヤボンディングを容易に行うことができる。その他の作用については、第 5 実施形態と同様である。

**【0161】**

以上、本発明の第 1 ~ 第 6 実施形態について説明したが、本発明はこうした実施形態に限定されるものでなく、第 1 ~ 第 6 実施形態を組み合わせて用いてもよいし、本発明の要旨を逸脱しない範囲において、種々なる態様で実施し得ることは勿論である。例えば、発振子 28 として、発振回路 51 を内蔵した発振子を用いてもよい。また、図 2 の開口部 26C は、スリット状の孔でもよい。

10

**【符号の説明】**

**【0162】**

|     |                                          |    |

|-----|------------------------------------------|----|

| 10  | 積算電力量計（計測機器）                             |    |

| 22  | 電力量計測回路（計測手段）                            |    |

| 24  | 半導体装置                                    |    |

| 26  | リードフレーム（搭載基材）                            |    |

| 28  | 発振子（電子部品）                                |    |

| 30  | LSI（半導体チップ）                              | 20 |

| 32  | モールド樹脂（封止部材）                             |    |

| 34  | 外部電極（電子部品の端子）                            |    |

| 44  | 振動片（発振素子）                                |    |

| 50  | 電極パッド（半導体チップの端子）                         |    |

| 51  | 発振回路                                     |    |

| 52  | ボンディングワイヤ（第 1 のボンディングワイヤ、第 2 のボンディングワイヤ） |    |

| 54  | 発振子用電極パッド（半導体チップの端子）                     |    |

| 200 | 半導体装置                                    |    |

| 202 | リードフレーム（搭載基材）                            |    |

| 300 | 半導体装置                                    | 30 |

| 302 | リードフレーム（搭載基材）                            |    |

| 400 | 半導体装置                                    |    |

| 402 | リードフレーム（搭載基材）                            |    |

| 412 | ボンディングワイヤ（第 1 のボンディングワイヤ、第 2 のボンディングワイヤ） |    |

| 500 | 半導体装置                                    |    |

| 502 | リードフレーム（搭載基材）                            |    |

| 512 | ボンディングワイヤ（第 1 のボンディングワイヤ、第 2 のボンディングワイヤ） |    |

【図1】

【図4】

【図6】

【図7】

【図 9】

【図 10】

【図 11】

【図 13】

【図 12】

【図14】

【図15】

【図16】

【図17】

【図 2 3】

【図 3 2】

【図 2 5】

【図2】

【図3】

【図5】

【図8】

【図18】

【図19】

【図20】

【図 2 1】

【図22】

【図24】

【図26】

【図27】

(a)

(b)

(c)

(d)

【図28】

【図 29】

【図 30】

## 【図 3 1】

## 【手続補正書】

【提出日】平成25年5月9日(2013.5.9)

## 【手続補正1】

【補正対象書類名】特許請求の範囲

【補正対象項目名】全文

【補正方法】変更

## 【補正の内容】

【特許請求の範囲】

## 【請求項1】

発振素子を含み、一方の面に複数の端子を有する電子部品と、

前記電子部品と電気的に接続されると共に、一方の面に複数の端子を有する半導体チップと、

前記電子部品の端子と前記半導体チップの端子とが同一の方向を向くように夫々が搭載される搭載基材と、

前記半導体チップの前記端子と前記搭載基材とを接続する第1のボンディングワイヤと、

前記電子部品の前記端子と前記半導体チップの前記端子とを接続する第2のボンディングワイヤと、

前記電子部品、前記半導体チップ、前記搭載基材、前記第1のボンディングワイヤ、及び前記第2のボンディングワイヤと、を封止する封止部材と、

を備え、

前記第1のボンディングワイヤは、前記第2のボンディングワイヤを跨いでいる半導体装置。

## 【請求項2】

前記第1のボンディングワイヤは、前記第2のボンディングワイヤの頂点を避けた位置で跨いでいる請求項1に記載の半導体装置。

## 【請求項3】

前記電子部品の前記端子の大きさは、前記半導体チップの前記端子よりも大きい請求項1又は2に記載の半導体装置。

## 【請求項4】

前記第2のボンディングワイヤは、前記電子部品の中心より前記半導体チップとは反対側へずれた位置に接続されている請求項1～3の何れか1項に記載の半導体装置。

## 【請求項5】

請求項1～4の何れか1項に記載の半導体装置と、

前記半導体装置から出力された信号に応じて積算量を計測する計測手段と、

を有する計測機器。

【手続補正2】

【補正対象書類名】明細書

【補正対象項目名】0006

【補正方法】変更

【補正の内容】

【0006】

請求項1に記載の半導体装置は、発振素子を含み、一方の面に複数の端子を有する電子部品と、前記電子部品と電気的に接続されると共に、一方の面に複数の端子を有する半導体チップと、前記電子部品の端子と前記半導体チップの端子とが同一の方向を向くように夫々が搭載される搭載基材と、前記半導体チップの前記端子と前記搭載基材とを接続する第1のボンディングワイヤと、前記電子部品の前記端子と前記半導体チップの前記端子とを接続する第2のボンディングワイヤと、前記電子部品、前記半導体チップ、前記搭載基材、前記第1のボンディングワイヤ、及び前記第2のボンディングワイヤと、を封止する封止部材と、を備え、前記第1のボンディングワイヤは、前記第2のボンディングワイヤを跨いでいる。

---

フロントページの続き

(72)発明者 吉田 裕一

宮崎県宮崎郡清武町大字木原 727 番地 ラピスセミコンダクタ宮崎株式会社内

(72)発明者 曽根 紀久

東京都八王子市東浅川町550 番地1 ラピスセミコンダクタ株式会社内

(72)発明者 山田 和也

東京都八王子市東浅川町550 番地1 ラピスセミコンダクタ株式会社内

(72)発明者 竹井 彰啓

東京都八王子市東浅川町550 番地1 ラピスセミコンダクタ株式会社内