Office de la Propriété

Intellectuelle

du Canada

Un organisme

d'Industrie Canada

Canadian

Intellectual Property

Office

An agency of

Industry Canada

CA 2318968 C 2004/07/20

(11)(21) 2 318 968

(12) BREVET CANADIEN

CANADIAN PATENT

(13) C

(86) Date de dépôt PCT/PCT Filing Date: 1999/02/19

(87) Date publication PCT/PCT Publication Date: 1999/09/02

(45) Date de délivrance/Issue Date: 2004/07/20

(85) Entrée phase nationale/National Entry: 2000/07/21

(86) N° demande PCT/PCT Application No.: US 1999/003625

(87) N° publication PCT/PCT Publication No.: 1999/044222

(30) Priorité/Priority: 1998/02/27 (09/031,887) US

(51) Cl.Int.<sup>6</sup>/Int.Cl.<sup>6</sup> H01L 21/68

(72) Inventeur/Inventor:

HENGST, RICHARD R., US

(73) Propriétaire/Owner:

SAINT-GOBAIN INDUSTRIAL CERAMICS, INC., US

(74) Agent: GOWLING LAFLEUR HENDERSON LLP

(54) Titre : MODELE DE CHASSIS VERTICAL ANTIDERAPANT A BRAS HORIZONTAUX ARRONDIS

(54) Title: SLIP FREE VERTICAL RACK DESIGN HAVING ROUNDED HORIZONTAL ARMS

(57) Abrégé/Abstract:

The invention relates to a vertical rack for semiconductor wafer processing having strictly horizontally disposed arms wherein each arm has a rounded tip and a smooth ( $R_a < 1 \mu\text{m}$ ) upper surface.

PCT

WORLD INTELLECTUAL PROPERTY ORGANIZATION

International Bureau

## INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

|                                                                                                                                                                                    |  |    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (51) International Patent Classification <sup>6</sup> :<br><br>H01L 21/00                                                                                                          |  | A1 | (11) International Publication Number: <b>WO 99/44222</b><br><br>(43) International Publication Date: 2 September 1999 (02.09.99)                                                                                                                                                                                                                                                                                                                                   |

| (21) International Application Number: PCT/US99/03625<br><br>(22) International Filing Date: 19 February 1999 (19.02.99)                                                           |  |    | (81) Designated States: AL, AM, AT, AU, AZ, BA, BB, BG, BR, BY, CA, CH, CN, CU, CZ, DE, DK, EE, ES, FI, GB, GH, GM, HR, HU, ID, IL, IN, IS, JP, KE, KG, KP, KR, KZ, LC, LK, LR, LS, LT, LU, LV, MD, MG, MK, MN, MW, MX, NO, NZ, PL, PT, RO, RU, SD, SE, SG, SI, SK, SL, TJ, TM, TR, TT, UA, UG, US, UZ, VN, YU, ZW, Eurasian patent (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European patent (AT, BE, CH, CY, DE, DK, ES, FI, FR, GB, GR, IE, IT, LU, MC, NL, PT, SE). |

| (30) Priority Data:<br>09/031,887 27 February 1998 (27.02.98) US                                                                                                                   |  |    | Published<br>With international search report.<br>Before the expiration of the time limit for amending the claims and to be republished in the event of the receipt of amendments.                                                                                                                                                                                                                                                                                  |

| (71) Applicant (for all designated States except US):<br>SAINT-GOBAIN INDUSTRIAL CERAMICS, INC.<br>[US/US]; 1 New Bond Street, Box Number 15138,<br>Worcester, MA 01615-0138 (US). |  |    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| (72) Inventor; and<br>(75) Inventor/Applicant (for US only): HENGST, Richard, R.<br>[US/US]; 522 Barre Road, Oakham, MA 01068 (US).                                                |  |    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| (74) Agents: DI MAURO, Thomas, M. et al.; Saint-Gobain Corporation, 1 New Bond Street, Box Number 15138, Worcester, MA 01615-0138 (US).                                            |  |    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

(54) Title: SLIP FREE VERTICAL RACK DESIGN HAVING ROUNDED HORIZONTAL ARMS

## (57) Abstract

The invention relates to a vertical rack for semiconductor wafer processing having strictly horizontally disposed arms wherein each arm has a rounded tip and a smooth ( $R_a < 1 \mu\text{m}$ ) upper surface.

WO 99/44222

## SLIP FREE VERTICAL RACK DESIGN HAVING ROUNDED HORIZONTAL ARMS

The manufacture of semiconductor devices such as integrated circuits typically requires heat treating silicon wafers in the presence of reactive gases. During this process, the temperatures and gas concentrations to which the devices are exposed must be carefully controlled, as the devices often include circuitry elements less than 1 um in size which are sensitive to minute variations in the processing environment.

The semiconductor manufacturing industry typically processes these wafers in either horizontal or vertical carriers. The horizontal carrier, typically called a "boat", has three or four horizontally disposed bars arranged in a semicircle design, with each bar having inwardly facing grooves set therein at regular intervals. Each set of grooves define a vertical space for carrying a vertically disposed wafer. The vertical carrier, typically called a "vertical rack", has three or four vertically disposed rods (or posts) arranged in a semicircle design, with each post having slots set therein at regular intervals to define a space for supporting a horizontally disposed wafer. To insure the geometrical precision required in this field, the three or four rods are fixed to a top plate and a bottom plate. The portions of the post between each slot, termed "teeth", are identically spaced in order to support wafers at regular intervals from and parallel to the bottom plate. The entire rack is then placed within a vertical furnace for processing the wafers.

Because a wafer processed on a vertical rack experiences less of a temperature gradient over its face (as compared to a wafer processed in a horizontal boat), semiconductor manufacturers are increasingly turning to vertical furnaces.

WO 99/44222

PCT/US99/03625

There is, however, a drawback to vertical furnacing. The wafers disposed on a conventional vertical rack are supported at their outside edge only. As such, the areas of the wafer resting on these teeth experience higher stress than the rest 5 of the wafer. When temperatures in the furnace exceed about 1000°C, these stresses often become significant and portions of the single crystal wafer move relative to each other along crystallographic plates in response to that stress. This 10 phenomenon, called "slip", effectively destroys the value of the semiconductor devices located in the area of the wafer where slip has occurred.

In response to the slip problem, the art has developed a host of vertical racks having extended, vertically-inclined teeth, whereby a horizontally-disposed wafer supported thereon 15 is supported only in a region near its center. See e.g., US Patent No. 5,492,229 ("Tanaka"), Figure 2b of WO 96/35228 ("Tomanovich") and Figures 5-7 of US Patent No. 5,586,880 ("Ohsawa"). These configurations provide what the art has termed "near-center support". Although the rack which 20 produces "near center support" has eliminated slip in many wafer processing applications, it is somewhat inefficient, as the portion of its arm which rises from the horizontal plane to produce the near-center support necessarily increases the vertical spacing period of the rack, that is, the wafer-to- 25 wafer distance. Tanaka, for example, specifically teaches that its riser vertically extend at least about 0.3 mm from the flat portion of the tooth. Accordingly, the near-center support style of vertical rack can typically accommodate only about 90% of the wafers typically accommodated by the 30 conventional vertical rack.

Figure 3(b) of Tomanovich discloses a vertical rack wherein the arms are strictly horizontal and do not rise. Although this rack has been found to eliminate slip in some

WO 99/44222

PCT/US99/03625

high temperature semiconductor wafer processing applications, it performs less well in more demanding applications.

EP 0807961 A1 discloses a vertical rack in which the horizontal arms have rounded edges. However, there is no recognition in Nakajima of the need to make the surface roughness of the horizontal portion as low as 1 um in order to prevent slip under extreme conditions. In fact, as Example 1 of Nakajima teaches that a surface roughness of 5-58 um is perfectly fine, Nakajima teaches away from providing a rack wherein the horizontal arms have a surface roughness of no more than 1 um.

Therefore, there is a need for a vertical rack which is as efficient as the conventional style rack and yet eliminates slip in more demanding wafer processing applications.

Applicant found that a horizontal arm having both a very smooth upper surface and a rounded edge were needed in order to prevent slip in extreme conditions. The understanding that both of these features are required is not at all recognized by the cited art.

The rack of the present invention comprises an arm which first extends strictly horizontally from the vertical rod and then slopes gently downward, and has a smooth upper surface. Preliminary experiments involving the rack of the present invention have shown that it has essentially eliminated slip in 200 mm silicon wafers in a 1200°C wafer processing application. By contrast, a similarly dimensioned vertical rack having strictly horizontal arms (i.e., Figure 3b of Tomanovich) produced slip in about 50% of the wafers in the same processing application.

Therefore, the rack of the present invention is more compact and efficient than the near-center support racks (as it has no riser) and is more effective at preventing slip than the strictly horizontal arm rack.

WO 99/44222

PCT/US99/03625

The exceptional performance of this rack is surprising in that its design would appear to encourage slip but in fact prevents slip. Specifically, the near center support racks seek to prevent slip by preventing too much sag in the inner 5 portions of the wafer. By providing a gently downsloping edge (or "rounded") portion, the rack of the present invention appears to promote sag in the inner portions of the wafer. However, this design has demonstrated effectiveness in preventing slip.

Without wishing to be tied to a theory, it is believed that the design of the present invention takes advantage of the monocrystalline nature of the silicon wafer. Specifically, the silicon wafer responds elastically in semiconductor wafer processing by slightly sagging as it is 10 exposed to high temperatures and then regaining its initial flatness as it cools. It appears that only when the sagging wafer is also confronted with a region of stress concentration (i.e., its sag is interrupted by a sharp supporting edge) does it produce slip.

Because the edge of the support arm of the present invention is rounded, the slightly sagging wafer is supported about an increased surface area whose pitch essentially eliminates (or substantially reduces) stress concentration. It is believed that both the increased surface area (which provides more 15 support to the sagging wafer) and the rounded nature of the edge (which prevents stress concentration) each have a role in the successful application of this rack.

Although Figures 5-6 of Ohsawa disclose a rack whose arms have a downward sloping edge, the accompanying text makes it 20 clear this rack provides only near center support. That is, the text teaches that construction of the arm proceeds by first making a transverse hole through the rod and then making a horizontal platform which connects to the hole, but does so above the bottom of the hole to produce a riser. This riser

WO 99/44222

PCT/US99/03625

makes the rack inefficient for the reasons explained above. Ohsawa does not teach or suggest eliminating the hole-making first step to eliminate its riser.

Therefore, in accordance with the present invention, 5 there is provided a vertical rack made of a ceramic having an iron concentration of no more than about 50 ppm and comprising:

10 a) a vertical support means comprising a generally horizontal base and an vertical portion extending vertically therefrom,

b) a plurality of vertically spaced, horizontal support means horizontally extending from the vertical portion, wherein at least one horizontal support means comprises:

15 i) a horizontal upper surface portion which extends continuously horizontally from the vertical portion and has a surface roughness  $R_a$  of no more than 1 micron ( $\mu_m$ ), and

ii) a rounded upper surface portion sloping downward from the horizontal upper surface portion.

20 Preferably, the vertical portion of the vertical rack further comprises an arcuate horizontal cross-section defining a maximum radius  $R_{max}$  having a centerpoint, the plurality of vertically spaced, horizontal support means horizontally extend from the vertical portion substantially towards the 25 centerpoint, the horizontal upper surface portion extends continuously horizontally from the vertical portion towards the centerpoint for a distance of at least 20% of  $R_{max}$ , and the rounded upper surface portion slopes downward from the horizontal upper surface portion towards the centerpoint.

30 Also in accordance with the present invention, there is provided a combination comprising:

a) the above rack, and

WO 99/44222

PCT/US99/03625

b) a plurality of wafers having a wafer radius of no more than  $R_{max}$ ,

wherein each wafer is horizontally supported by one of the plurality of horizontal support means.

5

Also in accordance with the present invention, there is provided a process for treating semiconductor wafers, comprising the steps of:

10 a) providing the above combination wherein each wafer has an  $R_{max}$  of at least 200 mm, and

b) raising the temperature of semiconductor wafers to at least 1000°C for at least 15 minutes.

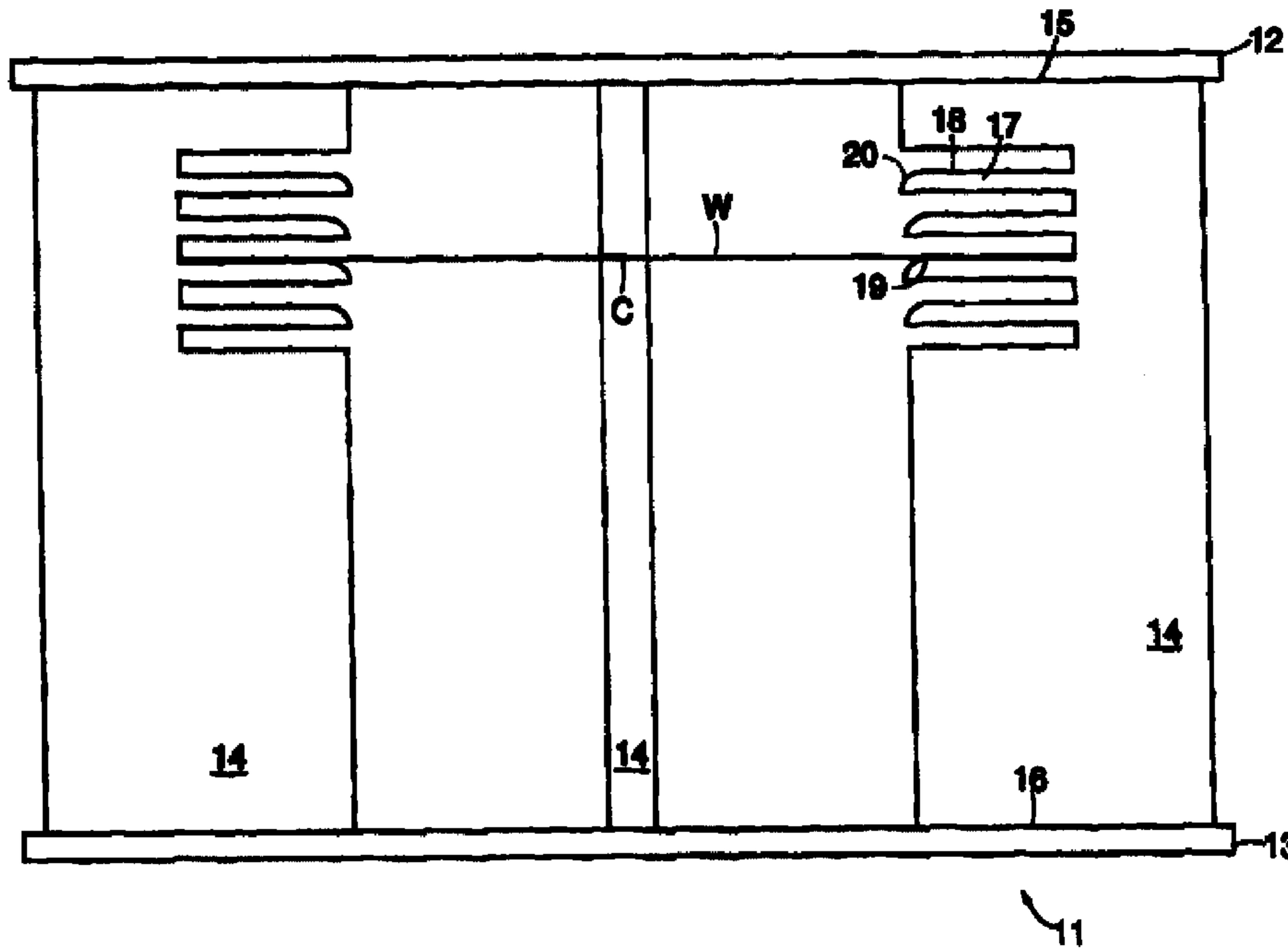

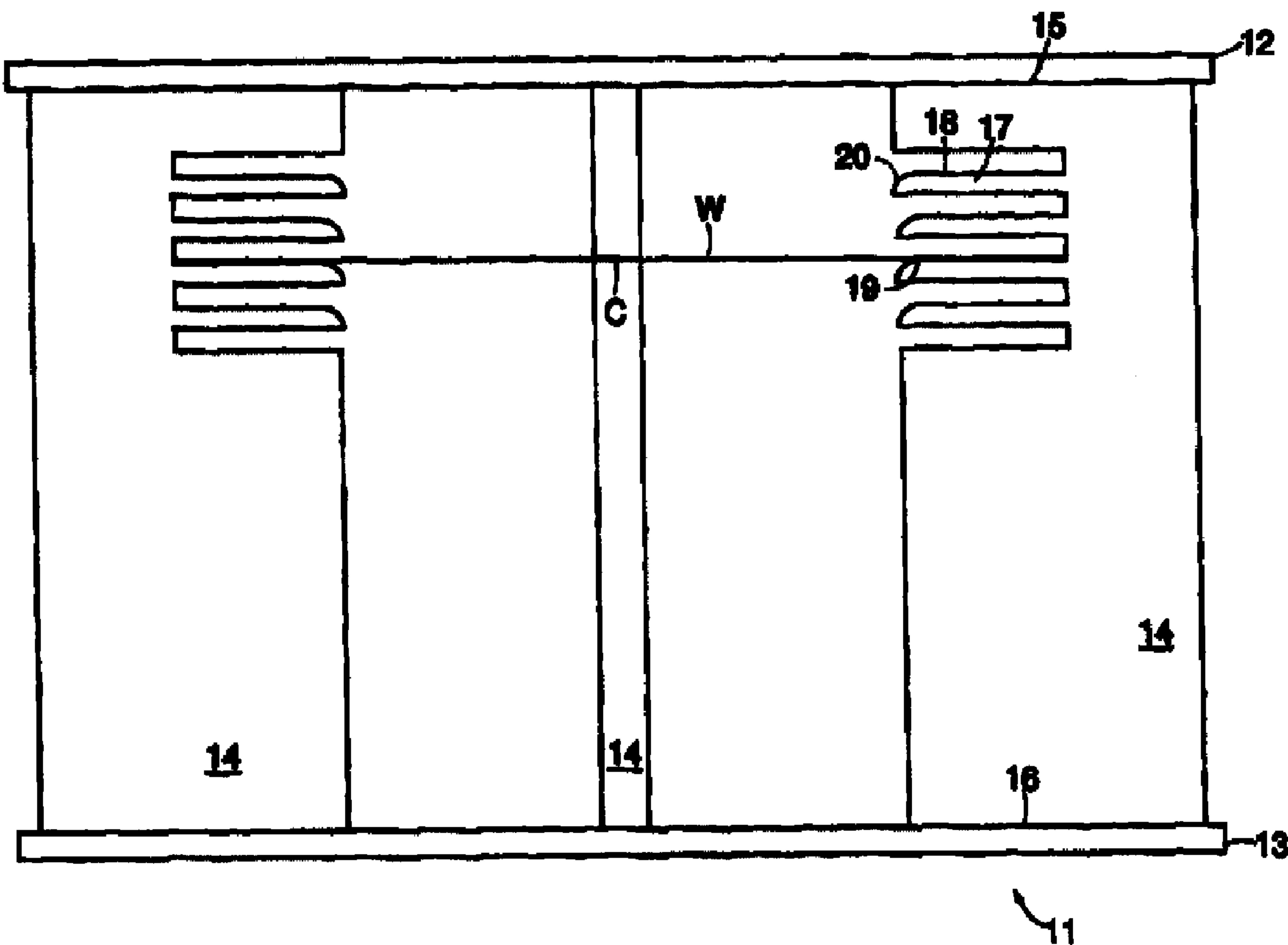

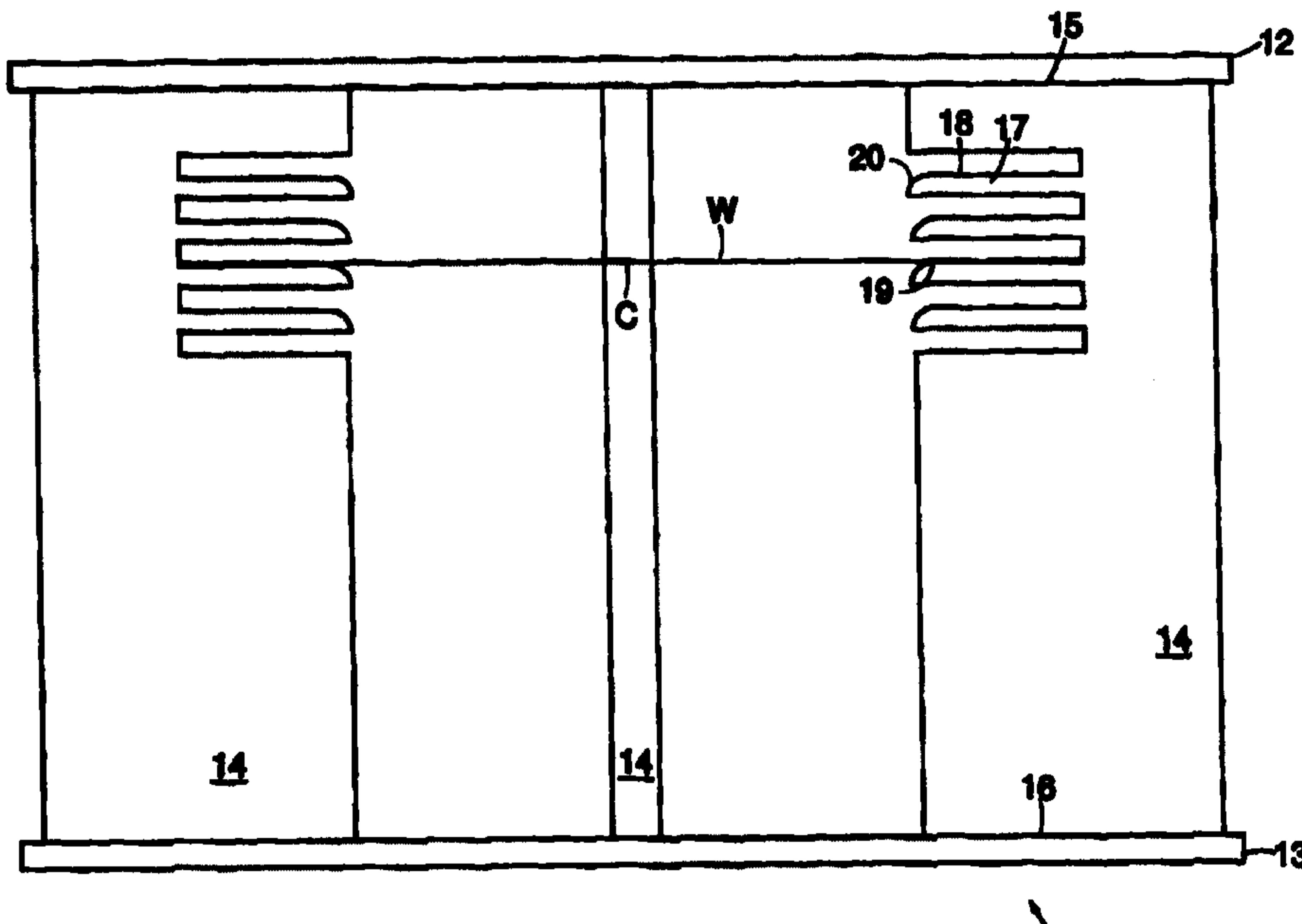

Figure 1 is a side view of the vertical rack of the present invention supporting a horizontally disposed wafer.

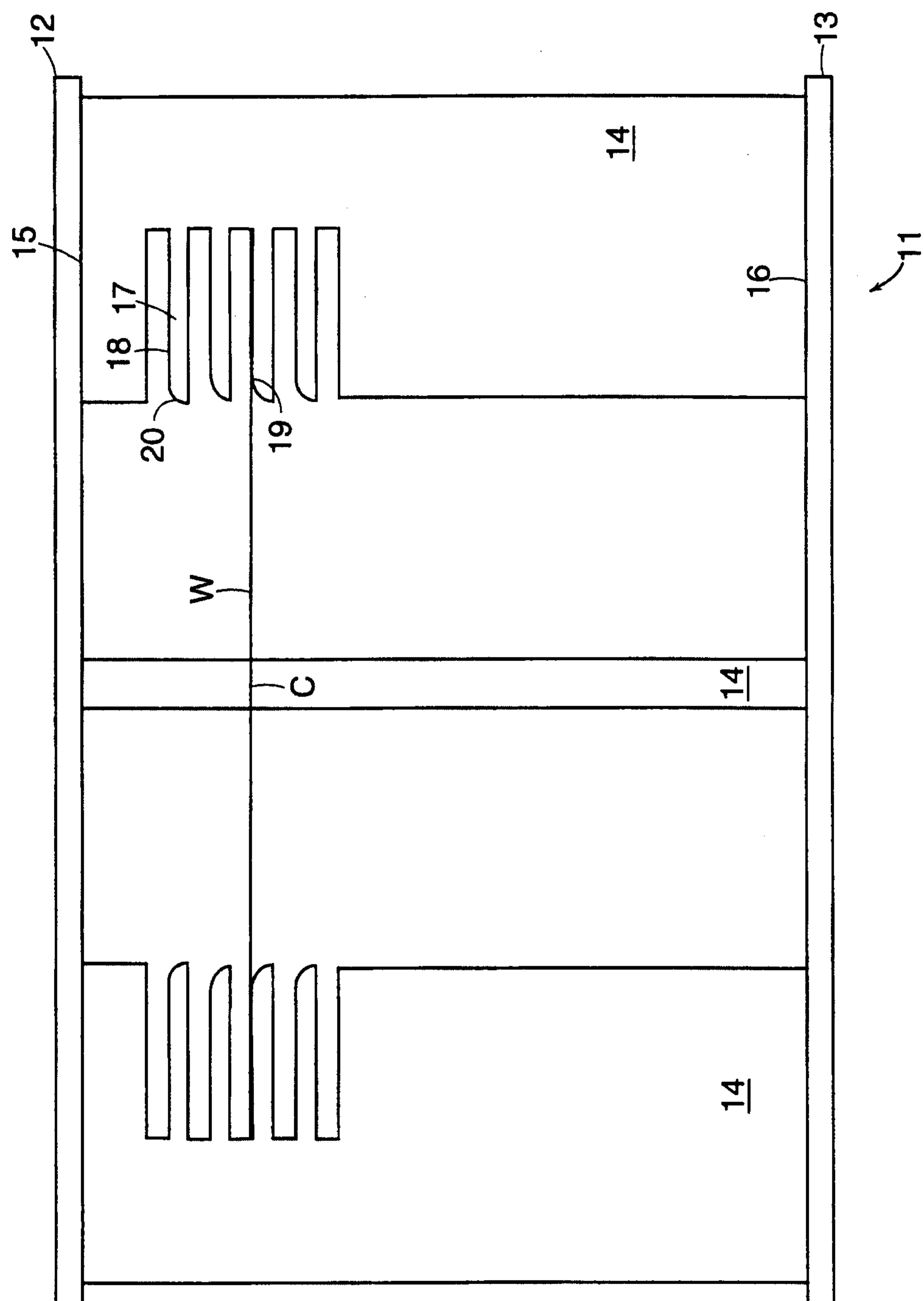

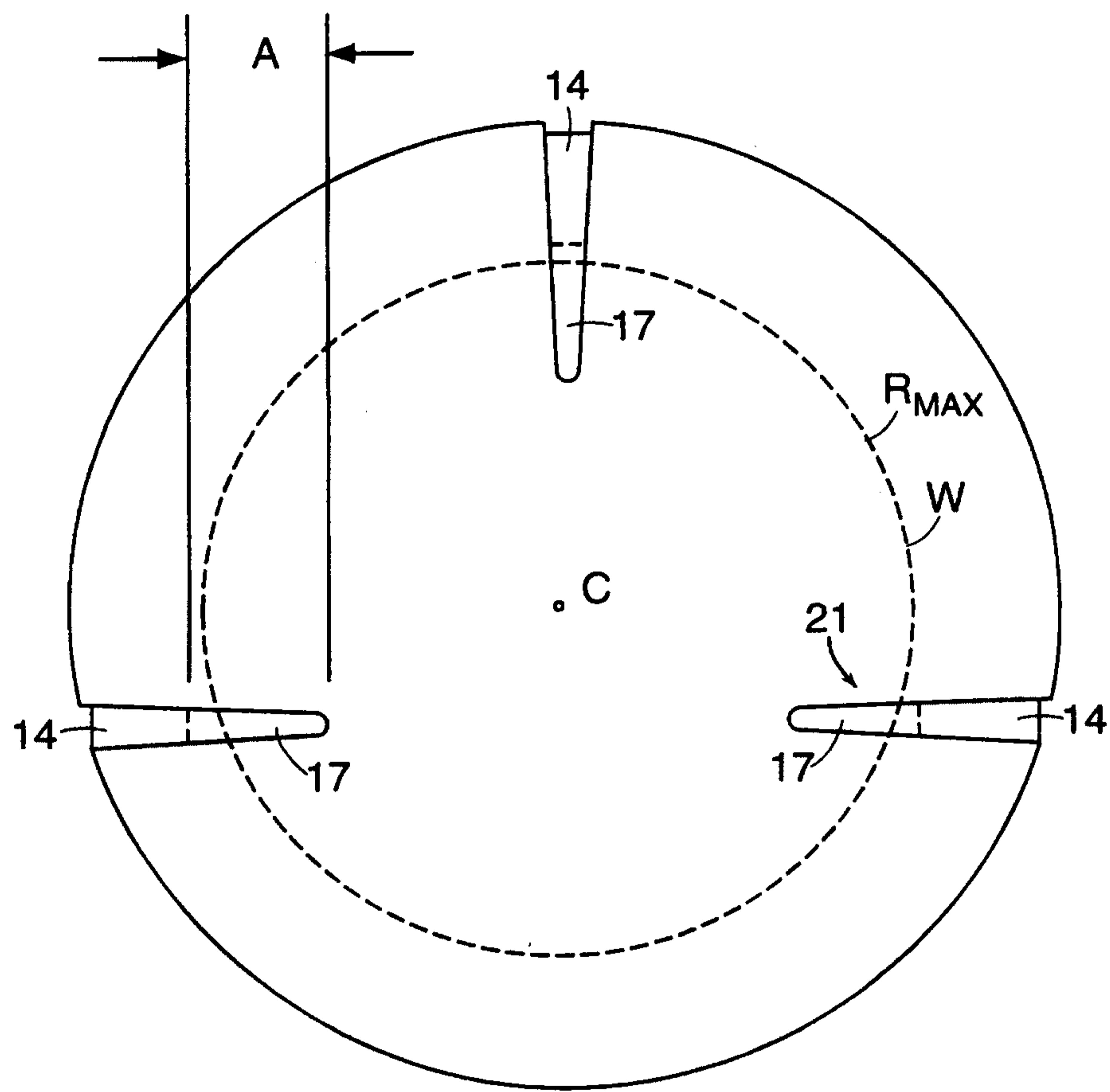

15 Figure 2 is a top view the preferred vertical rack/wafer combination of Figure 1.

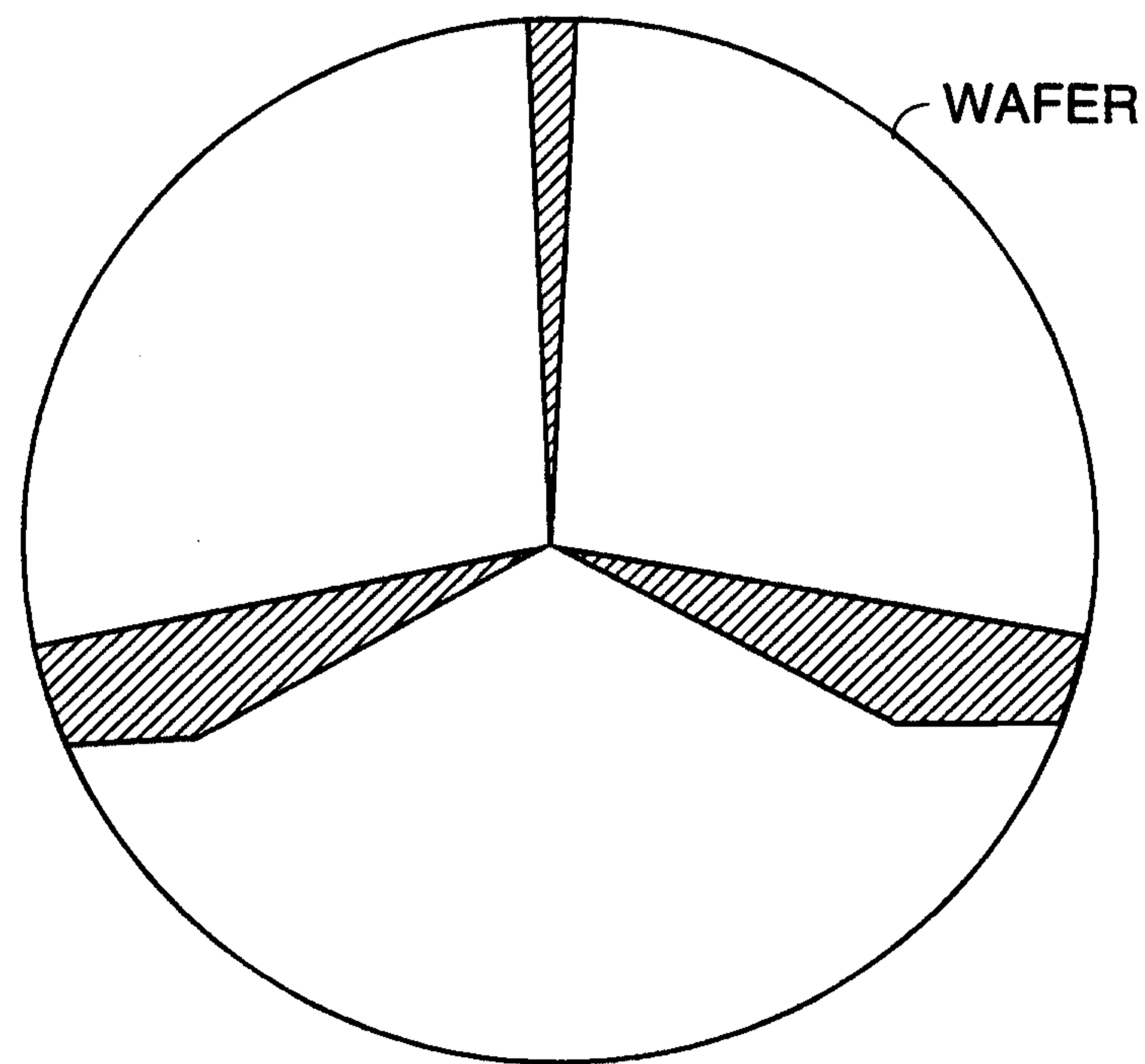

Figure 3 presents the areas of shadow produced by the preferred vertical rack of the present invention, as described by Figure 2.

20 Referring now to Figure 1, there is provided a preferred vertical rack 11/ wafer W combination, the vertical rack comprising:

25 a) a top plate 12,

b) a bottom plate 13, and

c) a plurality of vertical rods 14, the upper end 15 of each rod being fixed about the periphery of the top plate 12 and the lower end 16 of each rod being fixed about the periphery of the bottom plate 13, each of the vertical rods having a plurality of horizontal arms 17 spaced equidistantly from the bottom plate 13 to define a plurality of support levels for horizontally supporting the wafers W, each wafer having a centerpoint C,

30 wherein each arm comprises:

WO 99/44222

PCT/US99/03625

a) a horizontal upper surface portion 18 which extends continuously horizontally from the rod and continuously contacts the wafer W from the wafer edge such that the innermost contact 19 between the arm and the wafer is in the region between 20% and 80% of the wafer radius, measured from the wafer radius, and

5 b) a rounded upper surface portion 20 sloping downward from the horizontal upper surface portion 18 towards the wafer centerpoint C.

10 Figure 2 shows how the rods 14 are oriented to form a horizontal cross-section defining a maximum radius  $R_{max}$  (as shown by the dotted line) having a centerpoint C. In this Figure, the dotted line would also correspond to the largest wafer which could be accommodated by the rack.

15 In one preferred embodiment, the innermost contact between at least one and preferably each of at least three of the arms and their supported wafer is in the region of between 33% and 66% of the wafer radius. Moreover, the total contact area between the arms of one support level and their supported 20 wafer is typically between about 1% and about 5% of the surface area of the wafer face which contacts the arms.

25 To minimize slip-inducing stress, the surfaces of the arms upon which the wafers are supported (i.e., both the horizontal portion of the arm and its down sloping edge) have a surface roughness  $R_a$  of no more than 1  $\mu m$ , as defined by Section 3.9.1 of ANSI/ASME National Standard B46.1-1985. If the smoothness of the horizontal portion is about 2  $\mu m$ , then when the wafer expands during heat up, the peak portions of the arms will prevent the smooth expansion of the wafer and 30 this phenomenon will cause slip.

As the frequency of slip generally increases as the industry moves to larger diameter wafers, the advantages of using the rack of the present invention are more clearly demonstrated in applications having those larger diameter

WO 99/44222

PCT/US99/03625

wafers. Accordingly, the rack of the present invention is more advantageously used when processing wafers having a diameter of at least 200 mm (about 8 inch), more advantageously with wafers having a diameter of at least 250 mm (about 10 inch), and most advantageously with wafers having a diameter of at least 300 mm (about 12 inch). Accordingly, vertical racks of the present invention whose vertical rods define a wafer supporting diameter of at least 200 mm provide special advantage. More advantage is provided when the vertical rods define a wafer supporting diameter of at least 250 mm, and even greater advantage is provided when the vertical rods define a wafer supporting diameter of at least 300 mm.

Similarly, as the frequency of slip generally increases as the industry moves to higher processing temperatures, the advantages of using the rack of the present invention are more clearly demonstrated in applications having those higher processing temperatures. Accordingly, the rack of the present invention is more advantageously used when the temperature of the wafer becomes at least about 1000°C for at least 15 minutes. More advantage is provided when the temperature of the wafer becomes at least about 1100°C and even greater advantage is provided when the temperature of the wafer becomes at least about 1200°C for at least 30 minutes.

Although it is desirable that the arm extend from the rod at a perfectly horizontal angle, such perfection is rarely achieved commercially. Accordingly, the angle of deviation of the horizontal upper surface portion of the arm from horizontal (as defined by the base) is typically between about 0° and 0.2° degrees. By staying within this tolerance, the efficiency of the flat arm is retained.

The rounded edge of the arm not only provides an increased support area for the wafer during its critical sagging state, but also is free of stress concentrating

WO 99/44222

features. The curvature of the rounded edge is preferably substantially hemispherical and defines a radius  $R$  of between 3 mm and 50 mm, more preferably between 5 mm and 20 mm. Its surface roughness  $R_a$  is generally no more than about 2  $\mu\text{m}$ , preferably no more than 1  $\mu\text{m}$ . In one preferred embodiment, the rounded edge provides a downward sloping support face having a grade of about 1/10 (i.e., it slopes downward about 0.5 mm over the last 5 mm of the arm). Generally, the rounded edge provides a downward sloping support face having a grade of 5 between about 1/30 and 1/3.

10

In some embodiments, as shown in Figure 2, the lateral edges 21 of the arms are rounded.

The distance which the horizontal upper surface portion typically extends from its vertical rod (found by measuring 15 the shortest distance between the end of the projection and the rod and shown as "A" in Figure 2) is generally dependent upon the size of the wafer to be processed. For example, when the wafer to be processed has a 6 inch diameter, the horizontal upper surface portion typically terminates at least 20 mm from the edge of the rod, usually between about 20 mm and about 40 mm from the rod, and preferably about 27 mm from the edge of the rod. When the wafer to be processed has an 8 inch diameter, the horizontal upper surface portion typically terminates at least 22 mm from the edge of the rod, usually 25 between about 30 mm and about 50 mm from the rod, and preferably about 36 mm from the edge of the rod. When the wafer to be processed has an 12 inch diameter, the horizontal upper surface portion typically terminates at least 30 mm from the edge of the rod, usually between about 40 mm and about 70 30 mm from the rod, and preferably about 54 mm from the edge of the rod.

Typically, the horizontal upper surface portion of the arm supports the wafer from its periphery to a distance corresponding to between 20% and 80% of the supported wafer

WO 99/44222

radius, more typically between 33% and 66% of the wafer radius.

The vertical rack of the present invention can be made from any ceramic material having an iron purity which allows 5 its use in the high temperature production of vertical racks for semiconductor processing. Preferably, the material is recrystallized silicon carbide. More preferably, the recrystallized silicon carbide component has less than 10 ppm iron. The rack material may also be CVD coated with refractory 10 materials such as silicon carbide, silicon nitride or diamond. Preferably, the rack comprises CRYSTAR, a recrystallized silicon carbide available from the Norton Company of Worcester, MA. In preferred embodiments, the rack material comprises siliconized silicon carbide. In preferred 15 embodiments, the rack material has a 1200°C flexural strength (4 point) of at least 150 MPa.

It has been observed that the arms of vertical racks typically shield, or "shadow", radiant heat and/or reactive gases (which enter from the periphery of the vertical furnace) 20 from the portions of the wafer inside of and adjacent to the posts. Accordingly, significant variations in temperature and/or gas concentration between the "shadowed" portion of the wafer and the rest of the wafer are produced. These variations contribute to slip-inducing stress. Therefore, in 25 some embodiments, the arms are radially oriented such that they cast a shadow on no more than 30% of the wafer, preferably no more than 10% of the wafer. For the purposes of the present invention, the shadow percentage is calculated by determining the percentage of the wafer face to which 30 reactant gases and/or heat can directly radially proceed from the rack periphery in a path unobstructed by the arms. The shaded portion of Figure 3 represents the shadow produced by the rods of Figure 2 upon the wafer.

I claim:

1. A vertical rack made of a ceramic having an iron concentration of no more than about 50 ppm and comprising:

5 a) a vertical support means comprising a generally horizontal base and an vertical portion extending vertically therefrom,

b) a plurality of vertically spaced, horizontal support means horizontally extending from the vertical portion,

wherein at least one horizontal support means comprises:

10 i) a horizontal upper surface portion which extends continuously horizontally from the vertical portion and has a surface roughness  $R_a$  of no more than 1 micron ( $\mu\text{m}$ ), and

ii) a rounded upper surface portion sloping downward from the horizontal upper surface portion.

2. The vertical rack of claim 1 wherein the vertical portion further comprises an arcuate horizontal cross-section defining a maximum radius  $R_{\max}$  having a centerpoint, wherein the plurality of vertically spaced, horizontal support means horizontally extend from the vertical portion substantially towards the centerpoint, wherein the horizontal upper surface portion extends continuously horizontally from the vertical portion towards the centerpoint for a distance of at least 20% of  $R_{\max}$ , and wherein the rounded upper surface portion slopes downward from the horizontal upper surface portion towards the centerpoint.

3. The rack of claim 2 wherein the base is a plate, and the vertical support means comprises at least three vertical rods.

4. The rack of claim 3 wherein each vertically spaced, horizontal supports means comprises a plurality of arms, wherein one arm extends horizontally from a single corresponding rod.

5. The rack of claim 4 wherein the vertical support means comprises no more than three vertical rods.

6. The rack of claim 1 wherein each vertically spaced, horizontal supports means comprises a plurality of arms, wherein one arm extends continuously horizontally from each of the at least three vertical rods, and at least one arm has rounded lateral edges.

7. The rack of claim 1 wherein  $R_{max}$  is at least about 200 mm and the ceramic has a four point flexural strength of at least 150 MPa at 1200.degree. C.

8. The rack of claim 1 wherein the rounded upper surface portion defines a radius of between 3 mm and 50 mm.

9. A combination comprising:

a) a vertical rack made of a ceramic having an iron concentration of no more than about 50 ppm and comprising:

i) a vertical support means comprising a generally horizontal base and a vertical portion extending vertically therefrom and defining a maximum radius,  $R_{max}$ ,

ii) a plurality of vertically spaced, horizontal support means horizontally extending from the vertical portion,

wherein at least one horizontal support means comprises:

20 -) a horizontal upper surface portion which extends continuously horizontally from the vertical portion and has a surface roughness Ra of no more than 1  $\mu$ m, and

-) a rounded upper surface portion sloping downward from the horizontal upper surface portion,

b) a plurality of wafers having a wafer radius of slightly less than  $R_{max}$ , wherein each wafer is horizontally supported by one of the plurality of horizontal support means.

10. The combination of claim 9 wherein the vertical portion of the rack

5 further comprises an arcuate horizontal cross-section defining a maximum radius  $R_{max}$  having a centerpoint, wherein the plurality of vertically spaced, horizontal support means horizontally extend from the vertical portion substantially towards the centerpoint, wherein the horizontal upper surface portion extends continuously horizontally from the vertical portion towards the centerpoint for a distance of at least

10 20% of  $R_{max}$ , and wherein the rounded upper surface portion slopes downward from the horizontal upper surface portion towards the centerpoint, the horizontal support of each wafer defines a point of innermost contact between each horizontal support means and its supported wafer, and wherein the point of innermost contact is in the region of between 20% of 80% of the wafer radius.

15 11. The combination of claim 10 wherein each wafer has a radius of at least 200 mm.

12. The combination of claim 9 wherein the rack is made of a ceramic having a four point flexural strength of at least 150 MPa at 1200.degree. C.

20 13. A process for treating semiconductor wafers, comprising the steps of:

providing the combination comprising:

a) a vertical rack made of a ceramic having an iron concentration of no more than about 50 ppm and comprising:

25 i) a vertical support means comprising a generally horizontal base and a vertical portion extending vertically therefrom and defining a maximum radius  $R_{max}$ ,

ii) a plurality of vertically spaced, horizontal support means horizontally extending from the vertical portion, wherein at least one horizontal support means comprises:

- ) a horizontal upper surface portion which extends continuously horizontally from the vertical portion and has a surface roughness  $R_a$  of no more than  $1 \mu\text{m}$ , and

- ) a rounded upper surface portion sloping downward from the horizontal upper surface portion, and

b) a plurality of wafers having a wafer radius of slightly less than  $R_{\max}$ , wherein each wafer is horizontally supported by one of the plurality of horizontal support means wherein each wafer has an diameter of at least 200 mm, and raising the temperature of semiconductor wafers to at least 1000.degree. C. for at least 15 minutes.

14. The process of claim 13 wherein the temperature of the wafers is raised to at least 1200° C. for at least 30 minutes.

1/3

FIG. 1

2/3

FIG. 2

3/3

FIG. 3