(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4737592号

(P4737592)

(45) 発行日 平成23年8月3日(2011.8.3)

(24) 登録日 平成23年5月13日(2011.5.13)

(51) Int.Cl.

F 1

G06F 21/22 (2006.01)

G06F 9/38 (2006.01)G06F 9/06 660L

G06F 9/38 330A

G06F 9/38 330F

請求項の数 3 (全 13 頁)

(21) 出願番号 特願2005-38760 (P2005-38760)

(22) 出願日 平成17年2月16日 (2005.2.16)

(65) 公開番号 特開2006-227777 (P2006-227777A)

(43) 公開日 平成18年8月31日 (2006.8.31)

審査請求日 平成20年2月13日 (2008.2.13)

(73) 特許権者 302062931

ルネサスエレクトロニクス株式会社

神奈川県川崎市中原区下沼部 1753番地

(74) 代理人 100089071

弁理士 玉村 静世

(72) 発明者 平岡 徹

東京都小平市上水本町5丁目22番1号

株式会社日立超エル・エス・アイ・システムズ内

(72) 発明者 杉野 貴美広

東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内

(72) 発明者 萩原 今朝巳

東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内

最終頁に続く

(54) 【発明の名称】データ処理装置

## (57) 【特許請求の範囲】

## 【請求項 1】

命令コードを実行可能な中央処理装置と、

暗号化された命令コードを保持可能な命令キャッシュと、

上記中央処理装置と上記命令キャッシュとの間に配置され、上記暗号化された命令コードを、上記命令キャッシュを介して取り込み、それを復号化して上記中央処理装置に供給するための命令コード復号化論理と、を含むデータ処理装置であって、

上記命令コード復号化論理は、上記暗号化された命令コードをパイプライン処理によつて順次復号化し、

上記中央処理装置は、分岐先命令アドレスに対応して、分岐先命令コードの復号化後の命令を、上記分岐命令アドレスに関連付けて保持可能な信号変換バッファを含み、上記信号変換バッファ内に分岐先アドレスに対応する分岐先命令コードが存在する場合には、それを読み出して実行することを特徴とするデータ処理装置。

## 【請求項 2】

上記命令キャッシュを介して上記命令コード復号化論理に取り込まれる命令コードは、コプロセッサによって暗号化されたものを含む請求項1記載のデータ処理装置。

## 【請求項 3】

マイクロコンピュータとして一つの半導体基板に形成された請求項2記載のデータ処理装置。

## 【発明の詳細な説明】

10

20

**【技術分野】****【0001】**

本発明は、データ処理技術、特に顧客プログラムの保護強化を図るための技術に関する。

**【背景技術】****【0002】**

ソフトウェア及びデータの保護に関する技術として、中央処理装置に暗号化・復号部及び鍵格納部を附加して、記憶装置に格納されている暗号化された機械語命令及びデータを復号部によって復号して中央処理装置で実行させ、また中央処理装置から記憶装置にデータを格納する時は暗号化部によってデータを暗号化して格納するようにした技術が知られている（例えば特許文献1参照）。

**【0003】**

また、情報処理装置においてソフトウェア等の機密保護を図る際に、暗号強度と計算機のスループットがトレードオフにならないようにし、もって機密保護と高速処理とをともに実現できるようにすることを目的とした技術として、第2の記憶手段に格納されている暗号化された命令及びデータを復号して第1の記憶手段に格納してデータ処理手段で実行及び処理し、データ処理手段から第2の記憶手段にデータを出力する時は一旦第1の記憶手段に格納した後、暗号化手段で暗号化して第2の記憶手段に格納する技術が知られている（例えば特許文献2参照）。

**【0004】**

【特許文献1】特開平2-155034号公報（図1）

【特許文献2】特開平9-259044号公報（図1）

**【発明の開示】****【発明が解決しようとする課題】****【0005】**

従来はメモリ上の暗号化された命令コードを一旦復号化して命令キャッシュやユーザRAM（ランダム・アクセス・メモリ）に置いてから中央処理装置によって命令が処理されていた。この方式では、命令キャッシュやユーザRAMには復号化された命令コードが存在するため、デバッグツールや悪意を持ったプログラムにより顧客プログラムの機密保護が守られないことがあり得る。そこで、命令キャッシュやユーザRAMとCPUの間で命令コードの復号化を実施することが必要となる。それについて本願発明者が検討したところ、中央処理装置で命令が処理される直前に復号化すると、復号化に要する処理時間が大きいため、命令の処理性能が大幅に劣化してしまうことが見いだされた。

**【0006】**

本発明の目的は、顧客プログラムの保護の強化を図ることにある。

**【0007】**

本発明の別の目的は、命令の処理性能を劣化させることなく、顧客プログラムの保護の強化を図るための技術を提供することにある。

**【0008】**

本発明の前記並びにその他の目的と新規な特徴は本明細書の記述及び添付図面から明らかになるであろう。

**【課題を解決するための手段】****【0009】**

本願において開示される発明のうち代表的なものの概要を簡単に説明すれば下記の通りである。

**【0010】**

すなわち、命令コードを実行可能な中央処理装置と、暗号化された命令コードを保持可能な命令キャッシュと、上記中央処理装置と上記命令キャッシュとの間に配置され、上記暗号化された命令コードを、上記命令キャッシュを介して取り込み、それを復号化して上記中央処理装置に供給するための命令コード復号化論理と、を含んでデータ処理装置を構

10

20

30

40

50

成する。

【0011】

上記の手段によれば、命令キャッシュと中央処理装置との間に命令コード復号化論理が設けられているため、命令キャッシュの内容は暗号化された命令コードとされ、復号化された命令コードが命令キャッシュに格納されることがない。このことが、顧客プログラムの保護の強化を達成する。

【0012】

このとき、命令の逐次読み出し時や分岐命令発生時の命令実行処理においてオーバヘッドが生じないようにするには、上記命令コード復号化論理において、上記暗号化された命令コードをパイプライン処理によって復号化すると良い。

10

【0013】

また、分岐命令発生時の分岐先命令コードの復号化処理によるオーバヘッドを隠蔽化するには、分岐先命令アドレスに対応して、分岐先命令コードの復号化後の命令を、上記分岐命令アドレスに関連付けて保持可能な信号変換バッファを上記中央処理装置内に設けると良い。

【0014】

そして、命令コード復号化によるオーバヘッドと分岐命令発生時の分岐先命令読み出しに関するオーバヘッドとの双方の隠蔽化を可能とするには、命令フェッチアドレスをキーとして当該命令の分岐先アドレスを出力可能な動的分岐予測機構としての分岐先アドレスバッファを上記中央処理装置内に設け、上記分岐先アドレスバッファを介して投機的に命令フェッチを実行するようにすると良い。

20

【0015】

さらに、上記構成のデータ処理装置は、マイクロコンピュータとして一つの半導体基板に形成することができる。

【発明の効果】

【0016】

本願において開示される発明のうち代表的なものによって得られる効果を簡単に説明すれば下記の通りである。

【0017】

すなわち、顧客プログラムの保護の強化を図るための技術を提供することができる。

30

【発明を実施するための最良の形態】

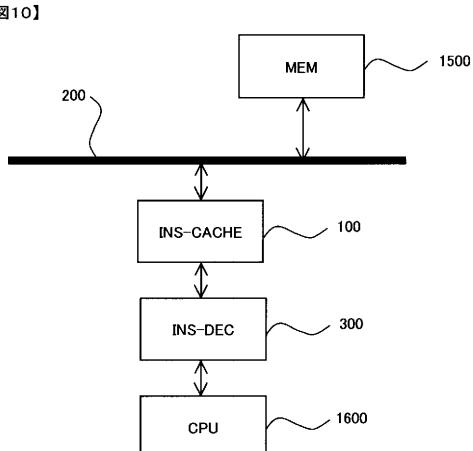

【0018】

図10には、本発明にかかるデータ処理装置の一例であるマイクロコンピュータが示される。

【0019】

図10に示されるデータ処理装置は、特に制限されないが、命令キャッシュ(INS-CACHE)100、命令コード復号化論理(INS-DEC)300、中央処理装置(CPU)1600、及びメモリ(MEM)1500などを含み、公知の半導体集積回路製造技術により、例えば単結晶シリコン基板などの一つの半導体基板に形成される。暗号化された命令コードは、上記命令キャッシュ100を介して上記命令コード復号化論理300に伝達される。上記命令コード復号化論理300は、暗号化された命令コードを上記CPU1600の直前で復号化してから上記CPU1600に供給する。上記CPU1600は、上記命令コード復号化論理300によって復号化された命令を実行する。例えば、上記暗号化された命令コードは、上記CPU1600や図示しないコプロセッサで暗号化し、上記MEM1500に格納されていてもよいし、上記MEM1500に予め格納されていてもよいし、上記データ処理装置の外部から暗号化された命令コードが伝達されるものであってもよい。

40

【0020】

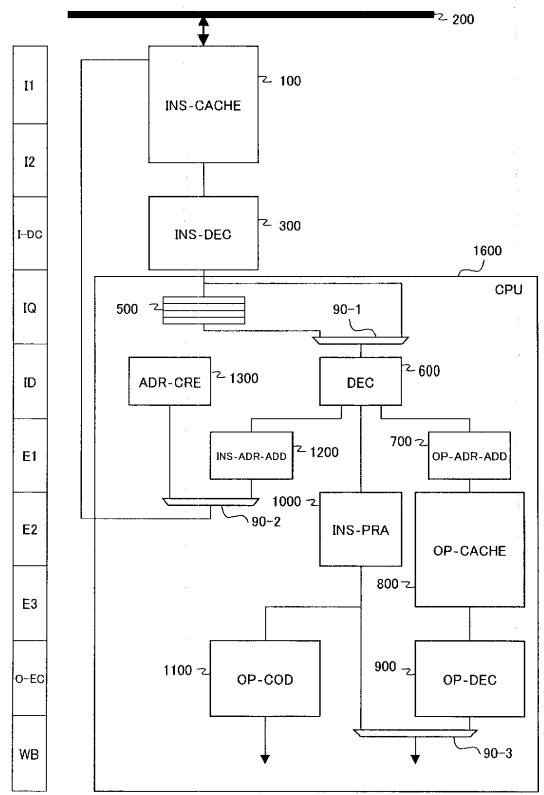

図1には、上記CPU1600の詳細な構成例が示される。

【0021】

50

図1に示されるようにCPU1600は、命令キュー500、命令デコーダ(DEC)600、オペランドアドレス加算器(OP-ADR-ADD)700、オペランドキャッシュ(OP-CACHE)800、オペランドデータ復号化論理(OP-DEC)900、命令実行部(INS-PRA)1000、オペランドデータ暗号化論理(OP-COD)1100、命令アドレス加算器(INS-ADR-ADD)1200、逐次命令フェッチアドレス生成論理(ADR-CRE)1300、及びセレクタ90-1, 90-2, 90-3を含んで成る。

#### 【0022】

上記命令キュー500は、上記命令コード復号化論理300から伝達された32バイトの命令を格納する。上記セレクタ90-1は、上記命令コード復号化論理300の出力と、上記命令キュー500の出力とを選択的に命令デコーダ600に伝達する。命令デコーダ600は、上記セレクタ90-1を介して伝達された命令の解読を行う。オペランドアドレス加算器700は命令のオペランドアドレスを生成する。オペランドキャッシュ800は、上記オペランドアドレスによって生成される。オペランドデータ復号化論理900は、上記オペランドキャッシュ800から出力された暗号化データを復号化する。命令実行部1000は、上記命令デコーダ600でデコードされた命令を実行する。この命令実行部1000での命令実行結果はセレクタ90-3及びオペランドデータ暗号化論理1100に伝達される。上記命令アドレス加算器1200は分岐命令の分岐先アドレスを計算する。上記逐次命令フェッチアドレス生成論理1300は逐次命令読み出し時のアドレスを計算する。セレクタ90-2は、命令をフェッチするため、上記命令アドレス加算器1200と上記逐次命令フェッチアドレス生成論理1300の出力とを選択的に上記命令キャッシュ100に伝達する。フェッチすべき命令が命令キャッシュ100内に存在する場合には、当該命令が命令コード復号化論理300に伝達される。しかし、フェッチすべき命令が命令キャッシュ100内に存在しない場合には、対応する命令がメモリ1500から読み出される。このとき、当該命令は命令キャッシュ100に記憶される。

#### 【0023】

図1において、I1, I2, I-DC~WB、及びO-DCなどは命令の処理におけるパイプライン処理との対応を示している。I1, I2は命令キャッシュ参照ステージを示し、I-DCは命令キャッシュ100から読み出された命令コードの復号化ステージを示し、IQは命令キューに滞留しているステージを示し、IDは命令の解読ステージを示し、E1はレジスタリード及び分岐先命令アドレス加算、オペランドアドレス加算ステージを示し、E2, E3は演算実行ステージ又はオペランドキャッシュ参照ステージを示し、O-ECはオペランドストアデータの暗号化ステージを示し、O-DCはオペランドキャッシュ800からのロードデータの復号化ステージを示し、WBは命令実行結果の書き込み(ライトバック)を示す。I-DCステージ、O-ECステージ、及びO-DCステージは通常数サイクル以上必要である。

#### 【0024】

一つの命令の命令長は2バイトで、一度の命令フェッチで命令キャッシュからフェッチする命令コードは4命令(8バイト)と仮定する。命令コードはメモリから読み出されるとバス200を通して命令キャッシュ100に格納される。逐次命令処理の場合、逐次命令フェッチアドレス生成論理1300で生成されたアドレスにより命令キャッシュ100を参照する。命令キャッシュ100から読み出された命令コードは命令コード復号化論理300に転送され復号化される。命令コード復号化論理300によって復号化された命令コードは、命令キュー500に格納され、また、命令デコーダ600に転送されて命令の解読が行われる。命令デコーダ600で解読された命令がロード型命令の場合、オペランドアドレス加算器700によりオペランドアドレスが生成され、そのアドレスに基づいてオペランドキャッシュ800が参照される。オペランドキャッシュ800から読み出されたオペランドは、オペランドデータ復号化論理900で復号化され、CPU1600内の図示されないレジスタに格納される。命令デコーダ600で解読された命令がストア型命令の場合、図示されないレジスタから読み出されたデータは命令実行部1000を経由し

10

20

30

40

50

、オペランドデータ暗号化論理 1100 で暗号化された後に、上記メモリ 1500 に書き込まれる。命令デコーダ 600 で解読された命令が演算型命令の場合、命令実行部 1000 で演算が行われ、その演算結果は、セレクタ 90 - 3 を介して、図示されないレジスタに書き込まれる。

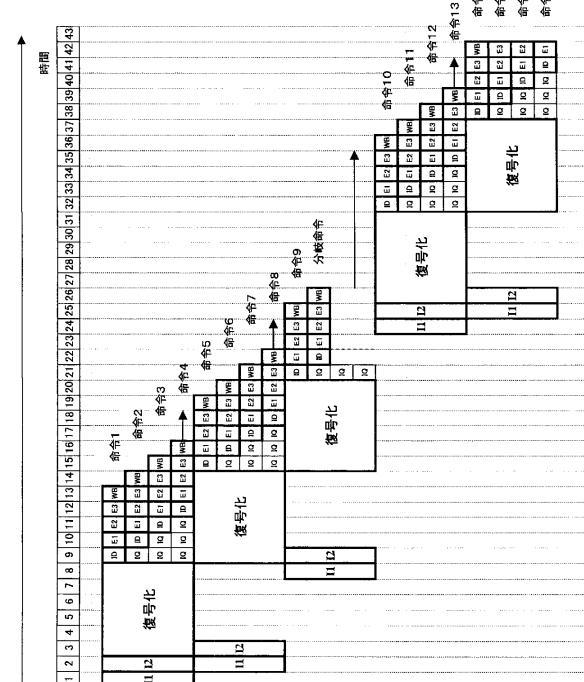

#### 【0025】

図 2 には、上記構成における命令処理タイミングが示される。

#### 【0026】

図 2において命令 1 から命令 4までの 8 バイトはサイクル 1 からサイクル 2 で命令キャッシュ 100 から読み出される。読み出された 8 バイトの命令コードはサイクル 3 からサイクル 8 の間で復号化される。復号化された命令コードは命令キューリスト 500 に転送するとともに、先頭の命令 1 は命令デコーダ 600 に転送される。命令 1 はサイクル 9 で命令の解読が行われる。説明の便宜上、命令 1 乃至命令 9 及び命令 10 乃至命令 17 は演算型命令と仮定する。以降命令 1 はパイプライン処理され、サイクル 13 で結果の書き込みが行われる。命令 2 は命令キューリスト 500 から命令デコーダ 600 に転送され、サイクル 10 で命令の解読が行われる。同様に命令 3 はサイクル 11 で命令の解読が行われ、命令 4 はサイクル 12 で命令の解読が行われる。次に命令 5 から命令 8 までの 8 バイトはサイクル 2 からサイクル 3 で命令キャッシュ 100 から読み出される。しかし、サイクル 4 では、命令コード復号化論理 300 が未だ命令 1 から命令 4 の復号化処理を行っているため、命令 5 から命令 8 の復号化処理の開始はサイクル 9 まで待たされる。命令 5 から命令 8 の復号化処理はサイクル 9 に開始され、サイクル 14 で完了する。復号化された命令コードは命令キューリスト 500 に転送するとともに、命令 5 は命令デコーダ 600 に転送される。従って命令 5 はサイクル 15 で命令の解読が行われ、サイクル 19 で結果の書き込みが行われる。このように命令 4 の終了（サイクル 16）と命令 5 の終了（サイクル 19）の間に 2 サイクルのオーバヘッド（処理の遅れ）が生じる。同様に命令 8 と命令 9 の間にも 2 サイクルのオーバヘッドが生じる。分岐命令はサイクル 22 で命令の解読が行われ、サイクル 23 で命令アドレス加算器 1200 により分岐先命令アドレスが求まる。その分岐先命令アドレスにより、サイクル 24 及びサイクル 25 で命令キャッシュ 100 を参照する。分岐先命令の命令コード（命令 10 から命令 13）の復号化処理はサイクル 26 に開始され、サイクル 31 で完了する。分岐先命令である命令 10 はサイクル 32 で命令の解読が行われ、サイクル 36 で結果の書き込みが行われる。

10

20

30

40

#### 【0027】

上記例によれば、以下の作用効果を得ることができる。

#### 【0028】

命令キャッシュ 100 と命令キューリスト 500 との間に命令コード復号化論理 300 が配置されたことにより、命令キャッシュ 100 の内容は暗号化された命令コードとなり、復号化された命令コードが命令キャッシュ 100 に格納されることが無いため、顧客プログラムの保護を強化することができる。すなわち、デバッグ機構により命令キャッシュ 100 の内容を表示したり、命令キャッシュ 100 の中の命令コードを他の記憶装置に転送しても、その命令コードを解読することはできないため、顧客プログラムの保護が実現できる。

#### 【0029】

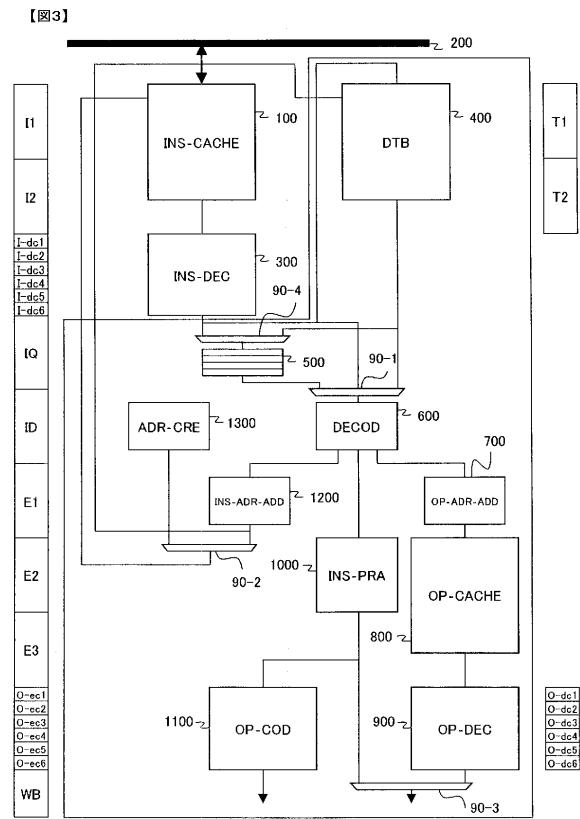

図 3 には、上記 C P U 1600 の別の構成例が示される。

#### 【0030】

図 3 に示される C P U 1600 が図 1 に示されるのと大きく相違するのは、命令コード復号化論理 300 において暗号化された命令コードの復号化がパイプライン処理によって行われる点、及び分岐先命令のアドレスに対応させてその分岐先の 8 命令分の暗号化された命令コードに対応する復号化後の命令コードを連想して保持するための復号変換バッファ（D T B）400 が設けられている点である。

#### 【0031】

図 3 において、I1, I2 は命令キャッシュ参照ステージを示し、I - d c 1 乃至 I -

50

d c 6 は命令キャッシュ 1 0 0 から読み出された命令コードの復号化ステージを示し、 I Q は命令キューに滞留しているステージを示し、 I D は命令の解読ステージを示し、 E 1 はレジスタリード及び分岐先命令アドレス加算、オペランドアドレス加算ステージを示し、 E 2 , E 3 は演算実行ステージまたはオペランドキャッシュ参照ステージを示し、 O - e c 1 乃至 O - e c 6 はオペランドストアデータの暗号化ステージを示し、 O - d c 1 乃至 O - d c 6 はオペランドキャッシュ 8 0 0 からのロードデータの復号化ステージを示し、 W B は命令実行結果の書き込み(ライトバック)を示す。 I - d c 1 ~ I - d c 6 ステージ O - e c 1 ~ O - e c 6 ステージ及び O - d c 1 ~ O - d c 6 ステージは通常数サイクル以上必要な復号化や暗号化の処理をパイプライン処理化したステージである。

## 【 0 0 3 2 】

10

命令キャッシュ 1 0 0 から読み出された命令コードは、セレクタ 9 0 - 4 を介して、命令コード復号化論理 3 0 0 に転送され復号化される。命令コード復号化論理 3 0 0 から出力される復号化された命令コードは命令キュー 5 0 0 に格納されるとともに、命令デコーダ 6 0 0 に転送されて命令の解読が行われる。また、分岐命令の分岐先の 8 命令については命令コード復号化論理 3 0 0 で復号化された後に、対応する分岐先命令アドレスと対にして信号変換バッファ 4 0 0 に格納される。命令デコーダ 6 0 0 で解読された命令がロード型命令の場合、オペランドアドレス加算器 7 0 0 によりオペランドアドレスが生成され、オペランドキャッシュ 8 0 0 が参照される。オペランドキャッシュ 8 0 0 から読み出されたオペランドはオペランドデータ復号化論理 9 0 0 で復号化されて C P U 1 6 0 0 内の図示されないレジスタに格納される。命令デコーダ 6 0 0 で解読された命令がストア型命令の場合、図示されないレジスタから読み出されたデータは命令実行部 1 0 0 0 を経由してオペランドデータ暗号化論理 1 1 0 0 で暗号化された後に、メモリ 1 5 0 0 に書き込まれる。命令デコーダ 6 0 0 で解読された命令が演算型命令の場合、命令実行部 1 0 0 0 で演算が行われ、その演算結果は、図示されないレジスタに書き込まれる。

## 【 0 0 3 3 】

20

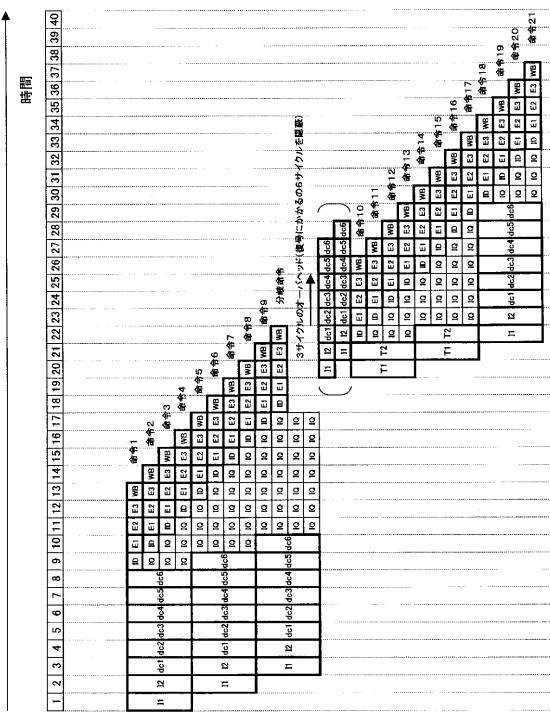

図 4 には、上記構成における命令処理タイミングが示される。

## 【 0 0 3 4 】

命令 1 から命令 4 までの 8 バイトはサイクル 1 からサイクル 2 で命令キャッシュ 1 0 0 から読み出される。読み出された 8 バイトの命令コードはサイクル 3 からサイクル 8 の間で復号化される。復号化された命令コードはセレクタ 9 0 - 4 7 を介して命令キュー 5 0 0 に転送される。尚、復号化された先頭の命令 1 は命令デコーダ 6 0 0 に転送される。命令 1 はサイクル 9 で命令の解読が行われる。説明の便宜上、命令 1 乃至命令 9 及び命令 1 0 乃至命令 2 1 は演算型命令と仮定する。以降命令 1 はパイプライン処理され、サイクル 1 3 で結果の書き込みが行われる。命令 2 は命令キュー 5 0 0 から命令デコーダ 6 0 0 に転送され、サイクル 1 0 で命令の解読が行われる。同様に命令 3 はサイクル 1 1 で命令の解読が行われ、命令 4 はサイクル 1 2 で命令の解読が行われる。次に命令 5 から命令 8 までの 8 バイトはサイクル 2 からサイクル 3 で命令キャッシュ 1 0 0 から読み出される。命令 5 から命令 8 の復号化処理はサイクル 4 に開始され、サイクル 9 で完了する。復号化された命令コードは命令キュー 5 0 0 に転送される。従って命令 5 はサイクル 1 3 で命令の解読が行われ、サイクル 1 7 で結果の書き込みが行われる。以降、命令 9 まで同様に処理される。分岐命令はサイクル 1 8 で命令の解読が行われ、サイクル 1 9 で命令アドレス加算器 1 2 0 0 により分岐先命令アドレスが求まる。その分岐先命令アドレスにより、サイクル 2 0 及びサイクル 2 1 で命令キャッシュ 1 0 0 を参照する。分岐先命令の命令コード(命令 1 0 から命令 1 3 )の復号化処理はサイクル 2 2 で開始され、サイクル 2 7 で完了する。一方、分岐先命令アドレスと「分岐先命令アドレス + 8 」のアドレスは信号変換バッファ 4 0 0 にも送られ、サイクル 2 0 で信号変換バッファ 4 0 0 内に当該分岐先アドレスに対応する復号化された分岐先命令コードが存在するか否か判定される。所望の分岐先命令コードが信号変換バッファ 4 0 0 に存在する場合、サイクル 2 1 で復号化された後の分岐先命令コードが信号変換バッファ 4 0 0 から読み出される。読み出された命令コードはセレクタ 9 0 - 4 を介して命令キュー 5 0 0 に転送される。先頭の命令 1 0 は命令デコ

30

40

50

ーダ 600 に転送される。また、サイクル 21 で信号変換バッファ 400 内に、「分岐先命令アドレス + 8」に対応する、復号化された分岐先命令コードが存在するか否か判定される。所望の命令コードが符号化変換バッファ 400 に存在する場合、サイクル 22 で復号化された後の分岐先命令コードが信号変換バッファ 400 から読み出される。読み出された命令コードは、セレクタ 90 - 4 を介して命令キューリスト 500 に転送される。分岐先命令である命令 10 はサイクル 22 で命令の解読が行われ、サイクル 26 で結果の書き込みが行われる。このように分岐命令と命令 10 の間には命令アドレス加算器 1200 で分岐先アドレスを計算して、信号変換バッファ 400 から分岐先命令コードを読み出すまでの 3 サイクルのオーバヘッドが生じる。尚、信号変換バッファ 400 に分岐先命令の命令コードが存在しない場合は、サイクル 27 で分岐先命令コードの復号化処理が完了するので、サイクル 28 で命令 10 の命令の解読を行うことができる。以降、命令 11 から命令 17 までは同様に命令が実行される。命令 10 から命令 13 までの命令コードはサイクル 21 に命令キャッシュ 100 から読み出され、命令 14 から命令 17 までの命令コードはサイクル 22 で命令キャッシュ 100 から読み出されるため、命令 18 から命令 21 までの命令コードはサイクル 23 で読み出される。読み出された命令コードはサイクル 24 から命令コード復号化処理され、サイクル 29 で復号化処理が完了する。復号化された命令コード（命令 18 から命令 21）は命令キューリスト 500 に転送されるとともに、先頭の命令 18 は命令デコーダ 600 に転送される。命令 18 はサイクル 30 で命令の解読が行われ、サイクル 34 で結果の書き込みが行われる。このような処理によれば、命令 10 から命令 21 の命令処理についてオーバヘッドが生じることはない。

10

20

#### 【0035】

上記の例によれば、命令キャッシュ 100 と命令キューリスト 500 の間に命令コードの復号化論理 300 を有することにより、命令キャッシュ 100 の内容は暗号化された命令コードとなり、復号化された命令コードが命令キャッシュ 100 に格納されることが無いため、顧客プログラムの保護を強化することができる。また、命令コード復号化論理 300 での復号化がパイプライン処理されることにより、逐次命令読み出し時のオーバヘッドを隠蔽化することができる。さらに、信号変換バッファ 400 を設けることにより、分岐先アドレスに対応して分岐先の命令コードの復号化後の命令を記憶するようになっているため、分岐命令発生時の復号化処理によるオーバヘッドを隠蔽化することが可能となる。

#### 【0036】

30

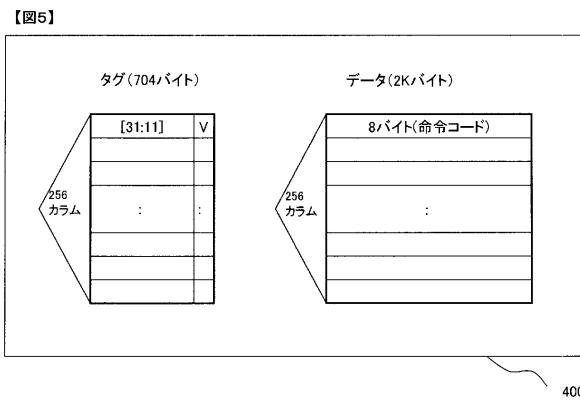

図 5 には、上記復号変換バッファ 400 の構成例が示される。

#### 【0037】

図 5 に示される復号変換バッファ 400 はタグ部とデータ部とを含む。特に制限されないが、ダイレクトマッピング方式が採用され、タグ部は 704 バイト構成とされ、データ部は 2K バイト構成とされる。尚、復号変換バッファ 400 は、2-way や 4-way のセットアソシティブ方式であっても良いし、フルアソシティブ方式であっても良い。

#### 【0038】

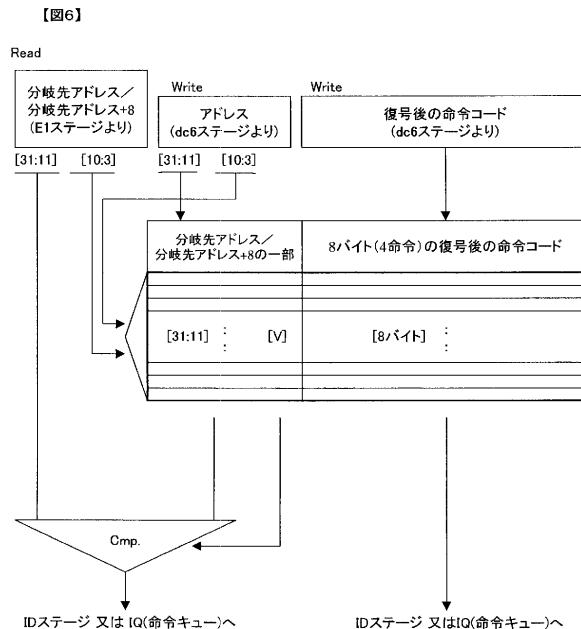

図 6 には、図 5 に示される復号変換バッファ 400 において参照（Read）及び書き込み（Write）についての動作が示される。

40

#### 【0039】

参照時は分岐先命令アドレスの [10 : 3] の 8 ビットにより 256 カラムの中からタグ及びデータを読み出す。読み出されたタグには、復号変換バッファに登録されている命令コードに対応する命令アドレスの [31 : 11] とその内容が有効であることを示すバリッドビット [V] が含まれる。コンパレータ（Comp.）では、分岐先アドレスの [31 : 11] と読み出されたタグの [31 : 11] との比較が行われる。バリッドビットが論理値 “1” で、かつ分岐先アドレスの [31 : 11] と読み出されたタグの [31 : 11] が一致した場合、復号変換バッファ 400 に復号後の命令コードが存在するため、復号変換バッファ 400 から読み出された命令コードが命令キューリスト 500 及び命令デコーダ 600 に転送される。復号変換バッファ 400 に復号後の命令コードが存在しない場合は

50

、命令コード復号化論理 300 で復号化された命令コードが命令キュー 500 及び命令デコーダ 600 に転送されるとともに、復号変換バッファ 400 にも転送されて復号変換バッファ 400 への書き込みが行われる。このとき、復号後の命令コードに対応する命令アドレスの [10 : 3] の 8 ビットにより 256 カラムの中の一つのカラムに書き込まれる。そしてタグには命令アドレスの [31 : 11] が書き込まれるとともに、バリッドビットに論理値 “1” が書き込まれる。また、復号後の命令コードも同じカラムに書き込まれる。

#### 【0040】

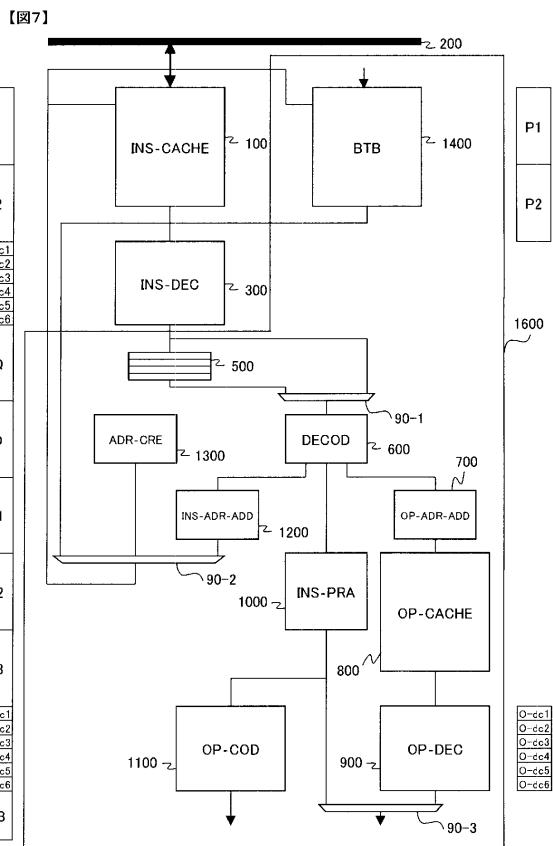

図 7 には、上記 C P U 1600 の別の構成例が示される。

#### 【0041】

図 7 に示されるのが、図 1 に示されるのと大きく相違するのは、暗号化された命令コードの復号化がパイプライン処理によって行われる点、さらには、動的分岐予測機構などによる投機的命令フェッチ方式を併用し、命令フェッチアドレスをキーとして当該命令フェッチする命令コードの中に以前に分岐成功した分岐命令が存在するときにその分岐命令の分岐先アドレスを出力可能な分岐先アドレスバッファ (B T B) 1400 を備える点である。そして上記分岐先アドレスバッファ 1400 が設けられたことに対応して、セレクタ 90 - 2 は、上記命令アドレス加算器 1200 の出力と、上記分岐先アドレスバッファ 1400 の出力信号と、上記逐次命令フェッチアドレス生成論理 1300 の出力とを選択的に上記命令キャッシュ 100 及び上記分岐先アドレスバッファ 1400 に伝達可能に構成される。

10

#### 【0042】

図 7において、I1, I2, I-dc1 などは命令の処理におけるパイプライン処理との対応を示している。I1, I2 は命令キャッシュ参照ステージを示し、I-dc1 乃至 I-dc6 は命令キャッシュ 100 から読み出された命令コードの復号化ステージを示し、IQ は命令キューに滞留しているステージを示し、ID は命令の解読ステージを示し、E1 はレジスタリード及び分岐先命令アドレス加算、オペランドアドレス加算ステージを示し、E2, E3 は演算実行ステージまたはオペランドキャッシュ参照ステージを示し、O-ec1 乃至 O-ec6 はオペランドストアデータの暗号化ステージを示し、O-dc1 乃至 O-dc6 はオペランドキャッシュ 800 からのロードデータの復号化ステージを示し、WB は命令実行結果の書き込み (ライトバック) を示す。I-dc1 ~ I-dc6 ステージ O-ec1 ~ O-ec6 ステージ 及び O-dc1 ~ O-dc6 ステージ は通常数サイクル以上必要な復号化や暗号化の処理をパイプライン処理化したステージである。

20

#### 【0043】

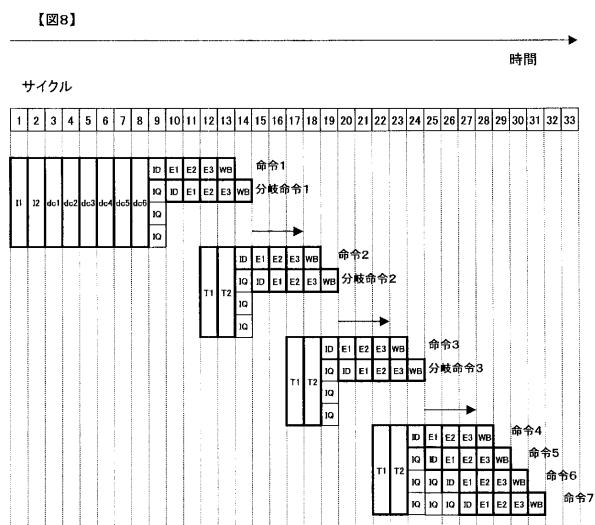

ここで、図 3 に示される構成によれば、図 8 に示されるように、命令の逐次読み出し時及び分岐命令発生時での命令コードの復号化処理オーバヘッドは隠蔽化されるものの、分岐命令発生時の分岐先命令読み出しに関するオーバヘッドは矢印で示されるように隠蔽化されない。これに対して図 7 に示される構成によれば、以下に詳述するように、命令コードの復号化によるオーバヘッドと、分岐命令発生時の分岐先命令読み出しに関するオーバヘッドとの両方を隠蔽化することができる。

30

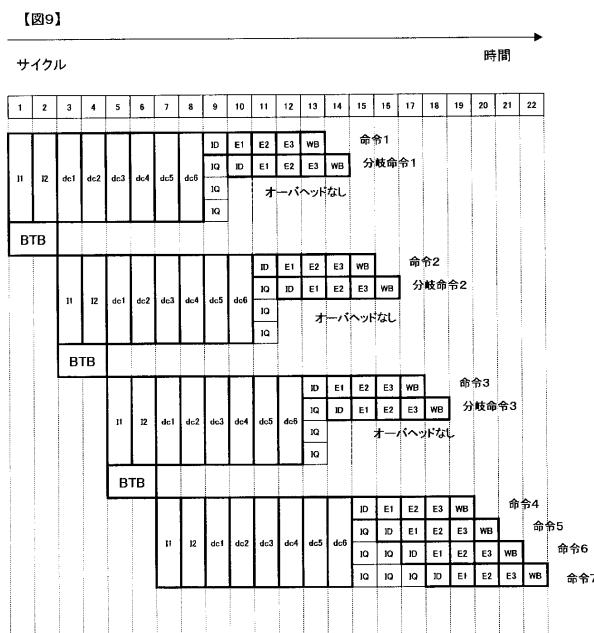

#### 【0044】

図 9 には、図 7 に示される構成における命令処理タイミングが示される。

#### 【0045】

命令 1 と分岐命令 1 はサイクル 1 及びサイクル 2 で命令キャッシュ 100 から読み出される。同時にサイクル 1 では分岐先アドレスバッファ 1400 が参照され、サイクル 2 では分岐命令 1 の分岐先アドレス (すなわち命令 2 の命令アドレス) が分岐先アドレスバッファ 1400 から出力される。サイクル 3 及びサイクル 4 では分岐先アドレスバッファ 1400 から出力された分岐命令 1 の分岐先アドレスにより命令 2 及び分岐命令 2 を命令キャッシュ 100 から読み出すとともに分岐先アドレスバッファ 1400 を参照し、サイクル 4 では分岐命令 2 の分岐先アドレス (すなわち命令 3 の命令アドレス) が分岐先アドレスバッファ 1400 から出力される。サイクル 5 及びサイクル 6 では分岐先アドレスバッ

40

50

ファ 1 4 0 0 から出力された分岐命令 2 の分岐先アドレスにより命令 3 及び分岐命令 3 が命令キャッシュ 1 0 0 から読み出されて分岐先アドレスバッファ 1 4 0 0 が参照され、サイクル 6 では分岐命令 3 の分岐先アドレス（すなわち命令 4 の命令アドレス）が分岐先アドレスバッファ 1 4 0 0 から出力される。サイクル 7 及びサイクル 8 では分岐先アドレスバッファ 1 4 0 0 から出力された分岐命令 3 の分岐先アドレスにより命令 4 から命令 7 までが命令キャッシュ 1 0 0 から読み出される。一方、命令 1 及び分岐命令 1 はサイクル 3 からサイクル 8 の間で復号化され、命令 1 はサイクル 9 に命令の解読が行われ、分岐命令 1 はサイクル 1 0 で解読される。命令 2 及び分岐命令 2 はサイクル 4 で命令キャッシュ 1 0 0 から読み出されているため、サイクル 5 からサイクル 1 0 の間で復号化され、命令 2 はサイクル 1 1 で命令の解読が行われ、分岐命令 2 はサイクル 1 2 で命令が解読される。

命令 3 及び分岐命令 3 はサイクル 6 で命令キャッシュ 1 0 0 から読み出されているため、サイクル 7 からサイクル 1 2 の間で復号化され、命令 3 はサイクル 1 3 で命令の解読が行われ、分岐命令 3 はサイクル 1 4 で解読される。命令 4 から命令 7 はサイクル 8 で命令キャッシュ 1 0 0 から読み出されているため、サイクル 9 からサイクル 1 4 の間で復号化され、命令 4 はサイクル 1 5 で解読され、命令 5 はサイクル 1 6 で解読され、命令 6 はサイクル 1 7 で解読され、命令 7 はサイクル 1 8 で解読される。このように分岐先アドレスバッファ 1 4 0 0 などの動的分岐予測機構によって投機的に命令フェッチを実行することにより、命令コードの復号化によるオーバヘッドと、分岐命令発生時の分岐先命令読み出しに関するオーバヘッドとの両方を隠蔽化することができる。

## 【0046】

10

以上本発明者によってなされた発明を具体的に説明したが、本発明はそれに限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

## 【0047】

例えば、命令キャッシュ 1 0 0 、命令コード復号化論理 3 0 0 、及び C P U 1 6 0 0 をそれぞれ別個の半導体チップにより形成することができる。

## 【0048】

以上の説明では主として本発明者によってなされた発明をその背景となった利用分野であるマイクロコンピュータに適用した場合について説明したが、本発明はそれに限定されるものではなく、各種データ処理装置に広く適用することができる。

## 【0049】

30

本発明は、C P U (中央処理装置)を含むことを条件に適用することができる。

## 【図面の簡単な説明】

## 【0050】

【図 1】本発明にかかるデータ処理装置の一例であるマイクロコンピュータにおける C P U の構成例ブロック図である。

【図 2】図 1 に示される構成の動作タイミング図である。

【図 3】上記マイクロコンピュータにおける C P U の別の構成例ブロック図である。

【図 4】図 3 に示される構成の動作タイミング図である。

【図 5】図 3 における主要部の構成例説明図である。

【図 6】図 3 における主要部の別の構成例説明図である。

40

【図 7】上記マイクロコンピュータにおける C P U の別の構成例ブロック図である。

【図 8】図 7 に示される構成の比較対象とされる構成の動作タイミング図である。

【図 9】図 7 に示される構成の動作タイミング図である。

【図 10】上記マイクロコンピュータの全体的な構成例ブロック図である。

## 【符号の説明】

## 【0051】

9 0 - 1 ~ 9 0 - 3 セレクタ

1 0 0 命令キャッシュ

2 0 0 バス

3 0 0 命令コード復号化論理

50

5 0 0 命令キュー

6 0 0 命令デコーダ

7 0 0 オペランドアドレス加算器

8 0 0 オペランドキャッシュ

9 0 0 オペランドデータ復号化論理

1 0 0 0 命令実行部

1 1 0 0 オペランドデータ暗号化論理

1 2 0 0 命令アドレス加算器

1 3 0 0 逐次命令フェッチアドレス生成論理

1 4 0 0 分岐先アドレスバッファ

1 5 0 0 メモリ

1 6 0 0 C P U

10

【図1】

【図1】

【図2】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

---

フロントページの続き

(72)発明者 小林 浩二

東京都小平市上水本町5丁目22番1号 株式会社日立超エル・エス・アイ・システムズ内

審査官 後藤 彰

(56)参考文献 特開2005-018434 (JP, A)

特開2004-246637 (JP, A)

特開2003-108442 (JP, A)

特開2001-142704 (JP, A)

特開平04-090027 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G 06 F 21 / 22

G 06 F 9 / 38